# RS-232C Interface with COP800

#### INTRODUCTION

This application note describes an implementation of the RS-232C interface with a COP888CG. The COP888CG 8-bit microcontroller features three 16-bit timer/counters, MICROWIRE/PLUS™ Serial I/O, multi-source vectored interrupt capability, two comparators, a full duplex UART, and two power saving modes (HALT and IDLE). The COP888CG feature set allows for efficient handling of RS-232C hardware handshaking and serial data transmission/reception.

### SYSTEM OVERVIEW

In this application, a COP888CG is connected to a terminal using the standard RS-232C interface. The serial port of the terminal is attached to the COP888CG interface hardware using a standard ribbon cable with DB-25 connectors on either end. The terminal keyboard transmits ASCII characters via the cable to the COP888CG interface. All characters received by the COP888CG are echoed back to the terminal screen. If the COP888CG detects a parity or framing error, it transmits an error message back to the terminal screen.

## HARDWARE DESCRIPTION

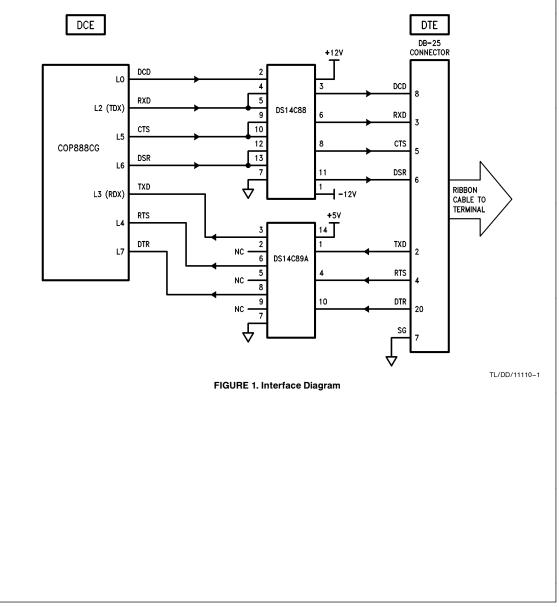

The COP888CG features used in this application include the user programmable UART, the 8-bit configurable L PORT, and vectored interrupts. In addition to the COP888CG, the RS-232C interface requires a DS14C88 driver and a DS14C89A receiver. The DS14C88 converts TTL/CMOS level signals to RS-232C defined levels and the DS14C89A does the opposite. *Figure 1* contains a diagram of the COP888CG interface hardware.

The COP888CG is configured as data communications equipment (DCE) and the terminal is assumed to be data terminal equipment (DTE). The following RS-232C signals are used to communicate between the COP888CG (DCE) and the terminal (DTE):

| RS-232C Signal Name       | Signal Origin |

|---------------------------|---------------|

| TxD (Transmit Data)       | DTE           |

| RxD (Receive Data)        | DCE           |

| CTS (Clear To Send)       | DCE           |

| RTS (Request To Send)     | DTE           |

| DSR (Data Set Ready)      | DCE           |

| DTR (Data Terminal Ready) | DTE           |

| DCD (Data Carrier Detect) | DCE           |

Five general purpose I/O pins on the COP888CG L PORT are used for the control signals CTS, DSR, DCD, RTS and DTR. Two additional L PORT pins are used for TxD and RxD. These two general purpose pins are configured for their alternate functions, UART transmit (TDX) and UART receive (RDX). According to the RS-232C interface standard, DCE transmits data to DTE on RxD and receives data from DTE on TxD. Therefore, the UART transmit data pin (TDX) is used for the RS-232C receive data signal (RxD) and the UART receive data pin (RDX) is used for the RS-232C transmit data signal (TxD). In this example, all handshaking between DCE and DTE is performed in hardware. National Semiconductor Application Note 739 Michelle Giles May 1991

IS-232C Interface with COP800

The terminal is setup to interface with the COP888CG by selecting the 9600 baud, 7 bits/character, odd parity and one stop bit options. The local echo back of characters is disabled to allow the COP888CG to perform the echo back function. The terminal is also configured to use the hard-ware control signals (CTS, DSR, RTS, DTR) for handshaking.

#### SOFTWARE DESCRIPTION

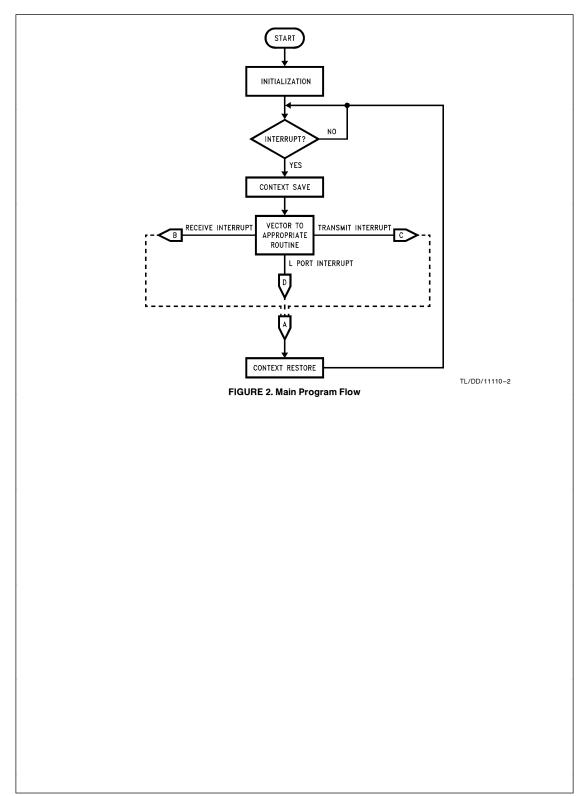

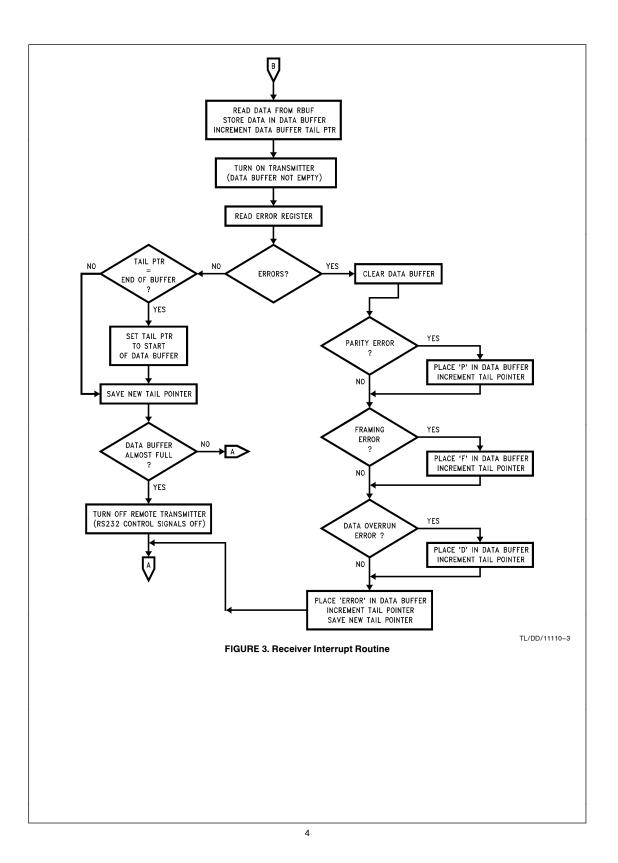

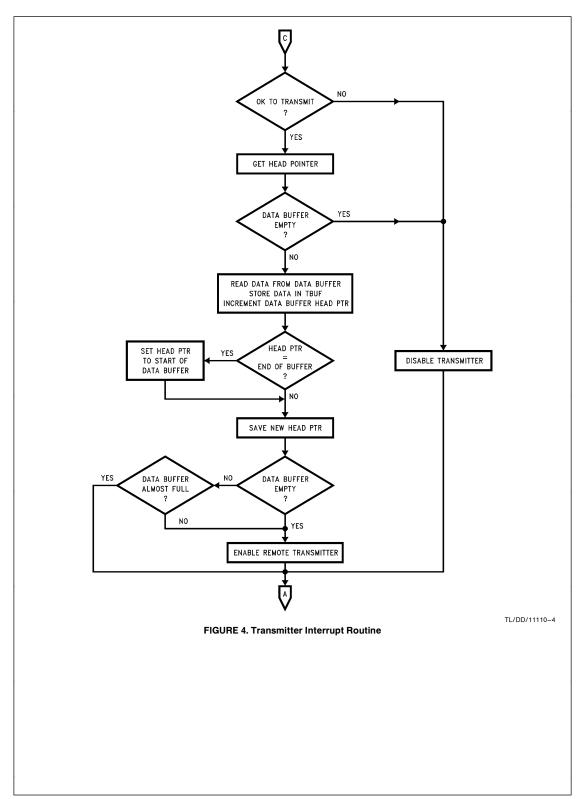

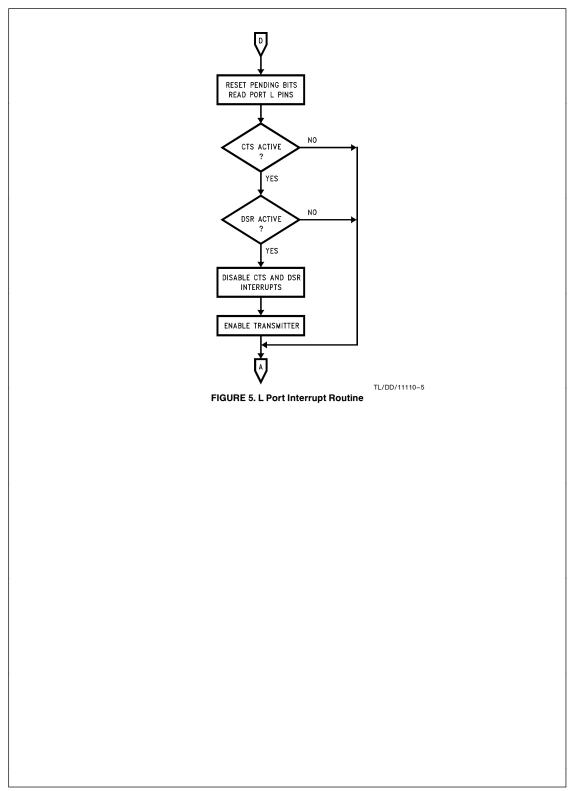

The software for this application consists of an initialization routine, several interrupt routines, and a disable routine. These routines handle RS-232C handshaking, transmitting and receiving of characters, error checking, and echoing back of received characters. *Figures 2* thru 5 contain flow-charts of the routines. The complete code is given at the end of this application note.

The initialization routine configures the UART, initializes the transmit/receive data buffer, and enables the 8-bit L PORT handling of RS-232C control signals. In this particular example, the UART is configured to operate at 9600 BAUD in full duplex, asynchronous mode. The framing format is chosen to be: 7 bits/character, odd parity, and one stop bit. Different baud rates, modes of operation, and framing formats may be selected by setting the ENUCMD, ENUICMD, BAUDVAL and PSRVAL constants located at the beginning of the code to alternative values. (Refer to the COP888CG data sheet or COP888 Family User's Manual for details on configuring the UART.) Each RS-232C control signal is assigned to an L PORT pin. Pins L0, L2, L5 and L6 are configured as outputs for the DCD, TxD, CTS and DSR signals, respectively. Pins L3, L4 and L7 are configured as inputs for TxD, RTS and DTR, respectively. The transmit/receive data buffer is a circular buffer whose location and size is selected by setting the START and END constants located at the beginning of the program. The initialization routine sets up the buffer based on these constants.

The interrupt routines respond to transmit buffer empty, receive buffer full, and L PORT interrupts. A generic context switching routine is used for entering and exiting all interrupts. This routine saves the contents of the accumulator, the PSW register and the B pointer before vectoring to the appropriate interrupt routine. It also restores the contents of saved registers before a return from interrupt is executed.

The UART transmitter interrupt is called when the transmit buffer empty flag (TBMT) is set. This routine checks for active RTS and DTR control signals. If both signals are active and there is data to be transmitted, a byte of data is loaded into the UART transmit buffer. Otherwise, the UART transmitter is disabled.

The L PORT interrupts are used to indicate an active-low transition of RTS and/or DTR. When both signals are active (the remote receiver is ready to accept data), this routine enables the UART transmitter.

The UART receiver interrupt routine is called when the receive buffer full flag (RBFL) is set. This routine reads the

AN-739

MICROWIRE/PLUS™ is a trademark of National Semiconductor Corporation.

© 1995 National Semiconductor Corporation TL/DD11110

RRD-B30M75/Printed in U.S.A

UART receive buffer and checks for errors. If no errors are detected, the incoming data is placed in the data buffer for echoing. If errors are detected, an error message is queued for transmission.

The receiver interrupt disables the remote transmitter by deactivating CTS whenever the transmit/receive data buffer is almost full. This action prevents the data buffer from overflowing. Note that CTS is turned off before the buffer is completely full to insure buffer space will exist for storing characters which are in the process of being sent when CTS is deactivated.

The disable routine clears the UART control registers, disables the L PORT interrupts, and de-activates the RS-232C control signals.

## CONCLUSION

The user configurable UART, multiple external interrupt capabilities, and vectored interrupt scheme of the COP888CG microcontroller allow for an efficient implementation of the RS-232C interface standard. This application note shows how the COP888CG may be configured for connection to a terminal using these features. However, the code for this application can be easily adapted to other applications requiring different baud rates or framing formats, connection to a modem (DCE), separate transmit and receive buffers, incoming command decoding and/or handling of character strings. The versatility of the RS-232C standard and the COP888CG provides a means to develop practical solutions for many applications.

NATIONAL SEMICONDUCTOR CORPORATION COP800 CROSS ASSEMBLER, REV:D1,12 OCT 88

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>14<br>15<br>16<br>7 |                                      | <pre>ito simulate an RS232 port isignals, echo back of rece iroutime called INIT initia iThe transmitting and recei iinterrupt routines. The UF iThe user must select value ithis code. i NOTES:</pre> | ines uses the COP888CG UART and several I/O pins<br>interface. The code handles hardware control<br>sived characters, and error checking. A single<br>alizes the UART and hardware control signals.<br>ving of characters is handled in several<br>ART is disabled by calling the DISABLE routine.<br>is for several constants before compiling<br>er is enabled only when the transmit/receive<br>oty and the appropriate RS232 control signals<br>receiver are present.<br>is always enabled. the remote transmitter<br>iiter is disabled whenever the transmit/<br>fer is full.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17<br>18<br>19<br>20<br>21<br>22                                                   | 0089                                 | ;Definition of Constants<br>ENUCMD = 089                                                                                                                                                               | ∛Value to put in the ENU register<br>∛Selects bits per char and parity option<br>∛DEFAULT = 081 (7 bits/char and odd parity)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 23<br>24<br>25<br>26<br>27<br>28<br>29                                             | 0020                                 | ENUICMD = 020                                                                                                                                                                                          | ;Value to put in the ENUI register<br>;Selects number of stop bits, uart clock option,<br>;sync/async option, xmit/rcv interrupt enable,<br>;and TDX pin enable<br>;DEFAULT = 023 ( 1 stop bit, internal BRG,<br>;async operation, no interrupt, and TDX enabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 20<br>31<br>32<br>34<br>35<br>36<br>38<br>39<br>41<br>42<br>43<br>45               | 0004<br>00C8                         | BAUDVAL = 04<br>PSRVAL = 0C8                                                                                                                                                                           | <pre>Baud rate divisor equals N - 1<br/>Baud rate prescalar<br/>Baud rate prescalar<br/>Baud rate prescalar<br/>Baud Divisor<br/>FC = CKI frequency<br/>N = Baud Divisor<br/>P = Prescalar<br/>GIVEN: CALCULATE: BAUDVAL: PSRVAL:<br/>CKI = 10MHz N = 5<br/>BR = 9600 P = 13 04 0CB<br/>GIVEN: N = 10<br/>BR = 4800 P = 13 09 0CB<br/>See tables in users manual for translation<br/>Sof N and P to BAUDVAL and PSRVAL<br/>See Tables in users manual for translation<br/>Sof N and P to BAUDVAL and PSRVAL<br/>See Tables in users manual for translation<br/>See Tables in Us</pre> |

| 46<br>47<br>48<br>49<br>50<br>51                                                   | 0010<br>001D<br>001E<br>001F<br>000E | START       =       010         END       =       01D         HEAD       =       01E         TAIL       =       01F         SIZE       =       0E                                                      | Beginning address of the xmit/rcv buffer<br>End address of the xmit/rcv buffer<br>RAM address where current head of buffer stored<br>RAM address where current tail of buffer stored<br>Size of transmit/receive data buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                    |                                      |                                                                                                                                                                                                        | TL/DD/11110-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| -                    |              |       |            | =  |                           |      |                                                                                |

|----------------------|--------------|-------|------------|----|---------------------------|------|--------------------------------------------------------------------------------|

| 52<br>53             | 0000<br>0005 |       | DCD<br>CTS | =  | 00<br>05                  |      | position of DCD signal on L port pins<br>position of CTS signal on L port pins |

| 54                   | 0007         |       | DTR        | =  | 07                        |      | position of DTR signal on L port pins                                          |

| 55                   | 0004         |       | RTS        | =  | 04                        |      | position of RTS signal on L port pins                                          |

| 56                   | 0006         |       | DSR        | =  |                           |      | position of DSR signal on L port pins                                          |

| 57                   | 0005         |       | ETDX       | =  | 05                        |      | position of TDX enable pin in ENUI                                             |

| 58                   | 0000         |       | TIE        | =  | 00                        | ∛Bit | position of TX interrupt enable bit                                            |

| 59                   | 0001         |       | RIE        | 20 | 01                        |      | position of RX interrupt enable bit                                            |

| 60                   | 0005         |       | PE         | =  | 05                        |      | position of parity error in ENUR                                               |

| 61                   | 0006         |       | FE         | Ŧ  | 06                        |      | position of framing error in ENUR                                              |

| 62<br>63<br>64<br>65 | 0007         |       | DOE        | =  | 07                        | iBit | position of data overrun error in ENUR                                         |

| 65<br>66<br>67       |              |       | . INCLD    | со | P888.INC                  |      |                                                                                |

| 68 0002              | 3008         | MAIN: | JSR        | IN | IT                        |      | ;INITIALIZE UART                                                               |

| 69 0004              |              |       | JÞ         | •  |                           |      | DO OTHER TASKS                                                                 |

| 70 0005              |              |       | JSR        |    | SABLE                     |      | DISABLE UART                                                                   |

| 71 0007<br>72<br>73  | FF           | INIT: | JP         | •  |                           |      | DO DTHER TASKS                                                                 |

| 74 0008              | 9FFF         | 1011. | LD         | в. | #PSW                      |      |                                                                                |

| 75 000A              |              |       | RBIT       |    | E, (B)                    |      | DISABLE ALL INTERRUPTS                                                         |

| 76 000B              |              |       | LD         |    | R,#00                     |      | JUART OFF (POWERDOWN)                                                          |

| 77 ØØØE              |              |       | LD         |    | RTLC, #065                |      | SET I/O                                                                        |

| 78 0011              | 9FDØ         |       | LD         | в, | #PORTLD                   |      | NOT READY TO RECEIVE                                                           |

| 79 0013              |              |       | SBIT       |    | R, [B]                    |      | TURN OFF DATA SET READY                                                        |

| 80 0014              |              |       | SBIT       |    | S, [B]                    |      | ; TURN OFF CLEAR TO SEND                                                       |

| 81 0015<br>82 0016   |              |       | RBIT<br>LD |    | D, [B]<br>AD, #START      |      | ; TURN ON DATA CARRIER DETECT<br>;INIT HEAD POINTER                            |

| 83 0019              |              |       | LD         |    | IL, #START                |      | INIT TALL POINTER                                                              |

| 84 001C              |              |       | LD         |    | #ICNTRL                   |      | CONFIGURE PORTL INTERRUPTS                                                     |

| 85 001E              |              |       | RBIT       |    | EN, [B]                   |      | DISABLE PORTL INTERRUPTS                                                       |

| 86 001F              |              |       | LD         |    | EDG, #090                 |      | ; SELECT FALLING EDGE FOR RTS AND DTR                                          |

| 87 0022              | BCC99Ø       |       | LD         | WK | EN, #090                  |      | ; ENABLE RTS AND DTR INTERRUPT                                                 |

| 88 0025              |              |       | LD         |    | PND, #00                  |      | CLEAR PORTL INTERRUPT PENDING FLAGS                                            |

| 89 0028              |              |       | SBIT       |    | EN, [B]                   |      | ; ENABLE PORT L INTERRUPTS                                                     |

| 90 0029              |              |       | LD         |    | U, #ENUCMD                |      | SELECT BITS/CHAR AND PARITY OPTION                                             |

| 91 0020              |              |       | LD         |    | UR, #00                   | un.  | ;CLEAR ERROR BITS<br>;SELECT CLOCK,INTERRUPTS,STOPBITS                         |

| 92 002F<br>93 0032   |              |       |            |    | UI, #ENUIC<br>UD, #BAUDV( |      | SETUP BRG                                                                      |

| 94 0035              |              |       | LD         |    | #ENUI                     | 16.  |                                                                                |

| 95 0037              |              |       | SBIT       |    | E, [B]                    |      | ;ENABLE TRANSMITTER INTERRUPT                                                  |

| 96 0038              |              |       | SBIT       |    | E, [B]                    |      | ENABLE RECEIVER INTERRUPT                                                      |

| 97 0039              |              |       | LD         | PS | R, #PSRVAL                |      | JUART DN                                                                       |

| 98 ØØ3C              |              |       | LD         |    | #PORTLD                   |      | READY TO RECEIVE                                                               |

| 99 ØØ3E              |              |       | RBIT       |    | R, [B]                    |      | TURN ON DATA SET READY                                                         |

| 100 003F             |              |       | RBIT       |    | S, [B]                    |      | ; TURN ON CLEAR TO SEND                                                        |

| 101 0040<br>102 0042 |              |       | LD<br>SBIT |    | #PSW<br>E,[B]             |      | SENABLE ALL INTERRUPTS                                                         |

|                      | 10           |       | 0011       |    | _,                        |      | TL/DD/11                                                                       |

NATIONAL SEMICONDUCTOR CORPORATION COP800 CROSS ASSEMBLER, REV: D1, 12 OCT 88 RET 103 0043 8E 104 DISABLE: 105 IDISABLE INTERRUPTS 106 0044 BDEF68 RBIT GIE, PSW STURN OFF HANDSHAKING SIGNALS SUART POWERDOWN SCLEAR WART CONTROL REGISTERS 107 0047 BCD061 PORTLD, #061 LD 108 004A BCBE00 LD PSR, #00 109 004D BCBA00 ENU, #00 LD 110 0050 BCBC00 LD ENUI, #00 111 0053 BCBB00 LD ENUR, #00 IDISABLE RTS AND DTR INTERRUPTS 112 0056 9FC9 113 0058 6C I D B, #WKEN RTS, [B] RBIT 114 0059 6F DTR, CB3 RBIT 115 005A BDEF78 SBIT GIE, PSW JENABLE INTERRUPTS 116 005D 8E RET 117 118 119 INTERRUPT ROUTINES 120 INTERRUPT START ADDRESS = 0FF ØØFF 121 122 ØØFF 67 PUSH A CONTEXT SAVE 123 0100 9DFE LD A, B 124 0102 67 125 0103 9DEF PUSH Α A, PSW LD 126 0105 67 127 0106 B4 128 0107 8C PUSH A VIS REST: A CONTEXT RESTORE POP 129 0108 9CEF A, PSW Х 130 010A 8C POP Α 131 010B 9CFE 132 010D 8C ¥ A, B POP A 133 010E 8F RETI 134 135 FORT L INTERRUPTS 136 137 ; The port L interrupts are used to indicate a return to active ; state of the DTR and RTS signals from the remote receiver. ; If both DTR and RTS are active, the remote receiver is ready ; to accept data and the CDP transmitter is enabled. 138 139 140 141 FORT L INTERRUPT LINT: 142 143 010F BCCA00 WKPND, #00 RESET PENDING BITS LD 144 0112 9DD2 LD A, PORTLP READ PORT L PINS FREE FORT L FINS FIF RTS (ACTIVE LOW) NOT PRESENT THEN REMOTE NOT READY TO RECEIVE 145 0114 6010 IFBIT #RTS, A 146 0116 06 147 0117 6080 JP NOTRDY IFBIT #DTR, A FIF DTR (ACTIVE LOW) NOT PRESENT 148 0119 03 JP NOTRDY THEN REMOTE NOT READY TO RECEIVE 149 Ø11A 9FBC READY: LD B, #ENUI 150 0110 78 SBIT TIE, (B) REST FRE-ENABLE TRANSMITTER INTERRUPT 151 Ø11D E9 NOTRDY: JP SEXIT INTERRUPT 152 153 TL/DD/11110-8 NATIONAL SEMICONDUCTOR CORPORATION COP800 CROSS ASSEMBLER, REV:D1, 12 OCT 88

| 4                            |         |                                                                              | INTERRUPT                                             | the following                                               |             |  |  |  |

|------------------------------|---------|------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|-------------|--|--|--|

| 5                            | ; The l | The UART receive interrupt does the following:<br>1. Reads the received data |                                                       |                                                             |             |  |  |  |

| 7                            | ;       | 2. Checks for receiver errors                                                |                                                       |                                                             |             |  |  |  |

| 8                            | ;       |                                                                              | 3. If no errors detected, places the received data in |                                                             |             |  |  |  |

| 9                            | ;       | the                                                                          | transmit/receive but                                  | ffer and enables the transmitter.                           |             |  |  |  |

| 0                            | ţ       |                                                                              |                                                       | transmit/receive buffer is cleared                          |             |  |  |  |

| 1                            | ;       | ofi                                                                          | ALL data and an errow                                 | message is placed in the data buffer.                       |             |  |  |  |

| 2                            | RCVINT: |                                                                              | 0 7011                                                | RECEIVER INTERRUPT                                          |             |  |  |  |

| 3 011E 9D1F<br>4 0120 9CFE   |         | LD<br>X                                                                      | A, TAIL<br>A, B                                       | GET TAIL POINTER                                            |             |  |  |  |

| 5 0122 9D89                  |         | ĹD                                                                           | A, RBUF                                               | FREAD RECEIVED DATA                                         |             |  |  |  |

| 6 0124 A2                    |         | x                                                                            | A, [B+]                                               | STORE RECEIVED DATA                                         |             |  |  |  |

| 7 Ø125 9DBB                  |         | LD                                                                           | A, ENUR                                               | READ ERROR REGISTER                                         |             |  |  |  |

| 8 0127 BDBC78                |         | SBIT                                                                         | TIE, ENUI                                             | SENABLE TRANSMITTER INTERRUPT                               |             |  |  |  |

| 9 012A 60E0                  |         | ANDSZ                                                                        | A, #0E0                                               | CHECK FOR PE, DOE, FE                                       |             |  |  |  |

| 0 012C 1A                    |         | JP                                                                           | ERROR                                                 | THROW DATA AWAY IN BUFFER                                   |             |  |  |  |

| 1 012D 9DFE<br>2 012F 921E   |         | LD<br>IFEQ                                                                   | A, B<br>A, #END+1                                     | ILOAD ACC WITH NEW TAIL PTR                                 |             |  |  |  |

| 3 0131 9810                  |         | LD                                                                           | A, #START                                             | SET TAIL PTR TO START OF BUFFER                             |             |  |  |  |

| 4 0133 9C1F                  |         | x                                                                            | A, TAIL                                               | SAVE TAIL PTR                                               |             |  |  |  |

| 5 0135 9D1E                  |         | ĹD                                                                           | A, HEAD                                               | IS DATA BUFFER FULL?                                        |             |  |  |  |

| 6 Ø137 A1                    |         | SC                                                                           | •                                                     |                                                             |             |  |  |  |

| 7 Ø138 BD1F81                |         | SUBC                                                                         | A, TAIL                                               | ;A = HEAD - TAIL                                            |             |  |  |  |

| 8 013B 89                    |         | IFNC                                                                         |                                                       | ;IF BORROWED (TAIL ) HEAD)                                  |             |  |  |  |

| 9 013C 940E                  |         | ADD                                                                          | A, #SIZE                                              | THEN ADD BUFFER SIZE TO RESULT                              |             |  |  |  |

| 0 013E 9303                  |         | IFGT                                                                         | A,#03                                                 | IF DATA BUFFER NOT FULL                                     |             |  |  |  |

| 1 0140 2107                  | RXOFF:  | JMP                                                                          | REST                                                  | ; THEN EXIT INTERRUPT<br>; ELSE TURN OFF REMOTE TRANSMITTER |             |  |  |  |

| 2 0142 BDD07D<br>3 0145 2107 | RXUFF:  | JMP                                                                          | CTS, PORTLD<br>REST                                   | EXIT INTERRUPT                                              |             |  |  |  |

| 4                            | ERROR:  | JUP                                                                          | KCD1                                                  | JEXIT INTERROFT                                             |             |  |  |  |

| 5 0147 BC1E10                | Ennon:  | LD                                                                           | HEAD, #START                                          | CLEAR BUFFER                                                |             |  |  |  |

| 6 014A 9F10                  |         | LD                                                                           | B, #START                                             | POINT TO START OF BUFFER                                    |             |  |  |  |

| 7 014C 6020                  |         | IFBIT                                                                        | PE,A                                                  |                                                             |             |  |  |  |

| 8 014E 9A50                  |         | LD                                                                           | [B+],#'P'                                             | ;P = PARITY                                                 |             |  |  |  |

| 9 0150 6040                  |         | IFBIT                                                                        | FE,A                                                  |                                                             |             |  |  |  |

| 0 0152 9A46                  |         | LD                                                                           | [B+],#'F'                                             | ;F = FRAMING                                                |             |  |  |  |

| 1 0154 6080                  |         | IFBIT                                                                        | DOE, A                                                |                                                             |             |  |  |  |

| 2 0156 9844                  |         | LD                                                                           | [B+], #'D'                                            | ;D = DATA OVERRUN<br>;BLANK SPACE                           |             |  |  |  |

| 3 0158 9A20<br>4 015A 9A45   |         | LD<br>LD                                                                     | [B+],#020<br>[B+],#'E'                                | BLHMA BPHCE                                                 |             |  |  |  |

| 5 015C 9A52                  |         | LD                                                                           | [B+],#'R'                                             |                                                             |             |  |  |  |

| 6 015E 9A52                  |         | LD                                                                           | [B+], #'R'                                            |                                                             |             |  |  |  |

| 7 0160 9A4F                  |         | LD                                                                           | [B+],#'O'                                             |                                                             |             |  |  |  |

| 8 Ø162 9A52                  |         | LD                                                                           | [B+], #'R'                                            |                                                             |             |  |  |  |

| 9 0164 9A0A                  |         | LD                                                                           | EB+],#ØA                                              | ILINE FEED                                                  |             |  |  |  |

| 0 0166 9A0D                  |         | LD                                                                           | [B+],#0D                                              | CARRIAGE RETURN                                             |             |  |  |  |

| 1 0168 9DFE                  | OUTERR: |                                                                              | A, B                                                  | SAVE NEW TAIL PTR                                           |             |  |  |  |

| 2 016A 9C1F                  |         | X<br>JMP                                                                     | A, TAIL                                               |                                                             |             |  |  |  |

| 13 016C 2107<br>14           |         | JINP                                                                         | REST                                                  |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             | TL/DD/11110 |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

|                              |         |                                                                              |                                                       |                                                             |             |  |  |  |

NATIONAL SEMICONDUCTOR CORPORATION COP800 CROSS ASSEMBLER, REV: D1, 12 OCT 88

228 018D 09 229 018E A1

231 0192 89

232 0193 940E

238 Ø19F 2107

239 240

241 242 Ø1A1 B5

244 245

246

247

249

252

254

JUART TRANSMIT INTERRUPT The UART transmit interrupt does the following: : 1. Checks for RTS and DTR signals (OK to transmit?) If DK to transmit and buffer not empty, transmits data.

If not DK to transmit or buffer empty, disables transmitter. ; XMITINT: TRANSMITTER INTERRUPT LD A, PORTLP A, #090 IS IT OK TO TRANSMITT? ANDS7 IDLE IND: GO TURN OFF TRANSMITTER JMP YES: GET PTR TO DATA LD A, HEAD 217 0176 BD1F82 218 0179 219C A, TAIL IDLE IF DATA BUFFER EMPTY IFEG THEN TURN OFF TRANSMITTER JMP FLSE А, В X LD A, [B+] GET TRANSMIT DATA X A, TBUF LD ILDAD ACC WITH NEW HEAD PTR A.B A, #END+1 IF END OF DATA BUFFER IFEQ SET HEAD PTR TO START OF BUFFER LD A, #START 225 Ø186 9C1E A, HEAD х 226 Ø188 9D1E A, HEAD IS DATA BUFFER FULL? LD 227 Ø18A BD1F82 IFEQ A, TAIL IF BUFFER EMPTY THEN NOT FULL ELSE CHECK HOW FULL JP NFULL SC ;A = HEAD - TAIL ;IF BORROWED (TAIL ) HEAD) ;THEN ADD BUFFER SIZE TO RESULT 230 018F BD1F81 SUBC A, TAIL IFNC A, #SIZE A, #03 ADD 233 0195 9303 IF DATA BUFFER NOT FULL IFGT 234 0197 BDD06D NFULL: CTS, PORTLD THEN TURN ON REMOTE TRANSMITTER RBIT 235 019A 2107 JMP REST : ELSE EXIT INTERRUPT 236 019C 9FBC 237 019E 68 IDLE: B, #ENUI TIE, (B) LD RBIT IDISABLE TRANSMITTER INTERRUPT JMP REST SEXIT INTERRUPT Software Trap SFTINT: RPND RESTART 243 01A2 2000 JMP. ØØ VECTOR INTERRUPT TABLE .=01E2 Ø1F2 248 01E2 010F ADDRW LINT IL PORT INTERRUPT Ø1EC .=01EC 250 01EC 016E . ADDRW . ADDRW XMITINT TRANSMITTER INTERRUPT 251 Ø1EE Ø11E RCVINT 01FE .=01FE 253 Ø1FE Ø1A1 . ADDRW SFTINT SOFTWARE INTERRUPT/TRAP . END

TL/DD/11110-10

**AN-**739

| NATIONAL SEMICONDUCT<br>COP800 CROSS ASSEMBL                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL TABLE                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| CTS         0005           DSR         0006           ENUCMD         0089           ERROR         0147           HEAD         001E           LINT         010F           NOTRDY         011D           PORTLD         0000           PSW         00EF           REST         0107           SFTINT         01A1           TAIL         001F | BAUD         Q0BD           DCD         Q0Q0           DTR         Q0Q7           ENUI         Q0BC           ETDX         Q0Q5           ICNTRL         Q0E8           LPEN         Q0Q6           QUTERR         Q168           PORTLP         Q0D9           RBUF         Q0B9           RIE         Q0Q1           SIZE         Q0Q6           TBUF         Q0B8           WKPND         Q0CA | BAUDVA         0004           DISABL         0044           END         001D           ENUICM         0020           FE         0006           IDLE         019C           MAIN         0005           PE         0005           PSR         008E           RCVINT         0114           SP         007D           TIE         0000           X         00FC | CNTRL 00EE<br>DOE 0007<br>ENU 00BA<br>ENUR 00BB<br>GIE 0000<br>INIT 000B<br>* NFULL 0197<br>PORTLC 00D1<br>PSRVAL 00C8<br>READY 011A<br>RXOFF 0142<br>START 0010<br>WKEDG 00C8<br>XMITIN 016E | *                                                                                                                                                                                                        | TL/DD/11110-11                                                                                                                                                                                               |

| NATIONAL SEMICONDUCT<br>COP800 CROSS ASSEMBL                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| MACRO TABLE                                                                                                                                                                                                                                                                                                                                 | ER, REVIDI, 12 001 00                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| ND WARNING LINES                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| NO ERROR LINES                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| 267 ROM BYTES USE                                                                                                                                                                                                                                                                                                                           | D                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| SOURCE CHECKSUM = 680<br>OBJECT CHECKSUM = 090                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| INPUT FILE C:UART.<br>LISTING FILE C:UART.<br>OBJECT FILE C:UART.                                                                                                                                                                                                                                                                           | PRN                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               | TL/DD/11110-12                                                                                                                                                                                           |                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| LIFE SUPPORT POL                                                                                                                                                                                                                                                                                                                            | ICY                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| NATIONAL'S PRODU<br>DEVICES OR SYSTE<br>SEMICONDUCTOR C                                                                                                                                                                                                                                                                                     | CTS ARE NOT AU<br>MS WITHOUT THE                                                                                                                                                                                                                                                                                                                                                                  | EXPRESS WRI                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                               |                                                                                                                                                                                                          |                                                                                                                                                                                                              |

| into the body, or (b<br>failure to perform,<br>with instructions fo                                                                                                                                                                                                                                                                         | ces or systems ar<br>are intended for s<br>) support or sustain l<br>when properly used<br>r use provided in the<br>acted to result in a s                                                                                                                                                                                                                                                        | urgical implant<br>life, and whose<br>in accordance<br>e labeling, can                                                                                                                                                                                                                                                                                        | support device of be reasonably e                                                                                                                                                             | ponent is any compo<br>or system whose failure<br>xpected to cause the<br>or system, or to affe                                                                                                          | e to perform can<br>failure of the life                                                                                                                                                                      |

| National Semiconductor<br>Corporation<br>2000 Semiconductor Drive<br>P.O. Box 56000<br>Santa Clara, CA 95052-80<br>Tel: 1(800) 272-9959<br>TWX: (910) 339-9240                                                                                                                                                                              | D-82256 Fürstenfeldbruck<br>90 Germany<br>Tel: (81-41) 35-0<br>Telex: 527649<br>Fax: (81-41) 35-1                                                                                                                                                                                                                                                                                                 | National Semiconductor<br>Japan Ltd.<br>Sumitomo Chemical<br>Engineering Center<br>Bldg. 7F<br>1-7-1, Nakase, Mihama-Ku<br>Chiba-Ciry,<br>Ciba Prefecture 261<br>Tel: (043) 299-2500<br>Fax: (043) 299-2500                                                                                                                                                   | National Semiconductor<br>Hong Kong Ltd.<br>13th Ficor, Straight Block,<br>Ocean Centre, 5 Canton Rd.<br>Tsimshatsiu, Kowloon<br>Hong Kong<br>Tei: (852) 2737-1600<br>Fax: (852) 2736-9960    | National Semiconductores<br>Do Brazil Ltda.<br>Rue Deputado Lacorda Franco<br>120-3A<br>Sao Paulo-SP<br>Brazil 05418-000<br>Tel: (55-11) 212-5066<br>Telex: 391-1131931 NSBR BR<br>Fax: (55-11) 212-1181 | National Semiconductor<br>(Australia) Pty, Ltd.<br>Building 16<br>Business Park Drive<br>Monash Business Park<br>Nottinghill, Melbourne<br>Victoria 3168 Australia<br>Tel: (3) 558-9999<br>Fax: (3) 558-9998 |