# ▼ MOTOROLA MULTIMEDIA DEVICE DATA

# Multimedia

**Device Data**

| Selection Guides                         | 1 |

|------------------------------------------|---|

| Data Sheets                              | 2 |

| Evaluation Kits                          | 3 |

| Application Notes and Technical Articles | 4 |

| Glossary                                 | 5 |

| Handling and Design Guidelines           | 6 |

| Quality and Reliability                  | 7 |

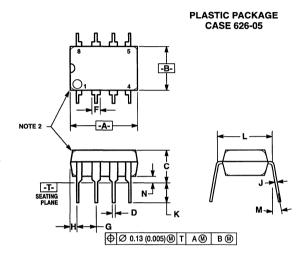

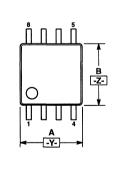

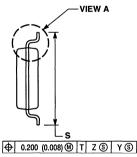

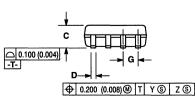

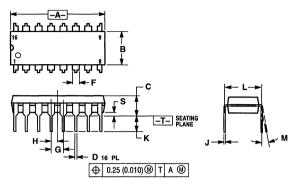

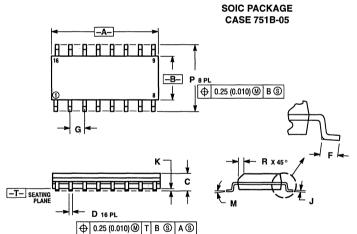

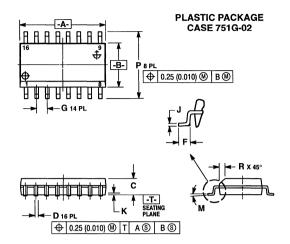

| Mechanical Data                          | 8 |

### **DATA CLASSIFICATION**

### **Product Preview**

This heading on a data sheet indicates that the device is in the formative stages or under development at the time of printing of this data book. Please check with Motorola for current status. The disclaimer at the bottom of the first page reads: "This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice."

### Advance Information

This heading on a data sheet indicates that the device is in sampling, preproduction, or first production stages at the time of printing of this data book. Please check with Motorola for updated information. The disclaimer at the bottom of the first page reads: "This document contains information on a new product. Specifications and information herein are subject to change without notice."

### Fully Released

A fully released data sheet contains neither a classification heading nor a disclaimer at the bottom of the first page. This document contains information on a product in full production. Guaranteed limits will not be changed without written notice to your local Motorola Semiconductor Sales Office.

### Technical Summary

The Technical Summary is an abridged version of the complete device data sheet that contains the key technical information required to determine the correct device for a specific application. Complete device data sheets for these more complex devices are available from your Motorola Semiconductor Sales Office or authorized distributor.

|  | , |  |  |

|--|---|--|--|

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

|  |   |  |  |

# Multimedia

## **Device Data**

Motorola offers a broad range of semiconductor multimedia products for a wide variety of applications. The *Motorola Multimedia Device Data Book* is a new book that contains specifications on these parts as well as information on Evaluation Kits, a selection of Application Notes, Handling and Design Guidelines, and Reliability and Quality information. Functional and Technical Selection Guides are also included to help you select the appropriate part for your application.

New Motorola multimedia devices are being introduced continually. For the latest releases, additional technical information, and pricing, please contact your nearest Motorola Semiconductor Sales Office or authorized distributor. A complete listing of sales offices and authorized distributors is included at the back of this book.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and @are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 1995 "All Rights Reserved" Printed in U.S.A.

Some of the terms in the glossary originally appeared in the book *Video Demystified* by Keith Jack and are reprinted by permission of Brooktree Corporation and HighText Publications, Inc.

### **TABLE OF CONTENTS**

### **CHAPTER 1 — SELECTION GUIDES**

| <b>Functional Selection Gui</b>                                                                                                                                            | des                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1–3                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A/D and D/A Converters .                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 1–3                                                                                                                                                                                                                  |

| CD-i Parts                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 1–3                                                                                                                                                                                                                  |

| Chroma Delay Lines                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 1–3                                                                                                                                                                                                                  |

| Comb Filters                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–3                                                                                                                                                                                                                    |

| Deflection                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–3                                                                                                                                                                                                                    |

| Encoders/Modulators                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 1–3                                                                                                                                                                                                                  |

| Sound                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–3                                                                                                                                                                                                                    |

| Transistor Arrays                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–4                                                                                                                                                                                                                    |

| Video and Audio Amplifiers                                                                                                                                                 | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1–4                                                                                                                                                                                                                    |

| Video Processors/Demodu                                                                                                                                                    | ılators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1–4                                                                                                                                                                                                                    |

|                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                        |

| Discontinued/Not Recomm                                                                                                                                                    | nended For New Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1–4                                                                                                                                                                                                                    |

|                                                                                                                                                                            | les                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                        |

| A/D and D/A Converters .                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–5                                                                                                                                                                                                                    |

| CD-i Parts                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–5                                                                                                                                                                                                                    |

| Chroma Delay Lines                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–5                                                                                                                                                                                                                    |

|                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                        |

| Encoders/Modulators                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–6                                                                                                                                                                                                                    |

| Video and Audio Amplifiers                                                                                                                                                 | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1–6                                                                                                                                                                                                                    |

| Other Functions                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–6                                                                                                                                                                                                                    |

|                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                        |

| CHAPTER 2 — DATA 9                                                                                                                                                         | CHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                        |

|                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                        |

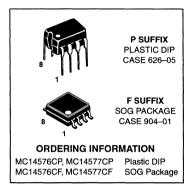

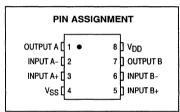

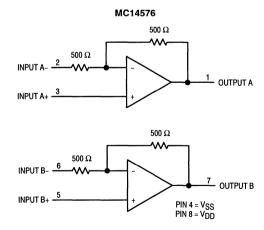

| MC14576C                                                                                                                                                                   | Dual Video Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2–3                                                                                                                                                                                                                    |

|                                                                                                                                                                            | Dual Video Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                        |

| MC14576C<br>MC14577C<br>MC44131                                                                                                                                            | Dual Video Amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2–3                                                                                                                                                                                                                    |

| MC14577C                                                                                                                                                                   | Dual Video Amplifier Improved Stereoton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2–3<br>. 2–11                                                                                                                                                                                                          |

| MC14577C<br>MC44131                                                                                                                                                        | Dual Video Amplifier Improved Stereoton Chroma Delay Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2–3<br>. 2–11<br>. 2–23                                                                                                                                                                                                |

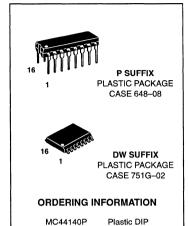

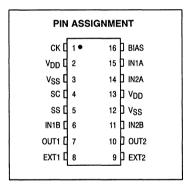

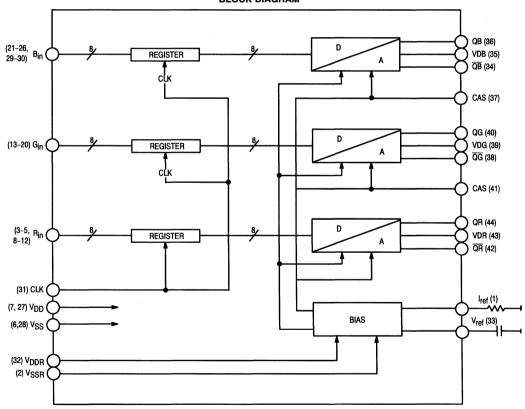

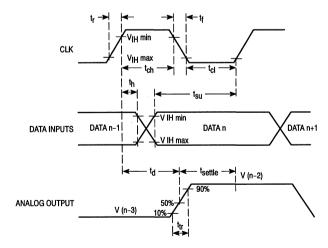

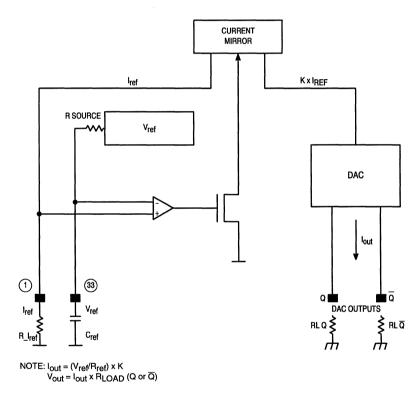

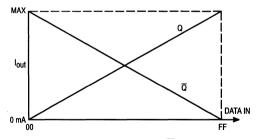

| MC14577C<br>MC44131<br>MC44140                                                                                                                                             | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2–3<br>. 2–11<br>. 2–23<br>. 2–34                                                                                                                                                                                      |

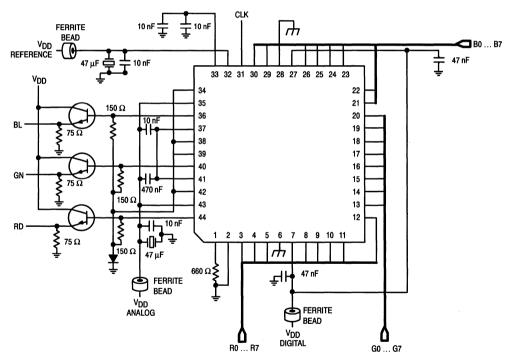

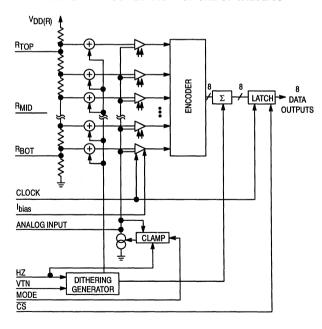

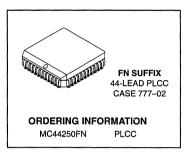

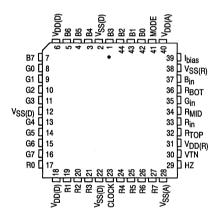

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250                                                                                                                       | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2–3<br>. 2–11<br>. 2–23<br>. 2–34<br>. 2–44                                                                                                                                                                            |

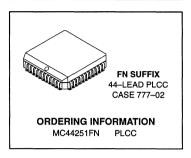

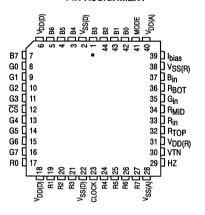

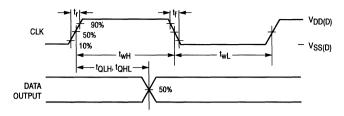

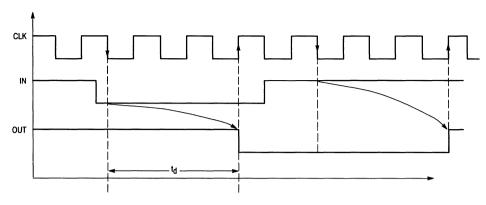

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250<br>MC44251                                                                                                            | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2–3<br>. 2–11<br>. 2–23<br>. 2–34<br>. 2–44<br>. 2–60                                                                                                                                                                  |

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250<br>MC44251<br>MC44701                                                                                                 | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder                                                                                                                                                                                                                                                                                                                                                                                                                   | 2–3<br>. 2–11<br>. 2–23<br>. 2–34<br>. 2–44<br>. 2–60<br>. 2–76                                                                                                                                                        |

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250<br>MC44251                                                                                                            | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder                                                                                                                                                                                                                                                                                                                                                                               | 2-3<br>. 2-11<br>. 2-23<br>. 2-34<br>. 2-44<br>. 2-60<br>. 2-76                                                                                                                                                        |

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250<br>MC44251<br>MC44701<br>MC44702<br>MC141543                                                                          | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display                                                                                                                                                                                                                                                                                                                                            | . 2–3<br>. 2–11<br>. 2–23<br>. 2–34<br>. 2–44<br>. 2–60<br>. 2–76<br>. 2–77                                                                                                                                            |

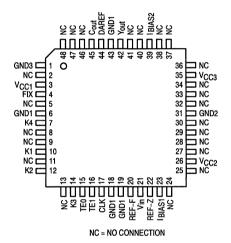

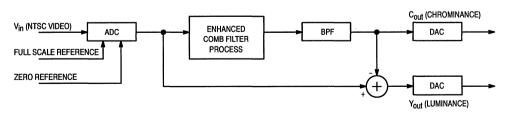

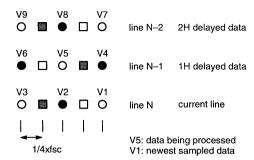

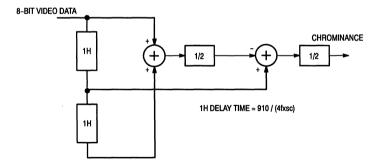

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250<br>MC44251<br>MC44701<br>MC44702<br>MC141543<br>MC141620                                                              | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter                                                                                                                                                                                                                                                  | 2–3<br>. 2–11<br>. 2–23<br>. 2–34<br>. 2–44<br>. 2–60<br>. 2–76<br>. 2–78<br>. 2–91                                                                                                                                    |

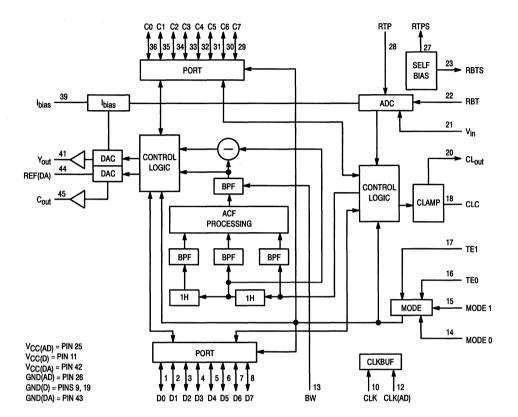

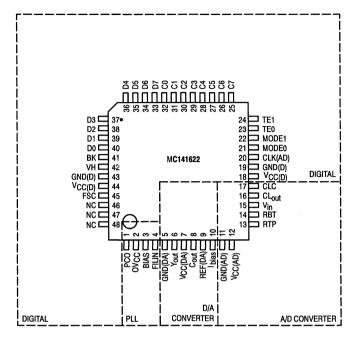

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250<br>MC44251<br>MC44701<br>MC44702<br>MC141543<br>MC141620<br>MC141621A                                                 | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF)                                                                                                                                                                                                                                                                                            | 2–3<br>. 2–11<br>. 2–23<br>. 2–34<br>. 2–44<br>. 2–60<br>. 2–76<br>. 2–78<br>. 2–91<br>. 2–99                                                                                                                          |

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250<br>MC44251<br>MC44701<br>MC44702<br>MC141543<br>MC141620<br>MC141621A<br>MC141621A                                    | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF) Advanced Comb Filter - II (ACF-II)                                                                                                                                                                                                                                                         | 2–3<br>. 2–11<br>. 2–23<br>. 2–34<br>. 2–44<br>. 2–60<br>. 2–77<br>. 2–78<br>. 2–91<br>. 2–99<br>2–116                                                                                                                 |

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250<br>MC44251<br>MC44701<br>MC44702<br>MC141543<br>MC141620<br>MC141621A<br>MC141621A                                    | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF) Advanced Comb Filter - II (ACF-II) Advanced Comb Filter - I (ACF-II)                                                                                                                                                                                                                       | 2–3<br>. 2–11<br>. 2–23<br>. 2–34<br>. 2–44<br>. 2–60<br>. 2–76<br>. 2–78<br>. 2–91<br>. 2–99<br>2–116<br>2–130                                                                                                        |

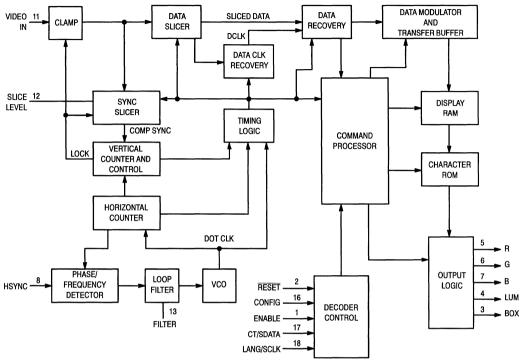

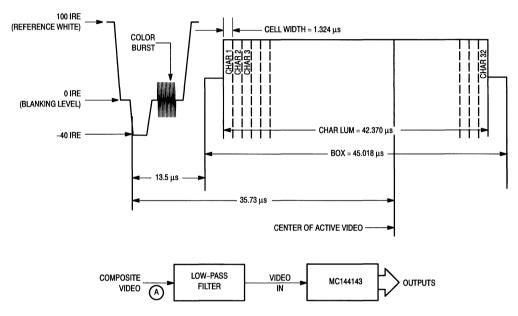

| MC14577C<br>MC44131<br>MC44140<br>MC44200<br>MC44250<br>MC44251<br>MC44701<br>MC44702<br>MC141543<br>MC141620<br>MC141621A<br>MC141622<br>MC141624<br>MC141624<br>MC141624 | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter - II (ACF-II) Advanced Comb Filter - II (ACF-II) Closed Caption Decoder                                                                                                                                                                                                                          | 2–3<br>. 2–11<br>. 2–23<br>. 2–34<br>. 2–44<br>. 2–60<br>. 2–76<br>. 2–77<br>. 2–91<br>. 2–99<br>2–116<br>2–130<br>2–142                                                                                               |

| MC14577C MC44131 MC44140 MC44200 MC44250 MC44251 MC44701 MC44702 MC141543 MC141620 MC141621A MC141622 MC141624 MC144143 MC144144                                           | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF) Advanced Comb Filter - II (ACF-II) Closed Caption Decoder Enhanced Closed Caption Decoder                                                                                                                                                              | 2-3<br>. 2-11<br>. 2-23<br>. 2-34<br>. 2-44<br>. 2-60<br>. 2-77<br>. 2-78<br>. 2-91<br>. 2-99<br>2-116<br>2-130<br>2-142<br>2-159                                                                                      |

| MC14577C MC44131 MC44140 MC44200 MC44250 MC44251 MC44701 MC44702 MC141543 MC141620 MC141621A MC141622 MC141624 MC144143 MC144144 MC145073                                  | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF) Advanced Comb Filter - II (ACF-II) Advanced Comb Filter - I (ACF-II) Closed Caption Decoder Enhanced Closed Caption Decoder Stereo Audio Sigma-Delta ADC                                                                                               | 2-3<br>. 2-11<br>. 2-23<br>. 2-34<br>. 2-44<br>. 2-60<br>. 2-76<br>. 2-78<br>. 2-91<br>. 2-99<br>2-116<br>2-130<br>2-142<br>2-159<br>2-160                                                                             |

| MC14577C MC44131 MC44140 MC44200 MC44250 MC44251 MC44701 MC44702 MC141543 MC141620 MC141621A MC141622 MC141624 MC144143 MC144144                                           | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF) Advanced Comb Filter - II (ACF-II) Advanced Comb Filter - I (ACF-I) Closed Caption Decoder Enhanced Closed Caption Decoder Stereo Audio Sigma—Delta ADC Stereo Audio Sigma—Delta DAC                                                                                | 2-3<br>. 2-11<br>. 2-23<br>. 2-34<br>. 2-44<br>. 2-60<br>. 2-76<br>. 2-78<br>. 2-91<br>. 2-99<br>2-116<br>2-130<br>2-142<br>2-159<br>2-160<br>2-174                                                                    |

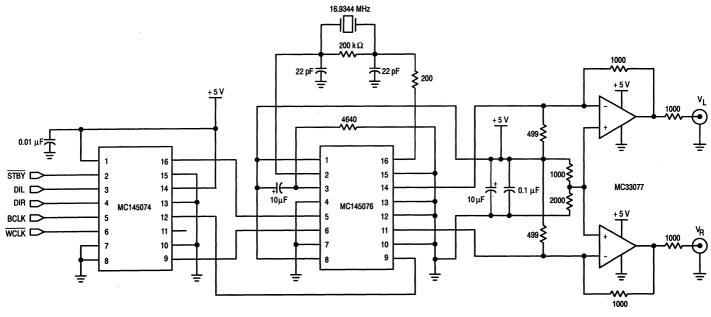

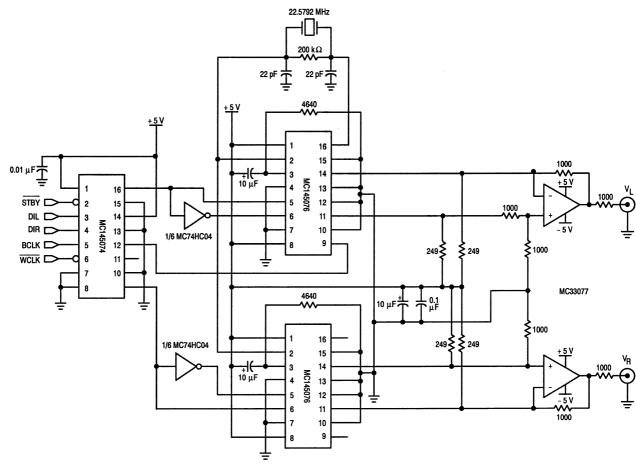

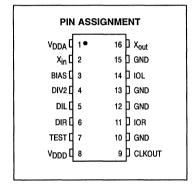

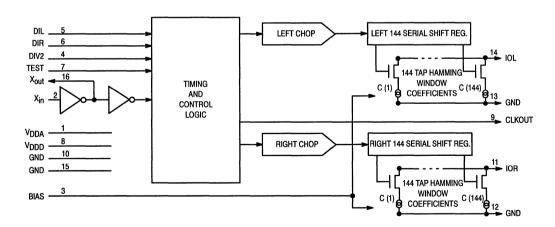

| MC14577C MC44131 MC44140 MC44200 MC44250 MC44251 MC44701 MC44702 MC141543 MC141620 MC141624 MC141624 MC141627 MC141624 MC141644 MC145073 MC145073 MC145074 MC145076        | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF) Advanced Comb Filter - II (ACF-II) Advanced Comb Filter - I (ACF-II) Closed Caption Decoder Enhanced Closed Caption Decoder Stereo Audio Sigma—Delta ADC Stereo Audio FIR Smoothing Filter                                                                          | 2-3<br>. 2-11<br>. 2-23<br>. 2-34<br>. 2-44<br>. 2-60<br>. 2-76<br>. 2-78<br>. 2-91<br>2-130<br>2-142<br>2-159<br>2-160<br>2-174<br>2-174                                                                              |

| MC14577C MC44131 MC44140 MC44200 MC44250 MC44251 MC44701 MC44702 MC141543 MC141620 MC141621A MC141624 MC141624 MC141624 MC145073 MC145074 MC145076 MCD212                  | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF) Advanced Comb Filter - II (ACF-II) Advanced Comb Filter - I (ACF-II) Closed Caption Decoder Enhanced Closed Caption Decoder Stereo Audio Sigma-Delta ADC Stereo Audio Sigma-Delta DAC Stereo Audio Fils Smoothing Filter Video Decoder and System Controller (JTAG) | 2-3<br>. 2-11<br>. 2-23<br>. 2-34<br>. 2-46<br>. 2-76<br>. 2-77<br>. 2-99<br>2-113<br>2-145<br>2-159<br>2-174<br>2-174<br>2-174<br>2-194                                                                               |

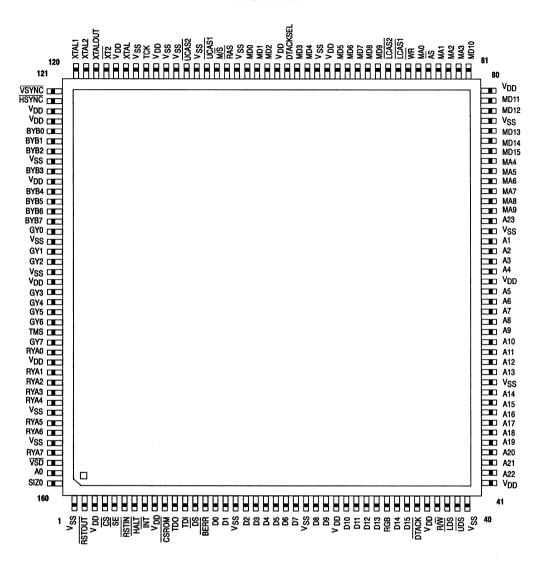

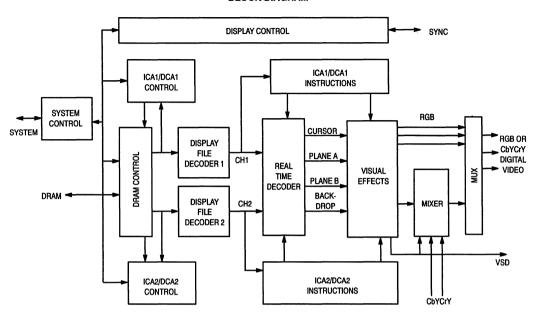

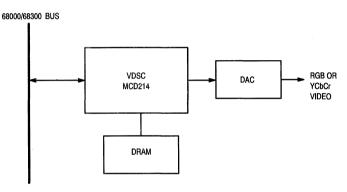

| MC14577C MC44131 MC44140 MC44200 MC44250 MC44251 MC44701 MC44702 MC141543 MC141620 MC141621A MC141624 MC141624 MC144143 MC144144 MC145073 MC145076 MCD212 MCD214           | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF) Advanced Comb Filter – II (ACF-II) Advanced Comb Filter – II (ACF-I) Closed Caption Decoder Enhanced Closed Caption Decoder Stereo Audio Sigma-Delta ADC Stereo Audio Sigma-Delta DAC Stereo Audio FIR Smoothing Filter Video Decoder and System Controller (VDSC)  | 2-3<br>. 2-11<br>. 2-23<br>. 2-34<br>. 2-44<br>. 2-66<br>. 2-77<br>. 2-78<br>. 2-91<br>. 2-99<br>2-116<br>2-159<br>2-159<br>2-159<br>2-174<br>2-187<br>2-194<br>2-194<br>2-207                                         |

| MC14577C MC44131 MC44140 MC44200 MC44250 MC44251 MC44701 MC44702 MC141543 MC141620 MC141621A MC141624 MC141624 MC141624 MC145073 MC145074 MC145076 MCD212                  | Dual Video Amplifier Improved Stereoton Chroma Delay Line Triple 8-Bit Video DAC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Triple 8-Bit Video ADC Three-State Outputs Multistandard Digital Video Encoder Multistandard Digital Video Encoder Advanced Monitor On-Screen Display Enhanced Comb Filter Advanced Comb Filter (ACF) Advanced Comb Filter - II (ACF-II) Advanced Comb Filter - I (ACF-II) Closed Caption Decoder Enhanced Closed Caption Decoder Stereo Audio Sigma-Delta ADC Stereo Audio Sigma-Delta DAC Stereo Audio Fils Smoothing Filter Video Decoder and System Controller (JTAG) | 2-3<br>2-11<br>2-23<br>2-34<br>2-44<br>2-60<br>2-76<br>2-77<br>2-78<br>2-91<br>2-99<br>2-116<br>2-159<br>2-160<br>2-174<br>2-189<br>2-189<br>2-199<br>2-199<br>2-199<br>2-199<br>2-199<br>2-2-189<br>2-2-189<br>2-2-27 |

MOTOROLA TABLE OF CONTENTS

### **CHAPTER 3 — EVALUATION KITS**

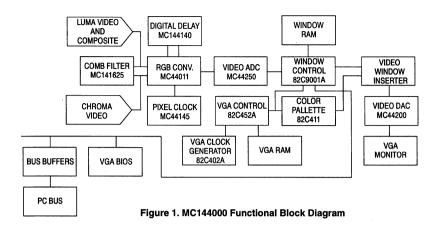

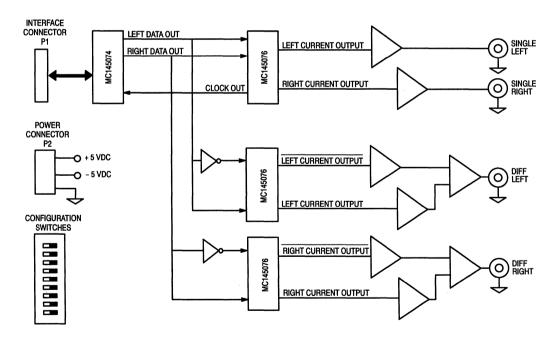

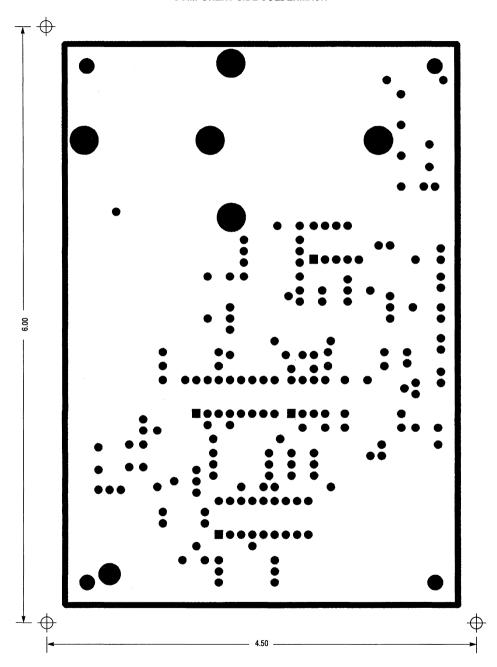

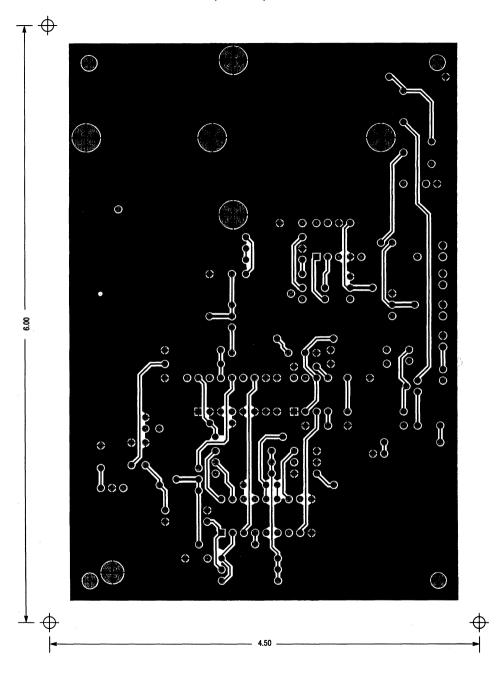

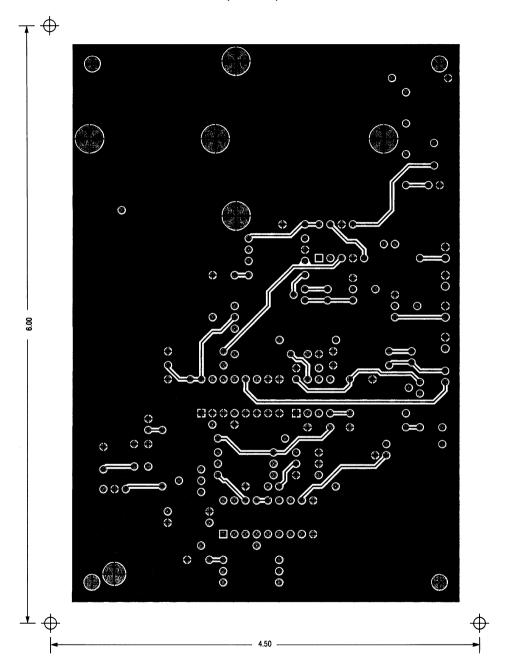

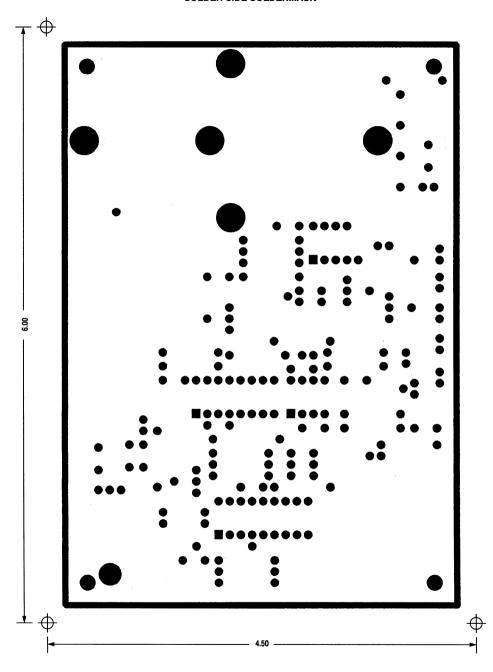

| MC141522EVK<br>MC144000EVK<br>MC145074EVK | ACF-II Evaluation Board Operating Manual 3-3 PC Video Capture Evaluation Kit 3-10 Stereo Audio Sigma-Delta DAC Evaluation Board 3-12 |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 4 — APP                           | LICATION NOTES AND TECHNICAL ARTICLES                                                                                                |

| AN1235<br>AN1244<br>AR361                 | A Set Top Closed–Caption Decoder                                                                                                     |

| CHAPTER 5 — GLC                           | SSARY                                                                                                                                |

| Terms and Abbreviation Useful Addresses   | ns                                                                                                                                   |

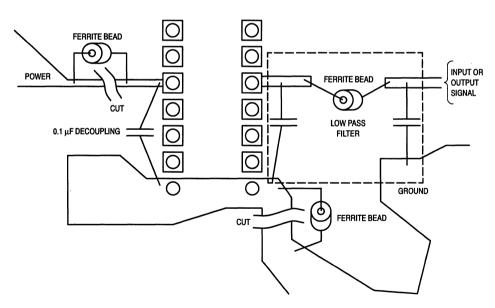

| CHAPTER 6 — HAN                           | DLING AND DESIGN GUIDELINES6-1                                                                                                       |

| CHAPTER 7 — QUA                           | LITY AND RELIABILITY7–1                                                                                                              |

| CHAPTER 8 — MEC                           | PHANICAL DATA                                                                                                                        |

| SALES OFFICES                             |                                                                                                                                      |

# **Selection Guides**

MOTOROLA SELECTION GUIDES

1-1

### **FUNCTIONAL SELECTION GUIDE**

This selection guide includes all Motorola devices characterized in this book. Other devices also used in multimedia applications, but associated with other product families, appear in the following documents.

Title

| DL111/D                                                                                                                                                            | Bipolar Power Transistor Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DL128/D                                                                                                                                                            | Linear and Interface ICs Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SG73/D                                                                                                                                                             | Master Selection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SG169/D                                                                                                                                                            | MOS Digital–Analog IC Quarterly Update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CA                                                                                                                                                                 | Data Sheets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MC                                                                                                                                                                 | Data Sheets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TDA                                                                                                                                                                | Data Sheets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1DA                                                                                                                                                                | Data Sticets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| A/D AND D/A CONVE                                                                                                                                                  | RTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Device #                                                                                                                                                           | Function Page #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MC10319                                                                                                                                                            | Single Channel A/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MC10321                                                                                                                                                            | Single Channel A/D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MC10322                                                                                                                                                            | Single Channel 8-Bit Video DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MC10324                                                                                                                                                            | Single Channel 8–Bit Video DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MC44200                                                                                                                                                            | Triple 8–Bit Video DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MC44250                                                                                                                                                            | Triple 8-Bit Video ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                    | Triple 8-Bit Video ADC Three-State Outputs 2-76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MC44251                                                                                                                                                            | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MC145073                                                                                                                                                           | Stereo Audio Sigma-Delta ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MC145074                                                                                                                                                           | Stereo Audio Sigma-Delta DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MC145076                                                                                                                                                           | Stereo Audio FIR Smoothing Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

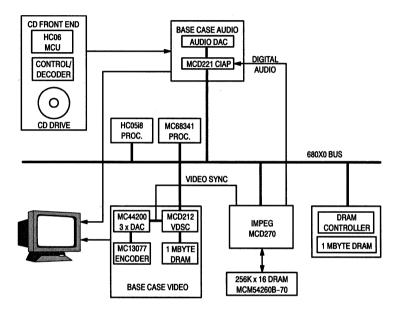

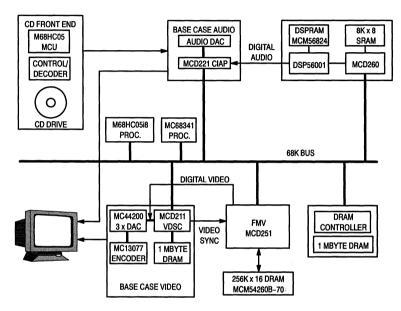

| CD-i                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Device #                                                                                                                                                           | Function Page #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DOVICE II                                                                                                                                                          | · -g- ··                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MCD212                                                                                                                                                             | Video Decoder and System Controller / ITAG) 2_104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MCD212                                                                                                                                                             | Video Decoder and System Controller (JTAG)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MCD214                                                                                                                                                             | Video Decoder and System Controller (VDSC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

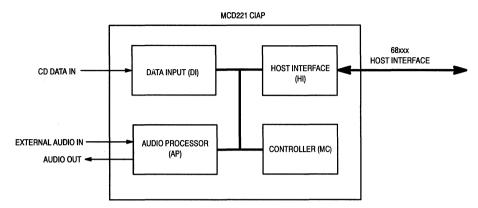

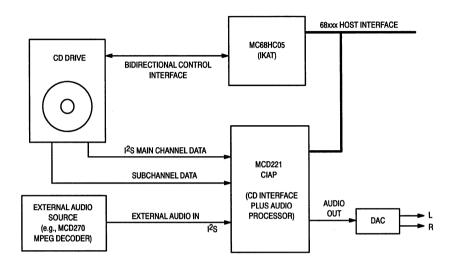

| MCD214<br>MCD221                                                                                                                                                   | Video Decoder and System Controller (VDSC)       2–207         CD-Interface and Audio Processor (CIAP)       2–218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

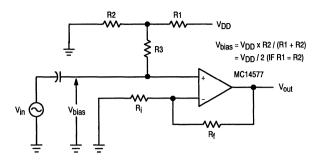

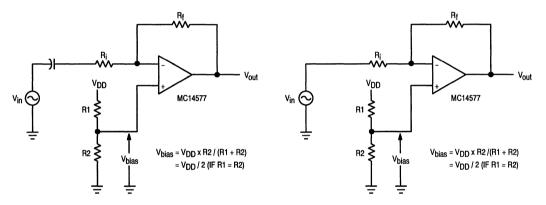

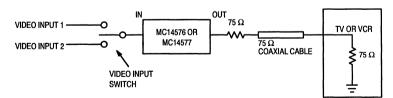

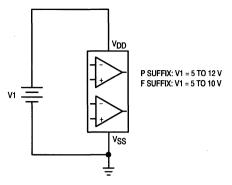

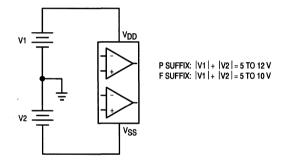

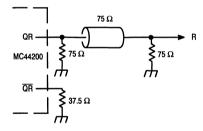

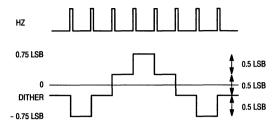

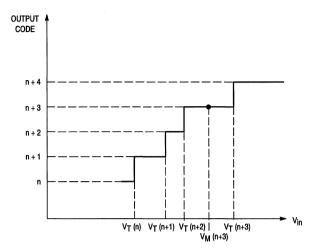

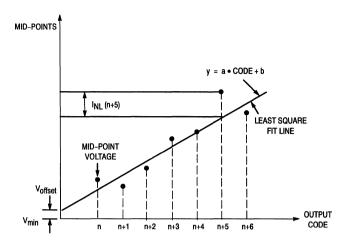

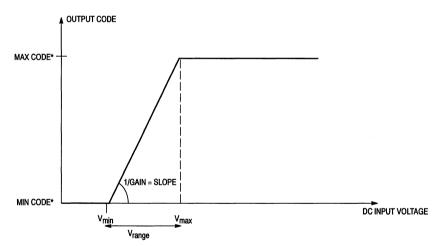

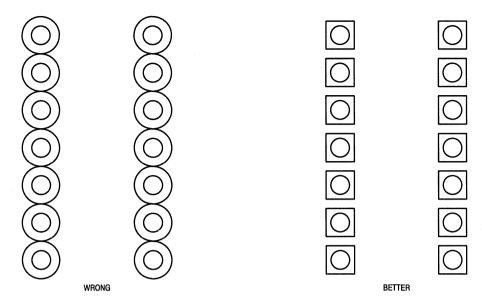

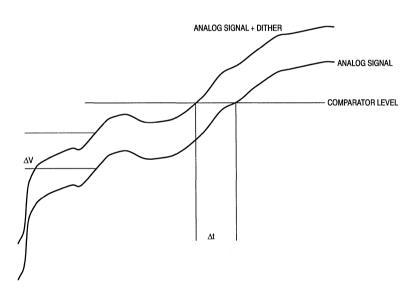

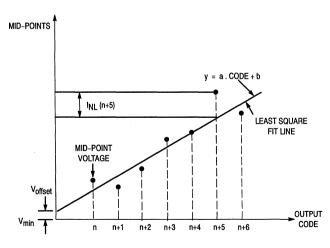

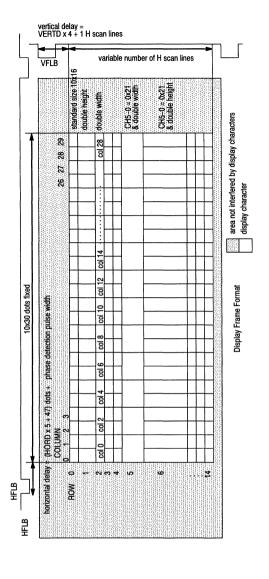

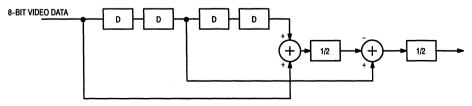

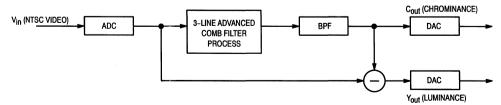

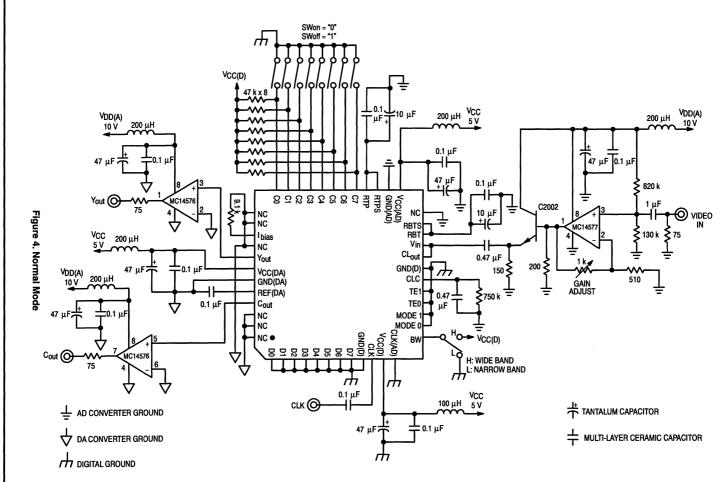

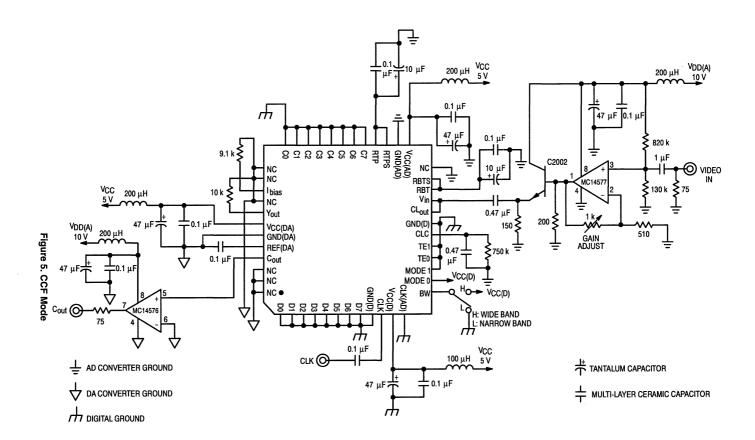

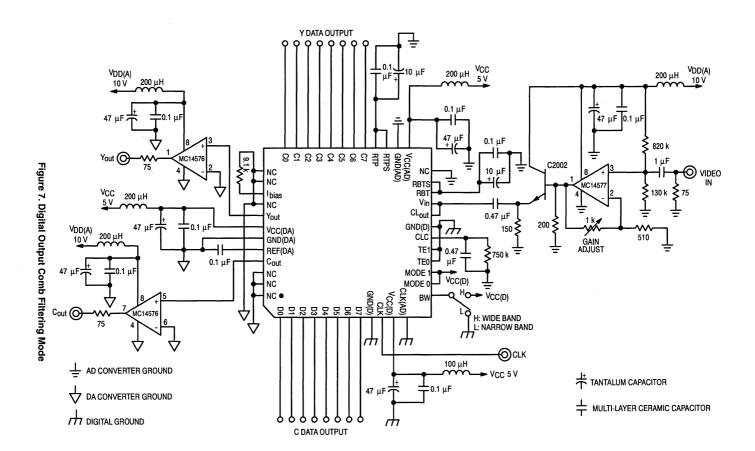

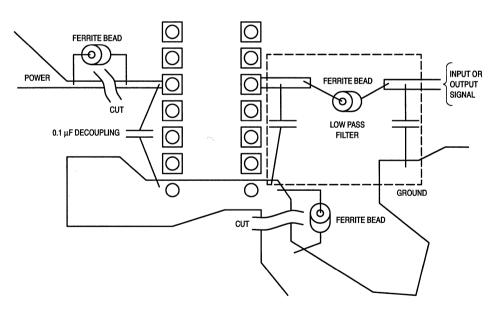

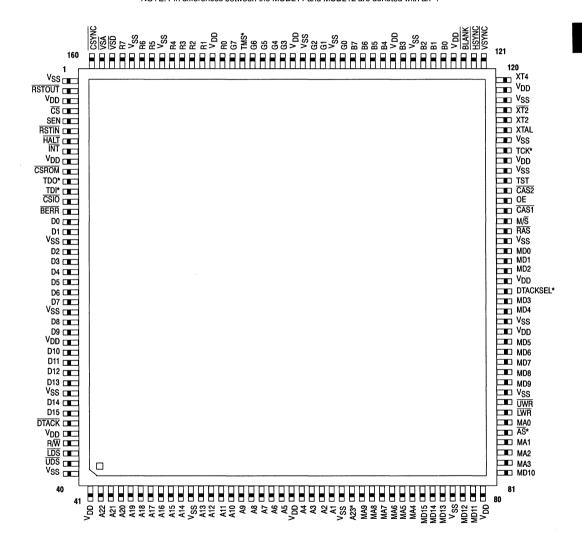

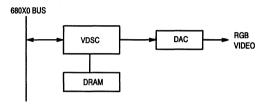

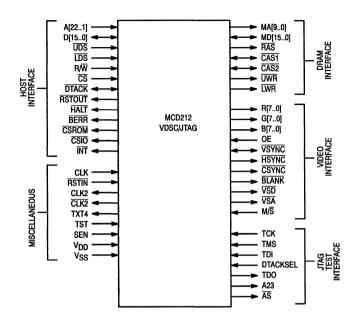

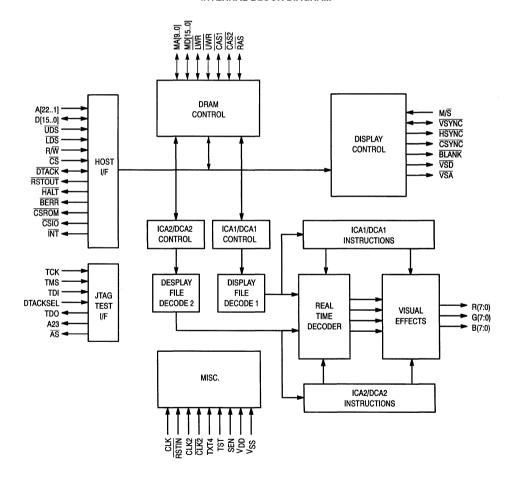

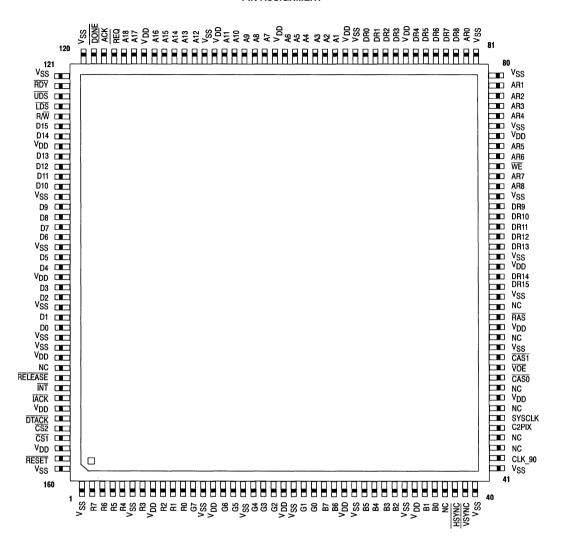

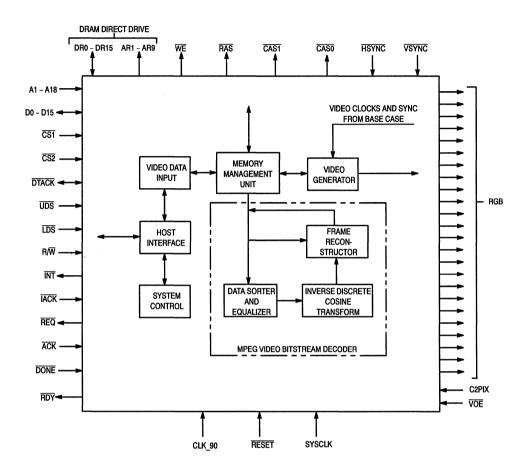

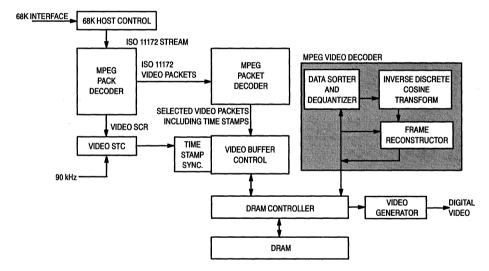

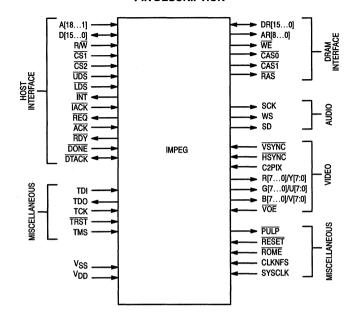

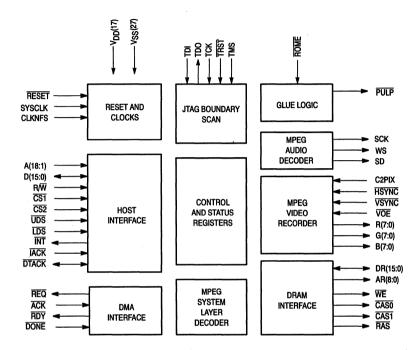

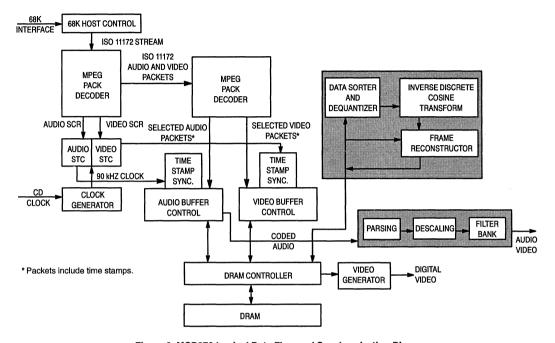

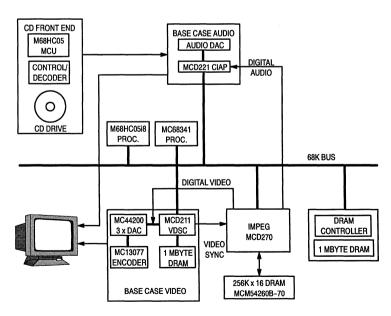

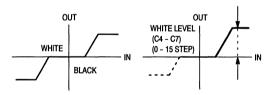

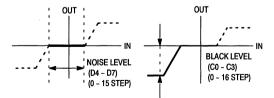

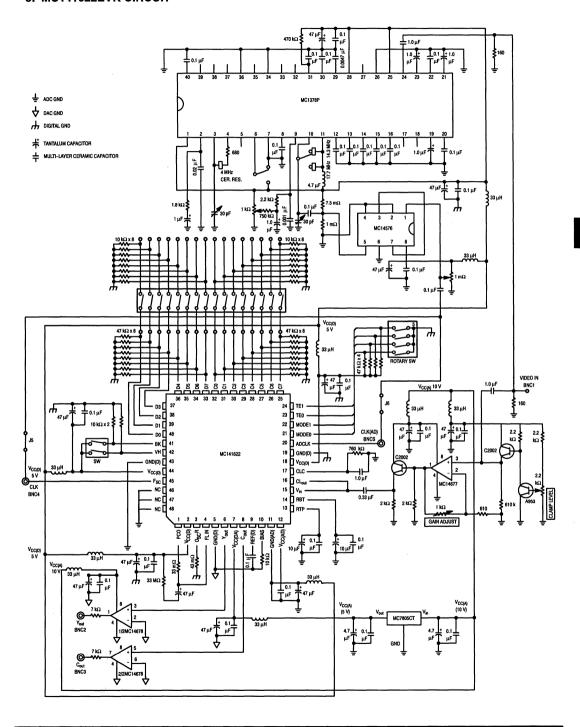

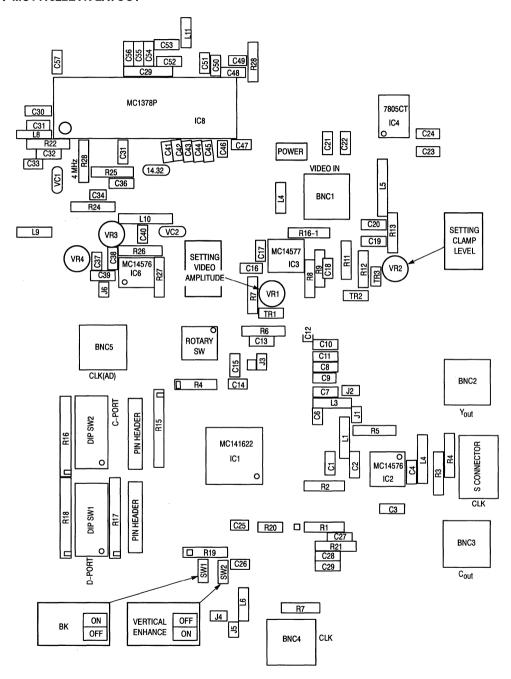

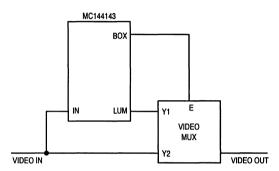

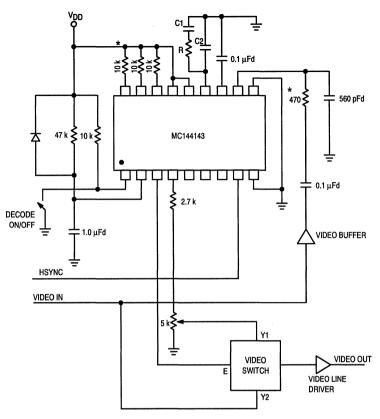

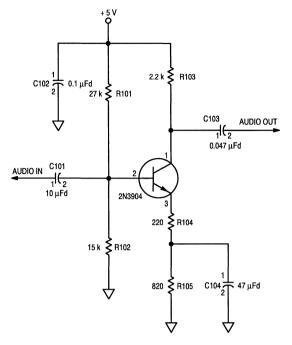

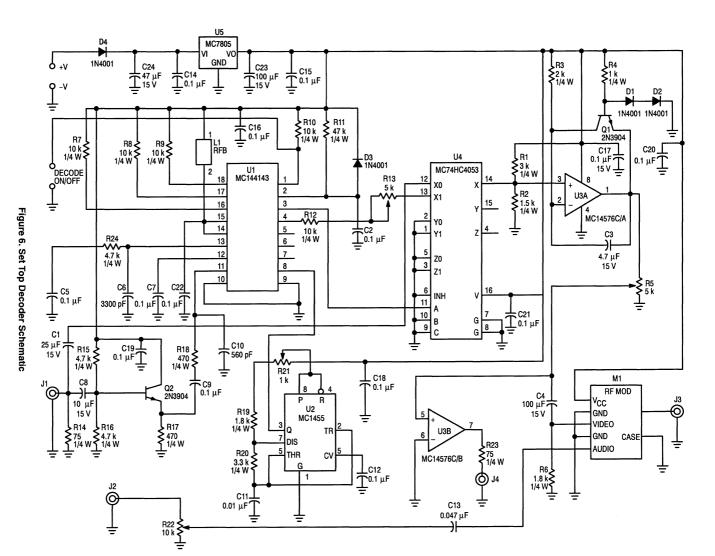

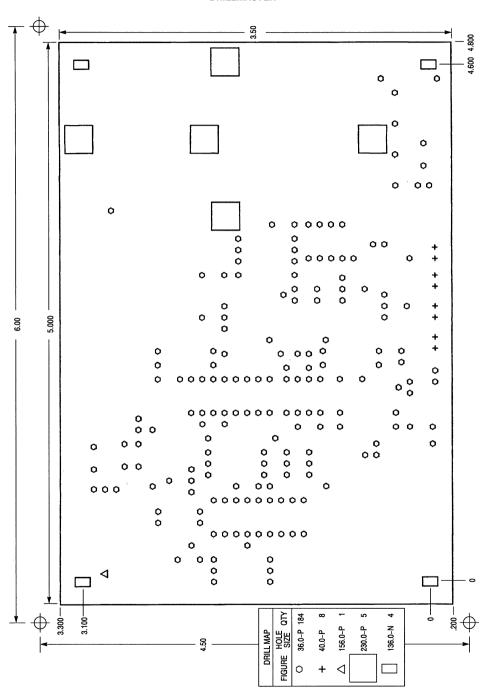

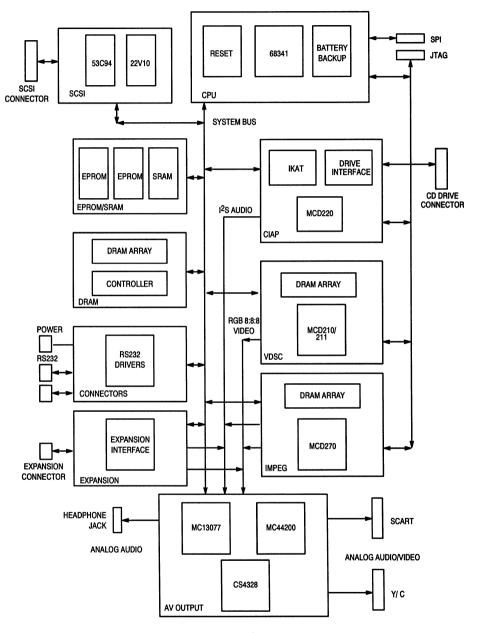

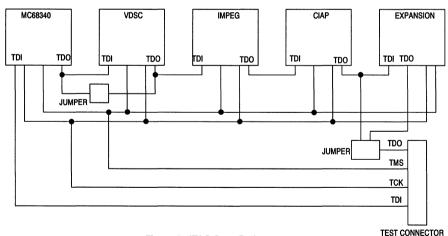

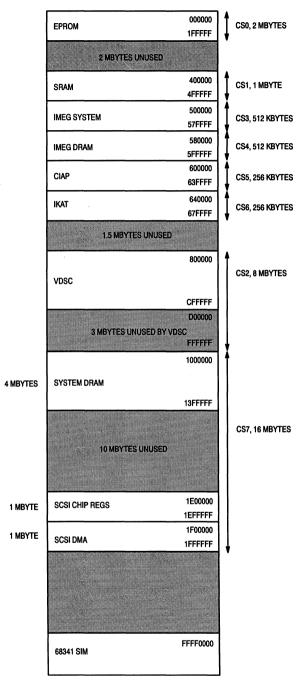

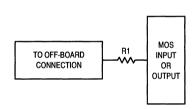

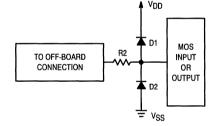

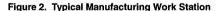

| MCD214<br>MCD221<br>MCD251                                                                                                                                         | Video Decoder and System Controller (VDSC)       2–207         CD-Interface and Audio Processor (CIAP)       2–218         MPEG Full Motion Video Decoder (FMV)       2–226                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |