MOTOROLA

DL156/D REV 1

## **Fast Static RAM** BiCMOS, CMOS, and Module Data

#### DATA CLASSIFICATION

#### **Product Preview**

This heading on a data sheet indicates that the device is in the formative stages or in design (under development). The disclaimer at the bottom of the first page reads: "This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice."

#### Advance Information

This heading on a data sheet indicates that the device is in sampling, preproduction, or first production stages. The disclaimer at the bottom of the first page reads: "This document contains information on a new product. Specifications and information herein are subject to change without notice."

#### Fully Released

A fully released data sheet contains neither a classification heading nor a disclaimer at the bottom of the first page. This document contains information on a product in full production. Guaranteed limits will not be changed without written notice to your local Motorola Semiconductor Sales Office.

BurstRAM, DSPRAM, and ParityRAM are trademarks of Motorola, Inc. SPARC is a registered trademark of SPARC International, Inc. i486 is a trademark of Intel Corp.

### **Fast Static RAM** BiCMOS, CMOS, and Module Data

Motorola offers a broad range of fast SRAMs for virtually any digital data processing system application. This data book contains complete specifications for individual FSRAM circuits in data sheet form, as well as an explanation of Motorola's reliability and quality program and an applications section.

For information on Dynamic RAM devices, please refer to DL155/D. For information on Military Memory devices, please refer to DL144/D.

New Motorola memories are being introduced continually. For the latest releases, additional technical information, and pricing, please contact your nearest authorized Motorola distributor or Motorola Sales Office. A complete listing of distributors and sales offices is included at the back of this book.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 1993 Previous Edition © 1992 "All Rights Reserved"

Printed in U.S.A.

MOTOROLA FAST SRAM DATA

#### **TABLE OF CONTENTS**

| ALPHANUMERIC IN  | DEX           |                                                                          | viii  |

|------------------|---------------|--------------------------------------------------------------------------|-------|

| CHAPTER 1 — SELE | CTOR GUIDE A  | AND CROSS REFERENCE                                                      |       |

|                  |               |                                                                          |       |

| CHAPTER 2 — BICM | OS STATIC RA  | Ms                                                                       |       |

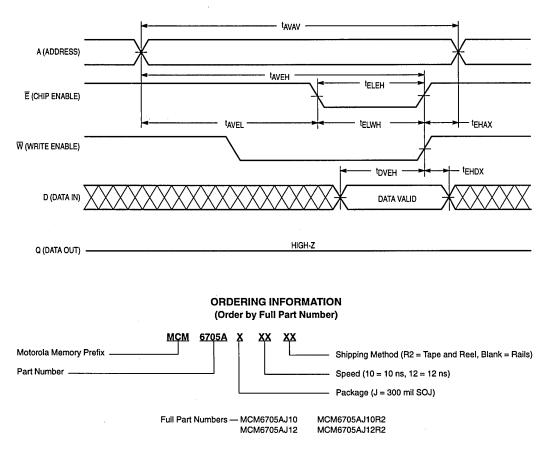

| MCM6705A         | 32K x 9       | 10/12 ns, evolutionary pinout                                            | 2-3   |

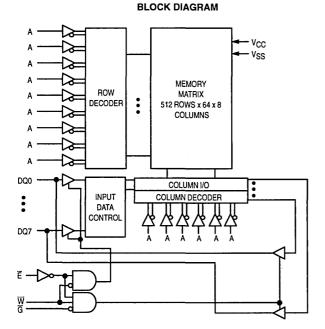

| MCM6706A         | 32K x 8       | 8/10/12 ns, use for new quals and designs, evolutionary pinout           | 2-9   |

| MCM6706R         | 32K x 8       | 6/7/8 ns, use for new guals and designs, revolutionary pinout            | 2-15  |

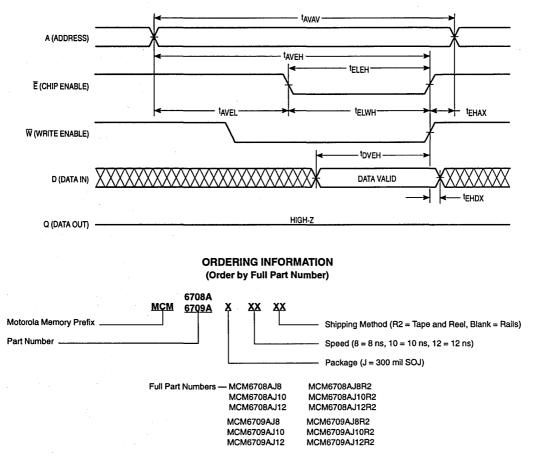

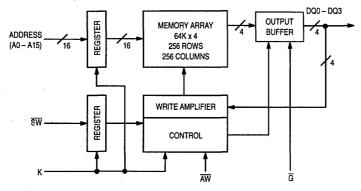

| MCM6708A/6709A   | 64K x 4       | 8/10/12 ns, use for new guals and designs                                |       |

| MCM6709R         | 64K x 4       | 6/7/8 ns, revolutionary pinout, output enable                            | 2-27  |

| MCM6726          | 128K x 8      | 10/12/15 ns, revolutionary pinout                                        | 2-33  |

| MCM6726A         | 128K x 8      | 8/10/12/15 ns, revolutionary pinout                                      | 2-39  |

| MCM6728          | 256K x 4      | 10/12/15 ns, revolutionary pinout                                        | 2-45  |

| MCM6728A         | 256K x 4      | 8/10/12/15 ns, revolutionary pinout                                      | 2-51  |

| MCM6729          | 256K x 4      | 10/12/15 ns, output enable, revolutionary pinout                         | 2-57  |

| MCM6729A         | 256K x 4      | 8/10/12/15 ns, output enable, revolutionary pinout                       | 2-63  |

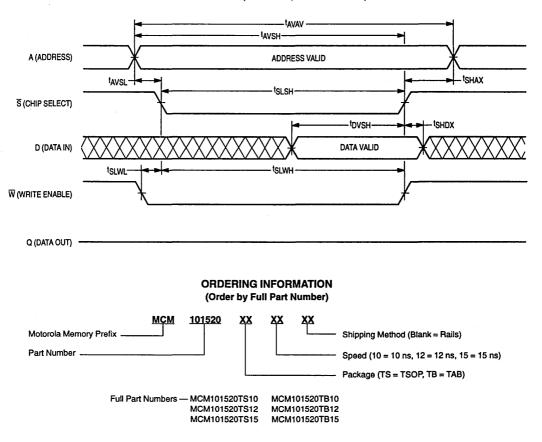

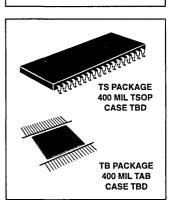

| MCM101520        | 4M x 1        | 10/12/15 ns, 100K ECL compatible at - 5.2 V                              | 2-69  |

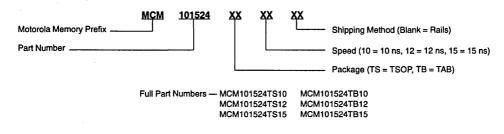

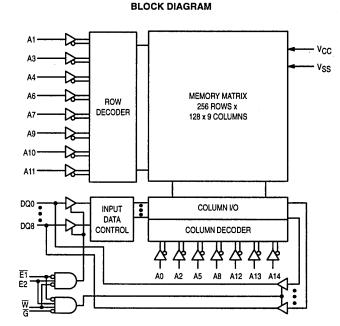

| MCM101524        | 1M x 4/2M x 2 | 10/12/15 ns, 100K ECL compatible at - 5.2 V                              | 2-74  |

| CHAPTER 3 CMO    | S STATIC RAM  | S                                                                        |       |

| MCM6205C         | 32K x 9       | 15/17/20/25/35 ns                                                        | 3-3   |

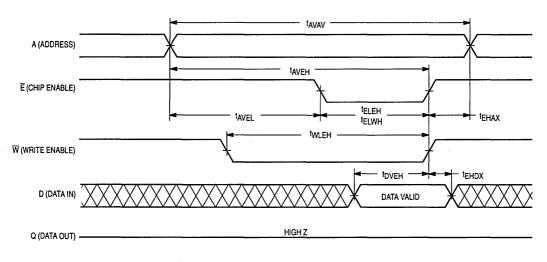

| MCM6205D         | 32K x 9       | 15/20/25 ns                                                              |       |

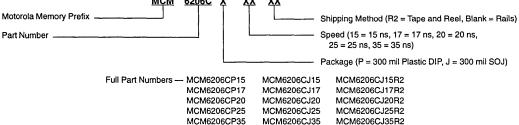

| MCM6206C         | 32K x 8       | 15/17/20/25/35 ns                                                        | 3-15  |

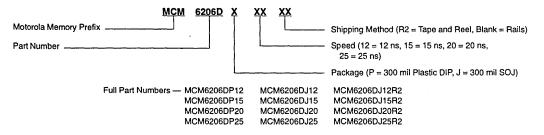

| MCM6206D         | 32K x 8       | 12/15/20/25 ns                                                           | 3-21  |

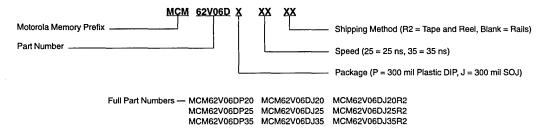

| MCM62V06D        | 32K x 8       | 25/35 ns, first 3.3 V fast SRAM                                          |       |

| MCM6208C         | 64K x 4       | 15/20/25/35 ns                                                           | 3-33  |

| MCM6209C         | 64K x 4       | 15/20/25/35 ns, output enable                                            | 3-39  |

| MCM6226A         | 128K x 8      | 20/25/35/45 ns                                                           | 3-45  |

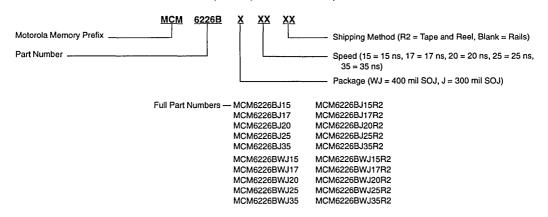

| MCM6226B         | 128K x 8      | 15/17/20/25/35 ns                                                        | 3-51  |

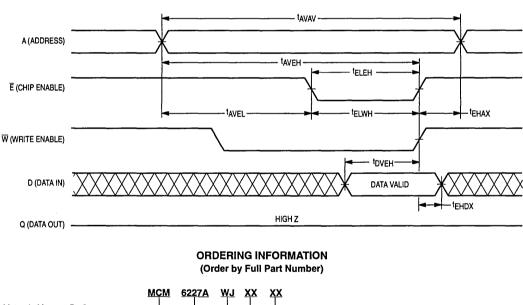

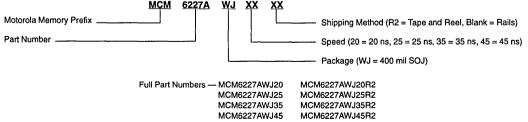

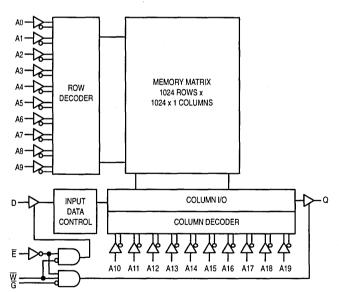

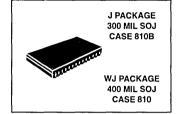

| MCM6227A         | 1M x 1        | 20/25/35/45 ns, separate I/O                                             | 3-58  |

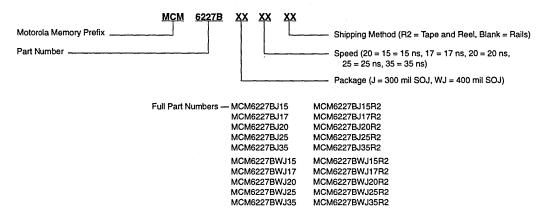

| MCM6227B         | 1M x 1        | 15/17/20/25/35 ns                                                        | 3-64  |

| MCM6229A         | 256K x 4      | 20/25/35/45 ns, output enable                                            | 3-71  |

| MCM6229B         | 256K x 4      | 15/17/20/25/35 ns                                                        | 3-77  |

| MCM6246          | 512K x 8      | 20/25/35 ns                                                              |       |

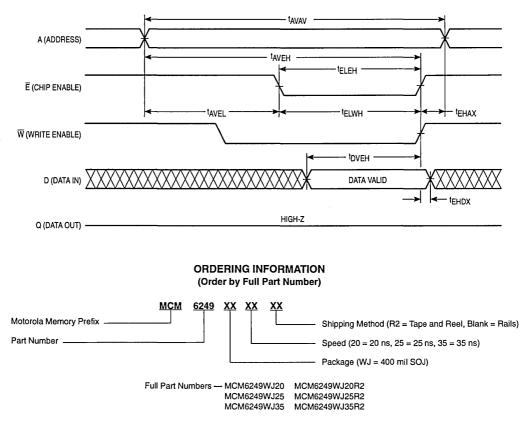

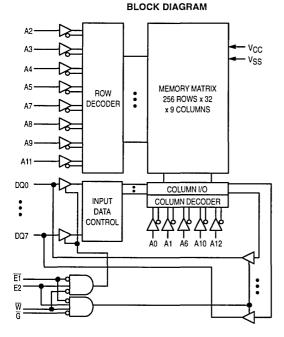

| MCM6249          | 1M x 4        | 20/25/35 ns                                                              | 3-90  |

| MCM6264C         | 8K x 8        | 12/15/20/25/35 ns                                                        | 3-96  |

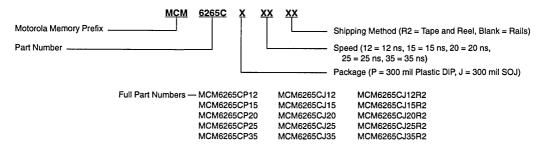

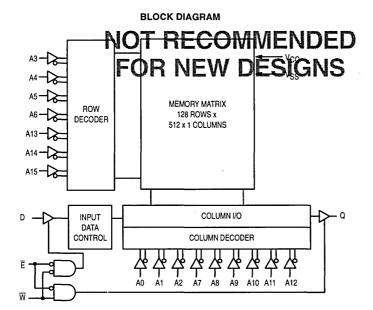

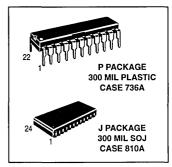

| MCM6265C         | 8K x 9        | 12/15/20/25/35 ns                                                        | 3-102 |

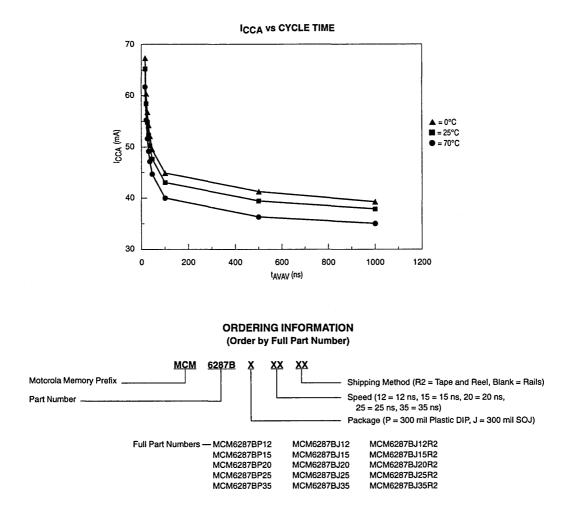

| MCM6287B         | 64K x 1       | 12/15/20/25/35 ns                                                        | 3-108 |

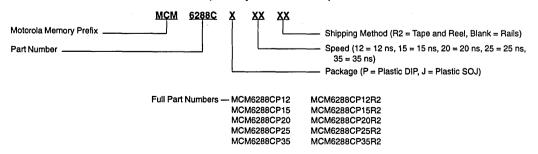

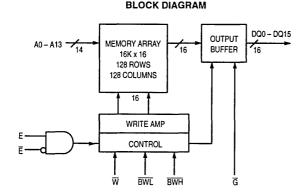

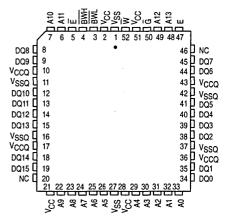

| MCM6288C         | 16K x 4       | 12/15/20/25/35 ns                                                        | 3-115 |

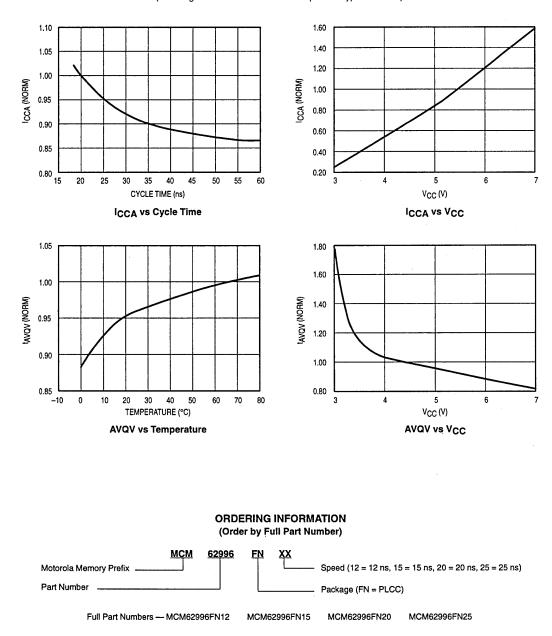

| MCM62996         | 16K x 16      | 12/15/20/25 ns, choice of 5 V or 3.3 V power supplies for output buffers | 3-121 |

#### TABLE OF CONTENTS (Continued)

#### **CHAPTER 4 — APPLICATION SPECIFIC STATIC RAMs**

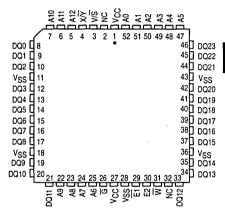

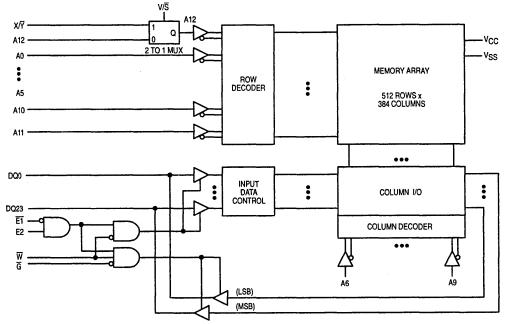

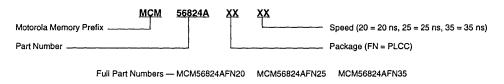

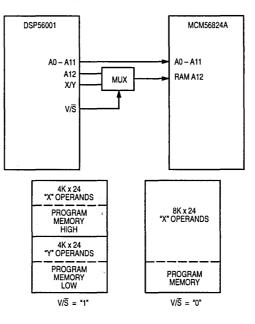

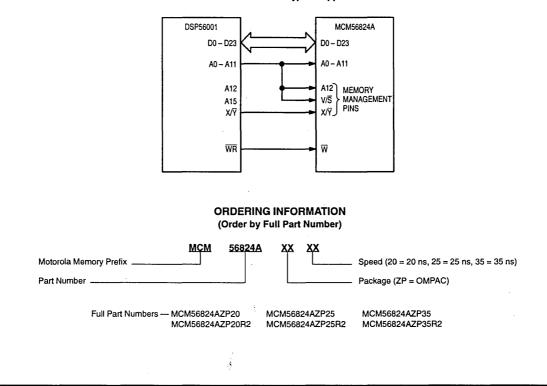

| MCM56824A   | 8K x 24  | 20/25/35 ns, DSPRAM for DSP56001 applications                              |

|-------------|----------|----------------------------------------------------------------------------|

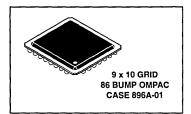

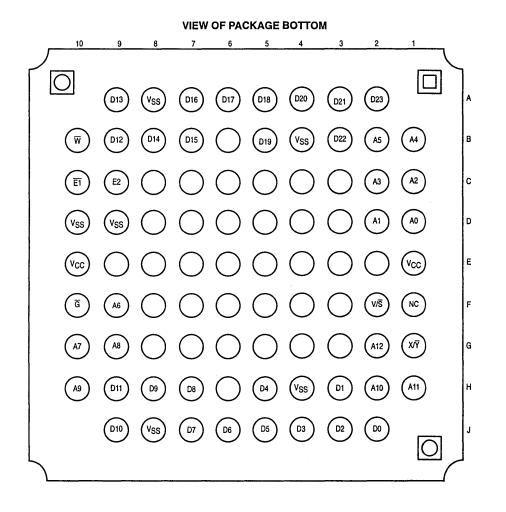

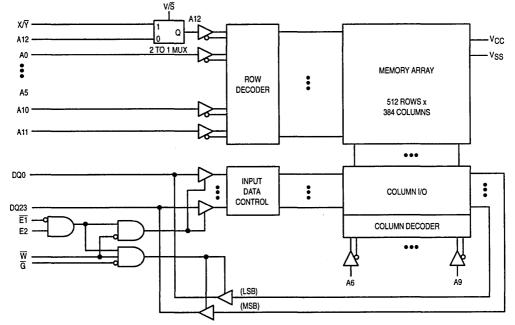

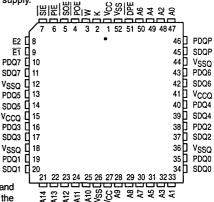

| MCM56824AZP | 8K x 24  | 20/25/35 ns, OMPAC version of DSPRAM for DSP56000 4-10                     |

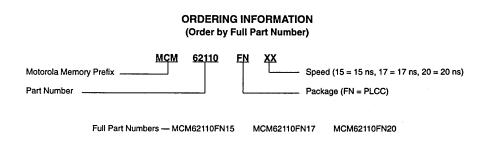

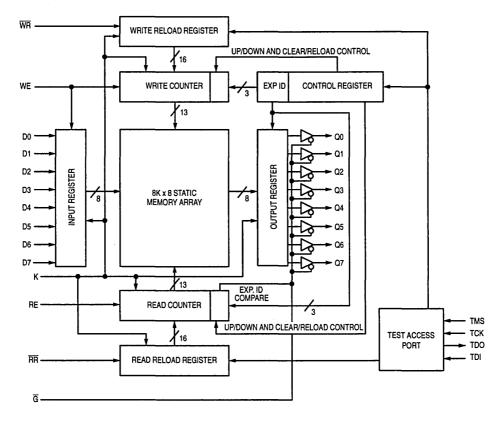

| MCM62110    | 32K x 9  | 15/17/20 ns, dual I/Os for 88110 and others 4-18                           |

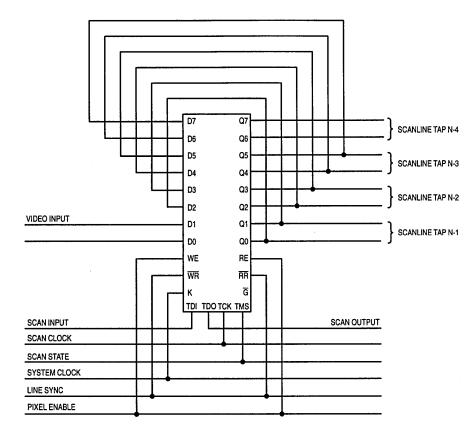

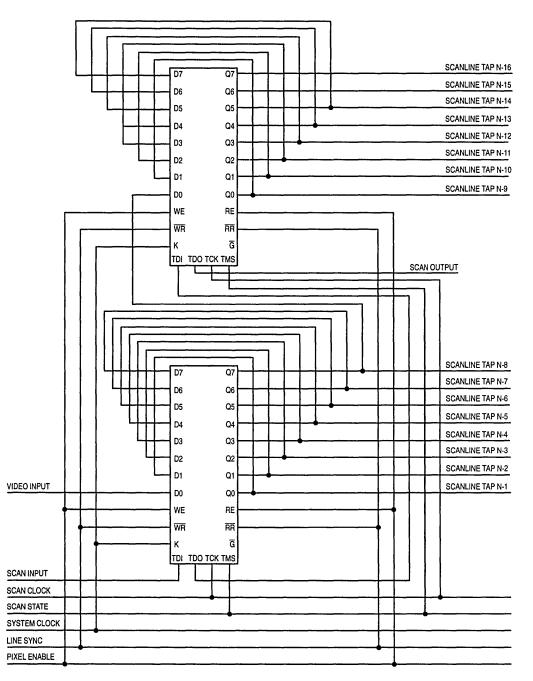

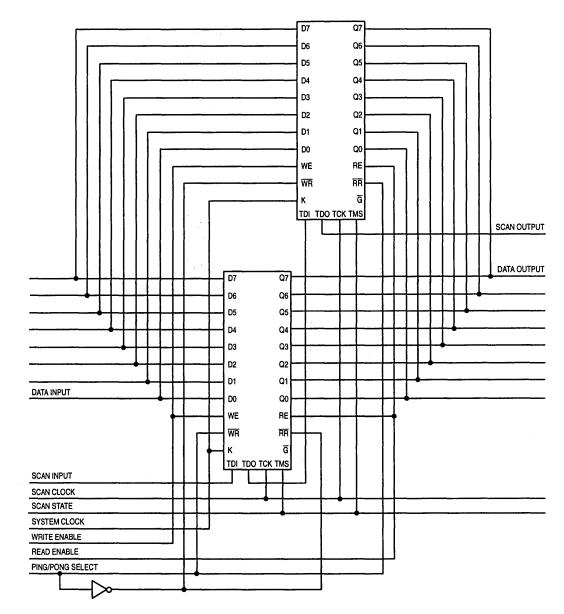

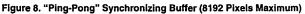

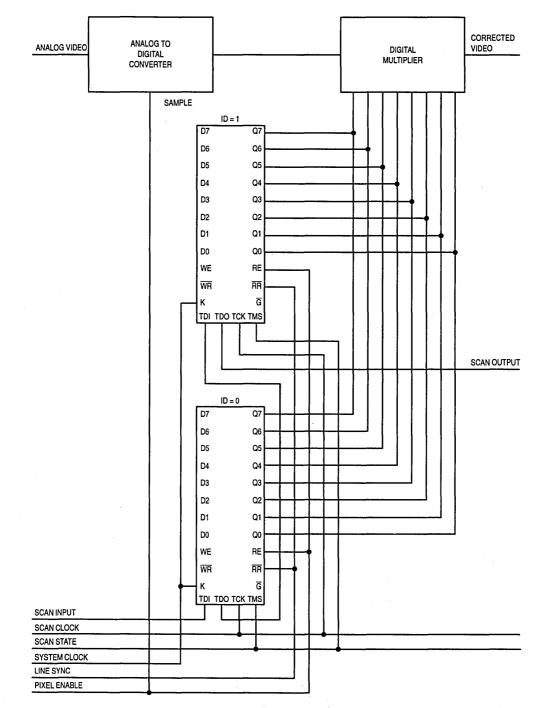

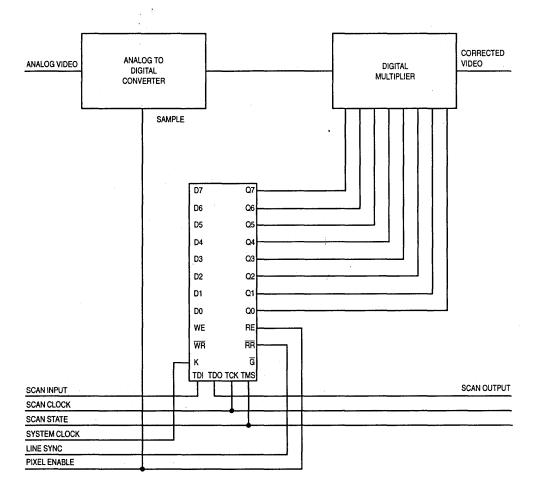

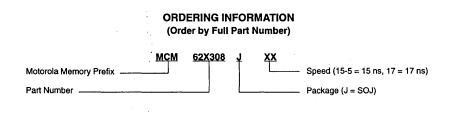

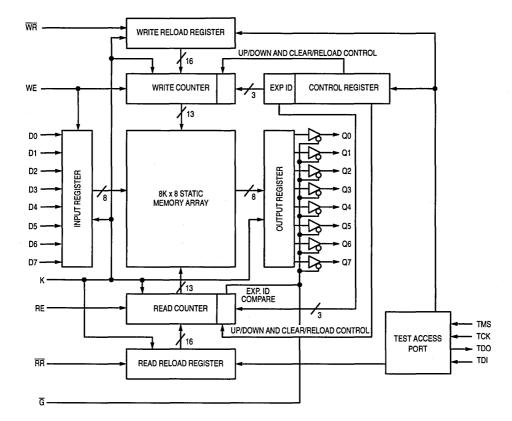

| MCM62X308   | 8K x 8   | synchronous line buffer 4-28                                               |

| MCM62Y308   | 8K x 8   | synchronous line buffer 4-49                                               |

| MCM62T316   | 8K x 16  | 12 ns synchronous cache tag with comparators                               |

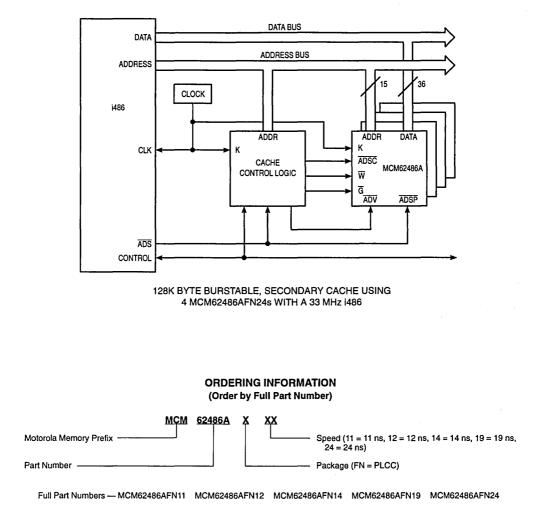

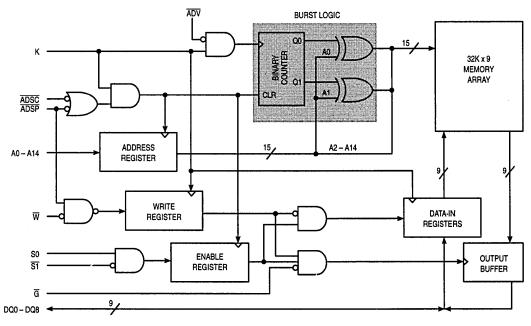

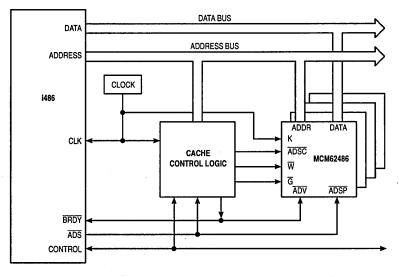

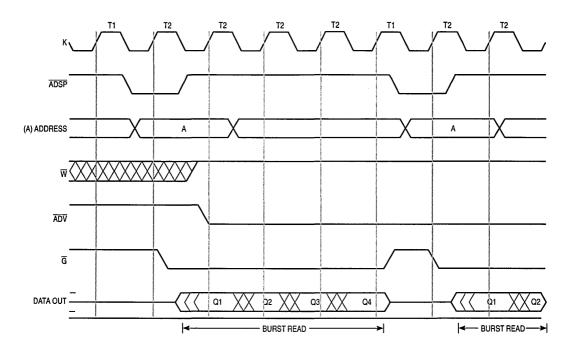

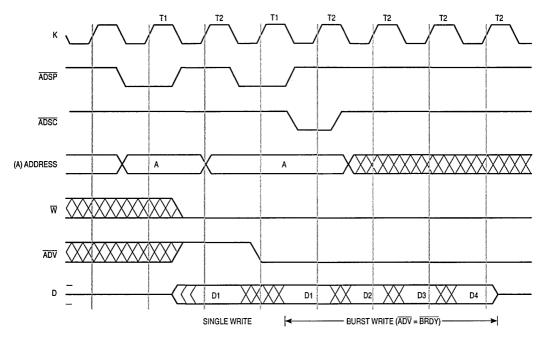

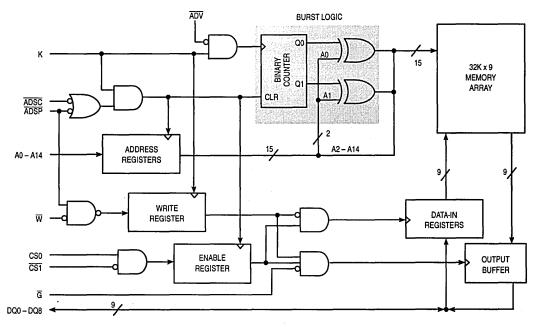

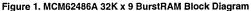

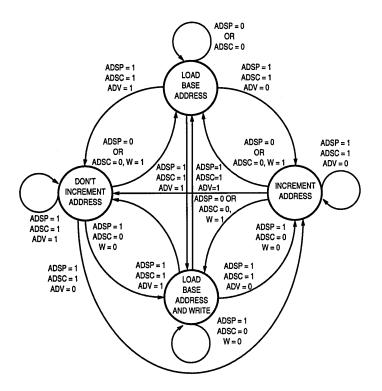

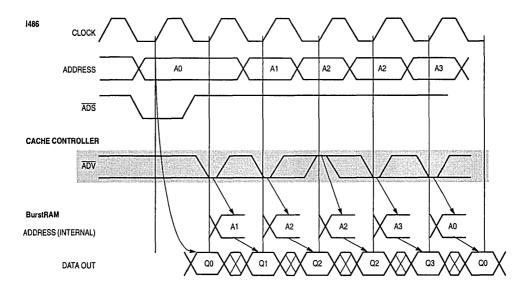

| MCM62486A   | 32K x 9  | 11/12/14/19/24 ns, i486 synchronous BurstRAM cache 4-67                    |

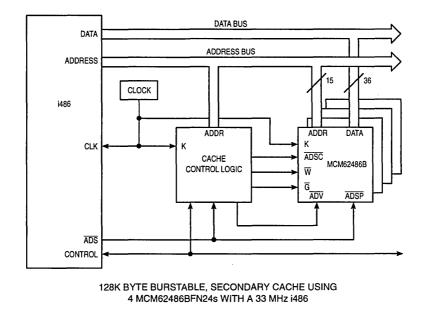

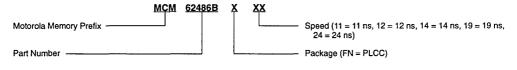

| MCM62486B   | 32K x 9  | 11/12/14/19/24 ns 4-76                                                     |

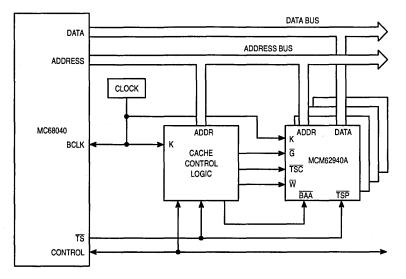

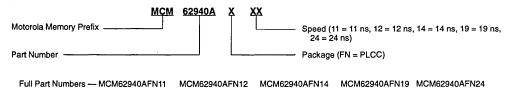

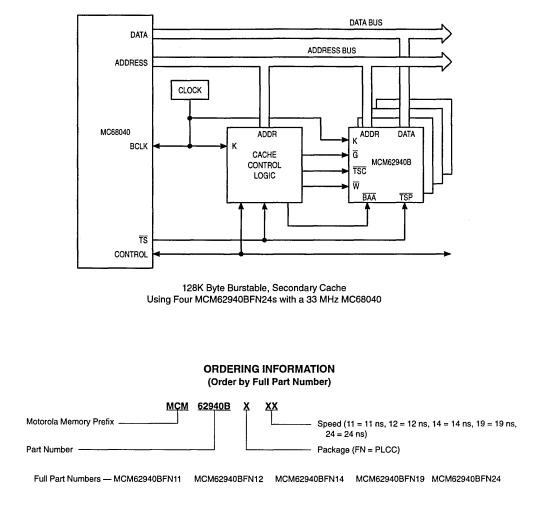

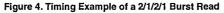

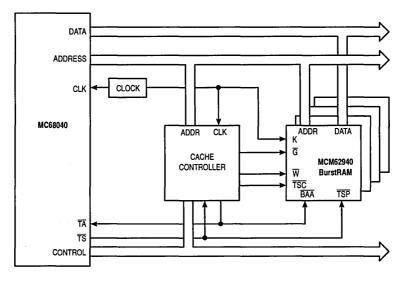

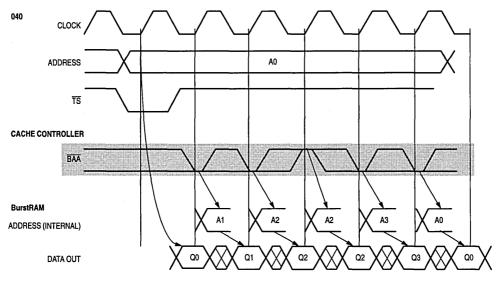

| MCM62940A   | 32K x 9  | 11/12/14/19/24 ns, 68040 synchronous BurstRAM cache 4-85                   |

| MCM62940B   | 32K x 9  | 11/12/14/19/24 ns 4-93                                                     |

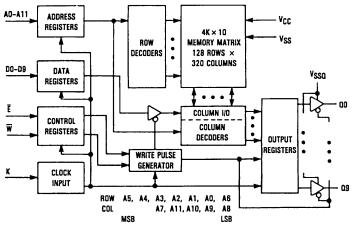

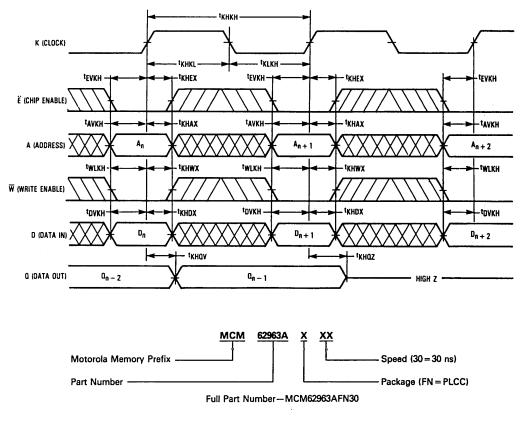

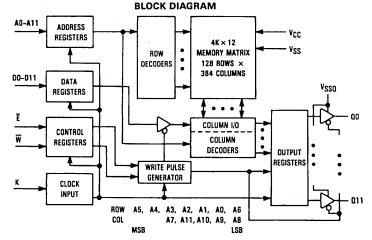

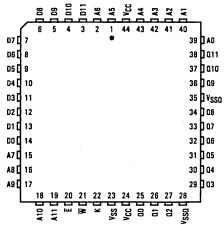

| MCM62963A   | 4K x 10  | 30 ns, output registers 4-101                                              |

| MCM62973A   | 4K x 12  | 18/20 ns, output registers 4-106                                           |

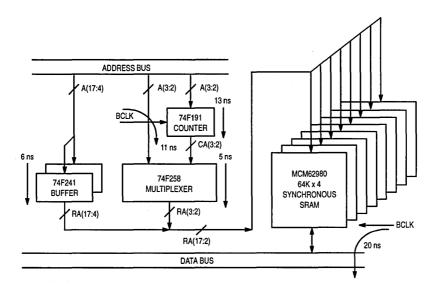

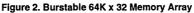

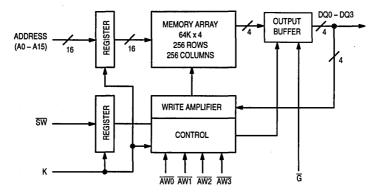

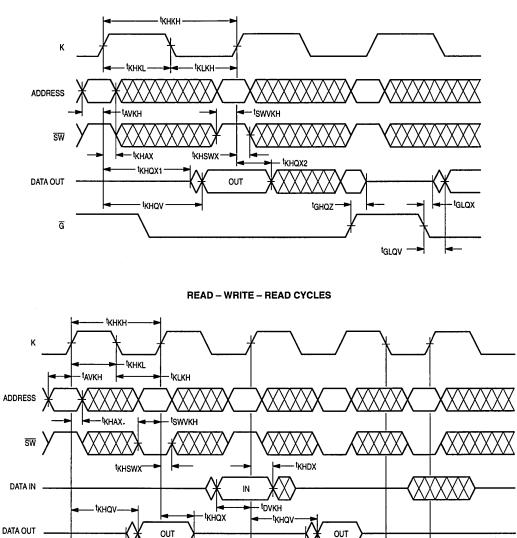

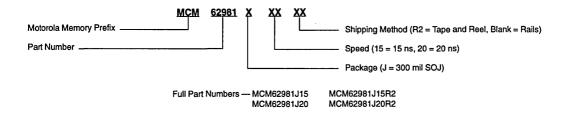

| MCM62980    | 64K x 4  | 15/20 ns, registered address 4-111                                         |

| MCM62981    | 64K x 4  | 15/20 ns, ParityRAM, synchronous, registered address                       |

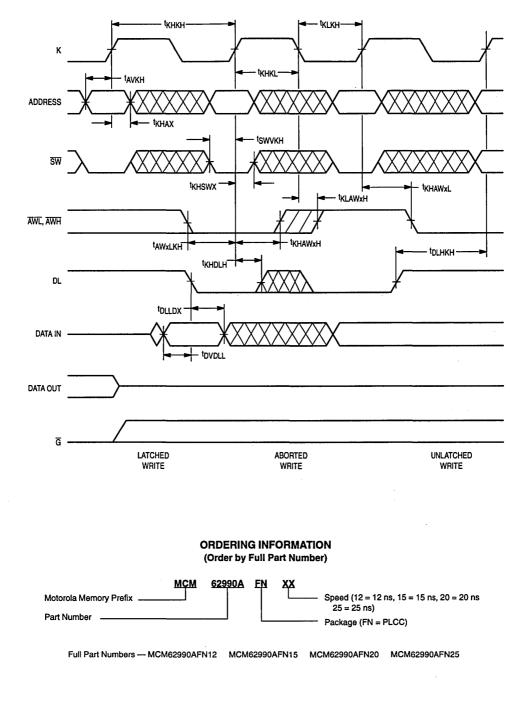

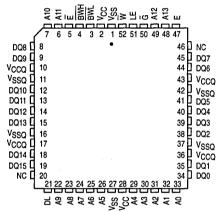

| MCM62990A   | 16K x 16 | 12/15/20/25 ns, designed for advanced RISC-CISC applications 4-123         |

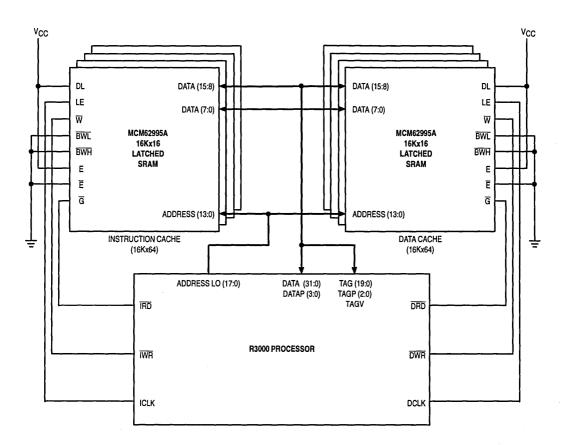

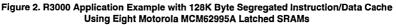

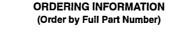

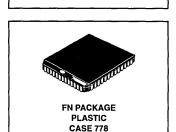

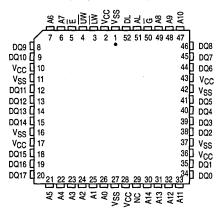

| MCM62995A   | 16K x 16 | 12/15/20/25 ns, DSP96000 and MIPS R3000 applications                       |

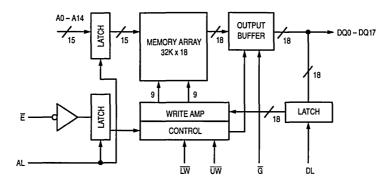

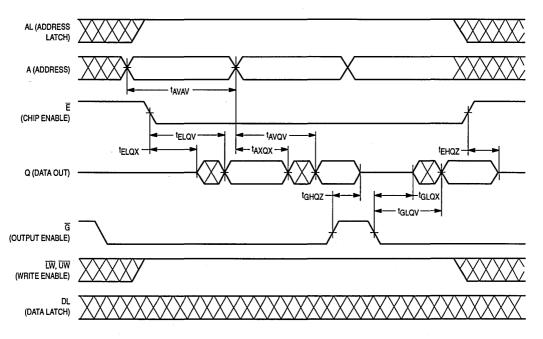

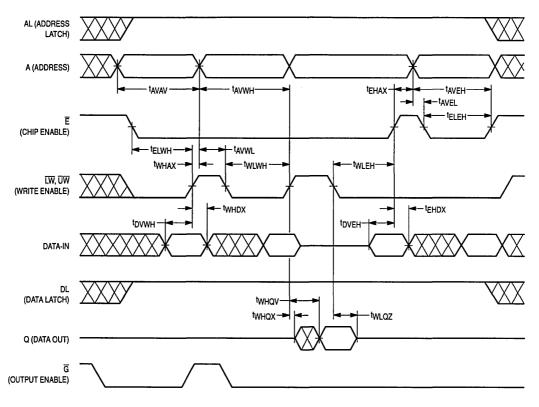

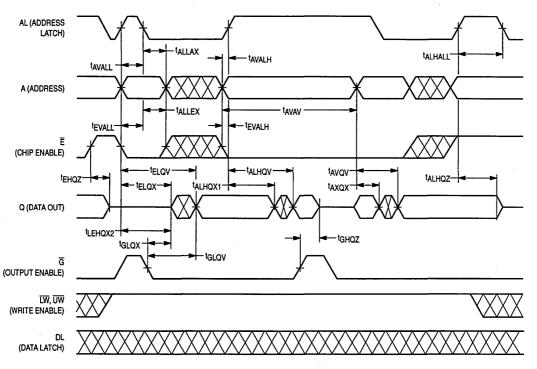

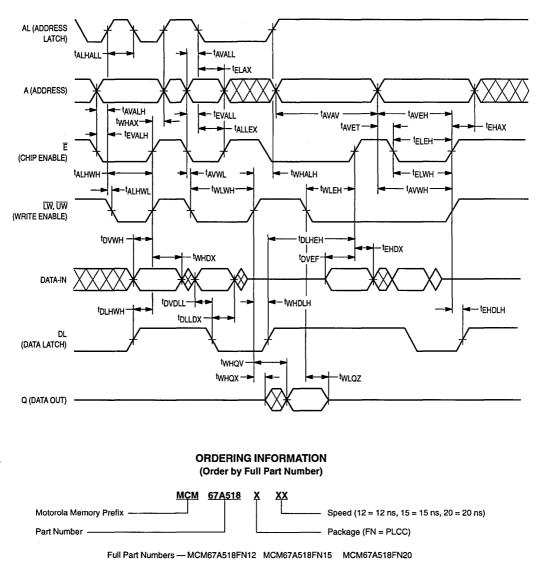

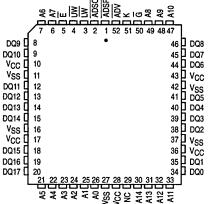

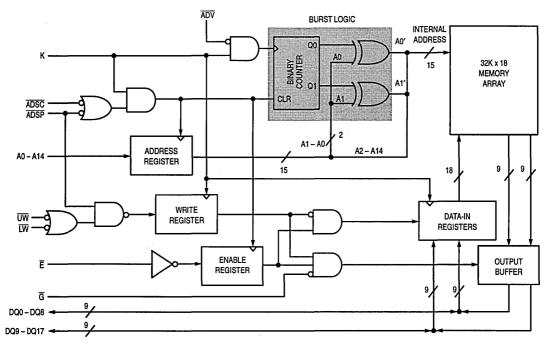

| MCM67A518   | 32K x 18 | 12/15/20 ns, asynchronous, latched address 4-142                           |

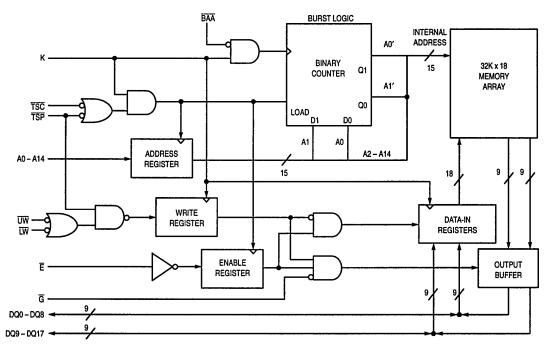

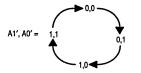

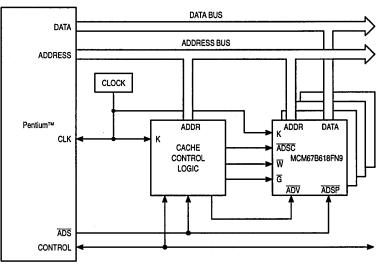

| MCM67B518   | 32K x 18 | 9/12/18 ns, i486/Pentium BurstRAM                                          |

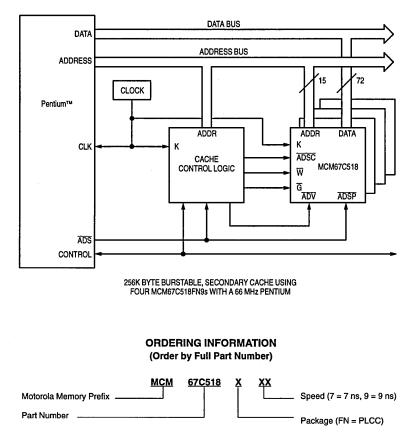

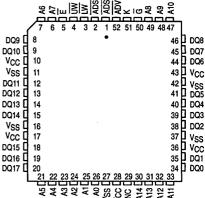

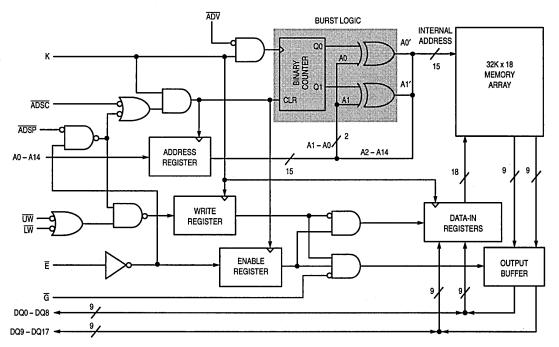

| MCM67C518   | 32K x 18 | 7/9 ns, pipelined i486/Pentium BurstRAM 4-162                              |

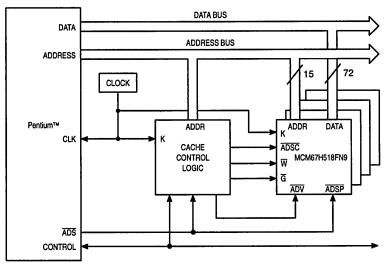

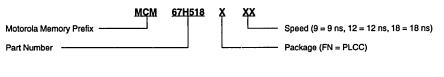

| MCM67H518   | 32K x 18 | 9/12/18 ns, i486/Pentium BurstRAM, supports address pipelining 4-171       |

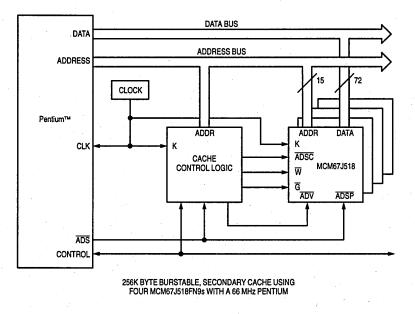

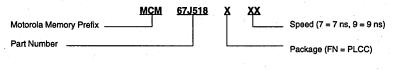

| MCM67J518   | 32K x 18 | 7/9 ns, pipelined i486/Pentium BurstRAM, supports address pipelining 4-180 |

| MCM67M518   | 32K x 18 | 9/11/14/19 ns. 68040/PowerPC BurstRAM                                      |

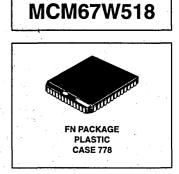

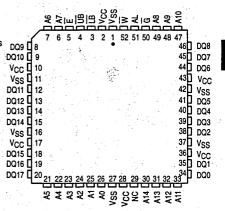

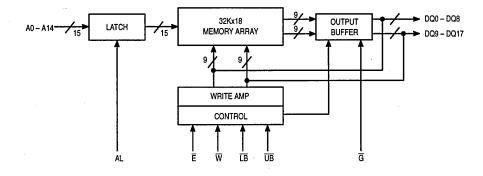

| MCM67W518   | 32K x 18 | 12/15/20 ns, asynchronous with byte enable 4-197                           |

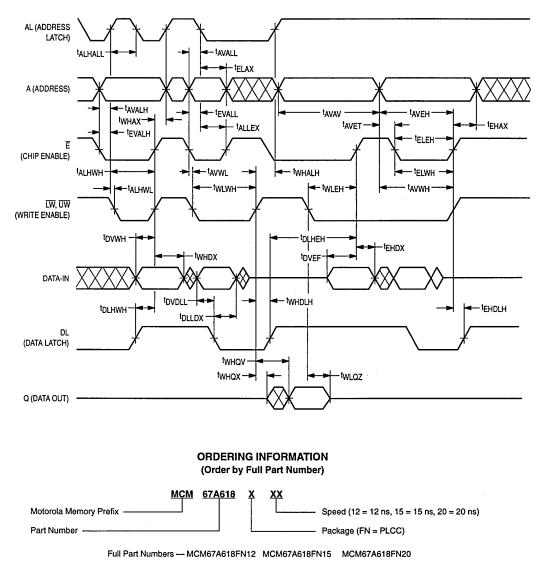

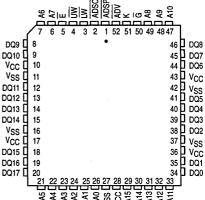

| MCM67A618   | 64K x 18 | 12/15/20 ns, asynchronous, latched address 4-207                           |

| MCM67B618   | 64K x 18 | 11/14/19 ns, i486/Pentium BurstRAM                                         |

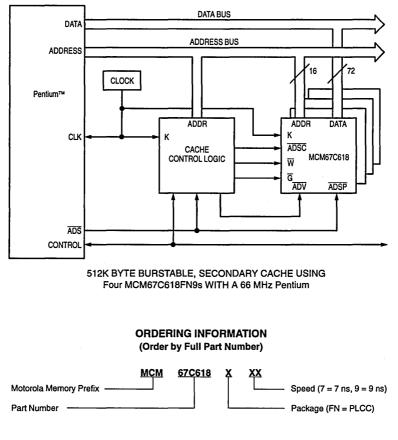

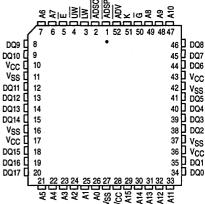

| MCM67C618   | 64K x 18 | 9 ns, pipelined i486/Pentium BurstRAM 4-227                                |

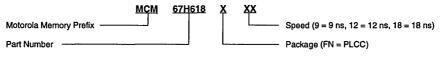

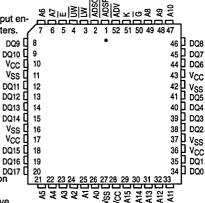

| MCM67H618   | 64K x 18 | 9/12/18 ns, i486/Pentium BurstRAM, supports address pipelining 4-236       |

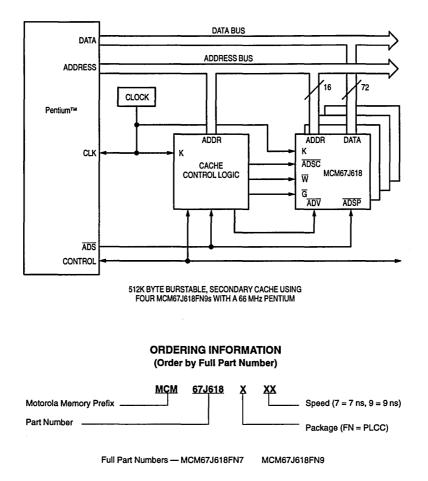

| MCM67J618   | 64K x 18 | 7/9 ns, pipelined i486/Pentium BurstRAM, supports address pipelining 4-245 |

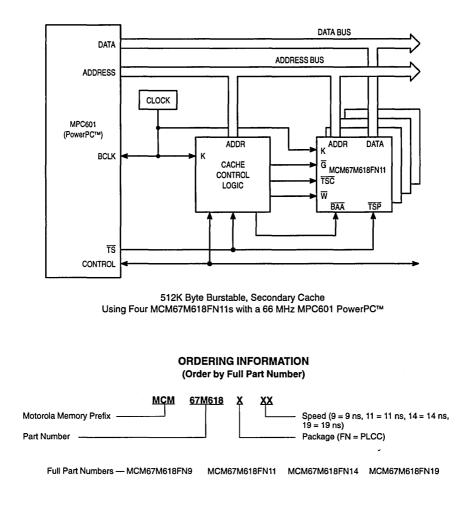

| MCM67M618   | 64K x 18 | 11/14/19 ns. 68040/PowerPC BurstRAM 4-254                                  |

| MCM67W618   | 64K x 18 | 12/15/20 ns, asynchronous with byte enable 4-262                           |

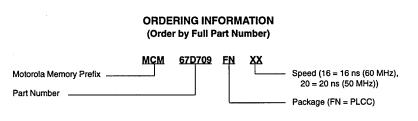

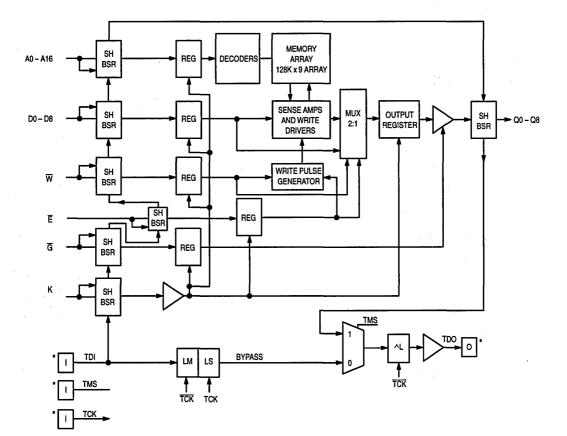

| MCM67D709   | 128K x 9 | 16/20 ns, dual I/O or separate I/O                                         |

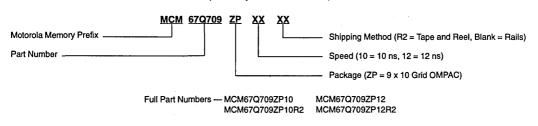

| MCM67Q709   | 128K x 9 | 10/12 ns. separate I/O                                                     |

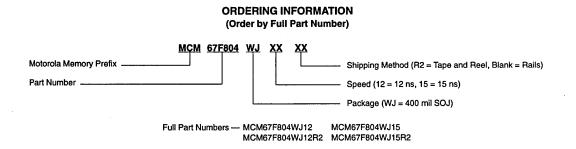

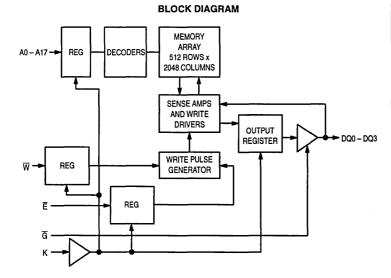

| MCM67F804   | 256K x 4 | 12/15 ns, secondary cache RISC, 3.3 V output levels                        |

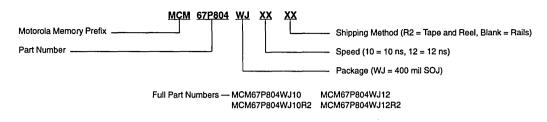

| MCM67P804   | 256K x 4 | 10/12 ns, secondary cache RISC, 3.3 V output levels                        |

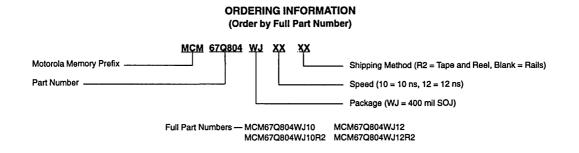

| MCM67Q804   | 256K x 4 | 10/12 ns, secondary cache RISC, 3.3 V output levels                        |

|             | LUUINA   |                                                                            |

#### **CHAPTER 5 — FAST STATIC RAM MODULES**

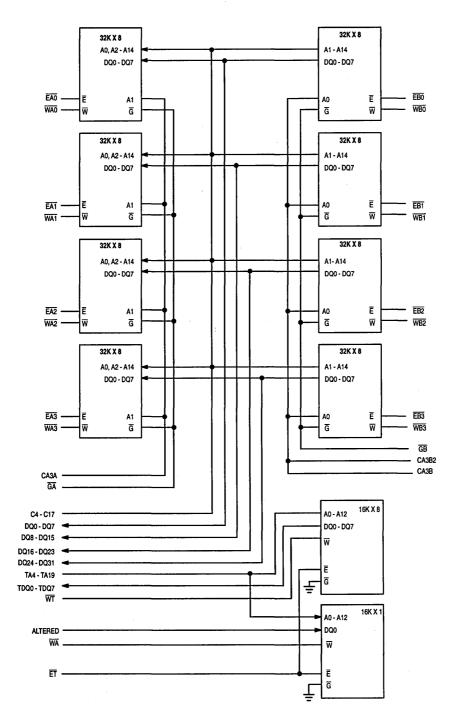

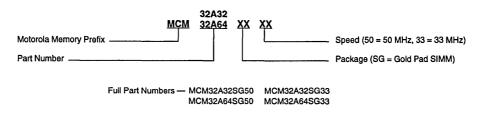

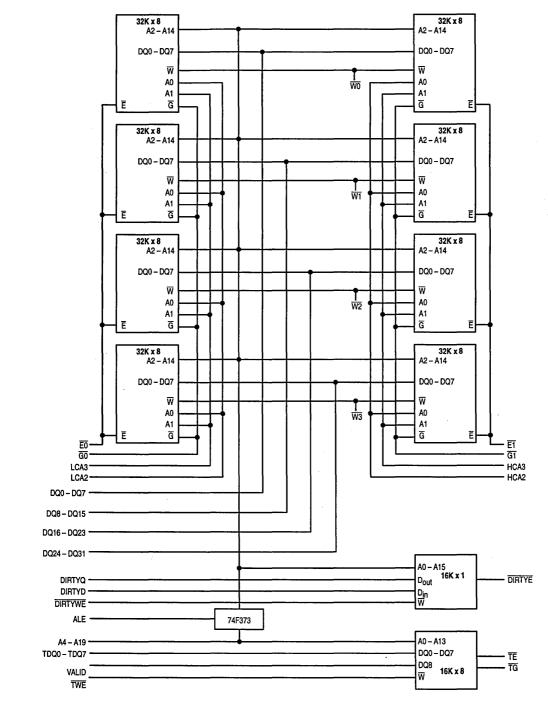

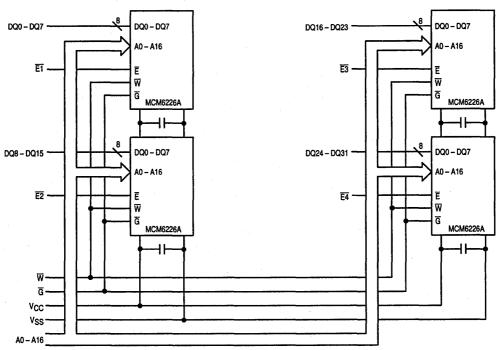

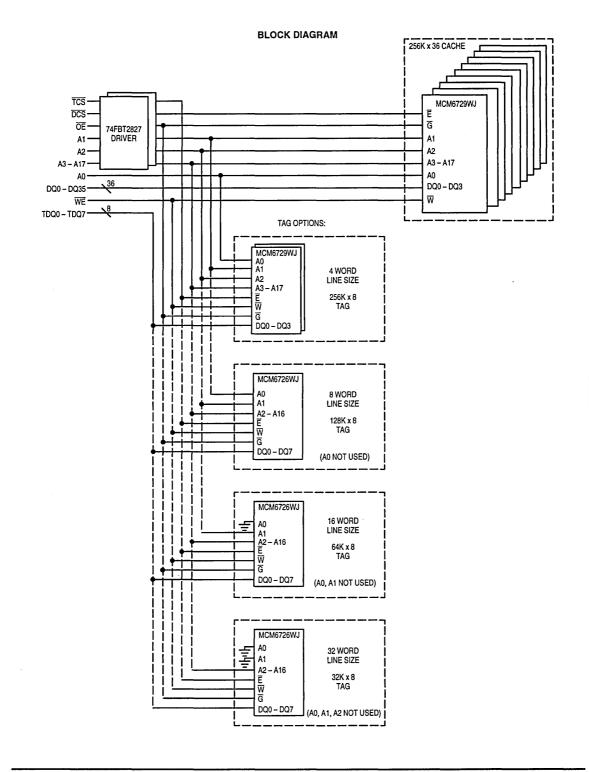

| MCM32A32        | 128KB     | cache module with tag for 486 processor               | 5-3  |

|-----------------|-----------|-------------------------------------------------------|------|

| MCM32A64        | 256KB     | cache module with tag for 486 processor               |      |

| MCM32AB32       | 128KB     | cache module with tag, valid, dirty for 486 processor | 5-12 |

| MCM32AB64       | 256KB     | cache module with tag, valid, dirty for 486 processor | 5-12 |

| MCM32AB128      | 512KB     | cache module with tag, valid, dirty for 486 processor | 5-12 |

| MCM32128        | 128K x 32 | 20/25/35 ns, JEDEC standard module                    | 5-15 |

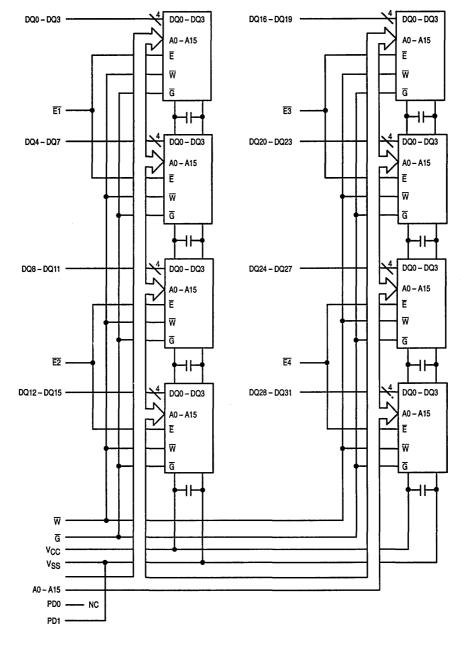

| MCM32257        | 256K x 32 | 20/25/35 ns, 1M byte module                           | 5-22 |

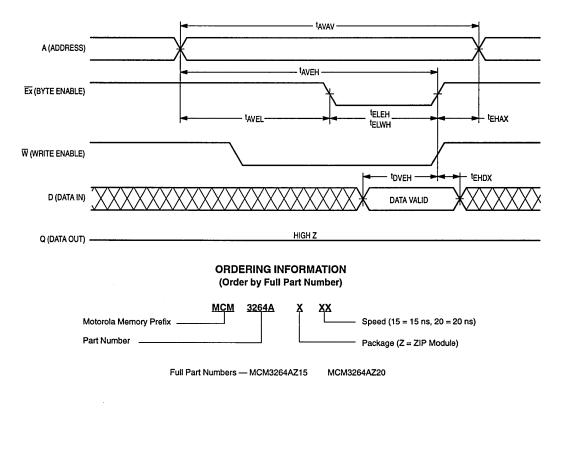

| MCM3264A        | 64K x 32  | 15/20 ns, perfect for 32-bit system, JEDEC standard.  | 5-29 |

| MCM4464         | 64K x 44  | 12/15/17 ns, 256K byte R4000 cache module             | 5-36 |

| MCM44256        | 256K x 44 | 12/15/17 ns, 1M byte R4000 cache module               | 5-44 |

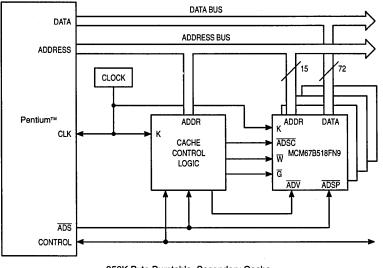

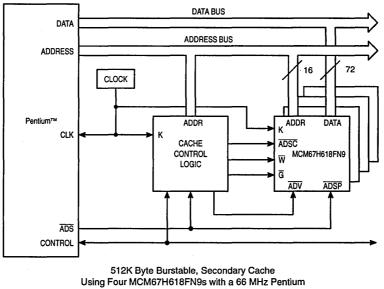

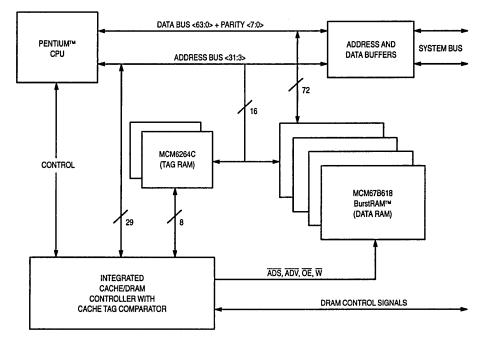

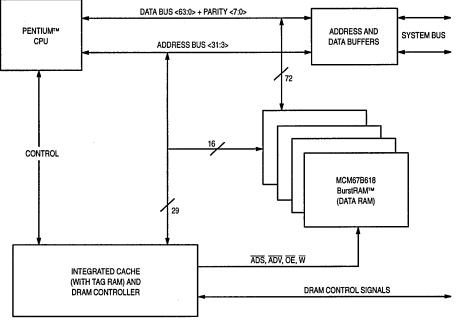

| MCM72BA32       | 256K      | BurstRAM cache module for Pentium                     | 5-52 |

| MCM72BA64       | 512KB     | BurstRAM cache module for Pentium                     | 5-52 |

|                 |           |                                                       |      |

| CHAPTER 6 — MIL | ITARY     |                                                       | 6-1  |

#### CHAPTER 7 — RELIABILITY

| Reliability Information | 7-3 |

|-------------------------|-----|

|                         |     |

#### **TABLE OF CONTENTS (Concluded)**

#### **CHAPTER 8 — APPLICATIONS**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ) Curves                                                                |      |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|--|--|--|--|--|--|--|--|

| APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | NOTES                                                                   |      |  |  |  |  |  |  |  |  |

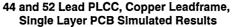

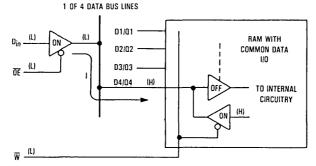

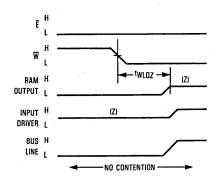

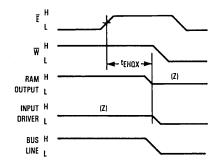

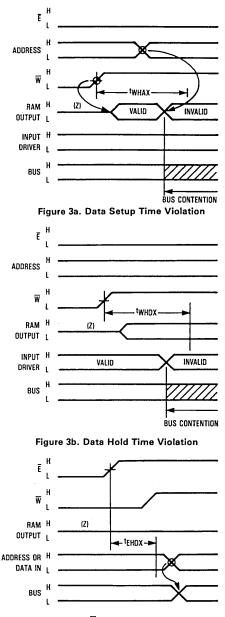

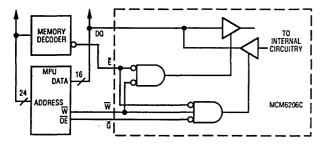

| AN971                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Avoiding Bus Contention in Fast Access RAM Designs                      | 8-11 |  |  |  |  |  |  |  |  |

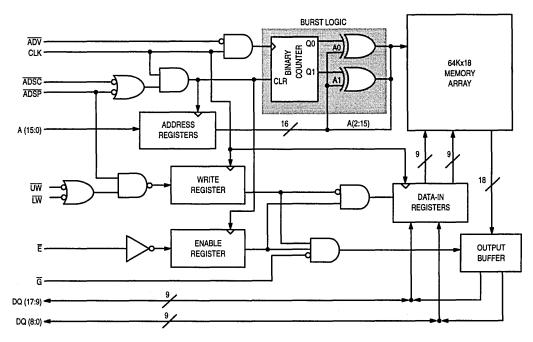

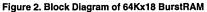

| AN1209                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | The Motorola BurstRAM                                                   | 8-15 |  |  |  |  |  |  |  |  |

| AN1210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A Protocol Specific Memory for Burstable Fast Cache Memory Applications | 8-19 |  |  |  |  |  |  |  |  |

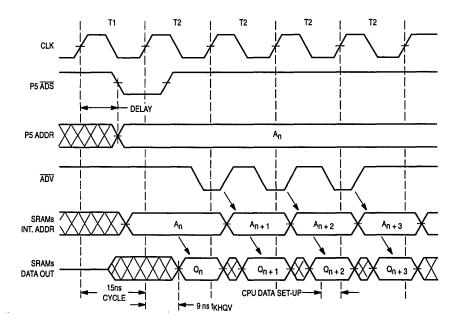

| AN1223                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A Zero Wait State Secondary Cache for Intel's Pentium™                  | 8-25 |  |  |  |  |  |  |  |  |

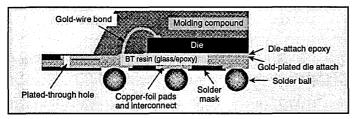

| AR354                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Novel Overmolded Pad-Array Carrier May Obsolete Plastic Quad Flat Packs | 8-33 |  |  |  |  |  |  |  |  |

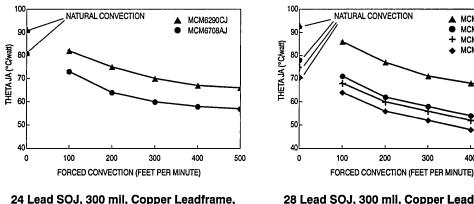

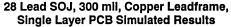

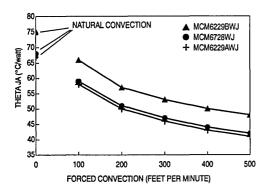

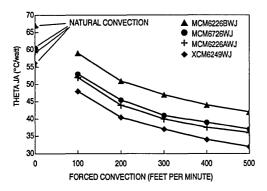

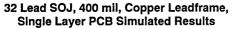

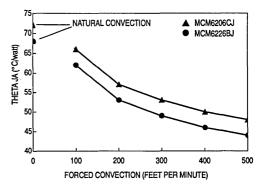

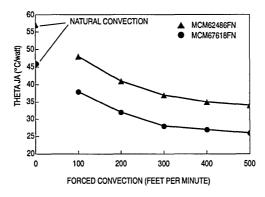

| Thermal Performance of FSRAM Packages       8         APPLICATIONS NOTES       8         AN971       Avoiding Bus Contention in Fast Access RAM Designs       8-         AN1209       The Motorola BurstRAM       8-         AN1210       A Protocol Specific Memory for Burstable Fast Cache Memory Applications       8-         AN1223       A Zero Wait State Secondary Cache for Intel's Pentium™       8-         AR354       Novel Overmolded Pad-Array Carrier May Obsolete Plastic Quad Flat Packs       8-         CHAPTER 9 — MECHANICAL       8-         Case Outlines       8- |                                                                         |      |  |  |  |  |  |  |  |  |

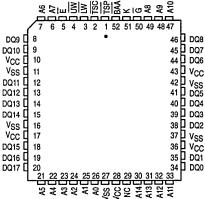

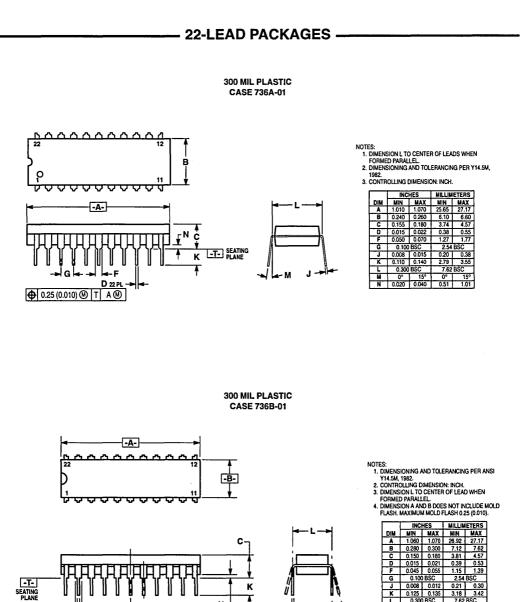

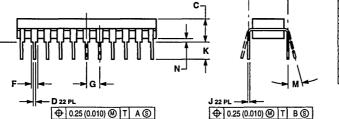

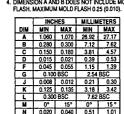

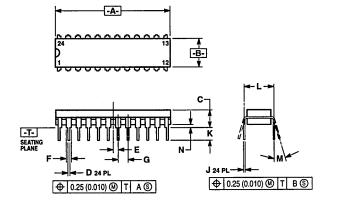

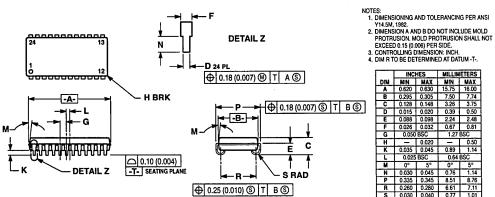

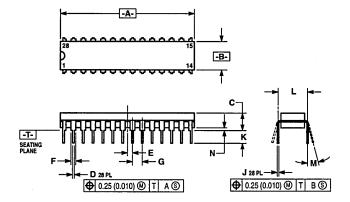

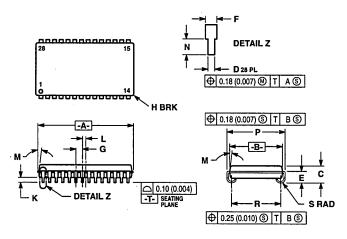

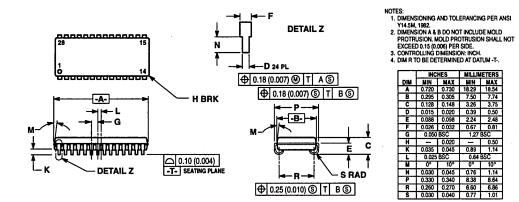

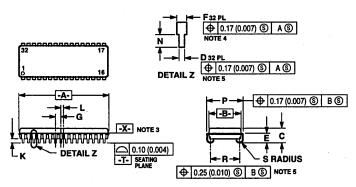

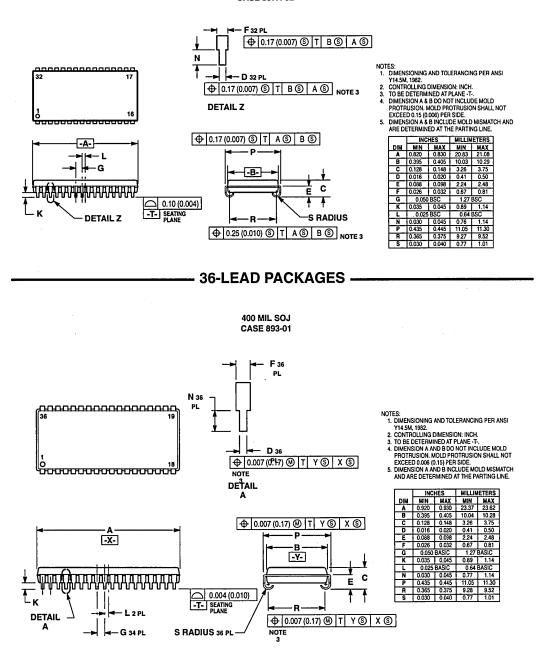

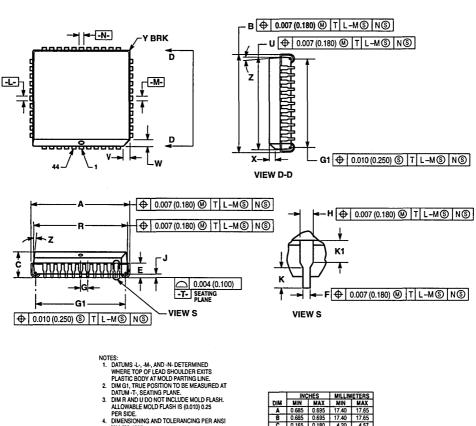

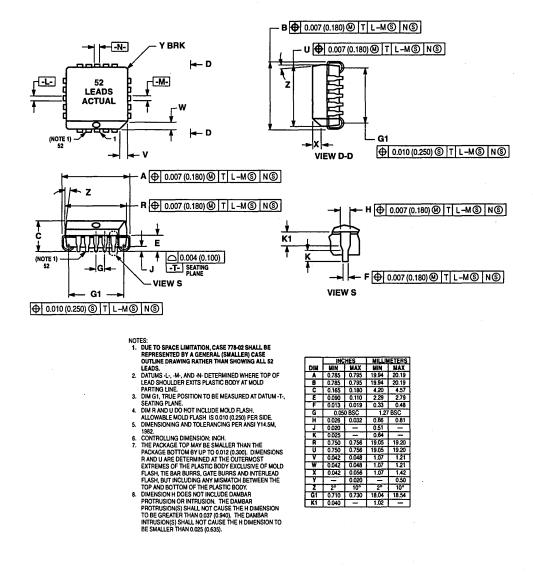

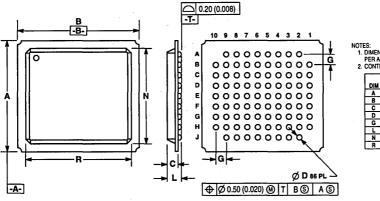

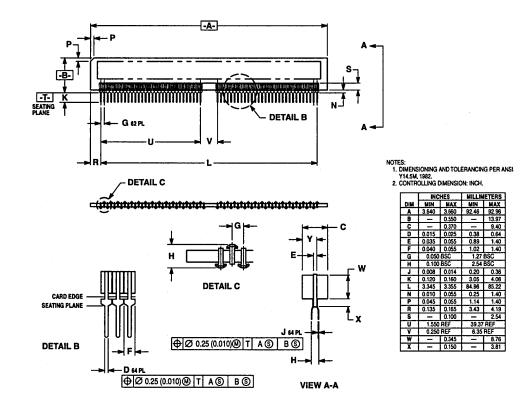

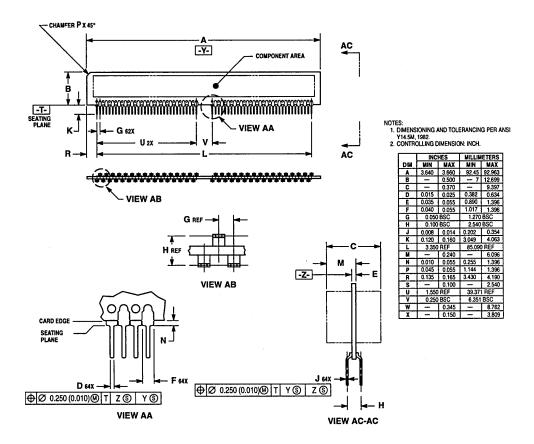

| Case Outlines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                         | 9-3  |  |  |  |  |  |  |  |  |

| TRMEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                         | 9-13 |  |  |  |  |  |  |  |  |

#### SALES OFFICES

#### **ALPHANUMERIC INDEX**

| Device     | Org       | Access Time (ns) | Comments                                              | Page  |

|------------|-----------|------------------|-------------------------------------------------------|-------|

| MCM32A32   | 128KB     | 15/20            | Cache module with tag for 486 processor               | 5-3   |

| MCM32A64   | 256KB     | 15/20            | Cache module with tag for 486 processor               | 5-3   |

| MCM32AB32  | 128KB     | 33/50 MHz        | Cache module with tag, valid, dirty for 486 processor | 5-12  |

| MCM32AB64  | 256KB     | 33/50 MHz        | Cache module with tag, valid, dirty for 486 processor | 5-12  |

| MCM32AB128 | 512KB     | 33/50 MHz        | Cache module with tag, valid, dirty for 486 processor | 5-12  |

| MCM3264A   | 64K x 32  | 15/20            | Perfect for 32-bit system; JEDEC standard             | 5-29  |

| MCM4464    | 64K x 44  | 12/15/17         | 256K byte R4000 cache module                          | 5-36  |

| MCM6205C   | 32K x 9   | 15/17/20/25/35   |                                                       | 3-3   |

| MCM6205D   | 32K x 9   | 15/20/25         |                                                       | 3-9   |

| MCM6206C   | 32K x 8   | 15/17/20/25/35   |                                                       | 3-15  |

| MCM6206D   | 32K x 8   | 12/15/20/25      |                                                       | 3-21  |

| MCM62V06D  | 32K x 8   | 25/35            | First 3.3 V fast SRAM                                 | 3-27  |

| MCM6208C   | 64K x 4   | 15/20/25/35      |                                                       | 3-33  |

| MCM6209C   | 64K x 4   | 15/20/25/35      | Output enable                                         | 3-39  |

| MCM6226A   | 128K x 8  | 20/25/35/45      |                                                       | 3-45  |

| MCM6226B   | 128K x 8  | 15/17/20/25/35   |                                                       | 3-51  |

| MCM6227A   | 1M x 1    | 20/25/35/45      | Separate I/O                                          | 3-58  |

| MCM6227B   | 1M x 1    | 15/17/20/25/35   |                                                       | 3-64  |

| MCM6229A   | 256K x 4  | 20/25/35/45      | Output enable                                         | 3-71  |

| MCM6229B   | 256K x 4  | 15/17/20/25/35   |                                                       | 3-77  |

| MCM6246    | 512K x 8  | 20/25/35         |                                                       | 3-84  |

| MCM6249    | 1M x 4    | 20/25/35         |                                                       | 3-90  |

| MCM6264C   | 8K x 8    | 12/15/20/25/35   |                                                       | 3-96  |

| MCM6265C   | 8K x 9    | 12/15/20/25/35   |                                                       | 3-102 |

| MCM6287B   | 64K x 1   | 12/15/20/25/35   |                                                       | 3-108 |

| MCM6288C   | 16K x 4   | 12/15/20/25/35   |                                                       | 3-115 |

| MCM6705A   | 32K x 9   | 10/12            | Evolutionary pinout                                   | 2-3   |

| MCM6706A   | 32K x 8   | 8/10/12          | Use for new quals and designs; evolutionary pinout    | 2-9   |

| MCM6706R   | 32K x 8   | 6/7/8            | Use for new quals and designs; revolutionary pinout   | 2-15  |

| MCM6708A   | 64K x 4   | 8/10/12          | Use for new quals and designs                         | 2-21  |

| MCM6709A   | 64K x 4   | 8/10/12          | Use for new quals and designs                         | 2-21  |

| MCM6709R   | 64K x 4   | 6/7/8            | Revolutionary pinout; output enable                   | 2-27  |

| MCM6726    | 128K x 8  | 10/12/15         | Revolutionary pinout                                  | 2-33  |

| MCM6726A   | 128K x 8  | 8/10/12/15       | Revolutionary pinout                                  | 2-39  |

| MCM6728    | 256K x 4  | 10/12/15         | Revolutionary pinout                                  | 2-45  |

| MCM6728A   | 256K x 4  | 8/10/12/15       | Revolutionary pinout                                  | 2-51  |

| MCM6729    | 256K x 4  | 10/12/15         | Output enable, revolutionary pinout                   | 2-57  |

| MCM6729A   | 256K x 4  | 8/10/12/15       | Output enable, revolutionary pinout                   | 2-63  |

| MCM72BA32  | 256KB     |                  | BurstRAM cache module for Pentium                     | 5-52  |

| MCM72BA64  | 512KB     |                  | BurstRAM cache module for Pentium                     | 5-52  |

| MCM32128   | 128K x 32 | 20/25/35         | JEDEC standard module                                 | 5-15  |

| MCM32257   | 256K x 32 | 20/25/35         | 1M byte module                                        | 5-22  |

| MCM44256   | 256K x 44 | 12/15/17         | 1M byte R4000 cache module                            | 5-44  |

| Device             | Org               | Access Time (ns) | Comments                                                     | Page  |

|--------------------|-------------------|------------------|--------------------------------------------------------------|-------|

| MCM56824A          | 8K x 24           | 20/25/35         | DSPRAM for DSP56001 applications                             | 4-3   |

| MCM56824AZP        | 8K x 24           | 20/25/35         | OMPAC version of DSPRAM for DSP560010                        | 4-10  |

| MCM62110           | 32K x 9 15/17/20  |                  | Dual I/Os for 88110 and others                               | 4-18  |

| MCM62X308 8K x 8 S |                   |                  | Synchronous line buffer                                      | 4-28  |

| MCM62Y308          | 8K x 8            |                  | Synchronous line buffer                                      | 4-49  |

| MCM62T316          | T316 8K x 16 12 5 |                  | Synchronous Cache Tag with Comparators                       | 4-65  |

| MCM62486A          | 32K x 9           | 11/12/14/19/24   | i486 synchronous BurstRAM cache                              | 4-67  |

| MCM62486B          | 32K x 9           | 11/12/14/19/24   | i486 synchronous BurstRAM cache                              | 4-76  |

| MCM62940A          | 32K x 9           | 11/12/14/19/24   | 68040 synchronous BurstRAM cache                             | 4-85  |

| MCM62940B          | 32K x 9           | 11/12/14/19/24   | 68040 synchronous BurstRAM cache                             | 4-93  |

| MCM62963A          | 4K x 10           | 30               | Synchronous, output registers                                | 4-101 |

| MCM62973A          | 4K x 12           | 18/20            | Synchronous, output registers                                | 4-106 |

| MCM62980           | 64K x 4           | 15/20            | Synchronous, registered address                              | 4-111 |

| MCM62981           | 64K x 4           | 15/20            | ParityRAM, synchronous, registered address                   | 4-117 |

| MCM62990A          | 16K x 16          | 12/15/20/25      | Designed for advanced RISC-CISC applications                 | 4-123 |

| MCM62995A          | 16K x 16          | 12/15/20/25      | DSP96000 and MIPS R3000 applications                         | 4-130 |

| MCM62996           | 16K x 16          | 12/15/20/25      | Choice of 5 V or 3.3 V power supplies for output buffers     | 3-121 |

| MCM67A518          | 32K x 18          | 12/15/20         | Asynchronous, latched data                                   | 4-142 |

| MCM67B518          | 32K x 18          | 9/12/18          | i486/Pentium BurstRAM                                        | 4-153 |

| MCM67C518          | 32K x 18          | 7/9              | Pipelined i486/Pentium BurstRAM                              | 4-162 |

| MCM67H518          | 32K x 18          | 9/12/18          | i486/Pentium BurstRAM, supports address pipelining           | 4-171 |

| MCM67J518          | 32K x 18          | 7/9              | Pipelined i486/Pentium BurstRAM, supports address pipelining | 4-180 |

| MCM67M518          | 32K x 18          | 9/11/14/19       | 68040/PowerPC BurstRAM                                       | 4-189 |

| MCM67W518          | 32K x 18          | 12/15/20         | Asynchronous with byte enable                                | 4-197 |

| MCM67A618          | 64K x 18          | 12/15/20         | Asynchronous, latched address                                | 4-207 |

| MCM67B618          | 64K x 18          | 11/14/19         | i486/Pentium BurstRAM                                        | 4-218 |

| MCM67C618          | 64K x 18          | 9                | Pipelined i486/Pentium BurstRAM                              | 4-227 |

| MCM67H618          | 64K x 18          | 9/12/18          | i486/Pentium BurstRAM, supports address pipelining           | 4-236 |

| MCM67J618          | 64K x 18          | 7/9              | Pipelined i486/Pentium BurstRAM, supports address pipelining | 4-245 |

| MCM67M618          | 64K x 18          | 11/14/19         | 68040/PowerPC BurstRAM                                       | 4-254 |

| MCM67W618          | 64K x 18          | 12/15/20         | Asynchronous with byte enable                                | 4-262 |

| MCM67D709          | 128K x 9          | 16/20            | Dual I/O or separate I/O                                     | 4-272 |

| MCM67Q709          | 128K x 9          | 10/12            | Separate I/O                                                 | 4-281 |

| MCM67F804          | 256K x 4          | 12/15            | Synchronous, secondary cache RISC, 3.3 V output levels       | 4-291 |

| MCM67P804          | 256K x 4          | 10/12            | Synchronous, secondary cache RISC, 3.3 V output levels       | 4-297 |

| MCM67Q804          | 256K x 4          | 10/12            | Secondary cache RISC, 3.3 V output                           | 4-302 |

| MCM101520          | 4M x 1            | 10/12/15         | 100K ECL compatible at - 5.2 V                               | 2-69  |

| MCM101524          | 1M x 4/<br>2M x 2 | 10/12/15         | 100K ECL compatible at - 5.2 V                               | 2-74  |

ALPHANUMERIC INDEX x

#### **Selector Guide and Cross Reference**

; ;

MOTOROLA FAST SRAM DATA

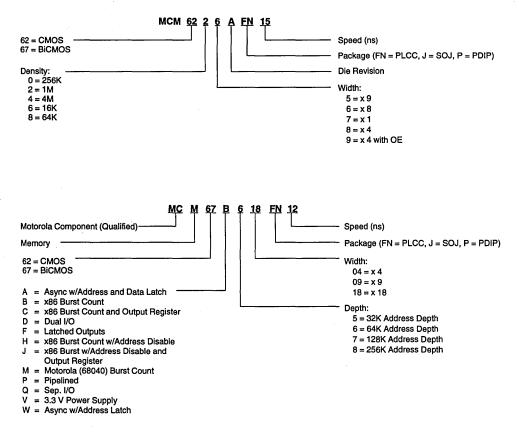

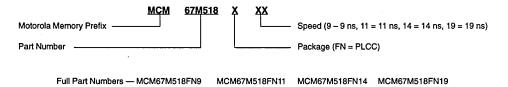

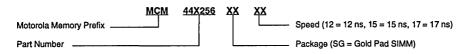

#### **DEVICE/PART NUMBER DESIGNATORS**

NOTE: There are some exceptions to these device numbering schemes, i.e., MCM62990A is a CMOS 16K x 16 and NOT a 512K x 90 device.

| ≤        |  |

|----------|--|

| Ō        |  |

| <b>–</b> |  |

| O.       |  |

| Ť        |  |

| õ        |  |

| ř        |  |

| ≻        |  |

| -        |  |

| ×.       |  |

| Ś        |  |

| -        |  |

| S        |  |

| Ť        |  |

| ×        |  |

| 2        |  |

| -        |  |

| õ        |  |

| 2        |  |

| 5        |  |

| -        |  |

| Density | Config-<br>uration | Access<br>(ns) | Cycle<br>(ns) | Supplier | Part<br>Number | No.<br>Pins | Width<br>(mils) | Package   | Revol.<br>Pinout | Syn-<br>chronous                      | Latches | Output<br>Enable | Special<br>Function |

|---------|--------------------|----------------|---------------|----------|----------------|-------------|-----------------|-----------|------------------|---------------------------------------|---------|------------------|---------------------|

| 8M      | 256K x 36          | 12             | _             | Motorola | MCM44256       | 80          |                 | SIMM      |                  |                                       | [       | 0                | ٥                   |

|         |                    | 15             |               | Motorola | MCM44256       | 80          |                 | SIMM      |                  |                                       |         | <b></b>          | \$                  |

|         |                    | 17             | _             | Motorola | MCM44256       | 80          |                 | SIMM      |                  |                                       |         | <b>o</b>         | 0                   |

|         | 256K x 32          | 20             | _             | Motorola | MCM32257       | 64          |                 | ZIP       |                  |                                       |         | 0                |                     |

|         |                    | 20             | -             | AT&T     | ATTM32257      |             |                 |           |                  |                                       |         |                  |                     |

|         |                    | 20             | -             | Micron   | MT8S25632      |             |                 |           |                  |                                       |         |                  |                     |

|         |                    | 20             | 1             | IDT      | IDT7MP4045     |             |                 |           |                  | · · · · · · · · · · · · · · · · · · · |         |                  |                     |

|         |                    | 25             | _             | Motorola | MCM32257       | 64          |                 | ZIP       |                  |                                       |         | <u>ہ</u>         |                     |

|         |                    | 25             | —             | AT&T     | ATTM32257      |             |                 |           |                  |                                       |         | <u> </u>         |                     |

|         |                    | 25             | -             | Micron   | MT8S25632      |             |                 |           |                  |                                       |         |                  |                     |

|         |                    | 25             | _             | IDT      | IDT7MP4045     |             |                 |           |                  |                                       |         |                  |                     |

|         |                    | 35             | _             | Motorola | MCM32257       | 64          |                 | ZIP       | 1                |                                       |         | 0                |                     |

|         |                    | 35             | _             | AT&T     | ATTM32257      | 1           |                 |           |                  |                                       |         |                  |                     |

|         |                    | 35             | _             | Micron   | MT8S25632      |             |                 |           |                  |                                       |         |                  |                     |

| 4M      | 64K x 72           | _              | 15            | Motorola | MCM72BA64      | 136         |                 | SIMM      |                  | 0                                     |         | 0                | 0                   |

|         |                    | _              | 16.6          | Motorola | MCM72BA64      | 136         |                 | SIMM      |                  | 0                                     |         | <u>ہ</u>         | ٥                   |

|         | 128K x 32          |                | 20            | Motorola | MCM32AB128     | 112         |                 | SIMM      | 1                |                                       | 0       | <b></b>          | 0                   |

|         |                    |                | 30            | Motorola | MCM32AB128     | 112         |                 | SIMM      |                  |                                       | 0       | 0                | 0                   |

|         |                    | 20             | _             | Motorola | MCM32128       | 64          |                 | ZIP, SIMM |                  |                                       |         | 0                |                     |

|         |                    | 20             | _             | AT&T     | ATTM32128      |             |                 |           |                  |                                       |         |                  |                     |

|         |                    | 20             | -             | Micron   | MT4S12832      |             |                 |           | 1                |                                       |         |                  |                     |

|         |                    | 25             | _             | Motorola | MCM32128       | 64          |                 | ZIP, SIMM |                  |                                       |         | 0                |                     |

|         |                    | 25             | —             | AT&T     | ATTM32128      | 1           |                 |           |                  |                                       |         |                  |                     |

|         |                    | 25             | _             | Micron   | MT4S12832      | 1           |                 |           |                  |                                       |         |                  |                     |

|         |                    | 35             |               | Motorola | MCM32128       | 64          |                 | ZIP, SIMM | 1                |                                       |         | 0                |                     |

|         |                    | 35             | _             | AT&T     | ATTM32128      |             |                 |           |                  |                                       |         |                  |                     |

|         |                    | 35             | _             | Micron   | MT4S12832      |             |                 |           |                  |                                       |         |                  |                     |

|         | 512K x 8           | 25             |               | Motorola | MCM6246        | 36          | 400             | SOJ       | 0                |                                       |         |                  |                     |

|         |                    | 25             | _             | Micron   | MT5C512K8A1    | 32          | 400             | SOJ       |                  | _                                     |         |                  |                     |

|         |                    | 25             |               | Micron   | MT5C512K8B2    | 36          | 400             | SOJ, TSOP | 0                |                                       |         |                  |                     |

|         |                    | 25             |               | Micron   | MT5LC512K8C3   | 32          | 400             | SOJ       |                  |                                       |         |                  |                     |

|         |                    | 25             | _             | Micron   | MT5LC512K8D4   | 36          | 400             | SOJ, TSOP | 0                |                                       |         |                  |                     |

|         |                    | 25             | _             | NEC      | µPD434008      | 32/36       | 400             | SOJ       | 0                |                                       |         |                  |                     |

|         |                    | 30             | _             | Motorola | MCM6246        | 36          | 400             | SOJ       | 0                |                                       |         |                  |                     |

|         |                    | 30             | -             | Micron   | MT5C512K8A1    | 32          | 400             | soj       |                  |                                       |         |                  |                     |

# SELECTOR GUIDE/CROSS REFERENCE

**\_\_\_**

SELECTOR GUIDE 1-3

ł

| Density | Config-<br>uration | Access<br>(ns) | Cycle<br>(ns) | Supplier | Part<br>Number | No.<br>Pins | Width<br>(mils) | Package      | Revol.<br>Pinout | Syn-<br>chronous | Latches | Output<br>Enable | Special<br>Function |

|---------|--------------------|----------------|---------------|----------|----------------|-------------|-----------------|--------------|------------------|------------------|---------|------------------|---------------------|

|         |                    | 30             |               | Micron   | MT5C512K8B2    | 36          | 400             | SOJ, TSOP    | 0                |                  |         |                  |                     |

|         |                    | 30             | _             | Micron   | MT5LC512K8C3   | 32          | 400             | SOJ          | <u> </u>         |                  |         |                  |                     |

|         |                    | 30             | _             | Micron   | MT5LC512K8D4   | 36          | 400             | SOJ, TSOP    | 0                |                  |         |                  |                     |

|         |                    | 35             | _             | Motorola | MCM6246        | 36          | 400             | SOJ          | 0                |                  |         |                  |                     |

|         |                    | 35             | · _           | Micron   | MT5C512K8A1    | 32          | 400             | SOJ          |                  |                  |         |                  | _                   |

|         |                    | 35             |               | Micron   | MT5C512K8B2    | 36          | 400             | SOJ, TSOP    | 0                |                  |         |                  |                     |

|         |                    | 35             | —             | Micron   | MT5LC512K8C3   | 32          | 400             | SOJ          |                  |                  |         |                  |                     |

|         |                    | 35             | _             | Micron   | MT5LC512K8D4   | 36          | 400             | SOJ, TSOP    | 0                |                  |         |                  |                     |

| ľ       | 2M x 2             | 10             | -             | Motorola | MCM101524      | 36          | 400             | SOJ, SOP     | 0                |                  |         |                  | ECL                 |

|         |                    | 12             | —             | Motorola | MCM101524      | 36          | 400             | SOJ, SOP     | 0                |                  |         |                  | ECL                 |

|         |                    | 15             | —             | Fujitsu  | MBM100C524     | 32/36       | *               | SOJ, TSOP    | 0                |                  |         |                  |                     |

|         |                    | 15             | —             | Fujitsu  | MBM101C524     | 32/36       | *               | SOJ, TSOP    | 0                |                  |         |                  |                     |

|         |                    | 15             | —             | Fujitsu  | MBM10C524      | 32/36       | •               | SOJ, TSOP    | 0                |                  |         | 1                | -                   |

|         |                    | 15             | -             | Motorola | MCM101524      | 36          | 400             | SOJ, SOP     | 0                |                  |         |                  | ECL                 |

| Ĩ       | 1M x 4             | 20             | —             | Motorola | MCM6249        | 32          | 400             | SOJ          | 0                |                  |         |                  |                     |

|         |                    | 20             | _             | Micron   | MT5C1M4A1      | 32          | 400             | SOJ          | 1                |                  |         |                  | -                   |

|         |                    | 20             | -             | Micron   | MT5C1M4B2      | 32          | 400             | SOJ, TSOP    | 0                |                  |         |                  |                     |

|         |                    | 20             | —             | Micron   | MT5LC1M4C3     | 32          | 400             | SOJ          |                  |                  |         |                  | -                   |

|         |                    | 20             | —             | Micron   | MT5LC1M4D4     | 32          | 400             | SOJ, TSOP    | • •              |                  |         |                  |                     |

|         |                    | 20             | _             | NEC      | μPD434004      | 32/36       | 400             | SOJ          | 0                | _                |         |                  |                     |

|         |                    | 25             | -             | Hitachi  | HM624100       | 32          | 400             | SOJ, TSOP II | 0                |                  |         |                  |                     |

|         |                    | 25             | —             | Fujitsu  | MB82B206       | 36          | 400             | SOJ          | 0                |                  |         |                  |                     |

|         |                    | 25             | _             | Motorola | MCM6249        | 32          | 400             | SOJ          | 0                |                  |         |                  |                     |

|         |                    | 25             |               | Micron   | MT5C1M4A1      | 32          | 400             | SOJ          |                  |                  |         |                  |                     |

|         |                    | 25             | -             | Micron   | MT5C1M4B2      | 32          | 400             | SOJ, TSOP    | 0                |                  |         |                  |                     |

|         |                    | 25             | -             | Micron   | MT5LC1M4C3     | 32          | 400             | SOJ          |                  |                  | _       |                  |                     |

|         |                    | 25             | _             | Micron   | MT5LC1M4D4     | 32          | 400             | SOJ, TSOP    | 0                |                  |         |                  |                     |

|         |                    | 25             | —             | NEC      | μPD434004      | 32/36       | 400             | SOJ          | 0                |                  |         |                  |                     |

|         |                    | 30             | -             | Motorola | MCM6249        | 32          | 400             | SOJ          | 0                |                  |         |                  |                     |

|         |                    | 30             | -             | Hitachi  | HM624100       | 32          | 400             | SOJ, TSOP II | 0                |                  |         |                  |                     |

|         |                    | 35             | _             | Motorola | MCM6249        | 32          | 400             | SOJ          | 0                |                  |         |                  |                     |

|         |                    | 35             | —             | Hitachi  | HM624100       | 32          | 400             |              | 0                |                  |         |                  |                     |

|         |                    | 35             | -             | Fujitsu  | MB82B206       | 36          | 400             | SOJ          | 0                |                  |         |                  |                     |

|         |                    | 35             | _             | Micron   | MT5C1M4A1      | 32          | 400             | SOJ          |                  |                  |         |                  |                     |

|         |                    | 35             | _             | Micron   | MT5C1M4B2      | 32          | 400             | SOJ, TSOP    | 0                |                  |         |                  |                     |

SELECTOR GUIDE 1-4

| <      |   |

|--------|---|

| ō      | ļ |

| ㅋ      |   |

| 0      |   |

| עב     | Ì |

| 0      |   |

|        | ļ |

| 2      |   |

| - "    | Í |

| ώ      |   |

|        |   |

| S      | ļ |

| Ω,     |   |

| ≥      |   |

| $\leq$ |   |

| σ      | ĺ |

| Đ,     | 1 |

| H      |   |

| -      |   |

| Density | Config-<br>uration | Access<br>(ns) | Cycle<br>(ns) | Supplier | Part<br>Number | No.<br>Pins | Width<br>(mils) | Package       | Revol.<br>Pinout | Syn-<br>chronous | Latches  | Output<br>Enable | Special<br>Function |

|---------|--------------------|----------------|---------------|----------|----------------|-------------|-----------------|---------------|------------------|------------------|----------|------------------|---------------------|

|         |                    | 35             |               | Micron   | MT5LC1M4C3     | 32          | 400             | SOJ           |                  |                  |          |                  |                     |

|         |                    | 35             | -             | Micron   | MT5LC1M4D4     | 32          | 400             | SOJ, TSOP     | 0                |                  |          |                  |                     |

| ľ       | 4M x 1             | 10             | —             | Motorola | MCM101520      | 36          | 400             | SOJ, SOP, TAB | 0                |                  |          |                  | ECL                 |

|         |                    | 12             | _             | Motorola | MCM101520      | 36          | 400             | SOJ, SOP, TAB | 0                |                  |          | [                | ECL                 |

|         |                    | 15             | —             | Motorola | MCM101520      | 36          | 400             | SOJ, SOP, TAB | 0                |                  |          |                  | ECL                 |

|         |                    | 15             | -             | Fujitsu  | MBM100C520     | 32/36       |                 | SOJ, TSOP     | 0                |                  |          |                  |                     |

|         |                    | 15             |               | Fujitsu  | MBM101C520     | 32/36       |                 | SOJ, TSOP     | 0                |                  |          |                  |                     |

|         |                    | 15             |               | Fujitsu  | MBM10C520      | 32/36       |                 | SOJ, TSOP     | <u> </u>         |                  |          |                  |                     |

| 2M      | 32K x 72           |                | 15            | Motorola | MCM72BA32      | 1           |                 | SIMM          |                  | 0                |          | <u>ہ</u>         | 0                   |

|         | 1                  | -              | 16.6          | Motorola | MCM72BA32      |             |                 | SIMM          |                  | 0                |          | 0                | 0                   |

| ĺ       | 64K x 44           | 12             | -             | Motorola | MCM4464        | 80          |                 | SIMM          |                  |                  |          | <b></b>          |                     |

|         |                    | 15             | —             | Motorola | MCM4464        | 80          |                 | SIMM          |                  |                  |          | <b></b>          |                     |

|         |                    | 17             |               | Motorola | MCM4464        | 80          |                 | SIMM          | · · .            |                  |          | 0                |                     |

|         |                    | 17-5           | _             | Motorola | MCM4464SG      | 80          |                 | SIMM          |                  |                  |          | <b></b>          |                     |

| 2M      | 64K x 32           | -              | 20            | Motorola | MCM32AB64      | 112         |                 | SIMM          |                  |                  | ٥        | <b></b>          | 0                   |

|         |                    | _              | 30            | Motorola | MCM32AB64      | 112         |                 | SIMM          |                  |                  | 0        | 0                | <u> </u>            |

|         |                    | 15             | -             | Motorola | MCM3264A       | 64          |                 | ZIP           |                  |                  |          | <b>\$</b>        |                     |

|         |                    | 15             | -             | Micron   | MT8S6432Z      |             |                 |               |                  |                  | _        |                  |                     |

| 1       |                    | 15             | —             | IDT      | IDT7MP4036B    |             |                 |               | •                |                  |          |                  |                     |

|         |                    | 20             | —             | Motorola | MCM3264A       | 64          |                 | ZIP           |                  |                  |          | <b>\$</b>        |                     |

|         |                    | 20             | -             | AT&T     | ATTM3264       |             |                 |               |                  |                  |          |                  |                     |

|         |                    | 20             | —             | Micron   | MT8S6432Z      |             |                 |               |                  |                  |          |                  |                     |

|         |                    | 20             | —             | IDT      | IDT7MP4036B    |             |                 |               |                  |                  |          |                  |                     |

|         |                    | 15             | -             | Motorola | MCM32A64       | 128         |                 | SIMM          |                  |                  |          | <u>ہ</u>         |                     |

| 1       |                    | 20             |               | Motorola | MCM32A64       | 128         |                 | SIMM          |                  |                  |          | 0                |                     |

| 1M      | 32K x 32           | —              | 20            | Motorola | MCM32AB32      | 112         |                 | SIMM          |                  |                  | 0        | <b></b>          | 0                   |

|         |                    |                | 30            | Motorola | MCM32AB32      | 112         |                 | SIMM          |                  |                  | 0        | <b></b>          | ٥                   |

| ľ       | 64K x 18           | 12             | —             | Motorola | MCM67A618      | 52          |                 | PLCC          |                  |                  | <u>ہ</u> | 0                |                     |

|         |                    | 15             |               | Motorola | MCM67A618      | 52          |                 | PLCC          |                  |                  | 0        | 0                |                     |

|         |                    | 20             | -             | Motorola | MCM67A618      | 52          |                 | PLCC          |                  |                  | 0        | <b></b>          |                     |

|         |                    | 9              | 15            | Motorola | MCM67B618      | 52          |                 | PLCC          |                  | ٥                |          | <u>ہ</u>         | ٥                   |

|         |                    | 10             | 12.5          | Cypress  | CY7C1031       |             |                 |               |                  |                  |          |                  |                     |

|         |                    | 9              | 15            | IC Works | ICW73B596      | 1           |                 |               |                  |                  |          |                  |                     |

|         |                    | 12             | 20            | Motorola | MCM67B618      | 52          |                 | PLCC          | 1                | 0                |          | <u>ہ</u>         | 0                   |

|         |                    | 12             | 15            | Cypress  | CY7C1031       | <u> </u>    |                 |               |                  | -                |          | [                | -                   |

SELECTOR GUIDE 1-5

| Density | Config-<br>uration | Access<br>(ns) | Cycle<br>(ns) | Supplier | Part<br>Number | No.<br>Pins | Width<br>(mils) | Package | Revol.<br>Pinout | Syn-<br>chronous | Latches | Output<br>Enable | Special<br>Function |

|---------|--------------------|----------------|---------------|----------|----------------|-------------|-----------------|---------|------------------|------------------|---------|------------------|---------------------|

|         | ····               | 12             | 20            | IC Works | ICW73B596      |             | ( <b></b>       |         |                  |                  |         |                  |                     |

|         |                    | 18             | 25            | Motorola | MCM67B618      | 52          |                 | PLCC    |                  | 0                |         | •                | 0                   |

|         |                    | 14             | 20            | Cypress  | CY7C1031       |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 7              | 12.5          | Motorola | MCM67C618      | 52          |                 | PLCC    |                  | <u>ہ</u>         |         | 0                | <b></b>             |

|         |                    | 9              | 15            | Motorola | MCM67C618      | 52          |                 | PLCC    |                  | <u>ہ</u>         |         | 0                | 0                   |

|         |                    | 9              | 15            | Motorola | MCM67H618      | 52          |                 | PLCC    |                  | \$               |         | ٥                | ٥                   |

|         |                    | 12             | 20            | Motorola | MCM67H618      | 52          |                 | PLCC    |                  |                  |         | 0                | 0                   |

|         |                    | 18             | 25            | Motorola | MCM67H618      | 52          |                 | PLCC    |                  | <u>ہ</u>         |         | 0                | 0                   |

|         |                    | 7              | 12.5          | Motorola | MCM67J618      | 52          |                 | PLCC    |                  | 0                |         | 0                | <u>ہ</u>            |

|         |                    | 9              | 15            | Motorola | MCM67J618      | 52          |                 | PLCC    |                  | 0                |         | 0                | 0                   |

| 1       |                    | 9              | 12.5          | Motorola | MCM67M618      | 52          |                 | PLCC    |                  | 0                |         | 0                | 0                   |

|         |                    | 11             | 15            | Motorola | MCM67M618      | 52 -        |                 | PLCC    |                  | <u>ہ</u>         |         | 0                | 0                   |

|         |                    | 10             | 15            | Cypress  | CY7C1032       |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 14             | 20            | Motorola | MCM67M618      | 52          |                 | PLCC    |                  | \$               |         | 0                | ٥                   |

|         |                    | 19             | 25            | Motorola | MCM67M618      | 52          |                 | PLCC    |                  | <b>\$</b>        |         | 0                | 0                   |

|         |                    | 12             |               | Motorola | MCM67W618      | 52          |                 | PLCC    |                  |                  | 0       |                  |                     |

|         |                    | 15             | -             | Motorola | MCM67W618      | 52          |                 | PLCC    |                  |                  | 0       |                  |                     |

|         |                    | 20             | _             | Motorola | MCM67W618      | 52          |                 | PLCC    |                  |                  | 0       |                  |                     |

|         |                    | 20             | -             | Sharp    | LH521028       | 52          |                 |         |                  |                  |         |                  |                     |

| . 1     | 128K x 8           | 20             | _             | Motorola | MCM6226A       | 32          | 400             | SOJ     |                  |                  |         | 0                |                     |

|         |                    | 20             | _             | AT&T     | ATT7C109J      |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 20             | -             | IDT      | IDT711024S     |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 20             |               | Micron   | MT5C1008DJ     |             |                 |         | 1                |                  |         |                  |                     |

|         |                    | 20             | _             | NEC      | μPD431008      |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 20             | -             | Sharp    | LH521007K      |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 20             |               | Sony     | CXK581120J     |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 20             | -             | Samsung  | KM681001       |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 25             | _             | Motorola | MCM6226A       | 32          | 400             | SOJ     |                  |                  |         | 0                |                     |

|         |                    | 25             | -             | AT&T     | ATT7C109J      |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 25             | _             | Cypress  | CY7C109        |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 25             | -             | IDT      | IDT711024S     |             |                 |         | 1                |                  |         |                  |                     |

|         |                    | 25             | -             | Micron   | MT5C1008DJ     |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 25             | -             | Samsung  | KM681001       |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 25             | -             | Sharp    | LH521007K      |             |                 |         |                  |                  |         |                  |                     |

|         |                    | 35             |               | Motorola | MCM6226A       | 32          | 400             | SOJ     |                  |                  |         | 0                |                     |

SELECTOR GUIDE

MOTOROLA FAST SRAM DATA

| ≤        |   |

|----------|---|

| ō        |   |

| Ē        |   |

| <u>o</u> |   |

| 2        |   |

| Ч        |   |

| ≻        | ļ |

| Ξ.       | i |

| ≥        |   |

| പ്പ      |   |

| ~        |   |

| ч<br>Ч   |   |

| 5        |   |

| ź        |   |

| Ē        |   |

| ¥        |   |

| Э        |   |

| م        |   |

|          |   |

| Density | Config-<br>uration | Access<br>(ns) | Cycle<br>(ns) | Supplier | Part<br>Number | No.<br>Pins | Width<br>(mils) | Package | Revol.<br>Pinout | Syn-<br>chronous | Latches     | Output<br>Enable | Special<br>Function |

|---------|--------------------|----------------|---------------|----------|----------------|-------------|-----------------|---------|------------------|------------------|-------------|------------------|---------------------|

|         |                    | 35             | _             | Cypress  | CY7C109        | 1           |                 |         |                  |                  |             |                  |                     |

|         |                    | 35             |               | Micron   | MT5C1008DJ     |             | <u>├</u>        |         | <u> </u>         |                  |             |                  |                     |

|         |                    | 35             |               | Samsung  | KM681001       |             |                 |         |                  |                  |             |                  |                     |

|         |                    | 35             |               | Sharp    | LH521007K      |             |                 |         |                  |                  |             |                  |                     |

|         |                    | 35             | -             | Sony     | CXK581020SJ    |             |                 |         |                  |                  |             |                  |                     |

|         |                    | 45             |               | Motorola | MCM6226A       | 32          | 400             | SOJ     |                  |                  |             | 0                |                     |

|         |                    | 45             |               | Cypress  | CY7C109        |             |                 |         |                  |                  |             |                  |                     |

|         |                    | 45             | -             | Micron   | MT5C1008DJ     |             |                 |         |                  |                  |             |                  |                     |

|         |                    | 45             | _             | Sony     | CXK581020SJ    |             |                 |         |                  |                  |             |                  |                     |

|         |                    | 15             | _             | Motorola | MCM6226B       | 32          | 300/400         | SOJ     |                  |                  |             | 0                |                     |

| 1       |                    | 15             |               | AT&T     | ATT7CC108      |             | 11              |         |                  |                  |             |                  |                     |

|         |                    | 15             | —             | Quality  | QS812880       |             |                 |         |                  |                  |             | -                |                     |

| 1       |                    | 17             |               | Motorola | MCM6226B       | 32          | 300/400         | soj     | <u> </u>         |                  |             | 0                |                     |

|         |                    | 20             | -             | Motorola | MCM6226B       | 32          | 300/400         | SOJ     |                  |                  |             | 0                |                     |

|         |                    | 20             | _             | Quality  | QS812880       |             |                 |         |                  |                  |             | -                |                     |

|         |                    | 25             | _             | Motorola | MCM6226B       | 32          | 300/400         | SOJ     |                  |                  |             | 0                |                     |

|         |                    | 25             |               | Quality  | QS812880       |             |                 |         |                  |                  |             |                  |                     |

|         |                    | 35             |               | Motorola | MCM6226B       | 32          | 300/400         | SOJ     |                  |                  | ·           | <u>ہ</u>         |                     |

| ļ       |                    | 8              | -             | Motorola | MCM6726A       | 32          | 400             | soj     | 0                |                  |             | 0                |                     |

|         |                    | 10             |               | Motorola | MCM6726        | 32          | 400             | soj     | 0                |                  |             | 0                |                     |

|         |                    | 10             | -             | Motorola | MCM6726A       | 32          | 400             | SOJ     | 0                |                  |             | 0                |                     |

|         |                    | 10             | -             | IDT      | IDT71B124      |             |                 |         |                  |                  |             |                  |                     |

|         |                    | 10             | -             | Samsung  | KM68B1002      |             | 11              |         |                  |                  |             |                  |                     |

|         |                    | 12             | -             | Motorola | MCM6726        | 32          | 400             | SOJ     | 0                |                  |             | <u>ہ</u>         |                     |

|         |                    | 12             | -             | Motorola | MCM6726A       | 32          | 400             | SOJ     | 0                |                  |             | 0                |                     |

|         |                    | 12             | —             | IDT      | IDT71B124      |             |                 |         |                  |                  |             |                  |                     |

|         |                    | 15             | -             | Motorola | MCM6726        | 32          | 400             | SOJ     | 0                |                  |             | ٥                |                     |

|         |                    | 15             |               | Motorola | MCM6726A       | 32          | 400             | SOJ     | 0                |                  |             | 0                |                     |

|         |                    | 15             | —             | IDT      | IDT71B124      |             |                 | ·       |                  |                  |             |                  |                     |

|         | 128K x 9           | 16             | _             | Motorola | MCM67D709      | 52          |                 | PLCC    | 0                | ٥                |             | <b></b>          |                     |

|         |                    | 20             | —             | Motorola | MCM67D709      | 52          |                 | PLCC    | 0                | 0                |             | 0                |                     |

|         |                    | 5              | 10            | Motorola | MCM67Q709      |             |                 |         | 0                | 0                |             | [                |                     |

|         |                    | 6              | 12            | Motorola | MCM67Q709      |             |                 |         | 0                | 0                |             | [                |                     |

|         | 256K x 4           | 20             |               | Motorola | MCM6229A       | 28          | 400             | SOJ     |                  |                  |             | 0                |                     |

| 1       |                    | 20             |               | AT&T     | ATT7C106J      |             | 1               |         |                  |                  | · · · · · · |                  |                     |

1

SELECTOR GUIDE 1-7

| Density | Config-<br>uration | Access<br>(ns) | Cycle<br>(ns) | Supplier   | Part<br>Number | No.<br>Pins | Width<br>(mils) | Package | Revol.<br>Pinout | Syn-<br>chronous | Latches | Output<br>Enable | Special<br>Function |

|---------|--------------------|----------------|---------------|------------|----------------|-------------|-----------------|---------|------------------|------------------|---------|------------------|---------------------|

|         |                    | 20             |               | Hitachi    | HM624256AJ     | 1           |                 |         |                  |                  |         |                  |                     |