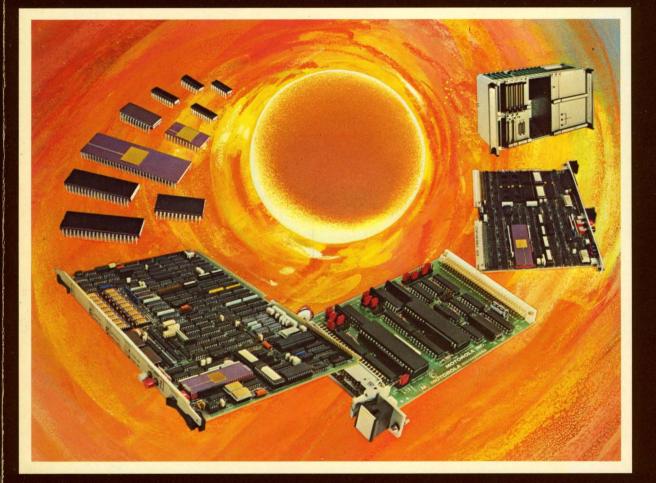

# 16/32-BIT MICROCOMPUTER SYSTEM COMPONENTS

MOTOROLA INC.

D 127

The information in this book has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies.

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola and 🛞 are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity/Affirmative Action Employer.

Motorola, Inc. general policy does not recommend the use of its components in life support applications wherein a failure or malfunction of the component may directly threaten life or injury. Per Motorola Terms and Conditions of Sale, the user of Motorola components in life support applications assumes all risks of such use and idemnifies Motorola against all damages.

| VMEmodules                                       | 1 |

|--------------------------------------------------|---|

| VERSAmodules                                     | 2 |

| I/Omodules                                       | 3 |

| <b>Operating Systems</b>                         | 4 |

| Development Systems                              | 5 |

| Bus Technical Summaries                          | 6 |

| Customer Support                                 | 7 |

| Appendices<br>Module Current<br>Supplied Current | 8 |

| Index                                            | 9 |

Benchmark 20, EXORbus, EXORciser<sup>®</sup>, EXORdisk, EXORmacs<sup>®</sup>, EXORset, EXORterm, HDS-200, HDS-400, HDSdebug, I/Omodule, MACSbug, MDOS, Micromodule, RAMbus, RMS68K, SYMbug, SYSTEM V/68, TENbug, UNIbug, UNIdos, UNItst, VERSAbug, VERSAbus, VERSAdos, VERSAmodule, VMC 68/2, VMEbug, VMEmodule, VME/10, and 020bug are trademarks of Motorola Inc.

DEC, PDP-11, VAX and VMS are trademarks of Digital Equipment Corporation. Ethernet® is a registered trademark of Xerox Corporation LARK is a trademark of Control Data Corporation. SASI is a trademark of Shugart Associates. UNIX is a trademark of AT&T Bell Laboratories.

The MVMEBUG, MVME101BUG, M68KVBUG, M68KVBUG2 and M68KVBUG3 EPROM sets are copyrighted by Motorola and may be copied only under prior written agreement from Motorola. MVMEBUG1, MVMEBUG2, MVME101BUGLF, MVME101BUGLC, M68KVBUGLC, M68KVBUG2LF, M68KVBUG2LF, M68KVBUG2LF, M68KVBUG2LC, M68KVBUG3LC Sources are copyrighted and licensed by Motorola. They may be obtained only under the required license agreement with Motorola.

#### Standard Warranty

Seller warrants that its products sold hereunder will at the time of shipment be free and clear of all liens and encumbrances and will be free from defects in material and workmanship and will conform to Seller's applicable specifications or, if appropriate, to Buyer's specifications accepted by Seller in writing If products sold hereunder are not as warranted, Seller shall, at its option, refund the purchase price, repair, or replace the product, provided proof of purchase and written notice of nonconformance is received by Seller within ninety (90) days from date of initial shipment, and provided said nonconforming products are, with Seller's written authorization,\* returned FOB Seller's plant or authorized repair center within thirty (30) days from expiration of said ninety (90) day period. Upon verification by Seller that the product does not confirm to this warranty, Seller will pay the cost of transporting such replacement of repaired goods to Buyer's plant within the contiguous 48 United States and Canada. This warranty shall not apply to any products Seller determines have been, by Buyer or otherwise, subjected to testing for other than specified electrical characteristics or to operating and/or environmental conditions in excess of the maximum values established in applicable specifications, or have been the subject of mishandling, misuse, neglect, improper testing, repair, alteration, damage, assembly or processing that alters physical or electrical properties. This warranty excludes all costs of shipping, customs clearance and related charges outside the contiguous 48 United States and Canada.

IN NO EVENT WILL SELLER BE LIABLE FOR ANY INCIDENTAL OR CONSEQUENTIAL DAMAGES. THIS WARRANTY EXTENDS TO BUYER ONLY AND NOT TO BUYER'S CUSTOMERS OR USERS OF BUYER'S PRODUCTS AND IS IN LIEU OF ALL OTHER WARRANTIES WHETHER EXPRESS, IMPLIED OR STATUTORY INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS.

\*Customer Return Authorization Number is available from Four-Phase Field Engineering. Call toll-free to your regional office: Eastern (800) 538-9832, Central (800) 538-9841, Western (800) 538-9800, and California Only (800) 662-9260.

# M) MOTOROLA

# 16/32-BIT MICROCOMPUTER SYSTEM COMPONENTS

Prepared by Technical Information Center

### Preface

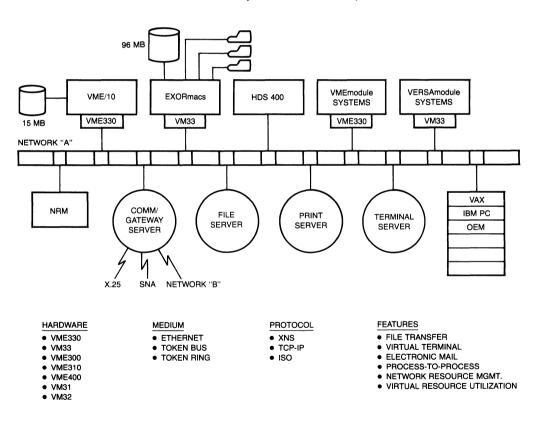

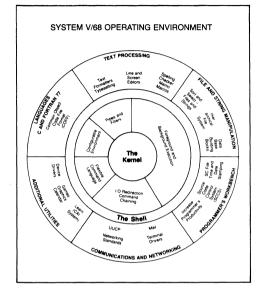

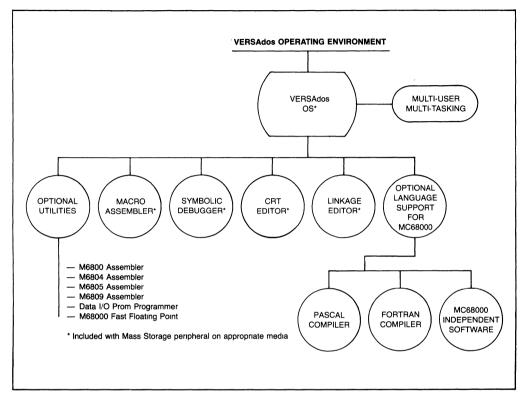

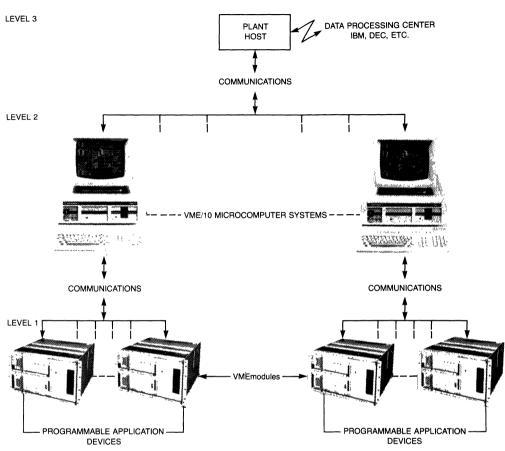

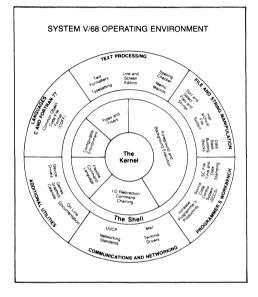

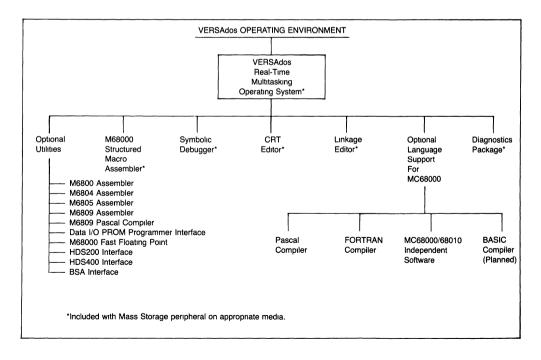

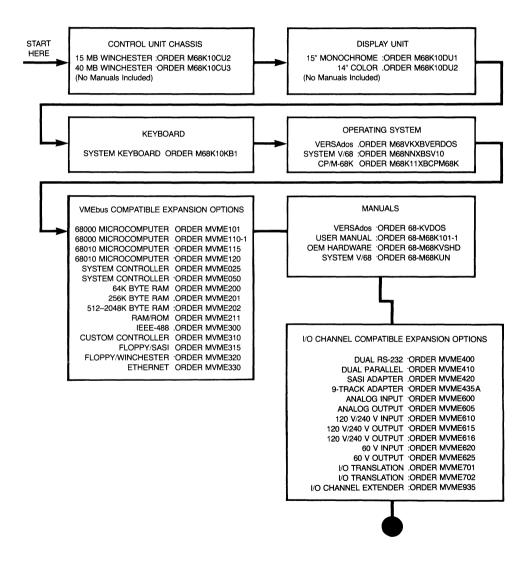

Following Motorola's tradition of serving current and future needs of the fast evolving electronics market, Motorola Microsystems offers a range of high-quality microcomputer systems, modular components, peripherals and associated hardware and software. Support for design and development or configuration and integration of OEM products for today's MC68000-, MC68008- and MC68010-based products is provided by the SYSTEM V/68 and VERSAdos Operating Systems and by development hardware/software tools, development instrumentation and board level system components. Support for tomorrow's MC68020-based OEM products will be assured by MC68020 hardware/software tools, MC68020 development instrumentation, board-level MC68020 system components and a multiprocessor operating system.

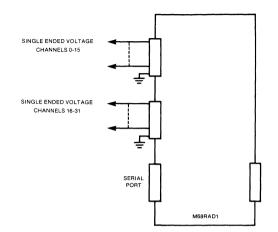

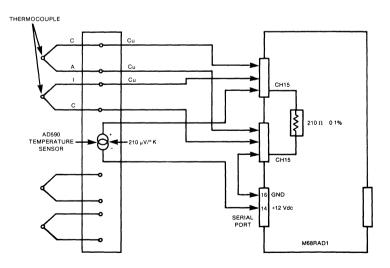

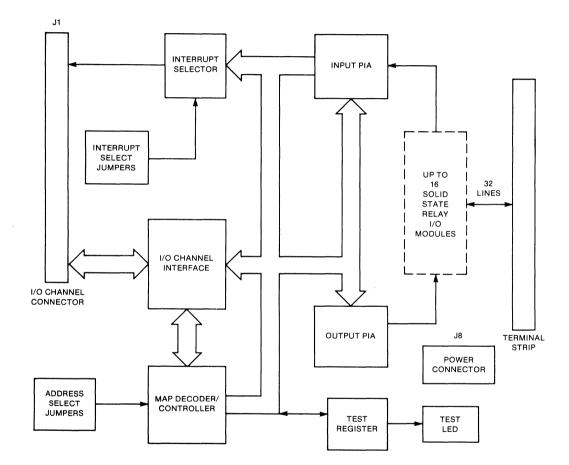

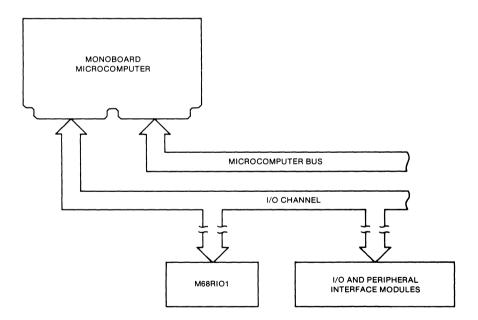

Today's OEM is offered a wide selection of microcomputer system functions implemented for Motorola's standard VERSAbus as VERSAmodules and for the international standard VMEbus as VMEmodules. A number of communications, peripheral control and industrial control functions implemented for Motorola's standard I/O Channel adjunct to VERSAbus and VMEbus are also available to the OEM for his products.

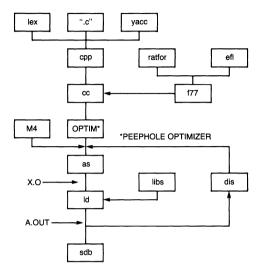

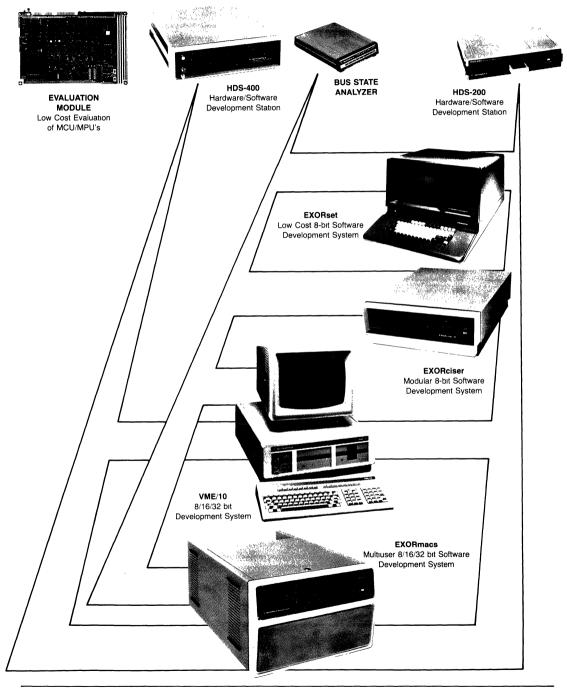

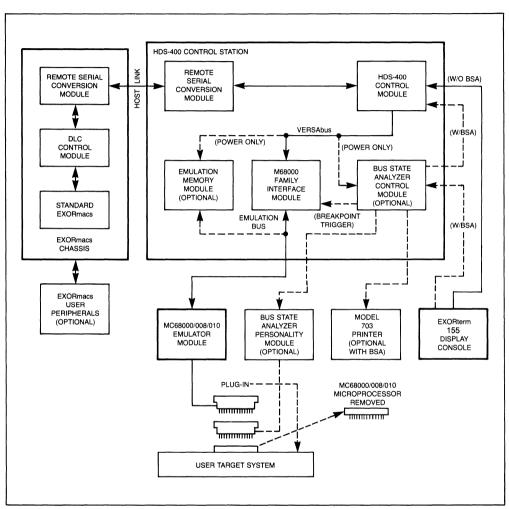

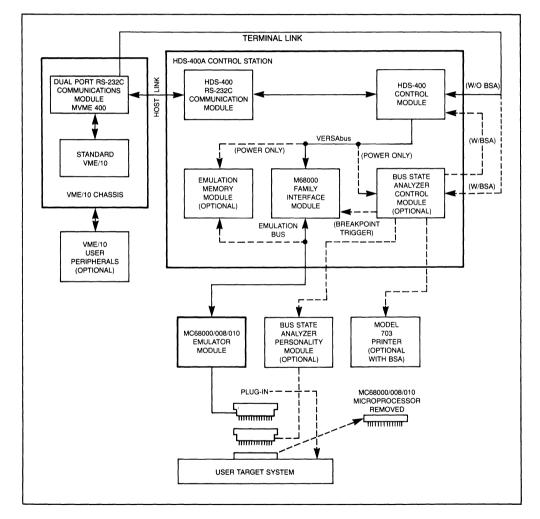

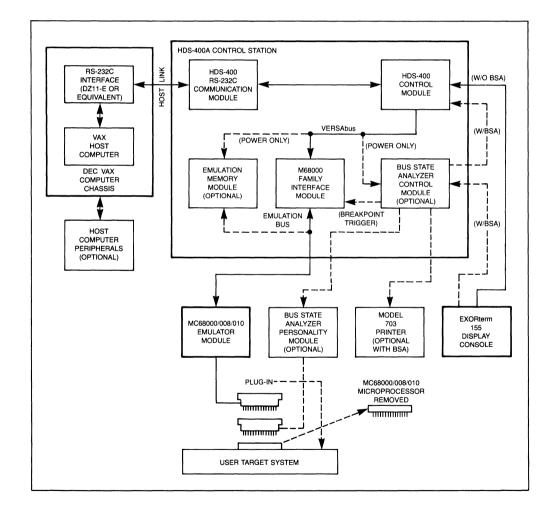

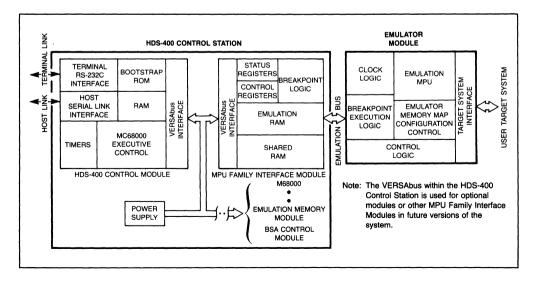

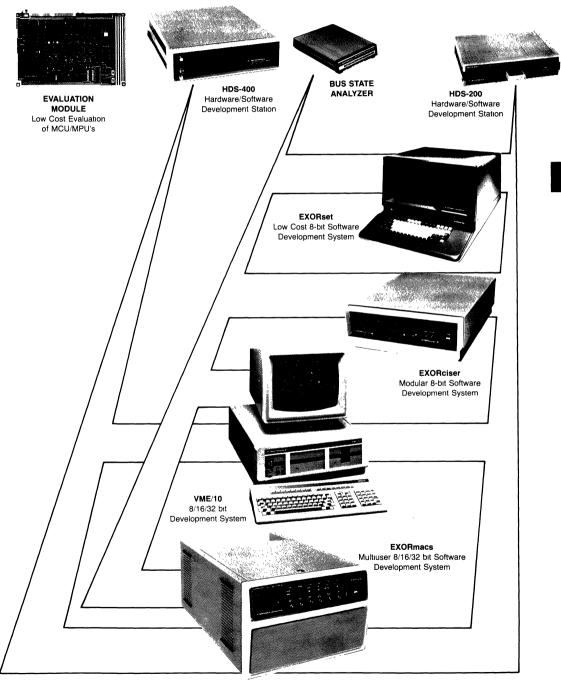

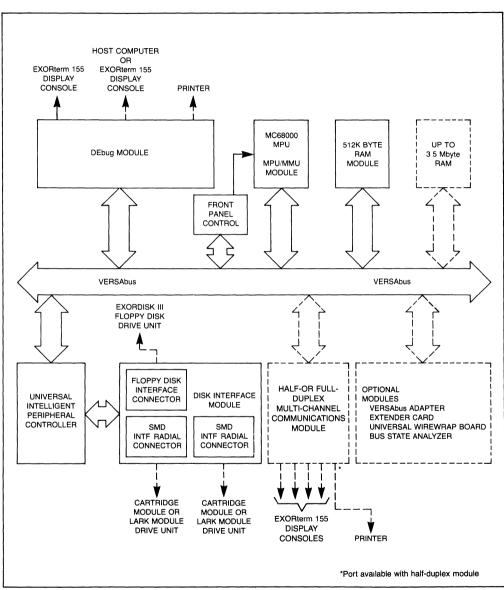

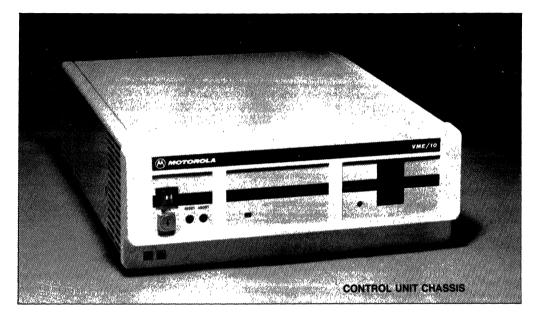

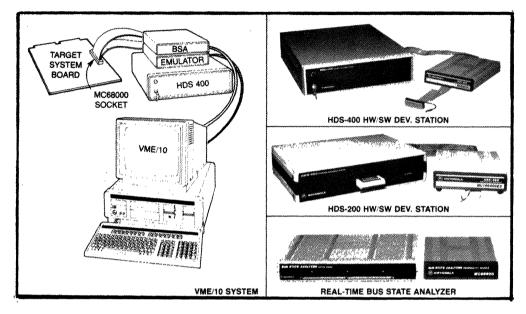

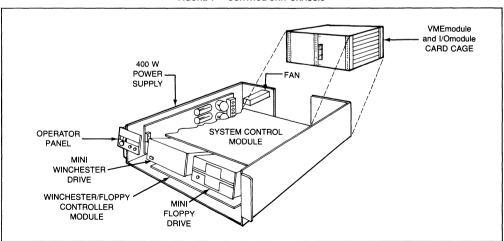

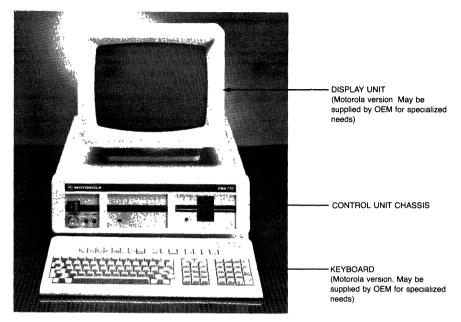

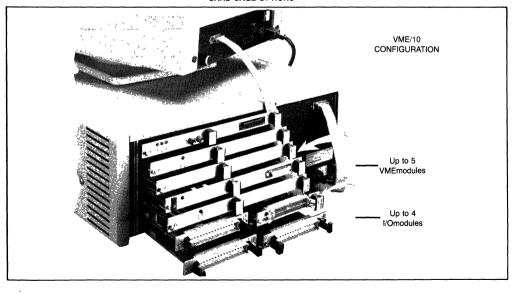

Complementing this broad range of board level, 16/32-bit microcomputer system components, Motorola Microsystems offers the OEM three categories of products which aid the design of microcomputer systems and shorten their development time. These are: 1. powerful host/development systems including the advanced VME/10 OEM Microcomputer System and the EXORmacs Development System running under the SYSTEM V/68 operating system or the VERSAdos Real-Time Multitasking Operating System, 2. development instrumentation including the HDS-400 Microprocessor Hardware/Software Development State anulation of any member of the family of Motorola 16/32-bit microprocessors and including, also, the Bus State Analyzer which samples the system bus allowing operations and events to be recorded for analysis, and 3. software support in the form of operating systems, highlevel languages support for development systems and debugging packages for VMEmodule and VERSAmodule monoboard microcomputers.

> First Edition MOTOROLA INC., 1984 "All Rights Reserved"

Printed in U.S.A.

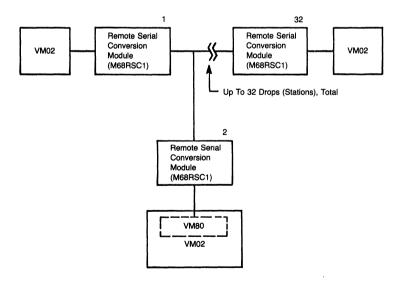

MOTOROLA 16/32-BIT MICROCOMPUTER SYSTEM COMPONENTS

Microprocessor applications range in complexity from those using board level products in systems of 8/16-bit data/address paths and having modest data transfer rates to those for which solutions will be found using the 32-bit MC68020 which accesses 4 gigabytes of linear memory space and executes 2.5 million instructions per second.

For those applications requiring a system providing rugged mechanical structure, non-multiplexed and asynchronous data transfers, a powerful interrupt structure. flexible data and address paths, support for system failure detection and data transfer rates up to 40 megabytes per second, Motorola's VMEbus-compatible board level products - VMEmodules - can offer a quick solution.

Since its introduction in October, 1981, the VMEbus Interconnect System has gained such acceptance that it has become a de facto world standard. The bus is presently being standardized by both the IEEE and the IEC. Both a VMEbus Manufacturers Group and a VMEbus Users Group have been formed; the former to assure a high degree of technical compatibility between products and the latter to promote understanding of the bus, related hardware, operating systems and applications software.

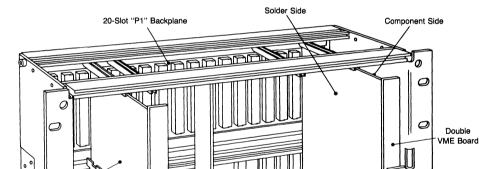

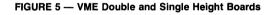

VMEmodule compatibility with VMEbus results in many benefits for board level product users. One benefit is that since VMEbus is based on the EUROCARD standard which specifies not only the board format but also the enclosures, card racks and connectors, there is a high degree of mechanical and electromechanical interchangeability between the products of all vendors.

Presently, there are more than 500 products available from the more than 100 vendors worldwide giving the user an ever-widening range of choices for his designs. In addition, Motorola, Signetics and others are committed to the design and production of LSI-implemented bussupport functions which make interfacing the VMEbus easier and will result in the availability of an even greater variety of powerful VMEbus-compatible products.

# **VMEmodule Data Sheets**

| MVMEBUG      | VMEbug Debugging Package<br>for MVME110-1                                                                     | 1 0          |

|--------------|---------------------------------------------------------------------------------------------------------------|--------------|

| MVMEBUG1     | VMEbug Source Object<br>Modules on VERSAdos                                                                   | 1-2          |

|              | Dskt.                                                                                                         | 1-2          |

| MVMEBUG2     | VMEbug Source Object<br>Modules on VERSAdos                                                                   | 4.0          |

| MVME025      | CartSystem Controller                                                                                         | 1-2          |

| MVME101      | VMEmodule<br>MC68000 VMEmodule Mono-                                                                          | 1-6          |

| MVME101BUG   | board Microcomputer                                                                                           | 1-8          |

|              | Debugging Package for<br>MVME101 MPU Module                                                                   | 1-17         |

| MVME101BUGLF | 101bug Source Object<br>Module on VERSAdos<br>Dskt                                                            | 1-17         |

| MVME101BUGLC | 101bug Source Object<br>Module on VERSAdos                                                                    | 1-17         |

| MVME110-1    | Cart<br>MC68000 VMEmodule Mono-                                                                               | 1-17         |

|              | board Microcomputer                                                                                           | 1-20         |

| MVME115M     | VMEmodule Monoboard<br>Microcomputer                                                                          | 1-27         |

| MVME200      | 64K Byte Dynamic RAM<br>Module                                                                                | 1-31         |

| MVME201      | 256K Byte Dynamic RAM                                                                                         |              |

| MVME202      | Module                                                                                                        | 1-31<br>1-37 |

| MVME222-1    | 1 Mbyte Dynamic RAM<br>Module                                                                                 | 1-37         |

| MVME222-2    | 2 Mbyte Dynamic RAM                                                                                           |              |

| MVME211      | Module<br>Static RAM/ROM/EPROM                                                                                | 1-37         |

| MVME300      | Memory Module<br>IEEE-488<br>Listener/Talker/Controller                                                       | 1-41         |

|              | Module                                                                                                        | 1-44         |

| MVME310      | Controller Module                                                                                             | 1-52         |

| MVME315      | Intelligent Peripheral                                                                                        | 1-57         |

| MVME320      | Winchester/Floppy Disk                                                                                        |              |

| MVME330      | Controller                                                                                                    | 1-63         |

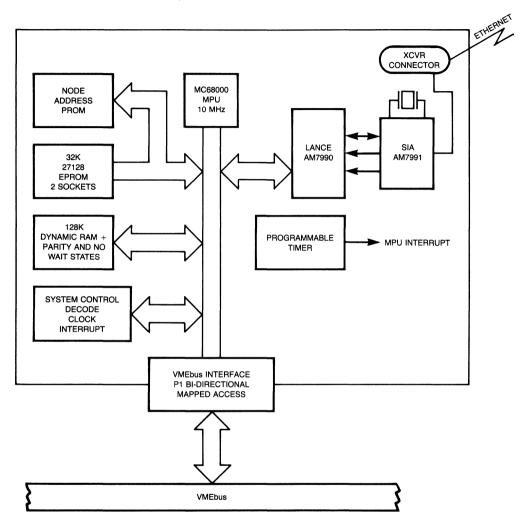

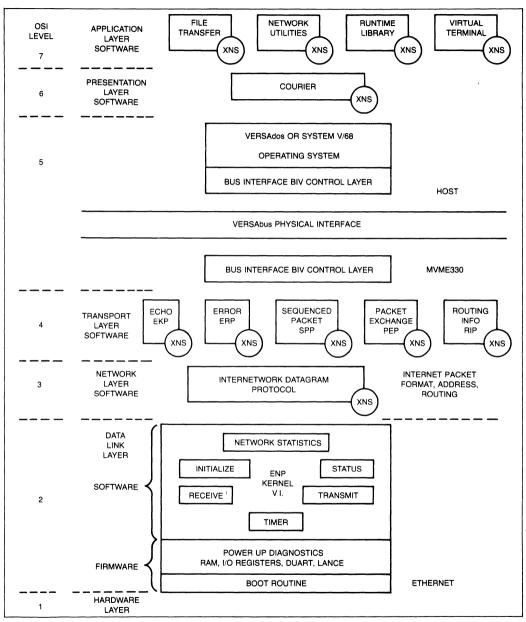

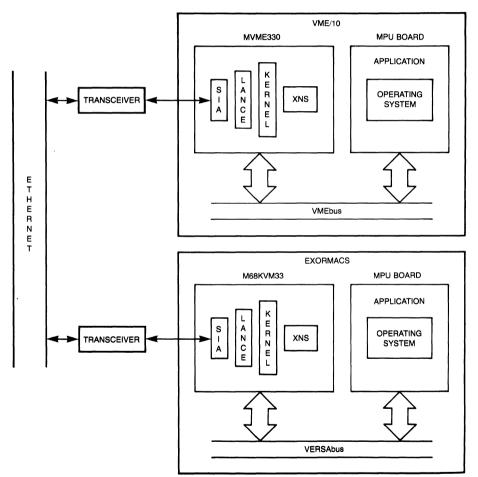

|              | Processor/LAN Controller                                                                                      | 1-67         |

| MVME910-3    | Module                                                                                                        |              |

| MVME911      | Switching Power Supply VMEmodule 300 Watt                                                                     | 1-77         |

| MVME920      | Switching Power Supply<br>20-Slot VMEbus Backplane<br>9-Slot VMEbus Backplane<br>5-Slot I/O Channel Backplate | 1-77         |

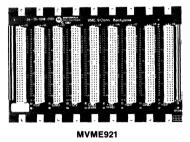

| MVME921      | 9-Slot VMEbus Backplane                                                                                       | 1-77<br>1-77 |

| MVME922      | 5-Slot I/O Channel Backplate                                                                                  | 1-77         |

| MVME930      | VIVIEDUS Extender Module                                                                                      | 1-77         |

| MVME931-1    | VMEbus Wirewrap Module,                                                                                       | 1-77         |

| MVME932      | VMEbus Extender Module                                                                                        | 1-77         |

| MVME933-1    | VMEbus Wirewrap Module.                                                                                       |              |

| MVME935      | Single High                                                                                                   | 1-77         |

| MVME940-1    | Pin Header                                                                                                    | 1-77         |

|              | Channel Chassis with 200                                                                                      |              |

|              | Watt Switching Power                                                                                          | 1-77         |

| MVME941      | Supply                                                                                                        |              |

| MVME942      | Channel Card Cage<br>20-Slot VMEbus Card Cage                                                                 | 1-77         |

# MVMEBUG MVMEBUG1 MVMEBUG2

# VMEbug Debugging Packages for the VMEmodule Monoboard Microcomputer

#### VMEbug Resident Package

- EPROM Resident System DEbug Monitor

- More Than 30 Commands for DEbug, Up/Downline Load

- Single-line Assembler/Disassembler for Assembly Language Program Development

- Full Speed Execution of System and User-Developed Programs Operating in the VMEmodule Monoboard Microcomputer System

- Virtual Terminal Capability for Up/Downline Load from an EXORmacs Development System or from a Cross-Computer

- Powerful Software and System DEbug Command Set Allows Access to all VMEmodule I/O, Control and Memory Facilities Plus the Full 16M Byte Direct Address Range of the VMEbus System Bus

- Includes all Required Installation and Operation

Documentation

- Includes Bootstrap Loader for both MVME420, SASI Peripheral Adapter and the M68RWIN1 Disk Controller

# VMEbug Source and Relocatable Object Module Package

- Source and Relocatable Object Modules for VMEbug on Diskette or Cartridge Disk

- Relocatable Object Modules Allow Users to Include Only the VMEbug Items Needed in Their End System; to Link in Their Own Up/Downline Loader; and/or to Link in Their Own Bootstrap Loader

- Source Modules Allow User Modification of VMEbug as Desired

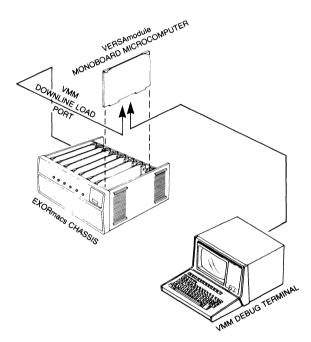

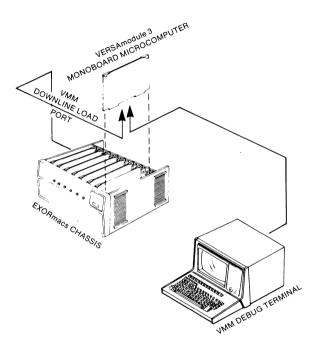

The VMEmodule Monoboard Microcomputer debug package, VMEbug, is available as two separate product offerings. VMEbug is an EPROM-based resident package ready for installation and immediate use with the VMEmodule Monoboard Microcomputer installed in a VMEbus based backplane. Such a backplane is provided within Motorola's VMEmodule Chassis (MVME940). VMEbug Source and Relocatable Object Modules are a separate product available on either VERSAdos compatible diskette, or cartridge

VMEbug provides a powerful evaluation and system debugging tool for VMEmodule Systems. The EPROM Resident Package will operate in 32K bytes of ROM space. VMEbug uses the first 1152 words of RAM storage for Interrupt Vectors and temporary storage. The EPROM resident package is delivered in four 8K byte EPROMs. Table 1 lists the commands available to the user.

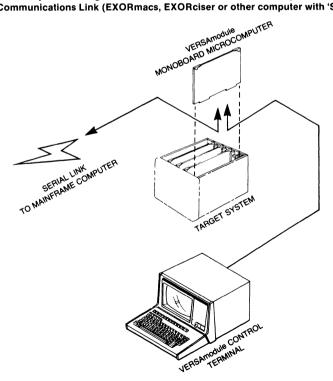

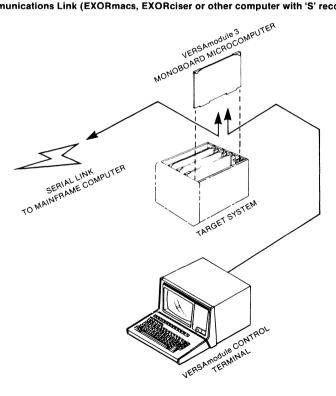

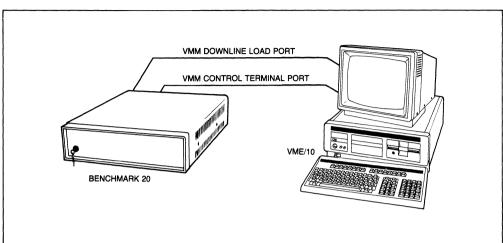

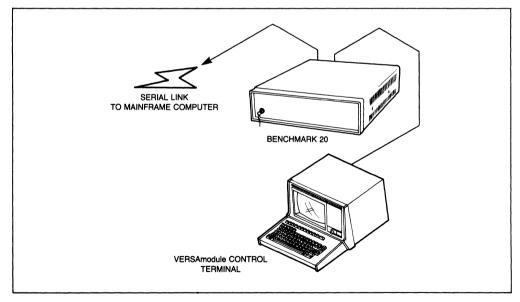

The package permits execution of system and userdeveloped programs operated in a VMEmodule Monoboard Microcomputer system environment under complete operator control. VMEbug may be utilized with a VMEmodule Monoboard Microcomputer in a standalone environment with only a user provided standard RS-232C asynchronous ASCII terminal. Alternately, it may be used with a second serial I/O port connected to a host computer for up/downline loading of programs in Motorola "S" Record format. When connected to a host computer in this manner, the VMEmodule/VMEbug/ Operator Terminal combination appears as a normal asynchronous ASCII terminal (a virtual terminal) to the host operating system. The second serial I/O port, the host computer interface, would be implemented through an I/Omodule board or other similar functional element. VMEbug may also be used with the MVME420 or the M68RWIN1 controllers (or both) and appropriate disks to load programs from disk to memory.

In a typical debug session, the user will download his program to a VMEmodule Monoboard from the host computer used for software development. After loading, VMEbug commands may be used to examine and modify memory, set breakpoints to run particular program segments, and track program progress. The user may set up and examine a variety of conditions using any of the powerful commands listed in Table 1, such as the Register Display/Set series and the

### MVMEBUG MVMEBUG1 MVMEBUG2

memory block manipulation commands. The Data Conversion command serves as an aid in examining and modifying data by converting hexadecimal to decimal, and decimal to hexadecimal. If corrections or program patches are required, these may be performed and checked in the VMEmodule. The user may have a corrected copy to the host computer files by using the Memory Dump command for upline load. Creating program patches may be aided by use of the Display Offsets command to assist with relocatable and positionindependent code. The user may also copy all traffic to the serial port debug terminal on a printer attached to an auxiliary parallel port by use of the Attach Printer command. This may be useful for desk debugging following a debug session. The parallel printer interface port may be implemented through the appropriate I/Omodule board.

The user may communicate with the host computer as a terminal for purposes other than up/downline load by executing the Transparent Mode command or the Send Message to Port 2 command. By using the Port Format command, the serial port may be reconfigured for such attributes as baud rate, stop bits and number of data bits. In the Transparent Mode, the two serial ports must operate at the same baud rate.

Bootstrap load and dump commands permit the user to

bootstrap from several controller/device combinations. The controller boards currently supported are the M68RWIN1 Winchester Disk Controller and the MVME420 SASI Peripheral Adapter. The drives currently supported are the 5¼" Winchester and the 5¼" Floppy or 8" Floppy on the M68RWIN1, and the 8" Winchester and 8" Floppy on the MVME420. The Boot Dump command permits the user to write his operating system to a diskette/disk in bootstrap load format for subsequent use in boot loading. The IOP command permits the user to create the diskette/disk format required.

VMEbug may be used for debug in total systems environments which include the VMEmodule Monoboard Microcomputer and with other Motorola VMEmodules as well as userdeveloped VMEbus compatible modules.

The Source and Relocatable Object Module Package provides users with the information to link VMEbug into their specific systems in either modified or unmodified form. The Relocatable Object Modules are designed to permit creation of a load module with or without the "S" Record up/downline loader. Users may also apply the Relocatable Object Modules substituting their own device bootstrap loader for the VMEbug disk bootstrap loader.

Source Modules permit the user to modify or customize any of the VMEbug functions as desired.

| Command                                                            | Description                               |  |  |  |

|--------------------------------------------------------------------|-------------------------------------------|--|--|--|

| MD < addr1> [ <count>]</count>                                     | Memory Display/Disassembly                |  |  |  |

| MM < address > [; <opts>]</opts>                                   | Memory Modify/Disassembly/Assembly        |  |  |  |

| MS < address > < data>                                             | Memory Set                                |  |  |  |

| A0A7 [ <expression>]</expression>                                  | Display/Set Address Register              |  |  |  |

| .D0D7 [ <expression>]</expression>                                 | Display/Set Data Register                 |  |  |  |

| .PC [ <expression>]</expression>                                   | Display/Set Program Counter               |  |  |  |

| .SR [ <expression>]</expression>                                   | Display/Set Status Register               |  |  |  |

| .SS [ <expression>]</expression>                                   | Display/Set Supervisor Stack Pointer      |  |  |  |

| US [ <expression>]</expression>                                    | Display/Set User Stack Pointer            |  |  |  |

| DF                                                                 | Display Formatted Registers (All)         |  |  |  |

| BF <address1><address2><word></word></address2></address1>         | Block Fill (with 16-bit data word) Memory |  |  |  |

| BM <address1><address2><address3></address3></address2></address1> | Block Move                                |  |  |  |

| BS' <address 1=""><address 2=""><data></data></address></address>  | Block of Memory Search                    |  |  |  |

| BI <address1><address2></address2></address1>                      | Block Initialize                          |  |  |  |

| BT <address1><address2></address2></address1>                      | Block Test of Memory                      |  |  |  |

| DC <expression></expression>                                       | Data Conversion                           |  |  |  |

| OF                                                                 | Display Offsets                           |  |  |  |

| .R0R6 [ <expression>]</expression>                                 | Display/Set Relative Offset Register      |  |  |  |

#### TABLE 1 — VMEbug Commands

# MVMEBUG MVMEBUG1 MVMEBUG2

| Command                                                                 | Description                                                                |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------|

| BR [ <address>[;<count>]]</count></address>                             | Breakpoint Set (up to 8)                                                   |

| NOBR [ <address><address>]</address></address>                          | Breakpoint Remove (any or all)                                             |

| GO [ <address>]</address>                                               | Execute Program                                                            |

| GT <breakpoint address=""></breakpoint>                                 | Go Until Breakpoint (sets temporary breakpoint)                            |

| GD [ <address>]</address>                                               | Go Direct (No Breakpoint or Track Set, and<br>no Exception Vector Changes) |

| TR [ <count>]</count>                                                   | Trace (set for number of instructions)                                     |

| TT <breakpoint address=""></breakpoint>                                 | Trace to Temporary Breakpoint                                              |

| PA                                                                      | Printer Attach (Print as well as display)                                  |

| NOPA                                                                    | Reset Printer Attach                                                       |

| PF [ <port number="">]</port>                                           | Port Format (set Serial Port Attributes)                                   |

| TM [ <exit character="">]</exit>                                        | Transparent Mode (Two serial ports                                         |

|                                                                         | transparently connected)                                                   |

| *text                                                                   | Send Message to Port 2                                                     |

| HE                                                                      | HELP (Display VMEbug commands)                                             |

| DU <address1> <address2><text></text></address2></address1>             | Dump ("S" Record Upline load)                                              |

| LO [; <opts>] [ = text]</opts>                                          | Load ("S" Record Downline load)                                            |

| VE [=text]                                                              | Verify ("S" Record Downline load verify)                                   |

| BD [ <device>] [<controller>]</controller></device>                     | Boot Dump                                                                  |

| BH [ <device>] [<controller>]</controller></device>                     | Bootstrap Halt                                                             |

| BO [ <device>] [<controller>] [<string>]</string></controller></device> | Bootstrap Operating System                                                 |

| IOP                                                                     | I/O Physical to Disk                                                       |

| ЮТ                                                                      | I/O "Teach" to Disk                                                        |

| Command Line Edit and Control Functions:                                |                                                                            |

| (BREAK)                                                                 | Abort Command                                                              |

| (DEL)                                                                   | Delete Character                                                           |

| (CTRL-D)                                                                | Redisplay Line                                                             |

| (CTRL-H)                                                                | Delete Character                                                           |

| CTRL-W)                                                                 | Suspend Output*                                                            |

| CTRL-X)                                                                 | Cancel Command Line                                                        |

| (cr)                                                                    | Send Line to Memory                                                        |

#### TABLE 1 — VMEbug Commands (continued)

1

#### **Ordering Information**

| Part Number | Description                                                                                                                                             |  |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MVMEBUG     | VMEbug, the VMEmodule Monoboard Microcomputer System Debug Package,<br>includes EPROM set* and User's Manual.                                           |  |  |  |

| MVMEBUG1    | Source and Relocatable Object Modules for the VMEbug system on VERSAdos<br>Diskette for the EXORmacs Development System.* Includes User's Manual.       |  |  |  |

| MVMEBUG2    | Source and Relocatable Object Modules for the VMEbug system on VERSAdos<br>Cartridge Disk for the EXORmacs Development System.* Includes User's Manual. |  |  |  |

| MVMEBUG/D2  | MVMEbug Debugging Packages User's Manual                                                                                                                |  |  |  |

\*The MVMEBUG EPROM set is copyrighted by Motorola and may be copied only under prior written agreement from Motorola MVMEBUG1 and MVMEBUG2 Sources are copyrighted and licensed by Motorola They may be obtained only under the required license agreement with Motorola

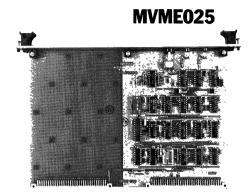

# ADVANCE INFORMATION

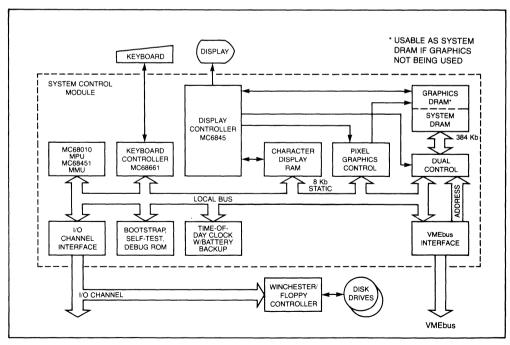

# VMEmodule System Controller

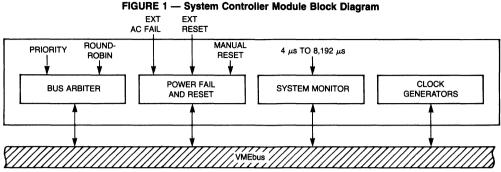

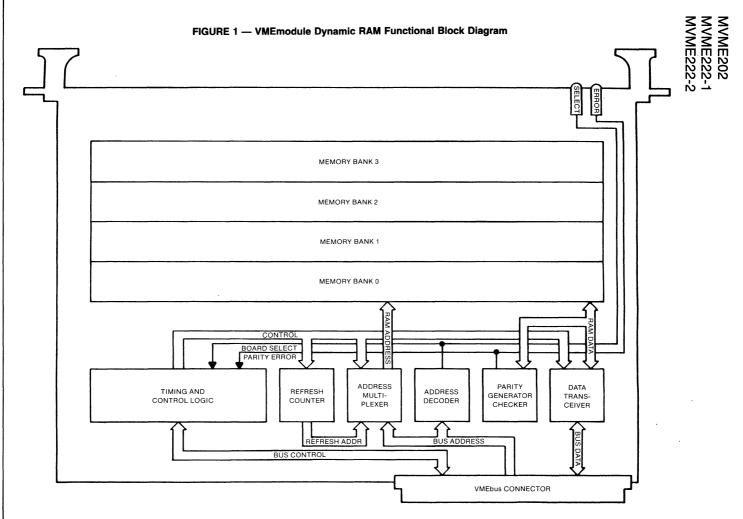

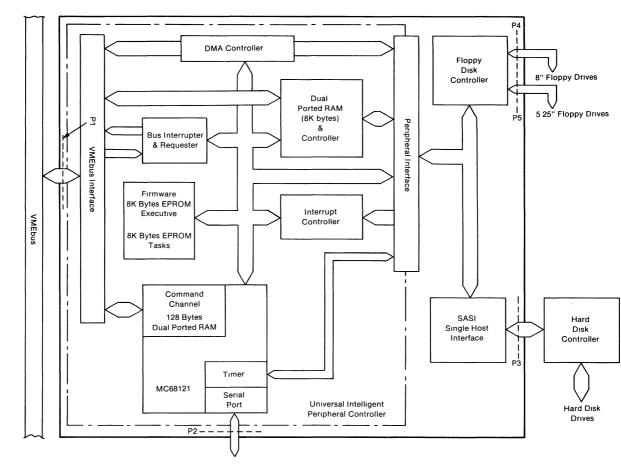

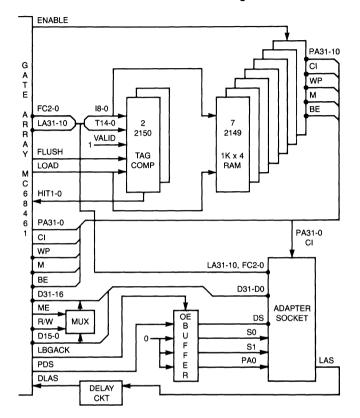

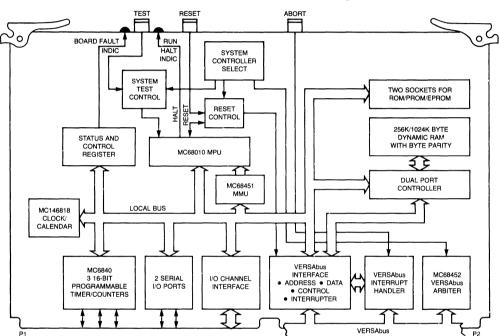

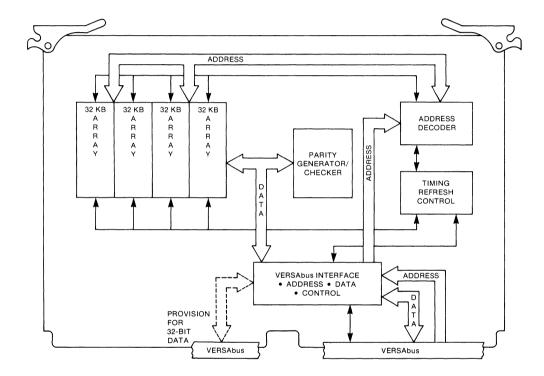

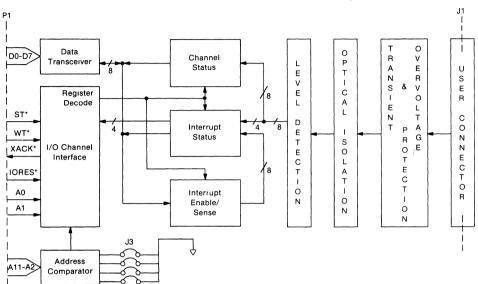

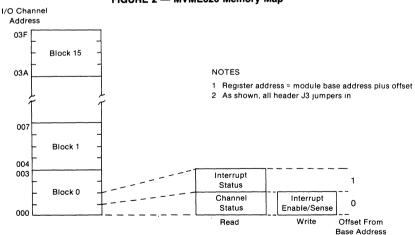

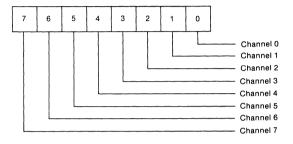

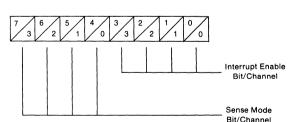

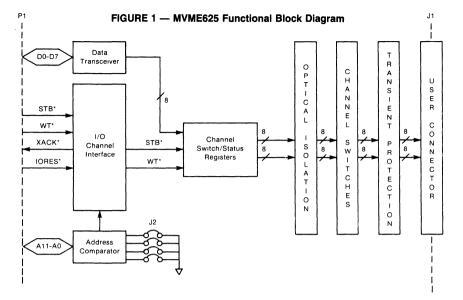

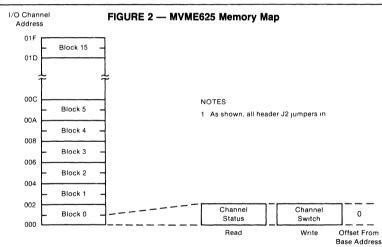

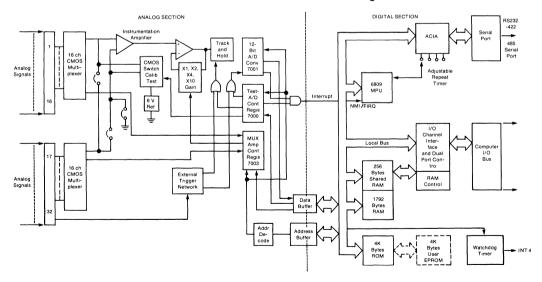

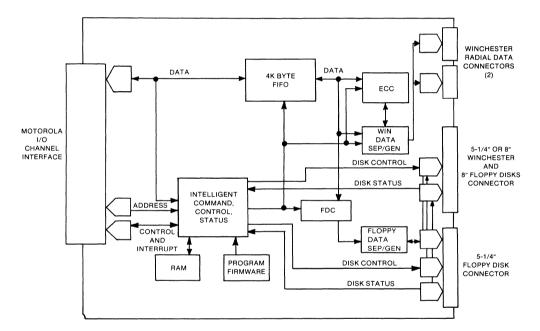

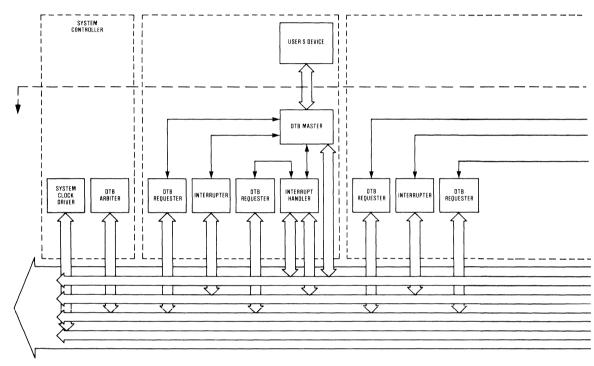

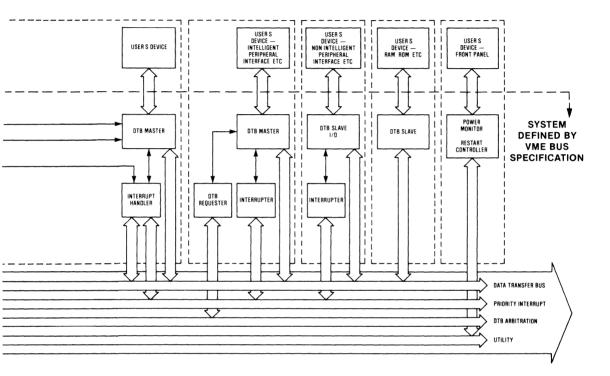

The MVME025 System Controller offers the arbitration, monitor and utility functions usually required in a VMEbus system. In one module it combines clock generation, AC fail and system reset control, bus timeout and error control and bus arbitration eliminating the need for these functions on other modules. The module is especially useful in multiprocessor and intelligent DMA device applications, and is recommended in applications employing Motorola's MC68010 Monoboard Microcomputer, part number MVME115M. Figure 1 is a functional block diagram of the System Controller module.

- Provides VMEbus System Clock, AC Fail, System Reset and System Test Utility Functions

- Arbiter with Selectable Priority or Round Robin Select Modes

- Supports Four Levels of Bus Request/Allocation

- Supports VMEbus System Power Fail Timing for Orderly Power Down

- Selectable Power Fail Input Polarity

- Supports VMEbus System Power Restart Timing for Power Up and Self Test

- 16 MHz System Clock

- Bus Watchdog Timer Period Selectable from 4 to 8192 microseconds

- Longword Access Error Detector

- Front Panel BERR\* LED Indicator

- Front Panel SYSFAIL\* LED Indicator

- Double High Eurocard Form Factor

- VMEbus Compatible

#### **BUS ARBITER**

Bus arbitration is used to prevent simultaneous access of the VMEbus by two masters and for scheduling bus allocation to optimize resource use in a multiprocessor configuration. The System Controller module has a header for jumper selection of one of two arbitration modes: priority or round robin select. In the priority mode when more than one bus request is pending, the arbiter will grant the bus to the requester of highest priority level. This mode is typically used in systems where bus loading by fixed rate masters such as DMA devices is nearly 100%. Where it is desirable to uniformly distribute the bus loading available to non-fixed data

rate masters, the round robin select mode is used. This mode assigns the bus on a rotating priority basis.

#### **AC POWER FAIL AND RESET PROVISIONS**

A means for executing an orderly power down in the event of a power failure is a requisite for any computer system. Such a means is provided by the arbitration structure of the VMEbus which also provides a system reset line and an ac power fail line for use in conjunction with an external power monitor module whose function is to detect power failure and also reset the system on power up, initiating a power-up self test.

Both the system reset and ac fail lines are available at connector P2 on the system controller module which has logic for detecting the ac fail signal and for asserting the VMEbus ACFAIL\* and SYSRESET\* signals using proper timing. The module also has a header by means of which positive true or negative true ac power fail input signal polarity can be selected or the signal disabled.

Logic on the module, in addition to detection of the signal from the power monitor, also causes an approximately 500 millisecond assertion of the SYSFAIL\* signal on 1) detection of the ACFAIL\* assertion, 2) operation of the front panel pushbutton RESET switch and 3) execution of power up.

#### **BUS WATCHDOG TIMER**

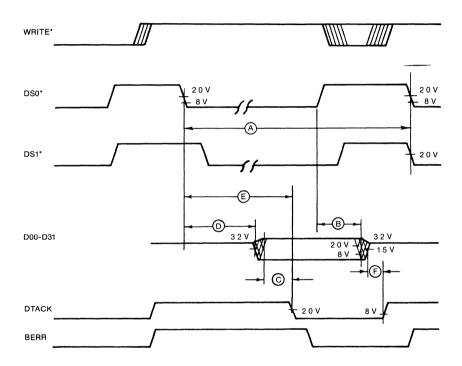

To provide a mechanism for recovering from errors, the module has bus watchdog timer circuitry which terminates a data transfer cycle if a response is not received from a slave within a selected period of time. The circuitry monitors the AS\*, DS1\* and DS2\* lines and starts the timer when any of these is asserted. Lines DTACK\* and BERR\* are also monitored and when either is asserted in a normal data transfer sequence, the timer is stopped. In an instance where timeout occurs before either is asserted, BERR\* is driven low and remains low until AS\*, DS1\* and DS0\* are driven high regardless of the state of DTACK\*. The module has a jumper header for selection of a timer period in microseconds. A value equivalent to any of the twelve powers of two between 4 and 8192 can be selected.

### MVME025

#### LONGWORD ERROR DETECTOR

Circuitry which checks the accessed location against the size of the data being transferred can be a valuable tool for preventing one common software error. The module monitors the LWORD\* and A01 lines and when LWORD\* is asserted at the start of a longword transfer asserts BERR\* if A01 is high (indicating an incorrect double word transfer). BERR\* remains high until AS\*, DS1\* and DS0\* are driven high regardless of the state of DTACK\*.

#### FRONT PANEL INDICATORS

On its front panel, the module has LED indicators for the BERR\* and SYSFAIL\* lines each of which lights when the corresponding signal is asserted.

#### SYSTEM CLOCK

The System Controller provides a clock output to VMEbus specifications: SYSCLK. SYSCLK is a 16 MHz symmetrical system clock which can be used by other modules on the VMEbus for general clocking functions.

| Characteristics                                               | Specifications                                 |

|---------------------------------------------------------------|------------------------------------------------|

| Bus Allocation Speed                                          | 100 ns (typ) 130 ns (max)                      |

| Form Factor                                                   | Double High Eurocard                           |

| Power Requirements                                            | +5 Vdc at 0.5 A (typ)<br>+5 Vdc at 0.8 A (max) |

| Temperature<br>Operating<br>Storage                           | 0°C to +55°C<br>-55°C to +85°C                 |

| Humidity                                                      | 8% to 80% (non condensing)                     |

| Physical Characteristics<br>PC Board Height<br>PC Board Depth | 9.2 in. (234 mm)<br>6.3 in. (160 mm)           |

#### **Electrical, Mechanical and Environmental Specifications**

#### **Ordering Information**

| Part Number Description |                                                                                                                                                 |  |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MVME025                 | VMEmodule System Controller with Two Mode Bus Arbiter, AC Power Fail Circuitry,<br>Watchdog Bus Timer and System Clock. Includes User's Manual. |  |  |

| MVME025/D1              | VMEmodule System Controller User's Manual                                                                                                       |  |  |

# ADVANCE INFORMATION

# **MVME101**

# VMEmodule Monoboard Microcomputer

- High Performance 16-bit Monoboard Microcomputer

- MC68000 16-Bit MPU

1

- Sixteen 32-bit data, address and stack registers

- 14 addressing modes

- 16 megabyte direct addressing range

- Memory mapped I/O

- 56 powerful instruction types

- Operations on five data types including bit, byte, word, long word and BCD

- Provides interlock instruction for multiprocessor systems

- 256 multilevel vectored interrupts including internal exceptions, traps and external interrupts

- Architecturally optimized for efficient support of highlevel languages

- VMEbus Compatible

- Double Eurocard Form Factor

- Up to 128K Bytes of On-Board ROM

- Up to 64K Bytes of On-Board RAM

- Full Operation Isolated from VMEbus (Multiprocessor Mode)

- Two RS-232C Serial I/O Ports

- 20 Programmable I/O Lines

- Triple Programmable 16-Bit Counter/Timer (accessible from off board)

- · Hexadecimal LED Status Display

- Seven Jumper-Selectable Interrupt Priority Levels

- VMEbus Arbiter

- 0°-70°C Operating Temperature Range

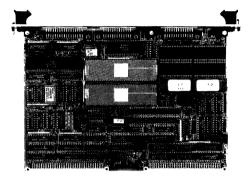

The MVME101 Monoboard Microcomputer is a high performance processing module designed to function as a standalone microcomputer, as a single CPU/controller in a VMEbus system or as a single CPU element in a multiprocessor

VMEbus configuration. This module features Motorola's MC68000 16-bit microprocessor with an address range of 16 megabytes.

Sockets are provided for up to 256K bytes of user-supplied memory. Synchronous and asynchronous serial communication at up to 19.2K baud is supported through two front panel ports and two independent 8-bit parallel communication channels are available at a rear panel connector. Access to a triple 16-bit programmable timer is also provided.

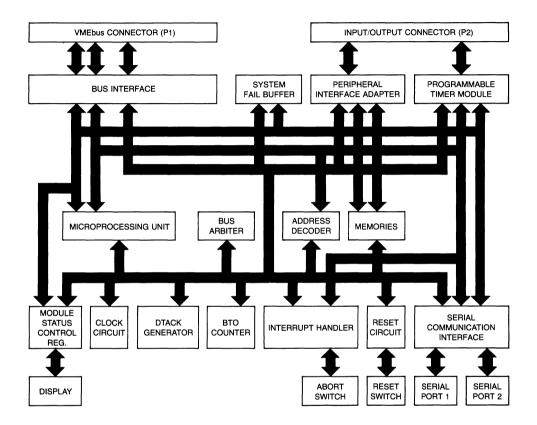

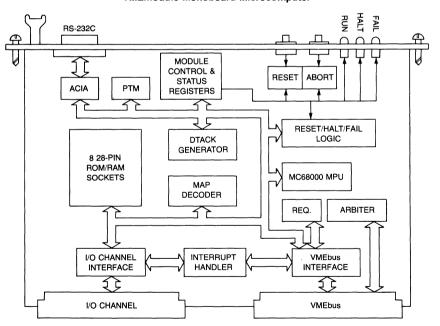

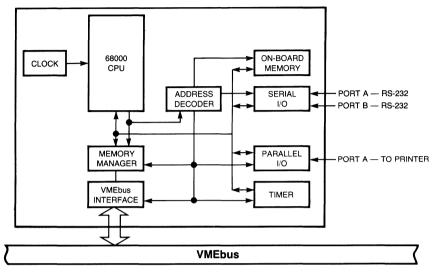

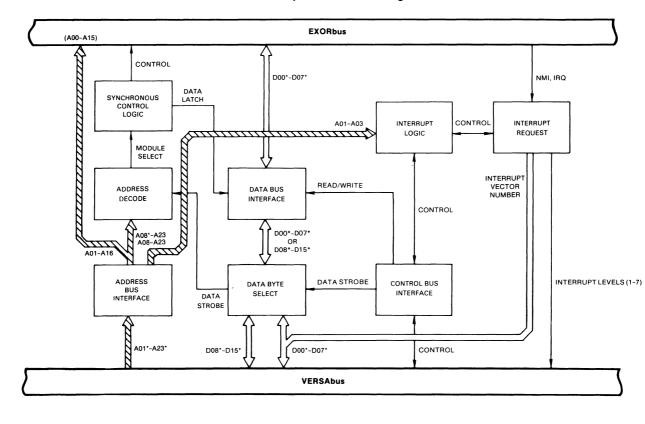

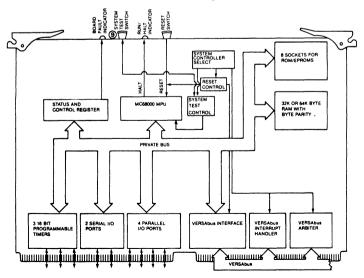

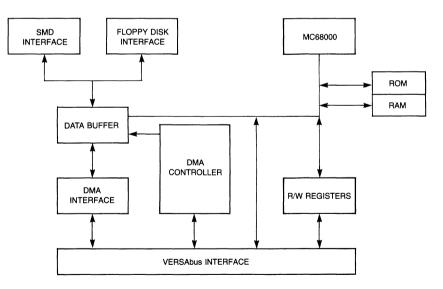

The MVME101 Monoboard Microcomputer in combination with a VMEmodule chassis, other VMEmodules and the VERSAdos Real-Time Operating System can provide a complete design environment which frees the system designer to develop the unique software/firmware required for an application. Figure 1 diagrams the major functional components of the MVME101 Monoboard Microcomputer.

#### DATA ORGANIZATION IN MEMORY

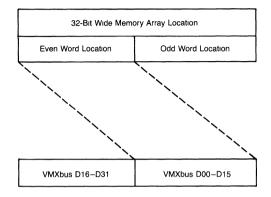

To provide asynchronous byte addressing over the eight megaword range accessible using address lines A01 through A23, the MC68000 separates its 16-bit data word into a lower data byte (D00–D07) and an upper data byte (D08–D15). Rather than address line A00, the external signals lower data strobe (corresponding to the lower data byte) and upper data strobe (corresponding to the upper data byte) are used to access a byte within a data word.

Accordingly, any memory block for the MC68000 must be made up of two identical blocks, one connected to the lower data lines and activated by the lower data strobe LDS\*, the other connected to the upper data byte lines and activated by the upper data strobe UDS\*.

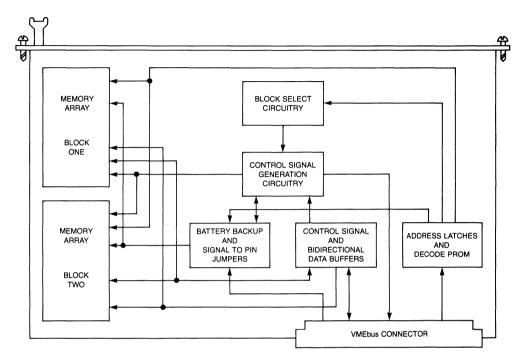

#### FIGURE 1 — MVME101 Functional Block Diagram

#### **MVME101 Memory Array**

An array of eight 28-pin sockets connected as four pairs is provided on the module for user-supplied RAM or ROM. These can be any JEDEC standard byte-wide static memory in a 24- or 28-pin dual in-line package and of 2K, 4K, 8K, 16K or 32K size, of single +5.0 V operation, having high impedance (MOS) inputs and three-state outputs and meeting the timing requirements described in the MC68000 Monoboard Microcomputer User's Manual, MVME101/D1.

#### Address Map Configuration

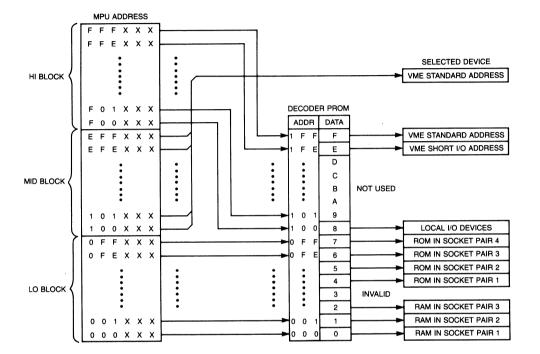

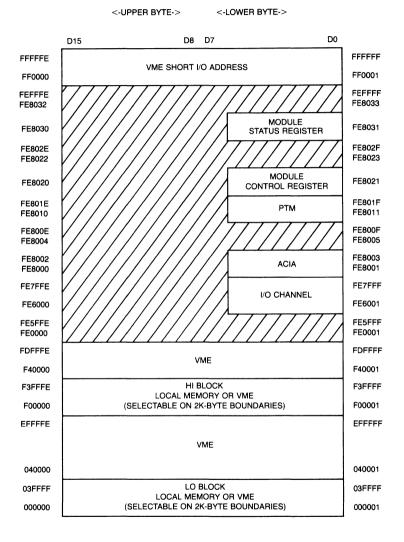

The module has address decoding logic which divides the

16 megabyte address range of the MPU into high, middle and low blocks, as shown in Figure 2. All accesses by the MPU of the middle block, from 100000 to F00000, are directed off-board to the VMEbus. Accesses of the 00000 to 0FFFFF low range addresses and of the F00000 to FFFFFF high range addresses are decoded by a decoder PROM and on-board device selection logic According to the internal ROM program, high and low block accesses are directed to global memory and memory-mapped devices, local I/O devices and the four local memory device socket pairs.

The decoder PROM, organized as  $512 \times 4$  bits, divides the two megabytes of high and low block addresses into  $512 \ 4K$

1

#### FIGURE 2 — Address Map Configuration

byte segments. Use of this programmable device provides a means of mapping local and global resources into separate memory areas as required by an application. The monoboard is shipped with the decoder PROM programmed to provide the map organization shown in Table 1. Local I/O devices and the module Control and Status Registers are mapped by the PROM as shown in Table 2.

The PROM program and the MVME101 Debug Package accommodate the requirement of the monoboard for ROM in memory socket pair #4. ROM is required since, following power up or reset, the MPU on the first four cycles fetches the supervisor stack and program counter values from the first eight locations of the memory socket pair #4 address area. Note also that the RAM, in socket pair #1, required by the debugger is reflected in the decoder PROM program map.

#### Local Memory Device Configuration

The module has four jumper headers which are used to configure the module for use with the specific type and size of memories installed in socket pairs one through four. Another header allows jumper selection of the proper timing for the type of ROM devices used.

#### **VMEbus ARBITER/REQUESTER**

A system which permits multiple master-type modules to share the data transfer bus must use a means of dealing in an orderly manner with concurrent requests for use of the bus. The VMEbus means is to use modules having bus request and/or bus arbitration capabilities and to designate one master type module as the system controller. The MVME101

| Address                         | Contents                                                | Selected Devices                                     |

|---------------------------------|---------------------------------------------------------|------------------------------------------------------|

| FFFFF                           | VMEbus Short I/O Addresses                              | Global I/O-devices                                   |

| FF0000<br>FEFFFF<br>:<br>FE1000 | VMEbus Standard Addresses                               | Global Memory<br>or<br>Memory-mapped Devices         |

| FE0FFF<br>:<br>FE0000           | On-board I/O Registers<br>(Only odd addresses used)     | Local I/O-devices                                    |

| FDFFFF<br>:<br>F04000           | VMEbus Standard Addresses                               | Global Memory<br>or<br>Memory-mapped Devices         |

| F03FFF<br>:<br>F00000           | MVME101bug Debug Package<br>or<br>User-provided Program | 2 x 8K bytes Local ROM<br>in<br>Memory Socket Pair 4 |

| EFFFFF                          | VMEbus Standard Addresses                               | Global Memory<br>or<br>Memory-mapped Devices         |

| 002FFF<br>:<br>002000           | User Program/Data                                       | 2 x 2K bytes Local RAM<br>in<br>Memory Socket Pair 3 |

| 001FFF<br>:<br>001000           | User Program/Data                                       | 2 x 2K bytes Local RAM<br>in<br>Memory Socket Pair 2 |

| 000FFF<br>:<br>000800           | User Program/Data                                       |                                                      |

| 0007FF<br>:<br>000400           | MVME101bug Data/Stack                                   | 2 x 2K bytes Local RAM<br>in<br>Memory Socket Pair 1 |

| 0003FF<br>:<br>000000           | MPU Exception Vectors                                   |                                                      |

### TABLE 1 — MVME101 Address Map (As Shipped)

| Device | Address                                                                                                                                                      | Mode                                                                                                                        | Register                                                                                                                                                                                                                                                                                                                 |  |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MCR    | FE00F1                                                                                                                                                       | r/w                                                                                                                         | Module Control Register                                                                                                                                                                                                                                                                                                  |  |  |  |

| MSR    | FE00E1                                                                                                                                                       | r/w                                                                                                                         | Module Status Register                                                                                                                                                                                                                                                                                                   |  |  |  |

| PTM    | FE00DF<br>FE00DF<br>FE00DD<br>FE00DB<br>FE00DB<br>FE00D9<br>FE00D9<br>FE00D7<br>FE00D7<br>FE00D7<br>FE00D5<br>FE00D5<br>FE00D3<br>FE00D3<br>FE00D3<br>FE00D1 | read<br>write<br>read<br>write<br>read<br>write<br>read<br>write<br>read<br>write<br>read<br>write<br>read<br>write<br>read | LSB buffer register<br>Timer #3 latches<br>Timer #3 counter<br>MSB buffer register<br>LSB buffer register<br>Timer #2 latches<br>Timer #2 counter<br>MSB buffer register<br>LSB buffer register<br>Timer #1 latches<br>Timer #1 counter<br>MSB buffer register<br>status register<br>control register #2<br>no operation |  |  |  |

|        | FE00D1<br>FE00D1                                                                                                                                             | write                                                                                                                       | CR20 = 1: control register #1<br>CR20 = 0: control register #3                                                                                                                                                                                                                                                           |  |  |  |

| PIA    | FE00C7<br>FE00C5<br>FE00C5<br>FE00C3<br>FE00C1<br>FE00C1                                                                                                     | r/w<br>r/w<br>r/w<br>r/w<br>r/w                                                                                             | Section B control register<br>CRB-2 = 1: Section B peripheral register<br>CRB-2 = 0: Section B data direction register<br>Section A control register<br>CRA-2 = 1: Section A peripheral register<br>CRA-2 = 0: Section A data direction register                                                                         |  |  |  |

| PCI2   | FE00B7<br>FE00B5<br>FE00B3<br>FE00B3<br>FE00B1<br>FE00B1                                                                                                     | r/w<br>r/w<br>read<br>write<br>read<br>write                                                                                | command register<br>mode register #1 / mode register #2<br>status register<br>SYN1 register / SYN2 register / DLE register<br>receive holding register<br>transmit holding register                                                                                                                                      |  |  |  |

| PCI1   | FE00A7<br>FE00A5<br>FE00A3<br>FE00A3<br>FE00A1<br>FE00A1                                                                                                     | r/w<br>r/w<br>read<br>write<br>read<br>write                                                                                | command register<br>mode register #1 / mode register #2<br>status register<br>SYN1 register / SYN2 register / DLE register<br>receive holding register<br>transmit holding register                                                                                                                                      |  |  |  |

#### TABLE 2 — I/O Register Address Map (As Shipped)

module uses a programmable logic array to implement bus requester and arbiter functions which comply with the bus arbitration protocols of the VMEbus specification. Additional circuitry is used to meet the VMEbus timing and driving requirements.

#### **BUS ARBITER**

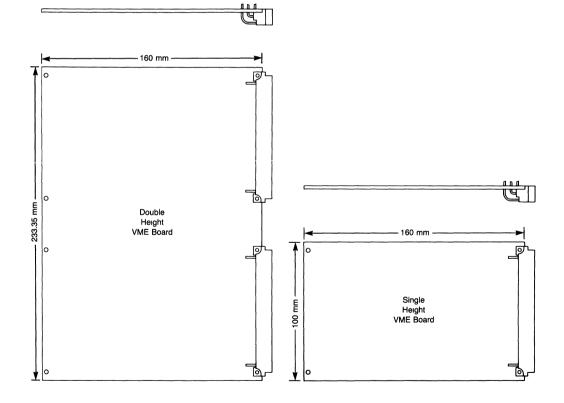

So that it can be used as the system controller in a VMEbus

system, the MVME101 module has an option ONE single level arbiter which arbitrates requests on level 3. System controller operation requires that the module be placed in slot #1 of the VMEbus backplane to insure that the module is first in the daisy chain arbitration structure and has, therefore, the highest priority. The module also has a header from which a jumper is removed to disable the arbiter when the module is used at a lower priority in a multi-processor system.

#### **BUS REQUESTER**

The module has a type ROR (release on request) bus requester so that the module can be used in systems where maximum data transfer rate is essential. The requester monitors all four bus request lines and releases the VMEbus signal BBSY\* only when another bus request is pending. This operation reduces the number of arbitrations required of a bus master.

Two means of requesting the VMEbus are provided by the module:

- the ROR mode in which the bus is automatically requested when the MPU starts either a VMEbus data transfer cycle or interrupt vector fetch and

- under program control by setting the Bus Block Transfer Request (BBTR) control register bit.

The latter method protects routines against interruption by other bus requests. With BBTR set, VMEbus is never released except when the module is used in a multilevel arbitration system. Then a higher level request causes the module arbiter to assert BCLR\* resulting in a maskable auto vector interrupt request at the MPU providing the option of clearing BBTR under control of an interrupt service routine. To control idle state time in the software transparent ROR mode, the 128 microsecond Bus Request Time Out counter can be activated by setting an appropriate control bit in the module control register.

The module has two headers for jumper determination of the priority level at which the requester will operate. One allows connection of the module's bus request out signal to the VMEbus signal line of appropriate priority level. The other allows:

- connection of the VMEbus bus grant in line of the appropriate level to the bus requester,

- connection of the requester bus grant out signal to the appropriate VMEbus line

- connection of unused VMEbus bus grant input to bus grant output lines for propagation of these signals to the system modules having bus requesters of those levels.

#### **VMEbus INTERFACE**

VMEbus is characterized by the asynchronous bidirectional operation required for complex, high performance systems. The VMEbus interface on MVME101 supports operation in a multiprocessor system and the full 16 megabyte address range of the MC68000 MPU. Access to the backplane address, data and control lines is provided by the triple row, 96pin VMEbus connector at the upper rear of the module. Pin assignments, connector physical characteristics and VMEbus signal and timing requirements are fully described in the VMEbus specification manual — MVMEBS/D1.

On the module, logic independent of the MPU generates the signal handshaking and timing required by the VMEbus data transfer protocol. Of the 14 address modifier codes defined by the VMEbus specification, a subset of six is supported by the module. These are listed in Table 3. Note that address modifier lines 3 and 5 are not driven by the interface logic but are kept in the high state by terminating resistors on the backplane

#### **Bus Supervision Counters**

The module has two counters for supervising VMEbus accesses: the Bus Request Timeout Counter (BRTO) and the Data Transfer Timeout Counter (DTTO). Each can independently be enabled and disabled under software control by setting in the control register the bit corresponding to that counter.

If bit 6 in the control register is set at the time the MPU accesses an off-board location, the BRTO counter starts. After 128 microseconds, if the bus is not yet available bit 6 in the status register is set and the signal Bus Error is asserted.

If bit 7 in the control register is set at the time the MPU asserts a data strobe at the beginning of an off-board data transfer cycle, the DTTO counter starts. After 8 microseconds, if the data transfer is not yet acknowledged bit 7 in the status register is set and the signal Bus Error is asserted

#### **Operating Mode Control**

The module has a header for jumper connection to the arbiter of the VMEbus system control signals required for

| AM Address Modifier |   | ſ |   |   |   |   |                                        |

|---------------------|---|---|---|---|---|---|----------------------------------------|

| Code                | 5 | 4 | 3 | 2 | 1 | 0 | Function                               |

| 3E                  | 1 | 1 | 1 | 1 | 1 | 0 | standard supervisory program access    |

| 3D                  | 1 | 1 | 1 | 1 | 0 | 1 | standard supervisory data access       |

| ЗA                  | 1 | 1 | 1 | 0 | 1 | 0 | standard non-privileged program access |

| 39                  | 1 | 1 | 1 | 0 | 0 | 1 | standard non-privileged data access    |

| 2D                  | 1 | 0 | 1 | 1 | 0 | 1 | short supervisory I/O data access      |

| 29                  | 1 | 0 | 1 | 0 | 0 | 1 | short non-privileged I/O data access   |

TABLE 3 — Address Modifier Codes

**Reset and Hait Functions**

operating in the system controller configuration or in the standard non-controller configuration. Included are the output signal SYSCLK, the bidirectional signal SYSFAIL<sup>\*</sup>, and the RESET\* input and output signals. When the module is operated in the isolated mode, none of these signals is connected.

System and local reset can be performed by either the

power up reset circuitry or the reset switch. Local reset and

system halt can be executed by the MPU. Connection or not

to VMEbus of the signals SYSFAIL\* and SYSRESET\* required for operating in a particular mode is accomplished by jumper in the mode configuration header.

#### **INTERRUPT HANDLER**

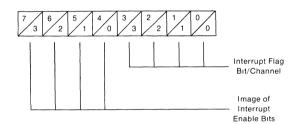

The module interrupt handler circuitry manages all interrupt requests of local and system origin. It determines the pending interrupt request of highest priority and asserts a corresponding code on the three MPU interrupt priority lines. The module has two headers for jumper determination of which of the

| Din                           | Pin Signal |                                  |  |  |  |  |

|-------------------------------|------------|----------------------------------|--|--|--|--|

| Pin Signal<br>Number Mnemonic |            | Description                      |  |  |  |  |

|                               | Mnemonic   | Description                      |  |  |  |  |

| Row A Pins                    |            |                                  |  |  |  |  |

| 1 through 32                  | GND        | System Ground                    |  |  |  |  |

|                               |            |                                  |  |  |  |  |

| Row C Pins                    |            |                                  |  |  |  |  |

| 1                             | +5.0 V     | Supply                           |  |  |  |  |

| 2                             | CB2        | PIA Peripheral Control, Side B   |  |  |  |  |

| 3                             | CB1        | PIA Interrupt Control, Side B    |  |  |  |  |

| 4                             | PB7        | PIA Peripheral Data, Side B      |  |  |  |  |

| 5                             | PB6        | PIA Peripheral Data, Side B      |  |  |  |  |

| 6                             | PB5        | PIA Peripheral Data, Side B      |  |  |  |  |

| 7                             | PB4        | PIA Peripheral Data, Side B      |  |  |  |  |

| 8                             | PB3        | PIA Peripheral Data, Side B      |  |  |  |  |

| 9                             | PB2        | PIA Peripheral Data, Side B      |  |  |  |  |

| 10                            | PB1        | PIA Peripheral Data, Side B      |  |  |  |  |

| 11                            | PB0        | PIA Peripheral Data, Side B      |  |  |  |  |

| 12                            | PA7        | PIA Peripheral Data, Side A      |  |  |  |  |

| 13                            | PA6        | PIA Peripheral Data, Side A      |  |  |  |  |

| 14                            | PA5        | PIA Peripheral Data, Side A      |  |  |  |  |

| 15                            | PA4        | PIA Peripheral Data, Side A      |  |  |  |  |

| 16                            | PA3        | PIA Peripheral Data, Side A      |  |  |  |  |

| 17                            | PA2        | PIA Peripheral Data, Side A      |  |  |  |  |

| 18                            | PA1        | PIA Peripheral Data, Side A      |  |  |  |  |

| 19                            | PA0        | PIA Peripheral Data, Side A      |  |  |  |  |

| 20                            | CA2        | PIA Peripheral Control, Side A   |  |  |  |  |

| 21                            | CA1        | PIA Peripheral Interrupt, Side A |  |  |  |  |

| 22                            | +5.0 V     | Supply                           |  |  |  |  |

| 23                            | C3*        | PTM Clock Input 3                |  |  |  |  |

| 24                            | O3         | PTM Output 3                     |  |  |  |  |

| 25                            | G3*        | PTM Gate Input 3                 |  |  |  |  |

| 26                            | C2*        | PTM Clock Input 2                |  |  |  |  |

| 27                            | 02         | PTM Output 2                     |  |  |  |  |

| 28                            | G2*        | PTM Gate Input 2                 |  |  |  |  |

| 29                            | C1*        | PTM Clock Input 1                |  |  |  |  |

| 30                            | 01         | PTM Output 1                     |  |  |  |  |

| 31                            | G1*        | PTM Gate Input 1                 |  |  |  |  |

| 32                            | + 5.0 V    | Supply                           |  |  |  |  |

### **MVME101**

seven VMEbus interrupt lines, which of the four local I/O devices or which of the two VMEbus signals BCLR\* and SYSFAIL\* are used as user vector and auto vector interrupt request sources by the MPU. The non-maskable, auto vectored interrupt level 7 is not available but is reserved for software abort and ac power failure.

#### CONTROL REGISTER

The module control register is an 8-bit read/write register which resides in the local I/O segment of the memory map. Bits in the register can be set/cleared to control the module hexadecimal display, the SYSFAIL\* signal output, the block transfer request, the bus request timeout counter and data transfer timeout counter.

#### STATUS REGISTER

The module status register is an 8-bit read/write register which resides in the local I/O segment of the memory map. Bits in the register indicate the current level of the VMEbus signals ACFAIL\*, SYSFAIL\*, ABORT\*, BCLR\*, BAV\*, the local signal PC11RXD\* and whether or not a bus request timeout or a data transfer timeout has occurred.

#### VMEbus CONNECTOR P1

The electrical and mechanical characteristics of VMEbus connector P1 are fully described in the VMEbus Specification Manual MVMEBS/D1.

#### **PERIPHERAL INPUT/OUTPUT CONNECTOR P2**

Peripheral Connector P2 is a DIN 41612 connector with 64 pins (rows a & c) installed. Pin assignments and signal descriptions for Connector P2 are given in Table 4.

#### **COMMUNICATIONS INTERFACES**

Interfaces for both serial and parallel communications are provided on the module. An externally accessible triple programmable timer module is also provided. The two serial ports are accessible via two 25-pin connectors on the front panel. The programmable timer module and the parallel port are accessible via a rear panel connector, P2.

#### **Serial Ports**

The serial communication capability of MVME101 is derived from two MC68661C Enhanced Programmable Communication Interface devices. These devices support several synchronous or asynchronous protocols in full or half duplex mode, provide software selectable baud rates ranging from 50 to 19200 baud. On MVME101, both ports are RS-232C compatible and may, by jumper, be configured as data set or data terminal. Prior to beginning serial data communications, the MC68661C registers must be loaded with a set of mode and command bytes as described in the device data

#### Parallel Port

sheet.

A universal means of interfacing peripheral equipment to the module is provided by a MC6821 Peripheral Interface Adapter (PIA). This device has two 8-bit bidirectional peripheral data buses and four control lines providing a general parallel communications capability for the control of various peripherals. Each of the peripheral data lines can be programmed as an input or output and each of the four control/ interrupt lines can be programmed for operation in one of the several modes. The module has a header in which, to establish interrupt priorities, PIA interrupt output lines can be jumper connected to the desired autovectored interrupt request lines.

#### Programmable Timer Module

A generally useful timing function is provided by a MC6840 Programmable Timer Module (PTM) which contains three cascadable, 16-bit binary counters, three corresponding control registers and a status register. The module has a header for jumper configuration of the PTM inputs and outputs to obtain various modes of operation. The PTM can be programmed to generate module interrupts and/or output signals such as square waves, gated delay signals and signal pulses of controlled or modulated duration for use in event counting and interval or frequency measurement.

#### Software/Firmware Support

Motorola provides standard software packages to support VMEmodule Monoboard Microcomputers within the categones of Real-Time Executives and operating systems, and Debuggers/Loaders. The principal features of these software products are as follows:

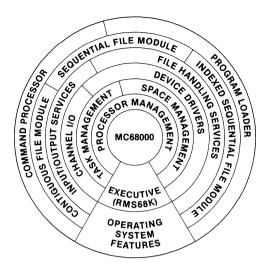

#### RMS68K- Real-Time Multitasking System Software

- Memory Resident (ROMable)

- Physical (Channel) I/O

- Multitask Dynamic Scheduling

- Software and Hardware Interrupt Processing

- High Speed Interrupt Response

- Intertask Communication and Task Synchronization

- Dynamic Allocation and Management of RAM

- User Trap Handling

- Exception Processing

- Time Delay, Periodic Task Activation, Time-Of-Day

- Easy Addition Of User-Written Device Drivers

- Upward Compatible To Real-Time Disk Operating System

- Compatible with EXORmacs System Software

- Customization via SYSGEN

# MVME101

#### VERSAdos — Real-Time Disk Operating System

- Provides All Real-Time Multitasking Software Features of RMS68K

- Device Independent I/O and Logical I/O

- Wait and Proceed I/O

- Standard Device Drivers

- Multi-Level File Directories

- Shared File Access

- Dynamic or Contiguous File Space Allocation

- · Random, Sequential, and Indexed Sequential File Access

#### VME101bug — Debug/Monitor/Loader Firmware

- Initialization

- Display/Change Memory

- Display/Change Registers

- Set and Clear Breakpoints

- Block Initialize

- Block Move

- · Search for a (masked) Value

- Trace with Optional Instruction Count

- Downline/Upline Load

- Single-line Assembler/Disassembler

#### Hardware/Software Development Support

The recommended vehicles for developing 16/32-bit microcomputer systems based on a VMEmodule Monoboard Microcomputer are the EXORmacs MC68000 Development System and the VME/10 Microcomputer System in either the VERSAdos Real Time Operating System or SYSTEM V/68 Operating System environment. Both operating systems offer a complete set of high performance software development tools. Both support Motorola's 16/32-bit hardware emulators and bus state analyzer used for hardware/software integration and debugging in the target system.

#### Mechanical and Environmental Specifications

| Characteristics          | Specifications              |

|--------------------------|-----------------------------|

| Power Requirements       | + 5.0 Vdc at 180 mAdc (typ) |

| Temperature              |                             |

| Operating                | 0°C to +70°C                |

| Storage                  | - 55°C to + 85°C            |

| Relative Humidity        | 0 to 95% (non-condensing)   |

| Physical Characteristics |                             |

| PC Board only            |                             |

| Height                   | 9.2 in. (234 mm)            |

| Depth                    | 6.3 in. (160 mm)            |

| Thickness                | 0.63 in. (16 mm)            |

| PC Board & Front Panel   |                             |

| Height                   | 10.3 in. (262 mm)           |

| Depth                    | 7.4 in. (188 mm)            |

| Thickness                | 0.8 in. (20.3 mm)           |

| PC Board Form Factor     | Double High Eurocard        |

#### **Ordering Information**

| MVME101    | VMEmodule Monoboard Microcomputer with the MC68000L8 MPU, two serial ports<br>and two parallel I/O ports. Includes eight sockets for 2K to 32K-byte RAM/ROM<br>devices, 16 bi-directional parallel I/O lines, three off-board-accessible programmable<br>16-bit counter/timers, hexadecimal LED status display and seven interrupt levels with<br>bus arbitration. |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MVME101/D1 | VMEmodule Monoboard Microcomputer User's Manual                                                                                                                                                                                                                                                                                                                    |

# MVME101BUG MVME101BUGLF MVME101BUGLC

# VME101bug Debugging Packages for the MVME101 Monoboard Microcomputer

#### **101bug Resident Package**

- EPROM Resident System Debug Monitor

- 30 Powerful Commands

- Single-line Assembler/Disassembler for convenient Program Monitoring

- Full Speed Execution of System and User-Developed Programs Operating in the VMEmodule Monoboard Microcomputer System

- Virtual Terminal Capability for Up/Downline Load from an EXORmacs Development System or from any Host Computer

- Command Set Allows Access to all VMEmodule I/O, Control and Memory Facilities Plus the Full 16 Mbyte Direct Address Range of the VMEbus

- Includes Disk Controller Initialization and Disk I/O commands for the MVME315 Intelligent Floppy Controller/ SASI Interface

- Includes Boot Facilities for Loading the VERSAdos O.S. and for Dumping VMEbus System RAM Contents to Disk.

- Includes all Required Installation and Operation Documentation

# 101bug Source and Relocatable Object Module Package

- Source and Relocatable Object Modules for 101bug on Diskette or Cartridge Disk

- Relocatable Object Modules Allow Users to Include Only the 101bug Items Needed in Their End System

- Source Modules Allow User Modification of 101bug as Desired

The MVME101 Monoboard Microcomputer debug package, 101bug, is available as two separate product offerings. 101bug is an EPROM-based resident package ready for installation and immediate use with the MVME101 Monoboard Microcomputer installed in a VMEbus backplane. Such a backplane is provided within Motorola's MVME900 Series Chassis. 101bug Source and Relocatable Object Modules are a separate product available on either VERSAdos compatible floppy disk or cartridge.

101bug provides a powerful evaluation and system debugging tool for VMEmodule Systems. The EPROM Resident Package will operate in 32K bytes of ROM space. 101bug uses the first 4K bytes of RAM storage for Interrupt vectors and temporary storage. The EPROM resident package is delivered in two 16K byte EPROMs. Table 1 lists the commands available to the user.

The package permits execution of system and userdeveloped programs operated in a MVME101 Monoboard Microcomputer system environment under complete operator control. 101bug may be utilized with a Monoboard Microcomputer in a standalone environment with only a user provided standard RS-232C asynchronous ASCII terminal. Alternately, it may be used with the second serial I/O port of the MVME101 connected to a host computer for up/downline loading of programs in Motorola "S" Record format. When connected to a host computer in this manner, the MVME101/ 101bug combination appears as a virtual terminal to the host operating system.

MVME101bug also provides program and operating system downloading facilities from floppy or hard disk into the VMEbus system RAM through the MVME315 Intelligent Floppy Controller/SASI Interface.

After loading, 101bug commands may be used to examine and modify memory, set breakpoints to run particular program segments, and track program progress. The user may set up and examine a variety of conditions using any of the powerful commands listed in Table 1, such as the Register Display/ Set series and the memory block manipulation commands.

### MVME101BUG MVME101BUGLF MVME101BUGLC

The Data Conversion command serves as an aid in examining and modifying data by converting hexadecimal to decimal, and decimal to hexadecimal. If corrections or program patches are required, these may be performed and checked in the VMEmodule. The user may send a corrected copy to the host computer files by using the Memory Dump command for upline load. Alternatively, memory contents can be saved on floppy or hard disk via the MVME315 Intelligent Floppy Controller/SASI Interface. Creating program patches may be aided by use of the Display Offsets command to assist with relocatable and position-independent code. The user may also copy all traffic to the serial port debug terminal on a printer attached to the MVME101 parallel port by use of the Attach Printer command. This may be useful for disk debugoing following a debug session.

The user may communicate with the host computer as a terminal for purposes other than up/downline load by executing the Transparent Mode command. By using the Port Format command, the serial port may be reconfigured for such attributes as baud rate, stop bits and number of data bits.

Bootstrap load and dump commands permit the user to bootstrap from several device combinations through the MVME315 Intelligent Floppy Controller/SASI Interface. The drives currently supported are the 5¼" Winchester and the 5¼" Floppy and/or 8" Floppy. The Boot Dump command permits the user to write complete memory contents to a diskette/ disk in bootstrap load format for subsequent use in boot loading. The IOT command permits the user to create the floppy/ hard disk format required.

101bug may be used for debug in system environments which include the MVME101 Monoboard Microcomputer, other Motorola VMEmodules and user-developed VMEbus compatible modules.

The Source and Relocatable Object Module Packages provide users with the information to link 101bug into their specific systems in either modified or unmodified form. The Relocatable Object Modules are designed to permit creation of a load module with or without the "S" Record up/downline loader.

Source Modules permit the user to modify or customize any of the 101bug functions as desired.

|                                                                                                                                                                                                       | Command                                                                                                                                                      | Description                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MM <add< td=""><td>r&gt;[<count>]<br/>ress&gt;[;<opts>]<br/>ress&gt;<data></data></opts></count></td><td>Memory Display/Disassembly<br/>Memory Modify/Disassembly/Assembly<br/>Memory Set</td></add<> | r>[ <count>]<br/>ress&gt;[;<opts>]<br/>ress&gt;<data></data></opts></count>                                                                                  | Memory Display/Disassembly<br>Memory Modify/Disassembly/Assembly<br>Memory Set                                                                                                                                                                                                                       |

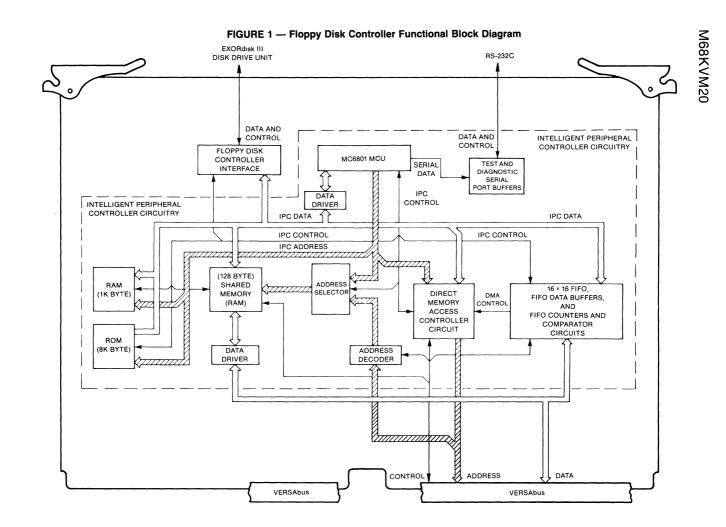

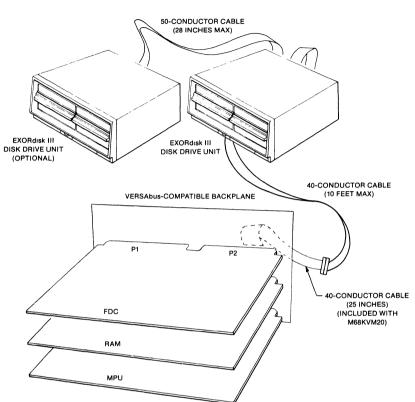

| .D                                                                                                                                                                                                    | [ <expression>]<br/>[<expression>]<br/>[<expression>]<br/>[<expression>]<br/>[<expression>]</expression></expression></expression></expression></expression> | Display All Address Registers<br>Display/Set Address Register<br>Display/Set Data Register<br>Display/Set Data Register<br>Display/Set Program Counter<br>Display/Set Status Register<br>Display/Set Supervisor Stack Pointer<br>Display/Set User Stack Pointer<br>Display Formatted Registers (All) |