# 8-bit MCU Applications Manual

DL408/D REV 1

MOTOROLA

# 8-bit MCU Applications Manual

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

Includes literature available at July 1992

All trademarks recognized.

© MOTOROLA INC.

All Rights Reserved

First Edition DL408/D, 1990

DL408/D Rev. 1, 1992

Printed in Great Britain by Tavistock Press (Bedford) Ltd. 5000 8/92

#### **Preface**

This compilation of Application Notes, Engineering Bulletins, Design Concepts, etc. was originally published by the European Literature Centre of Motorola Ltd. in Milton Keynes, England, and has subsequently gained worldwide acceptance.

Because of the worldwide popularity of the Application Manuals Series it is important for the reader to take note of the following:

The various Application Notes, Engineering Bulletins, Design Concepts, etc. which are included were developed at Design Centres strategically located throughout the global community and many were originally written to support a local need. Whilst the basic concepts of each of the publications included may have broad global applicability, specific Motorola semiconductor parts may be referred to that are currently available for limited distribution in a specific region and may only be supported by the country of origin of the document in which it is referenced.

Also included in the series for completeness and historical significance are documents that may no longer be available individually because obsolete devices are referenced or perhaps, simply, the original document is out of print. Such items are marked in the Table of Contents, Cross Reference, Abstracts and on the first page of the document with the letters 'HI' to indicate that these documents are included for Historical Information only.

All the Application Notes, Engineering Bulletins, Design Concepts, etc. are included to enhance the user's knowledge and understanding of Motorola's products. However, before attempting to design-in a device referenced in this Series, the user should contact the local Motorola supplier or sales office to confirm product availability and if application support is available.

Thank you.

#### Other books in this series include:

DL409/D Rev. 1 16/32-bit Applications Manual

DL410/D Power Applications Manual

DL411/D Communications Application Manual

DL412/D Industrial Control Applications Manual

DL413/D Radio, RF and Video Applications Manual

DL414/D FET Applications Manual

#### **Contents**

| Daviss Cra           | ss Reference                                                                         | page |

|----------------------|--------------------------------------------------------------------------------------|------|

|                      | f Applications Documents                                                             |      |

|                      | s Documents                                                                          | 10   |

| Application<br>AN427 | MC68HC11 EEPROM Error Correction Algorithms in C                                     | 21   |

| AN431                | Temperature Measurement and Display Using the MC68HC05B4 and the MC14489             |      |

| AN432                | 128K byte Addressing with the M68HC11                                                |      |

| AN433                | TV On-Screen Display Using the MC68HC05T1                                            |      |

| AN434                | Serial Bootstrap for the RAM and EEPROM1 of the MC68HC05B6                           |      |

| AN436                | Error Detection and Correction Routines for M68HC05 Devices Containing EEPROM        |      |

| AN440                | MC68HC805B6 and MC68HC705B5 Serial/Parallel Programming Module                       |      |

| AN441                | MC68HC05E0 EPROM Emulator                                                            |      |

| AN442                | Driving LCDs with M6805 Microprocessors                                              |      |

| AN446                | MCM2814 Gang-Programmer Using an MC68HC805B6                                         |      |

| AN448                | "FLOF" Teletext using M6805 Microcontrollers                                         |      |

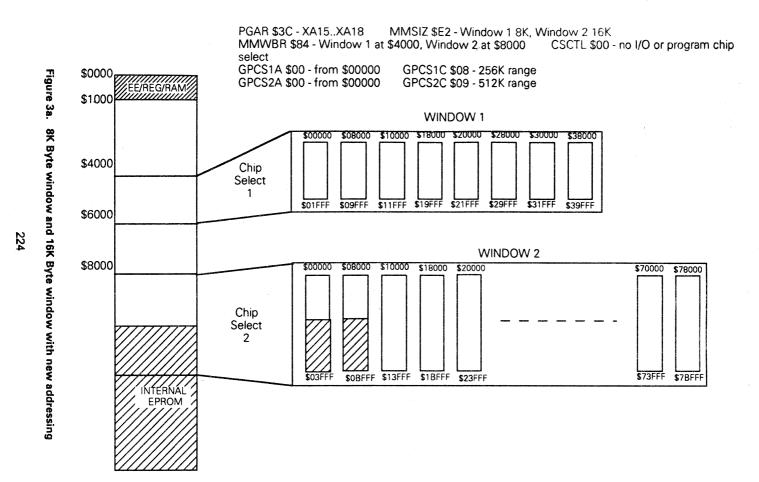

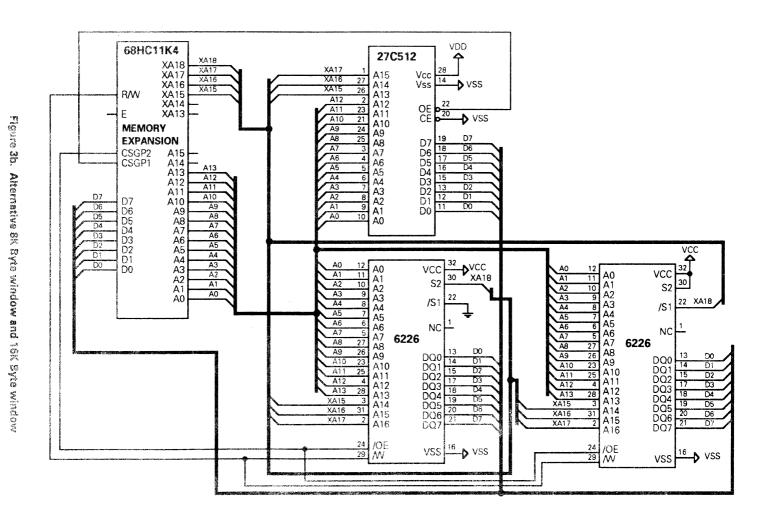

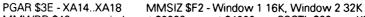

| AN452                | Using the MC68HC11K4 Memory Mapping Logic                                            |      |

| AN459                | A Monitor for the MC68HC05E0                                                         |      |

| AN890                | Low Voltage Inhibit (LVI) Capability of the M6805 HMOS Microcomputer Family HI       |      |

| AN900                | Using the M6805 Family On-Chip 8-Bit A/D Converter                                   |      |

| AN940                | Telephone Dialling Techniques Using the MC6805                                       |      |

| AN974                | MC68HC11 Floating-Point Package                                                      |      |

| AN991                | Using the Serial Peripheral Interface to Communicate Between Multiple Microcomputers |      |

| AN1010               | MC68HC11 EEPROM Programming from a Personal Computer                                 |      |

| AN1050               | Designing for Electromagnetic Compatibility (EMC) with HCMOS Microcontrollers        |      |

| AN1055               | M6805 16-bit Support Macros                                                          |      |

| AN1057               | Selecting the Right Microcontroller Unit                                             |      |

| AN1058               | Reducing A/D Errors in Microcontroller Applications                                  |      |

| AN1060               | MC68HC11 Bootstrap Mode                                                              |      |

| AN1064               | Use of Stack Simplifies M68HC11 Programming                                          |      |

| AN1065               | Use of the MC68HC68T1 Real-Time Clock with Multiple Time Bases                       |      |

| AN1066               | Interfacing the MC68HC05C5 SIOP to an I2C Peripheral                                 |      |

| AN1067               | Pulse Generation and Detection with Microcontroller Units                            |      |

| AN1091               | Low Skew Clock Drivers and their System Design Considerations                        |      |

| AN1097               | Calibration-Free Pressure Sensor System                                              |      |

| AN1102               | Interfacing Power MOSFETs to Logic Devices                                           |      |

| AN1120               | Basic Servo Loop Motor Control Using the MC68HC05B6 MCU                              |      |

| AN1203               | A Software Method for Decoding the Output from the MC14497/MC3373 Combination        | 643  |

| ANE405               | Bi-Directional Data Transfer Between MC68HC11 and MC6805L3 Using SPI MI              |      |

| ANE418               | MC68HC805B6 Low-Cost EEPROM Microcomputer Programming Module **I                     |      |

| ANE420               | Monitor Program for the MC68HC05B6 Microcomputer Unit HI                             |      |

| EB400                | Secure Single Chip Microcomputer Manufacture                                         |      |

| EB401                | SCAM Modules for Smart Cards                                                         | 691  |

| EB404                | "Memories Are Made of This" a Look at Memory Considerations for Smart Card           |      |

| ED                   | Applications                                                                         |      |

| EB405                | Smart Cards: How to Deal Yourself a Winning Hand,                                    |      |

| EB408                | MC68HC705T3 Bootloader                                                               |      |

| Additional I         | nformation                                                                           | 723  |

# **Device Cross Reference**

#### **Device Cross Reference**

This quick-reference list indicates where specific components are featured in applications documents reproduced in this Manual.

| M68HC05      | AN//31                                |

|--------------|---------------------------------------|

|              | -                                     |

|              |                                       |

|              |                                       |

| M68HC05E0    |                                       |

| M68HC11      |                                       |

| WIOOFICTT    |                                       |

|              |                                       |

|              |                                       |

|              |                                       |

|              |                                       |

| ••••••       |                                       |

| MOOOF        |                                       |

| M6805        |                                       |

| ,            |                                       |

| MC68HC05B4   |                                       |

| MC68HC05B6   | _                                     |

|              |                                       |

|              |                                       |

|              |                                       |

|              |                                       |

| MC68HC05C4   |                                       |

|              | AN1067                                |

| MC68HC05C5   |                                       |

| MC68HC05E0   |                                       |

| MC68HC05J1   |                                       |

| MC68HC05L6   |                                       |

| MC68HC05SC11 | · · · · · · · · · · · · · · · · · · · |

| MC68HC05SC21 |                                       |

|              |                                       |

| MC68HC05T1   | AN433                                 |

| MC68HC05T7   | AN448                                 |

| MC68HC11     | AN974                                 |

|              | AN1010                                |

|              | ANE405 HI                             |

|              |                                       |

| MC68HC11A8    | AN1067   |

|---------------|----------|

| MC68HC11A8P1  | AN1065   |

| MC68HC11G5    | AN432    |

| MC68HC11K4    | AN452    |

| MC68HC68T1    | AN1065   |

| MC68HC705B5   | AN440    |

| MC68HC705C8   | AN1067   |

| MC68HC705T3   | EB408    |

| MC68HC805B6   | AN440    |

|               | AN446    |

|               |          |

| MC74LS26      | AN1102   |

| MC3373        | AN1203   |

| MC6805L3      | ANE405 H |

| MC6805SC01    | EB401    |

| MC6805SC03    | EB401    |

| MC14489       | AN431    |

| MC14497       | AN1203   |

| MC68705P3     | AN940    |

| MC68705R3     | AN991    |

| MC144115      | AN441    |

| MC144115P     | AN442    |

| MC145000      | AN442    |

| MC145003      | AN442    |

| MC145004      | AN442    |

| MCC68HC05SC11 | EB400    |

| MCC68HC05SC21 | EB400    |

| MCM60L256     | AN441    |

| MCM2814       | AN446    |

| MPM3004       | AN1120   |

| MPX2000       | AN1097   |

| MTP3055E      | AN1102   |

| MTP3055EL     | AN1102   |

| PCF8573       | AN1066   |

### Abstracts of Applications Documents

#### **Abstracts**

#### AN427 MC68HC11 EEPROM Error Correction Algorithms in C

A modified Hamming code is used to correct one-bit errors and detect two-bit errors in data blocks of up to 11 bits – avoiding the problem of erroneous correction of two-bit errors. The technique is implemented entirely in 'C', and additional functions are provided to program and read MC68HC11 EEPROM using the encoding/decoding algorithms.

#### AN431 Temperature Measurement and Display Using the MC68HC05B4 and the MC14489

Shows the basic building blocks of a temperature control system based on the M68HC05 B-series MCUs. Software routines provided include Look-Up Table Interpolation, Binary to BCD Conversion, Degrees C to Degrees F Conversion, and the basis of a real-time counter/clock. Uses a thermistor as the sensing element to allow easy interfacing to the A/D converter of the MC68HC05B4, but the software principles are easily adapted to other sensors.

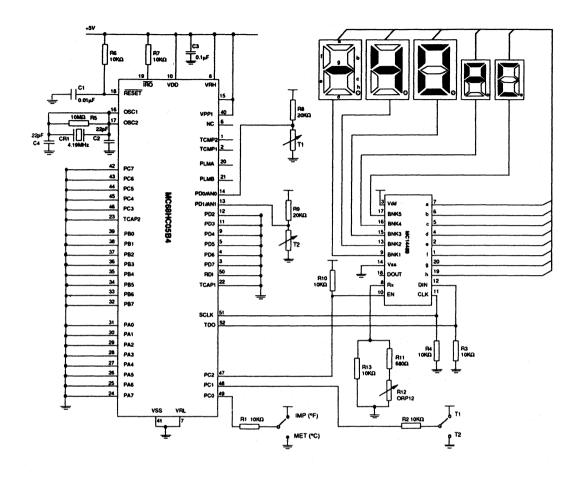

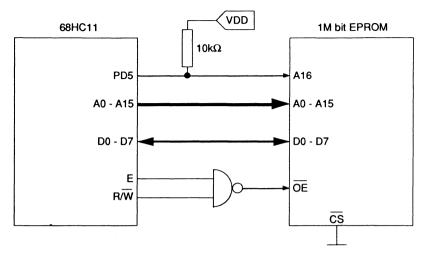

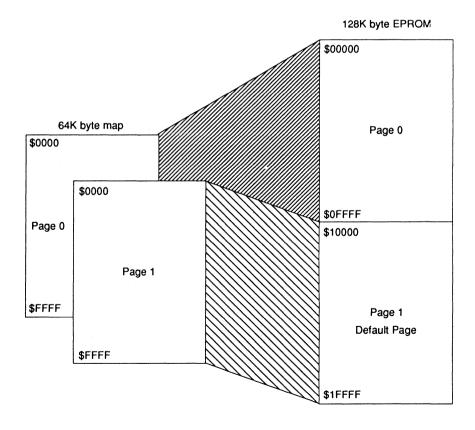

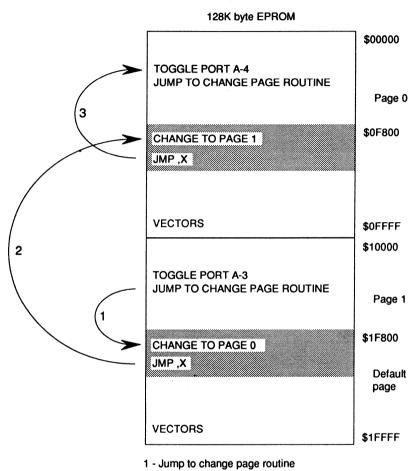

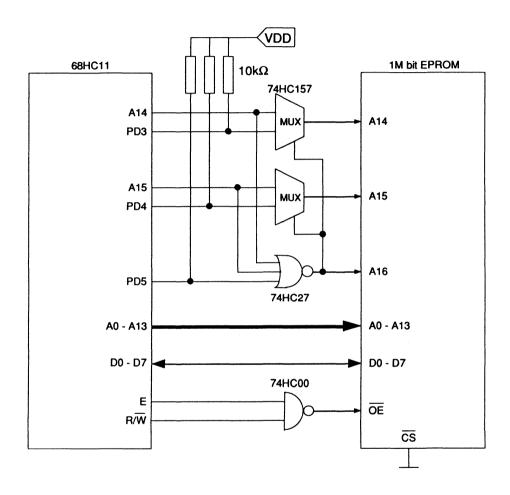

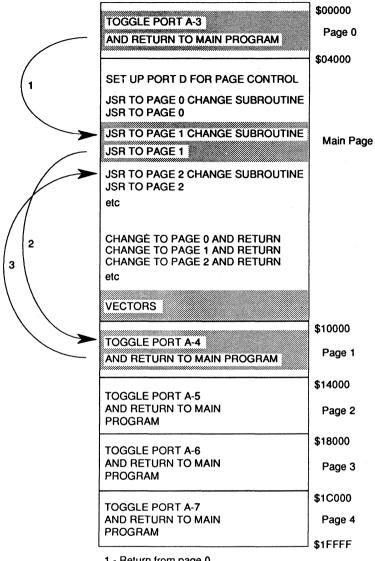

#### AN432 128K byte Addressing with the M68HC11

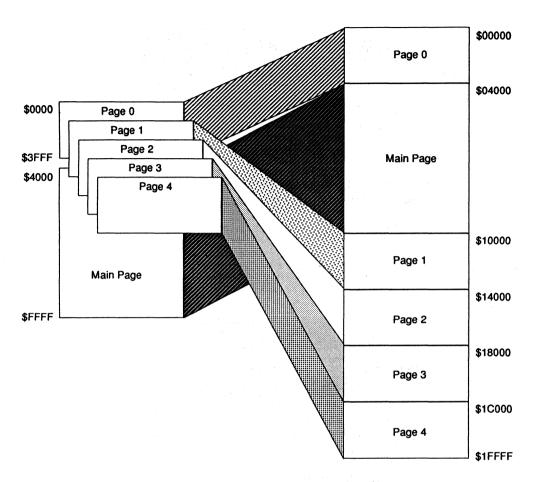

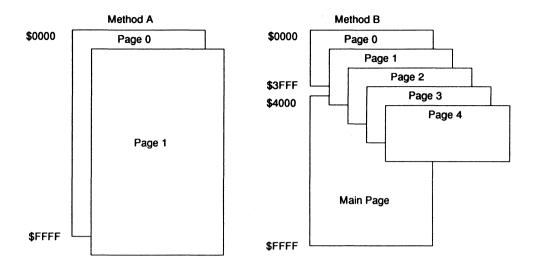

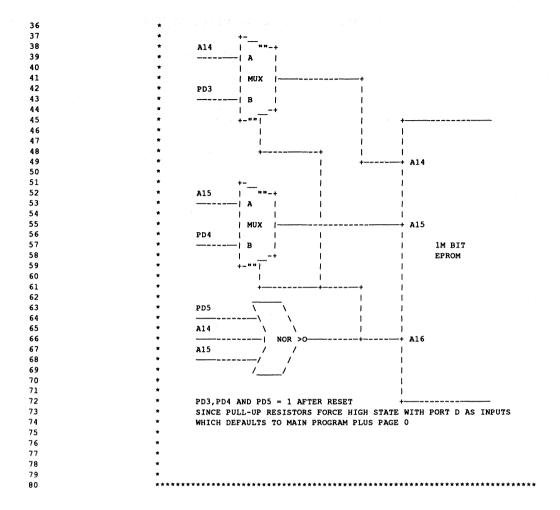

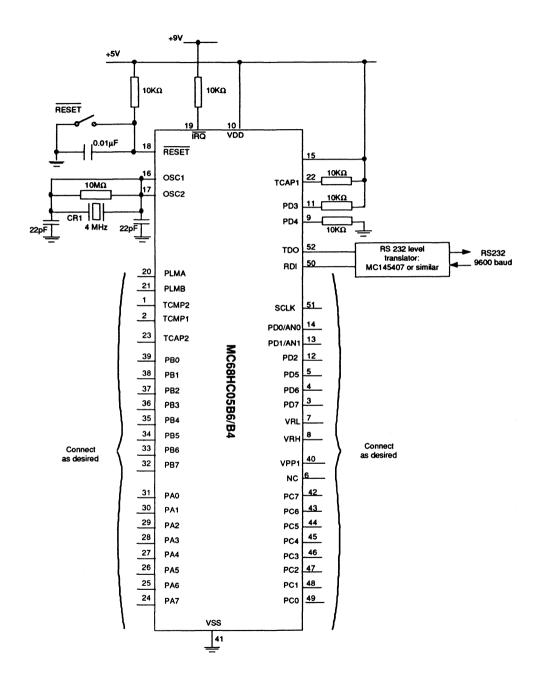

The 64K byte direct addressing capability of the M68HC11 family is insufficient for some applications. This note describes two methods of memory paging – one software only, the other hardware plus software – that allow the MCU to address a 1Mbit EPROM (128K bytes) by manipulation of the address lines. The two methods illustrate the concept of paging and the inherent compromises; the technique may be expanded to other memory combinations. Includes full software listings.

#### AN433 TV On-Screen Display Using the MC68HC05T1

The T-series devices in the M68HC05 MCU Family provide a convenient and cost-effective means of adding On Screen Display capability (OSD) to TVs and VCRs. The MC68HC05T1 is atthe centre of the T-series price/performance range, and is used in this example. Full software listings are provided for a ROM-efficient implementation of an 8-row by 16-character display, including Programme Change, Channel Mode, Automatic Search, Analogues and Channel Name.

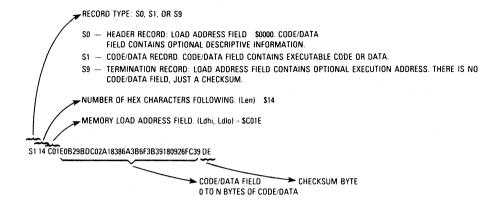

#### AN434 Serial Bootstrap for the RAM and EEPROM1 of the MC68HC05B6

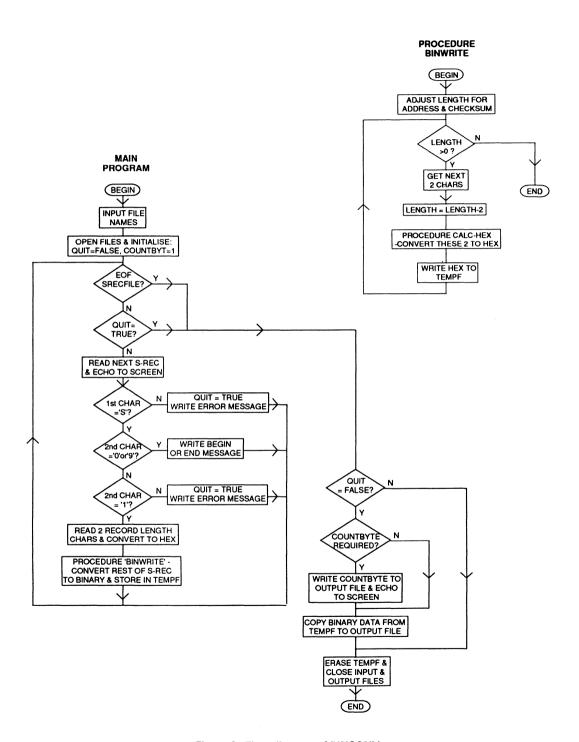

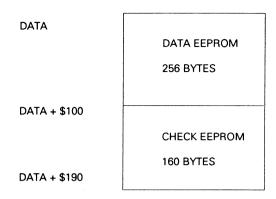

The MC68HC05B6 has 256 bytes of on-chip EEPROM, called EEPROM1, which can be used for non-volatile data storage. In many applications EEPROM1 stores a look-up table or system set-up variables – in these cases it is necessary to initialise the memory during system manufacture. The RAM bootstrap program in the 'B6 mask ROM uses a simple protocol in order to save ROM space, and cannot accept the S-records that are the normal assembler output. This note explains how to convert assembler output to the 'B6 bootstrap format, and how to bootstrap data into EEPROM1.

#### AN436 Error Detection and Correction Routines for M68HC05 Devices Containing EEPROM

Applications based on M68HC05 MCUs increasingly require large amounts of critical data to be stored in the on-chip EEPROM. This note describes 'HC05 software routines which allow stored data to be encoded so that single bit errors in retreived data may be corrected, and two bit errors detected. The routines use a simple Linear Block Code (Hamming Code) for encoding the stored data. They were written originally for the MC68HC05-SC21 Smart Card MPU, but can be modified easily to run on any 'HC05 MCU with EEPROM.

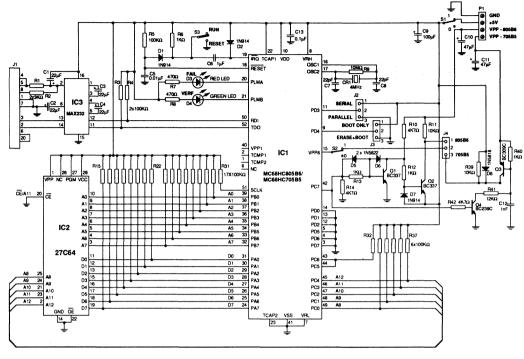

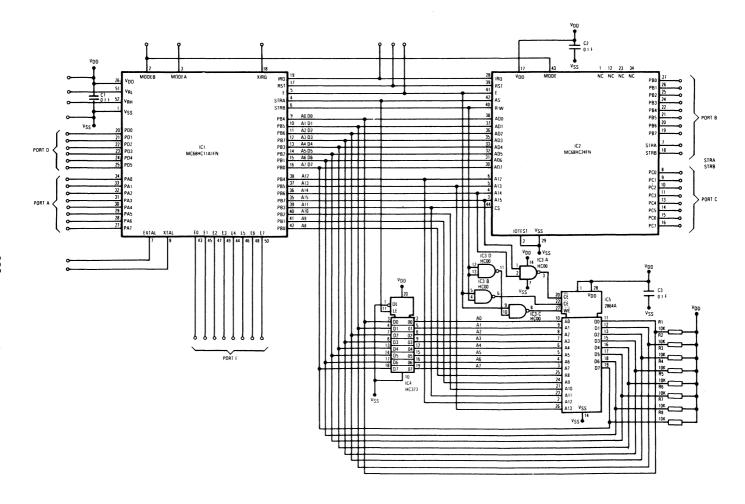

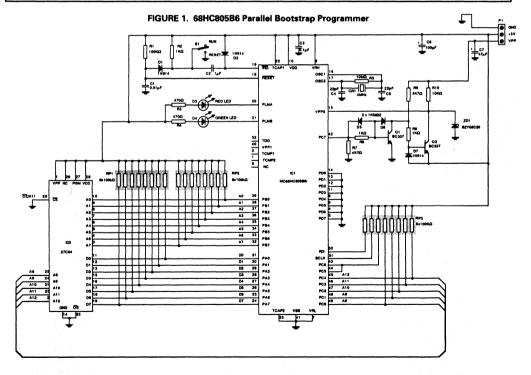

#### AN440 MC68HC805B6 and MC68HC705B5 Serial/Parallel Programming Module

The MC68HC05B serial/parallel programmer module allows the user to program MC68HC805B6 and MC68HC705B5 MCUs. This note describes its various operating modes, and gives details of its construction and use. Includes circuit diagram and parts list.

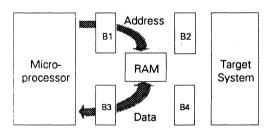

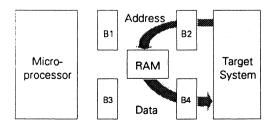

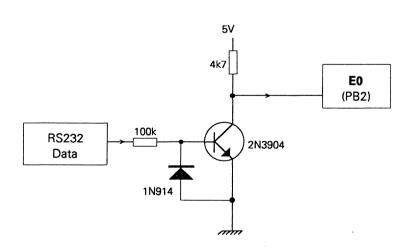

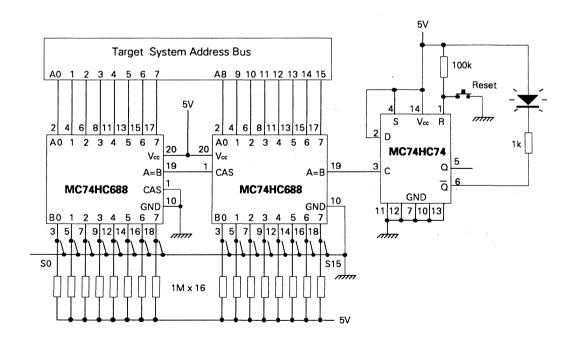

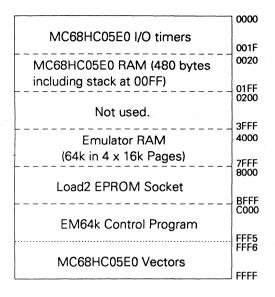

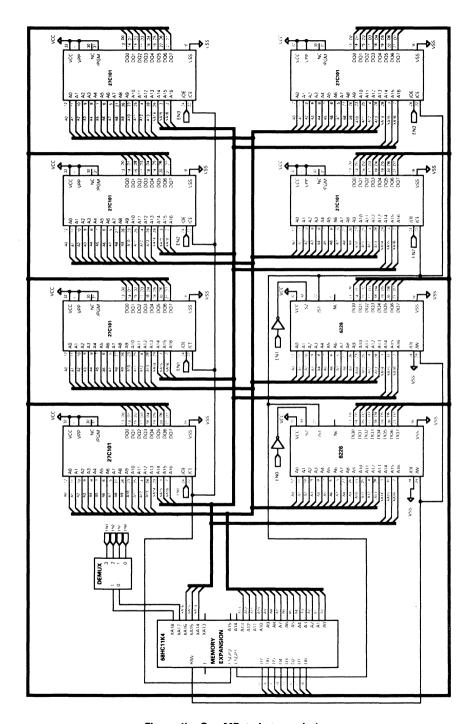

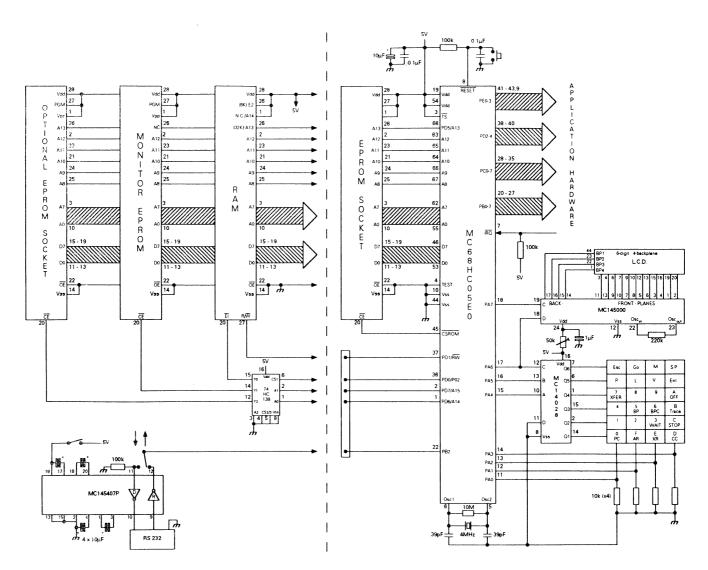

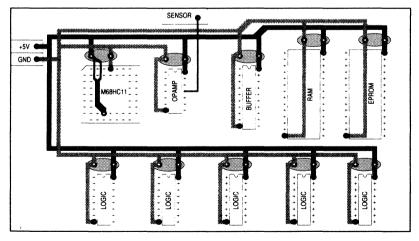

#### AN441 MC68HC05E0 EPROM Emulator

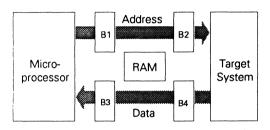

Unlike other members of the M6805 family, the MC68HC05E0 has no on-chip ROM but can address a full 64K bytes of external memory; the external memory may be ROM, EPROM, RAM and/or additional hardware. This EPROM emulator illustrates a typical use of this type of MCU; it includes a keyboard, LCD, serial communication and 64K of paged RAM. It can replace with RAM the program ROM or EPROM in a target system through a cable connection to the system's EPROM socket, and can be used to debug and modify the target system software. Includes an assembled listing of the emulator control program.

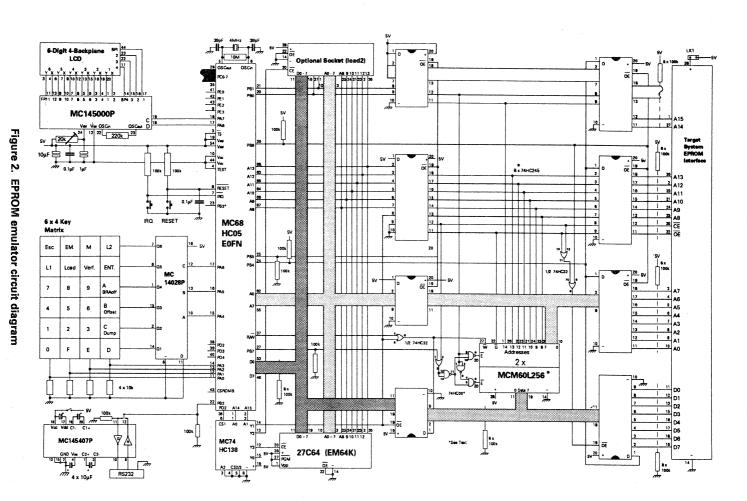

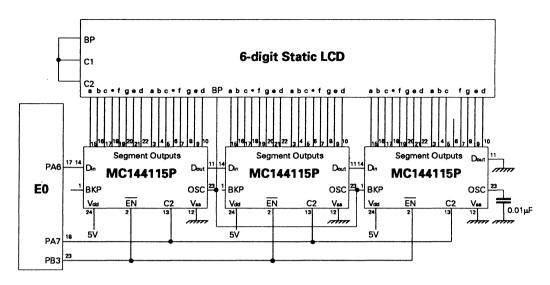

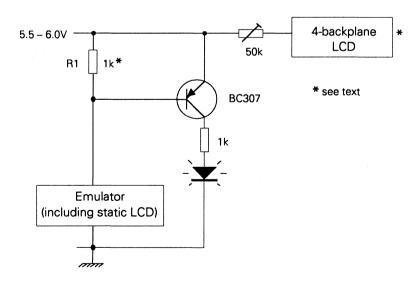

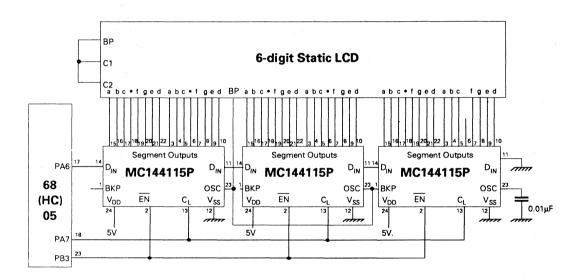

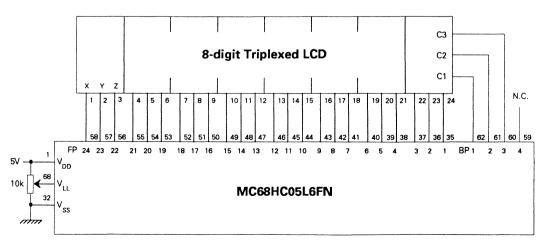

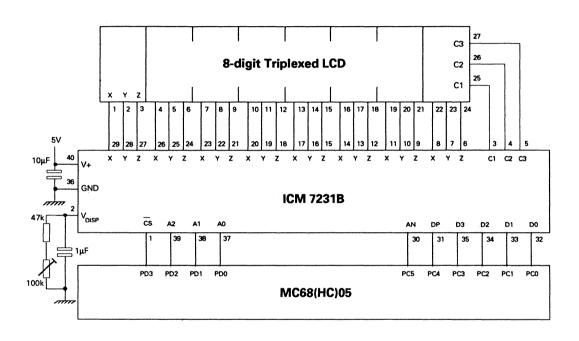

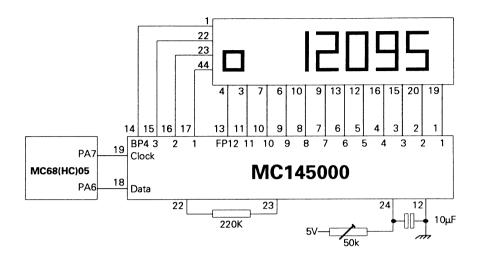

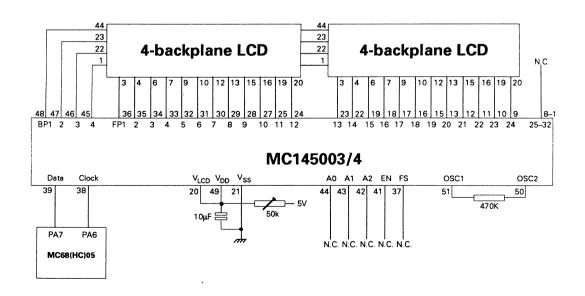

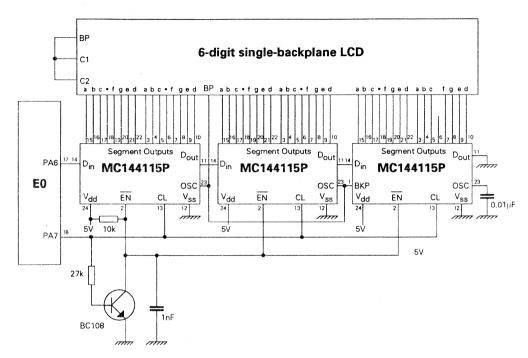

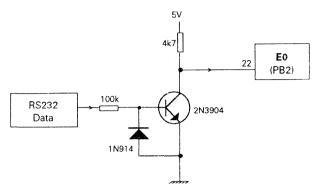

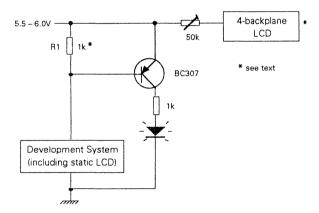

#### AN442 Driving LCDs with M6805 Microprocessors

The MC68HC05L series of MCUs include circuitry for direct LCD drive. Other MCUs in the M6805 and M68HC05 families have a variety of I/O and display drive capabilities. This comprehensive note describes alternative LCD drive arrangements for applications with different numbers of backplanes and display drive capabilities, including software-based and display driver chip solutions. Circuits and software listings are provided. The techniques apply equally to other MCU families such as the M6801 and M68HC11.

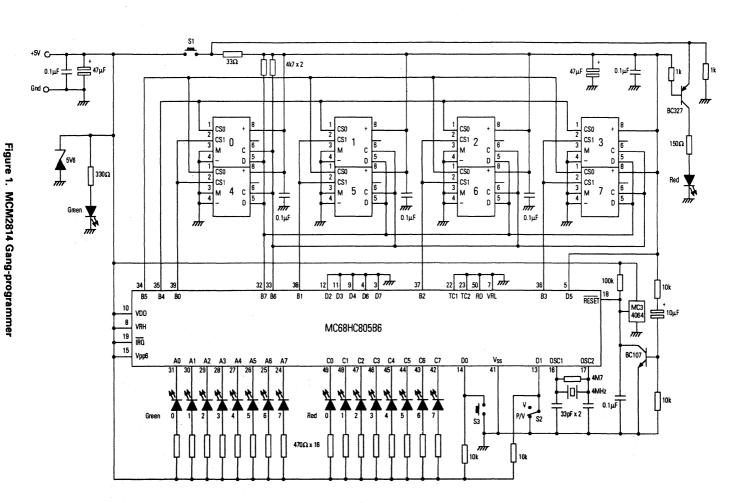

#### AN446 MCM2814 Gang-Programmer Using an MC68HC805B6

Non-volatile memories (NVM) such as the MCM2814 are widely used in consumer equipment such as television receivers to store semi-permanent, user-defined information. They may also contain data such as optimum sound and picture settings. In a production environment, the initial loading of this data can be achieved quickly by copying an existing NVM. This note describes a programmer based on an MC68HC805B6 which in four

seconds can fully program eight MCM2814s in parallel and verify them individually.

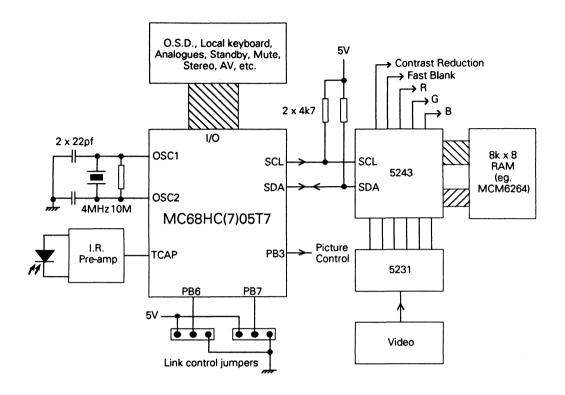

#### AN448 "FLOF" Teletext using M6805 Microcontrollers

The "-T" members of Motorola's M68HC05 MCU family provide a cost-effective method of adding On Screen Display (OSD) to TVs and VCRs. This note describes an example of Full Level One Feature (FLOF) Teletext control software written for the MC68HC05T7 to control type 5243 Teletext chips. Around 3K bytes of ROM are used, allowing the code to fit with tuning, OSD and stereofunctions into the 7.9K bytes of the MC68HC05T7. The example software includes the Spanish implementation of Packet 26; Packet 26 allows for the substitution of specific characters for a particular country.

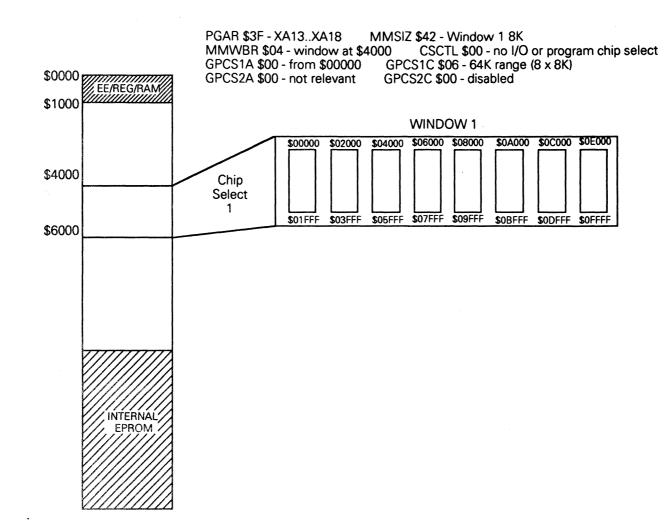

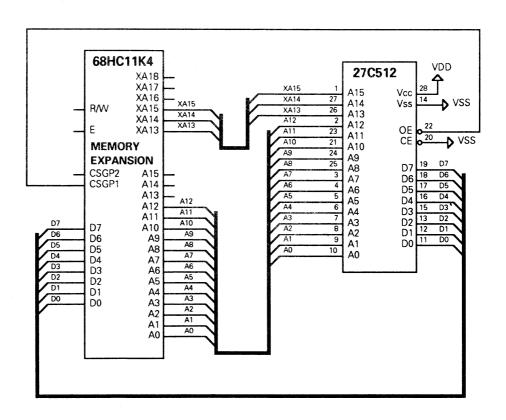

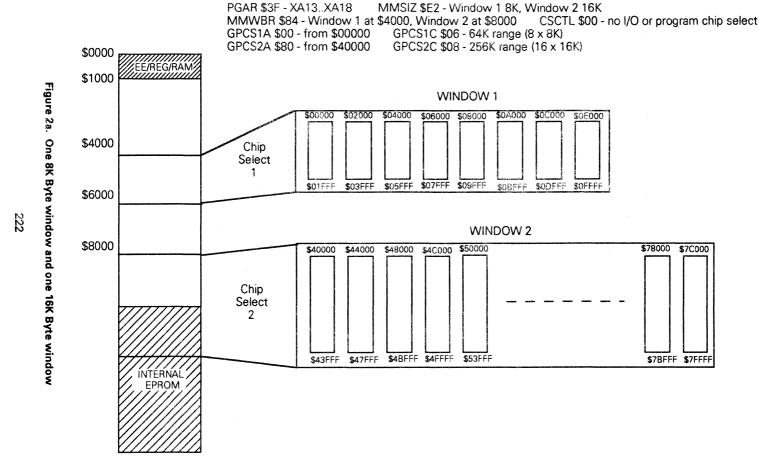

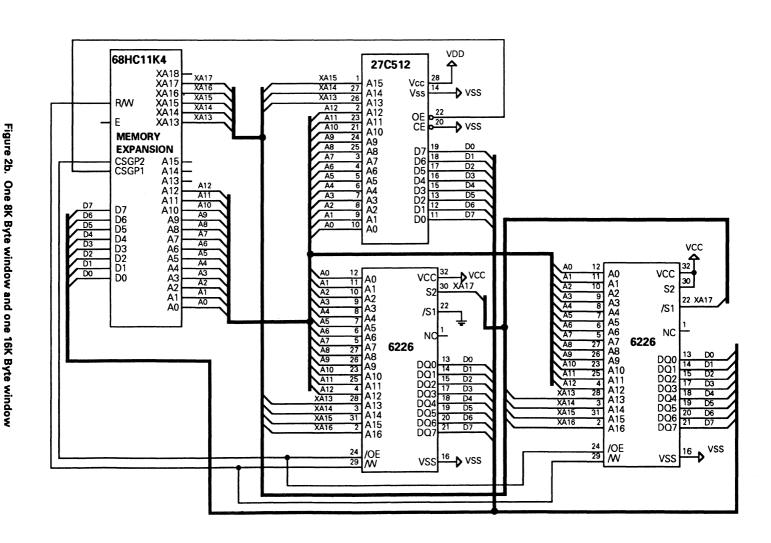

#### AN452 Using the MC68HC11K4 Memory Mapping Logic

The MC68HC11K4 includes memory expansion logic which allows the 64 KByte addressing range of the M68HC11 CPU to be extended to more than 1 MByte. This note discusses the operation of this logic and provides examples of memory maps and possible hardware configurations.

#### AN459 A Monitor for the MC68HC05E0

Development systems for single-chip MCUs can be complex and relatively expensive. This can dissuade potential users from designing them into new applications. This note describes a simple "entry level" development system suitable for debugging hardware and software for the M6805 family of microprocessors. Includes full descriptions, circuit diagram and a listing of the monitor software.

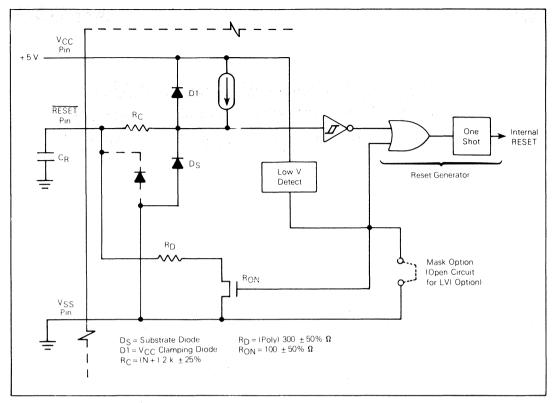

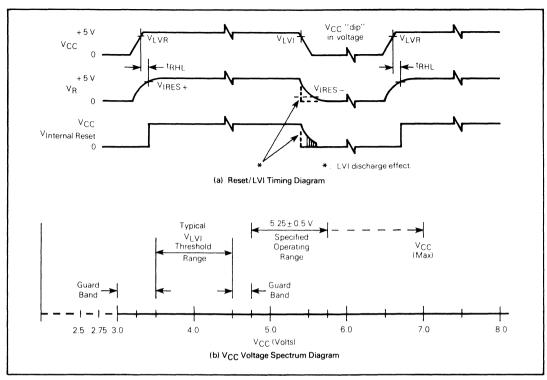

#### AN890 Low Voltage Inhibit (LVI) Capability of the M6805 HMOS Microcomputer (MCU) Family

The LVI option provides a cost effective means for the MCU to sense a drop in supply voltage and then shut itself down in well-defined manner. Because the option does not require any additional external parts it provides an overall product cost reduction. The LVI option is provided at the time of manufacture by on-chip circuitry contained in part of the user's ROM pattern. This application note includes an LVI schematic diagram as well as a listing of the monitor and self-check programs.

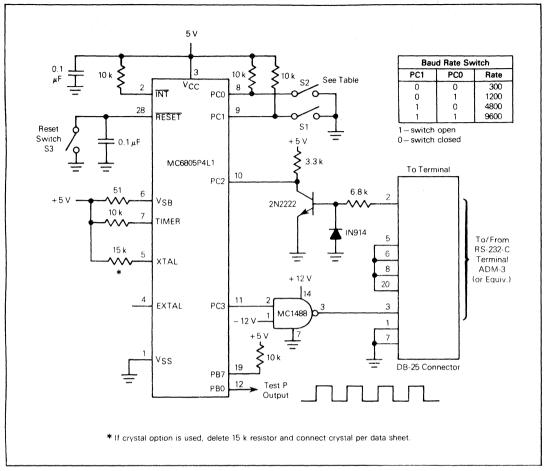

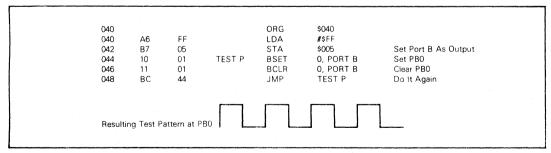

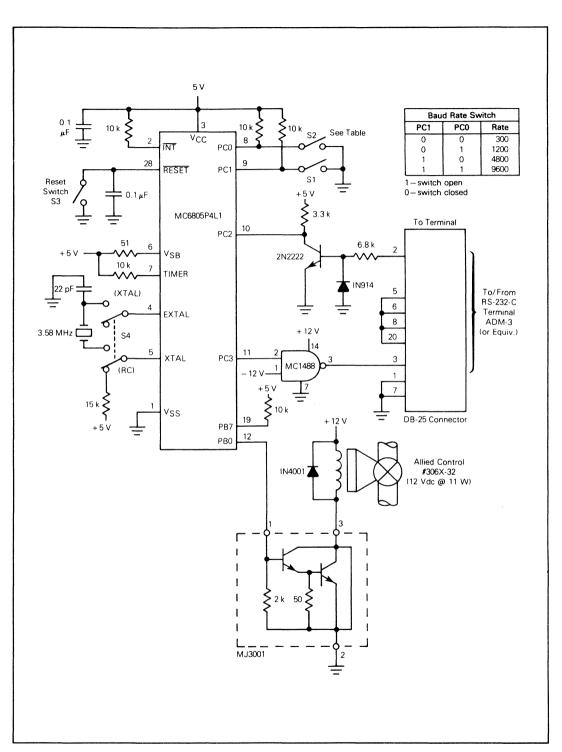

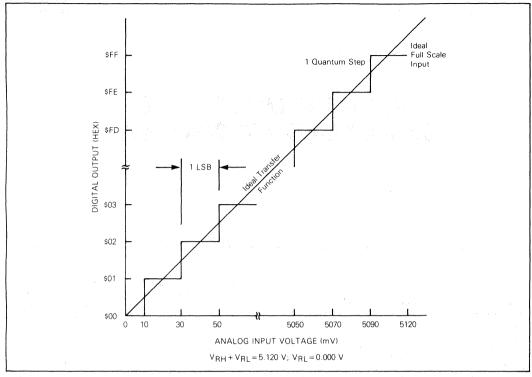

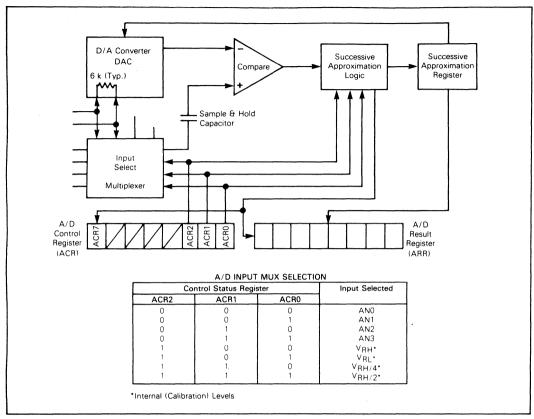

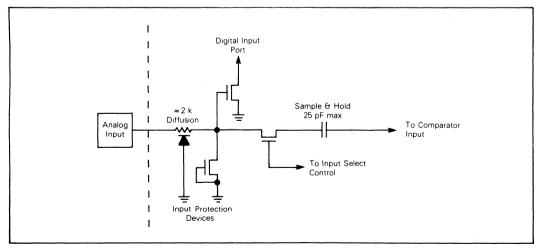

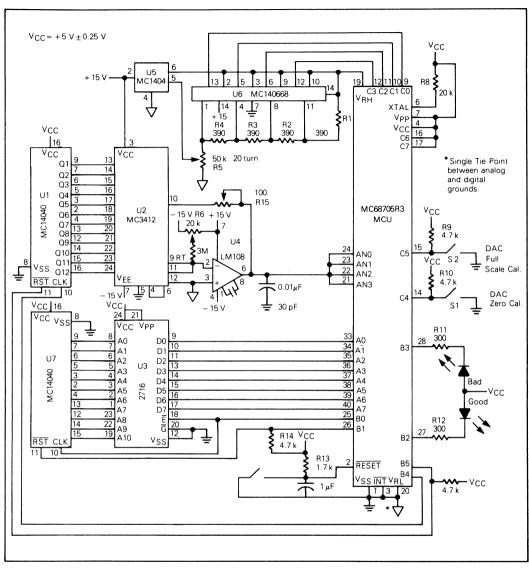

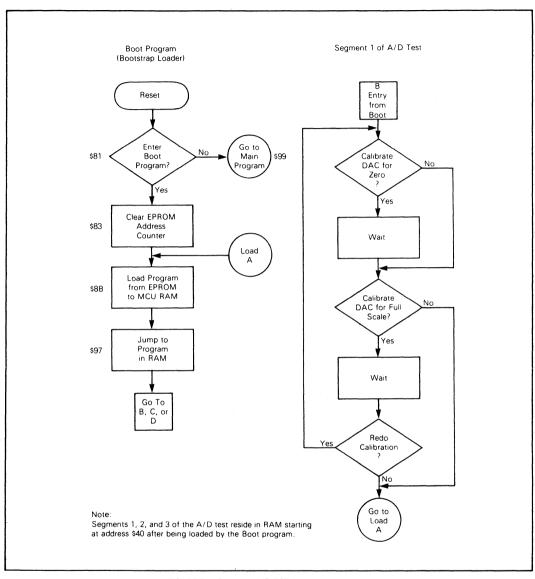

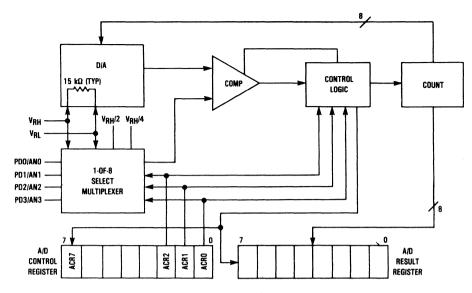

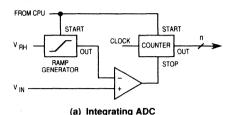

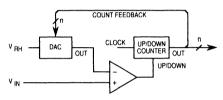

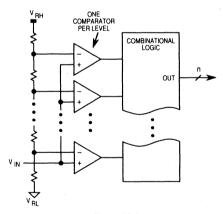

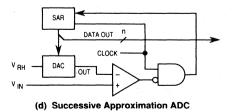

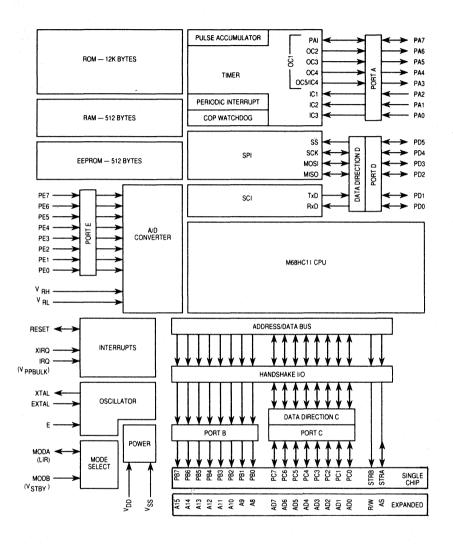

#### AN900 Using the M6805 Family On-Chip 8-Bit A/D Converter

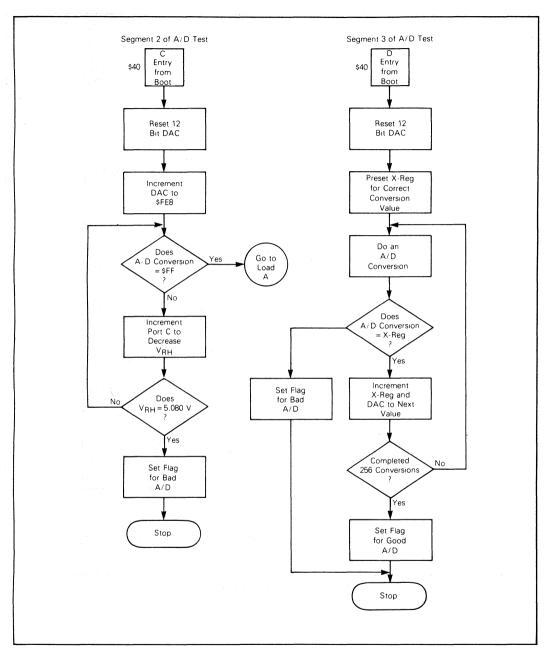

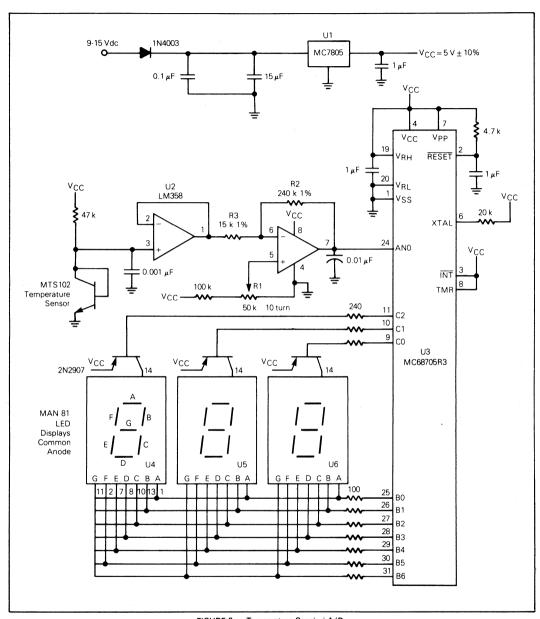

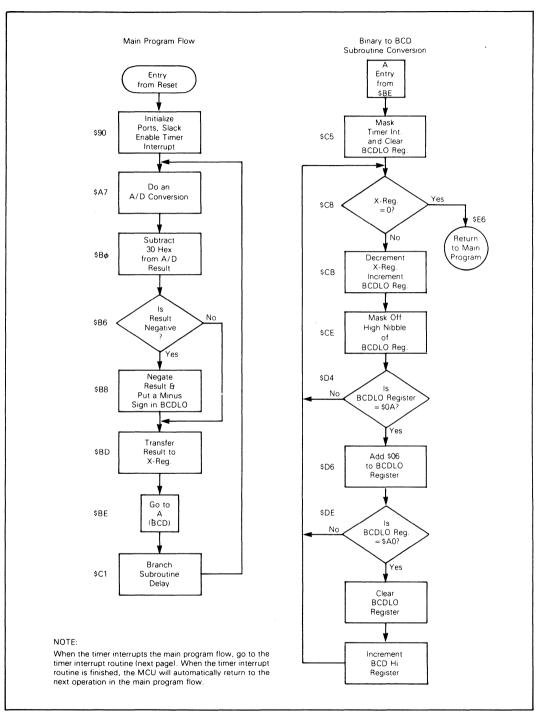

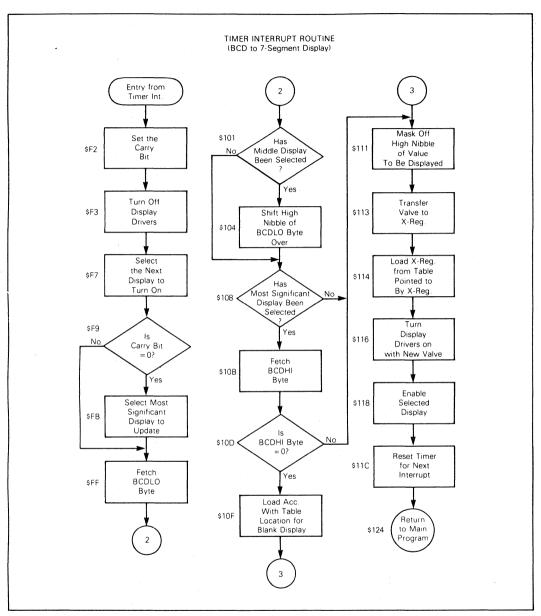

Factors which should be considered when using on-chip analog-to-digital (A/D) converters are covered. The pertinent circuit elements and terminology are defined and a self-test hardware/software technique is illustrated. An example on how to manipulate the converted analog data from a temperature sensor is given. It is intended for the digital designer with little or no programming experience.

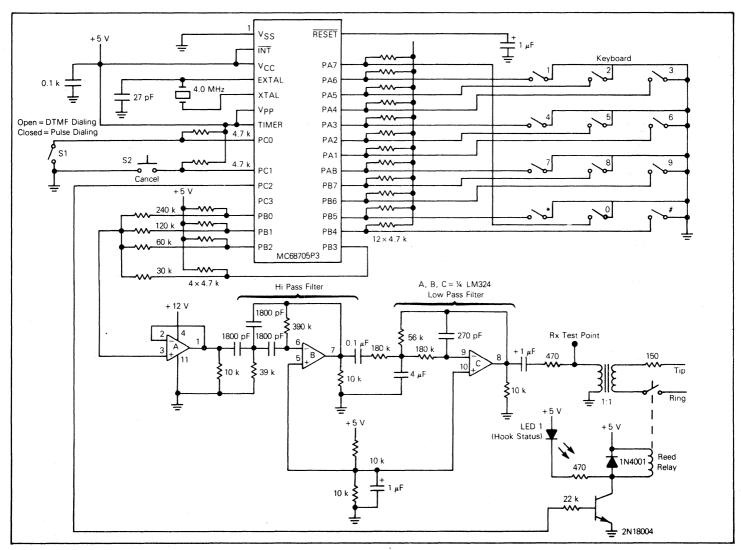

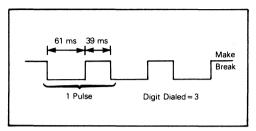

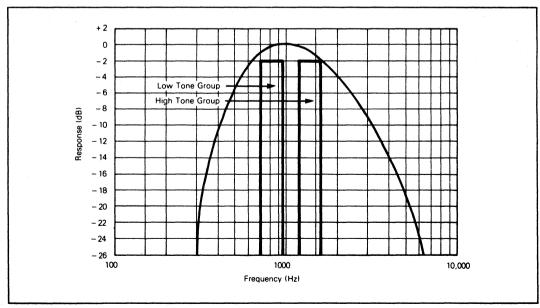

#### AN940 Telephone Dialling Techniques Using the MC6805

Intelligent telephones are increasing in popularity – MCUs from the versatile M6805 family make ideal controllers. This demonstration board, based on an MC68705P3 single-chip MCU, shows two cost-effective methods of DTMF and pulse-type dialling. Full hardware schematic and software listings included.

#### AN974 MC68HC11 Floating-Point Package

While most MC68HC11 applications can be implemented using 16-bit integer precision, certain algorithms may be difficult or impossible without floating-point. This application note details an efficient floating-point package that includes basic trig functions and square root in addition to add, subtract, multiply and divide. It requires just over 2k bytes of memory, with only 10 bytes of page zero RAM in addition to stack RAM.

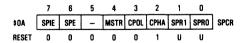

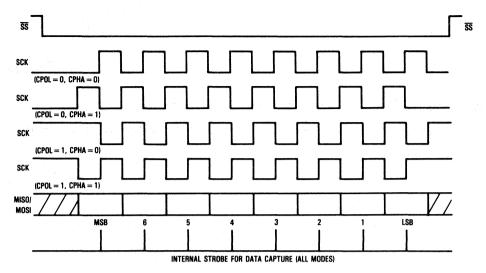

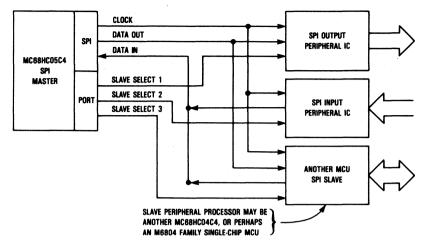

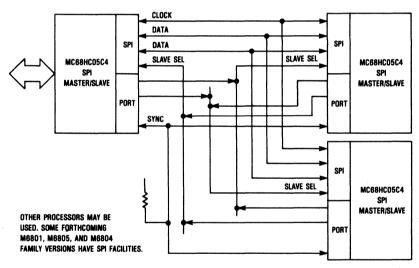

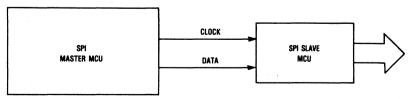

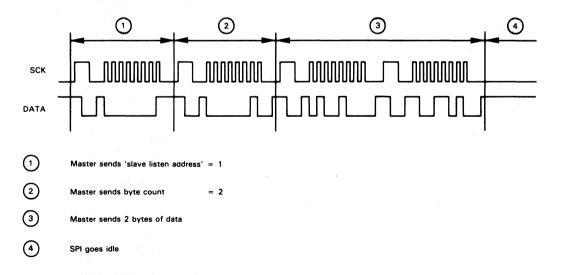

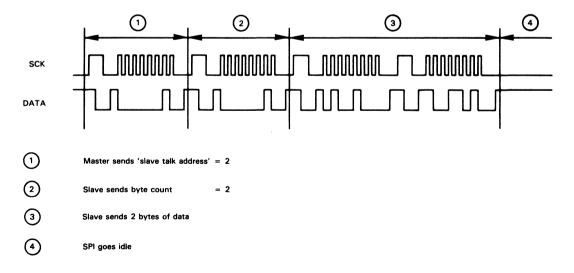

#### AN991 Using the Serial Peripheral Interface to Communicate Between Multiple Microcomputers

Communication between multiple processors can be difficult when different types are used. One solution is the SPI, an interface intended for communication between ICs on the same board. It can be implemented in software, allowing communication between two MCUs where one has SPI hardware and the other does not. Costly expansion buses and UARTs are eliminated. The scheme is illustrated with a temperature/time display circuit using an MC68HC05C4 and an MC68705R3.

#### AN1010 MC68HC11 EEPROM Programming from a Personal Computer

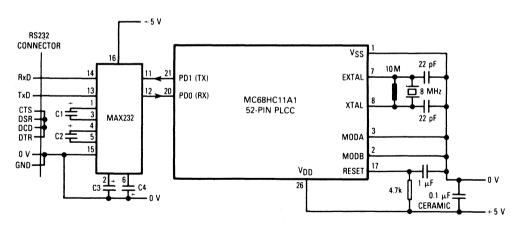

Describes a simple and reliable method of programming the MC68HC11's internal EEPROM (or EEPROM connected to its external bus) by downloading data in Motorola S-record format from a standard personal computer (PC) fitted with a serial communications port. Includes BASIC program for the PC (to Program External EEPROM/RAM, Program Internal EEPROM, or Verify internal or External EEPROM/RAM) and the source listing of MC68HC11 code for downloading to RAM to receive S records.

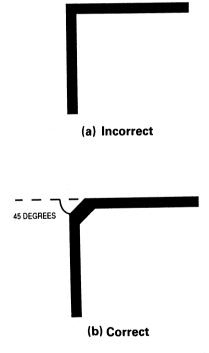

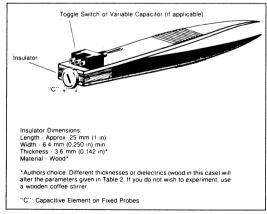

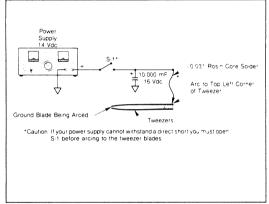

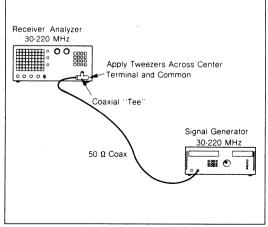

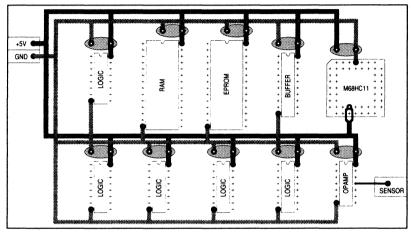

#### AN1050 Designing for Electromagnetic Compatibility (EMC) with HCMOS Microcontrollers

As the operating speeds of the latest HCMOS devices increase, the MCU system designer must take more account of the electromagnetic compatibility (EMC) of the finished product. This discussion relates mainly to emission control, but most of the techniques also reduce electromagnetic susceptibility. Subjects include Legal Requirements, RFI Problems, types of radiation, Supply Decoupling, Grounding Techniques and PCB Layouts. Incorporates an article reprint from EMC Technology describing an EMI/RFI diagnostic probe.

#### AN1055 M6805 16-bit Support Macros

MCUs from the M6805 family are usually chosen for applications requiring small program memory and low computing power, where their low cost is an important benefit. However they may also be used in more advanced applications by employing the advanced software techniques described here. The examples are suitable for 'black box' operation (they may be used without knowing how they work) and consist of macros and subroutines that support pseudo registers on the '6805, simulating registers and addressing modes available on the M68HC11.

#### AN1057 Selecting the Right Microcontroller Unit

Selecting the proper MCU for an application is one of the critical decisions which can control the success or failure of the project. There are numerous criteria to consider; many of them are presented here along with the thought processes guiding their selection. The reader should attach an appropriate grading scale before evaluating the total and making the correct decision.

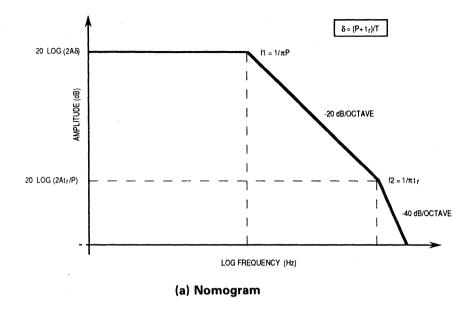

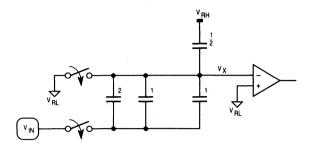

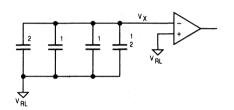

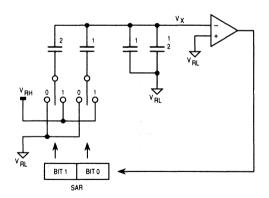

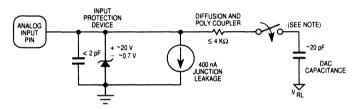

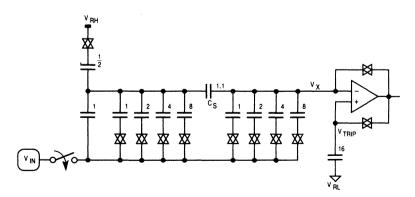

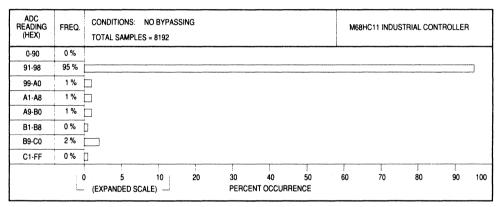

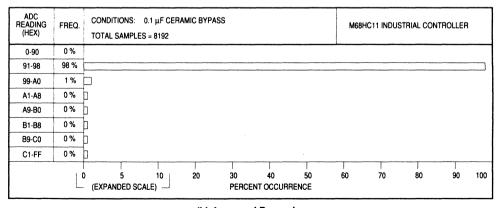

#### AN1058 Reducing A/D Errors in Microcontroller Applications

The MCU with integrated Analogue to Digital Converter provides a highly cost-effective solution for many mixed analogue/digital applications. However, combining a wide bandwidth ADC system on the same die as a high-speed CPU can lead to noise problems in the analogue measurements. This comprehensive note lays down basic system guidelines for the design phase of an MCU-based product, to avoid ADC problems. Includes an examination of a real-world system.

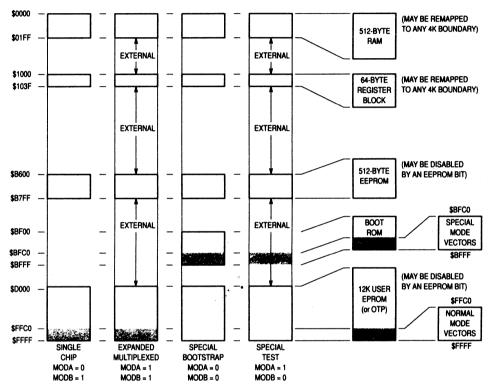

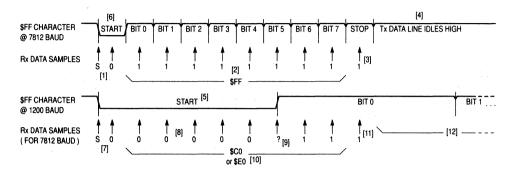

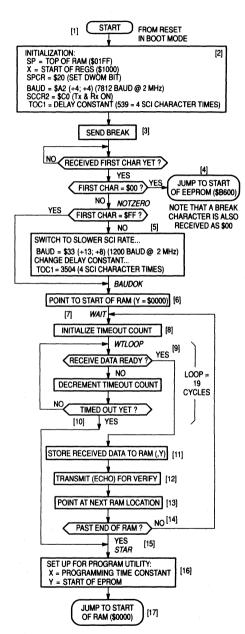

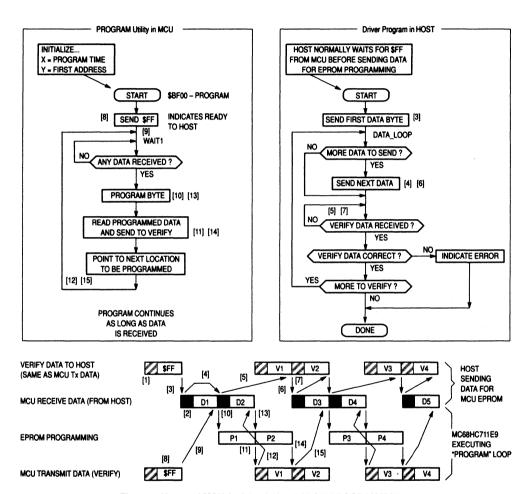

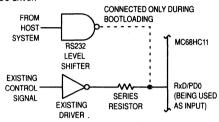

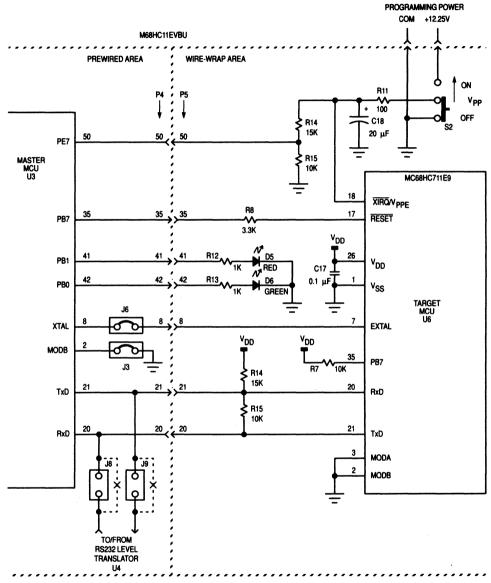

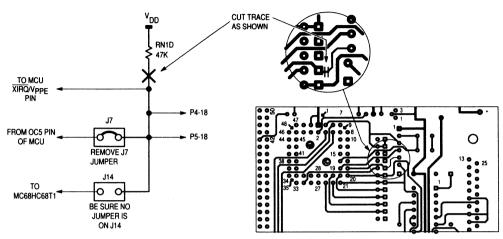

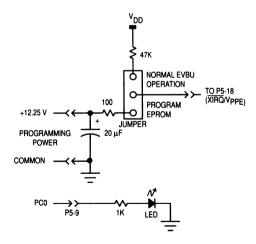

#### AN1060 MC68HC11 Bootstrap Mode

The M68HC11 Bootstrap Mode allows a user program to be loaded into internal RAM through the Serial Communications Interface (SCI). In addition to operating normally, this program can do anything a factory test program can do since the protected control bits become accessible; Expanded Mode resources are available because the control bits can be changed by the bootstrap program. Although the basic concepts are simple, some subtle implications of this mode need careful consideration, both to avoid problems and to find useful applications. Includes commented listings for selected M68HC11 bootstrap ROMs.

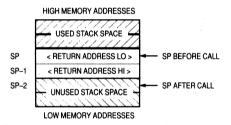

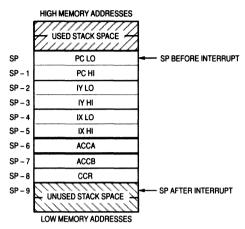

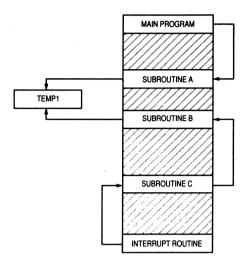

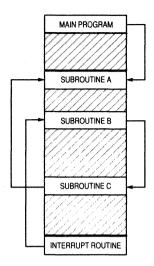

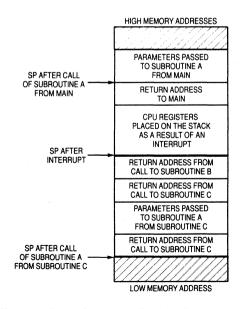

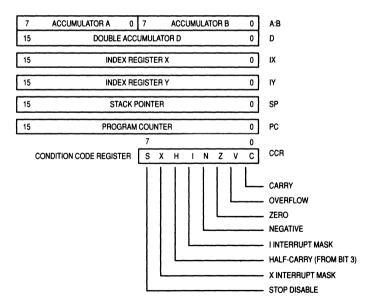

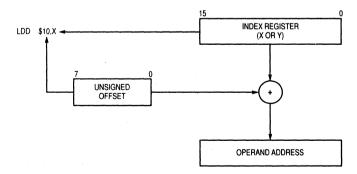

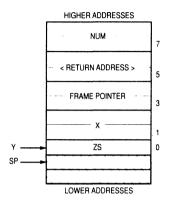

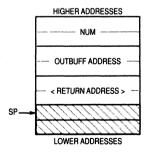

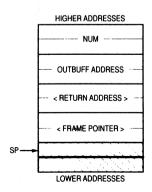

#### AN1064 Use of Stack Simplifies M68HC11 Programming

Architectural extensions to the M6800 family built in to the MC68HC11 allow easy manipulation of data on the stack. The CPU uses the stack for subroutine and interrupt return addresses. This note discusses two additional uses – the storage of local variables and subroutine parameter passing – that can simplify programming and debugging. It describes the basic operation of the MC68HC11 stack, the concept of local and

global variables, subroutine parameter passing, and the use of the instruction set to achieve the additional uses. Includes example listings illustrating the techniques.

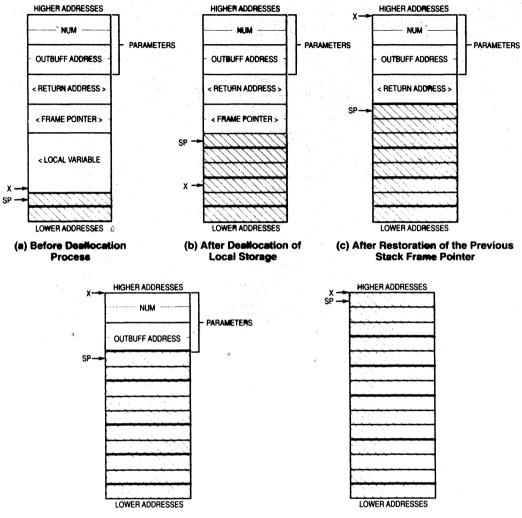

#### AN1065 Use of the MC68HC68T1 Real-Time Clock with Multiple Time Bases

The MC68HC68T1 Real Time Clock plus RAM can use a crystal or the 50/60Hz line frequency as its timebase; a Serial Peripheral Interface is provided for communication with a microcomputer. Applications are often line powered during normal operation, using the line frequency as timebase, but must continue to maintain the correct time of day froma crystal source when mains power is lost. The MC68HC68T1 is not capable of switching between the two frequency sources directly, and additional support by the MCU is necessary. This note describes the necessary hardware and software, based on an MC68HC11A8P1 MCU.

#### AN1066 Interfacing the MC68HC05C5 SIOP to an I<sup>2</sup>C Peripheral

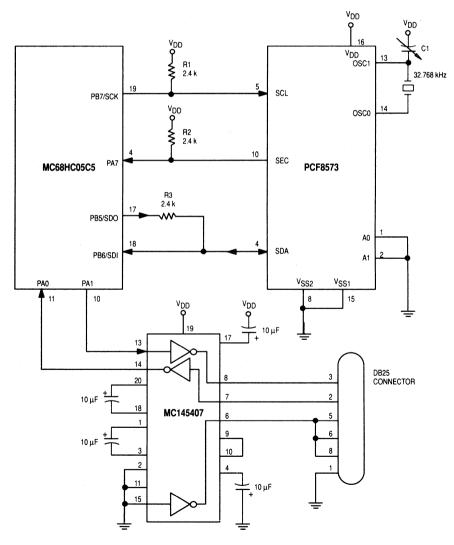

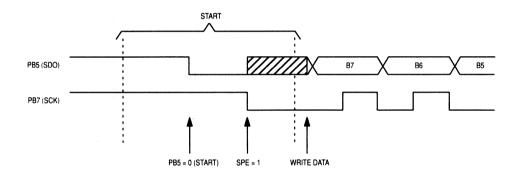

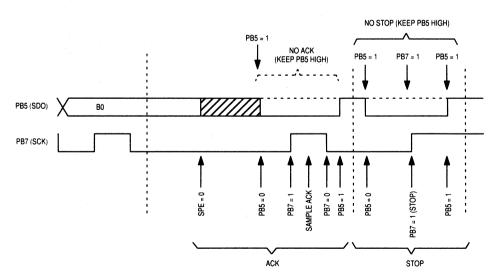

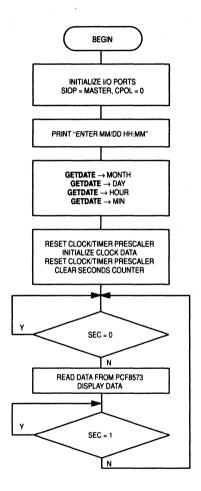

A standard MCU may not have all the peripherals required in a system on chip. The problem can be solved by interfacing the MCU to off-chip peripherals, ideally using a synchronous serial communication port. Unfortunately these peripherals may not have an interface that is compatible with Motorola's simple synchronous Serial I/O Port (SIOP). This note describes how the SIOP on the MC68HC05C5 can be interfaced to an I<sup>2</sup>C peripheral, in this case the PCF8573 Clock/Timer. Includes circuit and software listings for a timer/calendar application that can interface with a terminal.

#### AN1067 Pulse Generation and Detection with Microcontroller Units

MCUs are often required to generate timed output pulses, and to detect and measure input pulses. Output pulses might strobe a display latch, transmit a code or meter an action in a process control system. Input pulses can range from microseconds to hours, and include detecting pushbutton closures, receiving codes or measuring engine rotation. This note describes various methods of generation and detection using several families of Motorola MCUs with differing timer structures. Includes program listings.

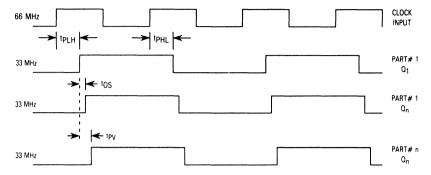

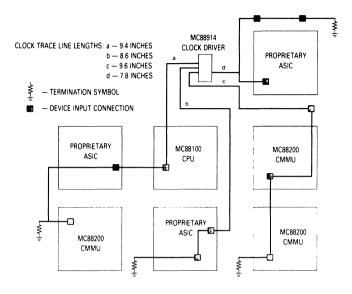

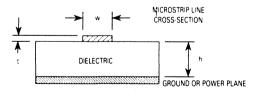

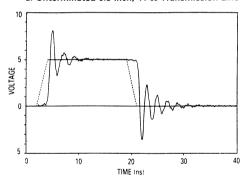

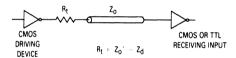

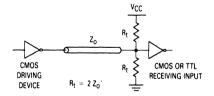

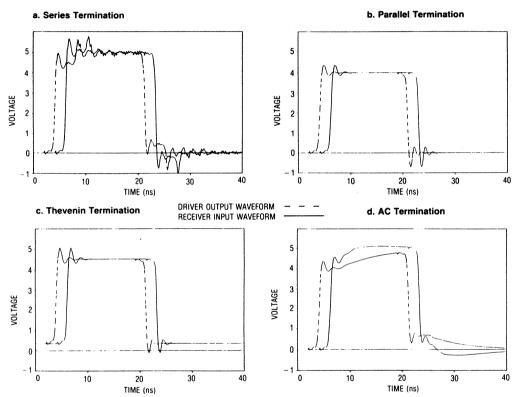

#### AN1091 Low Skew Clock Drivers and their System Design Considerations

With microprocessor-based systems now running at 33MHz and beyond, low-skew clock drivers have become essential — Motorola produces several devices with less than 1ns skew between outputs. Unfortunately, simply plugging one of these high performance clock drivers into a board does not guarantee trouble-free operation. Careful board layout and system noise considerations must also be taken into account.

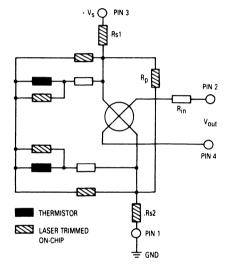

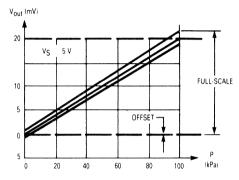

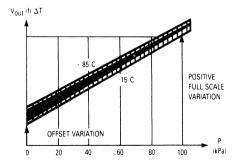

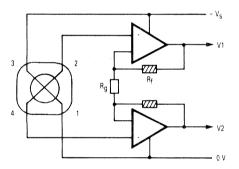

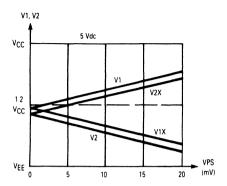

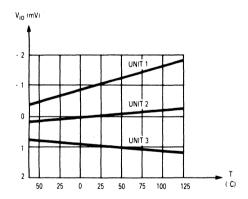

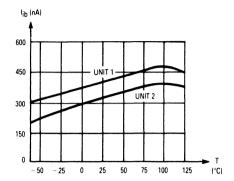

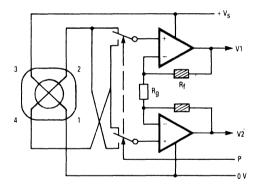

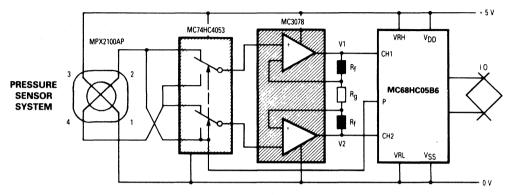

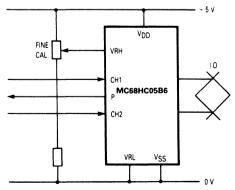

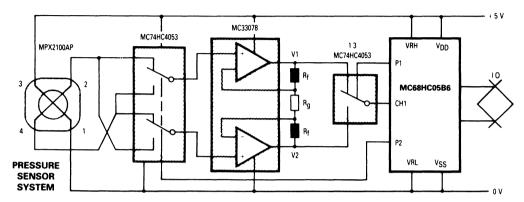

#### AN1097 Calibration-Free Pressure Sensor System

The MPX2000 Series of pressure transducers give an output signal proportional to applied pressure. They are available as both ported and unported assemblies for pressure, vacuum and differential measurement. By using the on-chip A/D converter of the MC68HC05B6 MCU, an accurate, reliable and versatile pressure measurement system can be designed which needs no external calibration.

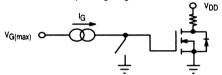

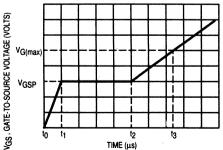

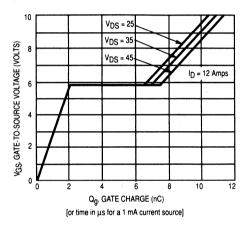

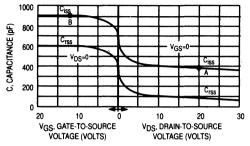

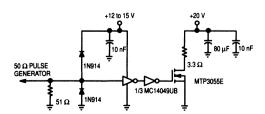

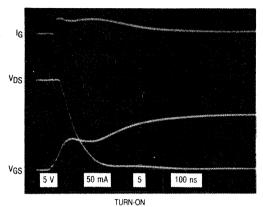

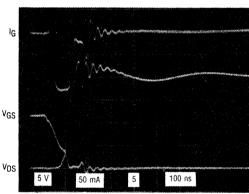

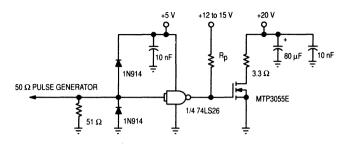

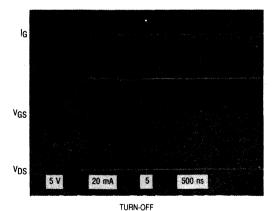

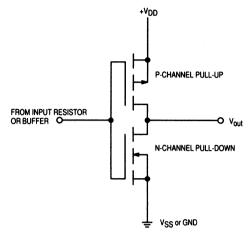

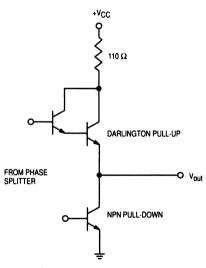

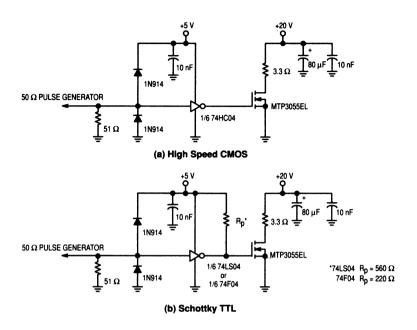

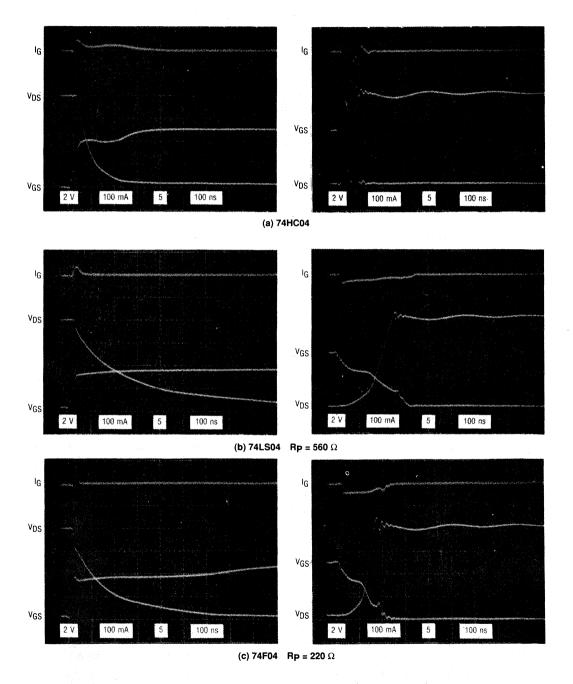

#### AN1102 Interfacing Power MOSFETs to Logic Devices

Most popular power MOSFETs need 10 volts of gate drive to support their maximum drain current. This creates problems when attempting to drive from 5 volt logic. The new Logic Level power MOSFETs solve some but not all of the problems. This note discusses easy methods of directly interfacing both types of MOSFET to TTL and CMOS logic, and to microprocessors such as the M68HC11. Discusses a method of calculating switching times, to minimise switching losses, and stresses the significance of logic power supply variations.

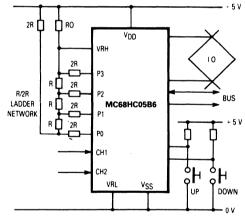

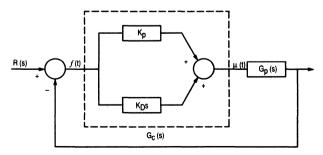

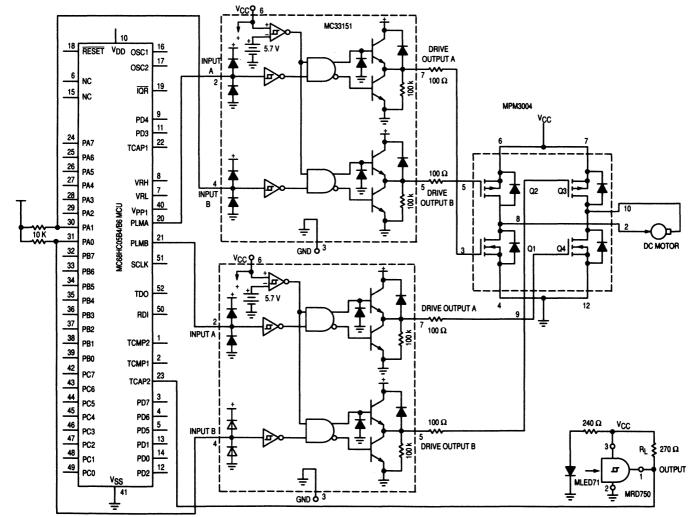

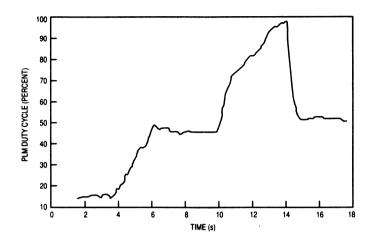

#### AN1120 Basic Servo Loop Motor Control Using the MC68HC05B6 MCU

A Proportional Derivative (PD) closed-loop speed control for a brush motor can be created using four integrated circuits, two opto discretes and less than 200 bytes of code. The use of an MCU in feedback control systems is increasingly commonplace. It is justified when system flexibility is needed, for example to accommodate varying drive motors or to allow wear parameters to be stored in EEPROM. This design is based on an MC68HC05B6 MCU and an MPM3004 power MOSFET H-bridge.

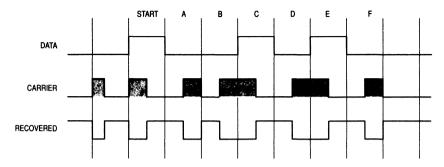

#### AN1203 A Software Method for Decoding the Output from the MC14497/MC3373 Combination

Infrared communication is now widely used as a simple and effective means of remote control over short distances. A variety of encoding methods is used, including the biphase scheme implemented by the MC14497, a complete building block for IR data transmission. The MC3373 is a companion receiver chip to the MC14497, providing front-end processing to interface a photo detector to a TTL level. This note describes, with software listings for the MC68HC01 and the MC68HC05, the decoding of the data at the output of the MC3373.

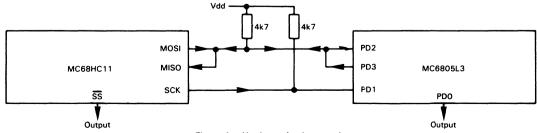

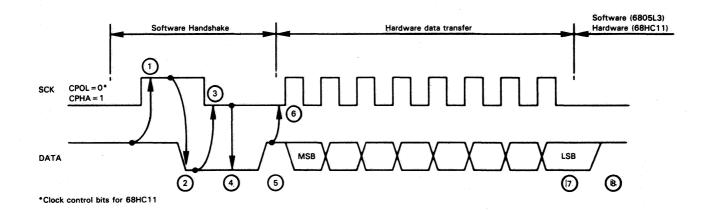

#### ANE405 BI-Directional Data Transfer Between MC68HC11 and MC6805L3 Using SPI

The powerful Serial Peripheral Interface available on many Motorola MCUs is implemented in 2 forms (the HCMOS families support only Level 1, Level 2 is implemented only on HMOS processors). Both levels communicate easily with each other, but Level 2 has additional

capabilities including asynchronous communication. This note describes a method of achieving synchronous communication between levels 1 and 2, and explains the on-chip differences in SPI implementation.

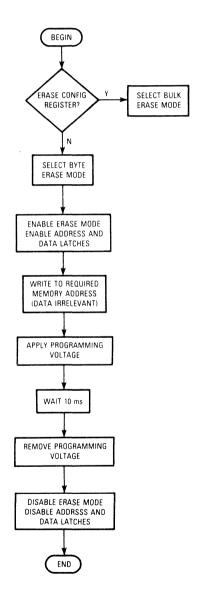

#### ANE418 MC68HC805B6 Low-Cost EEPROM Microcomputer Programming Module H

The EEPROM feature of the MC68HC805B6 microcomputer enables the user to emulate the MC68HC05B6 and the MC68HC05B4. This note describes one programming technique for the MC68HC805B6 internal EEPROM, and describes the design of the simple programming module required.

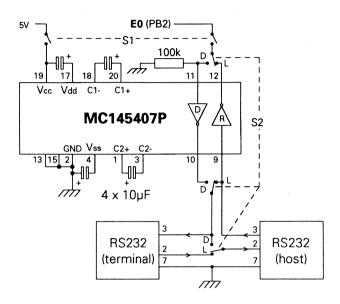

#### ANE420 Monitor Program for the MC68HC05B6 Microcomputer Unit HI

A monitor program is available in the mask ROM of a 68HC05B6 MCU (XC68HC05B6FN MONITOR) which allows the user to write and debug small portions of 68HC05B6 code. It is used in conjuction with a monitor circuit module, +5V power supply and RS-232 terminal. This note includes a description of the facilities available from the software, a circuit diagram of the module and a listing of the monitor code.

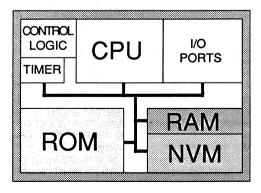

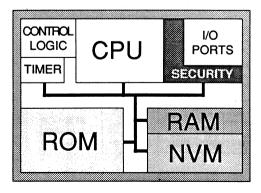

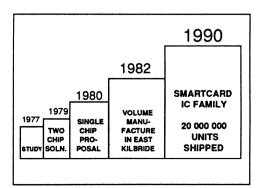

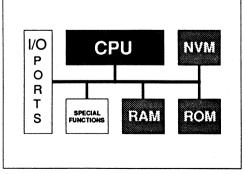

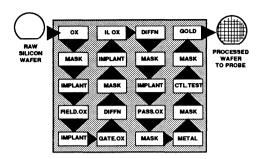

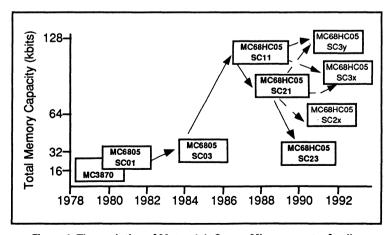

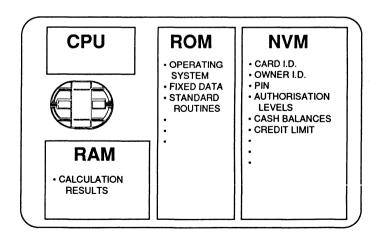

#### EB400 Secure Single Chip Microcomputer Manufacture

Security is the fundamental requirement in designing and manufacturing Smart Card MCUs. This Bulletin summarises the purpose and history of Smart Cards, and explains some of the problems of testing devices after manufacture without prejudicing security. The manufacturing process is necessarily different to that of 'normal' MCUs.

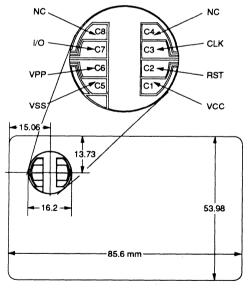

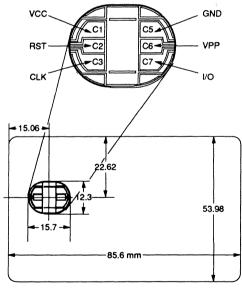

#### EB401 SCAM Modules for Smart Cards

Motorola's SCAM range of assembly modules consists of the Smart Card product family packaged for insertion in ISO standard plastic cards. This Bulletin lists the planned devices and shows the IS7816/2 contact dimensions, locations and connections. All devices conform to all relevant ISO standards.

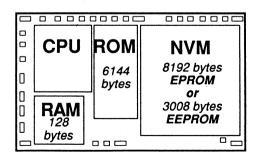

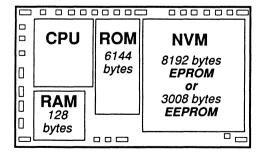

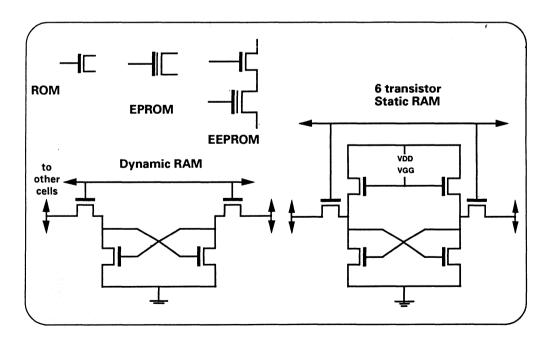

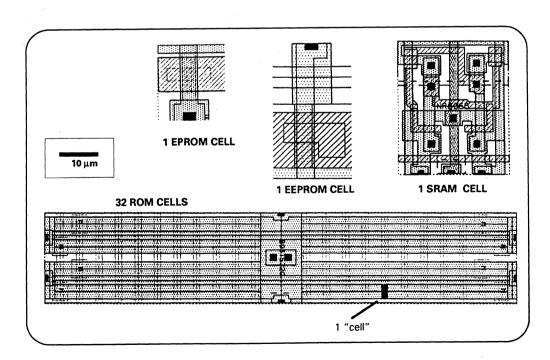

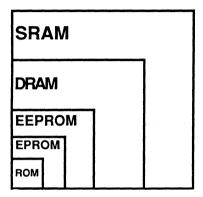

### EB404 "Memories Are Made of This" ... a Look at Memory Considerations for Smart Card Applications

A Smart Card application typically uses many millions of units per year, so unit cost is crucial to its success. This paper discusses some of the issues concerning memory size and type – and their effect on the specification and cost of secure microcomputers – with particular reference to physical size. (11pp)

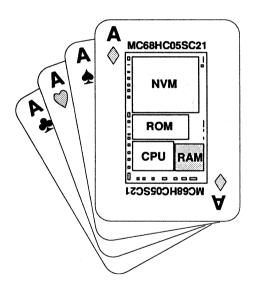

#### EB405 Smart Cards: How to Deal Yourself a Winning Hand

An overview of the current Smart Card market and the various types of product on offer. It looks at ways of determining what features must be provided by a suc-

cessful Smart Card implementation in a given application. Because of the high production volumes, it is essential to choose the optimum product, and to ask the right questions at the start.

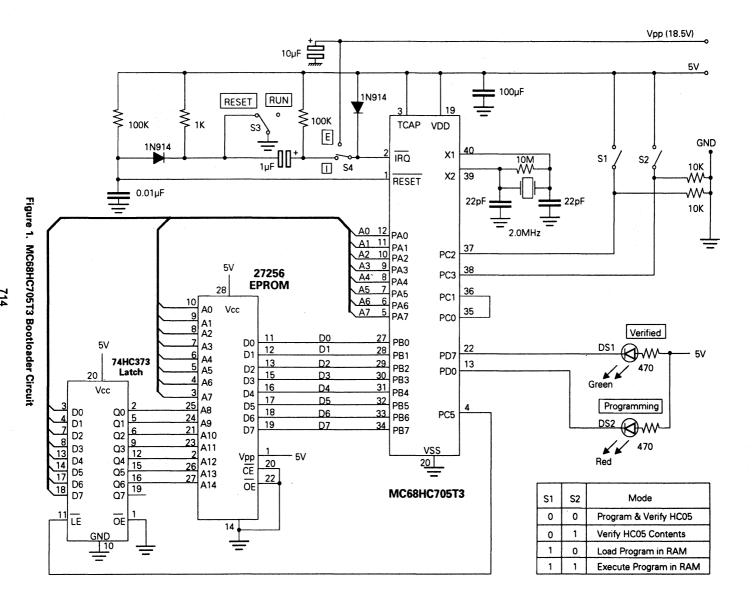

#### EB408 MC68HC705T3 Bootloader

This bootloader for the MC68HC705T3 has four switch-selected modes of operation. In addition to programming and verifying the internal EPROM from an external EPROM, it is also possible to load and execute a program in RAM locations \$0100-\$01FF. A handshake facility is included to allow the external EPROM to be replaced by an intelligent data source and to provide a limited debug capability. Includes circuit diagram and software listing.

# **Applications Documents**

#### **AN427**

## MC68HC11 EEPROM Error Correction Algorithms in C

By Richard Soja Motorola Ltd East Kilbride Glasgow

#### INTRODUCTION

This application note describes a technique for correcting one bit errors, and detecting two bit errors, in a block of data ranging from 1 to 11 bits in length. The technique applied is a modified version of a Hamming code, and has been implemented entirely in C. Additional functions have been provided to program and read the EEPROM on an MC68HC11 microcontroller unit using the error encoding and decoding algorithms.

#### **ENCODING AND DECODING ALGORITHMS**

Some texts [1], [2] describe the use of simultaneous equations to calculate check bits in Hamming distance-3 error correcting codes. These codes are so named because there are at least 3 bit differences between each valid code in the set of available codes. The codes are relatively easy to generate and can be used to correct one bit errors. However, their main drawback is that if two bit errors occur, then the correction will be made erroneously. This is because the condition of two bit errors corresponds exactly with a one bit error from another valid code.

The technique described here is based on an algorithmic strategy which produces Hamming distance-4 codes over the range of 1 to 11 data bits. This type of code is capable of correcting single bit errors and detecting 2 bit errors.

Alternatively, if the errors are only to be detected, without correction, then up to 3 bit errors can be detected. The reason for this is that the condition of a 3 bit error in one code corresponds to a one bit error from an adjacent valid code. The implication of this is that, if the algorithms are used to correct errors, then a 3 bit error will be corrected erroneously, and flagged as a 1 bit error.

The C program is divided into 3 modules, plus one header file:

#### 1. FECOR1.C

This is the main program segment, and serves only to illustrate the method of calling and checking the algorithms.

#### 2. HAMMING.C

This module contains the functions which encode and decode the data

#### 3. EEPROG.C

This module contains the EEPROM programming functions tailored for an MC68HC11 MCU.

#### 4. HC11REG.H

This is the header file which contains the MC68HC11 I/O register names, defined as a C structure.

#### IMPLEMENTATION OF ERROR CORRECTION STRATEGY

The basic principle of decoding the error correcting codes is to use a Parity check matrix, H, to generate a syndrome word which identifies the error. The H matrix can be generated as follows:

- Identify how many data bits are needed. For example: 8

data bits

- Use the standard equation to derive the number of check bits required: If k is the number of check bits, and m the number of data bits, then for the Hamming bound to be satisfied:

$2^k \ge m + k + 1$

A simple way to understand why this equation holds true is as follows: If one can generate a check code which is able to identify where a single error occurs in a bit stream, then the check code must have at least the same number of unique combinations as there are bits in the bit stream, plus 1 extra combination to indicate that no error has occurred. e.g. if the total number of data plus check bits were 7, then the check code must consist of 3 bits, to cover the range 1 to 7 plus one extra (0) to indicate no error at all.

In this example, if m=8 then, by rearranging the above equation:

$$2^{k} - k - 1 >= 8$$

One way to solve for k is to just select values of k starting at say, 1 and evaluating until the bound is reached. This method is implemented algorithmically in function InitEncode() in module HAMMING.C

For m=8, the solution is k=4. Note that this value exceeds the Hamming bound, which means that additional data bits can be added to the bit stream, thus increasing the efficiency of the code. In fact, the maximum number of data bits is 11 in this case.

A Parity matrix, H is created from a 'horizontally orientated' binary table. The number of columns (b1 to b12) in the matrix correspond to the total number of data and check bits, and the number of rows (r1 to r4) to the number of check bits.

| i.e. | b1 | b2 | b3 | b4 | b5 | <b>b6</b> | ь7 | <b>b8</b> | b9 | b10 | b11 | b12 |

|------|----|----|----|----|----|-----------|----|-----------|----|-----|-----|-----|

| r1   | 1  | 0  | 1  | 0  | 1  | 0         | 1  | 0         | 1  | 0   | 1   | 0   |

| r2   | 0  | 1  | 1  | 0  | 0  | 1         | 1  | 0         | 0  | 1   | 1   | 0   |

| r3   | 0  | 0  | 0  | 1  | 1  | 1         | 1  | 0         | 0  | 0   | 0   | 1   |

| r4   | 0  | 0  | 0  | 0  | 0  | 0         | 0  | 1         | 1  | 1   | 1   | 1   |

Because the H matrix in this form, is simply a truncated 4 bit binary table, it can easily be generated algorithmically.

The position of all the check bits (C1 to C4) within the encoded word is the position of the single 1s in the columns of H. The remaining bits correspond to the data bits (D1 to D8).

5. Each check bit is generated by taking each row of H in turn, and modulo-2 adding all bits with a 1 in them except the check bit positions.

i.e. C1=D1+D2+D4+D5+D7 C2=D1+D3+D4+D6+D7 C3=D2+D3+D4+D8 C4=D5+D6+D7+D8

6. The syndrome, s, is the binary weighted value of all check bits

i.e.

$$s=1*C1+2*C2+4*C3+8*C4$$

7. The error position (i.e. column) is determined by the value of the syndrome word, provided it is not zero. A zero syndrome means no error has occurred. Note that this error correction technique can correct errors in either data or check bits - which is not necessarily the case with certain other error correction strategies.

The advantage of this method, where the check bits are interspersed in a binary manner throughout the code word, is that the error position can be calculated algorithmically.

An important point to note is that the parity check matrix described above generates Hamming distance-3 codes, which means that 2 errors will cause erroneous correction. This can be fixed by adding an extra parity check bit, C5, which is the modulo-2 addition of all data and check bits together.

i.e.C5=C1+C2+D1+C3+D2+D3+D4+C4+D5+D6+D7+D8

The code word then becomes:

C1 C2 D1 C3 D2 D3 D4 C4 D5 D6 D7 D8 C5

To determine if an uncorrectable error has occurred (i.e. 2 errors) in the received word, the extra parity bit is tested. If the syndrome is non-zero and the parity bit is wrong, then a correctable error has occurred. If the syndrome is non-zero and the parity bit is correct, then an uncorrectable error has occurred.

#### **EFFICIENCY**

The following table lists the relative efficiencies of this algorithm, against data size.

| Data bits | Encoded bits | Efficiency % |

|-----------|--------------|--------------|

| -1        | 4            | 25           |

| 2         | 6            | 33           |

| 3         | 7            | 43           |

| 4         | 8            | 50           |

| 5         | 10           | 50           |

| 6         | 11           | 55           |

| 7         | 12           | 58           |

| 8         | 13           | 62           |

| 9.        | 14           | 64           |

| 10        | 15           | 67           |

| 11        | 16           | 69           |

The implementation of the above techniques are given in the module HAMMING.C.

In order to maintain orthogonality in the EEPROM algorithms, the encoded data used by the functions in module EEPROG.C are forced to either 1 byte or 2 byte (word) sizes. This also eliminates the complexities of packing and unpacking data in partially filled bytes.

#### CONCLUSIONS

In this application note, the encoding algorithm's generator matrix is the same as the parity check matrix.

The C functions <read> and <write> in the module HAMMING.C return a status value - 0, 1 or 2 - which indicates whether the data has no errors, 1 corrected error, or 2 erroneously corrected errors. This means that if the status value is 0 or 1, then the data can be assumed good. If the status value is 2, then the data will be bad.

Alternatively the functions can be used for error detection only, without correction. In this case, a status value of 1 corresponds to either 1 or 3 bit errors, while a status value of 2 indicates that 2 bit errors have occurred.

By using the C functions listed in this application note, the encoded data size can easily be changed dynamically. To do this, the function <InitEncode> must be called with

the required new data size. The global variables used by all the encoding, decoding and EEPROM programming and reading functions are automatically updated. This allows the encoding and error correction process to be virtually transparent to the user. In addition, the functions <write> and <read> will automatically increment the address pointer by the correct encoded data size set up by <InitEncode>. This simplifies the structure of loops to program and read back data. Example code is provided in module EECOR1.C.

The encoding and decoding algorithms listed here may be applied to other forms of data, such as that used in serial communications, or for parallel data transfers.

By incorporating the error correction or detection-only schemes described in this application note, the integrity of data storage and transfer can be greatly improved. The impact on EEPROM usage is to increase its effective reliability and extend its useful life beyond the manufacturers' guaranteed specifications.

#### REFERENCES

- Carlson, 'Communication Systems', Chapter 9, McGraw-Hill.

- [2] Harman, 'Principles of the Statistical Theory of Communication', Chapter 5, McGraw-Hill

#### **MODULE EECOR1.C**

Tests EEPROM error detection using a modified hamming encoding scheme.

```

typedef unsigned char byte;

typedef unsigned int word;

/* Global variables used by main() */

byte *ee addr, *start addr, *end addr, i, Error;

word data;

/************************

/* External global variables */

extern byte CodeSize;

/* = number of bits in encoded data */

/* External Functions */

extern byte read(word *data,byte **addr);

extern byte write(word data,byte **addr);

/* Function returns error status */

/* "

/* Table of Status returned by read and write functions

Returned Status

Condition

No errors detected or corrected.

Ω

One error detected and corrected.

1

Two errors detected, but correction is erroneous.

2

Notes:

1/ When the returned value is 2, the function <read> will returned a bad value in variable

<data> due to the inability to correctly correct two errors. <read> also automatically increments

the address pointer passed to it, to the next memory space. The incremented value takes into

account the actual size of the encoded data. i.e. either 1 or 2 byte increment.

2/ Function <write> also performs a read to update and return an error status. This gives an

immediate indication of whether the write was successful. <write> also automatically increments

the address pointer passed to it, to the next free memory space. The incremented value takes into

account the actual size of the encoded data. i.e. either 1 or 2 byte increment.

/******************************

int main()

CodeSize=InitEncode(11):

/* Get code size (less 1) needed

/* by 11 data bits

/* Initialise EEPROM start address

ee addr=(byte *)0xb600;

for (i=1; i \le 0x10; i++)

/* and 'erase' EEPROM

/* Function successful if Error<>2

Error=write(0x7ff, &ee addr);

ee addr=(byte *)0xb600;

/* Reset EEPROM address

Error=write(0x5aa, &ee addr);

/* Write 0x5aa & increment ee addr

/* Write 0x255 at next available address

Error=write(0x255,&ee addr);

CodeSize=InitEncode(4);

/* Change number of data bits to 4

start_addr=ee_addr;

/* Save start address for this data

for(i=1;i<0x10;i<<=1)

/* Program 'walking 1s'

Error=write(i, &ee addr);

/* Save end address

end addr=ee addr;

ee addr=start addr;

```

/\* Read back all the 4 bit data

/\* <data> good if Error=0 or 1

while (ee\_addr<end addr)

} /\* main \*/

Error=read(&data, &ee\_addr);

#### **MODULE HAMMING.C**

/\*Modules to Generate hamming codes of distance 4, for data sizes in the range 1 bit to 11 bits. The upper bound is limited by the encoded word type bit range (16 bits).

Corrects 1 bit error in any position (check or data), and detects 2 bit errors in any position.

After execution of the Cecode> function, the global variable <ErrFlag> is updated to indicate level of error correction.

```

ErrFlag

Condition

0

No errors detected or corrected.

One error detected and corrected.

1

Two errors detected, but correction is erroneous.

Note that when ErrFlag is 2, function < Decode> will return a bad value, due to its inability to

correctly correct two errors.

#define TRUE 1

#define FALSE 0

typedef unsigned char byte;

typedef unsigned int word;

byte DataSize, CodeSize, EncodedWord, ErrFlag;

/* Function prototypes */

byte OddParity(word Code);

word Power2 (byte e);

byte InitEncode (byte DataLength);

word MakeCheck (word Data);

word Encode (word Data);

word Decode (word Code);

byte OddParity(Code)

word Code;

Returns TRUE if Code is odd parity, otherwise returns FALSE

byte p;

p=TRUE;

while (Code!=0)

if (Code & 1) p=!p;

Code>>=1;

return(p);

word Power2 (e)

byte e;

Returns 2^e

word P2;

signed char i;

P2=1;

if ((signed char)(e)<0)

return(0);

```

else

```

for (i=1;i \le (signed char)(e);i++)

P2<<=1;

return (P2);

}

}

byte InitEncode (DataLength)

byte DataLength;

Returns the minimum number of total bits needed to provide

Hamming distance 3 codes from a data size defined by passed

variable <DataLength>. This value also updates global variable <DataSize>.

i.e. finds the minimum solution of (k+m) for the inequality:

2^k \ge k + m + 1

In addition, updates global variable < EncodedSize > to reflect number of bytes

per encoded data. < EncodedSize> will be either 0 or 1.

byte CheckLength.i:

DataSize=DataLength; /* DataSize used by other functions in this module */

CheckLength=1;

while ((Power2 (CheckLength)-CheckLength-1) < DataLength)

CheckLength++;

i=CheckLength+DataLength;

EncodedWord=i / 8;

/* =0 if byte sized, =1 if word sized

return (CheckLength+DataLength);

word MakeCheck (Data)

word Data:

Returns a check word for Data, based on global variables <DataSize>

and <CheckSize>. The H parity matrix is generated by a simple for loop.

byte i, H, CheckSize, CheckValue, Check, CheckMask;

word DataMask:

Check=0:

CheckMask=1;

CheckSize=CodeSize-DataSize;

for (i=1;i<=CheckSize;i++)

CheckValue=FALSE:

DataMask=1;

for (H=1; H<=CodeSize; H++)

/* Column with single bit set

if ((0x8000 % H)!=0)

{

if ((H & CheckMask)!=0)

CheckValue^=((DataMask & Data)!=0);

DataMask<<=1;

if (CheckValue) Check | = CheckMask;

CheckMask<<=1;

return (Check);

```

```

word Encode (Data)

word Data:

Returns an encoded word, consisting of the check bits

concatenated on to the most significant bit of <Data>.

A single odd parity bit is concatenated on to the Encoded word to

increase the hamming bound from 3 to 4, and provide 2 bit error

detection as well as 1 bit correction.

concatenating positions.

word Code:

Code=Data | (MakeCheck(Data) << DataSize);

if (OddParity(Code))

Code | = Power2 (CodeSize);

return (Code);

word Decode (Code)

word Code:

Returns the error corrected data word, decoded from <Code>.

Uses global variable  DataSize> to determine position of the

check bits in <Code>.

Updates global variable <ErrFlag> to indicate error status i.e.:

ErrFlag

Status

Ω

No errors found

1

Single error corrected

Double error - invalid correction

2

*/

word ParityBit, Data, Check, ErrorCheck, Syndrome, DataMask;

byte DataPos, CheckSize, CheckPos, H, DataBit;

ErrFlag=0;

ParityBit=Code & Power2 (CodeSize);

/* Extract parity bit.

*/

DataMask=Power2 (DataSize) -1;

/* Make data mask */

Data=Code & DataMask:

/* Extract data bits.

CheckSize=CodeSize-DataSize;

/* Extract check bits,

Check=(Code>>DataSize) & (Power2(CheckSize)-1); /* ignoring parity.

ErrorCheck=MakeCheck (Data);

Syndrome=Check ^ ErrorCheck;

/* Get bit position of error.

if (Syndrome>0) ErrFlag++;

/* Increment flag if error exists.

H=0;

DataPos=0;

CheckPos=DataSize.

DataBit=TRUE;

while ((H!=Syndrome) & (DataPos<DataSize))

/* Identify which data or

*/

/* code bit is in error.

*/

H++:

DataBit=(0x8000 % H);

if (DataBit) DataPos++;

CheckPos++;

if (DataBit) Code^=Power2(DataPos-1);

Code^=Power2 (CheckPos-1);

Code|=ParityBit;

if (OddParity(Code)) ErrFlag++;

return (Code & DataMask);

```

#### **MODULE EEPROG.C**

```

/*Module to program MC68HC11 EEPROM.

Contains <read> and <write> functions to encode and decode data

formatted by modified hamming scheme.

#include <HC11REG.H>

#define regbase (*(struct HC11IO *) 0x1000)

#define eras 0x16

#define writ 0x02

typedef unsigned char byte;

typedef unsigned int word;

union twobytes

word w:

byte b[2];

/* Word stored as MSB, LSB

*/

) udata;

extern byte EncodedWord, ErrFlag;

/* Function prototypes */

extern word Encode (word Data):

extern word Decode (word Code);

void delay (word count);

void eeprog(byte val,byte byt,byte *addr,word count);

void program(byte byt,byte *addr);

byte read(word *data,byte **addr);

byte write (word data, byte **addr);

void delay (count)

word count:

regbase.TOC1=regbase.TCNT+count;

/* Set timeout period on OC1 and

regbase.TFLG1=0x80;

/* clear any pending OC1 flag.

/* Wait for timeout flag.

do; while ((regbase. TFLG1 & 0x80) == 0);

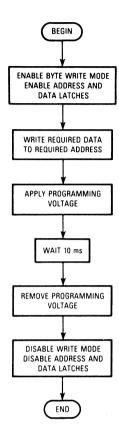

void eeprog (val, byt, addr, count)

byte val;

/* val determines Erase or Write operation

*/

byte byt;

/* byt is byte to be programmed

/* addr is address of encoded byte in EEPROM

byte *addr;

word count;

/* count is number of E clock delays

regbase.PPROG=val;

/* Enable address/data latches

*addr=bvt;

/* Write value to required eeprom location

++regbase.PPROG;

/* Enable voltage pump

*/

/* Allow for software overhead

*/

if (count<100) count=100;

delay (count);

/* wait a bit

*/

-regbase.PPROG;

/* Disable pump, then addr/data latches

*/

regbase.PPROG=0;

```

```

void program(byt,addr)

byte byt;

byte *addr;

{

eeprog(eras, byt, addr, 20000);

/* First erase byte

eeprog(writ, byt, addr, 20000);

/* Then write value

byte read(data,addr)

word *data:

byte **addr;

udata.b[1] = * (*addr) ++;

/* Read back data LSB first, and inc address */

if (EncodedWord)

/* If word stored then read MSB

udata.b[0]=*(*addr)++;

/* Inc address for next call to this function */

/* else only byte stored, so clear MSB

udata.b[0]=0;

*data=Decode (udata.w);

/* Decode data, which updates <ErrFlag>,

return (ErrFlag);

/* and return ErrFlag

*/

byte write(data,addr)

word data:

byte **addr;

byte *oldaddr;

'udata.w=Encode (data);

/* Encode data.

oldaddr=*addr;

/* Save initial address for verification.

program(udata.b[1], (*addr)++);

/* Program LSB first to allow for either

if (EncodedWord)

/* 1 or 2 byte encoded data

/* MSB of word sized data, & inc address

program(udata.b[0], (*addr)++);

return (read (&udata.w, &oldaddr));

/* Return <ErrFlag> to calling segment

```

#### HC11REG.H

```

HC11 structure - I/O registers for MC68HC11 */

struct HC11IO {

unsigned char

PORTA:

/* Port A - 3 input only, 5 output only

unsigned char

Reserved;

PIOC:

unsigned char

/* Parallel I/O control

unsigned char

PORTC:

/* Port C */

unsigned char

PORTB;

/* Port B - Output only

unsigned char

PORTCL:

/* Alternate port C latch

unsigned char

Reserved1;

unsigned char

DDRC:

/* Data direction for port C

unsigned char

PORTD:

/* Port D

/* Data direction for port D

unsigned char

DDRD;

unsigned char

PORTE:

/* Port E

Timer Section */

CFORC;

/* Compare force

unsigned char

unsigned char

OC1M;

/* Ocl mask

unsigned char

OCID;

/* Ocl data

int

TCNT;

/* Timer counter

int

TIC1:

/* Input capture 1

/* Input capture 2

int

TIC2;

TIC3;

/* Input capture 3

int

TOC1;

/* Output compare 1

int

TOC2;

/* Output compare 2

int

/* Output compare 3

int

TOC3:

int

TOC4;

/* Output compare 4

TOC5;

/* Output compare 5

int

unsigned char

TCTL1;

/* Timer control register 1

TCTL2;

/* Timer control register 2

unsigned char

unsigned char

/* Main timer interrupt mask 1

TMSK1;

unsigned char

TFLG1;

/* Main timer interrupt flag 1

unsigned char

TMSK2:

/* Main timer interrupt mask 2

unsigned char

TFLG2;

/* Main timer interrupt flag 2

Pulse Accumulator Timer Control */

unsigned char

PACTL:

/* Pulse Acc control

unsigned char

PACNT;

/* Pulse Acc count

```

```

/*

SPI registers */

unsigned char

SPCR:

/* SPI control register

unsigned char

SPSR:

/* SPI status register

unsigned char

SPDR:

/* SPI data

register

SCI registers */

unsigned char

BAUD:

/* SCI baud rate control

unsigned char

SCCR1:

/* SCI control register 1

/* SCI control register 2

unsigned char

SCCR2:

unsigned char

SCSR;

/* SCI status register

/* SCI data

unsigned char

SCDR;

register

A to D registers */

unsigned char

ADCTL;

/* AD control register

unsigned char ADR[4];

/* Array of AD result registers

Define each result register */

#define

ADR[0]

adr1

#define

adr2

ADR[1]

#define

adr3

ADR[2]

#define

adr4

ADR[3]

unsigned char Rsrv[4];

/* Reserved for A to D expansion

System Configuration */

unsigned char

OPTION:

/* System configuration options

/* Arm/Reset COP timer circuitry

unsigned char

COPRST:

unsigned char

/* EEPROM programming control reg

PPROG:

unsigned char

HPRIO;

/* Highest priority i-bit int & misc

/* RAM - I/O mapping register

unsigned char

INIT;

/* Factory TEST control register

/* EEPROM cell - COP,ROM,& EEPROM en

unsigned char

TEST1:

unsigned char

CONFIG;

};

/*

End of structure HC11 */

```

## Temperature measurement and display using the MC68HC05B4 and the MC14489

By Jeff Wright, Motorola Ltd., East Kilbride

#### INTRODUCTION

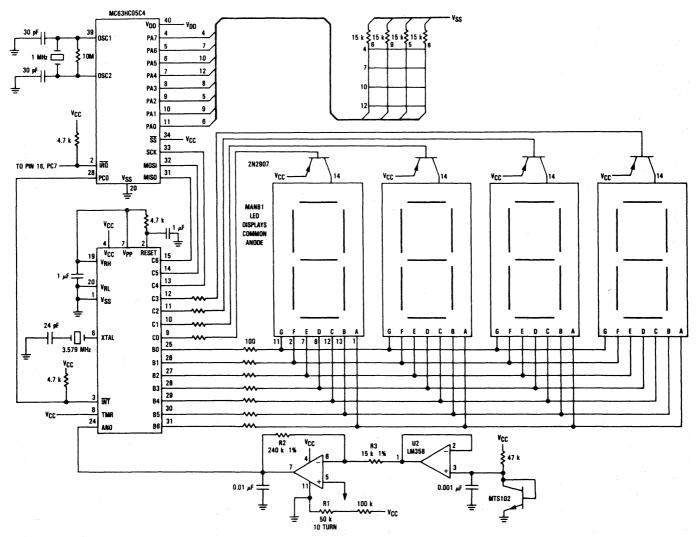

This application note is intended to show the basic building blocks of a temperature control system based on the MC68HC05Bx family of MCUs. Software routines in the application include look-up table interpolation, binary to BCD conversion, DegC to DegF conversion and the basis of a real time counter/clock. For temperature display the Multi-character LED display driver MC14489 is used, driven from the B4's SCI, resulting in simple hardware with a low component count. The temperature sensing element used here is a thermistor to allow easy interfacing to the A/D converter of the HC05B4, but the software principles shown would be the same for many other types of sensors. A software listing is included at the end of this application note.

#### TEMPERATURE MEASUREMENT

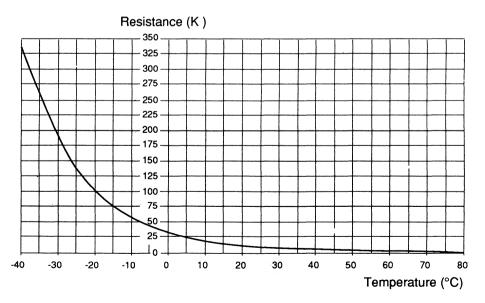

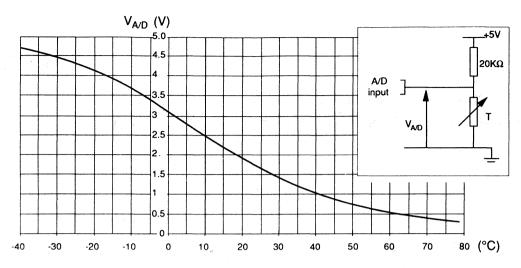

A pre-calibrated thermistor was chosen as the temperature sensing element. Its characteristic curve over the temperature range of -40 to 80 °C is shown in Figure 1. To get the best accuracy from the HC05B4's on-board A/D, the input signal shbuld be scaled to use as much of the available VRH-VRL range as possible. Here VRH is connected to Vdd and VRL is tied to Vss. In this case, using the thermistor as potential divider with a 20k $\Omega$  resistor results in a signal range of approximately 0.3V to 4.7V over the -40 to 80 °C temperature range. The voltage across the thermistor (input to the A/D), plotted against temperature, is shown in Figure 2.

Figure 1. Thermistor resistance vs Temperature

Figure 2. A/D input voltage vs Temperature (inset: circuit used)

As can be seen from Figure 2, the response is non-linear and so a look-up table approach is the simplest way of obtaining the required accuracy. The thermistor characteristics are stored as a series of points in a table in ROM and a linear interpolation between adjacent points is used to obtain the temperature that corresponds to a given A/D reading. The number of points that must be stored depends on how non-linear the response is and the required accuracy of the result. In this case 16 points were chosen; in order to keep the software simple (and

therefore fast), they are spread at intervals of 16 through the A/D result range of 0-255. For each point (16, 32, 48 etc.), the voltage on the A/D input was calculated and the corresponding temperature was obtained from the graph of Figure 2. These points were then used to form the look-up table shown in Figure 3, resulting in a temperature range of -40 to 79 °C. Figure 4 shows the reconstructed response of the thermistor obtained by linear interpolation of the points in the look-up table.

|            |             |           | T                  |

|------------|-------------|-----------|--------------------|

| A/D RESULT | A/D (volts) | TEMP (°C) | TEMP (°C 2s Compl) |

| 0          | 0           | -         | -                  |

| 16         | 0.31        | 79        | 4F                 |

| 32         | 0.63        | 56        | 38                 |

| 48         | 0.94        | 43        | 2B                 |

| 64         | 1.26        | 34        | 22                 |

| 80         | 1.57        | 27        | 1B                 |

| 96         | 1.88        | 21        | 15                 |

| 112        | 2.20        | 15        | 0F                 |

| 128        | 2.51        | 10        | 0A                 |

| 144        | 2.82        | 5         | 05                 |

| 160        | 3.14        | -1        | FF .               |

| 176        | 3.45        | -6        | FA                 |

| 192        | 3.77        | -11       | F5                 |

| 208        | 4.08        | -18       | EE                 |

| 224        | 4.39        | -26       | E6                 |

| 240        | 4.71        | -40       | D8                 |

| 255        | 5.0         | •         | -                  |

Figure 3. Interpolated A/D input voltage vs Temperature

Figure 4. Interpolated A/D input voltage vs Temperature

The temperature reading is updated every second; the software to accomplish this is relatively simple:

The timer is set to overflow every 125 mS with a 4.1934 MHz crystal. The timer overflow interrupt routine updates the real time counters TICKS, SECS, MINS & HRS and sets the flag bit SEC every time a second has elapsed.

The main program loop is executed every second (via the SEC flag bit) and after checking the metric/imperial selector switch the temperature is measured by the subroutine ADCONV. This routine starts by reading the thermistor selector switch and setting up the A/D control register accordingly. An A/D conversion is then carried out four times on the selected channel and the results accumulated in the accumulator and the temporary register TEMP. This result is then divided by 4 by rotating, to obtain the average A/D result. The averaging technique is employed to try and reduce the effect of noise on the A/D input. The number of conversions to average is determined by time constraints and the noise levels in the surrounding environment. The upper nibble of the result is then used to access the look-up table to obtain the 'base' temperature value. If the temperature limit is exceeded then the TLIMIT flag is set before exiting from the routine.

Temperature table entries are stored in 2's complement form so that the interpolation between positive and negative values will work successfully. The interpolation is carried out by obtaining the difference between the base value and the next in the table, multiplying this by the lower nibble of the A/D result and then dividing by 16. This result is then subtracted from the base value to obtain the real temperature in 2's complement °C which is stored in the register NEWTMP before exiting from the routine. The difference information is subtracted from the base value rather than added because the thermistor has a negative temperature co-efficient (NTC) so that an increase in the A/D result corresponds to a drop in temperature.

If the imperial mode is selected (°F) then the next stage before updating the display is to convert from °C to °F and this is carried out in the subroutine CTOF.

Converting from °C to °F is accomplished by multiplying by 1.8 and adding 32. First the sign of the temperature in °C is stored via the flag bit NEGNUM, then the maximum °F limit (53 °C) is checked before the magnitude is multiplied by 1.8 (multiply by 115 and divide by 64). Again, use is made of rotating to do the dividing, in order to increase execution speed. The sign of the result is then restored and 32 added to obtain the temperature in 2's complement °F.

#### TEMPERATURE DISPLAY

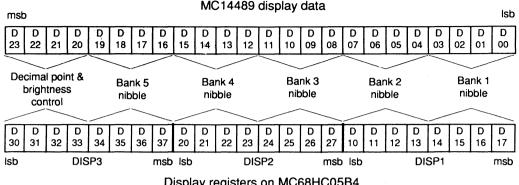

An MC14489 multi-character display driver was chosen for this purpose as it can be easily interfaced to a wide range of Motorola MCUs, requires almost no external components and has a character set that includes the degree symbol (°). The MC14489 can also be cascaded if the application was expanded to require a larger display. The MC14489 would normally be driven from an SPI on the MCU but here, since the the 68HC05B family does not have an SPI, use is made of the SCI clock output feature that is available on this family.

Before the temperature can be written to the display driver it has to be converted into the correct data format.

The first stage of this is to convert from 2's complement binary to BCD. This is carried out in the routine CONBCD which is called from SETDISP. The sign of the temperature is stored in the flag bit NEGNUM before SETDISP is called: then, after first checking if the TLIMIT flag is set, the temperature is converted to BCD in DEC0-2 by CONBCD. This is accomplished by rotating left the binary number followed immediately by a rotate left of the BCD result; this has the effect of multiplying the current BCD result by 2 and adding in the new binary bit at the same time. After each rotate the BCD registers are checked and adjusted for overflow (>\$09) before the bit counter contained in the index register is decremented. This process of rotate then adjust is continued until all the binary bits have been used; the BCD result will then be resident in the registers DEC0, 1 & 2.

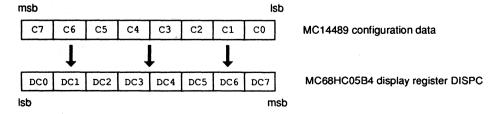

The rest of the routine SETDISP is concerned with setting up the display registers DISP1, 2, 3 and the display control register DISPC. The MC14489 data format is msb first whereas the 68HC05B4 SCI transmits lsb first; this means that the bit order of the data stream has to be stored in reverse in the display registers. This can be confusing when trying to work out the codes that have to be stored in the B4 to generate a specific character.

Figures 5a and 5b show the 14489 data format and the corresponding bit positions in the B4 registers DISP1, 2, 3 & C. The sign of the temperature is restored and the numeric display registers are configured to display '-' if the temperature limit has been exceeded before exiting from the SETDISP routine.

The main program loop then calls the subroutine DISPL which actually transmits the contents of the display registers to the MC14489 via the SCI. The MC14489 contains special Bit Grabber circuitry that allows either the internal display registers or the configuration register to be updated without address or steering bits so that updating the display involves a simple transmission of either 3 bytes for the display registers or 1 byte for the configuration register. Even for cascaded 14489s there is no need for address bits – see the MC14489 data sheet for more details.

The MC14489 can be clocked at up to 4 MHz at 5 volts so here the maximum transmit baud rate of the SCI is used – 131.072 KHz with a 4.19304 MHz crystal. The transmission of the display data only takes place if there has been a change in the data since the last time. If there has been a change, the 3 data registers are transmitted in turn starting with DISP3 and the OLD registers are updated ready for the change check next time round. After the last byte has gone, the SCI and 14489 are disabled before returning to the main loop.

The last subroutine called from the main program is the 14489 configuration update routine DISCON. This routine operates in a similar manner to DISPL, checking to see if there has been a change to the config. data before transmitting it.

This completes the operation of the program which now jumps back to the start of the main loop and waits for the SEC bit to be set again before repeating the temperature measurement and display sequence.

Figure 5a. MC14489 to MC68HC05B4 display register mapping

Display registers on MC68HC05B4

Figure 5b. MC14489 to MC68HC05B4 display register mapping

# **HARDWARE**

As already mentioned, the use of the MC14489 results in a very low component count for the application; the hardware schematic can be seen in Figure 6. The only I/O pins required are for reading the option switches and for controlling the enable of the MC14489. Pulldowns are required on the clock and data pins as these become high impedance when the SCI is disabled. The LED displays are common cathode; a single external resistor is all that is required to set the brightness level of the displays. In this case though, a light dependent resistor, R12 (ORP12), has been used to control the display brightness for a variety of background lighting conditions. The resistance of R12 decreases with increasing light and so R11 must be incorporated to ensure that the maximum source current spec, of the MC14489 is not exceeded in very bright lighting conditions. R13 ensures there is still enough drive current for the LEDs in dark conditions.

# APPLICATION AREAS

As mentioned in the introduction, this application note is designed only to show some fundamental building blocks of a temperature control system based on the 68HC05Bx family of MCUs. Where possible, the software has been written in a modular fashion, so that the routines can easily be transported to another application and the binary to BCD routine could be expanded to handle larger numbers. The large number of I/O,

PWMs and timer functions unused show that the 68HC05B family has plenty of functionality left to perform other control functions. For example, in process control, fluid flow or speed sensors could be connected to the timer input capture pins, pressure sensors to the other A/D pins, a keypad to the I/O lines and the other I/O & PWMs used to perform output control functions.

Figure 6. Hardware schematic

```

************

1

2

3

* %

* *

4

* %

8 *

68HC05B4 TEMPERATURE MEASUREMENT & DISPLAY

5

* %

<u>۾</u> *

6

* %

Jeff Wright, Motorola East Kilbride.

7

Last Updated 22/02/90

* &

9

*% This software was written by Motorola for demonstration

10

*% purposes only. Motorola does not assume any liability arising

out of the application or use of this software and does not

11

12

* %

2 *

quarantee its functionality

13

* %

14

15

16

17

18

I/O and INTERNAL registers definition

19

20

21

I/O registers

22

23 00000000

EQU

$00

PORTA

port A.

24 00000001

$01

PORTB

EOU

port B.

25 00000002

port C.

PORTC

EOU

$02

26 00000003

PORTD

EOU

$03

port D.

27 00000004

DDRA

EOU

504

port A DDR.

28 00000005

$05

port B DDR.

DDRB

EQU

29 00000006

DDRC

EOU

$06

port C DDR.

30

31

32

A/D registers

33

34 00000008

ADDATA EQU

$08

A/D data register.

35 00000009

ADSTC' EQU

$09

A/D status and control register.

36 00000007

coco

EQU

7

Conversion complete flag.

37

38

39

40

41

SCI registers

42

43 0000000d

$0D

BAUD

EQU

SCI baud register.

44 0000000e

SCCR1

EQU

SCI control register 1.

45 0000000f

SCCR2

EQU

$0F

SCI control register 2.

46 00000010

SCSR

EOU

$10

SCI status register.

47 00000007

TDRE

EQU

7

48 00000006

TC

EQU

6

49 00000011

SCDAT

EQU

$11

SCI data register.

50

51

52

TIMER registers

53

54 00000012

TCR

EQU

$12

Timer control register.

55 00000005

TOIE

EQU

5

Timer overflow interrupt enable.

56 00000006

OCTE

EQU

Timer output compares interrupt enable.

57 00000007

ICIE

EOU

7

Timer input captures interrupt enable.

58

59 00000013

TSR

EOU

$13

Timer status register.

60 00000003

OCF2

EOU

3

Timer output compare 2 flag.

61 00000004

ICF2

EQU

4

Timer input capture 2 flag.

62 00000005

TOF

EQU

5

Timer overflow flag.

63 00000006

OCF1

Timer output compare 1 flag.

EOU

6

64 00000007

7

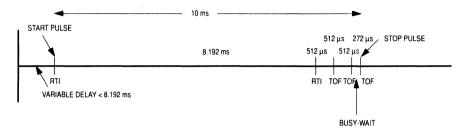

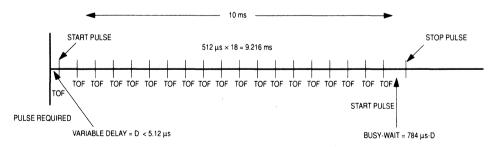

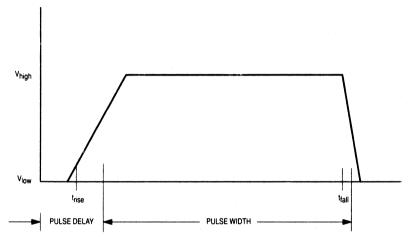

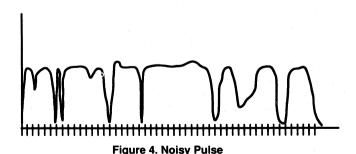

ICF1

EQU

Timer input capture 1 flag.

```

```

65

66 00000014

TIC1HI EQU

Timer input capture register 1 (16-bit).

$14

67 00000015

TIC1LO EQU

$15

68 00000016

TOC1HI EQU

$16

Timer output compare register 1 (16-bit).

69 00000016

TOC1LO EQU

$16

70 00000018

TIMHI

EOU

$18

Timer free running counter (16-bit).

71 00000019

TIMLO

EOU

519

72 0000001a

TIMAHI EOU

Timer alternate counter register (16-bit).

$1A

73 0000001b

TIMALO

EOU

$1B

74 0000001c

TIC2HI

Timer input capture register 2 (16-bit).

FOU

SIC

75 0000001d

TIC2LO

EOU

$1D

76 0000001e

TOC2HI

Timer output compare register 2 (16-bit).

EOU

SIE

77 0000001f

TOC2LO

EQU

$1F

78

79

80

81

MEMORY MAP DEFINITION

82

83

84 00000020

TEST

EQU

$20

TEST register

Start address of ROMO.

85 00000020

ROM0

EQU

$0020

86 00000050

RAM

EQU

$0050

Start address of RAM.

87 00000f00

UROM

EQU

$0F00

Start address of main user ROM.

88

89

90

91

***************** RAM ALLOCATION *****************

92

93

94

SECTION.S .RAM, ADDR=$50

95

96

97 00000050

TICKS

RMR

1

98 00000051

SECS

RMB

1

99 00000052

MTNS

RMR

1

100 00000053

HRS

RMR

1

101

102 00000054

FLAG

RMB

1

103 00000000

OVERFL

O

EOU

104 00000001

NEGNUM

EOU

1

105 00000002

TLIMIT

EOU

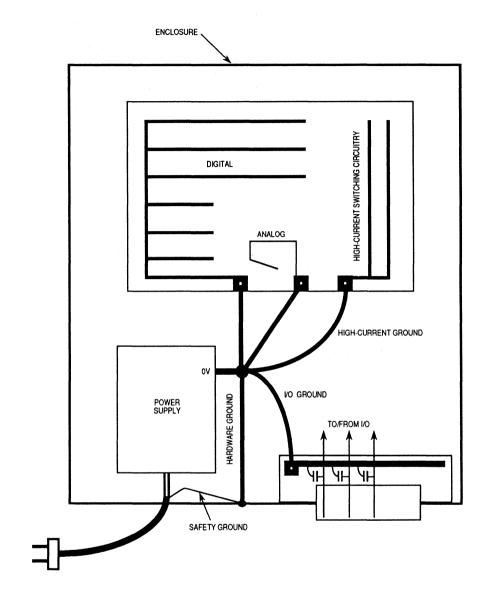

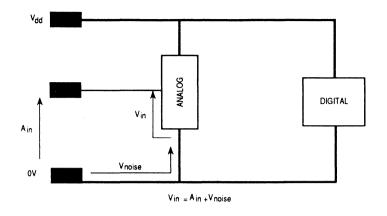

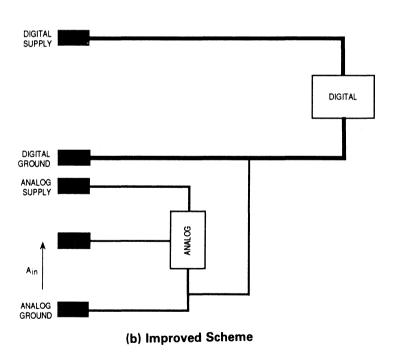

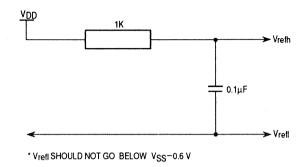

2

106 00000003

SEC

EOU

3

107

108 00000055

MODE

RMB

1

109 00000000

IMP

EOU

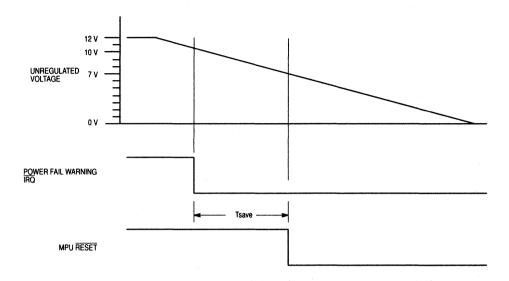

0

110

111 00000056

BIN0

RMB

1

112 00000057

DEC2

RMB

1

113 00000058

DEC1

RMB

1

114 00000059

DEC0

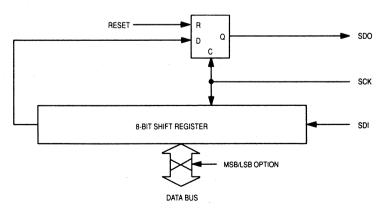

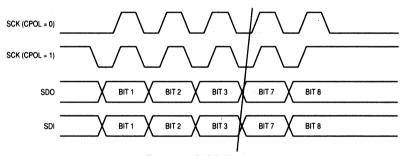

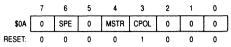

RMB

1

115

116 0000005a

NEWTMP

RMB

1

117 0000005ь

TEMP

RMB

1

118 0000005c

TEMP1

RMB

1

119 0000005d

TEMP2

RMB

1

120

121 0000005e

DISP1

RMB

1

122 0000005f

DISP2

RMB

1

123 00000060

DISP3

RMB

1

124 00000061

DISPC

RMB

1

125 00000062

OLDD1

RMB

1

126 00000063

OLDD2

RMB

1

```

```

127 00000064

OLDD3

RMB

128 00000065

OLDDC

RMB

1

129

130

131

SECTION .PAGEO, ADDR=$020

132

133 00000020 004f382b221b150f ADTAB

FCB

$00,$4F,$38,$2B,$22,$1B,$15,$0F

134 00000028 0a05fffaf5eee6d8

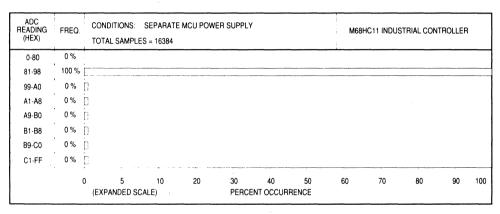

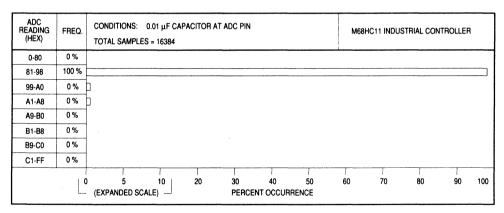

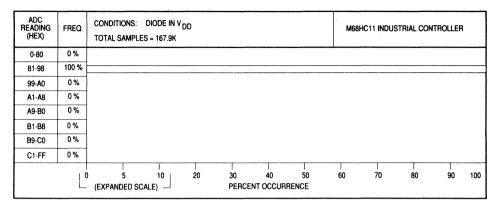

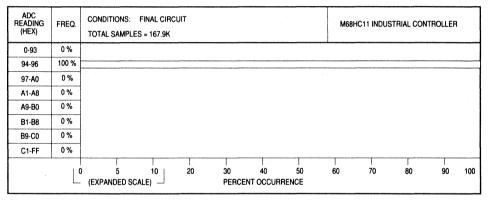

FCB