# AN-595 **Application Note**

eliminating the 25 watt output stage and

# 25-WATT AND 10-WATT VHF MARINE BAND TRANSMITTERS

Prepared by ion about John Hatchett is shown and to not blue and yet vehicle as they 25 of

Applications Engineering

Design, performance and construction information are provided in this report for two power amplifiers suitable for VHF marine band (156-162 MHz) applications. Rated power output levels are 25 watts and 10 watts. Methods of meeting the FCC low power output (one watt or less) requirement are discussed in detail. Both amplifiers can be tuned to cover 144-175 MHz and performance data is provided for this frequency range. when the amplifiers are operating at rated output powe

**MOTOROLA** Semiconductor Products Inc.

# 25-WATT AND 10-WATT VHF MARINE BAND TRANSMITTERS

### INTRODUCTION

This report gives design, performance and construction information for two 12.5 volt, FM transmitter power amplifiers designed for VHF marine band (156-162 MHz) applications. One of the amplifiers provides 25 watts of output power and the other 10 watts. Both have provisions for meeting the FCC requirement of being switchable to give one watt or less power output. Both designs have been subjected to open and short circuit load conditions at high line voltage and all load phase angles without damage to any transistor.

Components and construction techniques consistent with low cost, high volume production have been employed. The use of circuit designs and a printed circuit board layout which are common to both amplifiers minimizes the number of different components required and also makes it possible to extend the 10 watt amplifier to 25 watt capability by the addition of one more stage. The amplifiers are tunable from 144 to 175 MHz and

therefore are also useful for other VHF applications such as amateur two meter and land-mobile radio.

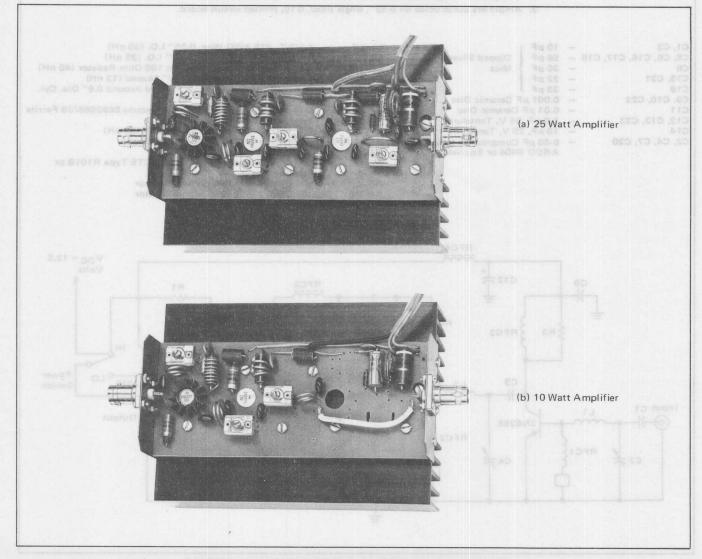

Performance information is given in Table 1 and also in the Transmitter Performance Section. A photograph of the amplifiers appears in Figure 1 and schematic diagrams in Figure 2.

## DEVICE CONSIDERATIONS

The three RF transistor types employed in the amplifier designs are part of the Motorola VHF series optimized for 12.5 volt FM operation. They are of balanced emitter construction and the 25 watt device is manufactured using the Motorola \*Isothermal technology process. The Isothermal design provides an additional measure of ruggedness to resist damage at high power levels over a wide range of thermal and VSWR excursions.

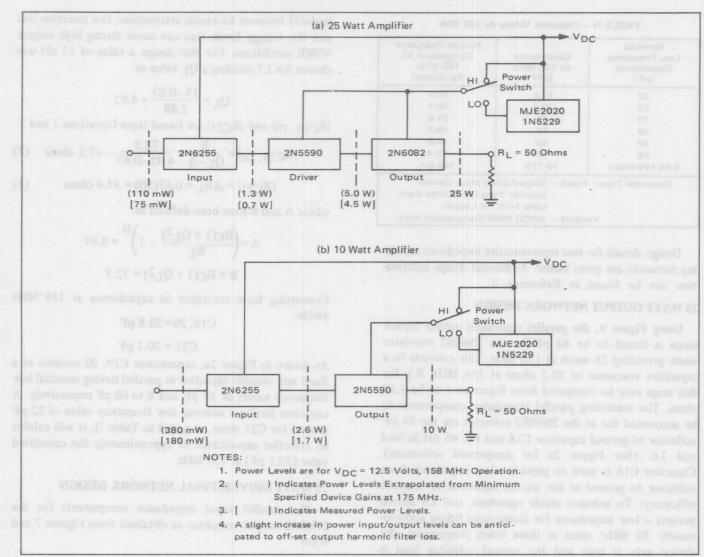

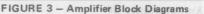

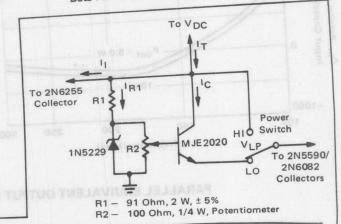

The power levels that each RF transistor must supply when the amplifiers are operating at rated output power at 158 MHz and 12.5 volts are given on the block diagrams of Figure 3. Both expected worst case power levels, as determined from the minimum specified device gains, and the power levels actually measured for constructed amplifiers have been included. A slight increase in these levels will be necessary to off-set any output harmonic filter loss. The expected effect of this additional loss (typically 0.3 to 0.5 dB) on the input power requirements can be obtained from Figure 13. The 10 watt amplifier shows the flexibility of achieving an optional, more economical, low power system from the 25 watt

design simply by eliminating the 25 watt output stage and matching the 2N5590 driver into 50 ohms. If a lower input power is required, higher gain devices are available for use in the 10 watt design. Two additional line-ups are shown below with expected worst case power levels for 158 MHz, 12.5 volt operation.

135mw - 2N6255 - 2N6081 - 10w 80 mw - MRF607 - 2N6081 - 10w

The 2N6081 transistor is also of \*Isothermal design and provides increased ruggedness as well as higher gain for the 10 watt system. For the 25 watt amplifier, the power required from the input stage will typically be less than one watt for 158 MHz operation. This makes the more economical 2N4427 device also a suitable candidate for this stage in 25 watt marine band applications. The design methods given in the following sections can also be applied to determine matching network component values for these alternate device line-ups.

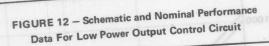

An MJE2020 transistor is used in conjunction with a 1N5229 zener diode to provide a regulated dc supply voltage suitable for powering the transmitters during the low power output operating mode. The MJE2020 is a medium power transistor designed for use in general purpose audio amplifier and switching applications. The device is in the economical Motorola Case 199 plastic package. It is rated for a maximum continuous collector current of 5.0 ADC and a maximum power dissipation of 80 watts at 25°C case temperature.

### **CIRCUIT DESCRIPTION**

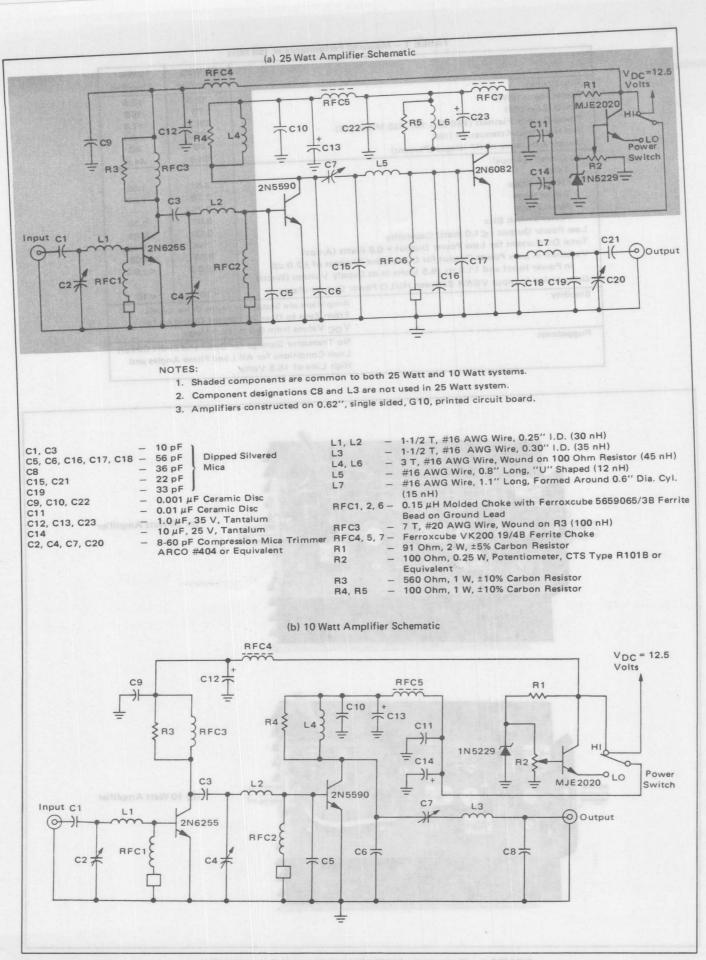

As indicated by the schematic diagrams of Figure 2, all the amplifier stages are of the common-emitter configuration and all are operated Class C. Except for a minor variation in the 2N5590 output network, all component values and transistor types used for the 10 watt amplifier are also common to the first two stages of the 25 watt amplifier.

#### **TRANSMITTER RF DESIGN**

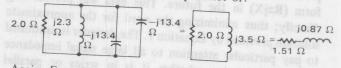

The transmitter gain stages have been designed for 158 MHz operation using large-signal transistor impedance data. These impedances for the 2N6082 and 2N5590 transistors appear in Figures 4 through 9. Large signal data for the 2N6255 transistor can be obtained from its data sheet. The resistive (Rin) and reactive (Cin, Cout) parallel impedance components are given by the curves. The \*Trademark of Motorola Inc.

Circuit diagrams external to Motorola products are included as a means of illustrating typical semiconductor applications; consequently, complete information sufficient for construction purposes is not necessarily given. The information in this Application Note has been car fully checked and is believed to be entirely reliable. However, no responsibility is assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor devices described any license under the patent rights of Motorola Inc. or others.

### TABLE 1 – Measured Performance at 158 MHz

|                                                                                 |                                                                                                                                             | 25 Watt   | 10 Watt       |  |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|--|

|                                                                                 |                                                                                                                                             | Amplifier | Amplifier     |  |

| Vdc (Volts)                                                                     |                                                                                                                                             | 12.5      | 12.5          |  |

| Power Input (mW)                                                                |                                                                                                                                             | 75        | 180           |  |

| Power Gain (dB)                                                                 |                                                                                                                                             | 25.2      | 17.4          |  |

| Power Output Flatness (156.275-157.425                                          | MHz) (dB)                                                                                                                                   | ±0.1      | ±0.1          |  |

| 2nd Harmonic Attenuation (dB)                                                   |                                                                                                                                             | 40        | 40            |  |

| Overall Efficiency of RF Stages (Percent)                                       |                                                                                                                                             | 56.8      | 44.5          |  |

| DC Current (Amps):                                                              | 10 - 10                                                                                                                                     |           |               |  |

| Total                                                                           |                                                                                                                                             | 3.61      | 1.89          |  |

| Output Stage                                                                    |                                                                                                                                             | 2.70      | 1.60          |  |

| Driver Stage                                                                    |                                                                                                                                             | 0.75      | -             |  |

| Input Stage                                                                     |                                                                                                                                             | 0.07      | 0.20          |  |

| Power Switch Bias                                                               |                                                                                                                                             | 0.09      | 0.09          |  |

| Low Power Output (≤1.0 Watt) Capabili                                           | ty                                                                                                                                          | Yes       | Yes           |  |

| Total DC Current for Low Power Output = 0.8 Watts (Amps)                        |                                                                                                                                             | 0.95      | 1.08          |  |

| Variation in Low Power Output for Cumu<br>in Power Input and 11.0 to 15.5 Volts |                                                                                                                                             | <±0.2     | <±0.2         |  |

| Degradation in Input VSWR Between HI/                                           | LO Power Output (Percent)                                                                                                                   | <10       | <10           |  |

| Stability                                                                       | Amplifiers are Stable for Input Drive Levels<br>From Zero to Over 30 Percent Overdrive for<br>V <sub>DC</sub> Values from 8.0 to 15.5 Volts |           |               |  |

| Ruggedness                                                                      |                                                                                                                                             |           | Short Circuit |  |

| nuggeoness                                                                      | No Transistor Damage for Open and Short Circui<br>Load Conditions for All Load Phase Angles and<br>High Line of 15.5 Volts                  |           |               |  |

FIGURE 1 - Photograph of VHF Marine Transmitter Power Amplifiers

FIGURE 2 - Schematic Diagrams for 25 Watt and 10 Watt Amplifiers

approximate resistive portion of the load ( $R'_L$ ), that must be presented to the collector by the associated matching network, has been calculated for an output power level, P, and a collector supply voltage, V<sub>CC</sub>, from Equation 1.

$$R'_{L} = \frac{(V_{CC})^2}{2P}$$

(1)

A detailed discussion related to the characterization of RF power transistors for large signal input and output impedances and the derivation and limitations of Equation 1 can be found in Reference 1. It is anticipated that several of the RF Power transistors applicable to VHF marine band transmitters will have their large signal impedance characterizations published in series equivalent form (R±jX) in the future. This data will provide R'L directly; thus minimizing the need for the approximate solution provided by Equation 1. The designer is cautioned to pay particular attention to all large signal impedance data to determine whether it is in series or parallel equivalent form and to use it accordingly.

In all cases the transistor matching networks have been designed for the lowest Q that is still consistent with practical component values, reasonable harmonic suppression and smooth tuning. This permits the transmitters to be adjusted for an approximately flat response over the 156.275 to 157.425 MHz frequency band allocated to ship to ship and ship to shore communications.

For the 10 watt transmitter, the network following the 2N5590 transistor must step impedance up to match the 50 ohm load. For the 25 watt transmitter, this network must step the impedance down to match the combined base to ground impedance of the 2N6082 transistor. To best achieve these two varying requirements and still facilitate using a common printed circuit layout, two matching network configurations have been used (See Figure 2).

All fixed value capacitors from 12 to 56 pF used in the amplifiers are dipped silvered mica units. The effective capacitance of these components at 158 MHz will deviate from their low frequency value for nominal capacitance values above approximately 15 pF. These larger valued capacitors have been characterized at 158 MHz and the results tabulated in Table II. The table also provides the capacitance range at 158 MHz for the 8-60 pF variable capacitors.

| Nominal<br>Low Frequency<br>Capacitance<br>(pF) | Capacitance<br>At 158 MHz<br>(pF) | Parallel Reactance<br>Component At<br>158 MHz<br>Xp (Ohms)                        |

|-------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------|

| 22                                              | 27.5                              | 36.7                                                                              |

| 27                                              | 33.5                              | 30.1                                                                              |

| 33                                              | 47                                | 21.8                                                                              |

| 39                                              | 52                                | 19.3                                                                              |

| 47                                              | 68                                | 14.9                                                                              |

| 56                                              | 75                                | 13.4                                                                              |

| 8-60 (Variable)                                 | 10-110                            | 108-9.1                                                                           |

|                                                 | Lead 1/16                         | ver Mica, Cornell-<br>ype CM04 With Each<br>'' in Length.<br>04 Compression Mica. |

Design details for two representative impedance matching networks are given below. Additional design information can be found in Reference 2.

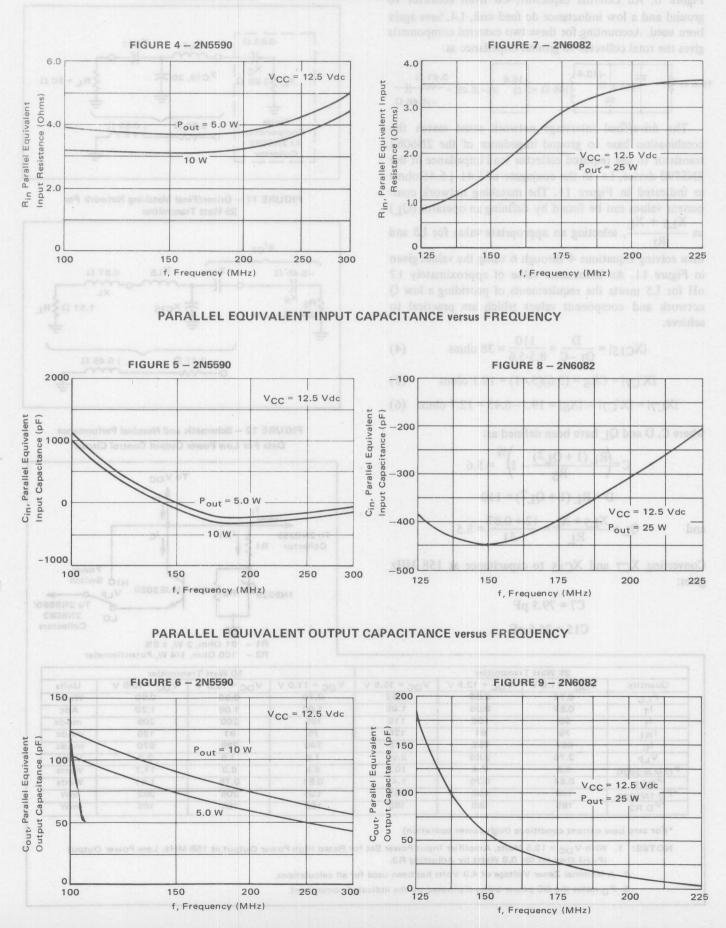

#### **25 WATT OUTPUT NETWORK DESIGN**

Using Figure 9, the parallel equivalent output capacitance is found to be 40 pF for the 2N6082 transistor when providing 25 watts at 158 MHz. This converts to a capacitive reactance of 25.2 ohms at 158 MHz. R'L for this stage may be computed from Equation 1 to be 3.12 ohms. The remaining parallel impedance components to be accounted for at the 2N6082 collector are the 56 pF collector to ground capacitor C18 and the 45 nH dc feed coil L6. (See Figure 2a for component references). Capacitor C18 is used to provide a low impedance from collector to ground at the second harmonic to improve efficiency. To enhance stable operation, coil L6 should present a low impedance for frequencies below approximately 30 MHz; since at these lower frequencies, the device gain is high and the normal collector load is essentially removed by capacitor C21. An inductance of 45 nH meets this condition and also permits adequate decoupling from the dc line at 158 MHz. Accounting for L6 and using the 158 MHz value from Table II of 75 pF for C18 gives the total impedance at the 2N6082 collector to be:

3.12

$$\Omega$$

$\left[\begin{array}{c} -j0.83 \Omega\\ \Omega\\ \Omega\\ \Omega\end{array}\right]$

$\left[\begin{array}{c} -j0.83 \Omega\\ \Omega\\ \Omega\end{array}\right]$

The conversion from parallel to series form has been made using Equation 1 of the Appendix. The output network must therefore be designed to transform the 50 ohm external load to the conjugate of 2.88 ohms resistance in series with 0.83 ohms negative reactance. The required load impedance that must be present to the collector is therefore 2.88 + j 0.83 ohms as noted in Figure 10.

For the purpose of network design, an operator (QL) for the network in Figure 10 will be defined as  $\frac{X_{L7} + X_C}{R_C}$ It should be noted that this QL is not intended to represent the loaded Q as defined by the 3 dB bandwidth points of the network. Values of QL, when defined as  $\frac{X_{L7} + X_C}{R_C}$  of approximately 5 to 8 will provide a good tradeoff between harmonic attenuation, low insertion loss and the voltage levels that can occur during high output VSWR conditions. For this design a value of 15 nH was chosen for L7 yielding a  $Q_L$  value of

$$Q_{\rm L} = \frac{15 - 0.83}{2.88} = 4.92$$

|XC19, 20| and |XC21| are found from Equations 2 and 3.

$$|X_{C19, 20}| = \frac{B}{Q_{L}-A} = \frac{72.5}{4.92-0.67} - 17.1 \text{ ohms}$$

(2)

$$|X_{C21}| = AR_L = 0.67(50) = 33.4 \text{ ohms}$$

(3)

where A and B have been defined as:

$$A = \left(\frac{R_{C}(1 + Q_{L}^{2})}{R_{L}} - 1\right)^{72} = 0.67$$

$$B = R_{C}(1 + Q_{L}^{2}) = 72.5$$

Converting from reactance to capacitance at 158 MHz yields: C19, 20=58.8 pF

$$C21 = 30.1 \text{ pF}$$

As shown in Figure 2a, capacitance C19, 20 consists of a fixed and variable capacitor in parallel having nominal low frequency values of 33 pF and 8 to 60 pF respectively. A capacitor having a nominal low frequency value of 22 pF is used for C21 since, as noted in Table II, it will exhibit an effective capacitance of approximately the calculated value (30.1 pF) at 158 MHz.

### 25 WATT DRIVER/FINAL NETWORK DESIGN

The parallel input impedance components for the 2N6082 output transistor as obtained from Figures 7 and 8 are:

$$R_{in} = 2.0$$

ohms

$$C_{in} = -440 \text{ pF}$$

The negative sign associated with C<sub>in</sub> indicates the actual parallel reactance component is an inductance. At 158 MHz this inductive reactance will have a value of 2.3 ohms. The two external base to ground capacitors, C16 and C17 (see Figure 2a for component references) provide a course impedance match at 158 MHz and a low impedance to ground at the second harmonic. Two capacitors in parallel have been used to minimize lead inductance and to provide an electrically symmetrical arrangement. Neglecting the effect of RFC6 but including measured values from Table II for C16 and C17 yields a combination base to ground impedance of:

Again Equation 1 of the Appendix has been used to convert from parallel to series form.

As noted in Figure 3a the required output power from the 2N5590 transistor is approximately 5 watts. For this condition, the parallel output impedance components are

#### PARALLEL EQUIVALENT INPUT RESISTANCE versus FREQUENCY

7

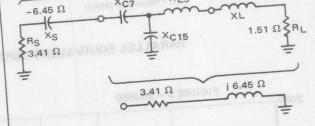

15.6 ohms and 70 pF as obtained from Equation 1 and Figure 6. An external capacitor, C6 from collector to ground and a low inductance dc feed coil, L4, have again been used. Accounting for these two external components es the total collector to ground impedance as:

gives the total

$$-j13.4$$

$15.6 \Omega$   $fig14.4 \Omega$   $ji45 \Omega = {\Omega - j8.25} = -m - (fig16.45 \Omega) - j6.45 \Omega$

The drive/final interstage network must match th combination base to ground impedance of the 2N6082 transistor to the required collector load impedance of the 2N5590 device, i.e. to the conjugate of 3.41 -j 6.45 ohms as indicated in Figure 11. The matching network component values can be found by defining an operator (QL)  $X_{L5} + X_L$ , selecting an appropriate value for L5 and

then solving Equations 4 through 6 using the values given in Figure 11. An inductance value of approximately 12 nH for L5 meets the requirements of providing a low Q network and component values which are practical to achieve.

$$|X_{C15}| = \frac{D}{O_{L}-C} = \frac{110}{8.5-5.6} = 38 \text{ ohms}$$

(4)

$$V'_{C7} = CRs = (5.6)(3.41) = 19.1 \text{ ohms}$$

(5)

$$|X_{C7}| = |X_{C7}| - |X_S| = 19.1 - 6.45 = 12.7 \text{ ohms}$$

(6)

where C, D and QL have been defined as:

$$C = \left(\frac{R_L (1 + Q_L^2)}{R_S} - 1\right)^{\frac{1}{2}} = 5.6$$

D = R<sub>L</sub> (1 + Q<sub>L</sub><sup>2</sup>) = 110

Q<sub>L</sub> =  $\frac{X_{L5} + X_L}{R_L} = \frac{12 + 0.87}{1.51} = 8.5$

Converting XC7 and XC15 to capacitance at 158 MHz gives:

#### $C7 = 79.5 \, \text{pF}$

C15 = 26.5 pF

FIGURE 10 - Output Network Configuration For 25 Watt Transmitter -0.83 Ω XL7 16 = 50 Ω XC XC19, 20 Rc \$2.88 Ω i 0.83 S 2.88 Ω Series Components 0 ~~~ At 2N6082 Collector FIGURE 11 - Driver/Final Matching Network For 25 Watt Transmitter X'C7 0.87 54 XL5 XC7

|            | 25 Watt Transmitter      |              |                          | 10 Watt Transmitter      |                          |                          |       |

|------------|--------------------------|--------------|--------------------------|--------------------------|--------------------------|--------------------------|-------|

|            |                          |              | V <sub>DC</sub> = 15.5 V | V <sub>DC</sub> = 11.0 V | V <sub>DC</sub> = 12.5 V | V <sub>DC</sub> = 15.5 V | Units |

| Quantity   | V <sub>DC</sub> = 11.0 V | VDC = 12.5 V | 0.92                     | 0.70                     | 0.80                     | 0.90                     | Watts |

| PLO        | 0.72                     | 0.80         |                          |                          | 1.08                     | 1.20                     | Adc   |

| IT         | 0.87                     | 0.95         | 1.05                     | 1.00                     |                          | 205                      | mAd   |

| 1          | 98                       | 100          | 110                      | 185                      | 200                      |                          |       |

| IB1        | 75                       | 91           | 125                      | 75                       | 91                       | 125                      | mAdd  |

| IC         | 697                      | 759          | 815                      | 740                      | 789                      | 870                      | mAdd  |

| VLP        | 2.75                     | 2.80         | 2.90                     | 1.8                      | 1.9                      | 2.0                      | Volts |

| PD MJE2020 | 5.8                      | 7.4          | 10.3                     | 6.8                      | 8.3                      | 11.7                     | Watts |

| PDB1       | 0.51                     | 0.75         | 1.41                     | 0.51                     | 0.75                     | 1.41                     | Watts |

| *PD 1N5229 | 138                      | 206          | 352                      | 138                      | 206                      | 352                      | mW    |

| *PD R2     | 185                      | 185          | 185                      | 185                      | 185                      | 185                      | mW    |

\*For zero base current conditions (high power operation)

NOTES: 1. With VDC = 12.5 Volts, Amplifier Input Power Set for Rated High Power Output at 158 MHz. Low Power Output (PLO) then set for 0.8 Watts by Adjusting R2.

- 2. A Nominal Zener Voltage of 4.3 Volts has been used for all calculations.

- 3. PD notes the DC power being dissipated by the indicated component.

Again, Table II indicates a fixed capacitor having a nominal low frequency value of 22 pF should be used for C15 and that the 8 to 60 pF trimmer capacitor is suitable for C7.

This completes the matching network discussion. Similar procedures can be followed for the remaining input and interstage networks. The printed circuit board layout has been configured to minimize interconnecting lead inductance in the RF signal path, however, in some cases it will be necessary to account for a small amount of additional interconnect inductance (on the order of 5 to 10 nH) in order to accurately determine the component values.

#### **DESIGN CONSIDERATIONS FOR LOW POWER** (≤1.0 WATT) OPERATION

ped with a control for switching from rated power output to one watt or less power output. A variety of design problems can be encountered in meeting this requirement. The transmitter must be designed to remain stable under the different conditions imposed upon it during this radical variation from normal operation. In addition, tradeoffs in the low power circuitry between complexity, cost, and sensitivity of the low power output level with system variations must be considered.

In general, the possible approaches available for reducing the output power to less than one watt can be divided into two categories:

- a. The dc supply supply voltage can be altered to reduce the amount of RF gain available.

b. The RF signal level itself can be reduced. The FCC regulations require that all VHF ship station transmitters operating in the 156-162 MHz band be equip-Consideration has been given to both categories. TABLE III - Performance of Low Power Control Circuits for 25 Watt Transmitter Method Schematic Diagram Description Disadvantages Comments Advantage Decreasing DC Supply Voltage 1 to Input Stage. Power Switch o LO a. Using Dropping Resistor or Potentiometer. Unsatisfactory—With 1a the Low Power Output will Nominally Vary from 0.15 to 1.0 Watt as Vdc Changes from 11.0 to 16.0 Volts. Both 1a and 1b Require Less Than  $\pm$  1.0 dB Variation in Input Power to Prevent Power Output from Ex-ceeding 1.0 Watt or Being Cut-Off. Low Power Components are Adequate a. (Collector Current is Approximately 60 mAdc). Very Low DC Collector Voltage Required (Approximately 1.0 Volt). To 2N6255 Collector To Vdd Method 1a is Critical to Both Input Power and Vdc Variations. Method 1b is Critical to Input Power Varib. Low Power Output Level can be Adb. c. Low Cost HI b. Using Dropping Resistor and Zener Diode. To - To Vdc Degrades Input VSWR Significantly when Switching from High to Low Power. 2N6255 Collector Power o Switch LO Sold of T Relatively Low Power Components are Suitable but now must Control Approximately 250 mAdc. Required DC Collector Voltage is Still Low (Approximately 2.0 Volts). 2 Decreasing DC Supply Voltage Similar to Above Unsatisfactory-Similar to Above to Driver Stage b. Doesn't Degrade Input VSWR as Badly as Method 1. Critical to Input Power and/or Vdc Input Stage is Operating at Full Power Level with Mismatched Load. Unsatisfactory-Low Power Output Varies only  $\pm$  0.2 Watt for \*Standar Test Condition, but because of Ex-tremely Low Initial Level (0.25 Watts) Absolute Value of Output can become too Low. Removing DC Supply Voltage Relatively Low Power Output is Achieved (Approximately 0.25 Watts). 3 Switch Lowest in Cost. a. To Vdc to Output Stage To 2N6082 b. Low Effect on Input VSWR. Collector LO Relatively Insensitive to Both Input Power and VDC Variations. No Means of Adjusting Low Power b. Output Level Driver Stage is Operating at Full Power Level with Mismatched Load. Satisfactory – Low Power Output Varies ± 0.3 Watts for \*Standard Test Condition. Most of Power Out-put Change is due to Vdc Variation. Decreasing DC Supply Voltage Power a Relatively Insensitive to Both Input Power and Vdc Variations. High DC Current Level Involved PLO To 2N6255 to all Three Stages. Switch 2N5590 Bulky-High Power Resistor ь. All Stages are Operating at Low Gain a. Using High Power Dropping Resistor or Potentiometer. 2N6082 b HIP То Vdd Collecto Low Power Output Level can be Adjusted. Degrades Input VSWR с. d. Collector Voltage Values are Higher (Approximately 3.5 Volts). Satisfactory–Low Power Output Varies Less Than ± 0.2 Watts for \*Standard Test Condition. b. Using Zener Regulated DC Not Sensitive to Input Power or Vdc Must Provide Adequate Heat Sink for Control Transistor. To Vdc To 2N6255, Suitable Low Cost Plastic Encapsu-lated Semiconductors are Available b. Degrades Input\_VSWR 2N5590, and 2N6082 LOPPowe Components are Relatively Compact and Light in Weight. Collectors d. Economical, Low Power, Potentiom eter can be used to Set Low Power Output Level. Also b and d of Method 4a Decreasing DC Supply Voltage All the Advantages of Method 4b Except that Input Stage is now Operating at High Gain. Recommended Choice-Low Power Output Varies Less Than ±0.2 Watts for Standard Test Condition. Input VSWR is Degraded Less Than 10% in Going from High to Low Power Out-put Operation. To Vdc a. Same as Method 4b but does not Significantly Effect Input VSWR to Driver and Output Stages Using Zener Regulated DC To 2N5590 Input Stage is Operating at Full HI b. Low Effect on Input VSWR and 2N6082 Collectors wer Level with Mismatched Load. LO Power \*Standard Test Condition - Combined Changes of ± 2 dB in Power Input and 11.0 to 16.0 Volts in Vdc. Reference is Low Power Output of 0.8 Watts with Vdc = 12.5 Volts and Power Input Corresponding to that Required for 25 Watts High Power Output.

Attenuating the RF signal level appears to be the least desirable approach from the standpoint of circuit complexity, ease of achieving front panel control, and the effect on RF gain during normal power output operation. Many possible approaches of reducing power by altering the DC supply voltage have been investigated in detail for the 25 watt transmitter and the results summarized in Table III. These methods are of primary importance when a regulated dc supply is not being employed. If a dc regulator is being used then the decrease in dc supply voltage can best be accomplished in the dc regulator circuitry. Each method of Table III has been evaluated on the basis of:

- a. Variation of power amplifier input VSWR when switched from normal to low power operation.

- b. Sensitivity of low power output level to changes in battery voltage and input drive power.

- c. Cost.

- d. Adjustability of output power level.

- e. Physical size of components.

Method 5 of Table III appears to offer the best overall choice and this approach has been incorporated in both the 25 watt and 10 watt transmitter designs. If, however, cost is of primary concern, an appropriate power resistor can be used to drop the dc supply voltage to the driver and output stage (similar to Method 4a).

Nominal current, voltage and component power dissipation values for Method 5 are given in Figure 12 for

both the 25 and 10 watt transmitters. Heat sink considerations for the MJE2020 transistor are considered in the Thermal Design Section.

#### **TRANSMITTER PERFORMANCE**

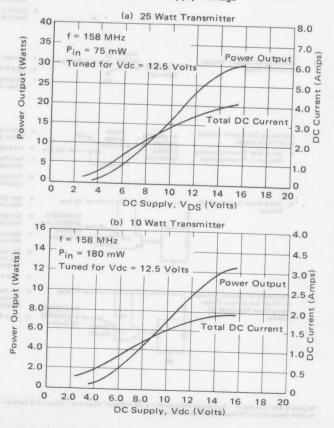

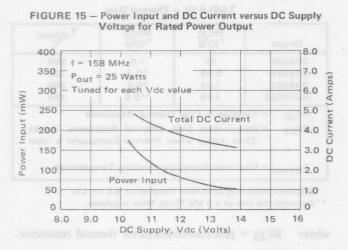

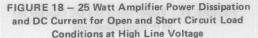

In addition to the data given in Table I, the curves in Figures 13 and 14 provide additional performance information for a 25 watt and a 10 watt transmitter operating at 158 MHz. Figure 15 shows the amount of input power and dc current required for the 25 watt amplifier for various values of dc supply voltage. This information will be of use if it is intended to use a regulated dc supply to drive the transmitter since the regulated dc voltage will, of necessity, be reduced below the nominal battery voltage.

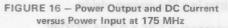

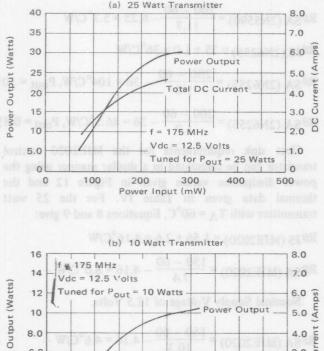

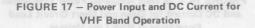

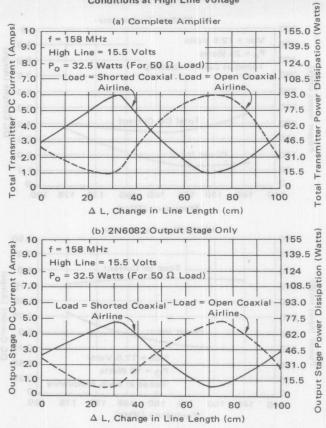

Figures 16 and 17 provide performance information for the transmitters when tuned for other frequencies in the 144 to 175 MHz band.

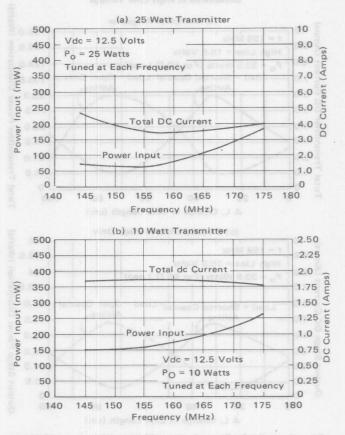

High load VSWR testing has been done on both amplifiers at high line voltage and for all load phase angles without damage to any transistor. Figure 18 indicates current and power dissipation levels that can be experienced when the 25 watt amplifier output is mismatched into open and short circuit loads. This data was obtained by adjusting the amplifier for rated power output into a 50 ohm load with a dc supply voltage of 13.6 volts. The supply voltage was then increased to 15.5 volts causing the output power to increase to 32.5 watts. The 50 ohm load was then removed and replaced with an open or short circuited air line of variable length. As indicated by the curves, worst case power dissipation for

#### FIGURE 14 – Power Output And DC Current Versus DC Supply Voltage

the output stage can increase from a normal 50 ohm load value of 13.3 watts to approximately 75 watts. Prolonged operation in this worst case condition with an ambient temperature of only 25°C will require a heat sink specification for the 2N6082 transistor of 0.12°C/W in order to keep the device junction temperature from exceeding 200°C. Designing the heat sink to be adequate for this infrequent mode of operation would normally be uneconomical and impractical. Therefore, if it is required to operate with this worst case load condition, the need for a protection circuit which will reduce either the RF drive power, the dc supply voltage, or the dc supply

6.0

4.0

2.0

0

0

100

200

Power Input (mW)

300

Power

current during high VSWR load conditions should be considered even though transistors capable of withstanding infinite VSWR conditions are used. It is, however, important to use transistors capable of withstanding momentary worst case short and open load conditions so as to prevent device failure during the reaction time of the protection circuitry. The 2N5590 and 2N6082 output devices exhibit this degree of ruggedness.

#### THERMAL DESIGN

Proper thermal analysis and good thermal construction techniques are very important in RF power transmitter design and fabrication. Transmitter construction should include the use of:

- a. A smooth heat sink surface to maximize heat sink to transistor case contact area.

- b. A proper amount of thermal joint compound between heat sink and transistor case interface.

- c. Torque as specified for the transistor when fastening the transistor to the heat sink.

- d. A heat sink configuration that will permit locating the higher power level stages near the maximum heat transfer position on the heat sink.

Using the measured dc current values given in Table I and the measured RF power levels given in Figure 3, the approximate power dissipated in each transmitter RF stage, PD, can be calculated from Equation 7.

$$P_{D} = P_{in}(rf) + P_{in}(dc) - P_{out}(rf)$$

(7)

Cur

3.0

1.0

0

500

otal DC Current 2.0 0

400

Power dissipation for the 2N6255 and 2N5590 devices will be greater for the 10 watt transmitter and, in the case of the 2N6255 device, the worst dissipation will occur during the low power mode of operation. This happens, since at this time, the 2N6255 stage is receiving normal dc voltage and RF drive power but is working into a mismatched load.

Solving Equation 7 for a dc supply voltage of 12.5 volts yields:

2N6082 stage,  $P_D = 13.3 \text{ W} - 25 \text{ Watt Amplifier}$

2N5590 stage,  $P_D = 11.7 \text{ W} - 10 \text{ Watt Amplifier}$

2N6255 stage,  $P_D =$

Operating at Rated Power \*1.7 W - 10 Watt Amplifier Operating in Low Power

Mode

1.0 W - 10 Watt Amplifier

Thermal data for the transistors being used appears in Table IV.

For any single transistor stage, the heat sink to ambient thermal resistance ( $R\theta_{SA}$ ) requirement may be computed from Equations 8 and 9.

$$R\theta_{\rm JS} = R\theta_{\rm JC} + R\theta_{\rm CS} \tag{8}$$

$$R\theta_{SA} = \frac{T_j(max) - T_A}{P_D} - R\theta_{JS}$$

(9)

TABLE IV - Thermal Data

| Devic        | e      | R∂JC<br>°C/W  | RθCS<br>°C/W                                       | TJ(max)<br>C   |

|--------------|--------|---------------|----------------------------------------------------|----------------|

| 2N625        | 5      | 35            | 1.0                                                | 200            |

| 2N559        | 0      | 5.85          | *0.3                                               | 200            |

| 2N608        | 2      | 1.92          | *0.3                                               | 200            |

| MJE20        | 20     | 1.56          | **2.6                                              | 150            |

| RθJC<br>RθCS | = Case | e-to-Heat Sin | Thermal Resista<br>k Thermal Res<br>en Thermal Con | istance, Value |

\*Assumes Mounting Stud Nut Torqued at 6.5 In. Lb. \*\*Assumes the Use of a 3 Mil Thick Mica Insulator.

where  $R\theta_{JS}$  = junction-to-heat-sink thermal resistance.

$T_A$  = ambient temperature.

Heat sink requirements for the 25 watt transmitter output stage can be obtained by using the appropriate  $P_D$ value and data from Table IV in Equations 8 and 9. If the maximum ambient temperature requirement is assumed to be 60°C this gives:

$R\theta JS (2N6082) = 1.92 + 0.3 = 2.22^{\circ}C/W$  $R\theta SA (2N6082) = \frac{200 - 60}{13.3} - 2.22 = 8.3^{\circ}C/W$

Calculating heat sink requirements for the 10 watt transmitter in a like manner yields:

$$R\theta_{JS} (2N5590) = 5.85 + 0.3 = 6.25^{\circ}C/W$$

$$R\theta_{SA} (2N5590) = \frac{200 - 60}{11.7} - 6.25 = 5.7^{\circ}C/W$$

$$R\theta_{JS} (2N6255) = 35 + 1.0 = 36^{\circ}C/W$$

$$R\theta_{SA} (2N6255) = \frac{200 - 60}{1.0} - 36 = 104^{\circ}C/W, P_{out} = 10W$$

$$R\theta_{SA} (2N6255) = \frac{200 - 60}{1.7} - 36 = 46.5^{\circ}C/W, P_{out} = 0.8W$$

Heat sink requirements for the MJE2020 control transistor can be calculated in a similar manner using the power dissipation values given in Figure 12 and the thermal data given in Table IV. For the 25 watt transmitter with  $T_A = 60^{\circ}C$ , Equations 8 and 9 give:

$$^{KO}JS (MJE2020) = 1.56 + 2.6 = 4.16^{\circ}C/W$$

$R\theta_{SA} (MJE2020) = \frac{150 - 60}{7.4} - 4.16 = 8.0^{\circ}C/W - 4.16 = 8.0^{\circ}C/W$

Nominal Supply Voltage of 12.5 Volts.

$$R\theta_{SA} (MJE2020) = \frac{150 - 60}{10.3} - 4.16 = 4.6^{\circ}C/W - 10^{\circ}C/W$$

High Line Voltage of 15.5 Volts.

\*Assumes approximately 40% of the power to the 2N5590 stage is being reflected because of impedance mismatch introduced during low power operation.

The MJE2020 device only dissipates significant power during transmission in the low power mode. During this time the power being dissipated by the output stage RF transistor is negligible. Therefore, if the MJE2020 is properly located near the RF output device, a common heat sink will serve both transistors.

The following points apply:

a. The  $R\theta_{SA}$  values have been computed for continuous transmitter operation. The heat sink requirements will be reduced for duty cycle conditions.

b. If operation into mismatched loads is anticipated, the  $R\theta_{SA}$  values must be modified to take into account the increased dissipation that can occur for these operating conditions.

c. It is not necessary for the heat sink to extend the entire amplifier length as shown in Figure 1. The only requirement is that the sink meet the  $R\theta_{SA}$  requirements of the driver, final and control transistors.

# CONSTRUCTION

The amplifiers have been constructed to minimize the amount of modifications required prior to reproducing the units economically in large quantities:

a. Low cost components have been used.

b. The number of tuning adjustments have been minimized.

c. A commonality of components exists between the 25 watt and 10 watt transmitters.

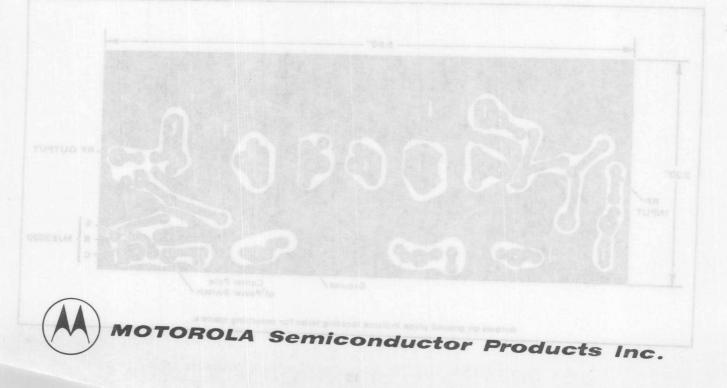

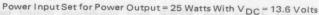

d. Single sided printed circuit board construction adaptable to high volume assembly techniques such as wave soldering and automatic component insertion has been employed. A full scale layout for the board artwork appears in Figure 19. The printed circuit board of Figure 19 has been laid out to minimize component lead length and interconnection inductance in the RF signal path and to maximize the amount of area available for the ground plane. It is imperative that the high level ground currents for the 25 watt output stage be confined as much as possible to this stage and not permitted to circulate in the vicinity of the low level input stage. If this conduction does occur, a degradation in transmitter gain and also an unnecessary increase in input VSWR when switching from normal to low power operation can result. Controlling the ground current flow becomes more difficult if a conducting plate. such as a heat sink, is grounded only near the amplifier output and input. This grounding condition will permit a significant portion of the load ground current to return to the output stage ground via the heat sink and low level input stage ground path. To alleviate this problem, additional RF ground returns must be provided between the heat sink and the circuit ground. Ground returns between the heat sink and the vicinity of each emitter lead for the 2N6082 and 2N5590 stages are especially important. These ground connections can be accomplished by using properly located spacers capable of providing a good RF connection between the printed circuit board ground and the heat sink. Suitable spacer locations are indicated in Figure 19.

Mounting and thermal information pertaining to the 2N5590 and 2N6082 device packages can be found in Reference 5. Ideally, these packages should be secured to the heat sink prior to being soldered into the circuit. This, however, is not easily achievable with the construction method being employed. Therefore, adequate precautions must be taken when soldering the device packages to the circuit board in order to assure proper alignment with the heat sink mounting holes and to eliminate tension

FIGURE 19 - Foil Side of Printed Circuit Board Artwork for 25/10 Watt VHF Power Amplifiers

between the ceramic to metal joints. Two alternate construction approaches are:

a. Put the amplifier circuit pattern on the component side of the board. This, however, will not permit the use of wave soldering techniques.

b. Use a double sided board layout which will require the use of plated through holes, eyelets or wrap-around grounds.

Regardless of the construction method used, it is essential to proper electrical performance that the RF transistors have their emitters grounded near the device package and that all component and interconnection lead lengths in the RF signal path be held to an absolute minimum.

The MJE2020 control transistor has been located on the back side of the printed circuit board to permit mounting directly on the heat sink. An alternate approach would be to locate the transistor on the component side over a cut out in the board and then use a spacer of low thermal resistance material between the heat sink and transistor. This second method would simplify assembly procedures at the expense of a slight increase in thermal resistance between the transistor case and heat sink. In either case, a mica washer must be used to electrically isolate the transistor from the sink. The MJE2020 device is available in several standard lead form configurations. The board layout of Figure 19 will accommodate configuration A. A description of the various lead configurations, mounting, and heat sinking techniques for the MJE2020 package (Case 199) are discussed in detail in Reference 6.

must be taken when soldering the device packages to the circuit board in order to assure proper alignment with the heat sink mounting, holes, and to eliminate tension

#### APPENDIX SERIES AND PARALLEL EQUIVALENTS

To convert a parallel resistance and reactance combination to series:

$$R_{S} = \frac{R_{P}}{1 + \left(\frac{R_{P}}{X_{P}}\right)^{2}}, X_{S} = \frac{X_{P}}{1 + \left(\frac{X_{P}}{R_{P}}\right)^{2}}$$

(1)

To convert a series resistance and reactance combination to parallel

$$R_P = R_S + \frac{(X_S)^2}{R_S}, X_P = X_S + \frac{(R_S)^2}{X_S}$$

(2)

### REFERENCES

- 1. "Systemizing RF Power Amplifier Design," by Roy Hejhall, Application Note AN-282A.

- "Matching Network Designs with Computer Solutions," by Frank Davis, Application Note AN-267.

- "Design Techniques For an 80 Watt, 175 MHz Transmitter For 12.5 Volt Operation," by John Hatchett. Application Note AN-577.

- "VHF Power Amplifiers Using Paralleled Output Transistors," by John Hatchett. Application Note AN-585.

- 5. "Mounting Stripline-Opposed-Emitter (SOE) Transistors," by Lou Danley. Application Note AN-555.

- "Mounting Procedure For, And Thermal Aspects Of, Thermopad Plastic Devices," by Larry Wing. Application Note AN-290B.

FIGURE 13 - Poll Side of Printed Circuit Board Artwork for 25/10 Wate Vielt Frower Amplified