## AN449

### MOTOROLA SEMICONDUCTOR APPLICATION NOTE

# An MC68340 to M88000 MBUS Bus Translator

By Dave McCartney Highend Applications Group Motorola Ltd, East Kilbride

### INTRODUCTION

In a high performance processor system built around the M88000 family it makes sense to off-load many of the common I/O tasks to a dedicated I/O processor. This I/O processor is likely to be from a different family and therefore will use a different bus structure from that of the main processor system. Therefore some form of interface is required between the main processor bus system and the bus system of the I/O processor. This application note describes a circuit that can act as an interface between an M88000 type MBUS and the bus system of an I/O processor system based on the MC68340 which has an M68000 type asynchronous bus.

### FUNCTIONAL DESCRIPTION

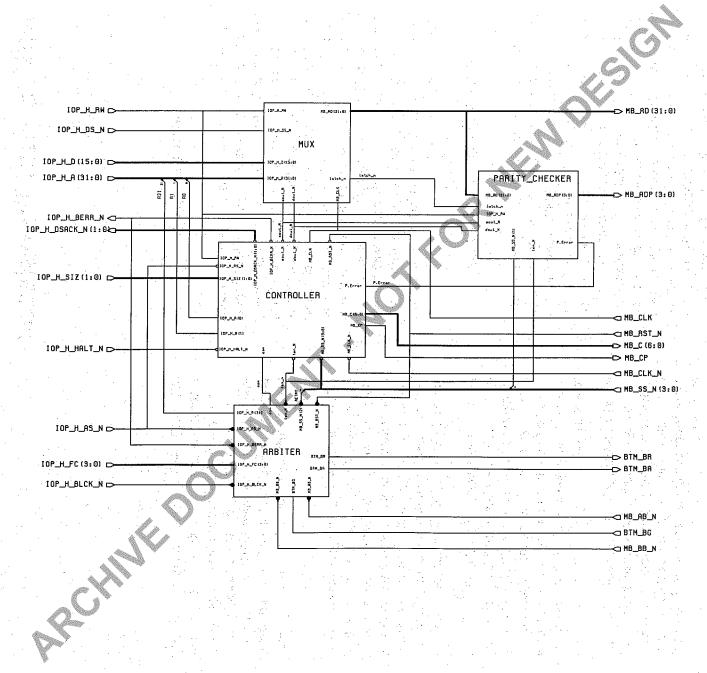

The function of this interface circuit is to translate all of the signal lines from the I/O processor to the type of signals required for an M88000 MBUS structure. The application is constructed from several PALs and standard TTL packages. The main section consists of a state machine built from a registered PAL. This is used to control the operation of the translator and allows for differing processor speeds and memory architectures. A block diagram of the full translator is shown in Figure 1. External connections via two 96 way DIN connectors are shown in Figure 1a. The translator consists of four main functional blocks as follows: ARBITER — This block monitors the I/O processor's bus cycles until it detects a valid bus cycle from the I/O processor which indicates an access to memory on the MBUS. It then implements the standard MBUS bus arbitration protocol to gain control of the MBUS and signals the controller block once bus tenure has been obtained.

CONTROLLER — This block generates the seven bits of control information required by MBUS along with the parity bit for these control signals. In addition this block also generates the handshake signals to the I/O processor to terminate its bus cycles. It also generates some internal control signals for other parts of the bus translator.

MUX — This takes as input the 32-bit address bus and 16-bit data bus of the I/O processor and multiplexes them on to the 32-bit multiplexed address and data lines of the 88000 MBUS. The 16-bit data bus from the I/O processor is duplicated to produce a 32-bit data bus for the MBUS system.

4. PARITY CHECKER — This block generates the four parity bits during the address phase of all MBUS cycles and during the data phase of MBUS write cycles. In addition, this block checks for any parity errors during the data phase of all MBUS read cycles.

MOTOROLA

Figure 1. Top-level block diagram

MOTOROLA 2

に設置などの影響

1.1

يَ يُعْرِي

1.00

AN449/D

ESIGN

MOTOROLA 3

### **CIRCUIT DESCRIPTION**

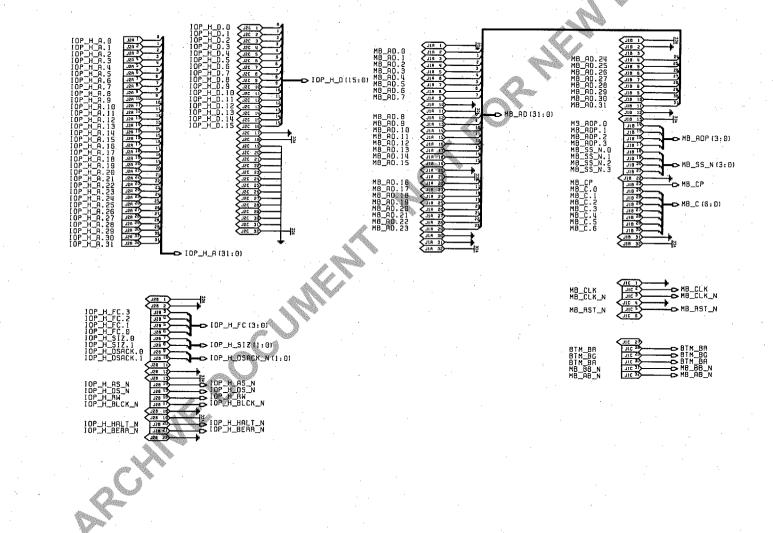

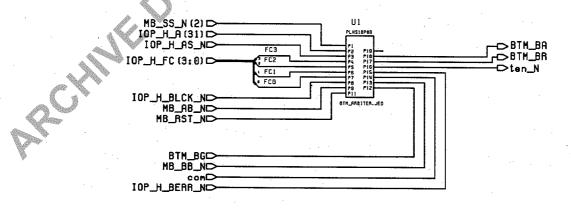

**ARBITER** — This is implemented in a 18P8 PAL (U1) as shown in Figure 2. The PAL equations are given in the appendix (see BTM\_ARBITER) and describe in detail the operation of this block.

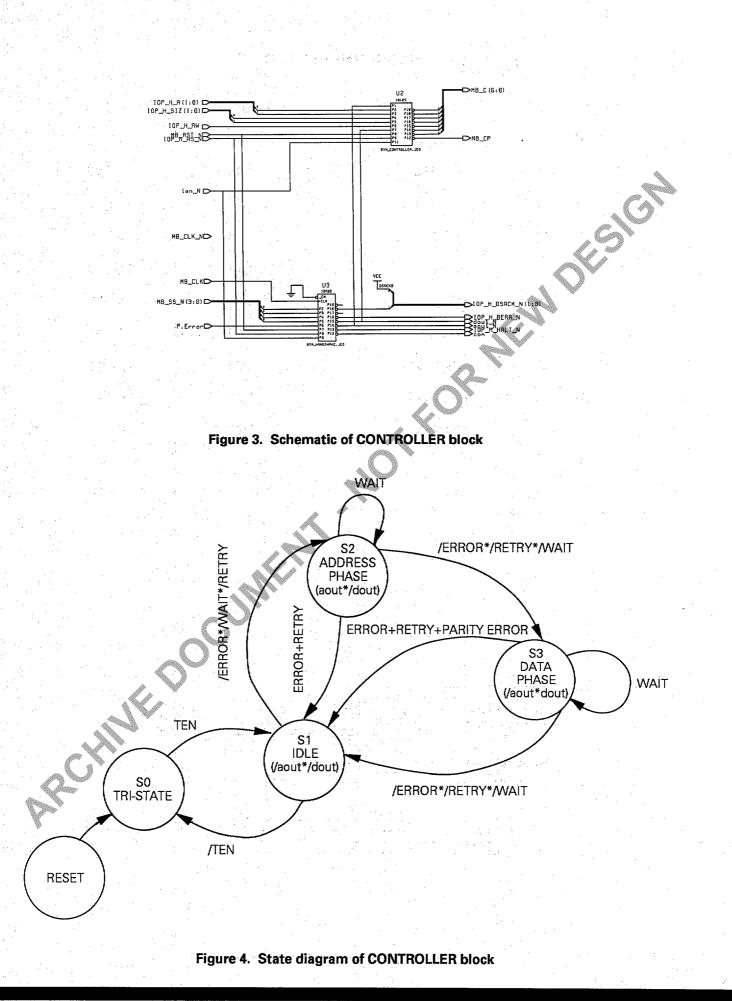

**CONTROLLER** — This is implemented using two PALs (U2) and (U3) as shown in Figure 3. The 16R6 PAL implements a simple state machine to generate two control signals, AOUT and DOUT, plus the handshake signals to the I/O processor. The state diagram is shown in Figure 4. The 16L8 PAL generates the seven MBUS control signals and the parity bit for these signals. It uses the AOUT and DOUT control signals to signify which phase is currently being run on the MBUS. The PAL equations are given in the appendix (see BTM\_CONTROLLER and BTM\_HANDSHAKE) and describe the detailed operation.

MUX — This block contains buffers and latches on the address and data buses of the I/O processor which allow them to be multiplexed onto one 32-bit bus on the MBUS, as shown in Figure 5. The buffers U5, U6, U7 and U21 are used to buffer the I/O processor's 32-bit address bus to the MBUS address and data lines. The output enable of these buffers is controlled by the AOUT control signal produced by the Controller block. The latched buffers U8, U9, U10 and U11 are used to buffer the 16-bit data bus from the I/O processor and multiplex it onto the MBUS address and data lines. Since the I/O processor's data bus is only 16 bits wide it is duplicated to produce a 32-bit bus on the MBUS side of the translator. During I/O processor read cycles the data on the MBUS side is valid only during rising MBUS clock edges. The latching capabilities of the 74FCT652 devices are used to sample the data on the clock edge and supply the appropriate 16 bits to the I/O processor. The PAL (U4) takes as input the internal DOUT signal produced by the Controller sub-block and uses this with the I/O processor's read/write signal to derive control signals for the latches and output enables for the data buffers. The PAL equations

are given in the appendix (see MUX\_CONTROLLER). This PAL also produces a latch enable signal which is fed to the Parity Checker sub-block.

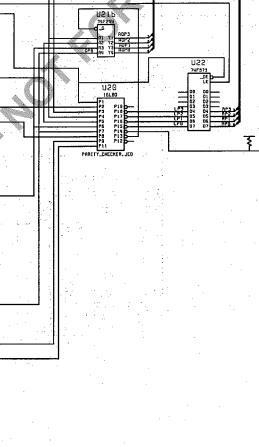

PARITY CHECKER — This optional sub-block performs the function of generating the four MBUS parity bits during all address phases and during data phases of MBUS write cycles. These parity bits are then driven out on the parity lines defined by MBUS. During the data phase of an MBUS read transaction this block samples the parity bits from the MBUS slave and again generates parity based on the data from the slave. It then compares the generated parity with the sampled values from the slave and signals any error to the Controller sub-block. The circuit diagram of this block is shown in Figure 6. To minimise the number of parity generator devices used in the design all the parity generation is done only on the multiplexed MBUS address and data lines. U12, U13, U14 and U15 are transparent latches which are used to sample the data during MBUS read cycle data phases. The outputs of these latches are fed into U16, U17, U18 and U19 parity generator devices to produce the four parity bits. These bits are then buffered through one half of U21 to the MBUS parity lines. The PAL (U20) generates the output enable signal for the U21 buffer to turn it on only during address phases and the data phases of MBUS write cycles. The latch (U22) is used to sample the four parity bits during an MBUS read and then feed these to the PAL. The comparison between the generated parity and the sampled parity is performed in the PAL and an error signal called P.Error is generated for any comparison that fails. This is used in the Controller sub-block to force an early termination of the bus transaction. The PAL equations for U20 are given in the appendix (see PARITY\_CHECKER). In any systems where parity is not considered to be an important feature this Parity Checker sub-block can be omitted from the design and the P.Error input to the Controller sub-block would then be pulled high (to its negated state).

**COMPONENTS LIST**

|      | •        |                |          |         |

|------|----------|----------------|----------|---------|

| U1   | PAL18P8  | U12            |          | 74F373  |

| U2 · | PAL16L8  | U13            |          | 74F373  |

| U3   | PAL16R6  | U14            |          | 74F373  |

| U4   | PAL16L8  | U15            |          | 74F373  |

| U5   | 74F827   | U16            |          | 74F280  |

| U6   | 74F827   | U17            |          | 74F280  |

| U7   | 74F827   | U18            | (A)      | 74F280  |

| U8   | 74FCT652 | U19            |          | 74F280  |

| U9   | 74FCT652 | U20            | <b>.</b> | PAL16L8 |

| U10  | 74FCT652 | U21            | · · · ·  | 74F244  |

| U11  | 74FCT652 | U22            |          | 74F373  |

|      |          |                |          | :       |

|      |          |                |          |         |

|      |          |                |          |         |

|      |          |                |          |         |

|      |          |                |          |         |

|      |          | • <sup>•</sup> |          |         |

| 0    |          |                |          |         |

|      |          |                |          |         |

MOTOROLA 6

EN DESIGN AN449/D IOP\_H\_D (15:0) D U5 Ť \_L Figure 5. Schematic of MUX block C88 589 CA5 SA5 U6 Ť ⊷MB\_RD (31:0) U7 747827 UIO 74HCT85: CBR CBR CBR CBR SBB ŤĘ U21a oout, IOP\_H\_A (31:0) 🗆 -Dlatch\_n UU JELEC dout\_N⊖-IOP\_H\_R₩⊡-P19 P18 P17 P10 P15 P14 P13 P13 YCC MB\_CLKC-IOP\_H\_DS\_NC ARCHIN

U15 74F288

I1. I2 SUM\_E I3

÷

Ē

F

SUM\_0

U17 745288

SUM\_

SUH\_

U18 745268

U19 74F280

SUM 6P0

GP3

GP2

GP 1

- A

-DP.Error

### **APPENDIX**

This appendix contains the full source listings of the PAL equations used in this design. These source listings are shown in PALASM syntax as defined by AMD.

### U1 - 18P8B - BTM\_ARBITER

| TITLE    | BTM ARBITER        |

|----------|--------------------|

| PATTERN  | BTM_A001           |

| REVISION | 1.0                |

| AUTHOR   | Dave McCartney     |

| COMPANY  | MOTOROLA EKB       |

| DATE     | 14th December 1989 |

### CHIP BTM\_ARBITER PAL18P8

;This PAL implements the ARBITER sub-block of the MBIOPBTM module. It monitors the IOP bus until ;it detects a Data address space bus cycle with A31= 1. The PAL then monitors the MBUS ;arbitration signals and generates a Bus Request to the MBUS Arbiter. On receipt of a Bus Grant ;it asserts the BA signal which is reflected in the MBUS BB signal. It then negates ;the Bus Request. The internal Bus Tenure signal TEN is generated for the controller sub-block ;and then the PAL waits for the internal Transaction Complete signal COM.

| ;      |          |       |       | PIN D  | EFINIT  | IONS    | · .        |                                        |             | d. Nor |

|--------|----------|-------|-------|--------|---------|---------|------------|----------------------------------------|-------------|--------|

| ;PINS  | 1        | 2     | 3     | 4      | 5       | 6       | 7          | 8                                      | .9          | 10     |

|        | /RETRY   | A31   | /AS   | FC3    | FC2     | FC1     | FC0        | /BLCK                                  | /AB         | GND    |

| ;PINS  | 11       | 12    | 13    | 14     | .15     | 16      | 17         | 10 4                                   |             |        |

| /1 1NO | /RST     | BG    | /BB   | COM    | /BERR   |         |            | 18                                     | 19          | 20     |

|        | ,101     | . 50  | 100   | COM    | / BERR  | /TEN    | BR         | BA                                     | av C        | VCC    |

| ;PIN 1 | . = /RET | RY =  | MBUS  | System | 1 Statu | s Line  | 2          | MB                                     | ss N (2     | , ·    |

| ;PIN.2 | 2 = A31  | = Add | lress | line A | 31 fro  | m the 3 | IOP        | · · · · · · · · · · · · · · · · · · ·  | HA(3        |        |

| ;PIN 3 | = /AS    | = Add | lress | strobe | from    | the IOH | ? 🔏        | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | HAS         | -      |

| ;PIN 4 | l = FC3  | = Fun | ction | code   | 3 from  | the IC  | DP .       |                                        | H FC        |        |

| ;PIN 5 | = FC2    | = Fun | ction | code   | 2 from  | the     | DP .       | IOF                                    | H FC (      | 2)     |

| ;PIN 6 | 5 = FC1  | = Fun | ction | code   | 1 from  | the IC  | )P         | IOF                                    | H FC (      | 1)     |

| ;PIN 7 | = FC0    | = Fun | ction | code   | 0 from  | the IC  | DP         | IOF                                    | H FC.(      | 0)     |

| ;PIN 8 | = /BLC   | K = B | us lo | ck sig | nal fr  | om the  | IOP        | IOF                                    | HBLC        | КN     |

| ;PIN 9 | = /AB    | = MBU | S Arb | itrati | on Bus  | y Signa | <b>a</b> l | MB                                     | AB N        | · ·    |

|        | .1 = /RS |       |       |        |         | *       |            |                                        | RST N       |        |

| ;PIN 1 | 2 = BG   | = Bus | Gran  | t Sign | al fro  | m MBUS  | Arbit      | er BTM                                 | I BG        |        |

| PIN 1  | 3 = /BB  | = MB  | US Bu | s Busy | Signa   | 1       |            | MB                                     | BB N        |        |

| ;PIN 1 | 4 = COM  | = Tr  | ansac | tion C | omplet  | e Inter | nal S      | ignal –                                | ·· <u> </u> |        |

| ;PIN 1 | .5 = /BE | RR =  | Bus E | rror S | ignal   | from th | ne IOP     | IOP                                    | H_BERI      | RN     |

|        | 6 = /TE  |       |       |        |         |         |            |                                        | · ·         |        |

| ;PIN 1 | 7 = BR   | = Bus | Requ  | est Si | gnal t  | o MBUS  | Arbite     | er BTM                                 | BR          |        |

| ;PIN 1 | 8 = BA : | = Bus | Ackn  | owledg | e to M  | BUS Arb | oiter      | BTM                                    | BA          |        |

|        |          |       |       |        |         |         |            |                                        |             |        |

;Internal Bus Tenure signal /TEN is used to enable main controller sub-block when the MBIOPBTM has ;gained control of the MBUS. Internal Transaction Complete signal /COM is generated by the ;controller sub-block to terminate a bus tenure.

Boolean Equations

EQUATIONS

BR.TRST = VCC BR=A31\*/FC1\*FC0\*AS\*/RETRY\*/TEN\*/COM\*/BA\*/BERR\*/RST

BA.TRST = VCC BA=BG\*/BB\*/RST+BA\*/COM\*/RETRY\*/RST+BA\*BLCK\*/RETRY\*/RST ; Generate Bus Request

; Generate Bus Acknowledge

TEN.TRST = VCC TEN=BA\*/COM\*/RETRY\*/RST

; Generate bus tenure once bus is obtained

SIMULATION

ESIG

### U2 - 16L8B - BTM\_CONTROLLER

| TITLE    | BTM_CONTROLLER     |   |

|----------|--------------------|---|

| PATTERN  | BTM C001           |   |

| REVISION | 1.0                |   |

| AUTHOR   | Dave McCartney     |   |

| COMPANY  | MOTOROLA EKB       |   |

| DATE     | 28th November 1989 | 7 |

|          |                    |   |

CHTP BTM\_CONTROLLER PAL16L8

IND 20 VOC ;This PAL generates the 7-bit MBUS Control bus and the Parity bit for ; this control bus. It generates the control bus signals for three ; distinct phases, namely IDLE, ADDRESS and DATA. The tristate control ; for all the PAL outputs is connected to the internal Bus Tenure signal ;TEN generated by the Arbiter sub-block. The PAL output phase is determined by the state of two internal signals AOUT and DOUT which ; are generated by the BTM Handshake PAL.

| ;     |      | PIN I | DEFINIT | IONS | ,    |     |       | 1. A. |     |     |

|-------|------|-------|---------|------|------|-----|-------|-------------------------------------------|-----|-----|

| PINS  | 1    | 2     | 3       | 4    | 5    | 6   | 7     | 8                                         | . 9 | 10  |

| 1     | AOUT | A0    | A1      | SIZO | SIZ1 | R_W | /DOUT | /RESET                                    | /AS | GND |

| ;PINS | 11   | 12    | 13      | 14   | 15   | 16  | 17    | 18                                        | 19  | 20  |

| 1     | TEN  | CP    | C6      | C5   | C4   | C3  | C2    | C1 -                                      | C0  | vcc |

;PIN 1 = /AOUT = Internal signal indicating Address Phase ;PIN 2 = A0 = Address line A0 from the IOP IOP\_H\_A(0) ;PIN 3 = A1 = Address line A1 from the IOP IOP H\_A(1) ;PIN 4 = SIZO = Size 0 line from the IOP IOP\_H\_SIZ(0) ;PIN 5 = SIZ1 = Size 1 line from the IOP IOP H SIZ(1) ;PIN 6 = R W = Read/write line from the IOP IOP H RW ;PIN 7 = /DOUT = Internal signal showing Data Phase ;PIN 8 = /RESET = MBUS Reset Signal MB RST N ;PIN 9 = /AS = Address Strobe from the IOP IOP H AS N ;PIN 11 = /TEN = Bus Tenure Internal Signal ;PIN 12 = CP = Parity bit for MBUS Control Signals MB CP PIN 13 = C6 = MBUS Control Signal 6 MB C(6) ;PIN 14 = C5 = MBUS Control Signal 5 MB C(5) ;PIN 15 = C4 = MBUS Control Signal 4 MB C(4);PIN 16 = C3 = MBUS Control Signal 3 MB C(3) ;PIN 17 = C2 = MBUS Control Signal 2 MB\_C(2) ;PIN 18 = C1 = MBUS Control Signal 1 MB C(1) ;PIN 19 = C0 = MBUS Control Signal 0 MB C(0)

;The internal signals AOUT and DOUT are generated by the BTM Handshake ;PAL and the internal TEN signal comes from the BTM\_Arbiter PAL

Boolean Equations

#### EQUATIONS

| CO.TRST = TEN                         | ;Enable output during MBUS Tenure        |

|---------------------------------------|------------------------------------------|

| C0 = AOUT*/DOUT*/RESET                | ;Only assert during Address Phase        |

| C1.TRST = TEN                         | ;Enable output during MBUS Tenure        |

| C1 = /AOUT*DOUT*/RESET                | ;Shows LDT during Data Phase             |

| C2,TRST = TEN                         | ;Enable output during MBUS Tenure        |

| C2 <sup>**</sup> = /AOUT*/DOUT*/RESET | Assert as Read during Idle Phase         |

| +AOUT*/DOUT*R_W*/RESET                | Assert during Address Phase for Rea      |

| +/AOUT*DOUT*R_W*/RESET                | ;Assert during Data Phase for Reads      |

|                                       |                                          |

| C3.TRST = TEN                         | ;Enable output during MB                 |

| C3 = /AOUT*DOUT*AS*/RESET*/A0         | */A1*SIZ0*/SIZ1 ;Byte transfer Data Phas |

+/AOUT\*DOUT\*AS\*/RESET\*/A0\*/A1\*/SIZ0\*SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*/A0\*/A1\*SIZ0\*SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*/A0\*/A1\*/SIZ0\*/SIZ1

during MBUS Tenure r Data Phase ;Word transfer Data Phase ;3 Byte transfer Data Phase ;Long Word transfer Data Phase

se for Reads

C4.TRST = TEN

- C4 = /AOUT\*DOUT\*AS\*/RESET\*A0\*/A1\*SIZ0\*/SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*/A1\*/SIZ0\*SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*/A1\*SIZ0\*SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*/A1\*/SIZ0\*/SIZ1

- C5.TRST = TEN

- C5 = AOUT\*/DOUT\*AS\*/RESET

+/AOUT\*DOUT\*AS\*/RESET\*/A0\*A1\*SIZ0\*/SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*/A0\*A1\*/SIZ0\*SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*/A0\*A1\*SIZ0\*SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*/A0\*A1\*/SIZ0\*/SIZ1

C6.TRST = TEN

C6 = /AOUT\*DOUT\*AS\*/RESET\*A0\*A1\*SIZ0\*/SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*A1\*/SIZ0\*SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*A1\*SIZ0\*SIZ1 +/AOUT\*DOUT\*AS\*/RESET\*A1\*/SIZO\*/SIZ1

CP.TRST = TEN

- /CP = AOUT\*/DOUT\*/R W+/AOUT\*DOUT\*/R W\*SIZO\*/SIZ1 +/AOUT\*DOUT\*R\_W\*/SIZ0\*SIZ1

;Enable output during MBUS Tenure ;Byte transfer Data Phase ;Word transfer Data Phase ;3 Byte transfer Data Phase ;Long Word transfer Data Phase

;Enable output during MBUS Tenure ;Global flag Address Phase ;Byte transfer Data Phase ;Word transfer Data Phase ;3 Byte transfer Data Phase ;Long Word transfer Data Phase

Enable output during MBUS Tenure ;Byte transfer Data Phase ;Word transfer Data Phase ;3 Byte transfer Data Phase ;Long Word transfer Data Phase

JE-SIGN

;Enable output during MBUS Tenure ;address Phase Write a i ad Wo xead 3 ] a Read Lop ;data Phase Write Byte data Phase Read Word ;data Phase Read 3 Byte ;data Phase Read Long Word

### U3 - 16R6D - BTM HANDSHAKE

| TITLE    | BTM_HANDSHAKE      |

|----------|--------------------|

| PATTERN  | BTM_H001           |

| REVISION | 1.0                |

| AUTHOR   | Dave McCartney     |

| COMPANY  | MOTOROLA EKB       |

| DATE     | 12th December 1989 |

CHIP

#### BTM HANDSHAKE

;This PAL generates the handshake signals to the IOP to terminate the ; IOP bus cycles. These include DSACK1 (16-bit port size), BERR and HALT. ; It also generates the AOUT and DOUT signals to signify what state the ;MBUS is in and it generates a transaction complete COM signal which ; is used by the Arbiter to terminate bus tenure. The PAL operates as ;a state machine which is clocked by the main MBUS system clock and ; implements 3 distinct phases for MBUS :-

PAL16R6

| IDLE PHASE    | AOUT negated and DOUT negated  |

|---------------|--------------------------------|

| ADDRESS PHASE | AOUT asserted and DOUT negated |

| DATA PHASE    | AOUT negated and DOUT asserted |

ALM DE SICH ; On gaining MBUS tenure the state machine shows an idle phase until the first rising clock edge when it moves into address phase. It will stay ; in this phase until an O.K. status is seen on the MBUS system status lines. The machine then moves into Data phase and again waits for an O.K. before ; returning to Idle phase where it waits until MBUS tenure is relinquished.

#### PIN DEFINITIONS

|    | ; PINS  | 5 1           | 2       | 3         | - 4       | 5       | 6        | 7       | 8         | 9       | 10    |      |

|----|---------|---------------|---------|-----------|-----------|---------|----------|---------|-----------|---------|-------|------|

|    |         | CLOCK         | /ss3    | /SS2      | /SS1      | /SSO    | /PE      | /RESE   | T /AS     | /TEN    | GNE   | )    |

| ۰. |         |               |         |           |           |         |          |         | - A.      |         |       |      |

|    | PINS    | 5 11          | 12      | 13        | 14        | 15      | 16       | s 17    | 18        | 1       | 9     | 20   |

|    | /       | /0E           | СОМ     | /HALT     | /AOUT     | /DOUT   |          | 89°     | /DSACK10  |         |       | VCC  |

|    | · · ·   | , 01          | 0011    | / 11110 1 | , 11001   | ,       |          |         | ) DOMORIC | , JOSH  | ONT   | VCC  |

|    | • D T N | 1 - CT O      | от – м  |           |           | -1-     | . Anna S |         |           | WD OT W |       |      |

|    |         | 1 = CLO       |         |           |           | 38      |          |         |           | MB_CLK  |       |      |

|    |         | 2 = /SS       |         |           |           |         |          |         | 1         | MB_SS_  |       |      |

|    |         | 3 = /SS       |         |           |           |         |          |         | · .       | MB_SS_  | N(2)  |      |

|    | ;PIN    | 4 = /SS       | 1 = MB  | JS Syste  | em Stati  | us line | 🖗 l (Wa  | uit)    |           | MB_SS_  | N(1)  |      |

|    | ;PIN    | 5 = /SS       | 0 = MBI | JS Syste  | em Stati  | us line | 9 0 (EC  | D)      |           | MB SS   | N(O)  |      |

|    | ;PIN    | 6 = /PE       | = Inte  | ernal Pa  | arity E   | rror Si | gnal     |         |           |         |       |      |

|    | ;PIN    | 7 = /RE       | SET = 1 | BUS Res   | set Sia   | nal     | -        |         |           | MB RST  | N     |      |

|    |         | 8 = /DS       |         |           |           |         | TOP      |         |           | IOP H   | _     |      |

|    |         | 9 = /TE       |         |           |           |         |          |         |           |         |       |      |

|    |         | 11 = /01      |         |           |           |         |          |         |           |         |       |      |

|    |         |               |         |           |           |         |          |         | ч.        |         |       |      |

|    |         | 12 = COI      |         |           |           |         |          | e Signa | .т.       |         |       |      |

|    |         | $13 = /H_{2}$ |         |           |           |         |          |         |           | IOP_H_  | HALT_ | _N · |

| 7  | PIN     | 14 = /A       | out 😑 🕻 | Interna:  | l Signa   | l showi | .ng Add  | lress p | hase      |         |       |      |

|    | PIN     | 15 = /D0      | : = TUC | Interna.  | l Signa   | l showi | ng Dat   | a phas  | e         |         |       |      |

|    | ;PIN    | 16 = /B       | ERR = 1 | BERR har  | idshake   | to the  | IOP      | _       |           | IOP H   | BERR  | N    |

|    |         | 18 = /D       | _ Y22.  |           |           |         |          | 1 to I  | OP        | (Not C  | -     | -    |

|    |         | 19 = /D       |         |           |           |         |          |         |           | IOP H   |       |      |

|    | ,       | - June 1      | b       |           | - manyasi |         | , TOT (  | abes p  |           |         |       | ·    |

;The internal PE signal is generated by the parity checker block and the internal bus tenure signal TEN is generated by the Arbiter block. The transaction complete signal COM is an output which is used by the Arbiter ; to terminate the MBUS tenure. The AOUT and DOUT signals are used to ;produce to MBUS control signals C(6:0) and are used by the multiplexer ; block to control the information placed on the MBUS AD(31:0) lines.

For a normal bus cycle this PAL will generate a normal DSACK handshake ;to the IOP. A cycle which results in an error on the MBUS system status ; lines gives a BERR handshake to the IOP. A retry cycle forces a retry ; handshake by the assertion of HALT and BERR to the IOP, and MBUS tenure ; is terminated early. A detected Parity error during the data phase of ;an MBUS read cycle results in a Late Bus Error Handshake to the IOP ;following the normal DSACK termination.

Boolean Equations

|   | EQUATIONS                                                                                  |                                                                                                                                                |

|---|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   | HALT:= SS2*AS*/RESET<br>+HALT*AS*/RESET                                                    | Assert if RETRY is valid<br>HOLD till AS negates                                                                                               |

|   | DOUT:= AOUT*/DOUT*AS*/RESET*TEN<br>*/SS1*/SS2*/SS3*/PE<br>+DOUT*AS*SS1*/RESET*TEN          | ;Change to Data Phase if<br>;no error detected<br>;Hold if WAIT detected                                                                       |

|   | AOUT:= /AOUT*/DOUT*AS*/RESET*TEN*/]<br>*/SS1*/SS2*/SS3*/PE<br>+AOUT*AS*SS1*/RESET*TEN      | DSACK1 ;Enter Address Phase<br>;if no error detected<br>;Hold if WAIT detected                                                                 |

|   | COM = /AS*/RESET*TEN<br>+SS3*/RESET*TEN<br>+SS2*/RESET*TEN                                 | Assert when IOP AS negates to terminate tenure<br>Assert if ERROR asserted to terminate tenure<br>Assert if RETRY asserted to terminate tenure |

| • | BERR := SS3*AS*/RESET*TEN<br>+SS2*AS*/RESET<br>+PE*AS*DSACK1*/RESET*TEN<br>+BERR*AS*/RESET | Assert if ERROR detected<br>Assert if RETRY detected<br>Assert if Parity Error detected<br>Hold till AS negates                                |

|   | DSACK1 = DSACK1C*AS*/BERR                                                                  | ;Assert DSACK after clock edge<br>;Negate when AS negates<br>;or BERR asserts                                                                  |

|   | DSACK1C :=/AOUT*DOUT*AS*/RESET*TEN<br>*/SS3*/SS2*/SS1<br>+DSACK1*AS*/RESET*TEN             | ;Assert at end of Data Phase<br>;if no errors or wait asserted<br>;Hold till AS negates                                                        |

|   | SIMULATION                                                                                 |                                                                                                                                                |

|   |                                                                                            |                                                                                                                                                |

|   |                                                                                            |                                                                                                                                                |

|   |                                                                                            |                                                                                                                                                |

|   | 65                                                                                         |                                                                                                                                                |

|   |                                                                                            |                                                                                                                                                |

|   |                                                                                            |                                                                                                                                                |

|   |                                                                                            |                                                                                                                                                |

|   |                                                                                            |                                                                                                                                                |

|   |                                                                                            |                                                                                                                                                |

|   |                                                                                            |                                                                                                                                                |

MOTOROLA

13

### **U4 - 16L8E - MUX CONTROLLER**

| TITLE    | MUX_CONTROLLER     |

|----------|--------------------|

| PATTERN  | MUX_C001           |

| REVISION | 1.0                |

| AUTHOR   | Dave McCartney     |

| COMPANY  | MOTOROLA EKB       |

| DATE     | 18th December 1989 |

|          |                    |

#### MUX CONTROLLER CHIP PAL16L8

J JND 20 VCC ;This PAL generates the control signals required to operate 74FCT652 ; bus transceivers during the data phase of every MBUS cycle when the ;module has been granted MBUS tenure. These control signals consist ; of output enables for data flow in either direction, a signal which ;selects either real time or stored data and a signal which controls the data latches inside the 75FCT652 devices. In addition a second ;latch control signal is generated which is used by the Parity Checker ;block to hold data coming from an MBUS slave.

| PTN | DEFINITIONS |

|-----|-------------|

|     |             |

| ;PINS | 1  | 2     | 3     | 4     | 5     | 6   | . 7    | 8   | 9  | 10  |

|-------|----|-------|-------|-------|-------|-----|--------|-----|----|-----|

|       | A1 | /DOUT | R_W   | CLK   | /DS   | NC  | NC     | NC  | NC | GND |

|       |    |       |       |       | 14.14 |     |        | · · |    | · 4 |

| ;PINS | 11 | 12    | 13    | 14    | 15    | 16  | 17     | 18  | 19 | 20  |

|       | NC | NC    | /GBA0 | /GBA1 | GAB   | SBA | /LATCH | CBA | NC | VCC |

;PIN 1 = A1 = Address line A1 from the IOP IOP H\_A(1) ;PIN 2 = /DOUT = Internal Signal Showing Data phase ;PIN 3 = R W = Read/Write line from the IOP IOP H\_RW. ;PIN 4 = CLK = MBUS System Clock MB CLK ;PIN 5 = /DS = Data Strobe from the IOP IOP\_H\_DS\_N ;PIN 13 = /GBA0 = Transceiver Enable B to A direction ;PIN 14 = /GBA1 = Transceiver Enable B to A direction ;PIN 15 = GAB = Transceiver Enable A to B direction ;PIN 16 = SBA = Real time or Stored data Select for B to A ;PIN 17 = /LATCH = Latch signal used by Parity Checker ;PIN 18 = CBA = Use to latch data into internal latches

;All of the above internal signals generated by the PAL are fed directly to the appropriate control inputs on the 74FCT652 devices.

Boolean Equations

EQUATIONS

GBA0.TRST = VCC GBA0 = DOUT\*R W\*A1\*/GBA1\*/GAB +GBA0\*DS

;Output always enabled ;Assert for A1=1 for a read ;Hold till DS negates

;Output always enabled

;Output always enabled

:Output always enabled

;Output always enabled

;Hold till DS negates

;Negate during read and low clock

;Asserted at end of data phase

;Real time during read and low clock

;Assert for writes

GBA1.TRST = VCC GBA1 = DOUT\*R W\*/A1\*/GBA0\*/GAB ;Output always enabled ;Assert for A1=0 for a read +GBA1\*DS ;Hold till DS negates

GAB.TRST = VCC GAB = DOUT\*/R\_W\*/GBA0\*/GBA1

CBA.TRST = VCC /CBA = DOUT\*R W\*/CLK

SBA.TRST = VCC

/SBA = DOUT\*R\_W\*/CLK

LATCH.TRST = VCC LATCH = DOUT\*R W\*CLK +LATCH\*CBA\*DS

SIMULATION

### U20 - 16L8D - PARITY\_CHECKER

| TITLE    | PARITY_CHECKER    |   |

|----------|-------------------|---|

| PATTERN  | PARITY P001       | , |

| REVISION | 1.0               |   |

| AUTHOR   | Dave McCartney    |   |

| COMPANY  | MOTOROLA EKB      |   |

| DATE     | 16th January 1990 |   |

| AUTHOR<br>COMPANY<br>DATE                                          | Dave McCartney<br>MOTOROLA EKB<br>16th January 1990                                                                                                                  |                                                                        |             |           |     |                           |      |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------------|-----------|-----|---------------------------|------|

| CHIP                                                               | PARITY_CONTRL                                                                                                                                                        | PAL16L8                                                                |             |           |     |                           |      |

| ;generator<br>;a parity                                            | is used to compare the swith the four bits error if they do not phase of read cycles                                                                                 | read from an MBU<br>agree. This chec                                   | S slave and | d generat | es  |                           | S) - |

| 7                                                                  | PIN DEFINITION                                                                                                                                                       |                                                                        |             |           |     |                           |      |

| ;PINS 1                                                            | 2 3 4                                                                                                                                                                | 5 6 7                                                                  | . 8         | 9         | 10  | . (N                      |      |

| /TEN                                                               | /WAIT R_W GP3                                                                                                                                                        | GP2 GP1 GP                                                             | 0 LATCH     | /AOUT     | GND |                           |      |

| PINS 11                                                            | 12 13 14                                                                                                                                                             | 15 16 17                                                               | 18          | 19        | 20  | Contraction of the second |      |

| /DOUT                                                              | NC /OC /PE                                                                                                                                                           | LPO LP1 LP2                                                            |             | NC        | vcc |                           |      |

| ;PIN 2 = /<br>;PIN 3 = R<br>;PIN 4 = G<br>;PIN 5 = G<br>;PIN 6 = G | TEN = Bus Tenure Int<br>WAIT = MBUS System S<br>_W = Read/Write line<br>P3 = Generated parit<br>P2 = Generated parit<br>P1 = Generated parit<br>P0 = Generated parit | tatus line 1 MB_S<br>from the IOP IOP<br>y bit 3<br>y bit 2<br>y bit 1 | _           | C C C     | st. |                           |      |

| •                                                                  | ATCH = Internal late                                                                                                                                                 | -                                                                      |             |           |     |                           |      |

|                                                                    | AOUT = Internal sign                                                                                                                                                 |                                                                        |             |           |     |                           |      |

|                                                                    | <pre>/DOUT = Internal sig<br/>/OC = Output Control</pre>                                                                                                             |                                                                        |             |           |     |                           | •    |

|                                                                    | /PE = Internal Parit                                                                                                                                                 |                                                                        | y Dies      |           | 1   |                           |      |

| •                                                                  | LP0 = Latched read p                                                                                                                                                 | - <i>1</i>                                                             |             |           |     |                           |      |

|                                                                    | LP1 = Latched read p                                                                                                                                                 |                                                                        |             |           |     |                           |      |

|                                                                    | LP2 = Latched read p                                                                                                                                                 | - SPACEStineStelle                                                     |             |           |     |                           |      |

|                                                                    | LP3 = Latched read p                                                                                                                                                 |                                                                        |             |           |     |                           |      |

;The internal output control signal OC is used to control a four-bit ;tri-state buffer which allows the generated parity bits to be driven ;out on the ADP bus during the data phase of write cycles. The internal ;LATCH control signal is the signal used to latch the data and parity bits ;during read cycles and is used by the PAL to enable the parity checking. ;For a fault during parity checking the PAL generates the active low ;Parity Error signal (/PE) which is detected by the controller block and ; a bus error is returned to the IOP.

Boolean Equations

EQUATIONS

;

OC.TRST = VCC OC = TEN\*/R W+TEN\*R W\*AOUT\*/DOUT

;Output always enabled ;Valid for all write cycles ;or address phase of reads

PE.TRST = VCC ;Output always enabled PE = GP0\*/LP0\*R\_W\*/WAIT\*/OC\*/LATCH ;Is GP0=LP0 during read +GP1\*/LP1\*R\_W\*/WAIT\*/OC\*/LATCH;or GP1=LP1 +GP2\*/LP2\*R W\*/WAIT\*/OC\*/LATCH; or GP2=LP2 +GP3\*/LP3\*R\_W\*/WAIT\*/OC\*/LATCH;or GP3=LP3

SIMULATION

resthering of the second Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and 🖗 are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Literature Distribution Centres:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036. EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England. ASIA PACIFIC: Motorola Semiconductors (H.K.) Ltd.; Silicon Harbour Center, No. 2, Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

### A) MOTOROLA

Printed in Great Britain by Tavistock Press (Bedford) Ltd. 4500 9/91 PO.2097