DL413/D

# Radio, RF and Video Applications

DL413/D

# Radio, RF and Video Applications

This manual is a compilation of Application Notes and other applications literature concerned with Motorola's semiconductors for Radio, RF and Video applications. The documents were published originally by Motorola under the references shown in the Contents list. Specific data on all of Motorola products, including the devices mentioned in this manual, can be obtained through Motorola's Franchised Distributors and Sales Offices.

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others. Motorola products are not designed, intended or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and @ are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Includes literature available at May 1991(AD66) All trademarks recognized.

© MOTOROLA INC. All Rights Reserved First Edition 1991 — DL413/D Printed in Great Britain by Tavistock Press (Bedford) Ltd. 5000 7/91

### Contents

#### page

| Device Cros   | s Reference                                                                                                            | 7   |

|---------------|------------------------------------------------------------------------------------------------------------------------|-----|

| Abstracts of  | Applications Documents                                                                                                 | 11  |

| Applications  | 3 Documents                                                                                                            |     |

| AN433         | TV On-Screen Display Using the MC68HC05T1                                                                              |     |

| AN438         | 300W, 88-108MHz Amplifier Using the TP1940 MOSFETs Push-Pull Transistor                                                |     |

| AN531         | MC1596 Balanced Modulator                                                                                              | 41  |

| AN535         | Phase-Locked Loop Design Fundamentals                                                                                  |     |

| AN545A        | Television Video IF Amplifier Using Integrated Circuits                                                                | 67  |

| AN556         | Interconnection Techniques for Motorola's MECL 10,000 Series Emitter Coupled<br>Logic                                  |     |

| AN721         | Impedance Matching Networks Applied to RF Power Transistors                                                            | 103 |

| AN761         | Video Amplifier Design: Know Your Picture Tube Requirements                                                            | 121 |

| AN779         | Low-Distortion 1.6 to 30MHz SSB Driver Designs                                                                         |     |

| AN791         | A Simplified Approach to VHF Power Amplifier Design                                                                    |     |

| AN827         | The Technique of Direct Programming by Using a Two-Modulus Prescaler                                                   |     |

| AN829         | Application of the MC1374 TV Modulator                                                                                 |     |

| AN847         | Tuning Diode Design Techniques                                                                                         |     |

| AN860         | Power MOSFETs versus Bipolar Transistors                                                                               |     |

| AN878         | VHF MOS Power Applications                                                                                             |     |

| AN879         | Monomax: Application of the MC13001 Monochrome Television Integrated Circuit                                           |     |

| AN921         | Horizontal APC/AFC Loops                                                                                               |     |

| AN923         | 800MHz Test Fixture Design                                                                                             |     |

| AN932         | Application of the MC1377 Colour Encoder                                                                               |     |

| AN955         | A Cost Effective VHF Amplifier for Land Mobile Radios                                                                  |     |

| AN969         | Operation of the MC145159 PLL Frequency Synthesizer with Analog Phase Detector                                         |     |

| AN980         | VHF Narrowband FM Receiver Design Using the MC3362 and the MC3363 Dual Conversion Receivers                            | 273 |

| AN1019        | Decoding Using the TDA3330, with Emphasis on Cable In/Cable Out Operation                                              |     |

| AN1040        | Mounting Considerations for Power Semiconductors                                                                       |     |

| AN1041        | Mounting Procedures for Very High Power RF Transistors                                                                 |     |

| AN1044        | The MC1378 — A Monolithic Composite Video Synchronizer                                                                 |     |

| AN1051        | Transmission Line Effects in PCB Applications                                                                          |     |

| AN1076        | Speeding up Horizontal Outputs                                                                                         |     |

| AN1080        | External-Sync Power Supply with Universal Input Voltage Range for Monitors                                             | 403 |

| AN1103        | Using the CR3424 for High Resolution CRT Applications                                                                  |     |

| AN1106        | Considerations in Using the MHW801 and MHW851 Series RF Power Modules                                                  |     |

| AN1107        | Understanding RF Data Sheet Parameters                                                                                 |     |

| ANE416        | MC68HC05B4 Radio Synthesizer                                                                                           |     |

| ANHK02        | Low Power FM Transmitter System MC2831A                                                                                |     |

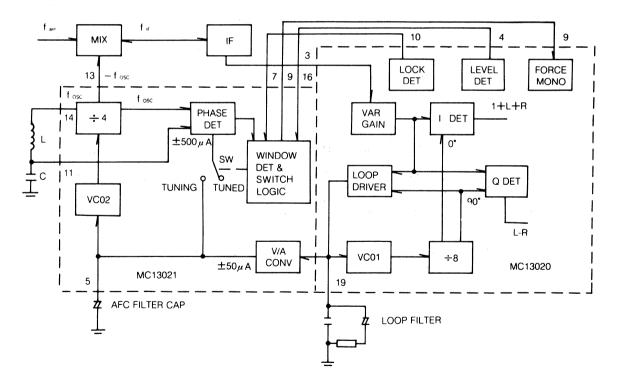

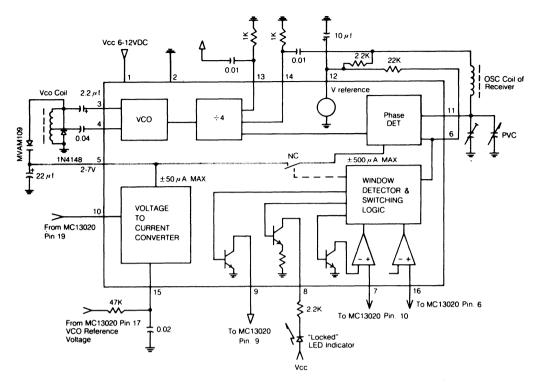

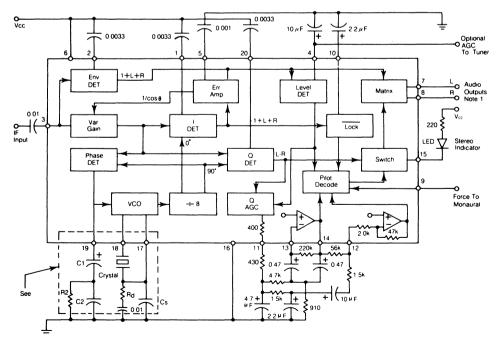

| ANHK07        | A High Performance Manual-Tuned Receiver for Automotive Application Using<br>Motorola ICs MC13021, MC13020 and MC13041 |     |

| EB104         | Get 600 Watts RF from Four Power FETs                                                                                  |     |

| EB109         | Low Cost UHF Device Gives Broadband Performance at 3.0 Watts Output                                                    | 505 |

| Additional Ir | formation                                                                                                              | 511 |

# Device Cross Reference

### **Device Cross Reference**

## This quick-reference list indicates where specific components are featured in applications documents reproduced in this Manual.

| 2N5401     | AN1076 |

|------------|--------|

| BF393      | AN761  |

| CR3424     | AN1103 |

| MC68HC05B4 | ANE416 |

| MC68HC05T1 | AN433  |

| MC1323     | AN761  |

| MC1324     | AN761  |

| MC1330     | AN545A |

| MC1350     | AN545A |

| MC1352     | AN545A |

| MC1374     | AN829  |

| MC1377     | AN932  |

|            | AN1044 |

| MC1378     | AN1044 |

| MC1396     | AN761  |

| MC1596     | AN531  |

| MC2831A    | ANHK02 |

| MC3362     | AN980  |

| MC3363     | AN980  |

| MC3423     | AN1080 |

| MC13001    | AN879  |

| MC13020    | ANHK07 |

| MC13021    | ANHK07 |

| MC13041    | ANHK07 |

| MC145026   | ANHK02 |

| MC145028   | ANHK02 |

| MC145157   | ANE416 |

|            |        |

| MC145159  | AN969  |

|-----------|--------|

| MC145160  | ANHK02 |

| MC145412  | ANHK02 |

| MHW801    | AN1106 |

| MHW851    | AN1106 |

| MJE18004  | AN1080 |

| MOC8102   | AN1080 |

| MPSG1000  | AN1076 |

| MRF50     | EB104  |

| MRF141G   | AN1041 |

| MRF151G   | AN1041 |

| MRF153    | AN1041 |

| MRF154    | AN1041 |

| MRF155    | AN1041 |

| MRF175G   | AN1041 |

| MRF176G   | AN1041 |

| MRF237    | AN955  |

| MRF430    | AN1041 |

| MRF630    | EB109  |

| MRF1946A  | AN955  |

| MTP4N90   | AN1080 |

| MTP3055EL | AN1076 |

| TDA3301   | AN1044 |

| TDA3330   | AN1019 |

| TP1940    | AN438  |

| UC3842A   | AN1080 |

| UC3843A   | AN1080 |

|           |        |

# Abstracts of Applications Documents

.

.

### **Abstracts**

#### AN433 TV On-Screen Display Using the MC68HC05T1

The T-series devices in the M68HC05 MCU Family provide a convenient and cost-effective means of adding On Screen Display capability (OSD) to TVs and VCRs. The MC68HC05T1 is at the centre of the T-series price/ performance range, and is used in this example. Full software listings are provided for a ROM-efficient implementation of an 8-row by 16-character display, including Programme Change, Channel Mode, Automatic Search, Analogues and Channel Name.

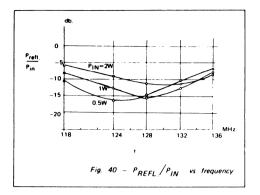

#### AN438 300W, 88–108MHz Amplifier Using the TP1940 MOSFETs Push-Pull Transistor

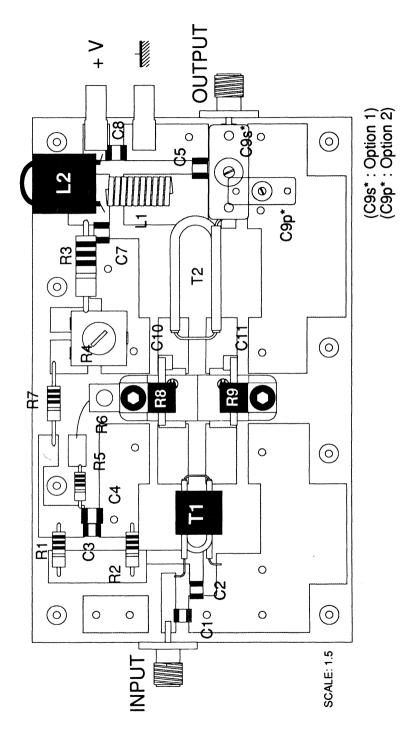

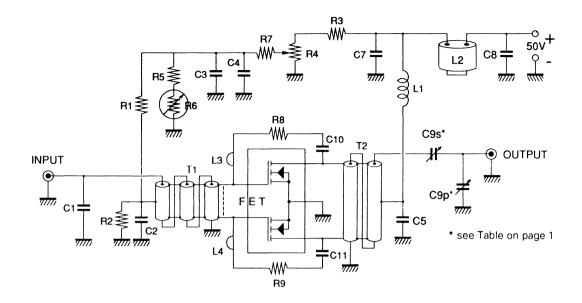

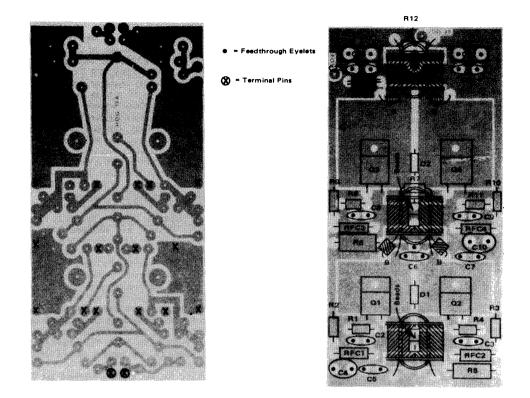

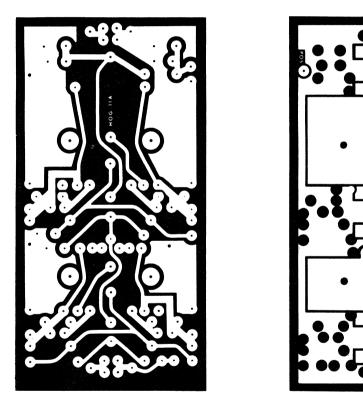

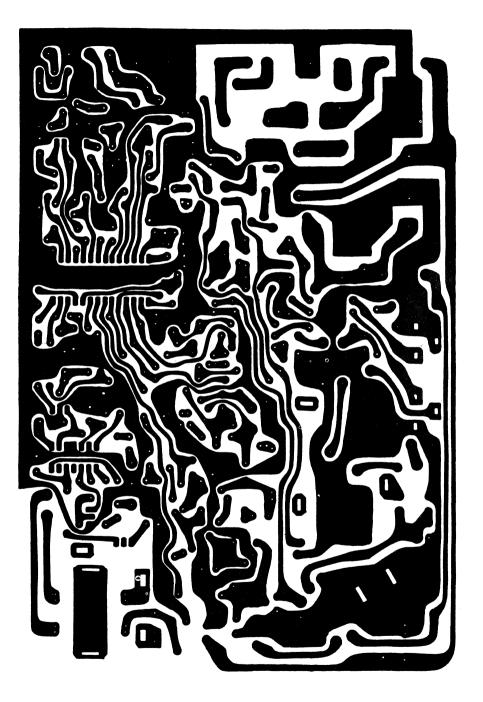

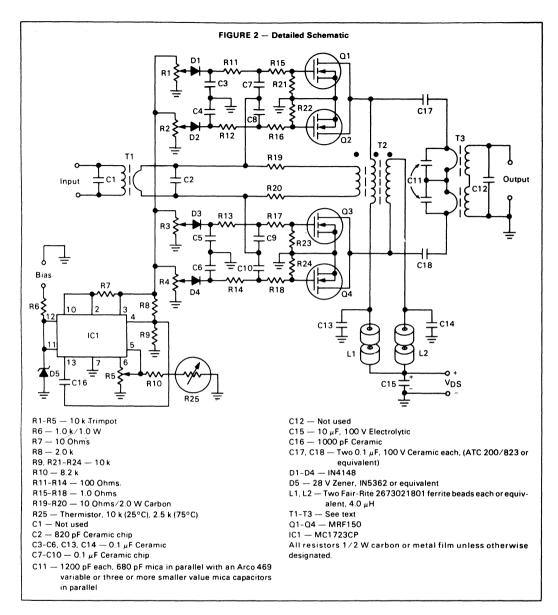

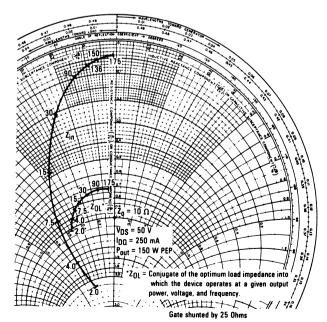

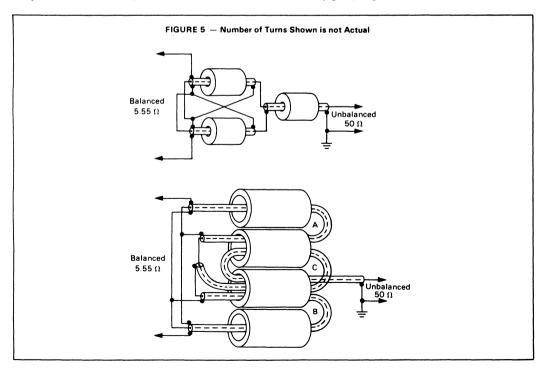

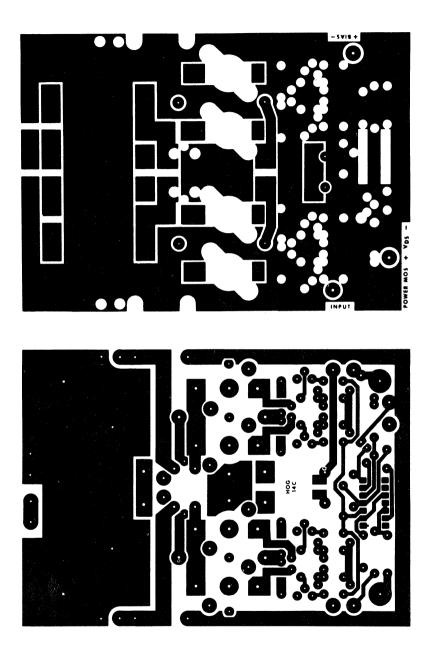

Provides the design of an efficient 300W amplifier with high power gain, compact physical layout and operation on a 50V power supply. It uses the TP1940, a high power, high gain, broadband push-pull Power MOSFET with low Reverse Transfer Capacitance. Includes circuit, parts list, PCB attwork and component layout.

#### AN531 MC1596 Balanced Modulator

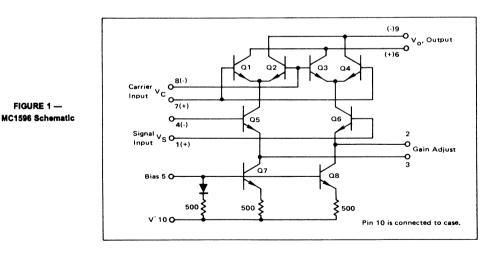

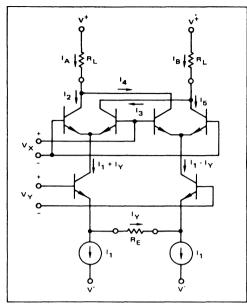

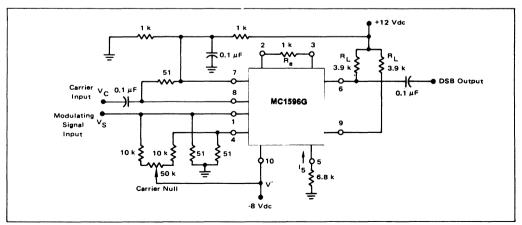

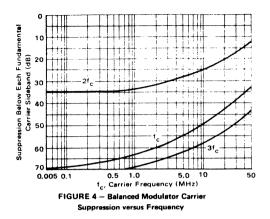

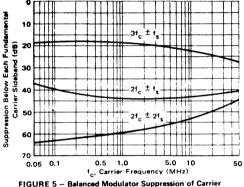

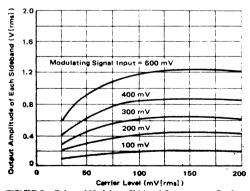

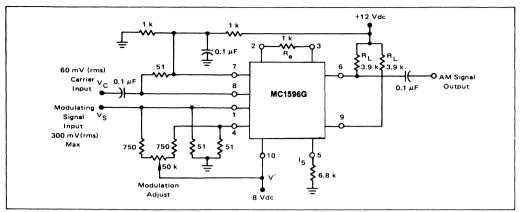

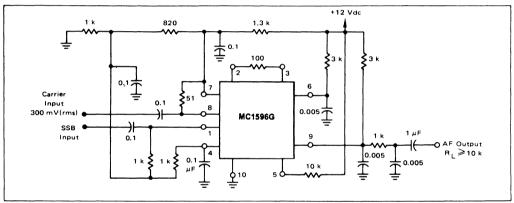

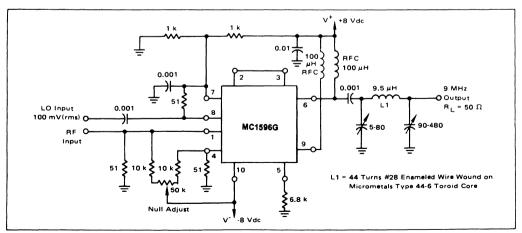

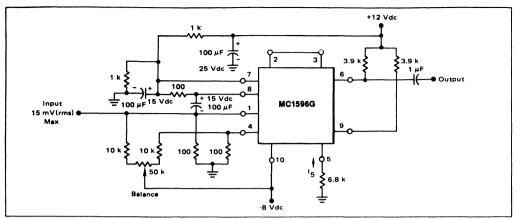

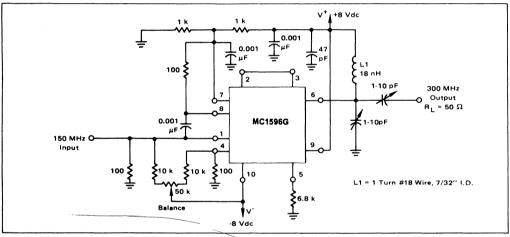

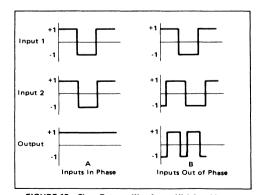

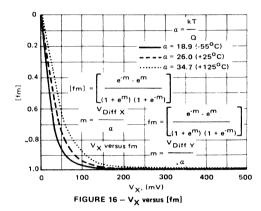

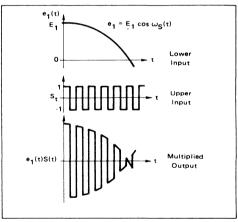

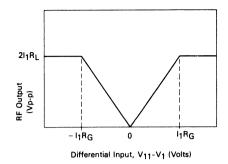

The MC1596 Monolithic Balanced Modulator is a versatile HF communications building block. It functions as a broadband, double-sideband suppressed-carrier balanced modulator without the need for transformers or tuned circuits. This article describes device operation and biasing, and gives circuit details for typical modulator/ demodulator applications in AM, SSB and suppressedcarrier AM. Additional uses as an SSB Product Detector, AM Modulator/Detector, Mixer, Frequency Doubler, Phase Detector and others are also illustrated. An appendix gives detailed AC and DC analysis.

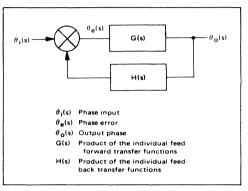

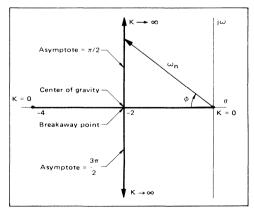

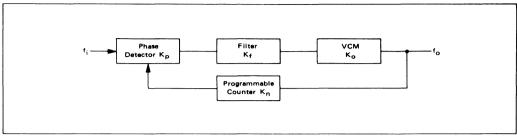

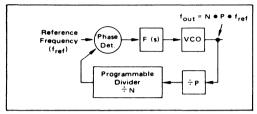

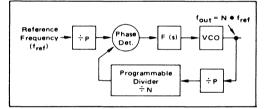

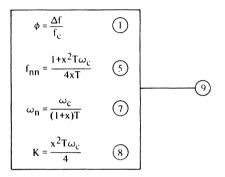

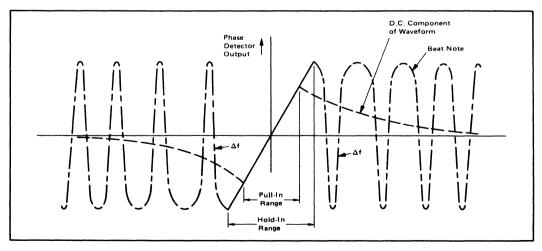

#### AN535 Phase-Locked Loop Design Fundamentals

The fundamental design concepts for phase-locked loops implemented with integrated circuits are outlined. The necessary equations required to evaluate the basic loop performance are given in conjunction with a brief design example.

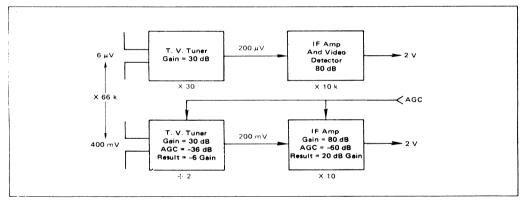

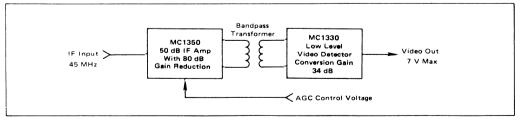

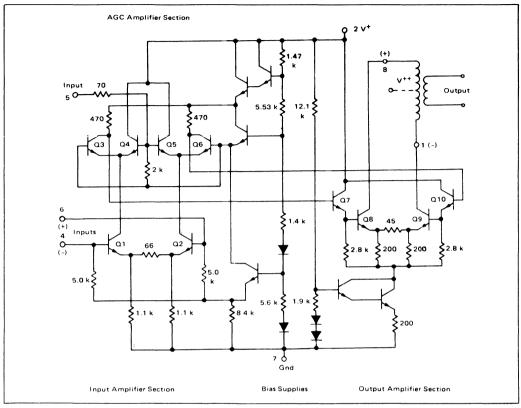

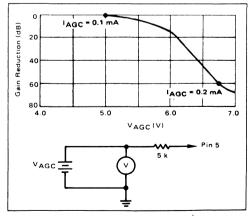

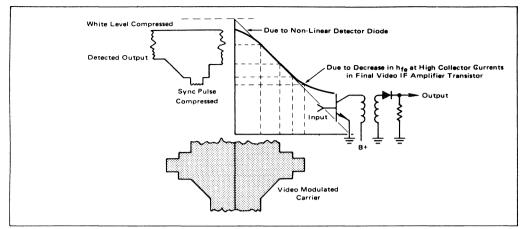

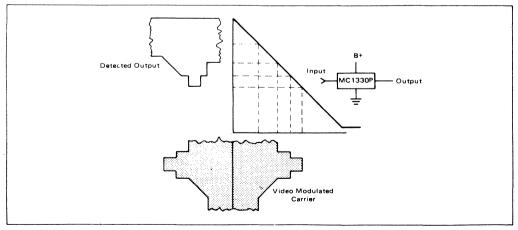

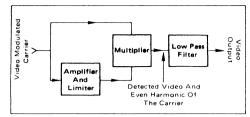

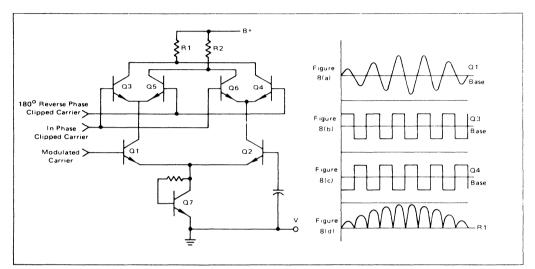

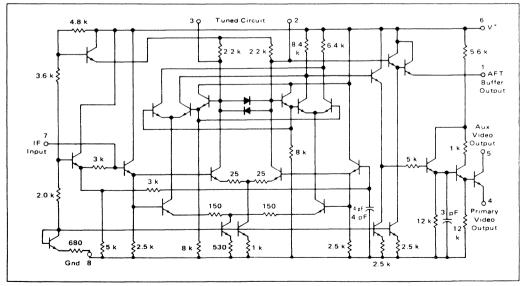

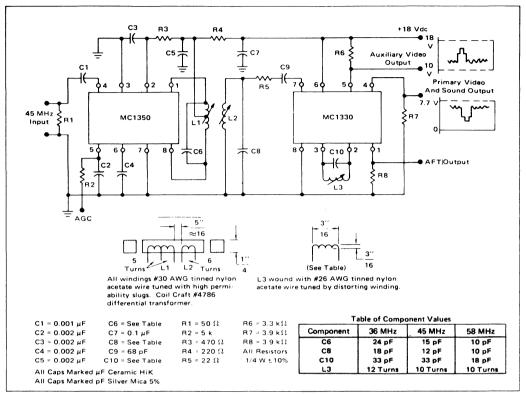

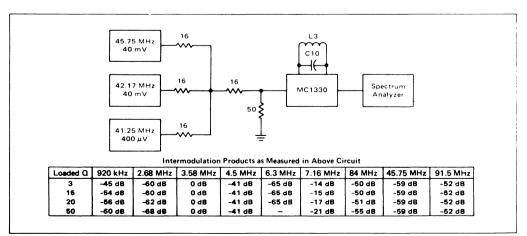

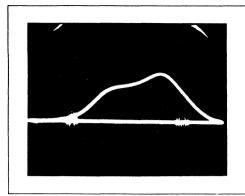

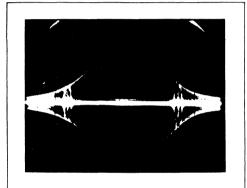

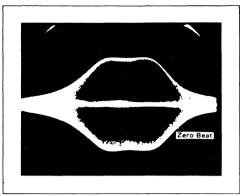

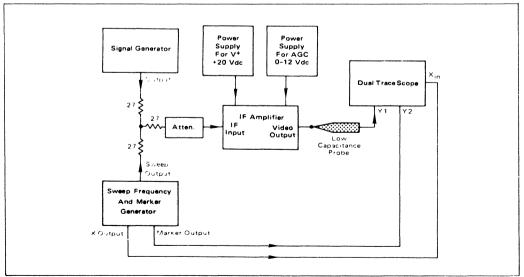

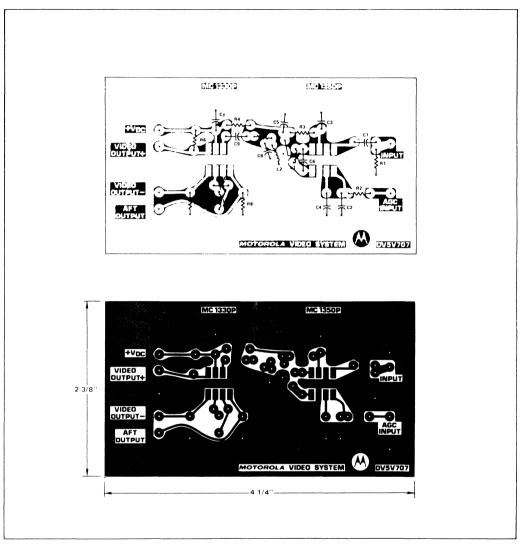

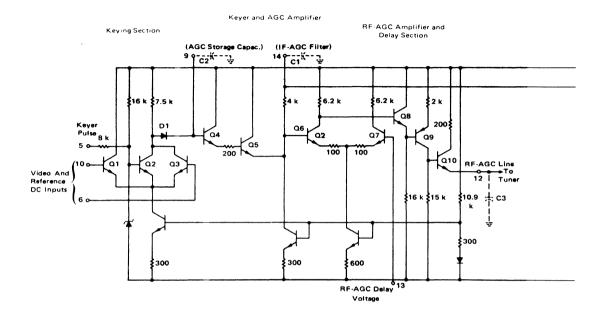

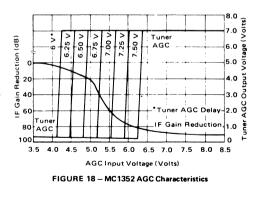

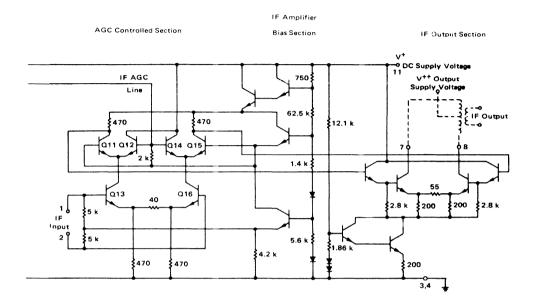

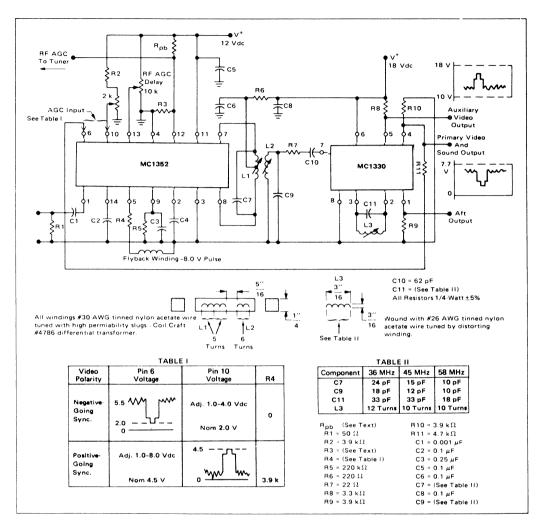

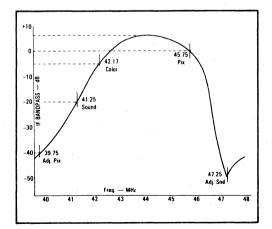

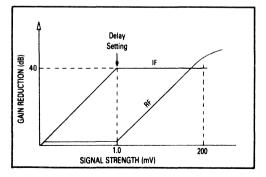

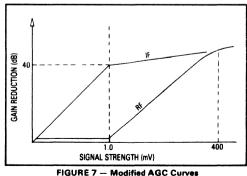

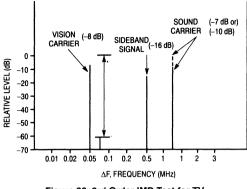

#### AN545A Television Video IF Amplifier Using Integrated Circuits

This application note considers the requirements of the video IF amplifier section of a television receiver, and gives working circuit schematics using integrated circuits which have been designed specially for consumer oriented products. The integrated circuits used are the MC1350 MC1352 and the MC1330.

#### AN556 Interconnection Techniques for Motorola's MECL 10,000 Series Emitter Coupled Logic

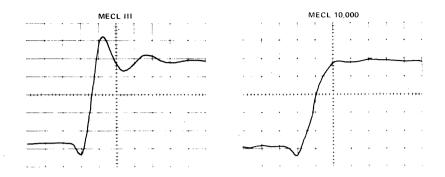

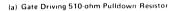

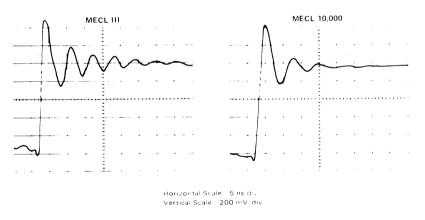

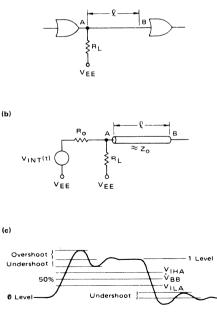

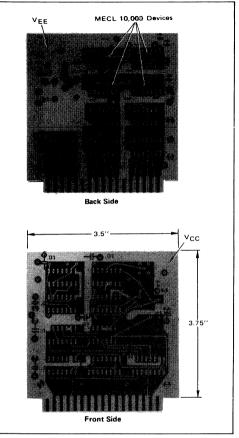

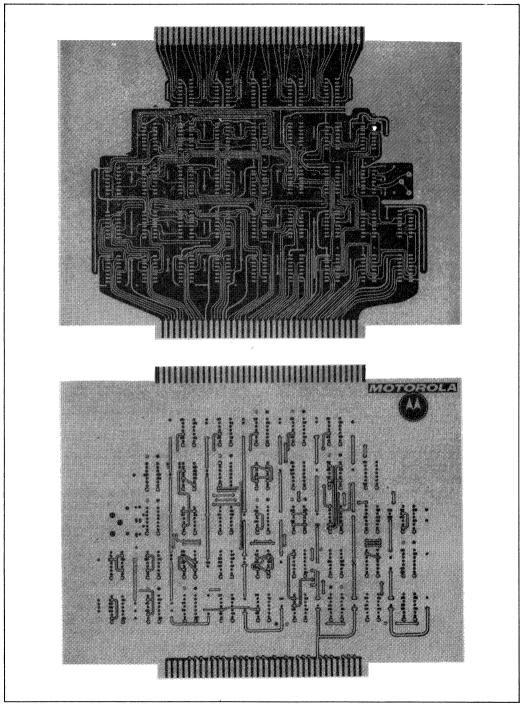

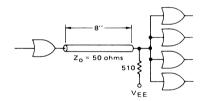

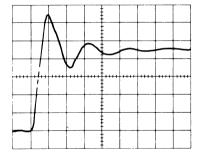

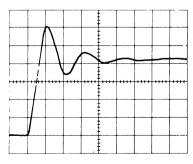

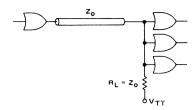

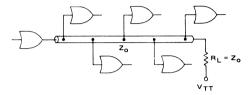

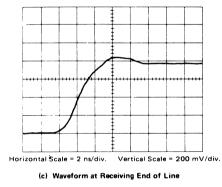

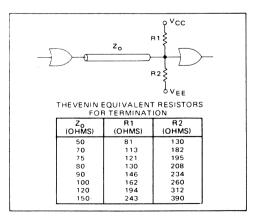

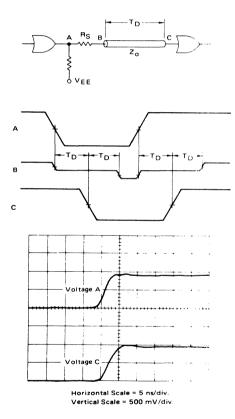

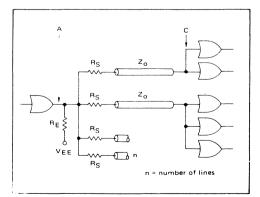

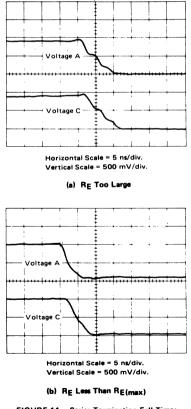

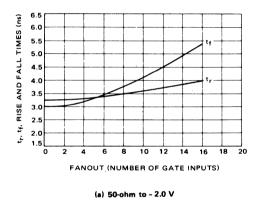

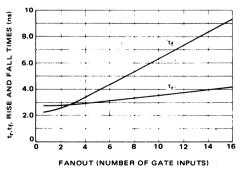

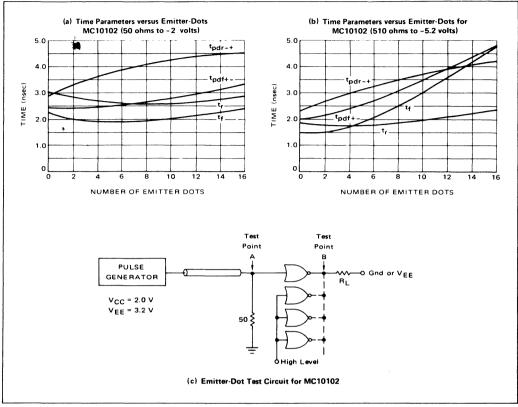

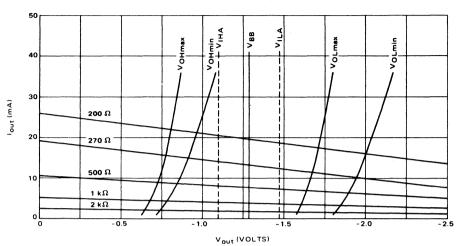

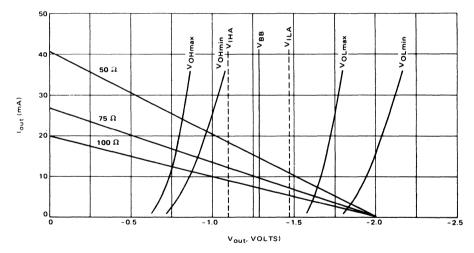

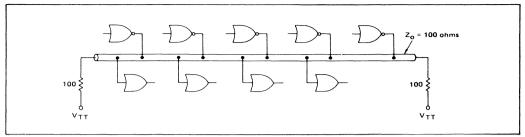

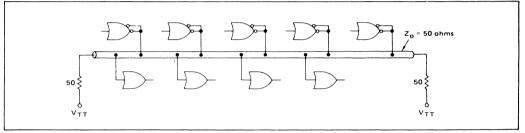

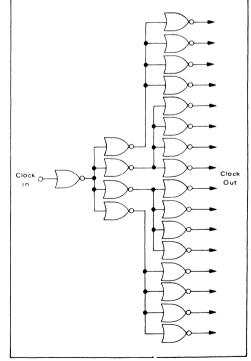

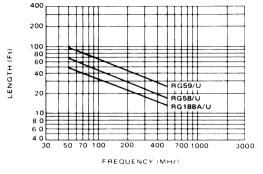

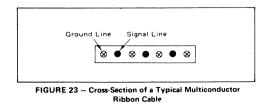

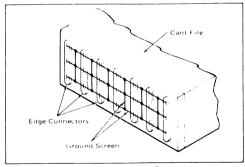

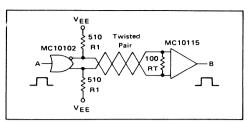

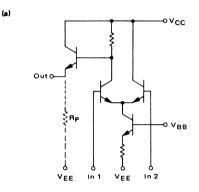

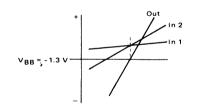

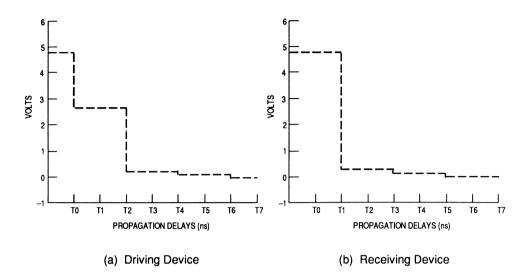

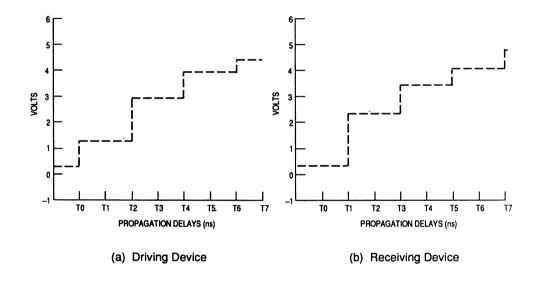

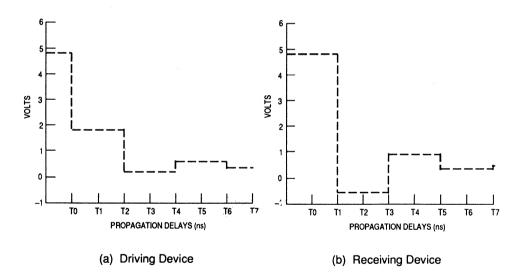

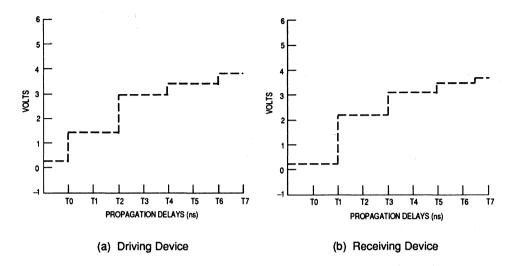

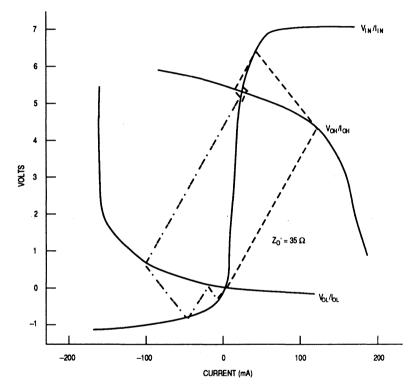

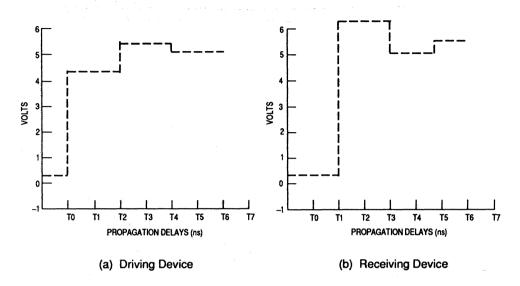

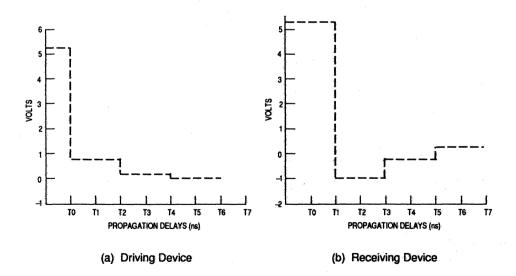

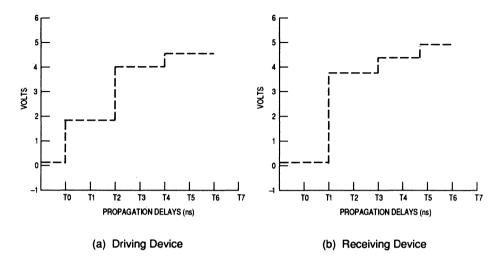

The MECL 10,000 Series is designed to be the most usable very high speed logic available. It satisfies the growing need for high clock rate capability and short propagation delays with minimum layout constraints. This comprehensive note describes some characteristics of high speed digital signal lines and the wiring rules for MECL 10,000. Discussions include PCB interconnects and wirewrapping techniques.

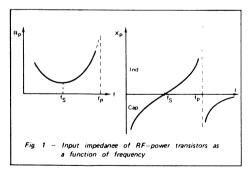

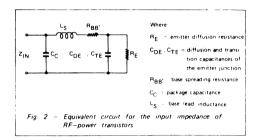

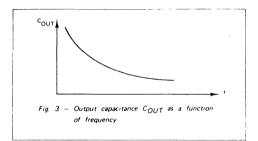

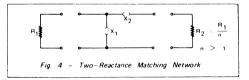

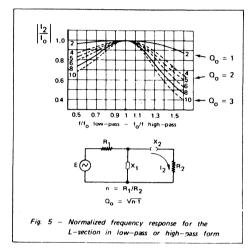

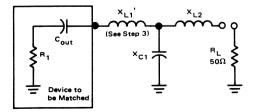

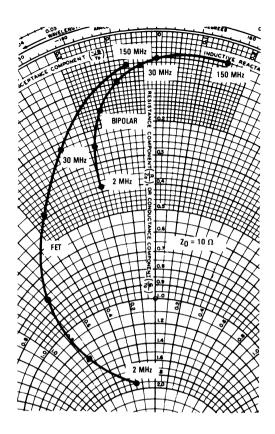

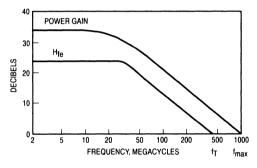

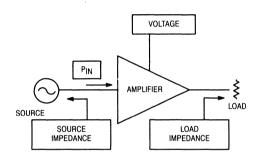

#### AN721 Impedance Matching Networks Applied to RF Power Transistors

This note covers the basics of interstage and output impedance matching of RF power transistors. Graphical and numerical methods of solution are clearly described along with sample problems. Photos, schematics and charts are generously provided throughout.

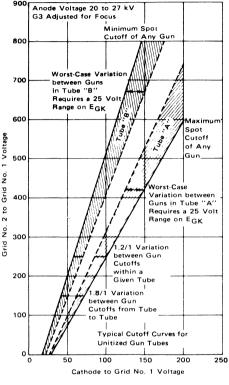

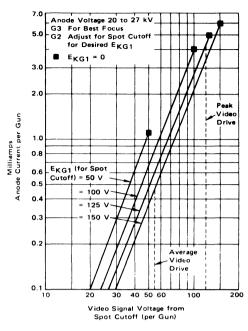

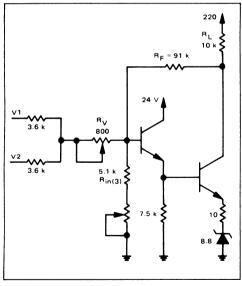

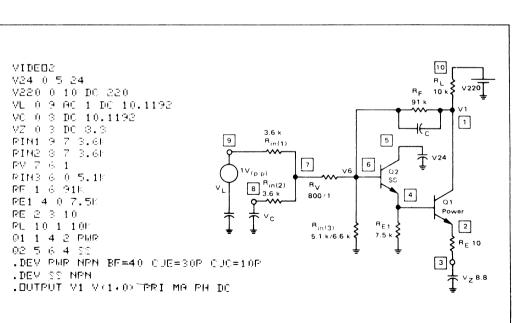

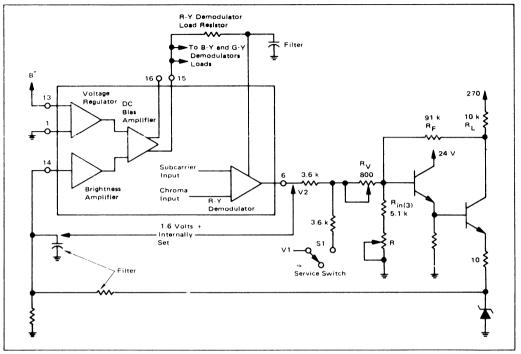

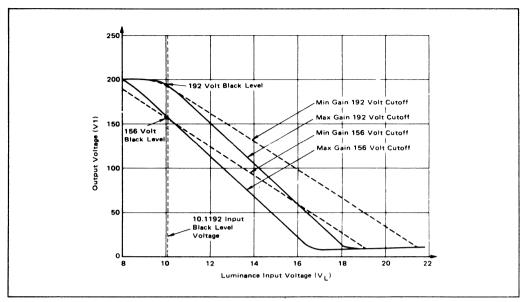

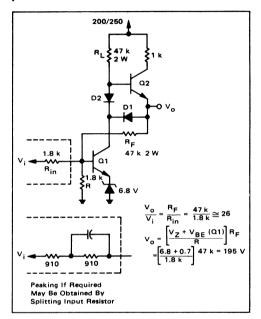

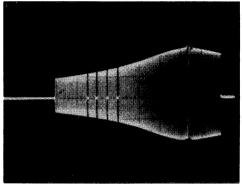

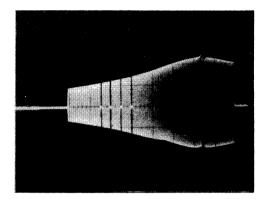

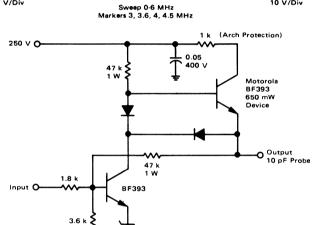

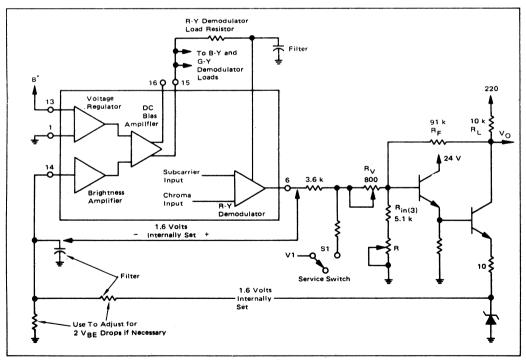

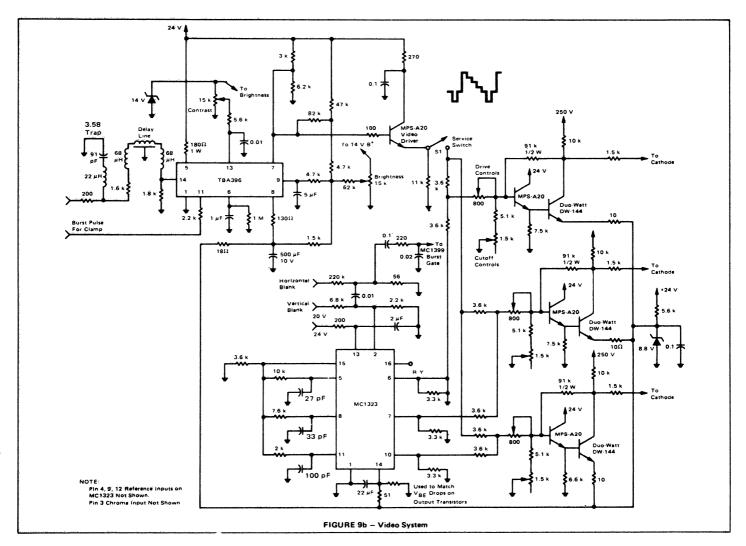

#### AN761 Video Amplifier Design: Know Your Picture Tube Requirements

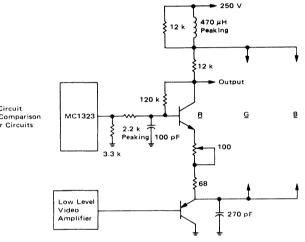

This note describes video amplifier design considerations for unitized gun and conventional picture tubes. Some unique design techniques are discussed taking advantage of Motorola's MC1323 chroma demodulator. Design objectives of video amplifiers are discussed.

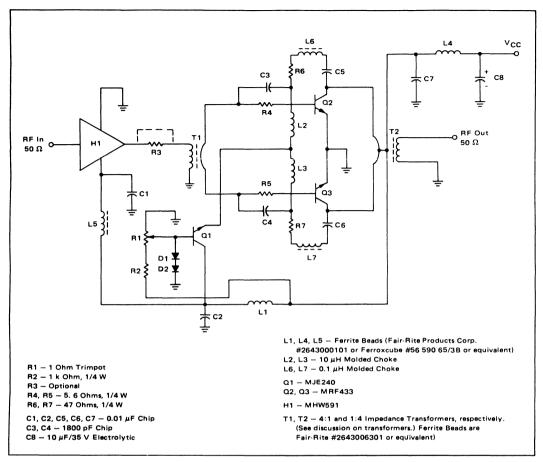

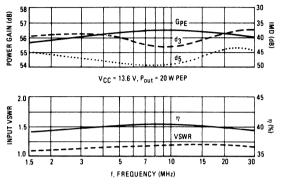

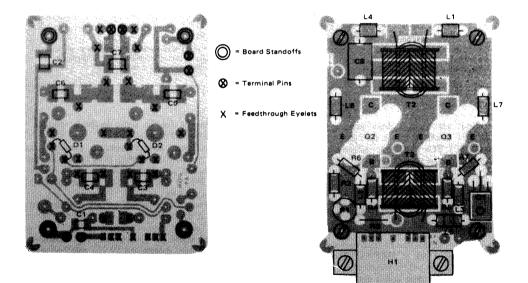

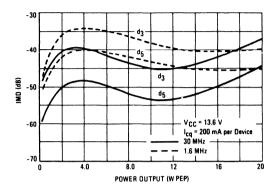

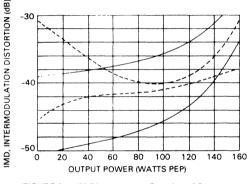

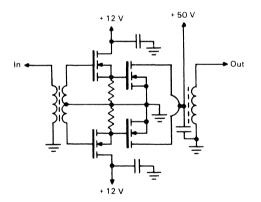

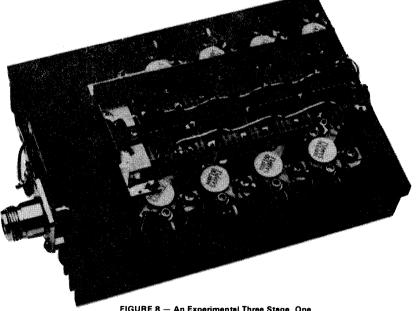

#### AN779 Low-Distortion 1.6 to 30MHz SSB Driver Designs

A general discussion for broadband drivers and their requirements for linear operation. Design examples are given using Motorola plastic transistors and high-gain hybrid modules designed for operation in the 1.0 to 250MHz range. The amplifiers range in power gain from 25 to 55dB and are capable of driving power amplifiers to levels up to several hundred watts.

#### AN791 A Simplified Approach to VHF Power Amplifier Design

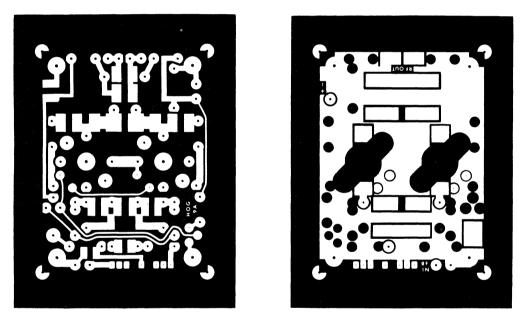

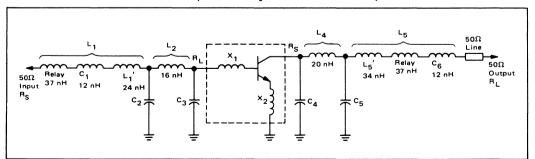

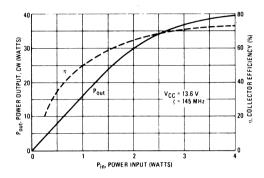

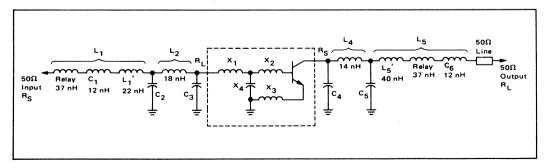

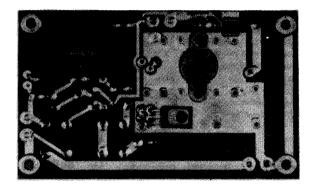

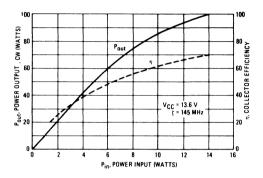

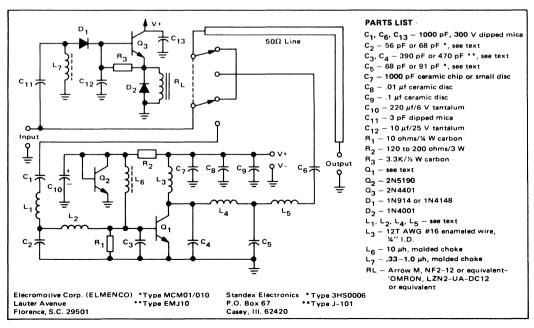

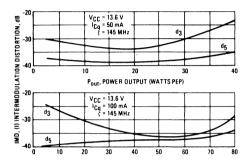

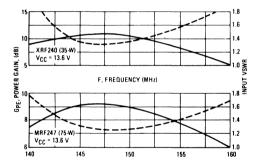

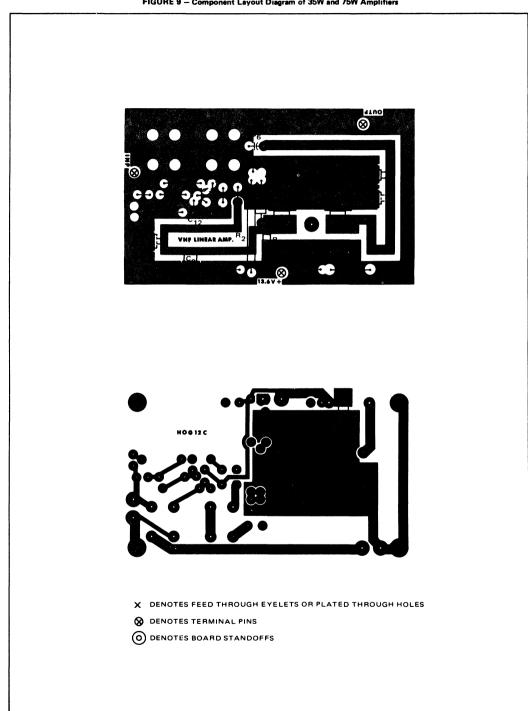

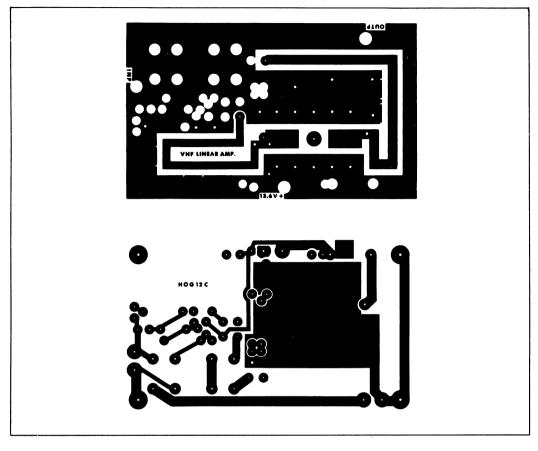

The design of 35W and 75W VHF linear amplifiers. The construction technique features printed inductors, the design theory of which is fully described. Complete constructional details, including a printed circuit layout, facilitate easy reproduction of the amplifier.

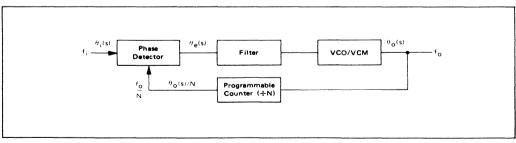

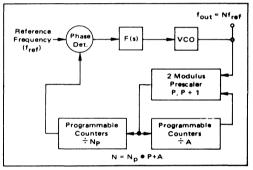

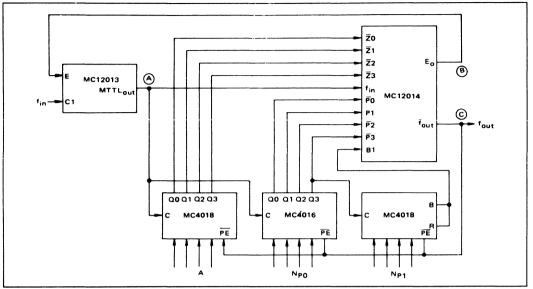

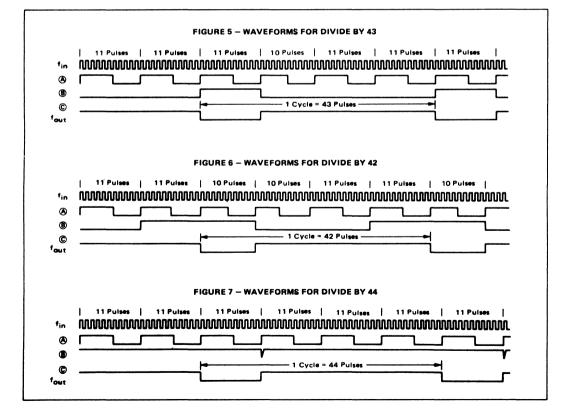

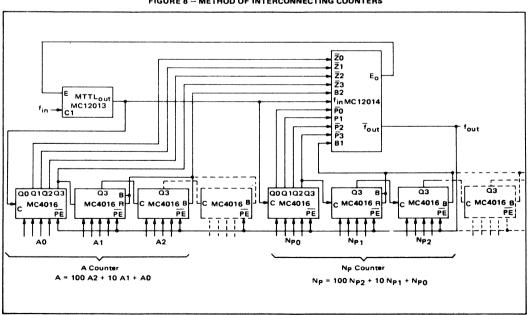

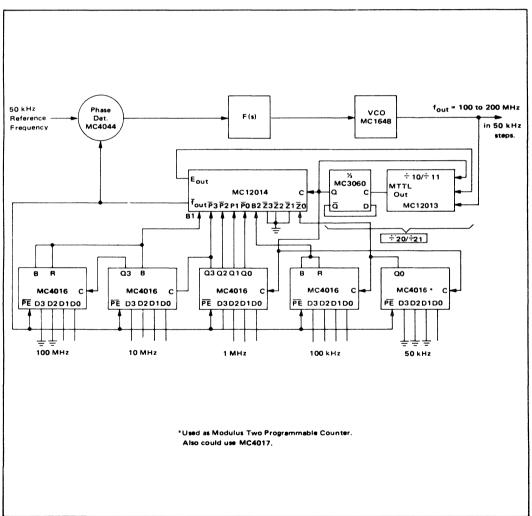

#### AN827 The Technique of Direct Programming by Using a Two-Modulus Prescaler

The technique and system described here offer a new approach to the construction of a phase-locked loop divider.

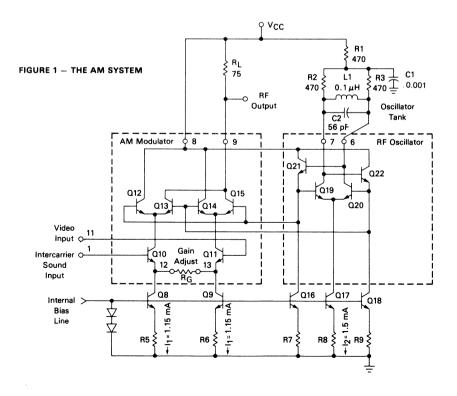

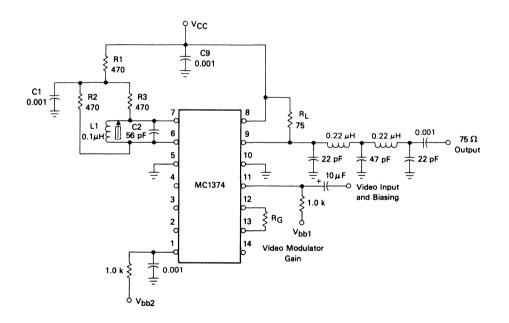

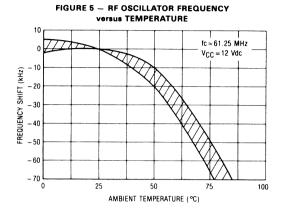

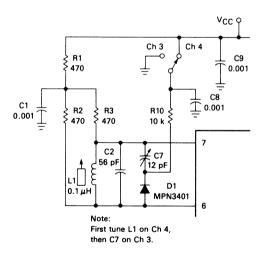

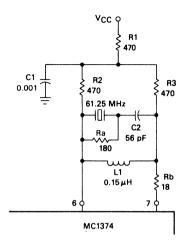

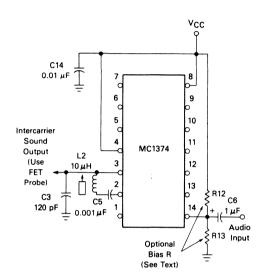

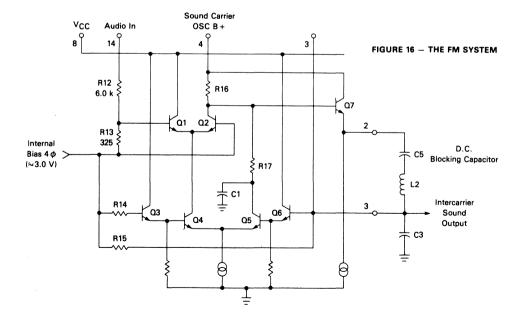

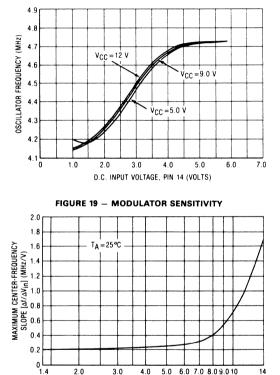

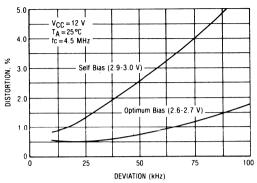

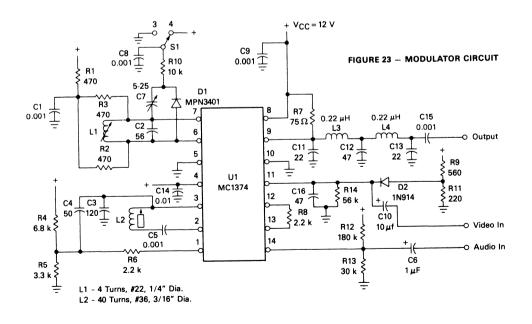

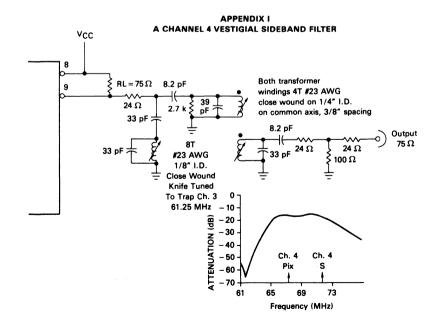

#### AN829 Application of the MC1374 TV Modulator

The MC1374 was designed for use in applications where separate audio and composite video signals are available, which need converting to a high quality VHF television signal. It is ideally suited as an output device for subscription TV decoders, video disc and video tape players.

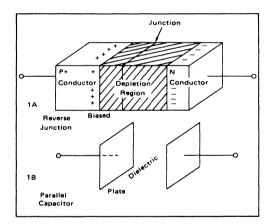

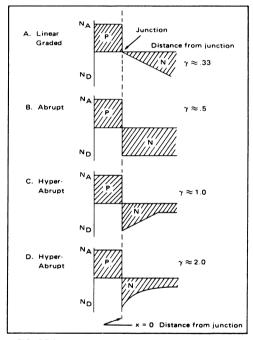

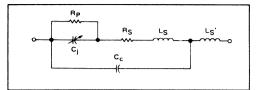

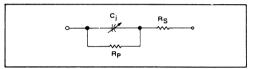

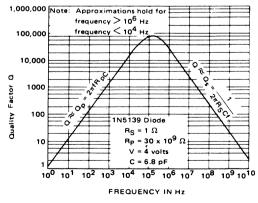

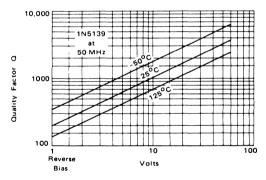

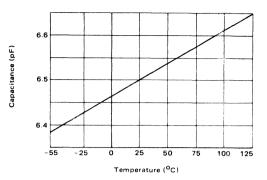

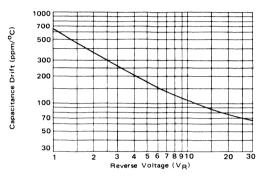

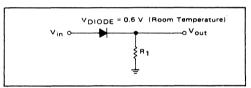

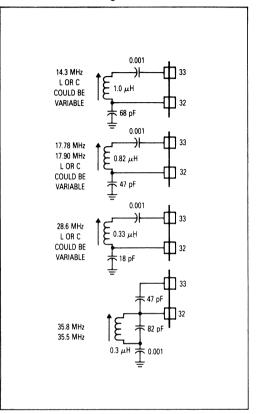

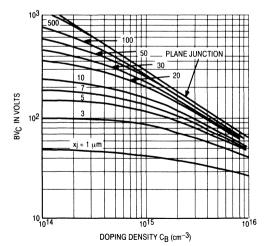

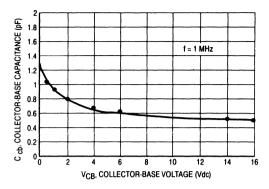

#### AN847 Tuning Diode Design Techniques

Tuning diodes are voltage-variable capacitors employing the junction capacitance of a reverse-biased PN junction. A simplified theory of tuning diodes is presented, and a number of considerations to be employed in designs using tuning diodes are also discussed.

#### AN860 Power MOSFETs versus Bipolar Transistors

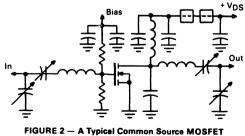

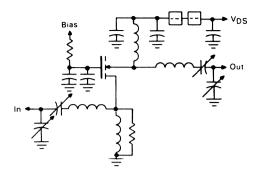

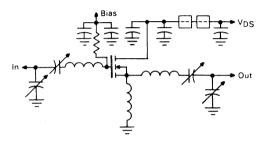

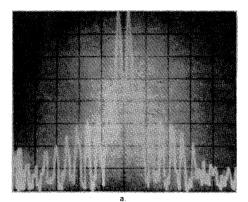

This application note discusses the characteristics of FETs and bipolar devices. Both have the same basic geometry but with some mask changes. One is processed as a MOSFET and the other as a bipolar. It is doubtful that the power FET will ever replace the bipolar transistor in all areas of communications equipment. It will have its applications in low and medium power VHF and UHF amplifiers, eliminating the need for internal matching, and up to medium power low band and VHF SSB, where the high order IMD is beginning to be more significant due to the crowded frequency spectrums.

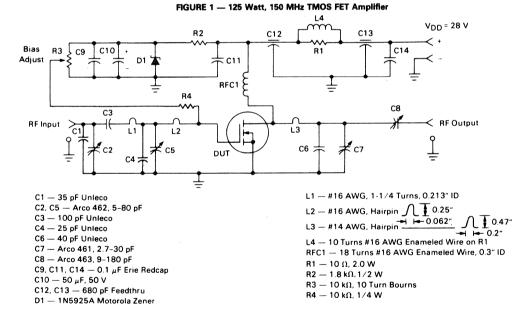

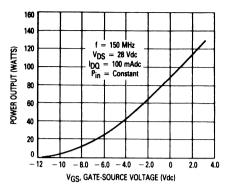

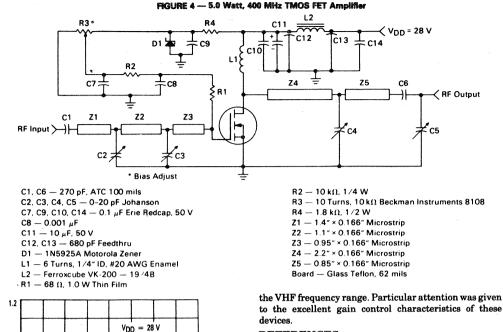

#### AN878 VHF MOS Power Applications

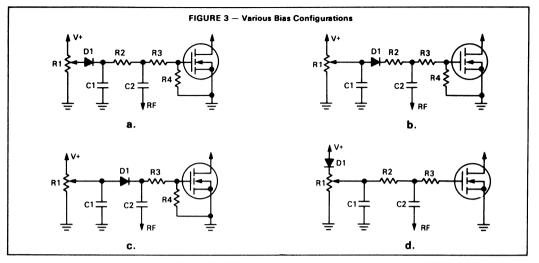

The construction characteristics and advantages of RF power FETs are described with emphasis on the VHF frequency range. Particular attention is given to the excellent gain control characteristics of these devices.

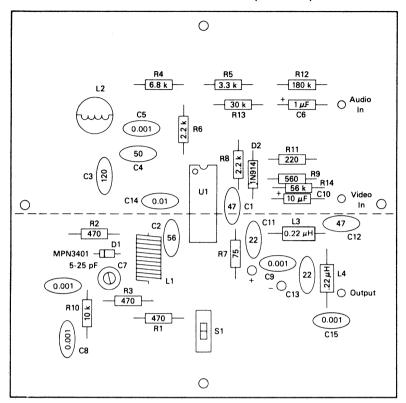

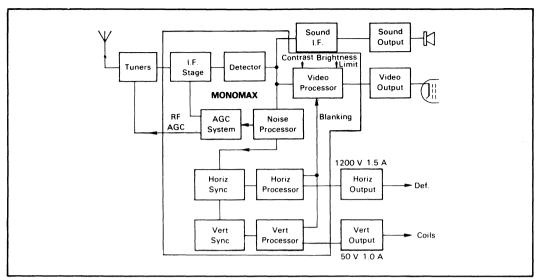

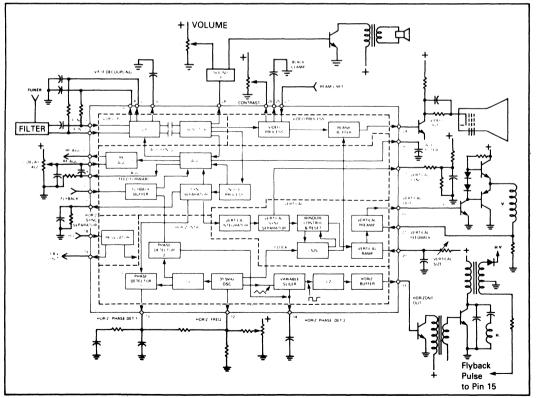

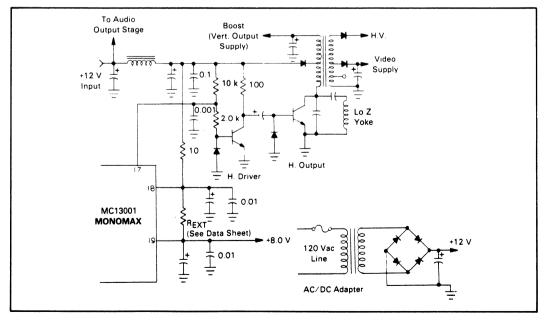

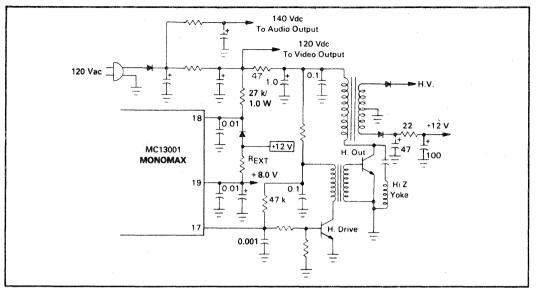

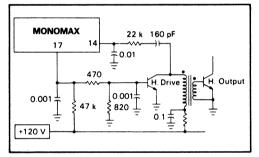

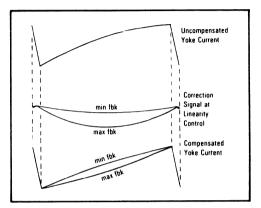

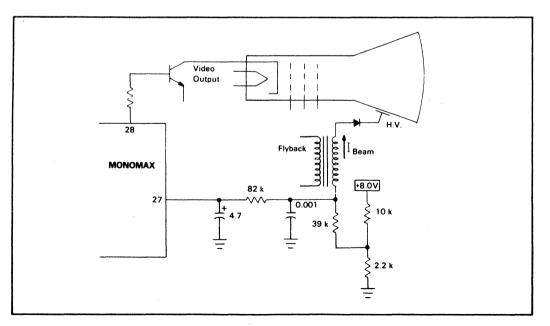

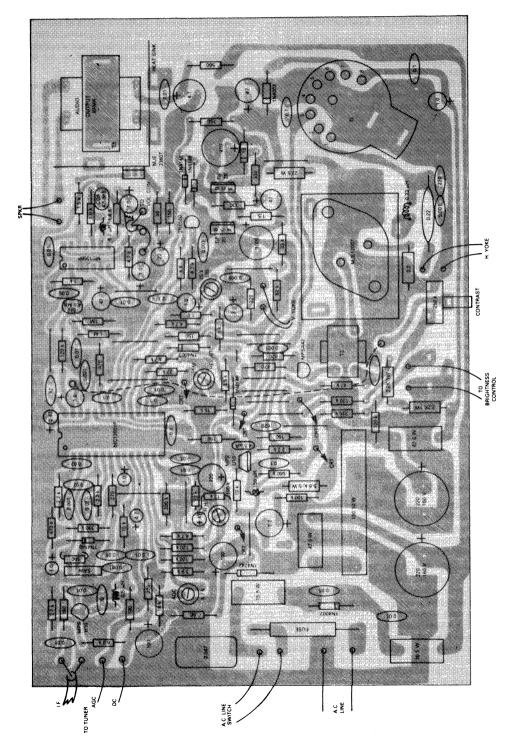

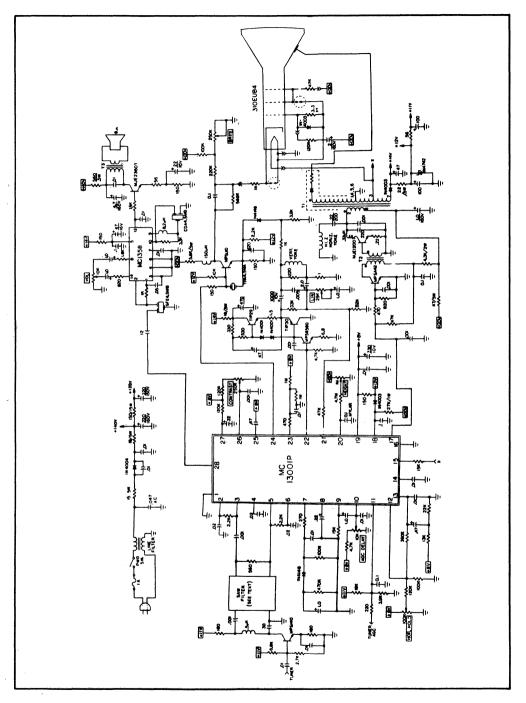

#### AN879 Monomax: Application of the MC13001 Monochrome Television Integrated Circuit

This application note presents a complete 12" black and white line-operated television receiver including artwork for the printed circuit board. It is intended to provide a good starting point for the first-time user. Some of the most common pitfalls are overcome and the significance of component selections and locations are discussed.

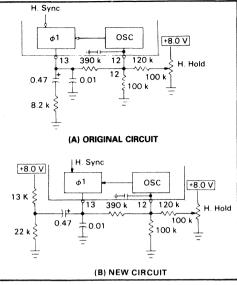

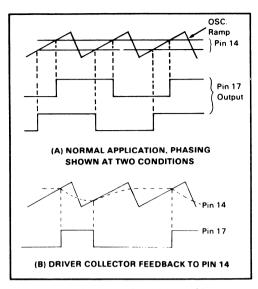

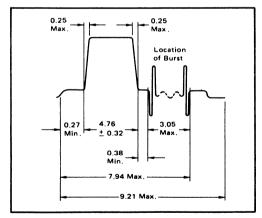

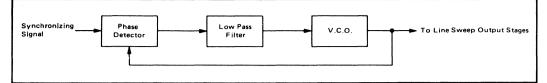

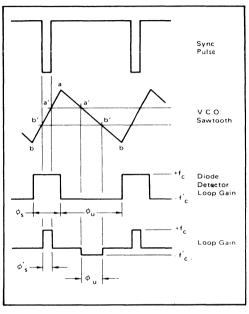

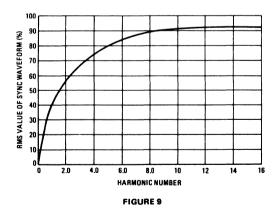

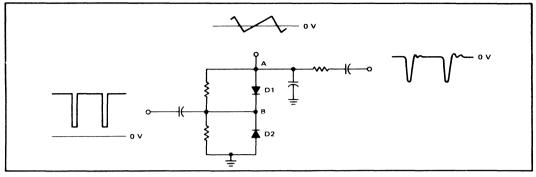

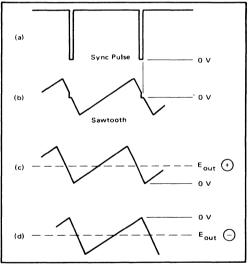

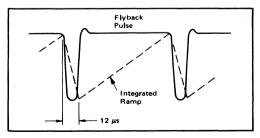

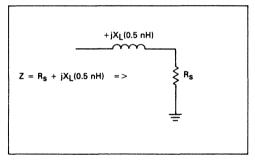

#### AN921 Horizontal APC/AFC Loops

The most popular method used in modern television receivers to synchronize the line frequency oscillator is the phase locked loop. The operating characteristics and parameters of the loops are discussed.

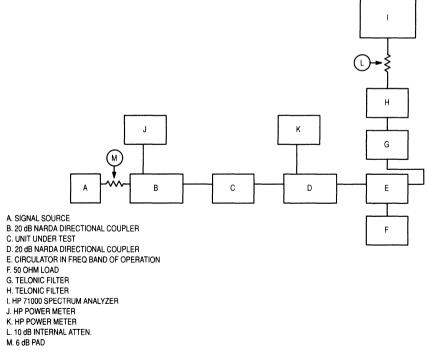

#### AN923 800MHz Test Fixture Design

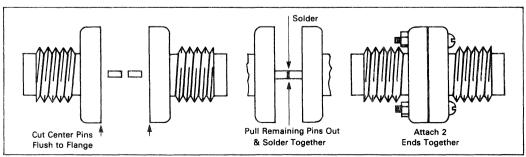

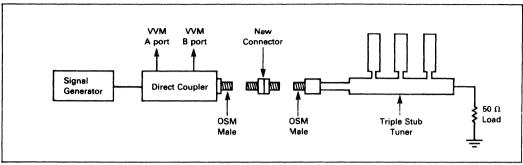

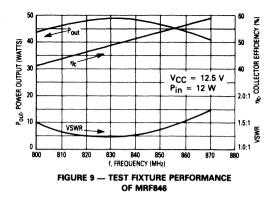

Techniques for the general case of UHF-800MHz circuit design are presented. Emphasis is placed specifically on test fixture design for the 800MHz. Text fixtures, the most valuable tools available for measuring and maintaining device consistency, are also presented.

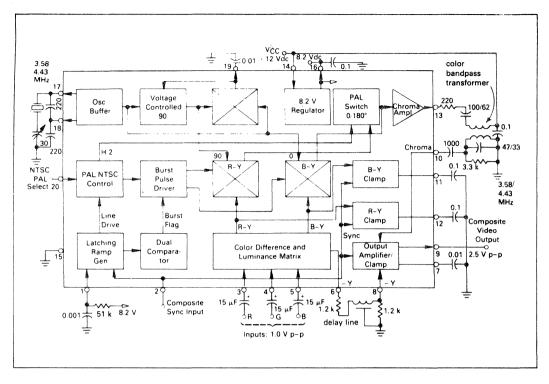

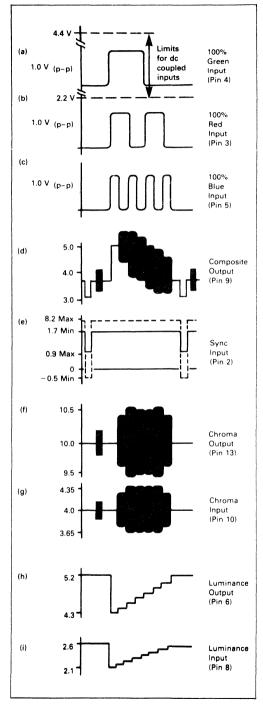

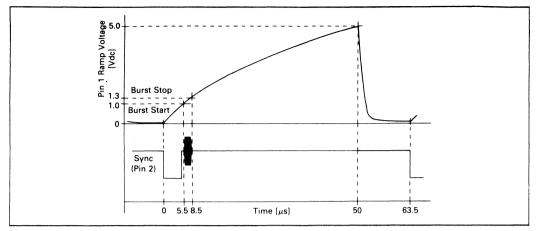

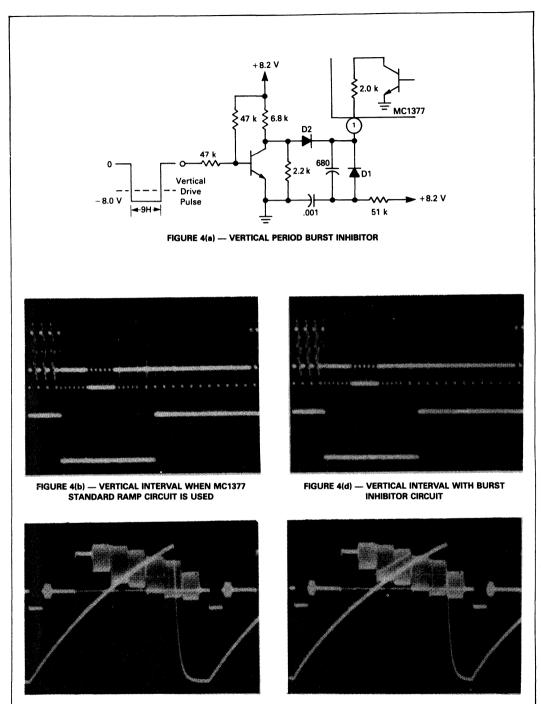

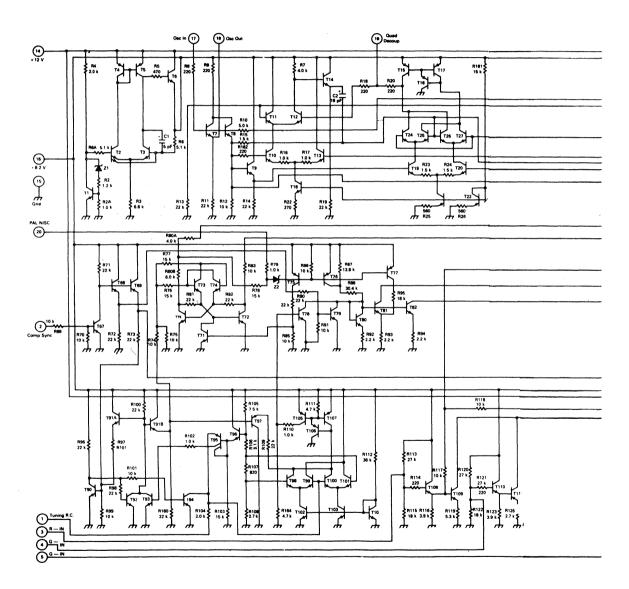

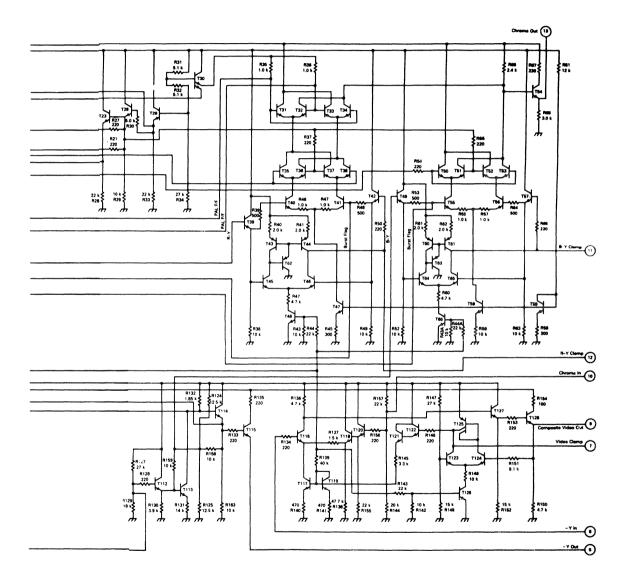

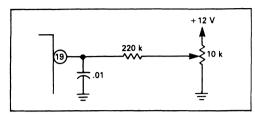

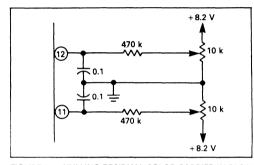

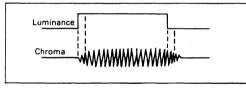

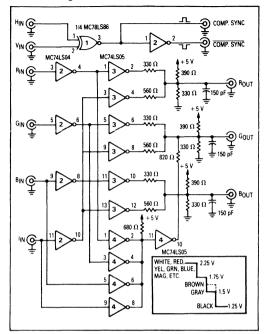

#### AN932 Application of the MC1377 Colour Encoder

The MC1377 is and economical, high quality, RGB encoder for NTSC or PAL applications. It accepts RGB and composite sync inputs, and delivers a 1V p-p composite NTSC or PAL video output into a 75 $\Omega$  load. It can provide its own colour oscillator and burst gating, or it can easily be driven from external sources. Performance virtually equal to high-cost studio equipment is possible with common colour receiver components.

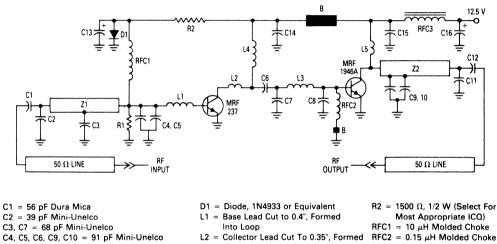

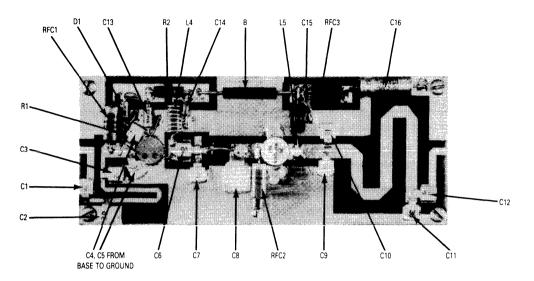

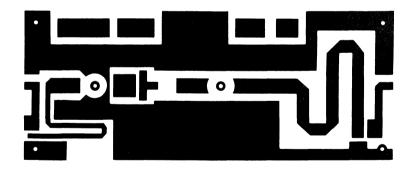

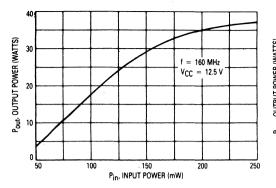

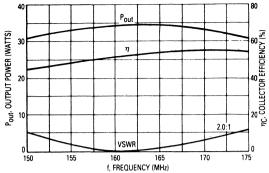

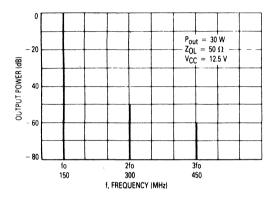

#### AN955 A Cost Effective VHF Amplifier for Land Mobile Radios

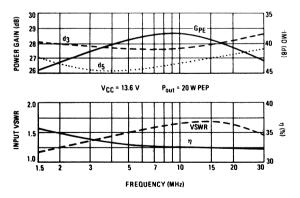

This application note describes a two-stage, 30 watt VHF amplifier featuring high gain, broad bandwidth and outstanding ruggedness to load mismatch, achieved by the use of the new MRF1946A power transistor.

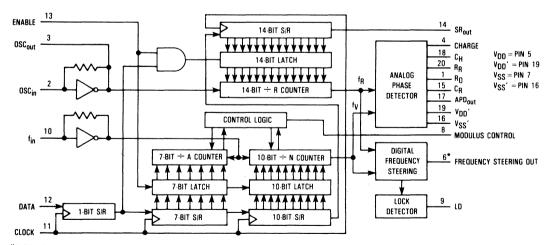

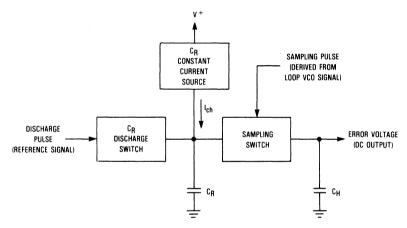

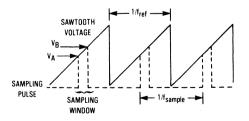

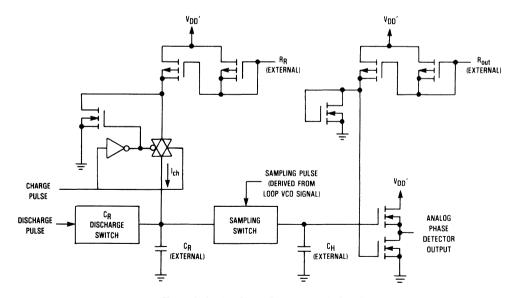

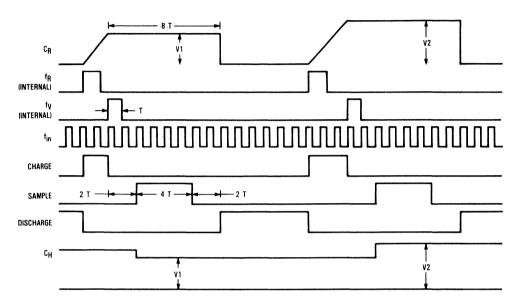

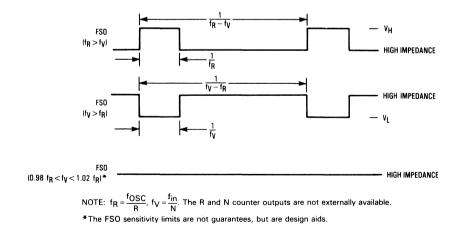

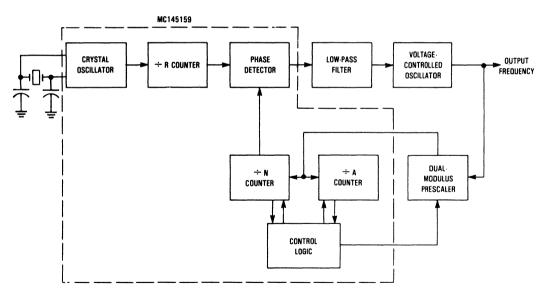

#### AN969 Operation of the MC145159 PLL Frequency Synthesizer with Analog Phase Detector

The MC145159 is a phase-locked loop frequency synthesizer with an improved sample-and-hold phase detector. It incorporates a range of features making it of particular interest in 2-way radios, cellular radiotelephones and avionics equipment. This note discusses its open loop characteristics, and shows that it reduces VCO modulation sidebands while allowing wider loop bandwidths than are possible with digital phase detectors.

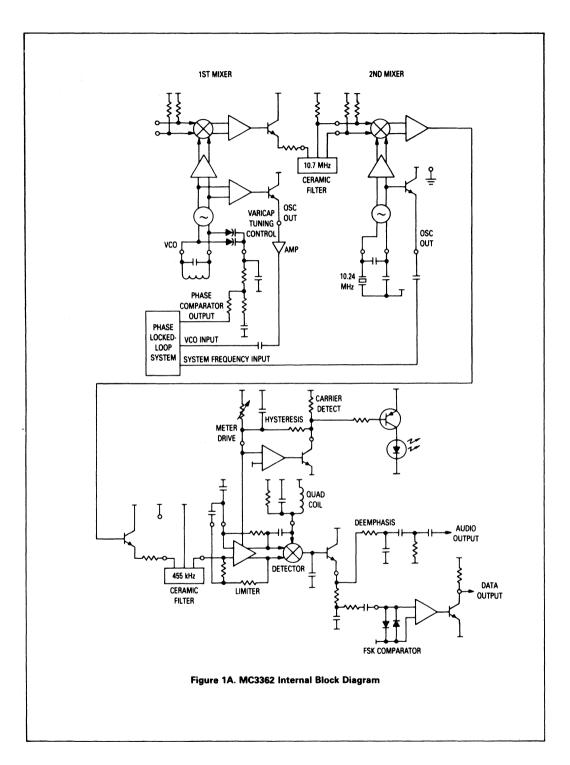

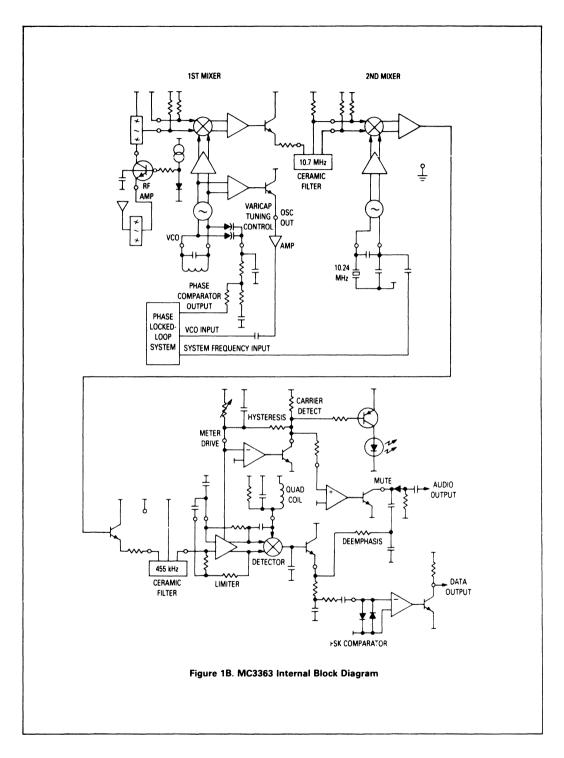

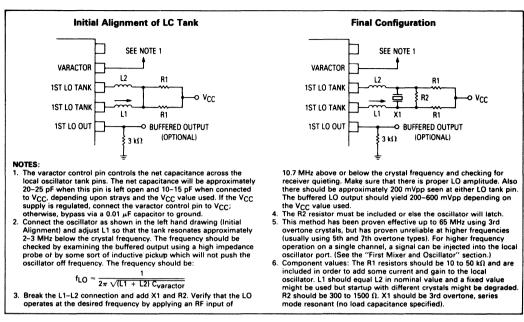

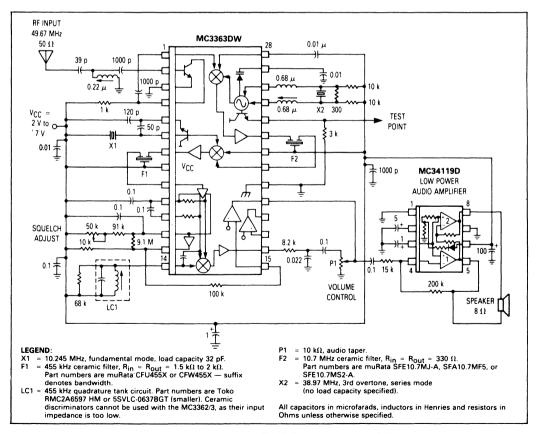

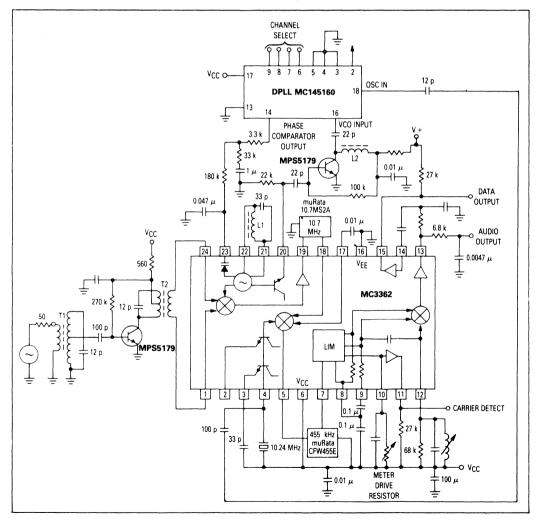

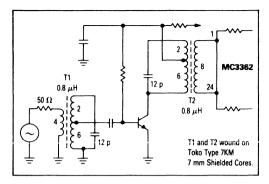

#### AN980 VHF Narrowband FM Receiver Design Using the MC3362 and the MC3363 Dual Conversion Receivers

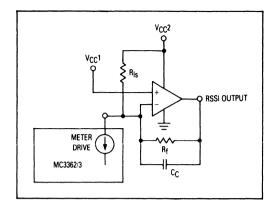

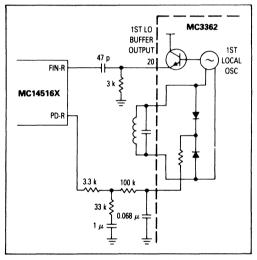

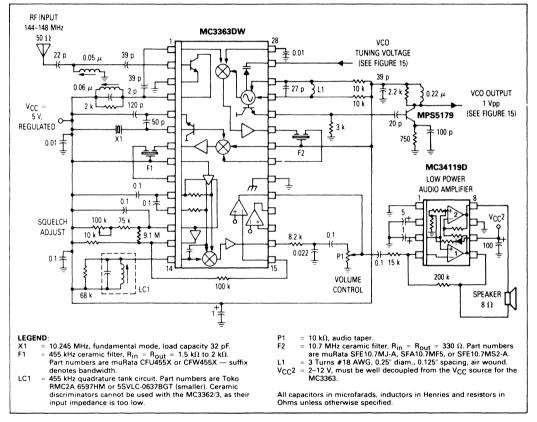

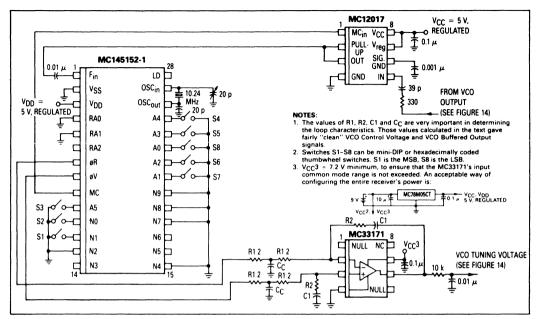

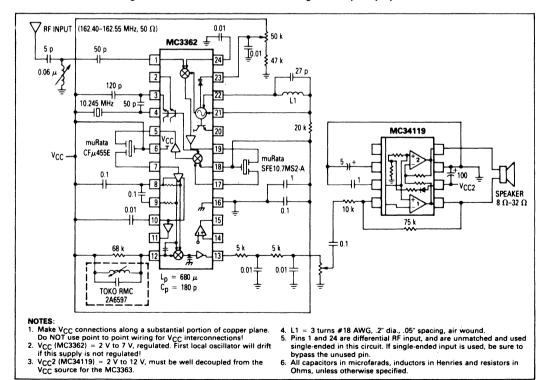

The MC3362 and MC3363 narrow-band FM dual conversion receivers feature excellent VHF performance with low power drain, making them ideal for cordless telephones, narrowband voice and data receivers and RF security devices. This note provides a detailed description of the operation of the two devices, plus circuits and descriptions for four applications: A single Channel VHF FM Narrowband Receiver; A Ten Channel Frequency Synthesized Cordless Telephone Receiver; A 256 Channel Frequency Synthesized Two Metre Amateur Band Receiver; and A Single Chip Weather Band Receiver.

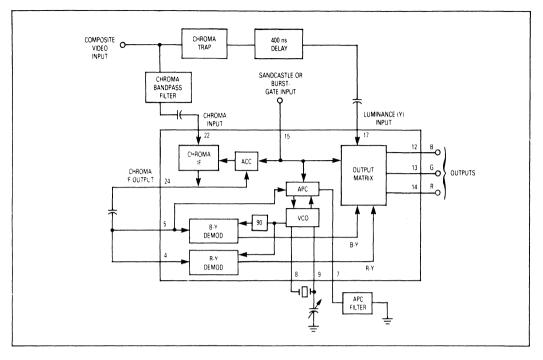

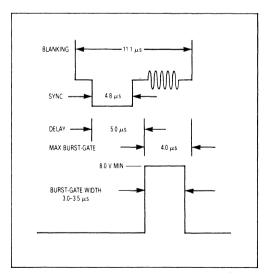

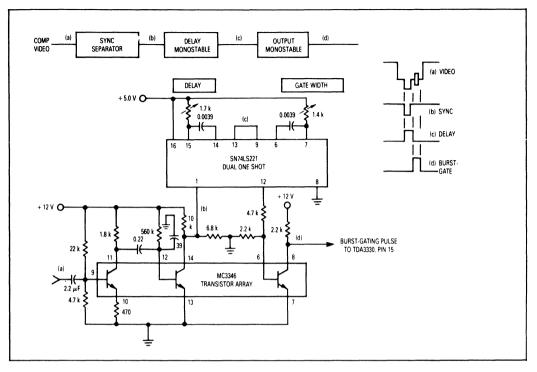

#### AN1019 Decoding Using the TDA3330, with Emphasis on Cable In/Cable Out Operation

The TDA3330 is a Composite Video to RGB Colour Decoder originally intended for PAL and NTSC colour TV receivers and monitors — so its data sheet concentrates on picture tube drive. This practical application note supplements the data sheet by providing circuits for video cable drive as used in video processing, frame store and other specialized applications, and expands on TDA3330 functional details. Includes PCB artwork and layout of an evaluation board.

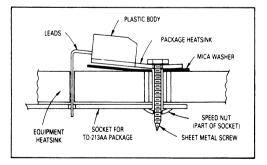

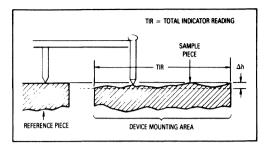

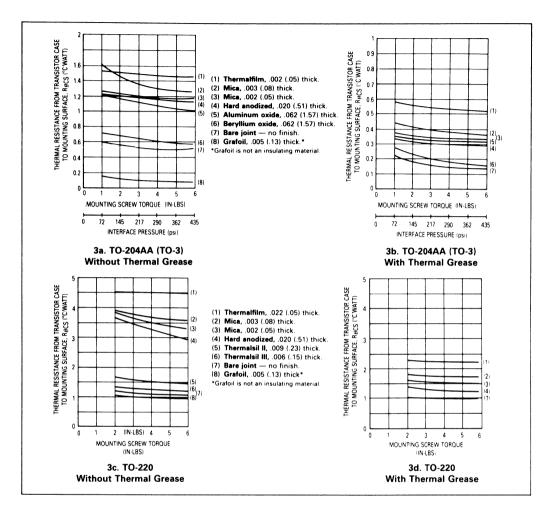

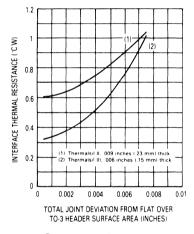

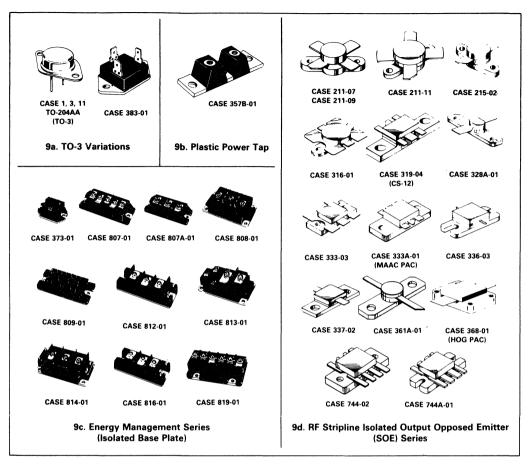

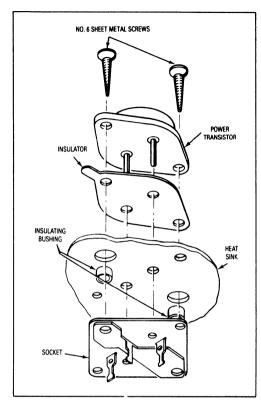

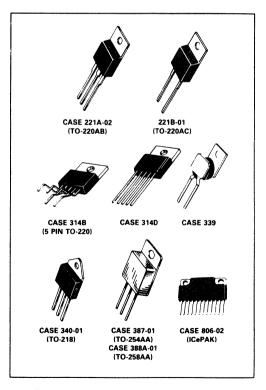

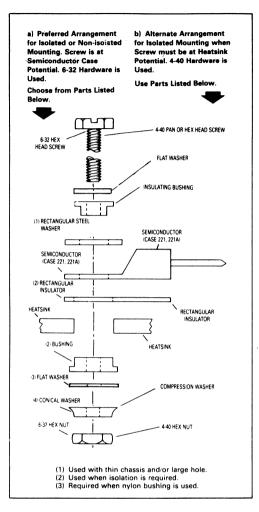

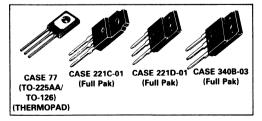

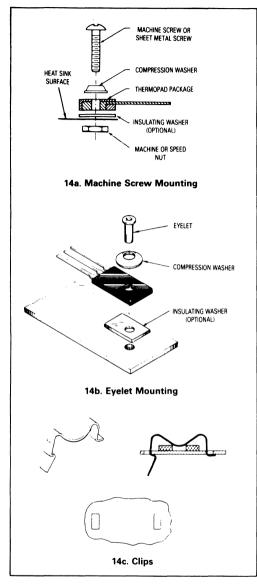

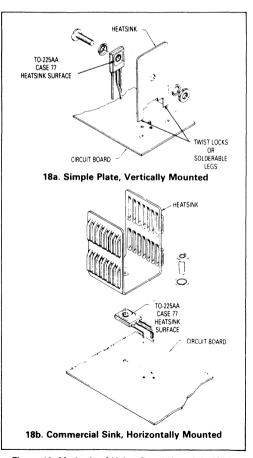

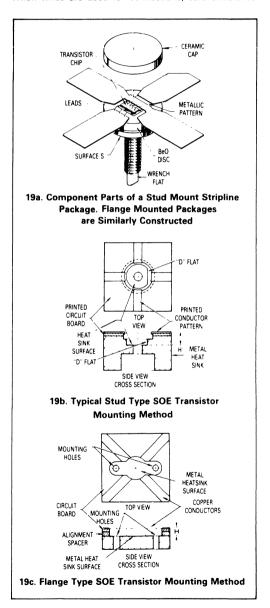

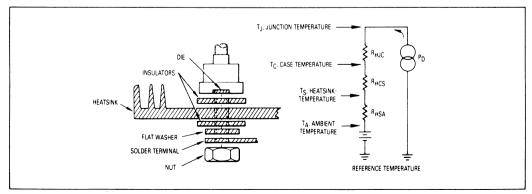

#### AN1040 Mounting Considerations for Power Semiconductors

The operating environment is a vital factor in setting current and power ratings of a semiconductor device. Reliability is increased considerably for relatively small reductions in junction temperature. Faulty mounting not only increases the thermal gradient between the device and its heat sink, but can also cause mechanical damage. This comprehensive note shows correct and incorrect methods of mounting all types of discrete packages, and discusses methods of thermal system evaluation.

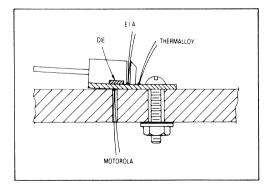

#### AN1041 Mounting Procedures for Very High Power RF Transistors

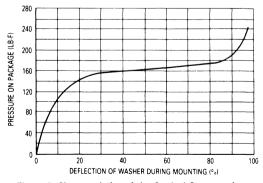

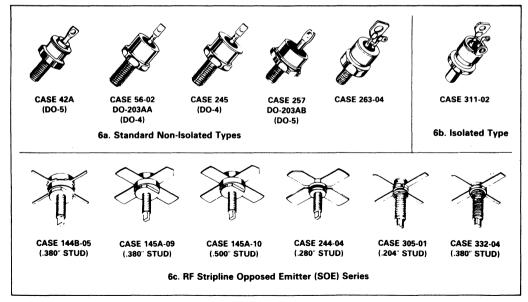

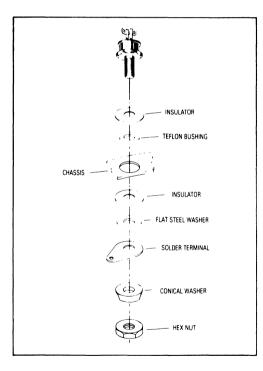

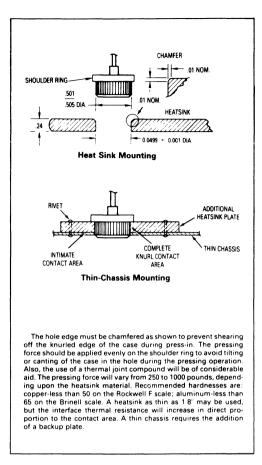

High power (200-600W) RF semiconductors such as the MRF153... and MRF141G... series dissipate an abnormally large amount of heat within a small physical area. Heat sink material, surface finish, mounting screws, washers and screw torque are extremely important factors in ensuring reliability. This note explains why

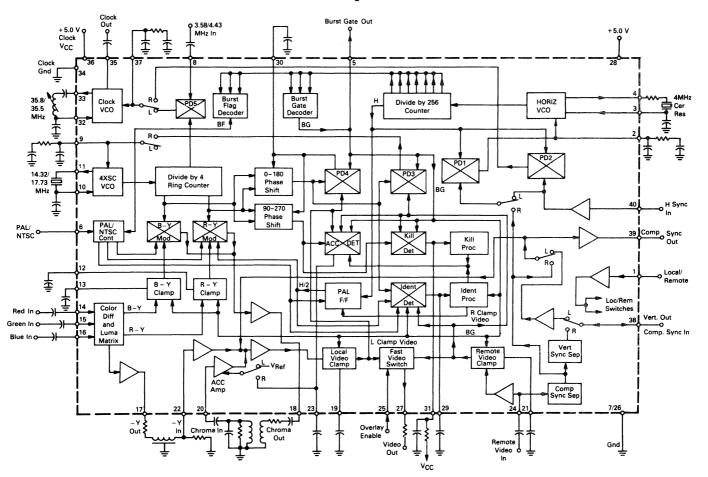

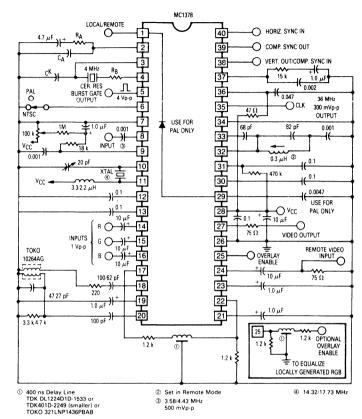

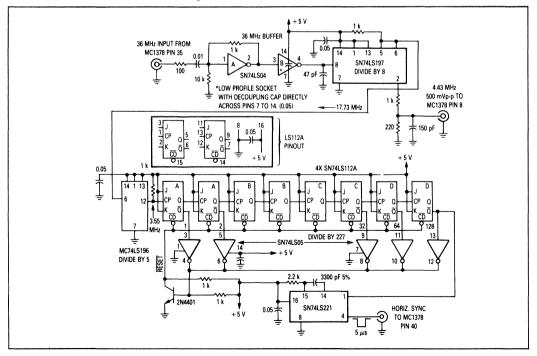

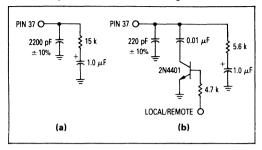

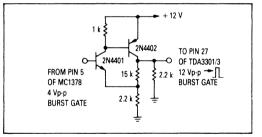

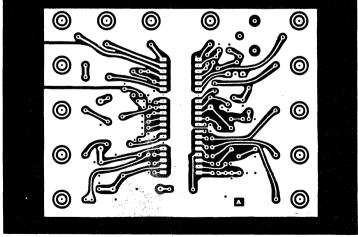

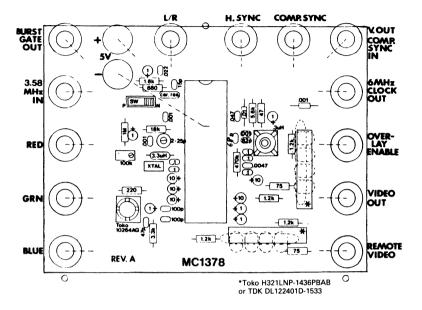

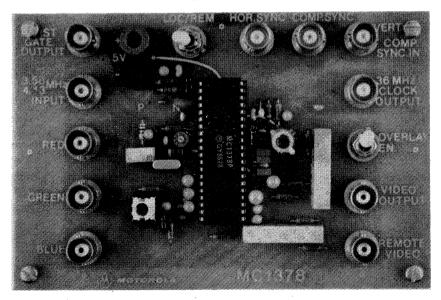

#### AN1044 The MC1378 — A Monolithic Composite Video Synchronizer

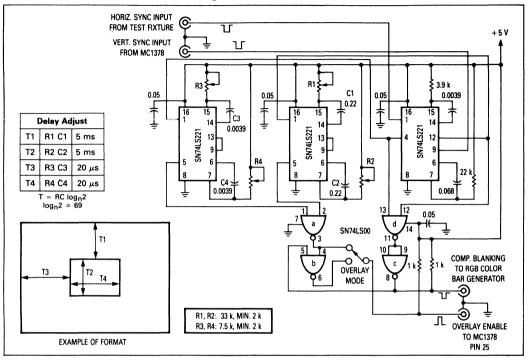

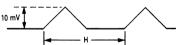

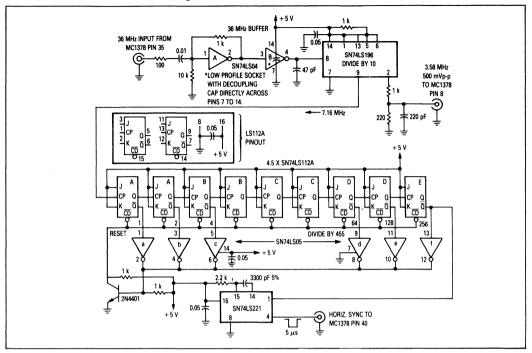

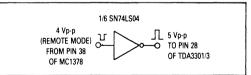

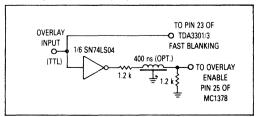

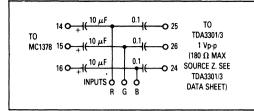

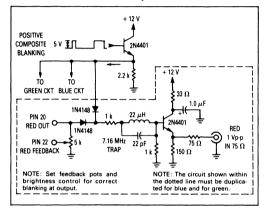

The MC1378 provides an interface between a remote composite colour video source and local RGB. On-chip circuitry can lock a local computer to the remote source, switching between local and remote signals to generate composite video overlays. This detailed note describes local and remote operation, picture-in-picture applications and the design of test fixtures to help system development. Printed circuit artwork for an evaluation board is provided. The NTSC/PAL colour encoder is similar to the MC1377, discussed in detail in AN932.

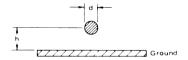

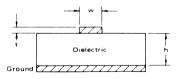

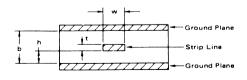

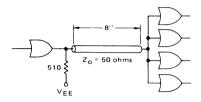

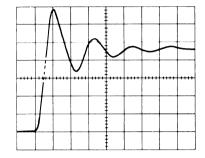

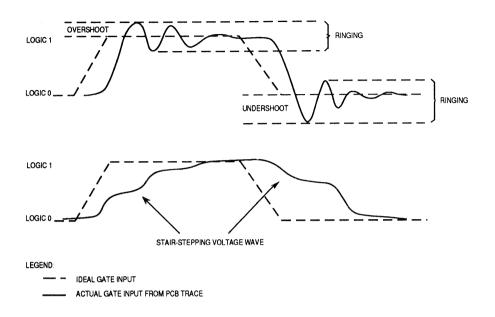

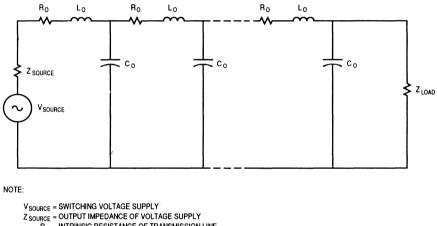

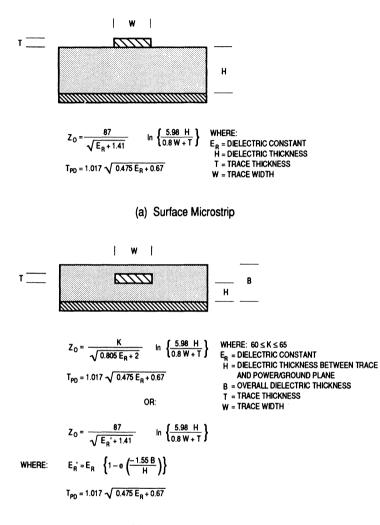

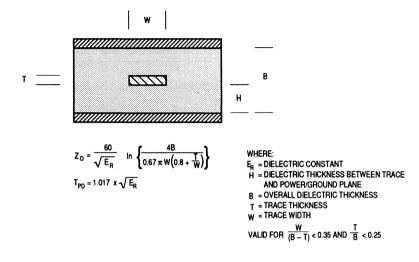

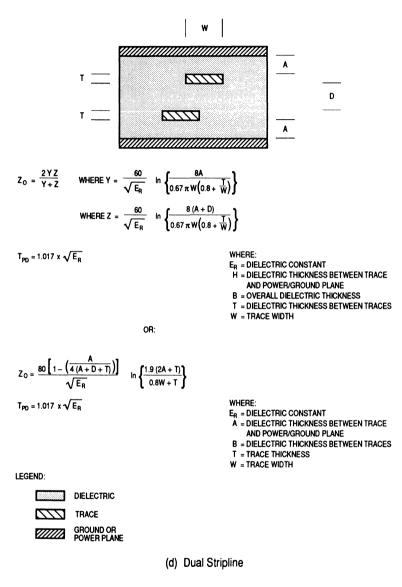

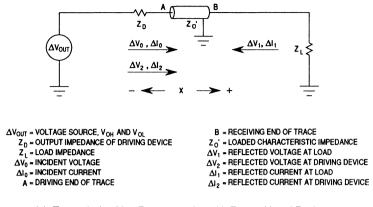

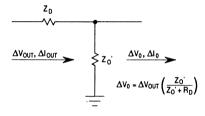

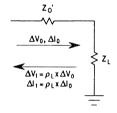

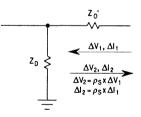

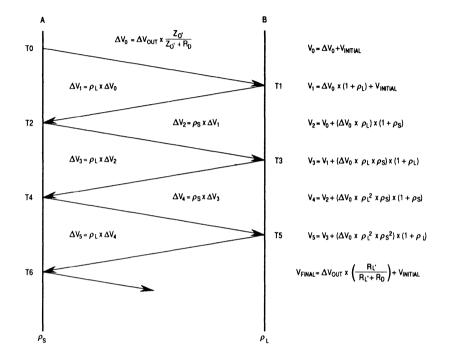

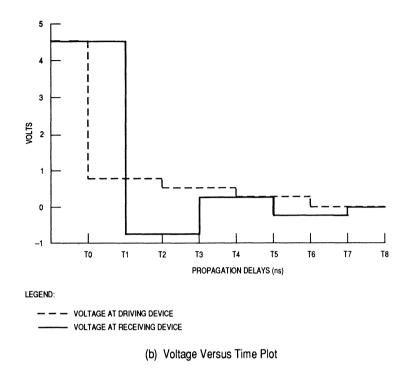

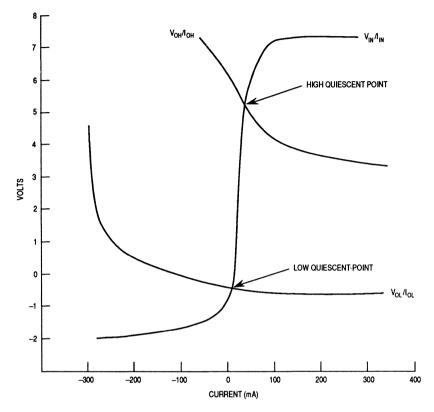

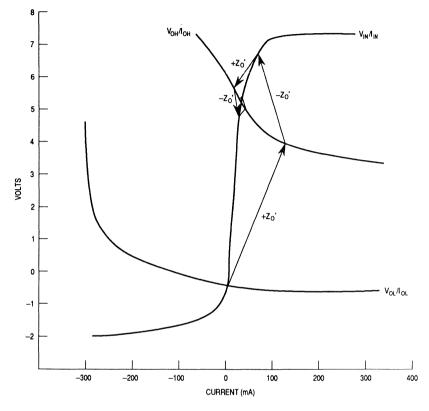

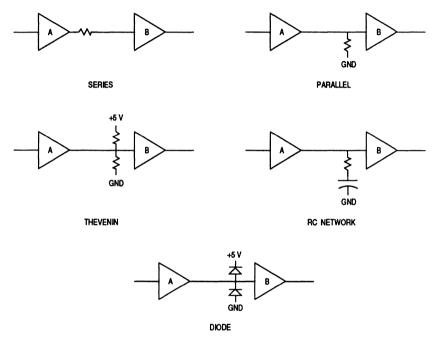

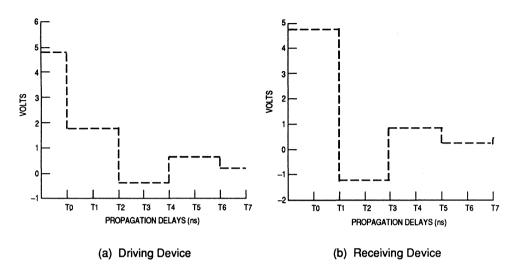

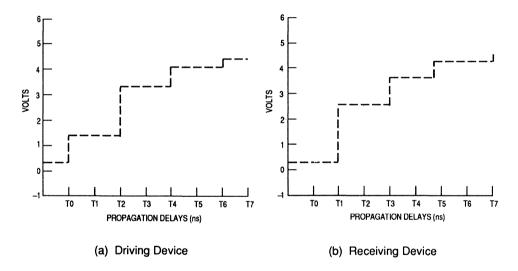

#### AN1051 Transmission Line Effects in PCB Applications

As rise and fall times become faster in order to achieve high operating speeds, transmission line effects on PCBs can be very significant, with the possibility of unpredictable behaviour. This note presents a guideline as to when to analyse, discusses the characteristics of different types of PCB trace, describes Lattice Diagram and Bergeron Plot analysis, and summarises termination methods. Includes 10 worked examples.

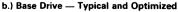

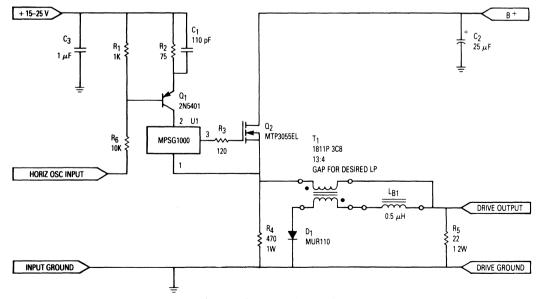

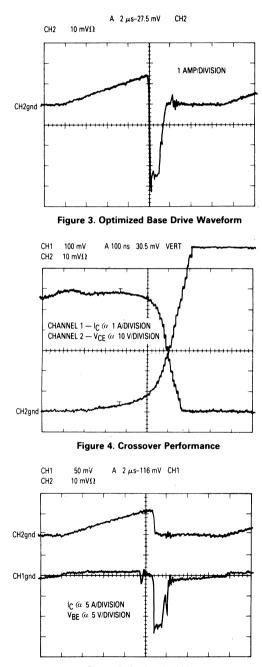

#### AN1076 Speeding up Horizontal Outputs

Motorola's SCANSWITCH transistors are designed specifically as fast drivers for horizontal outputs. Optimum performance is achieved when 5 base drive conditions are met. This successful base drive circuit starts with the output transistor's physics and works back to the horizontal oscillator.

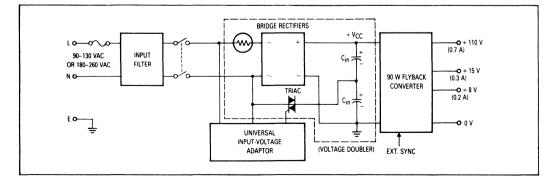

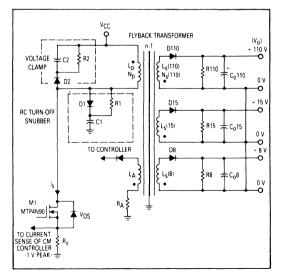

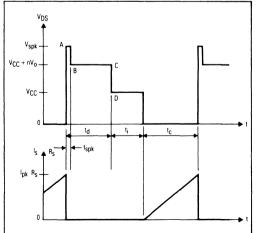

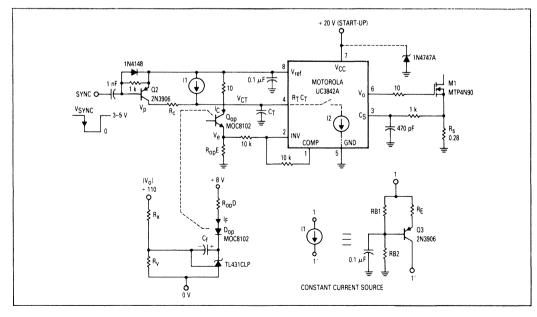

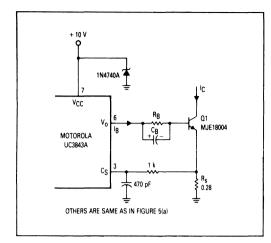

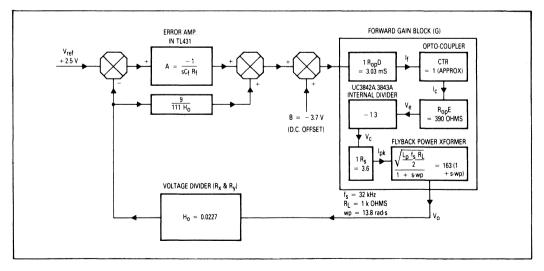

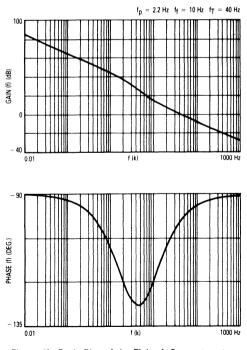

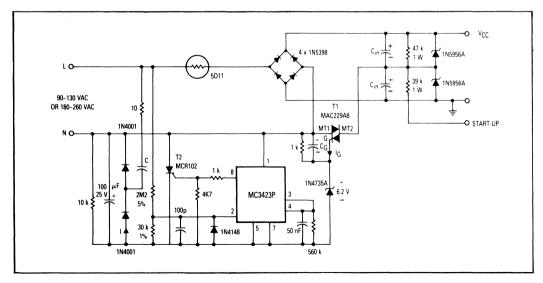

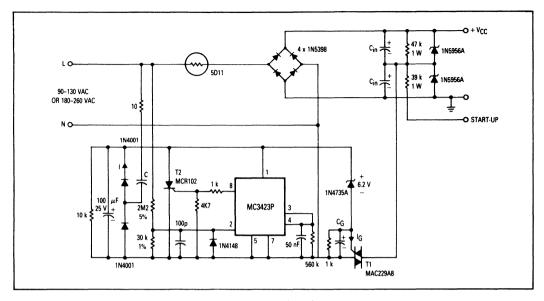

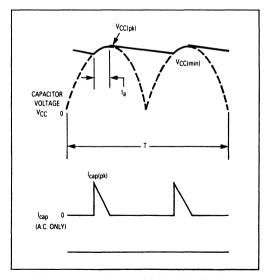

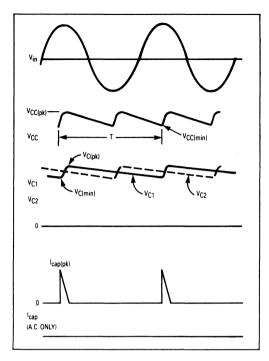

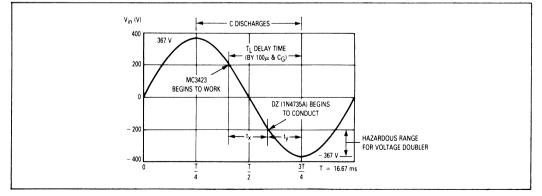

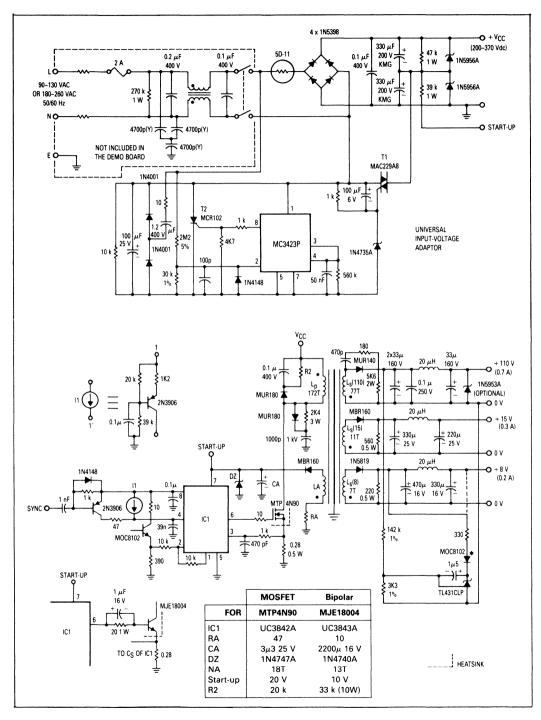

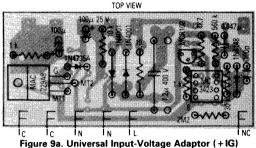

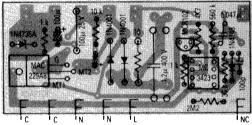

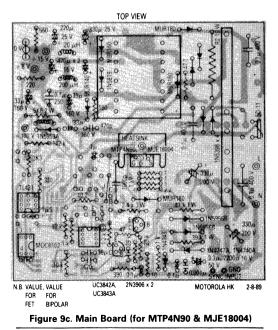

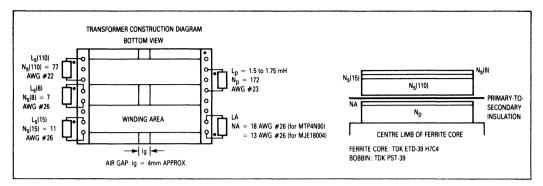

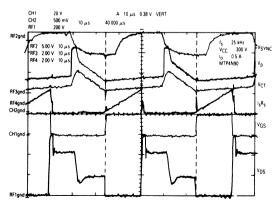

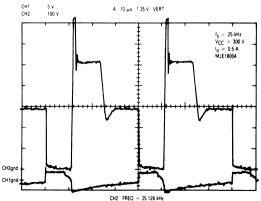

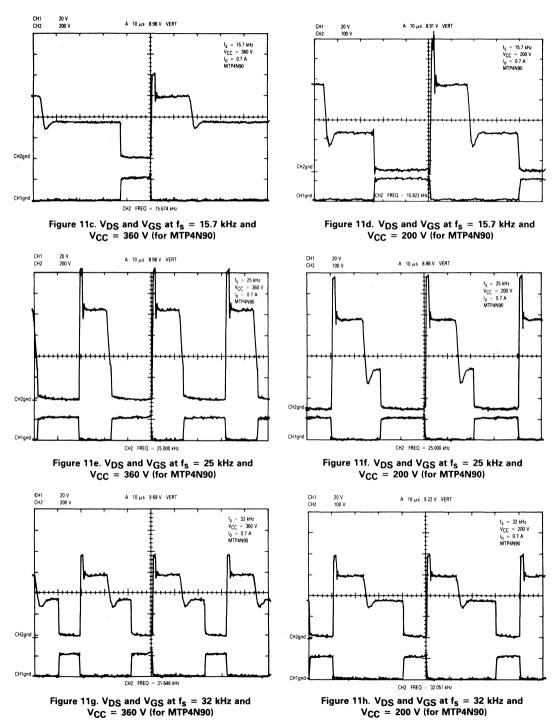

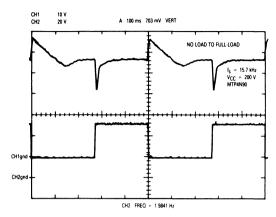

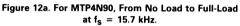

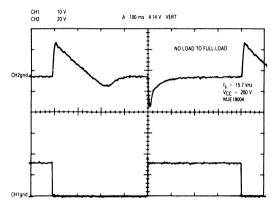

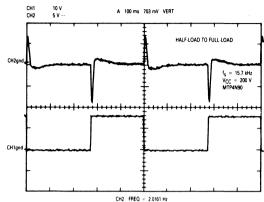

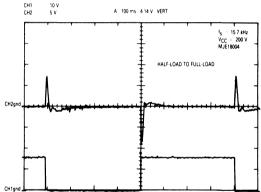

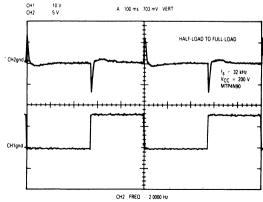

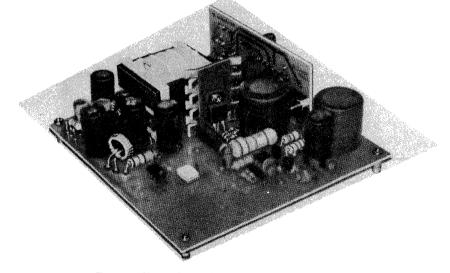

#### AN1080 External-Sync Power Supply with Universal Input Voltage Range for Monitors

As the resolution of colour monitors increases, the performance and features of their power supplies becomes more critical. EMI/RFI generated by switching power supplies can adversely affect resolution if switching frequency is not synchronised to horizontal scanning frequency. This 90W flyback switching supply demonstrates the use of new high-performance devices in a low-cost design, and includes a new universal input voltage adapter.

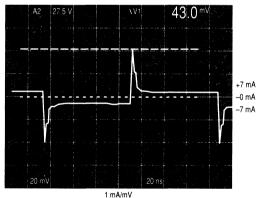

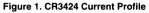

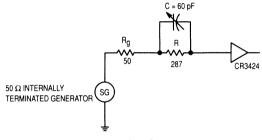

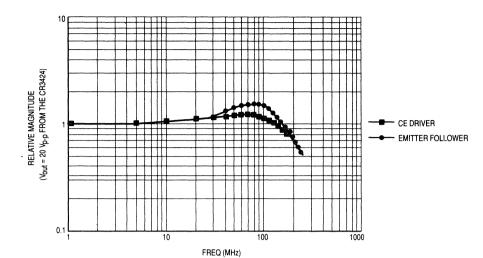

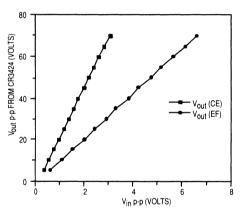

#### AN1103 Using the CR3424 for High Resolution CRT Applications

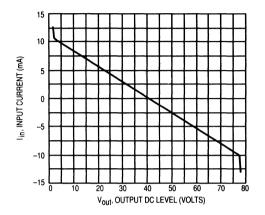

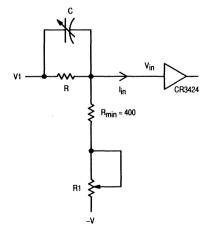

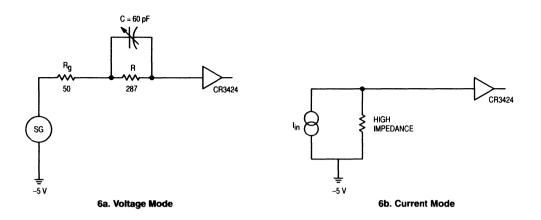

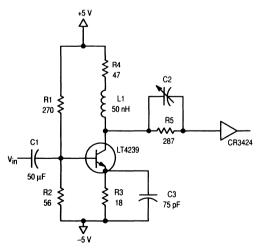

The CR3424 hybrid video amplifier solves the problem of video amplifier speed that has hitherto limited the performance of ultra-high resolution CRT monitors. The amplifier achieves less than 2.9ns rise and fall time for a 40V output swing. This note discusses the effect of the video amplifier on CRT picture quality, input characteristics of the CR3424, and two example drive circuits.

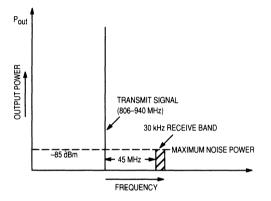

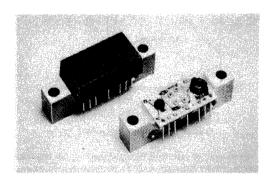

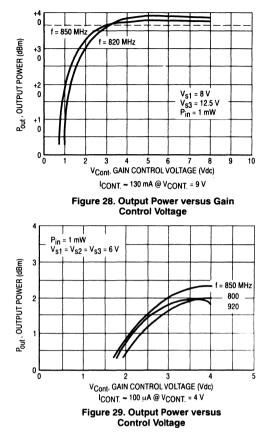

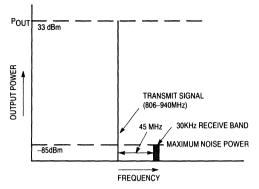

#### AN1106 Considerations in Using the MHW801 and MHW851 Series RF Power Modules

The MHW801 and MHW851 series of power modules are designed for use in cellular portable radios. A considerable amount of applications information is included in the data sheet; this note provides additional information concerning general electrical considerations, noise characteristics, gain control, circuit considerations and mounting.

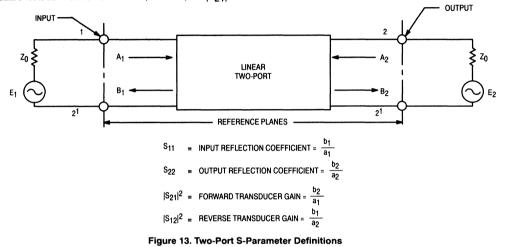

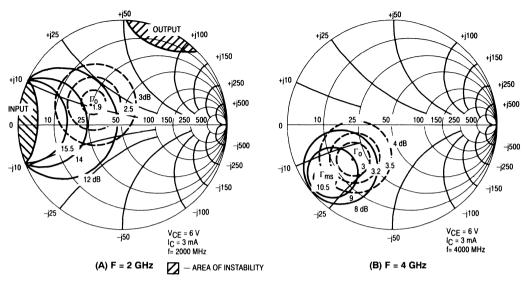

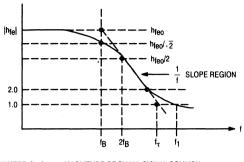

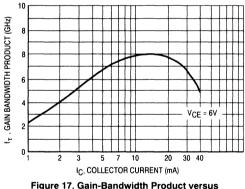

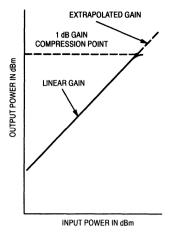

#### AN1107 Understanding RF Data Sheet Parameters

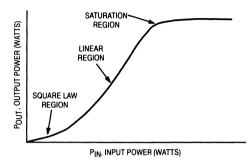

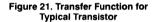

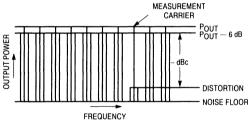

The data sheet is often the only source of information about the characteristics and capability of a product. This is especially true of RF devices, which have many unique specifications. It is therefore important that the manufacturer and designer speak a common language. This paper reviews the significance of the quoted values and highlights critical characteristics. Descriptions cover the procedures used to obtain impedance and thermal data, the importance of test circuits, low noise considerations and linearity requirements.

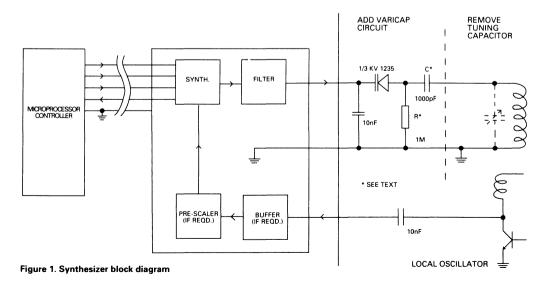

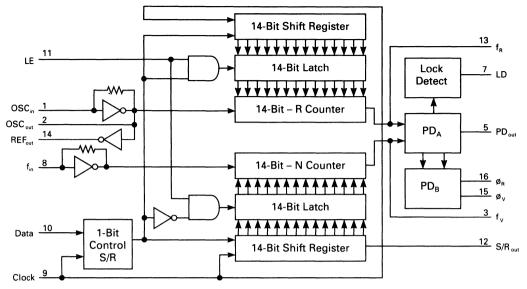

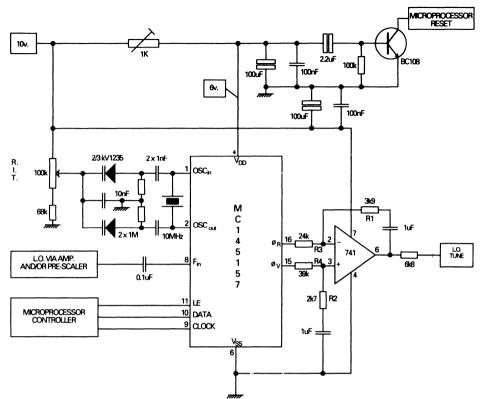

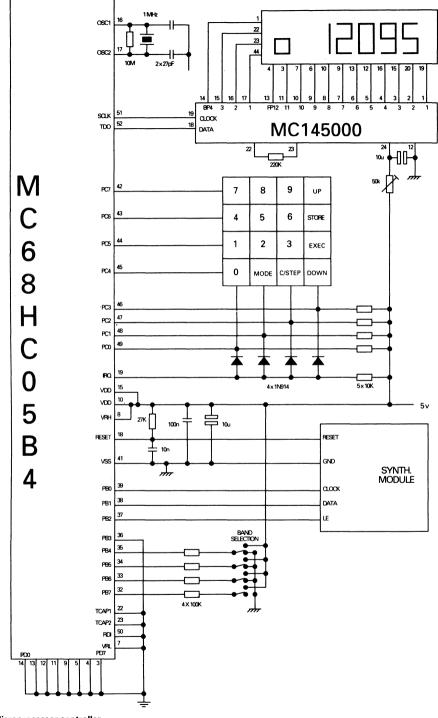

#### ANE416 MC68HC05B4 Radio Synthesizer

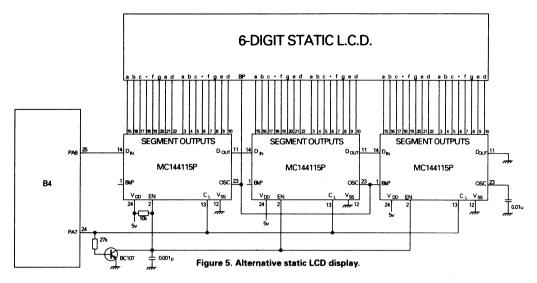

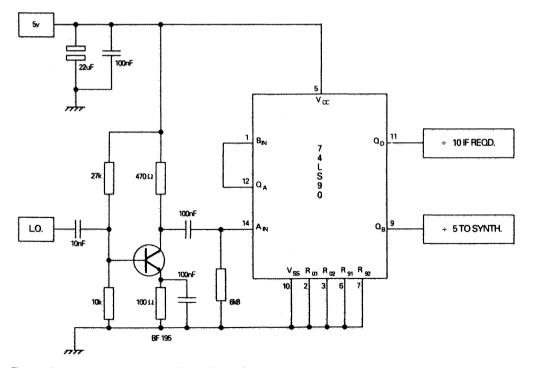

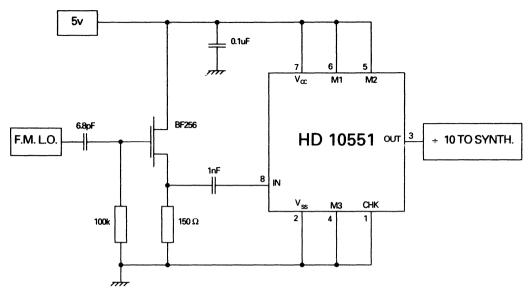

Synthesis of the local oscillator in a superheterodyne radio provides many advantages over mechanical tuning, including accuracy, stability and storing often-used frequencies. In this application, an MC145157 CMOS Synthesizer is controlled by an MC68HC05B4 MCU — the software is mask programmed in parts marked 'MC68HC05B4 DEMO', but could alternatively be programmed into an MC68HC05B6. A 6-digit LCD driver is controlled through the Serial Communications Interface, while the standby mode is used to eliminate interference with the radio.

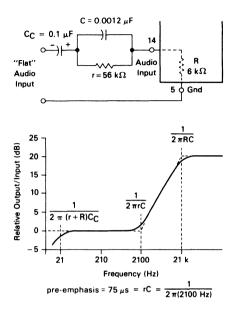

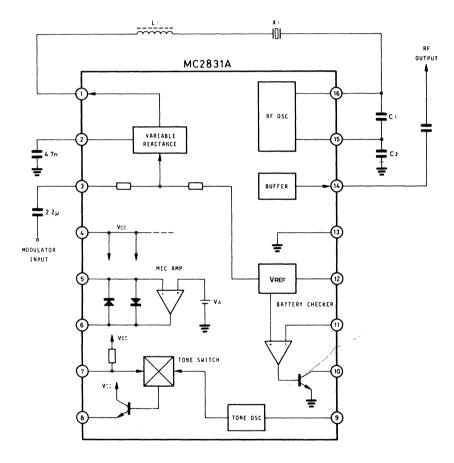

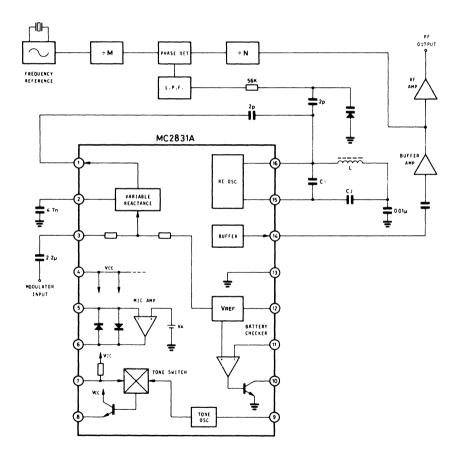

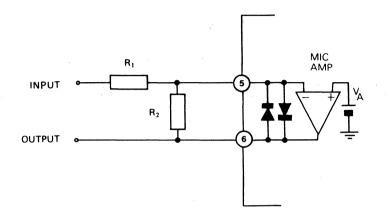

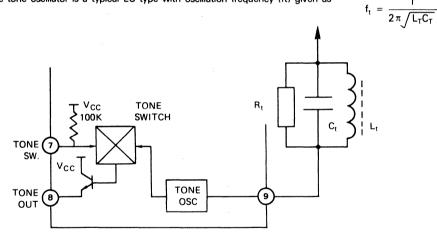

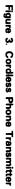

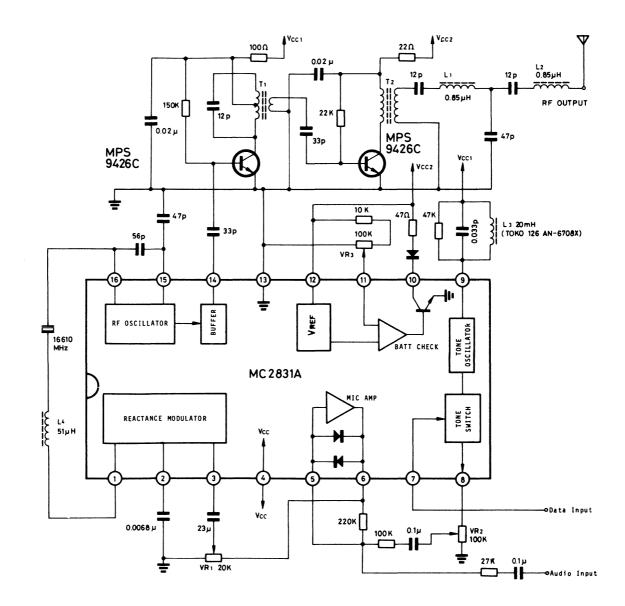

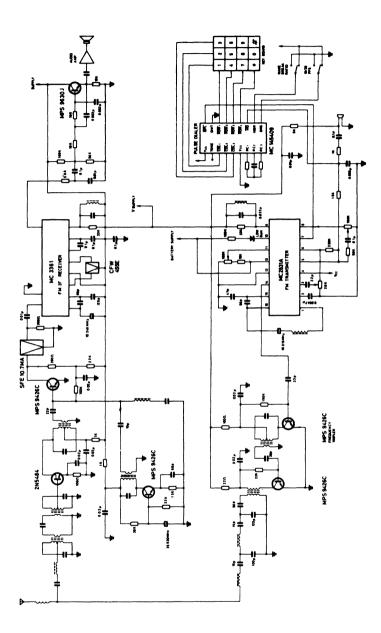

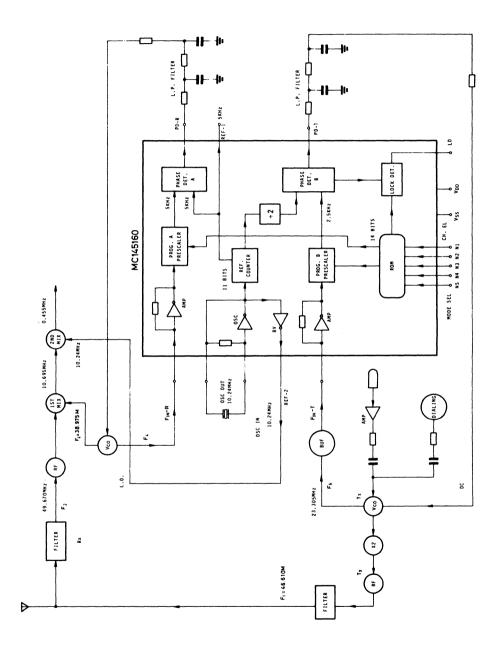

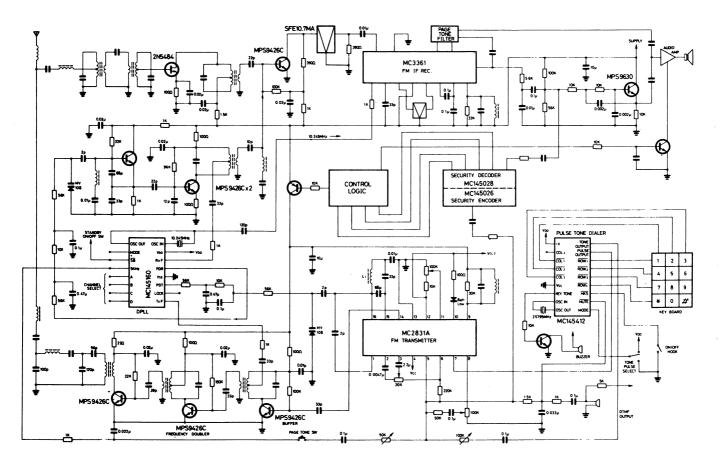

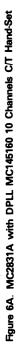

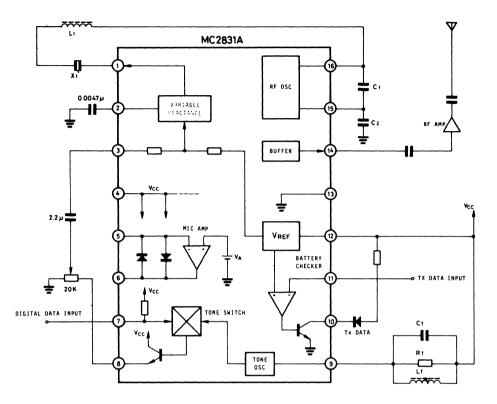

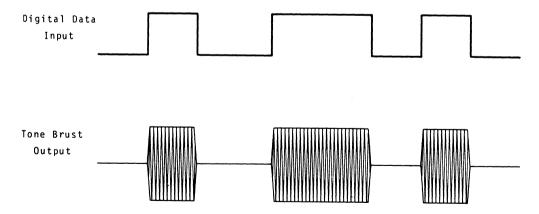

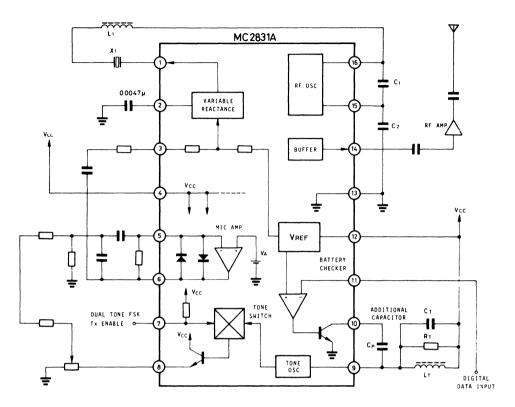

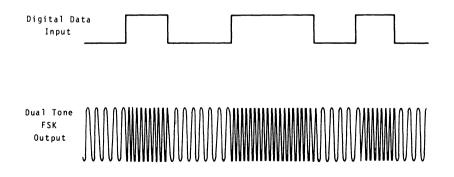

#### ANHK02 Low Power FM Transmitter System MC2831A

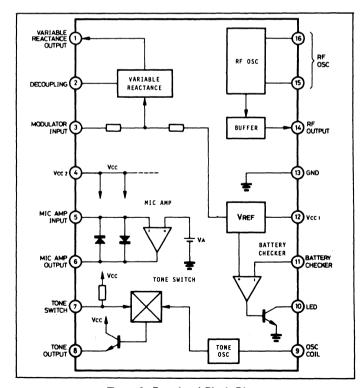

This application note provides information concerning the MC2831A, a one-chip low-power FM transmitter system designed for FM communication equipment such as FM transceivers, cordless telephones, remote control and RF data link.

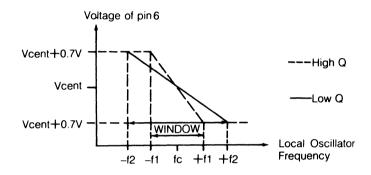

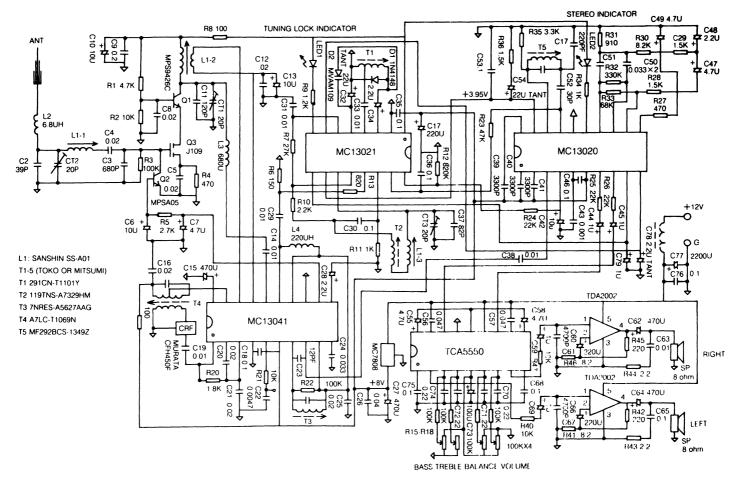

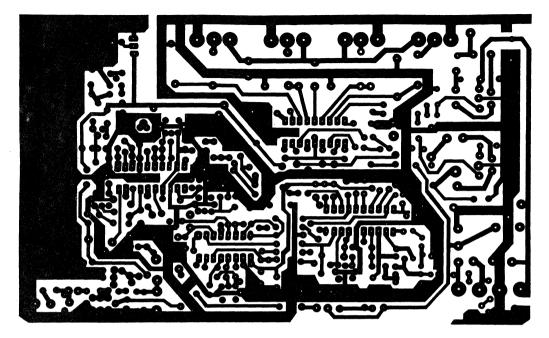

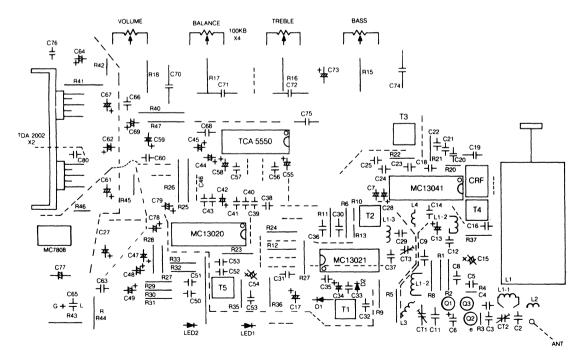

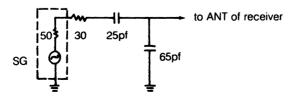

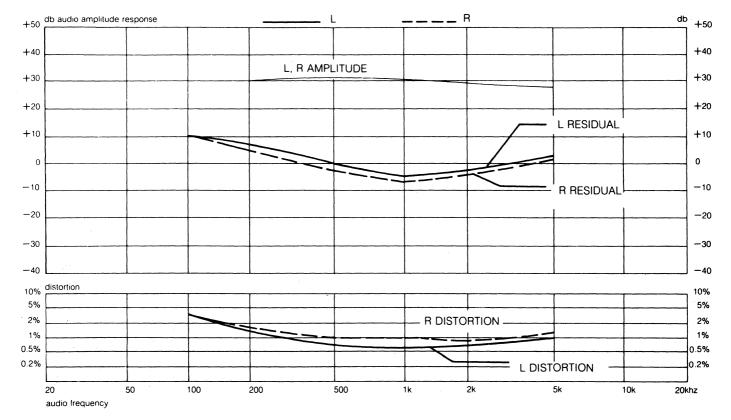

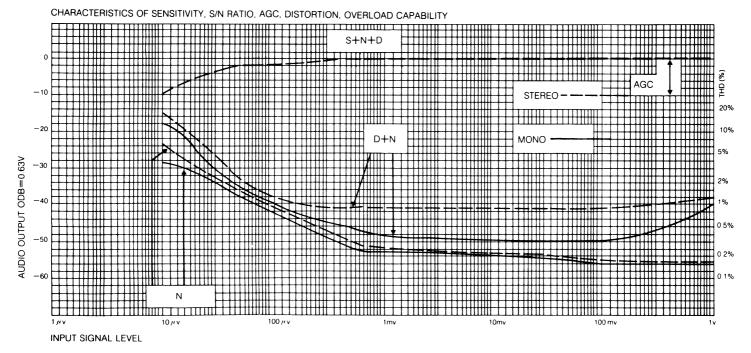

#### ANHK07 A High Performance Manual-Tuned Receiver for Automotive Application Using Motorola ICs MC13021, MC13020 and MC13041

This design is intended to provide radio engineers with a good start in automotive manually-tuned AM stereo receiver design. After discussing the most important principles of this type of receiver, a design is presented complete with circuit, PCB attwork and performance curves.

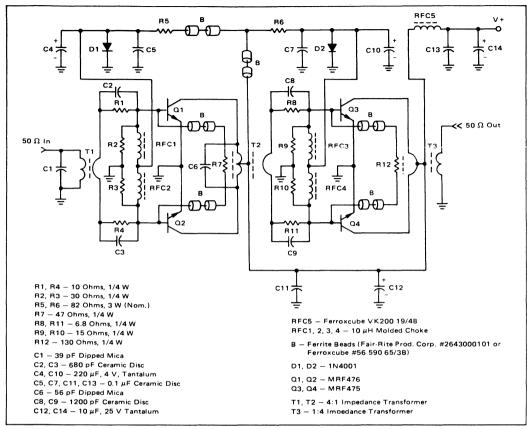

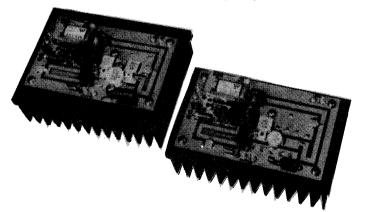

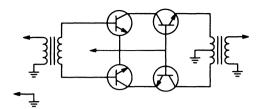

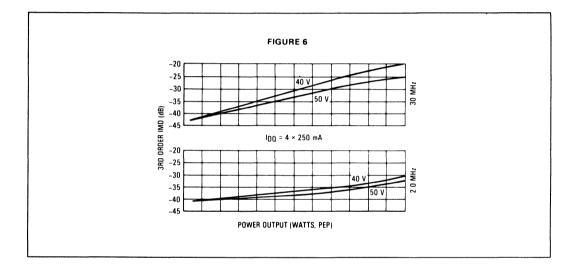

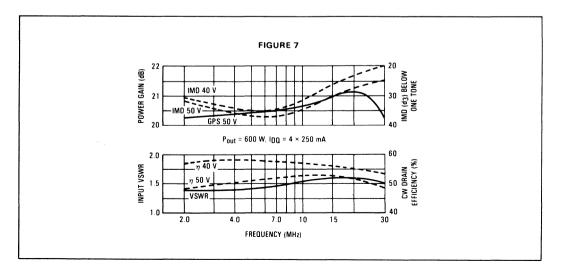

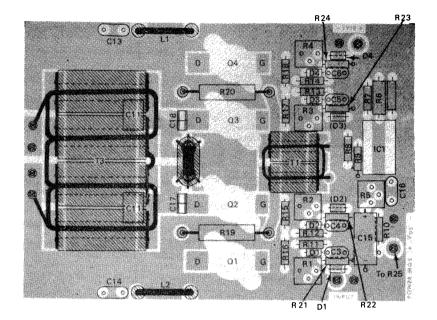

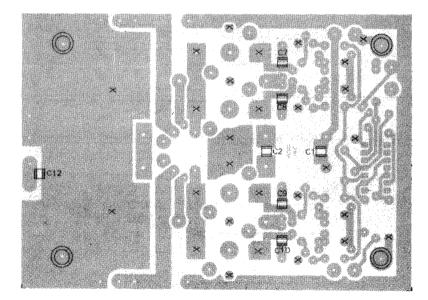

#### EB104 Get 600 Watts RF from Four Power FETs

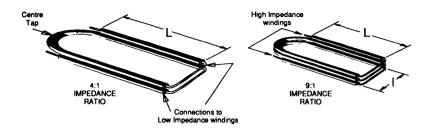

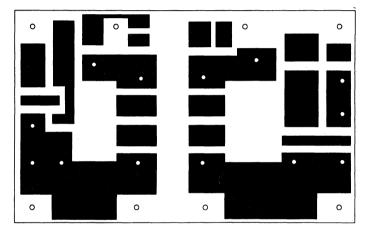

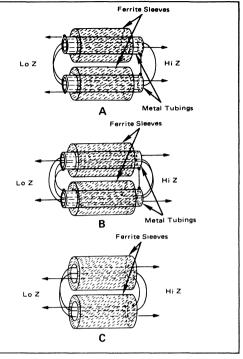

This unique push-pull/parallel circuit produces the power output of four devices without the loss and cost of power splitters and combiners. Full circuit details and PCB masters are provided for this MRF50 RF power FET design, including transformer details and performance analysis.

#### EB109 Low Cost UHF Device Gives Broadband Performance at 3.0 Watts Output

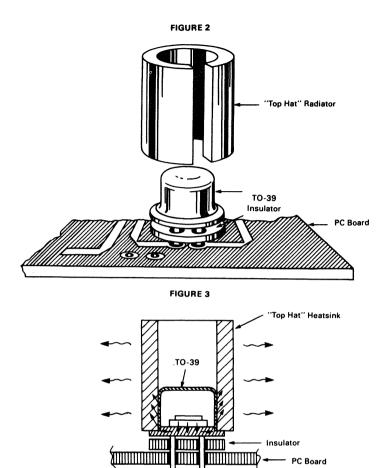

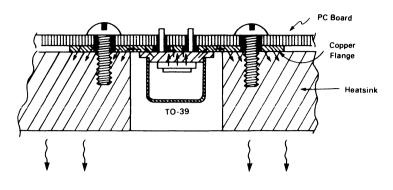

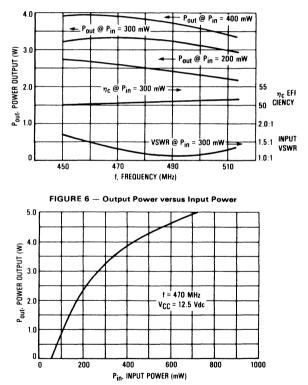

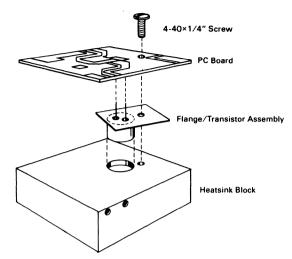

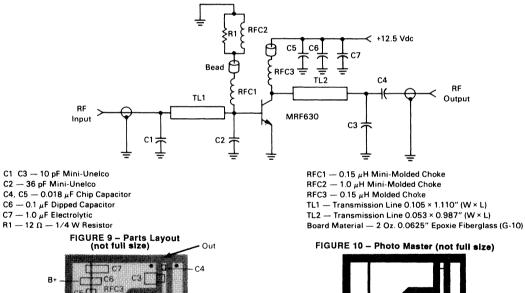

The package is the major cost in low to medium power RF transistors. Motorola introduced the common emitter TO-39 some years ago to limit cost increases. Good design and construction techniques can extend its use to broadband UHF amplifiers, like this broadband application of the low-cost MRF630, a transistor capable of 3W output power with 10dB gain at 512MHz. Emphasis is placed on mounting techniques.

## Applications Documents

### TV on-screen display using the MC68HC05T1

By Peter Topping Motorola Ltd., East Kilbride, Scotland

#### INTRODUCTION

The "T" members of the MC68HC05 family of MCUs provide a convenient and cost effective method of adding on-screendisplay (OSD) to TVs and VCRs. As well as the OSD capability, they include 8 Kbytes of ROM (adequate for Teletext, frequency-synthesis, stereo and OSD), 320 bytes of RAM, a 16-bit timer and 8 pulse-width-modulated D/A converters. The MC68HC(7)05T7/8 also includes IIC hardware and, by using a 56/64 pin package, 4 ports of I/O independent of the OSD, serial and D/A outputs. It is thus suitable for large fullfeature chassis. The MC68HC05T1 is in the middle of the price/performance range and includes most of the features of the MC68HC05T8 but in a 40-pin package. This is achieved by sharing I/O with the other pin functions (SPI, OSD, D/A). Even if all these features are used there is sufficient I/O for most applications. The low cost MC68HC05T4 has 5 Kbytes of ROM and 96 bytes of RAM making it suitable for simpler (mono, non-Teletext) applications.

#### 68HC05T1 OSD FEATURES

- Programmable display of 10 rows of 18 characters

- 24 byte (18 data + 6 control) single row architecture

- Settable in software to any one of four standards

- Zero inter-row and inter-column spacing

- 64 user-defined mask-programmable 8 x 13 characters

- Programmable horizontal position

- Character colour selectable from 4 colours/row

- Software programmable (start, stop and colour) window

- 4 character sizes (normal, double height and/or width)

- Half-dot character rounding

- Selectable half-dot black outline

#### **OSD CHARACTERISTICS**

The HC05TX series have an OSD capability of 10 rows of 18 characters. Each row can contain characters of four colours selected from the eight available colours (black, blue, green, cyan, red, magenta, yellow and white). The rows can independently select double height and/or double width and the start and stop positions of a background window of any colour. The signals sent to the TV are Red, Green, Blue, fast-blanking and half-tone. Separate horizontal and vertical synchronisation inputs are required.

The OSD architecture employed includes only a single line of display RAM. This makes the software more complicated but reduces the silicon area required to implement the OSD function. The software is required to update the display RAM on a regular basis. When operating in the 625-line PAL standard the updates must occur at 1.66 ms (26 lines) intervals in order to display adjacent lines. The OSD hardware can generate an interrupt when an update is required.

are 18 data registers (one for each character) and 6 control registers arranged as shown below. The table is for the T1, some of the control bits are different in the T4/7/8

- \$20-\$31 OSD Data registers

- \$32 CAS Read status, Write colours 1 & 2 and outline enable

- \$33 C34 Colours 3 & 4

- \$34 RAD Row address, character size, int\_enable, RGB invert.

- \$35 WCR OSD & PLL enable, Window enable and start column

- \$36 CCP Window colour and end column

- \$37 HPD Horizontal position, standard selection

The OSD display is timed from an on-chip 14 MHz oscillator which is phase locked to the TV's line synchronisation pulses. The vertical synchronisation depends on the standard in use. Four standards are available (15.75 kHz/60 Hz, 31.5 kHz/120 Hz, 15.625 kHz/50 Hz and 31.25 kHz/100 Hz). The standard is selected by control bits in the T1/2 but is automatic in the T4 and the T7/8.

64 OSD characters are mask programmed along with the user ROM. The spacing and full size of the characters is the same at

$8 \times 13$  (for 625-line standard). This allows continuous graphics. Half-dot interpolation hardware doubles the apparent resolution to produce smoother characters. A software selectable black outline (a half-dot wide) is also implemented in the hardware. Because the half-dot circuitry has to know the information for the next line of pixels, a 14th line is available in the character generator ROM to facilitate look ahead. The vertical height of a character is 26 lines (52 including interlace) and the horizontal width is 2 2/7  $\mu$ s (1/7  $\mu$ s per half pixel).

#### SOFTWARE

There are several approaches to writing OSD software to operate with the single line architecture. The choice will affect the amount of ROM and RAM used. One principle is to have a separate interrupt routine for each type of row to be displayed. This method will use little RAM but will be inefficient in its use of ROM. The other approach is to write a single interrupt routine which transfers display information from a block of normal RAM to the display RAM as it is required for each new line. This method will be more ROM efficient but requires a RAM location for every display character. The amount of RAM used depends on the maximum amount of data which has to be displayed at any one time. The choice between these two methods will depend on the type of data to be displayed. The first method may be better if much of the displayed data is fixed. This could be, for example, a series of menus. The second method will however be more appropriate if the data is mostly variable. This will usually be the case in conventional TV applications.

This application note describes an implementation of the second of the above approaches. A block of RAM is used to contain a copy of all the data to be displayed. The size of this block can be changed to reflect the number of rows and the number of characters per row. The choice made in the example described here is 8 rows of 16 characters. This is slightly less

than the maximum available and was chosen because the total number of characters (128) corresponds to the available page 1 RAM in the MC68HC05T1. The choice of 16 characters per row also slightly simplifies the software. The software allows any eight of the ten available rows to be used but only the first 16 of the 18 available characters. This choice does not prevent access to the right-hand-side of the screen as the display can be moved to the right under software control. The use of page 1 for the RAM does not incur any significant compromise in execution time. It also leaves free the page 0 RAM for the rest of the TV control software, which would be made less efficient if it had to use page 1 RAM, where direct addressing and bit manipulation instructions cannot be used. This choice slightly increases the ROM used by the OSD code, as 3-byte extended store instructions sometimes need to be used to write data to the RAM used for OSD characters.

The 1-byte indexed addressing mode can however be used in page 1. This addressing mode can access up to address \$1FE and is made use of in the example software. For example the OSDCLR routine used to initialise RAM locations used for OSD employs a CLR DRAM-1,X instruction. DRAM is the start of page 1 RAM at \$100 so DRAM-1 evaluates as \$FF a 1-byte offset

#### INTERRUPT ROUTINE

The OSD update interrupt routine (NLINE) shown in the program listing transfers data from page 1 RAM to display RAM each time an interrupt occurs. The first operation is to increment the pointer which selects the next row number. This pointer (OSDL) is subsequently used to transfer the appropriate data from page 1 RAM to the OSD RAM. So that any row number can be used the pointer selects the number from a table unique to each type of display. The appropriate table is determined by the value of LIND. The pointer is incremented until the corresponding row number is zero when the pointer is reset to zero. This allows any sub-set of up to 8 of the 10 available rows to be used. The next row number (ORed with the character size information contained in RAM) is written into the appropriate register (\$34). The row number in this register is compared by the OSD hardware with the current position of the raster. When they match, an interrupt is generated and the next interrupt routine is performed. The other control registers are then updated from the page 0 RAM locations, which are used for this purpose

To save RAM only three (RAD, CAS & CCR) of the six control registers are loaded in this way. The pointer OSDL is multiplied by 3 using the table M3, as this is guicker than shifting and adding. In this example the other registers are loaded by the main program and therefore have fixed values for each display. The fixed registers are Colour 3/4 (\$33), Window enable/start column (\$35) and Horizontal position delay (\$37). As this choice would not allow windows to be enabled on individual rows. window enable is controlled by the un-used bit (6) in the RAM byte used to update the Colour 1/2 register (CAS). This choice of fixed registers limits the flexibility of the display but clearly all registers can be updated on a line-by-line basis if more RAM is used. The limitations imposed by this choice are that colours 3 & 4, the window start column and the horizontal position apply to a whole display rather than to individual lines. In practice these constraints were not found to be significant restrictions for the displays required for TV use.

The interrupt routine then transfers the relevant OSD data from page 1 RAM into the OSD data registers. This is done using linear, repetitive code in order to minimise the time taken by the interrupt routine. The code used 8 cycles (4  $\mu$ s) for each byte transferred. Less ROM space would be utilised if a loop was employed but this would use 28 cycles per byte. The best choice depends on whether time or ROM use is more critical. The example code includes a cycle count to calculate the length of the interrupt routine. The time taken is 121 ± 4  $\mu$ s. This includes the time taken by the interrupt itself. An alternative method of OSD data transfer (TOSD2) using a loop is

included as comments in the listing. It would take an additional  $165 \, \mu s$ .

The last task performed by the interrupt routine is to control any character or window flashing. The software allows one or two characters (on a selected row) and one window (on the same or a different row) to be flashed at a rate determined by the MCU's timer. This function could be performed outwith the interrupt routine in the main program and the time taken to perform it is not included in the figure given above.

#### MAIN OSD PROGRAM

The remainder of the OSD control program does not write directly to most of the display registers. It simply puts the required display and control information into the blocks of RAM allocated for this purpose, together with supplying the coordinates of any required flashing characters or windows. It must, however, write to the display control registers not updated by the interrupt routine; in this example these are \$33, \$35 and \$37. The program has 4 main parts. These are the idle, channel name table, program/channel number and analogue displays. The idle display applies when no transient display (eg program number and channel number or name) is on. The OSD idle condition is selectable between blank and a small program number at the bottom right hand corner of the screen.

The OSD example program (assembler listing included) is just part of the code required to control a TV set. This program was incorporated in HC05T1 software along with four other modules. These were the base module (idle loop, transient control, locai keyboard, IR, IIC and 'reset), the tuning module (PLL, analogue and NVM control), the stereo module (stereoton and Nicam) and the Teletext module (FLOF level 1.5). The microprocessor in a TV application will usually need to handle the reception of IR commands. Polled methods of IR reception are most effective if the time made unavailable to them by interrupts is minimised. It is for this reason that the illustrated OSD interrupt routine was written to execute as fast as possible. This is, however, not so much of a problem if the TCAP facility is used for IR reception. When a falling edge occurs, the timer value is saved and it does not matter if the interrupt which processes this information is not serviced until several hundred microseconds later. The allowable size of this delay will of course depend on the IR protocol in use. The biphase protocol used with the example OSD software (transmitter chip: MC144105) has a minimum spacing of 1 ms between consecutive edges.

The next section describes the OSD features of this software. Some of the data used in the OSD is passed from other modules (particularly the tuning module) The same RAM allocation file was used in all modules so this part of the listing shows the locations used to pass data between them.

#### OSD FEATURES PROVIDED IN THE EXAMPLE PROGRAM

#### Program change

When keys 0-9, PC- or PC+ are pressed, the new program number appears (in cyan) at the bottom-right-hand corner of the screen in double height/double width characters and stays for 5 seconds after the last change. Above this display either the channel name (if one has been defined) or the channel number is shown (normal size). After 5 seconds this display times out and there is either no display or a permanent normal size program number display. This is selectable using the Teletext MIX key.

For program numbers of 10 and over, three keys are required. They are selected by first pressing "—" Two flashing dashes are displayed, the first 0-9 key (only 0-4 valid) will be taken as the tens digit and the second as the units digit. If a new program number has not been selected within 30 seconds, the TV returns to the previous display (nothing or the old program number).

#### **Channel mode**

When the P/C key is pressed, the program number and channel name (or number) is displayed for 5 seconds as an indication of the current status. If it is pressed again during this period, the TV changes to channel mode. This will remain for 30 seconds after the last key-press. The display (in yellow) shows the program number as in program mode along with the channel number. The channel number flashes to show that it will be changed if a number or PC- or PC+ key is pressed. New channels can be selected. If the STORE key is pressed then the current channel is stored against the current program number if no key is pressed for 30 seconds, the TV returns to program mode. If the channel has been changed but STORE not pressed then the TV will reture back to the channel stored against the current program.

#### Automatic search

When SEARCH is pressed the TV goes into the channel mode and the on screen display is as described above. The channel number is incremented at a rate of 2 per second until a signal is found. The search then stops. A press of STORE returns the TV to program mode, storing the new channel against the current program number.

#### Analogues

When any of the analogues are selected the appropriate logo is displayed along with a horizontal bar indicating the current value in the D/A convertor (full-scale 63). Display returns to default (nothing or program number) 5 seconds after the last change. If no analogue is selected the volume is shown (and adjusted) when the ANALOGUE +/- keys are used.

#### Channel name table

Up to 24 channels can have a 4 character name and standard bit associated with them. If the channel number and standard of one of these entries in the table correspond to those selected by the current program number then the name is displayed along with the program number when the program is selected or when P/C is pressed. Entry of names is done using the Teletext INDEX key. When it is pressed a table of six lines is displayed. Each line (identified by a "station" number in the leftmost column) contains a channel number, standard and the associated name. All of this data is user definable.

One character on the screen flashes to indicate the current position of the cursor. The character at the cursor position can be changed through 0-9, A-Z and space by pressing PC+ or PC- (0-9 for channel number digits and PAL/SECAM for standard). When a character (or the standard) is changed, its colour changes from yellow to red. The cursor is moved to the left and right by the Teletext RED and GREEN keys and up and down by the BLUE and YELLOW keys. The current line appears in a light blue (cyan) window as opposed to the dark blue window used for the other lines. The whole table scrolls when the cursor is required to go beyond the bottom (or top) of the current display.

To save a name the STORE key is pressed. This will save the name and standard on the current line against its channel number. This is indicated by the colour of any changed characters returning to yellow. Any changes which have been made to lines other than the one being stored are lost. Channel 00 cannot have a name. The procedure for removing a name from the table is to set the channel number to zero and then to save the line. Any name left on the line will not be used. The table display is exited by pressing the Teletext INDEX key. The function of each key is shown at the bottom of the display.

#### EXAMPLE PROGRAM

| 1                                    |                         |                                                                                                                                                                                                |

|--------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 ***                                | *******                 | ***************************************                                                                                                                                                        |

| 4 *<br>5 *                           | т                       | TV/Teletext/OSD/Stereo program (MC68HC05T1/8). *                                                                                                                                               |

| 6 *                                  |                         | On-Screen-Display module *                                                                                                                                                                     |

| 9 * 1<br>10 *                        | No liability            | *<br>e was developed by Motorola Ltd. for demonstration purposes. *<br>y can be accepted for its use in any specific application. *<br>al software copyright Motorola - all rights reserved. * |

| 11 *<br>12 *                         |                         | P. Topping 25th May '90 *                                                                                                                                                                      |

| 13 *<br>14 ***                       | * * * * * * * * * * * * | *<br>************************************                                                                                                                                                      |

| 15                                   |                         |                                                                                                                                                                                                |

| 17                                   |                         |                                                                                                                                                                                                |

| 18<br>19                             | IMPORT                  | CHEX, CBCD, READ, WRITE, CDISP2                                                                                                                                                                |

| 20<br>21<br>22                       |                         | NLINE, PCOSD, DRAM, ANOSD, PRDŞP, CHST<br>CUP, CDWN, CLFT, CRGT, PLUS, MINUS, SAVE, OSDLE, OSDEF                                                                                               |

| 23                                   | LIB                     | RAMT1.S05                                                                                                                                                                                      |

| 23<br>23                             | SECTION                 | N.S.RAM,COMM                                                                                                                                                                                   |

| 23 ***<br>23 *                       | ********                | ******                                                                                                                                                                                         |

| 23 *                                 | Telete:                 | xt RAM allocation. *                                                                                                                                                                           |

| 23 *<br>23 ***                       | **********              | *                                                                                                                                                                                              |

| 23                                   |                         |                                                                                                                                                                                                |

| 23 00000000 SUB<br>23 00000001 R1    | 1 RMB<br>RMB            | l<br>1 mode register                                                                                                                                                                           |

| 23 00000002 R2<br>23 00000003 R3     | RMB                     | 1 page request address register                                                                                                                                                                |

| 23 00000004 C1                       | RMB<br>RMB              | l page req. data reg. col. 0 : mag.<br>l """ 1 : pgt.                                                                                                                                          |

| 23 00000005 C2                       | RMB                     | 1 " " " " 2 : pgu.                                                                                                                                                                             |

| 23 00000006 C3<br>23 00000007 C4     | RMB<br>RMB              | 1 " " " " " 3 : ht.                                                                                                                                                                            |

| 23 0000008 C5                        | RMB                     | 1 " " " " 5 : mt.                                                                                                                                                                              |

| 23 0000009 C6                        | RMB                     | 1 " " " " 6 : mu.                                                                                                                                                                              |

| 23 000000a SUB.<br>23 000000b R4     | 2 RMB<br>RMB            | l<br>l display chapter register                                                                                                                                                                |

| 23 000000c R5                        | RMB                     | 1 display control register (normal)                                                                                                                                                            |

| 23 0000000d R6<br>23 0000000e R7     | RMB                     | <pre>l display control register (news/sub)</pre>                                                                                                                                               |

| 23 0000000e R7<br>23 0000000f SUB    | RMB<br>3 RMB            | l display mode register                                                                                                                                                                        |

| 23 0000010 R8                        | RMB                     | active chapter register                                                                                                                                                                        |

| 23 00000011 R9<br>23 00000012 R10    | RMB<br>RMB              | 1 active row register<br>1 active column register                                                                                                                                              |

| 23 00000013 R11                      | RMB                     | l active column∢register<br>1 active data register                                                                                                                                             |

| 23 00000014 PH                       | RMB                     | 1 2nd " "                                                                                                                                                                                      |

| 23 00000015 PT<br>23 00000016 PU     | RMB<br>RMB              | 1 3rd " "<br>1 4th " "                                                                                                                                                                         |

| 23 00000017 LIF                      | RMB                     | 9 LINKED PAGE No. LIFO BUFFER                                                                                                                                                                  |

| 23 0000020 PAG<br>23 0000027 PAG     |                         | 7 PAGE NO. INPUT BUFFER                                                                                                                                                                        |

| 23 00000027 PAG<br>23 0000002a PAG   |                         | 3 ACO PAGE No.<br>3 ACI PAGE No.                                                                                                                                                               |

| 23 000002d PAG                       | 2 RMB                   | 3 AC2 PAGE No.                                                                                                                                                                                 |

| 23 00000030 PAG<br>23 00000033 PAG   |                         | 3 AC3 PAGE No.<br>3 CYAN PAGE No.                                                                                                                                                              |

| 23 00000036 PAG                      |                         | 3 INDEX PAGE NO.                                                                                                                                                                               |

| 23 00000039 PDP<br>23 0000003a ACC   | RMB                     | 1 PAGE DIGIT POINTER                                                                                                                                                                           |

| 23 0000003a ACC<br>23 0000003e WAC   | RMB<br>C RMB            | 4 DISP, RED, GREEN, YELLOW AC. CIR.<br>1 WORKING ACC No.                                                                                                                                       |

| 23 0000003f ADDI                     | RMB                     | 1 IIC ADDRESS                                                                                                                                                                                  |

| 23 00000040 DPN<br>23 00000041 SUBJ  | C RMB<br>ADR RMB        | 1 IIC DATA POINTER FOR WRITE<br>1 IIC SUB-ADDRESS                                                                                                                                              |

| 23 00000C42 IOB                      |                         | 4 IIC BUFFER, +2 4 +3 RSRVD FOR PLL                                                                                                                                                            |

| 23 00000046 STA                      | 12 RMB                  | 1 0: ROW24 FETCH FLAG                                                                                                                                                                          |

| 23 *<br>23 *                         |                         | 1: REMOTE REPEATING<br>2: SEARCH/STANDBY IIC LOCK                                                                                                                                              |

| 23 *                                 |                         | 3: STANDBY STATUS                                                                                                                                                                              |

| 23 *<br>23 *                         |                         | 4: UPDATE PENDING                                                                                                                                                                              |

| 23 *                                 |                         | 5: DIFFERENCE FOUND<br>6: NO TELETEXT TRANSMISSION                                                                                                                                             |

| 23 *                                 |                         | 7: MIXED                                                                                                                                                                                       |

| 23 00000047 LINI<br>23 00000048 STAT |                         | 1 LINK OPTIONS<br>1 0: CYAN LINK ON                                                                                                                                                            |

| 23 *                                 |                         | 1: YELLOW LINK ON                                                                                                                                                                              |

| 23 *<br>23 *                         |                         | 2: GREEN LINK ON                                                                                                                                                                               |

| 2.3                                  |                         | 3: LINKS/ROW24 ON                                                                                                                                                                              |

| 23<br>23                   | ******           | *******    | ******* | ***************************************                                |

|----------------------------|------------------|------------|---------|------------------------------------------------------------------------|

| 23                         | *                | General    | RAM all | location. *                                                            |

| 23                         | *                |            |         | *                                                                      |

| 23<br>23                   | *****            | *******    | ******* | ***************                                                        |

| 23 00000049                | PLLHI            | RMB        | 1       | PLL DIVIDE RATIO MSB                                                   |

| 23 0000004a                | PLLOW            | RMB        | 1       | PLL DIVIDE RATIO LSB                                                   |

| 23 000004b<br>23 000004c   | W1               | RMB        | 1       | WORKING                                                                |

| 23 0000042<br>23 000004d   | W2<br>W3         | RMB<br>RMB | 1       |                                                                        |

| 23 0000004e                | COUNT            | RMB        | 1       | LOOP COUNTER                                                           |

| 23 0000004f                | KOUNT            | RMB        | 1       | LOCAL KEYBOARD COUNTER                                                 |

| 23 00000050                | CNT              | RMB        | 1       | 12.8mS (inc, free running)                                             |

| 23 00000051<br>23          | CNT1<br>*CNT2    | RMB<br>RMB | 1<br>1  | 12.8mS (inc, reset every 1S during transient)                          |

| 23 00000052                | CNT3             | RMB        | i       | 3.25 S (inc, store timeout)<br>3.25 S (dec, automatic standby timeout) |

| 23 0000053                 | CNT4             | RMB        | 1       | 12.8mS (cleared for row24 delay when page arrives)                     |

| 23 00000054<br>23 00000055 | CNT5             | RMB        | 1       | 12.8mS (inc, transient mute)                                           |

| 23 00000056                | TMR<br>STAT      | RMB<br>RMB | 1       | TRANSIENT DISPLAY SECONDS COUNTER<br>0: TV/TELETEXT                    |

| 23                         | *                | NHD        | •       | 1: IIC R/W                                                             |

| 23                         | * 1              |            |         | 2: HOLD                                                                |

| 23                         | *                |            |         | 3: IR REPEAT INHIBIT                                                   |

| 23<br>23                   | *                |            |         | 4: TRANSIENT DISPLAY ON<br>5: TIME HOLD                                |

| 23                         | *                |            |         | 6: SUB-PAGE MODE                                                       |

| 23                         | *                |            |         | 7: IR TASK PENDING                                                     |

| 23 00000057                | STAT4            | RMB        | 1       | 0: KEY FUNCTION PERFORMED                                              |

| 23                         | *                |            |         | 1: LOCAL REPEATING<br>2: P/C PROG : 0, CHAN : 1                        |

| 23                         | *                |            |         | 3: MUTE (TRANSIENT)                                                    |

| 23                         | *                |            |         | 4: OSD STATUS TRANSIENT                                                |

| 23<br>23                   | *                |            |         | 5: MUTE (BUTTON)<br>6: Coincidence Mute                                |

| 23                         | *                |            |         | 5: COINCIDENCE MUTE<br>7: SEARCH                                       |

| 23 00000058                | PWR              | RMB        | 1       | \$55 AT RESET, \$AA NORMALLY                                           |

| 23 00000059                | PROG             | RMB        | 1       | CURRENT PROGRAM NUMBER                                                 |

| 23 0000005a<br>23 0000005b | CHAN<br>DISP     | RMB<br>RMB | 1       | CURRENT CHANNEL NUMBER                                                 |

| 23 0000005c                | FTUNE            | RMB        | 1       | CURRENT DÍSPLAY NUMBER<br>Fine tuning register                         |

| 23 000005d                 | AVOL             | RMB        | ĩ       | VOLUME LEVEL                                                           |

| 23 0000005e                | KEY              | RMB        | 1       | CODE OF PRESSED KEY (LOCAL)                                            |

| 23 0000005f<br>23 00000063 | NUMO<br>IRRA1    | RMB<br>RMB | 4       | LED DISPLAY RAM                                                        |

| 23 00000064                | IRRA1            | RMB        | 1       | IR INTERRUPT TEMP.                                                     |

| 23 00000065                | IRRA3            | RMB        | ī       |                                                                        |

| 23 00000066                | IRRA4            | RMB        | 1       |                                                                        |

| 23 00000067<br>23 00000068 | DIFFH<br>DIFFL   | RMB<br>RMB | 1       | IR TIME DIFFERENCE                                                     |

| 23 00000069                | IRH              | RMB        | 1       | IR CODE BIT                                                            |

| 23 0000006a                | IRL              | RMB        | 1       | COLLECTION                                                             |

| 23 000006b                 | IRCODE           |            | 1       |                                                                        |

| 23 0000006c<br>23 0000006d | IRCNT<br>IRCMCT  | RMB<br>RMB | 1<br>1  |                                                                        |

| 23 0000006e                | OLDIR            | RMB        | 1       |                                                                        |

| 23                         | *****            | *******    | ******  | *******                                                                |

| 23                         | *                |            |         | *                                                                      |

| 23<br>23                   | *                | RAM all    | ocation | for Stereoton. *                                                       |

| 23                         | *****            | *******    | ******  | ****                                                                   |

| 23                         |                  |            |         |                                                                        |

| 23 0000006f                | POLLTM           | RMB        | 1       | Poll timer                                                             |

| 23 00000070<br>23 00000071 | TONEA<br>LBAL    | RMB<br>RMB | 1       | Tone (unadjusted for loudness)<br>Loudspeaker balance variable         |

| 23 00000072                | LVL              | RMB        | î       | Loudspeaker left volume (reg 1)                                        |

| 23 00000073                | LVR              | RMB        | 1       | Loudspeaker right volume (reg 2)                                       |

| 23 00000074                | HVL              | RMB        | 1       | Headphone volume left (reg 3)                                          |

| 23 00000075<br>23 00000076 | HVR<br>TONE      | RMB<br>RMB | 1<br>1  | Headphone volume right (reg 4)<br>Tone variable (Bass/Treble) (reg 5)  |

| 23 00000077                | MATRIX           | RMB        | i       | Current matrix (reg 6)                                                 |

| 23 00000078                | MATNO            | RMB        | 1       | Present mode (mono/stereo/lan 1/11.12/12.11)                           |

| 23 00000079                | WS1              | RMB        | 1       | Workspace 1 (no interrupt useage                                       |

| 23 0000007a<br>23          | WS2              | RMB        | 1       | Workspace 2 for these please)                                          |

| 23<br>23 0000007b          | VAV              | RMB        | 1       |                                                                        |

| 23                         |                  |            |         |                                                                        |

| 23 0000007c                | MONCNT           | RMB<br>RMB | 1       | Mono ident count Ident detection                                       |

| 23 0000007d<br>23 0000007e | STECNT<br>DULCNT | RMB<br>RMB | 1       | Stereo ident count variables<br>Dual lang ident count                  |

| 23 0000007f                | ERRCNT           | RMB        | i       | Error ident count                                                      |

| 23 00000080                | RCOUNT           |            | 1       | Ident countdown                                                        |

| 23 0000081<br>23           | RANGE            | RMB        | 1       | Total ident poll number                                                |

| 23 00000082                | TEMP             | RMB        | 1       |                                                                        |

|                            |                  |            | -       |                                                                        |

| 23 |                      |              |            |              |                                                           |                 |

|----|----------------------|--------------|------------|--------------|-----------------------------------------------------------|-----------------|

|    | 0000083              | STAT5        | RMB        | 1            | 0: LOUDNESS                                               |                 |

| 23 |                      | *            |            | -            | 1: VCR                                                    |                 |

| 23 |                      | *            |            |              | 2: OSD NAME TABLE                                         |                 |

| 23 |                      | *            |            |              | 3: OSD DEFAULT P/C NUMBER                                 |                 |

| 23 |                      | *            |            |              | 4: ANALOGUE OSD ON                                        |                 |

| 23 |                      | *            |            |              | 5: NAME-TABLE STANDARD                                    |                 |

| 23 |                      | *            |            |              | 6: STANDARD CHANGED                                       |                 |

| 23 |                      | *            |            |              | 7: RE-INITIALISE TELETEXT                                 |                 |

| 23 |                      |              |            |              |                                                           |                 |

|    | 0000084              | STAT6        | RMB        | 1            | 0: 2-DIGIT PROGRAM ENTRY                                  |                 |

| 23 |                      |              |            |              |                                                           |                 |

| 23 | 0000085              | TMPRG        | RMB        | 1            | TEMPORARY PROGRAM NUMBER                                  |                 |

| 23 |                      | ******       | *******    | *******      | * * * * * * * * * * * * * * * * * * * *                   | ****            |

| 23 |                      | *            |            |              |                                                           | *               |

| 23 |                      | *            | OSD RAM    | allocat      | ion.                                                      | *               |

| 23 |                      | *            |            |              |                                                           | *               |

| 23 |                      | ******       | *******    | *******      | * * * * * * * * * * * * * * * * * * * *                   | * * * * *       |

| 23 |                      |              |            |              |                                                           |                 |

|    | 00000086             | CASI         | RMB        | 1            | ROW 1, colour 1/2 & outline                               |                 |

|    | 0000087              | RAD1         |            | 1            | Row address & character siz                               | e               |

|    | 0000088              | CCR1         |            | 1            | Window colour & end column                                |                 |

|    | 0000089              | CAS2         |            | 1            | ROW 2, colour 1/2 & outline                               |                 |

|    | 0000008a             | RAD2         | RMB        | 1            | Row address & character siz                               | e               |

|    | 000008Ъ              | CCR2         | RMB        | 1            | Window colour & end column                                |                 |

|    | 0000008c<br>0000008d | CAS3         | RMB        | 1            | ROW 3, colour 1/2 & outline                               |                 |

|    |                      | RAD3         |            | 1            | Row address & character siz                               | e               |

|    | 0000008e<br>0000008f | CCR3         | RMB        | 1            | Window colour & end column<br>ROW 4, colour 1/2 & outline | anable          |

|    | 00000090             | CAS4<br>RAD4 | rme<br>Rme | 1            | Row address & character siz                               | enable          |

|    | 00000091             | CCR4         | RMB        | 1            | Window colour & end column                                |                 |

|    | 00000092             | CAS5         | RMB        | 1            | ROW 5, colour 1/2 & outline                               | enable          |

|    | 00000093             | RAD5         | RMB        | i            | Row address & character siz                               | enabre<br>e     |

|    | 00000094             | CCR5         | RMB        | î            | Window colour & end column                                |                 |

|    | 00000095             | CAS6         | RMB        | ī            | ROW 6, colour 1/2 & outline                               | enable          |

|    | 00000096             | RAD6         | RMB        | ī            | Row address & character siz                               |                 |

|    | 00000097             | CCR6         | RMB        | ī            | Window colour & end column                                |                 |

| 23 | 0000098              | CAS7         | RMB        | ī            | ROW 7, colour 1/2 & outline                               | enable          |

| 23 | 00000099             | RAD7         | RMB        | ī            | Row address & character siz                               |                 |

| 23 | 0000009a             | CCR7         | RMB        | 1            | Window colour & end column                                |                 |

|    | 000009Ъ              | CAS8         | RMB        | 1            | ROW 8, colour 1/2 & outline                               | enable          |

|    | 000009c              | RAD8         | RMB        | 1            | Row address & character siz                               | e               |

|    | D000009d             | CCR8         | RMB        | 1            | Window colour & end column                                |                 |

| 23 |                      |              |            |              |                                                           |                 |

|    | 000009e              | OSDL         | RMB        | 1            | CURRENT OSD ROW POINTER                                   |                 |

|    | 1600000              | LIND         | RMB        | 1            | ROW TABLE INDEX                                           |                 |

|    | 000000a0             | BROW         | RMB        | 1            | CHARACTER FLASH ROW                                       |                 |

|    | 000000a1             | BCOL         | RMB        | 1            | CHATACTER FLASH COLUMNS                                   |                 |

| 23 | 000000a2             | WROW         | RMB        | 1            | WINDOW FLASH ROW                                          |                 |

| 23 |                      | *ROW1        | RMB        | 1            | FIRST ROW No. (NAME TABLE)                                |                 |

|    | 000000a3             | ANAL         | RMB        | 1            |                                                           |                 |

|    | 000000a4             | ANAF         | RMB        | 1            |                                                           |                 |

| 23 | 0000004              | ANA          | Nº1D       | 1            |                                                           |                 |

|    | 00000a5              | TEMP 2       | RMB        | 1            |                                                           |                 |

| 23 |                      |              |            | -            |                                                           |                 |

| 23 | 000000a6             |              | RMB        | 3            | UNUSED                                                    |                 |

| 23 |                      |              | _          |              |                                                           |                 |

| 23 | 000000a9             | STACK        | RMB        | 22           | 23 BYTES USED FOR STACK                                   |                 |

|    | 000000bf             | SP           | RMB        | 1            | (1 INTERRUPT AND 9 NESTED S                               | UBS)            |

| 23 |                      |              |            |              |                                                           |                 |

| 23 |                      |              |            |              |                                                           |                 |

|    | 0000000              | KEYI         | EQU        | \$00         |                                                           |                 |

|    | 0000000              | KEYO         | EQU        | \$00         |                                                           |                 |

| 23 | 0000000              | KEYIO        | EQU        | \$00         |                                                           |                 |

| 23 | 0000003              | SERO         | EQU        | \$03         |                                                           |                 |

| 23 |                      |              |            |              | - (                                                       |                 |

|    | 0000000a             | VOLU         | EQU        | \$0A         | D/A 2 JP08 IN EVB                                         |                 |

|    | 000000b              | CONT         | EQU        | \$0B         | D/A 3 JP09 IN EVB                                         |                 |

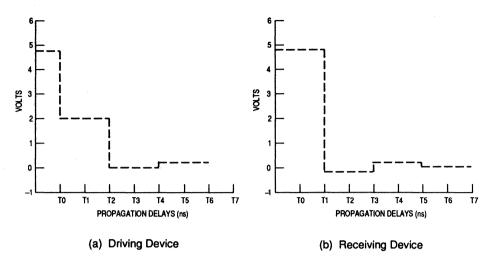

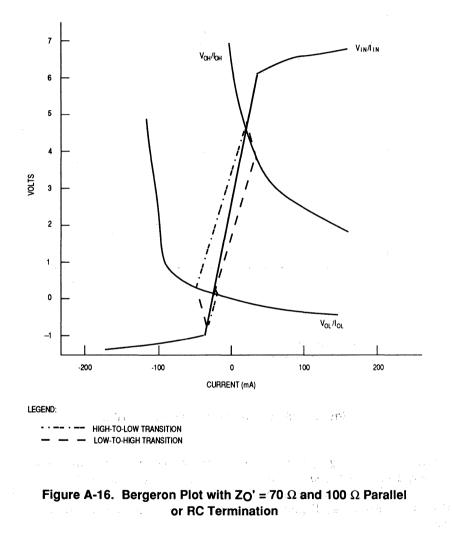

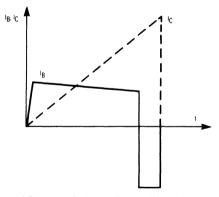

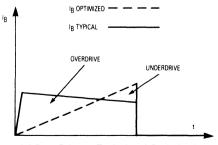

|    | 000000c              | BRIL         | EQU        | \$0C         | D/A 4 JP10 IN EVB<br>D/A 5 JP11 IN EVB                    |                 |