# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

MC145488

# **Dual Data Link Controller (DDLC)**

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any products relembly the prove reliability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, the indication of the support of the statement of the support of the sup subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and @ are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

### **TABLE OF CONTENTS**

| aragraph<br>Number | Title                               | Page<br>Number |

|--------------------|-------------------------------------|----------------|

|                    | Section 1<br>Overview               |                |

| 1.1                | Intoduction                         | 1-1            |

| 1.2                | Features                            | 1-1            |

| 1.3                | DDLC Overview                       | 1-2            |

| 1.4                | HDLC Protocol Overview              | 1-2            |

|                    |                                     |                |

|                    | Section 2 Block Diagram Description |                |

| 2.1                | Transmit Bit Handler                | 2-1            |

| 2.1.1              | Packet Operation                    | 2-1            |

| 2.1.1.1            | State Diagram                       | 2-2            |

| 2.1.1.2            | Abort Character                     | 2-3            |

| 2.1.1.3            | Flow Control Mechanisms             | 2-3            |

| 2.1.1.3.1          | ISDN D-Channel Contention           | 2-3            |

| 2.1.1.3.2          | Modem Flow Control                  | 2-4            |

| 2.1.1.4            | Interrupts                          | 2-4            |

| 2.1.2              | Transmit FIFO                       | 2-4            |

| 2.1.3              | Transparent Operation               | 2-4            |

| 2.1.4              | Interfram Time Fill                 | 2-5            |

| 2.2                | Receive Bit Handler                 | 2-5            |

| 2.2.1              | Packet Operation                    | 2-5            |

| 2.2.1.1            | State Diagram                       | 2-5            |

| 2.2.1.2            | Non-Octet Aligned Packets           | 2-5            |

| 2.2.1.3            | Address Recognition (Filtering)     | 2-6            |

| 2.2.2              | Receive FIFO                        | 2-6            |

| 2.2.3              | Transparent Operation               | 2-7            |

| 2.2.4              | Interrupts                          | 2.7            |

| 2.3                | DMA Conntroller                     | 2-7            |

| 2.3.1              | DMA Operation                       | 2-7            |

| 2.3.2              | Buffer Descriptions                 | 2-8            |

| 2.3.2.1            | Transmit Buffer Descriptors         | 2-8            |

| 2.3.2.2            | Receive Buffer Descriptors          | 2-8            |

| 2.3.2.3            | Address Expansion                   | 2-9            |

| 2.3.3              | Transmit Channel Operation          | 2-10           |

| 2.3.4              | Receive Channel Operation           | 2-11           |

| 2.4                | Microprocessor Interface            | 2-11           |

|                    |                                     |                |

| 2.4.1              | System Slave Mode                   | 2-12           |

### **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                        | Page<br>Number |

|---------------------|----------------------------------------------|----------------|

| 2.4.3               | Interrupt Operation                          | 2-13           |

| 2.5                 | Serial Interface                             | 2-13           |

| 2.6                 | Serial Control Port                          | 2-13           |

| 2.7                 | Timer                                        | 2-13           |

| 2.7.1               | Watchdog Timer                               | 2-14           |

| 2.8                 | Power Consumptions                           | 2-14           |

|                     |                                              |                |

|                     | Section 3 Register Descriptions              |                |

| 3.1                 | System Control Register                      | 3-1            |

| 3.1                 | Master Status Register (Interrupt Vector)    | 3-1            |

| 3.3                 | Interrupt Enable Register                    | 3-2            |

| 3.4                 | SCP Status/Control Register & Tx/Rx Register | 3-3<br>3-4     |

| 3.5                 | Timer Register                               | 3-4            |

| 3.6                 | Serial Interface Control Register            | 3-6            |

| 3.7                 | Transmit Control Register                    | 3-8            |

| 3.8                 | Receive Control Register                     | 3-9            |

| 3.9                 | Transmit Status Register                     | 3-10           |

| 3.10                | Receive Status Register                      | 3-11           |

| 3.11                | Address Compare Register                     | 3-13           |

| 3.12                | Address Wildcard Bit Register                | 3-14           |

| 3.13                | CRC Error Count Register                     | 3-14           |

| 3.14                | DMA Base Address Registers                   | 3-14           |

| 3.15                | Transmit Frame Length Register               | 3-15           |

| 3.16                | Receive Buffer Length Register               | 3-15           |

| 3.17                | Receive Frame Length Register (Read Only)    | 3-15           |

| 3.18                | Transmit Byte Count (Read Only)              | 3-15           |

|                     |                                              |                |

|                     | Section 4 Signal Descriptions                |                |

| 4.1                 | MPU Interface Pins                           | 4-1            |

| 4.1.1               | 68000 Operation                              | 4-1            |

| 4.1.1.1             | Address and Data Bus                         | 4-2            |

| 4.1.1.2             | Control Buss                                 | 4-2            |

| 4.1.1.3             | Bus Arbitration                              | 4-3            |

| 4.1.1.4             | Interrupt Signals                            | 4-3            |

| 4.1.1.5             | Miscellaneous Signals                        | 4-4            |

| 4.1.2               | 80186 Operation                              | 4-4            |

| 4.1.2.1             | Address and Data Bus                         | 4-4            |

| 4.1.2.2             | Control Bus                                  | 4-5            |

| 4.1.2.3             | Bus Arbitration                              | 4-6            |

| 4.1.2.4             | Interrupt Signals                            | 4-6            |

| 4.1.2.5             | Miscellaneous Signals                        | 4-7            |

### **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number | Title                                  |              |  |  |  |

|---------------------|----------------------------------------|--------------|--|--|--|

| 4.2<br>4.2.1        | Serial Communication Pins              | 4-7<br>4-7   |  |  |  |

| 4.2.1               | Timeslot Mode                          | 4-7<br>4-9   |  |  |  |

| 4.2.3               | Modem Mode (Packet Operation)          | 4-10         |  |  |  |

| 4.2.4               | Modem Mode (Transparent Operation)     | 4-11         |  |  |  |

| 4.2.5               | Serial Control Port                    | 4-12         |  |  |  |

| 4.3                 | Power Supply                           | 4-13         |  |  |  |

|                     | Section 5                              |              |  |  |  |

|                     | Bus Operation                          |              |  |  |  |

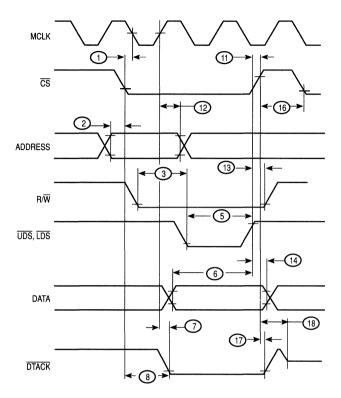

| 5.1                 | 68000 System Operation                 | 5-1          |  |  |  |

| 5.1.1               | Bus Width Selection                    | 5-2          |  |  |  |

| 5.1.2<br>5.1.2.1    | Host Operation                         | 5-2<br>5-2   |  |  |  |

| 5.1.2.1             | Write Cycle                            | 5-2<br>5-3   |  |  |  |

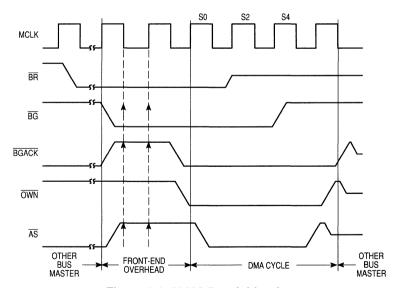

| 5.1.3               | DMA Operation                          | 5-3          |  |  |  |

| 5.1.3.1             | DMA Write Cycle                        | 5-4          |  |  |  |

| 5.1.3.2             | DMA Read Cycle                         | 5-5          |  |  |  |

| 5.1.3.3             | Bus Error Recovery                     | 5-6          |  |  |  |

| 5.1.3.4             | Wait-State Generator and DTACK Control | 5-6          |  |  |  |

| 5.1.4               | Bus Arbitration                        | 5-6          |  |  |  |

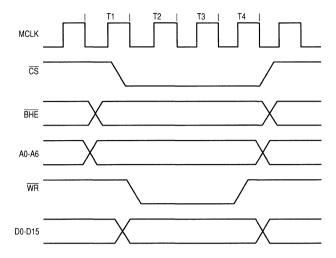

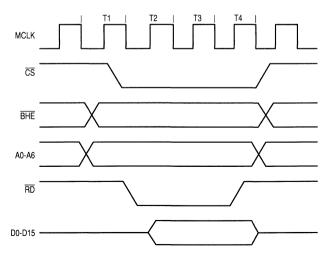

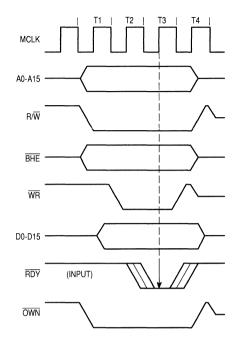

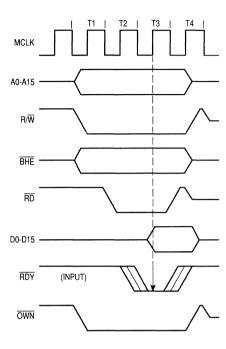

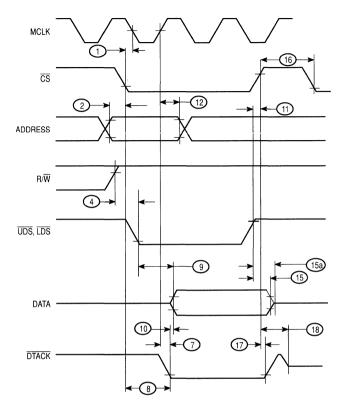

| 5.2<br>5.2.1        | 80186 System Operation                 | 5-8<br>5-8   |  |  |  |

| 5.2.1<br>5.2.1.1    | Host Processor Operation               | 5-6<br>5-8   |  |  |  |

| 5.2.1.2             | Read Cycle                             | 5-9          |  |  |  |

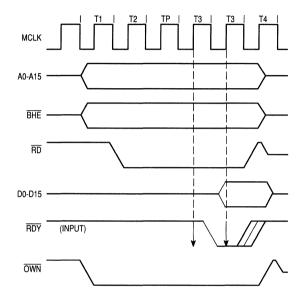

| 5.2.2               | DMA Operation                          | 5-10         |  |  |  |

| 5.2.2.1             | DMA Write Cycle                        | 5-10         |  |  |  |

| 5.2.2.2             | DMA Read Cycle                         | 5-10         |  |  |  |

| 5.2.2.3             | Wait-State Generator and Read Control  | 5-11         |  |  |  |

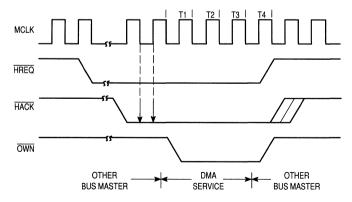

| 5.2.3               | Bus Arbitration                        | 5-11         |  |  |  |

| 5.3                 | Interrupt Operation                    | 5-13         |  |  |  |

| 5.3.1<br>5.3.1.1    | Interrupt Sources                      | 5-13<br>5-14 |  |  |  |

| 5.3.1.1             | Normal Interrupts                      | 5-14<br>5-15 |  |  |  |

| 5.3.1.3             | Bit-Handler Fault Interrupts           | 5-15         |  |  |  |

| 5.3.1.4             | System Fault interrupts                | 5-15         |  |  |  |

| 5.3.1.5             | SCP Complete Interrupt                 | 5-15         |  |  |  |

| 5.3.2               | Interrupt Request (IRQ) Pin            | 5-15         |  |  |  |

| 5.3.3               | Interrupt Vector                       | 5-16         |  |  |  |

| 5.3.4               | 68000 Interrupt Acknowlege Cycle       | 5-16         |  |  |  |

| 5.3.5               | 80186 Interrupt Acknowledge Cycle      | 5-17         |  |  |  |

| 5.4                 | Reset Operation                        | 5-17         |  |  |  |

# **TABLE OF CONTENTS (Continued)**

| Paragraph<br>Number                                                                                                                                                | Title                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                    | Section 6 Serial Interface Operation                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                  |  |  |  |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.3.1<br>6.4<br>6.4.1<br>6.4.2<br>6.4.3                                      | Interchip Digital Link (IDL) Interface for ISDN Applications Functional Description Subrate Multiplexing (CCITT I.460) Transparent Operation Timeslot Interface Mode Selection Long-Frame Operation Short-Frame Operation Subrate Multiplexing Transparent Operation Modem Interface Transparent Modem Operation Serial Control Port (SCP) Serial Control Port Description SCP Master Mode SCP Slave Mode                                       | 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6<br>6-7<br>6-7<br>6-7<br>6-8<br>6-9<br>6-10<br>6-11                        |  |  |  |

| 7.1<br>7.1.1<br>7.1.2<br>7.1.2.1<br>7.1.2.2<br>7.1.2.3<br>7.1.3<br>7.1.4<br>7.1.5<br>7.2<br>7.21<br>7.2.1.1<br>7.2.1.2<br>7.2.1.3<br>7.2.1.4<br>7.2.1.5<br>7.2.1.4 | Section 7 Applications  ISDN Voice/Data Terminal Adapter IDL and SCP Interfaces MPU/DMA Interfaces Interrupt Vectors DMA Bus Arbitration Decoder PALs User Interface (Microcomputer Keyboard/Display Controller) Real-Time Operating System Summary ISDN Terminal Card for the Macintosh SE Terminal Card Hardware Desciption The Macintosh SE Expansion Bus Data, Address, and Control Buses Interrups PAL Device Serial Buses IDL Bus SCP Bus | 7-1<br>7-2<br>7-2<br>7-3<br>7-4<br>7-4<br>7-5<br>7-6<br>7-7<br>7-8<br>7-9<br>7-9<br>7-15<br>7-15<br>7-16<br>7-16 |  |  |  |

| 7.2.1.6<br>7.2.1.7<br>7.2.2                                                                                                                                        | S/T Transceiver and Line Interface Blocks  Codec/Filter Block  Terminal Card Software                                                                                                                                                                                                                                                                                                                                                           | 7-16<br>7-22<br>7-22                                                                                             |  |  |  |

### **TABLE OF CONTENTS (Concluded)**

| Paragraph<br>Number  | Title                                                  | Page<br>Number |

|----------------------|--------------------------------------------------------|----------------|

| 7.2.2.2              | Description of the Individual Blocks                   | 7-24           |

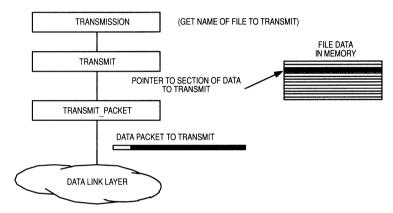

| 7.2.2.2.1            | Transmit Procedures                                    | 7-24           |

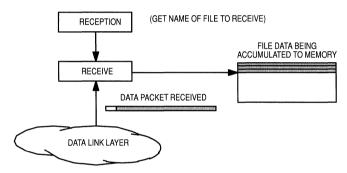

| 7.2.2.2.2            | Reception Procedure                                    | 7-25           |

| 7.2.2.2.3            | Data Link Layer                                        | 7-26           |

| 7.2.2.2.4            | Physical Layer                                         | 7-27           |

| 7.2.2.2.5            | Hardware Interface                                     | 7-28           |

| 7.2.2.2.6<br>7.2.2.3 | Hardware Drivers                                       | 7-28<br>7-29   |

| 7.2.2.3<br>7.2.2.3.1 | Implementation Issues                                  | 7-29<br>7-29   |

| 7.2.2.3.1            | Flow Control and Error Recovery in the Data Link Layer | 7-29<br>7-30   |

| 7.2.2.3.2            | Summary                                                | 7-30<br>7-31   |

|                      | Section 8 Electrical Specifications                    |                |

| 8.1                  | Maximum Ratings                                        | 8-1            |

| 8.2                  | Thermal Characteristics                                | 8-1            |

| 8.3                  | DC Electrical Characteristics                          | 8-1            |

| 8.4                  | Power Considerations                                   | 8-2            |

| 8.5                  | MPU/DMA Timing Characteristics (68000 Mode)            | 8-2            |

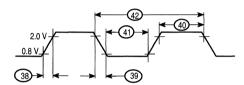

| 8.6                  | MCLK Timing Characteristics                            | 8-8            |

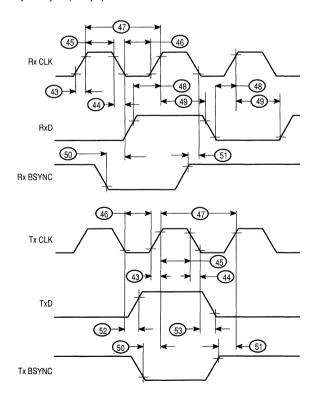

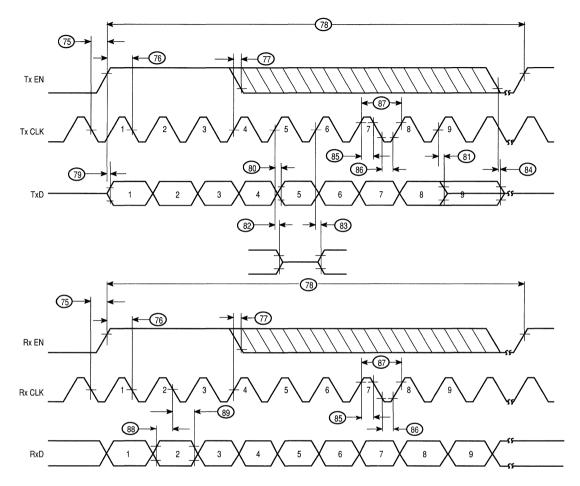

| 8.7                  | Serial Interface (Modem Mode) Timing Characteristics   | 8-9            |

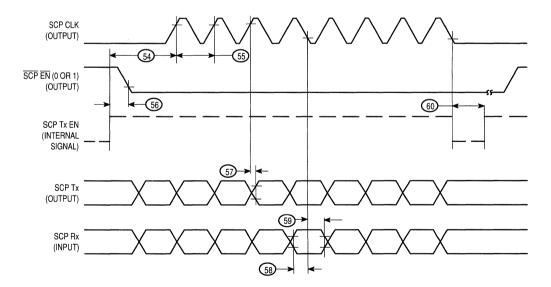

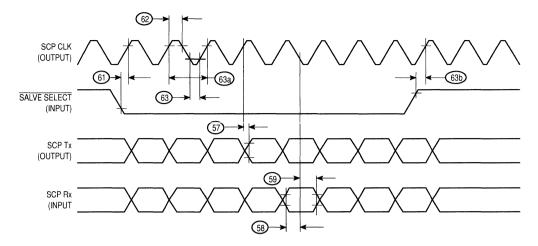

| 8.8                  | Serial Control Port Timing Characteristics             | 8-10           |

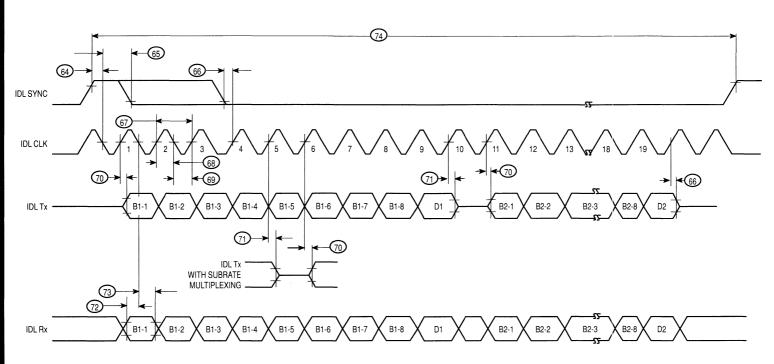

| 8.9                  | IDL Timing Characteristics                             | 8-11           |

| 8.10                 | Serial Interface Timing Characteristics:               | 0.10           |

| 8.11                 | Long- and Short-Frame Modes                            | 8-12<br>8-16   |

| 0.11                 | Will OrbiNA Timing Characteristics (60100 Mode)        | 0-10           |

|                      | Section 9 Mechanical Data                              |                |

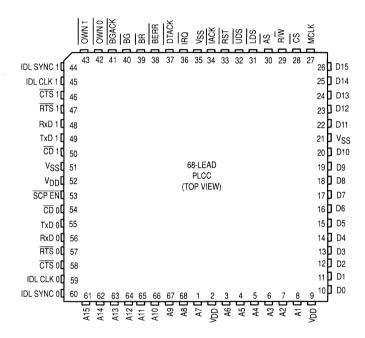

| 9.1                  | Pin Assignment                                         | 9-1            |

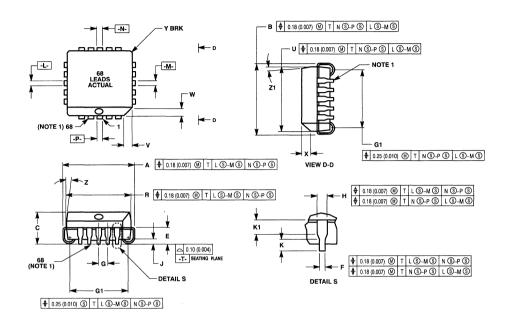

| 9.2                  | Package Dimensions                                     | 9-2            |

### LIST OF TABLES

| Table<br>Number          | Title                                                                                           |                           |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------|---------------------------|--|--|

| 3-1                      | Reset Operation Results                                                                         | 3-17                      |  |  |

| 4-1<br>4-2<br>4-3<br>4-4 | 68000 Mode Pin Functions 80186 Mode Pin Functions Serial Interface Pins MPU Interface Pin Names | 4-1<br>4-5<br>4-8<br>4-13 |  |  |

| 5-1                      | Interrupt Priority and Vector Values                                                            | 5-14                      |  |  |

| 6-1                      | Timeslot Byte Alignment                                                                         | 6-4                       |  |  |

| 7-1<br>7-2               | System Decoder PALs                                                                             | 7-4<br>7-5                |  |  |

### LIST OF ILLUSTRATIONS

| Figure<br>Number                                                                            | Title                                                                                                                                                                                                                                                                                                          | Page<br>Number                                                                           |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 1-1                                                                                         | HDLC Frame Format                                                                                                                                                                                                                                                                                              | 1-2                                                                                      |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7                                               | DDLC Block Diagram (One Transceiver Shown) Transmitter State Diagram HDLC Operation Receiver State Diagram HDLC Operation Alternate Receive Buffer Operation Transmit DMA State Diagram DMA Receive State Diagram Timer Clock Selection                                                                        | 2-1<br>2-2<br>2-6<br>2-9<br>2-10<br>2-12<br>2-14                                         |

| 3-1                                                                                         | Register Memory Map                                                                                                                                                                                                                                                                                            | 3-16                                                                                     |

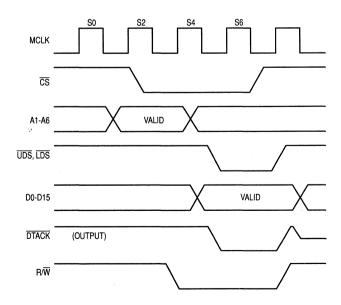

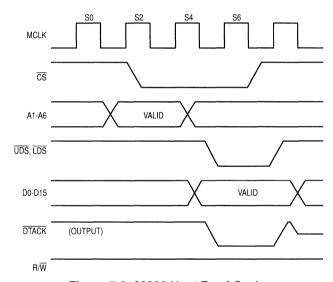

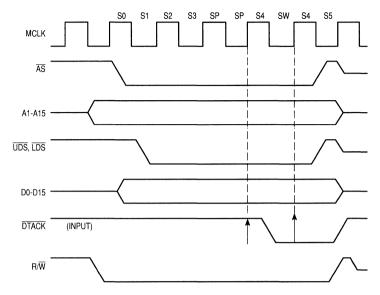

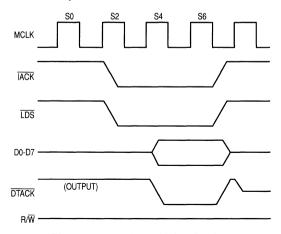

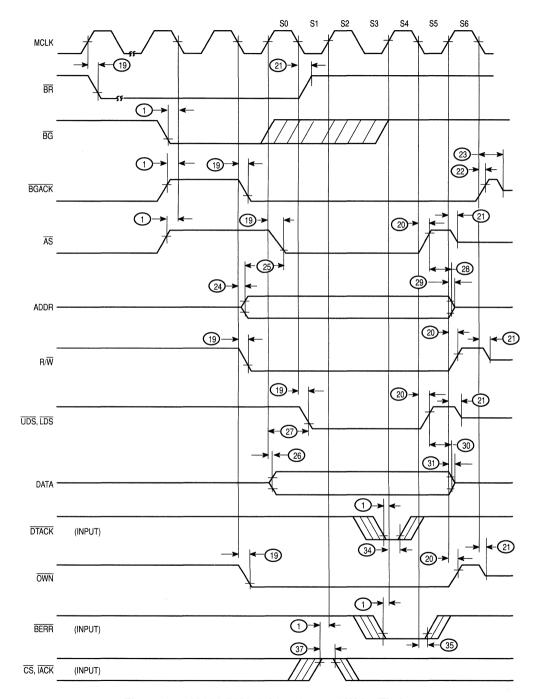

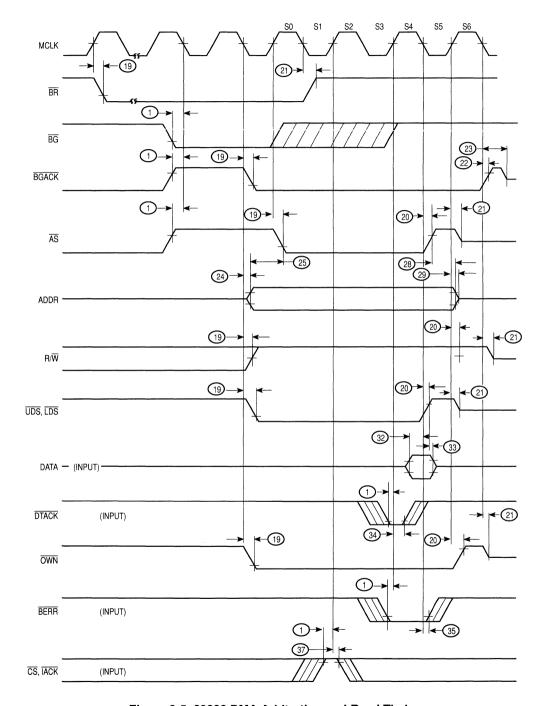

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5                                                             | 68000 Host Write Cycle 68000 Host Read Cycle 68000 DMA Write Cycle 68000 DMA Read Cycle 68000 DMA Write Cycle with One Programmed Wait-State                                                                                                                                                                   | 5-2<br>5-3<br>5-4<br>5-5                                                                 |

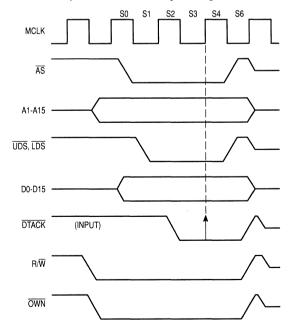

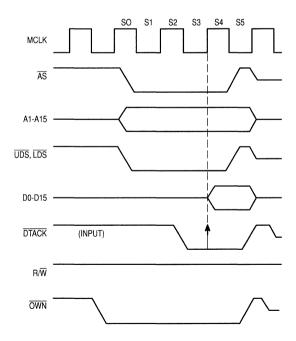

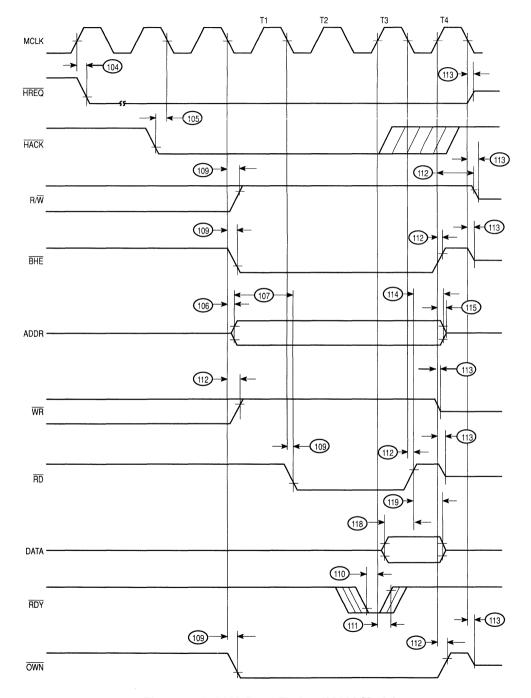

| 5-6<br>5-7<br>5-8<br>5-9<br>5-10<br>5-11                                                    | and a Delayed DTACK 68000 Bus Arbitration 80186 Host Write Cycle 80186 Host Read Cycle 80186 DMA Write Cycle 80186 DMA Read Cycle 80186 DMA Cycle with One Programmed Wait-State                                                                                                                               | 5-7<br>5-7<br>5-9<br>5-9<br>5-11<br>5-11                                                 |

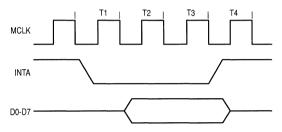

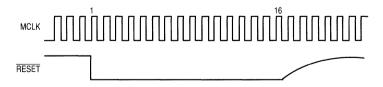

| 5-12<br>5-13<br>5-14<br>5-15                                                                | and Delayed RDY  80186 Mode Bus Arbitration  68000 IACK Cycle  80186 INTA Cycle  Watchdog-Generated Reset                                                                                                                                                                                                      | 5-12<br>5-12<br>5-16<br>5-17<br>5-17                                                     |

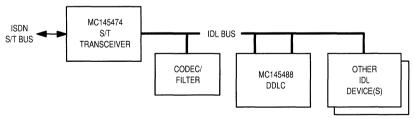

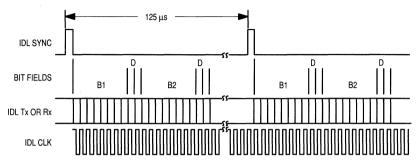

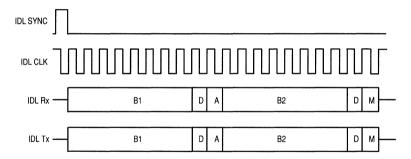

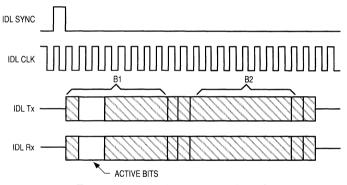

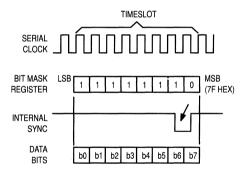

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9<br>6-10<br>6-11<br>6-12<br>6-13 | Typical IDL Bus Application IDL Frame Timing IDL Bus Signals IDL Subrate Multiplexing Transparent Byte Alignment PCM Highway Application PCM Bus Timeslot Operation Long-Frame Timeslot Operation Short-Frame Modem Application Transparent Modem Operation ISDN Terminal Application SCP Module Block Diagram | 6-1<br>6-2<br>6-2<br>6-3<br>6-4<br>6-5<br>6-5<br>6-6<br>6-7<br>6-8<br>6-9<br>6-9<br>6-10 |

# LIST OF ILLUSTRATIONS (Concluded)

| Figure<br>Number                                                                                            | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page<br>Number                                                                                        |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

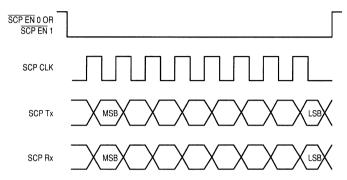

| 6-14<br>6-15                                                                                                | SCP Pin Functions — Master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6-11<br>6-12                                                                                          |

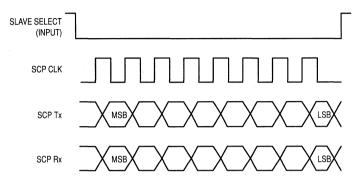

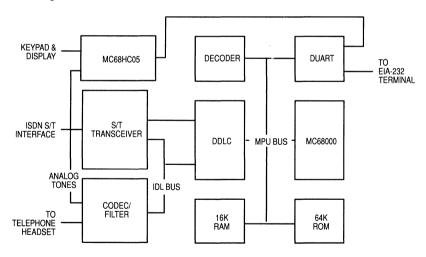

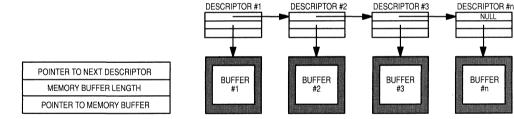

| 7-1 7-2 7-3 7-4 7-5 7-6 7-7 7-8 7-9 7-10 7-11 7-12 7-13 7-14 7-15 7-16 7-17 7-18 7-19 7-20 7-21             | ISDN Terminal Adapter and Voice and Data Block Diagram IDL, SCP Bus Connections 128K Byte Memory Map Real-Time Multitasking Operating System Terminal Adapter Software/Hardware Model Macintosh SE ISDN Terminal Card Hardware Block Diagram DDLC typedef (C Language) DDLC bufferAlloc() Procedure (C Language) Macintosh SE ISDN Terminal Card (MPU Section) STRead/Write() Procedure (C Language) scp transfer() Procedure (C Language) Macintosh SE ISDN Terminal Card (S/T Transceiver Section) ISDN Transmit Pair Interface and Protection McIntosh SE ISDN Terminal Card (Codec/Filter Section) Terminal Card Software Block Diagram Transmit Procedure Reception Procedure Buffer Descriptor Linked List of Descriptors Circular Queue of Descriptors Data Link Headers | 7-1 7-2 7-3 7-7 7-8 7-9 7-10 7-14 7-17 7-19 7-20 7-21 7-21 7-22 7-23 7-25 7-26 7-29 7-30 7-31         |

| 8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7<br>8-8<br>8-9<br>8-10<br>8-11<br>8-12<br>8-13<br>8-14<br>8-15 | Test Load 68000 MPU Write Timing 68000 MPU Read Timing 68000 DMA Arbitration and Write Timing 68000 DMA Arbitration and Read Timing MCLK Timing Diagram Serial Interface (Modem Mode) Timing Diagram SCP Master Mode SCP Slave Mode IDL Timing Timeslot Mode Timing Long-Frame Operation Timeslot Mode Timing Short-Frame Operation MPU Read Timing (80186 Mode) MPU Write Timing (80186 Mode) DMA Write Timing (80186 Mode)                                                                                                                                                                                                                                                                                                                                                    | 8-2<br>8-4<br>8-5<br>8-6<br>8-7<br>8-8<br>8-9<br>8-10<br>8-11<br>8-13<br>8-14<br>8-15<br>8-17<br>8-17 |

### **SECTION 1 OVERVIEW**

#### 1.1 INTRODUCTION

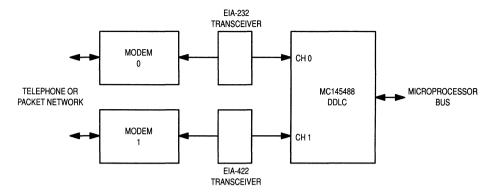

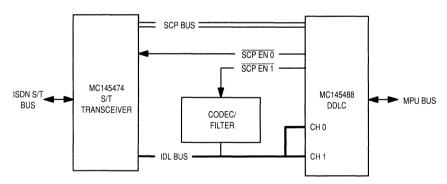

The MC145488 is a two-channel ISDN LAPD controller with an on-chip direct memory access (DMA) controller. It is intended for ISDN terminal and switch applications where one or two channels of data will use HDLC-type protocols. The DDLC is ideally suited for use with the MC145474 S/T transceiver. The interchip digital link (IDL) easily connects the chips together, providing a powerful layer one/layer two ISDN solution. A serial control port is provided to efficiently control the MC145474 or other ISDN family devices. The DDLC is compatible with 68000 and 80186 bus structures.

Places where significant changes or clarifications have been made between this data sheet and the Advance Information data sheet are indicated by change bars in the left margin.

#### 1.2 FEATURES

- Two Independent Full-Duplex Bit-Oriented Protocol Controllers Supports: HDLC, SDLC, CCITT X.25, CCITT Q.921 (LAPD), and V.120 at Basic and Primary Rates

- Four Channel On-Chip DMA Controller 64 Kbyte Address Range with Expansion Control Internal Programmable Wait-State Generator Two Buffer Descriptors for Each Receiver Channel

- Compatible with 68000 and 80186 Bus Structures Nonmultiplexed 16- or 8-Bit Data Bus

- Bit-Level HDLC Processing Including:

Flag Generation/Detection Abort Generation/Detection Zero Insertion/Deletion **CRC-CCITT** Generation/Checking Residue Bit Handler

- TEI/SAPI Address Comparison Three Address Comparison Wildcard Bits for Block Comparisons

- Transparent Mode for Codec Compatibility

- Programmable Interrupt Vector Generation

- Two Independent Timers Configurable as a Watchdog Timer

- · Flexible Serial Interface with:

IDL Interface for Connection to Other ISDN Family Devices Timeslot Interface for Connection to PBX-Type Backplanes Modem Interface for Other Applications

- Supports CCITT Specification 1.460

- Supports DMI Specification 3.1 Modes 0, 1, 2, and 3

- Serial Control Port for ISDN Family Device Control

- Low-Power CMOS with Automatic Power-Down

#### 1.3 DDLC OVERVIEW

The MC145488 Dual Data Link Controller (DDLC) is a high-performance two-channel protocol controller with an on-chip direct memory access controller (DMAC). Each channel has a full-duplex transceiver with independent protocol controllers to handle the bit-level tasks of HDLC-type bit-oriented protocols including LAPB and LAPD. Each channel also has dedicated DMA controllers for transmit and receive. A transparent mode is provided which bypasses the protocol circuitry so that serial data may be directly DMAed between the host processor's memory and the serial interface. The DDLC's microprocessor interface is configurable to 68000 or 80186 systems and may be used in eight-bit or sixteen-bit modes.

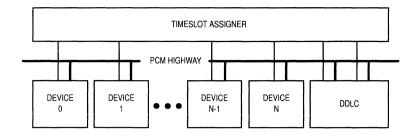

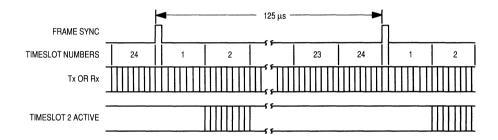

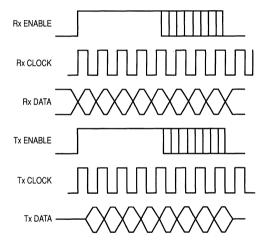

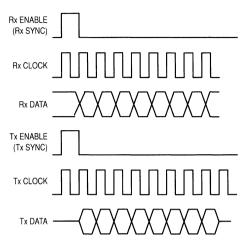

Each channel has a serial data interface which operates up to primary rate speeds in three modes: IDL, Timeslot, and Modem. In the IDL (interchip digital link) mode for ISDN applications, the IDL bus is supported. While in the IDL D mode, access control lines to the D-channel, through the MC145474 S/T transceiver, are included. The timeslot mode is used to connect the DDLC to PBX-type PCM highway backplanes. Both long-frame and short-frame timing are supported as well as synchronous transmit and receive. In the modem mode, each channel has its own separate transmit and receive clock inputs along with modem control lines (RTS, CTS, and CD). The two channels are independent and may be in different interface modes.

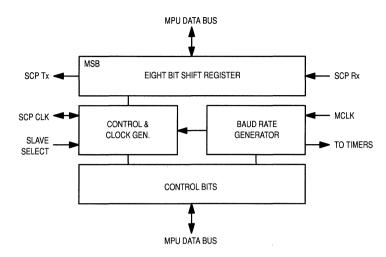

A serial control port (SCP) is provided to pass control information to other devices in a system. The SCP is compatible with Motorola's Serial Peripheral Interface (SPI) and National Semiconductor's Microwire Plus\*. Two internal timers may be used for general purpose, low resolution timing of HDLC-type protocols. One of the timers may be configured as a watchdog timer to reset the entire system in the event of a hardware or software failure.

Power consumption is an important aspect of ISDN terminal designs, and the DDLC was designed to use the minimum power possible while maintaining maximum functionality. The DDLC keeps power consumption to a minimum with an automatic power-down feature that turns off sections of circuitry that are not being used. Only those circuits that are actually used, such as when the CS\* pin is activated for a register read/write or when the DMA controller performs a bus transaction, does the chip enter the normal power state for the duration of the access and for any time required for internal processing.

Two internal loopback functions and special chip and system test modes are available. The loopbacks are controlled by the host for on-line maintenance. The test modes are activated by bits in the master control register and provide access to the internal state machines.

#### 1.4 HDLC PROTOCOL OVERVIEW

HDLC (High-Level Data Link Control) and its descendants, LAPB (Link Access Protocol-Balanced) and LAPD (Link Access Protocol for the D-channel), are bit-oriented synchronous protocols which are finding increased usage in data communications systems. LAPB and LAPD share the basic format of HDLC but differ in certain aspects of the software implementations. See Figure 1-1.

Figure 1-1. HDLC Frame Format

<sup>\*</sup>Microwire is a trademark of National Semiconductor Corp.

The DDLC in the packet mode transmits and receives data in a format called a frame or packet. All frames start with an opening flag and end with a closing flag. Between the flags, a frame contains an address field, control field, information field, and a cyclic redundancy check field (CRC).

Flag — The flag is the unique binary pattern (01111110). It provides the frame boundary and a reference for the position of each field of the frame. The DDLC transmitter generates a flag pattern internally and the opening flag and closing flags are appended to a frame automatically. Two successive frames can share one flag as a closing flag of the first frame and the opening flag of the succeeding frame. The receiver searches for a flag on a bit-by-bit basis and recognizes a flag at any time. The receiver establishes frame synchronization with every flag. The flags mark boundaries and references for each data field but they are not transferred to the receive FIFOs or memory.

Address Field — The 8- or 16-bits following the opening flag comprise the address field. The address field is used to distinguish between the various devices in a network. Devices receiving frame not addressed to them may discard and ignore the frames. The DDLC has address recognition circuitry included which relieves the host from this task.

Control Field — The 8- or 16-bits following the address field are the control field. Commands and responses between the devices in a network are exchanged in this field.

Information Field — This field follows the control field and precedes the CRC field. The information field contains the "data" to be transferred and may be a null field. Additionally, the information field is not necessarily an integral number of octets in length. The DDLC receives non-octet frames as octets and LSB-justifies the extra "orphan" bits at the end of the field. The number of orphan bits is indicated in a residue register.

Cycle Redundancy Check Field — The 16-bits preceding the closing flag are the CRC field. This field detects bit errors in the address, control, and information fields. Checking is with the standard CCITT polynominal  $\times$  16  $\times$  12  $\times$  5 + 1 for both the transmitter and receiver. Both the transmitter and receiver polynomial register are initialized to all '1s' when a flag character is detected, then begins calculating the CRC. The transmitter calculates the CRC on all bits of the frame except for the flags and transmits the complement of the resulting remainder as the CRC field. The receiver performs the similar computation on all bits except for the flags and compares the result to F0B8 (hex). When the result matches F0B8, the frame is accepted and the buffer is closed. CRC generation and checking are automatically performed by the DDLC. The CRC field is transferred to the buffer in memory. If desired, frames with CRC errors can be discarded automatically. All CRC errors are logged in a counter. For network-level error checking, the transmitter can generate faulty CRCs to simulate transmission errors.

**Zero Insertion and Deletion** — Zero insertion and deletion, which allows the content of the frame to be transparent, is automatically performed by the DDLC. A binary '0' is inserted by the transmitter after any succession of five '1s' within a frame (between flags). This eliminates the possibility of data imitating a flag character. The receiver deletes all '0s' that were inserted by the transmitter to regenerate the original data.

**Abort** — The function of prematurely terminating a data frame is called an abort. The transmitter aborts a frame by sending between seven and fourteen consecutive '1s'. When the receiver detects an abort character, it responds by clearing the FIFO and clearing the buffer in memory. It then begins searching for a new frame.

Idle and Interframe Time Fill — For LAPB and other applications, there are three states that the data link may be in: in-frame, inter-frame time fill, and idle. In-frame is the period from e beginning of an opening flag and the end of a closing flag. Inter-frame time fill is the period between frames

when continuous flags are transmitted. Idle is an out-of-frame period when continuous '1s' are on the link. In LAPD, on the D-channel, there are only two states: in-frame and idle. Continuous flags are not transmitted between frames.

MOTOROLA MC145488

### **SECTION 2 BLOCK DIAGRAM DESCRIPTION**

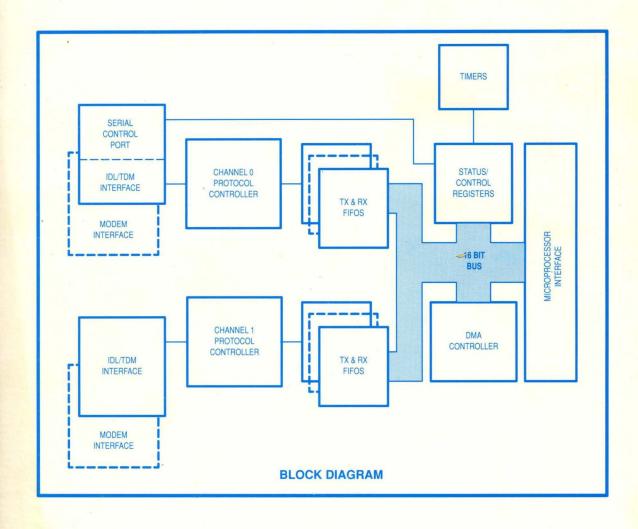

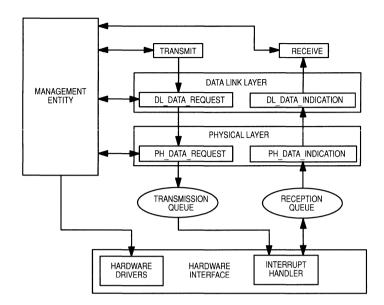

This section describes the internal blocks of the DDLC. The blocks include two protocol controllers which handle the bit-level aspects of HDLC-like packet protocols and four FIFOs which buffer the data, a four-channel DMA controller and a microprocessor interface block which connects the DDLC to the host system. The serial interface block is described in detail in Section 6. Figure 2-1 is a simplified block diagram of the DDLC. While the DDLC has two data transceivers, only one is shown for simplicity.

Figure 2-1. DDLC Block Diagram (One Transceiver Shown)

#### 2.1 TRANSMIT BIT HANDLER

Two identical bit-level protocol transmitters are provided which perform HDLC-type framing. This section describes the operation of one transmitter, but it applies to both.

#### 2.1.1 Packet Operation

The transmitter is designed to operate with as little intervention from the host processor as possible. To transmit a frame of data, the host merely informs the DDLC of the starting address of the data frame in memory and the length of the frame in bytes. The DDLC then transmits an opening flag and the data (LSB first) from memory. When the transmitter detects that the end of the data buffer has been reached, a CRC field and a closing flag are appended. Zeros are automatically inserted after ever string of five ones in the data to prevent imitation of a flag or abort character. The transmitter generates an abort character if the FIFO underruns. During inter-frame periods, the DDLC has the capability of transmitting either continuous flags (7E hex) or continuous marks (FF hex) as selected by the Inter-Frame Time Fill bit. For network-level fault isolation when the Force CRC Error bit is set, faulty CRCs are generated simulating a transmission error. The transmitter

also continuously monitors the  $\overline{\text{CTS}}$  pin and indicates the current state of the pin with the  $\overline{\text{CTS}}$  Status bit in the Transmit Status register.

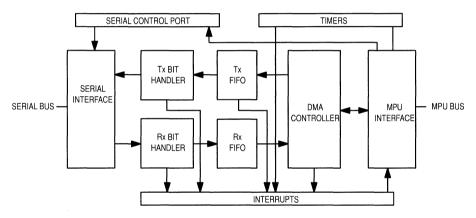

**2.1.1.1 STATE DIAGRAM.** Figure 2-2 is the state diagram for the transmitter in packet operation. IDLE is entered any time the Transmit Enable bit is low or when Mark Idle is selected and no data is ready to transmit. When data is ready or Flag Idle is selected, the SEND FLAG 1 state is entered. At least one flag character will be sent before the SEND DATA state is entered. The state machine remains in the SEND DATA state until an End-of-Frame (EOF) Tag is received through the FIFO from the DMA controller. SEND CRC then SEND FLAG 2 states are entered. After sending the closing flag, if data from another frame is ready, SEND DATA is entered allowing the closing flag to be shared with the following frame's opening flag. If no data is ready, either IDLE or SEND FLAG 1 is entered depending on the setting of the Inter-Frame Time Fill bit.

A FIFO underrun causes the state machine to enter the ABORT state where an abort character is sent to clear the link. When the modem control signals are used, if the  $\overline{\text{CTS}}$  pin goes inactive for more than one bit-time, an abort condition is generated and the current state is exited for the ABORT state. See Section 2.1.1.3 for a further discussion of flow control.

Figure 2-2. Transmitter State Diagram HDLC Operation

2.1.1.2 ABORT CHARACTER. The DDLC transmits an abort character which is compatible with DMI 3.1 modes 2 or 3 for restricted B-channel applications. In restricted access, no more than seven '0s' in a row may be transmitted. Because the HDLC protocol format may have any number of '0s' contiguously in the data field of a frame. DMI modes 2 and 3 invert all data before transmission. The DDLC inverts all transmitted data bits when the Data Invert bit of the Transmit Control register is set to '1'. Normally, with the data inverted, the maximum number of '0s' transmitted is six, the number of '1s' (inverted to '0s') of a flag (01111110) character. However, an HDLC abort character is seven to fourteen contiguous 's', which when inverted may be too many '0s', so the DDLC transmits an abort character of 01111111. This ensures that the maximum number of '0s' (inverted from '1s') is limited to seven even if the preceding data was five '1s'. In LAPB operation, the character following the abort character will always be a flag with the first bit of a '0'. When the DDLC is configured for ISDN D-channel use, an abort character of 11111111 is followed by idle (continuous '1s').

In certain applications a software-generated abort may be desired. The following is the recommended procedure to generate an abort: 1) clear the Buffer Ready bit and set the Force Abort bit, 2) reload the DMA pointers to the next frame's buffer, and 3) set the Buffer Ready bit. The DMA pointers must be updated before the Buffer Ready bit is set. This procedure disables any pending DMA requests then causes the transmitter to begin an abort sequence. At the same time the state machine clears the FIFO. The user then prepares the next frame for transmission. Simply negating the Transmit Enable bit will cause an abort sequence, but it is uncontrolled. The host processor does not know when the idle bits are actually transmitted and if the transmitter is re-enabled before at least seven '1s' were transmitted, a valid abort may not be transmitted.

When the Transmit DMA Complete Interrupt is enabled, if an abort sequence is generated due to negation of the CTS pin or a FIFO underrun, the Buffer Ready bit in the Transmit Control register is reset after the abort has been completely transmitted. The host is then free to prepare a buffer descriptor for the next frame to be transmitted, either a new frame or the aborted one. Control of the Buffer Ready bit is different if the Transmit Frame Complete Interrupt is enabled. This is discussed in Section 2.1.1.3.2.

2.1.1.3 FLOW CONTROL MECHANISMS. The DDLC provides two flow control mechanisms: one for basic rate ISDN applications and the other for standard modem applications. The following paragraphs describe the operation of the two schemes.

2.1.1.3.1 ISDN D-Channel Contention. When the DDLC is operating on the D-channel with the companion MC145474 S/T transceiver, the DREQ and DGNT lines must be used to comply with the basic rate D-channel contention algorithm. When the DDLC has a data frame to transmit, it asserts DREQ (high). The MC145474 transceiver monitors the S/T interface for activity on the D-channel and indicates the the channel is free by asserting DGNT (high). While DREQ is high, the DDLC samples DGNT on the falling edge of IDL SYNC. Transmission from the DDLC begins in the IDL D-bit time slots when DREQ and DGNT are both active. If a D-channel collision is detected on the S/T interface by the MC145474 transceiver, DGNT is negated (low), ISDN D-channel contention rules state that when a collision is detected, the colliding device must immediately stop transmitting and retransmit the frame at a later time when the D-channel is again available. When a collision is indicated, the DDLC automatically aborts the frame in progress and prepares to retransmit the entire frame when the D-channel again becomes available. This is done without interrupting the host. The Transmit Frame Complete Interrupt must be enabled to allow this operation. When the packet has been successfully transmitted a Transmit Frame Complete Interrupt is generated when the last '0' of the closing flag is transmitted.

If a software generated abort is desired while in D-channel operation, Transmit DMA Complete should be enabled and Transmit Frame Complete should be disabled before the Force Abort bit is set. This ensures that the aborted frame will not be retransmitted after the abort character is sent. After the Force Abort bit is cleared by the transmitter, the host is free to prepare a buffer descriptor for the next frame to be transmitted.

2.1.1.3.2 Modem Flow Control. The transmitter indicates to a modem that it has data ready to transmit with signals similar to D-channel operation. In this mode, Request-To-Send (RTS) is directly controlled by the Transmit Enable (TE) bit. When TE is high, the RTS pin is asserted (low). During inter-frame periods, either flags or marks, as selected, are transmitted but the RTS pin remains asserted until the user negates the TE bit. Transmission of a frame, if one is ready, actually begins when the modern asserts Clear-to-Send (CTS low). If CTS is negated for more than one Tx CLK period while a frame is in transmission, the frame is aborted and the DMA pointers are reset so that the frame can be retransmitted without interrupting the host.

Section 2.1.1.2 indicates that while the Transmit DMA Complete Interrupt is enabled, the Buffer Ready bit is reset after the abort character is transmitted. This operation is modified while the Transmit Frame Complete Interrupt is enabled, in which case the Buffer Ready bit remains set after an abort character is sent. When a collision is detected, an abort character is sent immediately followed by automatic retransmission of the colliding frame.

2.1.1.4 INTERRUPTS. There is one interrupt generated by the transmitter state machine. Transmit Frame Complete indicates that an entire frame and its closing flag have been successfully transmitted. It is issued when the state machine exits the SEND FLAG 2 state. Ordinarily this interrupt is used for basic rate ISDN D-channel operation. Two other interrupts associated with the transmitter are generated by the DMA controller and are discussed in Section 2.3.2.

#### 2.1.2 Transmit FIFO

The transmitter has a FIFO which buffers it from the DMA controller. It is four characters deep and nine bits wide. The ninth bit is a Tag bit which is attached to the last byte of a frame by the DMA controller. When the host has a message to send, the DMA controller fills the transmit FIFO and attempts to keep if full. A comparator in the controller keeps track of the FIFO occupancy and requests that the DMA controller load a word of data (16-bits) when the FIFO has two empty bytes. In 8-bit operation the DMA controller fetches one byte when there are one or more bytes available in the FIFO. At 64 kbps, DMA requests from a transmit FIFO are generated at approximately 250 ms intervals. If the DMA controller does not service a request and the FIFO underruns, an interrupt is queued and the current frame in transmission is aborted.

#### 2.1.3 Transparent Operation

The transmitter has the capability of operating with unframed data such as PCM-encoded voice or proprietary protocols. Raw data may be transmitted from memory with byte alignment maintained through the FIFO and transmitter. Byte alignment signals must be provided. In he modem mode, the alignment signal is externally generated. In IDL and timeslot operation, it is internally generated but user programmable. See Section 6.1.3 for further discussion. The DDLC transmits data continuously as long as there is data to transmit. To keep a continuous stream of data flowing, the Transmit DMA Complete Interrupt should be enabled. This interrupt occurs at least 16 bit-times before the FIFO becomes empty and the state machine enters the IDLE state. At 654 kbps, 250 ms is available to prepare the next buffer for transmission before the FIFO empties

MOTOROLA MC145488 and idle characters (either marks or flags) are transmitted. In 16 bit mode the DDLC transmits an even number of bytes. If an odd number is programmed it will transmit the least significant byte of the last 16 bit word read from memory by the DMA controller.

#### 2.1.4 Interframe Time Fill

The bit sequence that is transmitted between frames is determined by the value of the ITF bit in the Transmit Control register. The interframe time fill can be either the X.25 flag character (7E hex) or the LAPD marks ('1') idle. See Section 3.8 for further details on the ITF control bit.

#### 2.2 RECEIVE BIT HANDI ER

The receiver provides the complementary functions to the transmitter. This section describes the operation of one receiver, but it applies to both receivers.

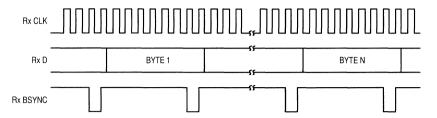

#### 2.2.1 Packet Operation

The receiver is reset and idle until the Receive Enable bit is set, at which time it begins searching for a flag character. When a flag is found, the selected address field of the frame, if desired, is checked and if a match is found, the DDLC passes the frame of data to the allocated buffer in memory. If no address match is found the DDLC clears the FIFO, resets the DMA pointers and searches for a new frame. Zeros inserted by the transmitter are removed from the data before placing the bytes in memory. When the closing flag is detected, the CRC field is checked and if found to be correct, the DDLC queues an interrupt indicating that a good data frame has been received and is in memory. If the CRC is found to be in error, the DDLC resets the buffer pointers to the start of the buffer and searches for a new frame. This in essence clears the buffer and discards the frame in error. In certain instances, frames with CRC errors will be of interest, A control bit is provided so that frames with CRC errors can be passed to memory. The Receive on CRC Error bit enables this feature and the CRC Error bit indicates that the frame has an error. All CRC errors are logged in the CRC Error register. The DDLC rejects undersize frames. If a frame of less than four octets between flags is found, it usually means that a bit error occurred, so OUT OF FRAME is entered.

If an abort character is found, the buffer pointers in the DMA controller are reset and the aborted frame is ignored. The FIFO is cleared and the receiver begins searching for a flag. No interrupt is generated.

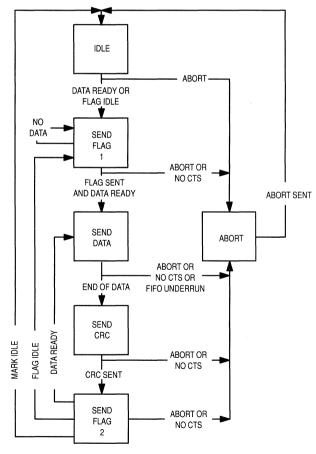

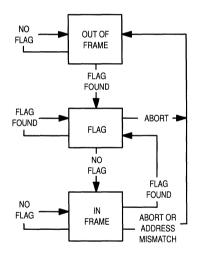

2.2.1.1 STATE DIAGRAM. Figure 2-3 shows the state diagram of the receiver. When the Receiver Enable bit is initially set, the state machine is in the OUT OF FRAME state. The pattern detector continuously searches for flags and when it finds one, the FLAG state is entered. If the next character is not a flag, the machine enters the IN FRAME state. Address recognition is sampled on the first or second byte after entering this state. If the address does not match, the OUT OF FRAME state is entered and the receiver searches for a new frame. When a flag is found in the IN FRAME state, an end of frame is assumed and the CRC checker is sampled and an End-of-Frame Tag is generated and passed to the FIFO. Then the FLAG state is entered. The receiver detects and reacts to aborted frames. If an abort is detected, the state machine enters OUT OF FRAME. Section 2.3.4 has more discussion of the different End-of-Frame Tag signals.

2.2.1.2 NON-OCTET ALIGNED PACKETS. The receiver has the capability of operating in non-octet aligned packet systems. The residue bit count indicating the number of orphan data bits at the end of the information field is placed in the RC bits of the Receive Status register. These bits are

valid until overwritten by another frame. In non-octet aligned systems the software should check the residue count soon after receiving a Receive Buffer Complete Interrupt to ensure that the residue count is not overwritten by the next frame. Orphan bits are LSB justified in memory. Note: The DDLC cannot transmit non-octet aligned frames.

**2.2.1.3 ADDRESS RECOGNITION (FILTERING).** The receiver can filter received frames by comparing their address fields to user programmable addresses. Two addresses may be programmed with another (broadcast, FF hex) hardwired into the receiver. Address filtering may be performed on either the first OR second octet following the opening flag of a frame. The ABS bit in the Receive Control register when high enables filtering on the first octet and when low filters on the second octet. Typically, in ISDN terminal applications, the TEI address (second) field will be of interest. In network applications, the SAPI (first) field will be checked. A separate Wildcard register allows selected bits of Compare Address 0 to be ignored during the comparison procedure. This provides a simple way to widen the "bandwidth" of the address filter allowing blocks of addresses to be passed to memory. If received frames are rejected by address recognition, the receiver is reset and searches for a new frame. Address recognition may be disabled by clearing the Address Compare Enable bit to '0'.

Figure 2-3. Receiver State Diagram HDLC Operation

#### 2.2.2 Receive FIFO

The receiver has a FIFO which is similar to the transmitter's. It is four characters deep and ten bits wide (eight hits for data and two bits for the Tag). Serial bytes are produced by the receiver and converted to parallel. As each byte is formed, it is pushed into the FIFO. A comparator in the controller keeps track of the occupancy of the FIFO and requests that the DMA controller place a word of data (16-bits) in memory when there are two or more bytes in the FIFO. In 8-bit operation the FIFO requests service when one or more bytes of data read ready to be placed in memory. If the FIFO overruns because the DMA controller did not service a request, an interrupt is queued. When a receiver is operating at 65 kbps in the 16-bit mode, DMA requests from that FIFO occur at approximately 250 ms intervals.

#### 2.2.3 Transparent Operation

The DDLC provides transparent operation for passing raw octet-aligned serial data to memory via DMA. This feature is useful for storing PCM voice or proprietary protocols in memory. When using the DDLC to pass PCM voice to memory, maximum buffer size of 4096 bytes should be used. Ordinarily, this will cause an interrupt every 500 ms. When the Buffer Overrun Interrupt is generated, the DMA controller automatically switches to the alternate buffer (if it is available) and begins placing data in it. No data will be lost in the change over from one buffer to the other. Note that the Receive DMA Complete Interrupt is not generated in transparent operation. Because the transparent mode requires that data to be in eight-bit quantities, synchronization procedures for defining octet boundaries are required. In the modem mode, the sync signal is externally generated and input on the CD\* pin. In IDL the timeslot operation, the sync signal is internally generated but user programmable. Once byte alignment is obtained in the receiver, it is maintained through the DMA controller into memory. Section 6.1.3 contains more details regarding transparent operation.

#### 2.2.4 Interrupts

There are two interrupts generated by the receiver. Receive idle indicates that 15 or more consecutive '1s' were received. This interrupt is considered normal operation. The current status of receive idle and carrier detect is available in the Receive Status register, but it must be kept in mind that they can change immediately after being read. The carrier detect pin also generates an interrupt when it changes state. Section 5.3 details all interrupts.

#### 2.3 DMA CONTROLLER

In order to relieve the host's software from critically timed data transfers to or from the protocol controllers, the DDLC provides four DMA channels, one for each transmitter and receiver.

#### 2.3.1 DMA Operation

When the DMA controller detects a service request from one of the FIFOs, it prepares the address and data from the transfer then requests ownership of the system bus from the host. When ownership is granted, the DMA controller assumes control of the bus and transfers data either to or from memory. Transfers are 16 bits or 8 bits depending on the selected bus width. In a 16-bit system, all transfers are word-wide. When the number of bytes in a received frame is odd, the last byte is placed in the most significant byte of the last word. The least significant byte will contain unknown data. The receive byte count will contain the correct number of bytes received (including the CRC). When odd length frames are transmitted, the last word read from memory will have the last byte transmitted in the most significant byte and the least significant byte of that word will be discarded. For operation in 80186 systems, see Section 5.3.

The DMA controller uses a round robin strategy to service internal DMA requests. A channel that was just serviced will not be polled again until all other channels have ben polled and serviced, if needed. The DDLC services one DMA request per bus arbitration cycle. For example, if two channels have request pending, when the DDLC assumes ownership of the bus, one channel is serviced then the bus is relinquished. The DDLC re-requests the bus no sooner than three MCLK cycles after the bus was relinquished allowing another bus master to begin a cycle. This type of operation improves system performance and guarantees that the DDLC will be well behaved. The DDLC prepares the data to be transferred (on receive DMA requests) and calculates the address before requesting the bus. This requires minimum overhead (dead) cycles while the host is transferring ownership of the bus. The next bus owner may assume ownership immediately after the DDLC has relinquished the bus.

It is impossible to precisely predict what the DDLC bus occupancy will be, but worst case with both channels operating full-duplex at 64 kbps (aggregate rate of 256 kbps) in a 16-bit 68000 system with a 12 MHz MCLK, approximately 0.66% of the host bus bandwidth will be consumed by the DDLC. This figure assumes 1-1/2 front-end overhead cycles and no wait-states. While the DDLC was designed to operate with both channels at 64 kbps, it is possible to operate at much higher data rates. Bus occupancy increases linearly with data rate. At very high data rates latency from the bus request to the bus grant and interrupt service latency become the limiting factors. It must also be kept in mind that the DDLC can generate interrupts quickly, especially with a large number of small data packets.

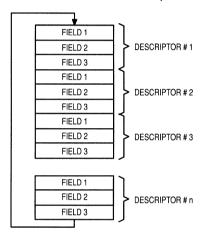

#### 2.3.2 Buffer Descriptors

As previously stated, the DDLC has four DMA channels. Pointer registers and counters are reguired so that the DMA controller knows where to place or fetch data in memory.

2.3.2.1 TRANSMIT BUFFER DESCRIPTORS. When the host has a frame of data to transmit, it informs the DMA controller where the data resides in memory. A 16-bit register, the Transmit Base Address register points to the first word of the transmitted frame and provides 64 kbyte address range. The host programs the address of the first word to be transmitted into this register. The length of the data frame must also be given to the DMA controller so a 12-bit Transmit Frame Length register is used to indicate the length of the frame in bytes. Frames of up to 4096 bytes in length may be transmitted.

Back to back frames can be transmitted by updating the transmit buffers when the Transmit DMA Complete interrupt is generated. The transmit framer works as follows. The last byte read into the transmit FIFO due to a DMA termination is tagged. The transmit framer detects this tagged byte in the FIFO and automatically appends a closing CRC and flag after the tagged byte is sent. If the transmit buffers have been updated and new untagged bytes are in the transmit FIFO a new transmit frame is started. The DDLC guarantees that at least one flag will occur between transmitted

**Note:** Once a transmit buffer descriptor has been prepared, it must not be disturbed until the Transmit DMA Complete or Transmit Frame Complete interrupts are generated. Modifying the contents of an active buffer descriptor may result in data being transmitted from unintended areas of memory.

2.3.2.2 RECEIVE BUFFER DESCRIPTORS. The receive buffer descriptors have a 16-Bit Receive Buffer Base Address register, a 12-Bit Buffer Length register, and a 12-Bit Frame Length register. The 16-Bit Base Address register provides 64 kbyte address range and contains the address of the first word of the data buffer which will accept a data frame. The 12-Bit Frame Length register indicates the length of the memory buffer in bytes. Buffers of up to 4096 bytes may be built. The DMA controller will never place data outside of the boundaries set-up by these two registers. The Frame Length register indicates the number of bytes including the CRC) received.

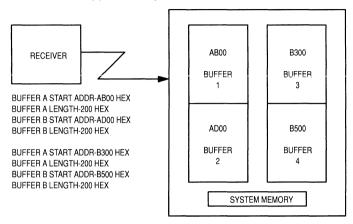

Each channel has a pair of buffer descriptors. These may be used alternately so that while one buffer is filling, another buffer is ready in-waiting. If back-to-back data frames are received, after the first buffer has been closed, the second is immediately ready for the next frame. There must be at least one buffer ready to accept data when the Rx Enable bit is set. Figure 2-4 describes the activity of the receiver with four buffers in memory. Initially, Buffer A Start Address is set to AB00 hex and Buffer B is set to AD00. The Length register is set to 200 hex. After the first frame is received, Buffer A is set to B300 hex to prepare for the third frame. After the second frame is received, the fourth

**MOTOROLA** MC145488 buffer is prepared with an address of B500. This process continues for the entire session. In a typical ISDN B-channel system at 64 kbps with frames of 256 bytes in length, interrupts requesting new buffer allocations will occur at approximately 32 ms intervals.

Figure 2-4. Alternate Receive Buffer Operation

If a package is coming in and no buffers are ready, the receive FIFO will overrun, the Receiver Enable bit is reset, and an interrupt is queued indicating the overrun. If both descriptors are ready, then Buffer A will be filled. If a received frame is larger than a buffer, the Buffer (A or B) Overrun Interrupt will be queued, but the receiver will continue to receive and the DMA controller will place the data in the alternate buffer (if it is available). If an alternate buffer is not ready, the Rx FIFO Overrun Interrupt will be generated and the receiver is reset.

Two buffer ready bits, Buffer A Rdy and Buffer B Rdy of the Receive Control register, are provided which allow the DMA controller to operate on that buffer. DMA activity on a receive channel begins when there is data in the FIFO and a buffer ready bit is set. As the buffer fills, the byte count increments. When the last byte has been placed in memory and the CRC has been checked OK, the selected buffer ready bit, Buffer A Rdy or Buffer B Rdy is cleared halting future DMA activity on that buffer until it is again prepared by the host.

Once a data frame has been completely received, the number of bytes received is indicated in the Frame Length register. The number in this register is valid only when the Receive DMA Complete bit (Buffer A or Buffer B) in the Receive Status register is set to '1'. If non-octet aligned frames are received, the number of residue bits (valid bits) in the last byte is indicated in the RC bits of the Receive Status register. The residue bits in memory will be least significant bit justified. For octet-aligned systems, the residue count should always be '0'.

Note: As with the transmitter, once a receive buffer descriptor has been prepared, it must not be disturbed until the closing flag has been found and DMA activity on the buffer has stopped. This is indicated by the Receive DMA Complete (Buffer A or B) interrupt. Modifying the contents of an active receive buffer descriptor may result in data being placed intl unintended areas of memory.

**2.3.2.3 ADDRESS EXPANSION.** The DDLC provides signals for expansion of the 64 kbyte address space. The  $\overline{OWN}$  pins are activated with timing identical to the address pins to enable external address circuitry onto the address bus. Using the  $\overline{OWN}$  pins with the R/ $\overline{W}$  pin, the transmit and receive buffers may all be on separate 64 kbyte pages in memory. Section 7 describes address expansion techniques in more detail.

#### 2.3.3 Transmit Channel Operation

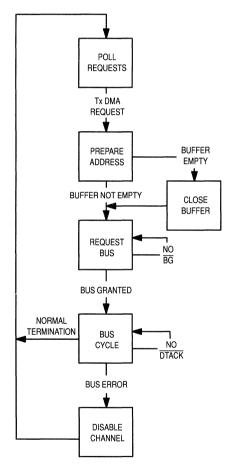

Figure 2-5 is a simplified state diagram of the DMA controller's operation when a transmit channel requests service. The DMA controller continuously polls the four channels for DMA requests. When a transmit request is found an address pointer into the buffer is prepared and compared to the ending address of the buffer. If the pointer is pointing to the last byte of the buffer, an EOF Tag is prepared to inform the transmitter and the DMA Complete interrupt is generated. The bus is then requested. When it is granted a read cycle is performed. Data read from memory is placed into the FIFO in ascending address order. If during the bus cycle a bus error or address error is detected, the Buffer Ready bit is cleared halting further DMA requests from that channel. A System Error interrupt is then queued.

Figure 2-5. Transmit DMA State Diagram

An internal counter keeps track of the number of bytes transferred to the FIFO. When its count equals the number in the Frame Length register, an End-of-Frame Tag is generated and loaded into the FIFO along with the last byte. The Buffer Ready bit is reset, a Transmit DMA Complete interrupt is queued, and further DMA activity on that channel is suspended. The host prepares the next frame by setting up another buffer descriptor and setting the Buffer Ready bit high.

Four interrupts are produced by the transmitter DMA channel Transmit DMA Complete indicates that the last byte of data has been transferred from the buffer into the transmit FIFO. FIFO underrun indicates the DMA requests were not serviced and the FIFO underran. Bus error is generated when the BERR pin is activated during a DMA cycle, and address error is generated when either IACK or  $\overline{\text{CS}}$  are activated during a DMA cycle.

Communication from the DMA controller to the transmitter is through the Tag bit as there is an unknown time delay from the DMA controller's activities to the time when the transmitter actually operates on the data. The EOF Tag informs the transmitter to close the frame with a CRC field and flag. Note that if the software reacts to the DMA Complete interrupt and prepares the next frame's buffer, the end of the previous frame may still be in the FIFO while the first two bytes of the next frame are loaded. When the transmitter finds this situation, after closing the first frame it shares the flag between frames and begins the next frame.

This section has only described the internal operation of the DMA controller. For details about DMA from the MPU's point of view, see Section 5.1.2.

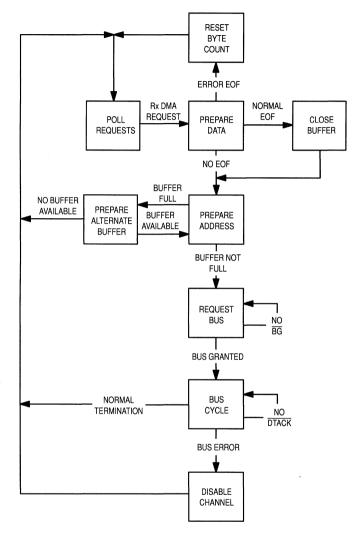

#### 2.3.4 Receive Channel Operation

Figure 2-6 is a simplified state diagram for operation of the DMA controller when a receive channel requests service. The DMA controller first gets data from the FIFO and arranges it into ascending order for 68000 or 80186 operation. While it is preparing the data, it examines the Tag bits. If the Tag indicates that an error was received, the byte counter is reset enabling the buffer to be reused. If a normal EOF is found, the Buffer Ready (A or B) bit is cleared and Receive DMA Complete interrupt is queued. If no Tag is found, a pointer to the next buffer location is prepared. If the pointer indicates that the buffer is full, a Buffer Overrun interrupt is gueued and the alternate buffer is activated (if it is available). Only after the data and address are ready is Bus Request asserted. A write cycle is then executed when ownership is granted, if a bus error or address error is detected during a bus cycle, a System Error interrupt is gueued and the RxEn bit is cleared resetting the receiver.

As with the transmitter, all communication between the receiver and DMA blocks is through the Tag bits in the FIFO. Because three end-of-frame conditions are reported, two bits are used. When a CRC Error Tag is detected, the Receive CRC Error bit in the Receive Status register is set (if RCE in the Control register is set) and the CRC Error Log counter is incremented. If RCE is not set, the Receive Byte Counter is reset enabling the buffer to be reused. When an Abort Tag is detected, the Byte Counter is reset effectively clearing the buffer for reuse. When a normal EOF is found, the Buffer Ready (A or B) is cleared, and a Receive DMA Complete interrupt is gueued. When the next frame arrives, the alternate buffer will be used.

When transparent mode is used no tags are generated so the Rx DMA Complete interrupt is never generated. The DMA controller generates a Buffer Overrun interrupt when the buffer actually fills. At 654 kbps the host has approximately 375 ms before the FIFO overruns or 250 ms before the alternate buffer is activated.

#### 2.4 MICROPROCESSOR INTERFACE

The microprocessor block interfaces the internal 16-bit bus to the host's 8- or 16-bit bus. All timing conversion and buffering is also performed. This block has three modes of operation: system slave, system master, and interrupt generator. This section will describe the operation of these three modes. Operation of the DDLC in an 80186 system is described in Section 5.2.

Figure 2-6. DMA Receive State Diagram

#### 2.4.1 System Slave Mode

When the DDLC is in this mode, it appears as fast memory to the host processor. The host can read or write from or to the registers in the DDLC. This mode is entered when the  $\overline{CS}$  pin is activated. Internal address decoding circuitry is selected and the desired register is connected to the internal bus for access by the host. Section 5.1.1 describes 68000 operation and Section 5.2.1 describes 80186 operation.

#### 2.4.2 System Master (DMA) Mode

During DMA operation the DDLC becomes a system master and controls the system bus. When one of the internal FIFOs requests a DMA transfer, the DDLC negotiates with the system host for

ownership of the bus. After successful negotiation, one DMA request is serviced then the bus is relinquished. The DDLC has the capability of reading or writing data from or to memory. If the memory system is slow, the DDLC inserts wait states (user selectable) until the memory is ready to complete the access. The DDLC has the capability of recovering from system faults such as address or bus errors. If one of these faults are detected, the DDLC disables the particular DMA channel which encountered the fault and queues an interrupt indicating the fault. The points in the DMA register which had the fault remain where they were when the fault was detected, so the host may investigate the problem. A system fault on any channel will not affect the operation of any other channel. Sections 5.1.2 and 5.2.3 describe the operation of the DDLC as a bus master and the bus negotiation procedure.

#### 2.4.3 Interrupt Operation

The DDLC has 27 vectored interrupt sources to inform the host of its status. One group of interrupts is normal operation interrupts. These inform the host that particular task was completed and that new tasks are desired. Another group is bit handler faults which inform the host that a DDLC channel detected a fault from which it cannot recover without assistance from the host. A third group is the timer and SCP interrupts. The last group of interrupts is the system faults. These include bus errors and address errors. When a DMA channel encountered one of these errors, it stops operation on the affected channel and informs the host that the channel has been disabled. All interrupts are maskable. In the case of system faults, all channels' interrupts are enabled or masked as a aroup.

The interrupts are presented to the host as a vector number in an interrupt acknowledge cycle. The interrupts are encoded into four bits so the DDLC vector space consumes 16 out of 256 locations. For applications not using vectored interrupts, the equivalent vector number is accessible in the Master Status register.

Interrupts are queued internally and a priority mechanism is used to ensure that the most important interrupt is serviced first. Interrupt operation of the DDLC is described more fully in Section 5.3.

All interrupt status bits have a feature where they may be set by the user to generate an immediate interrupt. This is useful for software debugging.

#### 2.5 SERIAL INTERFACE

The serial interface block has a variety of configurations which make it compatible with most common interfaces. Each channel's serial interface is independent so two different configurations may be active simultaneously. The serial interface has an IDL mode, a timeslot mode, and a general purpose modem mode. The operation of these modes is fully described in Section 6.

#### 2.6 SERIAL CONTROL PORT

A Serial Control Port, similar to the Serial Peripheral Interface (SPI) on Motorola single-chip microprocessors, is provided to communicate with external devices via a serial ink. The SCP functions are multiplexed onto other serial pins so when the SCP is enabled, certain modem control features will be lost. Section 6.4 describes in detail the operation of the SCP.

#### 2.7 TIMERS

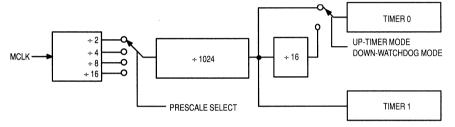

Two timers are provided for general purpose low-resolution protocol uses. The clock to the timer is derived from the Master MPU Clock (MCLK). The baud rate generator in the SCP block is used

to drive the timer divide chain. This clock is then divided by 1024 and applied to an eight-bit down-counter. The counter is readable and writable by the host and may be set to any value. The counter counts down toward zero from the current value. A non-maskable interrupt is generated when the counter underflows from FF to FE. The timers continue counting down after reaching FE. The status bit from the previous interrupt must be cleared before a new interrupt is generated. The timer function and interrupt are enabled by setting the Timer Enable bit in the Timer register to one. The timer interrupt status bits must be read while set before they may be cleared. See Section 5.3.3.

The timers are intended for low accuracy uses such as protocol timers. If the host is accessing the timer for a read or write and a count-down pulse arrives, the pulse is ignored. For its intended application, this will not cause any difficulty. Figure 2-7 describes the clock selection choices for the timers. A new count value can be written to the Timer register at any time while it is active. The timer will continue counting down from the new value.

Figure 2-7. Timer Clock Selection

#### 2.7.1 Watchdog Timer

Timer 0 may be configured as a watchdog timer for the entire host system. When the Watchdog Enable bit is set, an extra divide by 16 is added to the clock input of the counter. When the counter underflows from FF to FE, the Reset pin becomes an output for 16 MCLK cycles and a logic low is output. This provides a system reset to the host. The host can write any value (except FE hex) to the Timer register to setup any timeout. Timeouts of up to 5.6 seconds are available with a 12 MHz MCLK. See Section 5.4 for timing information on watchdog generated resets.

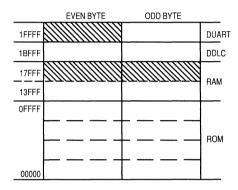

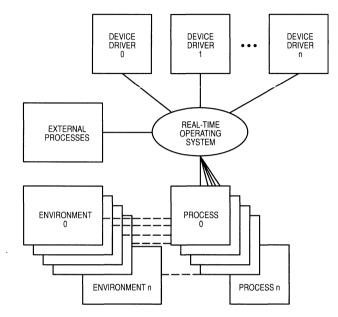

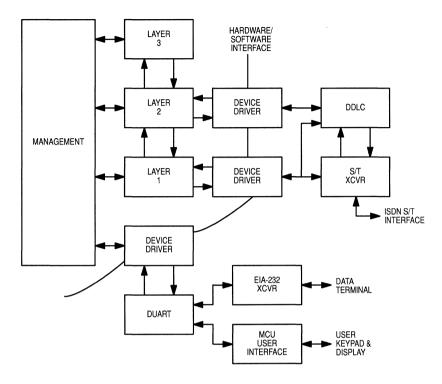

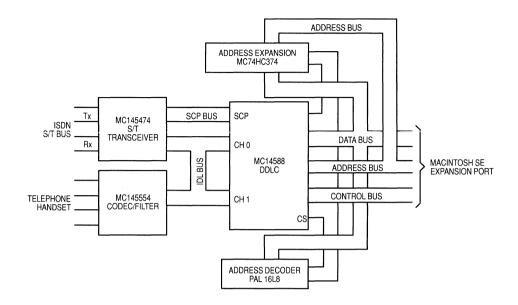

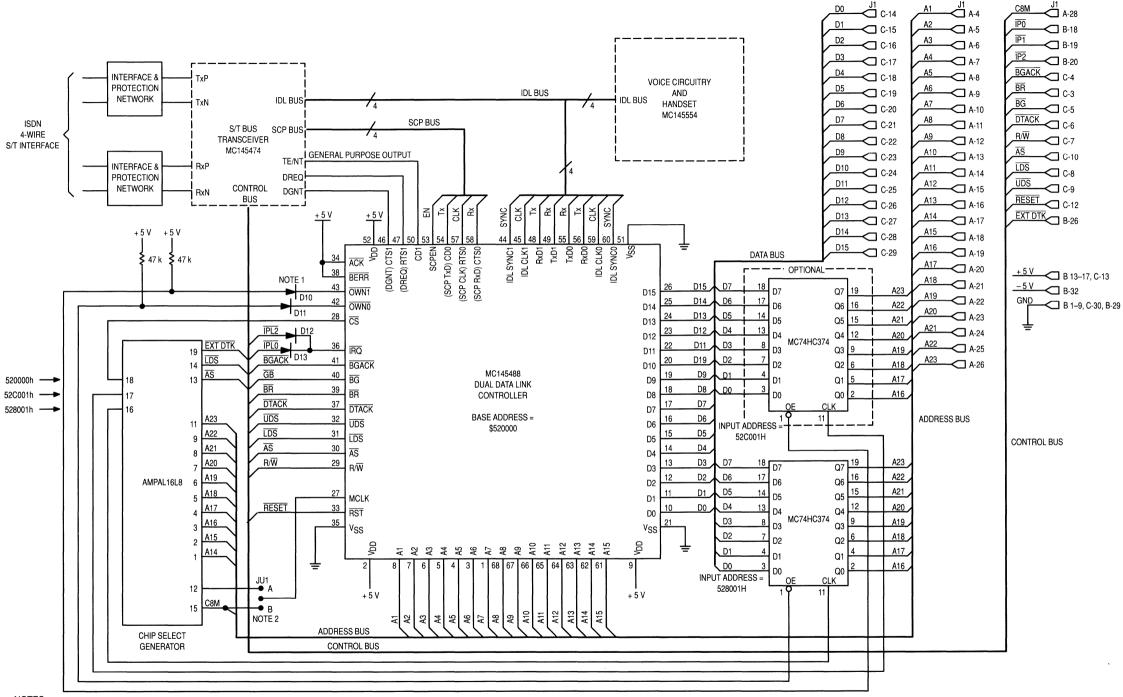

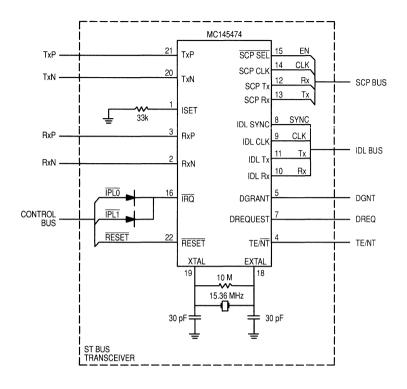

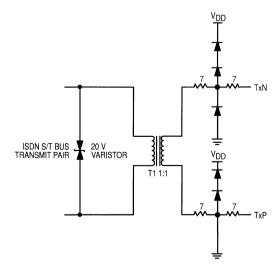

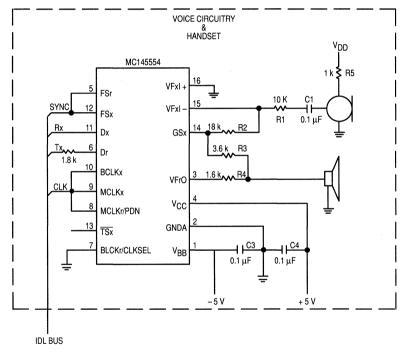

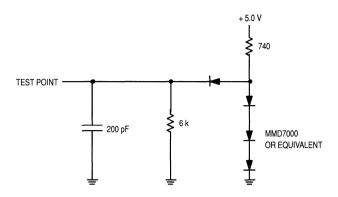

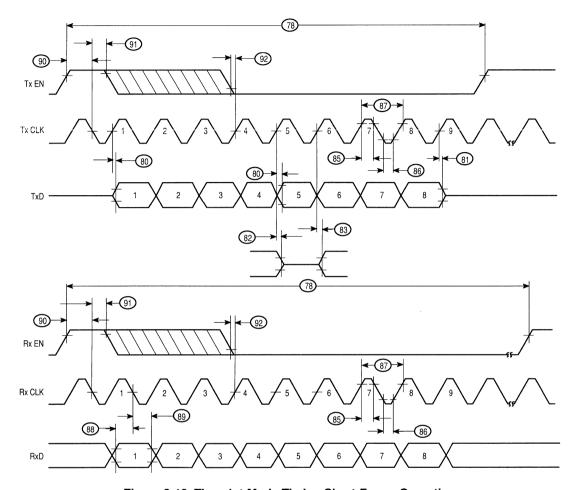

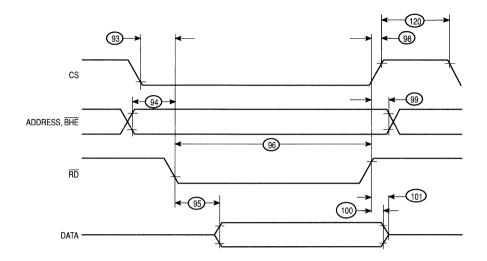

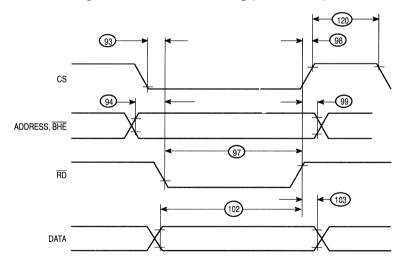

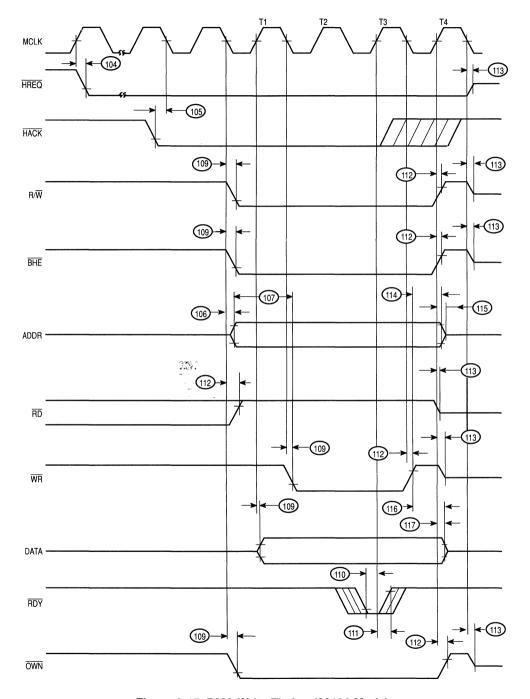

#### 2.8 POWER CONSUMPTION