### MC68606UM/AD

# MC68606 **Multi-Link LAPD Protocol Controller** User's Manual

This document contains information on a new product. Specifications and information herein are subject to change without notice. Motorola reserves the right to make changes to any products herein to improve functioning or design. Although the information in this document has been carefully reviewed and is believed to be reliable, Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. Motorola and (A) are registered trademarks of Motorola, Inc. is an Equal Employment Opportunity/Affirmative Action Employer.

| 3  | INTERNAL REGISTERS                        |

|----|-------------------------------------------|

| 4  | COMMAND SET                               |

| 5  | TRANSMIT PROCESS                          |

| 6  | RECEIVE PROCESS                           |

| 7  | EXCEPTION PROCESSING                      |

| 8  | MLAPD IMPLEMENTATION OF LAPD              |

| 9  | MLAPD IMPLEMENTATION OF SPECIAL MODES     |

| 10 | SIGNAL DESCRIPTION                        |

| 11 | BUS OPERATION                             |

| 12 | ELECTRICAL SPECIFICATIONS                 |

| 13 | MECHANICAL DATA                           |

| A  | SOFTWARE INTERFACE FLOWS<br>FOR THE MLAPD |

| В  | ABBREVIATIONS                             |

|    |                                           |

INTRODUCTION

MEMORY STRUCTURES

- 1 INTRODUCTION

- 2 MEMORY STRUCTURES

- 3 INTERNAL REGISTERS

- 4 COMMAND SET

- 5 TRANSMIT PROCESS

- **6** RECEIVE PROCESS

- 7 EXCEPTION PROCESSING

- 8 MLAPD IMPLEMENTATION OF LAPD

- 9 MLAPD IMPLEMENTATION OF SPECIAL MODES

- 10 SIGNAL DESCRIPTION

- 11 BUS OPERATION

- 12 ELECTRICAL SPECIFICATIONS

- 13 MECHANICAL DATA

- SOFTWARE INTERFACE FLOWS FOR THE MLAPD

- **B** ABBREVIATIONS

#### **TABLE OF CONTENTS**

| Paragraph    |                                                      | Page   |

|--------------|------------------------------------------------------|--------|

| Number       | Title                                                | Number |

|              | Section 1                                            |        |

|              | Introduction                                         |        |

| 1.1          | Feature Overview                                     |        |

| 1.2          | ISDN Communication Model                             |        |

| 1.3          | LAPD Frame Format                                    |        |

| 1.4          | System Environment                                   | . 1-6  |

| 1.4.1        | Physical Link Interface                              |        |

| 1.4.2        | Microprocessor System Bus Interface                  |        |

| 1.4.3        | Shared-Memory Control Components                     |        |

| 1.5          | Overview of MLAPD Functional Operation               |        |

| 1.5.1        | MLAPD Internal States and Command Structure Overview |        |

| 1.5.2        | Interrupt Structure Overview                         |        |

| 1.5.3        | Initialization Overview                              |        |

| 1.5.4        | Frame Reception Overview                             |        |

| 1.5.5        | Frame Transmission Overview                          | . 1-12 |

|              | Section 2                                            |        |

| 2.1          | Memory Structures                                    | 2.2    |

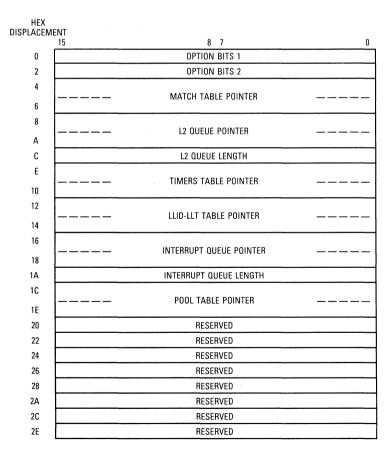

| 2.1<br>2.1.1 | Global Configuration Block                           |        |

| 2.1.1        | Constants Area                                       |        |

| 2.1.1.1      | Option Bits 1Option Bits 2                           |        |

| 2.1.1.2      | Match Table Pointer                                  |        |

| 2.1.1.3      | L2 Queue Pointer                                     |        |

| 2.1.1.5      | L2 Queue Length                                      |        |

| 2.1.1.6      | Timer Table Pointer                                  |        |

| 2.1.1.7      | LLID-LLT Table Pointer                               |        |

| 2.1.1.8      | Interrupt Queue Pointer                              |        |

| 2.1.1.9      | Interrupt Queue Length                               |        |

| 2.1.1.10     | Pool Table Pointer                                   |        |

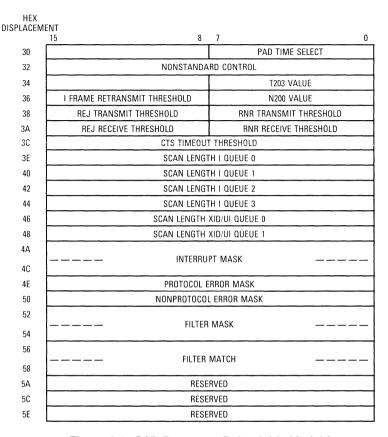

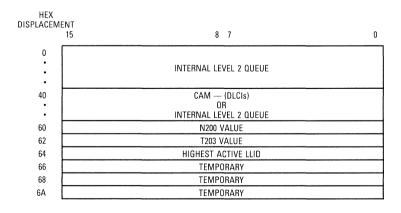

| 2.1.2        | Reloadable Variables Area                            | . 2-10 |

| 2.1.2.1      | Pad Time Select                                      | . 2-10 |

| 2.1.2.2      | Nonstandard Control                                  | . 2-10 |

| 2.1.2.3      | T203 Value                                           |        |

| 2.1.2.4      | I Frame Retransmit Threshold                         | . 2-12 |

| 2.1.2.5      | N200 Value                                           | . 2-12 |

| Paragraph<br>Number | Title                                      | Page<br>Number |

|---------------------|--------------------------------------------|----------------|

| 2.1.2.6             | REJ Transmit Threshold                     | . 2-12         |

| 2.1.2.7             | RNR Transmit Threshold                     | . 2-12         |

| 2.1.2.8             | REJ Receive Threshold                      | . 2-13         |

| 2.1.2.9             | RNR Receive Threshold                      | . 2-13         |

| 2.1.2.10            | CTS Timeout Threshold                      | . 2-13         |

| 2.1.2.11            | Scan Length I Queue 0                      | . 2-13         |

| 2.1.2.12            | Scan Length I Queue 1                      | . 2-13         |

| 2.1.2.13            | Scan Length I Queue 2                      | . 2-13         |

| 2.1.2.14            | Scan Length I Queue 3                      | . 2-14         |

| 2.1.2.15            | Scan Length XID/UI Queue 0                 | . 2-14         |

| 2.1.2.16            | Scan Length XID/UI Queue 1                 | . 2-14         |

| 2.1.2.17            | Interrupt Mask                             |                |

| 2.1.2.18            | Protocol Error Mask                        |                |

| 2.1.2.19            | Nonprotocol Error Mask                     | . 2-16         |

| 2.1.2.20            | Filter Mask and Filter Match               |                |

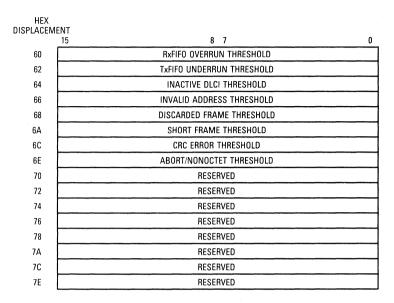

| 2.1.3               | Statistics Threshold Area                  | . 2-18         |

| 2.1.3.1             | RxFIFO Overrun Threshold                   |                |

| 2.1.3.2             | TxFIFO Underrun Threshold                  | . 2-18         |

| 2.1.3.3             | Inactive DLCI Threshold                    |                |

| 2.1.3.4             | Invalid Address Threshold                  |                |

| 2.1.3.5             | Discarded Frame Threshold                  | . 2-19         |

| 2.1.3.6             | Short Frame Threshold                      |                |

| 2.1.3.7             | CRC Error Threshold                        | . 2-19         |

| 2.1.3.8             | Abort or Nonoctet Threshold                | . 2-19         |

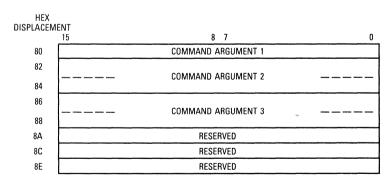

| 2.1.4               | Command Arguments Area                     | . 2-20         |

| 2.1.4.1             | Command Argument 1                         | . 2-20         |

| 2.1.4.2             | Command Argument 2                         |                |

| 2.1.4.3             | Command Argument 3                         |                |

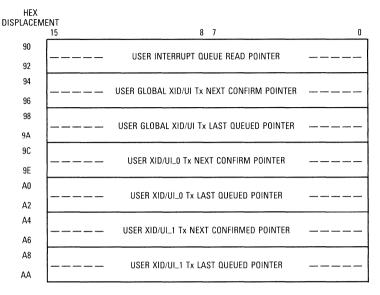

| 2.1.5               | User Area                                  | . 2-20         |

| 2.1.5.1             | User Interrupt Queue Read Pointer          | . 2-20         |

| 2.1.5.2             | User Global XID/UI Tx Next Confirm Pointer | . 2-20         |

| 2.1.5.3             | User Global XID/UI Tx Last Queued Pointer  | . 2-20         |

| 2.1.5.4             | User XID/UI Tx Next Confirm Pointer        | . 2-20         |

| 2.1.5.5             | User XID/UI Tx Last Queued Pointer         | . 2-20         |

| 2.1.5.6             | User XID/UI Tx Next Confirm Pointer        | . 2-21         |

| 2.1.5.7             | User XID/UI Tx Last Queued Pointer         | . 2-21         |

| 2.2                 | Match Table                                | . 2-21         |

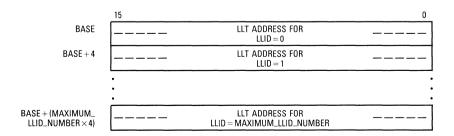

| 2.3                 | LLID-LLT Table                             |                |

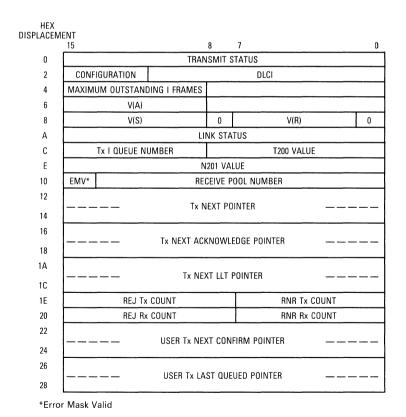

| 2.4                 | Logical-Link Table                         |                |

| 2.4.1               | Transmit Status                            |                |

| 2.4.2               | DLCI and Configuration Bits                |                |

| Paragraph<br>Number | Title                                          | Page<br>Number |

|---------------------|------------------------------------------------|----------------|

| 2.4.3               | Maximum Number of Outstanding I Frames (K)     | . 2-26         |

| 2.4.4               | V(A)                                           | 2-26           |

| 2.4.5               | V(S)/V(R)                                      | 2-26           |

| 2.4.6               | Link Status                                    | . 2-27         |

| 2.4.7               | Tx I Queue Number                              | . 2-29         |

| 2.4.8               | T200 Value                                     | . 2-29         |

| 2.4.9               | N201 Value                                     | . 2-29         |

| 2.4.10              | Receive Pool Number and Error Mask Valid (EVM) | . 2-31         |

| 2.4.11              | Tx Next Pointer                                | . 2-31         |

| 2.4.12              | Tx Next Acknowledge Pointer                    | . 2-31         |

| 2.4.13              | Tx Next LLT Pointer                            | . 2-31         |

| 2.4.14              | REJ Tx Counter                                 | . 2-32         |

| 2.4.15              | RNR Tx Counter                                 | . 2-32         |

| 2.4.16              | REJ Rx Counter                                 | . 2-32         |

| 2.4.17              | RNR Rx Counter                                 | . 2-33         |

| 2.4.18              | User Tx Next Confirm Pointer                   | . 2-33         |

| 2.4.19              | User Tx Last Queued Pointer                    | . 2-33         |

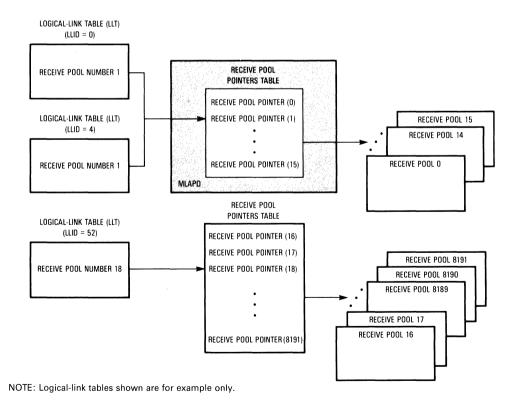

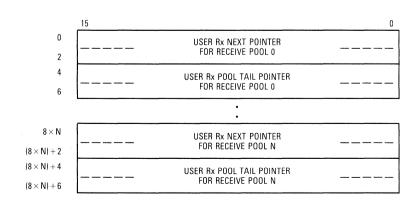

| 2.5                 | Receive Pool Pointers Table                    | . 2-34         |

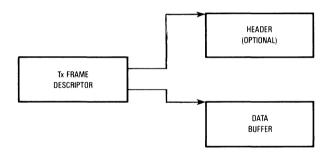

| 2.6                 | Transmit Frame Descriptor                      | . 2-35         |

| 2.6.1               | Status Bits                                    | . 2-36         |

| 2.6.2               | Next Tx Frame Descriptor Pointer               | . 2-37         |

| 2.6.3               | Data Buffer Pointer                            | . 2-37         |

| 2.6.4               | Control Bits and Data Length                   | . 2-37         |

| 2.6.5               | Frame Type and LLID                            | . 2-38         |

| 2.6.6               | Header Pointer                                 | . 2-39         |

| 2.6.7               | Header Length                                  | . 2-39         |

| 2.6.8               | Retransmit Count                               | . 2-39         |

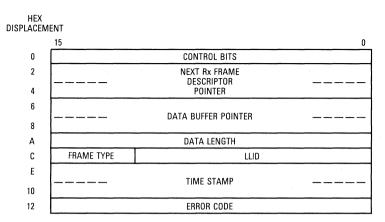

| 2.7                 | Receive Frame Descriptor                       | . 2-39         |

| 2.7.1               | Control Bits                                   | . 2-40         |

| 2.7.2               | Next Rx Frame Descriptor Pointer               | . 2-41         |

| 2.7.3               | Data Buffer Pointer                            | . 2-41         |

| 2.7.4               | Data Length                                    | . 2-41         |

| 2.7.5               | Frame Type and LLID                            | . 2-42         |

| 2.7.6               | Time Stamp                                     | . 2-44         |

| 2.7.7               | Error Code                                     | . 2-44         |

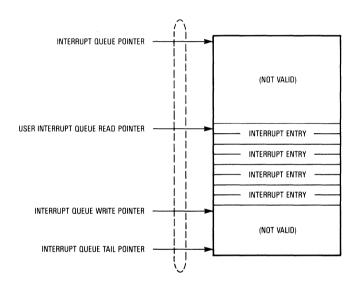

| 2.8                 | Interrupt Queue                                | . 2-44         |

| 2.8.1               | Interrupt Events                               |                |

| 2.8.2               | Interrupt Arguments                            |                |

| 2.8.2.1             | MDL Error Indication Arguments                 |                |

| 2.8.2.2             | Link Counter Threshold Reached Arguments       |                |

| Paragrapi<br>Number | Title                                         | Page<br>Number |

|---------------------|-----------------------------------------------|----------------|

| 2.9                 | Timer Table                                   | . 2-52         |

| 2.9.1               | Timer Operations                              | . 2-53         |

| 2.10                | Level 2 Queue                                 |                |

|                     | Section 3                                     |                |

|                     | Internal Registers                            |                |

| 3.1                 | Directly Accessible Registers                 | . 3-1          |

| 3.1.1               | Command Register                              | . 3-1          |

| 3.1.2               | Semaphore Register                            | . 3-2          |

| 3.1.3               | Interrupt Vector Register                     | . 3-2          |

| 3.1.4               | Data Register                                 | . 3-3          |

| 3.2                 | Indirectly Accessible Registers               |                |

| 3.2.1               | CAM                                           | 3-4            |

| 3.2.2               | N200 Value                                    | . 3-5          |

| 3.2.3               | T203 Value                                    |                |

| 3.2.4               | Highest Active LLID                           | . 3-5          |

| 3.2.5               | T200 Counter                                  |                |

| 3.2.6               | T203 Counter                                  | . 3-6          |

| 3.2.7               | Pool Number                                   | . 3-6          |

| 3.2.8               | L2 Tail Displacement                          | . 3-6          |

| 3.2.9               | External L2 Queue Displacement Registers      | . 3-6          |

| 3.2.10              | Tx XID/UI LLID                                |                |

| 3.2.11              | Tx XID/UI DLCI                                | . 3-7          |

| 3.2.12              | Internal L2 Queue Displacement Registers      | . 3-7          |

| 3.2.13              | Tx FD Status                                  | . 3-7          |

| 3.2.14              | Tx V(S)/V(R)                                  |                |

| 3.2.15              | CTS Timeout Counter                           | . 3-8          |

| 3.2.16              | Tx Maximum Number of Outstanding I Frames (K) | . 3-8          |

| 3.2.17              | Tx V(A)                                       |                |

| 3.2.18              | Tx Link Status                                | . 3-8          |

| 3.2.19              | Current Queue In-Service                      | . 3-8          |

| 3.2.20              | Scan Length Counter                           | . 3-9          |

| 3.2.21              | Tx   LLID                                     |                |

| 3.2.22              | Tx   DLCI                                     | . 3-9          |

| 3.2.23              | Retransmit Threshold                          | . 3-9          |

| 3.2.24              | Rx Address                                    | . 3-10         |

| 3.2.25              | Rx N201                                       | . 3-10         |

| 3.2.26              | Rx Link Status                                | . 3-10         |

| 3.2.27              | Rx LLID                                       | . 3-10         |

| 3.2.28              | Rx DLCI                                       | . 3-10         |

| Paragraph<br>Number | Title                                                  | Page<br>Number |

|---------------------|--------------------------------------------------------|----------------|

| 3.2.29              | Rx Frame ID                                            | . 3-10         |

| 3.2.30              | Tx Address                                             | . 3-11         |

| 3.2.31              | Time Stamp                                             | . 3-11         |

| 3.2.32              | RxFIFO Overrun Counter                                 | . 3-11         |

| 3.2.33              | TxFIFO Underrun Counter                                | . 3-11         |

| 3.2.34              | Invalid Address Counter                                | . 3-11         |

| 3.2.35              | Inactive DLCI Counter                                  | . 3-11         |

| 3.2.36              | Discarded Frame Counter                                | . 3-12         |

| 3.2.37              | Short Frame Counter                                    | . 3-12         |

| 3.2.38              | CRC Error Counter                                      | . 3-12         |

| 3.2.39              | Abort/Nonoctet Counter                                 |                |

| 3.2.40              | Tx REJ/RNR Counter                                     | . 3-12         |

| 3.2.41              | Rx REJ/RNR Counter                                     | . 3-13         |

| 3.2.42              | CTS Timeout Threshold                                  |                |

| 3.2.43              | Scan Length I Queues 0-3                               |                |

| 3.2.44              | Scan Length XID/UI Queues 0, 1                         |                |

| 3.2.45              | Interrupt Mask                                         |                |

| 3.2.46              | Protocol Error Mask                                    |                |

| 3.2.47              | Nonprotocol Error Mask                                 |                |

| 3.2.48              | Rx Maximum Number of Outstanding Frames or Filter Mask |                |

|                     | (Word 1)                                               |                |

| 3.2.49              | Rx V(A) or Filter Mask (Word 2)                        |                |

| 3.2.50              | Rx V(S)/V(R) or Filter Match (Word 1)                  |                |

| 3.2.51              | Rx Control or Filter Match (Word 2)                    |                |

| 3.2.52              | Tx LLT Transmit Status                                 |                |

| 3.2.53              | Nonstandard Control Field                              |                |

| 3.2.54              | Revision Number                                        |                |

| 3.2.55              | Tx Next Pointer                                        |                |

| 3.2.56              | Tx LLT Pointer                                         |                |

| 3.2.57              | Global XID/UI Head Pointer                             |                |

| 3.2.58              | I Queue 0-3 Head Pointer Registers                     |                |

| 3.2.59              | l Queue 0-3 Tail Pointer Registers                     |                |

| 3.2.60              | L2 Queue Pointer                                       |                |

| 3.2.61              | Match Table Pointer                                    | . 3-17         |

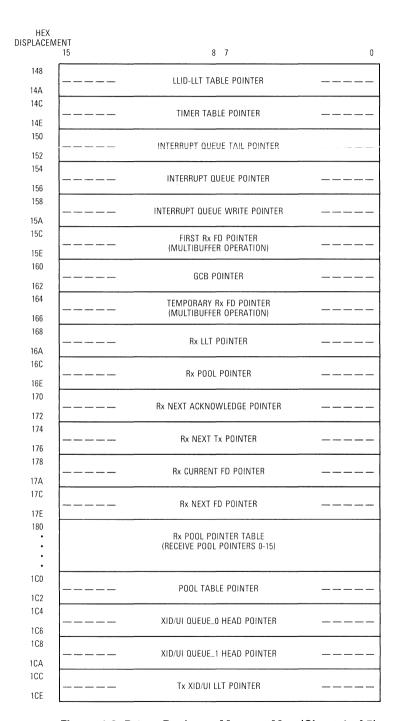

| 3.2.62              | LLID-LLT Table Pointer                                 | . 3-17         |

| 3.2.63              | Timer Table Pointer                                    | . 3-17         |

| 3.2.64              | Interrupt Queue Tail Pointer                           | . 3-17         |

| 3.2.65              | Interrupt Queue Pointer                                | . 3-18         |

| 3.2.66              | Interrupt Queue Write Pointer                          | . 3-18         |

| 3.2.67              | First Rx FD Pointer                                    | . 3-18         |

| 3.2.68              | GCB Pointer                                            | . 3-18         |

| Paragrapl<br>Number | h<br>Title                   | Page<br>Number |

|---------------------|------------------------------|----------------|

| 3.2.69              | Temporary Rx FD Pointer      | . 3-18         |

| 3.2.70              | Rx LLT Pointer               |                |

| 3.2.71              | Rx Pool Pointer              | . 3-19         |

| 3.2.72              | Rx Next Acknowledge Pointer  |                |

| 3.2.73              | Rx Next Tx Pointer           | . 3-19         |

| 3.2.74              | Rx Current FD Pointer        | . 3-19         |

| 3.2.75              | Rx Next FD Pointer           | . 3-19         |

| 3.2.76              | Pool Table Pointer           | . 3-20         |

| 3.2.77              | XID/UI Queue 0 Head Pointer  | . 3-20         |

| 3.2.78              | XID/UI Queue 1 Head Pointer  |                |

| 3.2.79              | Tx XID/UI LLT Pointer        | . 3-20         |

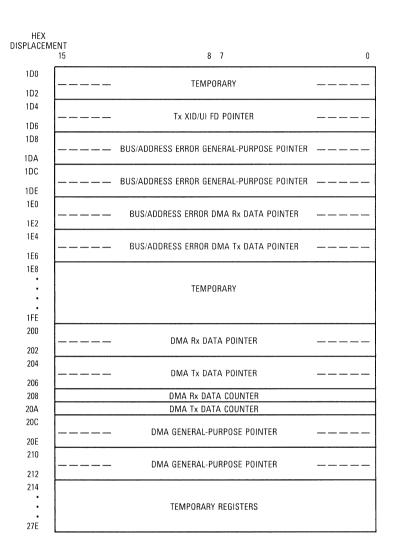

| 3.2.80              | Tx XID/UI FD Pointer         |                |

| 3.2.81              | Bus/Address Error Pointers   |                |

| 3.2.82              | DMA Rx Data Pointer          | . 3-21         |

| 3.2.83              | DMA Tx Data Pointer          | . 3-21         |

| 3.2.84              | DMA Rx Data Counter          | . 3-21         |

| 3.2.85              | DMA Tx Data Counter          |                |

| 3.2.86              | DMA General-Purpose Pointers | . 3-21         |

|                     | Section 4 Command Set        |                |

| 4.1                 | Initialization               | 4-1            |

| 4.1.1               | RESET Command                |                |

| 4.1.2               | SET_BUS_WIDTH_8 Command      | . 4-2          |

| 4.1.3               | SET_BUS_WIDTH_16 Command     | . 4-2          |

| 4.1.4               | INIT Command                 |                |

| 4.2                 | Test/Diagnostic              |                |

| 4.2.1               | DMA_TEST_Command             |                |

| 4.2.2               | DUMP Command                 | . 4-4          |

| 4.3                 | Host — MLAPD Interface       | . 4-9          |

| 4.3.1               | OFF-LINE Command             | . 4-9          |

| 4.3.2               | ON-LINE Command              | . 4-9          |

| 4.3.3               | RELOAD Command               | . 4-9          |

| 4.3.4               | DUMP_STATISTICS Command      | . 4-11         |

| 4.3.5               | PRESET_STATISTICS Command    | . 4-11         |

| 4.3.6               | ENABLE_IRQ Command           |                |

| 4.3.7               | ASSIGN_POOL_POINTER Command  | . 4-12         |

| 4.4                 | Protocol                     | 4-12           |

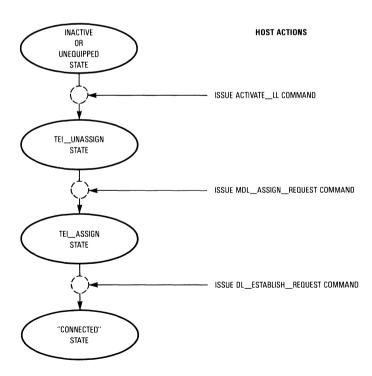

| 4.4.1               | MDL_ASSIGN_REQUEST Command   | . 4-13         |

| 4.4.2               | DL_ESTABLISH_REQUEST Command | . 4-13         |

| Paragraph<br>Number | n<br>Title                            | Page<br>Number |

|---------------------|---------------------------------------|----------------|

| 4.4.3               | DL_DATA_REQUEST Command               | . 4-14         |

| 4.4.4               | RELINK_REQUEST Command                | . 4-15         |

| 4.4.5               | GLOBAL_XID/UI_REQUEST Command         | . 4-15         |

| 4.4.6               | XID/UI_QUEUE_0_REQUEST Command        | 4-16           |

| 4.4.7               | XID/UI_QUEUE_1_REQUEST Command        | . 4-16         |

| 4.4.8               | MDL_ERROR_RESPONSE Command            | . 4-17         |

| 4.4.9               | DL_RELEASE_REQUEST Command            | . 4-17         |

| 4.4.10              | MDL_REMOVE_REQUEST Command            | . 4-18         |

| 4.5                 | Protocol Extension                    | . 4-18         |

| 4.5.1               | ACTIVATE_LL Command                   | . 4-18         |

| 4.5.2               | DEACTIVATE_LL Command                 | . 4-19         |

| 4.5.3               | REMOTE_STATUS_REQUEST Command         | . 4-20         |

| 4.5.4               | SET_LOCAL_BUSY Command                | 4-20           |

| 4.5.5               | CLEAR_LOCAL_BUSY Command              | . 4-21         |

| 4.5.6               | STOP_TX_I Command                     | 4-21           |

| 4.5.7               | STOP_GLOBAL_XID/UI Command            | . 4-21         |

| 4.5.8               | STOP_XID/UI_QUEUE_0 Command           | 4-22           |

| 4.5.9               | STOP_XID/UI_QUEUE_1 Command           | . 4-22         |

| 4.6                 | Command Summary                       | . 4-22         |

|                     | Section 5 Transmit Process            |                |

| 5.1                 | Transmit Servicing Scheme             | . 5-1          |

| 5.2                 | Transmit   Frame Process              |                |

| 5.2.1               | I Frame Queue Structure               |                |

| 5.2.2               | Logical-Link Transmit Queue Structure |                |

| 5.2.3               | I Frame Transmission Queueing         |                |

| 5.2.4               | MLAPD I Frame Queue Processing        |                |

| 5.2.5               | Stopping I Frame Transmission         |                |

| 5.2.6               | Collecting Acknowledged Frames        |                |

| 5.3                 | Transmit XID/UI Frame Processing      |                |

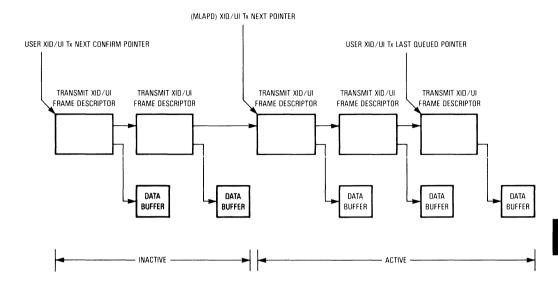

| 5.3.1               | XID/UI Queue Structure                |                |

| 5.3.2               | XID/UI Transmit Queue Usage           | 5-9            |

| 5.3.3               | XID/UI Frame Transmission Queueing    |                |

| 5.3.4               | MLAPD XID/UI Queue Processing         |                |

| 5.3.5               | Stopping XID/UI Frame Transmission    |                |

| 5.3.6               | Collecting Transmitted XID/UI Frames  |                |

| 5.4                 | Errors During Frame Transmission      |                |

|                     |                                       |                |

| Paragraph<br>Number |                                                | Page<br>Number |

|---------------------|------------------------------------------------|----------------|

|                     | Section 6                                      |                |

|                     | Receive Process                                |                |

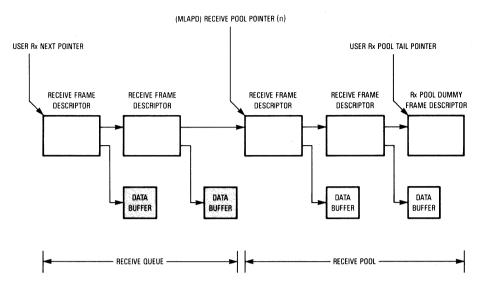

| 6.1                 | Receive Data Structures                        | . 6-1          |

| 6.1.1               | Receive Pool Format                            | . 6-1          |

| 6.1.2               | Receive Queue Format                           | . 6-3          |

| 6.1.3               | User Receive Pointers                          | . 6-3          |

| 6.2                 | MLAPD Receive Processing                       | . 6-4          |

| 6.3                 | Collecting Received Frames                     | . 6-4          |

|                     | Section 7                                      |                |

|                     | Exception Processing                           |                |

| 7.1                 | Interrupt Mechanism                            | . 7-1          |

| 7.1.1               | Interrupt Queue Handling                       |                |

| 7.1.2               | Selecting Polled or Interrupt-Driven Operation |                |

| 7.1.3               | Collecting Interrupt Events                    |                |

| 7.1.4               | Interrupt Queue Overflow                       |                |

| 7.2                 | Bus Error Operation                            |                |

| 7.3                 | Address Error Operation                        | . 7-3          |

|                     | Section 8                                      |                |

|                     | MLAPD Implementation of LAPD                   |                |

| 8.1                 | MLAPD Initialization Procedure                 | . 8-1          |

| 8.2                 | Initialization of Logical Links                |                |

| 8.2.1               | Broadcast Link Initialization                  |                |

| 8.2.1.1             | Broadcast Link Initialization Procedure        |                |

| 8.2.2               | Signaling Link Initialization                  | . 8-3          |

| 8.3                 | Assignment Procedure                           | . 8-4          |

| 8.4                 | Link Setup Procedure                           | . 8-4          |

| 8.5                 | Link Release Procedure                         | . 8-5          |

| 8.6                 | Collision of Unnumbered Command Frames         | . 8-7          |

| 8.7                 | Transmit Procedure                             | . 8-7          |

| 8.7.1               | Information Frame Preparation                  | . 8-7          |

| 8.7.2               | Information Frame Transmission                 |                |

| 8.7.3               | XID/UI/Nonstandard_control Frame Preparation   |                |

| 8.7.4               | XID/UI/Nonstandard_control Frame Transmission  |                |

| 8.8                 | Reception Procedure                            |                |

| 8.8.1               | Information Frame Reception                    |                |

| 8.8.2               | Invalid Frames Reception                       | . 8-10         |

| Paragraph<br>Number | Title                                           | Page<br>Number |

|---------------------|-------------------------------------------------|----------------|

| 8.8.3               | Bad Frames Reception                            | . 8-11         |

| 8.8.4               | Frame Reject Mode                               | . 8-11         |

| 8.8.5               | XID/UI/Nonstandard_control Frame Reception      | . 8-11         |

| 8.8.6               | Receiving an Out-Of-Sequence   Frame            | . 8-11         |

| 8.8.7               | Receiving a FRMR Frame                          | . 8-12         |

| 8.9                 | Frame Types Allowed in Each Link State          |                |

| 8.9.1               | TEI_UNASSIGN and EST_WAIT_TEI States            |                |

| 8.9.2               | TEI_ASSIGNED, AWAIT_EST, and AWAIT_REL States   |                |

| 8.9.3               | Connected States                                |                |

| 8.10                | Flow Control and Error Control Procedures       |                |

| 8.10.1              | Local Busy Condition                            |                |

| 8.10.2              | Awaiting Acknowledgement                        |                |

| 8.10.3              | Receiving Acknowledgement                       |                |

| 8.10.4              | Receiving a REJ Frame                           |                |

| 8.10.5              | Receiving a RNR Frame                           |                |

| 8.11                | Error Handling Options                          |                |

| 8.11.1              | Frame Reject Mode                               |                |

| 8.11.2              | CCITT/DMI Mode                                  |                |

| 0.1                 | Section 9 MLAPD Implementation of Special Modes | 0.1            |

| 9.1                 | Nonprotocol Links                               |                |

| 9.1.1               | Setup Procedure                                 |                |

| 9.1.2               | Release Procedure                               |                |

| 9.1.3               | Queuing Frames for Transmission                 |                |

| 9.1.4               | MLAPD Transmit Queue Processing                 |                |

| 9.1.5               | MLAPD Frame Transmission                        |                |

| 9.1.6               | Stopping Frame Transmission                     |                |

| 9.1.7               | Collecting Transmitted Frames                   |                |

| 9.1.8               | Receive Structures                              |                |

| 9.1.9               | MLAPD Frame Reception                           |                |

| 9.1.10              | Restrictions                                    |                |

| 9.2<br>9.2.1        | Multibuffer Mode                                |                |

| 9.2.1               | Filter Mode                                     |                |

| 9.2.2               | Restrictions                                    |                |

| 9.3                 | Parallel Assist Mode                            |                |

| 9.4                 | Line Monitor                                    |                |

| 9.4                 | System Loopback Testing                         |                |

| 9.6                 | Memory-to-Memory Operation                      |                |

| 9.6.1               | Handling Received Frames                        |                |

| 9.6.2               | Handling Transmit Frames                        |                |

|                     |                                                 |                |

| Paragraph<br>Number |                                                          | Page<br>Numbe |

|---------------------|----------------------------------------------------------|---------------|

|                     | Section 10                                               |               |

|                     | Signal Description                                       |               |

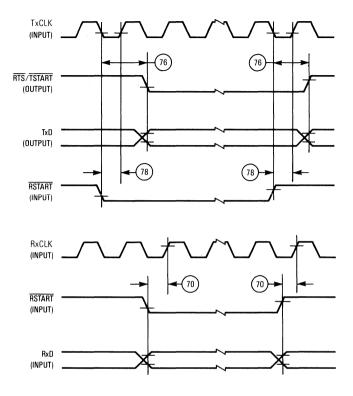

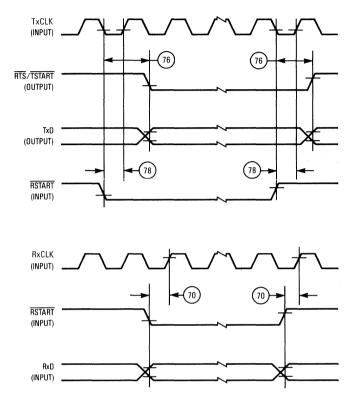

| 10.1                | Serial Interface                                         | 10-2          |

| 10.1.1              | Modem Control Signals                                    |               |

| 10.1.1.1            | Request-to-Send (RTS) or Transmit Start (TSRART)         | 10-2          |

| 10.1.1.2            | Clear-to-Send (CTS) or Receive Start (RSTART)            | 10-2          |

| 10.1.2              | Transmit Signals                                         | 10-3          |

| 10.1.2.1            | Transmit Clock (TxCLK)                                   | 10-3          |

| 10.1.2.2            | Transmit Data (TxD)                                      | 10-3          |

| 10.1.3              | Receive Signals                                          | 10-3          |

| 10.1.3.1            | Receive Clock (RxCLK)                                    | 10-3          |

| 10.1.3.2            | Receive Data (RxD)                                       | 10-4          |

| 10.2                | Motorola Bus Interface                                   | 10-4          |

| 10.2.1              | Motorola/Intel Mode (MOT/INT)                            | 10-4          |

| 10.2.2              | Address Bus (A1-A23)                                     | 10-4          |

| 10.2.3              | Data Bus (D0-D15)                                        | 10-5          |

| 10.2.4              | Bus Control Signals                                      | 10-5          |

| 10.2.4.1            | Chip Select (CS)                                         | 10-5          |

| 10.2.4.2            | Address Strobe(AS)                                       | 10-5          |

| 10.2.4.3            | Read/Write (R/W)                                         | 10-5          |

| 10.2.4.4            | Upper Data Strobe (UDS/A0) and Lower Data Stobe (LDS/DS) | 10-5          |

| 10.2.4.5            | Data Transfer Acknowledge (DTACK)                        | 10-6          |

| 10.2.5              | Bus Arbitration Signals                                  | 10-6          |

| 10.2.5.1            | Bus Request (BR)                                         | 10-6          |

| 10.2.5.2            | Bus Grant (BG)                                           | 10-6          |

| 10.2.5.3            | Bus Grant Acknowledge (BGACK)                            | 10-6          |

| 10.2.6              | Interrupt Control Signals                                | 10-7          |

| 10.2.6.1            | Interrupt Request (IRQ)                                  | 10-7          |

| 10.2.6.2            | Interrupt Acknowledge (IACK)                             | 10-7          |

| 10.2.7              | Bus Exception Signals                                    | 10-7          |

| 10.2.7.1            | Reset (RESET)                                            | 10-7          |

| 10.2.7.2            | Halt (HALT)                                              |               |

| 10.2.7.3            | Bus Error (BERR)                                         | 10-7          |

| 10.2.7.4            | Retry (RETRY)                                            | 10-7          |

| 10.2.8              | System Clock (CLK) Signal                                | 10-8          |

| 10.2.9              | Motorola Signal Summary                                  | 10-8          |

| 10.3                | Intel-Compatible Bus Interface                           | 10-9          |

| 10.3.1              | Motorola/Intel Mode (MOT/INT)                            |               |

| 10.3.2              | Address Bus (A0-A23)                                     | 10-9          |

| 10.3.3              | Data Bus (D0-D15)                                        | 10-9          |

| Paragraph<br>Number |                                 | Page<br>Number |

|---------------------|---------------------------------|----------------|

| 10.3.4              | Bus Control Signals             | 10-9           |

| 10.3.4.1            | Chip Select (CS)                | 10-9           |

| 10.3.4.2            | Address Strobe (AS)             | 10-9           |

| 10.3.4.3            | Read (RD)                       | 10-10          |

| 10.3.4.4            | Write ( <del>WR</del> )         | 10-10          |

| 10.3.4.5            | Bus High Enable (BHE)           | 10-10          |

| 10.3.4.6            | Ready (READY)                   | 10-10          |

| 10.3.5              | Bus Arbitration Signals         | 10-11          |

| 10.3.5.1            | Hold Request (HRQ)              | 10-11          |

| 10.3.5.2            | Hold Acknowledge (HOLDA)        | 10-11          |

| 10.3.6              | Interrupt Control Signals       |                |

| 10.3.6.1            | Interrupt Request (INTR)        | 10-11          |

| 10.3.6.2            | Interrupt Acknowledge (INTA)    | 10-11          |

| 10.3.7              | Bus Exception Signals           | 10-11          |

| 10.3.7.1            | Reset (RESET)                   | 10-11          |

| 10.3.7.2            | Halt (HALT)                     |                |

| 10.3.7.3            | Bus Error (BERR)                | 10-12          |

| 10.3.7.4            | Retry (RETRY)                   | 10-12          |

| 10.3.8              | System Clock (CLK) Signal       |                |

| 10.3.9              | Intel Signal Summary            | 10-12          |

|                     | Section 11 Bus Operation        |                |

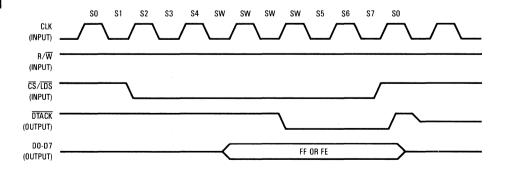

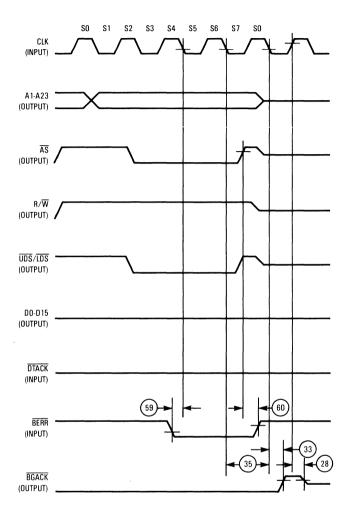

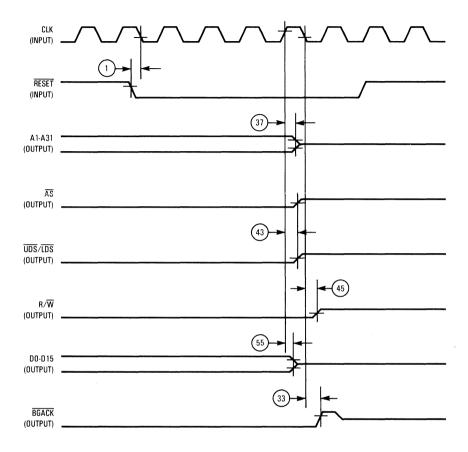

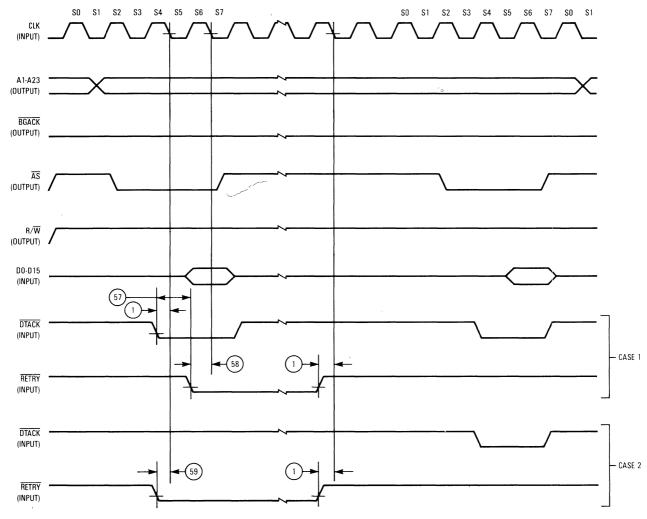

| 11.1                | Motorola Bus Operation          | 11-1           |

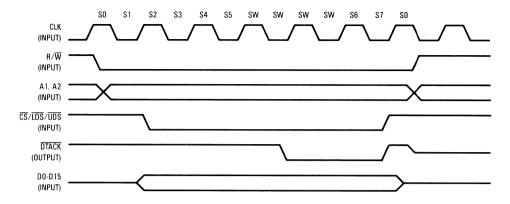

| 11.1.1              | Slave Operation Mode            |                |

| 11.1.1.1            | Host Processor Read Cycle       |                |

| 11.1.1.2            | Host Processor Write Cycle      |                |

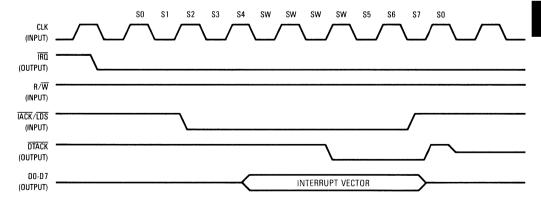

| 11.1.2              | Interrupt Acknowledge Cycle     |                |

| 11.1.3              | Master Operation                |                |

| 11.1.3.1            | DMA Priority Scheme             |                |

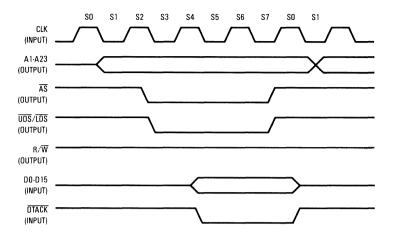

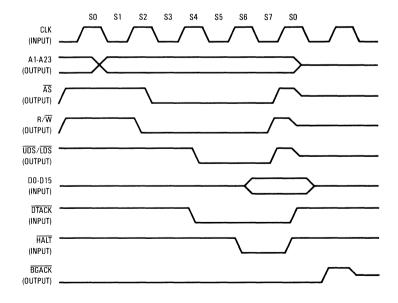

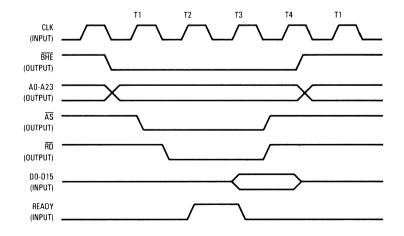

| 11.1.3.2            | MLAPD Read Cycles               |                |

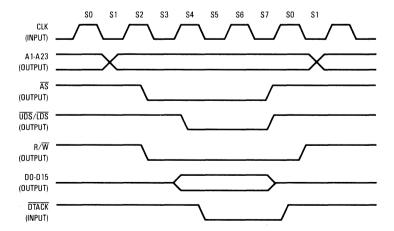

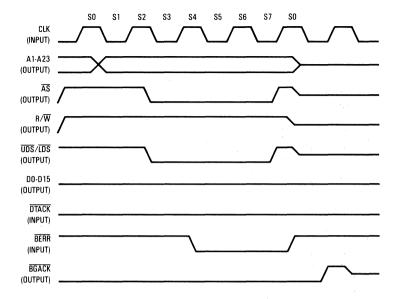

| 11.1.3.3            | MLAPD Write Cycles              |                |

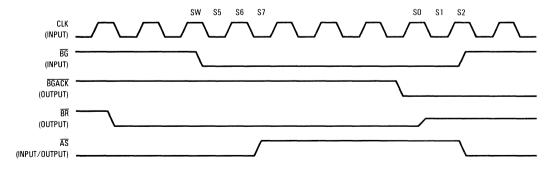

| 11.1.4              | Bus Arbitration                 |                |

| 11.1.5              | Bus Exception Control Functions |                |

| 11.1.5.1            | Halt                            | 11-7           |

| 11.1.5.1            | Bus Error                       |                |

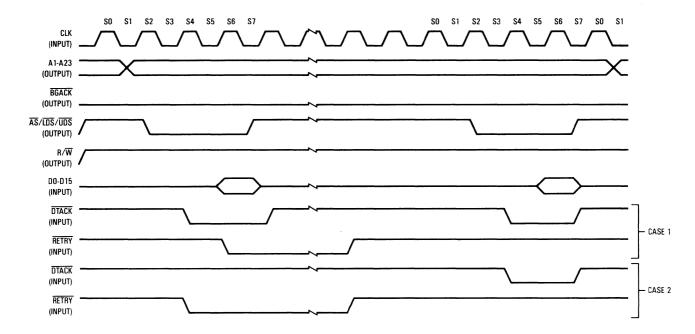

| 11.1.5.3            | Retry                           | 11-7           |

| 11.1.5.4            | Reset.                          | 11-8           |

|                     |                                 |                |

### **TABLE OF CONTENTS (Concluded)**

| Paragrapl<br>Number |                                                | Page<br>Number |

|---------------------|------------------------------------------------|----------------|

| 11.2                | Intel-Compatible Bus Operation                 | 11-8           |

| 11.2.1              | Slave Operation Mode                           | 11-8           |

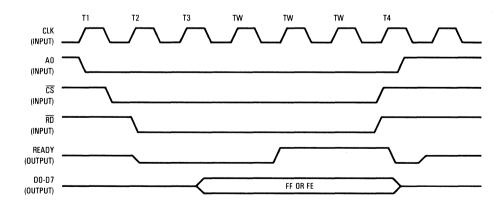

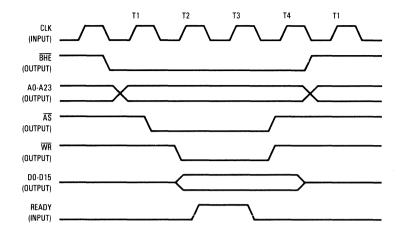

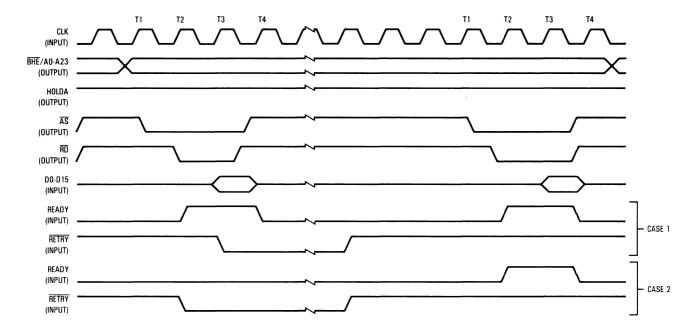

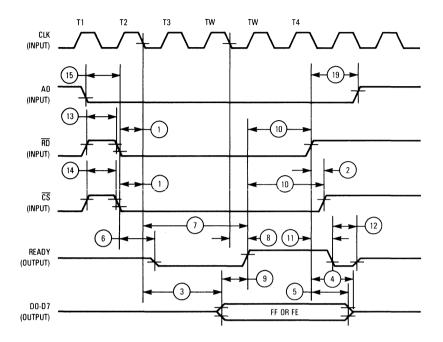

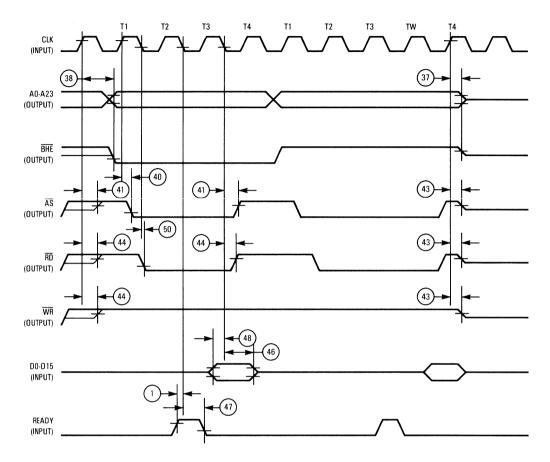

| 11.2.1.1            | Host Processor Read Cycle                      | 11-10          |

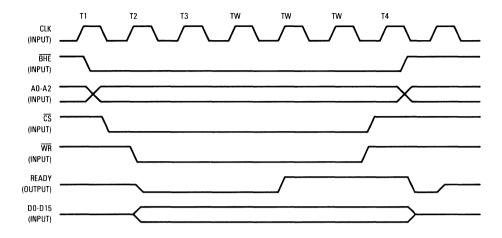

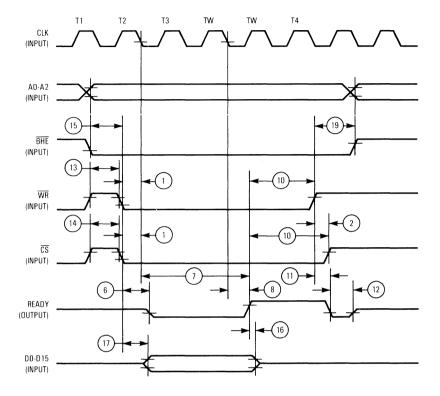

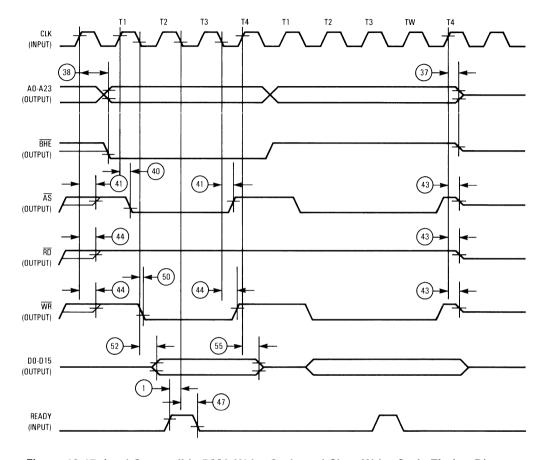

| 11.2.1.2            | Host Processor Write Cycle                     | 11-10          |

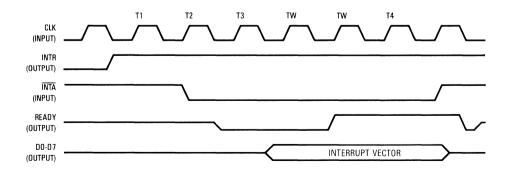

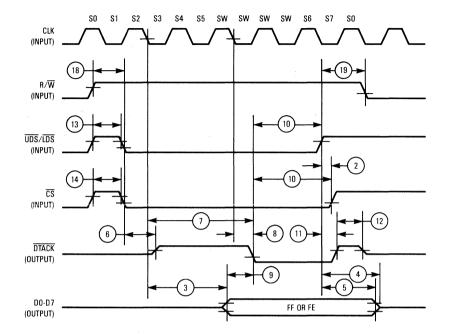

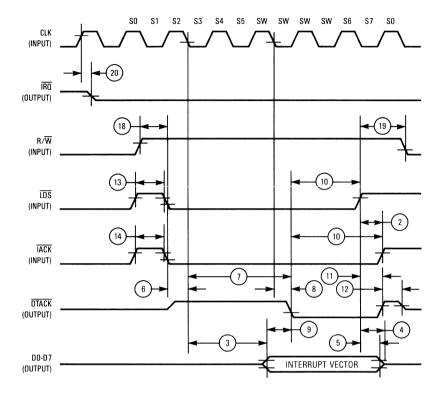

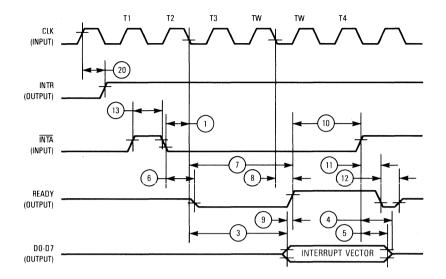

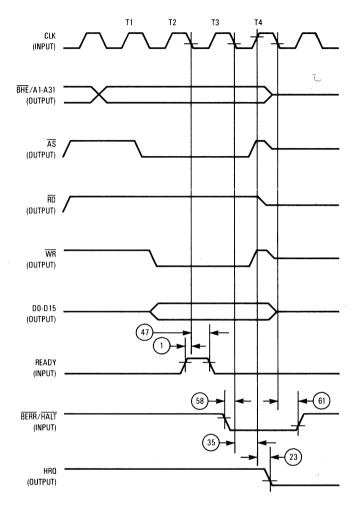

| 11.2.2              | Interrupt Acknowledge Cycle                    | 11-11          |

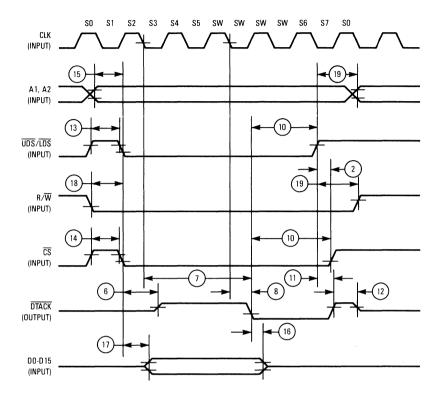

| 11.2.3              | Master Operation                               | 11-12          |

| 11.2.3.1            | DMA Priority Scheme                            | 11-12          |

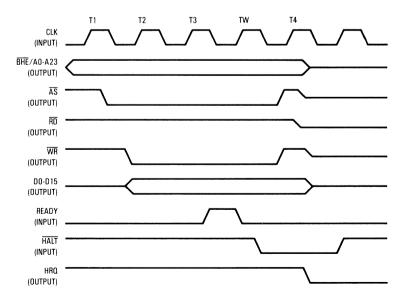

| 11.2.3.2            | MLAPD Read Cycle                               |                |

| 11.2.3.3            | MLAPD Write Cycle                              | <b>∮</b> 11-13 |

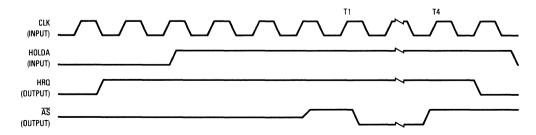

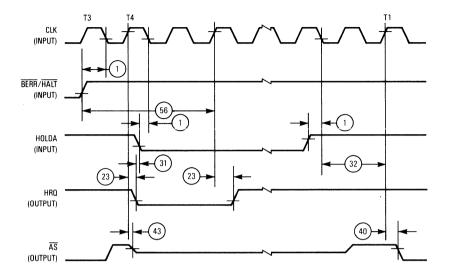

| 11.2.4              | Bus Arbitration                                |                |

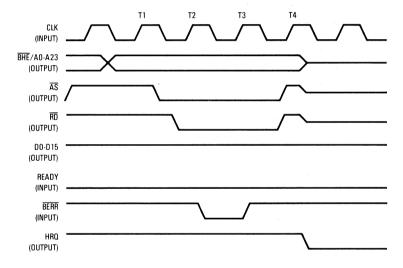

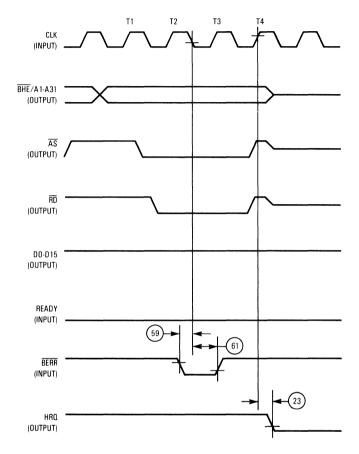

| 11.2.5              | Bus Exception Control Functions                | 11-14          |

| 11.2.5.1            | Halt                                           | 11-15          |

| 11.2.5.2            | Bus Error                                      |                |

| 11.2.5.3            | Retry                                          | 11-16          |

| 11.2:5.4            | Reset                                          | 11-16          |

|                     | Section 12                                     |                |

| 12.1                | Electrical Specifications                      | 10 1           |

| 12.1                | Maximum Ratings Thermal Characteristics        |                |

| 12.2                | Power Considerations                           |                |

| 12.3                | DC Electrical Characteristics                  |                |

| 12.4                | AC Electrical Characteristics                  |                |

| 12.5.1              | Motorola AC Electrical Characteristics         |                |

| 12.5.1              | Intel-Compatible AC Electrical Characteristics |                |

| 12.5.2              | inter-compatible Ac Electrical Characteristics | 12-17          |

|                     | Section 13                                     |                |

|                     | Mechanical Data                                |                |

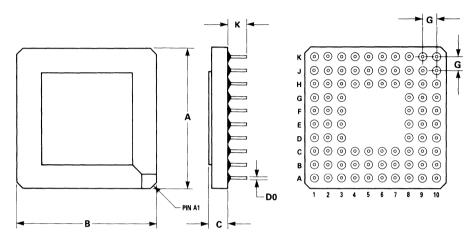

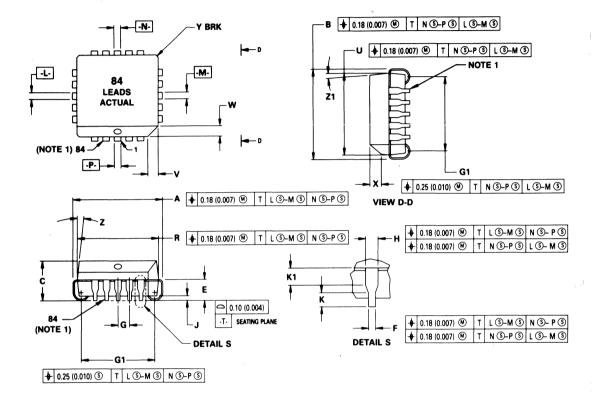

| 13.1                | Package Types                                  | 13-1           |

| 13.2                | Pin Assignments                                | 13-1           |

| 13.3                | Package Dimensions                             | 13-3           |

## Appendix A Software Interface Flows for the MALPD

## Appendix B Abbreviations

#### **LIST OF ILLUSTRATIONS**

| Figure<br>Number | Title                                             | Page<br>Number |

|------------------|---------------------------------------------------|----------------|

| 1-1              | Data Switching of the Future                      | 1-2            |

| 1-2              | LAPD In Relation to ISDN and ISO Models           | 1-4            |

| 1-3              | LAPD Frame Formats                                | 1-5            |

| 1-4              | Address Field Format                              | 1-5            |

| 1-5              | Control Field Formats                             | 1-5            |

| 1-6              | Command and Response Frames                       |                |

| 1-7              | MLAPD Protocol Controller Application Environment |                |

| 1-8              | Receive Process for Expanded Operation Mode       |                |

| 1-9              | Receive Process for On-Chip Operation Mode        |                |

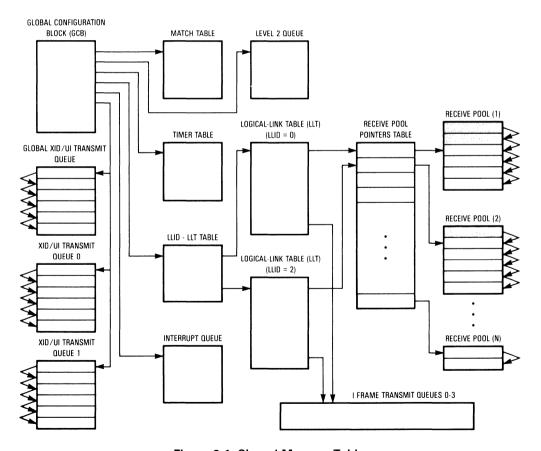

| 2-1              | Shared Memory Tables                              | 2-1            |

| 2-2              | GCB Format — Constants                            | 2-2            |

| 2-3              | GCB Format — Reloadable Variables                 | 2-3            |

| 2-4              | GCB Format — Statistics Threshold                 | 2-4            |

| 2-5              | GCB Format — Command Arguments                    | 2-4            |

| 2-6              | GCB — User Area                                   |                |

| 2-7              | Interrupt Mask Bits                               |                |

| 2-8              | Match Table Format                                | 2-22           |

| 2-9              | LLID-LLT Table                                    | 2-22           |

| 2-10             | Logical-Link Table Format                         | 2-23           |

| 2-11             | Transmit Status Bits Transition Table             |                |

| 2-12             | Receive Pool Pointers Table                       | 2-34           |

| 2-13             | Transmit Frame Configuration                      | 2-35           |

| 2-14             | Transmit Frame Descriptor                         |                |

| 2-15             | Receive Frame Descriptor                          |                |

| 2-16             | Interrupt Queue Structure                         |                |

| 2-17             | Interrupt Queue Entry Format                      |                |

| 2-18             | Timer Table Format                                |                |

| 2-19             | MLAPD Generated Level 2 Frames                    | 2-55           |

| 2-20             | Level 2 Queue Structure                           |                |

| 4-1              | DMA Transfer Configuration                        | 4-4            |

| 4-2              | Dump Registers Memory Map                         |                |

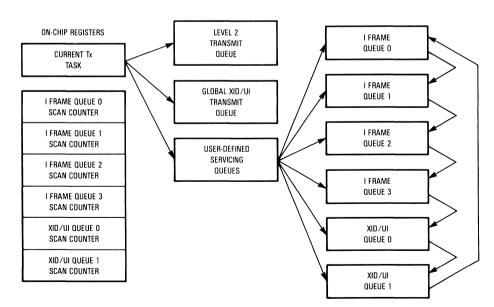

| 5-1              | Transmit Servicing Scheme                         | 5-2            |

| 5-1<br>5-2       | Transmit Servicing Scheme                         | 5-2<br>5-3     |

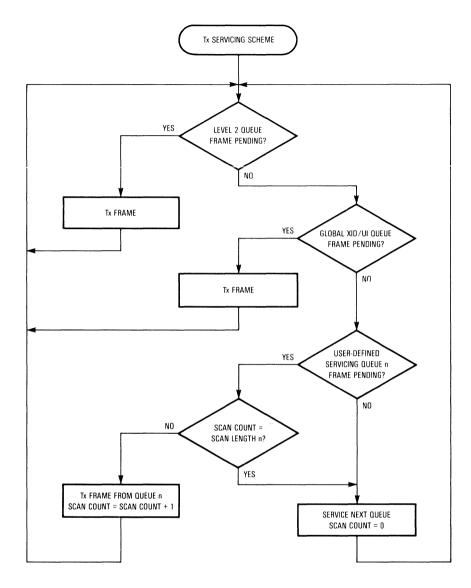

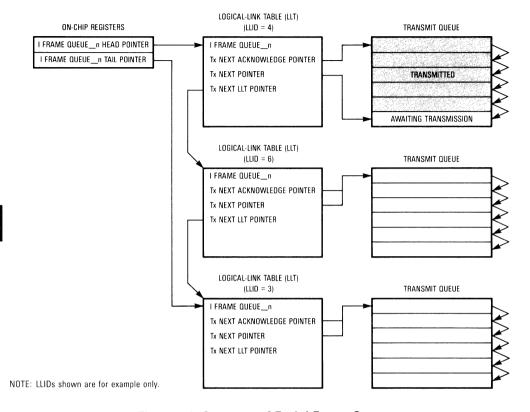

| 5-2<br>5-3       | Structure of Each I Frame Queue                   |                |

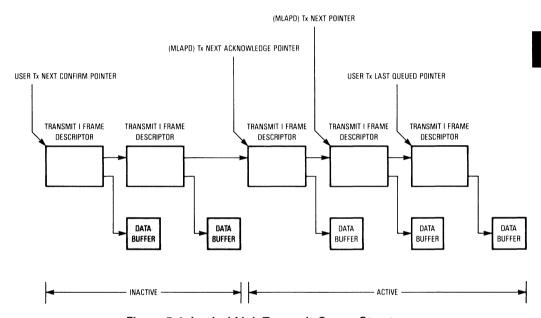

| 5-4              | Logical-Link Transmit Queue Structure             |                |

| 5-4<br>5-5       | XID/UI Transmit Queue Structure                   | 5-9            |

| J-J              | AID/OF Franching Queue Structure                  | J-J            |

### **LIST OF ILLUSTRATIONS (Continued)**

| Figure<br>Number                                                                                                                     | Title                                                     | Page<br>Number                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|

| 6-1<br>6-2                                                                                                                           | Receive Data Structure                                    | 6-2<br>6-3                                                                                  |

| 8-1                                                                                                                                  | MLAPD Protocol States                                     | 8-2                                                                                         |

| 9-1                                                                                                                                  | Memory-to-Memory Operation                                | 9-11                                                                                        |

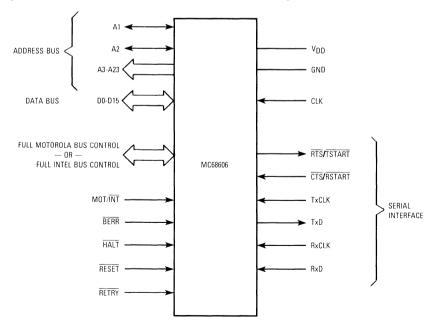

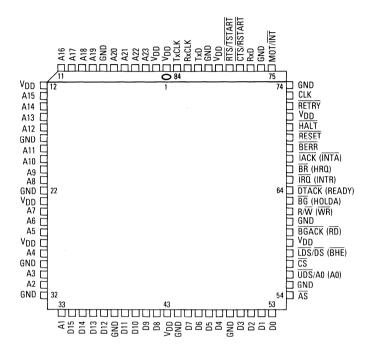

| 10-1                                                                                                                                 | MC68606 Signals                                           | 10-1                                                                                        |

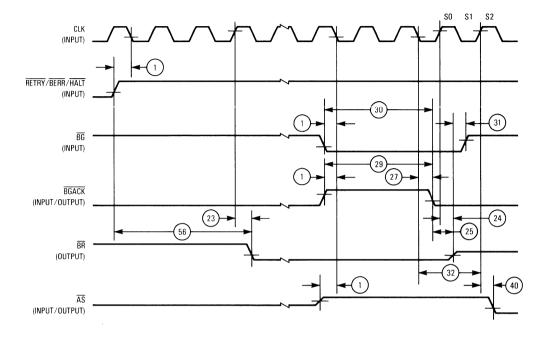

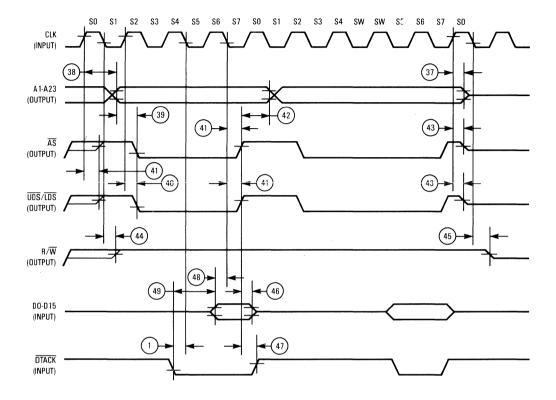

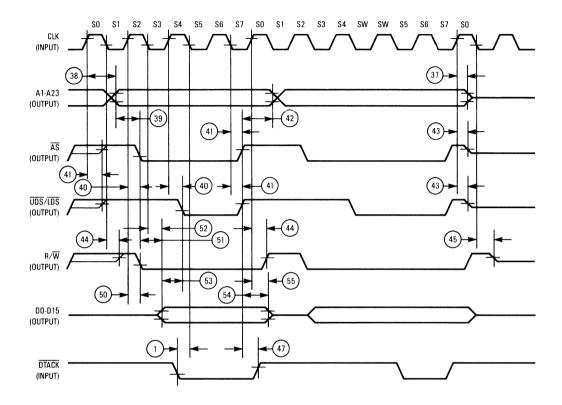

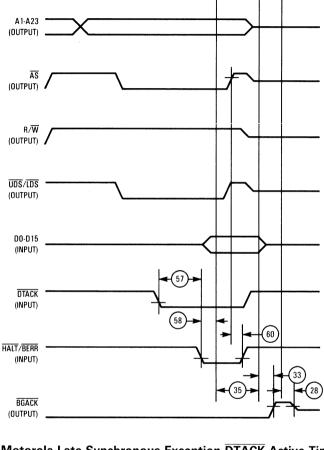

| 11-1<br>11-2<br>11-3<br>11-4<br>11-5<br>11-6<br>11-7<br>11-8<br>11-10<br>11-11<br>11-12<br>11-13<br>11-14<br>11-15<br>11-16<br>11-17 | Motorola Typical Host Byte Read Cycle Timing Diagram      | 11-7<br>11-8<br>11-9<br>11-10<br>11-11<br>11-11<br>11-13<br>11-14<br>11-14<br>11-15         |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11                                               | Motorola Host Processor Read Cycle Timing Diagram         | 12-6<br>12-7<br>12-8<br>12-9<br>12-10<br>12-11<br>12-12<br>12-13<br>12-14<br>12-15<br>12-16 |

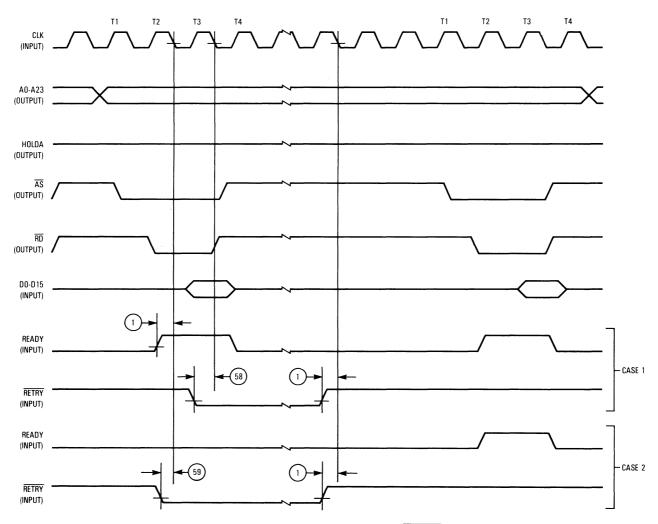

| 12-12                                                                                                                                | Intel-Compatible Host Processor Read Cycle Timing Diagram | 12-20                                                                                       |

### **LIST OF ILLUSTRATIONS (Concluded)**

| Figure<br>Number | Title                                                         | Page<br>Number |

|------------------|---------------------------------------------------------------|----------------|

| 12-13            | Intel-Compatible Host Processor Write Cycle Timing Diagram    | 12-21          |

| 12-14            | Intel-Compatible Interrupt Acknowledge Cycle Timing Diagram   | 12-22          |

| 12-15            | Intel-Compatible Bus Arbitration Timing Diagram               | 12-23          |

| 12-16            | Intel-Compatible DMA Read Cycle and Slow Read Cycle           |                |

|                  | Timing Diagram                                                | 12-24          |

| 12-17            | Intel-Compatible DMA Write Cycle and Slow Write Cycle         |                |

|                  | Timing Diagram                                                | 12-25          |

| 12-18            | Intel-Compatible Late Synchronous Exception READY Active      |                |

|                  | Timing Diagram                                                | 12-26          |

| 12-19            | Intel-Compatible Early Synchronous Exception READY Not Active |                |

|                  | Timing Diagram                                                | 12-27          |

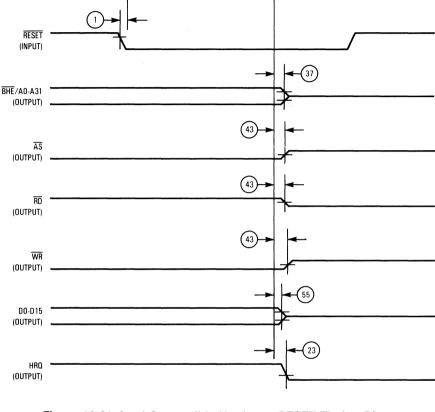

| 12-20            | Intel-Compatible Hardware RESET Timing Diagram                | 12-28          |

| 12-21            | Intel-Compatible Read Cycle with RETRY Timing Diagram         | 12-29          |

| 12-22            | Serial Data and Serial Clocks Timing Diagram                  | 12-30          |

#### LIST OF TABLES

| Table<br>Number | Title                                                   | Page<br>Number |

|-----------------|---------------------------------------------------------|----------------|

| 1-1             | Guide to Memory Structures                              | . 1-9          |

| 2-1<br>2-2      | Examples of Error Mask Handling                         |                |

| 3-1<br>3-2      | Motorola Bus Selection of Directly Accessible Registers |                |

| 4-1<br>4-2      | MLAPD Command Definitions                               |                |

| 8-1             | List of Link States                                     | . 8-1          |

| 10-1            | TxD Three-State Logic Control                           | . 10-4         |

| 10-2            | Motorola Data Strobe Control of Data Bus                |                |

| 10-3            | Motorola Signal Summary                                 | . 10-8         |

| 10-4            | Intel-Compatible Byte Addressing                        |                |

| 10-5            | Intel-Compatible Signal Summary                         | . 10-13        |

## SECTION 1 INTRODUCTION

The Motorola MC68606 Multi-Link LAPD (MLAPD) protocol controller is an integrated circuit implementing the link-access procedure (LAPD) protocol. LAPD is the proposed protocol for use at the link layer (ISO-Layer 2) for both signaling and data transfer in Integrated Services Digital Network (ISDN) configurations. The LAPD protocol is specified in International Telegraph and Telephone Consultative Committee (CCITT) Recommendation Q.920/Q.921.

The MLAPD device simplifies interfacing a microcomputer system to a packet network by providing the link-layer services of sequencing, error control, flow control, and multiplexing of logical links. Sequencing refers to numbering the frames to ensure arrival in the order of transmission. Error control ensures that frames arrive without errors; frames are retransmitted when errors are detected. Flow control ensures that the sender does not overwhelm the receiver with data. Multiplexing allows multiple logical-link connections to share a single physical circuit.

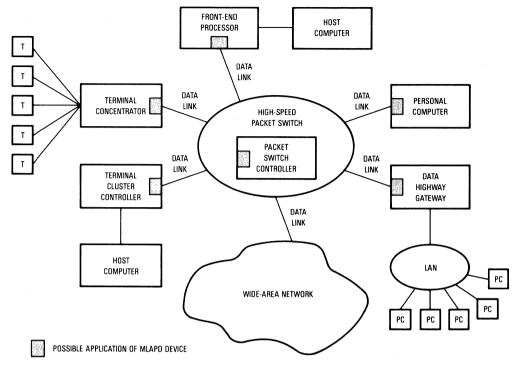

Current product implementations of this link-level protocol are accomplished with firmware. Firmware implementation significantly loads the local processor and presents limitations to both the maximum potential throughput of data and to the number of logical links which may be supported by such packet data interfaces. Figure 1-1 is a generic view of where the MLAPD device can be used to interconnect a variety of data endpoints in a high-speed packet switch network. The data links illustrated could differ functionally and provide data rates up to 2.048 Mbps.

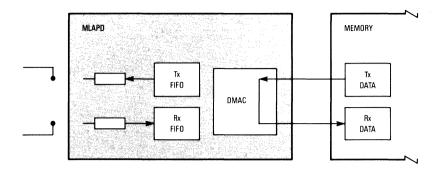

The MLAPD functions as an intelligent peripheral device to a central processing unit (CPU) in a microcomputer system. An on-chip direct memory access (DMA) controller transfers data packets to and from a buffer memory with minimal CPU assistance. A microcoded buffer-management scheme queues packets during transmission and reception. All link management duties are handled by the MLAPD device to maximize the bandwidth available for CPU operation and to increase the throughput for packet data transfer. This VLSI implementation provides a cost-effective solution, while encouraging a universal implementation of the LAPD protocol.

#### 1.1 FEATURE OVERVIEW

Key features of the MLAPD include:

• Full implementation of CCITT Recommendation Q.920/Q.921 LAPD with independent generation of commands and responses for each logical link.

Figure 1-1. Data Switching of the Future

- Control of up to 8192 logical links using a memory-based architecture, wherein the protocol controller and the supervising microprocessor communicate through shared memory.

- Reliable, interleaved data transfers for multiple logical links with the following protocol actions:

- HDLC framing with zero-bit insertion/deletion for a serial bit stream; or optional parallel assist mode where zero insertion/deletion is disabled and frame delineation is provided by external pins to simplify the external logic required to support a parallel interface to the physical level.

- Error control using a 16-bit cyclical redundancy check (CRC).

- Flow control to prevent data from accumulating at the receiving end faster than data can be processed.

- Termination of a nonchannelized serial bit stream with an aggregate rate in excess of 2.048 Mbps or optional memory-to-memory operation allowing the MLAPD to act as a LAPD controller independent of the system's physical level characteristics.

- User-defined priority for information (I) frame and exchange indentification/unnumbered information (XID/UI) frame transmission.

- Optional reception and transmission of a user-defined nonstandard LAPD unnumbered

(U) frame.

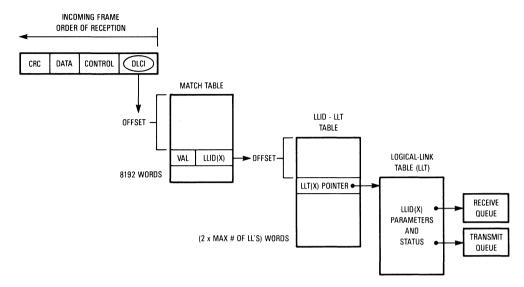

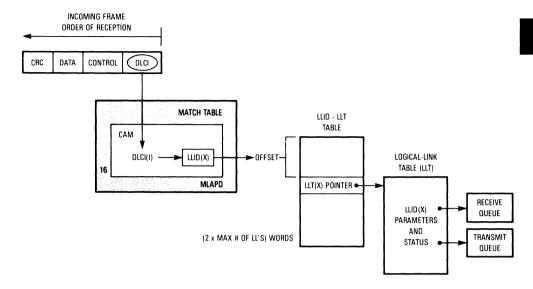

- On-chip, content addressable memory (CAM) provides address translation for up to 16 logical links. When supporting more than 16 logical links, translation is provided via a match table in shared memory.

- Error/statistical counters and maskable interrupts to the Level 3 process.

- Optional nonprotocol mode on a per-logical link basis, which allows the host to receive and transmit frames without application of the LAPD procedures by the MLAPD.

- Promiscuous receive mode in which the MLAPD receives all frames from the line and transfers the entire frame to memory:

- A received frame may be split between multiple memory buffers.

- A filtering mechanism allows the user to selectively receive frames based on the first 32-bits of each frame.

- System interface tailored for different microprocessor system implementations:

- Motorola M68000 and Intel iAPX86 Family bus interface options.

- 8- and 16-bit data bus support.

- Direct addressing of 16 Mbytes of system memory.

- Available in 12.5 MHz and 16.67 MHz system clock versions.

- 84-lead pin grid array (PGA) package and plastic, leadless chip carrier (PLCC) J-lead surface mount package.

- 1.5 micron HCMOS technology.

#### 1.2 ISDN COMMUNICATION MODEL

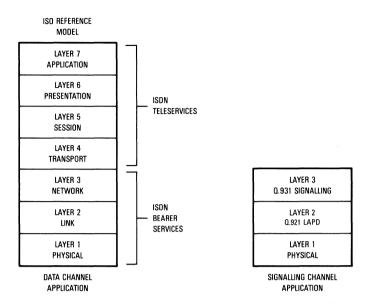

A review of the protocol conventions of the Open Systems Interconnect (OSI) model and of the proposed Integrated Services Digital Network (ISDN) model is pertinent to show where the LAPD protocol fits into both the OSI and ISDN models (see Figure 1-2). The LAPD protocol is the recommended data-link-layer protocol for a logical link used for signaling and also for a logical link used for data, or bearer, service. The physical level interface may also be the same for both signaling and data applications. The Level 3 interface depends upon the type of services provided. For termination of the link in a signaling case, the CCITT specifies the protocol in Recommendation Q.931. For data transport services, CCITT Recommendation X.25 Data Phase may be used at Level 3. In both applications, the LAPD protocol can be used as a universal link-layer protocol in an ISDN product family.

#### 1.3 LAPD FRAME FORMAT

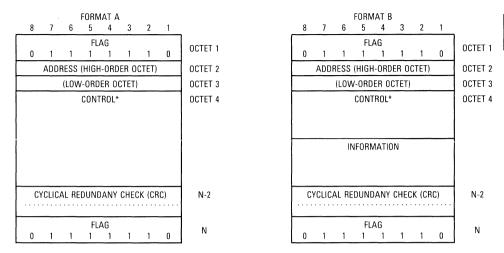

LAPD is specified by CCITT Recommendations Q.920/Q.921 (I.440/I.441). LAPD is a multiplexed derivative of the CCITT Recommendation X.25 LAPB, which is based on the HDLC frame format. The HDLC frame format consists of an address field (two bytes for LAPD), a control field (one or two bytes for LAPD), an optional information field of length n bytes (default of 128 or 260 bytes for LAPD), and a 16-bit CRC sequence. Frames are delineated by flag characters (011111110), and zero insertion/deletion is used to ensure data transparency. A minimum of two flags (an opening and closing flag) are transmitted between

Figure 1-2. LAPD In Relation to ISDN and ISO Models

frames. All frames are octet aligned. Octets within a frame are transmitted in ascending numerical order, with the least significant bit transmitted first. An exception to this rule is the transmission of the CRC sequence, where the coefficient of the highest order exponential term is transmitted first. The LAPD formats for frames containing and not containing an information field are shown in Figure 1-3.

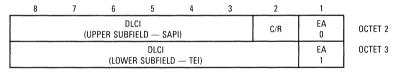

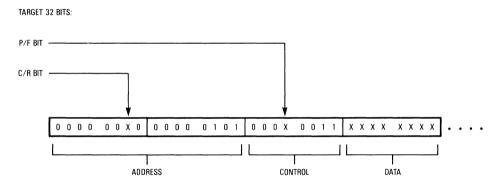

The address field format shown in Figure 1-4 specifies two Data-Link-Connection Identifier (DLCI) subfields, address field extension bits, and a command/response indication bit. The two DLCI subfields, service-access-point identifier (SAPI) and terminal-endpoint identifier (TEI), define the DLCI which is one of 8192 potential addresses, or logical links, that may be active on a single physical channel. The address field extension bit allows the address to span multiple octets by indicating which octet is the final address octet. The address field extension bit in the high order address byte is always set to zero and in the low order address byte is always set to one. The command/response bit identifies a frame as either a command or response. The endpoint designated as the user side sends commands with the C/R bit set to zero and responses with the C/R bit set to one. The endpoint designated as the network side sends commands with the C/R bit set to zero.

The control field defines the type of command or response frame. The three control field formats, supervisory (S), unnumbered (U) and information (I), are shown in Figure 1-5. The command and response frames defined for these three frame types are shown in Figure 1-6. S frames are used to perform data link supervisory control functions, such as I frame acknowledgement, I frame retransmission requests, and flow control. U frames provide

\* Unacknowledged Operation: One octet

Mutiple Frame Operation: Two octets for frames with sequence numbers (Modulo 128) One octet for frames without sequence numbers

Figure 1-3. LAPD Frame Formats

C/R = Command/response field bit = Address field extension bit DLCI = Data-Link-Connection Identifier SAPI = Service-Access Point Identifier = Terminal-Endpoint Identifier

Figure 1-4. Address Field Format

| CONTROL FIELD BITS<br>(MODULO 128) | 8 | 7 | 6 | 5    | 4 | 3 | 2 | 1   |

|------------------------------------|---|---|---|------|---|---|---|-----|

| I FORMAT                           |   |   |   | N(S) |   |   |   | 0   |

| TTOMWAT                            |   |   |   | N(R) |   |   |   | Р   |

| S FORMAT                           | Х | Х | Х | Х    | S | S | 0 | 1   |

| ĺ                                  |   |   |   | N(R) |   |   |   | P/F |

| U FORMAT                           | М | М | М | P/F  | M | М | 1 | 1   |

N(S) Send sequence number Poll bit

N(R) Receive sequence number P/F Poll bit when issued as a command Supervisory function bit Final bit when issued as a response Modifier function bit Reserved and set to zero

Figure 1-5. Control Field Formats

S

Μ

OCTET 4 OCTET 5 OCTET 4 OCTET 5 OCTET 4

| -           |             | -         | Encoding |     |   |      |   |   |    |     |

|-------------|-------------|-----------|----------|-----|---|------|---|---|----|-----|

| Format      | Commands Re | Responses | 8        | 7   | 6 | 5    | 4 | 3 | 2  | 1   |

| Information | I           |           |          |     |   | N(S) |   |   |    | 0   |

| Transfer    |             |           |          |     |   | N(R) |   | 7 |    | Р   |

| Supervisory | RR          | RR        | 0        | 0   | 0 | 0    | 0 | 0 | 0  | 1   |

|             |             |           |          |     |   | N(R) |   |   |    | P/F |

|             | RNR         | RNR       | 0        | 0   | 0 | 0    | 0 | 1 | 0  | 1   |

|             |             |           |          |     |   | N(R) |   |   |    | P/F |

|             | REJ         | REJ       | 0        | 0   | 0 | 0    | 1 | 0 | 0  | 1   |

|             |             |           |          |     |   | N(R) |   |   |    | P/F |

| Unnumbered  | SABME       |           | 0        | 1   | 1 | Р    | 1 | 1 | 1  | 1   |

|             |             | DM        | 0        | . 0 | 0 | F    | 1 | 1 | 1  | . 1 |

| Γ           | UI          |           | 0        | 0   | 0 | Р    | 0 | 0 | 1  | 1   |

|             | DISC        |           | 0        | 1   | 0 | Р    | 0 | 0 | 1  | 1   |

|             |             | UA        | 0        | 1   | 1 | F    | 0 | 0 | 1. | 1   |

|             |             | FRMR      | 1        | 0   | 0 | F    | 0 | 1 | 1  | 1   |

|             | XID         | XID       | 1        | 0   | 1 | P/F  | 1 | 1 | 1  | 1   |

DISC Disconnect

DM Disconnected mode

F Final bit FRMR Frame reject I Information

N(R) Receive sequence number N(S) Send sequence number

P Poll bit

P/F Poll bit when issued as a command/ Final bit when issued as a response

REJ Reject

RNR Receive-not-ready RR Receive ready

SABME Set asynchronous balanced mode extended

UA Unnumbered ackowledgement

UI Unnumbered information

XID Exchange identification

Figure 1-6. Command and Response Frames

additional data link control functions and unacknowledged information transfer. I frames transfer sequentially numbered frames containing information fields provided by Level 3.

The LAPD procedures define how the S, U, and I frames are used for peer-to-peer communication between data link entities. The details of the MLAPD implementation of these procedures is given in **SECTION 8 MLAPD IMPLEMENTATION OF LAPD**.

#### 1.4 SYSTEM ENVIRONMENT

The MLAPD protocol controller provides simultaneous control of a maximum of 8192 logical links, while under the overall supervision of a microprocessor. The communication between

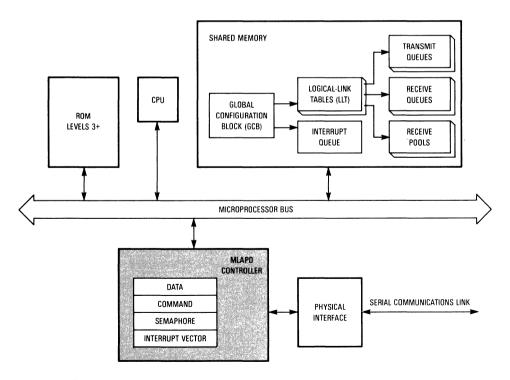

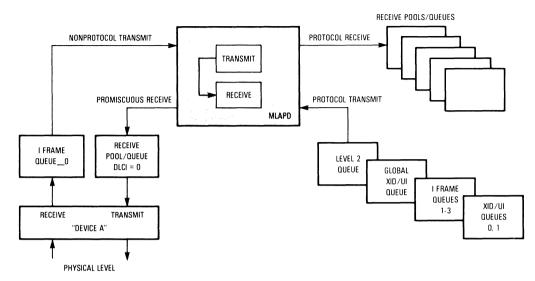

the microprocessor, hereafter referred to as the host processor or CPU, and the protocol controller is established through command and data block structures stored in shared memory. The Global Configuration Block (GCB), Logical-Link Tables (LLTs), Transmit and Receive Queues, Receive Pools, and Interrupt Queue are command and data blocks highlighted in Figure 1-7. This figure provides a simplistic overview of the MLAPD's shared memory structure.

#### 1.4.1 Physical Link Interface

The MLAPD serial interface provides HDLC-type decoding/encoding for the data stream entering/exiting the full-duplex serial interface. The three input signals from the physical interface are the transmit clock, receive clock, and receive data. The transmit data signal is an output to the physical interface. Nonreturn-to-zero (NRZ) data encoding/decoding is implemented. Two modem control signals, request-to-send (RTS) and clear-to-send (CTS), are also available. Electrical signal levels are transistor-transistor logic (TTL) compatible.

In addition, the MLAPD may be optionally configured to interface to a physical level which does not implement a serial HDLC-framed bit stream. In this mode, the MLAPD transmitter does not provide zero insertion, and the MLAPD receiver does not provide zero deletion

Figure 1-7. MLAPD Protocol Controller Application Environment

for data transparency. Additionally, the MLAPD does not delineate frames with flag sequences. Instead, the RTS and CTS signals function as transmit start (TSTART) and receive start (RSTART), respectively, to delineate a frame for the transmit and receive data lines. In particular, this mode can simplify the external logic required to support a physical level that implements a parallel interface, such as a backplane in a network switch or host computer.

#### 1.4.2 Microprocessor System Bus Interface

The host CPU can be any 8- or 16-bit microprocessor that supports multibus master capability, compatible with either the Motorola M68000 Family or the Intel iAPX86 Family bus interface definition. The important differences between the two families are the means of providing read, write, and data-byte selection signals. The desired bus operation mode of the MLAPD is selected at powerup.

The MLAPD has a 24-bit address bus to directly support a 16-Mbyte memory address space. A separate 16-bit data bus is provided, which may be configured for 8-bit operation. The MLAPD handles byte ordering in an appropriate fashion for the selected microprocessor family option.

The format for memory usage has 16-bit and 32-bit values stored at even boundaries enabling 16-bit microprocessors to operate efficiently in shared memory. To ensure compatibility with both 8-bit and 16-bit microprocessors, the configuration, command, and status information for logical-link control are built as linked table structures on a byte-wide basis.

#### 1.4.3 Shared-Memory Control Components

Referring to Figure 1-7, which illustrates the MLAPD protocol controller's application environment, the shared memory consists of several key control blocks. The control blocks are functionally partitioned into the following structures:

Global Configuration Block (GCB)

Logical-Link Tables (LLTs)

Receive and Transmit Queues

Receive Pool Pointers Table

Interrupt Queue

Match Table

Logical-Link Identification (LLID) number to LLT Table (LLID-LLT)

Timer Table

Level 2 Queue

Table 1-1 provides a summary of the functions performed by these blocks.

During system initialization, the host processor loads protocol and operational parameters into the shared-memory control structures and then stores pointers to the various memory

**Table 1-1. Guide to Memory Structures**

| Block Type                       | Purpose                                                                                                                                                             |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Global Configuration Block (GCB) | Contains pointers to other memory tables. Contains global information for all logical links. Contains user system and link options.                                 |

| Logical-Link Tables (LLTs)       | Contains specific link control parameters for the given link. Also contains pointers to the receive/transmit queues. Contains working protocol status for the link. |

| Receive and Transmit Queues      | Contains linked list of receive and transmit frame descriptors for information (I), unnumbered information (UI), and exchange identification (XID) frames.          |

| Receive Pools                    | Linked list of available receive frame descriptors with associated data buffers.                                                                                    |

| Interrupt Queue                  | Contains time-sequential list of interrupt status for each interrupt event.                                                                                         |

| Match Table                      | Contains translation from Data-Link-Connection Identifier (DLCI) to Logical-Link Identification (LLID) number for incoming frames (expanded operation mode).        |

| LLID-LLT Tables                  | Translates LLID into the address of the corresponding LLT.                                                                                                          |

| Level 2 Transmit Queue           | Contains Level 2 supervisory (S) and unnumbered (U) frames generated by MLAPD.                                                                                      |

| Timer Table                      | Implements T200/T203 for all logical links that are in multiple-frame established mode of operation.                                                                |

tables into the GCB. Next, the host programs the MLAPD protocol controller with the address of the GCB and commands the MLAPD to initialize itself by loading its internal registers from the shared memory tables. From this point on, the host and the MLAPD communicate primarily via software flags and an Interrupt Queue in shared memory.

#### 1.5 OVERVIEW OF MLAPD FUNCTIONAL OPERATION

Before describing the shared memory structures, internal registers, command set, and bus operation, a high-level summary of the command structure, the Interrupt Queue structure, and the MLAPD operational sequences may prove helpful.

#### 1.5.1 MLAPD Internal States and Command Structure Overview

The MLAPD functions in one of three internal states: off-line, on-line, or bus/address error. In the off-line state, the MLAPD will only execute host commands. In the on-line state, the MLAPD will execute host commands, receive frames, and transmit frames. In the bus/address error state, the MLAPD will only accept an OFF-LINE or RESET command from the host.

Transitions between these three states occur as the result of host commands and system error conditions. After reset, the MLAPD is in the off-line state. INIT and ON-LINE commands transfer the MLAPD to the on-line state. The OFF-LINE command transfers the MLAPD to the off-line state from either the on-line or the bus/address error state. The bus/address

error state is entered when the BERR signal is asserted during an MLAPD bus master cycle or when  $\overline{\text{CS}}$  or  $\overline{\text{IACK}}$  (INTA) signals are asserted during an MLAPD bus master cycle.

The host issues a command to the MLAPD by first writing the command arguments (if any) into the command argument fields in the GCB in shared memory. Second, the host performs a write operation to enter the command into the on-chip command register. These commands belong to one of the following five categories:

- 1) Initialization

- 2) Test/Diagnostics

- 3) Host/MLAPD Interface

- 4) Protocol

- 5) Protocol Extension

Upon receipt of a command, the MLAPD sets its on-chip semaphore register (SR) to the value 'FE' hex. After either command completion or command acceptance, depending on the specific command, the MLAPD sets the value of the SR to 'FF' hex. The host must always read the SR before writing a new command. See **3.1.2 Semaphore Register**.

#### 1.5.2 Interrupt Structure Overview

An Interrupt Queue is located in shared memory to support the speed requirement of reporting many interrupting events occurring in rapid succession across the various active logical links. Each entry in this Interrupt Queue consists of a Logical-Link Identification (LLID) number, if applicable, and a cause indication. Each of the potential interrupt sources may be individually masked by the host to prevent the reporting of a specific event. The Interrupt Queue is described in detail; refer to **2.8 INTERRUPT QUEUE**.

The MLAPD supports both systems using the interrupt-driven method and systems using the polled method for interrupt handling. After the MLAPD has written an entry into the Interrupt Queue, a hardware interrupt request may be asserted. This interrupt feature is enabled or disabled by the host. If interrupt-driven operation (interrupts are allowed in the system) is desired, the interrupt-vector register (IVR) must be programmed by the host during the initialization procedure, or it will assume the default value '0F' hex. If polled operation is desired, the host programs the MLAPD for this method at initialization.

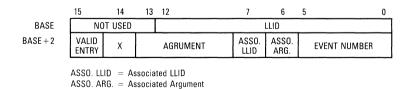

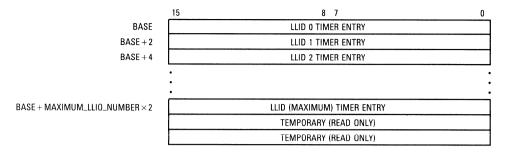

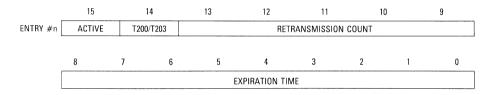

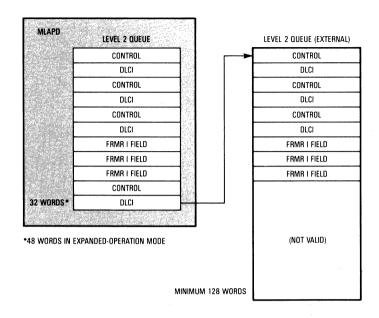

The IVR is on-chip and allows the MLAPD to return an indication of the interrupt cause as part of an interrupt acknowledge cycle on the system bus. The two possible vectors reported across the bus are: normal interrupt and severe interrupt.