# MC68HC05SU3A

TECHNICAL DATA

| INPUT/OUTPUT PORTS           |

|------------------------------|

| MEMORY AND REGISTERS         |

| RESETS AND INTERRUPTS        |

| TIMER                        |

| CPU CORE AND INSTRUCTION SET |

| LOW POWER MODES              |

| OPERATING MODES              |

| ELECTRICAL SPECIFICATIONS    |

| MECHANICAL SPECIFICATIONS    |

|                              |

|                              |

|                              |

|                              |

**GENERAL DESCRIPTION**

**PIN DESCRIPTIONS**

#### For More Information On This Product. Go to: www.freescale.com

|            | Freescale Semiconductor, Inc. |

|------------|-------------------------------|

| 1          | GENERAL DESCRIPTION           |

| 2          | PIN DESCRIPTIONS              |

| 3          | INPUT/OUTPUT PORTS            |

| <b>:</b> 4 | MEMORY AND REGISTERS          |

| 5          | RESETS AND INTERRUPTS         |

| 6          | TIMER                         |

| 7          | CPU CORE AND INSTRUCTION SET  |

| 8          | LOW POWER MODES               |

| 9          | OPERATING MODES               |

| 10         | ELECTRICAL SPECIFICATIONS     |

|            |                               |

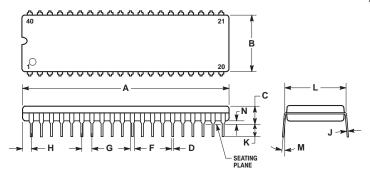

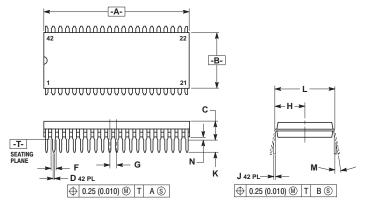

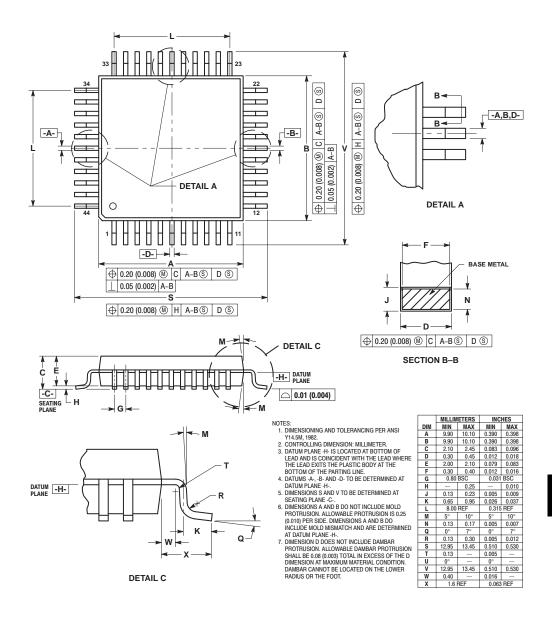

**MECHANICAL SPECIFICATIONS**

### MC68HC05SU3A

# High-density Complementary Metal Oxide Semiconductor (HCMOS) Microcontroller Unit

All Trade Marks recognized. This document contains information on new products. Specifications and information herein are subject to change without notice.

All products are sold on Motorola's Terms & Conditions of Supply. In ordering a product covered by this document the Customer agrees to be bound by those Terms & Conditions and nothing contained in this document constitutes or forms part of a contract (with the exception of the contents of this Notice). A copy of Motorola's Terms & Conditions of Supply is available on request.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

The Customer should ensure that it has the most up to date version of the document by contacting its local Motorola office. This document supersedes any earlier documentation relating to the products referred to herein. The information contained in this document is current at the date of publication. It may subsequently be updated, revised or withdrawn.

© MOTOROLA INC., 1998

## **Conventions**

Register and bit mnemonics are defined in the paragraphs describing them.

An overbar is used to designate an active-low signal, eg: RESET.

Unless otherwise stated, blank cells in a register diagram indicate that the bit is either unused or reserved; shaded cells indicate that the bit is not described in the following paragraphs; 'u' is used to indicate an undefined state (on reset).

# **TABLE OF CONTENTS**

| Paragrap<br>Number                                         | oh <b>TITLE</b>                                                                                                              | Page<br>Number                  |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|                                                            | 1<br>GENERAL DESCRIPTION                                                                                                     |                                 |

| 1.1<br>1.2<br>1.3                                          | Features Mask Options MCU Structure                                                                                          | 1-2                             |

|                                                            | 2<br>PIN DESCRIPTIONS                                                                                                        |                                 |

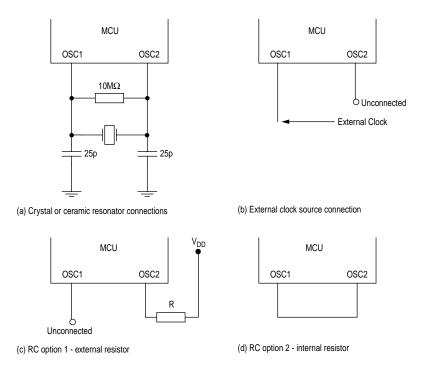

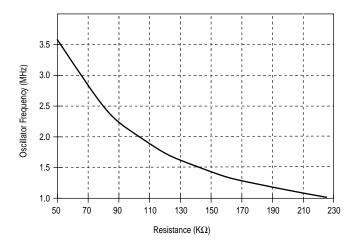

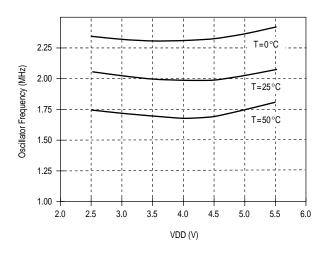

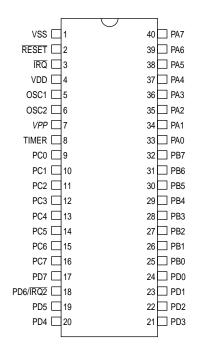

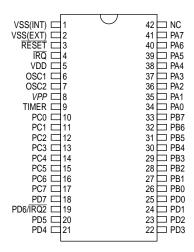

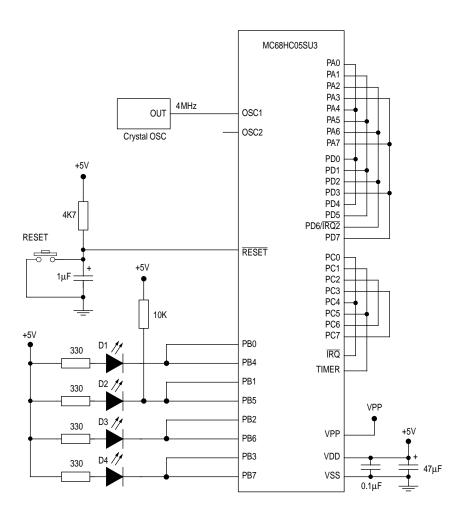

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.3               | Functional Pin Descriptions OSC1 and OSC2 Connections Crystal Oscillator External Clock RC Oscillator Option Pin Assignments | 2-2<br>2-3<br>2-3<br>2-4        |

|                                                            | 3<br>INPUT/OUTPUT PORTS                                                                                                      |                                 |

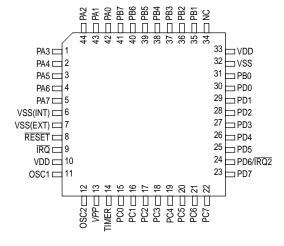

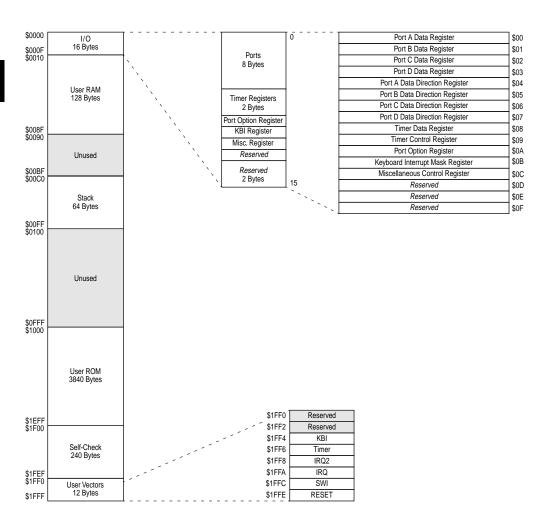

| 3.1<br>3.1.1<br>3.1.2<br>3.2<br>3.3<br>3.4<br>3.5<br>3.5.1 | Parallel Ports                                                                                                               | 3-1<br>3-2<br>3-2<br>3-3<br>3-3 |

|                                                            | 4 MEMORY AND REGISTERS                                                                                                       |                                 |

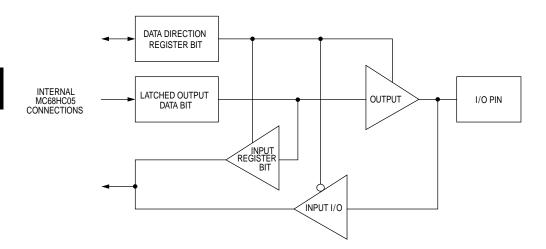

| 4.1                                                        | I/O Registers                                                                                                                | 4-1                             |

| 4.2 RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Paragrap<br>Number | h<br><b>TITLE</b>                     | Page<br>Numbe |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------|---------------|

| 4.4   Memory Map   4-2     4.5   I/O Registers Summary   4-3     5   RESETS   5-1     5.1.1   Power-On Reset (POR)   5-1     5.1.2   RESET Pin   5-1     5.1.3   Low Voltage Reset (LVR)   5-2     5.2.1   Non-maskable Software Interrupt (SWI)   5-3     5.2.2   Maskable Hardware Interrupts   5-5     5.2.2.1   External Interrupt (IRQ)   5-5     5.2.2.2   External Interrupt (IRQ)   5-5     5.2.2.3   Timer Interrupt (IRQ)   5-7     5.2.2.4   Keyboard Interrupt (KBI)   5-8      6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4.2                | RAM                                   | 4-1           |

| Sample   S | 4.3                |                                       |               |

| Section   Sect |                    | • •                                   |               |

| Section   Sect | 4.5                | I/O Registers Summary                 | 4-3           |

| 5.1.1       Power-On Reset (POR)       5-1         5.1.2       RESET Pin       5-1         5.1.3       Low Voltage Reset (LVR)       5-2         5.2       INTERRUPTS       5-2         5.2.1       Non-maskable Software Interrupt (SWI)       5-3         5.2.2       Maskable Hardware Interrupts       5-5         5.2.2.1       External Interrupt (IRQ)       5-5         5.2.2.2       External Interrupt 2 (IRQ2)       5-7         5.2.2.3       Timer Interrupt (KBI)       5-8         6         TIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TCR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1         Accumulator (A)       7-1         7.1.1       Accumulator (A)       7-2         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    |                                       |               |

| 5.1.1       Power-On Reset (POR)       5-1         5.1.2       RESET Pin       5-1         5.1.3       Low Voltage Reset (LVR)       5-2         5.2       INTERRUPTS       5-2         5.2.1       Non-maskable Software Interrupt (SWI)       5-3         5.2.2       Maskable Hardware Interrupts       5-5         5.2.2.1       External Interrupt (IRQ)       5-5         5.2.2.2       External Interrupt 2 (IRQ2)       5-7         5.2.2.3       Timer Interrupt (KBI)       5-8         6         TIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TCR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1         Accumulator (A)       7-1         7.1.1       Accumulator (A)       7-2         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.1                | RESETS                                | 5-1           |

| 5.1.2       RESET Pin.       5-1         5.1.3       Low Voltage Reset (LVR)       5-2         5.2       INTERRUPTS       5-2         5.2.1       Non-maskable Software Interrupt (SWI)       5-3         5.2.2       Maskable Hardware Interrupt (SWI)       5-5         5.2.2.1       External Interrupt (IRQ)       5-5         5.2.2.2       External Interrupt 2 (IRQ2)       5-7         5.2.2.3       Timer Interrupt (KBI)       5-8         6         TIMER         6         TIMER         6.1         Timer Control Register (TCR)       6-3         6.3       Timer Overview       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7         CPU CORE AND INSTRUCTION SET         7.1         Accumulator (A)       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                  |                                       |               |

| 5.1.3       Low Voltage Reset (LVR)       5-2         5.2       INTERRUPTS       5-2         5.2.1       Non-maskable Software Interrupt (SWI)       5-3         5.2.2.1       External Interrupt (IRQ)       5-5         5.2.2.2       External Interrupt 2 (IRQ2)       5-7         5.2.2.3       Timer Interrupt       5-7         5.2.2.4       Keyboard Interrupt (KBI)       5-8         6         TIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TDR)       6-4         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                  |                                       |               |

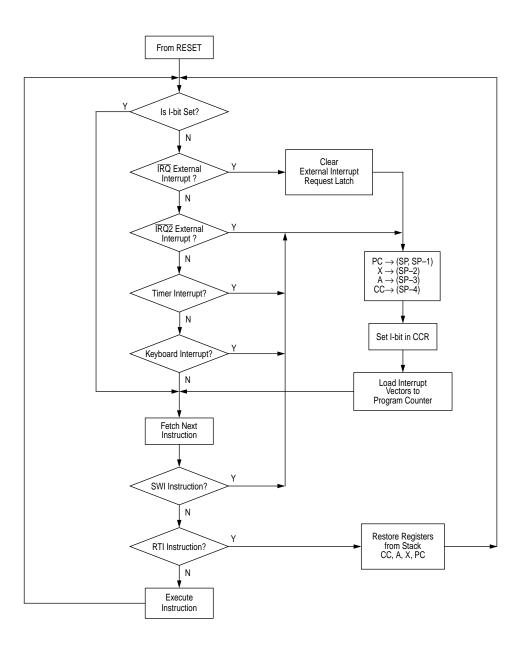

| 5.2       INTERRUPTS       5-2         5.2.1       Non-maskable Software Interrupt (SWI)       5-3         5.2.2       Maskable Hardware Interrupt (IRQ)       5-5         5.2.2.1       External Interrupt (IRQ)       5-5         5.2.2.2       External Interrupt 2 (IRQ2)       5-7         5.2.2.3       Timer Interrupt       5-7         5.2.2.4       Keyboard Interrupt (KBI)       5-8         6         TIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TDR)       6-4         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                    |                                       |               |

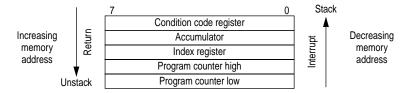

| 5.2.1       Non-maskable Software Interrupt (SWI)       5-3         5.2.2       Maskable Hardware Interrupts       5-5         5.2.2.1       External Interrupt (IRQ)       5-5         5.2.2.2       External Interrupt 2 (IRQ2)       5-7         5.2.2.3       Timer Interrupt (KBI)       5-7         5.2.2.4       Keyboard Interrupt (KBI)       5-8         6         TIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TDR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                       |               |

| 5.2.2       Maskable Hardware Interrupts (IRQ)       5-5         5.2.2.1       External Interrupt (IRQ)       5-5         5.2.2.2       External Interrupt 2 (IRQ2)       5-7         5.2.2.3       Timer Interrupt       5-7         5.2.2.4       Keyboard Interrupt (KBI)       5-8         6         TIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TDR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2.1       Register/memory Instructions       7-3         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/wri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5.2.1              |                                       |               |

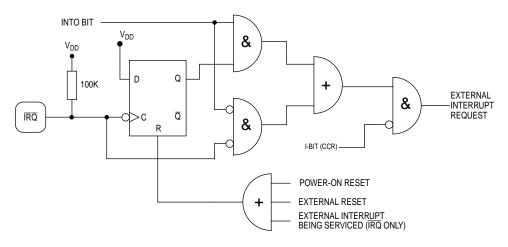

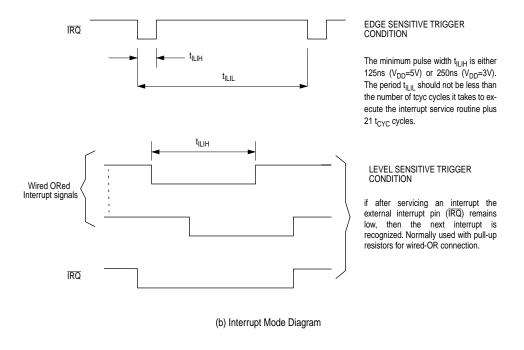

| 5.2.2.2       External Interrupt 2 (IRQ2)       5-7         5.2.2.3       Timer Interrupt       5-7         5.2.2.4       Keyboard Interrupt (KBI)       5-8         6         TIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TDR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.4       Read/modify/write instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.2.2              | • • •                                 |               |

| 5.2.2.3       Timer Interrupt       5-7         5.2.2.4       Keyboard Interrupt (KBI)       5-8         6         TIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TDR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5.2.2.1            | External Interrupt (IRQ)              | 5-5           |

| 6           TIMER           6.1         Timer Overview         6-1           6.2         Timer Control Register (TCR)         6-3           6.3         Timer Data Register (TDR)         6-4           6.4         Operation during Low Power Modes         6-4           7           CPU CORE AND INSTRUCTION SET           7.1         Registers         7-1           7.1.1         Accumulator (A)         7-1           7.1.2         Index register (X)         7-2           7.1.3         Program counter (PC)         7-2           7.1.4         Stack pointer (SP)         7-2           7.1.5         Condition code register (CCR)         7-2           7.2         Instruction set         7-3           7.2.1         Register/memory Instructions         7-4           7.2.2         Branch instructions         7-4           7.2.3         Bit manipulation instructions         7-4           7.2.4         Read/modify/write instructions         7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                  |                                       | 5-7           |

| FIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TDR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    | ·                                     |               |

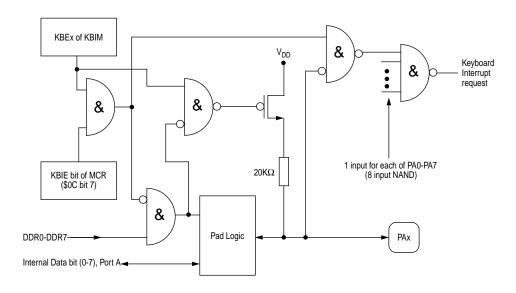

| TIMER         6.1       Timer Overview       6-1         6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TDR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5.2.2.4            | Keyboard Interrupt (KBI)              | 5-8           |

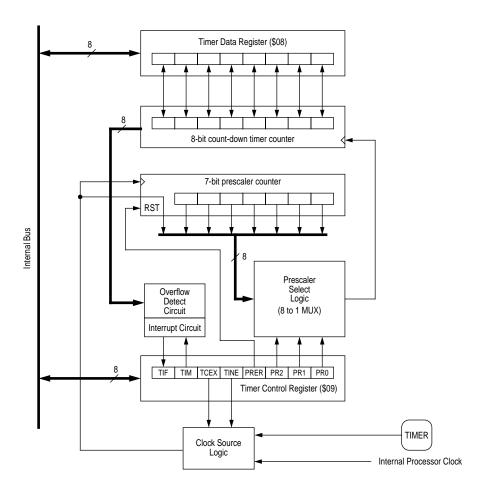

| 6.2       Timer Control Register (TCR)       6-3         6.3       Timer Data Register (TDR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                       |               |

| 6.3       Timer Data Register (TDR)       6-4         6.4       Operation during Low Power Modes       6-4         7         CPU CORE AND INSTRUCTION SET         7.1       Registers       7-1         7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6.1                |                                       |               |

| 7           CPU CORE AND INSTRUCTION SET           7.1         Registers         7-1           7.1.1         Accumulator (A)         7-1           7.1.2         Index register (X)         7-2           7.1.3         Program counter (PC)         7-2           7.1.4         Stack pointer (SP)         7-2           7.1.5         Condition code register (CCR)         7-2           7.2         Instruction set         7-3           7.2.1         Register/memory Instructions         7-4           7.2.2         Branch instructions         7-4           7.2.3         Bit manipulation instructions         7-4           7.2.4         Read/modify/write instructions         7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                  |                                       |               |

| 7 CPU CORE AND INSTRUCTION SET  7.1 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                    |                                       |               |

| CPU CORE AND INSTRUCTION SET           7.1         Registers         7-1           7.1.1         Accumulator (A)         7-1           7.1.2         Index register (X)         7-2           7.1.3         Program counter (PC)         7-2           7.1.4         Stack pointer (SP)         7-2           7.1.5         Condition code register (CCR)         7-2           7.2         Instruction set         7-3           7.2.1         Register/memory Instructions         7-4           7.2.2         Branch instructions         7-4           7.2.3         Bit manipulation instructions         7-4           7.2.4         Read/modify/write instructions         7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.4                | Operation during Low Power Modes      | 6-4           |

| 7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |                                       | Г             |

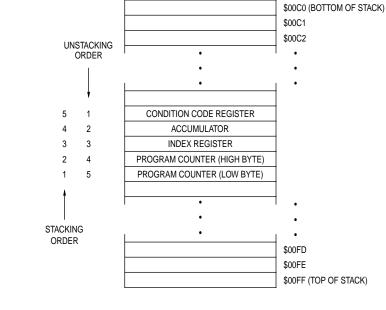

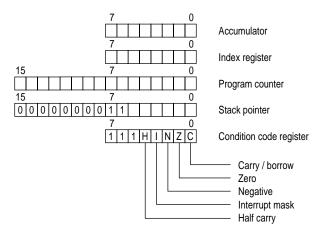

| 7.1.1       Accumulator (A)       7-1         7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7.4                | Destrictions                          | 7.4           |

| 7.1.2       Index register (X)       7-2         7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |                                       |               |

| 7.1.3       Program counter (PC)       7-2         7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                       |               |

| 7.1.4       Stack pointer (SP)       7-2         7.1.5       Condition code register (CCR)       7-2         7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                       |               |

| 7.1.5       Condition code register (CCR).       7-2         7.2       Instruction set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                       |               |

| 7.2       Instruction set       7-3         7.2.1       Register/memory Instructions       7-4         7.2.2       Branch instructions       7-4         7.2.3       Bit manipulation instructions       7-4         7.2.4       Read/modify/write instructions       7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |                                       |               |

| 7.2.1Register/memory Instructions7-47.2.2Branch instructions7-47.2.3Bit manipulation instructions7-47.2.4Read/modify/write instructions7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |                                       |               |

| 7.2.2Branch instructions7-47.2.3Bit manipulation instructions7-47.2.4Read/modify/write instructions7-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    |                                       |               |

| 7.2.3 Bit manipulation instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 7.2.2              | · · · · · · · · · · · · · · · · · · · |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.2.3              |                                       |               |

| 7.2.5 Control instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7.2.4              | Read/modify/write instructions        | 7-4           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.2.5              | Control instructions                  | 7-4           |

| Paragrapl<br>Number | h<br><b>TITLE</b>                   | Page<br>Number    |

|---------------------|-------------------------------------|-------------------|

| 7.2.6               | Tables                              | 7-1               |

| 7.2.0               | Addressing modes                    |                   |

| 7.3<br>7.3.1        | Inherent                            |                   |

| 7.3.1               | Immediate                           |                   |

| 7.3.3               | Direct                              |                   |

| 7.3.4               | Extended                            |                   |

| 7.3.5               | Indexed, no offset                  |                   |

| 7.3.6               | Indexed, 8-bit offset               |                   |

| 7.3.7               | Indexed, 16-bit offset              |                   |

| 7.3.8               | Relative                            |                   |

| 7.3.9               | Bit set/clear                       | _                 |

| 7.3.10              |                                     |                   |

| 7.0.10              | Dit tost and branch                 |                   |

|                     | 8                                   |                   |

|                     | LOW POWER MODES                     |                   |

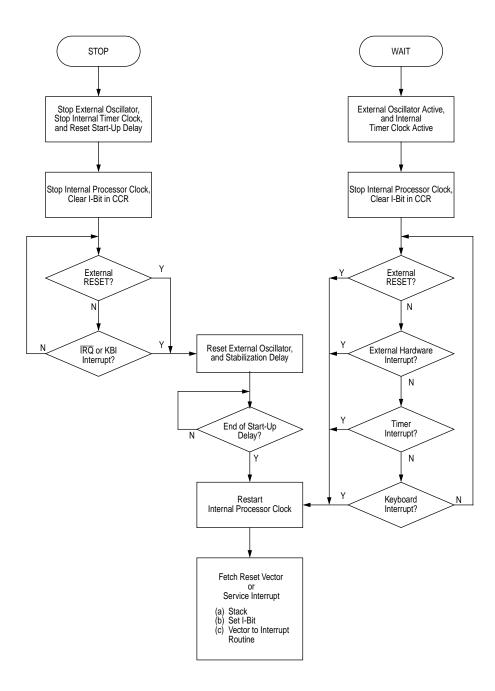

| 0.4                 | STOP Mode                           | 0.4               |

| 8.1<br>8.2          | WAIT Mode                           |                   |

| o.∠<br>8.3          | SLOW Mode                           |                   |

| 0.3                 | SLOW Mode                           | 3                 |

|                     | 9                                   |                   |

|                     | OPERATING MODES                     |                   |

| 9.1                 | User Mode                           | 0.4               |

| 9.1<br>9.2          | Self-Check Mode                     |                   |