| TRACE32 Online Help               |                                                 |               |

|-----------------------------------|-------------------------------------------------|---------------|

| TRACE32 Directory                 |                                                 |               |

| TRACE32 Index                     |                                                 |               |

| TRACE32 Documents                 |                                                 | Þ             |

| ICD In-Circuit Debugger           |                                                 |               |

| Processor Architecture Manuals    |                                                 |               |

| DSP56K                            |                                                 |               |

| DSP56K Debugger                   |                                                 | 1             |

|                                   | w Users                                         | 4             |

|                                   |                                                 | 5             |

|                                   |                                                 | 6             |

|                                   |                                                 |               |

| SYStem.Up Errors                  |                                                 | <b>9</b><br>9 |

| ·                                 |                                                 | 10            |

|                                   |                                                 | 13            |

| On-chip Flash Programming and Deb | pugging on 56F8xxx Derivatives                  | 13            |

|                                   | ctions                                          | 16            |

| SYStem.CPU                        | Select the used CPU                             | 16            |

| SYStem.CpuAccess                  | Run-time memory access (intrusive)              | 16            |

| SYStem.LOCK                       | Lock and tristate the debug port                | 17            |

| SYStem.MemAccess                  | Real-time memory access (non-intrusive)         | 17            |

| SYStem.Mode                       | Establish the communication with the target     | 18            |

| SYStem.CONFIG                     | Configure debugger according to target topology | 19            |

| Daisy-chain Example               |                                                 | 21            |

| TapStates                         |                                                 | 22            |

| SYStem.CONFIG.CORE                | Assign core to TRACE32 instance                 | 23            |

| SYStem.Option COP                 | Enable WATCHDOG                                 | 24            |

| SYStem.Option DE                  | Enable DE line                                  | 24            |

| SYStem.Option IMASKASM            | Disable interrupts while single stepping        | 24            |

| SYStem.Option IMASKHLL            | Disable interrupts while HLL single stepping    | 25            |

| SYStem.Option SoftBreakFix        | Enables "SoftBreakFix" patch                    | 25            |

| SYStem.JtagClock                  | Define JTAG clock                               | 26            |

| General Restrictions              |                                                 | 27            |

| FPU                               |                                                 | 30            |

| TrOnchip Commands            |                                                             | 31 |

|------------------------------|-------------------------------------------------------------|----|

| TrOnchip.view                | Opens configure panel                                       | 31 |

| TrOnchip.A                   | Trigger cycle                                               | 31 |

| TrOnchip.AANDB               | Triggers if event occurs on unit A and unit B               | 32 |

| TrOnchip.AAFTERB             | Triggers if event occurs first on unit A and then on unit B | 32 |

| TrOnchip.AORB                | Triggers if event occurs on unit A or unit B                | 32 |

| TrOnchip.B                   | Trigger cycle                                               | 32 |

| TrOnchip.BAFTERA             | Triggers if event occurs first on unit B and then on unit A | 33 |

| TrOnchip.CONVert             | Automatically convert range to single address               | 33 |

| TrOnchip.Count               | Delay counter                                               | 33 |

| TrOnchip.DMA                 | Trigger on DMA access                                       | 33 |

| TrOnchip.Mode                | Defines used triggers                                       | 34 |

| TrOnchip.OFF                 | Disable on-chip trigger unit                                | 34 |

| TrOnchip.RESet               | Resets settings                                             | 34 |

| Floating Point Formats       |                                                             | 35 |

| Integer Access Keywords      |                                                             | 35 |

| ONCE Connector (56002/56     | 5100)                                                       | 36 |

| JTAG Connector (56300, 56    | 6800, 56800E)                                               | 37 |

| Memory Classes               |                                                             | 39 |

| Support                      |                                                             | 40 |

| Available Tools              |                                                             | 40 |

| Compilers DSP56000           |                                                             |    |

| Compilers DSP56300           |                                                             | 42 |

| Compilers DSP56800/DSP56800E |                                                             | 42 |

| Realtime Operation Systems   |                                                             | 43 |

| 3rd Party Tool Integrations  |                                                             | 43 |

| Products                     |                                                             | 45 |

| Product Information          |                                                             | 45 |

| Order Information            |                                                             | 45 |

#### Version 24-May-2016

| TRACE32 DSP56 [POWER TRACE ETHERN                                                                                                                                                                                                                                                                                                                                     | eT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

| Eile Edit View Var Break Run CPU Misc Ir                                                                                                                                                                                                                                                                                                                              | ace <u>P</u> erf C <u>o</u> v <u>W</u> indow <u>H</u> elp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |

| N № + 4 C > II ⊠ % №                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |

| B::Register                                                                                                                                                                                                                                                                                                                                                           | III B::Data. dump (X:0x0) 💶 💌 🎤 B::SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                             |

| C - U - X1 0<br>Z - L - A2 0 A1 308400<br>N - S - B2 FF B1 920000<br>R0 0100 N0 0 M0 FFFFFF<br>R1 0 N1 0 M1 FFFFFF<br>R2 0 N2 0 M2 FFFFFF<br>R3 0 N3 0 M3 FFFFFF<br>R4 0 N4 0 M4 FFFFFF<br>R5 0 N5 0 M5 FFFFFF<br>R5 0 N5 0 M5 FFFFFF<br>R6 0300 N6 0 M6 FFFFFF<br>R7 0 N7 0 M7 FFFFFF<br>VBA 0 EP 0 SZ 0<br>PABEX 0139 PIL 0BF080<br>PABD 013A PDB 0144<br>PABF 0138 | X:0x0         ji Find         Modify         Mode         MemAccess           address         0         1         O         Down         CPU         O           x:000000         >300400         920000         NoDebug         O         Down         O         CPU         O           x:000001         000000         1000001         O         O         NoDebug         O         Denied         CpuAccess         O         Attach         O         Enable         O         Denied         Nonstop         Nonstop         Nonstop         Nonstop         Nonstop         JtagClock         5.0MHz         JtagClock         5.0MHz         S.0MHz         S.0MHz | Option<br>IMASKASM<br>IMASKHLL<br>DE<br>COP |

|                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |

| [B::Data.List]       ▶ Step       breakpoint       addr/line       source       106                                                                                                                                                                                                                                                                                   | Lup ► Go H Break Mode Find: \\pass\pass.asm #2,x:M_SSISR0,*; wait for frame sync to pass                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                             |

| 107 jclr<br>109 move                                                                                                                                                                                                                                                                                                                                                  | #2,x:M_SSISRO,* ; wait for frame sync<br>x:RX_BUFF_BASE,a ; receive left                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                             |

| 110 move<br>P 112 jsr                                                                                                                                                                                                                                                                                                                                                 | x:RX_BUFF_BASE+1,b ; receive right process_stereo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |

| 114 move<br>115 move                                                                                                                                                                                                                                                                                                                                                  | a,x:TX_BUFF_BASE ; transmit left<br>b,x:TX_BUFF_BASE+1 ; transmit right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |

| 117 move<br>118 move<br>119 move                                                                                                                                                                                                                                                                                                                                      | <pre>#TONE_OUTFUT,y0 ; set up control words<br/>y0,x:TX_BUFF_BASE+2<br/>#TONE_INPUT,y0</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ✓                                           |

| B::Break.List                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |

|                                                                                                                                                                                                                                                                                                                                                                       | Delect]       Delect]       Delect]         P       100p_1\6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                             |

| B::                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                             |

| emulate trigger devices trace                                                                                                                                                                                                                                                                                                                                         | Data Var PERF SYStem Step Go other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | previous                                    |

| P:000139 \\pass\pass\loop_1+0x6                                                                                                                                                                                                                                                                                                                                       | stopped at breakpoint                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | HLL UP ,                                    |

#### Architecture-independent information:

- "Debugger Basics Training" (training debugger.pdf): Get familiar with the basic features of a TRACE32 debugger.

- "T32Start" (app t32start.pdf): T32Start assists you in starting TRACE32 PowerView instances • for different configurations of the debugger. T32Start is only available for Windows.

- "General Commands" (general ref <x>.pdf): Alphabetic list of debug commands.

#### Architecture-specific information:

- "Processor Architecture Manuals": These manuals describe commands that are specific for the processor architecture supported by your debug cable. To access the manual for your processor architecture, proceed as follows:

- Choose Help menu > Processor Architecture Manual. -

- "RTOS Debugger" (rtos <x>.pdf): TRACE32 PowerView can be extended for operating system-. aware debugging. The appropriate RTOS manual informs you how to enable the OS-aware debugging.

# Warning

| NOTE: | To prevent debugger and target from damage it is recommended to connect or disconnect the debug cable only while the target power is OFF. |                                                                           |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|       | Recom                                                                                                                                     | mendation for the software start:                                         |

|       | 1.                                                                                                                                        | Disconnect the debug cable from the target while the target power is off. |

|       | 2.                                                                                                                                        | Connect the host system, the TRACE32 hardware and the debug cable.        |

|       | 3.                                                                                                                                        | Power ON the TRACE32 hardware.                                            |

|       | 4.                                                                                                                                        | Start the TRACE32 software to load the debugger firmware.                 |

|       | 5.                                                                                                                                        | Connect the debug cable to the target.                                    |

|       | 6.                                                                                                                                        | Switch the target power ON.                                               |

|       | 7.                                                                                                                                        | Configure your debugger e.g. via a start-up script.                       |

|       | Power                                                                                                                                     | down:                                                                     |

|       | 1.                                                                                                                                        | Switch off the target power.                                              |

|       | 2.                                                                                                                                        | Disconnect the debug cable from the target.                               |

|       | 3.                                                                                                                                        | Close the TRACE32 software.                                               |

|       | 4.                                                                                                                                        | Power OFF the TRACE32 hardware.                                           |

|       |                                                                                                                                           |                                                                           |

# **Quick Start**

Starting up the debugger is done as follows:

Select the device prompt for the ICD Debugger and reset the system.

b::

RESet

The device prompt B:: is normally already selected in the command line. If this is not the case enter B:: to set the correct device prompt. The RESet command is only necessary if you do not start directly after booting the TRACE32 development tool.

5. Specify the CPU specific settings.

**SYStem.CPU** <cputype>

The default values of all other option are set in such a way that it should be possible to work without modification. Please consider that this is probably not the best configuration for your target.

6. Set the JTAG shift frequency

SYStem.JtagClock <frequency>

Normally the default value is 1.0 MHz, but the 56800E requires a lower value in the starting process.

7. Inform the debugger about read only address ranges (ROM, FLASH).

MAP.BOnchip <range>

The B(reak)Onchip information is necessary to decide where on-chip breakpoints must be used. Onchip breakpoints are necessary to set program breakpoints to read-only memories. The sections of FLASH and ROM depend on the specific CPU and its chip selects.

8. Enter debug mode.

SYStem.Up

This command resets the CPU and enters debug mode. After this command is executed it is possible to access memory and registers.

9. Configure chip according application.

Register.Set OMR 3

; 56800: Development mode

Before loading binary data into the processor memory, the memory should be made writable. Therefore processor configuration registers have to be set e.g. OMR, SR or chip select register. The flash of the 56F8300 derivatives should be initialized here, too.

10. Load the program.

```

Data.LOAD.Elf program.elf ; ELF specifies the format,

; program.elf is the file name

```

The format of the Data.LOAD command depends on the file format generated by the compiler. Refer to **Supported Compilers** to find the command, that is necessary for your compiler.

A detailed description of the **Data.LOAD** command and all available options is given in the "General Commands Reference".

A typical start sequence for the DSP56858 is shown below. This sequence can be written to an ASCII file (script file) and executed with the command **DO** <filename>. Other sequences can be found on the CD in the DEMO directory.

| b::                                                       | ; Select the ICD device prompt                                                                                                                                                                                      |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WinCLEAR                                                  | ; Clear all windows                                                                                                                                                                                                 |

| SYStem.CPU 56858                                          | ; Select CPU (56800E class here)                                                                                                                                                                                    |

| SYStem.JtagClock 687000.                                  | ; Choose JTAG frequency                                                                                                                                                                                             |

| MAP.BOnchip 0x1f0001f03ff                                 | ; Specify where read-only memory is                                                                                                                                                                                 |

| SYStem.Up                                                 | ; Reset the target and enter debug<br>; mode                                                                                                                                                                        |

| Register.Set PP 0x1F000                                   | ; Set the extended program counter PP<br>; (not PC!) to the begin of the boot<br>; flash. The statement is redundant in<br>; this case, but remember the<br>; execution without loading a program<br>; starts here. |

| Register.Set OMR 0x0                                      | ; Prepare access to memory by using ; operating mode 0                                                                                                                                                              |

| Data.LOAD.Elf<br>ldm_external_memory.elf /LARGE<br>/VERFY | ; Load the application with option<br>; large memory model and verify the<br>; process                                                                                                                              |

| Go main                                                   | ; Run and break at main()                                                                                                                                                                                           |

| Data.List                                                 | ; Open source window                                                                                                                                                                                                |

| Register /SpotLight                                       | ; Open register window                                                                                                                                                                                              |

| Var.Local                                                 | ; Open window with local variables                                                                                                                                                                                  |

|                                                           |                                                                                                                                                                                                                     |

### SYStem.Up Errors

The **SYStem.Up** command is the first command of a debug session where communication with the target is required. If you receive error messages while executing this command this may have the following reasons.

- The JTAG lines are not connected correctly.

- The target has no power.

- The pull-up resistor between the JTAG[VCCS] pin and the target VCC is too large.

- The target is in reset:

The debugger controls the processor reset and use the RESET line to reset the CPU on every SYStem.Up. Therefore no external R-C combination or external reset controller is allowed.

• There is logic added to the JTAG state machine:

By default the debugger supports only one processor in one JTAG chain. If the processor is the only one member of a JTAG chain the debugger has to be informed about the target JTAG chain configuration. Use the SYStem.CONFIG command to specify the position of the device in the JTAG-chain. Debuggers for DSP56000 and DSP56100 do not support the SYStem.CONFIG options! For the DSP56800 chips the support depends to the license. There is a license upgrade available which also allows to debug 56800E core based chips. For Multicore DSP56300 systems e.g. DSP56720 or DSP56721 a Multicore License is necessary.

- Wrong CPU is selected

- JTAG clock is to high, especially for 56800E core based processors

- CPU executed illegal code and is in a bad state that can be only be reverted by re-powering the target. To avoid this situations first plug the debugger to the target, then power the target. The debugger will keep the target in RESET state until the command **SYStem.Up** was successful.

There are additional loads or capacities on the JTAG lines

| Debugging via<br>VPN | The debugger is accessed via Internet/VPN and the performance is very slow. What can be done to improve debug performance?                                                                                                                                                                                                                                                                       |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | The main cause for bad debug performance via Internet or VPN are low data throughput and high latency. The ways to improve performance by the debugger are limited:                                                                                                                                                                                                                              |

|                      | in practice scripts, use "SCREEN.OFF" at the beginning of the script and "SCREEN.ON" at the end. "SCREEN.OFF" will turn off screen updates. Please note that if your program stops (e.g. on error) without executing "SCREEN.OFF", some windows will not be updated.                                                                                                                             |

|                      | "SYStem.POLLING SLOW" will set a lower frequency for target state checks (e.g. power, reset, jtag state). It will take longer for the debugger to recognize that the core stopped on a breakpoint.                                                                                                                                                                                               |

|                      | "SETUP.URATE 1.s" will set the default update frequency of Data.List/<br>Data.dump/Variable windows to 1 second (the slowest possible setting).                                                                                                                                                                                                                                                  |

|                      | prevent unneeded memory accesses using "MAP.UPDATEONCE<br>[address-range]" for RAM and "MAP.CONST [addressrange]" for ROM/<br>FLASH. Address ranged with "MAP.UPDATEONCE" will read the specified<br>address range only once after the core stopped at a breakpoint or manual<br>break. "MAP.CONST" will read the specified address range only once per<br>SYStem.Mode command (e.g. SYStem.Up). |

| Setting a                                            | What can be the reasons why setting a software breakpoint fails?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Software<br>Breakpoint fails                         | Setting a software breakpoint can fail when the target HW is not able to implement the wanted breakpoint.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                      | Possible reasons:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                      | The wanted breakpoint needs special features that are only possible to realize by the trigger unit inside the controller.<br>Example: Read, write and access (Read/Write) breakpoints ("type" in Break.Set window). Breakpoints with checking in real-time for data-values ("Data").<br>Breakpoints with special features ("action") like TriggerTrace, TraceEnable, TraceOn/TraceOFF.                                                                                                                                                                           |

|                                                      | TRACE32 can not change the memory.<br>Example: ROM and Flash when no preparation with FLASH.Create,<br>FLASH.TARGET and FLASH.AUTO was made. All type of memory if the<br>memory device is missing the necessary control signals like WriteEnable or<br>settings of registers and SpecialFunctionRegisters (SFR).                                                                                                                                                                                                                                                |

|                                                      | Contrary settings in TRACE32.<br>Like: MAP.BOnchip for this memory range. Break.SELect. <breakpoint-type><br/>Onchip (HARD is only available for ICE and FIRE).</breakpoint-type>                                                                                                                                                                                                                                                                                                                                                                                |

|                                                      | RTOS and MMU:<br>If the memory can be changed by Data.Set but the breakpoint doesn't work it<br>might be a problem of using an MMU on target when setting the breakpoint to a<br>symbolic address that is different than the writable and intended memory<br>location.                                                                                                                                                                                                                                                                                           |

| Cannot release<br>from Software<br>Breakpoint        | Cannot make an HLL-step from a software breakpoint or the context switches while debugging                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                      | Possible reason: Interrupts are pending<br>In HLL-stepping mode always debug with SYStem.Option IMASKASM ON,<br>when interrupts are pending.                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                      | Possible reason: Routine is called again<br>Debugging in recursive routines can have strange side effects. The debugger<br>uses breakpoints to perfom HLL single steps. These breakpoints will place the<br>processor in debug state also when you try to step over a self call. So the<br>stackframe/context can switch or in case of fixed user breakpoints it seams that<br>the debugger cannot release from a breakpoint. Similar behavior can be<br>expected for debugging in nested interrupts or real time operating systems with<br>software interrupts. |

| 56800/56800E                                         | How can I set the program counter to including the extension bit from the SR register?                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PC Register is<br>not equal to<br>Program<br>Counter | Use the register PP e.g. Register.Set PP 0x1F0000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 56800E                                        | Debugger does not step correctly into routine or debugger does not load<br>HLL code for routine.                                                |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| AnySymbol<br>Option for<br>Metrowerks<br>800E | Use the /AnySymbol paramater when you load Metrowerks ELF files.                                                                                |

| 56800E                                        | Pointer type has wrong width.                                                                                                                   |

| Pointer has<br>wrong Width                    | The width of the pointer type depends on the memory model. The large memory model requieres the parameter /LARGE for the command Data.LOAD.ELF. |

The processor type must be selected by the **SYStem.CPU** command before issuing any other target related commands.

# **On-chip Flash Programming and Debugging on 56F8xxx Derivatives**

TRACE32 offers target based flash programming for the internal flash on the 56F8xx and 56F8300 derivative. Before accessing the flash the device has to be configured. Example scripts for programming and debugging can be found in /demo/dsp56800/flash and /demo/dsp56800e/compiler/mwerks/56f8323.

#### Configuration for flash programming:

- Select the CPU with **SYStem.CPU** and use **SYStem.Up** to enable debug mode.

- Optional: Adjust the processors system clock (SYS\_CLK) to allow a faster JTAG communication and shorter flash algorithm runtime.

Consult the processors architecture manual for the right PLL and Clock settings. An example for the 56F8323 can be found under *demo/dsp56800e/hardware/dsp568323demo/system.up*

• Set the chip configuration register and peripherals to enable access to the memory sections with flash.

Check the processor manual for correct setting of SR, OMR registers (especially EX bit and MODE bits) and the chip select peripheral register. The exact configuration depends on your application. Use the commands **Register.Set** and **Data.Set** to modify these registers.

Configure the Flash programming

Use the TRACE32 commands **FLASH.Create** and **FLASH.TARGET** to inform the debugger about Flash memory sections and the used flash algorithm. TRACE32 provides example scripts for all known derivatives with the configuration EX=0 and Mode=0. Look in the *demo/dsp56800/flash* and *demo/dsp56800e/flash* directories for these scripts.

The implementation of the FLASH.Create command differs from the standard:

- The physical range addresses are counted in words.

- The sector size is passed in bytes.

- The bus width is fixed to "Word".

- Additional access class parameter for 56800 and 56800E family.

**56800 family**: An additional parameter after the access size parameter is necessary. The 32 bit parameter tells the target program the address of the flash controller base register and the flash memory class to use. Bit 0..15 of this parameter give the base address of the flash controller registers, bit 16..31 specify the access class. Access class:

- 0 : Program flash memory or boot flash memory

- 1 : Data flash memory

Example:

```

; Program flash, control base is 0x1020

FLASH.Create 1. P:0x0000--0x7bff 0x200 TARGET Word 0x01020

; Data flash, 0x10000 + control base 0x1060

FLASH.Create 2. X:0x1800--0x1fff 0x200 TARGET Word 0x11060

```

**56800E family**: An additional parameter after the access size parameter is necessary, that tells the target program about the flash memory class. Access class:

1 : Boot flash 2 : Program flash 3 : Data flash.

Example:

```

; Boot Flash

FLASH.Create 1. P:0x020000--0x020FFF 0x200 TARGET Word 1

; Program Flash

FLASH.Create 2. P:0x000000--0x003FFF 0x400 TARGET Word 2

; Data Flash

FLASH.Create 3. X:0x001000--0x001FFF 0x200 TARGET Word 3

```

Enable Flash programming and download application

Use **FLASH.AUTO ALL** to enable cached write access to the flash memory and download your application with **Data.Load.** Alternatively it is also possible to use **FLASH.Erase** and **FLASH.Program**, especially when large memory blocks have been changed.

Disable Flash programming with FLASH.AUTO OFF or FLASH.Program OFF.

#### Configuration for debugging in flash:

- Select the CPU with **SYStem.CPU** and use **SYStem.Up** to enable debug mode.

- Load Symbols

Assuming that the application is already programmed into flash, load the symbols with the help of the TRACE32 command **Data.Load** with the additional parameters /NoCODE, /NOREG, /AS and optional /LARGE if you use the large memory model.

- Configure the flash programming

- Execute start-up code to configure the device

The start-up code of your application includes normally instructions to configure the chip registers and peripherals. You can execute the start-up code with the TRACE32 instruction "Go main /ONCHIP". The command lets the processor execute the code and breaks at *main* with the help of an on-chip breakpoint.

• Adjust JTAG-Clock and enable flash memory for write access.

Assuming that the PLL is initialized correctly by the start-up code, the JTAG frequency can be optimized to allow faster communication. The TRACE32 command **FLASH.AUTO ALL** enables the flash for writing. This is necessary for debugging in flash. The executed program code should not change the system clock (SYS\_CLK) otherwise the flash clock divider (can only be set one time after reset) and JTAG frequency can become invalid.

Debug your application

The step-over function uses asm single steps to perform, because this safes flash life cycles. For faster operation it is better to use break and go commands.

Shutdown the processor with FLASH.AUTO OFF and SYStem.Down to replace the software breakpoints with the original application code.

### SYStem.CPU

#### Select the used CPU

| Format:      | SYStem.CPU <cpu></cpu>                                                                                                                                                          |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <cpu>:</cpu> | 56002   56004   56005   56006   56007 (56000 processors)<br>56301   56302   56303   56307   56309   56311   56321   56362   56364   56366<br>  56367   56371 (56300 processors) |

|              | 56801   56803   56805   56807   56809   56811   56827 (56800 processors)                                                                                                        |

|              | 56852   56853   56854   56855   56857   56858 (56800E 5685x processors)                                                                                                         |

|              | 56F8322   56F8323   56F8345   56F8346   56F8347   56F8355   56F8356  <br>56F8357   56F8365   56F8366   56F8367 (56800E 56F83xx processors)                                      |

|              | 56F8122   56F8123   56F8145   56F8146   56F8147   56F8155   56F8156  <br>56F8157   56F8165   56F8166   56F8167 (56800E 56F81xx processors)                                      |

|              | 56F8013   56F8014 (56800E 56F80xx processors)                                                                                                                                   |

Selects the processor type.

# SYStem.CpuAccess

#### Run-time memory access (intrusive)

| Format:          | SYStem.CpuAccess Enable   Denied   Nonstop                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Default: Denied. |                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Enable           | Allow intrusive run-time memory access.<br>In order to perform a memory read or write while the CPU is executing the<br>program the debugger stops the program execution shortly. Each short stop<br>takes 1 100 ms depending on the speed of the debug interface and on the<br>number of the read/write accesses required.<br>A red S in the state line of the TRACE32 screen indicates this intrusive behavior<br>of the debugger. |

**Denied** Lock intrusive run-time memory access.

**Nonstop** Lock all features of the debugger, that affect the run-time behavior. Nonstop reduces the functionality of the debugger to:

- run-time access to memory and variables

- trace display

The debugger inhibits the following:

- to stop the program execution

- all features of the debugger that are intrusive (e.g. action Spot for breakpoints, performance analysis via StopAndGo mode, conditional breakpoints etc.)

# SYStem.LOCK

#### Lock and tristate the debug port

Format:

SYStem.LOCK [ON | OFF]

Default: OFF.

If the system is locked, no access to the debug port will be performed by the debugger. While locked, the debug connector of the debugger is tristated. The main intention of the lock command is to give debug access to another tool.

## SYStem.MemAccess

### Real-time memory access (non-intrusive)

| Format: | SYStem.MemAccess CPU   Denied <cpu_specific><br/>SYStem.ACCESS (deprecated)</cpu_specific> |

|---------|--------------------------------------------------------------------------------------------|

| CPU     | Real-time memory access during program execution to target is enabled.                     |

| Denied  | Real-time memory access during program execution to target is disabled.                    |

# SYStem.Mode

| Format:        | SYStem.Mode <mode></mode>                                                                                                                                                                  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <mode>:</mode> | Down<br>NoDebug<br>Go<br>Attach<br>Up                                                                                                                                                      |

| Down           | Disables the debugger (default). The state of the CPU remains unchanged. The JTAG port is tristated.                                                                                       |

| NoDebug        | Disables the debugger. The state of the CPU remains unchanged. The JTAG port is tristated.                                                                                                 |

| Go             | Resets the target and enables the debugger and start the program execution.<br>Program execution can be stopped by the break command or external trigger.                                  |

| Attach         | User program remains running (no reset) and the debug mode is activated.<br>After this command the user program can be stopped with the break command<br>or if any break condition occurs. |

| Up             | Resets the target, sets the CPU to debug mode and stops the CPU. After the execution of this command the CPU is stopped and all register are set to the default level.                     |

| StandBy        | Not available for DSP56K.                                                                                                                                                                  |

| Format:                            | SYStem.CONFIG <parameter> <number_or_address><br/>SYStem.MultiCore <parameter> <number_or_address> (deprecated)</number_or_address></parameter></number_or_address></parameter>                      |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <pre><parameter></parameter></pre> | state                                                                                                                                                                                                |  |

| (General):                         | CORE <core></core>                                                                                                                                                                                   |  |

| (JTAG):                            | DRPRE <bits><br/>DRPOST <bits><br/>IRPRE <bits><br/>IRPOST <bits><br/>TAPState <state><br/>TCKLevel <level><br/>TriState [ON   OFF]<br/>Slave [ON   OFF]</level></state></bits></bits></bits></bits> |  |

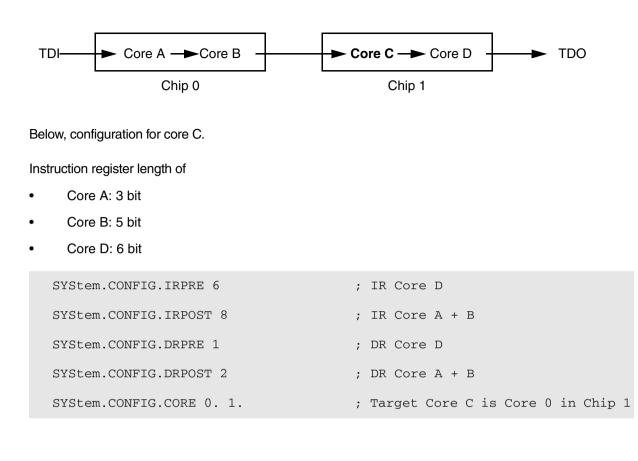

The four parameters IRPRE, IRPOST, DRPRE, DRPOST are required to inform the debugger about the TAP controller position in the JTAG chain, if there is more than one core in the JTAG chain (e.g. ARM + DSP). The information is required before the debugger can be activated e.g. by a **SYStem.Up**. See **Daisy-chain Example**.

For some CPU selections (SYStem.CPU) the above setting might be automatically included, since the required system configuration of these CPUs is known.

TriState has to be used if several debuggers ("via separate cables") are connected to a common JTAG port at the same time in order to ensure that always only one debugger drives the signal lines. TAPState and TCKLevel define the TAP state and TCK level which is selected when the debugger switches to tristate mode. Please note: nTRST must have a pull-up resistor on the target, TCK can have a pull-up or pull-down resistor, other trigger inputs needs to be kept in inactive state.

|  | Multicore debugging is not supported for the DEBUG INTERFACE (LA-7701). | ļ |

|--|-------------------------------------------------------------------------|---|

|  |                                                                         |   |

| state    | Show multicore settings.                                                                                                                                                                                                                                                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CORE     | For multicore debugging one TRACE32 GUI has to be started per core.<br>To bundle several cores in one processor as required by the system this<br>command has to be used to define core and processor coordinates within<br>the system topology.<br>Further information can be found in <b>SYStem.CONFIG.CORE</b> .                                               |

| DRPRE    | (default: 0) <number> of TAPs in the JTAG chain between the core of interest and the TDO signal of the debugger. If each core in the system contributes only one TAP to the JTAG chain, DRPRE is the number of cores between the core of interest and the TDO signal of the debugger.</number>                                                                    |

| DRPOST   | (default: 0) <number> of TAPs in the JTAG chain between the TDI signal<br/>of the debugger and the core of interest. If each core in the system<br/>contributes only one TAP to the JTAG chain, DRPOST is the number of<br/>cores between the TDI signal of the debugger and the core of interest.</number>                                                       |

| IRPRE    | (default: 0) <number> of instruction register bits in the JTAG chain<br/>between the core of interest and the TDO signal of the debugger. This is<br/>the sum of the instruction register length of all TAPs between the core of<br/>interest and the TDO signal of the debugger.</number>                                                                        |

| IRPOST   | (default: 0) <number> of instruction register bits in the JTAG chain<br/>between the TDI signal and the core of interest. This is the sum of the<br/>instruction register lengths of all TAPs between the TDI signal of the<br/>debugger and the core of interest.</number>                                                                                       |

| TAPState | (default: 7 = Select-DR-Scan) This is the state of the TAP controller when<br>the debugger switches to tristate mode. All states of the JTAG TAP<br>controller are selectable.                                                                                                                                                                                    |

| TCKLevel | (default: 0) Level of TCK signal when all debuggers are tristated.                                                                                                                                                                                                                                                                                                |

| TriState | (default: OFF) If several debuggers share the same debug port, this<br>option is required. The debugger switches to tristate mode after each<br>debug port access. Then other debuggers can access the port. JTAG:<br>This option must be used, if the JTAG line of multiple debug boxes are<br>connected by a JTAG joiner adapter to access a single JTAG chain. |

| Slave    | (default: OFF) If more than one debugger share the same debug port, all except one must have this option active.<br>JTAG: Only one debugger - the "master" - is allowed to control the signals nTRST and nSRST (nRESET).                                                                                                                                          |

#### **Daisy-chain Example**

| 0  | Exit2-DR         |

|----|------------------|

| 1  | Exit1-DR         |

| 2  | Shift-DR         |

| 3  | Pause-DR         |

| 4  | Select-IR-Scan   |

| 5  | Update-DR        |

| 6  | Capture-DR       |

| 7  | Select-DR-Scan   |

| 8  | Exit2-IR         |

| 9  | Exit1-IR         |

| 10 | Shift-IR         |

| 11 | Pause-IR         |

| 12 | Run-Test/Idle    |

| 13 | Update-IR        |

| 14 | Capture-IR       |

| 15 | Test-Logic-Reset |

|    |                  |

| Format:                  | SYStem.CONFIG.CORE < <i>coreindex</i> > < <i>chipindex</i> ><br>SYStem.MultiCore.CORE < <i>coreindex</i> > < <i>chipindex</i> > (deprecated) |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| <chipindex>:</chipindex> | 1i                                                                                                                                           |

| <coreindex>:</coreindex> | 1 k                                                                                                                                          |

Default coreindex: depends on the CPU, usually 1. for generic chips

Default *chipindex*: derived from CORE= parameter of the configuration file (config.t32). The CORE parameter is defined according to the start order of the GUI in T32Start with ascending values.

To provide proper interaction between different parts of the debugger the systems topology must be mapped to the debuggers topology model. The debugger model abstracts chips and sub-cores of these chips. Every GUI must be connect to one unused core entry in the debugger topology model. Once the **SYStem.CPU** is selected a generic chip or none generic chip is created at the default *chipindex*.

#### **None Generic Chips**

None generic chips have a fixed amount of sub-cores with a fixed CPU type.