# Z80 PROGRAMMING MANUAL V2.0

Z80 PROGRAMMING MANUAL V2.0 (MK78515)

| SECTION<br>NUMBER | PARAGRAPH<br>Number | TITLE                                | PAGE<br>Number |

|-------------------|---------------------|--------------------------------------|----------------|

| 1                 |                     | Z80 CPU ARCHITECTURE                 | 1-1            |

|                   | 1-1                 | INTRODUCTION                         | 1-1            |

|                   | 1-3                 | CPU REGISTERS                        | 1-1            |

|                   | 1-5                 | SPECIAL PURPOSE REGISTERS            | 1-1            |

|                   | 1-6                 | Program Counter (PC)                 | 1-1            |

|                   | 1-7                 | Stack Pointer (SP)                   | 1-2            |

|                   | 1-8                 | Two Index Registers (IX & IY)        | 1-2            |

|                   | 1-9                 | Interrupt Page Address Register (I)  | 1-2            |

|                   | 1-10                | Memory Refresh Register (R)          | 1-3            |

|                   | 1-11                | ACCUMULATOR AND FLAG REGISTERS       | 1-3            |

|                   | 1-12                | GENERAL PURPOSE REGISTERS            | 1-3            |

|                   | 1-13                | ARITHMETIC & LOGIC UNIT (ALU)        | 1-3            |

|                   | 1-15                | INSTRUCTION REGISTER AND CPU CONTROL | 1-4            |

| 2                 |                     | Z80 INSTRUCTION SET                  | 2-1            |

|                   | 2-1                 | INTRODUCTION                         | 2-1            |

|                   | 2-3                 | INSTRUCTION SET FEATURES             | 2-1            |

|                   | 2-4                 | ADDRESSING MODES                     | 2-1            |

|                   | 2-5                 | Immediate Addressing                 | 2-1            |

|                   | 2-6                 | Immediate Extended Addressing        | 2-1            |

|                   | 2-7                 | Modified Page Zero Addressing        | 2-2            |

|                   | 2-8                 | Relative Addressing                  | 2-2            |

|                   | 2-9                 | Extended Addressing                  | 2-3            |

|                   | 2-10                | Indexed Addressing                   | 2-3            |

|                   | 2-13                | Register Addressing                  | 2-4            |

|                   | 2-14                | Implied Addressing                   | 2-4            |

|                   | 2-15                | Register Indirect Addressing         | 2-4            |

|                   | 2-16                | Bit Addressing                       | 2-4            |

|                   | 2-17                | Stack Pointer Addressing             | 2-5            |

|                   | 2-20                | Subroutine Addressing                | 2-6            |

|                   | 2-29                | Subroutine Use of The Stack          | 2-7            |

|                   | 2-32                | Z80 STATUS INDICATORS (FLAGS)        | 2-8            |

| SECTION<br>NUMBER | PARAGRAPH<br>NUMBER | TITLE                                  | PAGE<br>NUMBER |

|-------------------|---------------------|----------------------------------------|----------------|

| 2 (contd.)        | 2-33                | Flag Register                          | 2-8            |

|                   | 2-34                | Carry Flag (C)                         | 2-8            |

|                   | 2-38                | Add/Subtract Flag (N)                  | 2-9            |

|                   | 2-39                | Parity/Over Flow Flag                  | 2-9            |

|                   | 2-47                | Half Carry Flag (H)                    | 2-10           |

|                   | 2 <b>- 4</b> 8      | Zero Flag (Z)                          | 2-10           |

|                   | 2-53                | Sign Flag (S)                          | 2-11           |

|                   | 2-55                | INTERRUPTS                             | 2-11           |

|                   | 2-56                | Interrupt Types                        | 2-11           |

|                   | 2-57                | Interrupt Enable - Disable             | 2-13           |

|                   | 2-63                | LOAD AND EXCHANGE INSTRUCTIONS         | 2-15           |

|                   | 2-64                | BLOCK TRANSFER AND SEARCH INSTRUCTIONS | 2-15           |

|                   | 2-69                | ARITHMETIC AND LOGICAL INSTRUCTIONS    | 2-15           |

|                   | 2-70                | ROTATE AND SHIFT INSTRUCTIONS          | 2-16           |

|                   | 2-71                | BIT MANIPULATION INSTRUCTIONS          | 2-16           |

|                   | 2-72                | JUMP, CALL, AND RETURN                 | 2-16           |

|                   | 2-73                | INPUT/OUTPUT INSTRUCTIONS              | 2-16           |

|                   | 2-76                | MISCELLANEOUS FEATURES                 | 2-16           |

|                   | 2-77                | Z80 ASSEMBLY LANGUAGE SYNTAX           | 2-16           |

|                   | 2-78                | INTRODUCTION                           | 2-16           |

|                   | 2-87                | LABELS                                 | 2-17           |

|                   | 2-91                | OPCODES                                | 2-18           |

|                   | 2-92                | STANDARD OPERANDS                      | 2-18           |

|                   | 2-93                | OPERAND NOTATION                       | 2-19           |

|                   | 2-95                | COMMENTS                               | 2-20           |

|                   | 2-96                | UPPER/LOWER CASE                       | 2-20           |

|                   | 2-97                | OPCODES - DETAILED DESCRIPTIONS        | 2-20           |

|                   | 2-98                | INTRODUCTION                           | 2-20           |

APPENDIX A ALPHABETICAL LISTING OF Z80 OPCODES

,

TABLE OF CONTENTS (Contd.)

| SECTION<br>NUMBER | PARAGRAPH<br>NUMBER T                          | ITLE                                                                                                                                                                                                                                 | PAGE<br>NUMBER                                   |

|-------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| APPENDIX B        | MOSTEK ASS                                     | EMBLER STANDARD PSEUDO-OPS                                                                                                                                                                                                           |                                                  |

| В                 | B-1                                            | INTRODUCTION                                                                                                                                                                                                                         | B-1                                              |

| APPENDIX C        | MOSTEK STA                                     | NDARD Z80 OBJECT CODE FORMAT                                                                                                                                                                                                         |                                                  |

| C                 | C-1<br>C-4<br>C-5<br>C-6<br>C-7<br>C-9<br>C-10 | INTRODUCTION<br>DATA RECORD FORMAT (TYPE 00)<br>END-OF-FILE RECORD (TYPE 01)<br>INTERNAL SYMBOL RECORD (TYPE 02)<br>EXTERNAL SYMBOL RECORD (TYPE 03)<br>RELOCATING INFORMATION RECORD (TYPE 04<br>MODULE DEFINITION RECORD (TYPE 05) | C-1<br>C-1<br>C-2<br>C-2<br>C-2<br>4) C-3<br>C-3 |

APPENDIX D

REFERENCE TABLES

iii

# LIST OF FIGURES

| FIGURE NO. | TITLE                          | PAGE NO. |

|------------|--------------------------------|----------|

| 1-1        | Z80 CPU Block Diagram          | 1-1      |

| 1-2        | Z80 CPU Register Configuration | 1-2      |

| TABLE NO. | TITLE                               | PAGE N0. |

|-----------|-------------------------------------|----------|

| 2-1       | Interrupt Enable/Disable Flip Flops | 2-14     |

#### PREFACE

This manual is designed to help the user program the Z80 microcomputer in assembly language. It also serves as a standard for the Z80 Assembly language.

It is assumed that the user has a background in logic and some experience with programming.

The manual consists mainly of a brief general description of the Z80 CPU architecture from the programmer's point of view and a detailed description of the Z80 instruction set. The description of the instruction set includes a description of the set's main features, specific information about assembly language syntax, and detailed descriptions of each of the Z80 opcodes. The manual also contains several appendices. Appendix A is an alphabetical list of the Z80 opcodes. Appendix B provides details of the Mostek assembler standard pseudo-ops. Appendix C describes the Mostek standard Z80 object code format. Appendix D provides binary, hexadecimal, and ASCII reference tables.

#### SECTION 1

#### **Z80 CPU ARCHITECTURE**

#### 1-1. INTRODUCTION.

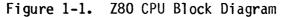

1-2. A block diagram of the internal architecture of the Z80 CPU is shown in Figure1-1. The diagram shows all of the major elements in the CPU and it should be referred to throughout the following description.

1-3. CPU REGISTERS.

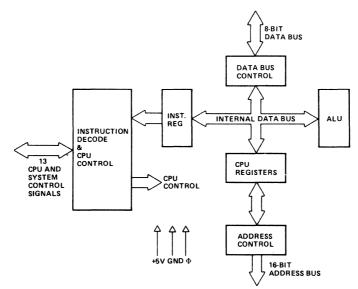

1-4. The Z80 CPU contains 208 bits of R/W memory that are accessible to the programmer. Figure 1-2 illustrates how this memory is configured into eighteen 8-bit registers and four 16-bit registers. All Z80 registers are implemented using static RAM. The registers include a set of special purpose registers, two sets of accumulator and flag registers, and two sets of six general purpose registers which may be used individually as 8-bit registers or in pairs as 16-bit registers.

1-5. SPECIAL PURPOSE REGISTERS.

1-6. Program Counter (PC). The program counter holds the 16-bit address of the current instruction being fetched from memory. The PC is automatically incremented after its contents have been transferred to the address lines. When a program jump occurs, the new value is automatically placed in the PC, overriding the incrementer. 1-7. Stack Pointer (SP). The stack pointer holds the 16-bit address of the current top of a stack located anywhere in external system RAM memory. The external stack memory is organized as a last-in first-out (LIFO) file. Data can be pushed onto the stack from specific CPU registers or popped off of the stack into specific CPU registers through the execution of PUSH and POP instructions. The data popped from the stack is always the last data pushed onto it. The stack allows simple implementation of multiple level interrupts, unlimited subroutine nesting and simplification of many types of data manipulation.

1-8. Two Index Registers (IX & IY). The two independent index registers hold a 16-bit base address that is used in indexed addressing modes. In this mode, an index register is used as a base to point to a region in memory from which data is to be stored or retrieved. An additional byte is included in indexed instructions to specify a displacement from this base. This displacment is specified as a two's complement signed integer. This mode of addressing greatly simplifies many types of programs, especially where tables of data are used.

1-9. Interrupt Page Address Register (I). The Z80 CPU can be operated in a mode where an indirect call to any memory location can be achieved in response to an interrupt. The I Register is used for this purpose to store the high order 8-bits of the indirect address while the interrupting device provides the lower 8-bits of the address. This feature allows interrupt routines to be dynamically located anywhere in memory with absolute minimal access time to the routine.

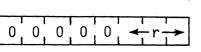

1-10. Memory Refresh Register (R). The Z80 CPU contains a memory refresh counter to enable dynamic memories to be used with the same ease as static memories. This 7-bit register is automatically incremented after each instruction fetch. The data in the refresh counter is sent out on the lower portion of the address bus along with a refresh control signal while the CPU is decoding and executing the fetched instruction. This mode of refresh is totally transparent to the programmer and does not slow down the CPU operation. The programmer can load the R register for testing purposes, but this register is normally not used by the programmer.

1-11. ACCUMULATOR AND FLAG REGISTERS. The CPU includes two independent 8-bit accumulators and associated 8-bit arithmetic or logical operations while the flag register indicates specific conditions for 8 or 16-bit operations, such as indicating whether or not the result of an operation is equal to zero. The programmer selects the accumulator and flag pair that he wishes to work with a single exchange instruction so that he may easily work with either pair.

1-12. GENERAL PURPOSE REGISTERS. There are two matched sets of general purpose registers, each set containing six 8-bit registers that may be used individually as 8-bit registers or as 16-bit register pairs by the programmer. One set is called BC, DE and HL while the complementary set is called BC', DE' and HL'. At any one time the programmer can select either set of registers to work with through a single exchange command for the entire set. In systems where fast interrupt response is required one set of general purpose registers and an accumulator/flag register may be reserved for handling this very fast routine. Only a simple exchange command need be executed to go between the routines. This greatly reduces interrupt service time by eliminating the requirement for saving and retrieving register contents in the external stack during interrupt or subroutine processing. These general purpose registers are used for a wide range of applications by the programmer. They also simplify programming, especially in ROM based systems where little external read/write memory is available.

1-13. ARITHMETIC & LOGIC UNIT (ALU).

1-14. The 8-bit arithmetic and logical instructions of the CPU are executed in the ALU. Internally the ALU communicates with the registers and the external data bus on the internal data bus. The type of functions performed by the ALU include:

Add Subtract Logical AND Logical Or Logical EXCLUSIVE OR Compare Left or right shifts or rotates (arithmetic and logical) Increment Decrement Set bit Reset bit Test bit

1-15. INSTRUCTION REGISTER AND CPU CONTROL.

1-16. As each instruction is fetched from memory, it is placed in the instructio register and decoded. The control section performs this function and then generate and supplies all of the control signals necessary to read or write data from or t the registers, controls the ALU and provides all required external control signals

1-4

#### **SECTION 2**

#### **Z80 INSTRUCTION SET**

#### 2-1. INTRODUCTION.

2-2. The Z80 instruction set of 158 instructions can best be described by first discussing in general the main features. These features include its addressing modes; status and flags; interrupt modes; load and exchange instructions; block transfer and search instructions; arithmetic and logical instructions; rotate and shift instructions; bit manipulation instructions; jump, call, and return instructions; input/ output instruction; and miscellaneous instructions. Included in the discussion of the addressing modes are descriptions of subroutines and subroutine use of the stack. Following this general description of the instruction set, specific information about the syntax of the assembly language is provided. Then each instruction is described in detail in alphabetical order.

#### 2-3. INSTRUCTION SET FEATURES.

2-4. ADDRESSING MODES. Most of the Z80 instructions operate on data stored in internal CPU registers, external memory or in the I/O ports. Addressing refers to how the address of this data is generated in each instruction. The following paragraphs gives a brief summary of the types of addressing used in the Z80. Many instructions include more than one operand (such as arithmetic instructions or loads). In these cases, two types of addressing may be employed. For example, load can use immediate addressing to specify the destination.

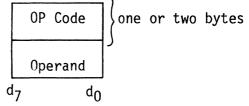

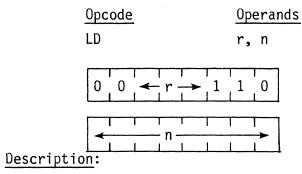

2-5. Immediate Addressing. In this mode of addressing the byte following the Op code in memory contains the actual operand.

Examples of this type of instruction would be to load the accumulator with a constant, where the constant is the byte immediately following the OP code.

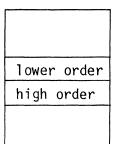

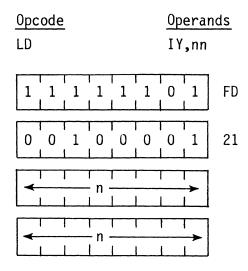

2-6. Immediate Extended Addressing. This mode is merely an extension of immediate addressing in that the two bytes following the OP code are the operand.

| OP Code | one or two bytes |

|---------|------------------|

| Operand | lower order      |

| Operand | high order       |

Examples of this type of instruction would be to load the HL register pair (16bit register) with 16 bits (2 bytes) of data.

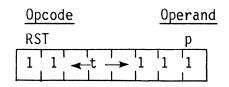

2-7. Modified Page Zero Addressing. The Z80 has a special single byte call instruction to any of 8 locations in page zero of memory. This instruction (which is referred to as a restart) sets the PC to an effective address in page zero. The value of this instruction is that it allows a single byte to specify a complete 16-bit address where commonly called subroutines are located, thus saving memory space.

OP Code one byte

b<sub>0</sub>

b7

Effective address is  $(b_5 \ b_4 \ b_3 \ 000)_2$

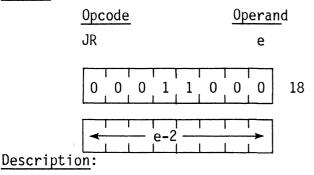

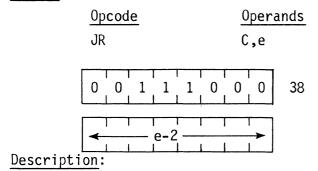

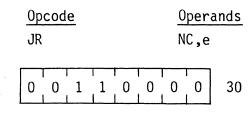

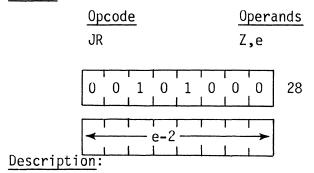

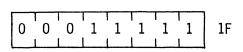

2-8. Relative Addressing. Relative addressing use one byte of data following the OP code to specify a displacement from the existing program to which a program jump can occur. This displacement is a signed two's complement number that is added to the address of the OP code of the following instruction.

| OP Code | Jump relative (one byte OP code)                           |

|---------|------------------------------------------------------------|

| Operand | 8-bit two's complement displacement added to Address (A+2) |

|         | Vadded to Address (A+2)                                    |

The value of relative addressing is that it allows jumps to nearby locations while only requiring two bytes of memory space. For most programs, relative jumps are by far the most prevalent type of jump due to the proximity of related program segments. Thus, these instructions can significantly reduce memory space requirements. The signed displacement can range between +127 and -128 from A+2. This allows for a total displacement of +129 to -126 from the jump relative OP code address. Another major advantage is that it allows for relocatable code.

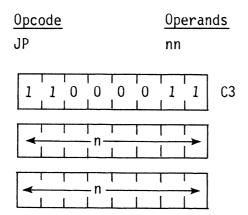

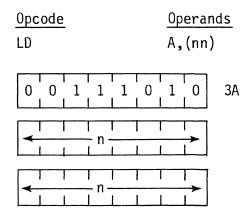

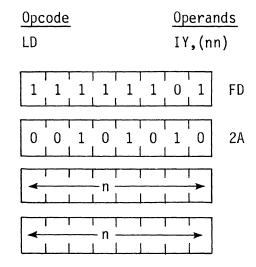

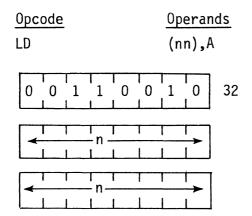

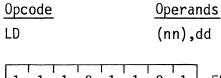

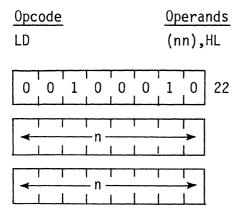

2-9. Extended Addressing. Extended Addressing provides for two bytes (16 bits) of address to be included in the instruction. This data can be an address to which a program can jump or it can be an address where an operand is located.

| OP Code                                  |  |

|------------------------------------------|--|

| Low order Address or Low order operand   |  |

| High Order Address or high order operand |  |

one or two bytes

Extended addressing is required for a program to jump from any location in memory to any other location, or load and store data in any memory location. When extended addressing is used to specify the source or destination address of an operand, the notation (nn) will be used to indicate the content of memory at nn, where nn is the 16-bit address specified in the instruction. This means that the two bytes of address nn are used as a pointer to memory location. The use of the parentheses always means that the value enclosed within them is used as a pointer to a memory location. For example, (1200) refers to the contents of memory at location 1200.

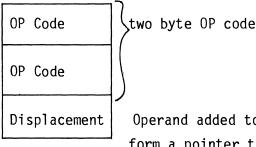

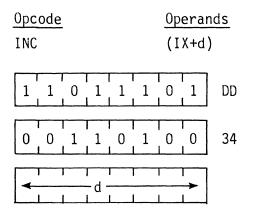

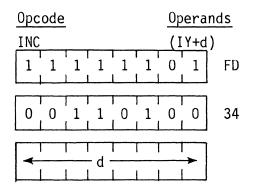

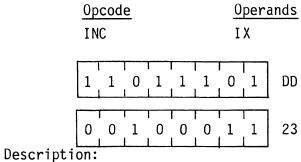

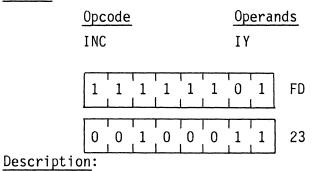

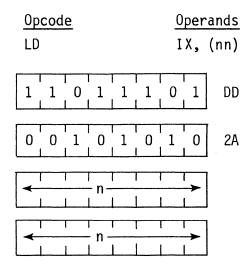

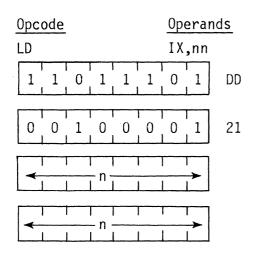

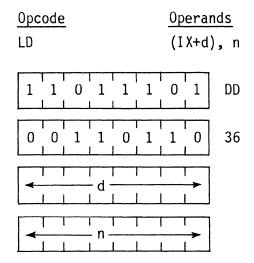

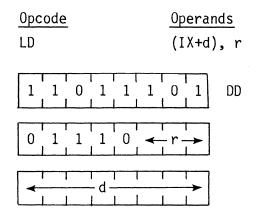

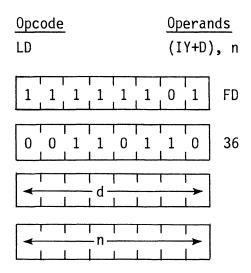

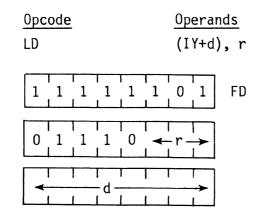

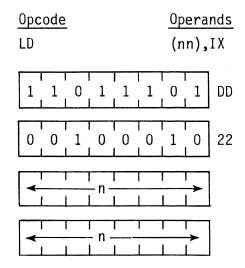

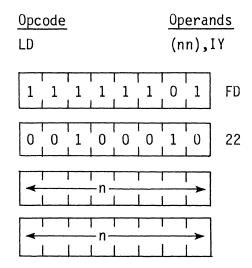

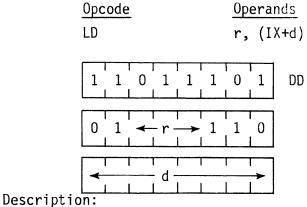

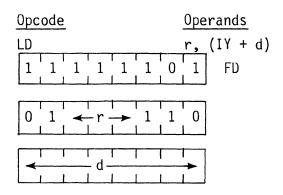

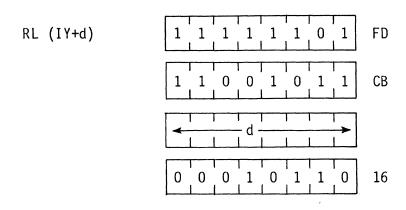

2-10. Indexed Addressing. In this type of addressing, the byte of data following the Op code contains a displacement which is added to one of the two index registers (the Op code specifies which index register is used) to form a pointer to memory. The contents of the index register are not altered by this operation.

Operand added to index register to form a pointer to memory.

2-11. An example of an indexed instruction would be to load the contents of the memory location (Index Register + Displacement) into the accumulator. The displacement is a signed two's complement number. Indexed addressing greatly simplifies programs using tables of data since the index register can point to the start of any table. Two index registers are provided since very often operations require two or more tables. Indexed addressing also allows for relocatable code.

2-12. The two index registers in the Z80 are referred to as IX and IY. To indicate indexed addressing the notation:

#### (IX+d) or (IY+d)

is used. Here d is the displacment specified after the OP code. The parentheses indicate that this value is used as a pointer to external memory.

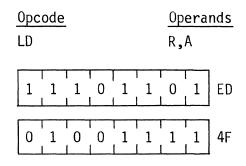

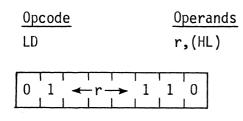

2-13. Register Addressing. Many of the Z80 OP codes contain bits of information that specify which CPU register is to be used for an operation. An example of register addressing would be to load the data in register B into register C.

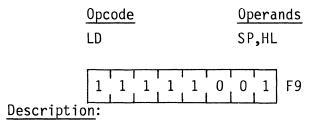

2-14. Implied Addressing. Implied addressing refers to operations where the Op code automatically implies one or more CPU registers as containing the operands. An example is the set of arithmetic operations where the accumulator is always implied to the destination of the results.

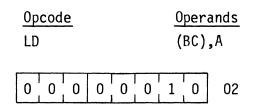

2-15. Register Indirect Addressing. This type of addressing specifies a 16-bit CUP register pair (such as HL) to be used as a pointer to any location in memory. This type of instruction is very powerful and it is used in a wide range of applications.

OP Code | one or two bytes

An example of this type of instruction would be to load the accumulator with the data in the memory location pointed to by the HL register contents. Indexed addressing is actually a form of register indirect addressing except that a displacement is added with indexed addressing. Register indirect addressing allows for very powerful but simple to implement memory accesses. The block move and search commands in the Z80 are extensions of this type of addressing where automatic register incrementing, decrementing and comparing have been added. The notation for indicating register indirect addressing is to put parentheses around the name of the register that is to be used as the pointer. For example, the symbol

#### (HL)

specifies that the contents of the HL register are to be used as a pointer to memory location. Often register indirect addressing is used to specify 16-bit operands. In this case, the register contents point to the lower order portion of the operand while the register contents are automatically incremented to obtain the upper portion of the operand.

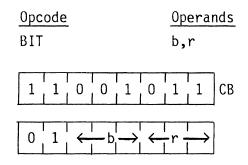

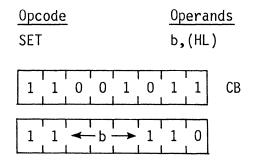

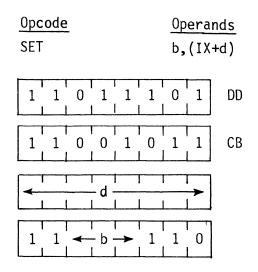

2-16. Bit Addressing. The Z80 contains a large number of bit set, reset and test instructions. These instructions allow any memory location or CPU register to be

specified for a bit operation through one of three previous addressing modes (register, indirect and indexed) while three bits in the OP code specify which of the eight bits is to be manipulated.

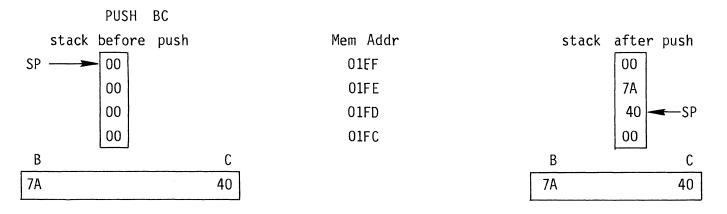

2-17. Stack Pointer Addressing. Memory locations may be addressed in the 16-bit stack pointer register (SP). There are two stack operations which may be performed:

- 1. PUSH, which puts data into a stack,

- 2. POP, which retrieves data from a stack.

Note that the stack area must reside in read/write memory. The stack pointer is initialized to the top location in the stack at the start of a program. In a stack operation a 16-bit register pair is transferred to or from the stack.

2-18. For the PUSH operation the contents of the register pair are transferred to the Stack:

- The most significant 8-bits of data are stored at the memory address less one than the contents of the stack pointer.

- 2. The least significant 8 bits of data are stored at the memory address less two than the contents of the stack pointer.

- 3. The stack pointer is automatically decremented by two.

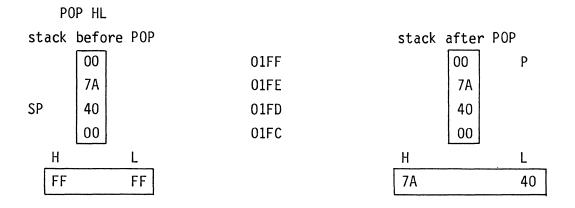

2-19. For the POP operation, 16 bits of data are taken from the stack and placed in the 16-bit register pair:

- The second register of the pair (or the least significant byte of the pair) is loaded from the memory address held in the stack pointer.

- 2. The first register of the pair (or the most significant byte of the pair)

is loaded from the memory address one greater than the address held in the stack pointer.

3. The stack pointer is automatically incremented by two.

2-20. Subroutine Addressing.

2-21. Subroutines are blocks of instructions that can be called during the execution of a sequence of instructions. Subroutines can be called from main programs or from other subroutines. A subroutine is entered by the CALL opcode as in:

#### CALL REWIND

2-22. Parameters such as those used by the macros are not used with subroutines. When a call instruction is encountered during execution of a program, the PC is changed to the first instruction of the subroutine. The subsequent address of the invoking program is pushed on the stack. Control will return to this point when the subroutine is finished. The processor continues to execute the subroutine until it encounters a RET (return) instruction. At this point the return address is popped off the stack into the PC, and the processor returns to the address of the instruction following the CALL, to continue execution from that point.

2-23. Subroutines of any size can be invoked from programs or other subroutines of any size, without restriction. Care must be taken when nesting subroutines (sub-routines within subroutines) that pushes and pops remain balanced at each level. If the processor encounters a RET with an un-popped push on the stack, the PC will be set to a meaningless address rather than to the next instruction following the CALL.

2-24. Tradeoffs must be considered between:

1. Using a block of code repetitively in line , and

2. calling the block repetitively as a subroutine.

2-25. Program size can usually by saved by using the subroutine. If the repetitive block contains N bytes and it is repeated on M occasions in the program,

1. MxN bytes would be used in direct programming, while

2. 3M (for CALLS)

+ n (for the block)

+ 1 (for the RET)

=3M+N+1 bytes would be required if using a subroutine.

2-26. For example, for a block of 20 bytes used 5 times, in-line programming would require 100 bytes while a subroutine would require 36.

2-27. An added advantage of subroutines is that with careful naming, program structures become clearer, easier to read and easier to debug and maintain. Subroutines written for one purpose can be employed elsewhere in the programs requiring the same functions.

2-28. Subroutines differ from Macros in several ways:

- Subroutine code is assembled into an object program only once although it may be called many times. Macro code is assembled in line every place the macro is used.

- Registers and pointers required by a subroutine must be set up before the CALL. No parameters are used and no argument string can be issued. Macros, through their use of parameters, can modify the settings of registers on each occurrence.

2-29. Subroutine Use Of The Stack. When a call to a subroutine is executed, the contents of the program counter are pushed onto the stack automatically. Recall that the program counter contains the next memory address to be executed. After the PC is pushed onto the stack, the starting address of the subroutine is placed into the PC and then branch to the subroutine, a return instruction pops the address off the stack into the PC, and control is transferred to the memory address after the call. These operations are automatic when the CALL and RET instructions are executed.

2-30. Note that parameters can be passed to a subroutine because the stack and stack pointer can be manipulated and updated by special Z80 instructions.

2-31. The save type of operation as described for a subroutine also occurs for external interrupts monitored by the CPU.

2-32. Z80 STATUS INDICATORS (FLAGS).

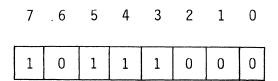

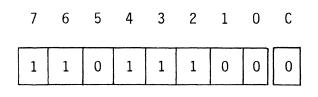

2-33. Flag Register. The flag register (F and F') supplies information to the user regarding the status of the Z80 at any given time. The bit positions for each flag are shown below:

7 6 1 5 4 3 2 0 Ζ Х Х P/V Ν С S Н

WHERE:

C = CARRY FLAG N = ADD/SUBTRACT FLAG P/V = PARITY/OVERFLOW FLAG H = HALF-CARRY FLAG Z = ZERO FLAG S = SIGN FLAG X = NOT USED

Each of the Z80 Flag Registers contains 6 bits of status information which are set or reset by CPU operations. (Bits 3 and 5 are not used.) Four of these bits are testable (C,P/V,Z and S) for use with conditional jump, call or return instructions. Two flags are not testable (H,N) and are used for BCD arithmetic.

2-34. Carry Flag (C). The carry bit is set or reset depending on the operation being performed. For ADD instructions that generate a carry and SUBTRACT instructions that generate a borrow, the Carry Flag will be set. The Carry Flag is reset by an ADD that does not generate a carry and a SUBTRACT that does not generate a borrow. This saved carry facilitates software routines for extended precision arithmetic. Also, the 'DAA' instruction will set the Carry Flag if the conditions for making the decimal adjustment are met.

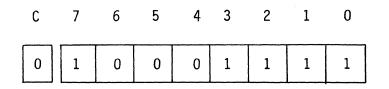

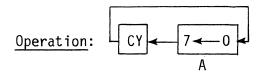

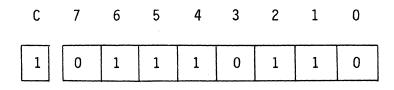

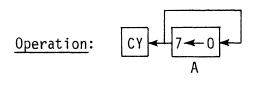

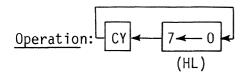

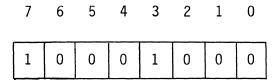

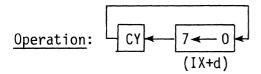

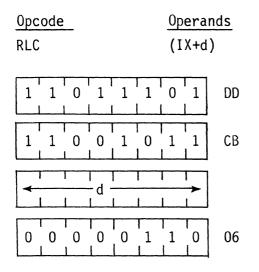

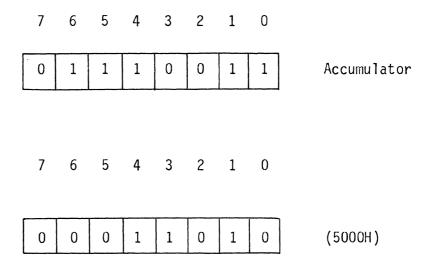

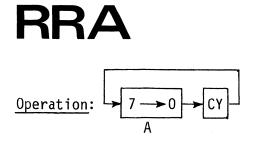

2-35. For instructions RLA, RRA, RL and RR, the carry bit is used as a link bet-

2-8

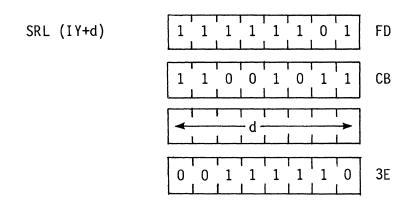

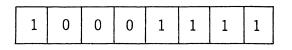

ween the LSB and MSB for any register or memory location. During instructions RLCA, RLC s and SLA s, the carry contains the last value shifted out of bit 7 of any register or memory locations. During instructions RRCA, RRC s, SRA s and SRL s the carry contains the last value shifted out of bit 0 of any register or memory location.

2-36. For the logical instructions AND s, OR s and XOR s, the carry will be reset.

2-37. The Carry Flag can also be set (SCF) and complemented (CCF).

2-38. Add/Subtract Flag (N). This flag is used by the decimal adjust accumulator instruction (DAA) to distinguish between ADD and SUBTRACT instructions. For all ADD instructions, N will be set to a 1.

2-39. Parity/Overflow Flag. This flag is set to a particular state depending on the operation being performed.

2-40. For arithmetic operations, this flag indicates an overflow condition when the result in the Accumulator is greater than the maximum possible number (+127) or less than the minimum possible number(-128). This overflow condition can be determined by examining the sign bits of the operands.

2-41. For addition, operands with different signs will never cause overflow. When adding operands with like signs and the result has a different sign, the overflow flag is set. For example:

| +120 | = | 0111 | 1000 | ADDEND             |

|------|---|------|------|--------------------|

| +105 | = | 0110 | 1001 | AUGEND             |

| +225 | = | 1110 | 0001 | ( <b>-</b> 95) SUM |

The adding of the two numbers together has resulted in a number that exceeds +127 and the two positive operands cause a negative number (-95) which is incorrect. The overflow flag is therefore set.

2-42. For subtraction, overflow can occur for operands of unlike signs. Operands of like sign will never cause overflow. For example:

|      | -127 | 0111 | 1111 | MINUEND    |

|------|------|------|------|------------|

| (-)_ | -64  | 1100 | 0000 | SUBTRAHEND |

|      | +191 | 1011 | 1111 | DIFFERENCE |

The minuend sign has changed from a positive to a negative, giving an incorrect difference. Overflow is therefore set. Another method for predicting an overflow is to observe the carry into and out of the sign bit. If there is a carry in and no carry out, or if there is no carry in and a carry out, then overflow has occurred. 2-10

2-43. This flag is also used with logical operations and rotate instructions to indicate the parity of the result. The number of 1 bits in a byte are counted. If the total is odd, ODD parity (P=0) is flagged. If the total is even, EVEN parity is flagged (P=1).

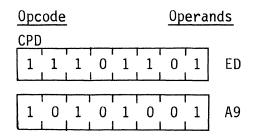

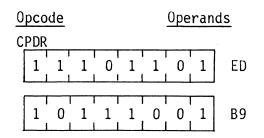

2-44. During search instructions CPI, CPIR, CPD, and CPDR and block transfer instructions LDI, LDIR, LDD, and LDDR, the P/V flag monitors the state of the byte count register (BC). When decrementing, the byte counter results in a zero value, the flag is reset to 0; otherwise, the flag is a 1.

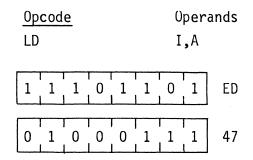

2-45. During LD A,I and LD A,R instructions, the P/V flag will be set with the contents of the interrupt enable flip-flop (IFF2) for storage or testing.

2-46. When inputting a byte from an I/O device, IN r,(C), the flag will be adjusted to indicate the parity of the data.

2-47. Half Carry Flag (H). The Half Carry Flag (H) will be set or reset depending on the carry and borrow status between bits 3 and 4 of an 8-bit arithmetic operation. This flag is used by decimal adjust accumulator instruction (DAA) to correct the result of a packed BCD add or subtract operation. The H flag will be set (1) or reset (0) according to the following table:

| Н | ADD                                           | SUBTRACT                      |

|---|-----------------------------------------------|-------------------------------|

| 1 | There is a carry from<br>Bit 3 to Bit 4       | There is a borrow from bit 4  |

| 0 | There is no carry from<br>from Bit 3 to Bit 4 | There is no borrow from bit 4 |

2-48. Zero Flag (Z). The Zero Flag (Z) is set or reset if the result generated by the execution of certain instructions is a zero.

2-49. For 8-bit arithmetic and logical operations, the Z flag will be set to a 1 if the resulting byte in the Accumulator is zero. If the byte is not zero, the Z flag is reset to 0.

2-50. For compare (search) instructions, the Z flag will be set to a '1' if a comparison is made between the value in the Accumulator and the memory location pointed to by the contents of the register pair HL. 2-51. When testing a bit in a register or memory location, the Z flag will contain the complemented state of the indicated bit (see Bit b,s).

2-52. When inputting or outputting a byte between a memory location and an I/O device (INI;IND:OUTI and OUTD), if the result of B-1 is zero, the Z flag is set; otherwise, it is reset. Also for byte inputs from I/O devices using IN r,(C), the Z flag is set to indicate a zero byte input.

2-53. Sign Flag (S). The Sign Flag (S) stores the state of the most significant bit of the Accumulator (Bit 7). When the Z80 performs arithmetic operations on signed numbers, binary two's complement notation is used to represent and process numeric information. A positive number is identified by a 0 in bit 7. A negative number is identified by a 1. The binary equivalent of the magnitude of a positive number is stored in bits 0 to 6 for a total range of from 0 to 127. A negative number is represented by the two's complement of the equivalent positive number. The total range for negative numbers is from -1 to -128.

2-54. When inputting a byte from an I/O device to a register, IN r, (C), the S flag will indicate either positive (S=0) or negative (S=1) data. The state of the four testable flags is specified as follows:

| FLAG   | ON CONDITION | OFF CONDITION |

|--------|--------------|---------------|

| Carry  | C            | NC            |

| Zero   | Z            | NZ            |

| Sign   | M (minus)    | P (plus)      |

| Parity | PE (even)    | PO (odd)      |

2-55. INTERRUPTS. The purpose of an interrupt is to allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start a peripheral service routine. Usually this service routine is involved with the exchange of data, or status and control information, between the CPU and the peripheral. Once the service routine is completed, the CPU returns to the operation from which it was interrupted.

## 2-56. Interrupt Types. Non-Maskable

A non-maskable interrupt will be accepted at all times by the CPU. When this occurs, the CPU ignores the next instruction that it fetches and instead does a restart to location 0066H. Thus, it behaves exactly as if it had received a restart instruction but it is to a location that is not one of the 8 software restart locations. A restart is merely a call to a specific address in page 0 of memory.

### Maskable

The CPU can be programmed to respond to the maskable interrupt in any one of the possible modes.

#### Mode 0

This mode is identical to the 8080A interrupt response mode. With this mode, the interrupting device can place any instruction on the data bus and the CPU will execute it. Thus, the interrupting device provides the next instruction to be executed instead of the memory. Often this will be a restart instruction since the interrupting device only needs to supply a single byte instruction. Alternatively, another instruction such as a 3 byte call to any location in memory could be executed.

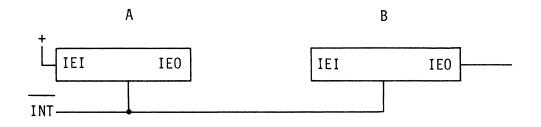

The number of clock cycles necessary to execute this instruction is 2 more than the normal number for the instruction. This occurs since the CPU automatically adds 2 wait states to an interrupt response cycle to allow sufficient time to implement an external daisy chain for priority control. After the application of RESET the CPU will automatically enter interrupt Mode 0.

#### Mode 1

When this mode has been selected by the programmer, the CPU will respond to an interrupt by executing a restart to location 0038H. Thus the response is identical to that for a non-maskable interrupt except that the call location is 0038H instead of 0066H. Another difference is that the number of cycles required to complete the restart instruction is 2 more than normal due to the two added wait states.

#### Mode 2

This mode is the most powerful interrupt response mode. With a single 8 bit byte from the user, an indirect call can be made to any memory location.

With this mode the programmer maintains a table of 16-bit starting addresses for every interrupt service routine. This table may be located anywhere in memory. When an interrupt is accepted, a 16-bit pointer must be formed to obtain the desired interrupt service routine starting address from the table. The upper 8 bits of this pointer are formed from the contents of the I Register. The I Register must have been previously loaded with the desired value by the programmer, i.e. LD I, A. Note that a CPU reset clears the I register so that it is initialized to zero. The lower eight bits of the pointer must be supplied by the interrupting device. Actually only 7 bits are required from the interrupting device as the least significant bit must be a zero. This is required since the pointer is used to get Interrupt Service Routine Starting Address Table

desired starting address pointed to by:

| I REG    | 7 BITS FROM |   |

|----------|-------------|---|

| CONTENTS | PERIPHERAL  | 0 |

The first byte in the table is the least significant (low order) portion of the address. The programmer must obviously fill this table in with the desired addresses before any interrupts are to be accepted.

Note that this table can be changed at any time by the programmer (if it is stored in Read/Write Memory) to allow different peripherals to be serviced by different service routines.

Once the interrupting device supplies the lower portion of the pointer, the CPU automatically pushes the program counter onto the stack, obtains the starting address from the table and does a jump to this address. This mode of response requires 19 clock periods to complete (7 to fetch the lower 8 bits from the interrupting device, 6 to save the program counter, and 6 to obtain the jump address).

Note that the Z80 peripheral devices all include a daisy chain priority interrupt structure that automatically supplies the programmed vector to the CPU during interrupt acknowledge. Refer to the Z80 PIO, Z80 SIO, and Z80 CTC manuals for details.

2-57. Interrupt Enable - Disable.

2-58. The Z80 CPU has two interrupt inputs, a software maskable interrupt and a non-maskable interrupt. The non-maskable interrupt (NMI) can not be disabled by the programmer and it will be accepted whenever a peripheral device requests it. This interrupt is generally reserved from very important functions that must be serviced whenever they occur, such as an impending power failure. The maskable interrupt (INT) can be selectively enabled or disabled by the programmer. This allows the programmer to disable the interrupt during periods where his program has timing constants that

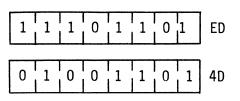

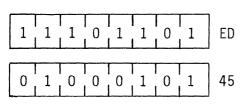

do not allow it to be interrupted. In the Z80 CPU there are enable flip flops (called  $IFF_1$  and  $IFF_2$ ) that are set or reset by the programmer using the Enable Interrupt (EI) and Disable Interrupt (DI) instructions. When the  $IFF_1$  is reset, an interrupt cannot be accepted by the CPU. Table 2-1 summarizes the effect of the different instructions on the two enable flip flops.

# 2-59. There are two enable flip flops, called $IFF_1$ and $IFF_2$ . IFF<sub>1</sub> IFF<sub>2</sub>

Actually disables interrupts Temporary storage location from being accepted. for IFF<sub>1</sub>.

The state of  $IFF_1$  is used to actually inhibit interrupts while  $IFF_2$  is used as a temporary storage location for  $IFF_1$ . The purpose of storing the  $IFF_1$  will be subsequently explained.

2-60. A reset to the CPU will force both  $IFF_1$  and  $IFF_2$  to the reset state so that interrupts are disabled. They can then be enabled by an EI instruction at any time by the programmer. When an EI instruction is executed, any pending interrupt request will not be accepted until after the instruction following EI has been executed. This single instruction delay is necessary for cases when the following instruction is a return instruction and interrupts must not be allowed until the return has been completed. The EI instruction sets both  $IFF_1$  and  $IFF_2$  to the enable state. When an interrupt is accepted by the CPU, both  $IFF_1$  and  $IFF_2$  are automatically reset, inhibiting further interrupts until the programmer wishes to issue a new EI instruction. Note that for all of the previous cases,  $IFF_1$  and  $IFF_2$  are always equal.

2-61. The purpose of  $IFF_2$  is to save the status of  $IFF_1$  when a non-maskable interrupt occurs. When a non-maskable interrupt is accepted,  $IFF_1$  is reset to prevent further interrupts until reenabled by the programmer. Thus, after a non-maskable interrupt has been accepted, maskable interrupts are disabled but the previous state of  $IFF_1$  has been saved so that the complete state of the CPU just prior to the non-maskable interrupt can be restored at any time. When a Load Register A with Register I (LD A,I) instruction or a Load Register A with Register R (LD A,R) instruction is executed, the state of  $IFF_2$  is copied into the parity flag where it can be tested or stored.

2-62. A second method of restoring the status of  $IFF_1$  is thru the execution of a Return from Non-Maskable Interrupt (RETN) instruction. Since this instruction indicates that the non-maskable interrupt service routine is complete, the contents of  $IFF_2$  are

2-14

"." indicates no change

now copied back into  $IFF_1$ , so that the status of  $IFF_1$  just prior to the acceptance of the non-maskable interrupt will be restored automatically.

| Action     | IFF <sub>1</sub> IF | FF2 |                  |   |                  |

|------------|---------------------|-----|------------------|---|------------------|

| CPU Reset  | 0                   | 0   |                  |   |                  |

| DI         | 0                   | 0   |                  |   |                  |

| EI         | 1                   | 1   |                  |   |                  |

| LD A,I     | •                   | •   | IFF <sub>2</sub> | > | Parity flag      |

| LD A,R     | •                   | •   | IFF <sub>2</sub> | > | Parity flag      |

| Accept NMI | 0                   | •   |                  |   |                  |

| RETN       | IFF <sub>2</sub>    | •   | IFF <sub>2</sub> | > | IFF <sub>1</sub> |

| Table 2-1. | Interrupt | Enable/Disable | Flip | Flops |

|------------|-----------|----------------|------|-------|

|------------|-----------|----------------|------|-------|

2-63. LOAD AND EXCHANGE INSTRUCTIONS. These instructions move data to and from registers, such as load B from D, load C from memory, store HL into memory, push IX into stack, and exchange AF with AF'.

0

0

RETI

Accept INT

2-64. BLOCK TRANSFER AND SEARCH INSTRUCTIONS. This group includes several useful instructions.

2-65. The load and increment instruction moves one byte of data from memory pointed to by HL to another memory location pointed to by DE. Both register pairs are automatically incremented and the byte counter (BC) is decremented. This instruction is extremely valuable in moving blocks of data.

2-66. Another instruction repeats the load and increment instruction automatically until the byte counter reaches zero. Thus, in one instruction, a block of data, up to 64K bytes in length, can be moved anywhere in memory.

2-67. The compare and increment instruction compares the contents of the accumulator with that of memory pointed to by HL. The appropriate flag bits are set, HL is automatically incremented, and the byte counter is decremented.

2-68. The compare, increment, and repeat instruction repeats the above instruction until either a match is found or the counter reaches zero.

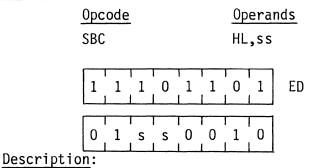

2-69. ARITHMETIC AND LOGICAL INSTRUCTIONS. These instructions include all the adds

2-16

and subtracts, increments, compares, exclusive-ors, etc. The Z80 features the indexed addressing mode and double precision add with carry and subtract with carry.

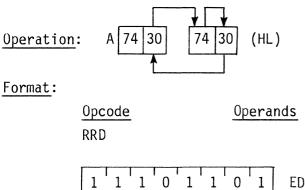

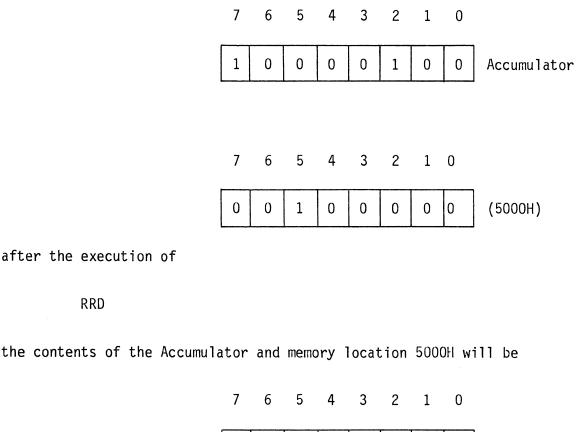

2-70. ROTATE AND SHIFT INSTRUCTIONS. The Z80 included four rotate accumulator instructions and logical shifts and arithmetic shifts. There are also two rotate digit instructions which are applicable to BCD arithmetic. With these adigit (4 bits) can be rotated with two digits in a memory location.

2-71. BIT MANIPULATION INSTRUCTIONS. There are three basic bit manipulation operations: test bit, set bit, and reset bit.

2-72. JUMP, CALL, AND RETURN. The Z80 has numerous conditional and unconditional jumps, calls, and returns. In addition, the Z80 has several jump relative instructions using relative addressing.

2-73. INPUT/OUTPUT INSTRUCTIONS.

2-74. The Z80 allows for a standard common I/O routine for all devices by including I/O instructions that use the C register to contain the IO device address. Therefore one I/O routine can be used with device address placed into register C before entering the routine. Also instead of being restricted to inputting or outputting to and from the accumulator only, any register can be used.

2-75. The Z80 has eight block tranfer I/O instructions which are similar to the memory block transfer instructions. HL is the memory pointer, C is the device pointer, and B is the byte counter. Therefore, an I/O block transfer can handle up to 256 bytes. Essentially, these commands are a processor implementation of direct memory access (DMA), invoked by a software sequence.

2-76. MISCELLANEOUS FEATURES. The Z80 instruction set also includes a no-operation instruction.

2-77. Z80 ASSEMBLY LANGUAGE SYNTAX.

2-78. INTRODUCTION.

2-79. The assembly language of the Z80 is designed to minimize the number of different opcodes corresponding to the set of basic machine operations and to provide for a consistent description of instruction operands. The nomenclature has been defined with special emphasis on mnemonic value and readability. 2-80. An assembly language program, or source program, consists of statements in a sequence which defines the user's program. The statements consist of:

- 1. labels,

- 2. opcodes or pseudo-ops

- 3. operands, and

- 4. comments.

2-81. Certain rules define how assembly language statements are to appear. A statement has four separate and distinct parts or fields.

| LABEL | OPCODE | OPERANDS | COMMENT |

|-------|--------|----------|---------|

|       |        |          |         |

e.g.: LOOP: LD HL, VALUE ;GET VALUE

2-82. The first field is the LABEL field. The label is a name used to reference the program counter, another label, or a constant.

2-83. The second field is the OPCODE field. It specifies the operation to be performed. There are 74 Z80 opcodes and several pseudo-ops that are standard for the Z80. The standard pseudo-ops are described in Appendix B.

2-84. The third field is the OPERAND field. It provides address or data information for the OPCODE field. There may be zero or more operands in the operand field depending on the requirements of the opcode field.

2-85. The fourth field is the COMMENT field. It is used to document a program. The comment field may appear in a statement without the other fields. Comments are ignored by an assembler, but they are printed in the assembly listing.

2-86. Each of the above parts, or fields, must be separated from each other by one or more commas, tabs, or blanks. If more than one operand appears, they must be separated from each other by one or more commas.

2-87. LABELS

2-88. A label is a symbol representing up to 16 bits of information and is used to specify an address or data. By using labels effectively, the user can write assembly language programs more rapidly and make fewer errors. 2-89. A label is composed of one or more characters. If more than 6 characters ar used for the label, only the first 6 will be recognized by a standard assembler The first character of a label must not be a number (0-9) or a restricted character The remaining characters connot include a restricted character. The restricted character acters are:

Control characters (0-2FH,7FH) Space ' ( ) \* = , - . / : ; < = >

Note that single dollar sign (\$) is reserved to represent the program counter.

2-90. A label can start in any column if followed by a colon (:). It does no require a colon if started in column one.

2-91. OPCODES. The bulk of this manual describes the Z80 opcodes. Opcodes are to 4 characters long and describe Z80 instructions.

2-92. STANDARD OPERANDS. There may be zero or more operands present in a statemen depending upon the opcode used. An operand which appears in a statement may tak one of the following forms.

A generic operand, such as the letter A, which stands for the accumulator

A constant. The constant must be in the range O through OFFFFH. It can be i the following forms:

Decimal - Any number may be denoted as decimal by following it with th letter 'D'. E.g., 35,249D. However, the assembler will conside any number which is undesignated as decimal. Hexadecimal - must begin with a number (0-9) and end with the letter 'H' E.g., OAF1H Octal - must end with the letter 'Q' or '0'. E.g., 377Q, 2770 Binary - must end with the letter 'B. e.g., 0110111B ASCII - letters enclosed in quote marks will be converted to their ASCI equivalent value. E.g., 'A' = 41H

3. A label which appears elsewhere in the program. Note that labels cannobe defined by labels which have not yet appeared in the user program for 2-pas assemblers.

E.g.:

L EQU H H EQU I I EQU 7 IS NOT ALLOWED. I EQU 7 H EQU I L EQU H IS ALLOWED.

4. The symbol \$ is used to represent the value of the program counter of the current instruction.

5. Expressions. Expression evaluation capability is a function of the features of a particular assembler. In general, arithmetic and logical expressions are allowed, and parentheses may be used to assure correct evaluation.

2-93. OPERAND NOTATION. The following notation is used in the assembly language:

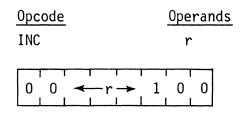

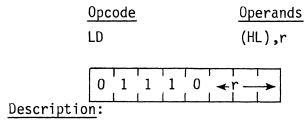

- 1) r specifies any one of the following registers: A,B,C,D,E,H,L.

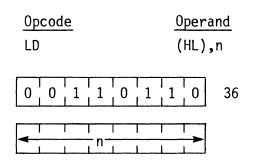

- 2) (HL) specifies the contents of memory at the location addressed by the contents of the register pair HL.

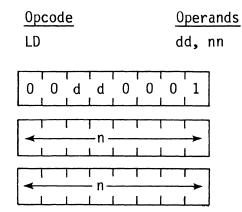

- n specifies a one-byte expression in the range 0 to 255. nn specifies a two byte expression in the range 0 to 65535.

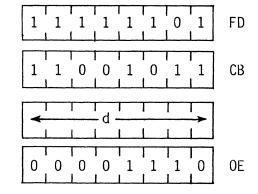

- 4) d specifies a one-byte expression in the range (-128,127).

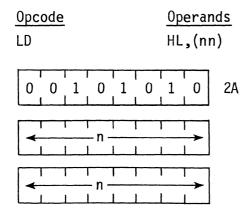

- 5) (nn) specifies the contents of memory at the location addressed by the two-byte expression nn.

- 6) b specifies an expression in the range (0.7).

- 7) e specifies a one-byte expression in the range (-126,129).

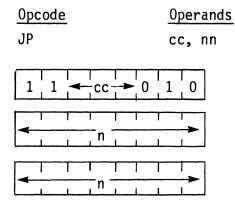

- 8) cc specifies the state of the flags for conditional JR and JP instructions.

- 9) qq specifies any one of the register pairs BC, DE, HL or AF.

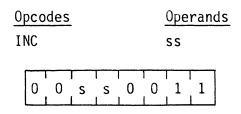

- 10) ss specifies any one of the following register pairs: BC, DE, HL, SP.

- 11) pp specifies any one of following register pairs: BC,DE, IX, SP.

- 12) rr specifies any one fo the following register pairs: BC, DE, IY, SP.

- 13) Specifies any of r,n, (HL, (IX+d), (IY+d).

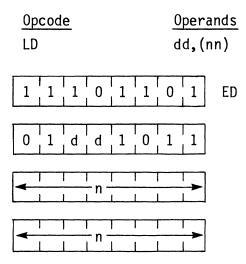

- 14) dd specifies any one of the following register pairs: BC, DE, HL, SP.

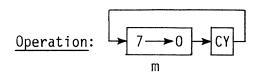

- 15) m specifies any of r, (HL), (IX+d), (IY+d).

The enclosing of an expression wholly in parentheses indicates a memory ad-NOTE: dress. The contents of the memory address equivalent to the expression value will be used as the operand value. 2-94. In doing relative addressing, the current value of the program counter must be subtracted from the label if a branch is to be made to that label address. E.g.:

JR NC,LOOP-\$

...will jump relative to 'LOOP'

2-95. COMMENTS. A comment is defined as any string of characters following a semicolon. Comments are ignored by an assembler, but they are printed on the assembly listing. Comments can begin in any column:

```

;

; this is a comment

;

```

2-96. UPPER/LOWER CASE.

NOTE: MOSTEK assemblers allow the user of lower case letters for labels and comments.

2-97. OPCODES - DETAILED DESCRIPTIONS.

2-98. INTRODUCTION. This section describes each Z80 opcode (instruction) in detail. The opcodes are presented in alphabetical order, one per page. Each instruction is introduced by its mnemonic opcode and symbolic operands. Then follows a brief description, operation, valid operand combinations, machine code, detailed description, condition bits affected, and one or more examples.

# ADCA, s

### Operation. A $\leftarrow$ A + s + CY

Format:

| Opcode | <u>Operands</u> |

|--------|-----------------|

| ADC    | A,s             |

The s operand is any of r,n, (HL),IX+d) or (IY+d) as defined for the analogous ADD instruction. These various possible opcode-operand combinations are assembled as follows in the object code:

| ADC A,r       | 1 | 0      | 0 | 0     | <b>←</b> | r* -   | <br> | ->          |    |

|---------------|---|--------|---|-------|----------|--------|------|-------------|----|

| ADC A,n       | 1 | 1      | 0 | 0     | 1        | 1      | 1    | 0           | CE |

|               | - | I<br>I | I | - n - | I        |        |      | <b>&gt;</b> |    |

| ADC A,(HL)    | 1 | 0      | 0 | 0     | 1        | 1      | 1    | 0           | 8E |

| ADC A,(IX+d)  | 1 |        | 0 | 1     | 1        | 1      | 0    | 1           | DD |

|               | 1 | 0      | 0 | 0     |          | 1      | 1    | 0           | 8E |

|               | • | 1      | 1 | d -   | 1        | 1      | <br> | <b>&gt;</b> |    |

| ADC A, (IY+d) | 1 | 1      | 1 | 1     | 1        | 1      | 0    | 1           | FD |

|               | 1 | 0      | 0 | 0     | 1<br>1   |        | 1    | 0           | 8E |

|               | - | 1      | l | d ·   | 1        | I<br>1 |      | →<br>-      |    |

r identifies registers B,C,D,E,H,L or A assembled as follows in the object code ield above:

| Register | <u> </u> |

|----------|----------|

| В        | 000      |

| С        | 001      |

| D        | 010      |

| E        | 011      |

| Н        | 100      |

| L        | 101      |

| A        | 111      |

#### Description:

The s operand, along with the Carry Flag ("C" in the F register) is added to the contents of the Accumulator, and the result is stored in the Accumulator.

| INSTRUCTION   | M CYCLES | T STATES      |

|---------------|----------|---------------|

| ADC A,r       | 1        | 4             |

| ADC A,n       | 2        | 7(4,3)        |

| ADC A,(HL)    | 2        | 7(4,3)        |

| ADC A, (IX+d) | 5        | 19(4,4,3,5,3) |

| ADC A,(IY+d)  | 5        | 19(4,4,3,5,3) |

Condition Bits Affected:

| S: | Set if  | result   | is | negative; |

|----|---------|----------|----|-----------|

|    | reset ( | otherwis | e  |           |

- Z: Set if result is zero; reset otherwise

- H: Set if carry from Bit 3; reset otherwise

- P/V: Set if overflow: reset otherwise

- N: Reset

- C: Set if carry from Bit 7; reset otherwise

#### Example:

If the Accumulator contains 16H, the Carry Flag is set, the HL register pair contains 6666H, and address 6666H contains 10H, after the execution of ADC A,(HL) the Accumulator will contain 27H.

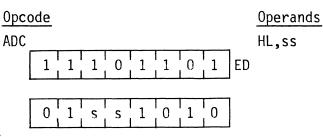

## ADC HL, ss

Operation: HL←HL+ss+CY

Format:

#### Description:

The contents of register pair ss (any of register pairs DC, DE, HL or SP) are added with the Carry Flag (C flag in the F register) to the contents of register pair HL, and the result is stored in HL. Operand ss is specified as follows in the assembled object code.

| Register |           |

|----------|-----------|

| Pair     | <u>ss</u> |

| BC       | 00        |

| DE       | 01        |

| HL       | 10        |

| SP       | 11        |

M CYCLES: 4 T STATES: 15(4,4,4,3)

## Condition Bits affected:

- S. Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- H: Set if carry out of Bit 11; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: Reset

- C: Set if carry from Bit 15; reset otherwise

Example:

If the register pair BC contains 2222H, register pair HL contains 5437H and the Carry Flag is set, after the execution of

ADC HL, BC

the contents of HL will be 765AH.

# ADD A, (HL)

<u>Operation</u>:  $A \leftarrow A + (HL)$

Format:

| 0 | pcod | <u>le</u> |   |   |   |   | 0pe | ran | ds |

|---|------|-----------|---|---|---|---|-----|-----|----|

| A | DD   |           |   |   |   |   | Α,( | HL) |    |

|   | 1    | 0         | 0 | 0 | 0 | 1 | 1   | 0   | 86 |

Description:

The byte at the memory address specified by the contents of the HL register pair is added to the contents of the Accumulator and the result is stored in the Accumulator.

M CYCLES: 2 T STATES: 7(4,3)

#### Condition Bits Affected:

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- H: Set if carry from Bit 3; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: reset

- C: Set if carry from Bit 7; reset otherwise

## Example:

If the contents of the Accumulator are AOH, and the content of the register pair HL is 2323H, and memory location 2323H contains byte O8H after the execution of ADD A, (HL) the Accumulator will contain A8H.

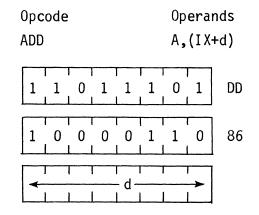

# ADD A, (IX+d)

<u>Operation</u>:  $A \leftarrow A + (IX+d)$

Format:

## Description:

The contents of the Index Register (register pair IX) is added to a displacemer d to point to an address in memory. The contents of this address is then added t the contents of the Accumulator and the result is stored in the Accumulator.

M CYCLES: 5 T STATES: 19(4,4,3,5,3)

## Condition Bits Affected:

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- H: set if carry from Bit 3; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: Reset

- C: Set if carry from

- Bit 7; reset otherwise

## Example:

If the Accumulator contents are 11H, the Index Register IX contains 1000H, and if th content of memory location

$1005 \mbox{H}$  is 22H, after the execution of

ADD A, (IX+5H)

the contents of the Accumulator will be 33H.

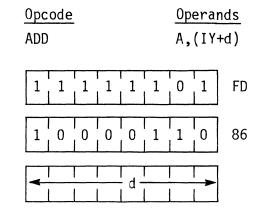

# ADD A, (IY+d)

Operation:  $A \leftarrow A+(IY+d)$

Format:

## Description:

The contents of the Index Register (register pair IY) are added to a displacem d to point to an address in memory. The contents of this address is then add to the contents of the Accumulator and the result is stored in the Accumulato

M CYCLES: 5 T STATES: 19(4,4,3,5,3)

#### Condition Bits Affected:

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- H: Set if carry from Bit 3; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: Reset

- C: Set if carry from bit 7: reset otherwise

#### Example:

If the Accumulator contents are 11H, the Index Register pair IY contains 1000H and if the content of memory

2-28

## ADD A,(IY+5H)

the contents of the Accumulator will be 33H.

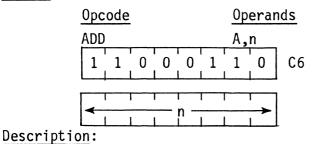

## ADD A, n

<u>Operation</u>:  $A \leftarrow A + n$

Format.

The integer n is added to the contents of the Accumulator and the results are stor $\epsilon$  in the Accumulator.

M CYCLES: 2 T STATES: 7(4,3)

### Condition Bits Affected:

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero; reset otherwise

- H: Set if carry from

Bit 3; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: Reset

- C: Set if carry from

- Bit 7; reset otherwise

## Example:

If the contents of the Accumulator are 23H, after the execution of ADD A,33H

the contents of the Accumulator will be 56H.

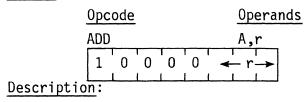

## ADD A, r

<u>Operation</u>: A ← A + r

Format:

The contents of register r are added to the contents of the Accumulator, and the result is stored in the Accumulator. The symbol r identifies the registers A,B,C,D,E,H or L assembled as follows in the object code:

| Register | <u> </u> |

|----------|----------|

| А        | 111      |

| В        | 000      |

| С        | 001      |

| D        | . 010    |

| E        | 011      |

| Н        | 100      |

| L        | 101      |

## M CYCLES: 1 T STATES: 4

## Condition Bits Affected:

- S: Set if result is negative; reset otherwise

- Z: Set if result is zero: reset otherwise

- H: Set if carry from

- Bit 3; reset otherwise

- P/V: Set if overflow; reset otherwise

- N: Reset

- C: Set if carry from Bit 7; reset otherwise

## Example:

If the contents of the Accumulator are 44H, and the contents of register C are 11H after the execution of

ADD A,C

the contents of the Accumulator will be 55H.

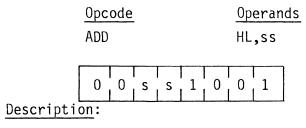

## ADD HL, ss

Operation: HL ← HL + ss

Format:

The contents of register pair ss (any of register pairs BC, DE, HL or SP) are added to the contents of register pair HL and the result is stored in HL. Operand ss is specified as follows in the assembled object code.

| <u>Registe</u> r |    |

|------------------|----|

| Pair             | SS |

| BC               | 00 |

| DE               | 01 |

| HL               | 10 |

| SP               | 11 |

M CYCLES: 3 T STATES: 11(4,4,3)

Condition Bits Affected:

- S: Not affected

- Z: Not affected

- H: Set if carry out of

- Bit 11; reset otherwise

- P/V: Not affected

- N: Reset

- C: Set if carry from Bit 15; reset otherwise

## Example:

If register pair HL contains the integer 4242H and register pair DE contains 1111H, after the execution of

Ð

ADD HL,DE

the HL register will contain 5353H

# ADD IX, pp

## Operation: $IX \leftarrow IX + pp$

Format:

| Opcod  | de       |   |   |   |   | <u>0p</u> | era | nds |

|--------|----------|---|---|---|---|-----------|-----|-----|

| ADD    |          |   |   |   |   | ΙX        | ,pp |     |

|        |          | 0 | 1 | 1 | 1 | 0         | 1   | DD  |

| ,<br>, |          |   |   | r | , |           | ·   |     |

| 0 0    | ן נ<br>ו | р | р | 1 | 0 | 0         | 1   |     |

### Description:

The contents of register pair pp (any of register pairs BC,DE, IX or SP) are added to the contents of the Index Register IX, and the results are stored in IX. Operand pp is specified as follows in the assembled object code.

| <u>Register</u> |   |    |

|-----------------|---|----|

| Pair            |   | pp |

| BC              |   | 00 |

| DE              |   | 01 |

| IX              | 1 | 10 |

| SP              |   | 11 |

M CYCLES: 4 T STATES: 15(4,4,4,3)

Condition Bits Affected:

- S; Not affected

- Z: Not affected

- H: Set if carry out of Bit 11; reset otherwise

- P/V: Not affected

- N: Reset

- C: Set if carry from Bit 15; reset otherwise

## Example:

If the contents of Index Register IX are 3333H and the contents of register pair BC are 5555H, after the execution of

ADD IX,BC

the contents of IX will be 8888H.

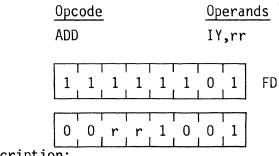

# ADD IY, rr

### )peration: $1Y \leftarrow 1Y + rr$

#### <sup>-</sup>ormat:

## Description:

The contents of register pair rr (any of register pairs BC,DE,IY or SP) are added to the contents of Index Register IY, and the result is stored in IY. Operand rr is specified as follows in the assembled object code.

| Register |    |  |  |  |

|----------|----|--|--|--|

| Pair     | rr |  |  |  |

| BC       | 00 |  |  |  |

| DE       | 01 |  |  |  |

| IY       | 10 |  |  |  |

| SP       | 11 |  |  |  |

M CYCLES: 4 T STATES: 15(4,4,4,3)

Condition Bits Affected:

- S: Not affected

- Z: Not affected

- H: Set if carry out of

- Bit 11; reset otherwise

- P/V: Not affected

- N: Reset

- C: Set if carry from Bit 15; reset otherwise

## Example:

If the contents of Index Register IY are 3333H and the contents of register pair are 5555H, after the execution of

ADD IY,BC

the contents of IY will be 8888H.

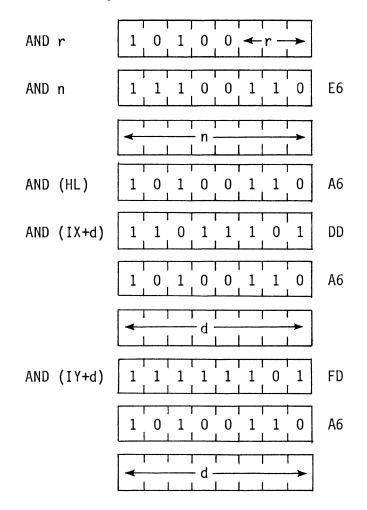

## AND s

<u>Operation</u>:  $A \leftarrow A$  s

Format:

| <u>Opcode</u> | <u>Operands</u> |

|---------------|-----------------|

| AND           | S               |

The s operand is any of r,n,(HL),(IX+d) or (IY+d), as defined for the analogous ADD instructions. These various possible opcode-operand combinations are assembled as follows in the object code:

\*r identifies registers B,C,D,E,H,L or A assembled as follows in the object code field above:

| Register | <u> </u> |

|----------|----------|

| В        | 000      |

| C        | 001      |

| D        | 010      |

| Е        | 011      |

| Н        | 100      |

| L        | 101      |

| А        | 111      |

## Description:

A logical AND operation, bit by bit, is performed between the byte specified by the s operand and the byte contained in the Accumulator; the result is stored in the Accumulator.

| INSTRUCTION | M CYCLES | <u>T STATES</u> |

|-------------|----------|-----------------|

| AND r       | 1        | 4               |

| AND n       | 2        | 7 (4,3)         |

| AND (HL)    | 2        | 7 (4,3)         |

| AND (IX+d)  | 5        | 19(4,4,3,5,3)   |

| AND (IY+d)  | 5        | 19(4,4,3,5,3)   |

### Condition Bits Affected:

| S: | Set i | f | result   | is | negative; |

|----|-------|---|----------|----|-----------|

|    | reset | C | otherwis | se |           |

- Z: Set if result is zero: reset otherwise

- H: Set

- P/V: Set if parity even; reset otherwise

- N: Reset

- C: Reset

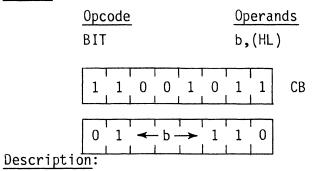

# BIT b, (HL)

## <u>Operation</u>: $Z \leftarrow (HL)_{b}$

Format:

After the execution of this instruction, the Z flag in the F register will contain the complement of the indicated bit within the contents of the memory address pointed to by the HL register pair. Operand b is specified as follows in the assembled object code:

| Bit Tested | _ <u>b</u> |

|------------|------------|

| 0          | 000        |

| 1          | 001        |

| 2          | 010        |

| 3          | 011        |

| 4          | 100        |

| 5          | 101        |

| 6          | 110        |

| 7          | 111        |

|            |            |

## M CYCLES: 3 T STATES: 12(4,4,4)

Condition Bits Affected:

- S: Unknown

- Z: Set if specified bit is 0; reset otherwise

- H: Set

- P/V: Unknown

- H: Reset

- C: Not affected

## Example:

If the HL register pair contains 4444H, and bit 4 in the memory location 4444H contains 1, after the execution of

BIT 4, (HL)

the Z flag in the F register will contain 0, and bit 4 in memory location 4444H will still contain 1. (Bit 0 in memory location 4444H is the least significant bit.)

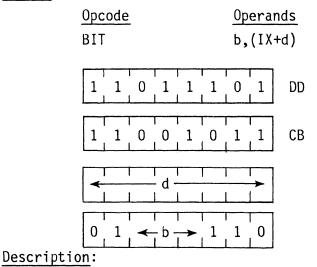

# BIT b, (IX+d)

## <u>Operation</u>: $Z \leftarrow \overline{(IX+d)}_b$

Format:

After the execution of this instruction, the Z flag in the F register will contain the complement of the indicated bit within the contents of the memory location pointed to by the sum of the contents of register pair IX (Index Register IX) and the two's complement displacement integer d. Operand b is specified as follows in the assembled object code.

| _ <u>b</u> |

|------------|

| 000        |

| 001        |

| 010        |

| 011        |

| 100        |

| 101        |

| 110        |

| 111        |

|            |

M CYCLES: 5 T STATES: 20(4,4,3,5,4)

## Condition Bits Affected:

- S: Unknown

- Z: Set if specified bit is

- 0; reset otherwise

- H: Set

- P/V: Unknown

- N: Reset

- C: Not affected

Example:

If the contents of Index Register IX are 2000H, and bit 6 in memory location 2004H contains 1, after the execution of

BIT 6, (IX+4H)

the Z flag in the F register will contain 0, and bit 6 in memory location 2004H will still contain 1. (Bit 0 in memory location 2004H is the least significant bit).

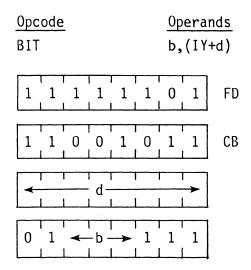

# BIT b, (IY+d)

<u>Operation</u>:  $Z \leftarrow \overline{(IY+d)}_b$

Format:

## Description:

After the execution of this instruction, the Z flag in the F register will contain the complement of the indicated bit within the contents of the memory location pointed to by the sum of the contents of register pair IY (Index Register IY) and the two's complement displacement integer d. Operand b is specified as follows in the assembled object code:

| Bit Tested | b   |

|------------|-----|

| 0          | 000 |

| 1          | 001 |

| 2          | 010 |

| 3          | 011 |

| 4          | 100 |

| 5          | 101 |

| 6          | 110 |

| 7          | 111 |

M CYCLES: 5 T STATES: 20(4,4,3,5,4)

## Condition Bits Affected:

- S: Unknown

- - 0; reset other wise

- H: Set

- P/V: Unknown

- N: Reset

- C: Not affected

## Example:

If the contents of Index Register are 2000H, and bit 6 in memory location 2004H contains 1, after the execution of

BIT 6, (IY+4H)

the Z flag in the F register will contain 0, and bit 6 in memory location 2004H will still contain 1. (Bit 0 in memory location 2004H is the least significant bit).

## BIT b, r

Operation:  $Z \leftarrow r_b$

Format:

## Description:

After the execution of this instruction, the Z flag in the F register will contain the complement of the indicated bit within the contents of the r - register. Operands b and r are specified as follows in the assembled object code:

| Bit Tested | b   | register | r   |

|------------|-----|----------|-----|

| 0          | 000 | В        | 000 |

| 1          | 001 | С        | 001 |

| 2          | 010 | D        | 010 |

| 3          | 011 | E        | 011 |

| 4          | 100 | Н        | 100 |

| 5          | 101 | L        | 101 |

| 6          | 110 | А        | 111 |

| 7          | 111 |          |     |

M CYCLES: 2 T STATES: 8 (4,4)

## Condition Bits Affected:

- S: Unknown

- Z: Set if specified bit is

- 0; reset otherwise

- H: Set

- P/V: Unknown

- H: Reset

- C: Not affected

Example:

If bit 4 in the B-register contains 1, after the execution of

BIT 4, B

the Z flag in the F register will contain 0, and bit 4 in the B register will still contain 1. (Bit 0 in the B-register is the least significant bit.)

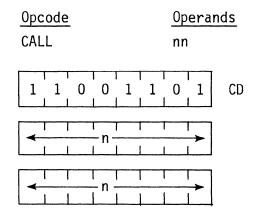

## CALL cc, nn

<u>Operation</u>: IF cc TRUE: (SP-1)  $\leftarrow PC_{H}$ (SP-2)  $\leftarrow PC_{I}$ , PC  $\leftarrow$  nn

Format:

$\begin{array}{ccc} \underline{Opcode} & \underline{Opcrands} \\ CALL & cc,nn \\ \hline 1 & 1 & \hline cc \rightarrow 1 & 0 & 0 \\ \hline & & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & & \\ \hline 1 & 1 & \hline & & & \\ \hline 1 & 1 & \hline & & & \\ \hline 1 & 1 & \hline \\ 1 & 1 & 1 & \hline \\ 1 & 1 & 1 & \hline$

Note: The first of the two n operands in the assembled object code above is the least significant byte of the two-byte memory address.

## Description:

If condition cc is true, this instruction pushes the current contents of the Program Counter (PC) onto the top of the external memory stack, then loads the operands nn into PC to point to the address in memory where the first opcode of a subroutine is to be fetched. (At the end of the subroutine, a Return instruction can be used to return to the original program flow by popping the top of the stack back into PC.) If condition cc is false, the Program Counter is incremented as usual, and the program continues with the next sequential instruction. The stack push is accomplished by first decrementing the current contents of the Stack Pointer (SP), loading the highorder byte of the PC contents into the memory address now pointed to by SP; then decrementing SP again, and loading the low-order byte of the PC contents into the top of the stack. Note: Because this is a 3-byte instruction, the Program Counter will have been incremented by 3 before the push is executed. Condition cc is programmed as one of eight status which corresponds to condition bits in the Flag Registe (register F). These eight status are defined in the table below, which also specific the corresponding cc bit fields in the assembled object code:

| CC  | Condition                                                                                                       | Relevant |

|-----|-----------------------------------------------------------------------------------------------------------------|----------|

|     | and the state of the | Flag     |

| 000 | NZ non zero                                                                                                     | Z        |

| 001 | Z zero                                                                                                          | Z        |

| 010 | NC non carry                                                                                                    | C        |

| 011 | C carry                                                                                                         | С        |

| 100 | PO parity odd                                                                                                   | P/V      |

| 101 | PE parity even                                                                                                  | P/V      |

| 110 | P sign positive                                                                                                 | S        |

| 111 | M sign negative                                                                                                 | S        |

If cc is true:

M CYCLES: 5 T STATES: 17(4,3,4,3,3)

If cc is false:

M CYCLES: 3 T STATES: 10(4,3,3)

Condition Bits Affected: None

#### Example:

If the C Flag in the F register is reset, the contents of the Program Counter are 1A47H, the contents of the Stack Pointer are 3002H, and memory locations have the contents:

| Location | Contents |

|----------|----------|

| 1A 47H   | D 4H     |

| 1A 48H   | 35H      |

| 1A 49H   | 21H      |

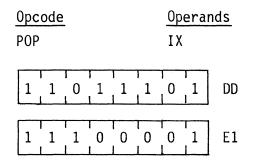

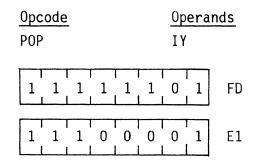

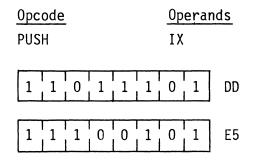

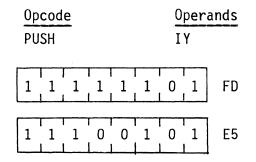

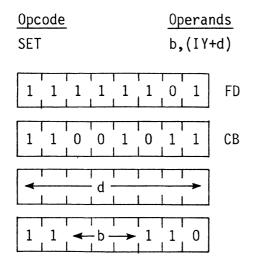

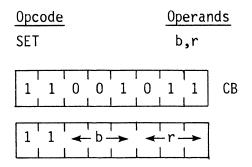

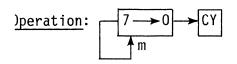

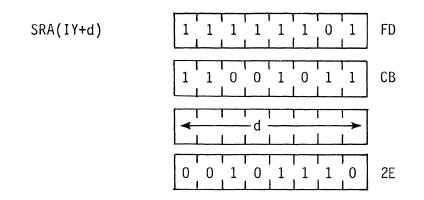

then if an instruction fetch sequence begins, the three-byte instruction D43521H will be fetched to the CPU for execution. The mnemonic equivalent of this is