Section

### Numerical and Functional Indexes **Product Cross Reference Guide**

**Microcomputers** Microprocessors Peripherals ROMs **Boards**

#### **CMOS Microprocessors** Peripherals ROMs **Consumer Products**

# LCD 4

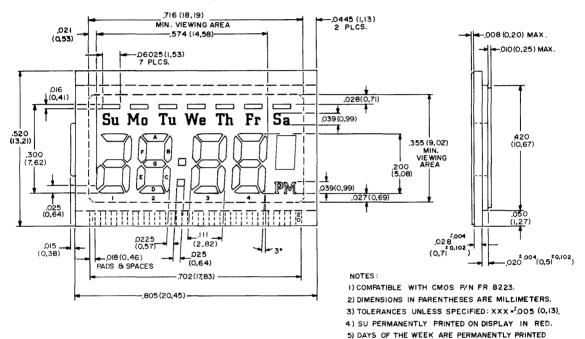

Packaging Information 5

Application Notes 6

**Representatives and Distributors 7**

# SECTION 1

# Numerical and Functional Indexes Product Cross Reference Guide

commodore commodore commodore commodore commodore commodore commodore commodore commodore commodore

### NUMERICAL INDEX NMOS

| Device       |                                              | Page  |

|--------------|----------------------------------------------|-------|

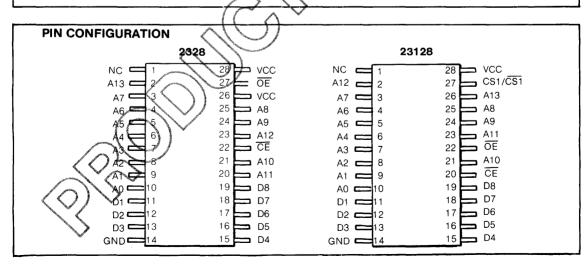

| 23128        | Static ROM (16384x8)                         | 2-153 |

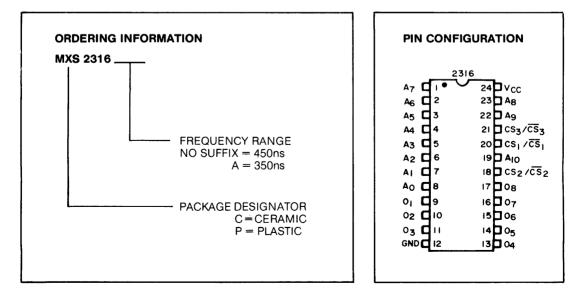

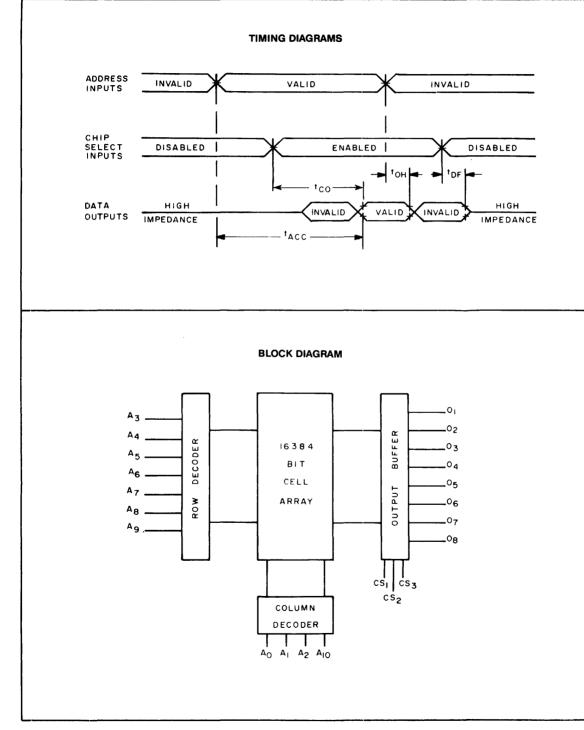

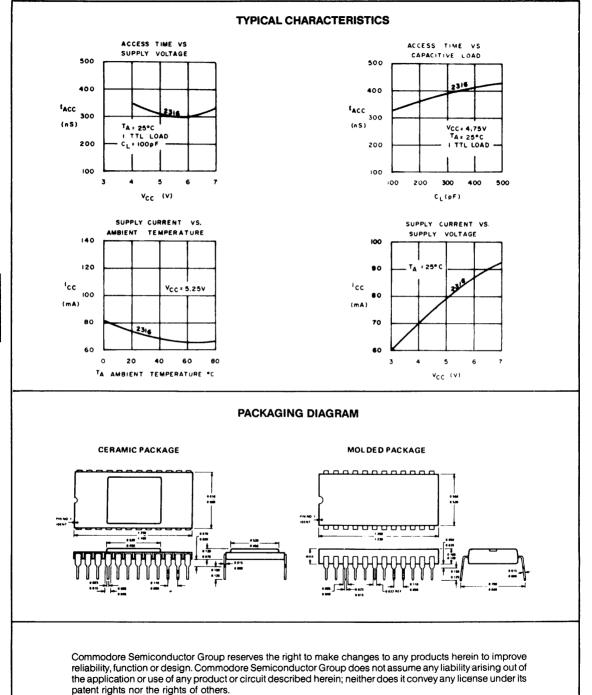

| 2316         | Static ROM (2048x8)                          | 2-137 |

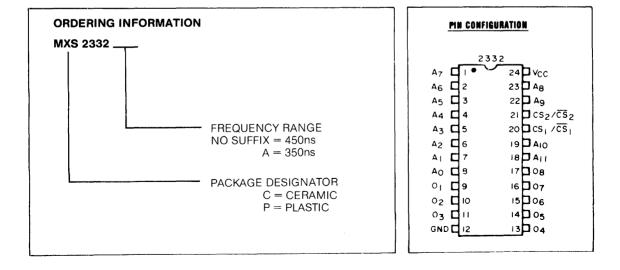

| 2332         | Static ROM (4096x8)                          | 2-141 |

| 2333         | Static ROM (4096x8)                          | 2-145 |

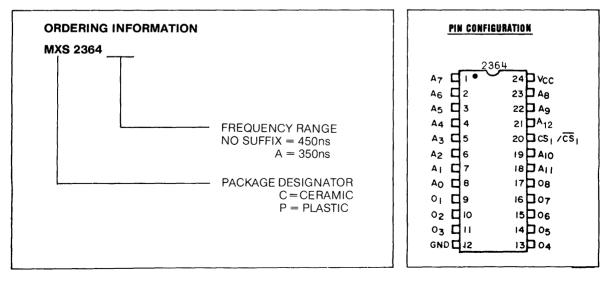

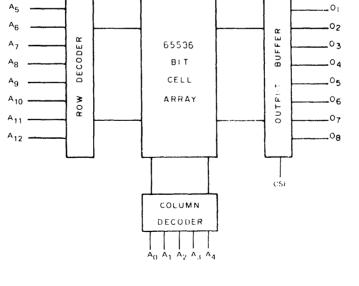

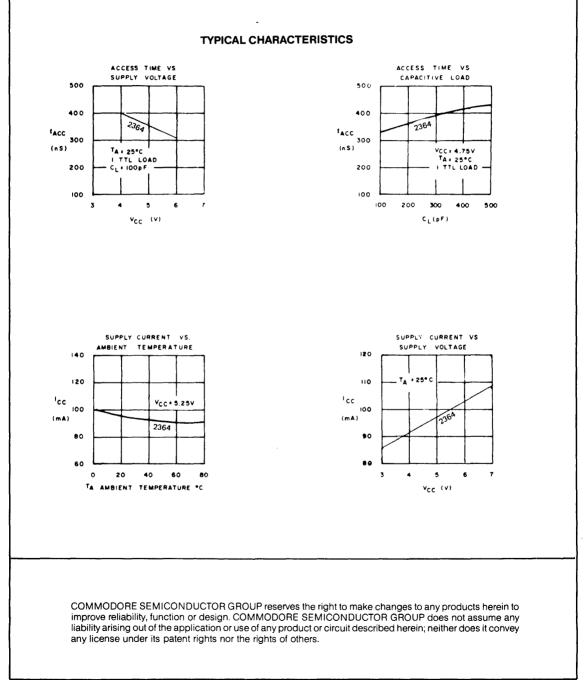

| 2364         | Static ROM (8192x8)                          | 2-149 |

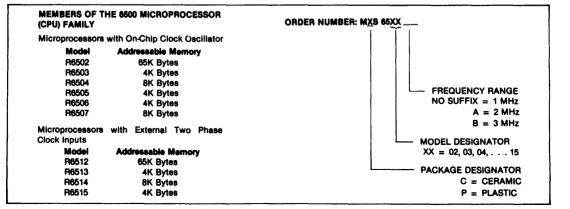

| 6500         | Microprocessor Family                        | 2-14  |

| 6500/1       | Single Chip Microcomputer                    | 2-2   |

| 6502         | Microprocessor                               | 2-22  |

| 6503         | Microprocessor                               |       |

| 6504         | Microprocessor                               | 2-22  |

| 6505         | Microprocessor                               | 2-22  |

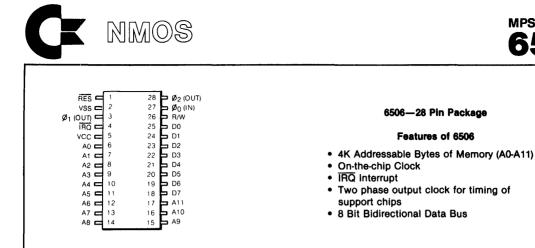

| 6506         | Microprocessor                               | 2-23  |

| 6507         | Microprocessor                               | 2-23  |

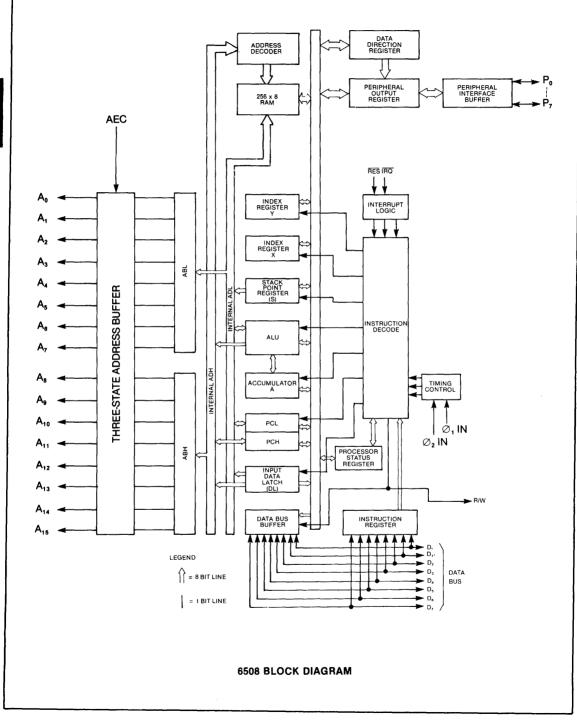

| 6508         | Microprocessor, with RAM and I/O             |       |

| 6509         | Microprocessor, with Memory Management       |       |

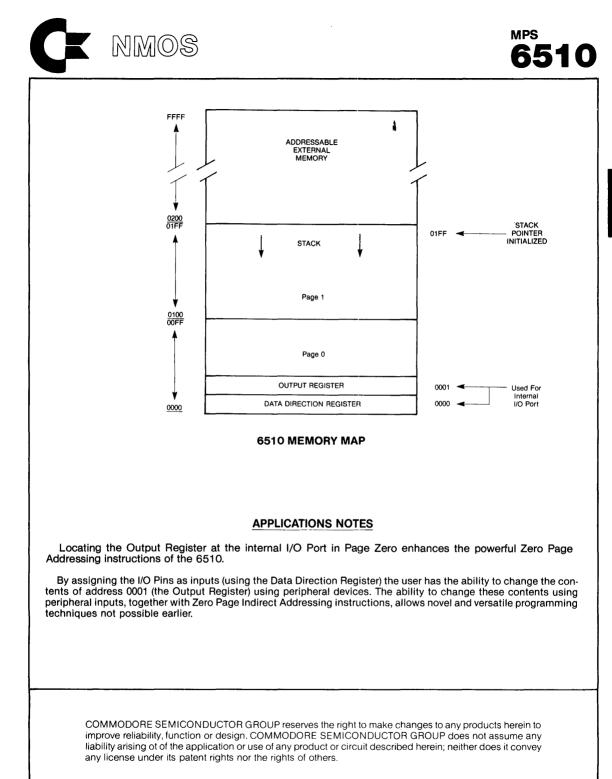

| 6510         | Microprocessor, with I/O                     |       |

| 6512         | Microprocessor                               | 2-23  |

| 6513         | Microprocessor                               | 2-24  |

| 6514         | Microprocessor                               | 2-24  |

| 6515         | Microprocessor                               | 2-24  |

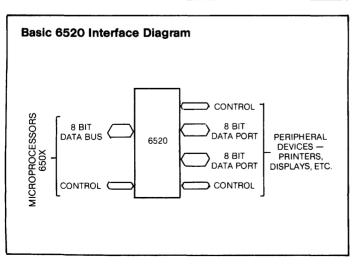

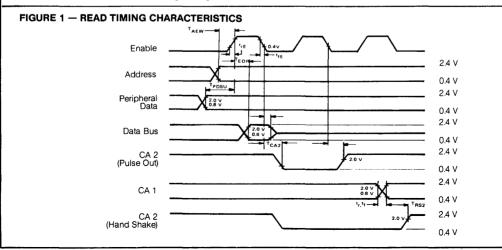

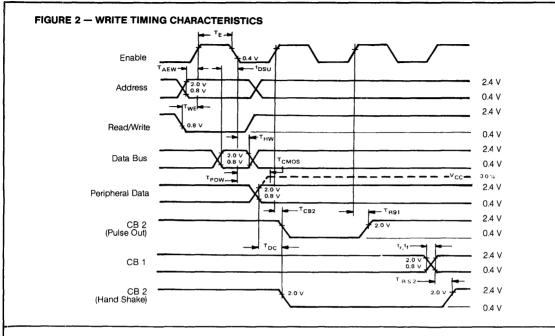

| 6520         | Peripheral Adapter                           | 2-46  |

| 6522         | Versatile Interface Adapter (VIA)            | 2-50  |

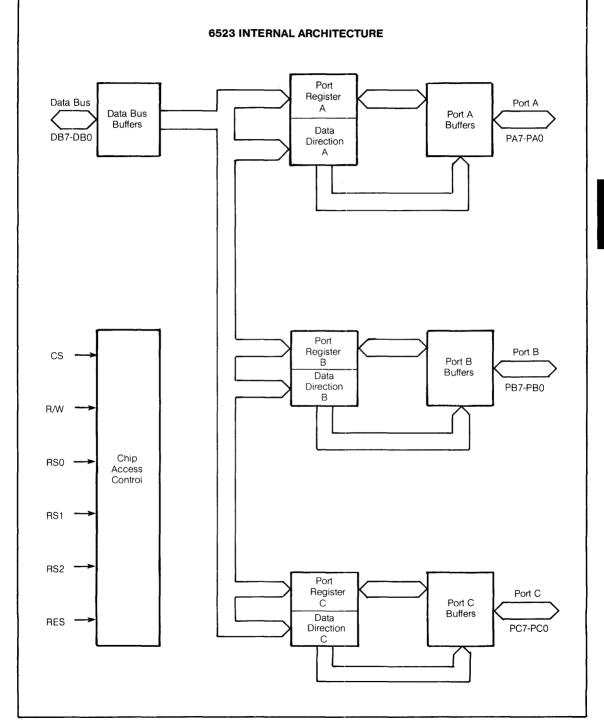

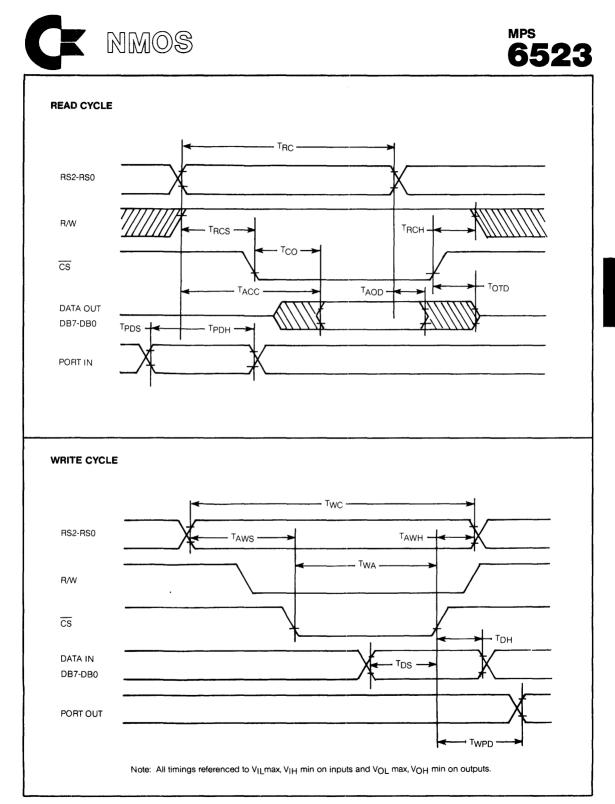

| 6523         | Tri-Port Interface                           | 2-66  |

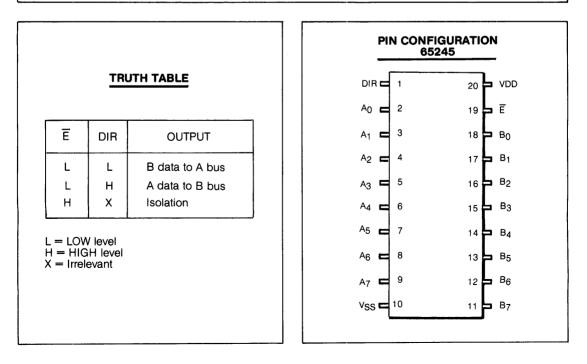

| 65245        | Octal Bus Transceiver with 3 State Outputs   |       |

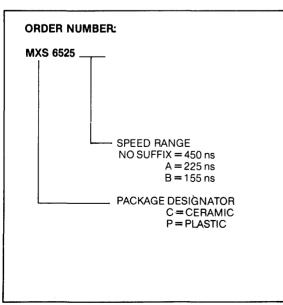

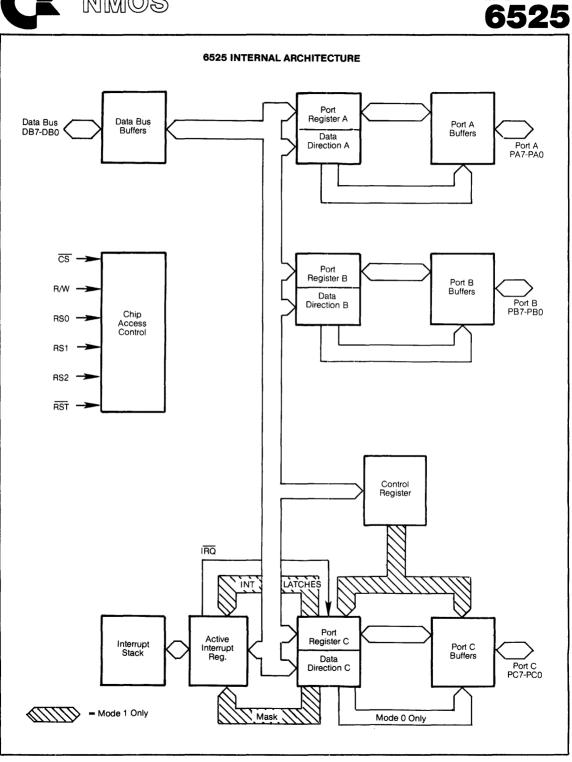

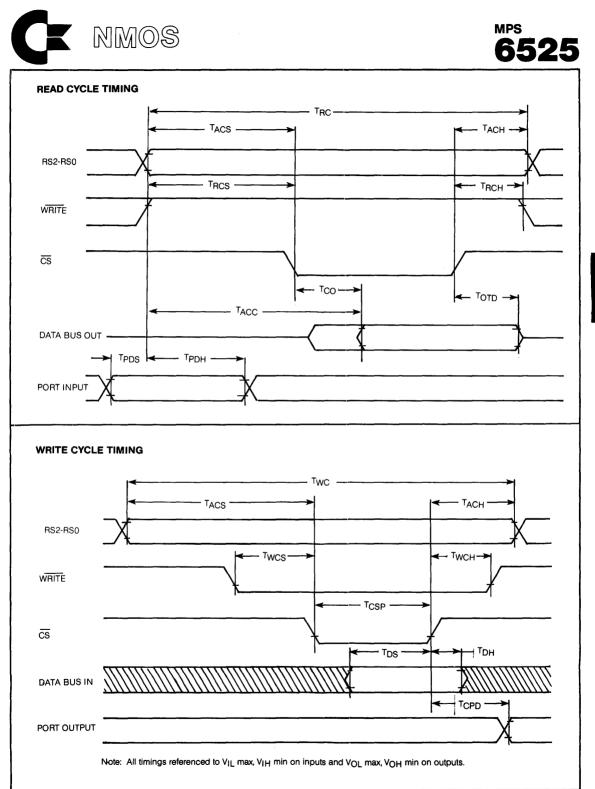

| 6525         | Tri-Port Interface                           | 2-76  |

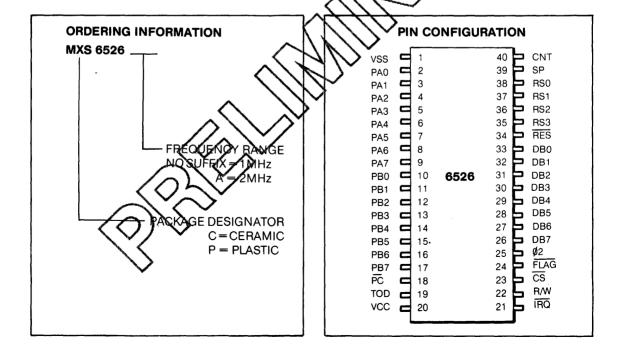

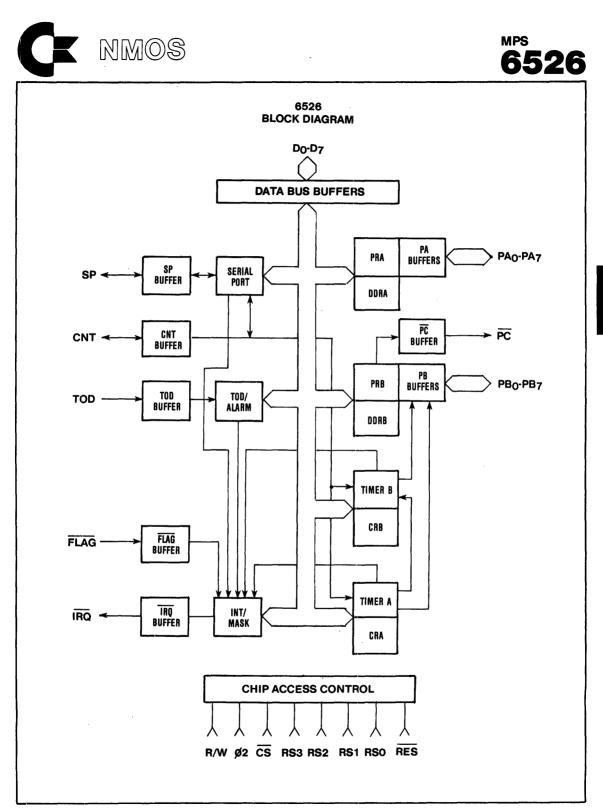

| 6526         | Complex Interface Adapter (CIA)              | 2-84  |

| 6529         | Single Port Interface                        |       |

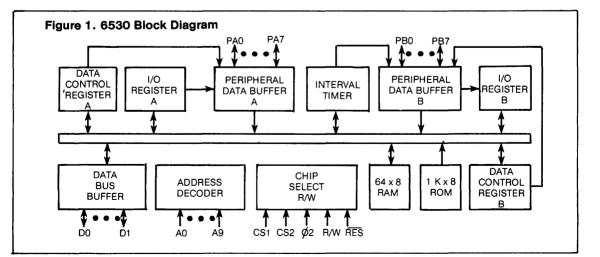

| 6530         | Memory, I/O, Timer Array                     | 2-96  |

| 6532         | Memory, I/O, Timer Array                     |       |

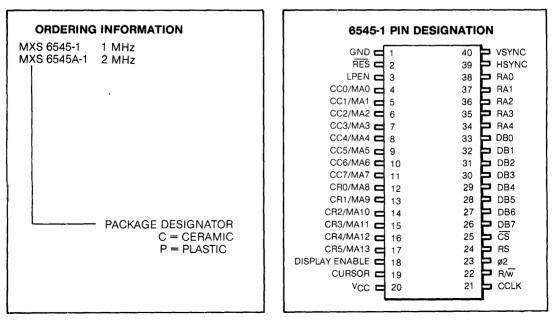

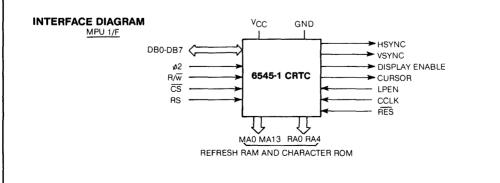

| 6545-1       | CRT Controller                               |       |

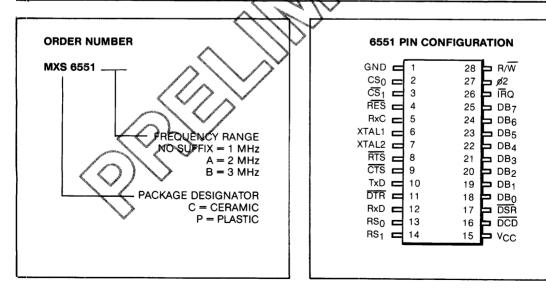

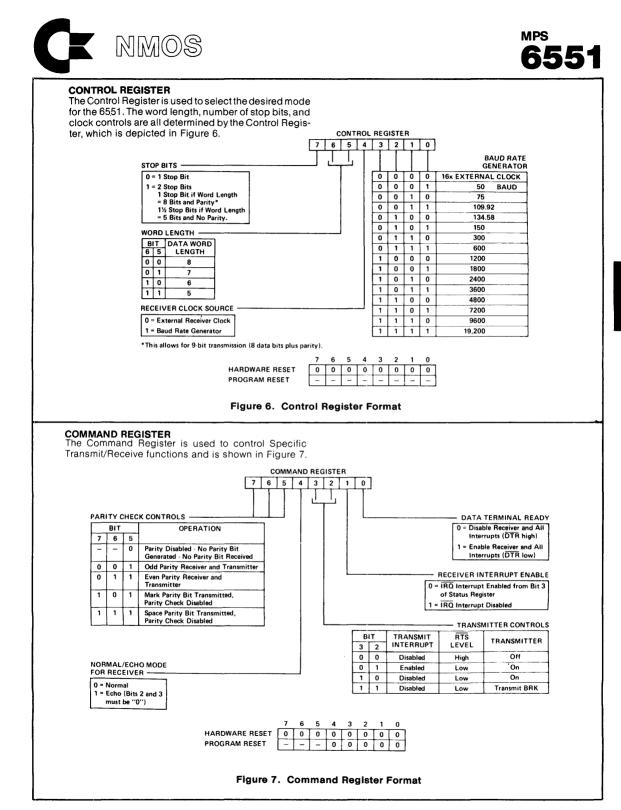

| 6551         | Asynchronous Communication Interface Adapter |       |

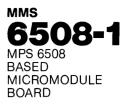

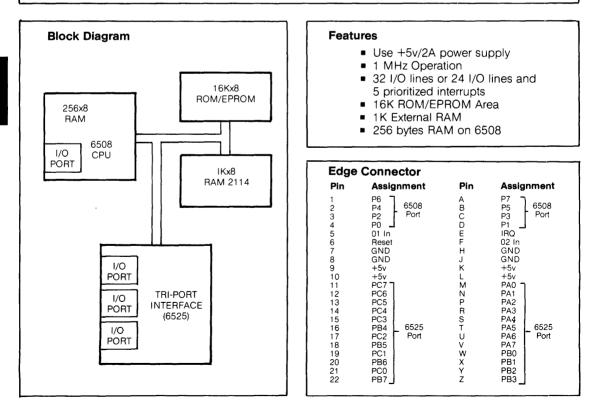

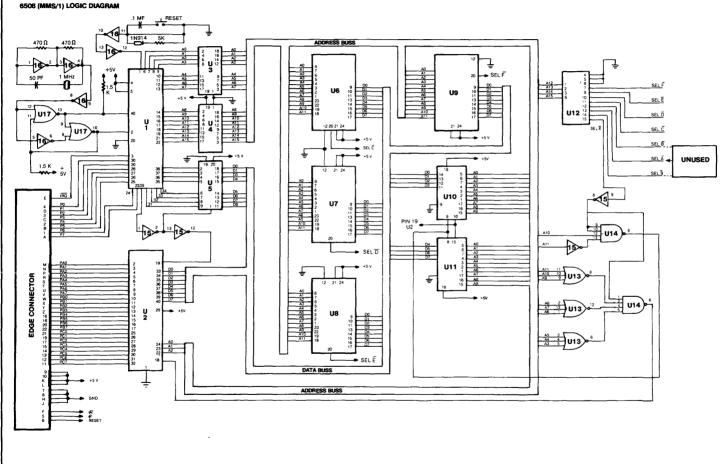

| MMS 6508-1   | Micromodule Board                            |       |

| 11110 0000-1 |                                              | - 107 |

### NUMERICAL INDEX CMOS

| Device | Description                                        | Page |

|--------|----------------------------------------------------|------|

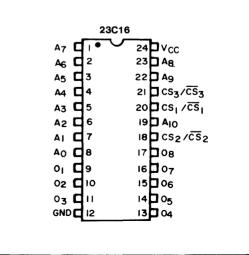

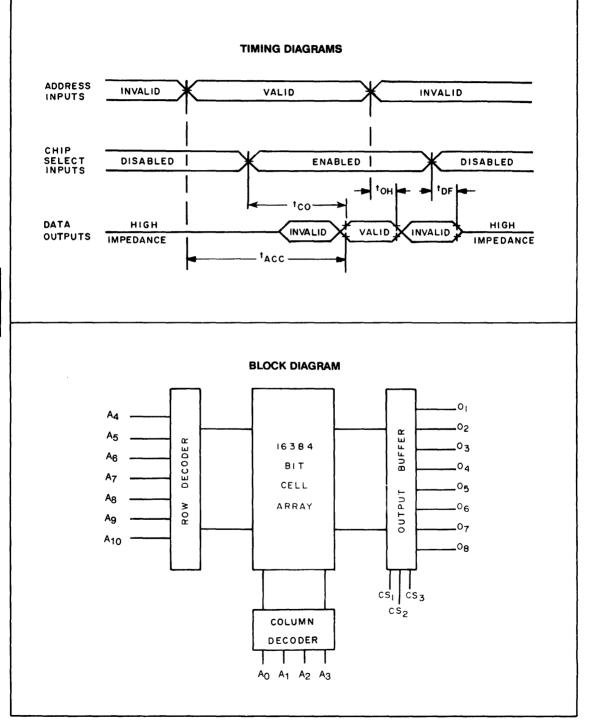

| 23C16  | Static ROM (2048x8)                                | 3-18 |

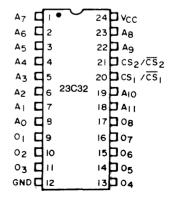

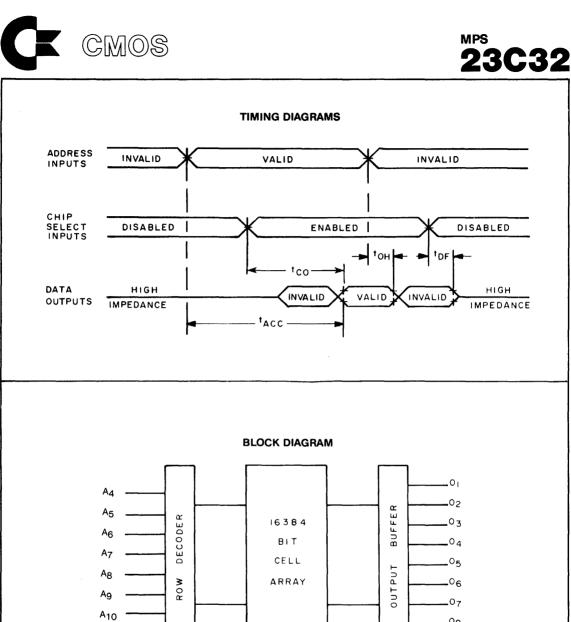

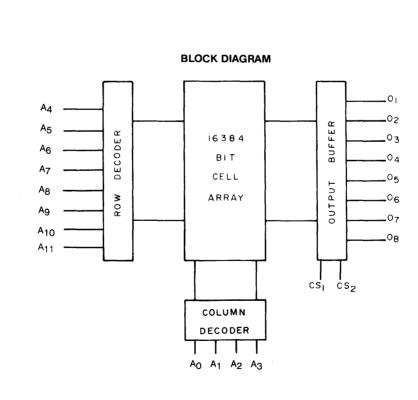

| 23C32  | Static ROM (4096x8)                                | 3-22 |

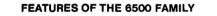

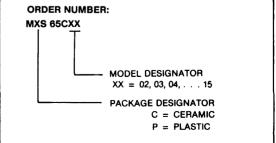

| 65C00  | Microprocessor Family                              |      |

| 65C02  | Microprocessor                                     | 3-10 |

| 65C03  | Microprocessor                                     | 3-10 |

| 65C04  | Microprocessor                                     | 3-10 |

| 65C05  | Microprocessor                                     | 3-10 |

| 65C06  | Microprocessor<br>Microprocessor<br>Microprocessor | 3-11 |

| 65C07  | Microprocessor                                     | 3-11 |

| 65C12  | Microprocessor                                     | 3-11 |

| 65C13  | Microprocessor                                     | 3-12 |

| 65C14  | Microprocessor                                     | 3-12 |

| 65C15  | Microprocessor                                     |      |

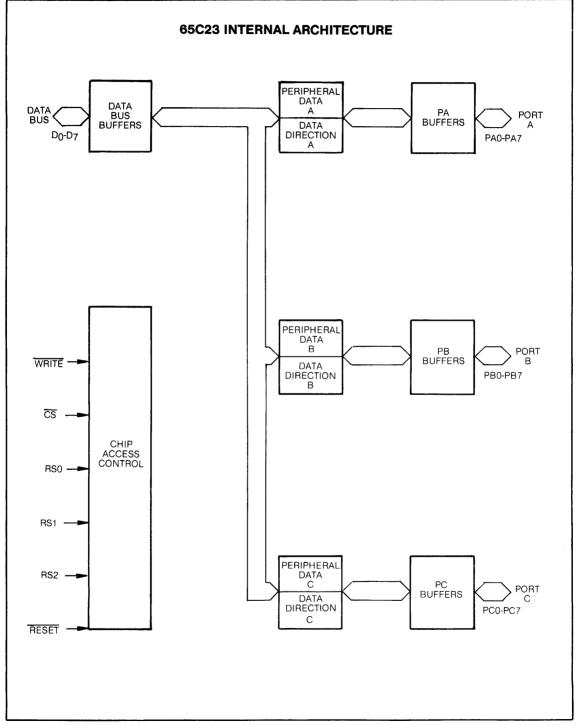

| 65C23  | Tri-Port Interface                                 | 3-13 |

### NUMERICAL INDEX CMOS

| Device | Description Page                                                                                                        | , |

|--------|-------------------------------------------------------------------------------------------------------------------------|---|

| 6600   | Low Power CMOS Remote Control Transmitter                                                                               |   |

| 8223   | 6-Function 3 <sup>1</sup> / <sub>2</sub> -4-Digit Stopwatch, <sup>1</sup> / <sub>2</sub> -Multiplexed LCD Display Drive |   |

| 8268   | 4-Digit 6F Alarm with Snooze, ½ Multiplexed Display Drive                                                               |   |

| 8668   | 5-Function 8-Digit Watch, ½ Multiplexed LCD Display Drive                                                               |   |

| 8868   | 8-Digit 6F Alarm with Snooze, ½ Multiplexed LCD Display                                                                 |   |

| 887X   | 5-Function 8-Digit LCD Alarm Watch 7-Segment Programmable Animation, 1/2 Multiplexed 3-57                               |   |

### NUMERICAL INDEX LCD

#### Page

| Device  | Description                                                                        | Page |

|---------|------------------------------------------------------------------------------------|------|

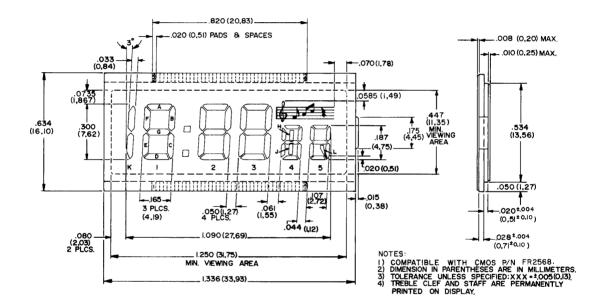

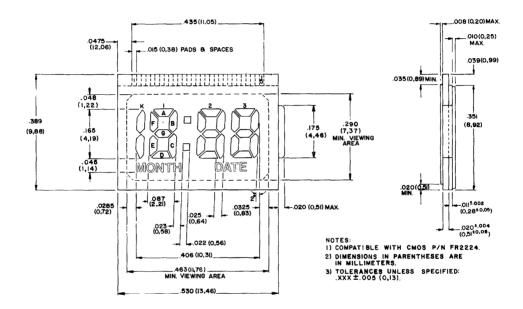

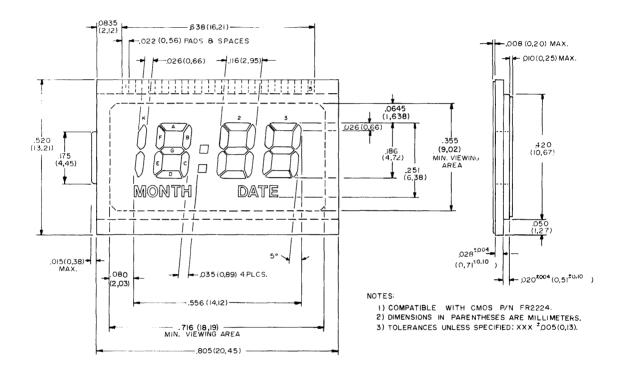

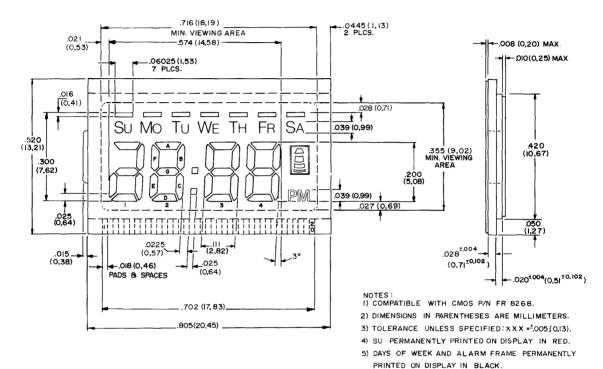

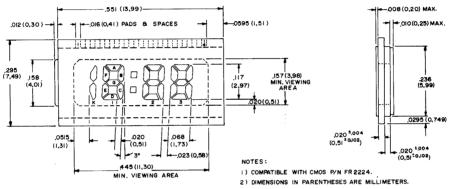

| 5002 K  | 5½ Digit Direct Drive Melody Alarm Clock Display                                   | 4-2  |

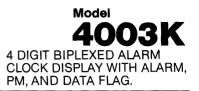

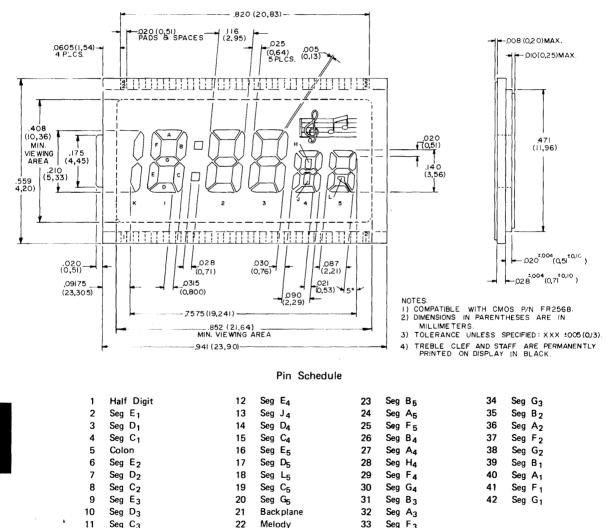

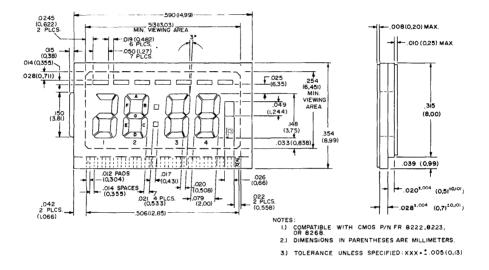

| 4003 K  | 4 Digit Biplexed Alarm Clock Display with Alarm, PM, and Data Flag                 | 4-3  |

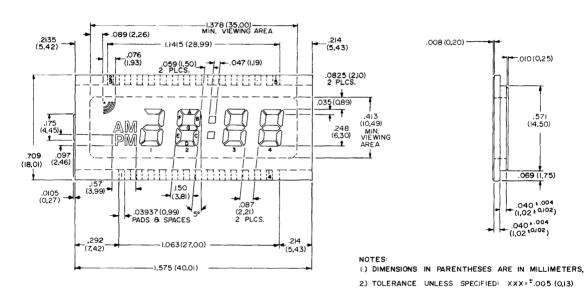

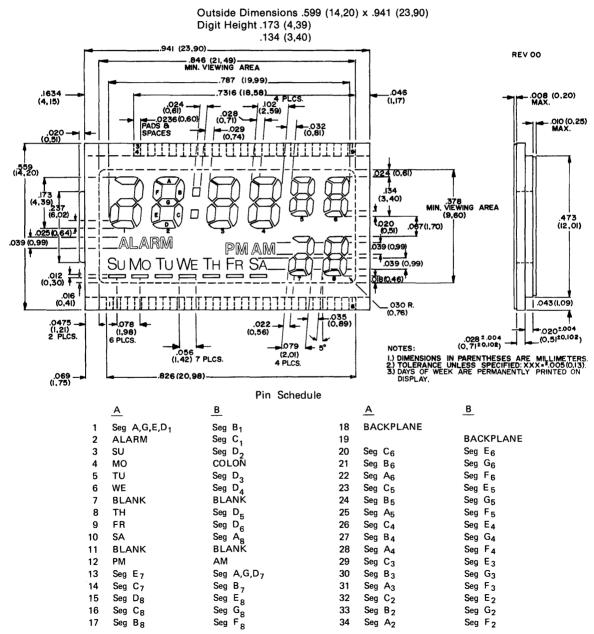

| 4004 L  | 4 Digit Direct Drive Clock Display with Alarm, AM and PM Flags                     | 4-4  |

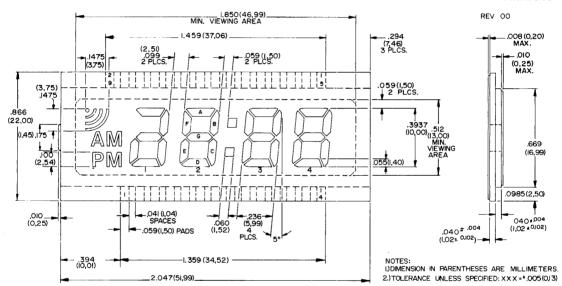

| 4005 N  | 4 Digit Direct Drive Alarm Clock with AM and PM Flags                              |      |

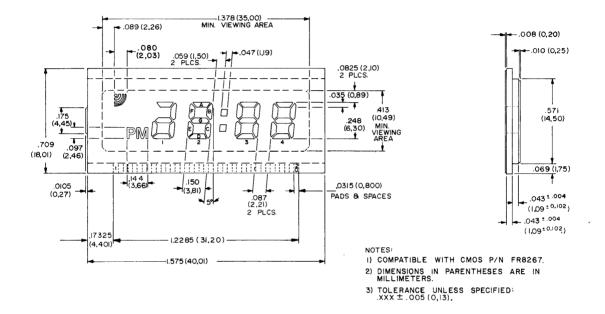

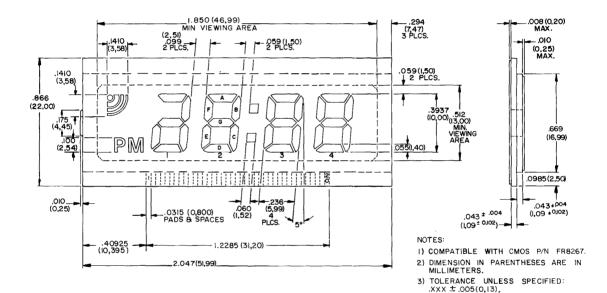

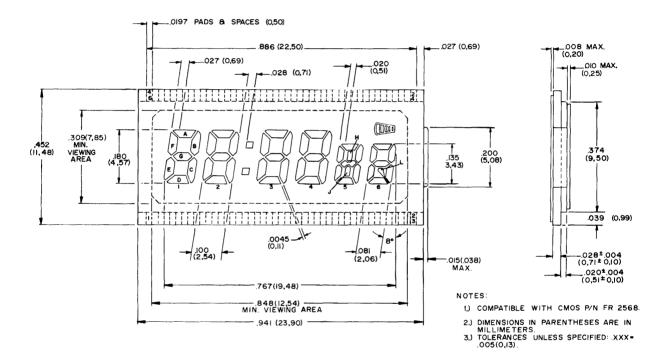

| 4006 L  | 4 Digit Biplexed Clock Display with Alarm and PM Flags                             |      |

| 4007 N  | 4 Digit Biplexed Alarm Clock Display with PM and Alarm Display                     |      |

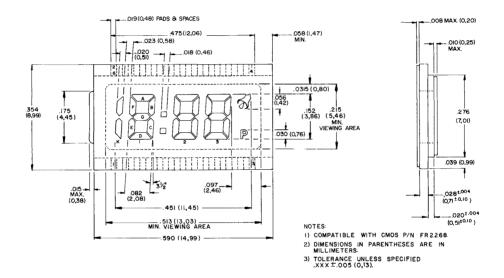

| 5015 F  | Men's 6 Digit Direct Drive Watch Display with Alarm Flags                          | 4-8  |

| 5017 B  | Ladies' 31/2 Direct Drive Watch Display with Alarm and PM Flags                    | 4-9  |

| 5018 E  | Men's 3½ Digit Direct Drive Watch Display with Alarm and PM Flags                  |      |

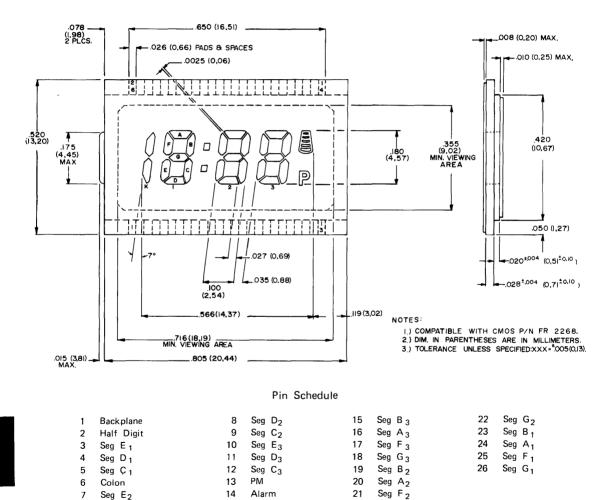

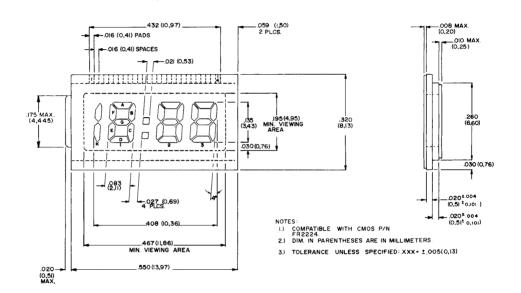

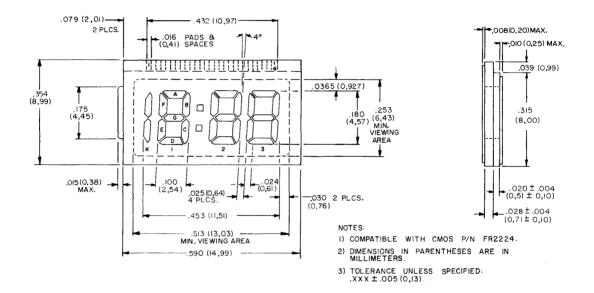

| 5053 BB | Ladies' 31/2 Digit Biplexed Watch Display                                          | 4-11 |

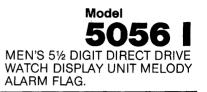

| 5056    | Men's 5½ Digit Direct Drive Watch Display Unit with Melody Alarm Flag              | 4-12 |

| 5060 B  | Ladies' 3½ Digit Biplexed Watch Display                                            | 4-13 |

| 5061 E  | Men's 3½ Digit Biplexed Watch Display                                              | 4-14 |

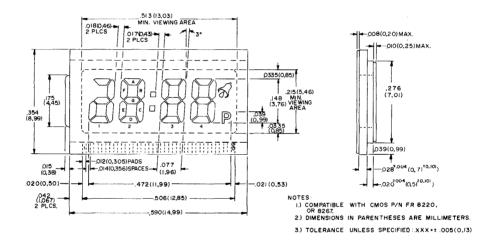

| 5075 A  | 3½ Digit Biplexed Pen Display                                                      | 4-15 |

| 5101 C  | Ladies' 31/2 Large Digit Biplexed Watch Display                                    | 4-16 |

| 5102 E  | Men's Biplexed Watch Display with PM, Alarm and Day Flag                           | 4-17 |

| 5103 C  | Ladies' 4 Digit Biplexed Watch Display with Alarm, PM and Day Flags                |      |

| 51041   | Men's 8 Digit Biplexed Watch Display with AM, PM, Alarm and Day Flags              |      |

| 5107 B  | Ladies' 4 Digit Biplexed Watch Display with Alarm and PM Flags                     | 4-20 |

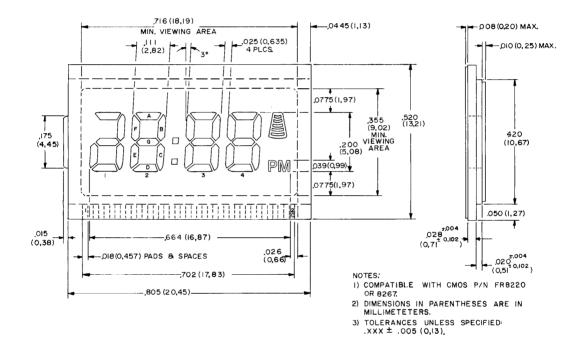

| 5108 E  | Men's Biplexed Watch Display with PM and Alarm Flags                               | 4-21 |

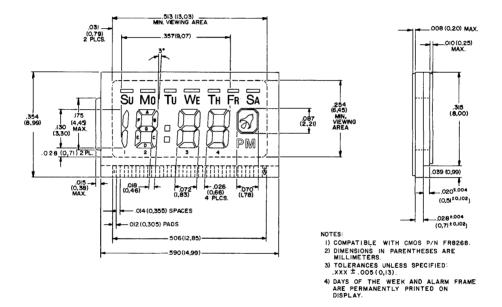

| 5109 C  | Ladies' 3½ Digit Biplexed Watch Display with Alarm, PM and Day Flags               | 4-22 |

| 5111 AA | 3½ Digit Direct Drive Pen Display with Alarm and PM Flags                          | 4-23 |

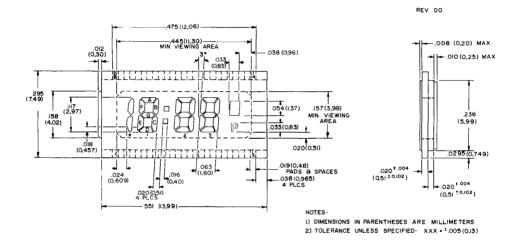

| 5112 AA | 31/2 Digit Biplexed Pen Display with Alarm and PM Flags                            |      |

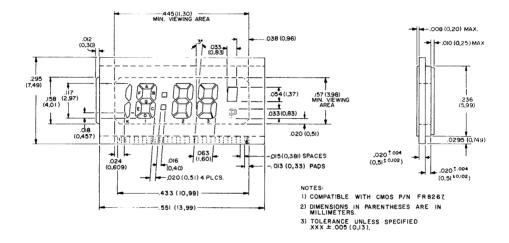

| 5114 AA | 3½ Digit Biplexed Pen Display                                                      |      |

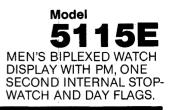

| 5115 E  | Men's Biplexed Watch Display with PM, One Second Interval Stopwatch and Day Flags. | 4-26 |

#

| 1   | . Octal Bus Transceiver, Our Equivalent Asynchronous Two-Way Communicator, |    |

|-----|----------------------------------------------------------------------------|----|

|     | TTL-CMOS Compatible                                                        |    |

| - 2 | 2. MPS 6525 Versus MC6821/82556-3                                          |    |

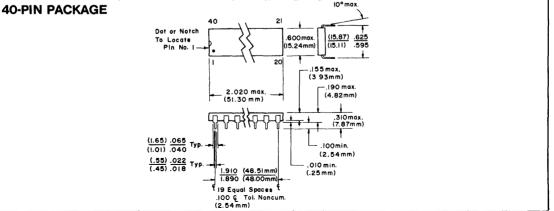

| 3   | 3. Handling the "RDY" Line in 6500 CPUs6-4                                 |    |

| 2   | I. MPS6520 Versus MC6820/MC68216-5                                         |    |

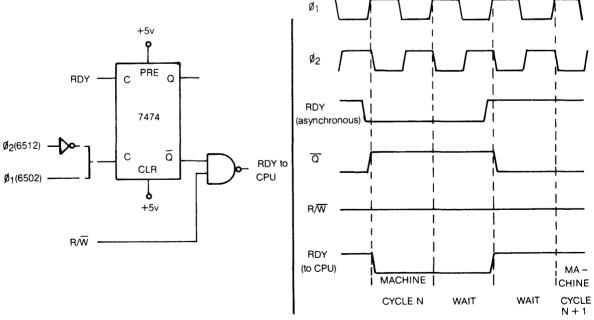

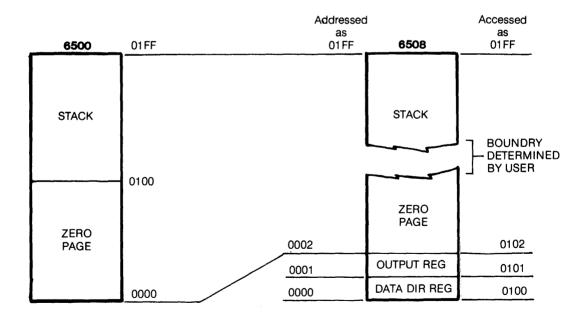

| 5   | 5. Dual Processor Configuration with the MPS65086-6                        |    |

| 6   | 6.7 6551 Versus 6850                                                       |    |

| 7   | 7. Memory Expansion with the 65086-8                                       |    |

| - 6 | 3. MPS 6545-1 Versus Competition6-9                                        | í. |

| ę   | ). MPS 6508 — An "Active" CPU During Block DMA6-1                          | 0  |

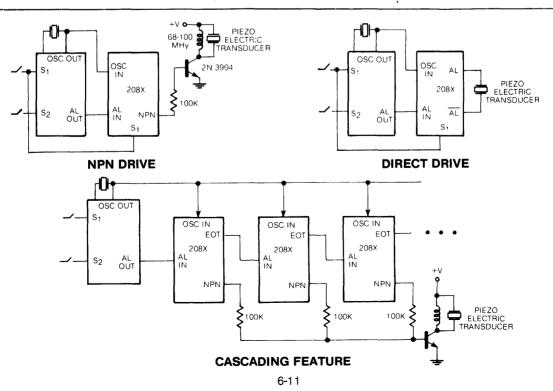

| 10  | ). FR208X — The "Melody" Chip6-1                                           | 1  |

|     |                                                                            |    |

#### **APPLICATION NOTES**

#### Page

| 11. MPS6508 Handling Vectored Interrupts                          | 6-12 |

|-------------------------------------------------------------------|------|

| 12. MPS — A Two in One Deal                                       | 6-13 |

| 13. 6508 RAM — Two Places at Once?                                | 6-14 |

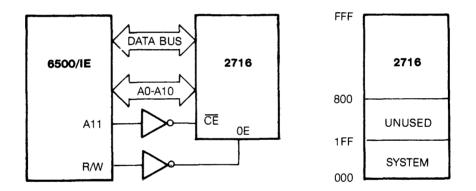

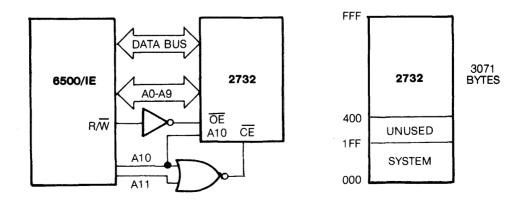

| 14. MPS 6500/IE — EPROM Applications                              |      |

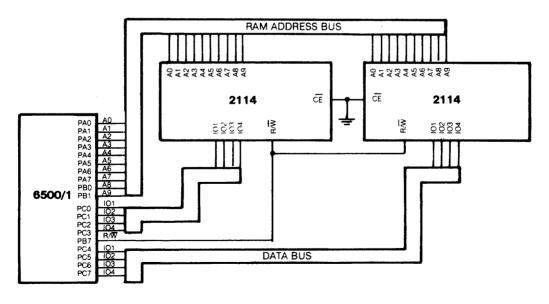

| 15. MPS6500/1 — RAM Memory Expansion                              |      |

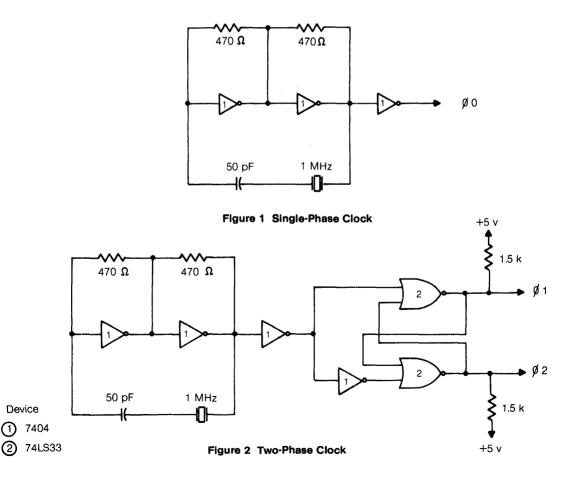

| 16. Simple Clock Generator for the MPS 6500 Microprocessor Family |      |

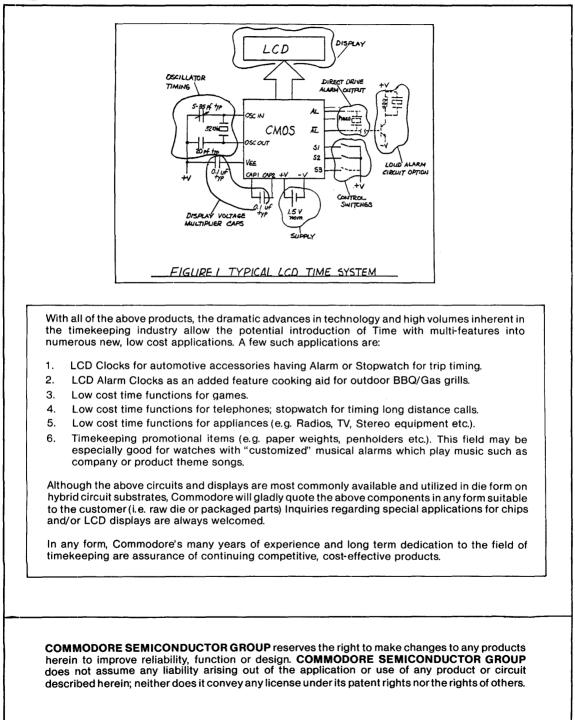

| CMOS/LCD Watch-Clock Circuits                                     |      |

| REPRESENTATIVES AND DISTRIBUTORS                                  |      |

| Representatives                                                   |      |

| Distributors                                                      |      |

### **FUNCTIONAL INDEX NMOS**

| MICROCO | OMPUTERS                                     | Page  |

|---------|----------------------------------------------|-------|

| 6500/1  | Single Chip Microcomputer                    | 2-2   |

| MICROPF | ROCESSORS                                    |       |

| 6500    | Microprocessor Family                        | 2-14  |

| 6502    | Microprocessor                               |       |

| 6503    | Microprocessor                               |       |

| 6504    | Microprocessor                               | 2-22  |

| 6505    | Microprocessor                               | 2-22  |

| 6506    | Microprocessor                               | 2-23  |

| 6507    | Microprocessor                               | 2-23  |

| 6508    | Microprocessor, with RAM and I/O             | 2-25  |

| 6509    | Microprocessor, with Memory Management       | 2-35  |

| 6510    | Microprocessor, with I/O                     |       |

| 6512    | Microprocessor                               |       |

| 6513    | Microprocessor                               |       |

| 6514    | Microprocessor                               | 2-24  |

| 6515    | Microprocessor                               | 2-24  |

| PERIPHE | RALS                                         |       |

| 6520    | Peripheral Adapter                           | 2-46  |

| 6522    | Versatile Interface Adapter (VIA)            | 2-50  |

| 6523    | Tri-Port Interface                           | 2-66  |

| 65245   | Octal Bus Transceiver with 3 State Outputs   | 2-73  |

| 6525    | Tri-Port Interface                           | 2-76  |

| 6526    | Complex Interface Adapter (CIA)              | 2-84  |

| 6529    | Single Port Interface                        | 2-92  |

| 6530    | Memory, I/O, Timer Array                     |       |

| 6532    | Memory, I/O, Timer Array                     | 2-107 |

| 6545-1  | CRT Controller                               | 2-117 |

| 6551    | Asynchronous Communication Interface Adapter | 2-129 |

| ROMs    |                                              |       |

| 2316    | Static ROM (2048x8)                          | 2-137 |

| 2332    | Static ROM (4096x8)                          | 2-141 |

# FUNCTIONAL INDEX NMOSPageBOARDSMMS 6508-1Micromodule Board2-154

## **FUNCTIONAL INDEX CMOS**

| MICROPR | ROCESSORS             | Page |

|---------|-----------------------|------|

| 65C00   | Microprocessor Family |      |

| 65C02   | Microprocessor        |      |

| 65C03   | Microprocessor        |      |

| 65C04   | Microprocessor        |      |

| 65C05   | Microprocessor        |      |

| 65C06   | Microprocessor        |      |

| 65C07   | Microprocessor        |      |

| 65C12   | Microprocessor        |      |

| 65C13   |                       |      |

| 65C14   | Microprocessor        |      |

| 65C15   | Microprocessor        |      |

| PERIPHE |                       |      |

| 65C23   | Tri-Port Interface    |      |

| ROMs    |                       |      |

| 23C16   | Static ROM (2048x8)   |      |

| 23C32   | Static ROM (4096x8)   |      |

۰.

#### REFERENCE GUID Ξ

R6503P

### ROM

| AMD             | Commodore        |

|-----------------|------------------|

| Part No.        | Replacement Part |

| AM9217BPC       | MPS2316          |

| AM9217BDC       | MCS2316          |

| AM9232BPC       | MPS2332          |

| AM9232BDC       | MCS2332          |

| <b>AMI</b>      | Commodore        |

| S68316A         | MPS2316          |

| S68332          | MPS2332          |

| <b>EA</b>       | Commodore        |

| EA2316B         | MPS2316          |

| EA2332          | MPS2332          |

| <b>G.I.</b>     | Commodore        |

| RO-3-9316B      | MPS2316          |

| RO-3-9332B      | MPS2332          |

| Intel           | Commodore        |

| P2316B          | MPS2316          |

| C2316B          | MCS2316          |

| P2332           | MPS2332          |

| C2332           | MCS2332          |

| <b>Motorola</b> | Commodore        |

| MCM68316B       | MPS2316          |

| MCM68332        | MPS2332          |

| <b>National</b> | <b>Commodore</b> |

| MM2316B         | MPS2316          |

| MM52132         | MPS2332          |

| MM52164         | MPS2364          |

| NEC             | <b>Commodore</b> |

| UPD2316B        | MPS2316          |

| UPD2332         | MPS2332          |

| UPD2364         | MPS2364          |

T.L. TMS4732NL TMS4732JL TMS4764NL MPS2364 TMS4764JL

| Mostek     | Commodore |

|------------|-----------|

| MK31000N-3 | MCS2316   |

| MK31000P-3 | MPS2316   |

| MK36000P-5 | MPS2364   |

MK36000N-5 MCS2364

Commodore

MPS2332

MPS2364

MPS2332

MCS2332

MCS2364

Commodore

**Replacement Part**

### MICROPROCESSORS

| Synertek    | Commodore   |

|-------------|-------------|

| SYP=Plastic | MPS=Plastic |

| SYC=Ceramic | MCS=Ceramic |

| SYP/C6502   | MPS/CS6502  |

| SYP/C6503   | MPS/CS6503  |

| SYP/C6504   | MPS/CS6504  |

| SYC/C6505   | MPS/CS6505  |

| SYP/C6506   | MPS/CS6506  |

| SYP/C6507   | MPS/CS6507  |

| SYP/C6512   | MPS/CS6512  |

| SYP/C6513   | MPS/CS6513  |

| SYP/C6514   | MPS/CS6514  |

| SYP/C6515   | MPS/CS6515  |

| A=2MHz      | A=2MHz      |

| B=3MHz      | B=3MHz      |

| SYP/C6502A  | MPS/CS6502A |

| SYP/C6502B  | MPS/CS6502B |

| SYP/C6503A  | MPS/CS6503A |

| SYP/C6503B  | MPS/CS6503B |

| SYP/C6504A  | MPS/CS6504A |

| Synertek<br>Part No. | Commodore<br>Replacement Part |

|----------------------|-------------------------------|

| SYP/C6504B           | MPS/CS6504B                   |

| SYP/C6505A           | MPS/CS6505A                   |

| SYP/C6505B           | MPS/CS6505B                   |

| SYP/C6506A           | •                             |

| SYP/C6506B           | MPS/CS6506A<br>MPS/CS6506B    |

|                      | MPS/CS6506B<br>MPS/CS6507A    |

| SYP/C6507A           | MPS/CS6507B                   |

| SYP/C6507B           |                               |

| SYP/C6512A           | MPS/CS6512A                   |

| SYP/C6512B           | MPS/CS6512B                   |

| SYP/C6513A           | MPS/CS6513A                   |

| SYP/C6513B           | MPS/CS6513B                   |

| SYP/C6514A           | MPS/CS6514A                   |

| SYP/C6514B           | MPS/CS6514B                   |

| SYP/C6515A           | MPS/CS6515A                   |

| SYP/C6515B           | MPS/CS6515B                   |

| SYP6520              | MPS6520                       |

| SYP6520A             | MPS6520A                      |

| SYC6520              | MCS6520                       |

| SYC6520A             | MCS6520A                      |

| SYP6522              | MPS6522                       |

| SYP6522A             | MPS6522A                      |

| SYC6522              | MCS6522                       |

| SYC6522A             | MCS6522A                      |

| SYP6530              | MPS6530                       |

| SYC6530              | MCS6530                       |

| SYP6532              | MPS6532                       |

| SYP6532A             | MPS6532A                      |

| SYC6532              | MCS6532                       |

| SYC6532A             | MCS6532A                      |

| SYP6545-1            | MPS6545-1                     |

| SYC6545-1            | MCS6545-1                     |

| SYP6551              | MPS6551                       |

| SYC6551              | MCS6551                       |

|                      |                               |

| Rockwell             | Commodore                     |

| R6502P               | MPS6502                       |

| R6502AP              | MPS6502A                      |

| R6502C               | MCS6502                       |

| R6502AC              | MCS6502A                      |

MPS6503

# PRODUCT CROSS REFERENCE GUIDE

# MICROPROCESSORS (CONT.)

| Rockwell          | Commodore               | Rockwell     | Commodore             |

|-------------------|-------------------------|--------------|-----------------------|

| Part No.          | <b>Replacement Part</b> | Part No.     | Replacement Part      |

| R6503AP           | MPS6503A                | R6515AC      | MCS6515A              |

| R6503AC           | MCS6503A                | R6520P       | MPS6520               |

| R6504P            | MPS6504                 | R6520AP      | MPS6520A              |

| R6504AP           | MPS6504A                | R6520C       | MCS6520               |

| R6504C            | MCS6504                 | R6520AC      | MCS6520A              |

| R6504AC           | MCS6504A                | R6522P       | MPS6522               |

| R6505P            | MPS6505                 | R6522AP      | MPS6522A              |

| R6505AP           | MPS6505A                | R6522C       | MCS6522               |

| R6505C            | MCS6505                 | R6522AC      | MCS6522A              |

| R6505AC           | MCS6505A                | R6530P       | MPS6530               |

| R6506P            | MPS6506                 | R6530C       | MCS6530               |

| R6506AP           | MPS6506A                | R6532P       | MPS6532               |

| R6506C            | MCS6506                 | R6532AP      | MPS6532A              |

| R6506AC           | MCS6506A                | R6532C       | MCS6532               |

| R6507P            | MPS6507                 | R6532AC      | MCS6532A              |

| R6507AP           | MPS6507A                | R6500/IP     | MPS6500/I             |

| R6507C            | MCS6507                 | R6500/IAP    | MPS6500/IA            |

| R6507AC           | MCS6507A                | R6500/IC     | MCS6500/I             |

| R6512P            | MPS6512                 | R6500/IAC    | MCS6500/IA            |

| R6512AP           | MPS6512A                | R6545-IP     | MPS6545-1             |

| R6512C            | MCS6512                 | R6545-IC     | MCS6545-I             |

| R6512AC           | MCS6512A                | R6551P       | MPS6551               |

| R6513P            | MPS6513                 | R6551C       | MCS6551               |

| R6513AP           | MPS6513A                |              |                       |

| R6513C            | MCS6513                 | Motorola     | Commodore             |

| R6513AC           | MCS6513A                | MC6820       | MPS6520               |

| R6514P            | MPS6514                 | MC6821       | MPS6520               |

| R6514AP           | MPS6514A                | MC68B21      | MPS6520A<br>MPS6545-1 |

| R6514C            | MCS6514                 | MC6845       | MP50545-1             |

| R6514AC           | MCS6514A                |              | Commentance           |

| R6515P<br>R6515AP | MPS6515                 | AMI<br>S6821 | Commodore<br>MPS6520  |

| R6515AP           | MPS6515A<br>MCS6515     | S68B21       | MPS6520               |

| 00100             | 00010                   | 000021       | WIF 3032UA            |

|                   |                         |              |                       |

|                   |                         |              |                       |

|                   |                         |              |                       |

# SECTION 2

# **NMOS** commodore commodora commodora commodore commodore semiconductor gro

# 6500/1 ONE-CHIP MICROCOMPUTER

#### INTRODUCTION

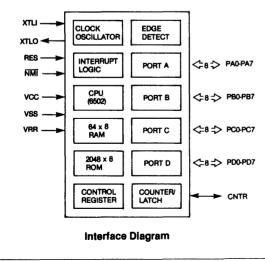

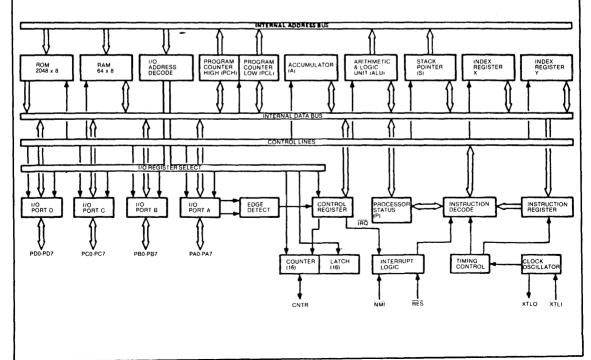

The MOS Technology 6500/1 is a complete, high-performance 8-bit NMOS microcomputer on a single chip, and is totally upward/downward software compatible with all members of the 6500 family.

The 6500/1 consists of a 6502 CPU, an internal clock oscillator, 2048 bytes of Read Only Memory (ROM), 64 bytes of Random Access Memory (RAM) and flexible interface circuitry. The interface circuitry includes a 16-bit programmable counter/latch with four operating modes, 32 bidirectional input/output lines (including two edge-sensitive lines), five interrupts and a counter I/O line.

#### **PRODUCT SUPPORT**

To allow prototype circuit development, Mos Technology offers a PROM compatible 64-pin Emulator device. This device provides all 6500/1 interface lines plus routing the address bus, data bus, and assoclated control lines off the chip to be connected to external memory.

| 0               | RDERING II      | NFORMATIO           |                      |

|-----------------|-----------------|---------------------|----------------------|

| Order<br>Number | Package<br>Type | Frequency<br>Option | Temperature<br>Range |

| MPS6500/1       | Plastic         | 1 MHz               | 0°C to 70°C          |

| MCS6500/1       | Ceramic         | 1 MHz               | 0°C to 70°C          |

| MPS6500/1A      | Plastic         | 2 MHz               | 0°C to 70°C          |

| MCS6500/1A      | Ceramic         | 2 MHz               | 0°C to 70°C          |

| MCS6500/1E E    | mulator De      | vice 1MHz           |                      |

' MCS6500/1EA Emulator Device 2MHz

Note: The RC frequency option is available only in the 1 MHz 6500/1.

#### FEATURES

- 6502 CPU -Software upward/downward compatibility

- -Decimal or binary arithmetic modes

- -13 addressing modes

- -True direct and indirect indexing

- -Memory addressable I/O

- 2048 x 8 mask programmable ROM

- 64 x 8 static RAM

- 32 bi-directional TTL compatible I/O lines (4 ports)

- 1 bi-directional TTL compatible counter I/O line

- 16-bit programmable counter/latch with four modes —Interval Timer —Event Counter

- -Pulse Generator -Pulse Width Measurement

- Five Interrupts

—Reset

—Non-maskable

—Counter

- 1 of 3 frequency references —Crystal —Clock —RC (resistor only)

- · 4 MHz max crystal or clock external frequency

- 2 MHz or 1 MHz internal clock

- 1 µs minimum instruction execution

- N-channel, silicon gate, depletion load technology

- Single + 5V power supply

- 500 mW operating power

- · Separate power pin for RAM

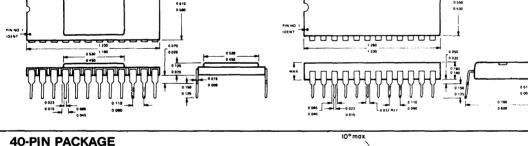

- 40 pin DIP

- 64 pin PROM compatible Emulator device

# MPS 6500/1

#### FUNCTIONAL DESCRIPTION

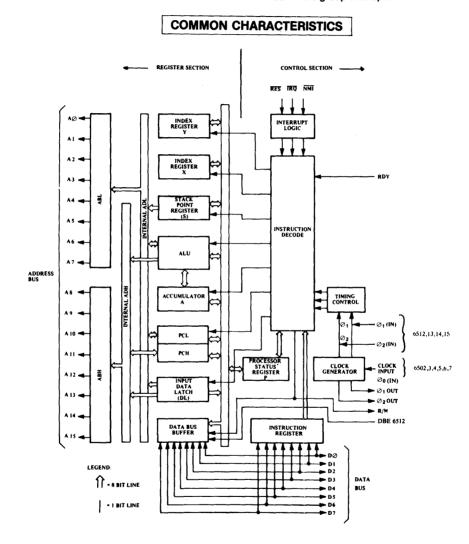

#### **CENTRAL PROCESSING UNIT (CPU)**

#### **Clock Oscillator**

The Clock Oscillator provides the basic timing signals used by the 6500/1 CPU. The reference frequency is provided by an external source, and can be from a crystal, clock or RC network input. The RC network mode is a mask option. The external frequency can vary from 200 kHz to 4 MHz. The internal Phase 2 ( $\emptyset$ 2) frequency is one-half the external reference frequency. A 4.7K ohm resistor will provide nominal 2 MHz oscillation and 1 MHz internal operation in the RC mask option ( $\pm$ 35%).

#### **Timing Control**

The Timing Control Logic keeps track of the specific instruction cycle being executed. Each data transfer which takes place between the registers is caused by decoding the contents of both the instruction Register and Timing Control Logic.

#### **Program Counter**

The 16-bit Program Counter provides the addresses which step the CPU through sequential instructions in a program. The Program Counter is incremented each time an instruction or data is fetched from memory.

#### Instruction Register and Decode

Instructions fetched from memory are gated onto the Internal Data Bus. These instructions are latched into the Instruction Register then decoded, along with timing and interrupt signals, to generate control signals for the various registers.

#### Arithmetic and Logic Unit (ALU)

All arithmetic and logic operations take place in the ALU, including incrementing and decrementing internal registers (except the Program Counter).

#### Accumulator

The accumulator is a general purpose 8-bit register that stores the results of most arithmetic and logic operations. In addition, the accumulator usually contains one of the two data words used in these operations.

#### **Index Registers**

There are two 8-bit index registers, X and Y. These registers can be used for general purpose storage, or as a displacement to modify the base address and thus obtain a new effective address. Pre- or post-indexing of indirect addresses is possible.

#### Stack Pointer

The Stack Pointer is an 8-bit register. It is automatically incremented and decremented under control of the CPU to perform stack manipulation under direction of either the program or interrupts NMI and IRQ. The stack allows simple implementation of nested subroutines and multiple level interrupts.

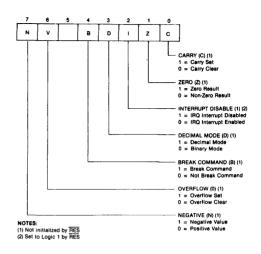

#### **Processor Status Register**

#### **Processor Status Register**

The 8-bit Processor Status Register contains seven status flags. Some of the flags are controlled by the program, others may be controlled both by the program and the CPU. The 6500 instruction set contains a number of conditional branch instructions which are designed to allow testing of these flags.

#### Interrupt Logic

Interrupt logic controls the sequencing of three interrupts; RES, NMI and IRQ. IRQ is generated by any one of three conditions: Counter Overflow, PAO Positive Edge Detected, and PA1 Negative Edge Detected.

#### MEMORY

#### 2048 x 8 ROM

The 2048 byte Read-Only Memory (ROM) contains the program instructions and other fixed constants. These program instructions and constants are mask programmed into the ROM during fabrication of the 6500/1 device. The 6500/1 ROM is memory mapped from 800 to FFF.

#### 64 x 8 RAM

The 64 byte Random Access Memory (RAM) is used for read/write memory during system operation, and contains the stack. This RAM is completely static in operation and requires no clock or dynamic refresh. A standby power pin, VRR, allows RAM memory to be maintained on 10% of the operating power in the event that VCC power is lost.

In order to take advantage of efficient zero page addressing capabilities, the RAM is assigned memory addresses 0 to 03F.

NMOS

#### INPUT/OUTPUT

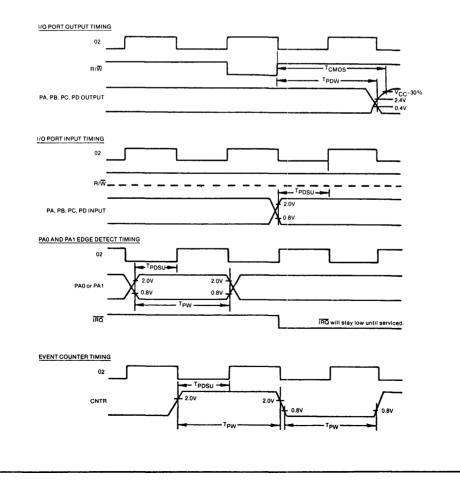

#### **Bidirectional I/O Ports**

The 6500/1 provides four 8-bit input/output ports (PA, PB, PC, and PD). Associated with the I/O ports are four 8-bit registers located on page zero. See the system memory map for specific addresses. Each I/O line is individually selectable as an input or an output without line grouping or port association restrictions.

An internal active transistor drives each I/O line to the low state. An internal passive resistance pulls the I/O lines to the high state, eliminating the need for external pull-up resistors.

An option is available to delete the internal pull-up resistance on 8-bit port groups or on the CNTR line at mask time. This option is employed to permanently assign an 8-bit port group to input functions, to interface with CMOS drivers, or to interface with external pull-up devices.

#### Inputs

Inputs are enabled by setting the appropriate bit of the I/O port to the high state (Logic 1). A low input signal causes a logic 0 to be read. A high input signal causes a logic 1 to be read. RES loads Logic 1 into the I/O ports, thereby initializing all I/O lines as inputs.

#### Outputs

Outputs are set by loading the desired bit pattern into the corresponding I/O ports. A Logic 1 selects a high output; a Logic 0 selects a low output.

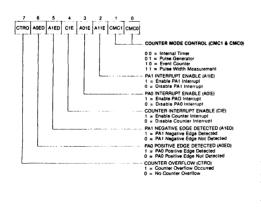

#### CONTROL REGISTER

The Control Register (CR) controls four Counter operating modes and three maskable interrupts. It also reports the status of three interrupt conditions. There are five control bits and three status bits. The control bits are set to Logic 1 or cleared to Logic 0 by writing the desired state into the respective bit positions. The Control Register is cleared to Logic 0 by the occurrence of RES.

**Control Register**

#### **EDGE DETECT CAPABILITY**

There is an asynchronous edge detect capability on two of the Port A I/O lines. This capability exists in addition to and independently from the normal Port A I/O functions. The maximum rate at which an edge can be detected is one-half the  $\oslash 2$  clock rate. The edge detect logic is continuously active. Each edge detect signal is associated with a maskable interrupt.

#### **PA0 Positive Edge Detection**

A positive (rising) edge is detectable on PA0. When this edge is detected, the PA0 Positive Edge Detected bit—Bit 6 in the Control Register—is set to Logic 1. When both this bit and the PA0 Interrupt Enable Bit—Bit 3 of the Control Register—are set to Logic 1, an IRQ interrupt request is generated. The PA0 Positive Edge Detected bit is cleared by writing to address 089.

#### PA1 Negative Edge Detection

A negative (failing) edge is detectable on PA1. When this edge is detected, the PA1 Negative Edge Detected bit—Bit 5 of the Control Register—is set to Logic 1. When both this bit and the PA1 Interrupt Enable bit—Bit 2 of the Control Register—are set to Logic 1, an IRQ Interrupt request is generated. The PA1 Negative Edge Detected bit is cleared by writing to address 08A.

#### COUNTER/LATCH

The Counter/Latch consists of a 16-bit decrementing Counter and a 16-bit Latch. The Counter is comprised of two 8-bit registers. Address 086 contains the Upper Count (UC) and address 087 contains the Lower Count (LC). The Counter counts either Ø2 clock periods or occurrences of an external event, depending on the selected counter mode. The UC and LC can be read at any time without affecting counter operation.

The Latch contains the Counter preset value. The Latch consists of two 8-bit registers. Address 084 contains the Upper Latch (UL) and address 085 contains the lower latch (LL). The 16-bit Latch can hold a count from 0 to 65,535. The Latch can be accessed as two write-only memory locations.

The Latch registers can be loaded at any time by storing into UL and LL. The UL can also be loaded by writing into address 088.

The Counter can be preset at any time by writing to address 088. Presetting the Counter in this manner causes the contents of the accumulator to be stored into the UL before the 16-bit value in the Latch (UL and LL) is transferred in the Counter (UC and LC).

The Counter is preset to the Latch value when the Counter overflows. When the counter decrements from 0000, Counter overflow occurs causing the next counter value to be the Latch value, not FFFF.

When the Counter overflows, Counter Overflow bit—Bit 7 of the Control Register—is set to Logic 1. When both this bit and the Counter Interrupt Enable bit—Bit 4 of the Control Register—are set, an IRQ interrupt request is generated. The Counter Overflow bit in the Control Register can be examined in an IRQ interrupt service routine to determine that the IRQ was generated by Counter overflow.

MMO

The Counter Overflow bit is cleared when the LC is read or Counter preset is performed by writing into address 088.

#### **COUNTER MODES**

The Counter operates in any of four modes. These modes are selected by the Counter Mode Control bits in the Control Register.

| Mode                    | CMC 1 | CMC 0 |

|-------------------------|-------|-------|

| Interval Timer          | 0     | 0     |

| Pulse Generator         | 0     | 1     |

| Event Counter           | 1     | 0     |

| Pulse Width Measurement | 1     | 1     |

The Interval Timer, Pulse Generator, and Pulse Wildth Measurement Modes are  $\oslash 2$  clock counter modes. The Event Counter Mode counts the occurrences of an external event on the CNTR line.

#### Interval Timer (Mode 0)

In this mode the Counter is free running and decrements at the  $\oslash 2$  clock rate. Counter overflow sets the Control Register status bit and causes the Counter to be preset to the Latch value.

The CNTR line is held in the high state.

#### Pulse Generator (Mode 1)

In this mode the Counter is free running and decrements at the  $\oslash 2$  clock rate. Counter overflow sets the Control Register status bit and causes the Counter to be preset to the Latch value.

The CNTR line toggles from one state to the other when Counter overflow occurs. Writing to address 088 will also toggle the CNTR line.

A symmetric or asymmetic output waveform can be generated on the CNTR line in this mode. A oneshot waveform can easily be generated by changing from Mode 1 to Mode 0 after only one occurrence of the output toggle condition.

#### Event Counter (Mode 2)

In this mode the CNTR line is used as an event input line. The Counter decrements each time a rising edge is detected on CNTR. The maximum rate at which this edge can be detected is one-half the  $\oslash 2$ clock rate. Counter overflow sets the Control Register status bit and causes the Counter to be preset to the Latch value.

#### Pulse Width Measurement (Mode 3)

This mode allows the accurate measurement of the duration of a low state on the CNTR line. The Counter decrements at the  $\emptyset$ 2 clock rate as long as the CNTR line is held in the low state. The Counter is stopped when CNTR is in the high state. If the CNTR pin is left disconnected, this mode may be selected to stop the Counter since the internal pull-up device will cause the CNTR input to be in the high state.

#### **RESET CONSIDERATIONS**

The occurrence of RES going from low to high causes initialization of various conditions in the 6500/1. All of the I/O ports (PA, PB, PC, and PD) and

CNTR are forced to the high (Logic 1) state. All bits of the Control Register are reset to Logic 0, causing the Interval Timer Mode (Mode 0) to be selected and all interrupt enabled bits to be cleared. Neither the Latch nor the Counter registers are initialized by RES. The Interrupt Disable bit in the CPU Processor Status Register is set and the program starts execution at the address contained in the Reset Vector location.

MPS

6500/1

#### **TEST LOGIC**

Special test logic provides a method for thoroughly testing the 6500/1. Applying a + 10V signal to the RES line places the 6500/1 in the test mode. While in this mode, all memory fetches are made from Port PC. External test equipment can use this feature to test internal CPU logic and I/O. A program can be loaded into RAM allowing the contents of the instruction ROM to be dumped to any port for external verification.

All 6500/1 microcomputers are tested by MOS Technology using this feature.

#### MEMORY ADDRESSABLE I/O

The I/O ports, registers, and commands are treated as memory and are assigned specific addresses. See the system memory map for the addresses. This I/O technique allows the full set of CPU instructions to be used in the generation and sampling of I/O commands and data. When an instruction is executed with an I/O address and appropriate R/W state, the corresponding I/O function is performed.

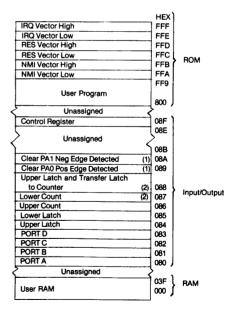

#### SYSTEM MEMORY MAP

#### Notes:

(1) I/O command only; i.e., no stored data.

(2) Clears Counter Overflow-Bit 7 in Control Register.

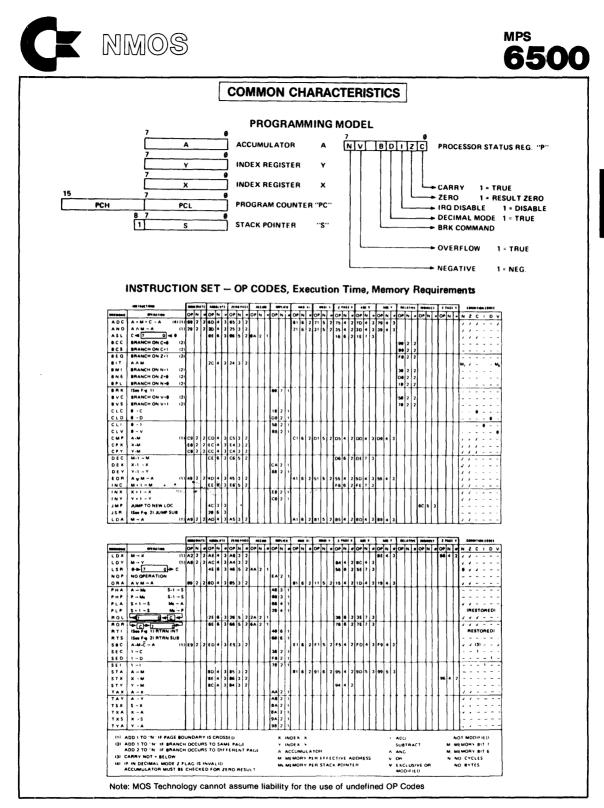

#### INSTRUCTION SET-ALPHABETIC SEQUENCE

- ADC Add Memory to Accumulator with Carry

- AND "AND" Memory with Accumulator ASL Shift Left One Bit (Memory or Accumulator)

- ASL Shift Left One Bit (Memory of Accu

- BCC Branch on Carry Clear BCS Branch on Carry Set

- BEO Branch on Result Zero

- BIT Test Bits in Memory with Accumulator

- BMI Branch on Result Minus

- BNE Branch on Result not Zero

- BPL Branch on Result Plus

- BRK Force Break

- BVC Branch on Overflow Clear

- BVS Branch on Overflow Set

- CLC Clear Carry Flag

- CLD Clear Decimal Mode

- CLI Clear Interrupt Disable Bit

- CLV Clear Overflow Flag

- CMP Compare Memory and Accumulator

- CPX Compare Memory and Index X

- CPY Compare Memory and Index Y

- DEC Decrement Memory by One

- DEX Decrement Index X by One

- DEY Decrement Index Y by One

- EOR "Exclusive-or" Memory with Accumulator

- INC Increment Memory by One

- INX Increment Index X by One

- INY Increment Index Y by One

- JMP Jump to New Location

- JSR Jump to New Location Saving Return Address

- LDA Load Accumulator with Memory

- LDX Load Index X with Memory LDY Load Index Y with Memory

- LDY Load Index Y with Memory LSR Shift One Bit Right (Memory or Accumulator)

- NOP No operation

- ORA "OR" Memory with Accumulator

- PHA Push Accumulator on Stack

- PHP Push Processor Status on Stack

- PLA Pull Accumulator from Stack

- PLP Pull Processor Status from Stack

- ROL Rotate One Bit Left (Memory or Accumulator) ROR Rotate One Bit Right (Memory or

- Accumulator)

- RTI Return from Interrupt

- RTS Return from Subroutine

- SBC Subtract Memory from Accumulator with Borrow

- SEC Set Carry Flag

- SED Set Decimal Mode

- SEI Set Interrupt Disable Status

- STA Store Accumulator in Memory

- STX Store Index X in Memory

- STY Store Index Y in Memory

- TAX Transfer Accumulator to Index X

- TAY Transfer Accumulator to Index Y

- TSX Transfer Stack Pointer to Index X

- TXA Transfer Index X to Accumulator

- TXS Transfer Index X to Stack Register

- TYA Transfer Index Y to Accumulator

# <sup>MPS</sup> 6500/1

#### SIGNAL DESCRIPTIONS

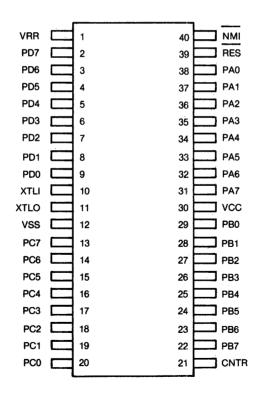

| SIGNAL<br>NAME | Pin<br>NO. | DESCRIPTION                                                                                                                                                                                                                 |

|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCC            | 30         | Main power supply + 5V                                                                                                                                                                                                      |

| VRR            | 1          | Separate power pin for RAM. In the<br>event that VCC power is lost, this<br>power retains RAM data.                                                                                                                         |

| VSS            | 12         | Signal ground                                                                                                                                                                                                               |

| XTLI           | 10         | Crystal, clock or RC network input<br>for internal clock oscillator.                                                                                                                                                        |

| XTLO           | 11         | Crystal or RC network output from<br>internal clock oscillator.                                                                                                                                                             |

| RES            | 39         | The Reset input is used to initialize<br>the 6500/1. This signal must not<br>transition from low to high for at<br>least eight cycles after VCC<br>reaches operating range and the in-<br>ternal oscillator has stabilized. |

+ 10V input enables the test mode.

| SIGNAL<br>NAME | PIN<br>NO.         | DESCRIPTIÖN                                                                                                                                                                                                    |

|----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMI            | 40                 | A negative going edge on the Non-<br>Maskable Interrupt signal requests<br>that a non-maskable interrupt be<br>generated within the CPU.                                                                       |

| PA0-PA7        | 38-31              | Four 8 bit ports used for either                                                                                                                                                                               |

| PB0-PB7        | 2 <del>9</del> -22 | input/öutput. Each line consists<br>of an active transistor to VSS and                                                                                                                                         |

| PC0-PC7        | 20-13              | a passive pull-up to +5V. The two                                                                                                                                                                              |

| PD0-PD7        | 9-2                | lower bits of the PA port (PA0 and<br>PA1) also serve as edge detect in-<br>puts with maskable interrupts.                                                                                                     |

| CNTR           | 21                 | This line is used as a Counter in-<br>put/output line. CNTR is an input in<br>the Event Counter and Pulse Width<br>Measurement modes and is an out-<br>put in the Interval Timer and Pulse<br>Generator modes. |

**Pin Configuration**

NMOS

#### ADDRESSING MODES

ACCUMULATOR ADDRESSING—This form of addressing is represented with a one byte instruction, implying an operation on the accumulator.

IMMEDIATE ADDRESSING—In immediate addressing, the operand is contained in the second byte of the instruction, with no further memory addressing required.

ABSOLUTE ADDRESSING—In absolute addressing, the second byte of the instruction specifies the eight low order bits of the effective address while the third byte specifies the eight high order bits.

ZERO PAGE ADDRESSING—The zero page instructions allow for shorter code and execution times by only fetching the second byte of the instruction and assuming a zero high address byte. Careful use of the zero page can result in significant increase in code efficiency.

INDEXED ZERO PAGE ADDRESSING —(X, Y indexing) — This form of addressing is used in conjunction with the index register and is referred to as "Zero Page, X" or "Zero Page, Y." The effective address is calculated by adding the second byte to the contents of the index register. Since this is a form of "Zero Page" addressing, the content of the second byte references a location in page zero. Additionally due to the "Zero Page" addressing nature of this mode, no carry is added to the high order 8 bits of memory and crossing of page boundaries does not occur.

INDEXED ABSOLUTE ADDRESSING —(X, Y indexing)—This form of addressing is used in conjunction with X and Y index register and is referred to as "Absolute, X", and "Absolute, Y." The effective address is formed by adding the contents of X or Y to the address contained in the second and third bytes of the instruction. This mode allows the index register to contain the index or count value and the instruction to contain the base address. This type of indexing allows any location referencing and the index to modify multiple fields resulting in reduced coding and execution time. **IMPLIED ADDRESSING**—In the implied addressing mode, the address containing the operand is implicitly stated in the operation code of the instruction.

**RELATIVE ADDRESSING**—Relative addressing is used only with branch instructions and establishes a destination for the conditional branch.

The second byte of the instruction becomes the operand which is an "Offset" added to the contents of the lower eight bits of the program counter when the counter is set at the next instruction. The range of the offset is -128 to +127 bytes from the next instruction.

INDEXED INDIRECT ADDRESSING—In indexed indirect addressing (referred to as [indirect, X]), the second byte of the instruction is added to the contents of the X index register, discarding the carry. The result of this addition points to a memory location on page zero whose contents is the low order eight bits of the effective address. The next memory location in page zero contains the high order eight bits of the effective address. Both memory locations specifying the high and low order bytes of the effective address.must be in page zero.

INDIRECT INDEXED ADDRESSING—In indirect indexed addressing (referred to as [Indirect, Y]), the second byte of the instruction points to a memory location in page zero. The contents of this memory location are added to the contents of the Y index register, the result being the low order eight bits of the effective address. The carry from this addition is added to the contents of the next page zero memory location, the result being the high order eight bits of the effective address.

ABSOLUTE INDIRECT—The second byte of the instruction contains the low order eight bits of a memory location. The high order eight bits of that memory location are contained in the third byte of the instruction. The contents of the fully specified memory location are the low order byte of the effective address. The next memory location contains the high order byte of the effective address which is loaded into the sixteen bits of the program counter.

# <sup>MPS</sup> 6500/1

#### INSTRUCTION SET

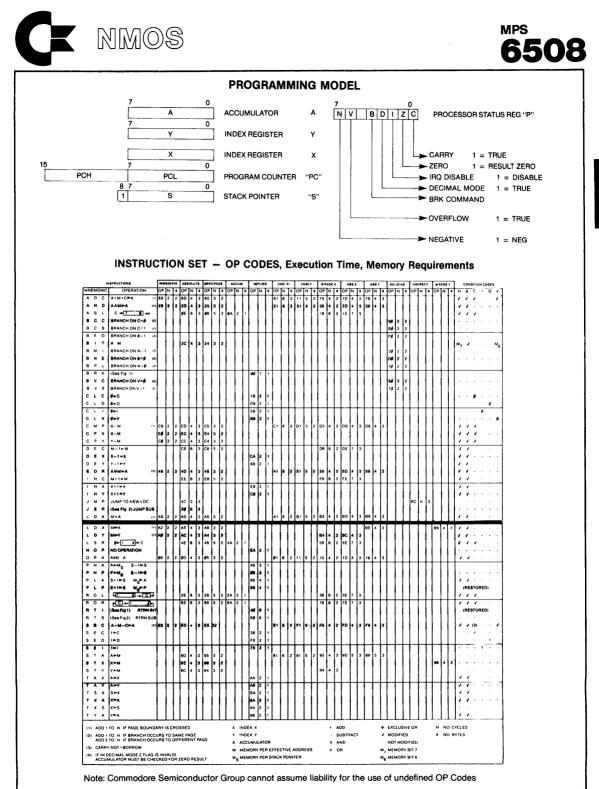

#### **INSTRUCTION SET - OP CODES, Execution Time, Memory Requirements**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10513-0CT+045                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | · · · ·                                                                     |                          | -                                                                                                                                                  | -                   | <b>T</b>                                                                                    | h                                                                                             |                                         | -                                                                                           | +                 | T     | -   |                                                                                                    | - T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | +        | -                        | -         | -                       | 17       |                                                            | -                                                    |      |                                                                                                                   | 1                 |                                 |                        | -           | -           | -   |          | _   | _       |    | _  | _   |     | -                       |                   |                                                                                        |   |                                                                                                 |                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------|-------------------|-------|-----|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------|-----------|-------------------------|----------|------------------------------------------------------------|------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------|------------------------|-------------|-------------|-----|----------|-----|---------|----|----|-----|-----|-------------------------|-------------------|----------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

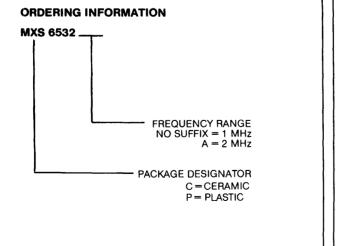

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OPLEATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | OP                                                                          |                          |                                                                                                                                                    | N                   |                                                                                             |                                                                                               | N                                       |                                                                                             |                   | N     | 1   | OP                                                                                                 | N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | +        | PN                       |           |                         |          | _                                                          | PN                                                   | -    |                                                                                                                   | N                 |                                 | 0₽                     |             |             | 0₽  | N        | -   | 0       | N  | -  | OP  | N   | •                       | N                 | Z                                                                                      | с | <u> </u>                                                                                        | D                                                                                                |