# MEMORY DATA BOOK

8000 S. Federal Way P.O. Box 6 Boise, Idaho 83707-0006 Telephone: 208-368-3900 Fax: 208-368-4617 E-mail: prodmktg@micron.com Internet: www.micron.com/mti Customer Comment Line: U.S.A. 800-932-4992

Fax 01-208-368-5018

©1999, Micron Technology, Inc. Printed in the U.S.A.

Micron Technology, Inc., reserves the right to change products or specifications without notice.

| M | I |        | N          |  |

|---|---|--------|------------|--|

|   |   | TECHNO | LOGY, INC. |  |

| DRAM                          | 1 |

|-------------------------------|---|

|                               | 2 |

|                               | 3 |

| TECHNICAL NOTES               | 4 |

| PRODUCT RELIABILITY           | 5 |

| PACKAGE INFORMATION           | 6 |

| SALES AND SERVICE INFORMATION | 7 |

reface ev. 2/99

#### i

####

\*The 8 Meg x 8 DDR SDRAM data sheet is found in the DDR/SLDRAM/RDRAM section.

#### SGRAM

SDRAM

| MT41LC256K32D4 25                                                              | 56K x 32 3.3  | 3V, SDR   | 1-51      |

|--------------------------------------------------------------------------------|---------------|-----------|-----------|

| MT45V512K32 51                                                                 | 2K x 32** 2.5 | 5V, DDR   | 1-1       |

| MT48LC2M32B2 2 M                                                               |               |           |           |

| DDR Double                                                                     | Data Rate SD  | OR Single | Data Rate |

| **The 512K x 32 DDR SGRAM data sheet is found in the DDR/SLDRAM/RDRAM section. |               |           |           |

General Information

<sup>†</sup>The 2 Meg x 32 SDRAM data sheet is found in the SDRAM section.

| DDR/SLDRAM/RDRAM |

|------------------|

|                  |

| MT46V16M4   |            |

|-------------|------------|

| MT46V32M4   |            |

| MT46V64M4   | 64 Meg x 4 |

| MT46V8M8    | 8 Meg x 8  |

| MT46V16M8   |            |

| MT46V32M8   |            |

| MT46V4M16   |            |

| MT46V8M16   | 8 Meg x 16 |

| MT46V16M16  |            |

| MT6V8M18    |            |

| MT49V8M18C  |            |

| MT45V512K32 |            |

| MT46V2M32   |            |

|             |            |

MT48LC32M4A2 ...... 32 Meg x 4 MT48LC32M8A2 ...... 32 Meg x 8 MT48LC1M16A1 S ..... 1 Meg x 16 MT48LC4M16A2..... 4 Meg x 16 MT48LC8M16A2 ...... 8 Meg x 16 MT48LC16M16A2 ..... 16 Meg x 16

#### 2.5V, DDR SDRAM ..... 1-3 2.5V, DDR SDRAM ..... 1-7 2.5V, DDR SDRAM ..... 1-9 2.5V, DDR SDRAM ..... 1-3 2.5V, DDR SDRAM ..... 1-7 2.5V. DDR SDRAM ...... 1-9 2.5V, DDR SDRAM ..... 1-3 2.5V, DDR SDRAM ..... 1-7 2.5V, DDR SDRAM ..... 1-9 2.5V, RDRAM ...... 1-13 2.5V, SLDRAM ..... 1-11 2.5V, DDR SGRAM ...... 1-1 2.5V, DDR SDRAM ..... 1-5

#### PAGE

PAGE

| 4KR                                | 1-17   |

|------------------------------------|--------|

| 4KR                                | 1-25   |

| 8KR                                | 1-33   |

| 4KR                                | 1-17   |

| 4KR, 2.5V I/O                      | 1-3    |

| 4KR                                | 1-25   |

| 8KR                                | 1-33   |

| 2KR, 4KR, S                        | 1-41   |

| 4KR                                | 1-17   |

| 4KR                                | 1-25   |

| 8KR                                | 1-33   |

| 4KR                                | 1-45   |

| 4KR                                | efresh |

| S Optional Self Refresh on 16Mb SD | RAMs   |

| (all other SDRAMs have Self Re     | fresh) |

PREFACE

#### PAGE Table of Contents ..... i viii

#### EDO DRAM

| MT4LC16M4G3     | 16 Meg x 4    |

|-----------------|---------------|

| MT4LC16M4G3 S   | 16 Meg x 4    |

| MT4LC16M4H9     | 16 Meg x 4    |

| MT4LC16M4H9 S   | 16 Meg x 4    |

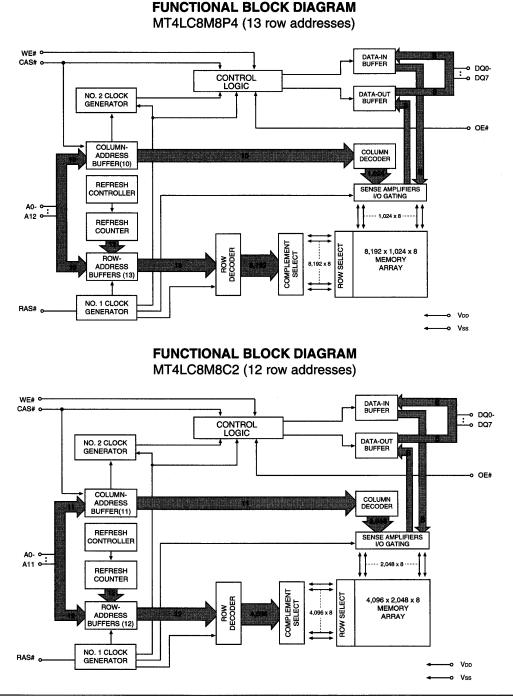

| MT4LC8M8P4      | 8 Meg x 8     |

| MT4LC8M8P4 S    | 8 Meg x 8     |

| MT4LC8M8C2      |               |

| MT4LC8M8C2 S    |               |

| MT4LC4M16R6     |               |

| MT4LC4M16R6 S   | 4 Meg x 16    |

| EDO<br>4KR<br>S | 4,096 Refresh |

| -               |               |

#### EDO, 8KR 1-55 1-55 EDO, 4KR ..... EDO, 4KR, S.... 1-55EDO, 8KR 1-59EDO, 8KR, S ..... 1-59 EDO, 4KR ..... 1-59 EDO, 4KR, S..... 1-59 EDO, DC, 4KR ..... 1-63 EDO, DC, 4KR, S 1-63 DC 8KR .....

#### FPM DRAM

| MT4LC16M4A7   | 16 Meg x 4    |

|---------------|---------------|

| MT4LC16M4A7 S | 16 Meg x 4    |

| MT4LC16M4T8   | 16 Meg x 4    |

| MT4LC16M4T8 S | 16 Meg x 4    |

| MT4LC8M8E1    | 8 Meg x 8     |

| MT4LC8M8E1 S  | 8 Meg x 8     |

| MT4LC8M8B6    |               |

| MT4LC8M8B6 S  | 8 Meg x 8     |

| MT4LC4M16F5   | 4 Meg x 16    |

| MT4LC4M16F5 S | 4 Meg x 16    |

| FPM           | 4,096 Refresh |

#### SDRAM DIMM/SODIMM

| MT2LSDT132U   | 1 Meg x 32  | З |

|---------------|-------------|---|

| MT4LSDT232UD  |             | 3 |

| MT2LSDT432U   | 4 Meg x 32  | 3 |

| MT4LSDT832U   | 8 Meg x 32  | 3 |

| MT4LSDT1632UD |             | З |

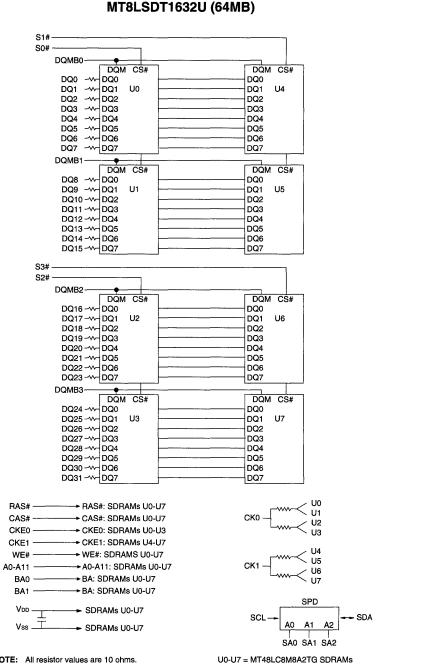

| MT8LSDT1632U  | 16 Meg x 32 | 3 |

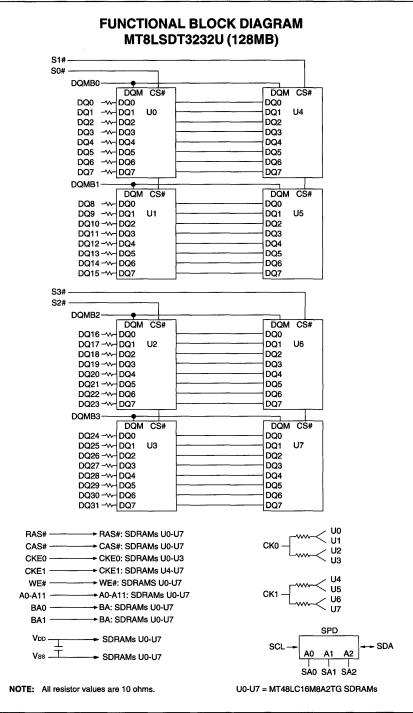

| MT8LSDT3232U  |             | 3 |

| MT4LSDT464H   | 4 Meg x 64  | 3 |

| MT4LSDT464H   | 4 Meg x 64  | 3 |

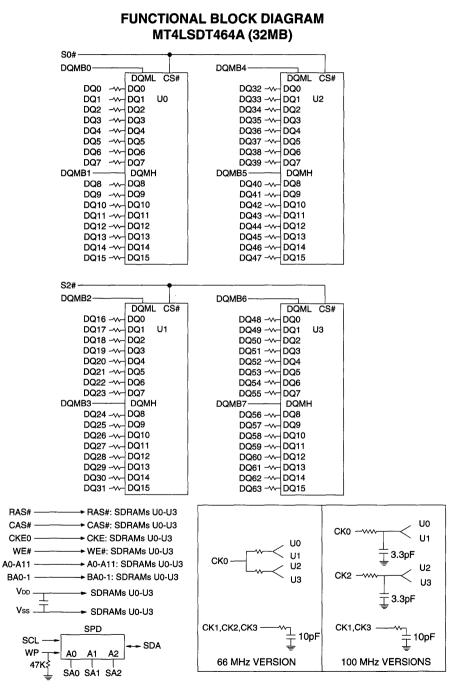

| MT4LSDT464A   |             | 3 |

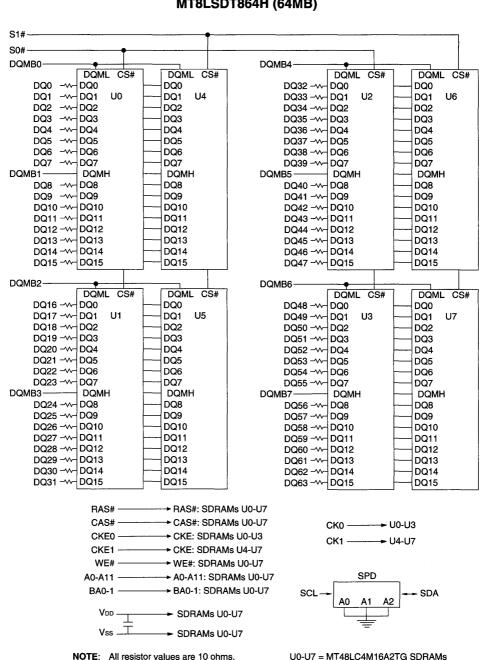

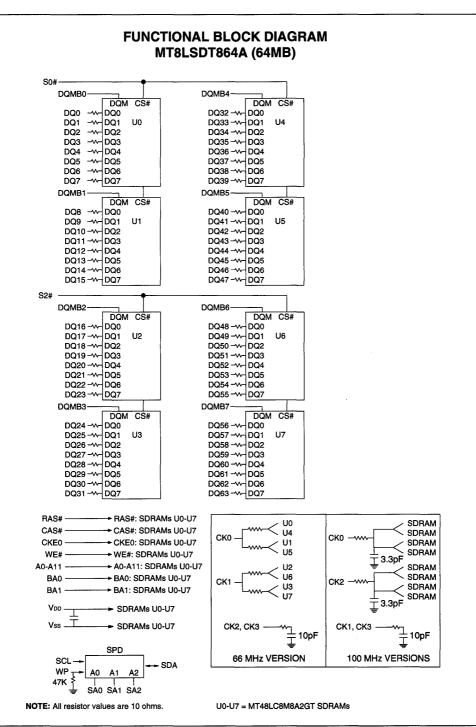

| MT8LSDT864H   |             | 3 |

| MT8LSDT864H   | 8 Meg x 64  | 3 |

| MT8LSDT864A   |             | 3 |

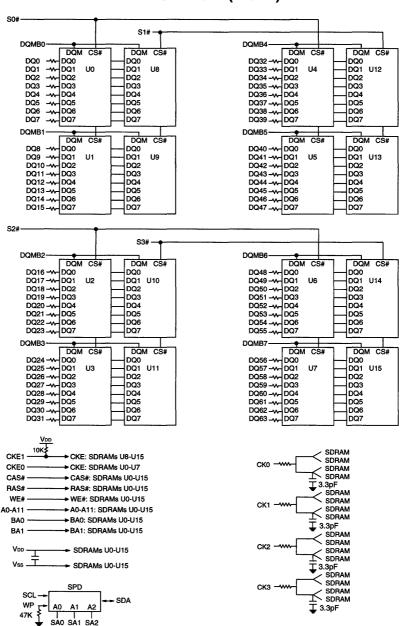

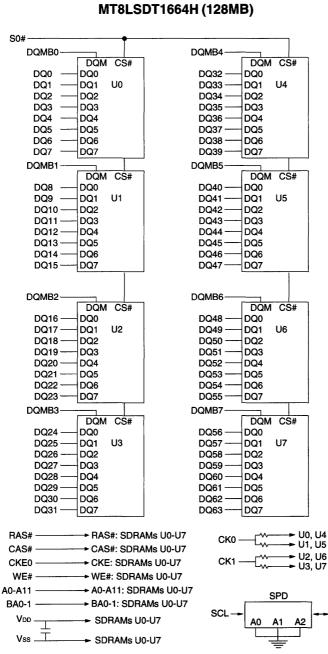

| MT8LSDT1664H  | 16 Meg x 64 | 3 |

| MT16LSDT1664A |             | 3 |

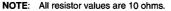

| MT16LSDT3264A |             | 3 |

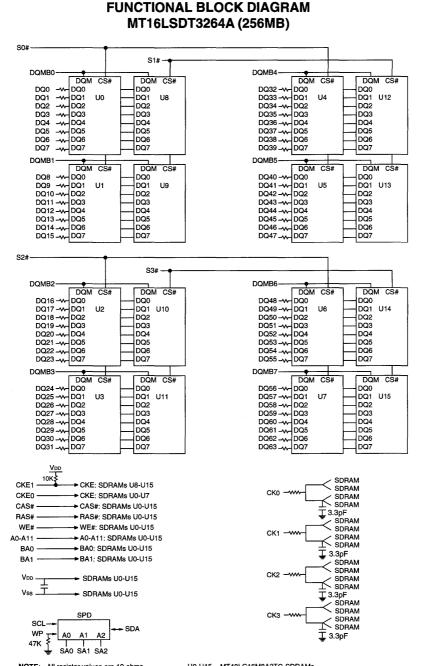

| MT5LSDT472A   |             | 3 |

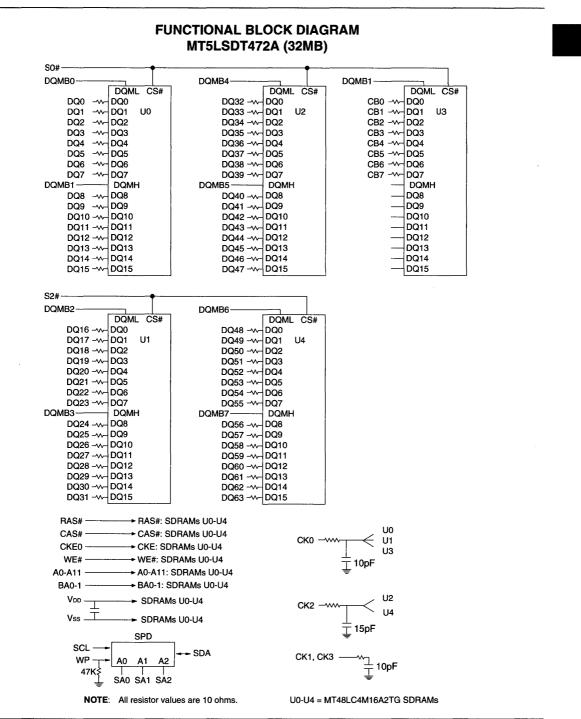

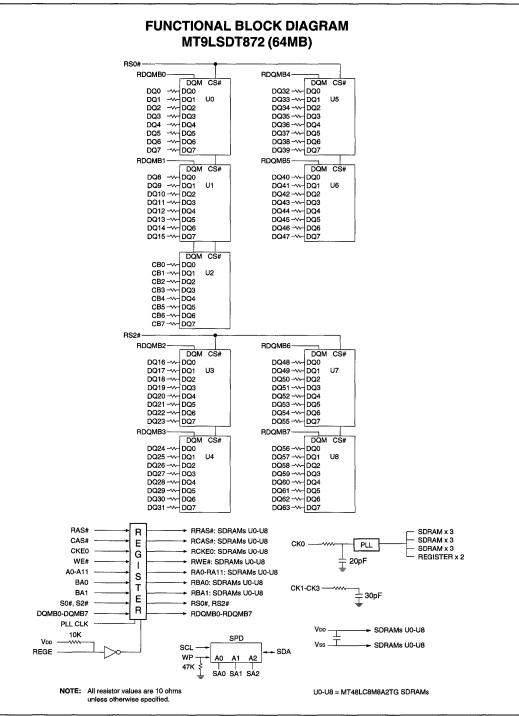

| MT9LSDT872    |             | 3 |

| MT9LSDT872A   |             | 3 |

| MT18LSDT1672A |             | 3 |

| MT18LSDT1672  |             | 3 |

|               |             |   |

#### FPM, 8KR 1-69 FPM, 8KR, S ..... 1-69 FPM, 4KR 1-69 FPM, 4KR, S ..... 1-69 FPM, 8KR ..... 1-73 FPM, 8KR, S ..... 1-73 1-73 FPM, 4KR ..... FPM, 4KR, S ..... 1-73 FPM, DC, 4KR ..... 1-77 FPM, DC, 4KR, S ..... 1-77 DC ...... Dual CAS

#### PAGE

PAGE

| 3.3V, DIMM   | 1-81  |

|--------------|-------|

| 3.3V, DIMM   | 1-81  |

| 3.3V, DIMM   | 1-85  |

| 3.3V, DIMM   | 1-85  |

| 3.3V, DIMM   | 1-89  |

| 3.3V, DIMM   | 1-93  |

| 3.3V, DIMM   | 1-93  |

| 3.3V, SODIMM | 1-101 |

| 3.3V, SODIMM | 1-105 |

| 3.3V, DIMM   | 1-97  |

| 3.3V, SODIMM | 1-101 |

| 3.3V, SODIMM | 1-105 |

| 3.3V, DIMM   | 1-109 |

| 3.3V, SODIMM | 1-113 |

| 3.3V, DIMM   | 1-109 |

| 3.3V, DIMM   | 1-117 |

| 3.3V, DIMM   | 1-121 |

| 3.3V, DIMM   | 1-125 |

| 3.3V, DIMM   | 1-129 |

| 3.3V, DIMM   | 1-129 |

| 3.3V, DIMM   | 1-133 |

|              |       |

#### SDRAM DIMM/SODIMM (continued)

:RON

| MT18LSDT3272  | 32 Meg x 72 |

|---------------|-------------|

| MT36LSDT3272  |             |

| MT18LSDT3272A |             |

| MT36LSDT6472  | Ų           |

|               | 0           |

#### SGRAM SODIMM

| MT2LG25664H  | 256K x 64 |

|--------------|-----------|

| MT2LG25664KH | 256K x 64 |

| MT4LG51264H  | 512K x 64 |

| MT4LG51264KH | 512K x 64 |

|              |           |

#### **DRAM DIMM/SODIMM**

| MT2LDT432U 4 Meg x 32       |

|-----------------------------|

| MT2LDT432U X 4 Meg x 32     |

| MT4LDT832U 8 Meg x 32       |

| MT4LDT832U X 8 Meg x 32     |

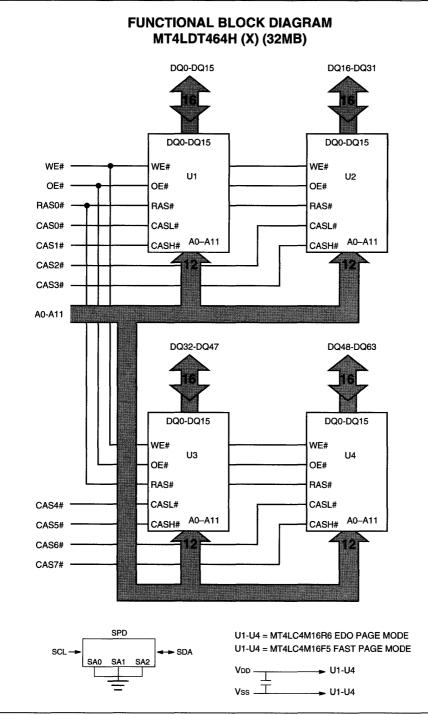

| MT4LDT464H 4 Meg x 64       |

| MT4LDT464H S 4 Meg x 64     |

| MT4LDT464H X 4 Meg x 64     |

| MT4LDT464H XS 4 Meg x 64    |

| MT4LDT464A 4 Meg x 64       |

| MT4LDT464A X 4 Meg x 64     |

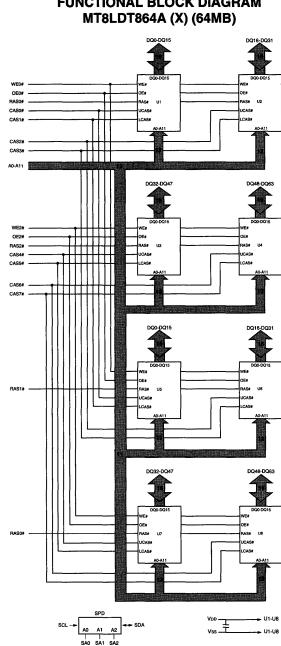

| MT8LDT864H 8 Meg x 64       |

| MT8LDT864H S 8 Meg x 64     |

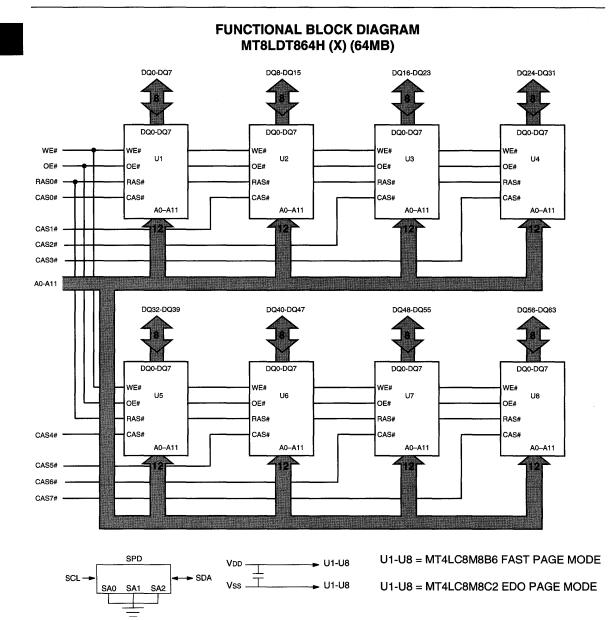

| MT8LDT864H X 8 Meg x 64     |

| MT8LDT864H XS 8 Meg x 64    |

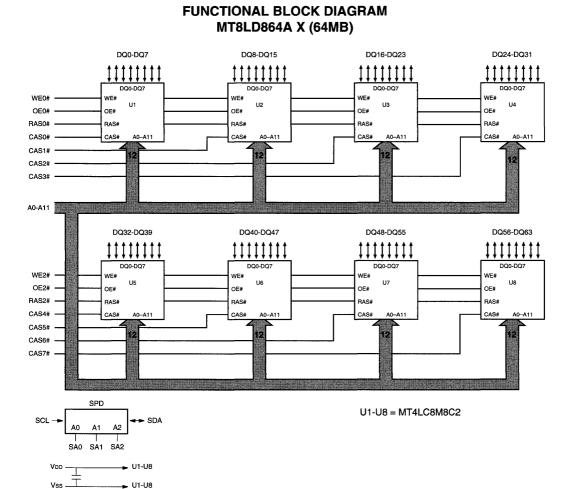

| MT8LDT864A 8 Meg x 64       |

| MT8LDT864A X 8 Meg x 64     |

| MT8LD864A X 8 Meg x 64      |

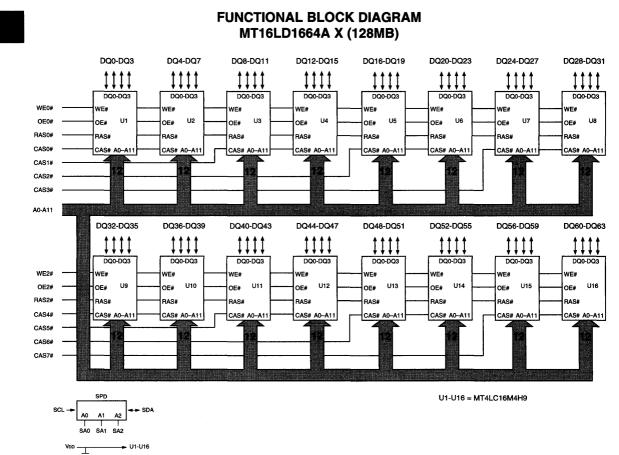

| MT16LD1664A X 16 Meg x 64   |

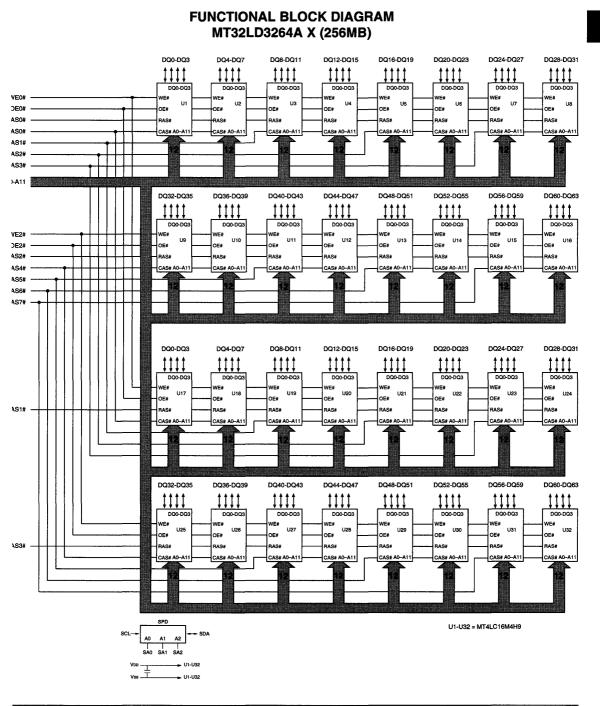

| MT32LD3264A X 32 Meg x 64   |

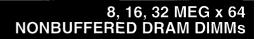

| MT9LD(T)872 X 8 Meg x 72    |

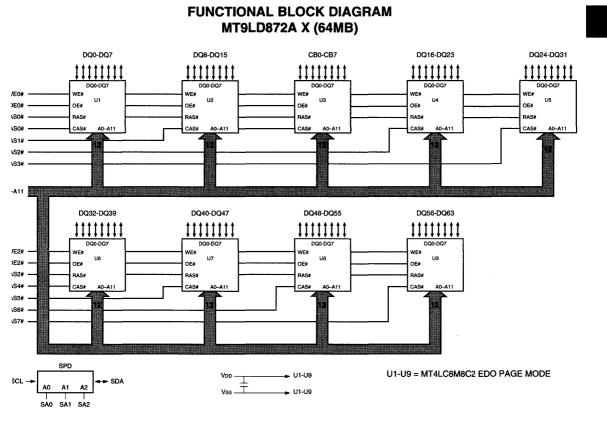

| MT9LD872A X 8 Meg x 72      |

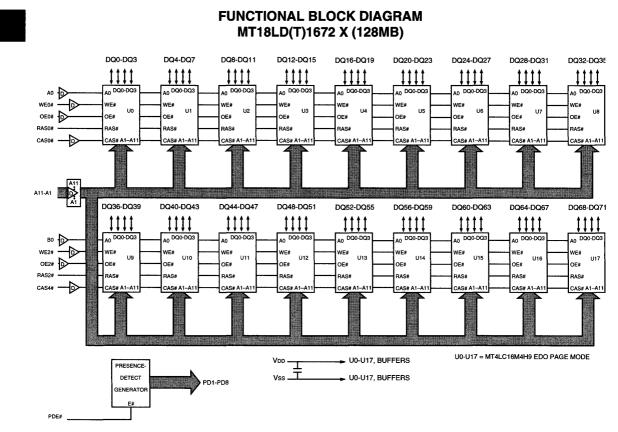

| MT18LD(T)1672 X 16 Meg x 72 |

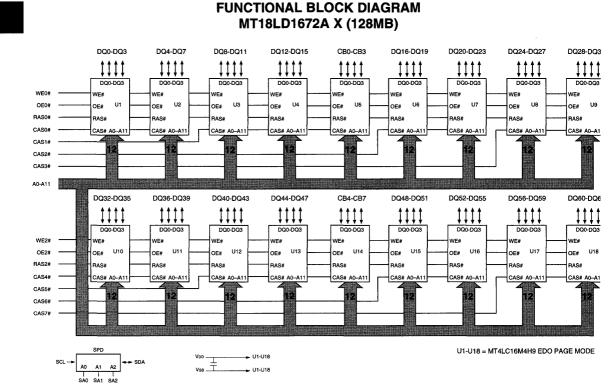

| MT18LD1672A X 16 Meg x 72   |

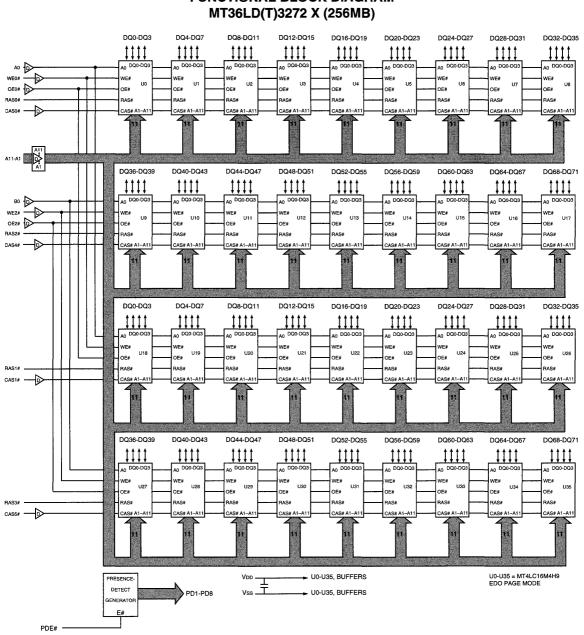

| MT36LD(T)3272 X 32 Meg x 72 |

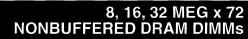

| MT36LD3272A X 32 Meg x 72   |

| N Nonbuffered               |

#### **ZBT SRAM\***

reface lev. 2/99

| MT55L128L18F   | 128K x 18 | 3.3V I/O, Flow-Through               | 2-1  |

|----------------|-----------|--------------------------------------|------|

| MT55L128L18P   | 128K x 18 | 3.3V I/O, Pipelined                  | 2-7  |

| MT55L256L18F   | 256K x 18 | 3.3V I/O, Flow-Through               | 2-13 |

| MT55L256L18P   | 256K x 18 | 3.3V I/O, Pipelined                  | 2-19 |

| MT56L256_18P** | 256K x 18 | 3.3V/2.5V I/O, SMART ZBT (Pipelined) | 2-37 |

| MT55L512_18F   | 512K x 18 | 3.3V/2.5V I/O, Flow-Through          | 2-25 |

| MT55L512_18P   | 512K x 18 | 3.3V/2.5V I/O, Pipelined             | 2-31 |

| MT56L512_18P   | 512K x 18 | 3.3V/2.5V I/O, SMART ZBT (Pipelined) | 2-37 |

| MT55L64L32F    | 64K x 32  | 3.3V I/O, Flow-Through               | 2-1  |

|                |           |                                      |      |

\*All ZBT SRAMs have 3.3V supply voltage.

\*\*The placeholder in the part number is replaced with an "L" for 3.3V I/O parts and a "V" for 2.5V I/O parts.

iii

## 3.3V, DIMM ..... 1-137

| 3.3V, DIMM | 1-141 |

|------------|-------|

| 3.3V, DIMM | 1-145 |

| 3.3V, DIMM | 1-149 |

|            |       |

#### PAGE

PAGE

| 3.3V | 1-153 |

|------|-------|

| 3.3V | 1-153 |

| 3.3V | 1-153 |

| 3.3V | 1-153 |

#### PAGE

| FPM, DIMM       1-157         EDO, DIMM       1-157         FPM, DIMM       1-157         FPM, SODIMM       1-165         FPM, SODIMM       1-165         FPM, SODIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-165         EDO, SODIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181                                      |                |             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|

| FPM, DIMM       1-157         EDO, DIMM       1-157         FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         FPM, SODIMM       1-161         FPM, SODIMM       1-165         FPM, SODIMM       1-165         FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, SODIMM       1-165         EDO, N, DIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181           EDO, DIMM | FPM, DIMM      | 1-157       |

| EDO, DIMM       1-157         FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         FPM, SODIMM       1-165         FPM, SODIMM       1-165         FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         FPM, S, SODIMM       1-165         FPM, N, DIMM       1-165         EDO, SODIMM       1-165         EDO, N, DIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-181         EDO, DIMM       1-181         EDO, DIMM       1-175                                                                                            |                | 1-157       |

| FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         FPM, S, SODIMM       1-161         FPM, S, SODIMM       1-161         FPM, S, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, DIMM       1-181         EDO, DIMM       1-181         EDO, DIMM       1-181                                                                             | FPM, DIMM      | 1-157       |

| FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         FPM, S, SODIMM       1-161         FPM, S, SODIMM       1-161         FPM, S, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, DIMM       1-181         EDO, DIMM       1-181         EDO, DIMM       1-181                                                                             | EDO, DIMM      | 1-157       |

| FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         FPM, SODIMM       1-161         FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, DIMM       1-181         EDO, DIMM       1-181                                                                                                                                                                                                                  |                | 1-165       |

| EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-175         EDO, DIMM       1-175         EDO, DIMM       1-181         EDO, DIMM       1-181         EDO, DIMM       1-181                                                                                                                                                              |                | 1-165       |

| EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, N, DIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175                                                                                                                                                                                                                                                                                          | EDO, SODIMM    | 1-165       |

| FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-175         EDO, N, DIMM       1-175         EDO, DIMM       1-175         EDO, DIMM       1-175                                                                                                                                                                                                                                                                                                                          | EDO, S, SODIMM | 1-165       |

| EDO, N, DIMM       1-161         FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, S, SODIMM       1-165         EDO, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-175         EDO, N, DIMM       1-175         EDO, N, DIMM       1-175         EDO, DIMM       1-175         EDO, DIMM       1-175         EDO, DIMM       1-175         EDO, DIMM       1-175                                                                                                                                                                                                                                                                                                                                                              | FPM, N, DIMM   | 1-161       |

| FPM, SODIMM       1-165         FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175                                                                                                                                                                                                                                                                                                                                                                      |                | 1-161       |

| FPM, S, SODIMM       1-165         EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, DIMM       1-175         EDO, DIMM       1-181         EDO, DIMM       1-175         EDO, DIMM       1-175         EDO, DIMM       1-175         EDO, DIMM       1-175                                                                                                                                                                                                                                                                                                                                                                                                                                       |                | 1-165       |

| EDO, SODIMM       1-165         EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-181         EDO, N, DIMM       1-175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                | 1-165       |

| EDO, S, SODIMM       1-165         FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | 1-165       |

| FPM, N, DIMM       1-161         EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-181         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, DIMM       1-175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                | 1-165       |

| EDO, N, DIMM       1-161         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, DIMM       1-175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                | 1-161       |

| EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, DIMM       1-175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | 1-161       |

| EDO, N, DIMM       1-169         EDO, N, DIMM       1-169         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, DIMM       1-181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                | 1-169       |

| EDO, N, DIMM       1-169         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, DIMM       1-181         EDO, DIMM       1-181                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | 1-169       |

| EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, DIMM       1-175         EDO, N, DIMM       1-181         EDO, N, DIMM       1-181         EDO, DIMM       1-175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | 1-169       |

| EDO, N, DIMM         1-181           EDO, DIMM         1-175           EDO, N, DIMM         1-181           EDO, DIMM         1-181           EDO, DIMM         1-175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                | 1-175       |

| EDO, DIMM         1-175           EDO, N, DIMM         1-181           EDO, DIMM         1-175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                | 1-181       |

| EDO, N, DIMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                | 1-175       |

| EDO, DIMM 1-175                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | 1-181       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | 1-175       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                | 1-181       |

| S Self Refresh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SS             | elf Refresh |

| MT55L64L32P              | 3.3V I/O, Pipelined                  | 2-7  |

|--------------------------|--------------------------------------|------|

| MT55L128L32F 128K x 32   | 3.3V I/O, Flow-Through               | 2-13 |

| MT55L128L32P 128K x 32   | 3.3V I/O, Pipelined                  | 2-19 |

| MT56L128_32P** 128K x 32 | 3.3V/2.5V I/O, SMART ZBT (Pipelined) | 2-37 |

| MT55L256_32F             | 3.3V/2.5V I/O, Flow-Through          | 2-25 |

| MT55L256_32P 256K x 32   | 3.3V/2.5V I/O, Pipelined             | 2-31 |

| MT56L256_32P 256K x 32   | 3.3V/2.5V I/O, SMART ZBT (Pipelined) | 2-37 |

| MT55L64L36F              | 3.3V I/O, Flow-Through               | 2-1  |

| MT55L64L36P              | 3.3V I/O, Pipelined                  | 2-7  |

| MT55L128L36F 128K x 36   | 3.3V I/O, Flow-Through               |      |

| MT55L128L36P 128K x 36   | 3.3V I/O, Pipelined                  | 2-19 |

| MT56L128_36P 128K x 36   | 3.3V/2.5V I/O, SMART ZBT (Pipelined) | 2-37 |

| MT55L256_36F 256K x 36   | 3.3V/2.5V I/O, Flow-Through          | 2-25 |

| MT55L256_36P 256K x 36   | 3.3V/2.5V I/O, Pipelined             |      |

| MT56L256_36P 256K x 36   | 3.3V/2.5V I/O, SMART ZBT (Pipelined) | 2-37 |

|                          |                                      |      |

\*All ZBT SRAMs have 3.3V supply voltage. \*\*The placeholder in the part number is replaced with an "L" for 3.3V I/O parts and a "V" for 2.5V I/O parts.

#### SYNCBURST SRAM<sup>†</sup>

| MT58LC64K18B4 64K x 18    | 3.3V I/O, Flow-Through        | 2-39        |

|---------------------------|-------------------------------|-------------|

| MT58LC64K18D9             | 3.3V I/O, Pipelined, SCD      | 2-43        |

| MT58LC64K18C6             | 3.3V I/O, Pipelined, DCD      | 2-47        |

| MT58LC128K18B4            | 3.3V I/O, Flow-Through        | 2-51        |

| MT58LC128K18E1            | 2.5V I/O, Flow-Through        | 2-51        |

| MT58LC128K18D9            | 3.3V I/O, Pipelined, SCD      | 2-55        |

| MT58LC128K18G1            | 2.5V I/O, Pipelined, SCD      | 2-55        |

| MT58LC128K18C6            | 3.3V I/O, Pipelined, DCD      | 2-59        |

| MT58LC128K18F1            | 2.5V I/O, Pipelined, DCD      | 2-59        |

| MT58L256_18F**            | 3.3V/2.5V I/O, Flow-Through   | 2-63        |

| MT58L256_18P              | 3.3V/2.5V I/O, Pipelined, SCD | 2-67        |

| MT58L256L18D              | 3.3V I/O, Pipelined, DCD      | 2-71        |

| MT58L512 18F              | 3.3V/2.5V I/O, Flow-Through   | 2-75        |

| MT58L512 18P              | 3.3V/2.5V I/O, Pipelined, SCD | 2-81        |

| MT58L512L18D              | 3.3V I/O, Pipelined, DCD      | 2-87        |

| MT58LC32K32B4             | 3.3V I/O, Flow-Through        | 2-39        |

| MT58LC32K32D9             | 3.3V I/O, Pipelined, SCD      | 2-43        |

| MT58LC32K32C6             | 3.3V I/O, Pipelined, DCD      | 2-47        |

| MT58LC64K32B4             | 3.3V I/O, Flow-Through        | 2-51        |

| MT58LC64K32E1             | 2.5V I/O, Flow-Through        | 2-51        |

| MT58LC64K32D9             | 3.3V I/O, Pipelined, SCD      | 2-55        |

| MT58LC64K32G1             | 2.5V I/O, Pipelined, SCD      | 2-55        |

| MT58LC64K32C6             | 3.3V I/O, Pipelined, DCD      | 2-59        |

| MT58LC64K32F1             | 2.5V I/O, Pipelined, DCD      | 2-59        |

| MT58L128_32F 128K x 32    | 3.3V/2.5V I/O, Flow-Through   | 2-63        |

| MT58L128_32P 128K x 32    | 3.3V/2.5V I/O, Pipelined, SCD | 2-67        |

| MT58L128L32D 128K x 32    | 3.3V I/O, Pipelined, DCD      | 2-71        |

| MT58L256_32F              | 3.3V/2.5V I/O, Flow-Through   | 2-75        |

| MT58L256_32P              | 3.3V/2.5V I/O, Pipelined, SCD | 2-81        |

| SCD Single-Cycle Deselect | DCD Double-Cyc                | lo Docelect |

| SCD Snigle-Cycle Deselect | DCD                           | Te Deselect |

<sup>+</sup>All SyncBurst SRAMs have 3.3V supply voltage. \*\*The placeholder in the part number is replaced with an "L" for 3.3V I/O parts and a "V" for 2.5V I/O parts.

iv

## PAGE

#### SYNCBURST SRAM<sup>†</sup> (continued)

#### PAGE

| ·····          | ··· · · · · · · · · · · · · · · · · · |                               |             |

|----------------|---------------------------------------|-------------------------------|-------------|

| MT58L256L32D   | 256K x 32                             | 3.3V I/O, Pipelined, DCD      | 2-87        |

| MT58LC32K36B4  |                                       | 3.3V I/O, Flow-Through        | 2-39        |

| MT58LC32K36D9  |                                       | 3.3V I/O, Pipelined, SCD      | 2-43        |

| MT58LC32K36C6  |                                       | 3.3V I/O, Pipelined, DCD      | 2-47        |

| MT58LC64K36B4  | 64K x 36                              | 3.3V I/O, Flow-Through        | 2-51        |

| MT58LC64K36E1  |                                       | 2.5V I/O, Flow-Through        | 2-51        |

| MT58LC64K36D9  | 64K x 36                              | 3.3V I/O, Pipelined, SCD      | 2-55        |

| MT58LC64K36G1  | 64K x 36                              | 2.5V I/O, Pipelined, SCD      | 2-55        |

| MT58LC64K36C6  | 64K x 36                              | 3.3V I/O, Pipelined, DCD      | 2-59        |

| MT58LC64K36F1  |                                       | 2.5V I/O, Pipelined, DCD      | 2-59        |

| MT58L128_36F** | 128K x 36                             | 3.3V/2.5V I/O, Flow-Through   | 2-63        |

| MT58L128_36P   | 128K x 36                             | 3.3V/2.5V I/O, Pipelined, SCD | 2-67        |

| MT58L128L36D   | 128K x 36                             | 3.3V I/O, Pipelined, DCD      | 2-71        |

| MT58L256_36F   | 256K x 36                             | 3.3V/2.5V I/O, Flow-Through   | 2-75        |

| MT58L256_36P   | 256K x 36                             | 3.3V/2.5V I/O, Pipelined, SCD | 2-81        |

| MT58L256L36D   | 256K x 36                             | 3.3V I/O, Pipelined, DCD      | 2-87        |

| SCD            | Single-Cycle Deselect                 | DCD Double-Cycl               | le Deselect |

|                |                                       |                               |             |

<sup>†</sup>All SyncBurst SRAMs have 3.3V supply voltage.

\*\*The placeholder in the part number is replaced with an "L" for 3.3V I/O parts and a "V" for 2.5V I/O parts.

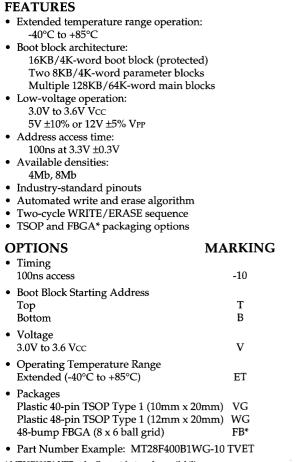

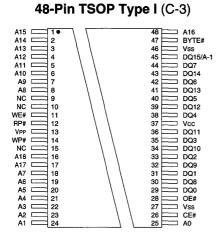

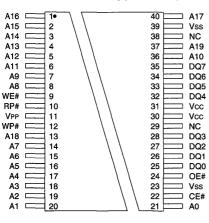

#### BOOT BLOCK FLASH MEMORY

| MT28F002B1      | 256K x 8             |

|-----------------|----------------------|

| MT28F200B1      | 128K x 16/256K x 8   |

| MT28F002C1      | 256K x 8             |

| MT28F004B1      | 512K x 8             |

| MT28F400B1      | 256K x 16/512K x 8   |

| MT28F008B1      | 1 Meg x 8            |

| MT28F800B1      | .512K x 16/1 Meg x 8 |

| MT28F400B5 ET   |                      |

| MT28F800B5 ET   | 512K x 16            |

| MT28F400B1 VET  | 256K x 16            |

| MT28F800B1 VET  | 512K x 16            |

| MT28F004B1 VET  | 512K x 8             |

| MT28F008B1 VET  | 1 Meg x 8            |

| MT28F008B3      |                      |

| MT28F800B3      | .512K x 16/1 Meg x 8 |

| MT28F008B5      | 1 Meg x 8            |

| MT28F800B5      | .512K x 16/1 Meg x 8 |

| BB<br>ET<br>SVT | Extended Temperature |

#### EVEN-SECTORED FLASH MEMORY

| MT28F016S5 |                         |

|------------|-------------------------|

| AUTO       | Automated W/E Algorithm |

| DPD        | Deep Power-Down         |

#### FLASH CARDS

| CompactFlash Card | 4MB |

|-------------------|-----|

| CompactFlash Card |     |

| CompactFlash Card |     |

| CompactFlash Card |     |

#### BB, AUTO, SVT ..... 3-1 BB, AUTO, SVT ...... 3-19 BB, AUTO, SVT ...... 3-23 BB, AUTO, Smart 5 ..... 3-27 BB, AUTO, 3V Only ..... 3-31 BB, AUTO, 5V Only ...... 3-39 AUTO ...... Automated W/E Algorithm V ...... Low Voltage

#### PAGE

| SE, AUTO, DPD | 3-47       |

|---------------|------------|

| SE Eve        | n Sectored |

#### PAGE

| 3.3V or 5V |  |

|------------|--|

| 3.3V or 5V |  |

| 3.3V or 5V |  |

| 3.3V or 5V |  |

|            |  |

PAGE

PAGE

#### GENERAL TECHNICAL NOTES

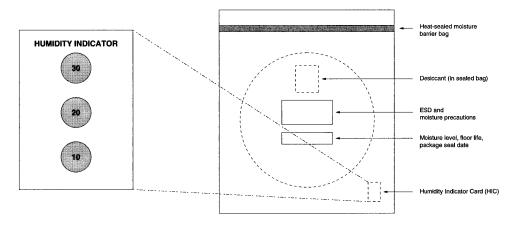

| TN-00-01<br>TN-00-03<br>TN-00-04<br>TN-00-05<br>TN-00-06<br>TN-00-07<br>TN-00-08<br>TN-00-09<br>TN-00-09 | Moisture Absorption in Plastic Packages     | 4-3<br>4-5<br>4-13<br>4-15<br>4-21<br>4-25<br>4-27 |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------|

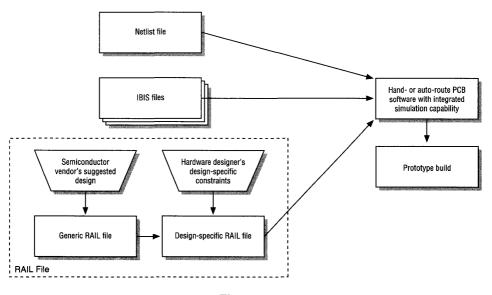

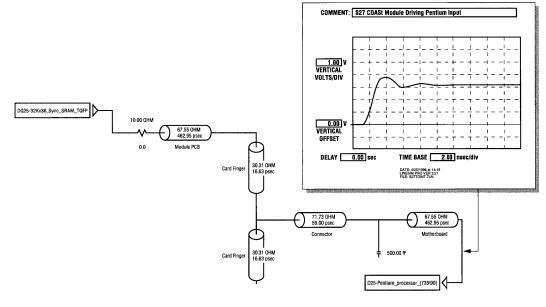

| TN-00-10                                                                                                 | Micron Meets the Need for Simulation Models |                                                    |

#### DRAM TECHNICAL NOTES

| TN-04-06 | OE#-Controlled LATE WRITE Cycles (DRAM)                      | 4-35  |

|----------|--------------------------------------------------------------|-------|

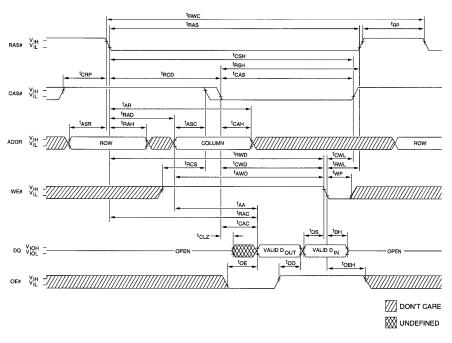

| TN-04-08 | DRAM Timing Parameters                                       | 4-37  |

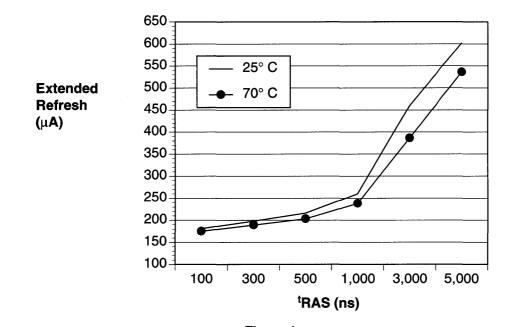

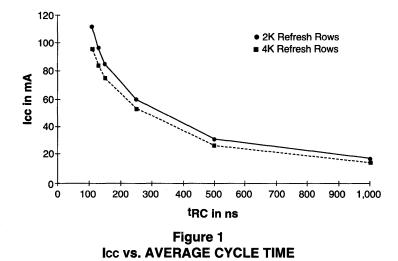

| TN-04-12 | LPDRAM Extended Refresh Current vs. RAS# Active Time (4Mb)   | 4-39  |

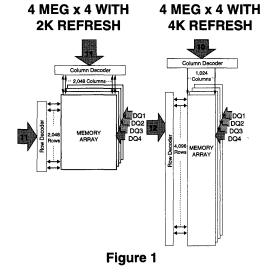

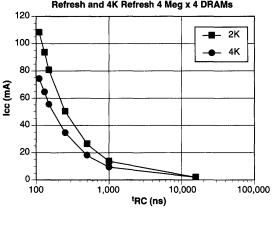

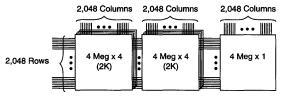

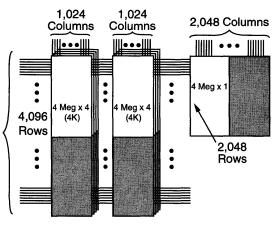

| TN-04-16 | 16Mb DRAM—2K vs. 4K Refresh Comparison                       | 4-41  |

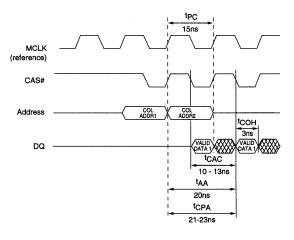

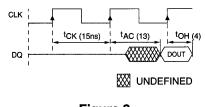

| TN-04-21 | Reduce DRAM Cycle Times With Extended Data-Out               | 4-43  |

| TN-04-28 | DRAM Soft Error Rate Calculations                            | 4-51  |

| TN-04-29 | Maximizing EDO Advantages at the System Level                | 4-55  |

| TN-04-30 | Various Methods of DRAM Refresh                              | 4-67  |

| TN-04-32 | Reduce DRAM Memory Cost With Cache                           | 4-71  |

| TN-04-35 | Designing in the Right DRAM "Refresh" Configuration          |       |

| TN-04-40 | EDO Compatibility With FPM DRAMs                             | 4-79  |

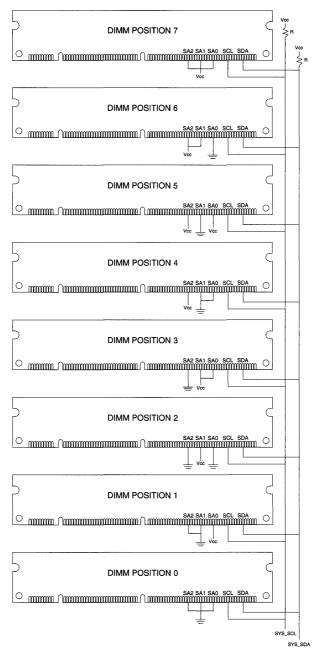

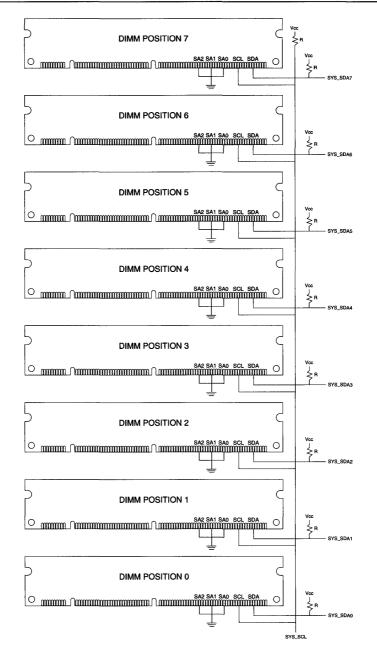

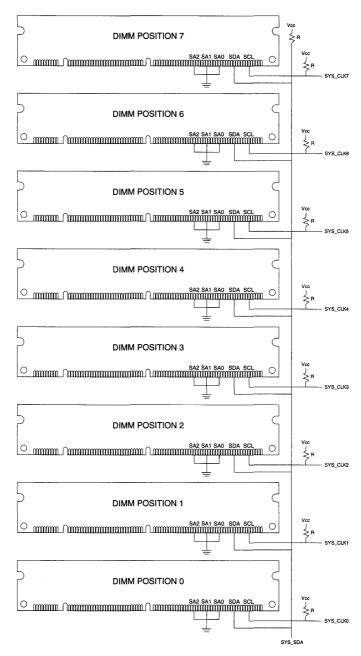

| TN-04-42 | Memory Module Serial Presence-Detect                         |       |

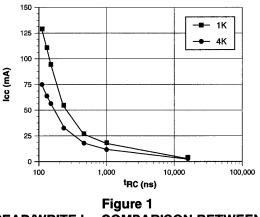

| TN-04-43 | 1 Meg x 16 DRAM Power Savings: 1K vs. 4K Row Refresh         | 4-101 |

| TN-04-44 | Maximizing DRAM Valid Data-Out Window                        | 4-105 |

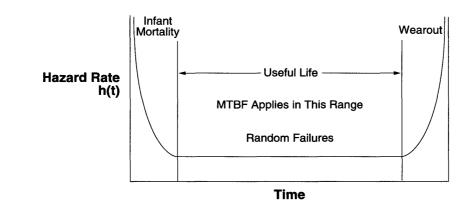

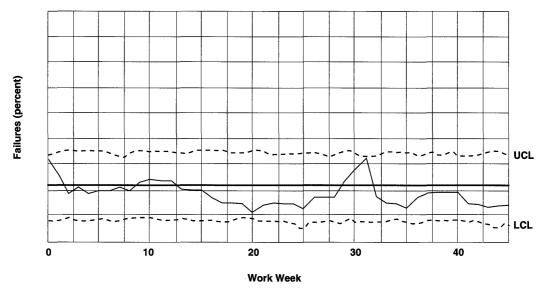

| TN-04-45 | DRAM Module Mean Time Between Failures (MTBF)                | 4-109 |

| TN-04-46 | The Best Graphics Solution for 66 MHz: SGRAM or EDO DRAM?    | 4-111 |

| TN-41-01 | Decrement Bursting With the SGRAM                            | 4-113 |

| TN-41-05 | Hiding the LOAD SPECIAL MODE REGISTER Command in the SGRAM   | 4-117 |

| TN-41-06 | SGRAM Package Compatibility                                  | 4-121 |

| TN-48-01 | Examples of READ-MODIFY-WRITE Cycles With Synchronous DRAMs  | 4-123 |

| TN-48-02 | Achieve Maximum Compatibility in SDRAM/SGRAM Design          | 4-127 |

| TN-48-03 | Designing for High Performance With Synchronous DRAM Modules |       |

| TN-48-04 | Is Your Module PC100?                                        |       |

| TN-48-05 | SDRAM WRITE to ACTIVE Command Timing                         | 4-141 |

#### SRAM TECHNICAL NOTES

| D  | ۸ | C  | E |

|----|---|----|---|

| Ľ. | А | J. | E |

| TN-05-14 | SRAM Thermal Design Considerations               | 4-145 |

|----------|--------------------------------------------------|-------|

| TN-05-21 | High-Speed Memory Design Techniques              | 4-151 |

| TN-05-24 | Interfacing with LVTTL SRAMs                     | 4-157 |

| TN-05-26 |                                                  | 4-159 |

| TN-55-01 | Designing with ZBT SRAMs                         | 4-161 |

| TN-58-01 | Designing for Multiple SyncBurst SRAM Vendors    |       |

| TN-58-02 | Designing with x36 SyncBurst SRAMs               | 4-175 |

| TN-58-03 | SyncBurst SRAMs in ASIC and Asynchronous Designs | 4-181 |

| TN-58-04 | Design Tips: SyncBurst SRAM Standards            | 4-185 |

| TN-58-05 | SyncBurst SRAMs in DSP Applications              |       |

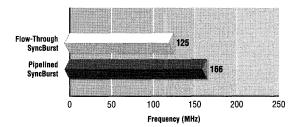

| TN-58-06 | Choosing the Right SyncBurst SRAM                | 4-195 |

| TN-58-07 | Banking SyncBurst SRAMs                          |       |

| TN-58-08 | Designing with 3.3V I/O Synchronous SRAMs        |       |

#### **SRAM TECHNICAL NOTES (continued)**

| TN-58-09 | Synchronous SRAM Bus Contention Design Considerations       | 4-211 |

|----------|-------------------------------------------------------------|-------|

| TN-58-12 | Using Parity SRAMs in Nonparity Applications                | 4-215 |

| TN-58-13 | Using SyncBurst SRAMs with the TI C6x DSP Family            | 4-217 |

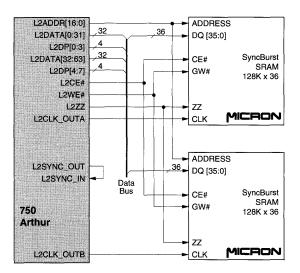

| TN-58-14 | SRAMs for the PowerPC 750 Arthur Processor                  | 4-219 |

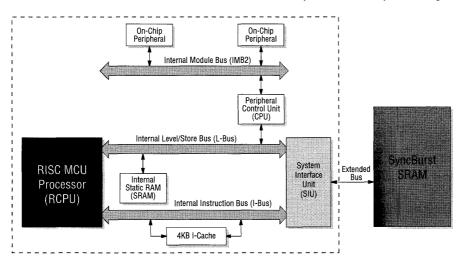

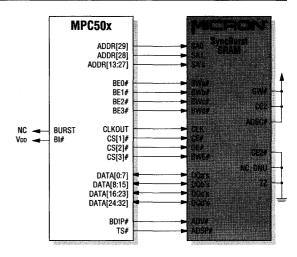

| TN-58-15 | Using SRAMs with PowerPC MPC505 and MPC509 Microcontrollers | 4-225 |

#### FLASH TECHNICAL NOTES

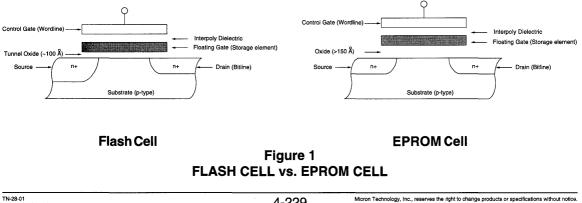

| TN-28-01 | Boot Block Flash Memory Technology                     | 4-229 |

|----------|--------------------------------------------------------|-------|

| TN-28-02 | Bulk Erase to Boot Block Conversion                    | 4-233 |

| TN-28-04 | Designing for SmartVoltage Technology Flash            | 4-237 |

| TN-28-05 | Micron-Intel Flash Compatibility                       | 4-243 |

| TN-28-06 | Designing for Multiple Boot Block Flash Memory Sources | 4-249 |

| TN-28-07 | Dual-Supply Boot Block Flash Advantages                | 4-255 |

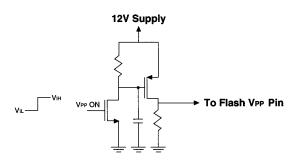

| TN-28-08 | High-Voltage Switching for Flash Memory Programming    | 4-259 |

#### PRODUCT RELIABILITY

| General Information | 5-1 |

|---------------------|-----|

| Overview            | 5-2 |

#### **PACKAGE INFORMATION**

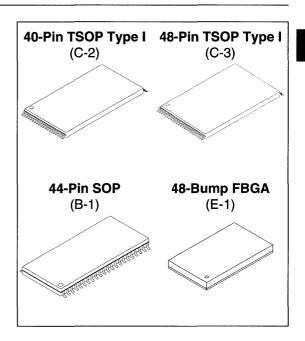

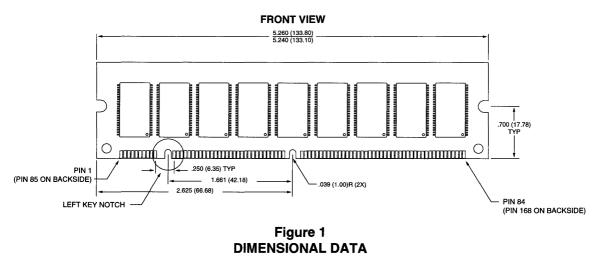

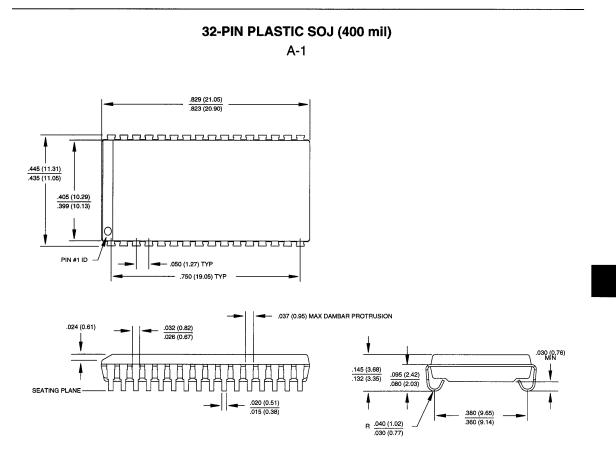

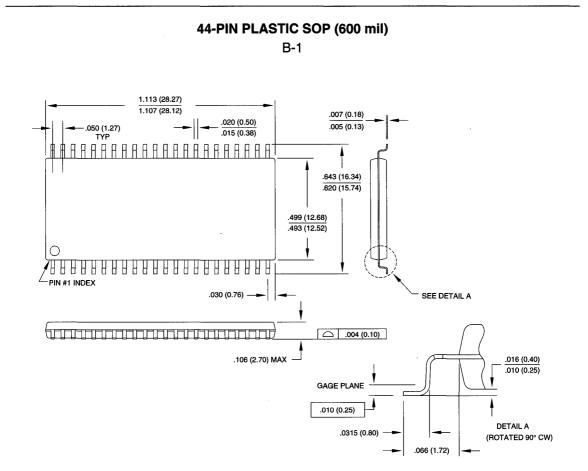

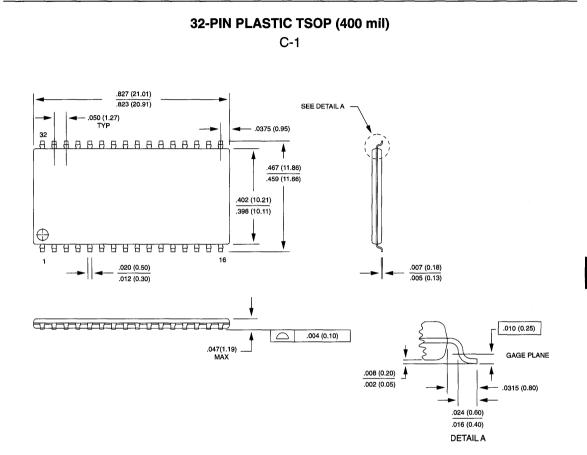

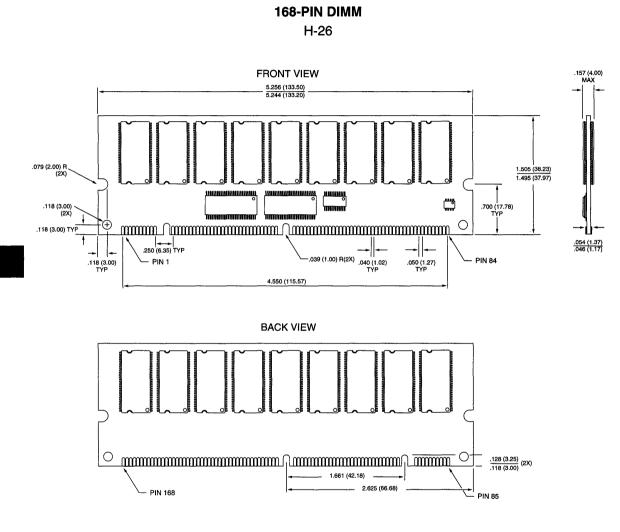

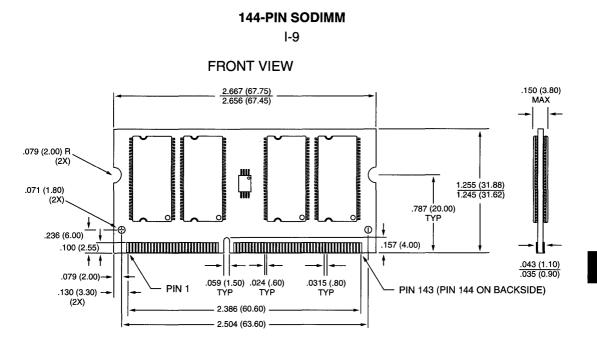

| Component Packaging | <b>6-</b> 1 |

|---------------------|-------------|

| Module Packaging    | 6-15        |

#### SALES AND SERVICE INFORMATION

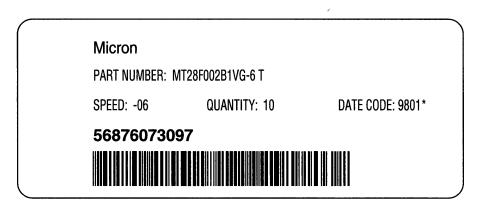

| CSN-01       | Master Container Bar Code Labels                      | 7-1  |

|--------------|-------------------------------------------------------|------|

| CSN-02       | Individual Box Bar Code Labels                        | 7-2  |

| CSN-03       | Product Dry Pack Labeling                             | 7-3  |

| CSN-04       | Shipping Quantity and Weight Charts                   | 7-4  |

| CSN-05       | Environmental Programs                                | 7-7  |

| CSN-06       | Electronic Data Interchange                           | 7-9  |

| CSN-07       | Returned Material Authorization (RMA) Procedures      | 7-10 |

| CSN-08       | ISO Standards                                         | 7-11 |

| CSN-10       | Customer Comment                                      | 7-12 |

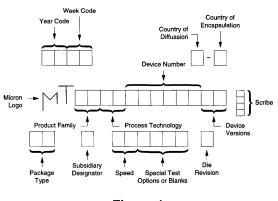

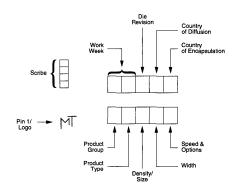

| CSN-11       | Product Mark/Label                                    | 7-13 |

| CSN-12       | Product Change Notification (PCN) System              | 7-15 |

| CSN-13       | Die Returned Material Authorization (RMA) Procedures  | 7-16 |

| CSN-15       | Tape-and-Reel Procedures                              | 7-17 |

| Ordering In  | Tape-and-Reel Procedures                              | 7-21 |

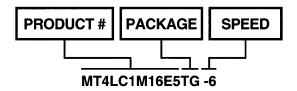

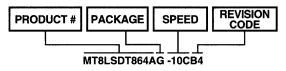

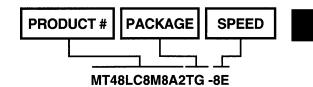

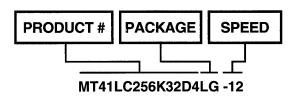

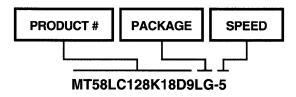

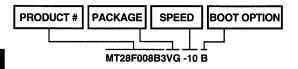

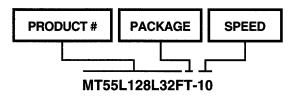

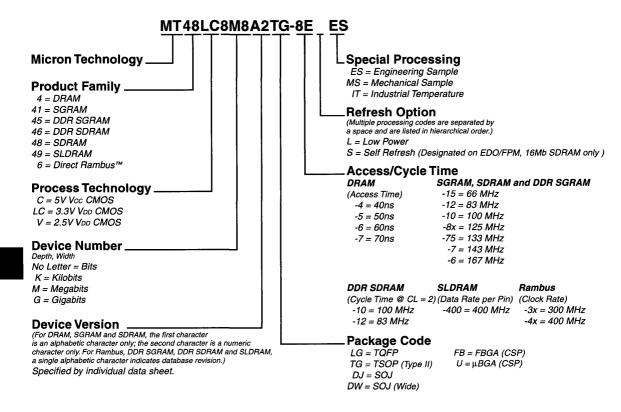

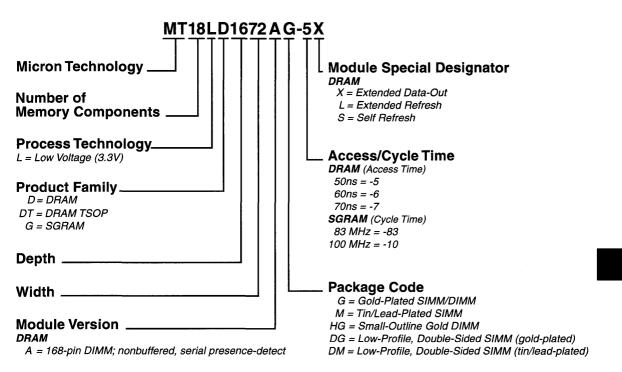

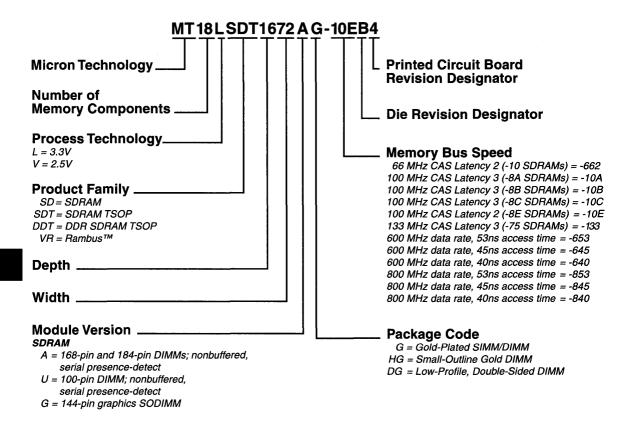

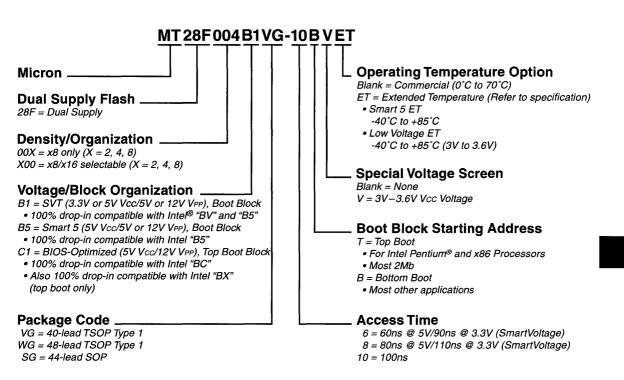

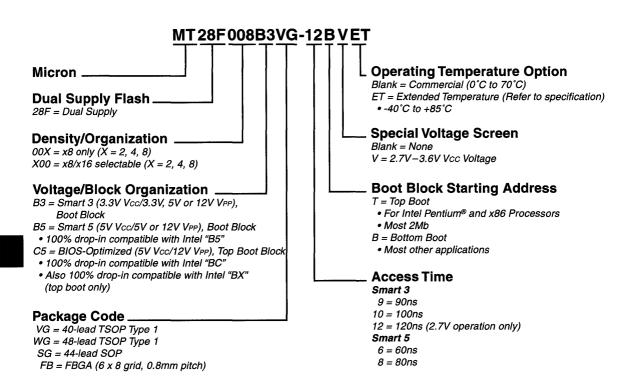

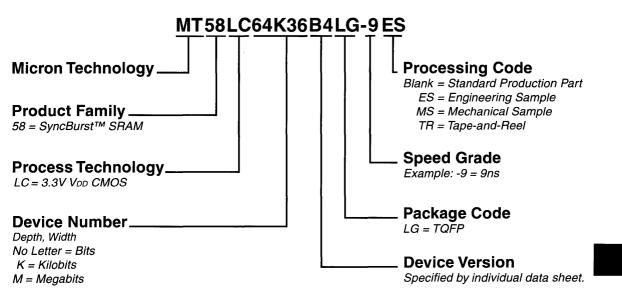

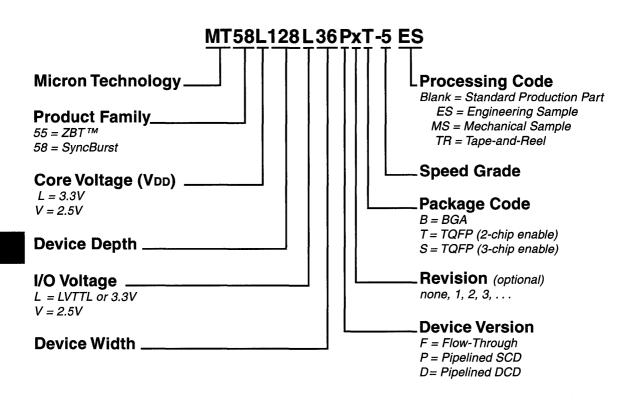

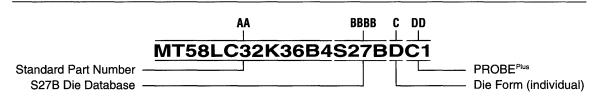

| Product Nu   | mbering                                               | 7-23 |

| North Ame    | North American Sales Representatives and Distributors |      |

| Internationa | Il Sales Representatives and Distributors             | 7-48 |

|              |                                                       |      |

PAGE

PAGE

## PAGE

PAGE

## **IMPORTANT NOTICE**

Micron Technology, Inc. (Micron), reserves the right to change products or specifications without notice. Customers are advised to obtain the latest versions of product specifications, which should be considered in evaluating a product's appropriateness for a particular use. There is no assurance that Micron's semiconductor products are appropriate for any application by a customer.

MICRON MAKES NO WARRANTIES, EX-PRESSED OR IMPLIED, INCLUDING ANY IMPLIED WARRANTIES OF MERCHANT-ABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OTHER THAN COMPLIANCE WITH MICRON'S SPECIFICATION SHEET FOR THE PRODUCT AT THE TIME OF DELIVERY. IN NO EVENT SHALL MICRON BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL OR CONSEQUENTIAL DAM-AGES AS A RESULT OF THE PERFOR-MANCE, ORFAILURE TOPERFORM, OF ANY MICRON PRODUCT.

ANY CLAIM AGAINST MICRON MUST BE MADE WITHIN 90 DAYS FROM THE DATE OF SHIPMENT BY MICRON AND MICRON HAS NO LIABILITY THEREAFTER. Micron's liability is limited to replacement of defective product, or either Customer or Micron may elect refund of amounts paid in lieu of replacement. The warranty covers only defects arising under normal use and not malfunctions resulting from misuse, abuse, modification or repairs by anyone other than Micron.

MICRON'S PRODUCTS ARE NOT AUTHO-RIZED FOR USE AS CRITICAL COMPO-NENTS IN LIFE SUPPORT DEVICES OR SYSTEMS OR FOR USE IN OTHER CRITICAL APPLICATIONS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF MICRON. Life support devices or systems are those which are intended to support or sustain life and whose failure to perform can be reasonably expected to result in a significant injury or death to the user. Critical components are those whose failure to perform can be reasonably expected to cause failure of a life support device or system or affect its safety or effectiveness. Critical applications are those applications that may involve potential risk of death, personal injury, or severe property or environmental damage.

MICRON DOES NOT WARRANT PRODUCT TO BE FREE OF CLAIMS OF PATENT, COPY-RIGHT, TRADEMARK, OR ANY OTHER IN-TELLECTUAL PROPERTY INFRINGEMENT BY ANY THIRD PARTY AND DISCLAIMS ANY SUCH WARRANTY OR INDEMNIFI-CATION AGAINST SUCH INFRINGEMENT.

Micron's terms and conditions of sale may be changed at any time without notice. Warranties may vary based on product type. Current warranty information will be included in Micron's confirmation statements.

Dear Customer:

Micron Technology, Inc., is dedicated to the design, manufacture and marketing of high-quality, highly reliable memory components. Our corporate mission is:

### "To be the most efficient and innovative global provider of semiconductor memory solutions."

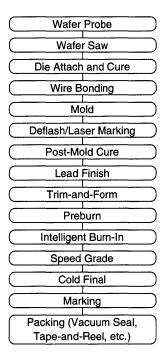

At Micron, we are investing time, talent and resources to bring you the finest DRAMs, SRAMs, Flash and other specialty memory products. We have developed a unique intelligent burn-in system, AMBYX<sup>™</sup>, which evaluates and reports the quality level of each and every component we produce.

We are dedicated to continuous improvement of all our products and services. This means continual reduction of electrical and mechanical defect levels. It also means the addition of new services such as bonded inventory, online forecasting and electronic data interchange programs. And when you have a design or application question, you can get the answers you need from our World Wide Web site (www.micron.com/mti) or by contacting one of Micron's Applications Engineers.

We're proud of our products, our progress and our performance. And we're pleased that you're choosing Micron as your memory supplier.

The Micron Team

#### **ADVANTAGES**

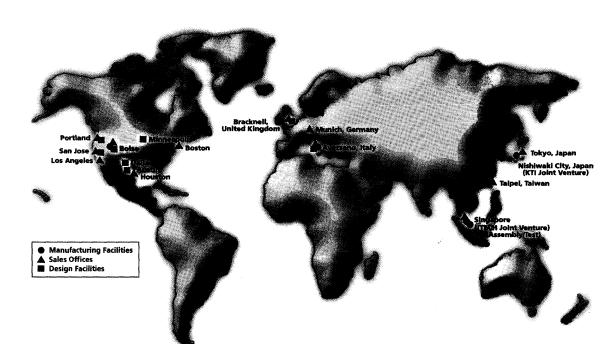

Micron Technology, Inc. (Micron), brings quality, productivity and innovation together to provide advantages for our customers. Our products feature some of the industry's fastest speeds. And we establish delivery standards based on customer expectations, including JIT programs, made possible by ever-increasing product reliability.

#### MEMORY PRODUCTS

Micron is working to provide customers with the widest range of memory products available anywhere. Our product line includes PC100, PC133 and double data rate (DDR) synchronous DRAM, as well as higher speed graphics RAM and higher density synchronous SRAM products. Micron's flash memory line offers boot block flash, sectored erase flash and flash cards. For the future, Micron plans production of both RDRAM\* and SLDRAM packet-based architectures.

#### **DIE SALES**

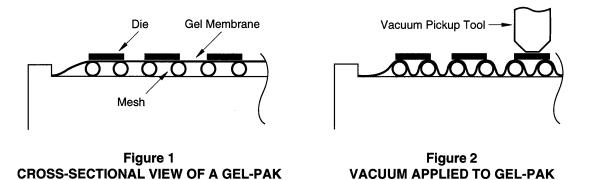

In addition to our durable packaging, Micron is one of the leaders in the industry in bare die. Demand for die is increasing for use in highly specialized applications. Micron's bare die products are available in 8-inch wafers and Gel-Pak.

#### **INTERNET ACCESS**

One visit to Micron's Web site will confirm that customer satisfaction continues to be a priority. We have dedicated significant resources to our Internet site in an effort to make complete product and service information readily available to our customers. Current data sheets are on line and ready for immediate access. Detailed information on our DRAM, RDRAM, DDR SDRAM, SDRAM, SLDRAM, SGRAM, SRAM, Module, Die and Flash offerings are provided to help our customers in selecting, ordering and obtaining the appropriate Micron device for their designs.

From our Web site, you can quickly look up Micron part numbers, identify local sales representatives and distributors, obtain product availability information or receive technical assistance from one of our Applications Engineers.

From products and service, to technology, to company news and employment—all of the information you need is at your fingertips.

Use the Internet to reach any Micron contact as well. All you need is the individual's "username" and you have the address: username@micron.com. It's that simple. Visit the Micron Web site or contact us by e-mail.

#### QUALITY

Quality is the most important thing we provide to our customers with each Micron shipment. That's because we believe that quality must be internalized consistently at each level of our company. We provide every Micron team member with the training and motivation needed to make Micron's quality philosophy a reality.

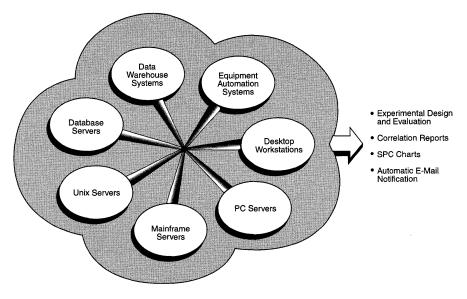

One way we have measurably improved both productivity and product quality is through our own quality improvement program formed by individuals throughout the company. Micron quality teams get together to address a wide range of issues within their areas. We consistently and regularly perform a company-wide selfassessment based on the Malcolm Baldrige National Quality Award criteria. We've also implemented statistical process controls to evaluate every facet of the memory design, fabrication, assembly and shipping process. And our AMBYX intelligent burn-in and test system\* gives Micron a unique edge in product reliability.

These quality programs have resulted in Micron becoming one of the first U.S. semiconductor manufacturers to receive ISO 9001 certification. ISO 9001 is the most comprehensive level of certification in the internationally recognized ISO family of specifications. The certification confirms that Micron's systems for accepting orders, reviewing customers' specifications, manufacturing and testing products, and delivering those products to our customers are quality controlled and produce consistent results.

\*For more information on AMBYX, see Section 5.

£

#### **ABOUT THIS BOOK**

#### CONTENT

Micron's 1999 *Memory Data Book* provides abbreviated lata sheets on Micron's line of DRAMs, SRAMs and Flash vlemory. For the most up-to-date, full-length data sheets, please visit our Web site at www.micron.com/mti or call he Micron Literature Room at 208-368-3900.

#### SECTION ORGANIZATION

Micron's 1999 *Memory Data Book* contains a detailed [able of Contents with a sequential index of products, as vell as product selection guides at the beginning of each ection. The *Data Book* is organized into seven sections:

- Section 1: DRAM selection guide and DRAM component and module data sheets.

- Section 2: SRAM selection guide and SRAM data sheets.

- Section 3: Flash Memory selection guide and Flash data sheets.

- Section 4: DRAM, SRAM and Flash technical notes.

- Section 5: Summary of Micron's unique quality and reliability programs and testing operation, including our AMBYX intelligent burn-in and test system.\*

- Section 6: Package information for DRAM, SRAM and Flash memory components and for DRAM modules.

- Section 7: Customer service notes and sales information, including part numbering guides and a list of sales representatives and distributors worldwide.

#### DATA SHEET SEQUENCE

Data sheets in this book are ordered first by width and second by depth. For example, the ZBT SRAM section begins with the  $128K \times 18$ , followed by all other  $\times 18$  configurations in order of ascending depth.

#### DATA SHEET DESIGNATIONS

As detailed in the table below, each Micron product data sheet is classified as either Advance, Preliminary (indicated on the top of each data sheet) or Final (final data sheets have no marking).

#### SURVEY

We have included a removable, postage-paid survey form in the front of this book. Your time in completing and returning this survey will enhance our efforts to continually improve our product literature.

For more information on Micron product literature, or to order additional copies of this publication, contact:

Micron Semiconductor Products, Inc. 8000 S. Federal Way P.O. Box 6 Boise, ID 83707-0006 Phone: 208-368-3900 Fax: 208-368-4617 E-mail: prodmktg@micron.com Customer Comment Line: 800-932-4992 Customer Comment Fax: 01-208-368-5018

#### **)ATA SHEET DESIGNATIONS**

| DATA SHEET MARKING | DEFINITION                                                                                                                                                                                                                                                                                  |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advance            | This data sheet contains initial descriptions of products still under development.                                                                                                                                                                                                          |

| Preliminary        | This data sheet contains initial characterization limits that are subject to change upon full characterization of production devices.                                                                                                                                                       |

| No Marking         | This data sheet contains minimum and maximum limits specified over the complete power supply and temperature range for production devices. Although considered final, these specifications are subject to change, as further product development and data characterization sometimes occur. |

#### IOTE: Micron uses acronyms to refer to certain industry-standard-setting bodies. These are defined below: EIA/JEDEC—Electronics Industry Association/Joint Electron Device Engineering Council PCMCIA—Personal Computer Memory Card International Association

Vicron's Quality/Reliability Handbook is available by calling 208-368-3900.

xii

#

| DRAM                          | 1 |

|-------------------------------|---|

| SRAM                          | 2 |

| FLASH MEMORY                  | 3 |

| TECHNICAL NOTES               | 4 |

| PRODUCT RELIABILITY           | 5 |

| PACKAGE INFORMATION           | 6 |

| SALES AND SERVICE INFORMATION | 7 |

| DRAM              | 1     |

|-------------------|-------|

| DDR/SLDRAM/RDRAM  | 1-1   |

| SDRAM             | 1-17  |

| SGRAM             | 1-51  |

| EDO DRAM          | 1-55  |

| FPM DRAM          | 1-69  |

| SDRAM DIMM/SODIMM | 1-81  |

| SGRAM SODIMM      | 1-153 |

| DRAM DIMM/SODIMM  | 1-157 |

#### DDR/SLDRAM/RDRAM PRODUCT SELECTION GUIDE

|           | Memory        | Part        |         | Clock <sup>1</sup> |           | Packa | ge/No. o | f Pins |      |

|-----------|---------------|-------------|---------|--------------------|-----------|-------|----------|--------|------|

| Product   | Configuration | Number      | Voltage | (MHz)              | Data Rate | FBGA  | TSOP     | TQFP   | Page |

| DDR SDRAM | 16 Meg x 4    | MT46V16M4   | 2.5V    | 100, 133           | 2x        | I     | 66       | -      | 1-3  |

| DDR SDRAM | 32 Meg x 4    | MT46V32M4   | 2.5V    | 100, 133           | 2x        | -     | 66       | _      | 1-7  |

| DDR SDRAM | 64 Meg x 4    | MT46V64M4   | 2.5V    | 100, 133           | 2x        | -     | 66       | -      | 1-9  |

| DDR SDRAM | 8 Meg x 8     | MT46V8M8    | 2.5V    | 100, 133           | 2x        | -     | 66       | -      | 1-3  |

| DDR SDRAM | 16 Meg x 8    | MT46V16M8   | 2.5V    | 100, 133           | 2x        | -     | 66       | -      | 1-7  |

| DDR SDRAM | 32 Meg x 8    | MT46V32M8   | 2.5V    | 100, 133           | 2x        | -     | 66       | —      | 1-9  |

| DDR SDRAM | 4 Meg x 16    | MT46V4M16   | 2.5V    | 100, 133           | 2x        | —     | 66       | -      | 1-3  |

| DDR SDRAM | 8 Meg x 16    | MT46V8M16   | 2.5V    | 100, 133           | 2x        |       | 66       | -      | 1-7  |

| DDR SDRAM | 16 Meg x 16   | MT46V16M16  | 2.5V    | 100, 133           | 2x        | -     | 66       | -      | 1-9  |

| RDRAM     | 8 Meg x 18    | MT6V8M18    | 2.5V    | 300, 400           | 2x        | 54    | -        | -      | 1-13 |

| SLDRAM    | 8 Meg x 18    | MT49V8M18C  | 2.5V    | 400                | 2x        | TBD   | -        | _      | 1-11 |

| DDR SGRAM | 512K x 32     | MT45V512K32 | 2.5V    | 150, 167           | 2x        | _     | _        | 100    | 1-1  |

| DDR SDRAM | 2 Meg x 32    | MT46V2M32   | 2.5V    | 150, 167           | 2x        | _     | _        | 100    | 1-5  |

NOTE: 1. DDR SDRAM (x4, x8, x16) clock rate at CAS latency of 2. DDR SGRAM (x32) clock rate at CAS latency of 3. DDR SDRAM (x32) clock rate at CAS latency of 3.

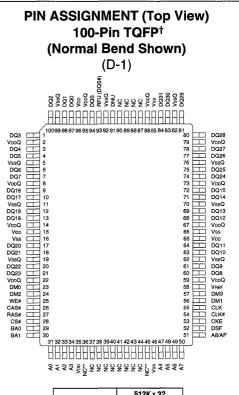

# DOUBLE DATA RATE SGRAM

## MT45V512K32 - 128K x 32 x 4 banks

For the latest data sheet, please refer to the Micron Web site: www.micron.com/mti/msp/html/datasheet.html

#### FEATURES

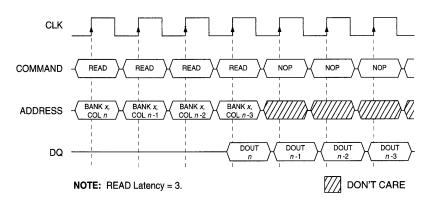

- Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle

- Bidirectional, intermittent data strobe (DQS) transmitted/received with data and used in capturing data at the receiver

- DQS edge-aligned with data for READs; centeraligned with data for WRITEs

- Differential clock inputs (CLK and CLK#)

- DLL to align DQ and DQS transitions with CLK transitions (JEDEC mode only)

- Commands entered on each positive CLK edge; data referenced to both edges of DQS

- Four internal banks for concurrent operation: 128K x 32 x 4 banks, with 9 row- and 8 column-address bits per bank

- Burst lengths: 2, 4, 8 or full page

- Auto precharge option for each burst access

- 16-column BLOCK WRITE

- BYTE WRITE operation (masking via DM0-3)

- · Auto Refresh and Self Refresh Modes

- 16ms, 2,048-cycle auto refresh (7.8µs/cycle)

- 2.5V (SSTL\_2 compatible) I/O

- +2.5V ±0.2V VDD, +2.5V ±0.2V VDDQ

- Same footprint as 2 Meg x 32 DDR SDRAM

#### **OPTIONS**

#### MARKING

- Timing JEDEC Mode Cycle Time (Clock Frequency) 6ns (≤ 167 MHz) @ CL = 3

-6

6.5ns (≤ 150 MHz) @ CL = 3

-65

- Plastic Package

100-pin TQFP (0.65mm lead pitch)

LG

100-pin TQFP, Reverse Bend

RG

- · Part Number Example: MT45V512K32LG-6

## **(EY TIMING PARAMETERS (JEDEC Mode)**

| SPEED | CLOCK FREQU | JENCY (1/ <sup>t</sup> ck) | ACCESS               | DQ-DQS                 |

|-------|-------------|----------------------------|----------------------|------------------------|

| GRADE | CL = 2*     | CL = 3*                    | TIME                 | SKEW                   |

| -6    | 111 MHz     | 167 MHz                    | ±0.1 <sup>t</sup> CK | ±0.075 <sup>t</sup> CK |

| -65   | 100 MHz     | 150 MHz                    | ±0.1 <sup>t</sup> CK | ±0.075 <sup>t</sup> CK |

CL = CAS (READ) latency

|                   | 512K x 32           |

|-------------------|---------------------|

| Configuration     | 128K x 32 x 4 banks |

| Refresh Count     | 2K                  |

| Row Addressing    | 512 (A0-A8)         |

| Bank Addressing   | 4 (BA0, BA1)        |

| Column Addressing | 256 (A0-A7)         |

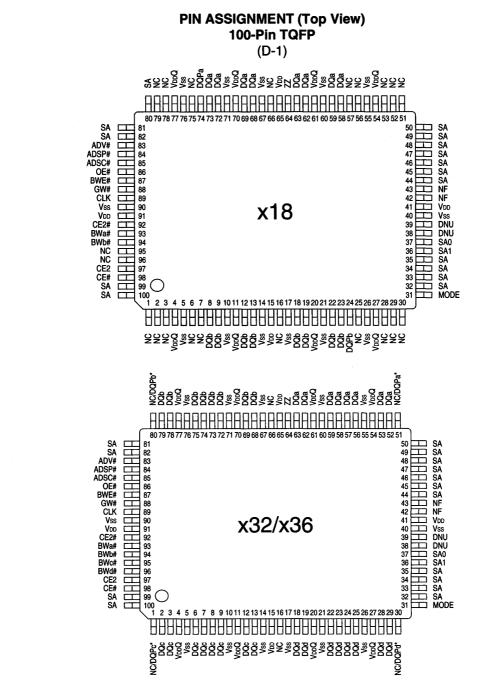

\*\*Reserved for 2 Meg x 32 DDR addressing †JEDEC standard MS-026 BHA (LQFP)

#### **16Mb DDR SGRAM PART NUMBERS**

| PART NUMBER   | ARCHITECTURE |

|---------------|--------------|

| MT45V512K32LG | 512K x 32    |

| MT45V512K32RG | 512K x 32    |

#### 512K x 32 DDR SGRAM •

#### NOTE

This device provides dual-mode operation: JEDEC mode and non-JEDEC mode. The recommended mode of operation for higher performance and/or more robust timing is the JEDEC mode. Accordingly, this document focuses primarily on the JEDEC mode of operation. The non-JEDEC mode differences are noted as exceptions in the text, and the non-JEDEC mode timing diagrams are included in Appendix I in the full-length version of this data sheet.

The device defaults to the non-JEDEC mode upon powerup to accommodate controllers designed for that mode of operation only. The device enters the JEDEC mode of operation when the DLL is enabled, via a LOAD MODE REGISTER command to the extended mode register. Once in the JEDEC mode, the device remains in that mode until powered down.

Note that the DLL may be disabled after entering JEDEC mode, but this mode of operation is provided for test and debug purposes only. Specifications unique to this mode of operation are not guaranteed.

#### **GENERAL DESCRIPTION**

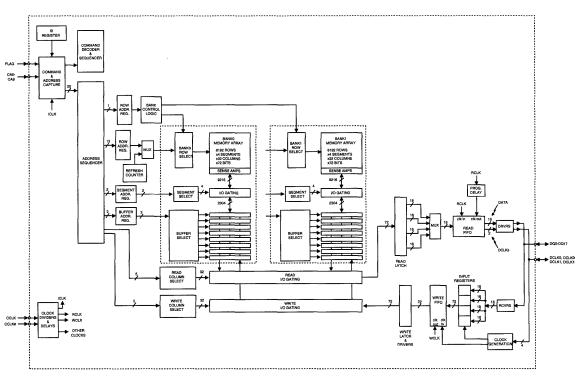

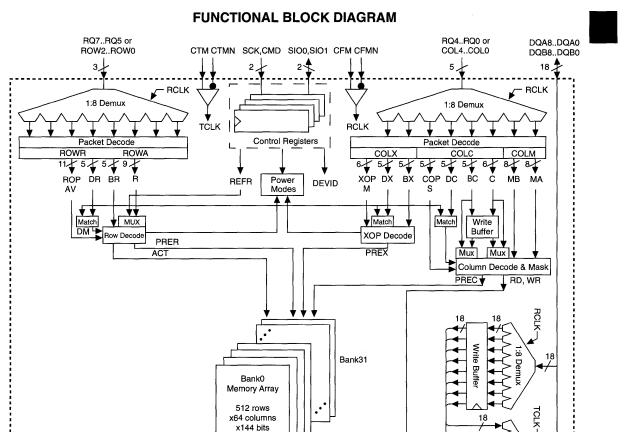

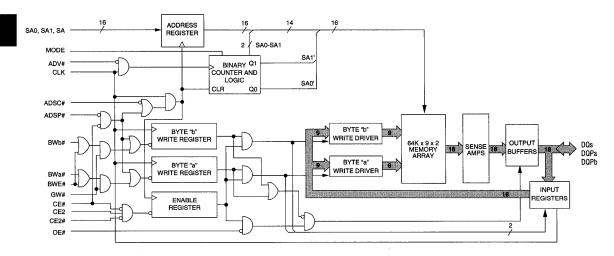

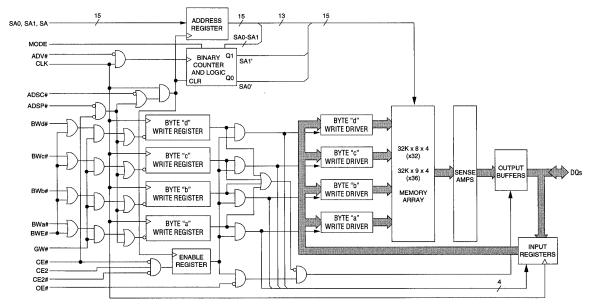

The 16Mb DDR SGRAM is a high-speed CMOS, dynamic random-access memory containing 16,777,216 bits. It is internally configured as a quad-bank DRAM, with each 4,194,304-bit bank organized as 512 rows by 256 columns by 32 bits.

The 16Mb DDR SGRAM uses a double data rate architecture to achieve high-speed operation. The double data rate architecture is essentially a 2*n* prefetch architecture with an interface designed to transfer two data words per clock cycle at the I/O pins. A single read or write access for the 16Mb DDR SGRAM consists of a single 64-bit, one-clockcycle data transfer at the internal DRAM core and two corresponding 32-bit, one-half-clock-cycle data transfers at the I/O pins.

A bidirectional data strobe (DQS) is transferred externally, along with data, for use in data capture at the receiver. DQS is an intermittent strobe transmitted by the DDR SGRAM during READs and by the memory controller during WRITES. DQS is edge-aligned with data for READs and center-aligned with data for WRITES. The 16Mb DDR SGRAM operates from a differential clock: CLK and CLK# (the crossing of CLK going HIGH and CLK# going LOW will be referred to as the positive edge of CLK). Commands (address and control signals) are registered at every positive edge of CLK. Input data is registered on both edges of DQS, and output data is referenced to both edges of DQS as well as to both edges of CLK.

Read and write accesses to the DDR SGRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an AC-TIVE command, which is then followed by a READ, WRITE or BLOCK WRITE command. The address bits registered coincident with the ACTIVE command are used to select the bank and row to be accessed (BA0, BA1 select the bank; A0-A8 select the row). The address bits registered coincident with the READ or WRITE command are used to select the bank and the starting column location for the burst access.

The DDR SGRAM provides for programmable READ or WRITE burst lengths of 2, 4 or 8 locations, or the full page. An AUTO PRECHARGE function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst sequence.

As with standard SGRAMs, the pipelined, multibank architecture of DDR SGRAMs allows for concurrent operation, thereby providing high effective bandwidth by hiding row precharge and activation time.

DDR SGRAMs differ from DDR SDRAMs in configuration and by providing 16-column BLOCK WRITE and full-page burst capability. The quad-bank pipelined architecture combined with the additional graphics functions results in a device particularly well suited to high-performance graphics applications or other highbandwidth applications.

The 16Mb DDR SGRAM is designed to operate in 2.5V, low-power memory systems. An auto refresh mode is provided, along with a power-saving power-down mode. All inputs are compatible with the JEDEC Standard for SSTL\_2. All outputs are SSTL\_2, Class II compatible.

# DOUBLE DATA RATE SDRAM

#### *'EATURES*

Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle Bidirectional, intermittent data strobe (DQS) transmitted/received with data and used in capturing data at the receiver DQS edge-aligned with data for READs; centeraligned with data for WRITEs Differential clock inputs (CLK and CLK#) DLL to align DQ and DQS transitions with CLK transitions Commands entered on each positive CLK edge; data referenced to both edges of DQS Four internal banks for concurrent operation Data mask (DM) for write data Burst lengths: 2, 4 or 8 Auto precharge option for each burst access Auto Refresh and Self Refresh Modes 64ms, 4,096-cycle refresh 2.5V (SSTL\_2 compatible) I/O +2.5V ±0.2V VDD, +2.5V ±0.2V VDDQ

#### **)PTIONS**

#### MARKING

TG

| Configuratio | n                      |      |

|--------------|------------------------|------|

| 16 Meg x 4   | (4 Meg x 4 x 4 banks)  | 16M4 |

| 8 Meg x 8    | (2 Meg x 8 x 4 banks)  | 8M8  |

| 4 Meg x 16   | (1 Meg x 16 x 4 banks) | 4M16 |

Plastic Package 66-pin TSOP (400 mil width, 0.65mm pin pitch)

| Timing - Cycle Time |     |

|---------------------|-----|

| 7.5ns @ CL = 2      | -75 |

| 10ns @ CL = 2       | -10 |

Part Number Example: MT46V8M8TG-75

#### **CEY TIMING PARAMETERS**

| SPEED | CLOCK FREQ | CLOCK FREQUENCY (1/ <sup>4</sup> CK) |  |  |

|-------|------------|--------------------------------------|--|--|

| GRADE | CL = 2*    | CL = 2.5*                            |  |  |

| -75   | 133 MHz    | 150 MHz                              |  |  |

| -10   | 100 MHz    | 133 MHz                              |  |  |

L = CAS (READ) latency

MT46V16M4 - 4 Meg x 4 x 4 banks MT46V8M8 - 2 Meg x 8 x 4 banks MT46V4M16 - 1 Meg x 16 x 4 banks

For the latest data sheet, please refer to the Micron Web site: www.micron.com/mti/msp/html/datasheet.html