# MICROCHIP DATA BOOK

# **Microchip Data Book**

# **1992 Second Edition**

SERVING A COMPLEX AND COMPETITIVE WORLD WITH USER - PROGRAMMABLE EMBEDDED CONTROL SYSTEM SOLUTIONS

"Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. No representation or warranty is given and no liability is assumed by Microchip Technology Inc. with respect to the accuracy or use of such information, or infringement of patents arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights." TI and TMS320 are trademarks of Texas Instruments Inc. DEC, VAX, VMS, and ULTRIX are trademarks of Digital Equipment Corp. MACINTOSH is a trademark of Apple Computer, Inc. IBM and IBM PC are trademarks of IBM Corp. I<sup>2</sup>C<sup>TM</sup> is a trademark of National Semiconductor. SMC is a trademark of National Semiconductor. SMC is a trademark of Standard Microsoft. PICPAK, PIC-ICE, PICPRO, PICALC, PICSIM, PROMASTER and PICMASTER are trademarks of Microchip Technology Inc. PIC is a registered trademark of Microchip Technology Inc. The Microchip logo and name is a registered trademark of Microchip Technology Incorporated. All rights reserved. Copyright © 1992, Microchip Technology Inc.

© 1992 Microchip Technology

Page

| SECTION 1 | MICROCONTROLI                        | ER PRODUCT SPECIFICATIONS                                           |  |  |  |

|-----------|--------------------------------------|---------------------------------------------------------------------|--|--|--|

|           | PIC®16C5X                            | EPROM-Based 8-Bit CMOS Microcontroller Series                       |  |  |  |

|           | PIC®16CR54                           | ROM-Based 8-Bit CMOS Microcontroller                                |  |  |  |

|           | PIC®16C71                            | 8-Bit CMOS EPROM Microcontroller with A/D Converter                 |  |  |  |

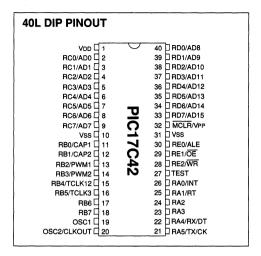

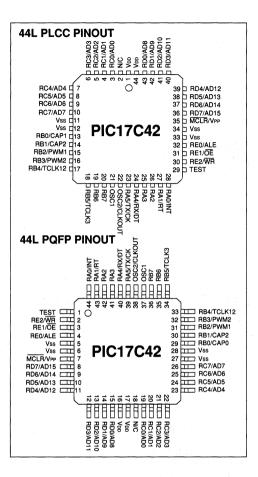

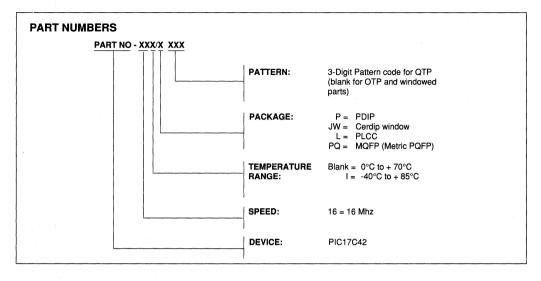

|           | PIC <sup>®</sup> 17C42               | High Performance 8-Bit CMOS EPROM Microcontroller                   |  |  |  |

| SECTION 2 | DEVELOPMENT SY                       | /STEMS                                                              |  |  |  |

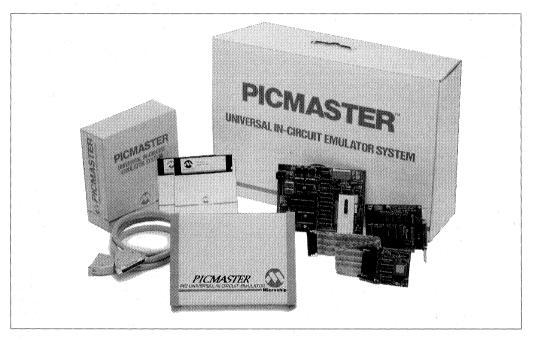

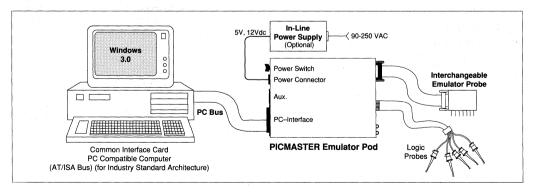

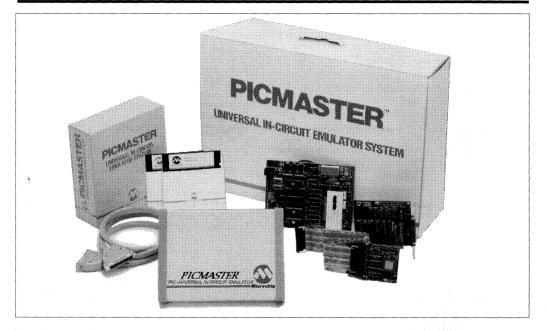

|           | PICMASTER-16™                        | PICMASTER Universal In-Circuit Emulator System                      |  |  |  |

|           | PICMASTER-17™                        | PICMASTER PIC®17CXX In-Circuit Emulator System                      |  |  |  |

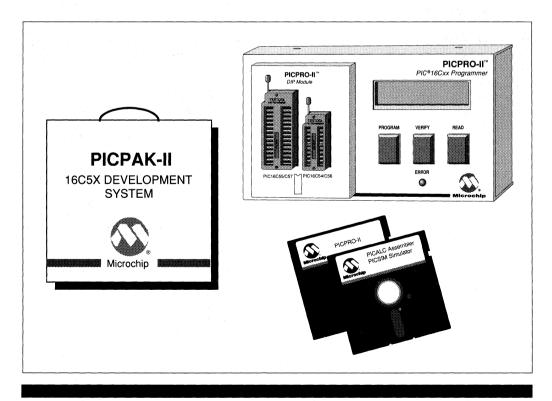

|           | PICPAK-II™                           | PIC®16C5x Low-Cost Microcontroller Development System               |  |  |  |

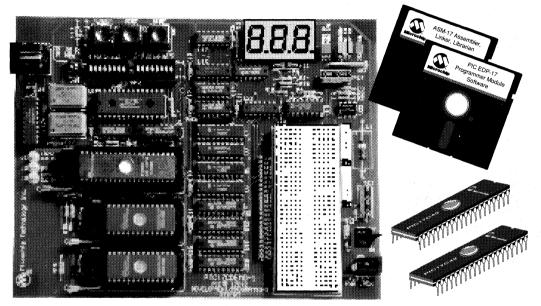

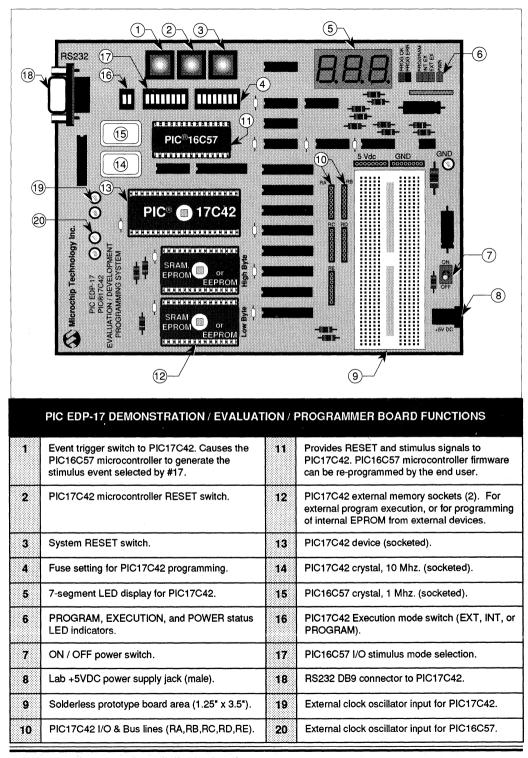

|           | PICPAK-17™                           | PIC®17C42 Evaluation/Development/Programmer Kit                     |  |  |  |

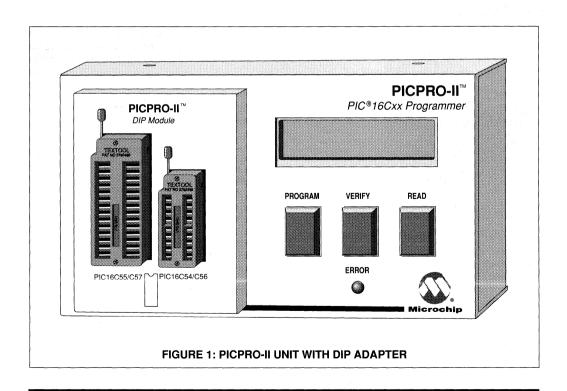

|           | PICPRO-II™                           | PIC®16C5x Microcontroller EPROM Programmer Unit2- 17                |  |  |  |

|           | PRO MASTER™                          | CMOS PIC® Microcontroller Programmer Unit                           |  |  |  |

|           |                                      |                                                                     |  |  |  |

| SECTION 3 | SERIAL EEPROM PRODUCT SPECIFICATIONS |                                                                     |  |  |  |

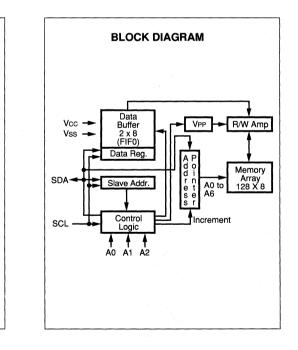

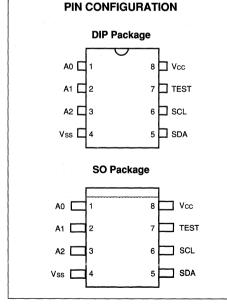

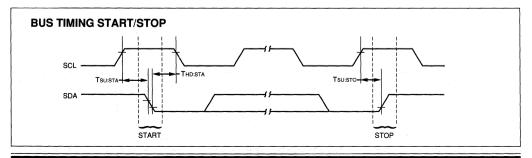

|           | 24C01A                               | 1K (128 x 8) CMOS Serial Electrically Erasable PROM                 |  |  |  |

|           | 24C02A                               | 2K (256 X 8) CMOS Serial Electrically Erasable PROM3- 9             |  |  |  |

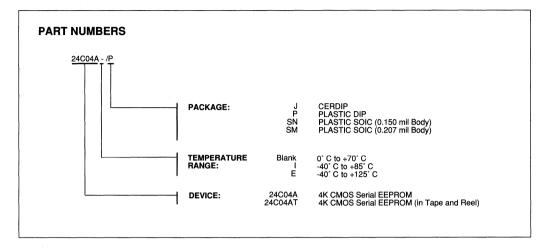

|           | 24C04A                               | 4K (512 x 8) CMOS Serial Electrically Erasable PROM3- 17            |  |  |  |

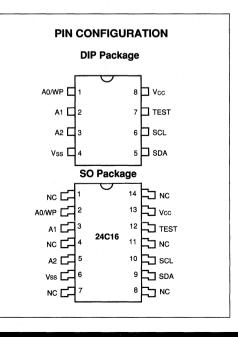

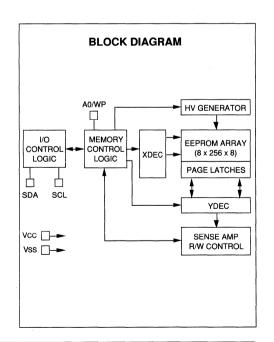

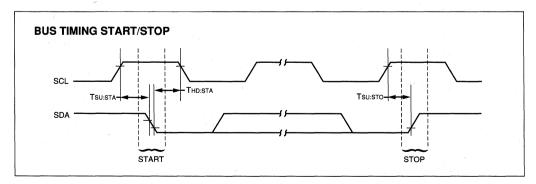

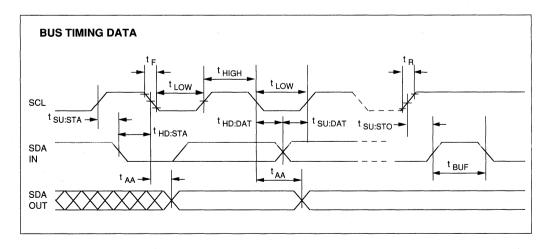

|           | 24C16                                | 16K (8x256x8) CMOS Serial Electrically Erasable PROM3- 25           |  |  |  |

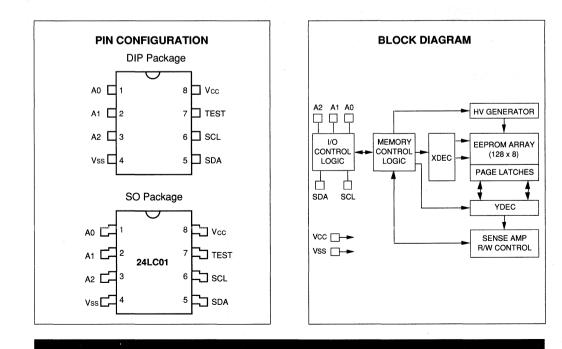

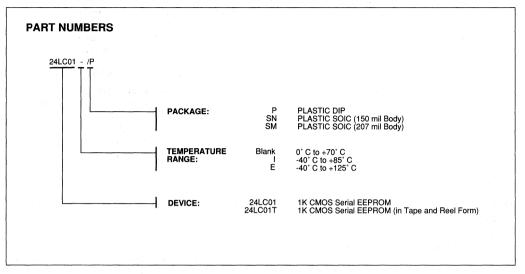

|           | 24LC01                               | 1K (128 x 8) CMOS Serial Electrically Erasable PROM                 |  |  |  |

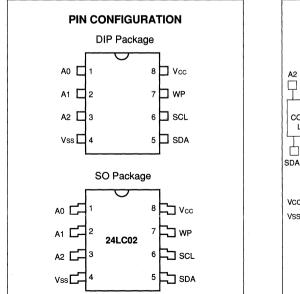

|           | 24LC02                               | 2K (256 x 8) CMOS Serial Electrically Erasable PROM                 |  |  |  |

|           | 24LC04                               | 4K (512 x 8) CMOS Serial Electrically Erasable PROM3- 49            |  |  |  |

|           | 24LC16                               | 16K (8 x 256 x 8) CMOS Serial Electrically Erasable PROM3- 57       |  |  |  |

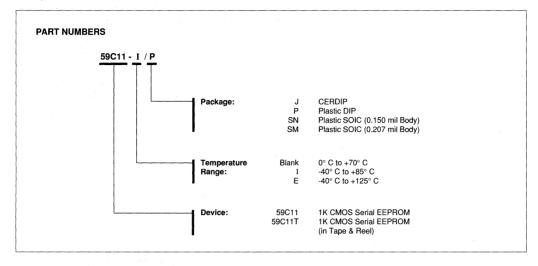

|           | 59C11                                | 1K (128 x 8 or 64 x 16) CMOS Serial Electrically Erasable PROM3- 65 |  |  |  |

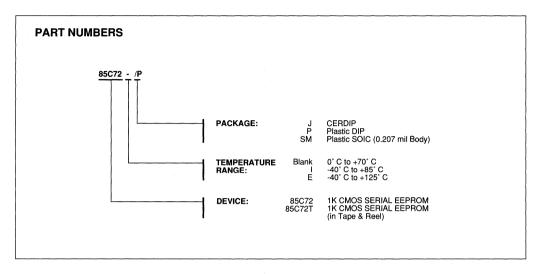

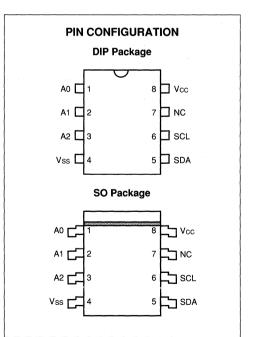

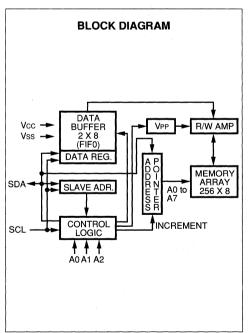

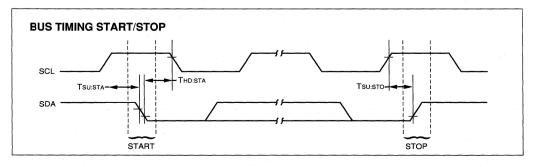

|           | 85C72                                | 1K (128 x 8) CMOS Serial Electrically Erasable PROM3- 73            |  |  |  |

|           | 85C82                                | 2K (256 x 8) CMOS Serial Electrically Erasable PROM                 |  |  |  |

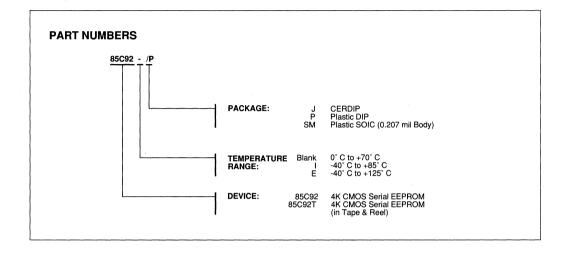

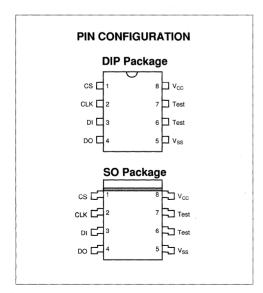

|           | 85C92                                | 4K (512 x 8) CMOS Serial Electrically Erasable PROM3- 89            |  |  |  |

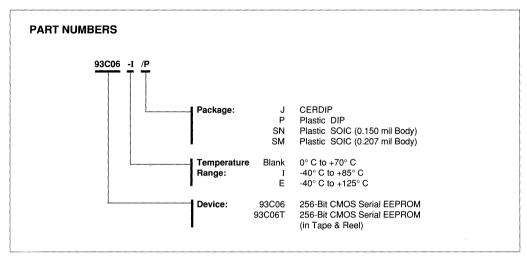

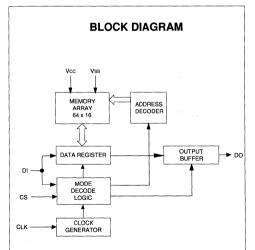

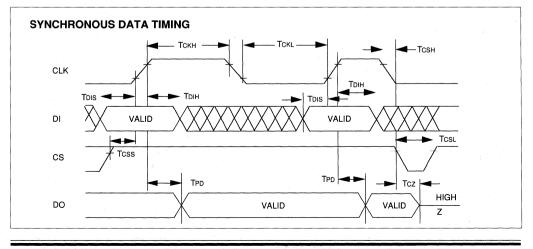

|           | 93C06                                | 256 Bits (16 x 16) CMOS Serial Electrically Erasable PROM           |  |  |  |

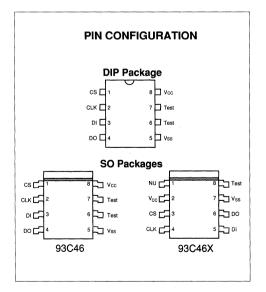

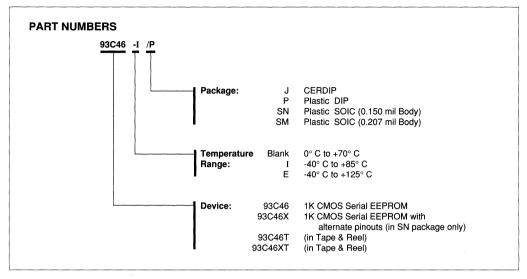

|           | 93C46                                | 1K (64 x 16) CMOS Serial Electrically Erasable PROM3-105            |  |  |  |

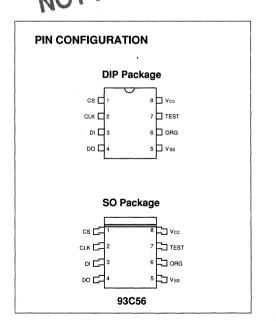

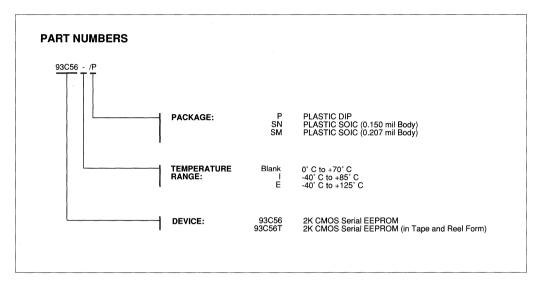

|           | 93C56                                | 2K (256 x 8 or 128 x 16) CMOS Serial Electrically Erasable PROM     |  |  |  |

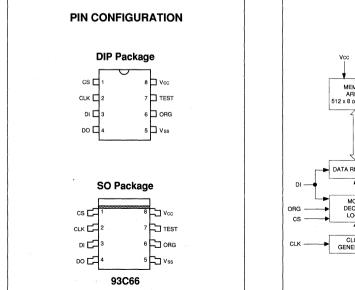

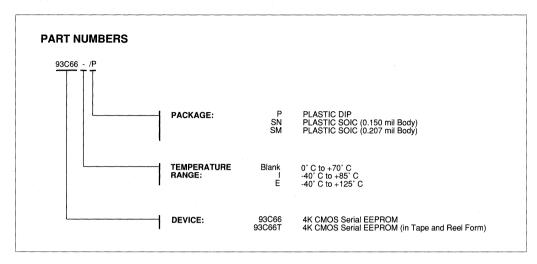

|           | 93C66                                | 4K (512 x 8 or 256 x 16) CMOS Serial Electrically Erasable PROM     |  |  |  |

|           | 93LC46/56/66                         | CMOS Serial Electrically Erasable PROM                              |  |  |  |

|           | 93LCS56                              | 2K CMOS Serial Electrically Erasable PROM3-137                      |  |  |  |

|           | 93LCS66                              | 4K CMOS Serial Electrically Erasable PROM                           |  |  |  |

2

1

# **Table of Contents**

### Page

| SECTION 4 | EEPROM PRODUCT SPECIFICATIONS     |                                                    |    |  |  |  |

|-----------|-----------------------------------|----------------------------------------------------|----|--|--|--|

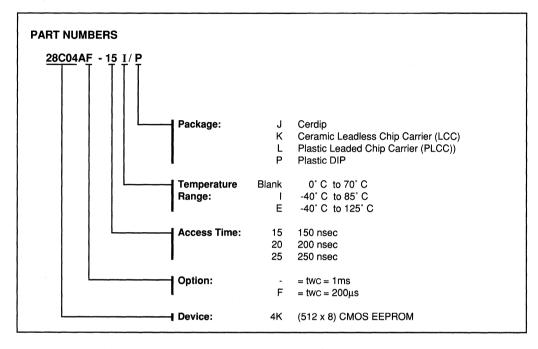

|           | 28C04A                            | 4K (512 x 8) CMOS Electrically Erasable PROM       | 1  |  |  |  |

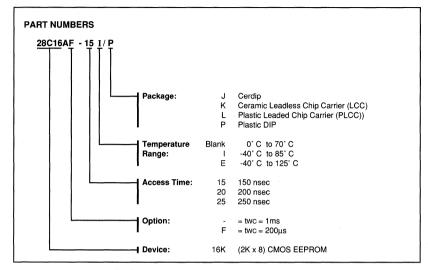

|           | 28C16A                            | 16K (2K x 8) CMOS Electrically Erasable PROM4-     | ç  |  |  |  |

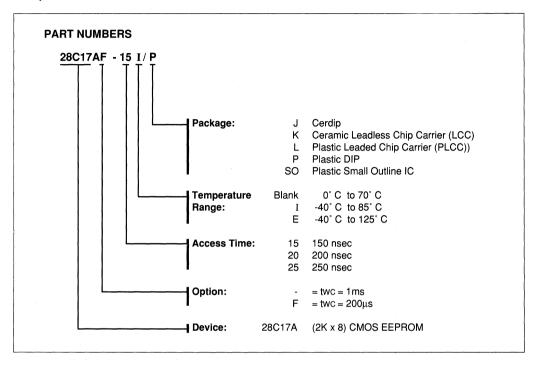

|           | 28C17A                            | 16K (2K x 8) CMOS Electrically Erasable PROM       | 17 |  |  |  |

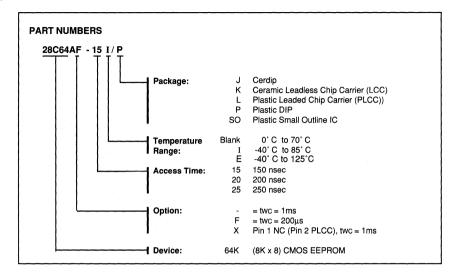

|           | 28C64A                            | 64K (8K x 8) CMOS Electrically Erasable PROM4-     | 25 |  |  |  |

|           |                                   |                                                    |    |  |  |  |

| SECTION 5 | EPROM PRODUCT SP                  |                                                    |    |  |  |  |

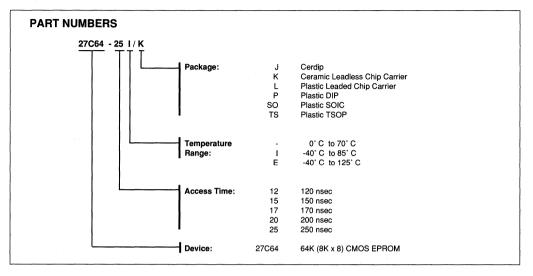

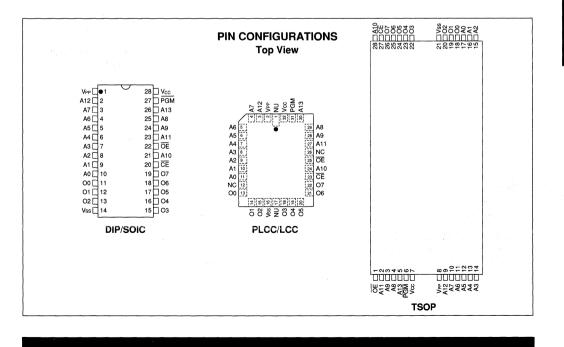

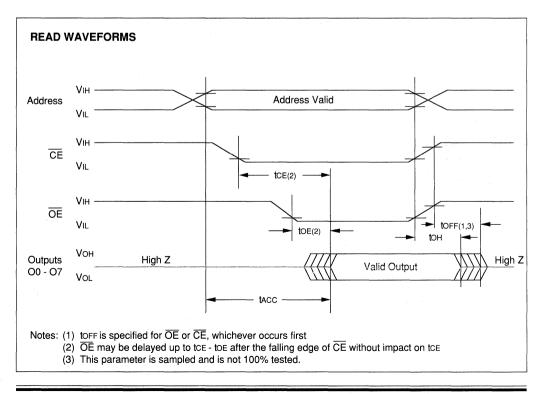

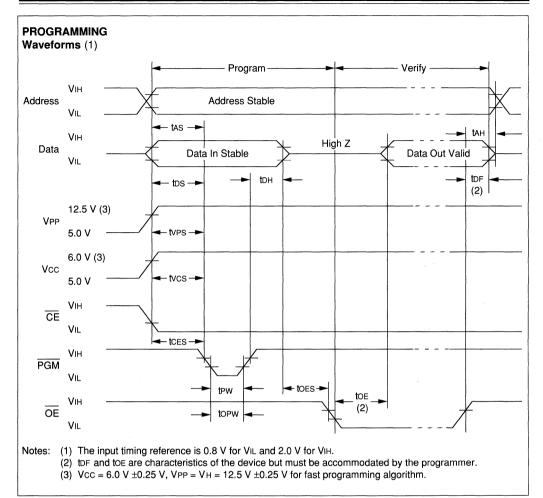

|           | 27C64                             | 64K (8K x 8) CMOS UV Erasable PROM5-               |    |  |  |  |

|           | 27C128                            | 128K (16K x 8) CMOS UV Erasable PROM5-             |    |  |  |  |

|           | 27C256                            | 256K (32K x 8) CMOS UV Erasable PROM               |    |  |  |  |

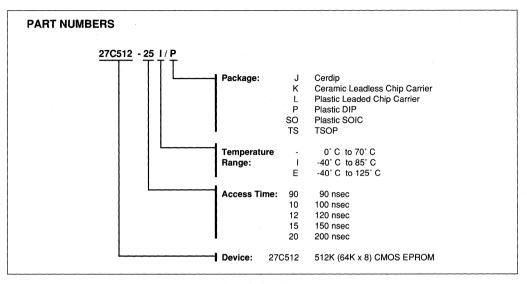

|           | 27C512                            | 512K (64K x 8) CMOS UV Erasable PROM5-             |    |  |  |  |

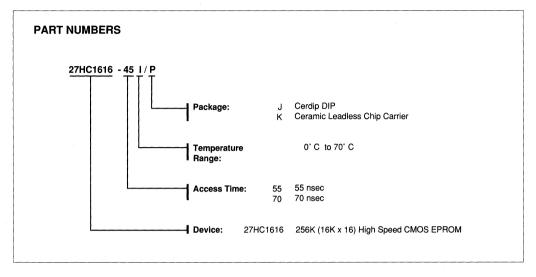

|           | 27HC1616                          | 256K (16K x 16) High Speed CMOS UV Erasable PROM5- |    |  |  |  |

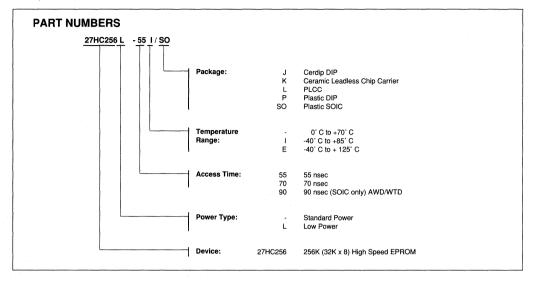

|           | 27HC256                           | 256K (32K x 8) High Speed CMOS UV Erasable PROM5-  |    |  |  |  |

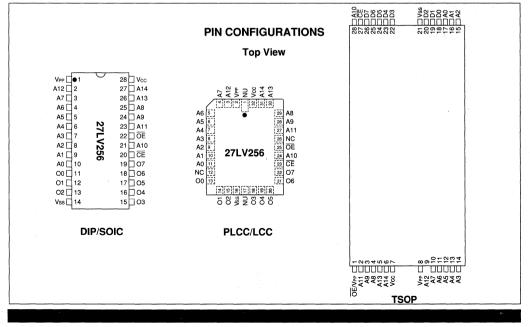

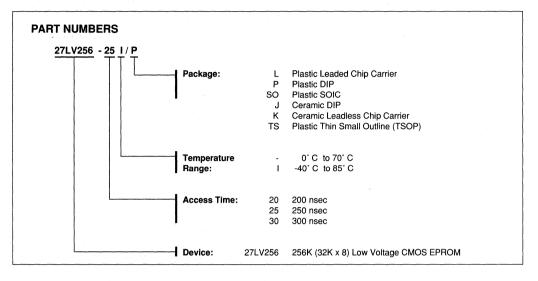

|           | 27LV256                           | 256K (32K x 8) Low Voltage CMOS Erasable PROM5-    | 49 |  |  |  |

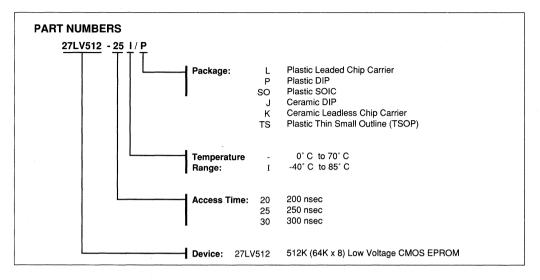

|           | 27LV512                           | 512K (64K x 8) Low Voltage CMOS Erasable PROM5-    | 57 |  |  |  |

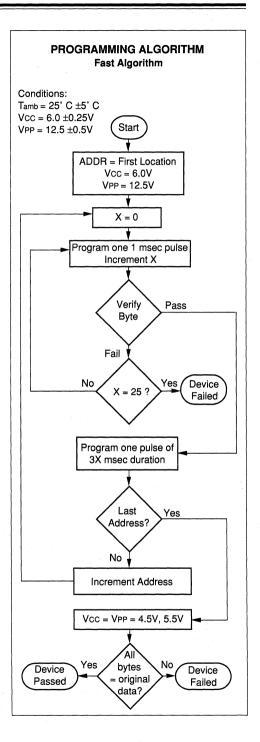

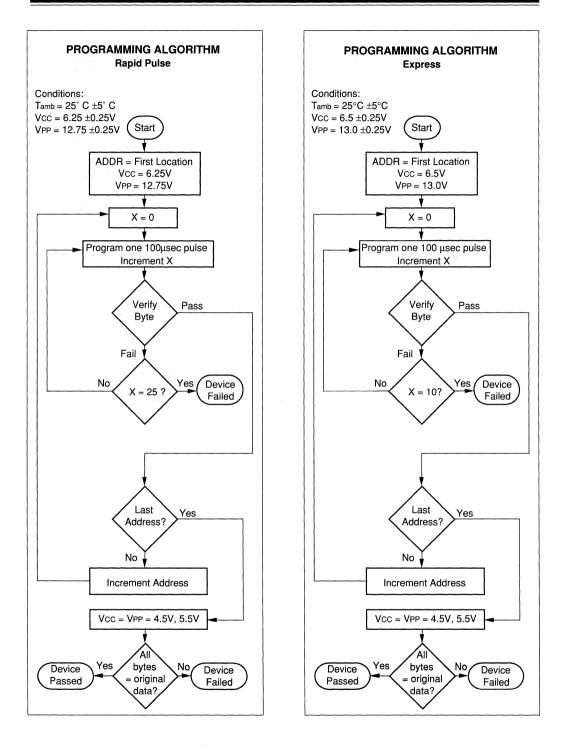

|           | 27CXXX                            | 27CXXX EPROM Family Programming Algorithm5-        | 65 |  |  |  |

| SECTION 6 | LOGIC PRODUCTS                    |                                                    |    |  |  |  |

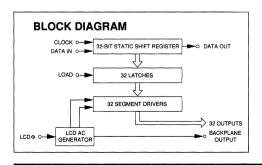

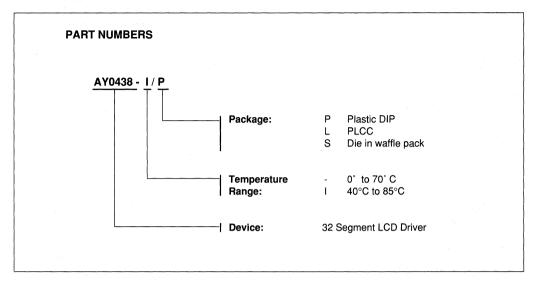

|           | AY0438                            | 32-Segment CMOS LCD Driver6-                       |    |  |  |  |

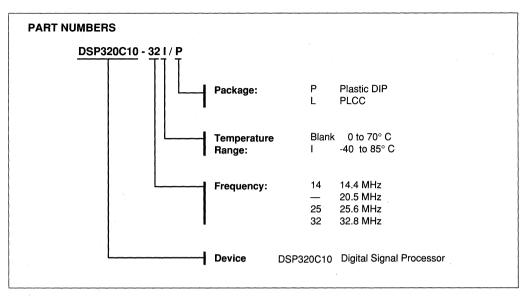

|           | DSP                               | Product Portfolio                                  |    |  |  |  |

|           | DSP320C10                         | CMOS Digital Signal Processor                      |    |  |  |  |

|           | D3F320010                         |                                                    |    |  |  |  |

| SECTION 7 | QUALITY AND RELIABILITY           |                                                    |    |  |  |  |

|           | Quality Without Comprom           | ise7-                                              |    |  |  |  |

|           |                                   | /                                                  |    |  |  |  |

|           | с ,                               |                                                    |    |  |  |  |

| SECTION 8 | PACKAGING                         |                                                    |    |  |  |  |

|           | Packaging Outlines and Dimensions |                                                    |    |  |  |  |

|           |                                   |                                                    |    |  |  |  |

| APPENDIX  | OFFICE LOCATIONS                  |                                                    |    |  |  |  |

|           | Factory Representatives           | A-                                                 |    |  |  |  |

|           |                                   |                                                    | 1  |  |  |  |

|           | Distributors                      | A-                                                 |    |  |  |  |

|           | Distributors<br>Factory Sales     | A                                                  |    |  |  |  |

|           |                                   |                                                    |    |  |  |  |

|           |                                   |                                                    |    |  |  |  |

4

5

6

7

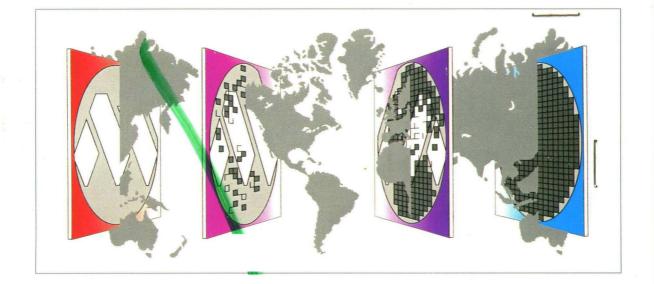

# SERVING A COMPLEX AND COMPETITIVE WORLD WITH USER-PROGRAMMABLE EMBEDDED CONTROL SYSTEM SOLUTIONS

"Microchip Technology draws its impetus from the technology expectations of a large base of longstanding customers. Microchip is small enough to respond quickly with technology to serve our customers' needs. Moreover, as a fully integrated IC Manufacturer, Microchip deploys its panoply of resources to act timely and efficiently, and on a worldwide scale: Technology Development, Design, Wafer Fabrication, Assembly and Test, Quality, Reliability and Customer Support.

"Worldwide competition leaves no room for divergence or mediocrity. Microchip Technology, committed to focus on and continuously improve all the aspects of its business, has a unique corporate culture. To improve performance, our employees are encouraged to analyze their methods continually. Personal empowerment expands the capability of personal responsibility to continually serve our customers better.

"Our industry's life-line is innovation. The fast pace of technological change is inherent in our industry. Microchip Technology has accelerated the rate of change of its technology and products to leadership in providing user-programmable space-sensitive embedded control solutions.

"Change is our ally. Driving and managing customer-focused change is our winning strategy."

Stove Saugh

Steve Sanghi President & Chief Executive Officer

Motivated by customer requirements....

...and powered by continuous improvement...

...riding and leading the wave of technological change.

# MICROCHIP TECHNOLOGY INCORPORATED

# **Company Profile**

# HIGHLIGHTS

- Focused on user-programmable embedded control solutions

- Providing RISC 8-bit user-programmable microcontrollers and supporting logic products

- Providing Serial and Parallel EEPROMs and EPROMs

- A unique corporate culture dedicated to continuous improvement

- Research and development of high performance

user-programmable products

- · A history of innovation

- An experienced executive team focussed on innovation

- Quality without compromise

- · Fully integrated manufacturing

- A global network of manufacturing and customer support facilities

# **BUSINESS SCOPE**

Microchip Technology Inc. manufactures and markets a variety of VLSI CMOS semiconductor components to support the user-programmable embedded control market. In particular, the company specializes in highly integrated, user-programmable RISC microcontrollers and related non-volatile memory products to meet growing market requirements for high performance, yet economical embedded control capability in an increasing number of price-sensitive products. Microchip's products feature the industry's most economical OTP (one-time programmable) capability, along with the compact size, integrated functionality, ease of development and technical support so essential to timely and cost-effective product development by our customers.

# **MARKET FOCUS**

Microchip targets selected markets where our advanced designs, progressive process technology and industry leading operating speeds enable us to deliver decidedly superior performance. The firm has positioned itself to maintain a dominant role as a supplier of high performance user-programmable microcontrollers and associated memory and logic products for embedded control applications.

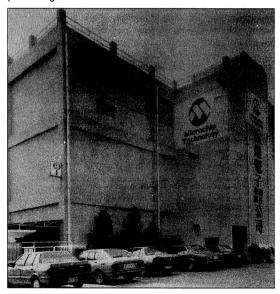

Company headquarters in Chandler, Arizona: Executive Offices, R & D, and Wafer Fabrication occupy this campus.

DS00027F-2

# **GUIDING VALUES**

#### **Customers Are Our Focus**

We establish successful customer partnerships by exceeding customer expectations for products, services and attitude. We earn our credibility through meeting commitments and producing quality products and services in a timely fashion. We believe each employee must effectively serve their internal customers in order for Microchip's external customers to be properly served.

#### **Quality Comes First**

We will perform correctly the first time, maintain customer satisfaction and measure our quality against requirements. We practice effective and standardized improvement methods, such as statistical process control to anticipate problems and implement root cause solutions. We believe that when quality comes first, reduced costs follow.

#### Continuous Improvement Is Essential

We utilize the concept of 'Vital Few" to establish our priorities. We concentrate our resources on continuously improving the Vital Few while empowering each employee to make continuous improvements in their area of responsibility. We strive for constructive and honest selfcriticism to identify improvement opportunities.

#### **Employees Are Our Greatest Strength**

We design jobs and provide opportunities in a fashion which clearly promotes pride in work, integrity, trust, teamwork, creativity, employee involvement and development, fairness, and productivity. We base recognition, advancement and compensation on an employee's achievement of excellence in team and individual performance. We provide for employee health and welfare by offering a competitive, comprehensive employee benefits program.

#### Products And Technology Are Our Foundation

We commit to ongoing investments and advancements in the design and development of our manufacturing process, device circuit and system technologies, which provide innovative, reliable and cost-effective products to support current and future market opportunities.

### **Total Cycle Times Are Competitive**

We focus resources to optimize cycle times to our customers by empowering employees to achieve efficient cycle times in their area of responsibility. We believe that cycle time reduction is achieved by streamlining processes through the systematic removal of barriers to productivity.

#### Safety Is Never Compromised

We place our concern for safety of our employees and community at the forefront of our decisions, policies and actions. Each employee is responsible for safety.

#### Profits Provide For Everything We Do

We strive to maintain competitive profits as they allow continued investments and future growth, and indicate the overall success of Microchip.

#### Communication Is Vital

We encourage open, honest, constructive, and ongoing communication in all company and community relationships to resolve issues, exchange information and share knowledge.

#### Suppliers, Representatives, And Distributors Are Our Partners

We maintain mutually beneficial partnerships with suppliers, representatives, and distributors who are an integral link in the achievement of our mission and guiding values.

#### Professional Ethics Are Practiced

We manage our business and treat customers, employees, shareholders, investors, suppliers, distributors, representatives, community and government in a manner that exemplifies our honesty, ethics and integrity. We recognize our responsibility to the community and are proud to serve as an equal opportunity employer.

# **PRODUCT FOCUS**

Microchip's product focus is user-programmable microcontrollers, nonvolatile memories and supporting logic. These product lines include PIC<sup>®</sup> microcontrollers, EEPROMs, and High Speed EPROMs in a broad range of technologies, speeds and packages.

Microchip is quick to capitalize on advances in one product line by incorporating those breakthroughs into other product families. Microchip targets selected markets where our advanced designs, progressive process technology and industry leading operating speeds enable us to deliver decidedly superior performance. The firm has recently positioned itself to play a dominant role as a supplier of high performance user-programmable microcontrollers and associated memory and logic products for embedded control applications.

PIC<sup>®</sup> Microcontrollers from Microchip combine high performance, low cost, and small package size. They offer the best price/ performance ratio in the industry. Large numbers of these devices are used in automotive and cost-sensitive consumer products, such as remote controls and appliances, computer peripherals, data entry, office automation, automotive control systems, security, and telecom applications.

The widely accepted NMOS PIC16XX (over 75 million units shipped) and CMOS PIC16CXX and PIC17CXX series are the industry's only 8-bit microcontrollers using a high speed RISC architecture. Microchip pioneered the use of RISC architecture to obtain high speed and instruction efficiency. The CMOS PIC16CXX is in high volume production, with more than 25 million units shipped, and has achieved nearly five thousand design wins worldwide.

The PIC17CXX family is the world's highest performance 8-bit microcontroller. It continues PIC's high performance RISC architecture with an 8-bit data word and 16-bit instruction word, allowing expanded internal/external memory. The PIC17C42 incorporates advanced motor control peripherals allowing control of two single-phase motors with a single PIC17C42. High performance inter-controller communications can be implemented with the PIC17C42's 4-megabits-per-second serial I/O.

Future CMOS PIC product families will include advanced features, such as higher speed, additional I/O, sophisticated timers, embedded A/D, extended instruction/data memory, inter-processor communication, and ROM, EPROM and E<sup>2</sup>PROM memories.

Both PIC16CXX and PIC17CXX families are supported by a range of user-friendly development systems including programmers, emulators and demonstration boards.

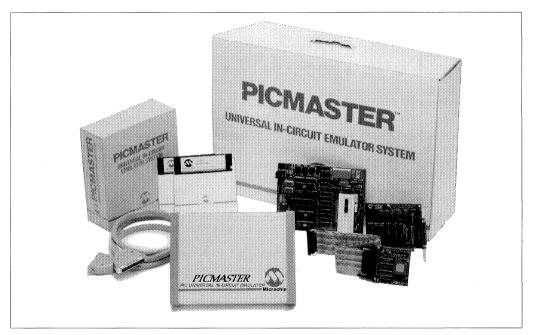

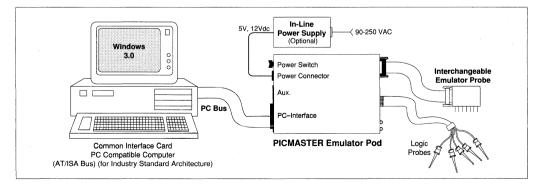

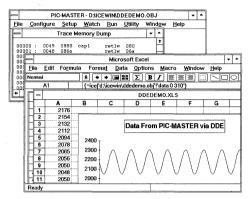

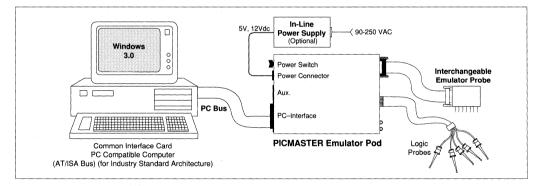

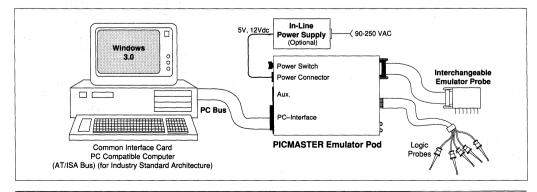

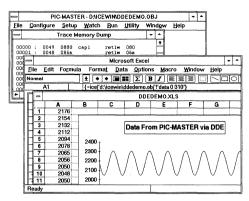

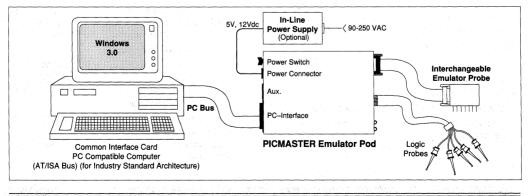

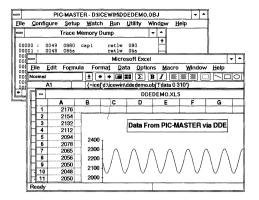

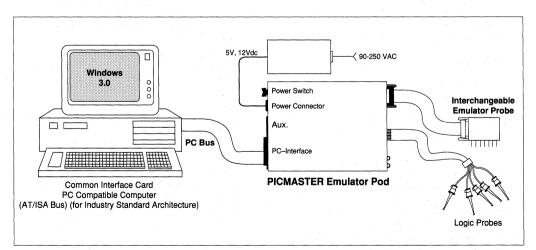

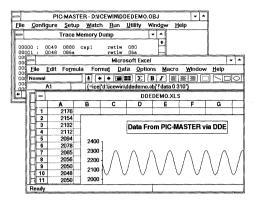

PICMASTER<sup>™</sup> is an advanced real-time emulator system using the user friendly Windows® software environment. PICMAS-TER<sup>™</sup> is a Microchip-designed universal emulator for both PIC16CXX and PIC17CXX families. PIC PRO II and PRO MASTER are advanced low cost programmers.

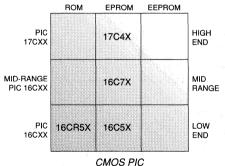

# MICROCONTROLLERS

CMOS PIC Microcontroller Families

# **DEVELOPMENT SYSTEMS**

### SOFTWARE SUPPORT

SERIAL EEPROMs

Both PIC families are supported by a selection of support software including assemblers, linker/loaders and libraries. The PIC16C5X family is also supported by a software simulator.

A full-featured compiler is under development to support both families.

Customers can obtain on-line updates on Microchip Development Systems and Support Software via the Electronic Bulletin Board System, "EBBS."

Microchip offers one of the broadest selections of CMOS Serial EEPROMs on the market for embedded control systems. Serial EEPROMs are available in variety of densities, operating voltages, bus interface protocols, operating temperature ranges and space saving packages. Device densities range from 1K bits up to 16K bits. In addition to 5V only operation, Microchip offers serials that read and write either at 2.5 or 2 volts. I<sup>2</sup>C<sup>TM</sup>, Microwire<sup>TM</sup> and 4 wire bus interface protocols are standard. Devices come in three standard operating temperature ranges; commercial, industrial and automotive. Small footprint packages include: 8 pin DIP, 8 pin SOIC in JEDEC and EIAJ body widths and 14 pin SOIC. Other key features of the Serial EEPROM product line include: ESD protection greater than 4K volts and endurance of 100K cycles worst case and 1M typical.

Microchip is a high volume supplier of Serial EEPROMs to all the major markets worldwide, i.e. consumer, automotive, industrial, computer and communications. Microchip is developing leading edge unique serial EEPROMs.

The CMOS EEPROM devices from Microchip are available in 4K, 16K, and 64K densities. The manufacturing process used for these EEPROMs ensures 10,000 to 100,000 write and erase cycles. Data retention is over 10 years. Short write times are less than 200 µsec. These EEPROMs work reliably under demanding conditions and operate efficiently at temperatures from -55 °C to +125 °C. Microchip's expertise in surface mount packaging supports our customers' needs in space-sensitive applications.

Typical applications include computer peripherals, engine control, pattern recognition and telecommunications.

Microchip's CMOS EPROM devices are produced in densities from 64K to 512K. High Speed EPROMs have access times as low as 55 nanoseconds. Typical applications include computer peripheral, military, instrumentation, and automotive devices. Microchip's expertise in Surface Mount Packaging led to the development of the Surface Mount OTP EPROM market where Microchip is the #1 supplier today. Microchip is also a leading supplier of low voltage EPROMs for battery powered applications.

Microchip delivers military devices that conscientious engineers can use with confidence. Our 883C compliant parts cover all quality fronts: DESC standard military drawing approval, high speed performance and quick turn availability.

Microchip's military products include CMOS memories, CMOS/ NMOS digital signal processors and microcontrollers - all highly reliable with fast access times and proven retention. Endurance is guaranteed in both dual in-line cerdip packages and leadless chip carriers.

### PARALLEL EEPROMs

**EPROMs**

# MILITARY PRODUCTS

# **Microchip Technology Incorporated**

### OTHER MICROCHIP PRODUCTS

# RESEARCH AND DEVELOPMENT OF PERFORMANCE PRODUCTS

# FUTURE PRODUCTS AND TECHNOLOGY

### FULLY INTEGRATED MANUFACTURING

# A GLOBAL NETWORK OF PLANTS AND FACILITIES

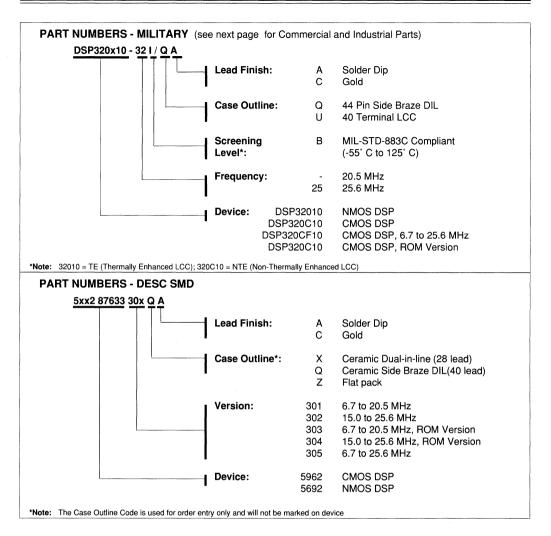

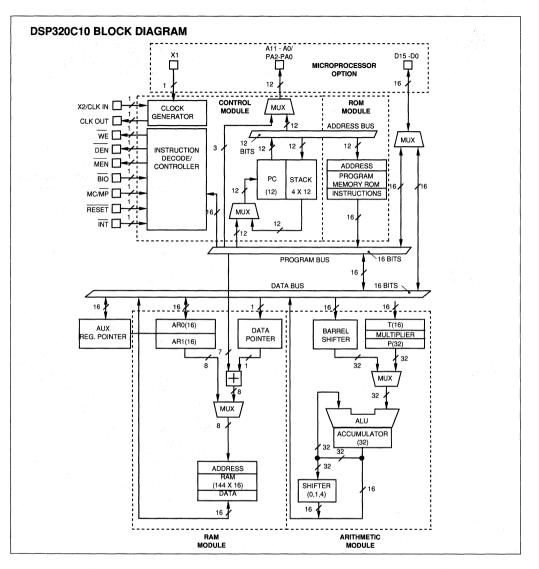

Other Microchip products, such as DSP products and Liquid Crystal Display Drivers, are mature products with proven track record and a large, repeat customer base. Microchip provides a wide package selection of single-chip DSPs that can be programmed for a wide variety of applications. Several variants of the industry standard 32010 and 320C10 are offered at speeds up to 25 MHz. The 320 DSP family is often found in commercial and military applications where medium and high performance parts are required.

Microchip's research and development activities, include exploring new process technologies and products that have industry leadership potential. Particular emphasis is placed on products that can be put to work in high performance embedded control markets.

Equipment is continually updated to bring the most sophisticated process, CAD and testing on line. Cycle times for new technology development are continuously reduced to bring innovative new products to our customers.

New process technology is constantly being developed for EEPROM, High Speed EPROM, and microcontroller products. Advanced process technology modules are being developed that will be integrated into our present product lines to achieve a range of compatible processes. Current production technology utilizes dimensions down to 0.9 microns.

More advanced technologies are under development, as well as advanced CMOS RISC-based microcontroller and CMOS EEPROM products. Objective specifications for new products are developed by close cooperation with our many customerpartners worldwide.

Microchip delivers fast turnaround through total control over all phases of production. Design, product development, mask making, wafer fabrication, assembly and quality assurance testing are conducted at facilities owned and operated by Microchip. Our integrated approach to manufacturing along with rigorous use of advanced statistical process control, continuous improvement and implementation of root cause solutions to problems, has brought forth tight product consistency levels and high yields which enable Microchip to compete successfully in world markets. Microchip's unique approach to SPC provides customers with excellent costs, quality, reliability and on-time delivery.

Microchip is a global competitor providing local service to the world's technology centers. The Company's focal point is the design and technology advancement facility in Chandler, Arizona. Most military and high performance parts emanate from here, along with front end wafer fabrication and electrical probing.

Microchip's assembly and test facility in Kaohsiung, Taiwan houses the technology and modern assembly methods necessary for plastic and ceramic packaging.

Sales and application offices are located in key cities throughout the Americas, Pacific Rim and Europe. Offices are staffed to meet the high quality expectations of our customers, and can be accessed for technical support, purchasing information and failure analysis.

# CHANDLER, AZ FACILITY

Chandler Wafer Fabrication: Diffusion Area

Chandler Wafer Fab: Sub-micron Alignment Area

# TAIWAN FACILITY

Microchip Technology Taiwan, established in 1966, was the first semiconductor manufacturing company in the Kaohsiung export processing zone in south Taiwan.

Microchip's Kaohsiung plant has progressively developed into an assembly and test facility of the highest standards.

The plants' excellent track record and continuing efforts to achieve higher levels of quality and technological advancement has resulted in superior yields and fast turnaround.

# **Microchip Technology Incorporated**

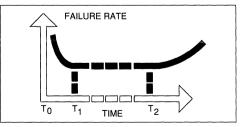

# QUALITY WITHOUT COMPROMISE

Product reliability is designed into Microchip products at the outset. Design margins are established to guarantee that every product can be easily produced, error-free and operates well beyond the tolerances of the manufacturing process.

All our quality assurance tests are run to tighter than customer specifications. Products are tested at least two machine tolerances higher than those specified by the customer.

Every new product is measured under accelerated stress testing. Qualification samples encompass the full range of processed tolerances at each step. Data sheets detailing these processes enable customers to reach accurate decisions based on known quantitative values.

To determine whether a process is within normal manufacturing variation, statistical techniques are put to work at each process step. In-process controls are performed by operators in the wafer fabrication division and immediate corrective action is taken if they deem a process is out of our very tight SPC control limits. Products are also sampled weekly through a variety of carefully monitored stress and accelerated life tests.

Microchip's positive documentation control program assures the correct document is always available at the point of use.

Individuals in all departments analyze the methods employed in their positions and formulate plans to improve performance. This continuous improvement process is never completed. Screening efforts alone are never considered enough. In all areas of our business, everyone is expected to make continuous improvements to support their part of Microchio's unique culture.

### CONTINUOUS IMPROVEMENT

### FORMING A QUALITY ALLIANCE WITH CUSTOMERS

Microchip works in tandem with customers to establish mutual programs to improve the performance of our products in their systems. Microchip's quality and reliability support is extended through final shipment of our customer's products. Microchip's quality programs ensure that our products can be used with such confidence that a customer can implement improvement programs

centered on us as a supplier.

# SECTION 1 MICROCONTROLLER PRODUCT SPECIFICATIONS

| PIC®16C5X  | EPROM-Based 8-Bit CMOS Microcontroller Series1-       | - 1  |

|------------|-------------------------------------------------------|------|

| PIC®16CR54 | ROM-Based 8-Bit CMOS Microcontroller1-                | - 61 |

| PIC®16C71  | 8-Bit CMOS EPROM Microcontroller with A/D Converter1- | -105 |

| PIC®17C42  | High Performance 8-Bit CMOS EPROM Microcontroller1-   | -169 |

1

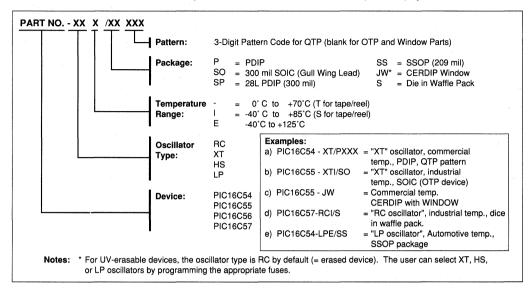

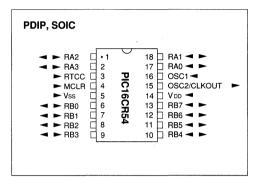

**PIC®16C5X**

# **EPROM-Based 8-Bit CMOS Microcontroller Series**

# FEATURES

#### High Performance RISC-like CPU

- · Only 33 single word instructions to learn

- All single cycle instructions (200 ns) except for program branches which are two-cycle

- Operating speed: DC 20 MHz clock input DC - 200 ns instruction cvcle

- 12-bit wide instructions

- 8-bit wide data path

- 512 2K x 12 on-chip EPROM program memory

- 25 72 x 8 general purpose registers (SRAM)

- 7 special function hardware registers

- 2 level deep hardware stack

- Direct, indirect and relative addressing modes for data and instructions

#### **Peripheral Features**

- · 12 20 I/O pins with individual direction control

- 8 bit real time clock/counter (RTCC) with 8-bit programmable prescaler

- · Power on reset

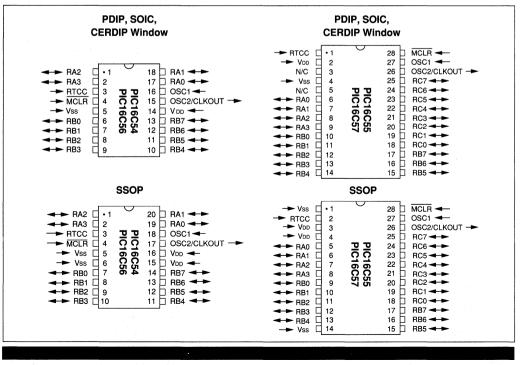

#### **FIGURE A - PIN CONFIGURATIONS**

- · Oscillator start-up timer

- Watchdog timer (WDT) with its own on-chip RC oscillator for reliable operation

- Security EPROM fuse for code-protection

- · Power saving SLEEP mode

- EPROM fuse selectable oscillator options:

- Low cost RC oscillator: RC

- Standard crystal/resonator: XT

- High speed crystal/resonator: HS

- Power saving low frequency crystal: LP

#### **CMOS Technology**

- · Low power, high speed CMOS EPROM technology

- · Fully static design

- · Wide operating voltage range:

- Commercial: 2.5V to 6.25V

- Industrial: 2.5V to 6.25V

- Automotive: 2.5V to 6.0V

- Low power consumption

- < 2 mA typical @ 5V, 4 MHz</li>

- 15 μA typical @ 3V, 32 KHz

- < 3 µA typical standby current @ 3V, 0°C to 70°C</li>

© 1992 Microchip Technology Inc.

# PIC®16C5X Series

### Table of Contents

| 1.0                                          | General Description3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1<br>2.0                                   | Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2.0                                          | Harvard Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

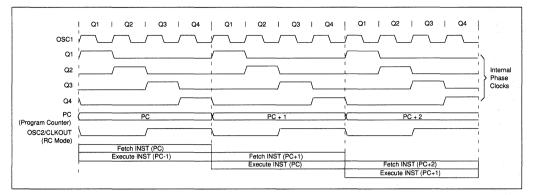

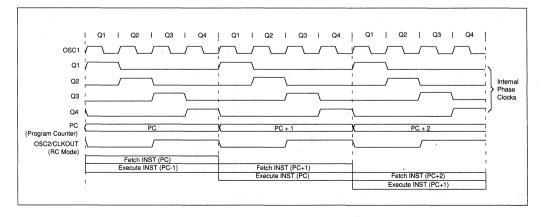

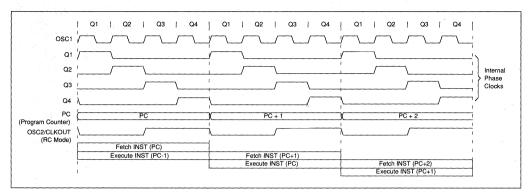

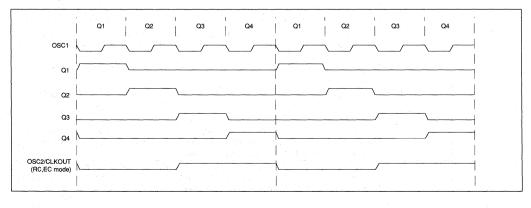

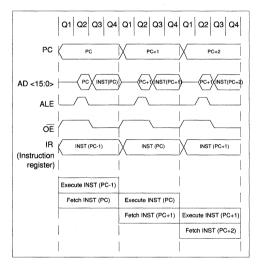

| 2.2                                          | Clocking Scheme/Instruction Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

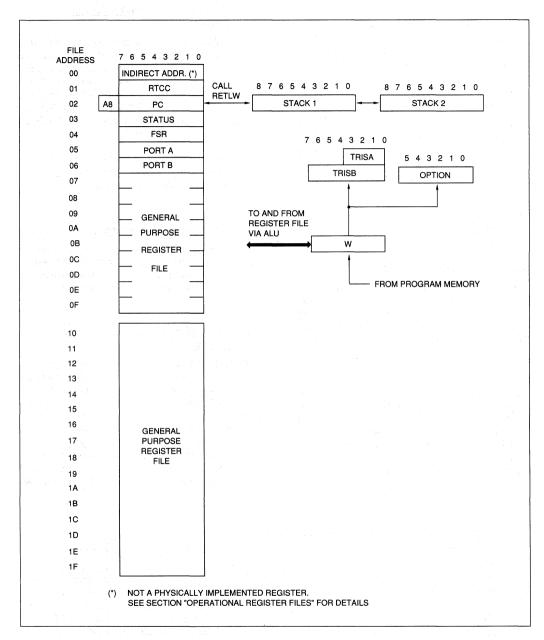

| 2.3                                          | Data Register File4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2.4<br>2.5                                   | Arithmetic/Logic Unit (ALU)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.0                                          | PIC16C5X Series Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1                                          | UV Erasable Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.2<br>3.3                                   | One-Time-Programmable (OTP) Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.3<br>4.0                                   | Quick-Turnaround-Production (QTP) Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.1                                          | Operational Register Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

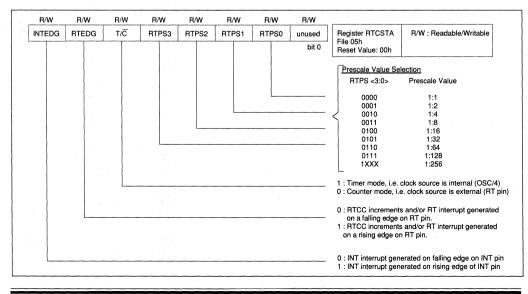

| 4.2                                          | f1 Real Time Clock/Counter Register (RTCC)6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.2.1<br>4.3                                 | Using RTCC with External Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4.4                                          | Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

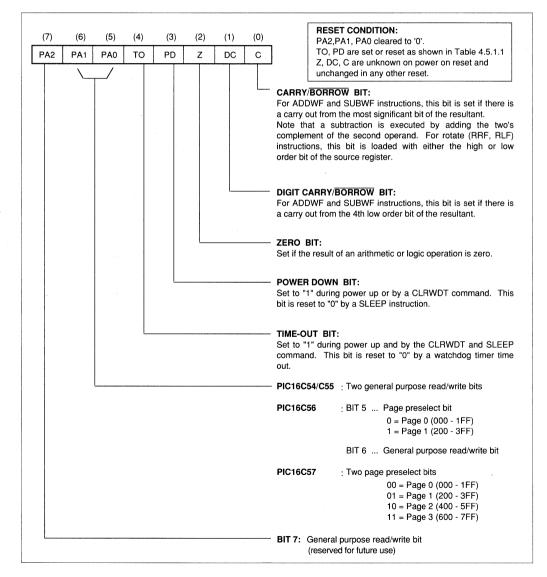

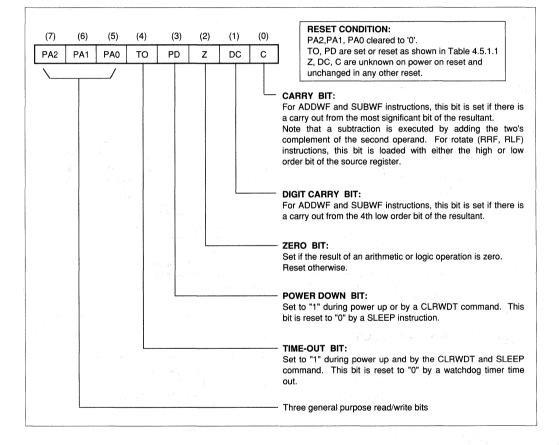

| 4.5                                          | f3 Status Word Register11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.5.1<br>4.5.2                               | Carry/Borrow and Digit Carry/Borrow Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

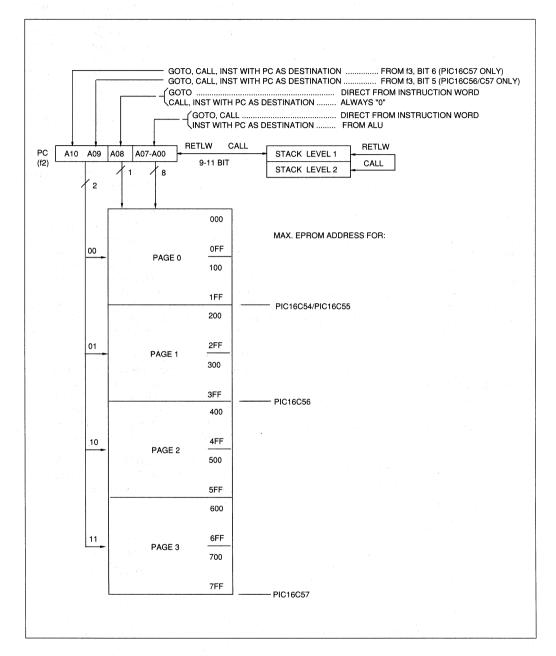

| 4.5.3                                        | Program Page Preselect (PIC16C56, PIC16C57 Only) 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.6                                          | f4 File Select Register (FSR) 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

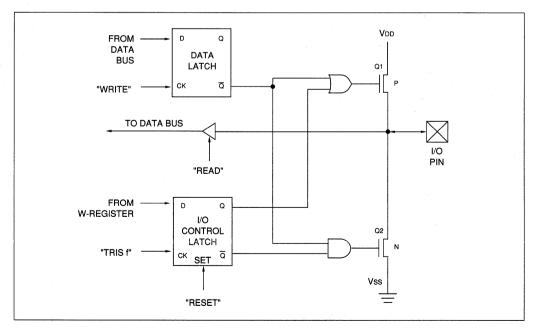

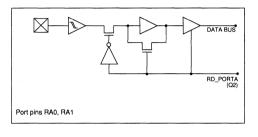

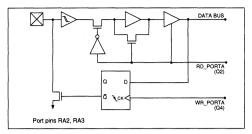

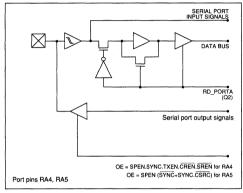

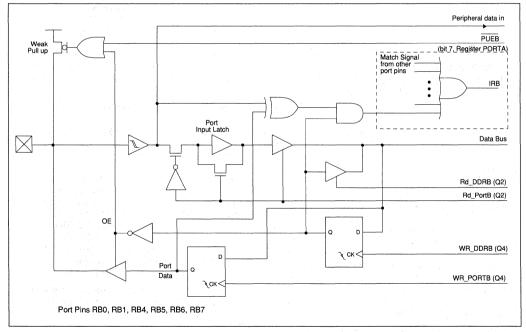

| 5.0                                          | I/O Registers (Ports)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.1<br>5.2                                   | f5 (Port A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5.3                                          | f7 (Port C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

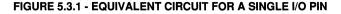

| 5.4                                          | I/O Interfacing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

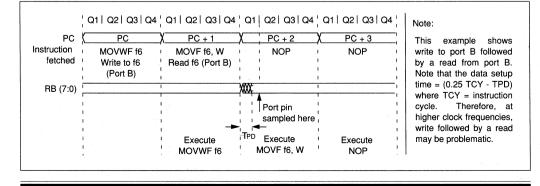

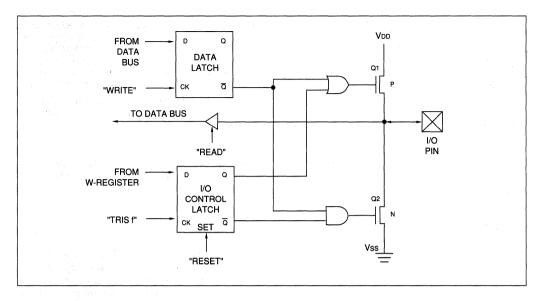

| 5.5<br>5.5.1                                 | I/O Programming Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

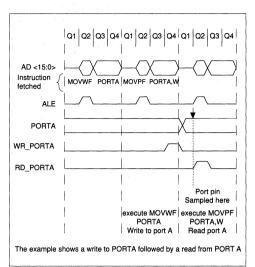

| 5.5.2                                        | Successive Operations on I/O Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5.5.3                                        | Operation in Noisy Environment14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.0<br>7.0                                   | General Purpose Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 7.1                                          | W Working Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7.2                                          | TRISA I/O Control Register for Port A (f5) 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 7.3<br>7 4                                   | TRISB I/O Control Register for Port B (f6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7.4<br>7.5                                   | TRISC I/O Control Register for Port C (f7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 8.0                                          | Reset Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

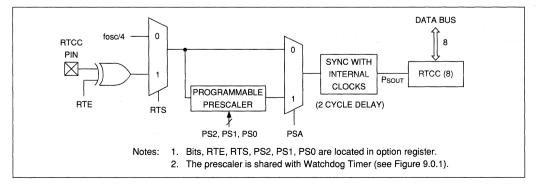

| 9.0                                          | Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 9.1<br>10.0                                  | Switching Prescaler Assignment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10.0                                         | Instruction Description 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11.0                                         | Watchdog Timer (WDT)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11.1<br>11.2                                 | WDT Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12.0                                         | Oscillator Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12.1                                         | Oscillator Types23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.2<br>12.3                                 | Crystal Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12.3                                         | Oscillator Start-up Timer (OST)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13.1                                         | Power On Reset (POR)25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

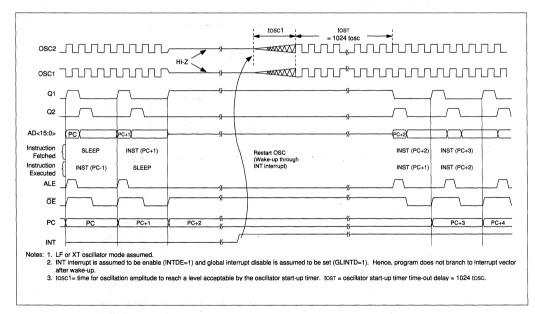

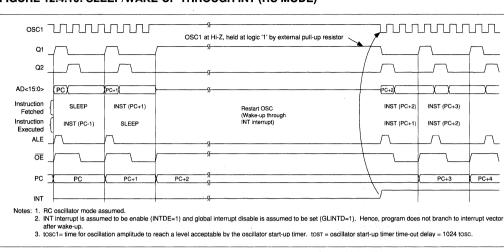

| 14.0                                         | Power Down Mode (SLEEP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14.1<br>15.0                                 | Wake-Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15.1                                         | Customer ID Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15.2                                         | Code Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.2.1<br>16.0                               | Verifying a Code-protected PIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16.1                                         | Absolute Maximum Batings 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16.3                                         | DC Characteristics: PIC16C5X-RC, XT, HS, LP (Com) 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16.4<br>16.5                                 | DC Characteristics: PIC16C5XI-RC, XT, HS, LP (Ind)31<br>DC Characteristics: PIC16C5XI-RC, XT, HS, LP (Auto)32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16.6                                         | DC Characteristics PIC16C5X-BC XT HS I P (Com)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                              | and PIC16C5XI-RC, XT, HS, LP (Ind)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16.7<br>16.8                                 | AC Characteristics: PIC16C5XI-RC, XT, HS, LP (Auto)34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10.0                                         | and PIC16C5XI-RC, XT, HS, LP (Ind) and (Auto)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16.9                                         | Electrical Structure of Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 17.0<br>18.0                                 | Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 19.0                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

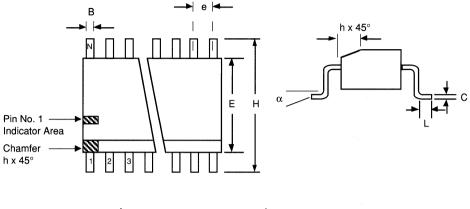

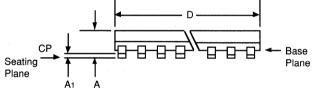

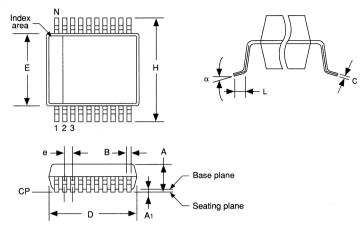

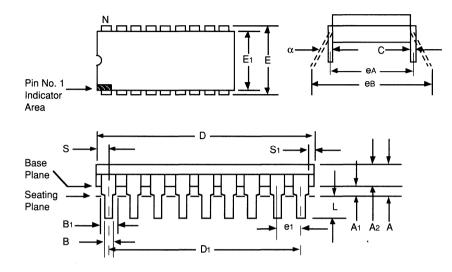

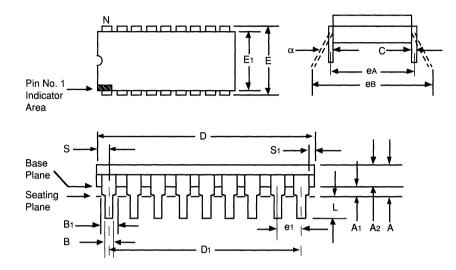

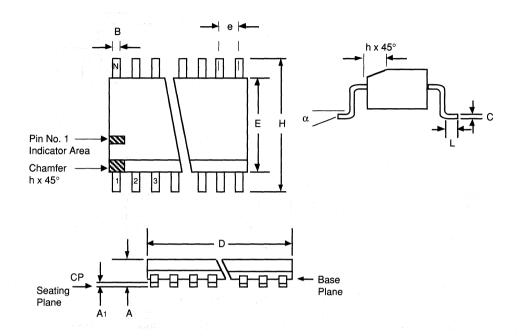

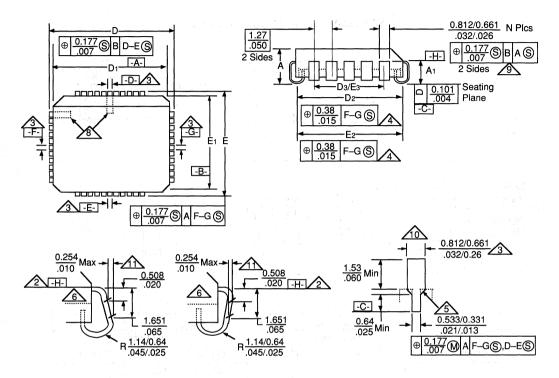

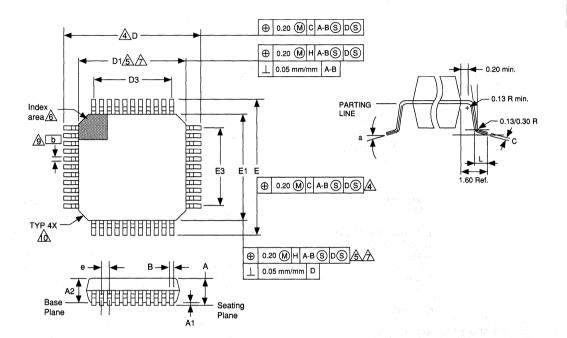

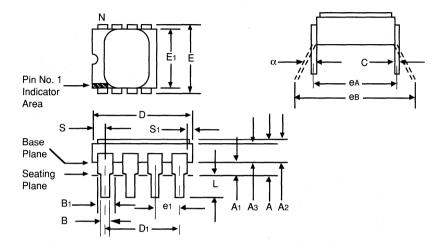

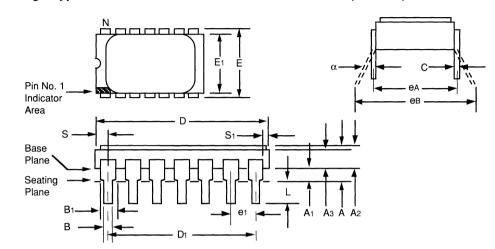

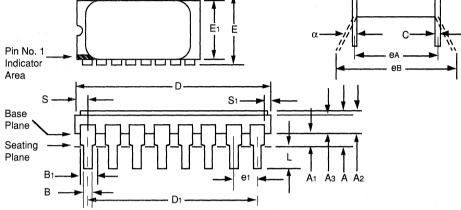

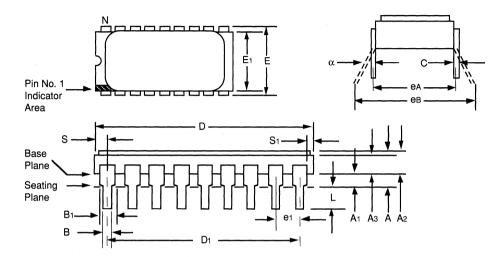

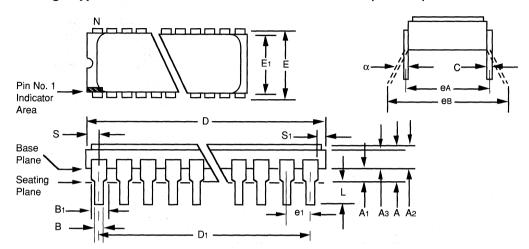

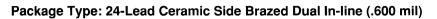

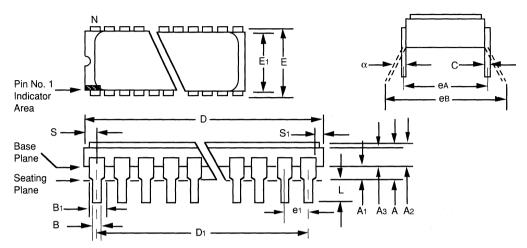

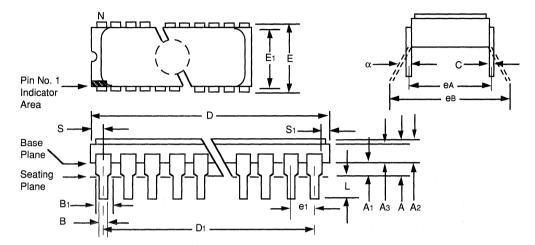

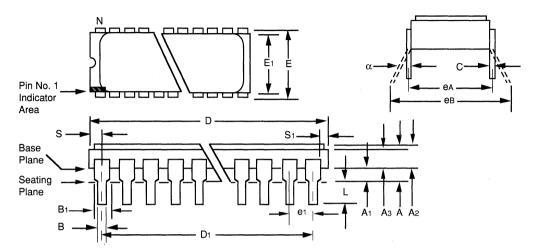

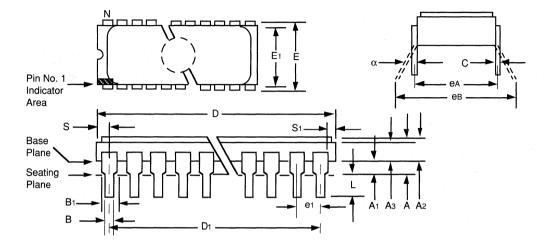

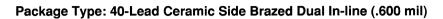

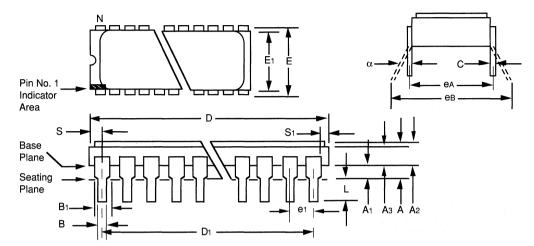

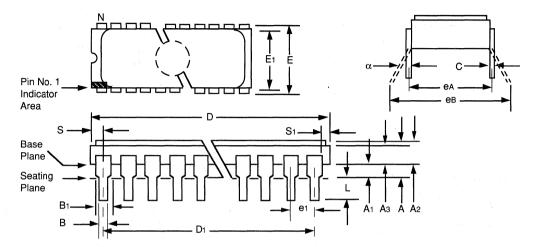

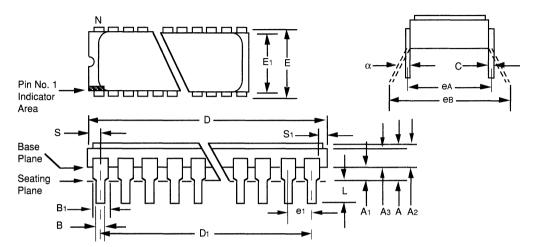

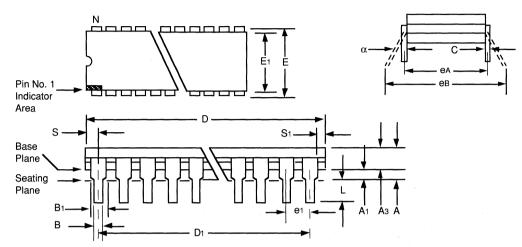

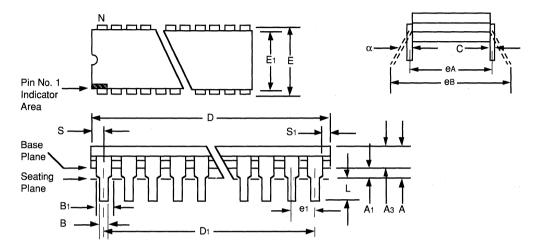

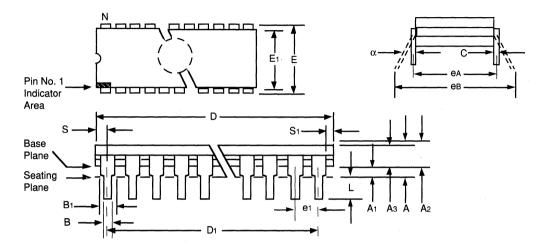

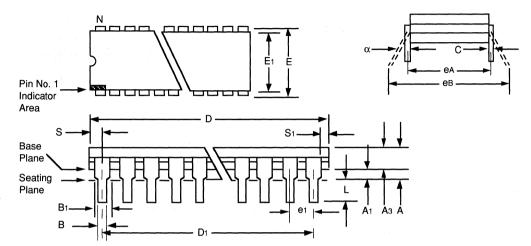

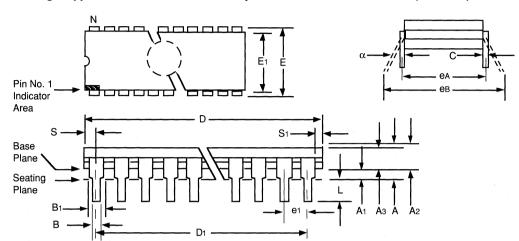

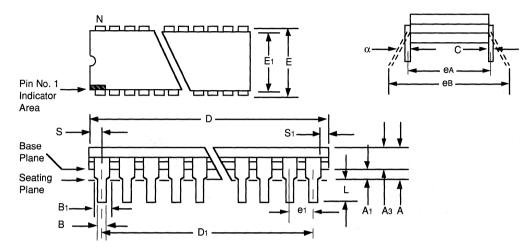

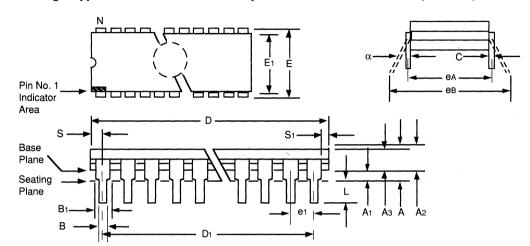

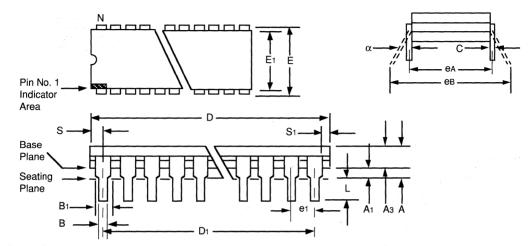

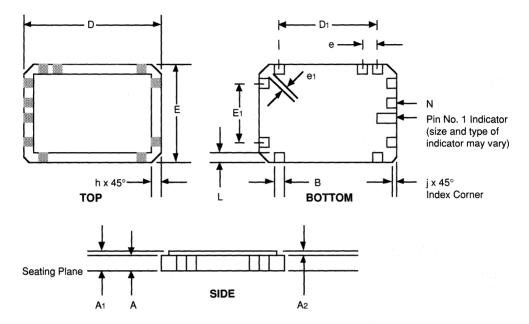

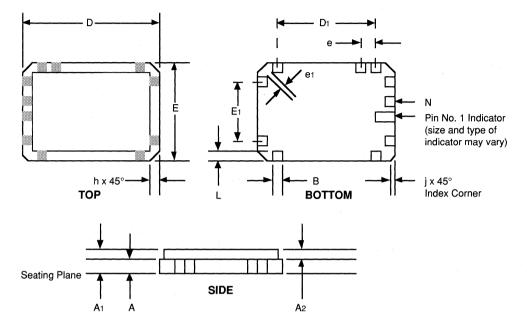

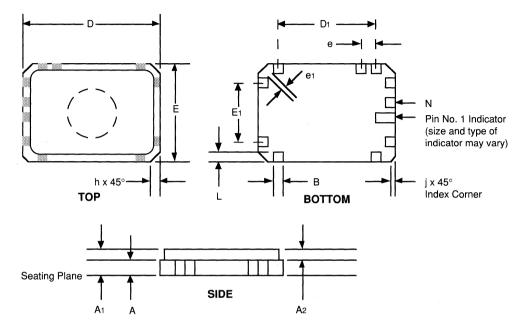

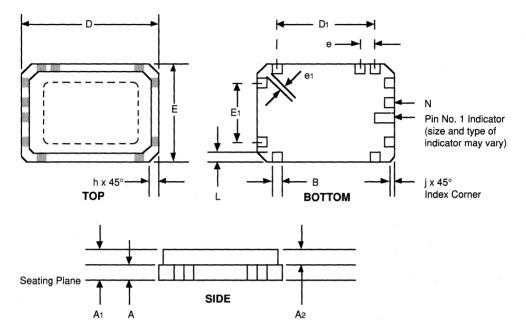

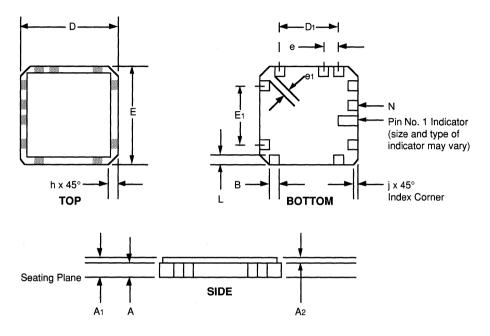

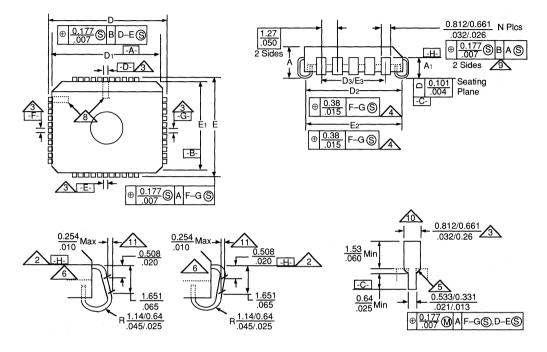

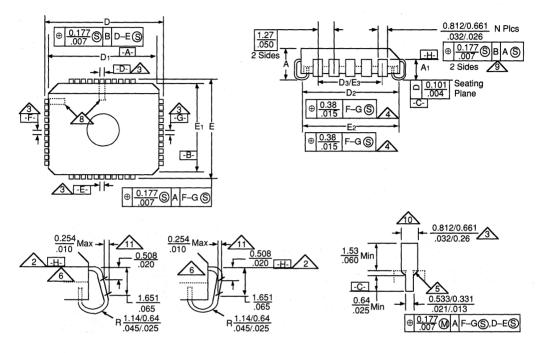

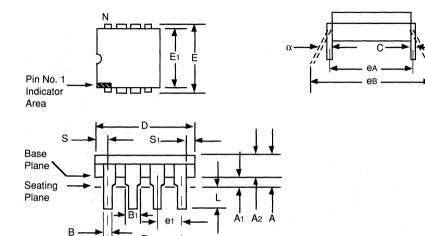

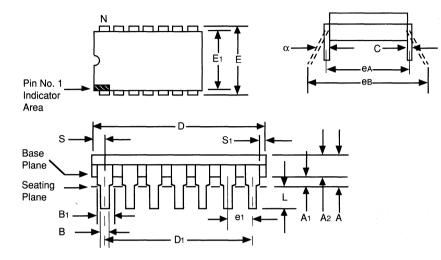

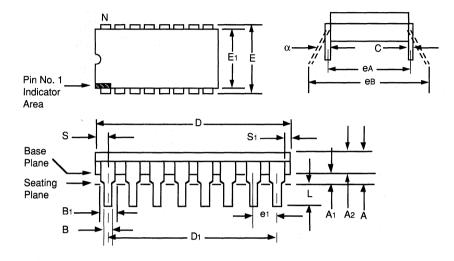

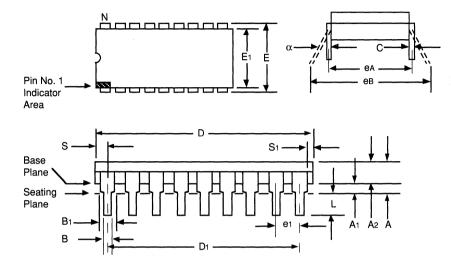

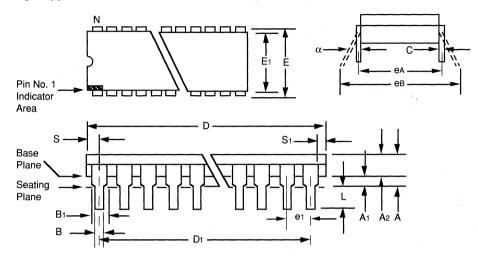

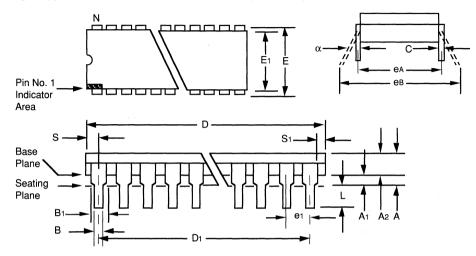

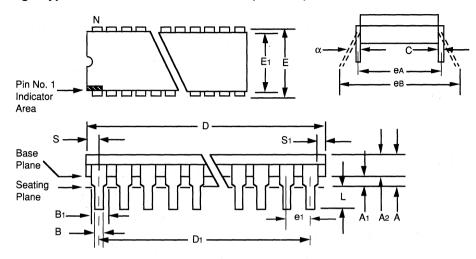

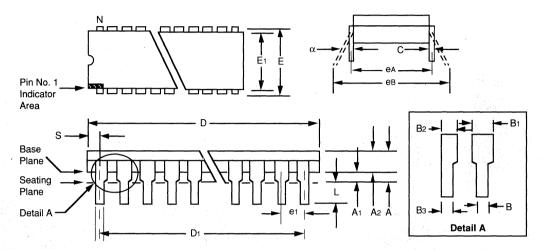

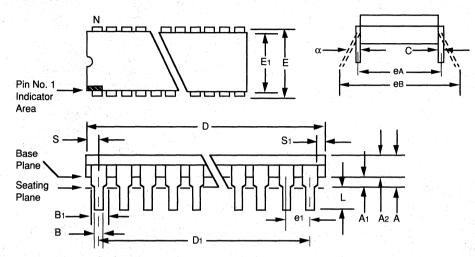

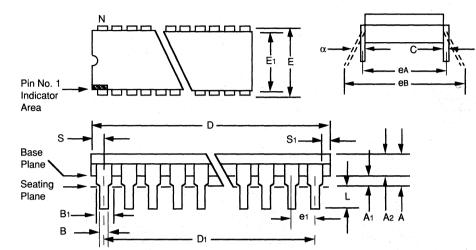

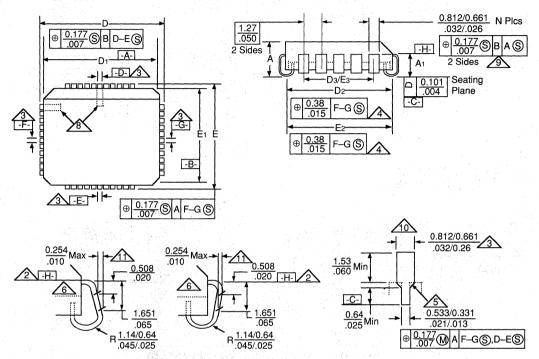

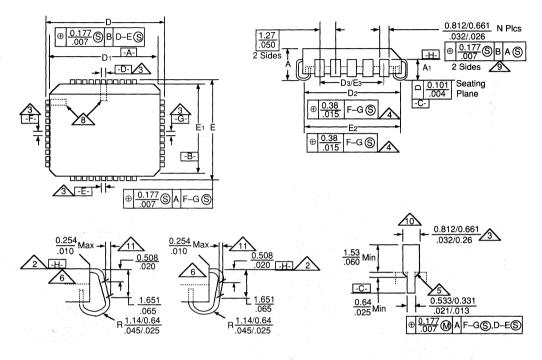

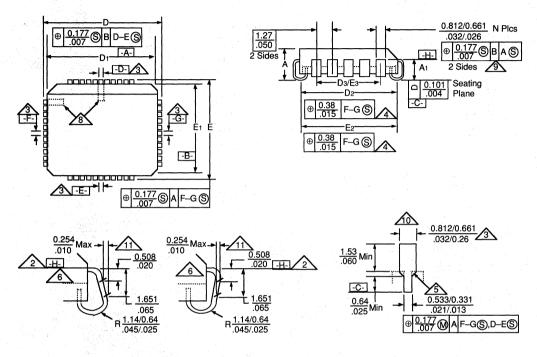

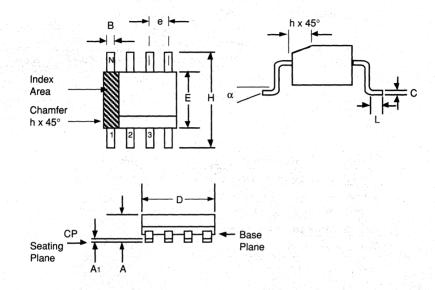

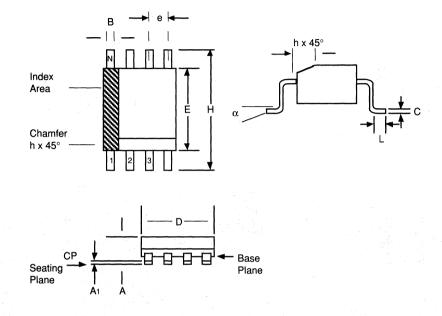

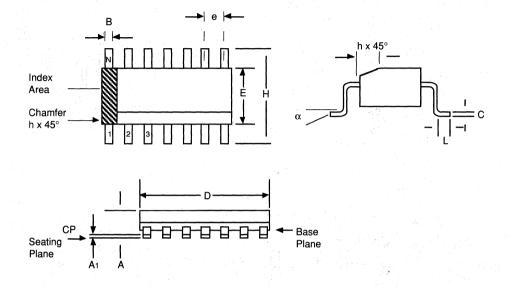

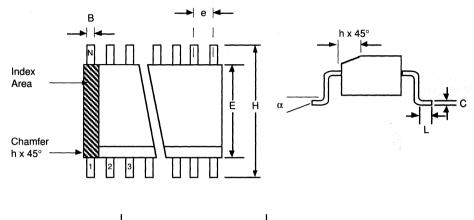

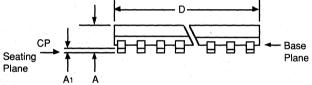

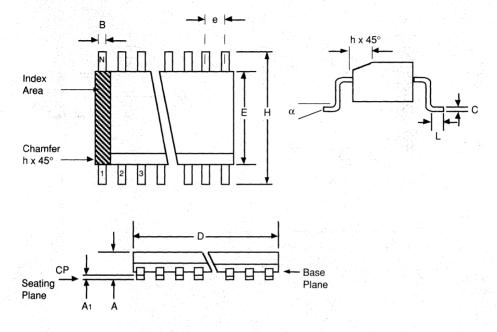

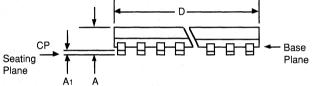

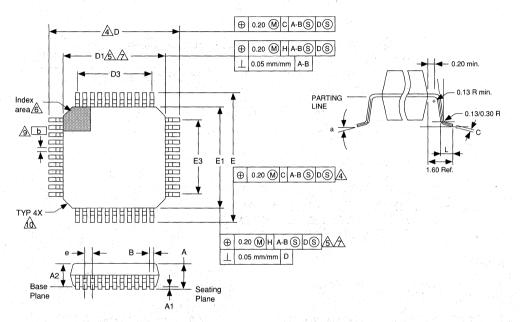

| 19.1                                         | Packaging Diagrams and Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                              | Packaging Diagrams and Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

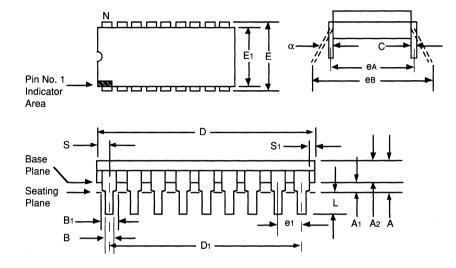

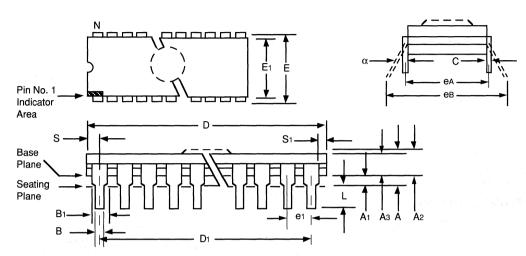

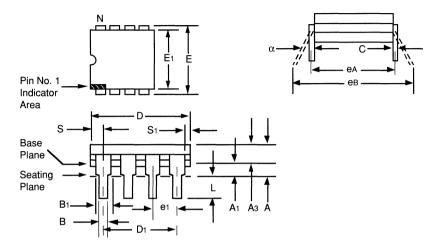

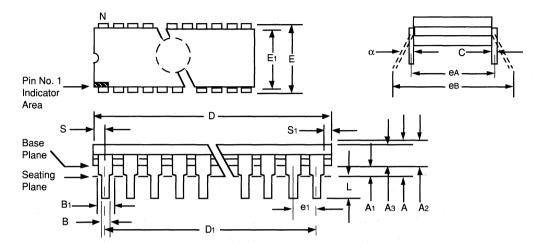

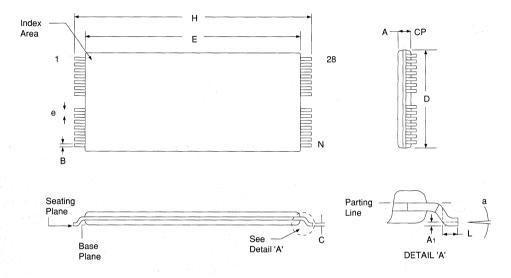

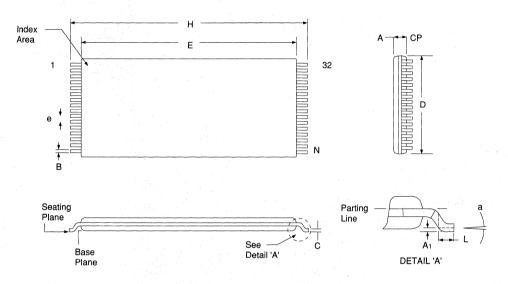

| 19.2                                         | 18-Lead Plastic Dual In-Line (.300 mil)45<br>28-Lead Plastic Dual In-Line (.600 mil)46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

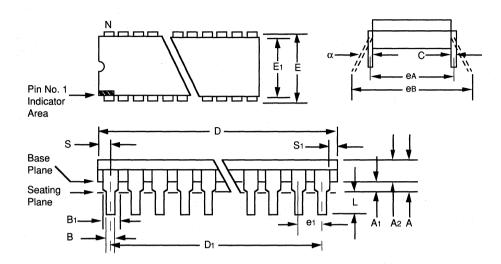

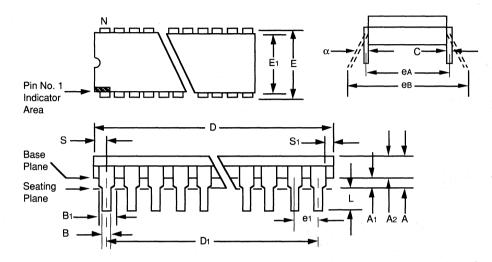

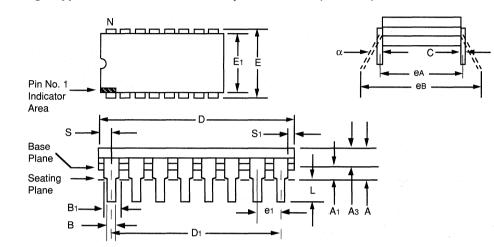

| 19.3                                         | 18-Lead Plastic Dual In-Line (.300 mil)         45           28-Lead Plastic Dual In-Line (.600 mil)         46           28-Lead Dual In-Line Plastic (300 mil)         47                                                                                                                                                                                                                                                                                                                                                                                                                         |

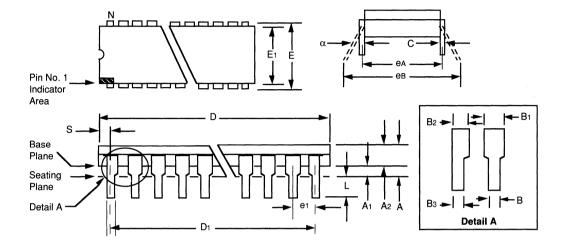

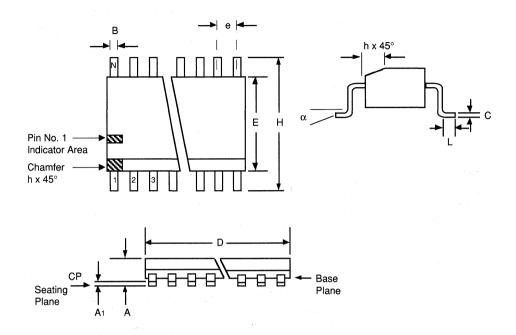

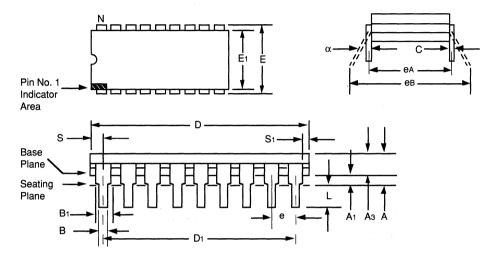

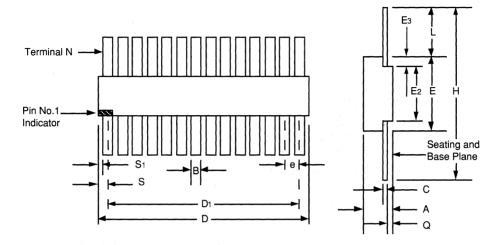

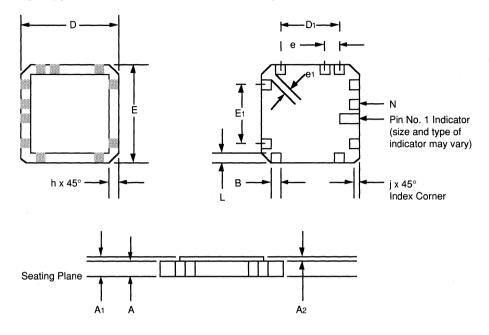

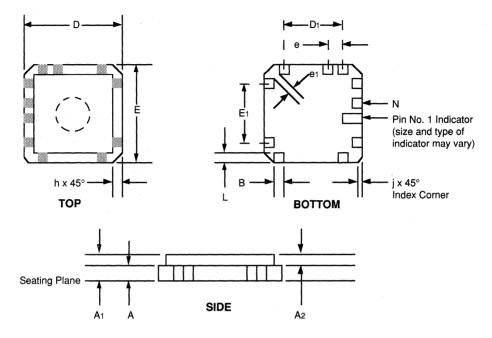

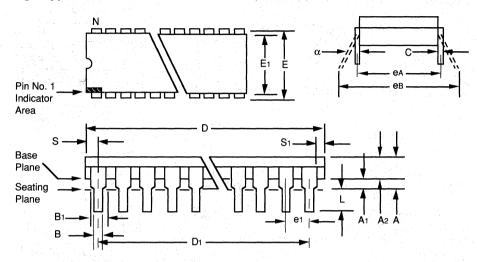

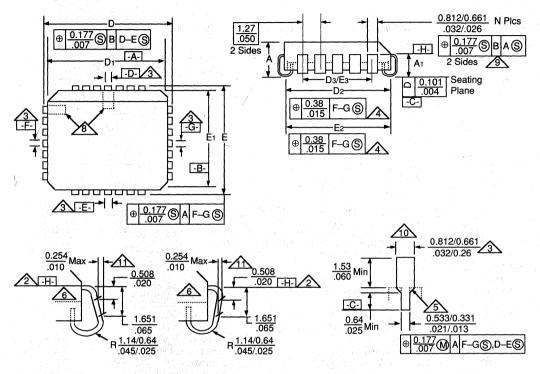

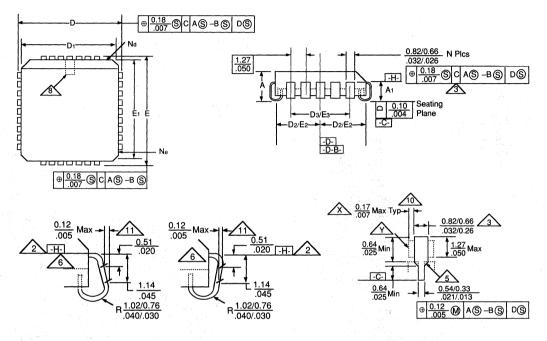

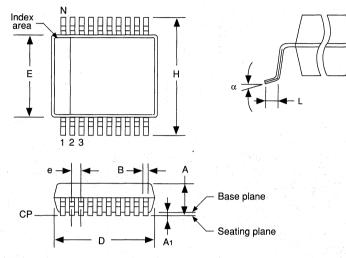

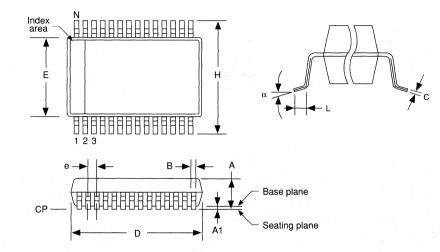

| 19.3<br>19.4<br>19.5                         | 18-Lead Plastic Dual In-Line (.300 mil)         45           28-Lead Plastic Dual In-Line (.600 mil)         46           28-Lead Plastic Surface Mount         47           28-Lead Plastic Surface Mount         48                                                                                                                                                                                                                                                                                                                                                                               |

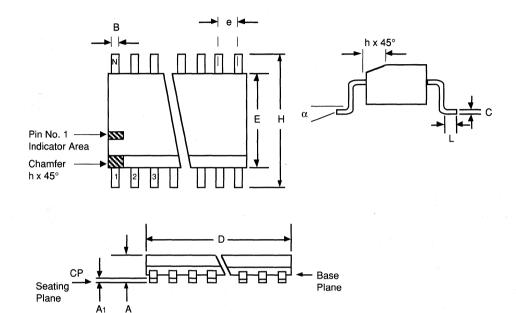

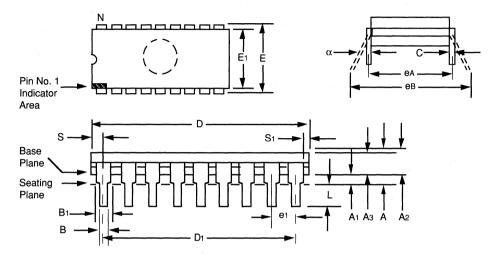

| 19.3<br>19.4<br>19.5<br>19.6                 | 18-Lead Plastic Dual In-Line (.300 mil)         45           28-Lead Plastic Dual In-Line (.600 mil)         46           28-Lead Dual In-Line Plastic (300 mil)         47           18-Lead Plastic Surface Mount         48           28-Lead Plastic Surface Mount         50                                                                                                                                                                                                                                                                                                                   |

| 19.3<br>19.4<br>19.5<br>19.6<br>19.7         | 18-Lead Plastic Dual In-Line (.300 mil)         45           28-Lead Plastic Dual In-Line (.600 mil)         46           28-Lead Dual In-Line Plastic (300 mil)         47           18-Lead Plastic Surface Mount         48           20-Lead Plastic Surface Mount         49           20-Lead Plastic Surface Mount         50           28-Lead Plastic Surface Mount         51                                                                                                                                                                                                             |

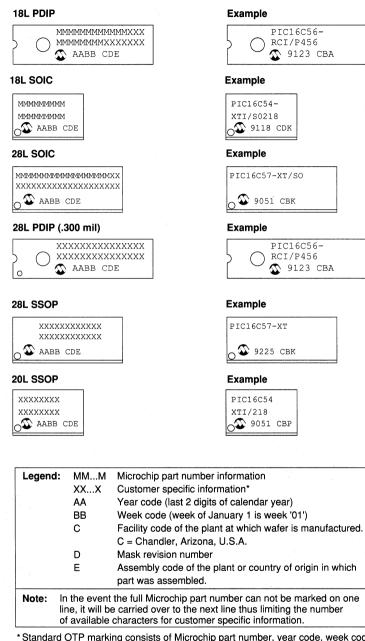

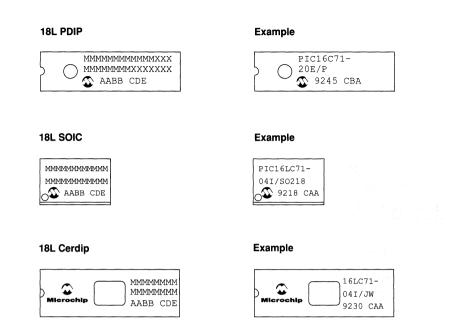

| 19.3<br>19.4<br>19.5<br>19.6                 | 18-Lead Plastic Dual In-Line (.300 mil)         45           28-Lead Plastic Dual In-Line (.600 mil)         46           28-Lead Dual In-Line Plastic (300 mil)         47           18-Lead Plastic Surface Mount         48           20-Lead Plastic Surface Mount         50           20-Lead Plastic Surface Mount         50           28-Lead Plastic Surface Mount         51           Package Marking Information         52           Development Support         54                                                                                                                   |

| 19.3<br>19.4<br>19.5<br>19.6<br>19.7<br>19.8 | 18-Lead Plastic Dual In-Line (.300 mil)         45           28-Lead Plastic Dual In-Line (.600 mil)         46           28-Lead Dual In-Line Plastic (300 mil)         47           18-Lead Plastic Surface Mount         48           28-Lead Plastic Surface Mount         49           20-Lead Plastic Surface Mount         50           28-Lead Plastic Surface Mount         50 |

| 20.1.1                      | Host System Requirements                         |

|-----------------------------|--------------------------------------------------|

| 20.1.2                      | Emulator System Components                       |

| 20.2                        | PIC-PAK™ Development Kit                         |

| 20.3                        | PICALC Cross-Assembler                           |

| 20.4<br>20.5                | PICSIM <sup>™</sup> Software Simulator           |

| 20.5                        | PRO MASTER™                                      |

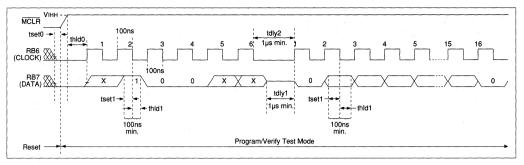

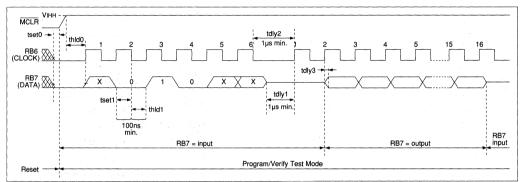

| 21.0                        | EPROM Programming                                |

| 21.1                        | Prototype Programmers                            |

| 21.2                        | Production Quality Programmers                   |

| 21.3                        | Gang Programmers                                 |

| 21.4                        | Factory Programming                              |

| Index                       |                                                  |

| Sales ar                    | nd Support 60                                    |

| Table                       | of Figures                                       |

|                             |                                                  |

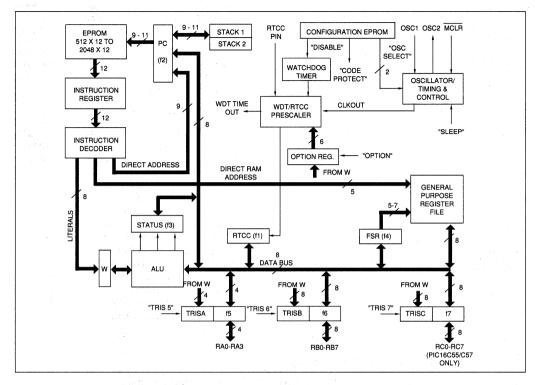

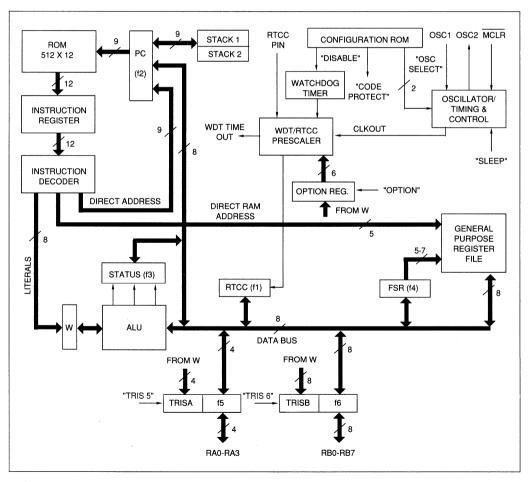

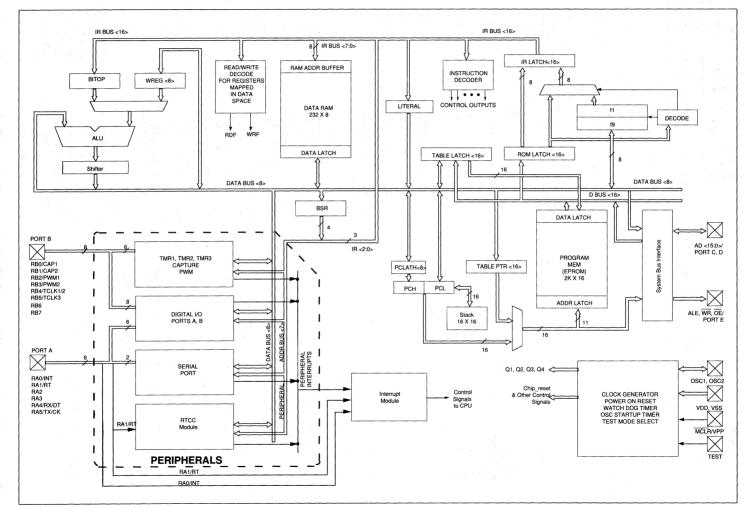

| 2.1.1                       | PIC16C5X Series Block Diagram                    |

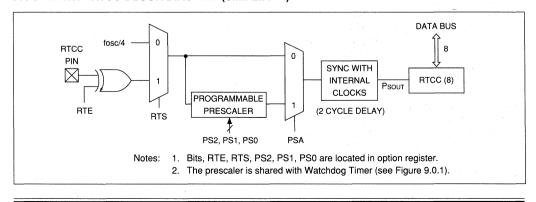

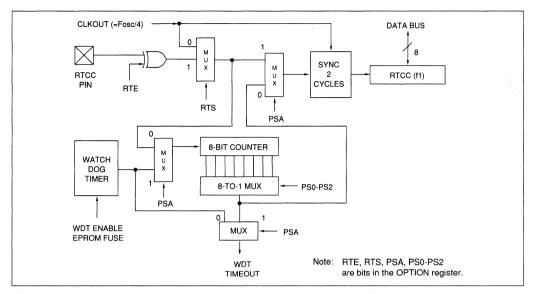

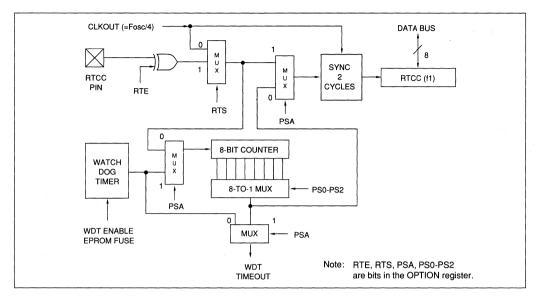

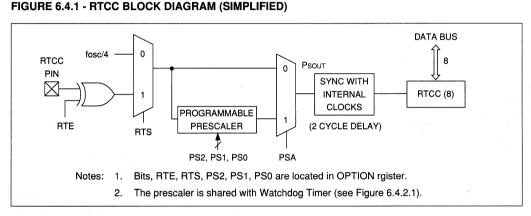

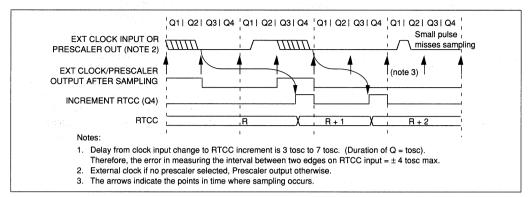

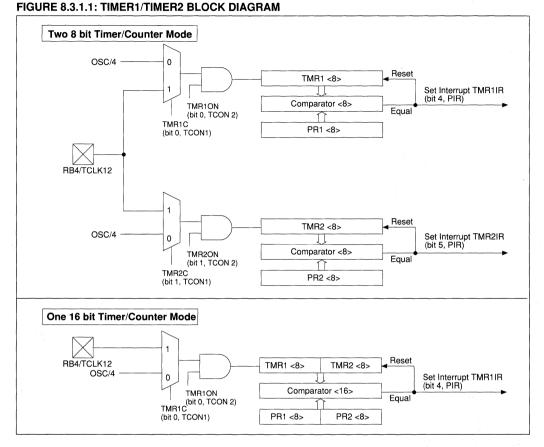

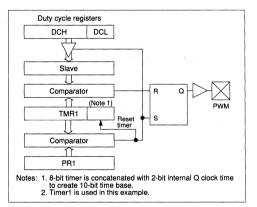

| 4.1.1                       | RTCC Block Diagram (Simplified)                  |

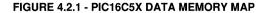

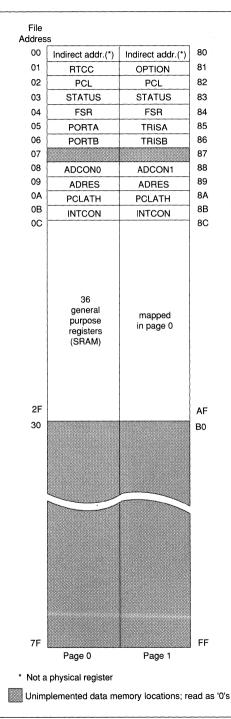

| 4.2.1                       | PIC16C5X Data Memory Map 7                       |

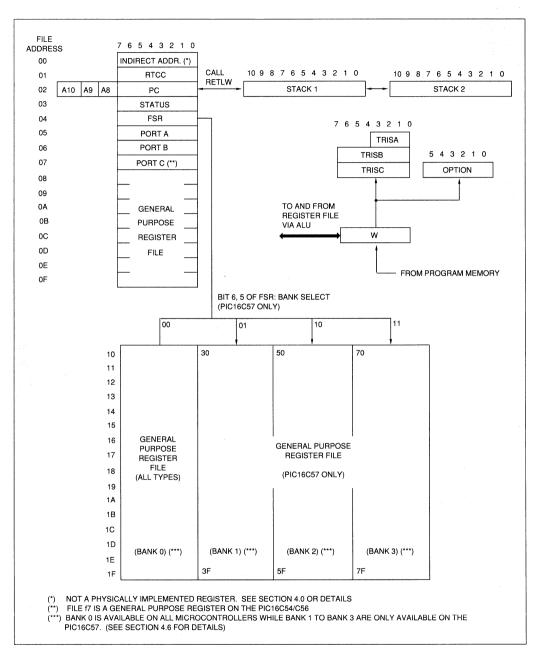

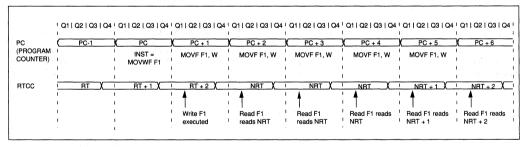

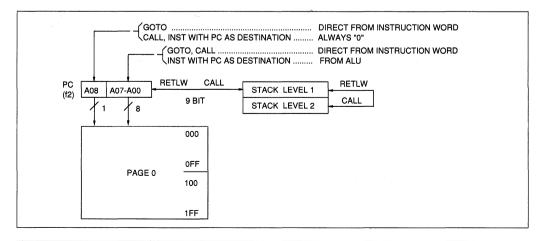

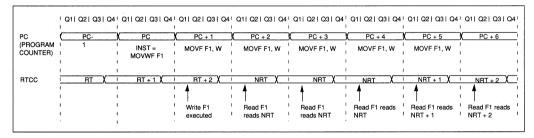

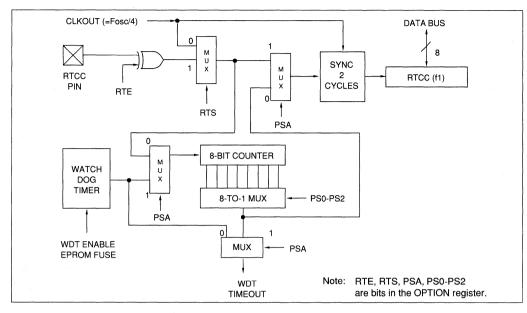

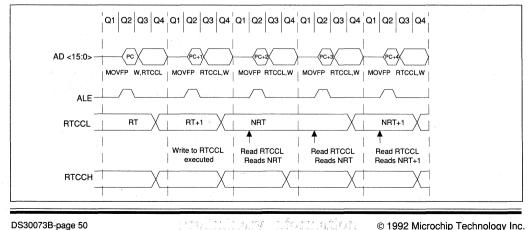

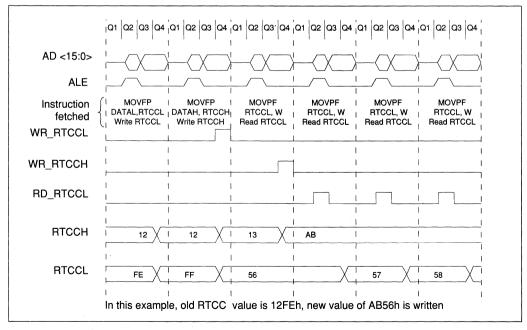

| 4.2.2A                      | RTCC Timing: INT Clock/No Prescale               |

| 4.2.2B                      | RTCC Timing: INT Clock/Prescale 1:28             |

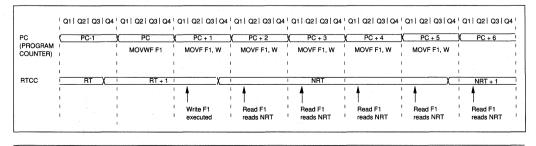

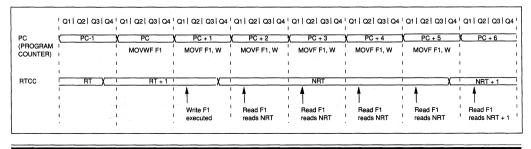

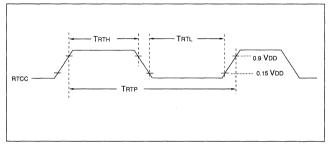

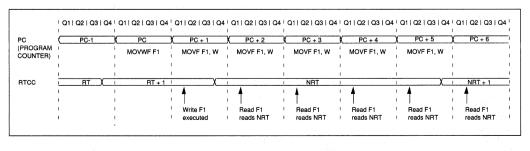

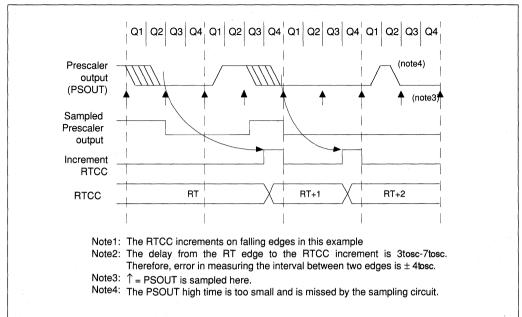

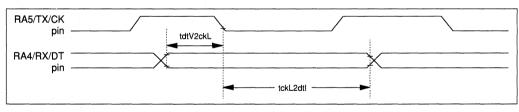

| 4.2.3                       | RTCC Timing with External Clock                  |

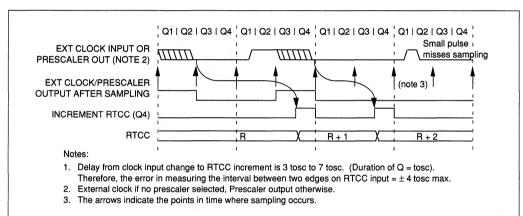

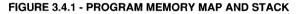

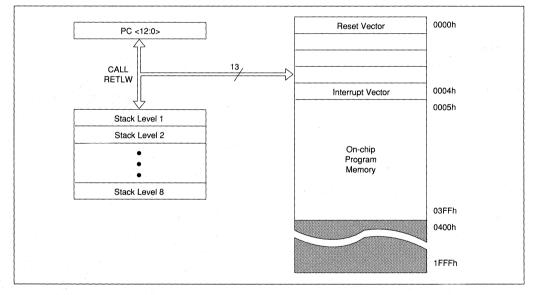

| 4.3.1                       | Program Memory Organization10                    |

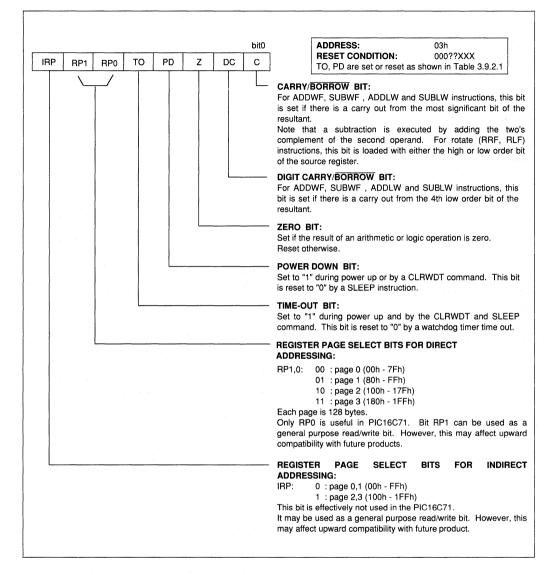

| 4.5.1                       | Status Word Register 1311                        |

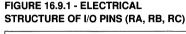

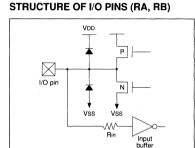

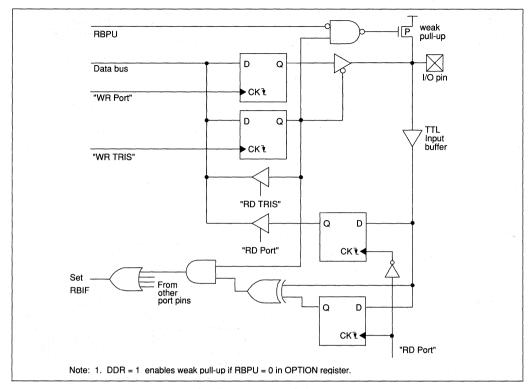

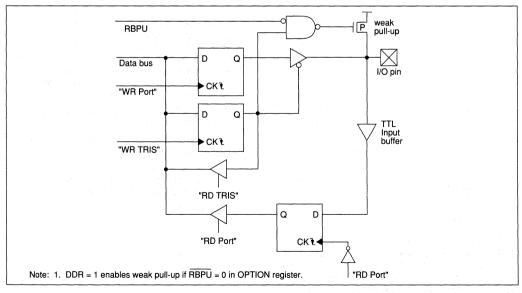

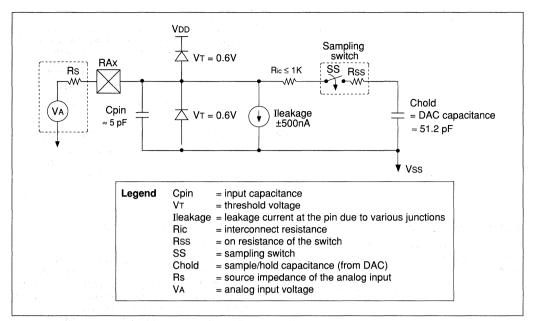

| 5.4.1                       | Equivalent Circuit for a Single I/O Pin          |

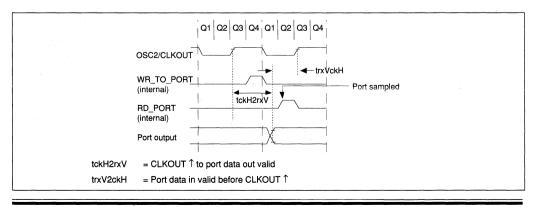

| 5.5.2.1                     | I/O Port Read/Write Timing                       |

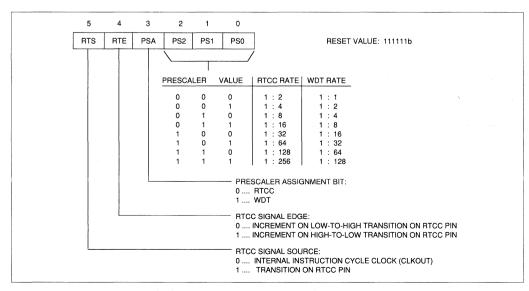

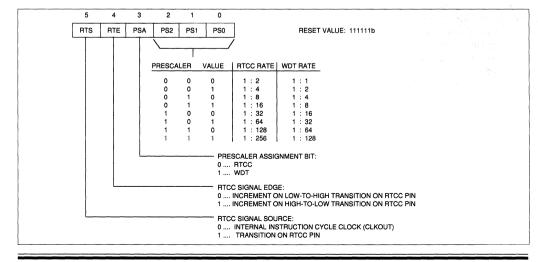

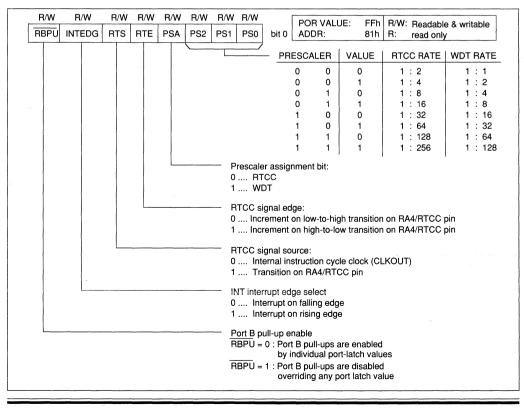

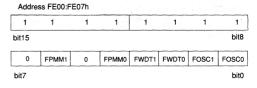

| 7.5.1 <sup>°</sup><br>9.0.1 | OPTION Register                                  |

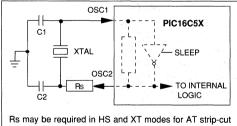

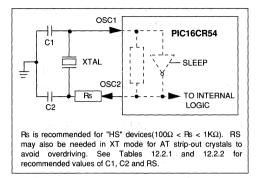

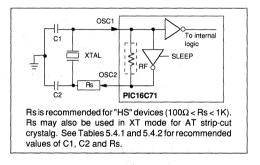

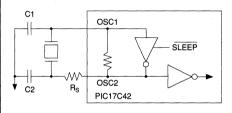

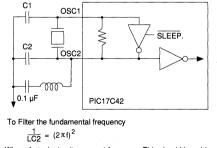

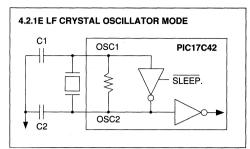

| 12.2.1                      | Crystal Operation (or Ceramic Resonator)         |

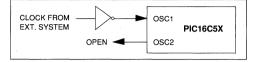

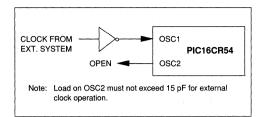

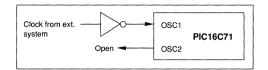

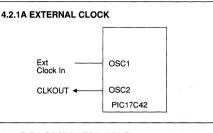

| 12.2.2                      | External Clock Input Operation                   |

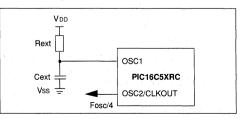

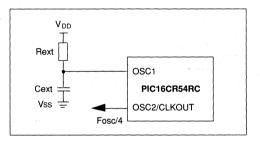

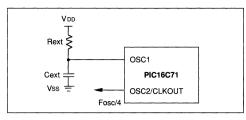

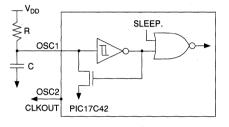

| 12.3.1                      | RC Oscillator (RC type only)24                   |

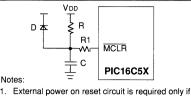

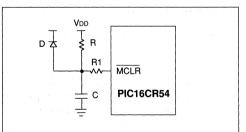

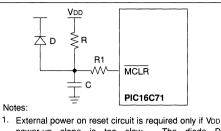

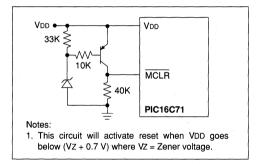

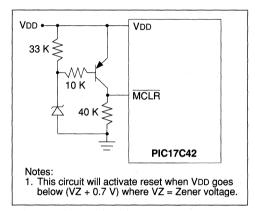

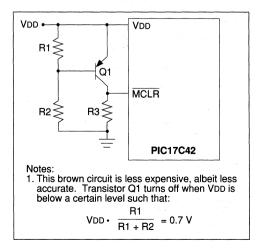

| 13.1.1                      | External Power on Reset Circuit                  |

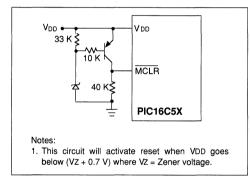

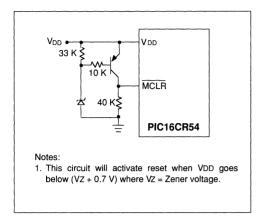

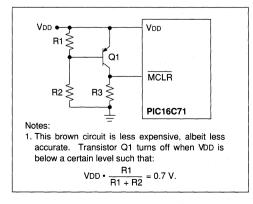

| 13.1.2                      | Brown Out Protection Circuit25                   |

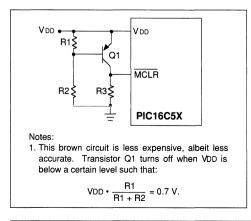

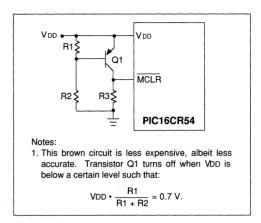

| 13.1.3                      | Brown Out Protection Circuit                     |

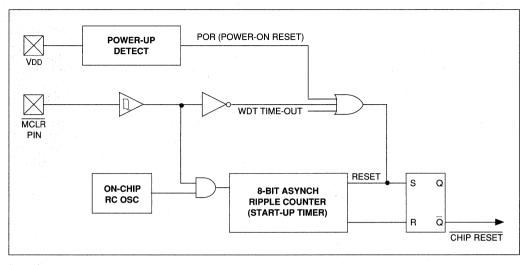

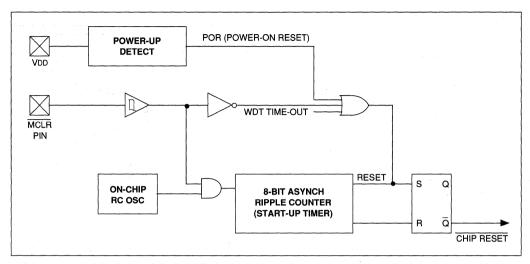

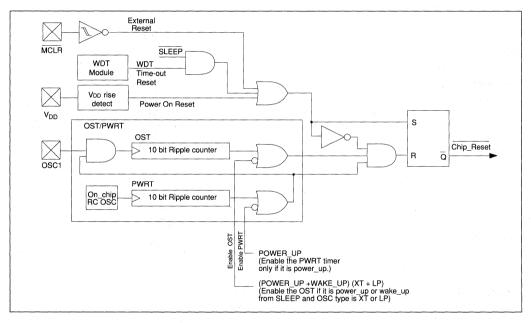

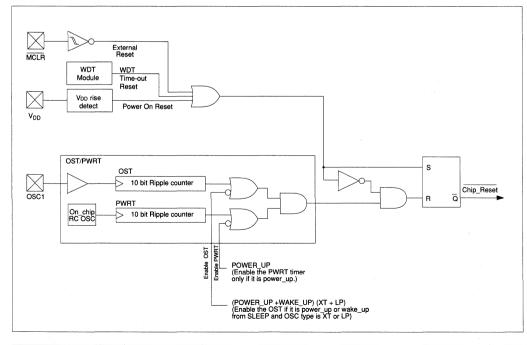

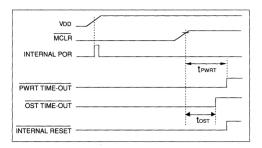

| 13.1.4                      | Simplified Power on Reset Block Diagram          |

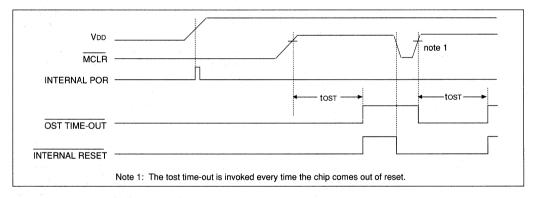

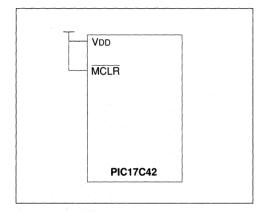

| 13.1.5                      | Using External Reset Input                       |

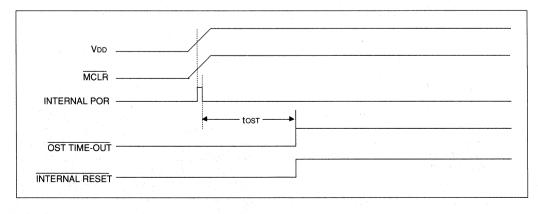

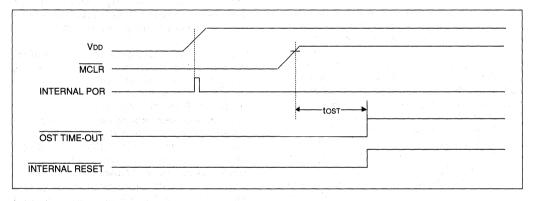

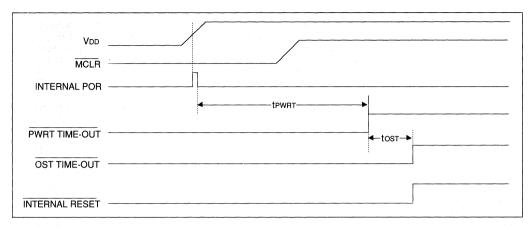

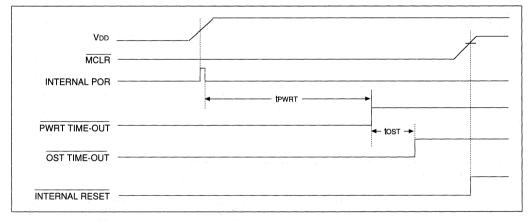

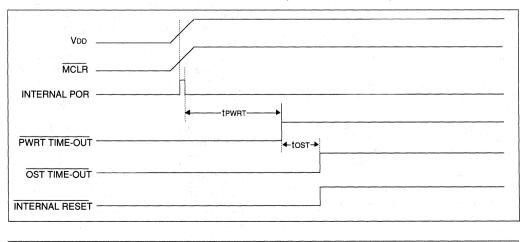

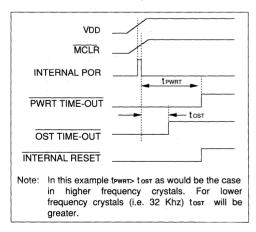

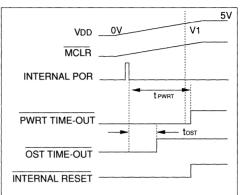

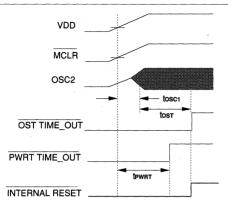

| 13.1.6                      | Using On-Chip POR (Fast Vob Rise Time)           |

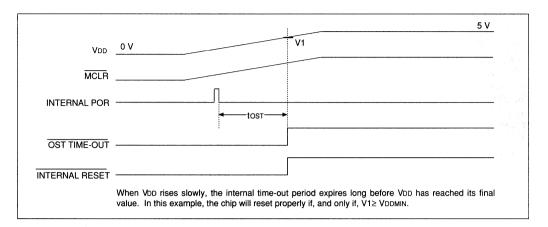

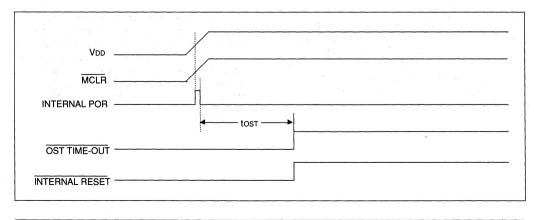

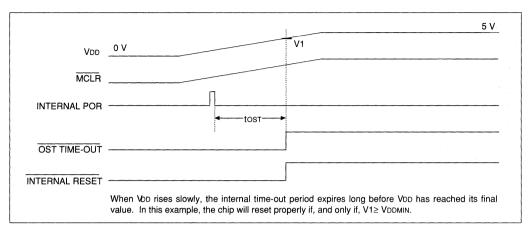

| 13.1.7<br>16.9.1            | Using On-Chip POR (Slow Vod Rise Time)           |

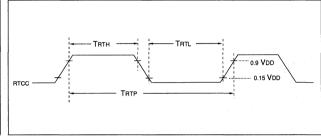

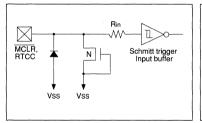

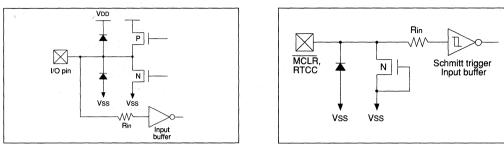

| 16.9.2                      | Electrical Structure of MCLR and RTCC Pins       |

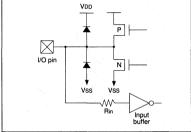

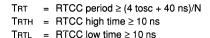

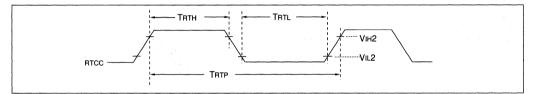

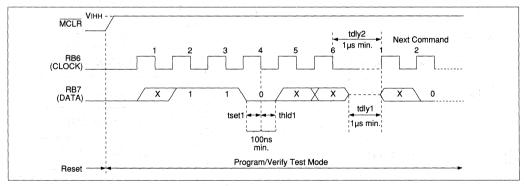

| 17.0.1                      | RTCC Timing                                      |

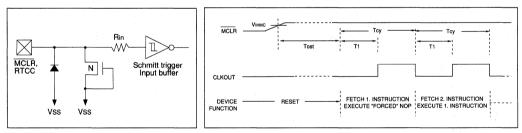

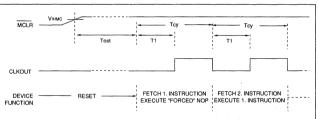

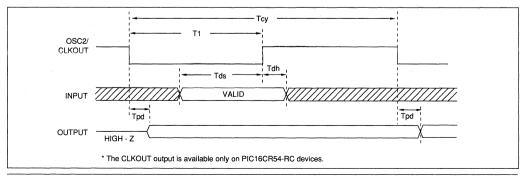

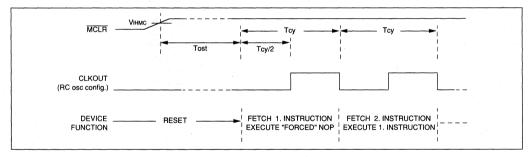

| 17.0.2                      | Oscillator Start-up Timing (PIC16CXRC)           |

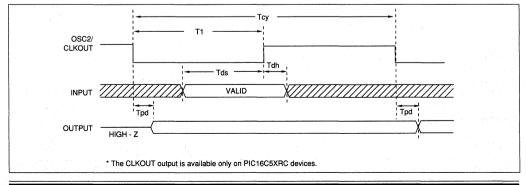

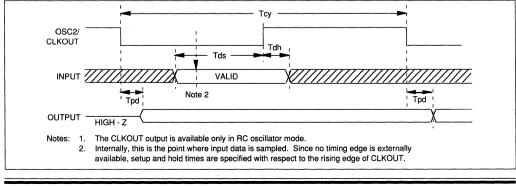

| 17.0.3                      | Input/Output Timing for I/O Ports (PIC16C5CRC)   |

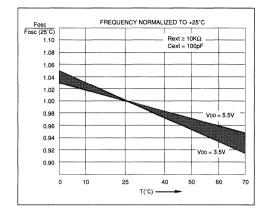

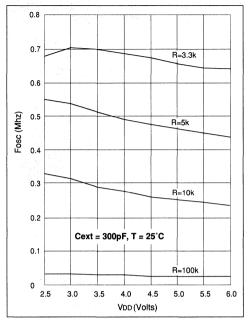

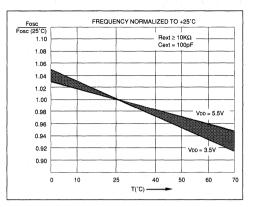

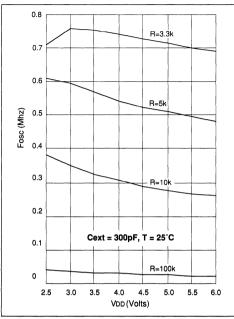

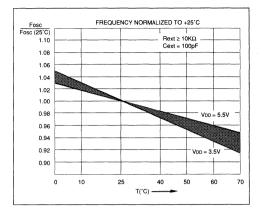

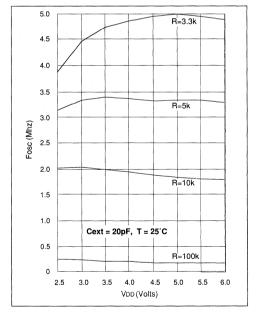

| 18.0.1                      | Typical RC Oscillator Frequency vs. Temperature  |

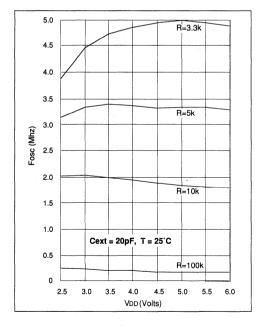

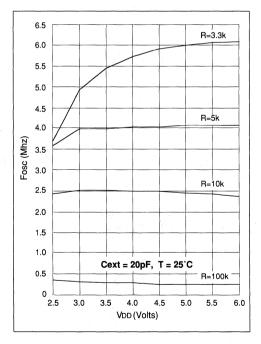

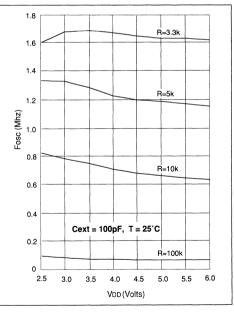

| 18.0.2<br>18.0.3            | Typical RC Oscillator Frequency vs Vod           |

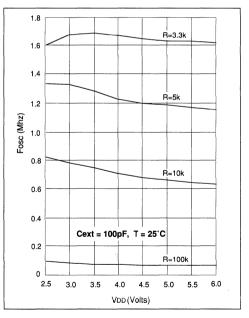

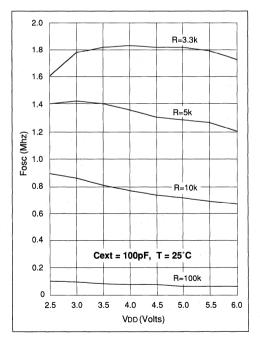

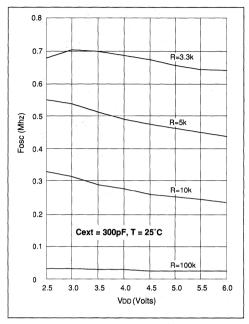

| 18.0.4                      | Typical RC Oscillator Frequency vs Vbb           |

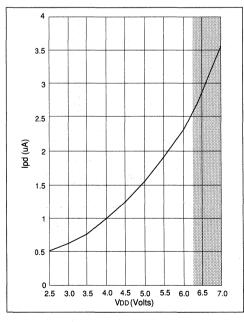

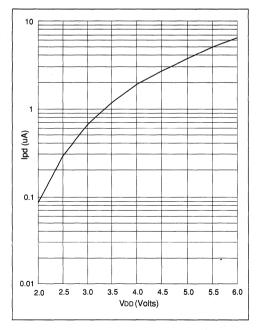

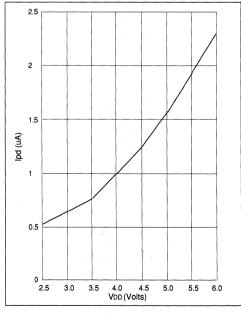

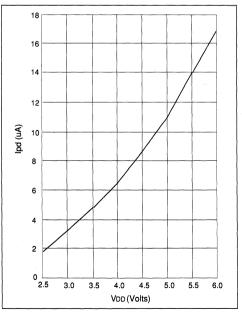

| 18.0.5                      | Typical IPD vs VDD (Watchdog Disabled 25°C)      |

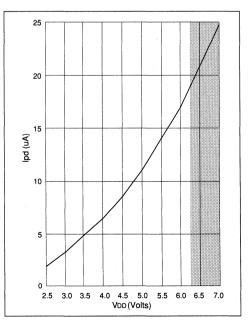

| 18.0.6                      | Typical IPD vs VDD (Watchdog Enabled 25°C)       |

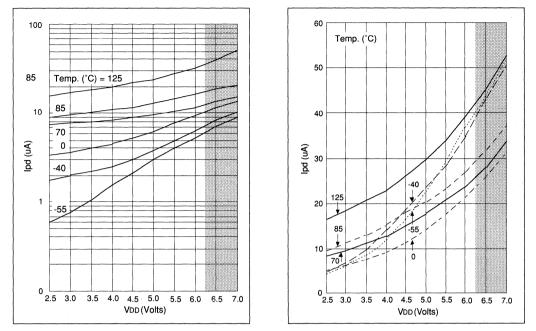

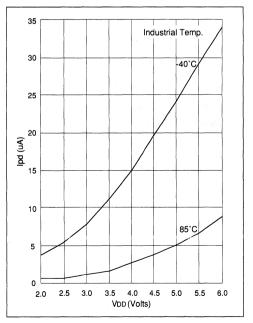

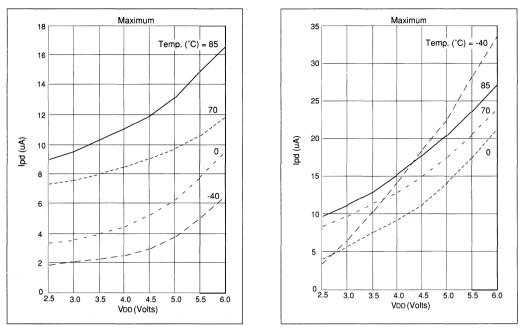

| 18.0.7                      | Maximum IPD vs VDD (Watchdog Disabled)           |

| 18.0.8                      | Maximum IPD vs VDD (Watchdog Enabled)            |

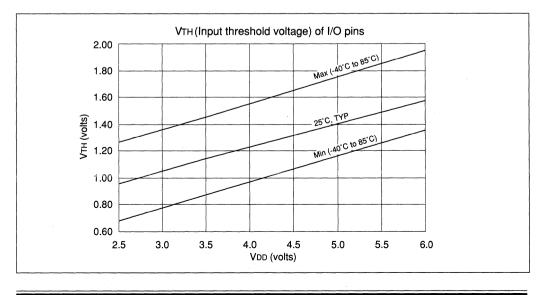

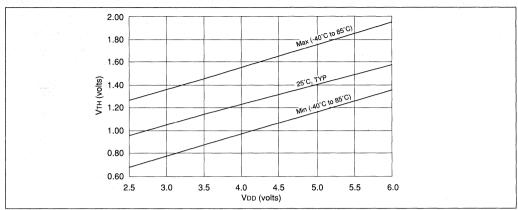

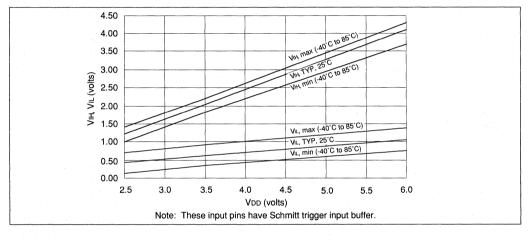

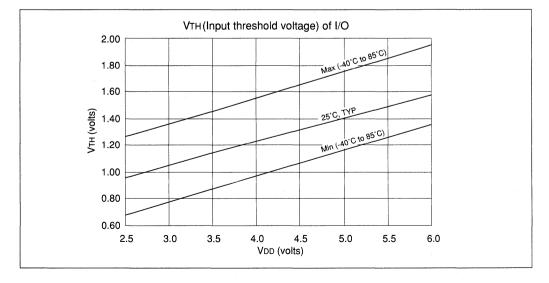

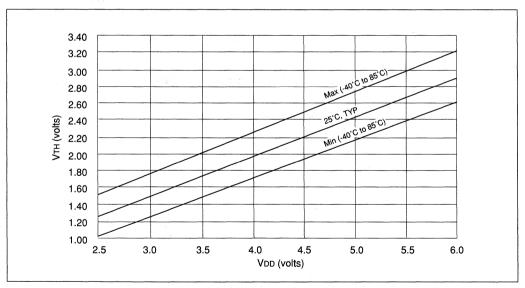

| 18.0.9                      | VTH (Input Threshold Voltage) of I/O Pins vs Vod |

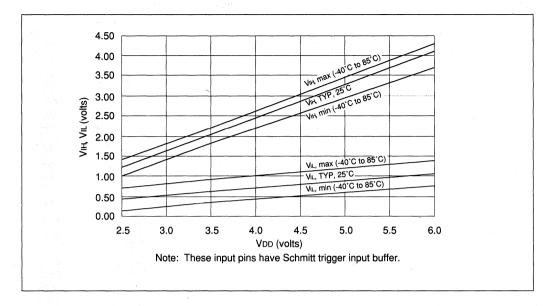

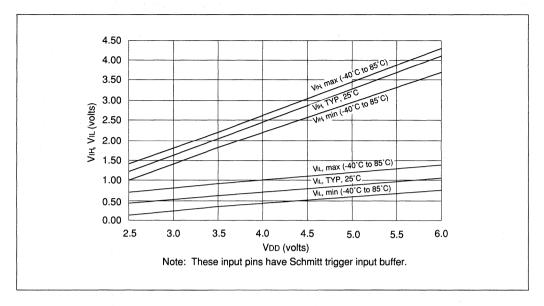

| 18.0.10                     | VIH, VIL for MCLR, RTCC and OSC1                 |

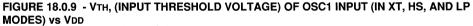

| 18.0.11                     | (in RC Mode) vs Vop                              |

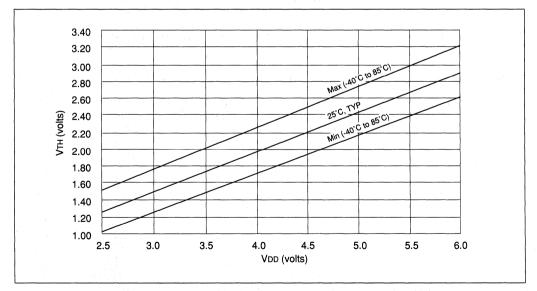

| 10.0.11                     | HS, and LP Modes vs VDD                          |

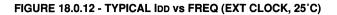

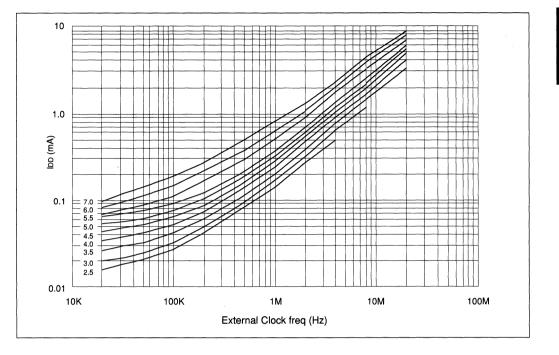

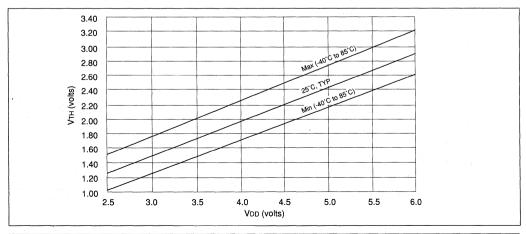

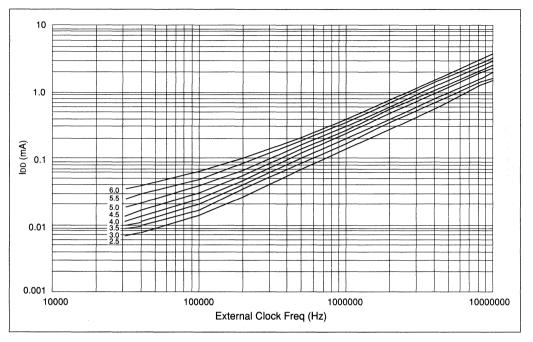

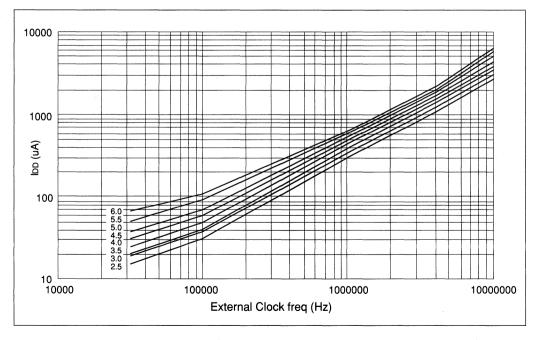

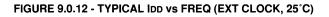

| 18.0.12                     | Typical Ibb vs Freg Ext Clock, 25°C              |

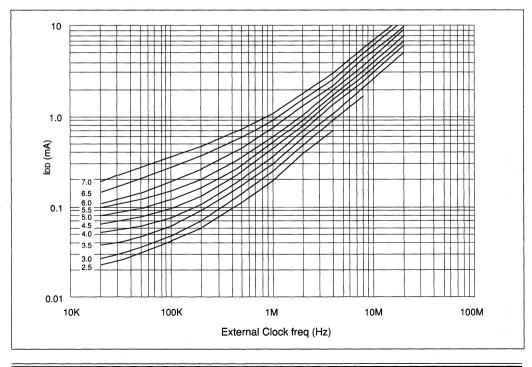

| 18.0.13                     | Maximum IbD vs Freq Ext Clock, -40° to +85°C     |

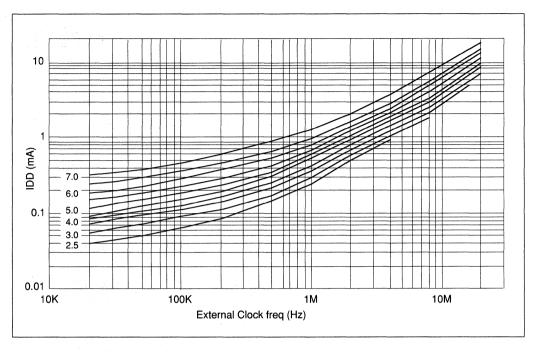

| 18.0.14                     | Maximum IDD vs Freq Ext Clock, -55° to +125°C 42 |

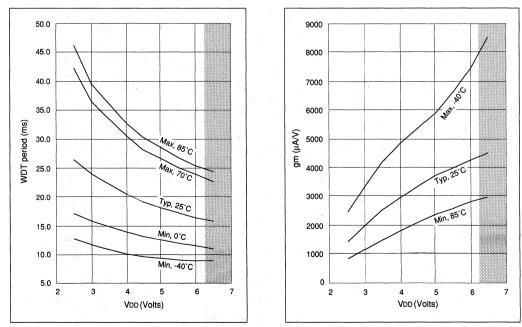

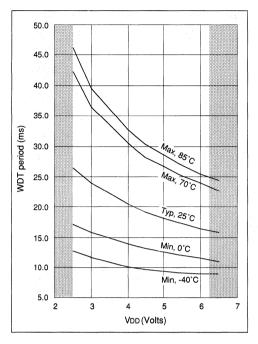

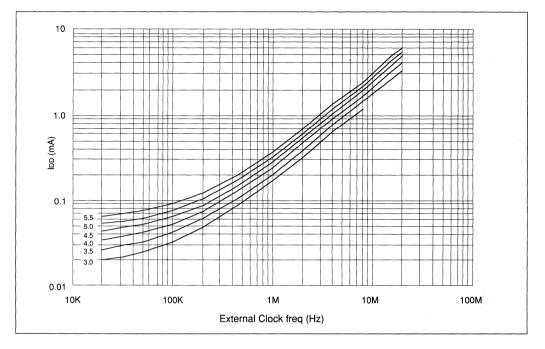

| 18.0.15                     | WDT Timer Time-out Period vs VDD                 |

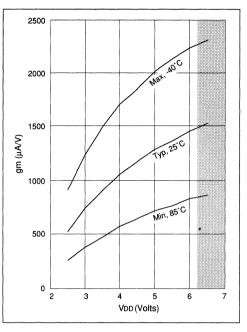

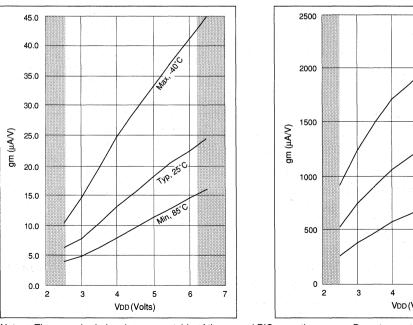

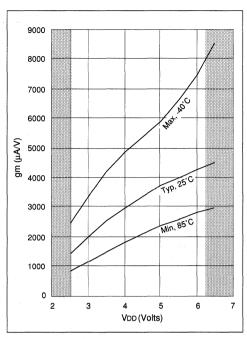

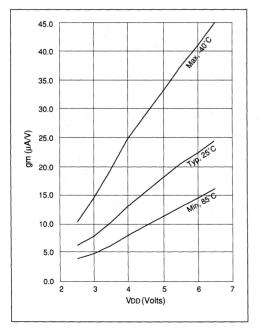

| 18.0.16                     | Transconductance (gm) of HS Oscillator vs Vpp    |

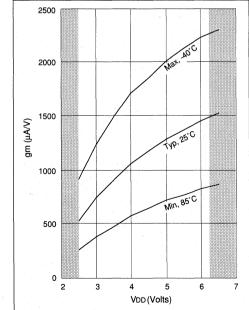

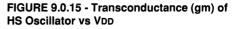

| 18.0.17                     | Transconductance (gm) of LP Oscillator vs VDD    |

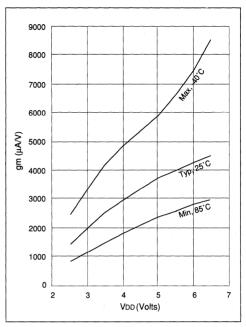

| 18.0.10                     | Transconductance (gm) of XT Oscillator VS VDD    |

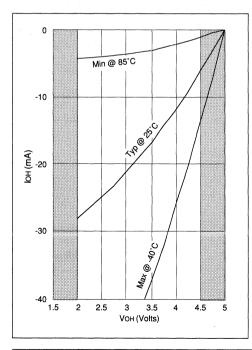

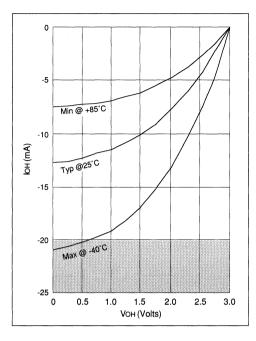

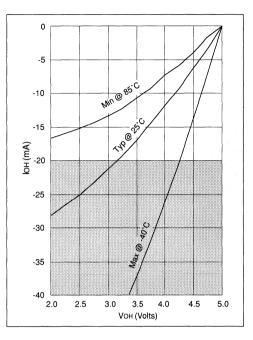

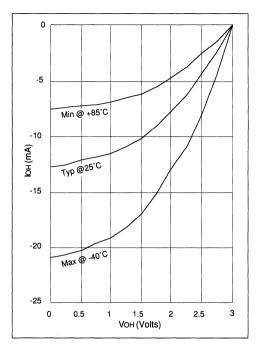

| 18 0 20                     | IOH VS VOH, VDD = 3V                             |

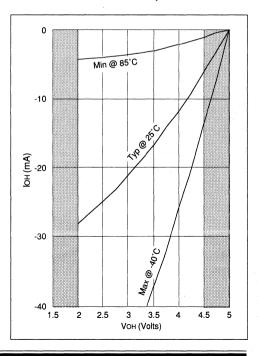

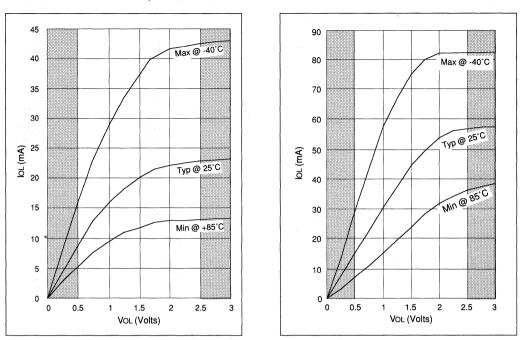

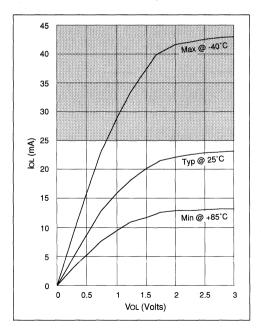

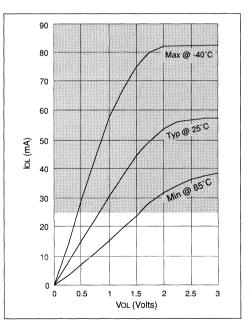

| 18.0.21                     | $IOL VS VOL, VDD = 3V \dots 44$                  |

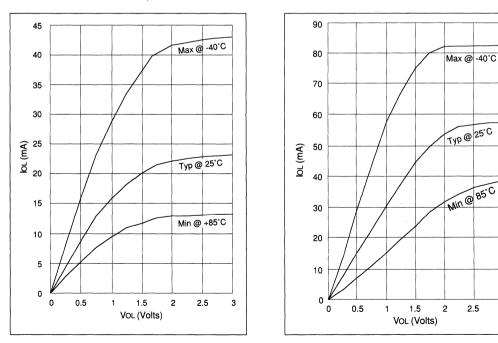

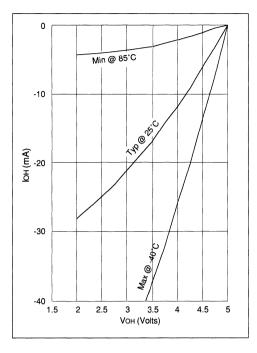

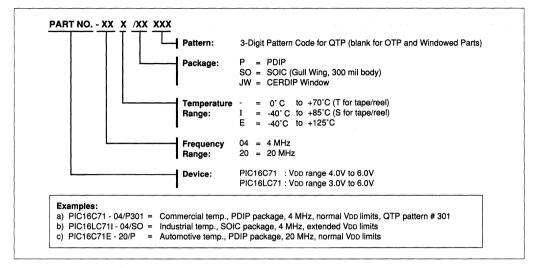

| 18.0.22                     | IOH VS VOH, VDD = 5V                             |