FBC Reference Manual

Curtis Priem

SUN Microsystems Inc.

2550 Garcia Avenue

Mountain View, CA 94030

Version 3.0

January 21, 1988

This Document contains unpublished, proprietary information and describes subject matter proprietary to SUN Microsystems Inc. This document may not be disclosed to third parties or copied or duplicated in any form without the prior written consent of SUN Microsystems Inc.

# CONTENTS

| Chapter | 1  | - | Introduction                                                                                                                 |  |  |

|---------|----|---|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Chapter | 2  | - | Register Summary                                                                                                             |  |  |

| Chapter | 3  | - | Addressing<br>Address Registers<br>Indexed Address Registers<br>Raster Offset Registers<br>Autoincrement Registers           |  |  |

| Chapter | 4  | - | Window Registers<br>CLIP Registers<br>Picking Window<br>Testing Window<br>TEC CLIPCHECK Register                             |  |  |

| Chapter | 5  | - | DRAW Command<br>DRAWSTATUS Register<br>Drawing Objects                                                                       |  |  |

| Chapter | 6  | - | BLIT Command<br>BLITSTATUS Register<br>Blitting Rectangles                                                                   |  |  |

| Chapter | 7  | - | FONT Command<br>FONT Register<br>FONTing Characters and Images                                                               |  |  |

| Chapter | 8  | - | STATUS Register                                                                                                              |  |  |

| Chapter | 9  | - | Attribute Registers<br>COLOR Registers<br>RASTEROP Register<br>PLANEMASK Register<br>PIXELMASK Register<br>PATTERN Registers |  |  |

| Chapter | 10 | _ | Miscellaneous Register                                                                                                       |  |  |

| Chapter | 11 | - | Configuration Register                                                                                                       |  |  |

#### 1 - INTRODUCTION

The FBC (Frame Buffer Controller) chip is the heart of the CG6 architecture. It contains the hardware to do 2D graphic rendering. The rendering hardware can execute the following commands:

| Command              | Source                                  | Destination                                  |

|----------------------|-----------------------------------------|----------------------------------------------|

|                      |                                         |                                              |

| DRAW<br>FONT<br>BLIT | PATTERN Register<br>CPU<br>Frame Buffer | Frame Buffer<br>Frame Buffer<br>Frame Buffer |

## 2 - REGISTER SUMMARY

There are a total of 76 user registers in the FBC which the CPU can access. The user registers are used to input the actual graphics commands and data. Only 33 of these registers need to be restored after a context switch.

There is one system register which the CPU can access using the HWC chip select. The system register is for hardware configuration and is accessed by the boot proms. They will reside in a different page from the user registers so that they can be protected by the MMU from user accesses. These registers do not need to be saved or restored during context switching.

All accesses to the registers will be 32 bit wide ONLY and are aligned to the 32 bit word boundary. This is the only type of access the 68020, 80386, and RISC processors have in common.

0 = zeros when read 1 = ones when read s = sign extended when read fbc = pointer to the FBC data structure fhc = pointer to the FBC Hardware Configuration data structure (protected) tec = pointer to the TEC data structure thc = pointer to the TEC Hardware Configuration data structure (protected)

| Address   | Name            |             | Description        |

|-----------|-----------------|-------------|--------------------|

|           | 31              | 0           | INDEXED ADDRESS RE |

| fbc+0x880 | ITRIABSX        | ·           | X for Integer Abso |

| fbc+0x884 | ITRIABSY        | +<br>       | Y for Integer Abso |

| fbc+0x888 | +<br>  ITRIABSZ | ++          | Z for Integer Abso |

| fbc+0x890 | ITRIRELX        | ++          | X for Integer Rela |

| fbc+0x894 | I ITRIRELY      | +<br>       | Y for Integer Rela |

| fbc+0x898 | 1               | +<br> <br>' | Z for Integer Rela |

| fbc+0x8c0 | <br>I IQUADABSX | <br>I       | X for Integer Abso |

| fbc+0x8c4 | IQUADABSY       | +<br>       | Y for Integer Abso |

| fbc+0x8c8 |                 | +           | Z for Integer Abso |

| fbc+0x8d0 | IQUADRELX       | +<br>       | X for Integer Rela |

| fbc+0x8d4 |                 | +<br>       | Y for Integer Rela |

| fbc+0x8d8 | IQUADRELZ       | +<br> <br>/ | Z for Integer Rela |

|           |                 |             |                    |

| fbc+0x900 | IRECTABSX       | +           | X for Integer Abs  |

| fbc+0x904 | IRECTABSY       | +           | Y for Integer Abs  |

| fbc+0x908 | IRECTABSZ       | +           | Z for Integer Abs  |

| fbc+0x910 | •               | +           | X for Integer Rel  |

| fbc+0x914 | IRECTRELY       | <br>        | Y for Integer Rel  |

| fbc+0x918 | IRECTRELZ       | '           | Z for Integer Rel  |

|           | 31              | 0           | RASTER OFFSET REG  |

| fbc+0x0c0 | RASTEROFFX      | <br>I       | X offset of rast   |

| fbc+0x0c4 | RASTEROFFY      | +<br> <br>/ | Y offset of rast   |

|           | 31              | 0           | AUTOINCREMENT REG  |

| fbc+0x0d0 | AUTOINCX        | <br>I       | X auto-increment   |

| fbc+0x0d0 | AUTOINCY        | +<br>1      | Y auto-increment   |

| TUCTOROUA | \               | /           | - 4400 2002 (Mont  |

| INDEXED ADDRESS REGISTERS<br>X for Integer Absolute Tri<br>Z for Integer Absolute Tri<br>X for Integer Relative Tri<br>Y for Integer Relative Tri<br>Z for Integer Relative Tri<br>X for Integer Absolute Quad<br>Y for Integer Absolute Quad<br>Z for Integer Absolute Quad<br>X for Integer Relative Quad<br>Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>Z for Integer Relative Quad<br>Z for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Rel Rectangle<br>X for Integer Rel Rectangle |                         |           |            |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------|------------|-------|

| Y for Integer Absolute Tri<br>Z for Integer Absolute Tri<br>X for Integer Relative Tri<br>Y for Integer Relative Tri<br>Z for Integer Relative Tri<br>X for Integer Absolute Quad<br>Y for Integer Absolute Quad<br>Z for Integer Relative Quad<br>X for Integer Relative Quad<br>Z for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>X for Integer Rel Rectangle                                                                                                                           | INDEX                   | ED ADDRES | SS REGISTI | ERS   |

| Z for Integer Absolute Tri<br>X for Integer Relative Tri<br>Z for Integer Relative Tri<br>Z for Integer Relative Tri<br>X for Integer Absolute Quad<br>Y for Integer Absolute Quad<br>Z for Integer Relative Quad<br>X for Integer Relative Quad<br>Z for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Rel Rectangle<br>X for Integer Rel Rectangle                                                                                                                          | X for                   | Integer   | Absolute   | Tri   |

| X for Integer Relative Tri<br>Y for Integer Relative Tri<br>Z for Integer Relative Tri<br>X for Integer Absolute Quad<br>Y for Integer Absolute Quad<br>X for Integer Relative Quad<br>Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Rel Rectangle<br>X for Integer Rel Rectangle                                                                                                                                                                                       | Y for                   | Integer   | Absolute   | Tri   |

| Y for Integer Relative Tri<br>Z for Integer Relative Tri<br>X for Integer Absolute Quad<br>Y for Integer Absolute Quad<br>Z for Integer Absolute Quad<br>X for Integer Relative Quad<br>Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>X for Integer Rel Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>X for Integer Rel Rectangle                                                                                                                                                                                                                     | Z for                   | Integer   | Absolute   | Tri   |

| Z for Integer Relative Tri<br>X for Integer Absolute Quad<br>Y for Integer Absolute Quad<br>Z for Integer Absolute Quad<br>X for Integer Relative Quad<br>Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>X for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>X for Integer Rel Rectangle<br>X for Integer Rel Rectangle                                                                                                                                                                                                                                                                                                                 | X for                   | Integer   | Relative   | Tri   |

| X for Integer Absolute Quad<br>Y for Integer Absolute Quad<br>Z for Integer Absolute Quad<br>X for Integer Relative Quad<br>Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                          | Y for                   | Integer   | Relative   | Tri   |

| Y for Integer Absolute Quad<br>Z for Integer Absolute Quad<br>X for Integer Relative Quad<br>Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Z for                   | Integer   | Relative   | Tri   |

| Y for Integer Absolute Quad<br>Z for Integer Absolute Quad<br>X for Integer Relative Quad<br>Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |           |            |       |

| Z for Integer Absolute Quad<br>X for Integer Relative Quad<br>Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X for                   | Integer   | Absolute   | Quad  |

| X for Integer Relative Quad<br>Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Y for                   | Integer   | Absolute   | Quad  |

| Y for Integer Relative Quad<br>Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Z for                   | Integer   | Absolute   | Quad  |

| Z for Integer Relative Quad<br>X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | X for                   | Integer   | Relative   | Quad  |

| X for Integer Abs Rectangle<br>Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Y for                   | Integer   | Relative   | Quad  |

| Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Z for                   | Integer   | Relative   | Quad  |

| Y for Integer Abs Rectangle<br>Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |           |            |       |

| Z for Integer Abs Rectangle<br>X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | X for                   | Integer   | Abs Recta  | angle |

| X for Integer Rel Rectangle<br>Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Y for                   | Integer   | Abs Recta  | angle |

| Y for Integer Rel Rectangle<br>Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Z for                   | Integer   | Abs Rect   | angle |

| Z for Integer Rel Rectangle<br>RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | X for                   | Integer   | Rel Recta  | angle |

| RASTER OFFSET REGISTERS<br>X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Y for                   | Integer   | Rel Rect   | angle |

| X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Z for                   | Integer   | Rel Rect   | angle |

| X offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         |           |            |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | RASTER OFFSET REGISTERS |           |            |       |

| Y offset of raster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | X of                    | fset of   | raster     |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Y of                    | fset of   | raster     |       |

AUTOINCREMENT REGISTERS

\_\_\_\_\_\_

\_\_\_\_\_/

CLIPCHECK

31

fbc+0x008 |

Description

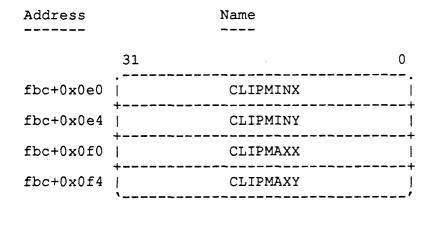

WINDOW REGISTERS

Upper Left X of Clip Window Upper Left Y of Clip Window lower Right X of Clip Window Lower Right Y of Clip Window

| CLIE | P CHEC | CK REG | ISTER    |

|------|--------|--------|----------|

| TEC  | Clip   | Check  | Register |

0

|           | 31 0      |             |

|-----------|-----------|-------------|

| fbc+0x100 | FCOLOR    | •           |

| fbc+0x104 | BCOLOR    |             |

| fbc+0x108 | RASTEROP  |             |

| fbc+0x10c | PLANEMASK |             |

| fbc+0x110 | PIXELMASK | -<br> <br>- |

| fbc+0x120 | PATTERNO  |             |

| fbc+0x124 | PATTERN1  |             |

| fbc+0x128 | PATTERN2  |             |

| fbc+0x12c | PATTERN3  |             |

| fbc+0x130 | PATTERN4  | +<br> <br>+ |

| fbc+0x134 | PATTERN5  | +<br> <br>_ |

| fbc+0x138 | PATTERN6  | -<br> <br>- |

| fbc+0x13c | PATTERN7  | -<br> <br>+ |

| fbc+0x11c | PATTALIGN | <br> <br>/  |

ATTRIBUTE REGISTERS Foreground Color Register Background Color Register RasterOp Register Plane Mask Register Pixel Mask Register Pattern Register 0 Pattern Register 1 Pattern Register 2 Pattern Register 3 Pattern Register 4 Pattern Register 5 Pattern Register 5 Pattern Register 6 Pattern Register 7 Pattern Alignment Register

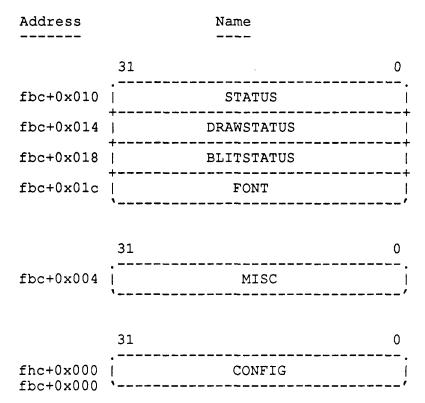

Description

STATUS & COMMAND REGISTERS Status Register DRAW Status Register BLIT Status Register Font Register MISCELLANEOUS REGISTER Miscellaneous Register

| CONFIGURATION | REGISTER |

|---------------|----------|

|               |          |

Configuration Register

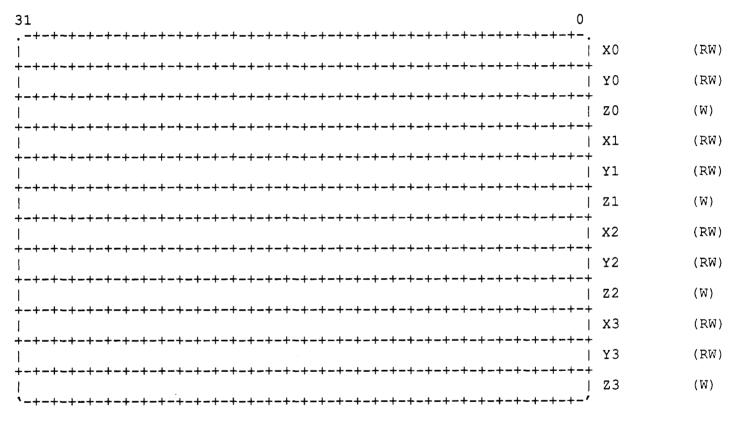

#### 3.1 - ADDRESS REGISTERS

The address registers have different meanings when doing DRAW, BLIT, or FONT commands. See each of the commands for details. When doing a DRAW or FONT, the address registers can represent either subpixels or pixels depending on if the FBC is in HRMONO mode (high resolution monochrome mode) or COLOR1 (1 plane COLOR mode, the FBC expands the source from 1 plane to 8 planes) respectively. When doing a DRAW, BLIT, or FONT the address registers represent pixel locations if the FBC is in COLOR8 mode (8 plane color mode). The Z registers do not store a Z value, but are used when the Z clip information is autoloaded from the TEC.

All the address registers can be read and written for context switching.

Figure 3-2 Address Registers (Signed Integer)

### 3.2 INDEXED ADDRESS REGISTERS

There are also a set of indexed address registers which reduces the number of accesses that need to be done to the FBC to load the absolute or relative coordinates for points, lines, triangles, quadrilaterals, and aligned rectangles, especially when these objects are chained. There is a 2 bit address INDEX which points to the next set of address registers that is to be modified. The INDEX is incremented after every X address is written for each of the objects and after Y is written for only the aligned rectangles. This allows the software to write only one x-y vertex to describe a chained point, line, triangle, or quadrilateral, and two vertices to describe a rectangle. The address INDEX can be read or written through the MISC register. The Y coordinate should always be loaded before the X coordinate.

The coordinate type of the indexed address registers can only be integer. For absolute coordinates, the contents of the RASTEROFFX or RASTEROFFY register is added to the value loaded into the FBC, and the result is placed into the registers pointed to by the address INDEX.

For relative coordinates, the contents of the X[INDEX-1] or Y[INDEX-1] register is added to the value loaded into the FBC, and the result is placed into the registers pointed to by the address INDEX.

Table 3-1 shows which address registers are affected by each of the index registers for every possible INDEX. The table also indicates which commands increment the INDEX.

| Index<br>Register      | INDEX=00    | INDEX=01    | INDEX=10    | INDEX=11    | INDEX++ |

|------------------------|-------------|-------------|-------------|-------------|---------|

| IPOINTABSX, IPOINTRELX | x0,x1,x2,X3 | X1,X2,X3,X0 | X2,X3,X0,X1 | x3,x0,x1,x2 | yes     |

| IPOINTABSY, IPOINTRELY | Y0,Y1,Y2,Y3 | Y1,Y2,Y3,Y0 | Y2,Y3,Y0,Y1 | Y3,Y0,Y1,Y2 | no      |

| IPOINTABSZ, IPOINTRELZ | Y0,Y1,Y2,Y3 | Y1,Y2,Y3,Y0 | Y2,Y3,Y0,Y1 | Y3,Y0,Y1,Y2 | no      |

| ILINEABSX, ILINERELX   | X0,X1,X2    | X1,X2,X3    | X2,X3,X0    | X3,X0,X1    | yes     |

| ILINEABSY, ILINERELY   | Y0,Y1,Y2    | Y1,Y2,Y3    | Y2,Y3,Y0    | Y3,Y0,Y1    | no      |

| ILINEABSZ, ILINERELZ   | Y0,Y1,Y2    | Y1,Y2,Y3    | Y2,Y3,Y0    | Y3,Y0,Y1    | no      |

| ITRIABSX, ITRIRELX     | X0,X1       | X1,X2       | X2,X3       | X3,X0       | yes     |

| ITRIABSY, ITRIRELY     | Y0,Y1       | Y1,Y2       | Y2,Y3       | Y3,Y0       | no      |

| ITRIABSZ, ITRIRELZ     | Y0,Y1       | Y1,Y2       | Y2,Y3       | Y3,Y0       | no      |

| IQUADABSX, IQUADRELX   | X0          | X1          | X2          | х3          | yes     |

| IQUADABSY, IQUADRELY   | YO          | Yl          | ¥2          | ¥3          | no      |

| IQUADABSZ, IQUADRELZ   | YO          | Yl          | ¥2          | Y3          | no      |

| IRECTABSX, IRECTRELY   | X0,X1       | X1,X2       | x2,x3       | X3,X0       | yes     |

| IRECTABSY, IRECTRELY   | Y0,Y1       | Y1,Y2       | Y2,Y3       | Y3,Y0       | yes     |

| IRECTABSZ, IRECTRELZ   | Y0,Y1       | Y1,Y2       | Y2, Y3      | Y3,Y0       | no      |

Table 3-1 Address Registers affected by Index Registers

#### 5.1 DRAW STATUS REGISTER

After the vertices have been entered, the DRAWSTATUS register is checked to see if the object can be drawn by the FBC (DRAW\_HARDWARE), or the object must be drawn by the software driver (DRAW\_SOFTWARE).

If an object is classified as DRAW\_HARDWARE, the FBC will be able to draw the object without any assistance from software. The definition of a DRAW\_HARDWARE object is:

| A) | The object is DRAW HIDDEN                               | (or)  |

|----|---------------------------------------------------------|-------|

|    | The object surrounds the clip window                    | (or)  |

| C) | 1) The object is not DRAW HIDDEN                        | (and) |

|    | 2) The object has only two active edges                 | (and) |

|    | 3) All of the vertices are between -2**14 and 2**14-1   | (and) |

|    | 4) a) All of the vertices are inside the test window    | (or)  |

|    | b) The object is a line and one of the end points       |       |

|    | is inside the test window                               | (or)  |

|    | c) All of the x vertices are inside the test window and |       |

|    | the top or bottom vertex is inside the test window      | (or)  |

|    | d) The object is an aligned rectangle (this includes    |       |

|    | vertical and horizontal lines)                          |       |

All other objects must be drawn by software. The FBC will only be able to help by doing horizontal lines, clipping, ROPs, etc. The definition of a DRAW SOFTWARE object is:

A) The object is not DRAW HARDWARE

The DRAWSTATUS register is updated whenever a value is written to the address or clip registers. The DRAW\_EXCEPTION bit in the register is set if one of the following bits are set:

| A) | DRAW_SOFTWARE    | (or) |

|----|------------------|------|

| B) | FBC FULL         | (or) |

| C) | TEC EXCEPTION    | (or) |

| D) | UNSUPPORTED ATTR | (or) |

| E) | ACC OVERFLOW     | (or) |

| F) | TECINTERSECT     |      |

The object is drawn by the FBC if the CPU reads the DRAWSTATUS register and the DRAW\_EXCEPTION bit is zero. If the DRAW\_EXCEPTION bit is set, the FBC will not render the object.

The DRAWSTATUS register is read only since by reloading the address and clip registers of the FBC during a context switch, the correct status will be regenerated.

| 31              | 24 23                             | 16 15                                   | 87                                                                                      | 0        |                |

|-----------------|-----------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------|----------|----------------|

| +-+-+           | +-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+++ | +-+-+-+-+-+-+-+                         | -+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+++-                                                     | -+-+-+   |                |

|                 | 10 01 1 10 01 1 10                |                                         |                                                                                         |          | DRAWSTATUS (R) |

| <b>`-+-+-</b> + | +-+-+-+-+-+-+-+-                  | +-+-+++++++++++++++++++++++++++++++++++ | -+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-++++++++++++++++++++++++++++++++++++++++++++++++++++ | -+-+-+-/ |                |

| Bits                  | Description    |                                                 |

|-----------------------|----------------|-------------------------------------------------|

| 31                    | DRAW EXCEPTION | (1=There is a DRAW exception)                   |

| 30                    |                | (1=TEC has an exception)                        |

| 29                    | FULL           | (1=FBC internal address registers are full)     |

| 28                    | BUSY           | (1=FBC is Busy)                                 |

| 25                    |                | R(1=Unsupported Attribute)                      |

| 24                    | HRMONO         | (1=High Resolution Monochrome)                  |

| 21                    | ACC OVERFLOW   |                                                 |

|                       | ACCPICK        | (1=Part of the Object Fell Inside PICK Window)  |

| 18                    | TECHIDDEN      | (1=Object is Hidden)                            |

| 17                    | TEC INTERSECT  |                                                 |

| 16                    | TEC VISIBLE    | (1=Object is Totally Inside the TEC CLIP check) |

| 15                    | BLIT HARDWARE  |                                                 |

| 14                    | BLIT SOFTWARE  | (1=Software must blit the rectangle)            |

| 13                    | BLIT SRC HID   | (1=Src Rect is Hidden)                          |

| 12                    | BLITSRCINT     | (1=Src Rect is Intersecting the CLIP Window)    |

|                       | BLIT_SRC_VIS   | (1=Src Rect is Totally Inside the CLIP Window)  |

|                       | BLIT_DST_HID   | (1=Dst Rect is Hidden)                          |

| 9                     | BLIT_DST_INT   | (1=Dst Rect is Intersecting the CLIP Window)    |

| 8                     | BLIT_DST_VIS   | (1=Dst Rect is Totally Inside the CLIP Window)  |

| 4                     | DRAW_HARDWARE  | (1=FBC can draw the Object)                     |

| 8<br>4<br>3<br>2<br>1 | DRAW_SOFTWARE  | (1=Software must draw the Object)               |

| 2                     | DRAW_HIDDEN    | (1=Object is Hidden)                            |

|                       | DRAW_INTERSECT | (1=Object is Intersecting the CLIP Window)      |

| 0                     | DRAW_VISIBLE   | (1=Object is Totally Inside the CLIP Window)    |

Figure 5-1 DRAW Status Register

# 5.2 DRAWING OBJECTS

The polygons can be drawn with bounding lines to form overlapping polygons or without bounding lines to form nonoverlapping polygons. Overlapping polygons are defined as the union of the (balanced) lines that connect the vertices of the polygon and all pixels inside the bounding lines. The points in common between two adjacent overlapping polygons will form a balanced line.

Nonoverlapping polygons are defined as all of the points on or within the ideal lines that connect the vertices except for the right most pixels and bottom line of each (trapezoid) section of the polygon. There are no points in common between two adjacent nonoverlapping polygons. Nonoverlapping lines and points are not drawn since they have no thickness. The attribute that selects between overlapping and nonoverlapping polygons is in the RASTEROP register.

When the edge of a polygon or a line falls half way between the center of two pixels, the FBC rounds to the right for horizontal midpoints or rounds down for vertical midpoints, with respect to the screen (not the x-y addressing).

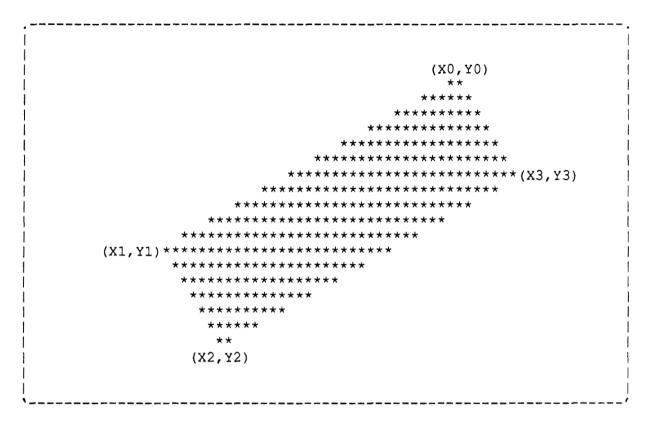

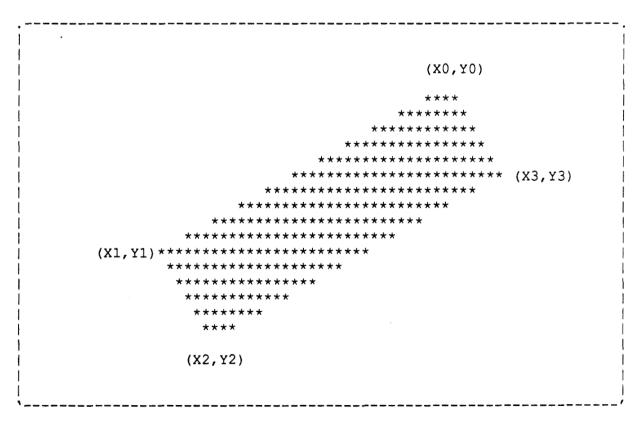

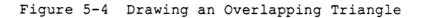

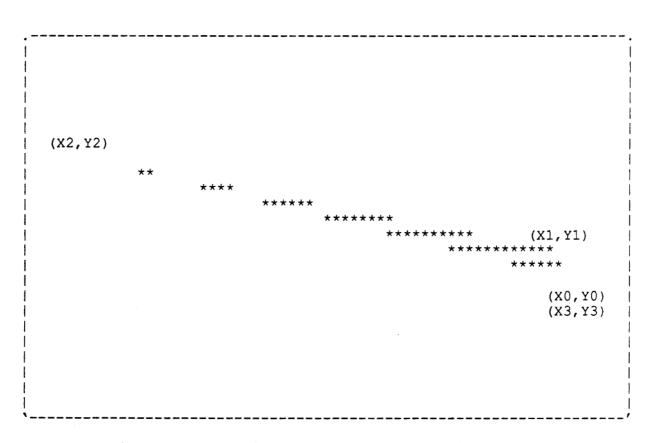

A quadrilateral can be drawn by entering four unique vertices into the IQUADABS or IQUADREL registers as shown in Figure 5-2 and 5-3. A triangle can be drawn by making two of the vertices the same or by entering only three vertices into the ITRIABS or ITRIREL registers as shown in Figure 5-4 and 5-5. A line can be drawn by making three of the vertices the same, by making two pair of vertices the same or, by entering only two vertices into the ILINEABS or ILINEREL registers as shown in Figure 5-6. A point can be drawn by making all four of the vertices the same or by entering only one vertex into the IPOINTABS or IPOINTREL registers as shown in Figure 5-7.

Figure 5-2 Drawing an Overlapping Quadrilateral

Figure 5-3 Drawing a Nonoverlapping Quadrilateral

Figure 5-5 Drawing a Nonoverlapping Triangle

Figure 5-7 Drawing an Overlapping Point

# 6 - BLIT COMMAND

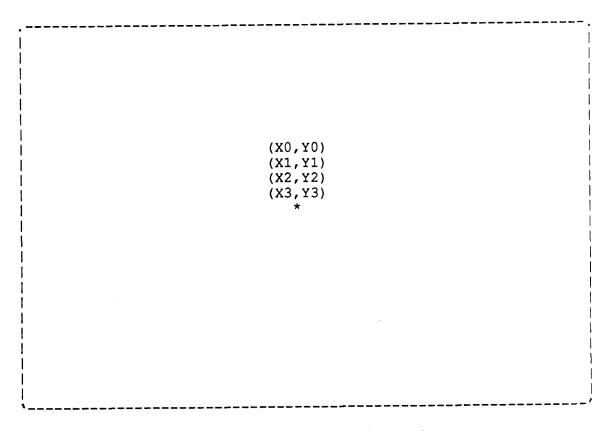

The FBC has the capability of doing a BLock Image Transfer (BLIT). The software can specify a rectangular area in the frame buffer as the source and another rectangular area in the frame buffer as the destination to which the source will be rasteroped. The source and destination can overlap in any direction and can be non-aligned.

The BLIT command can only be used in pixel coordinates (COLOR1 or COLOR8 mode). The meaning of the address registers for the BLIT command are shown in Table 6-1.

| Address<br>Register                    | -     |                            |                          | I                               | Descrip                                            | otion                                  |                                                |                            |                                                               |

|----------------------------------------|-------|----------------------------|--------------------------|---------------------------------|----------------------------------------------------|----------------------------------------|------------------------------------------------|----------------------------|---------------------------------------------------------------|

| X0<br>Y0<br>X1<br>Y1<br>X2<br>Y2<br>X3 |       | Y<br>X<br>Y<br>X<br>Y<br>X | coordinate coordinate    | for<br>for<br>for<br>for<br>for | upper<br>lower<br>lower<br>upper<br>upper<br>lower | left<br>right<br>left<br>left<br>right | corner<br>corner<br>corner<br>corner<br>corner | of<br>of<br>of<br>of<br>of | source<br>source<br>destination<br>destination<br>destination |

| ¥3                                     | Table |                            | coordinate<br>Address Re |                                 |                                                    | -                                      |                                                |                            | destination                                                   |

The addresses must be in the bounds of the screen and meet the constraints in Table 6-2.

| 1024x768 Color Mode   | 1024x1024 Color Mode  | 1152x900 Color Mode   |

|-----------------------|-----------------------|-----------------------|

|                       |                       |                       |

| X2 - X0 = X3 - X1     | X2 - X0 = X3 - X1     | X2 - X0 = X3 - X1     |

| Y2 - Y0 = Y3 - Y1     | Y2 - Y0 = Y3 - Y1     | Y2 - Y0 = Y3 - Y1     |

| 0 <= X0 <= X1 <= 1023 | 0 <= X0 <= X1 <= 1023 | 0 <= X0 <= X1 <= 1151 |

| 0 <= X2 <= X3 <= 1023 | 0 <= X2 <= X3 <= 1023 | 0 <= X2 <= X3 <= 1151 |

| 0 <= Y0 <= Y1 <= 767  | 0 <= Y0 <= Y1 <= 1023 | 0 <= Y0 <= Y1 <= 899  |

| 0 <= Y2 <= Y3 <= 767  | 0 <= Y2 <= Y3 <= 1023 | 0 <= Y2 <= Y3 <= 899  |

Table 6-2 Legal Address Register Ranges

### 6.1 BLIT STATUS REGISTER

After the vertices have been entered, the BLITSTATUS register is checked to see if the rectangle can be blitted by the FBC (BLIT\_HARDWARE), or it must be done by the software driver (BLIT\_SOFTWARE).

If an object is classified as BLIT\_HARDWARE, the FBC will be able to blit the rectangle without any assistance from software. The definition of a BLIT HARDWARE blit is:

| A) | Th | e destination rectangle is BLIT_DST_HID                           | (or)  |

|----|----|-------------------------------------------------------------------|-------|

| B) | 1) | The source rectangle is BLIT_SRC_HID                              | (and) |

|    | 2) | Blit source is included (BLIT_SRC_CHK=10)                         |       |

| C) |    | The source rectangle is BLIT SRC_VIS                              | (and) |

|    | 2) | Blit source is included (BLIT_SRC_CHK=10)                         | (and) |

|    | 3) | The destination rectangle is not BLIT_DST_HID                     | (and) |

|    | 4) | The source rectangle is between $-2**1\overline{4}$ and $2**14-1$ | (and) |

|    | 5) | The destination rectangle is between -2**14 and 2**14-1           |       |

| D) | 1) | Blit source is excluded (BLIT_SRC_CHK=01)                         | (and) |

|    | 2) | The destination rectangle is not BLIT_DST_HID                     | (and) |

|    | 3) | The source rectangle is between -2**14 and 2**14-1                | (and) |

|    |    |                                                                   |       |

4) The destination rectangle is between -2\*\*14 and 2\*\*14-1

All other blits must be done by software. The FBC will only be able to help by doing shifting, clipping, ROPs, etc. The definition of a BLIT\_SOFTWARE object is:

A) The object is not BLIT HARDWARE

The BLITSTATUS register is updated whenever a value is written to the address or clip registers. The BLIT\_EXCEPTION bit in the register is set if one of the following bits are set:

| A) | BLIT_SOFTWARE    | (or) |

|----|------------------|------|

| B) | FBC FULL         | (or) |

| C) | UNSUPPORTED ATTR | (or) |

| D) | ACC OVERFLOW     | (or) |

| E) | HRMONO           |      |

The rectangle is blitted by the FBC if the CPU reads the BLITSTATUS register and the BLIT\_EXCEPTION bit is zero. If the BLIT\_EXCEPTION bit is set, the FBC will not blit.

The BLITSTATUS register is read only since by reloading the address and clip registers of the FBC during a context switch, the correct status will be regenerated.

| 31     | 24 23 1                        | 6 15           | 8 7            | 0                   |

|--------|--------------------------------|----------------|----------------|---------------------|

|        |                                |                | 0 0 0          | BLITSTATUS (R)      |

| Bits   | Description                    |                |                |                     |

| 31     | BLIT EXCEPTION                 | (1=There is a  | BLIT exception | )                   |

| 30     | TEC EXCEPTION                  |                |                | ,                   |

| 29     | FULL                           |                |                | sters are full)     |

| 28     | BUSY                           | (1=FBC is Busy |                | -                   |

| 25     | UNSUPPORTED ATT                |                |                |                     |

| 24     | HRMONO —                       | (1=High Resolu | tion Monochrom | e)                  |

| 21     | ACC OVERFLOW                   | (1=Overflow in | FBC has occur  | red)                |

| 20     | ACC_PICK                       | (1=Part of the | Object Fell I  | nside PICK Window)  |

| 18     | TEC_HIDDEN                     |                |                |                     |

| 17     | TEC_INTERSECT                  | (1=Object is I | ntersecting th | e TEC CLIP check)   |

| 16     | TEC_VISIBLE                    |                |                | the TEC CLIP check) |

|        | BLIT_HARDWARE                  | (1=FBC can bli |                |                     |

| 14     | BLIT_SOFTWARE                  | (1=Software mu |                | ctangle)            |

| 13     | BLIT_SRC_HID                   | (1=Src Rect is | •              |                     |

| 12     | BLIT_SRC_INT                   |                |                | the CLIP Window)    |

| 11     | BLIT_SRC_VIS                   |                |                | e the CLIP Window)  |

| 10     | BLIT_DST_HID                   | (1=Dst Rect is | •              |                     |

| 9      | BLIT_DST_INT                   |                |                | the CLIP Window)    |

| 8      | BLIT_DST_VIS                   |                |                | e the CLIP Window)  |

| 4      | DRAW_HARDWARE                  | (1=FBC can dra |                | i o o t )           |

| 3<br>2 | DRAW_SOFTWARE                  |                | st draw the Ob | ject)               |

| 2      | DRAW_HIDDEN<br>DRAW INTERSECT  | (1=Object is H |                | e CLIP Window)      |

|        | DRAW_INIERSECT<br>DRAW_VISIBLE |                |                | the CLIP Window)    |

| 0      | DKWM_AT2TDTF                   | (I-ODJECT IS I | Juarry Inside  | CHE CHIF WINDOW/    |

Figure 6-1 BLIT Status Register

# 6.2 BLITTING RECTANGLES

Figure 6-2 gives an example of blitting the source to the destination rectangle.

Figure 6-2 Example of a BLIT

#### 7 - FONT COMMAND

The software can read and write to the frame buffer by using the FONT register. There are two ways to access the frame buffer; by plane and by pixel. If a character font is described in a single plane data structure, it can be written to the frame buffer through the FONT register in COLOR1 or HRMONO mode. The FBC will expand it to the eight planes of data (with the correct RASTEROP and COLOR) in COLOR1 mode and expand it to the proper grayscale value in HRMONO mode. The FONT register is write only in these modes since the FBC can not do a reverse conversion (8 planes to one). If a character font or image is described in an eight plane format, it can be written to the the frame buffer (with RASTEROP and COLOR) through the FONT register in COLOR8 mode. The Table 7-1 summarizes the different modes for the FONT register.

| Mode   | CPU Format | FB Format | FONT R/W |

|--------|------------|-----------|----------|

|        |            |           |          |

| HRMONO | 1 plane    | 8 planes  | W        |

| COLOR1 | 1 plane    | 8 planes  | W        |

| COLOR8 | 8 planes   | 8 planes  | W        |

Table 7-1 FONT Register Modes

Before a character or image is written to the frame buffer, address range and window comparisons must be done. This can be done by setting up the FBC to draw a rectangle around the area that is to be modified. The upper left and lower right points should be entered using the IRECTABSX and IRECTABSY registers. The STATUS register is then checked for any exceptions and to see if the object does not DRAW\_INTERSECT the clip window or is DRAW\_HIDDEN. If there are no special cases, the software can start downloading the image or font to the frame buffer.

The address registers must then be loaded with the font mask or font width mask (the horizontal line of pixels or subpixels that are to be RASTEROPed). This is done by loading (X0,Y0) with the left point and (X1,Y0) with the right most point of where the data will be placed in the frame buffer. The number of pixels or subpixels (inclusive) between X0 and X1 indicates the width of the data that will be loaded into the FONT register. The difference between X0 and X1 should not be greater than 31 for HRMONO and COLOR1 and should not be greater than 3 for COLOR8. No pixels or subpixels will be modified outside this range. This mask is combined with the clip mask before rendering.

Normally the AUTOINCX and AUTOINCY registers are used in conjunction with the font register.

The meaning of the address registers for a FONT command are given in Table 7-2.

| X0 | X coordinate for left pixel/subpixel of font  |

|----|-----------------------------------------------|

| YO | Y coordinate for left pixel/subpixel of font  |

| X1 | X coordinate for right pixel/subpixel of font |

| Y1 | (used only during clip window checking)       |

| X2 | (used only during clip window checking)       |

| ¥2 | (used only during clip window checking)       |

| ХЗ | (used only during clip window checking)       |

| Y3 | (used only during clip window checking)       |

|    |                                               |

Table 7-2 Address Registers for FONT Command

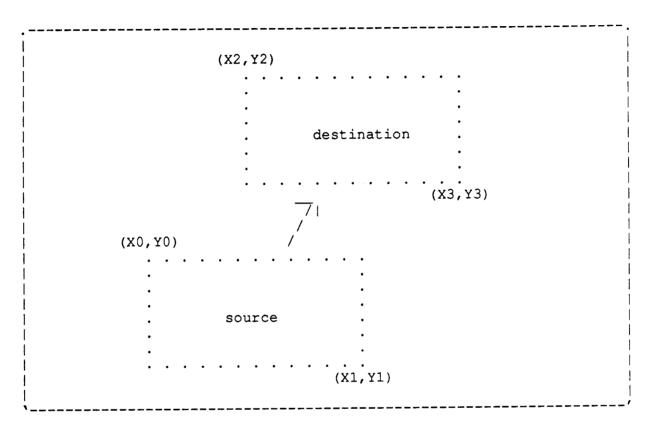

# 7.1 FONT REGISTER

The FONT register can be used in either HRMONO, COLOR1, or COLOR8 mode. The addressing is pixel coordinates for color mode and subpixel coordinates for anti-aliasing mode. Reads from the FONT register while in COLOR8 mode are normally done only for saving the contents of the screen, ie. when a window needs to be saved or moved.

The FONT register does not have to be saved during context switching because the frame buffer data may change before that context is used again.

31 Ω (W) Description Bits \_\_\_\_ \_\_\_\_\_ 31 Source Bit for Pixel (X0, Y0) 30 Source Bit for Pixel (X0+1, Y0) Source Bit for Pixel (X0+30,Y0) 1 Source Bit for Pixel (X0+31,Y0) 0 Figure 7-3 FONT Register Format (COLOR1 mode & 68020/SPARC mode) 31 0

|    |        |     | -   |       |         |      |

|----|--------|-----|-----|-------|---------|------|

| 31 | Source | Bit | for | Pixel | (X0+31, | ,YO) |

| 30 | Source | Bit | for | Pixel | (X0+30, | ,YO) |

| •  | •      |     |     | •     |         | •    |

| 1  | Source | Bit | for | Pixel | (X0+1,  | Y0)  |

| 0  | Source | Bit | for | Pixel | (X0,    | Y0)  |

|    |        |     |     |       |         |      |

Figure 7-4 FONT Register Format (COLOR1 mode & 80386 mode)

| 31       | 0                                                                        |     |

|----------|--------------------------------------------------------------------------|-----|

|          | +=+=+=+=+=+=+=+=+=+=+=+=+=+=+=+=+=+=+=                                   | (W) |

| Bits     | Description                                                              |     |

| 31<br>30 | Source Bit for Subpixel (X0, Y0)<br>Source Bit for Subpixel (X0+1, Y0)   |     |

| 1<br>0   | Source Bit for Subpixel (X0+30,Y0)<br>Source Bit for Subpixel (X0+31,Y0) |     |

| Figure   | 7-5 FONT Register Format (HRMONO mode & 68020/SPARC mode)                |     |

87 0 31 24 23 16 15 (X0,Y0) | (X0+1,Y0) | (X0+2,Y0) | (X0+3,Y0) | FONT (RW) 1 Bits Description Bits Description \_\_\_\_ ----\_\_\_\_\_ -----31 Pixel (X0,Y0), Plane 7 15 Pixel (X0+2,Y0), Plane 7

Pixel (X0,Y0), Plane 0

8

Pixel (X0+2,Y0), Plane 0

Pixel (X0+1,Y0), Plane 7

7

Pixel (X0+3,Y0), Plane 7

24 23 Pixel (X0+1,Y0), Plane 0 0 Pixel (X0+3,Y0), Plane 0 16

Figure 7-7 FONT Register Format (COLOR8 mode & 68020/SPARC mode)

| Bits | Description              | Bits | Description              |  |  |

|------|--------------------------|------|--------------------------|--|--|

|      |                          |      |                          |  |  |

| 31   | Pixel (X0+3,Y0), Plane 7 | 15   | Pixel (X0+1,Y0), Plane 7 |  |  |

| •    | • •                      | •    | • •                      |  |  |

| 24   | Pixel (X0+3,Y0), Plane 0 | 8    | Pixel (X0+1,Y0), Plane 0 |  |  |

| 23   | Pixel (X0+2,Y0), Plane 7 | 7    | Pixel (X0,Y0), Plane 7   |  |  |

| •    | • •                      |      | • • •                    |  |  |

| 16   | Pixel (X0+2,Y0), Plane 0 | 0    | Pixel (X0,Y0), Plane 0   |  |  |

|      |                          |      |                          |  |  |

Figure 7-8 FONT Register Format (COLOR8 mode & 80386 mode)

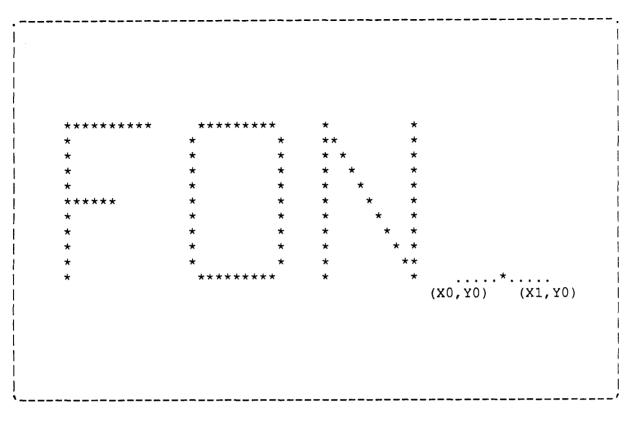

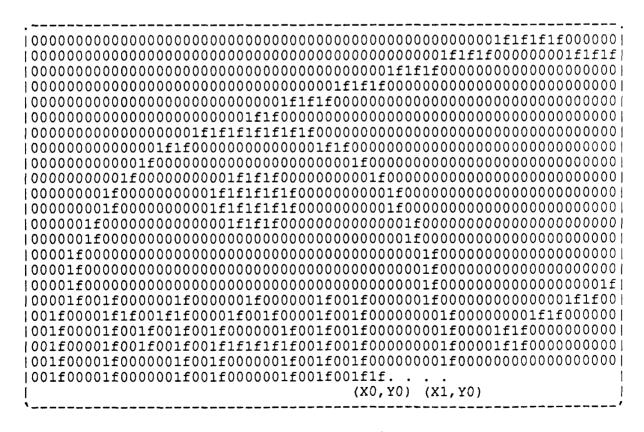

## 7.2 FONTING CHARACTERS AND IMAGES

Figure 7-9 gives an example of fonting a character in COLOR1 mode with the following initializations: AUTOINCX=0, AUTOINCY=-1, and X1=X0+10. The next value to be written to FONT is 0x04000000. Figure 7-10 gives an example of fonting an image in COLOR8 mode with the following initializations: AUTOINCX=4, AUTOINCY=0, X1=X0+3, mode=68020. The next value to be written to FONT is 0x1f1f001f.

Figure 7-9 Example of a FONTing a Character

Figure 7-10 Example of a FONTing an Image

## 8 - STATUS REGISTER

The STATUS register contains the status of DRAWSTATUS, BLITSTATUS, PT\_STATUS, and accumulated status. The STATUS register is updated whenever a value is written to the address or clip registers.

The FBC overflow state is accumulated in the STATUS register in the ACC\_OVERFLOW bit. The PICK is also accumulated in the STATUS register in the ACC\_PICK bit. An accumulated status is cleared by setting the ACC\_CLEAR bit and the appropriate bit for the flag that is to be cleared. All flags that do not have their bits set will not be affected. If the ACC\_CLEAR bit is not set, the value written will be loaded into the registers.

The status mask register can be read and written for context switching. The ACC\_CLEAR bit will always read zero so that when the STATUS is reloaded during a context switch the flags will be set and not cleared. Writing to the STATUS register can only affect the ACC status. The other status will be regenerated during a context switch by reloading the address and clip registers.

| 31                                   | 24 23                                   | 16 15            | 8 7                                                | 0           |

|--------------------------------------|-----------------------------------------|------------------|----------------------------------------------------|-------------|

| +-+-+-++++++++++++++++++++++++++++++ | -+-+-++++++++++++++++++++++++++++++++++ | -+-+-+-+-+-+-+-+ | -+-+-+-+-+-+-+-+++++++++++++++++++++++++++++++++++ | +           |

| 101 1 1 10 01                        | 0 0     0                               |                  |                                                    | STATUS (RW) |

| `-+-+-+-+-+                          | -+-+-+-+-+-+-+                          | -+-+-+-+-+-+-+-+ | -+-+-+-+-+-+-++                                    | +-'         |

| Bits                                                                             | Description                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                      |                                                                                                                    |

|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 31<br>30<br>29<br>28<br>25<br>24<br>21<br>20<br>18<br>17<br>16<br>15<br>14<br>13 | ACC_CLEAR (1=Clea<br>TEC_EXCEPTION (1=TEC<br>FULL (1=FBC<br>BUSY (1=FBC<br>UNSUPPORTED_ATTR(1=Unsu<br>HRMONO (1=High<br>ACC_OVERFLOW (1=Over<br>ACC_PICK (1=Part<br>TEC_HIDDEN (1=Obje<br>TEC_INTERSECT (1=Obje<br>TEC_VISIBLE (1=Obje<br>BLIT_HARDWARE (1=FBC<br>BLIT_SOFTWARE (1=Soft<br>BLIT_SRC HID (1=Src | has an exception)<br>internal address re<br>is Busy)<br>pported Attribute)<br>Resolution Monochr<br>flow in FBC has occ<br>of the Object Fell<br>ct is Hidden)<br>ct is Intersecting<br>ct is Totally Inside<br>can blit the rectand | gisters are full)<br>ome)<br>urred)<br>Inside PICK Window)<br>the TEC CLIP check)<br>e the TEC CLIP check)<br>gle) |

|                                                                                  | BLIT_SRC_VIS(1=SrcBLIT_DST_HID(1=DstBLIT_DST_INT(1=DstBLIT_DST_VIS(1=DstDRAW_HARDWARE(1=FBCDRAW_SOFTWARE(1=SoftDRAW_HIDDEN(1=ObjecDRAW_INTERSECT(1=Objec                                                                                                                                                       | Rect is Hidden)<br>Rect is Intersecting                                                                                                                                                                                              | ide the CLIP Window)<br>g the CLIP Window)<br>ide the CLIP Window)<br>)<br>Object)<br>the CLIP Window)             |

Figure 8-1 STATUS Register

# 9 - ATTRIBUTE REGISTERS

There are five attribute register sets: COLOR, RASTEROP, PLANEMASK, PIXELMASK, and PATTERN. They contain information about the current attributes of the FBC.

All the attribute registers can be read and written for context switching. It is expected that a copy of the attribute registers will be kept in memory so that on a context switch the attribute register contents will not have to be saved. Only the new context's attributes will have to be loaded.

The FBC must be idle before any of these registers can be written to.

#### 9.1 COLOR REGISTERS

The color registers contain the current foreground and background colors. They are used in combination with the RASTEROP register to determine the final graphics operation that is to be done when rendering to the frame buffer. In COLOR1 or COLOR8 mode the eight bits of color registers correspond to the eight planes of the frame buffer. In HRMONO mode only the lowest bit has meaning, the other seven bits are ignored.

| 31                                              | 8 7            | 0           |

|-------------------------------------------------|----------------|-------------|

| ·-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+         |                |             |

|                                                 |                | FCOLOR (RW) |

|                                                 |                | BCOLOR (RW) |

| <b>`</b> -+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+ | +-+-+-+-+-+-+- | -+-'        |

| Bits | Description                                  |

|------|----------------------------------------------|

|      |                                              |

| 7    | Color bit for plane 7 (COLOR Modes Only)     |

| 6    | Color bit for plane 6 (COLOR Modes Only)     |

| 5    | Color bit for plane 5 (COLOR Modes Only)     |

| 4    | Color bit for plane 4 (COLOR Modes Only)     |

| 3    | Color bit for plane 3 (COLOR Modes Only)     |

| 2    | Color bit for plane 2 (COLOR Modes Only)     |

| 1    | Color bit for plane 1 (COLOR Modes Only)     |

| 0    | Color bit for plane 0 (COLOR or HRMONO Mode) |

Figure 9-1 Foreground and Background Color Registers

### 9.2 RASTEROP REGISTER

The FBC contains two different types of rasterops: BOOLEAN (Pixrect type) and LINEAR (anti-aliasing). The rasterops will be done in parallel across all pixels in the 128 bit (16 pixel) datapath.

Both types of rasterops have 16 different logical operations with two colors and masking. There will be a sixteen bit rasterop register where the software will be able to program any of the 64K combinations of rasterops.

The BOOLEAN rasterops are done between each corresponding source and destination bit of every pixel.

|        | Code |

|--------|------|

|        |      |

| SOURCE |      |

| DESTIN | 1010 |

| OP_urop | Code | Description          | Pixrect rop | CTX_ROP Values          |

|---------|------|----------------------|-------------|-------------------------|

|         |      |                      | PIX OPCLR   | CTX ROP CLEAR           |

| 0       | 0000 | d < - (0)            | FIX_OFCHK   | CTX ROP NOR             |

| 1       | 0001 | d <- (~((d)   (s)))  |             |                         |

| 2       | 0010 | d <- ((d) & ~(s))    |             | CTX_ROP_ERASE           |

| 3       | 0011 | d <- (~(s))          |             | CTX_ROP_DRAW_INVERTED   |

| 4       | 0100 | d <- (~(d) & (s))    |             | CTX ROP ERASED REVERSED |

| 5       | 0101 | d < - (~(d))         |             | CTX_ROP_INVERT          |

| 6       | 0110 | d <- ((d) ^ (s))     |             | CTX_ROP_XOR             |

| 7       | 0111 | d <- (~((d) & (s)))  |             | CTX_ROP_NAND            |

| 8       | 1000 | d < - ((d) & (s))    |             | CTX_ROP_AND             |

| 9       | 1001 | $d < - ((d) ^ ~(s))$ |             | CTX_ROP_EQUIVALENT      |

| А       | 1010 | d <- (d)             | PIX_OPDST   | CTX_ROP_NOP             |

| в       | 1011 | d <- ((d)   ~(s))    | -           | CTX_ROP_PAINT_INVERTED  |

| С       | 1100 | d <- (s)             | PIX_OPSRC   | CTX_ROP_DRAW            |

| D       | 1101 | d <- (~(d)   (s))    |             | CTX_ROP_PAINT_REVERSED  |

| E       | 1110 | d <- ((d)   (s))     |             | CTX ROP PAINT           |

| F       | 1111 | d <- (~0)            | PIX_OPSET   | CTX_ROP_SET             |

Figure 9-2 16 BOOLEAN Raster Operations

Programming a Raster Operation for the FBC involves selecting the appropriate RasterOp for the four combinations of foreground and background bit values (ie. 00, 01, 10, 11) for any given plane that will result in the desired effect.

The LINEAR rasterops assume that the pixels each contain a linear grayscale value that represent the intensity of that pixel. If the FBC is in COLOR mode, the grayscale value will be operated on directly. If the FBC is in HRMONO mode, a source bit represents one of 16 subpixels for each pixel in the frame buffer. These subpixels can be altered to be s, ~s, 0, or 1 which is then masked againsted the clip window. The resulting subpixels are then applied to a flat antialiasing filter. The flat filter weighting is:

The grayscale value is calculated by adding together the weighting coefficients of the subpixels that are set and are not masked for a given subpixel line. The resulting value is the linear grayscale source which is applied to the linear rasterop.

There are 10 linear rasterops which are supported by the FBC. The 6 rasterops that are not supported must be done in a two step process. 1) The background must be prepared by clearing, setting, or complementing the data in the frame buffer. 2) The image must be merged into the frame buffer through the use of the DRAW, ERASE, etc. rasterops.

The linear rasterops are composed of the add/subtract with/without saturate functions. Figure 9-3 shows the LINEAR functions that corresponds to the BOOLEAN functions. When complementing the destination, the FBC must be set to PLOT for the initial drawing and to UNPLOT mode to erase the object. Bit 7 of the frame buffer is a direction bit that corresponds to the carry out of the add/subtract function. This bit allows the destination to be complemented and uncomplemented correctly. There are two indexes that correspond to each grayscale level.

| Code<br>SOURCE 1100<br>DESTIN 1010             |                                          |                                      |                                      |

|------------------------------------------------|------------------------------------------|--------------------------------------|--------------------------------------|

| OP_urop Code                                   | Description                              | PLOT                                 | UNPLOT                               |

| 0 0000                                         | • •                                      | d = sat(d - 1)<br>na                 | d = sat(d - 1)<br>na                 |

| 1 0001<br>2 0010<br>3 0011<br>4 0100<br>5 0101 | $d <- ((d) & \sim(s)) \\ d <- (\sim(s))$ | d = sat(d - s)<br>na<br>na           | d = sat(d - s)<br>na<br>na           |

| 5 0101<br>6 0110<br>7 0111                     | $d <- (~(d)) d <- ((d) ^ (s))$           | d = d + 1 $d = d + s$ na             | d = d - 1 $d = d - s$ na             |

| 8 1000<br>9 1001<br>A 1010                     | $d <- ((d) \& (s)) d <- ((d) ^ (s))$     | d = sat(d -~s)<br>d = d +~s<br>d = d | d = sat(d -~s)<br>d = d -~s<br>d = d |

| B 1011<br>C 1100<br>D 1101                     | d <- ((d)   ~(s))<br>d <- (s)            | d = sat(d +~s)<br>na<br>na           | d = sat(d +~s)<br>na<br>na           |

| E 111(<br>F 1111                               | ) $d < -((d) + (s))$                     | d = sat(d + s)<br>d = sat(d + 1)     |                                      |

Figure 9-3 10 LINEAR Raster Operations

Programming a Raster Operation for the FBC involves selecting the appropriate RasterOp for the four combinations of foreground and background bit values (ie. 00, 01, 10, 11) for only plane 0 that will result in the desired effect.

The RASTEROP register can override the values in the PLANEMASK, PIXELMASK, and PATTERN registers without affecting the values in the registers. The type of polygon is also stored in the RASTEROP register.

| 31 | 2      | 24 23 16 15<br>+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-            | 8 7                                                      | 0                          |      |

|----|--------|----------------------------------------------------------------|----------------------------------------------------------|----------------------------|------|

|    | 1 1    | 0 0 0 0      ROp11  <br>-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+ | ROp10   ROp01                                            | ROp00   RASTEROP           | (RW) |

|    | Bits   | Description                                                    |                                                          |                            |      |

|    | 31-30  | Override Plane Mask Selec<br>(00=Ignore, 01=Use zeroes         |                                                          | 11=Use PLANEMASK)          |      |

|    | 29-28  |                                                                | ct                                                       |                            |      |

|    | 27-26  | Override Pattern Select<br>(00=Ignore, 01=Use zeroes           |                                                          |                            |      |

|    | 25-24  | Polygon Draw Select<br>(00=Ignore, 01=Overlappir               |                                                          |                            |      |

|    | 23-22  | UNSUPPORTED_ATTR<br>(00=Ignore, 01=Unsupporte                  |                                                          |                            |      |

|    |        | Plot/Unplot Mode                                               | (0=PLOT, 1=UNPLO                                         | T>                         |      |

|    |        |                                                                | R[p]=1 and BCOLO<br>R[p]=1 and BCOLO<br>R[p]=0 and BCOLO | R[p]=1<br>R[p]=0<br>R[p]=1 |      |

|    | where: | FCOLOR[p] is the foregrou<br>BCOLOR[p] is the backgrou         |                                                          |                            |      |

|    |        | Figure 9-4 RasterOp Regi                                       | lster                                                    |                            |      |

### 9.3 PLANEMASK REGISTER

The plane mask register determines which planes should be written to and which should not. This allows the software to write only to the specified planes. The plane mask is tied directly to the frame buffer (it actual resides in the video ram) and works the same in color or anti-aliasing modes.

| 31       |                                                                                        | L_ 1 _ L_ L_ L_ L_ L L | 8 7                                  | 0              |

|----------|----------------------------------------------------------------------------------------|------------------------|--------------------------------------|----------------|

| 10000000 | -+-+-+-+-+-+-+-+-+-+-<br>0 0 0 0 0 0 0 0 0 0<br>-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+ | 0 0 0 0 0 0 0          | ) 0                                  | PLANEMASK (RW) |

| Bits     | Description                                                                            |                        |                                      |                |

| 7<br>6   | Plane 7 Mask<br>Plane 6 Mask                                                           |                        | sabled, 1=Writes<br>sabled, 1=Writes |                |

| •        | •                                                                                      | •                      | •                                    |                |

| 1<br>0   | Plane 1 Mask<br>Plane 0 Mask                                                           | •                      | sabled, 1=Writes<br>sabled, 1=Writes |                |

Figure 9-5 Plane Mask Register

### 9.4 PIXELMASK REGISTER

The pixel mask register determines which pixels should be written to and which should not. This allows the software to write to specified pixels for operations such as stenciling. The pixel mask is tied directly to the frame buffer and works the same in color or anti-aliasing mode.

|                |                                                    |            | +_+_+_+_+_+_+_+_+_<br> | PIXELMASK (RW)                                                 |

|----------------|----------------------------------------------------|------------|------------------------|----------------------------------------------------------------|

| Bits           | Description                                        |            |                        |                                                                |

| 31<br>30<br>29 | Mask for Pixel<br>Mask for Pixel<br>Mask for Pixel | (x%32==1)  | (left most)            | (1=Writes enabled)<br>(1=Writes enabled)<br>(1=Writes enabled) |

| 2<br>1<br>0    | Mask for Pixel<br>Mask for Pixel<br>Mask for Pixel | (x%32==30) | (right most)           | (1=Writes enabled)<br>(1=Writes enabled)<br>(1=Writes enabled) |

|                | Figure                                             | 9-6 PIXELM | ASK Register (68       | 020/SPARC mode)                                                |

|                |                                                    |            |                        |                                                                |

| 31                                             |                                               | 0              |

|------------------------------------------------|-----------------------------------------------|----------------|

| -                                              | <u>-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+-+</u> |                |

|                                                |                                               |                |