# Pentium<sup>™</sup> Processors and Related Products

Microprocessors

PCIsets

Peripheral Components

## Pentium<sup>™</sup> Processors and Related Products

Microprocessors, PCIsets, Peripheral Components

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

\*Other brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

©INTEL CORPORATION, 1995

### DATASHEET DESIGNATIONS

Intel uses various datasheet markings to designate each phase of the document as it relates to the product. The markings appear in the lower inside corner of each datasheet page. Following are the definitions of each marking:

| Datasheet Marking    | Description                                                                                                                                                                                             |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview      | Contains information on products in the design phase of<br>development. Do not finalize a design with this<br>information. Revised information will be published<br>when the product becomes available. |

| Advanced Information | Contains information on products being sampled or in the initial production phase of development.*                                                                                                      |

| Preliminary          | Contains preliminary information on new products in production.*                                                                                                                                        |

| No Marking           | Contains information on products in full production.*                                                                                                                                                   |

\* Specifications within these datasheets are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

λ

Pentium<sup>TM</sup> Processor Overview

Pentium<sup>TM</sup> Processor and Peripherals

### **Table of Contents**

| Alphanumeric Index                                                          | x     |

|-----------------------------------------------------------------------------|-------|

| CHAPTER 1                                                                   |       |

| Pentium™ Processor Overview                                                 |       |

| The Pentium™ Family - A Technical Overview                                  | 1-1   |

|                                                                             | 1-1   |

| CHAPTER 2                                                                   |       |

| Pentium™ Processor and Peripherals                                          |       |

| DATASHEETS                                                                  |       |

| Pentium Processor at iCOMP Index 510\60 MHz                                 | 2-1   |

| Pentium Processor at iCOMP Index 567\66 MHz                                 | 2-1   |

| Pentium Processor at iCOMP Index 610\75 MHz                                 | 2-32  |

| Pentium Processor at iCOMP Index 610\75 MHz                                 | 2-80  |

| Pentium Processor at iCOMP Index 735\90 MHz                                 | 2-80  |

| Pentium Processor at iCOMP Index 815\100 MHz                                | 2-80  |

| Future Pentium OverDrive™ Processor for Pentium Processor (510\60, 567\66)- |       |

| Based Systems Socket Specification                                          | 2-143 |

| Pentium Processor Reference Sheet                                           | 2-153 |

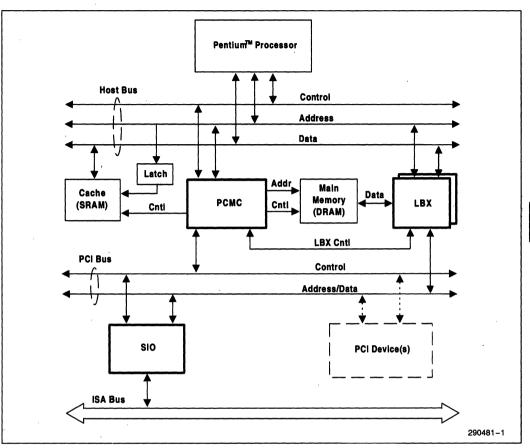

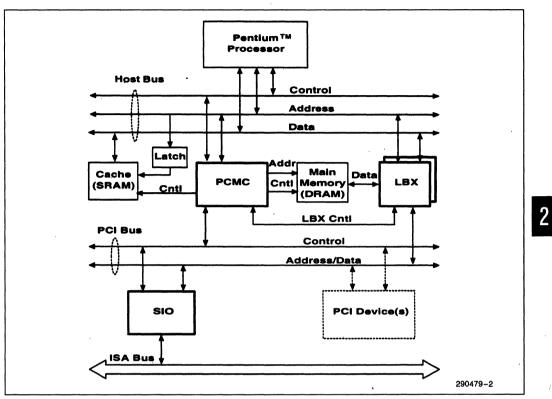

| 82430LX/82430NX PCIset                                                      | 2-154 |

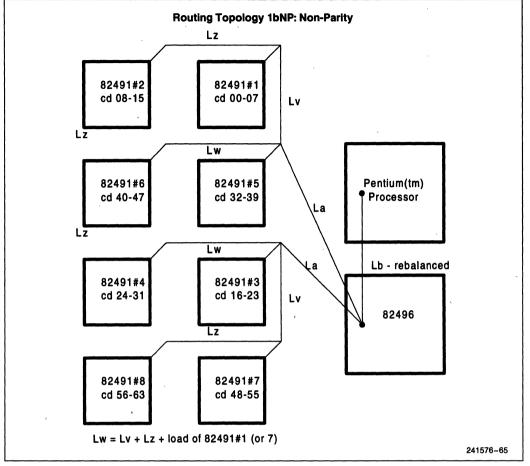

| 82496 Cache Controller and 82491 Cache SRAM for Use with the Pentium        |       |

| Processor                                                                   | 2-157 |

| 82497 Cache Controller and 82492 Cache SRAM                                 | 2-158 |

| 82498 Cache Controller and 82493 Cache SRAM                                 | 2-159 |

| 82433LX/82433NX Local Bus Accelerator (LBX)                                 | 2-160 |

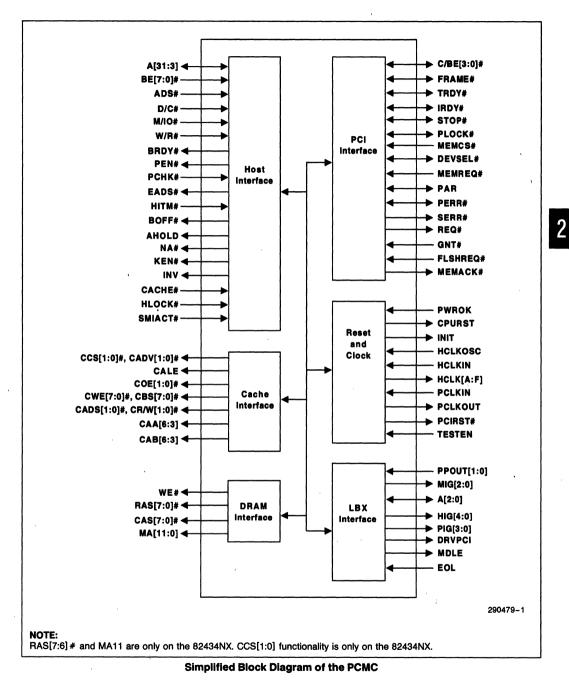

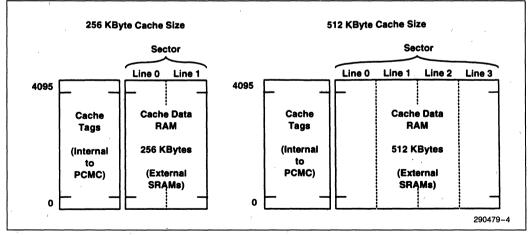

| 82434LX/82434NX PCI, Cache and Memory Controller (PCMC)                     | 2-213 |

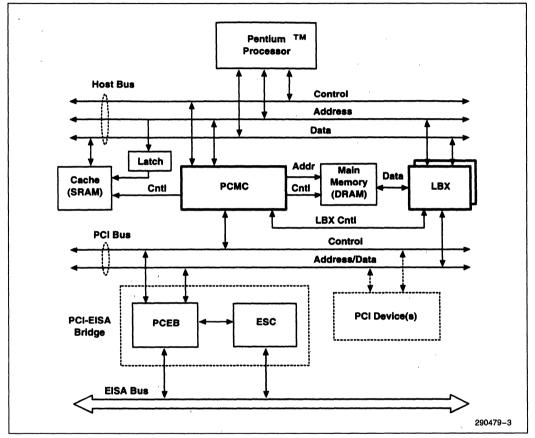

| 82420/82430 PCIset Bridge Component                                         | 2-404 |

| 82374EB/82374SB EISA System Component (ESC)                                 | 2-406 |

| 82375EB/82375SB PCI-EISA Bridge (PCEB)                                      | 2-409 |

| 82378 System I/O (SIO)                                                      |       |

| 82379AB System I/O-APIC (SIO.A)                                             |       |

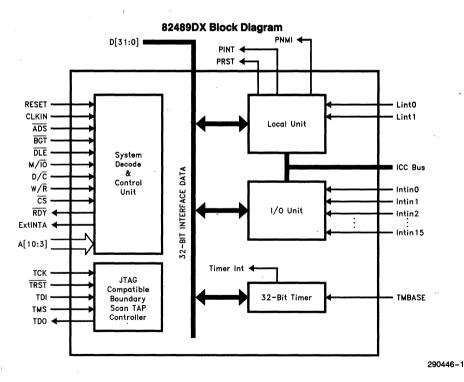

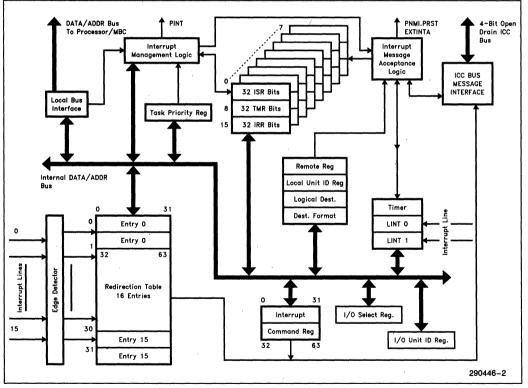

| 82489DX Advanced Programmable Interrupt Controller                          | 2-565 |

| APPLICATION NOTES                                                           |       |

|                                                                             | 2-579 |

| AP-479 Pentium Processor Clock Design                                       | 2-605 |

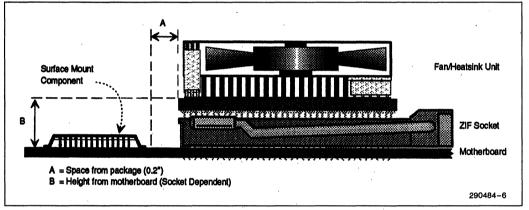

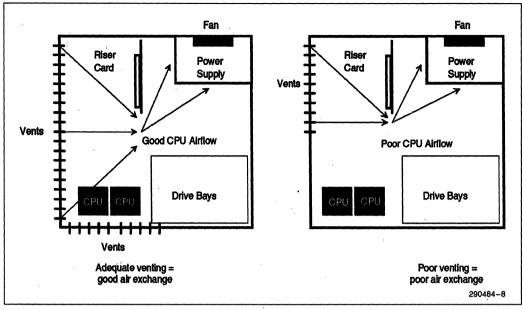

| AP-480 Pentium Processor Thermal Design Guidelines                          | 2-643 |

| AP-481 Design with the Pentium Processor, 82496 Cache Controller, and 82491 |       |

| Cache SRAM CPU-Cache Chipset                                                |       |

| AP-485 Intel Processor Identification with the CPUID Instruction            | 2-816 |

## Alphanumeric Index

| 82374EB/82374SB EISA System Component (ESC)                                       | 2-406 |

|-----------------------------------------------------------------------------------|-------|

| 82375EB/82375SB PCI-EISA Bridge (PCEB)                                            |       |

| 82378 System I/O (SIO)                                                            | 2-411 |

| 82379AB System I/O-APIC (SIO.A)                                                   | 2-563 |

| 82420/82430 PCIset Bridge Component                                               | 2-404 |

| 82430LX/82430NX PCIset                                                            | 2-154 |

| 82433LX/82433NX Local Bus Accelerator (LBX)                                       |       |

| 82434LX/82434NX PCI, Cache and Memory Controller (PCMC)                           | 2-213 |

| 82489DX Advanced Programmable Interrupt Controller                                | 2-565 |

| 82496 Cache Controller and 82491 Cache SRAM for Use with the Pentium™ Processor   |       |

| 82497 Cache Controller and 82492 Cache SRAM                                       | 2-158 |

| 82498 Cache Controller and 82493 Cache SRAM                                       | 2-159 |

| AP-388 82489DX User's Manual                                                      | 2-579 |

| AP-479 Pentium Processor Clock Design                                             | 2-605 |

| AP-480 Pentium Processor Thermal Design Guidelines                                | 2-643 |

| AP-481 Design with the Pentium Processor, 82496 Cache Controller, and 82491 Cache | 2 040 |

| SRAM CPU-Cache Chipset                                                            | 2-670 |

| AP-485 Intel Processor Identification with the CPUID Instruction                  | 2-816 |

| Future Pentium OverDrive™ Processor for Pentium Processor (510\60, 567\66)-Based  | 2010  |

| Systems Socket Specification                                                      | 2-143 |

| Pentium Processor at iCOMP Index 510\60 MHz                                       | 2-1   |

| Pentium Processor at iCOMP Index 567\66 MHz                                       | 2-1   |

| Pentium Processor at iCOMP Index 610 \75 MHz                                      | 2-32  |

| Pentium Processor at iCOMP Index 610\75 MHz                                       | 2-80  |

| Pentium Processor at iCOMP Index 010 (73 Milz                                     | 2-80  |

| Pentium Processor at iCOMP Index 735\30 MHz                                       | 2-80  |

| Pentium Processor Reference Sheet                                                 |       |

| The Pentium Family - A Technical Overview                                         | 2-155 |

|                                                                                   | 1-1   |

## Pentium<sup>™</sup> Processor Overview

# THE Pentium<sup>TM</sup> FAMILY—A TECHNICAL OVERVIEW

Intel's new Pentium processor combines the performance traditionally associated with minicomputers and workstations with the flexibility and compatibility that characterize the personal computer platform. Designed to meet the needs of today's and tomorrow's sophisticated software applications, the Pentium processor extends the range of Intel's microprocessor architecture to new heights, blurring previous distinctions between hardware platforms and creating an entirely new realm of possibilities for notebook computers, desktop PCs, and servers.

This paper begins by presenting an overview of the Pentium processor. Afterwards, it details the key technological features that enable this Intel solution to meet the market's evolving requirements for high performance, continued software compatibility, and advanced functionality.

### THE WORLD'S BEST PERFORMANCE FOR ALL PC SOFTWARE

The Pentium processor family includes the highest performing members of Intel's family of microprocessors-the Pentium processor at iCOMPTM index 510\60 MHz, Pentium processor at iCOMP index 567\66 MHz. Pentium processor at iCOMP index 610\75 MHz, Pentium processor at iCOMP index 735\90 MHz, and Pentium processor at iCOMP index 815\100 MHz. While incorporating new features and improvements made possible by advances in semiconductor technology, the Pentium processor is fully software compatible with previous members of the Intel microprocessor family-thereby preserving the value of users' software investments which are worth billions of dollars. The Pentium processor meets the demands of computing in a number of areas: advanced operating systems, such as Windows 4.0\*, UNIX\*, Windows-NT\*, OS/2\*, Solaris\* and NEXTstep\*; compute-intensive graphics applications such as 3-D modeling, computer-aided design/engineering (CAD/CAE), largescale financial analysis, high-throughput client/server, handwriting, and voice recognition; network applications; virtual reality; electronic mail that combines many of the above areas; and new applications yet to be developed.

The Pentium processor family was designed using an advanced process technology and has features that are less than a micron (one-millionth of a meter) in size. The Pentium processor ( $510\60$ ,  $567\66$ ) was developed utilizing 5V, 0.8 micron technology with 3.1 million transistors, while the Pentium processor ( $610\75$ ,  $735\90$ ,  $815\100$ ) was designed using 3.3V, 0.6 micron technology with 3.3 million transistors.

### THE PENTIUM PROCESSOR: TECHNICAL INNOVATIONS

A number of innovative product features contribute to the Pentium processor's unique combination of high performance, compatibility, data integrity and upgradability. These include:

- Superscalar architecture

- Separate code and data caches

- Branch prediction

- High-performance floating-point unit

- Enhanced 64-bit data bus

- Data integrity features

- SL technology power management features

- Multiprocessing support

- Performance monitoring

- Memory page size feature

- Intel OverDrive<sup>TM</sup> processor upgradability

### Superscalar Architecture

The Pentium processor's superscalar architecture enables the processor to achieve new levels of performance by executing more than one instruction per clock cycle. The term "superscalar" refers to a microprocessor architecture that contains more than one execution unit. These execution units—or pipelines—are where the chip processes the data and instructions that are fed to it by the rest of the system.

December 1994 Order Number: 242423-001 The Pentium processor's superscalar implementation represents a natural progression from previous generations of processors in the 32-bit Intel architecture. The Intel486TM processor, for example, is able to execute many of its instructions in one clock cycle, while previous generations of Intel microprocessors require multiple clock cycles to execute a single instruction.

This ability to execute multiple instructions per clock cycle is due to the fact that the Pentium processor's two pipelines can execute two instructions simultaneously. As with the Intel486 processor's single pipeline, the Pentium processor's dual pipelines execute integer instructions in five stages: *prefetch*, decode 1, decode 2, execute and writeback. This permits several instructions to be in various stages of execution, thus increasing processing performance.

The Pentium processor also uses hardwired instructions to replace many of the microcoded instructions used in previous microprocessor generations. Hardwired instructions are simple and commonly used, and can be executed by the processor's hardware without requiring microcode. This improves performance without affecting compatibility. In the case of more complex instructions, the Pentium processor's enhanced microcode further boosts performance by employing both dual integer pipelines to execute instructions.

### Separate Code and Data Caches

Another significant advancement is the Pentium processor's innovative on-chip cache implementation. Onchip caches increase performance by acting as temporary storage places for commonly-used instructions and data, replacing the need to go off-chip to the system's main memory to fetch information. The Intel486 microprocessor, for example, contains a single 8-Kbyte on-chip cache to handle both code and data caching functions. Intel Pentium Processor designers improved on this implementation by creating separate on-chip code and data caches. This increases performance because bus conflicts are reduced (with a single cache, conflicts can occur between instruction pre-fetches and data accesses) and the caches are available more often when they are needed.

The Pentium processor's code and data caches each contain 8 Kbytes of information, and both are organized as two-way set associative caches—meaning that they save time by searching only pre-specified 32-byte segments rather than the entire cache. This performance-enhancing feature is in turn supplemented by the Pentium processor's 64-bit data bus, which ensures that the dual caches and superscalar execution pipelines are continually supplied with data.

The Pentium processor's data cache uses two other important techniques: "writeback" caching and an algorithm called the MESI (Modified, Exclusive, Shared, Invalid) protocol. The writeback method transfers data to the cache without going out to main memory (data is written to main memory only when it is removed from the cache). In contrast, previous-generation "writethrough" cache implementations transfer data to the external memory each time the processor writes data to the cache. The writeback technique increases performance by reducing bus utilization and preventing needless bottlenecks in the system.

To ensure that data in the cache and in main memory are consistent, the data cache implements the MESI protocol. By obeying the rules of the protocol during reads/writes, the Pentium processor can maintain cache consistency and circumvent problems that might be caused by multiple processors using the same data.

### **Branch Prediction**

Branch prediction is an advanced computing technique that boosts performance by keeping the execution pipelines full. This is accomplished by predetermining the most likely set of instructions to be executed. The Pentium processor is the first PC-compatible microprocessor to use branch prediction, which until now has traditionally been associated with the mainframe computers.

For a better understanding of this concept, consider a typical application program. After each pass through a software loop, the program performs a conditional test to determine whether to return to the beginning of the loop or to exit and continue on to the next execution step. These two choices, or paths, are called branches. Branch prediction forecasts which branch the software will require, based on the assumption that the previous branch that was taken will be used again. The Pentium processor makes branch predictions using a Branch Target Buffer (BTB). This software-transparent innovation eliminates the need for recompiling code, thus increasing overall speed and application software performance.

To efficiently predict branches, the Pentium processor uses two prefetch buffers. One buffer prefetches code in a linear fashion (for the next execution step) while the other prefetches instructions based on addresses in the

# intəl.

Branch Target Buffer (to jump to the beginning of the loop). As a result, the needed code is always prefetched before it is required for execution.

The Pentium processor's prediction algorithm can not only forecast simple branch choices, but also support more complex branch prediction—for example, within nested loops. This is accomplished by storing multiple branch addresses in the Branch Prediction Buffer. The BTB's design allows 256 addresses to be recorded, and thus the prediction algorithm can forecast up to 256 branches.

### **High-Performance Floating-Point Unit**

The emerging wave of 32-bit compute-intensive software applications require a high degree of floatingpoint processing power to handle mathematical calculations. As the floating-point requirements of personal computer software have steadily increased, advances in microprocessor technology have been introduced to satisfy these needs. The Intel486 DX processor, for example, was the first Intel microprocessor to integrate math coprocessing functions on-chip; previous-generation Intel processors used off-chip math coprocessors when floating-point calculations were required.

The Pentium processor family takes math computational ability to the next performance level by using an enhanced on-chip floating-point unit that incorporates sophisticated eight-stage pipelining and hardwired functions. A three-stage floating-point instruction pipeline is appended to the integer pipelines. Most floatingpoint instructions begin execution in one of the integer pipelines, then move on to the floating-point pipeline. In addition, common floating-point functions—such as add, multiply and divide—are hardwired for faster execution.

As a result of these innovations, the Pentium processor (815\100) executes floating-point instructions five to ten times faster than the 33-MHz Intel486 DX processor, optimizing it for the high-speed numeric calculations inherent in advanced visual applications such as CAD and 3D graphics.

### **Enhanced 64-Bit Data Bus**

The data bus is the highway that carries information between the processor and the memory subsystem. Because of its external 64-bit data bus, the Pentium processor can transfer data to and from memory at rates up to 528 Mbytes/second, a more than five-fold increase over the peak transfer rate of the 66-MHz Intel486 DX2 microprocessor (105 Mbytes/second). This wider data bus facilitates high-speed processing by maintaining the flow of instructions and data to the processor's superscalar execution unit. As a result, the Pentium processor's (815\100) overall performance is over two and one-half times that of the Intel486 DX2-66 microprocessor.

In addition to having a wider data bus, the Pentium processor implements bus cycle pipelining to increase bus bandwidth. Bus cycle pipelining allows a second cycle to start before the first one is completed. This gives the memory subsystem more time to decode the address, which allows slower and less-expensive memory components to be used—resulting in a lower overall system cost. Burst reads and writes, parity on address and data, and a simple cycle identification all contribute to providing better bandwidth and improved system reliability.

The Pentium processor also has two write buffers, one corresponding to each pipeline, to enhance the performance of consecutive writes to memory. Write buffers improve performance by allowing the processor to proceed with the next pair of instructions, even though one of the current instructions needs to write to memory while the bus is busy.

### **Data Integrity Features**

Protecting important data and ensuring its integrity has become increasingly important as mission-critical applications continue to proliferate. To ensure the Pentium processor's reliability, Intel ran millions of simulations and tests. In addition, designers integrated two advanced features traditionally associated with mainframe-class designs—internal error detection and functional redundancy testing—to help preserve data integrity in today's evolving PC-based networks.

Internal error detection places parity bits on the internal code and data caches, translation look aside buffers, microcode, and branch target buffer. This feature helps detect errors in a manner that remains transparent to both the user and the system.

For situations where data integrity is especially crucial, the Pentium processor supports Functional Redundancy Checking (FRC). FRC requires the use of two Pentium chips, one acting as the master and the other as the "checker". The two chips run in tandem, and the checker compares its output with that of the master Pentium processor to assure that errors have not occurred. If a discrepancy is discovered, the system is notified.

### SL Enhanced Power Management Features

The Pentium processors (610\75, 735\90, 815\100) incorporate new SL technology features for superior power-management capabilities. These features operate at two levels: the microprocessor and the system. Power management at the processor level involves putting the processor into low power state during non-processor intensive tasks (such as word processing), or into a very low-power state when the computer is not in use ("sleep" mode). At the system level, Intel's SL technology uses system management mode (SMM) to control the way power is used by the computer (including peripherals). This mode provides intelligent system management that allow the microprocessor to slow down, suspend, or completely shut down various system components so as to maximize energy savings. All members of the Pentium processor family include SMM.

### **Multiprocessor Support**

The Pentium processor is ideal for the increasing wave of multiprocessing systems. Multiprocessing applications that combine two or more Pentium processors are well served by the chip's advanced architecture, separate on-chip code and data caches, chip sets for controlling external caches, and sophisticated data integrity features.

As previously discussed, the Pentium processor family uses the MESI protocol to maintain cache consistency among several processors. The Pentium processor also ensures that instructions are seen by the system in the order that they were programmed. This strong ordering helps software designed to run on a single-processor system to work correctly in a multiprocessing environment.

The Pentium processors  $(610\75, 735\90, 815\100)$  also include two new multiprocessor (MP) features: a multiprocessor interrupt controller on-chip and the dual processor mode. The processor's on-chip MP interrupt controller can support up to 60 processors. The dual processor mode enables two processors to share a single second-level cache, allowing the development of low-cost shared-cache multiprocessor systems for workstations and low-end servers.

### **Performance Monitoring**

Performance monitoring is a feature of the Pentium processor that enables system designers and application developers to optimize their hardware and software products by identifying potential code bottlenecks. Designers can observe and count clocks for internal processor events that affect the performance of data reads and writes, cache hits and misses, interrupts, and bus utilization. This allows them to measure the effect that their code has on both the Pentium processor architecture and their product, and to fine-tune their application or system for optimal performance. The benefit to end users is better value and higher performance, due to the greater synergy between the Pentium processor, its host system, and application software.

### Memory Page Size Feature

The Pentium processor offers the option of supporting either the traditional memory page size of 4 Kbytes, or a larger 4-Mbyte page. This feature—which is transparent to the application software—was provided to reduce the frequency of page swapping in complex graphics applications, frame buffers, and operating system kernels, where the increased page size allows users to map large, previously unwieldy objects. The larger page enables an increased page hit rate, which results in higher performance.

### Upgradability

As with all new implementations of the Intel 32-bit microprocessor architecture, the Pentium processor has been designed for easy upgradability using Intel's upgrade technology. This innovation protects user investments by adding performance that helps to maintain the productivity levels of Intel processor-based systems over their entire lifespans.

Upgrade technology makes it possible for users to take advantage of more advanced processor technology in their existing systems with an easy-to-install, singlechip performance upgrade. For example, Intel's first upgrade options, the OverDrive processors developed for Intel486 SX and Intel486 DX processors, apply the same speed-doubling technology used in the development of the Intel486 DX2 microprocessor.

Intel's upgrade processors will also be available for systems based on the Pentium processor family, ensuring an easy future upgrade path based on even more advanced processor technology. In addition, Pentium processor technology will be the basis of the upgrade processors now being developed for Intel486 processorbased systems.

## INCREASED PERFORMANCE: BY THE NUMBERS

The Pentium processor stands alone on the performance ladder when compared to all other PC-compatible microprocessors, raising the standard for the Intel 32bit architecture. While there are many ways to measure performance, three different examples are offered here to demonstrate the Pentium processor's speed and processing power: Intel's iCOMP index, the SPECint92 UNIX benchmark, and the SPECfp92 UNIX benchmark.

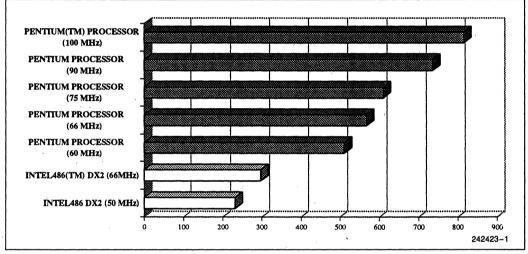

One indication of the Pentium processor's high performance is provided by Intel's iCOMP (Intel Comparative Microprocessor Performance) index. The iCOMP index, which measures the performance of the members of the Intel 32-bit architecture, was created so that computer users can more easily identify relative performance differences among Intel's microprocessors. The index is based on four distinct aspects of processor performance: integer, floating-point, graphics and video performance. Each of the four elements is considered for both 16- and 32-bit software, and is weighted relative to the estimated percentage of time it occupies the processor's attention (based on a mix of today's commonly used application software). As shown in Figure the Pentium processor at iCOMP index 1. 815\100 MHz has more than 2.7 times the relative performance of the 66-MHz Intel486 DX2 microprocessor, which has an iCOMP rating of 297.

Figure 1. iCOMP™ Index Ratings for Intel Processors

### THE Pentium™ FAMILY—A TECHNICAL OVERVIEW

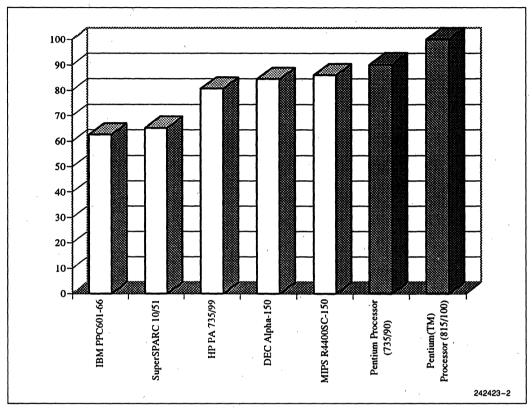

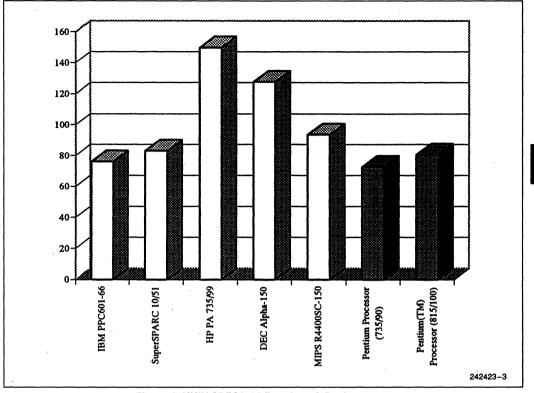

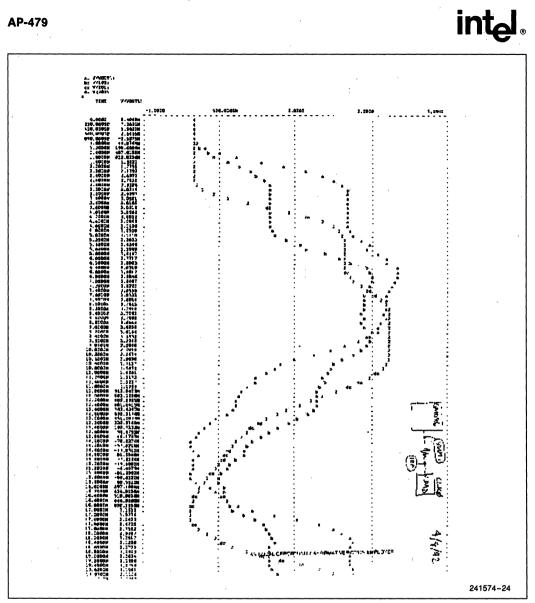

SPECint92 is a processor-intensive UNIX benchmark (Figure 2) that evaluates desktop performance using a representative mix of application instructions. With a SPECint92 rating of 100.0, the Pentium processor at iCOMP index 815\100 MHz outperforms many workstation-class, RISC-based processors, including members of the IBM, MIPS and Sun SPARC processor families. The SPECfp92 UNIX benchmark (Figure 3) is a useful measure of floating-point performance. The SPECfp92 rating for the Pentium processor at iCOMP index 815\100 MHz is 80.6. This is comparable to that of today's RISC architectures, and is more than 4.3 times that of the 66-MHz Intel486 DX2 processor.

#### Figure 2. UNIX SPECint92 Benchmark Performance

Figure 3. UNIX SPECfp92 Benchmark Performance

### HIGH PERFORMANCE WHILE MAINTAINING COMPATIBILITY

The Pentium processor family provides extremely highperformance because it incorporates the latest state-ofthe-art design principles. With its superscalar architecture, separate code and data caches, branch prediction, and an enhanced floating-point unit, the Pentium processor can meet the performance needs of today's—and tomorrow's—applications software. Meanwhile, it maintains complete compatibility with the \$50 billion installed base of software currently running on members of the Intel family. The Pentium processor's combination of performance and compatibility uniquely positions it to meet the needs of the emerging wave of notebook, desktop, and server applications. Not only will users experience dramatic performance improvements while running their current software, but they can also anticipate that new applications will take even further advantage of the Pentium processor's high-performance features.

. , , ,

## Pentium<sup>™</sup> Processor and Peripherals

• · · · · · •

### int PENTIUM™ PROCESSOR AT ICOMP INDEX 510\60 MHz PENTIUM™ PROCESSOR AT ICOMP INDEX 567\66 MHz

Binary Compatible with Large Software Base

- DOS, OS/2, UNIX, and WINDOWS

- 32-Bit Microprocessor - 32-Bit Addressing

- 64-Bit Data Bus

- Superscalar Architecture - Two Pipelined Integer Units

- Capable of under One Clock per Instruction

- Pipelined Floating Point Unit

- Separate Code and Data Caches

- 8K Code, 8K Write Back Data

- 2-Way 32-Byte Line Size

- Software Transparent

- MESI Cache Consistency Protocol

- Advanced Design Features - Branch Prediction - Virtual Mode Extensions

- 273-Pin Grld Array Package

- BiCMOS Silicon Technology

- Increased Page Size - 4M for Increased TLB Hit Rate

- Multi-Processor Support - Multiprocessor Instructions - Support for Second Level Cache

- Internal Error Detection - Functional Redundancy Checking - Built in Self Test

- Parity Testing and Checking

- IEEE 1149.1 Boundary Scan Compatibility

- Performance Monitoring

- Counts Occurrence of Internal **Events**

- Traces Execution through Pipelines

The Pentium processor (510\60, 567\66) provides the next generation of power for high-end workstations and servers. The Pentium processor (510\60, 567\66) is compatible with the entire installed base of applications for DOS. Windows, OS/2, and UNIX. The Pentium processor's superscalar architecture can execute two instructions per clock cvcle. Branch Prediction and separate caches also increase performance. The pipelined floating point unit of the Pentium processor (510\60, 567\66) delivers workstation level performance. Separate code and data caches reduce cache conflicts while remaining software transparent. The Pentium processor (510\60, 567\66) has 3.1 million transistors and is built on Intel's 0.8 Micron BiCMOS silicon technology.

MS-DOS and Windows are registered trademarks of Microsoft Corporation. OS/2 is a trademark of International Business Machines Corporation. UNIX is a registered trademark of UNIX System Laboratories, Inc.

241595-1

November 1994 Order Number: 241595-002

## Pentium<sup>™</sup> Processor (510\60, 567\66)

| CONTENTS                                            | PAGE |

|-----------------------------------------------------|------|

| 1.0 MICROPROCESSOR<br>ARCHITECTURE OVERVIEW         |      |

| 2.0 PINOUT                                          | 2-6  |

| 2.1 Pinout and Pin Descriptions                     |      |

| 2.1.1 Pentium™ Processor<br>(510\60, 567\66) Pinout | 2-6  |

| 2.2 Design Notes                                    | 2-9  |

| 2.3 Quick Pin Reference                             | 2-9  |

| 2.4 Pin Reference Tables                            | 2-16 |

| 2.5 Pin Grouping According to<br>Function           | 2-18 |

| 2.6 Output Pin Grouping Accordin<br>when Driven     |      |

|     | 1    |    |

|-----|------|----|

| CON | ITEN | TS |

| PAG |

|-----|

|-----|

| 3.0 ELECTRICAL SPECIFICATIONS  | 2-18 |

|--------------------------------|------|

| 3.1 Power and Ground           | 2-18 |

| 3.2 Decoupling Recommendations | 2-19 |

| 3.3 Connection Specifications  | 2-19 |

| 3.4 Maximum Ratings            | 2-19 |

| 3.5 D.C. Specifications        | 2-20 |

| 3.6 A.C. Specifications        | 2-20 |

| 4.0 MECHANICAL SPECIFICATIONS  | 2-29 |

| 5.0 THERMAL SPECIFICATIONS     | 2-31 |

### PENTIUM™ PROCESSOR (510\60, 567\66)

# intel

### 1.0 MICROPROCESSOR ARCHITECTURE OVERVIEW

The Pentium<sup>™</sup> processor (510\60, 567\66) is the next generation member of the Intel386<sup>™</sup> and Intel486<sup>™</sup> microprocessor family. It is 100% binary compatible with the 8086/88, 80286, Intel386 DX CPU, Intel386 SX CPU, Intel486 DX CPU, Intel486 SX and the Intel486 DX2 CPUs.

The Pentium processor (510\60, 567\66) contains all of the features of the Intel486 CPU, and provides significant enhancements and additions including the following:

- Superscalar Architecture

- Dynamic Branch Prediction

- Pipelined Floating-Point Unit

- Improved Instruction Execution Time

- Separate 8K Code and Data Caches

- Writeback MESI Protocol in the Data Cache

- 64-Bit Data Bus

- Bus Cycle Pipelining

- Address Parity

- Internal Parity Checking

- Functional Redundancy Checking

- Execution Tracing

- Performance Monitoring

- IEEE 1149.1 Boundary Scan

- System Management Mode

- Virtual Mode Extensions

The application instruction set of the Pentium processor (510\60, 567\66) includes the complete Intel486 CPU instruction set with extensions to accommodate some of the additional functionality of the Pentium processor (510\60, 567\66). All application software written for the Intel386 and Intel486 microprocessors will run on the Pentium processor (510\60, 567\66) without modification. The on-chip memory management unit (MMU) is completely compatible with the Intel386 and Intel486 CPUs.

The Pentium processor (510\60, 567\66) implements several enhancements to increase performance. The two instruction pipelines and floatingpoint unit on the Pentium processor (510\60, 567/66) are capable of independent operation. Each pipeline issues frequently used instructions in a single clock. Together, the dual pipes can issue two integer instructions in one clock, or one floating point instruction (under certain circumstances, 2 floating point instructions) in one clock. Branch prediction is implemented in the Pentium processor (510\60, 567\66). To support this, the Pentium processor (510\60, 567\66) implements two prefetch buffers, one to prefetch code in a linear fashion, and one that prefetches code according to the BTB so the needed code is almost always prefetched before it is needed for execution.

The floating-point unit has been completely redesigned over the Intel486 CPU. Faster algorithms provide up to 10X speed-up for common operations including add, multiply, and load.

The Pentium processor (510\60, 567\66) includes separate code and data caches integrated on chip to meet its performance goals. Each cache is 8 Kbytes in size, with a 32-byte line size and is 2-way set associative. Each cache has a dedicated Translation Lookaside Buffer (TLB) to translate linear addresses to physical addresses. The data cache is configurable to be writeback or writethrough on a line by line basis and follows the MESI protocol. The data cache tags are triple ported to support two data transfers and an inquire cycle in the same clock. The code cache is an inherently write protected cache. The code cache tags are also triple ported to support snooping and split line accesses. Individual pages can be configured as cacheable or noncacheable by software or hardware. The caches can be enabled or disabled by software or hardware.

The Pentium processor (510\60, 567\66) has increased the data bus to 64-bits to improve the data transfer rate. Burst read and burst writeback cycles are supported by the Pentium processor (510\60, 567\66). In addition, bus cycle pipelining has been added to allow two bus cycles to be in progress simultaneously. The Pentium processor (510\60, 567\66) Memory Management Unit contains optional extensions to the architecture which allow 4 Mbyte page sizes.

The Pentium processor (510\60, 567\66) has added significant data integrity and error detection capability. Data parity checking is still supported on a byte by byte basis. Address parity checking, and internal parity checking features have been added along with a new exception, the machine check exception. In addition, the Pentium processor (510\60, 567\66) has implemented functional redundancy checking to provide maximum error detection of the processor and the interface to the processor. When functional redundancy checking is used, a second processor, the "checker" is used to execute in lock step with the "master" processor. The checker samples the master's outputs and compares those values with the values it computes internally, and asserts an error signal if a mismatch occurs.

Preliminary

As more and more functions are integrated on chip, the complexity of board level testing is increased. To address this, the Pentium processor (510\60, 567\66) has increased test and debug capability. Like many of the Intel486 CPUs, the Pentium processor (510\60, 567\66) implements IEEE Boundary Scan (Standard 1149.1). In addition, the Pentium processor (510\60, 567\66) has specified 4 breakpoint pins that correspond to each of the debug registers and externally indicate a breakpoint match. Execution tracing provides external indications when an instruction has completed execution in either of the two internal pipelines, or when a branch has been taken. System management mode has been implemented along with some extensions to the SMM architecture. Enhancements to the Virtual 8086 mode have been made to increase performance by reducing the number of times it is necessary to trap to a virtual 8086 monitor.

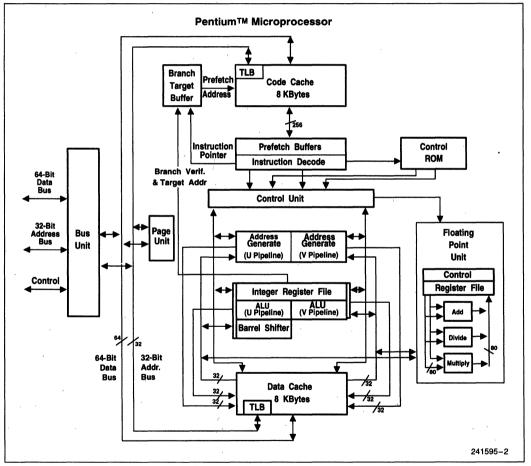

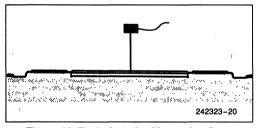

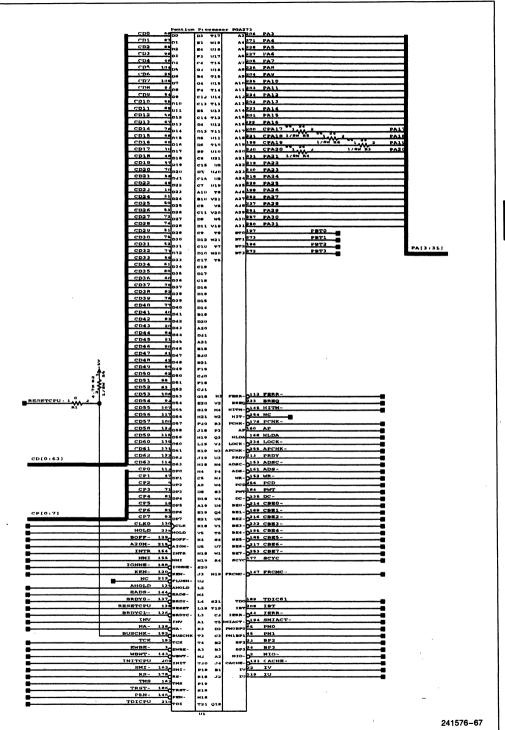

Figure 1-1 shows a block diagram of the Pentium processor (510\60, 567\66).

The block diagram shows the two instruction pipelines, the "u" pipe and the "v" pipe. The u-pipe can execute all integer and floating point instructions. The v-pipe can execute simple integer instructions and the FXCH floating point instructions.

Figure 1-1. Pentium™ Processor (510\60, 567\66) Block Diagram

The separate caches are shown, the code cache and data cache. The data cache has two ports, one for each of the two pipes (the tags are triple ported to allow simultaneous inquire cycles). The data cache has a dedicated Translation Lookaside Buffer (TLB) to translate linear addresses to the physical addresses used by the data cache.

The code cache, branch target buffer and prefetch buffers are responsible for getting raw instructions into the execution units of the Pentium processor (510\60, 567\66). Instructions are fetched from the code cache or from the external bus. Branch ad dresses are remembered by the branch target buffer. The code cache TLB translates linear addresses to physical addresses used by the code cache. The decode unit decodes the prefetched instructions so the Pentium processor (510\60, 567\66) can execute the instruction. The control ROM contains the microcode which controls the sequence of operations that must be performed to implement the Pentium processor (510\60, 567\66) architecture. The control ROM unit has direct control over both pipelines.

The Pentium processor (510\60, 567\66) contains a pipelined floating point unit that provides a significant floating point performance advantage over previous generations of the Pentium processor (510\60, 567\66).

The architectural features introduced in this chapter are more fully described in the *Pentium™ Processor* (510\60, 567\66) User's Manual.

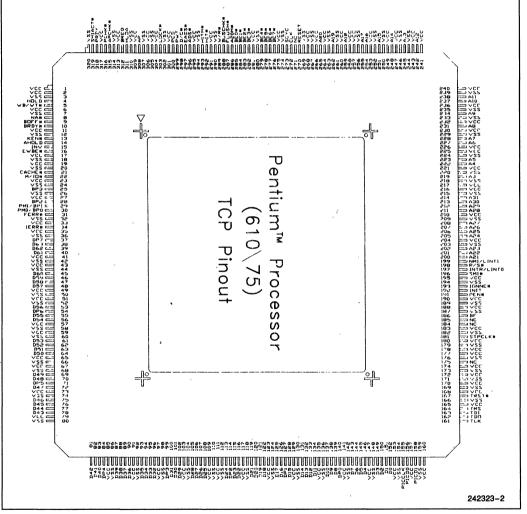

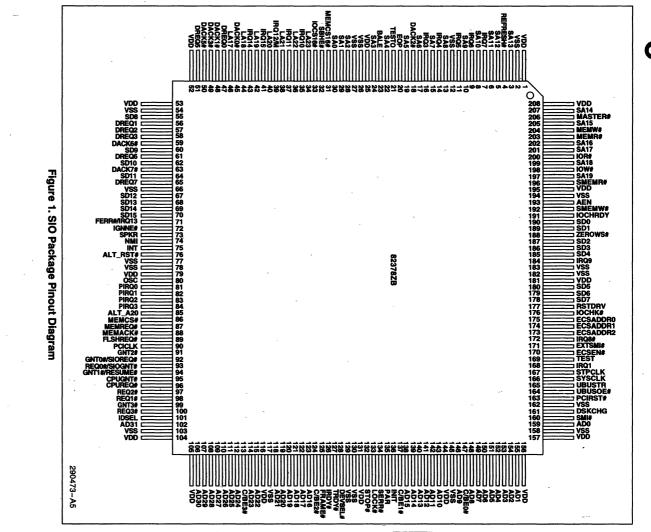

### 2.0 PINOUT

### 2.1 Pinout and Pin Descriptions

|   |          | -           | -              | •             | -        | -         | •        | -        | -        |          | ••             |          |            | ••               |           |           |          |               |                        |                  |                 |   |

|---|----------|-------------|----------------|---------------|----------|-----------|----------|----------|----------|----------|----------------|----------|------------|------------------|-----------|-----------|----------|---------------|------------------------|------------------|-----------------|---|

|   | 1        | 2           | 3              | 4             | 5        | 6         | 7        | 8        | 9        | 10       | 11             | 12       | 13         | 14               | 15        | 16        | 17       | 18            | 19                     | 20               | 21              | 1 |

| N | BE7#     | HIT#        |                | O<br>PCD      | 0<br>A30 |           | O<br>Vcc | O<br>Vcc | O<br>Vcc | O<br>Vcc | O<br>Vcc       | O<br>Vcc |            | O<br>Vcc         | O<br>Vcc  | O<br>Vcc  | O<br>Vcc | O<br>Vcc      | <b>0</b><br><b>A</b> 4 | O<br>BT3         | O<br>BT1        | w |

| • | BE3#     | BREQ        | LOCK#          | 0<br>D/C#     | HOLD     | A28       | Vss      | Vss      | Vas      | Vas      | Vss            | 0<br>V88 | 0<br>V##   | Vas              | ()<br>Vss | O.<br>Vas | 0<br>Vs# | 0<br>V88      | 0<br>A31               | 0<br>A29         | 0<br>A27        | ľ |

| v | Vcc      | FLUSH       | PRDY           | BEO#          | A20M#    | BE2#      | BE6#     | A24      | A22      | A20      | A18            | A16      | Ă14        | A12              | Ă10       |           |          | 0<br>A5       | A25                    | 0<br>A23         | Ă21             | [ |

|   | Vcc      | Vise<br>O   | BUSČHKA        |               |          | # BE4     |          | BTO      | Ā26      | A19      | Ă17<br>()      | A15      | <b>Ā13</b> | <b>Ă</b> 11<br>O | Â9<br>O   |           | A3       | NC            | <b>івт</b><br>О        | INIT             | ŤDI             | u |

| т | 0        | 0           | 0              | 0             | 0        | 0         | 0        | 0        | 0        | 0        | 0              | 0        | 0          | 0                | 0         | 0         | 0        | <b>irrst#</b> | NČ KO                  | 0                | 0               | т |

| s |          | $\cap$      |                |               |          |           |          |          |          |          |                |          |            |                  |           |           |          | Ò             | 0                      | 0                | 0               | s |

| R | 0        | 0           | PCHK#          | 0             |          |           |          |          |          |          |                |          |            |                  |           |           |          | O<br>R/S#     | ONC                    | O<br>Vas         | O<br>Vcc        | R |

| ۵ | O<br>Vcc | 0           | 0              | O<br>BE1#     |          |           |          |          |          |          |                |          |            |                  |           |           |          |               | O<br>NC                | 0<br>V35         |                 | a |

| P |          | O<br>Vas    | AP             | ADS           |          |           |          |          |          |          |                |          |            |                  |           |           |          | O<br>SMI#     | O<br>TMS               |                  |                 | P |

| N |          | O<br>Vas    | W/R#           | O<br>NC       |          |           |          |          |          |          |                |          |            | ,                |           |           |          |               | O<br>NMI               | 0<br>V85         | O<br>Vcc        | N |

| N | O<br>Vas | WB/WŢ#      | EADS#          | HITM          | •        |           |          |          |          |          |                |          |            |                  |           |           | F        | PEN# F        | RCMC                   | 0<br>F V88       | O<br>Vcc        | м |

| L | -        |             |                | BRDY          | *        |           |          |          |          |          | γ <b>ρ V</b> Ι |          |            |                  |           |           |          | RESET         | 0<br>D60               | Vss              | Vcc             | L |

| ĸ | Vas      | Vas         | NA#            | BOFF          | *        |           |          |          |          | т        | op Vi          | <b></b>  |            |                  |           |           |          |               | 0<br>D61               | Vss              | Vcc             | ĸ |

| J | Vsa      | IU<br>O     | KEN#           |               | *        |           |          |          |          |          |                |          |            |                  | ,         |           |          | D58           | 0<br>D62               | V88              | Vcc             | J |

|   | Vcc      | <b>V</b> 35 | FERR#          |               |          |           |          |          |          |          |                |          |            |                  |           |           |          | D63<br>O      | 0<br>D59               | Vss<br>O         | <b>D56</b>      | н |

| H | Vcc      | Vss<br>O    | <b>D</b> 5     | τα<br>Ο       |          |           |          |          |          |          |                |          |            |                  |           |           |          | <b>D53</b>    |                        | <b>V</b> 88      | Vcc<br>O        |   |

| G | Vcc      | V88<br>()   | D3<br>()<br>D5 | D8<br>0<br>D7 | -        |           |          |          |          |          |                |          |            |                  |           |           |          | D51           | D49<br>()<br>D55       | D57<br>()<br>V85 | Vcc<br>O<br>Vcc | G |

| F |          | 0           |                |               |          |           |          |          |          |          |                |          |            |                  |           |           |          | 0             |                        | D54<br>0<br>D57  | 0               | F |

| E | 0        | Vss         |                |               | 0        | 510       | UZJ      | 5-3      | ULI      | 552      | 520            | 030      | 514        | 540              | 038       | 537       | 690      | 0<br>D46      |                        | 0<br>D54         |                 | E |

| D | O        | 0           |                | 0<br>D13      | 0        | O<br>D16  | 0        | O<br>DP3 |          | 0        | 0<br>D28       | 0        | 0          | O<br>D40         | 0<br>D39  | 0         | 0<br>D35 | O<br>DP4      | 0<br>D38               | 0<br>D42         | 0               | D |

| c |          |             | PM1/BP1        | O<br>D4       | O<br>DP1 | O<br>D18  | O<br>D22 | O<br>D25 | 0<br>D29 | 0<br>D31 | 0              | 0        | O<br>D10   | O<br>D12         | 0<br>D19  | O<br>D21  | 0<br>D33 | 0<br>D36      | 0<br>D34               | 0<br>D50         | O<br>D52        | c |

| в | 0<br>V   | O<br>BP2    | O<br>BP3       | 0<br>D6       |          | ()<br>V35 | 0<br>Vas |          | 0<br>D17 | . D24    |                |          |            |                  |           |           |          |               | 0<br>D41               | 0<br>D47         | 0<br>D48        | в |

| A |          | M/IO#       | EWBE           |               |          |           |          |          | O<br>DP2 | 0<br>D23 | O<br>Vcc       |          | Vcc        |                  |           |           |          | Vcc           | O<br>DP5               | 0<br>D43         | 0<br>D45        | A |

|   |          | 2           | 3              | 4             | 5        |           | 7        |          | -        | 10       | 11             | 12       | 13         | 14               | 15        | 16        | 17       | 18            | 19                     | 20               | 21              |   |

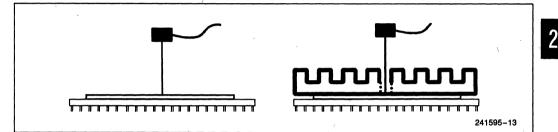

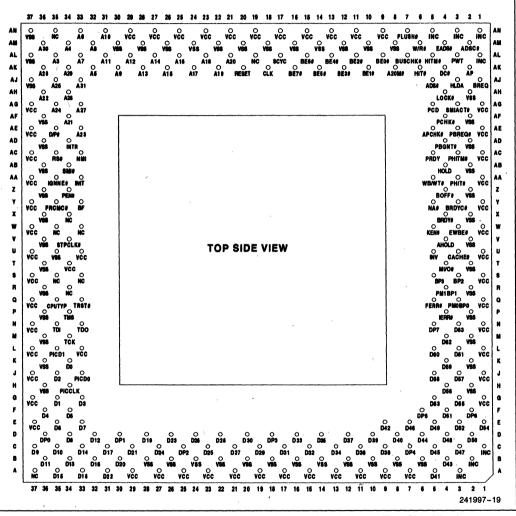

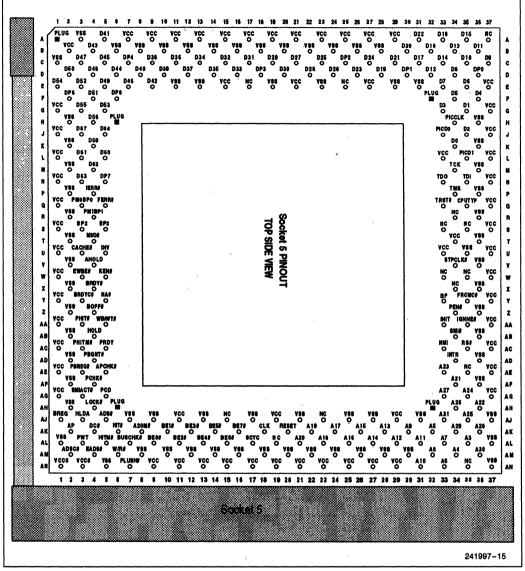

2.1.1 Pentium™ PROCESSOR (510\60, 567\66) PINOUT

Figure 2-1. Pentium™ Processor (510\60, 567\66) Pinout (Top View)

int

int<sub>el</sub>.

٦

2

|        | 21       | 20       | 19           | 18           | 17        | 16         | 15         | 14       | 13       | 12         | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4         | 3               | 2           | 1             |        |

|--------|----------|----------|--------------|--------------|-----------|------------|------------|----------|----------|------------|----------|----------|----------|----------|----------|----------|----------|-----------|-----------------|-------------|---------------|--------|

| A      | 0<br>D45 | 0<br>D43 | O<br>DP5     | O<br>Vcc     | O<br>Vcc  | O<br>Vcc   | O<br>Vcc   | O<br>Vcc | O<br>Vcc | O<br>Vcc   | O<br>Vcc | 0<br>D23 | O<br>DP2 | O<br>Vcc | O<br>Vcc | O<br>Vcc | O<br>Vcc | O<br>Vcc  | ewbe#           | 0<br>M/0#   | ÎNV           | A      |

| в      | 0        | 0<br>D47 | 0<br>D41     | 0<br>Vas     | 0<br>Vas  | 0<br>V##   | 0<br>V##   | O<br>Vas | 0<br>Vas | 0<br>V#8   | 0<br>V## | 0<br>D24 | 0<br>D17 | 0<br>V#8 | 0<br>Vas | 0<br>V== | 0<br>Vas |           | O<br>BP3        | O<br>BP2    | °             | В.     |

| с      | 0<br>D52 | 0<br>D50 | 0<br>D34     | 0<br>D36     | 0<br>D33  | 0<br>D21   | 0<br>D19   | 0<br>D12 | 0<br>D10 | 0          | 0<br>D26 | 0<br>D31 | 0<br>29  | 0<br>025 | 0<br>222 | 0<br>D18 | 0<br>DP1 | O<br>M    | PM1/BP1         | O<br>IERR#  | <b>8</b>      | С      |

| D      | 0<br>044 | 0<br>D42 | 0<br>D38     | O<br>DP4     | 0<br>D35  | 0<br>D37   | 0<br>D39   | 0<br>D40 | 0<br>D14 | 0<br>D30   | )<br>D28 | D32      | 0<br>027 | O<br>DP3 | 0<br>D20 | 0<br>D16 | 0<br>D15 | 0<br>D13  | 00 PN           |             | 0<br>Vec      | D      |

| E      | OP7      | 0<br>D54 | DP6          | 0<br>D46     |           |            |            |          |          |            |          |          |          |          |          |          | 0<br>011 | 02        | O<br>B          | 0<br>V88    | Vcc           | E      |

| F      | Vcc      | 0<br>D57 | 0<br>D49     | 0<br>D51     |           |            |            |          |          |            |          |          |          |          |          |          |          | O<br>De   | 0<br>D3         | O<br>Vas    | 0<br>Vee      | F      |

| G      | Vcc      | Vss      | 0<br>D55     | 0<br>D53     |           |            |            |          |          |            |          |          |          |          |          |          |          | 07        | 0               | O<br>Vas    | 80            | G      |

| н      | 0<br>D56 | VSS      | . O<br>D59   | O<br>D63     |           |            |            |          |          |            |          |          |          |          |          |          |          | DPO       | FERR#           | O<br>Vas    | 80            | н      |

| J      | Vec      | Vss      | 0<br>062     | 0<br>D58     | ľ         |            |            |          |          |            |          |          |          |          |          |          |          | CACHE#    | KEN#            | ON<br>N     | Vas<br>Vas    | J      |

| ĸ      | 0<br>Vcc | Vas      |              | с <b>і</b> к |           |            |            |          |          | Bott       |          | lione    |          |          |          |          |          | BOFF#     | NA#             | O<br>Vas    | 0<br>Vss      | к      |

| L      | Vcc      | Vss      | 000          | RESET        |           |            |            |          |          | BOU        | om       | VIGW     |          |          |          |          |          | BRDY#     | o <b>x</b><br>€ |             |               | L      |

| M      | Vcc      | -        | RCMC         | _            |           |            |            |          |          |            |          |          |          |          |          |          |          | HITM#     | EADS#           | O<br>WB/WT# |               | M      |

| N      | Vcc      | Vas      | NMI          |              |           |            |            |          |          |            |          |          |          |          |          |          |          | O<br>NC   | W/R#            | O<br>Vas    | O<br>Vcc      | N      |

| P      | Vcc      | V55      |              | O<br>SMI#    |           |            |            | ,        |          |            |          |          |          |          |          |          |          | ADS#      |                 | Vas         | 0<br>Vcc      | P      |

| ٩      | Vcc      | V38      | <b>N</b> C ( |              |           |            |            |          |          |            |          |          | ĩ        |          |          |          |          | O<br>BE1# | HLDA            | Vsa<br>Vsa  |               | Q      |

| R      | V        | V35      | NC O         | O<br>R/S#    |           |            |            |          |          |            |          |          |          |          |          |          |          | SCYC      | РСНК#           | O<br>Vas    |               | R      |

| S      |          |          | _            | O<br>TRST#   |           |            |            |          |          |            |          |          |          |          |          |          |          | BESI      |                 | 0<br>V##    | <b>8</b> 0    | S      |

| T<br>U |          |          |              | 0            | <b>A3</b> | <b>0</b>   |            | A        | A13      | A15        | A17      | A19      | A26      | BTO      | BT2      |          |          |           | BUSCHK#         | Vas         | Vec           | т<br>U |

| -      | A21      | A23      | A25          | 0<br>A5      | <b>A5</b> |            | 0<br>A10   | A12      | A14      | 0<br>A16   | A18      | A20      | A22      | A24      | BEG      |          | A20M     |           | -               | FLUSH#      | 0<br>Vec<br>0 | v      |

| v      | A27      | A29      | A31          | 0<br>Vas     | Vas       | Vss<br>Vss | Vss<br>Vss | V38      | Vas      | <b>V55</b> | Vas      | Vas      | Vss      | Vss<br>O | Vas      | A28      | Ю        |           | LOCK#           | BREQ        | BE3#          | w      |

| •      | O<br>BT1 | ВТЗ      | <b>0</b>     | Vcc          | Vœ        | O<br>Vœ    | Vcc        | Vcc      | Vœ       | Vcc        | Vcc      | Vec      | Vcc      | Vcc      | Vcc      | Vcc      | A30      | 0<br>PCD  | арснк#          | HIT#        | BĒ7#          |        |

|        | 21       | 20       | 19           | 18           | 17        | 16         | 15         | 14       | 13       | 12         | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4         | 3               | 2           | 1<br>2415     | 95-4   |

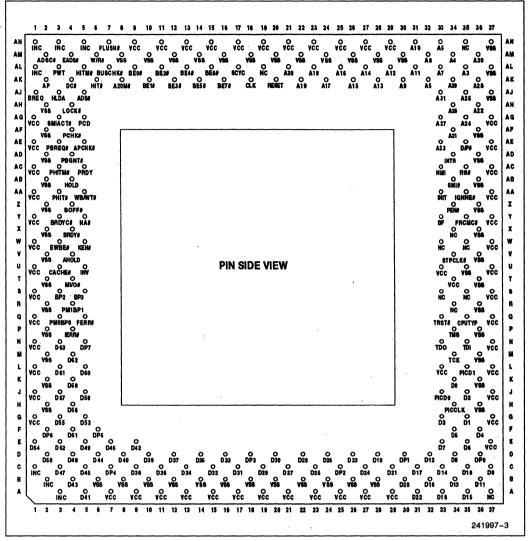

Figure 2-2. Pentium™ Processor (510\60, 567\66) Pinout (Bottom View)

Table 2-1. Pentium™ Processor (510\60, 567\66) Pin Cross Reference Table by Pin Name

| r      | 1        | n™ Processor | <u>.</u> | <b>/</b> \ |        |          |   |        | T        |

|--------|----------|--------------|----------|------------|--------|----------|---|--------|----------|

| Signal | Location | Signal       | Location |            | Signal | Location |   | Signal | Location |

| A3     | T17      | BE2#         | U06      |            | D18    | C06      |   | D54    | E20      |

| A4     | W19      | BE3#         | V01      |            | D19    | C15      |   | D55    | G19      |

| A5     | U18      | BE4#         | T06      |            | D20    | D07      |   | D56    | H21      |

| A6     | U17      | BE5#         | S04      |            | D21    | C16      |   | D57    | F20      |

| A7     | T16      | BE6#         | U07      |            | D22    | C07      |   | D58    | J18      |

| A8     | U16      | BE7#         | W01      |            | D23    | A10      | • | D59    | H19      |

| A9     | T15      | BOFF#        | K04      |            | D24    | B10      |   | D60    | L19      |

| A10    | U15      | BP2          | B02      |            | D25    | C08      |   | D61    | K19      |

| A11    | T14      | BP3          | B03      |            | D26    | C11      |   | D62    | J19      |

| A12    | U14      | BRDY#        | L04      |            | D27    | D09      |   | D63    | H18      |

| A13    | T13      | BREQ         | V02      |            | D28    | D11      |   | D/C#   | V04      |

| A14    | U13      | BT0          | Т08      |            | D29    | C09      |   | DP0    | H04      |

| A15    | T12      | BT1          | W21      |            | D30    | D12      |   | DP1    | C05      |

| A16    | U12      | BT2          | T07      |            | D31    | C10      |   | DP2    | A9       |

| A17    | T11      | BT3          | W20      |            | D32    | D10      |   | DP3    | D08      |

| A18    | U11      | BUSCHK#      | Т03      |            | D33    | C17      |   | DP4    | D18      |

| A19    | T10      | CACHE#       | J04      |            | D34    | C19      |   | DP5    | A19      |

| A20    | U10      | CLK          | K18      |            | D35    | D17      |   | DP6    | E19      |

| A21    | U21      | D0           | D03      |            | D36    | C18      |   | DP7    | E21      |

| A22    | U09      | D1           | E03      |            | D37    | D16      |   | EADS#  | M03      |

| A23    | U20      | D2           | E04      |            | D38    | D19      | l | EWBE#  | A03      |

| A24    | U08      | D3           | F03      |            | D39    | D15      |   | FERR#  | H03      |

| A25    | U19      | D4           | C04      |            | D40    | D14      |   | FLUSH# | U02      |

| A26    | T09      | D5           | G03      |            | D41    | B19      |   | FRCMC# | M19      |

| A27    | V21      | D6           | B04      |            | D42    | D20      | 1 | HIT#   | W02      |

| A28    | V06      | D7           | G04      |            | D43    | A20      |   | HITM#  | M04      |

| A29    | V20      | D8           | F04      |            | D44    | D21      |   | HLDA   | Q03      |

| A30    | W05      | D9           | C12      |            | D45    | A21      | 1 | HOLD   | V05      |

| A31    | V19      | D10          | C13      |            | D46    | E18      |   | IBT    | T19      |

| A20M#  | U05      | D11          | E05      |            | D47    | B20      |   | IERR#  | C02      |

| ADS#   | P04      | D12          | C14      |            | D48    | B21      |   | IGNNE# | S20      |

| AHOLD  | L02      | D13          | D04      |            | D49    | F19      |   | INIT   | T20      |

| AP     | P03      | D14          | D13      |            | D50    | C20      |   | INTR   | N18      |

| APCHK# | W03      | D15          | D05      |            | D51    | F18      | 1 | INV    | A01      |

| BE0#   | U04      | D16          | D06      |            | D52    | C21      |   | IU     | J02      |

| BE1#   | Q04      | D17          | B09      |            | D53    | G18      | 1 | IV     | B01      |

PRELIMINARY

Table 2-1. Pentium™ Processor (510\60, 567\66) Pin Cross Reference Table by Pin Name (Continued)

| Signal  | Location |

|---------|----------|

| KEN#    | J03      |

| LOCK#   | V03      |

| M/IO#   | A02      |

| NA#     | K03      |

| NMI     | N19      |

| PCD     | W04      |

| PCHK#   | R03      |

| PEN#    | M18      |

| PM0/BP0 | D02      |

| PM1/BP1 | C03      |

| PRDY    | U03      |

| PWT     | S03      |

#### Signal Location RESET L18 R/S# **R18** SCYC **R04** SMI# P18 SMIACT# T05 TCK T04 TDI T21 TD0 S21 TMS P19 TRST# S18 WB/WT# M02 W/R# N03

|        |                                                                                                                                                                                                                                                                                                                                 | <br><i>,</i>    |                                                                                                                                                                                                                                                                                      |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal | Location                                                                                                                                                                                                                                                                                                                        | Signal          | Location                                                                                                                                                                                                                                                                             |

| NC     | L03, N04,<br>Q19, R19,<br>S19, T18                                                                                                                                                                                                                                                                                              | V <sub>SS</sub> | B05, B06,<br>B07, B08,<br>B11, B12,                                                                                                                                                                                                                                                  |

| Vcc    | A04, A05,<br>A06, A07,<br>A08, A11,<br>A12, A13,<br>A14, A15,<br>A16, A17,<br>A18, C01,<br>D01, E01,<br>F01, F21,<br>G01, G21,<br>H01, J21<br>K21, L21,<br>K21, L21,<br>N21, P01,<br>P21, Q01,<br>Q18, Q21,<br>R01, R21,<br>S01, T01,<br>U01, W06,<br>W07, W08,<br>W09, W10,<br>W11, W12,<br>W13, W14,<br>W15, W16,<br>W17, W18 |                 | B13, B14,<br>B15, B16,<br>B17, B18,<br>E02, F02,<br>G02, G20,<br>H02, H20,<br>J01, J20,<br>K01, K02,<br>K20, L01,<br>L20, M01,<br>M20, N02,<br>N20, P02,<br>P20, Q02,<br>Q20, R02,<br>R20, S02,<br>T02, V07,<br>V08, V09,<br>V10, V11,<br>V12, V13,<br>V14, V15,<br>V16, V17,<br>V18 |

### 2.2 Design Notes

For reliable operation, always connect unused inputs to an appropriate signal level. Unused active LOW inputs should be connected to  $V_{CC}$ . Unused active HIGH inputs should be connected to GND.

No Connect (NC) pins must remain unconnected. Connection of NC pins may result in component failure or incompatibility with processor steppings.

### NOTE:

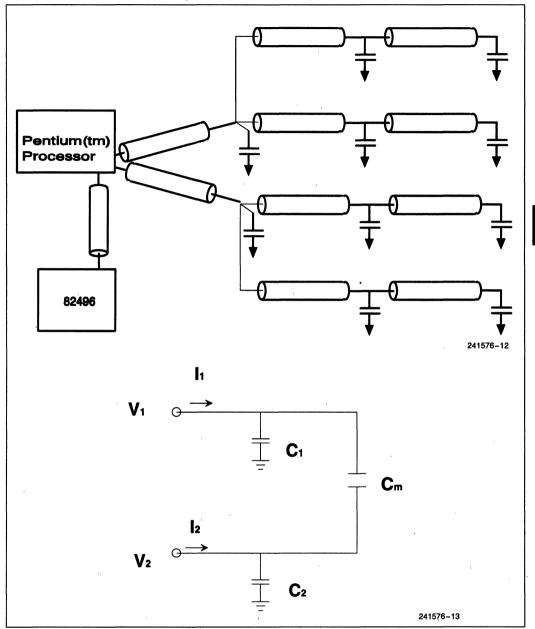

The No Connect pin located at L03 (BRDYC#) along with BUSCHK# are sampled by the Pentium processor (510\60, 567\66) at RESET to configure the I/O buffers of the processor for use with the 82496 Cache Controller/82491 Cache SRAM secondary cache as a chip set (refer to the 82496 Cache Controller/82491 Cache SRAM Data Book for Use with the Pentium<sup>TM</sup> Processor (510\60, 567\66) for further information).

### 2.3 Quick Pin Reference

This section gives a brief functional description of each of the pins. For a detailed description, see the Hardware Interface chapter in the *Pentium*™ *Processor (510\60, 567\66) User's Manual*, Vol. 1. Note that all input pins must meet their AC/DC specifications to guarantee proper functional behavior. In this section, the pins are arranged in alphabetical order. The functional grouping of each pin is listed at the end of this chapter.

The # symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage. When a # symbol is not present after the signal name, the signal is active, or asserted at the high voltage level.

Preliminary

| Symbol                | Type* | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A20M#                 | I     | When the <i>address bit 20 mask</i> pin is asserted, the Pentium™ Processor (510\60, 567\66) emulates the address wraparound at one Mbyte which occurs on the 8086. When A20M# is asserted, the Pentium processor (510\60, 567\66) masks physical address bit 20 (A20) before performing a lookup to the internal caches or driving a memory cycle on the bus. The effect of A20M# is undefined in protected mode. A20M# must be asserted only when the processor is in real mode. |

| A31–A3                | 1/0   | As outputs, the <i>address</i> lines of the processor along with the byte enables define the physical area of memory or I/O accessed. The external system drives the inquire address to the processor on A31–A5.                                                                                                                                                                                                                                                                   |

| ADS#                  | 0     | The <i>address status</i> indicates that a new valid bus cycle is currently being driven by the Pentium processor (510\60, 567\66).                                                                                                                                                                                                                                                                                                                                                |

| AHOLD                 | 1/0   | In response to the assertion of <i>address hold</i> , the Pentium processor (510\60, 567\66) will stop driving the address lines (A31-A3), and AP in the next clock. The rest of the bus will remain active so data can be returned or driven for previously issued bus cycles.                                                                                                                                                                                                    |

| AP                    | I/O · | Address parity is driven by the Pentium processor (510\60, 567\66) with even parity information on all Pentium processor (510\60, 567\66) generated cycles in the same clock that the address is driven. Even parity must be driven back to the Pentium processor (510\60, 567\66) during inquire cycles on this pin in the same clock as EADS # to ensure that the correct parity check status is indicated by the Pentium processor (510\60, 567\66).                            |

| APCHK#                | 0     | The <i>address parity check</i> status pin is asserted two clocks after EADS# is sampled active if the Pentium processor (510\60, 567\66) has detected a parity error on the address bus during inquire cycles. APCHK# will remain active for one clock each time a parity error is detected.                                                                                                                                                                                      |

| BE7#-BE0#             | 0     | The <i>byte enable</i> pins are used to determine which bytes must be written to external memory, or which bytes were requested by the CPU for the current cycle. The byte enables are driven in the same clock as the address lines (A31–3).                                                                                                                                                                                                                                      |

| BOFF #                | 1     | The <i>backoff</i> input is used to abort all outstanding bus cycles that have not yet completed. In response to BOFF #, the Pentium processor ( $510\60$ , $567\66$ ) will float all pins normally floated during bus hold in the next clock. The processor remains in bus hold until BOFF # is negated at which time the Pentium processor ( $510\60$ , $567\66$ ) restarts the aborted bus cycle(s) in their entirety.                                                          |

| BP[3:2]<br>PM/BP[1:0] | 0     | The <i>breakpoint</i> pins (BP3–0) correspond to the debug registers, DR3–DR0.<br>These pins externally indicate a breakpoint match when the debug registers<br>are programmed to test for breakpoint matches.                                                                                                                                                                                                                                                                     |

|                       |       | BP1 and BP0 are multiplexed with the Performance Monitoring pins (PM1 and PM0). The PB1 and PB0 bits in the Debug Mode Control Register determine if the pins are configured as breakpoint or performance monitoring pins. The pins come out of reset configured for performance monitoring.                                                                                                                                                                                       |

| BRDY#                 | I ·   | The <i>burst ready</i> input indicates that the external system has presented valid data on the data pins in response to a read or that the external system has accepted the Pentium processor (510\60, 567\66) data in response to a write request. This signal is sampled in the T2, T12 and T2P bus states.                                                                                                                                                                     |

### Table 2-2. Quick Pin Reference

int<sub>el</sub>.

| Gumbel  | Ture* | I able 2-2. Quick Pin Reference (Continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol  | Type* | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| BREQ    | 0     | The <i>bus request</i> output indicates to the external system that the Pentium processor (510\60, 567\66) has internally generated a bus request. This signal is always driven whether or not the Pentium processor (510\60, 567\66) is driving its bus.                                                                                                                                                                                                                                                                     |

| BT3-BT0 | 0     | The <i>branch trace</i> outputs provide bits 2-0 of the branch target linear address (BT2-BT0) and the default operand size (BT3) during a branch trace message special cycle.                                                                                                                                                                                                                                                                                                                                                |

| BUSCHK# | I     | The <i>bus check</i> input allows the system to signal an unsuccessful completion of a bus cycle. If this pin is sampled active, the Pentium processor (510\60, 567\66) will latch the address and control signals in the machine check registers. If in addition, the MCE bit in CR4 is set, the Pentium processor (510\60, 567\66) will vector to the machine check exception.                                                                                                                                              |

| CACHE#  | 0     | For Pentium processor (510\60, 567\66)-initiated cycles the <i>cache</i> pin indicates internal cacheability of the cycle (if a read), and indicates a burst writeback cycle (if a write). If this pin is driven inactive during a read cycle, Pentium processor (510\60, 567\66) will not cache the returned data, regardless of the state of the KEN# pin. This pin is also used to determine the cycle length (number of transfers in the cycle).                                                                          |

| CLK     | I     | The <i>clock</i> input provides the fundamental timing for the Pentium processor (510\60, 567\66). Its frequency is the internal operating frequency of the Pentium processor (510\60, 567\66) and requires TTL levels. All external timing parameters except TDI, TDO, TMS and TRST# are specified with respect to the rising edge of CLK.                                                                                                                                                                                   |

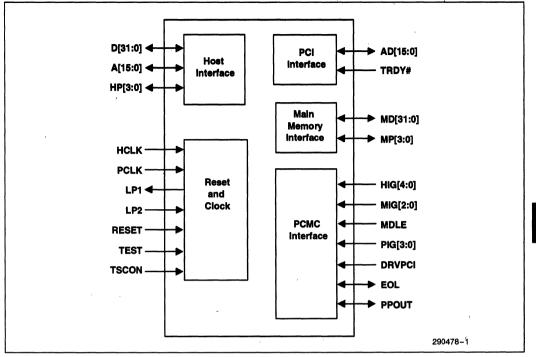

| D/C¥    | 0     | The <i>Data/Code</i> output is one of the primary bus cycle definition pins. It is driven valid in the same clock as the ADS# signal is asserted. D/C# distinguishes between data and code or special cycles.                                                                                                                                                                                                                                                                                                                 |