# Intel® Itanium® Architecture Software Developer's Manual

**Volume 2: System Architecture**

**Revision 2.1**

October 2002

Document Number: 245318-004

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. INTEL PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processors based on the Itanium architecture may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725, or by visiting Intel's website at http://www.intel.com.

Intel, Intel486, Itanium, Pentium, VTune and MMX are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © 2000-2002, Intel Corporation. All rights reserved.

\*Other names and brands may be claimed as the property of others.

### intط

# Contents

#### Part I: System Architecture Guide

| 1 | Abou   | ıt this Manual                                                        | 2:1  |

|---|--------|-----------------------------------------------------------------------|------|

|   | 1.1    | Overview of Volume 1: Application Architecture                        | 2:1  |

|   |        | 1.1.1 Part 1: Application Architecture Guide                          | 2:1  |

|   |        | 1.1.2 Part 2: Optimization Guide for the Intel® Itanium® Architecture | 2:2  |

|   | 1.2    | Overview of Volume 2: System Architecture                             | 2:2  |

|   |        | 1.2.1 Part 1: System Architecture Guide                               | 2:2  |

|   |        | 1.2.2 Part 2: System Programmer's Guide                               | 2:3  |

|   |        | 1.2.3 Appendices                                                      | 2:4  |

|   | 1.3    | Overview of Volume 3: Instruction Set Reference                       | 2:4  |

|   |        | 1.3.1 Part 1: Intel® Itanium® Instruction Set Descriptions            | 2:4  |

|   |        | 1.3.2 Part 2: IA-32 Instruction Set Descriptions                      | 2:4  |

|   | 1.4    | Terminology                                                           | 2:5  |

|   | 1.5    | Related Documents                                                     | 2:5  |

|   | 1.6    | Revision History                                                      | 2:6  |

| 2 | Intel® | ③ Itanium® System Environment                                         | 2:9  |

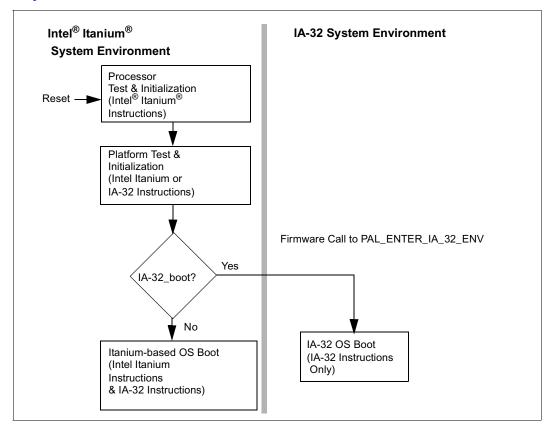

|   | 2.1    | Processor Boot Sequence                                               | 2:9  |

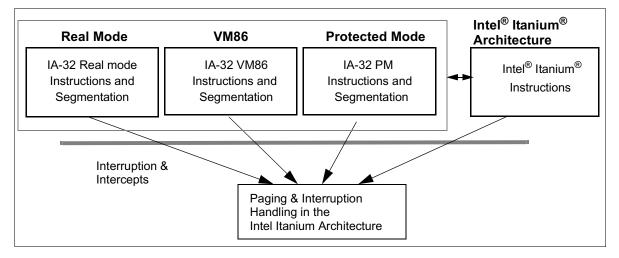

|   | 2.2    | Intel® Itanium® System Environment Overview                           |      |

| 3 | Syste  | em State and Programming Model                                        | 2:13 |

|   | 3.1    | Privilege Levels                                                      | 2:13 |

|   | 3.2    | Serialization                                                         | 2:13 |

|   |        | 3.2.1 Instruction Serialization                                       | 2:14 |

|   |        | 3.2.2 Data Serialization                                              | 2:14 |

|   |        | 3.2.3 Definition of In-flight Resources                               | 2:15 |

|   | 3.3    | System State                                                          | 2:15 |

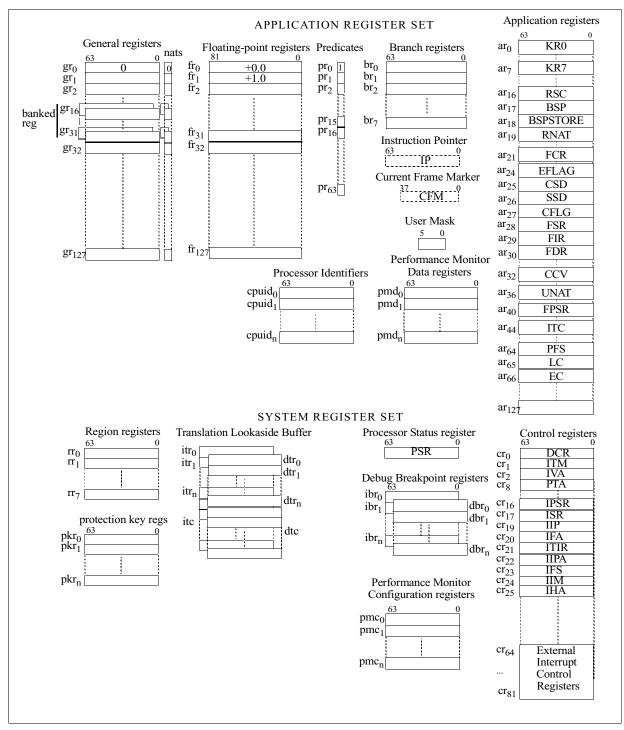

|   |        | 3.3.1 System State Overview                                           | 2:16 |

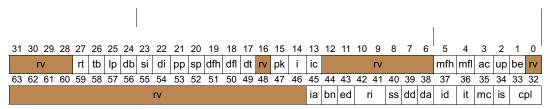

|   |        | 3.3.2 Processor Status Register (PSR)                                 | 2:18 |

|   |        | 3.3.3 Control Registers                                               | 2:24 |

|   |        | 3.3.4 Global Control Registers                                        | 2:25 |

|   |        | 3.3.5 Interruption Control Registers                                  | 2:29 |

|   |        | 3.3.6 External Interrupt Control Registers                            | 2:34 |

|   |        | 3.3.7 Banked General Registers                                        | 2:35 |

| 4 | Addr   | essing and Protection                                                 | 2:37 |

|   | 4.1    | Virtual Addressing                                                    | 2:37 |

|   |        | 4.1.1 Translation Lookaside Buffer (TLB)                              | 2:39 |

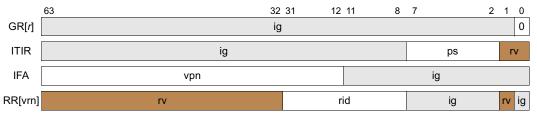

|   |        | 4.1.2 Region Registers (RR)                                           | 2:48 |

|   |        | 4.1.3 Protection Keys                                                 | 2:48 |

|   |        | 4.1.4 Translation Instructions                                        | 2:50 |

|   |        | 4.1.5 Virtual Hash Page Table (VHPT)                                  | 2:51 |

|   |        | 4.1.6 VHPT Hashing                                                    |      |

|   |        |                                                                       |      |

### االوا

|   |       | 4.1.7 VHP1 Environment                                              | 2:56  |

|---|-------|---------------------------------------------------------------------|-------|

|   |       | 4.1.8 Translation Searching                                         | 2:57  |

|   |       | 4.1.9 32-bit Virtual Addressing                                     | 2:60  |

|   |       | 4.1.10 Virtual Aliasing                                             | 2:61  |

|   | 4.2   | Physical Addressing                                                 | 2:61  |

|   | 4.3   | Unimplemented Address Bits                                          |       |

|   |       | 4.3.1 Unimplemented Physical Address Bits                           |       |

|   |       | 4.3.2 Unimplemented Virtual Address Bits                            |       |

|   |       | 4.3.3 Instruction Behavior with Unimplemented Addresses             |       |

|   | 4.4   | Memory Attributes                                                   |       |

|   | •••   | 4.4.1 Virtual Addressing Memory Attributes                          |       |

|   |       | 4.4.2 Physical Addressing Memory Attributes                         |       |

|   |       | 4.4.3 Cacheability and Coherency Attribute                          |       |

|   |       | 4.4.4 Cache Write Policy Attribute                                  |       |

|   |       | 4.4.5 Coalescing Attribute                                          |       |

|   |       | 4.4.6 Speculation Attributes                                        |       |

|   |       | 4.4.7 Sequentiality Attributes and Ordering                         |       |

|   |       |                                                                     |       |

|   |       | <b>9</b>                                                            |       |

|   |       | 4.4.9 Effects of Memory Attributes on Memory Reference Instructions |       |

|   |       | 4.4.10 Effects of Memory Attributes on Advanced/Check Loads         |       |

|   |       | 4.4.11 Memory Attribute Transition                                  |       |

|   | 4.5   | Memory Datum Alignment and Atomicity                                | 2:77  |

| 5 | Inter | ruptions                                                            | 2:79  |

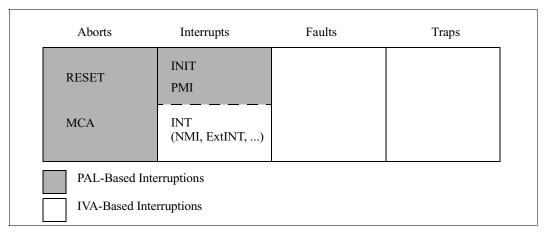

|   | 5.1   | Interruption Definitions                                            | 2:79  |

|   | 5.2   | Interruption Programming Model                                      | 2:81  |

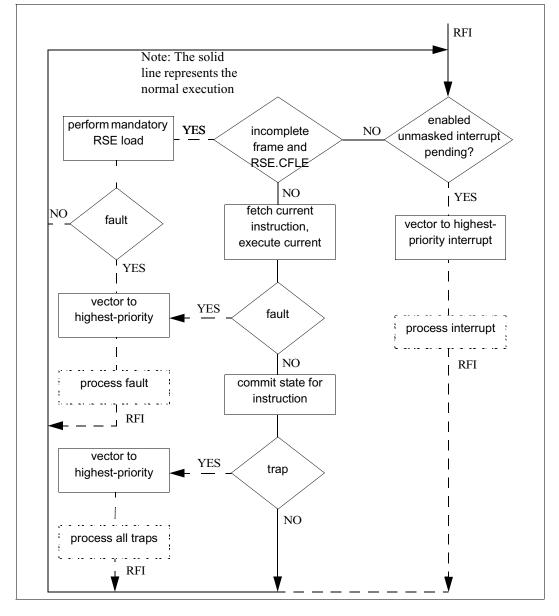

|   | 5.3   | Interruption Handling during Instruction Execution                  | 2:82  |

|   | 5.4   | PAL-based Interruption Handling                                     | 2:84  |

|   | 5.5   | IVA-based Interruption Handling                                     | 2:85  |

|   |       | 5.5.1 Efficient Interruption Handling                               |       |

|   |       | 5.5.2 Non-access Instructions and Interruptions                     |       |

|   |       | 5.5.3 Single Stepping                                               |       |

|   |       | 5.5.4 Single Instruction Fault Suppression                          |       |

|   |       | 5.5.5 Deferral of Speculative Load Faults                           |       |

|   | 5.6   | Interruption Priorities                                             |       |

|   | 0.0   | 5.6.1 IA-32 Interruption Priorities and Classes                     |       |

|   | 5.7   | IVA-based Interruption Vectors                                      |       |

|   | 5.8   | Interrupts                                                          |       |

|   | 0.0   | 5.8.1 Interrupt Vectors and Priorities                              |       |

|   |       | 5.8.2 Interrupt Enabling and Masking                                |       |

|   |       | 5.8.3 External Interrupt Control Registers                          |       |

|   |       | 5.8.4 Processor Interrupt Block                                     |       |

|   |       | 5.8.5 Edge- and Level-sensitive Interrupts                          |       |

|   |       |                                                                     |       |

| 6 | _     | ster Stack Engine                                                   |       |

|   | 6.1   | RSE and Backing Store Overview                                      |       |

|   | 6.2   | RSE Internal State                                                  |       |

|   | 6.3   | Register Stack Partitions                                           | 2:117 |

|   |       |                                                                     |       |

## intel®

|    | 6.4    | RSE Operation                                                        | 2:119 |

|----|--------|----------------------------------------------------------------------|-------|

|    | 6.5    | RSE Control                                                          | 2:120 |

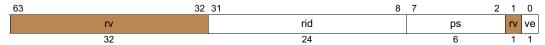

|    |        | 6.5.1 Register Stack Configuration Register                          | 2:120 |

|    |        | 6.5.2 Register Stack NaT Collection Register                         | 2:121 |

|    |        | 6.5.3 Backing Store Pointer Application Registers                    | 2:122 |

|    |        | 6.5.4 RSE Control Instructions                                       | 2:123 |

|    |        | 6.5.5 Bad PFS Used by Branch Return                                  | 2:124 |

|    | 6.6    | RSE Interruptions                                                    | 2:125 |

|    | 6.7    | RSE Behavior on Interruptions                                        |       |

|    | 6.8    | RSE Behavior with an Incomplete Register Frame                       | 2:127 |

|    | 6.9    | RSE and ALAT Interaction                                             | 2:127 |

|    | 6.10   | Backing Store Coherence and Memory Ordering                          | 2:128 |

|    | 6.11   | RSE Backing Store Switches                                           | 2:128 |

|    |        | 6.11.1 Switch from Interrupted Context                               | 2:129 |

|    |        | 6.11.2 Return to Interrupted Context                                 | 2:129 |

|    |        | 6.11.3 Synchronous Backing Store Switch                              | 2:129 |

|    | 6.12   | RSE Initialization                                                   |       |

| 7  | Debu   | gging and Performance Monitoring                                     | 2:131 |

|    | 7.1    | Debugging                                                            | 2:131 |

|    |        | 7.1.1 Data and Instruction Breakpoint Registers                      |       |

|    |        | 7.1.2 Debug Address Breakpoint Match Conditions                      |       |

|    | 7.2    | Performance Monitoring                                               |       |

|    |        | 7.2.1 Generic Performance Counter Registers                          |       |

|    |        | 7.2.2 Performance Monitor Overflow Status Registers (PMC[0]PMC[3])   |       |

|    |        | 7.2.3 Performance Monitor Events                                     |       |

|    |        | 7.2.4 Implementation-independent Performance Monitor Code Sequences. | 2:141 |

| 8  | Interr | uption Vector Descriptions                                           | 2:145 |

|    | 8.1    | Interruption Vector Descriptions                                     | 2:145 |

|    | 8.2    | ISR Settings                                                         |       |

|    | 8.3    | Interruption Vector Definition                                       |       |

| 9  | IA-32  | Interruption Vector Descriptions                                     | 2:187 |

|    | 9.1    | IA-32 Trap Code                                                      | 2:187 |

|    | 9.2    | IA-32 Interruption Vector Definitions                                |       |

| 10 | Itaniu | um®-based Operating System Interaction Model with IA-32 Applications | 2:213 |

|    | 10.1   | Instruction Set Transitions                                          | 2:213 |

|    | 10.2   | System Register Model                                                | 2:213 |

|    | 10.3   | IA-32 System Segment Registers                                       | 2:215 |

|    |        | 10.3.1 IA-32 Current Privilege Level                                 | 2:216 |

|    |        | 10.3.2 IA-32 System EFLAG Register                                   |       |

|    |        | 10.3.3 IA-32 System Registers                                        |       |

|    | 10.4   | Register Context Switch Guidelines for IA-32 Code                    |       |

|    |        | 10.4.1 Entering IA-32 Processes                                      |       |

|    |        | 10.4.2 Exiting IA-32 Processes                                       |       |

|    | 10.5   | IA-32 Instruction Set Behavior Summary                               |       |

### الint

|     | 10.6                 | System Memory Model                                        | 2:23 1                                                                                                                     |

|-----|----------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

|     |                      | 10.6.1 Virtual Memory References                           | 2:231                                                                                                                      |

|     |                      | 10.6.2 IA-32 Virtual Memory References                     | 2:232                                                                                                                      |

|     |                      | 10.6.3 IA-32 TLB Forward Progress Requirements             | 2:232                                                                                                                      |

|     |                      | 10.6.4 Multiprocessor TLB Coherency                        | 2:233                                                                                                                      |

|     |                      | 10.6.5 IA-32 Physical Memory References                    | 2:233                                                                                                                      |

|     |                      | 10.6.6 Supervisor Accesses                                 |                                                                                                                            |

|     |                      | 10.6.7 Memory Alignment                                    |                                                                                                                            |

|     |                      | 10.6.8 Atomic Operations                                   |                                                                                                                            |

|     |                      | 10.6.9 Multiprocessor Instruction Cache Coherency          |                                                                                                                            |

|     |                      | 10.6.10 IA-32 Memory Ordering                              |                                                                                                                            |

|     | 10.7                 | I/O Port Space Model                                       |                                                                                                                            |

|     |                      | 10.7.1 Virtual I/O Port Addressing                         |                                                                                                                            |

|     |                      | 10.7.2 Physical I/O Port Addressing                        |                                                                                                                            |

|     |                      | 10.7.3 IA-32 IN/OUT instructions                           |                                                                                                                            |

|     |                      | 10.7.4 I/O Port Accesses by Loads and Stores               |                                                                                                                            |

|     | 10.8                 | Debug Model                                                |                                                                                                                            |

|     |                      | 10.8.1 Data Breakpoint Register Matching                   |                                                                                                                            |

|     |                      | 10.8.2 Instruction Breakpoint Register Matching            |                                                                                                                            |

|     | 10.9                 | Interruption Model                                         |                                                                                                                            |

|     | 10.0                 | 10.9.1 Interruption Summary                                |                                                                                                                            |

|     |                      | 10.9.2 IA-32 Numeric Exception Model                       |                                                                                                                            |

|     | 10.10                | Processor Bus Considerations for IA-32 Application Support |                                                                                                                            |

|     | 10.10                | 10.10.1 IA-32 Compatible Bus Transactions                  |                                                                                                                            |

| 11  | Proces               | ssor Abstraction Layer                                     |                                                                                                                            |

|     |                      | 3301 AD3U                                                  |                                                                                                                            |

| • • |                      | -                                                          |                                                                                                                            |

| ••  | 11.1                 | Firmware Model                                             | 2:249                                                                                                                      |

| ••  |                      | Firmware Model                                             | 2:249<br>2:251                                                                                                             |

|     |                      | Firmware Model                                             | 2:249<br>2:251<br>2:252                                                                                                    |

|     |                      | Firmware Model                                             | 2:249<br>2:251<br>2:252<br>2:253                                                                                           |

|     |                      | Firmware Model                                             | 2:249<br>2:251<br>2:252<br>2:253<br>2:253                                                                                  |

|     |                      | Firmware Model                                             | 2:249<br>2:251<br>2:252<br>2:253<br>2:253                                                                                  |

|     | 11.1                 | Firmware Model                                             |                                                                                                                            |

|     |                      | Firmware Model                                             |                                                                                                                            |

|     | 11.1                 | Firmware Model                                             | 2:249<br>2:251<br>2:252<br>2:253<br>2:253<br>2:253<br>2:254<br>2:259                                                       |

|     | 11.1                 | Firmware Model                                             | 2:249<br>2:251<br>2:252<br>2:253<br>2:253<br>2:254<br>2:259<br>2:259                                                       |

|     | 11.1                 | Firmware Model                                             | 2:249<br>2:251<br>2:252<br>2:253<br>2:253<br>2:254<br>2:254<br>2:259<br>2:259                                              |

| •   | 11.1                 | Firmware Model                                             | 2:249<br>2:251<br>2:252<br>2:253<br>2:253<br>2:254<br>2:259<br>2:259<br>2:259<br>2:259                                     |

| •   | 11.1                 | Firmware Model                                             | 2:249<br>2:251<br>2:253<br>2:253<br>2:253<br>2:254<br>2:259<br>2:259<br>2:259<br>2:264<br>2:264                            |

| •   | 11.1                 | Firmware Model                                             | 2:249<br>2:251<br>2:252<br>2:253<br>2:253<br>2:254<br>2:259<br>2:259<br>2:259<br>2:264<br>2:265<br>2:265                   |

| •   | 11.1                 | Firmware Model                                             | 2:249<br>2:251<br>2:252<br>2:253<br>2:253<br>2:254<br>2:259<br>2:259<br>2:259<br>2:264<br>2:265<br>2:265                   |

|     | 11.1                 | Firmware Model                                             | 2:249<br>2:251<br>2:253<br>2:253<br>2:253<br>2:254<br>2:259<br>2:259<br>2:264<br>2:265<br>2:265<br>2:265<br>2:265          |

|     | 11.1                 | Firmware Model                                             | 2:249<br>2:251<br>2:253<br>2:253<br>2:253<br>2:254<br>2:259<br>2:259<br>2:259<br>2:265<br>2:265<br>2:265<br>2:265<br>2:273 |

|     | 11.1                 | Firmware Model                                             | 2:249 2:251 2:252 2:253 2:253 2:254 2:259 2:259 2:264 2:265 2:265 2:266 2:274 2:274                                        |

|     | 11.1                 | Firmware Model                                             | 2:249 2:251 2:252 2:253 2:253 2:254 2:254 2:259 2:259 2:264 2:265 2:265 2:265 2:274 2:274 2:274                            |

|     | 11.1<br>11.2<br>11.3 | Firmware Model                                             | 2:249 2:251 2:253 2:253 2:253 2:254 2:254 2:254 2:259 2:259 2:264 2:265 2:265 2:265 2:274 2:274 2:274 2:278                |

|     | 11.1<br>11.2<br>11.3 | Firmware Model                                             | 2:249 2:251 2:253 2:253 2:253 2:254 2:259 2:259 2:259 2:265 2:265 2:265 2:274 2:274 2:274 2:278 2:278                      |

|     | 11.1<br>11.2<br>11.3 | Firmware Model                                             | 2:249 2:251 2:253 2:253 2:253 2:254 2:259 2:259 2:259 2:265 2:265 2:265 2:274 2:274 2:274 2:278 2:278                      |

# intel®

|      | 0.11     | Power Management                                                           | 2:28              |

|------|----------|----------------------------------------------------------------------------|-------------------|

|      | 11.7     | PAL Glossary                                                               | 2:282             |

|      | 11.8     | PAL Code Memory Accesses and Restrictions                                  | 2:284             |

|      | 11.9     | PAL Procedures                                                             | 2:284             |

|      |          | 11.9.1 PAL Procedure Summary                                               | 2:28              |

|      |          | 11.9.2 PAL Calling Conventions                                             |                   |

|      |          | 11.9.3 PAL Procedure Specifications                                        |                   |

| Part | II: Svst | em Programmer's Guide                                                      |                   |

| 1    | _        | it the System Programmer's Guide                                           | 2:377             |

| •    | 1.1      | Overview of the System Programmer's Guide                                  |                   |

|      | 1.1      | · · · · · · · · · · · · · · · · · · ·                                      |                   |

|      | 1.2      | Related Documents                                                          | 2:378             |

| 2    | MP C     | oherence and Synchronization                                               | 2:38              |

|      | 2.1      | An Overview of Intel® Itanium® Memory Access Instructions                  | 2:38 <sup>2</sup> |

|      |          | 2.1.1 Memory Ordering of Cacheable Memory References                       | 2:38 <sup>2</sup> |

|      |          | 2.1.2 Loads and Stores                                                     | 2:382             |

|      |          | 2.1.3 Semaphores                                                           | 2:382             |

|      |          | 2.1.4 Memory Fences                                                        | 2:384             |

|      | 2.2      | Memory Ordering in the Intel® Itanium® Architecture                        | 2:384             |

|      |          | 2.2.1 Memory Ordering Executions                                           | 2:384             |

|      |          | 2.2.2 Memory Attributes                                                    | 2:396             |

|      |          | 2.2.3 Understanding Other Ordering Models: Sequential Consistency          |                   |

|      |          | and IA-32                                                                  | 2:397             |

|      | 2.3      | Where the Intel® Itanium® Architecture Requires Explicit Synchronization . | 2:398             |

|      | 2.4      | Synchronization Code Examples                                              | 2:399             |

|      |          | 2.4.1 Spin Lock                                                            | 2:399             |

|      |          | 2.4.2 Simple Barrier Synchronization                                       | 2:400             |

|      |          | 2.4.3 Dekker's Algorithm                                                   | 2:40°             |

|      |          | 2.4.4 Lamport's Algorithm                                                  | 2:402             |

|      | 2.5      | Updating Code Images                                                       | 2:404             |

|      |          | 2.5.1 Self-modifying Code                                                  | 2:404             |

|      |          | 2.5.2 Cross-modifying Code                                                 | 2:40              |

|      |          | 2.5.3 Programmed I/O                                                       | 2:406             |

|      |          | 2.5.4 DMA                                                                  |                   |

|      | 2.6      | References                                                                 | 2:408             |

| 3    | Interr   | ruptions and Serialization                                                 | 2:409             |

|      | 3.1      | Terminology                                                                | 2:409             |

|      | 3.2      | Interruption Vector Table                                                  | 2:410             |

|      | 3.3      | Interruption Handlers                                                      | 2:41 <sup>2</sup> |

|      |          | 3.3.1 Execution Environment                                                |                   |

|      |          | 3.3.2 Interruption Register State                                          |                   |

|      |          | 3.3.3 Resource Serialization of Interrupted State                          |                   |

|      |          | 3.3.4 Resource Serialization upon rfi                                      |                   |

### الint

|   | 3.4  | Interru  | ption Handling                                  | 2:414 |

|---|------|----------|-------------------------------------------------|-------|

|   |      | 3.4.1    | Lightweight Interruptions                       | 2:414 |

|   |      | 3.4.2    | Heavyweight Interruptions                       | 2:415 |

|   |      | 3.4.3    | Nested Interruptions                            | 2:417 |

| 4 | Cont | ext Mana | gement                                          | 2:419 |

|   | 4.1  | Preser   | rving Register State across Procedure Calls     | 2:419 |

|   |      | 4.1.1    | Preserving General Registers                    | 2:420 |

|   |      | 4.1.2    | Preserving Floating-point Registers             | 2:420 |

|   | 4.2  | Preser   | rving Register State in the OS                  | 2:421 |

|   |      | 4.2.1    | Preservation of Stacked Registers in the OS     | 2:422 |

|   |      | 4.2.2    | Preservation of Floating-point State in the OS  | 2:423 |

|   | 4.3  | Preser   | rving ALAT Coherency                            | 2:424 |

|   | 4.4  | Systen   | n Calls                                         | 2:424 |

|   |      | 4.4.1    | epc/Demoting Branch Return                      |       |

|   |      | 4.4.2    | break/rfi                                       |       |

|   |      | 4.4.3    | NaT Checking for NaTs in System Calls           | 2:426 |

|   | 4.5  | Contex   | xt Switching                                    |       |

|   |      | 4.5.1    | User-level Context Switching                    | 2:426 |

|   |      | 4.5.2    | Context Switching in an Operating System Kernel | 2:428 |

| 5 | Mem  | ory Mana | agement                                         | 2:429 |

|   | 5.1  | Addres   | ss Space Model                                  | 2:429 |

|   |      | 5.1.1    | Regions                                         | 2:429 |

|   |      | 5.1.2    | Protection Keys                                 | 2:431 |

|   | 5.2  | Transla  | ation Lookaside Buffers (TLBs)                  | 2:433 |

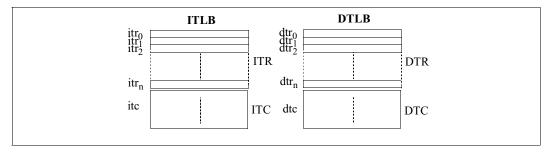

|   |      | 5.2.1    | Translation Registers (TRs)                     | 2:433 |

|   |      | 5.2.2    | Translation Caches (TCs)                        | 2:435 |

|   | 5.3  | Virtual  | Hash Page Table                                 | 2:438 |

|   |      | 5.3.1    | Short Format                                    | 2:439 |

|   |      | 5.3.2    | Long Format                                     | 2:440 |

|   |      | 5.3.3    | VHPT Updates                                    | 2:440 |

|   | 5.4  | TLB M    | liss Handlers                                   | 2:440 |

|   |      | 5.4.1    | Data/Instruction TLB Miss Vectors               |       |

|   |      | 5.4.2    |                                                 |       |

|   |      | 5.4.3    | Alternate Data/Instruction TLB Miss Vectors     |       |

|   |      | 5.4.4    | Data Nested TLB Vector                          |       |

|   |      | 5.4.5    | Dirty Bit Vector                                |       |

|   |      | 5.4.6    | Data/Instruction Access Bit Vector              |       |

|   |      | 5.4.7    | Page Not Present Vector                         |       |

|   |      | 5.4.8    | Data/Instruction Access Rights Vector           |       |

|   | 5.5  | Subpa    | ging                                            | 2:444 |

| 6 | Runt | ime Supp | port for Control and Data Speculation           | 2:447 |

|   | 6.1  |          | tion Deferral of Control Speculative Loads      |       |

|   |      | 6.1.1    | Hardware-only Deferral                          |       |

|   |      | 6.1.2    | Combined Hardware/Software Deferral             |       |

|   |      | 6.1.3    | Software-only Deferral                          | 2:448 |

# intel®

|    | 6.2    | Speculation Recovery Code Requirements                                   | 2:448 |

|----|--------|--------------------------------------------------------------------------|-------|

|    | 6.3    | Speculation Related Exception Handlers                                   | 2:449 |

|    |        | 6.3.1 Unaligned Handler                                                  | 2:449 |

| 7  | Instru | uction Emulation and Other Fault Handlers                                | 2:451 |

|    | 7.1    | Unaligned Reference Handler                                              | 2:451 |

|    | 7.2    | Unsupported Data Reference Handler                                       | 2:452 |

|    | 7.3    | Illegal Dependency Fault                                                 | 2:452 |

|    | 7.4    | Long Branch                                                              | 2:453 |

| 8  | Floati | ing-point System Software                                                | 2:455 |

|    | 8.1    | Floating-point Exceptions in the Intel® Itanium® Architecture            | 2:455 |

|    |        | 8.1.1 The Software Assistance Exceptions (Faults and Traps)              | 2:455 |

|    |        | 8.1.2 The IEEE Floating-point Exception Filter                           | 2:458 |

|    | 8.2    | IA-32 Floating-point Exceptions                                          | 2:460 |

| 9  | IA-32  | Application Support                                                      | 2:461 |

|    | 9.1    | Transitioning between Intel® Itanium® and IA-32 Instruction Sets         | 2:461 |

|    |        | 9.1.1 IA-32 Code Execution Environments                                  | 2:462 |

|    |        | 9.1.2 br.ia                                                              | 2:462 |

|    |        | 9.1.3 JMPE                                                               | 2:463 |

|    |        | 9.1.4 Procedure Calls between Intel® Itanium® and IA-32 Instruction Sets | 2:463 |

|    | 9.2    | IA-32 Architecture Handlers                                              | 2:464 |

|    | 9.3    | Debugging IA-32 and Itanium®-based Code                                  | 2:466 |

|    |        | 9.3.1 Instruction Breakpoints                                            | 2:466 |

|    |        | 9.3.2 Data Breakpoints                                                   | 2:466 |

|    |        | 9.3.3 Single Step Traps                                                  | 2:466 |

|    |        | 9.3.4 Taken Branch Traps                                                 | 2:466 |

| 10 | Exter  | nal Interrupt Architecture                                               | 2:467 |

|    | 10.1   | External Interrupt Basics                                                | 2:467 |

|    | 10.2   | Configuration of External Interrupt Vectors                              | 2:468 |

|    | 10.3   | External Interrupt Masking                                               | 2:468 |

|    |        | 10.3.1 PSR.i                                                             | 2:468 |

|    |        | 10.3.2 IVR Reads and EOI Writes                                          | 2:469 |

|    |        | 10.3.3 Task Priority Register (TPR)                                      |       |

|    |        | 10.3.4 External Task Priority Register (XTPR)                            | 2:469 |

|    | 10.4   | External Interrupt Delivery                                              |       |

|    | 10.5   | Interrupt Control Register Usage Examples                                |       |

|    |        | 10.5.1 Notation                                                          |       |

|    |        | 10.5.2 TPR and XPTR Usage Example                                        |       |

|    |        | 10.5.3 EOI Usage Example                                                 |       |

|    |        | 10.5.4 IRR Usage Example                                                 |       |

|    |        | 10.5.5 Interval Timer Usage Example                                      |       |

|    |        | 10.5.6 Local Redirection Example                                         |       |

|    |        | 10.5.7 Inter-processor Interrupts Layout and Example                     |       |

|    |        | 10.5.8 INTA Example                                                      | 2:475 |

| 11         | I/O Ar          | chitecture                                                                            | 2:477 |

|------------|-----------------|---------------------------------------------------------------------------------------|-------|

|            | 11.1            | Memory Acceptance Fence (mf.a)                                                        | 2:477 |

|            | 11.2            | I/O Port Space                                                                        | 2:478 |

| 12         | Perfo           | rmance Monitoring Support                                                             | 2:481 |

|            | 12.1            | Architected Performance Monitoring Mechanisms                                         | 2:481 |

|            | 12.2            | Operating System Support                                                              |       |

| 13         | Firmw           | vare Overview                                                                         | 2:485 |

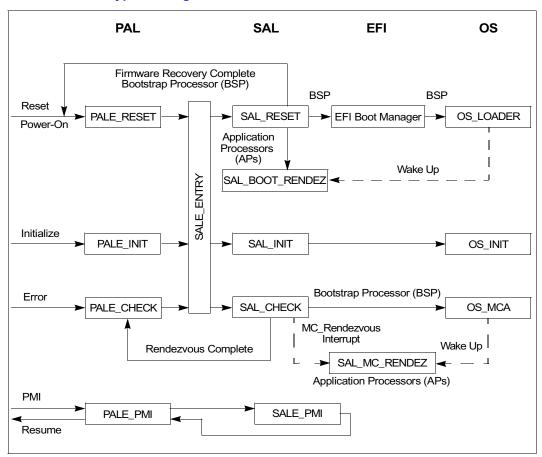

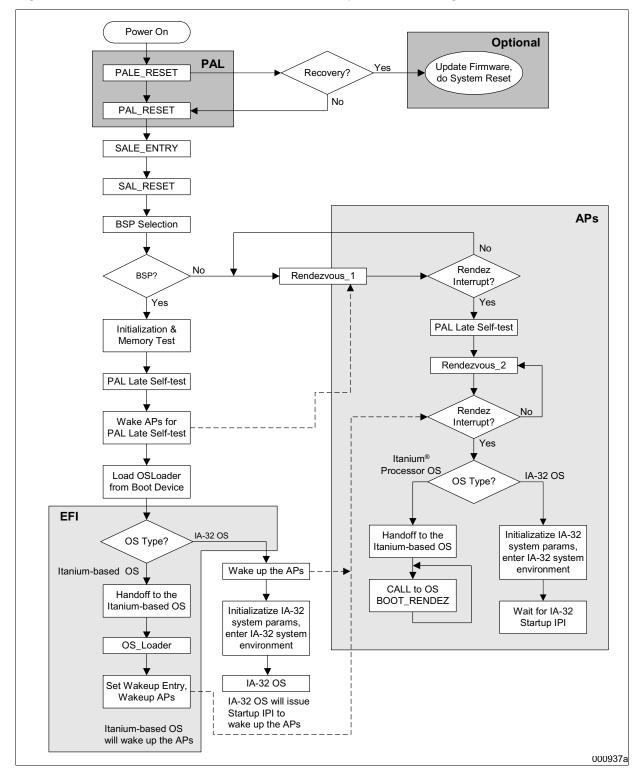

|            | 13.1            | Processor Boot Flow Overview                                                          | 2:485 |

|            |                 | 13.1.1 Firmware Boot Flow                                                             | 2:485 |

|            |                 | 13.1.2 Operating System Boot Steps                                                    | 2:487 |

|            | 13.2            | Runtime Procedure Calls                                                               |       |

|            |                 | 13.2.1 PAL Procedure Calls                                                            | 2:490 |

|            |                 | 13.2.2 SAL Procedure Calls                                                            |       |

|            |                 | 13.2.3 EFI Procedure Calls                                                            |       |

|            |                 | 13.2.4 Physical and Virtual Addressing Mode Considerations                            |       |

|            | 13.3            | Event Handling in Firmware                                                            |       |

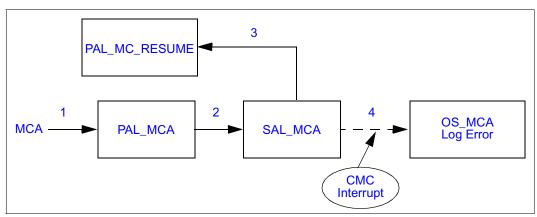

|            |                 | 13.3.1 Machine Check Abort (MCA) Flows                                                |       |

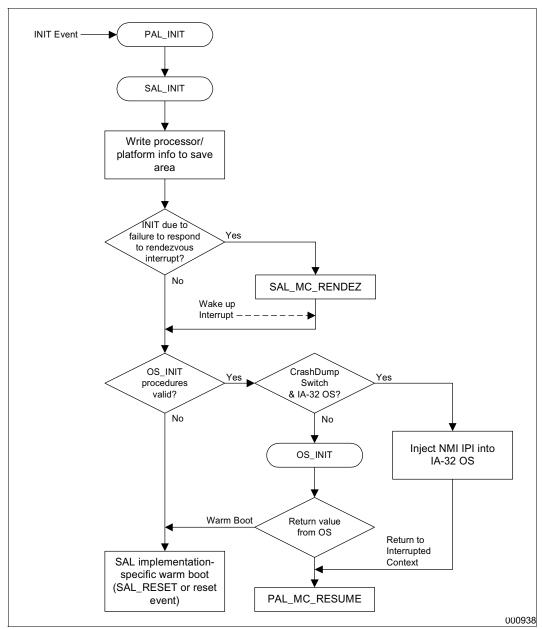

|            |                 | 13.3.2 INIT Flows                                                                     |       |

|            |                 | 13.3.3 PMI Flows                                                                      |       |

| A          | Code            | Examples                                                                              | 2:499 |

|            | A.1             | OS Boot Flow Sample Code                                                              |       |

|            | ures<br>: Syste | m Architecture Guide                                                                  |       |

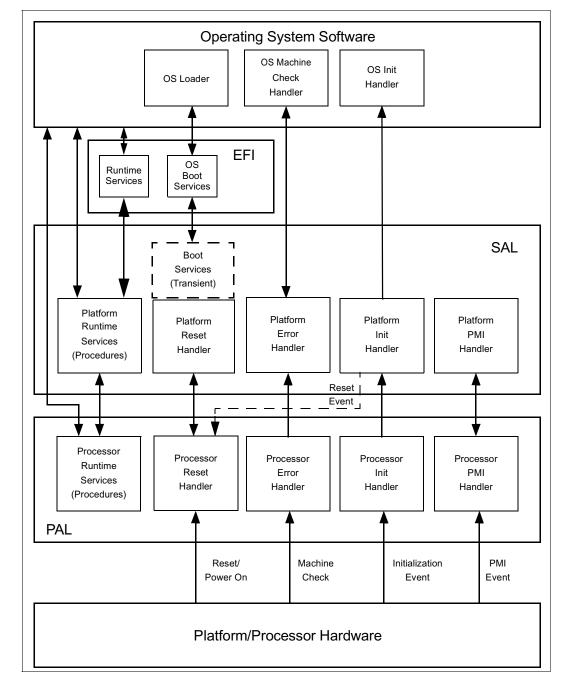

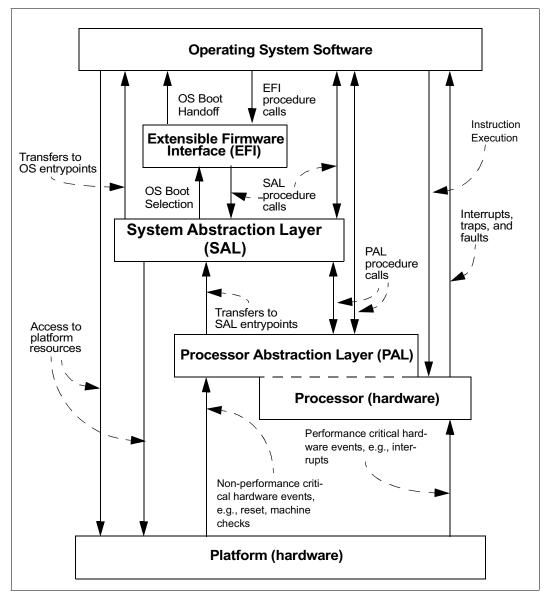

| 2-1        | -               | m Environment Boot Flow                                                               | 2:10  |

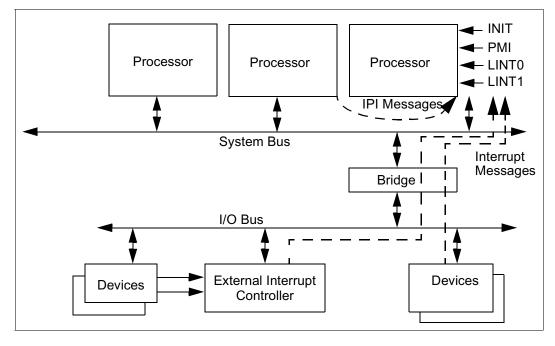

| 2-2        | Intel®          | Itanium® System Environment                                                           | 2:11  |

| 3-1        | Syster          | m Register Model                                                                      | 2:17  |

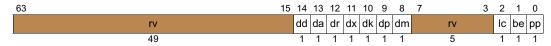

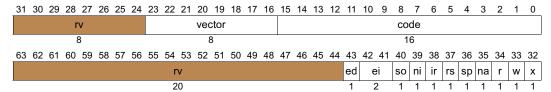

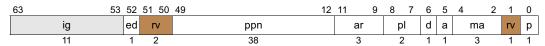

| 3-2        |                 | ssor Status Register (PSR)                                                            |       |

| 3-3        |                 | It Control Register (DCR – CR0)                                                       |       |

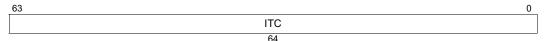

| 3-4        |                 | al Time Counter (ITC – AR44)                                                          |       |

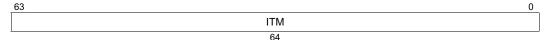

| 3-5        |                 | al Timer Match Register (ITM – CR1)                                                   |       |

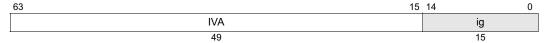

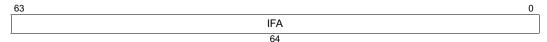

| 3-6        |                 | uption Vector Address (IVA – CR2)                                                     |       |

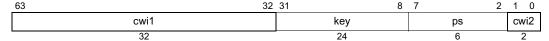

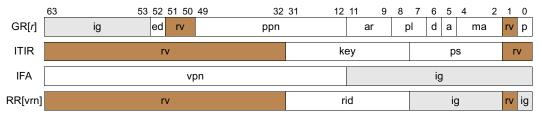

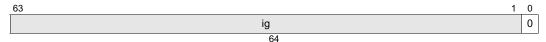

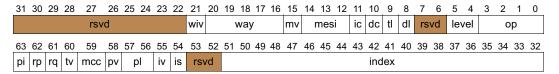

| 3-7        |                 | Table Address (PTA – CR8)                                                             |       |

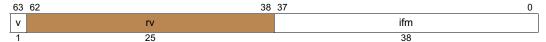

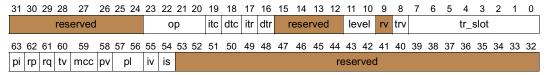

| 3-8<br>3-9 |                 | uption Status Register (ISR – CR17)<br>uption Instruction Bundle Pointer (IIP – CR19) |       |

| 3-10       |                 | uption Faulting Address (IFA – CR20)                                                  |       |

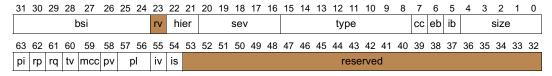

| 3-10       |                 | uption TLB Insertion Register (ITIR)                                                  |       |

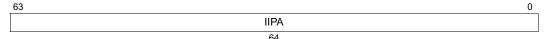

| 3-12       |                 | uption Instruction Previous Address (IIPA – CR22)                                     |       |

| 3-13       |                 | uption Function State (IFS – CR23)                                                    |       |

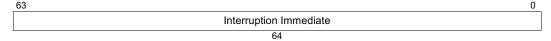

| 3-14       |                 | uption Immediate (IIM – CR24)                                                         |       |

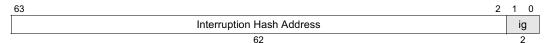

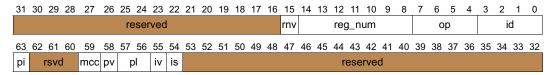

| 3-15       |                 | uption Hash Address (IHA – CR25)                                                      |       |

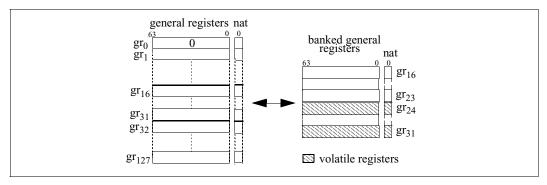

| 3-16       |                 | ed General Registers                                                                  |       |

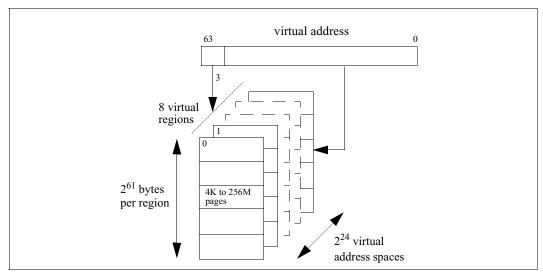

| 4-1        | Virtua          | I Address Spaces                                                                      | 2:38  |

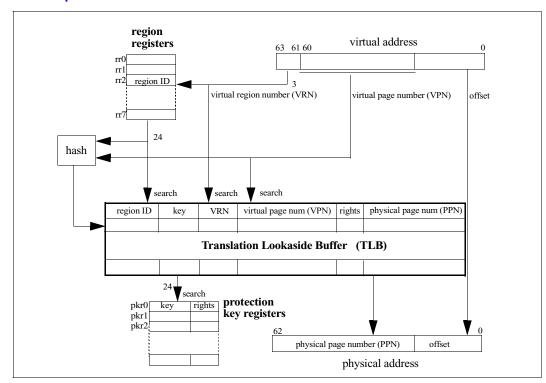

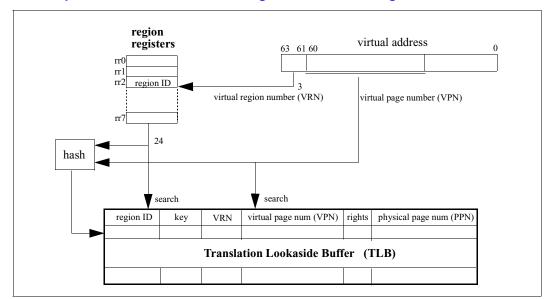

| 4-2        |                 | eptual Virtual Address Translation for References                                     |       |

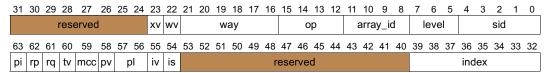

| 4-3        | TLB C           | Organization                                                                          | 2:39  |

# intel®

| 4-4                    | Conceptual Virtual Address Searching for Inserts and Purges                                                                     |       |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|

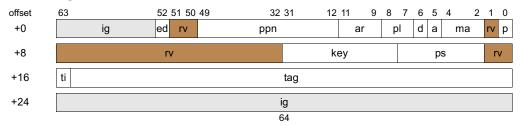

| 4-5                    | Translation Insertion Format                                                                                                    |       |

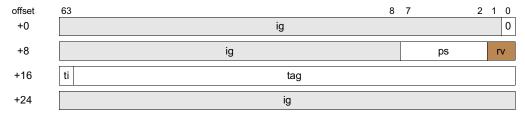

| 4-6                    | Translation Insertion Format – Not Present                                                                                      | 2:45  |

| 4-7                    | Region Register Format                                                                                                          | 2:48  |

| 4-8                    | Protection Key Register Format                                                                                                  |       |

| 4-9                    | Virtual Hash Page Table (VHPT)                                                                                                  | 2:51  |

| 4-10                   | VHPT Short Format                                                                                                               | 2:52  |

| 4-11                   | VHPT Not-present Short Format                                                                                                   | 2:53  |

| 4-12                   | VHPT Long Format                                                                                                                | 2:53  |

| 4-13                   | VHPT Not-present Long Format                                                                                                    | 2:54  |

| 4-14                   | Region-based VHPT Short-format Index Function                                                                                   |       |

| 4-15                   | VHPT Long-format Hash Function                                                                                                  |       |

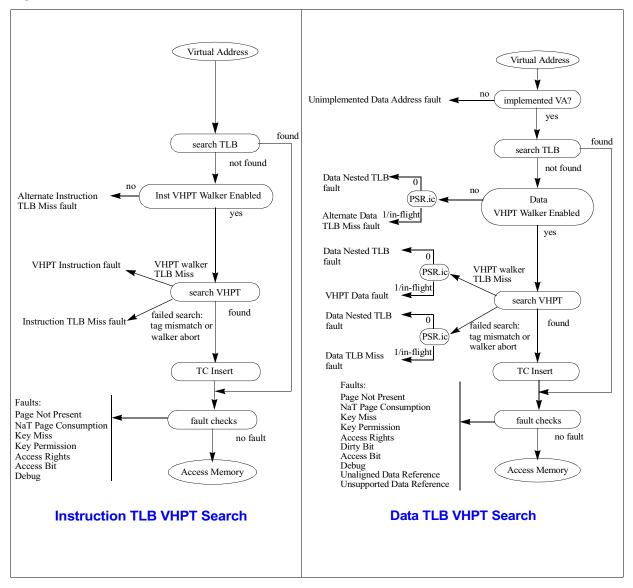

| 4-16                   | TLB/VHPT Search                                                                                                                 | 2:58  |

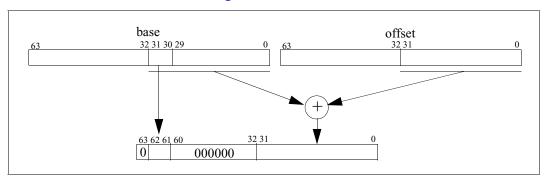

| 4-17                   | 32-bit Address Generation using addp4                                                                                           |       |

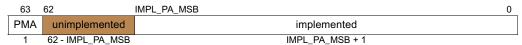

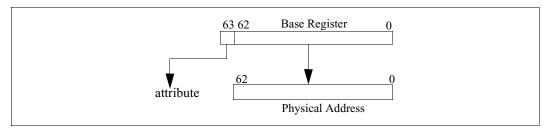

| 4-18                   | Physical Address Bit Fields                                                                                                     |       |

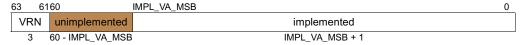

| 4-19                   | Virtual Address Bit Fields                                                                                                      |       |

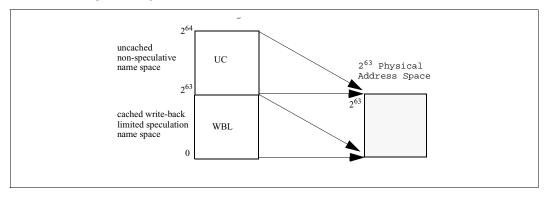

| 4-20                   | Physical Addressing Memory                                                                                                      |       |

| 4-21                   | Addressing Memory Attributes                                                                                                    |       |

| 5-1                    | Interruption Classification                                                                                                     |       |

| 5-2                    | Interruption Processing                                                                                                         |       |

| 5-3                    | Interrupt Architecture Overview                                                                                                 |       |

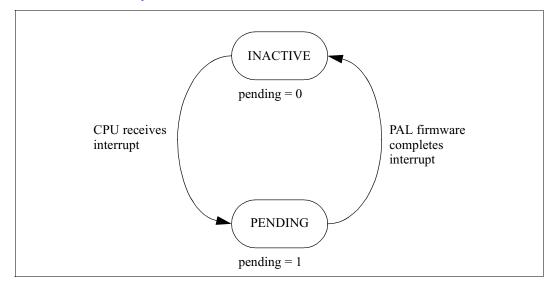

| 5-4                    | PAL-based Interrupt States                                                                                                      |       |

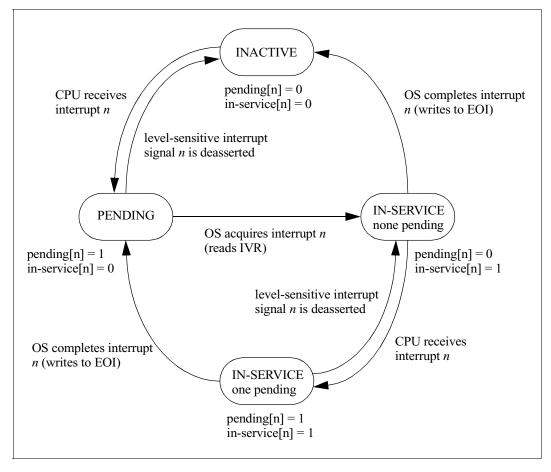

| 5-5                    | External Interrupt States                                                                                                       |       |

| 5-6                    | Local ID (LID – CR64)                                                                                                           |       |

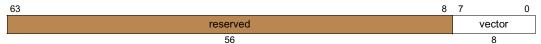

| 5-7                    | External Interrupt Vector Register (IVR – CR65)                                                                                 |       |

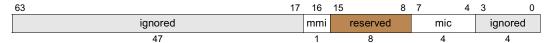

| 5-8                    | Task Priority Register (TPR – CR66)                                                                                             |       |

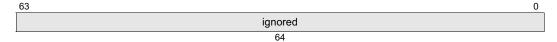

| 5-9                    | End of External Interrupt Register (EOI – CR67)                                                                                 |       |

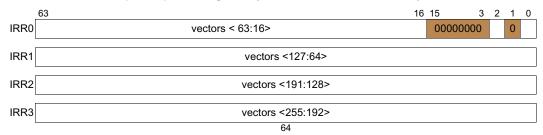

| 5-10                   | External Interrupt Request Register (IRR0-3 – CR68, 69, 70, 71)                                                                 |       |

| 5-11                   | Interval Timer Vector (ITV – CR72)                                                                                              |       |

| 5-12                   | Performance Monitor Vector (PMV – CR73)                                                                                         |       |

| 5-13                   | Corrected Machine Check Vector (CMCV – CR74)                                                                                    |       |

| 5-14                   | Local Redirection Register (LRR – CR80,81)                                                                                      |       |

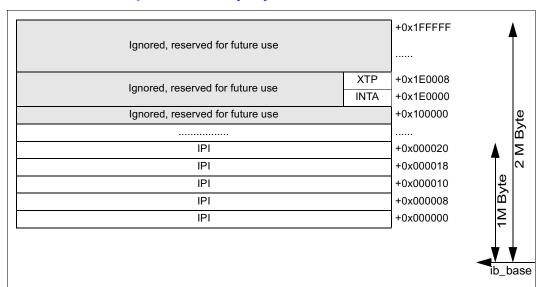

| 5-15                   | Processor Interrupt Block Memory Layout                                                                                         |       |

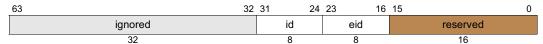

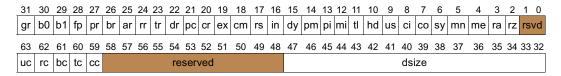

| 5-16                   | Address Format for Inter-Processor Interrupt Messages                                                                           |       |

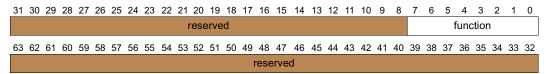

| 5-17                   | Data Format for Inter-Processor Interrupt Messages                                                                              |       |

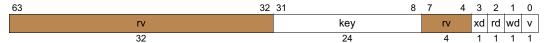

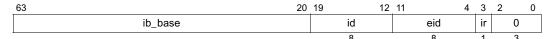

| 6-1                    | Relationship Between Physical Registers and Backing Store                                                                       |       |

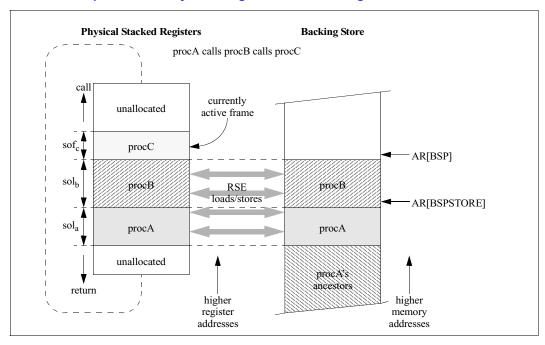

| 6-2                    | Backing Store Memory Format                                                                                                     |       |

| 6-3                    | Four Partitions of the Register Stack                                                                                           |       |

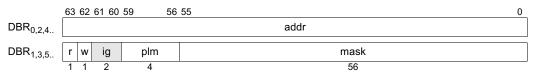

| 7-1                    | Data Breakpoint Registers (DBR)                                                                                                 |       |

| 7-2                    | Instruction Breakpoint Registers (IBR)                                                                                          |       |

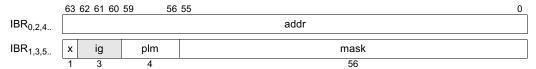

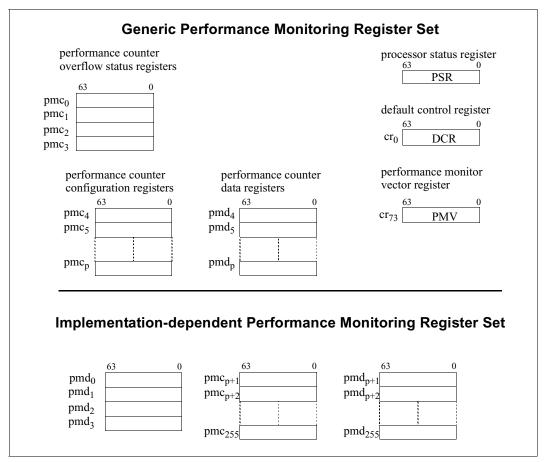

| 7-3                    | Performance Monitor Register Set                                                                                                |       |

| 7-4                    | Generic Performance Counter Data Registers (PMD[4]PMD[p])                                                                       |       |

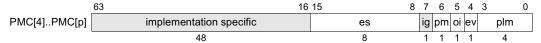

| 7- <del>4</del><br>7-5 | Generic Performance Counter Data Registers (PMD[4]PMD[p])                                                                       |       |

| 7-6                    | Performance Monitor Overflow Status Registers (PMC[0]PMC[3])                                                                    |       |

| 7-0<br>7-7             |                                                                                                                                 |       |

| 7-7<br>7-8             | Performance Monitor Interrupt Service Routine (Implementation Independent)  Performance Monitor Overflow Context Switch Routine |       |

| 7-0<br>9-1             |                                                                                                                                 |       |

|                        | IA-32 Trap Code                                                                                                                 |       |

| 9-2                    | IA-32 Trap Code                                                                                                                 |       |

| 9-3                    | IA-32 Intercept CodeIA-32 System Segment Register Descriptor Format (LDT, GDT, TSS)                                             |       |

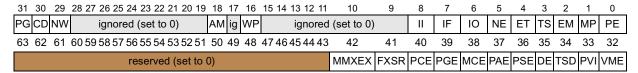

| 10-1<br>10-2           |                                                                                                                                 |       |

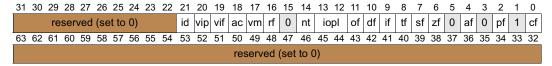

|                        | IA-32 EFLAG Register (CELC AR27)                                                                                                |       |

| 10-3                   | Control Flag Register (CFLG, AR27)                                                                                              | ZiZZL |

# int<sub>el®</sub>

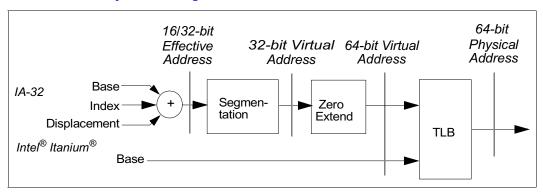

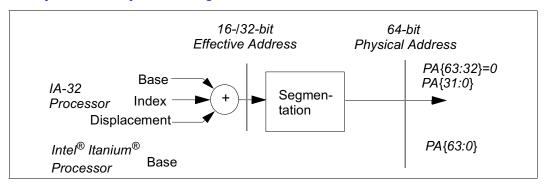

| 10-4  | Virtual Memory Addressing                                       | 2:231 |

|-------|-----------------------------------------------------------------|-------|

| 10-5  | Physical Memory Addressing                                      | 2:233 |

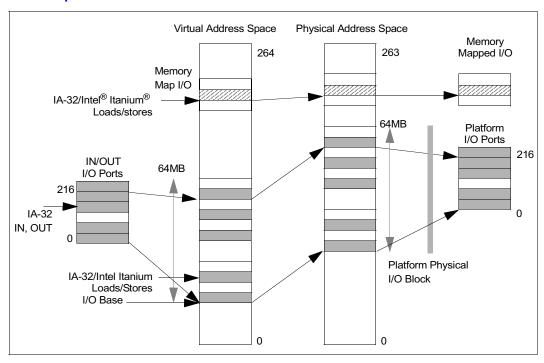

| 10-6  | I/O Port Space Model                                            | 2:239 |

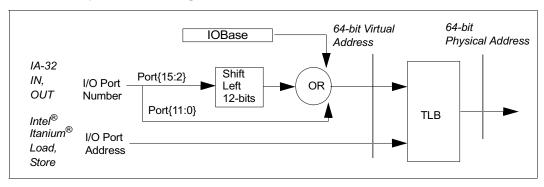

| 10-7  | I/O Port Space Addressing                                       | 2:239 |

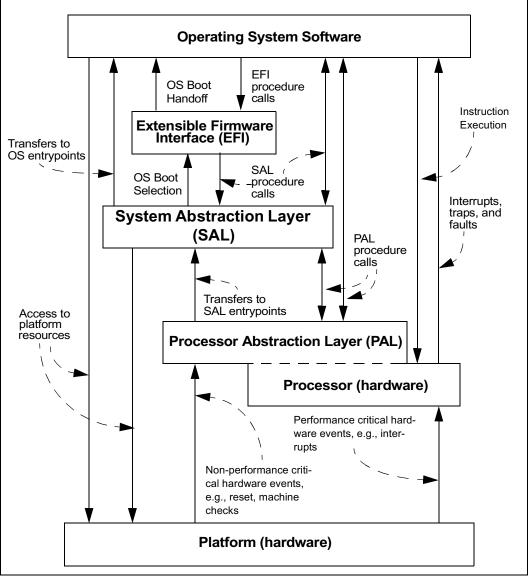

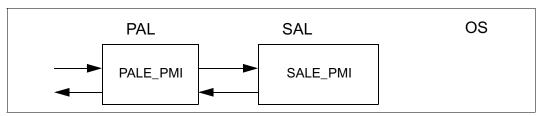

| 11-1  | Firmware Model                                                  | 2:250 |

| 11-2  | Firmware Services Model                                         | 2:251 |

| 11-3  | Firmware Entrypoints Logical Model                              | 2:252 |

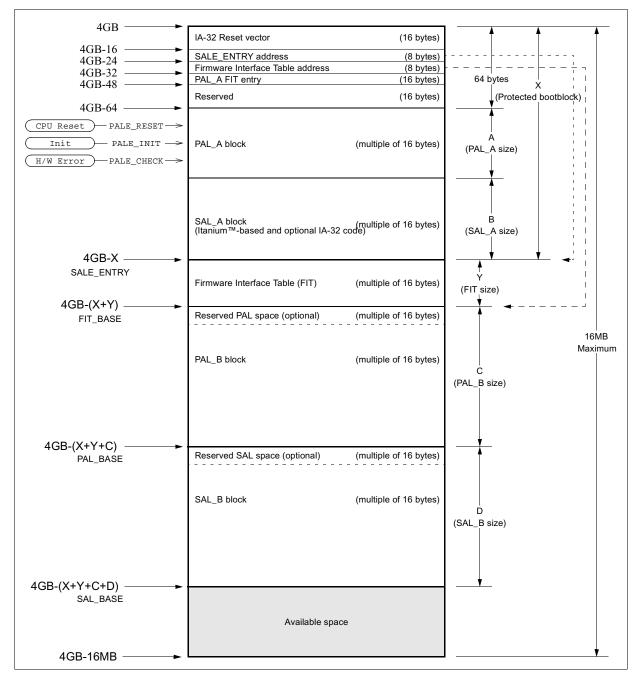

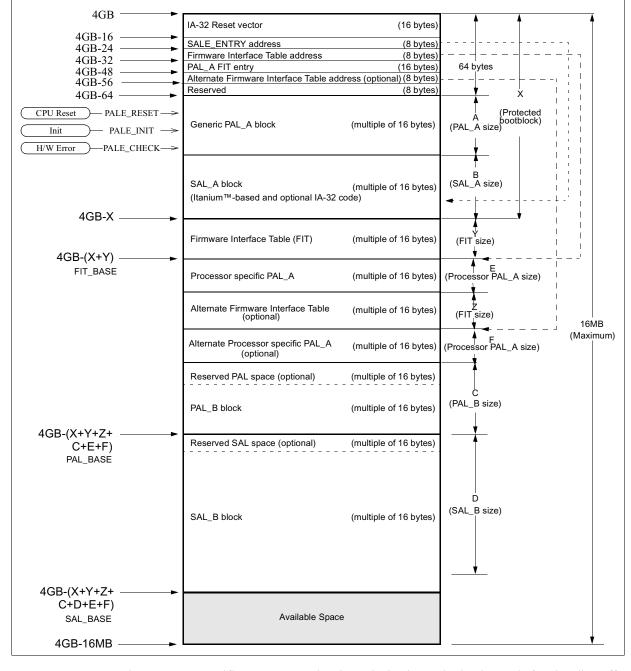

| 11-4  | Firmware Address Space                                          | 2:255 |

| 11-5  | Firmware Address Space with Processor-specific PAL_A Components |       |

| 11-6  | Firmware Interface Table                                        |       |

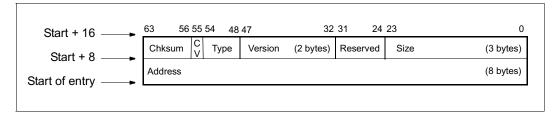

| 11-7  | Firmware Interface Table Entry                                  |       |

| 11-8  | SALE ENTRY State Parameter                                      | 2:261 |

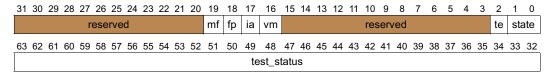

| 11-9  | Self Test State Parameter                                       | 2:262 |

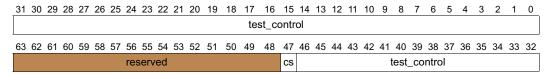

| 11-10 | Self-test Control Word                                          | 2:264 |

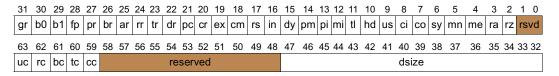

| 11-11 | Processor State Parameter                                       |       |

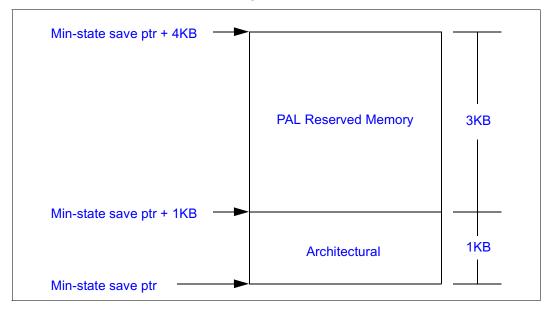

| 11-12 | Processor Min-state Save Area Layout                            |       |

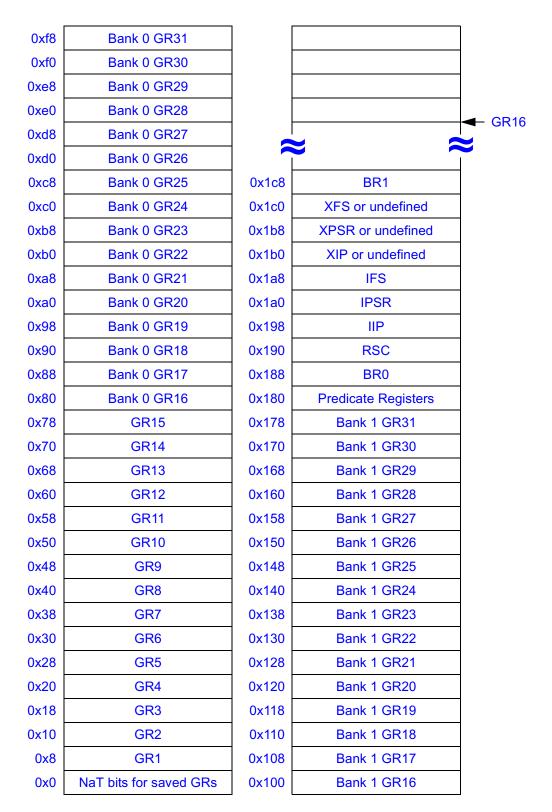

| 11-13 | Processor State Saved in Min-state Save Area                    |       |

| 11-14 | SALE_ENTRY State Parameter                                      |       |

| 11-15 | Processor State Parameter                                       |       |

| 11-16 | SALE_ENTRY State Parameter                                      |       |

| 11-17 | PMI Entrypoints                                                 |       |

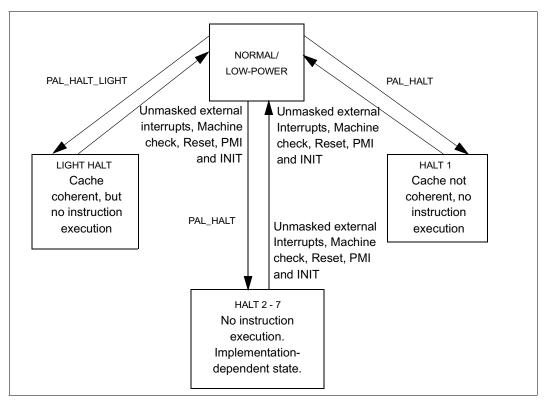

| 11-18 | Power States                                                    |       |

| 11-19 | operation Parameter Layout                                      |       |

| 11-20 | config_info_1 Return Value                                      |       |

| 11-21 | config info 2 Return Value                                      |       |

| 11-22 | config_info_1 Return Value                                      |       |

| 11-23 | config_info_2 Return Value                                      |       |

| 11-24 | config_info_3 Return Value                                      |       |

| 11-25 | Layout of line_id Return Value                                  |       |

| 11-26 | Layout of proc_n_log_info1 Return Value                         |       |

| 11-27 | Layout of proc_n_log_info2 Return Value                         |       |

| 11-28 | Layout of line_id Return Value                                  |       |

| 11-29 | Layout of platform_info Input Parameter                         |       |

| 11-30 | I/O Size and Type Information Layout                            |       |

| 11-31 | Layout of power buffer Return Value                             |       |

| 11-32 | Layout of log_overview Return Value                             |       |

| 11-33 | Layout of proc_n_log_info1 Return Value                         |       |

|       | Layout of proc_n_log_info2 Return Value                         |       |

| 11-35 | Pending Return Parameter                                        |       |

| 11-36 | level_index Layout                                              |       |

| 11-37 | Cache_Check Layout                                              |       |

| 11-38 | TLB_Check Layout                                                |       |

| 11-39 | Bus Check Layout                                                |       |

| 11-40 | Reg_File_Check Layout                                           |       |

| 11-41 | uarch_check Layout                                              |       |

| 11-42 | Layout of attrib Return Value                                   |       |

| 11-43 | Layout of PM_info Return Value                                  |       |

| 11-44 | Layout of hints Return Value                                    |       |

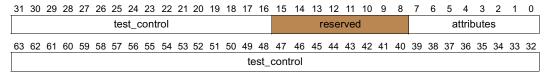

| 11-45 | Layout of test_info Argument                                    |       |

| 11-46 | Layout of test_param Argument                                   |       |

| 11-47 | Layout of min_pal_ver and current_pal_ver Return Values         |       |

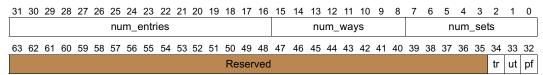

| 11-48 | Layout of tc_info Return Value                                  |       |

|       |                                                                 |       |

# $\text{intel}_{^{\tiny{\$}}}$

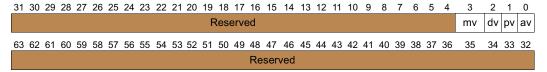

| 11-49              | Layout of vm_info_1 Return Value                                                         | 2:372 |

|--------------------|------------------------------------------------------------------------------------------|-------|

| 11-50              | Layout of vm_info_2 Return Value                                                         | 2:373 |

| 11-51              | Layout of TR_valid Return Value                                                          | 2:374 |

| Part II            | : System Programmer's Guide                                                              |       |

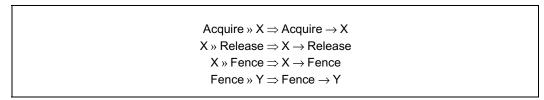

| 2-1                | Intel® Itanium® Ordering Semantics                                                       | 2:386 |

| 2-2                | Interaction of Ordering and Accesses to Sequential Locations                             |       |

| 2-3                | Why a Fence During Context Switches is Required in the Intel® Itanium® Architecture      |       |

| 2-3                | Spin Lock Code                                                                           |       |

| 2-5                | Sense-reversing Barrier Synchronization Code                                             |       |

| 2-6                |                                                                                          |       |

| 2-0                | Dekker's Algorithm in a 2-way System                                                     |       |

|                    | Lamport's Algorithm                                                                      |       |

| 2-8                | Updating a Code Image on the Local Processor                                             |       |

| 2-9                | Supporting Cross-modifying Code without Explicit Serialization                           |       |

| 2-10               | Updating a Code Image on a Remote Processor                                              |       |

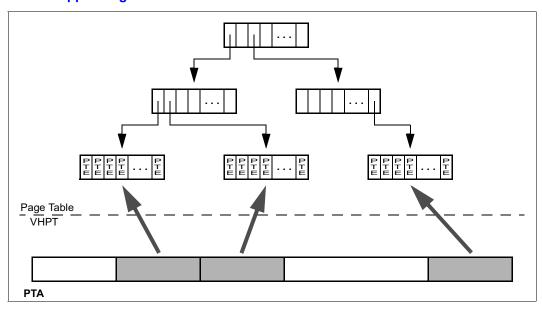

| 5-1                | Self-mapped Page Table                                                                   |       |

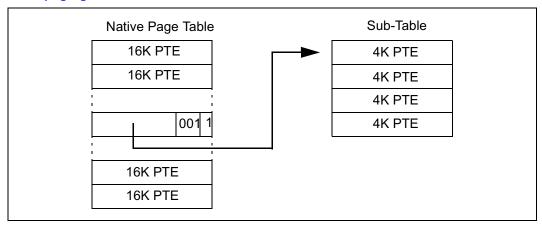

| 5-2                | Subpaging                                                                                |       |

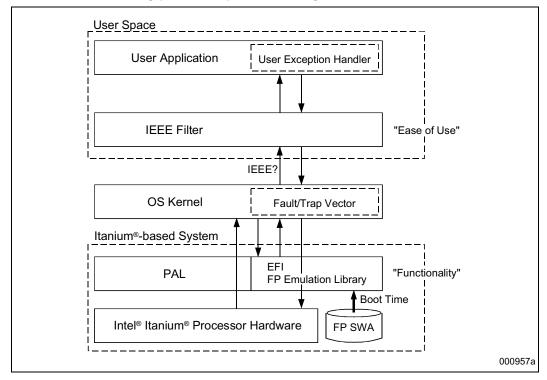

| 8-1                | Overview of Floating-point Exception Handling in the Intel® Itanium® Architecture        |       |

| 13-1               | Firmware Model                                                                           |       |

| 13-2               | Control Flow of Boot Process in a Multi-processor Configuration                          |       |

| 13-3               | Correctable Machine Check Code Flow                                                      |       |

| 13-4               | Uncorrectable Machine Check Code Flow                                                    |       |

| 13-5               | INIT Flow                                                                                | 2:497 |

|                    | System Architecture Guide                                                                | 0.46  |

| 3-1                | Processor Status Register Instructions                                                   |       |

| 3-2                | Processor Status Register Fields                                                         |       |

| 3-3                | Control Registers                                                                        |       |

| 3-4                | Control Register Instructions                                                            |       |

| 3-5                | Default Control Register Fields                                                          |       |

| 3-6                | Page Table Address Fields                                                                |       |

| 3-7                | Interruption Status Register Fields                                                      |       |

| 3-8                | ITIR Fields                                                                              |       |

| 3-9                | Interruption Function State Fields                                                       |       |

| 4-1                | Purge Behavior of TLB Instructions                                                       |       |

| 4-2<br>4-3         | Translation Interface Fields                                                             |       |

|                    | Page Access Rights                                                                       |       |

| 4-4<br>4-5         | Architected Page Sizes                                                                   |       |

|                    | Region Register Fields                                                                   |       |

| 4-6<br>4-7         | Protection Register Fields                                                               |       |

| 4- <i>7</i><br>4-8 | Translation Instructions                                                                 |       |

|                    | VHPT Long-format Fields                                                                  |       |

| 4-9<br>4-10        | TLB and VHPT Search Faults                                                               |       |

| 4-10<br>4-11       | Virtual Addressing Memory Attribute Encodings                                            |       |

| 4-11<br>4-12       | Physical Addressing Memory Attribute Encodings                                           |       |

| 4-12<br>4-13       | Permitted Speculation  Register Return Values on Non-faulting Advanced/Speculative Loads |       |

| 4-13<br>4-14       | · · · · · · · · · · · · · · · · · · ·                                                    |       |

| 4-14               | Ordering Semantics and Instructions                                                      | ∠:/∪  |

### int<sub>el®</sub>

| 4-15                   | Ordering Semantics                                                                | 2:70  |

|------------------------|-----------------------------------------------------------------------------------|-------|

| 4-16                   | ALAT Behavior on Non-faulting Advanced/Check Loads                                | 2:74  |

| 5-1                    | ISR Settings for Non-access Instructions                                          |       |

| 5-2                    | Programming Models                                                                |       |

| 5-3                    | Exception Qualification                                                           |       |

| 5-4                    | Qualified Exception Deferral                                                      |       |

| 5-5                    | Spontaneous Deferral                                                              |       |

| 5-6                    | Interruption Priorities                                                           |       |

| 5-7                    | Interruption Vector Table (IVT)                                                   |       |

| 5-8                    | Interrupt Priorities, Enabling, and Masking                                       |       |

| 5-9                    | External Interrupt Control Registers                                              |       |

| 5-10                   | Local ID Fields                                                                   |       |

| 5-11                   | Task Priority Register Fields                                                     |       |

| 5-12                   | Interval Timer Vector Fields                                                      |       |

| 5-13                   | Performance Monitor Vector Fields                                                 |       |

| 5-14                   | Corrected Machine Check Vector Fields                                             |       |

| 5-15                   | Local Redirection Register Fields                                                 |       |

| 5-16                   | Address Fields for Inter-Processor Interrupt Messages                             |       |

| 5-17                   | Data Fields for Inter-Processor Interrupt Messages                                |       |

| 6-1                    | RSE Internal State                                                                |       |

| 6-2                    | RSE Operation Instructions and State Modification                                 |       |

| 6-3                    | RSE Modes (RSC.mode)                                                              |       |

| 6-4                    | Backing Store Pointer Application Registers                                       |       |

| 6-5                    | RSE Control Instructions                                                          |       |

| 6-6                    | RSE Interruption Summary                                                          |       |

| 7-1                    | Debug Breakpoint Register Fields (DBR/IBR)                                        |       |

| 7-1                    | Debug Instructions                                                                |       |

| 7-3                    | Generic Performance Counter Data Register Fields                                  |       |

| 7-3<br>7-4             | Generic Performance Counter Data Register Fields (PMC[4]PMC[p])                   |       |

| 7- <del>4</del><br>7-5 | Reading Performance Monitor Data Registers                                        |       |

| 7-5<br>7-6             | Performance Monitor Instructions                                                  |       |

| 7-0<br>7-7             | Performance Monitor Overflow Register Fields (PMC[0]PMC[3])                       |       |

| 8-1                    | Writing of Interruption Resources by Vector                                       |       |

| 8-2                    | ISR Values on Interruption                                                        |       |

| 8-3                    | ISR.code Fields on Intel® Itanium® Traps                                          |       |

| 8-4                    | Interruption Vectors Sorted Alphabetically                                        |       |

| 9-1                    | Intercept Code Definition                                                         |       |

| 9-2                    | Segment Prefix Override Encodings                                                 |       |

| 9-3                    | Gate Intercept Trap Code Identifier                                               |       |

| 9-3<br>9-4             | System Flag Intercept Instruction Trap Code Instruction Identifier                |       |

| 10-1                   | IA-32 System Register Mapping                                                     |       |

| 10-1                   | IA-32 System Register MappingIA-32 System Segment Register Fields (LDT, GDT, TSS) |       |

| 10-2                   | IA-32 EFLAG Field Definition                                                      |       |

| 10-3                   |                                                                                   |       |

|                        | IA-32 Control Register Field Definition                                           |       |

| 10-5                   | IA-32 Instruction Summary                                                         |       |

| 10-6                   | Instruction Cache Coherency Rules                                                 |       |

| 10-7                   | IA-32 Load/Store Sequentiality and Ordering                                       |       |

| 10-8                   | IA-32 Interruption Vector Summary                                                 |       |

| 10-9                   | IA-32 Interruption Summary                                                        |       |

| 11-1                   | FIT Entry Types                                                                   |       |

| 11-2                   | function Field Values                                                             |       |

| 11-3                   | status Field Values                                                               | 2:261 |

### intط

| 11-4  | state Field Values                                                   | 2:263 |

|-------|----------------------------------------------------------------------|-------|

| 11-5  | Processor State Parameter Fields                                     |       |

| 11-6  | Software Recovery Bits in Processor State Parameter                  | 2:269 |

| 11-7  | function Field Values                                                | 2:273 |

| 11-8  | Processor State Parameter Fields                                     | 2:276 |

| 11-9  | function Field Values                                                | 2:277 |

| 11-10 | PMI Events and Priorities                                            | 2:278 |

| 11-11 | PMI Message Vector Assignments                                       | 2:279 |

| 11-12 | PAL Procedure Index Assignment                                       | 2:285 |

| 11-13 | PAL Cache and Memory Procedures                                      | 2:285 |

| 11-14 | PAL Processor Identification, Features, and Configuration Procedures | 2:286 |

| 11-15 | PAL Machine Check Handling Procedures                                | 2:287 |

| 11-16 | PAL Power Information and Management Procedures                      | 2:287 |

| 11-17 | PAL Processor Self Test Procedures                                   | 2:287 |

| 11-18 | PAL Support Procedures                                               | 2:288 |

| 11-19 | State Requirements for PSR                                           | 2:289 |

| 11-20 | Definition of Terms                                                  | 2:290 |

| 11-21 | System Register Conventions                                          |       |

| 11-22 | General Registers – Static Calling Convention                        | 2:292 |

| 11-23 | General Registers – Stacked Calling Conventions                      |       |

| 11-24 | Application Register Conventions                                     |       |

| 11-25 | Processor Bus Features                                               |       |

| 11-26 | cache_type Encoding                                                  | 2:298 |

| 11-27 | Cache Line State when inv = 0                                        |       |

| 11-28 | Cache Line State when inv = 1                                        |       |

| 11-29 | Cache Memory Attributes                                              | 2:303 |

| 11-30 | Cache Store Hints                                                    |       |

| 11-31 | Cache Load Hints                                                     | 2:303 |

| 11-32 | PAL_CACHE_INIT level Argument Values                                 |       |

| 11-33 | PAL_CACHE_INIT restrict Argument Values                              | 2:305 |

| 11-34 | IA-32 System Environment Entry Parameters                            |       |

| 11-35 | MP Information Table                                                 | 2:322 |

| 11-36 | SAL I/O Intercept Table                                              | 2:323 |

| 11-37 | IA-32 Resources at IA-32 System Environment Entry                    |       |

| 11-38 | Register Values at IA-32 System Environment Termination              |       |

| 11-39 | I/O Detail Pointer Description                                       |       |

| 11-40 | I/O Type Definition                                                  | 2:331 |

| 11-41 | I/O Size Definition                                                  | 2:331 |

| 11-42 | Pending Return Parameter Fields                                      | 2:338 |

| 11-43 | info_index Values                                                    |       |

| 11-44 | level_index Fields                                                   | 2:343 |

| 11-45 | err_type_index Values                                                |       |

| 11-46 | error_info Return Format when info_index = 2 and err_type_index = 0  |       |

| 11-47 | Cache_Check Fields                                                   |       |

| 11-48 | TLB_Check Fields                                                     |       |

| 11-49 | Bus Check Fields                                                     |       |

| 11-50 | Reg_File_Check Fields                                                |       |

| 11-51 | uarch check Fields                                                   |       |

| 11-52 | PM_info Fields                                                       |       |

| 11-53 | PM_buffer Layout                                                     | 2:355 |

### الint

| 11-54    | Processor Features                                                             | 2:360 |

|----------|--------------------------------------------------------------------------------|-------|

| 11-55    | info_request Return Value                                                      | 2:364 |

| 11-56    | RSE Hints Implemented                                                          |       |

| Part II: | System Programmer's Guide                                                      |       |

| 2-1      | Intel® Itanium® Architecture Provides a Relaxed Ordering Model                 | 2:386 |

| 2-2      | Acquire and Release Semantics Order Intel® Itanium® Memory Operations          |       |

| 2-3      | Loads May Pass Stores to Different Locations                                   |       |

| 2-4      | Loads May Not Pass Stores in the Presence of a Memory Fence                    |       |