|                                                                                   |                                                            | •           |                                           |

|-----------------------------------------------------------------------------------|------------------------------------------------------------|-------------|-------------------------------------------|

| ii nn <sub>n</sub> nn<br>ii nn nn<br>ii nn nn<br>ii nn nn<br>ii nn nn<br>ii nn nn | ntt eeee 11                                                | INTERNAL    | CORRESPONDENCE                            |

|                                                                                   |                                                            | · · · · ·   |                                           |

| To:                                                                               | John Bayliss<br>Dave Best<br>Dick Kaiser<br>Barb Slaughter |             | Date: 20 November 1980                    |

| From:                                                                             | Jim Weldon                                                 |             |                                           |

|                                                                                   |                                                            | <b>.cc:</b> | Brad Janeway<br>Paul Tyner<br>John Wipfli |

Subject: Technical Review of iAPX 432 Component User's Guide

The preliminary manual is now scheduled to go to print in early December, 1980, leaving very few working days to complete the manual, which will consist of about 80 pages including a preface, 5 chapters, and 2 component data sheets covering the GDP and IP.

Technical Review of this material must be accomplished by increments, with all input to be received not later than December 2, 1980, if we are to stay on schedule. If your comments are going to be of sweeping portent, we must commence receiving them at once to avoid reworking typeset material, which could result in slippage of schedule.

Please send your comments to:

Steven Andersen or Jim Weldon Marketing/Communications 210 California Avenue, Suite L Palo Alto, CA 94306 - telephone (415) 328-2160

or call: Steve Andersen - (408) 377-6881

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

BXP CREDIT i ICE iCS im Insite Intel intel Intelevision intellec iRMX iSBC iSBX Library Manager MCS Megachassis Micromap Multibus Multimodule PROMPT Promware RMX/80 System 2000 UPI µScope

and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or RMX and a numerical suffix.

#### LIST OF ILLUSTRATIONS

Chapter 1. Introduction to the iAPX Component User's Guide Figure 1-1 An iAPX 432 System 1-2 432 I/O Model Chapter 2. Introduction to iAPX GDP Architecture Figure 2-1 Operations Defined on a Data Type 2-2 Some operations Defined on Character and Integer 2-3 Operations Defined 2-4 Different Access Paths and Rights to the Same Object 2-5 Network of Objects as an Object 2-6 Access Segment Symbology Chapter 3. Introduction to the iAPX IP Architecture Figure 3-1 Main System and Peripheral Subsystem 3-2 Basic I/O Service Cycle 3-3 Peripheral Subsystem Interface 3-4 Peripheral Subsystem Hardware Interface 3-5 Interface Processor Window Chapter 4. iAPX Processor Environment Definition Figure 4-1 Basic iAPX Data Lengths 4-2 Hardware Error Detection 4-3 State Diagram for Processor Packetbus 4-4 Nominal Write Cycle Timing 4-5 Stretched Write Cycle Timing Minimum Write Cycle Timing 4-6 4-7 Minimum Read Cycle (Buffered System) 4-8 Minimum Read Cycle (Not Buffered) 4-9 Minimum Faulted Access Cycle

Chapter 5. An iAPX 432 Multiprocessor System Implementation

Figure

5-1 Block Diagram (Two Processor 432 System)

5-2 Physical Partitioning (Two Processor 432 system)

5-3 Address/Specification Demultiplexing

5-4 Local Access Operation

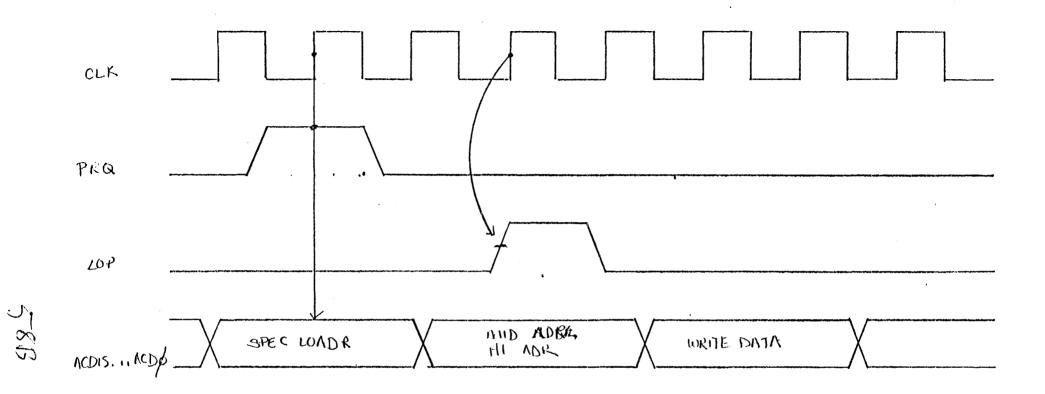

5-5 Cancelled Access Detection

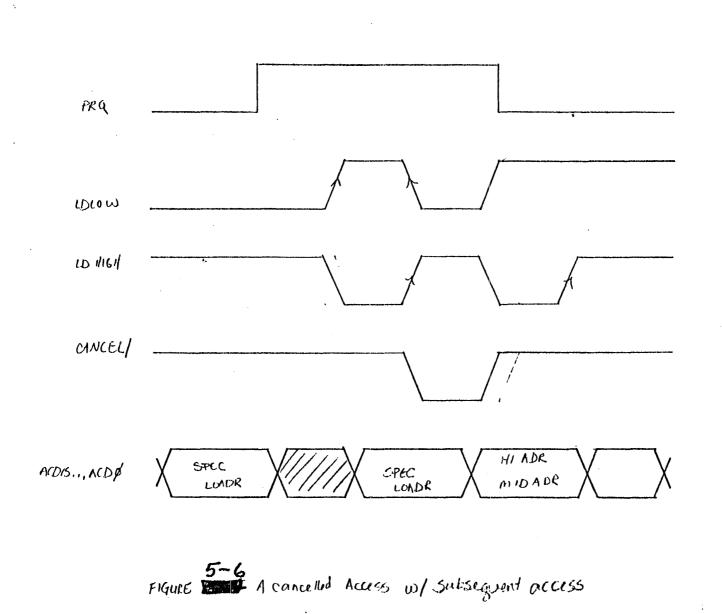

5-6 Cancelled Access (With Subsequent Access)

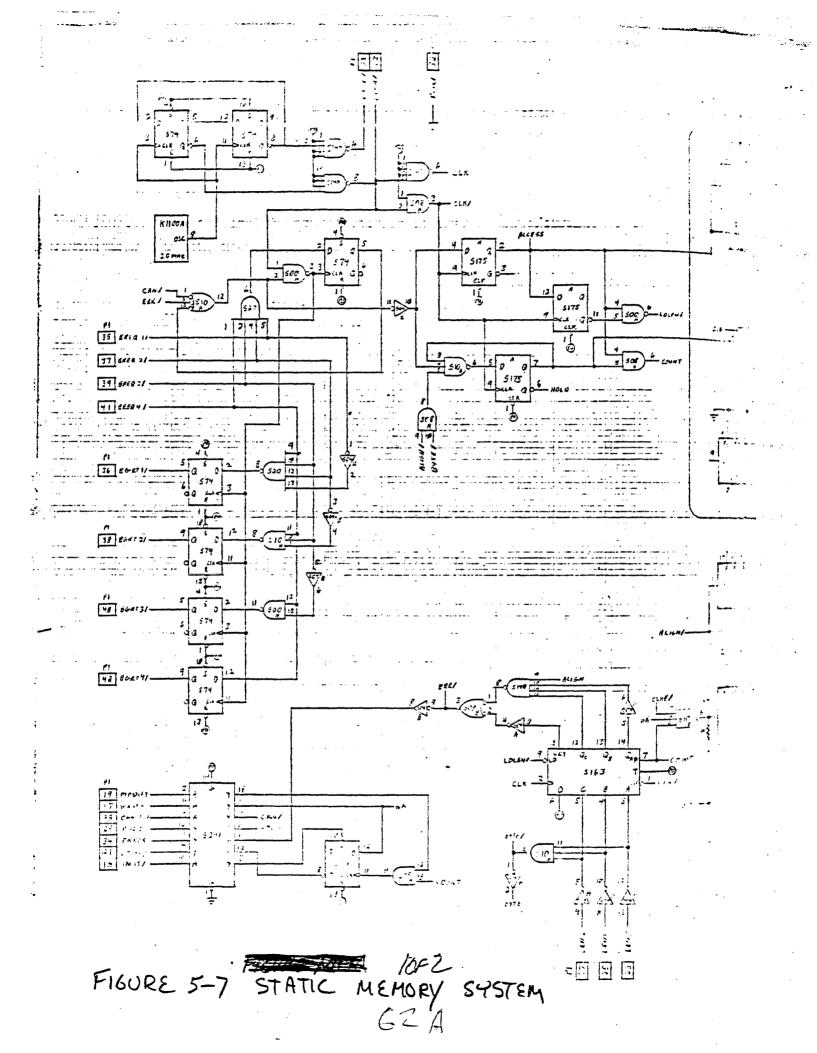

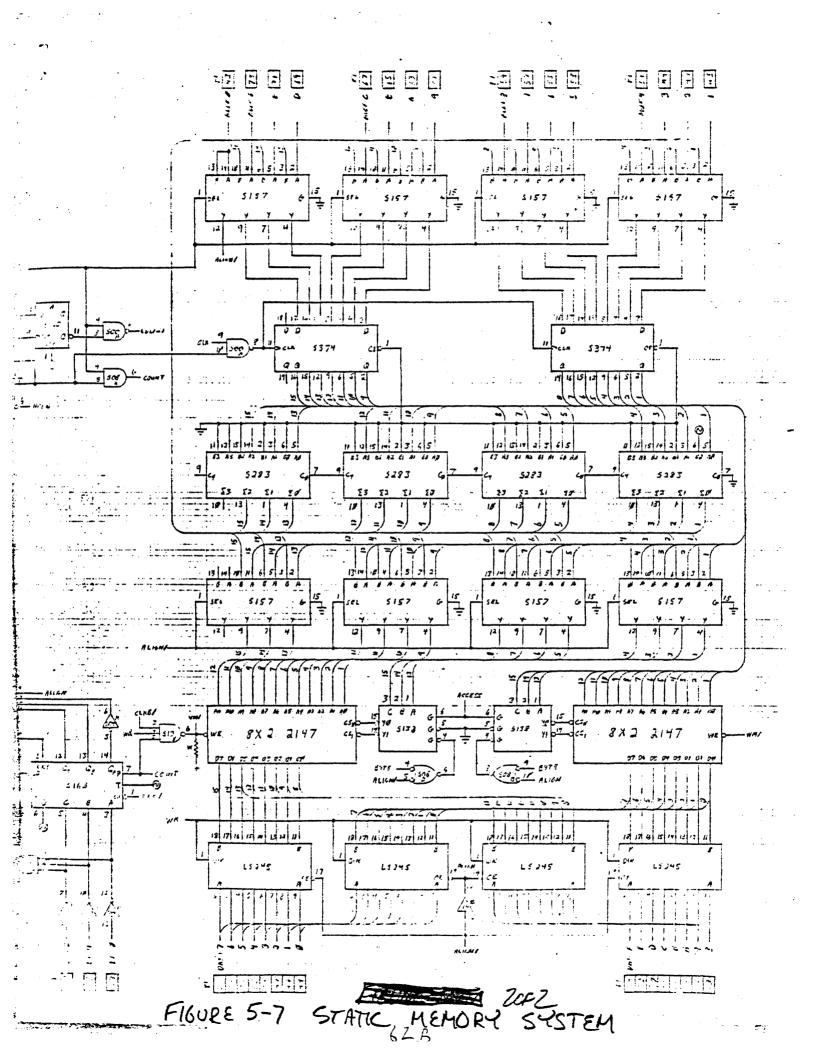

5-7 Static Memory System

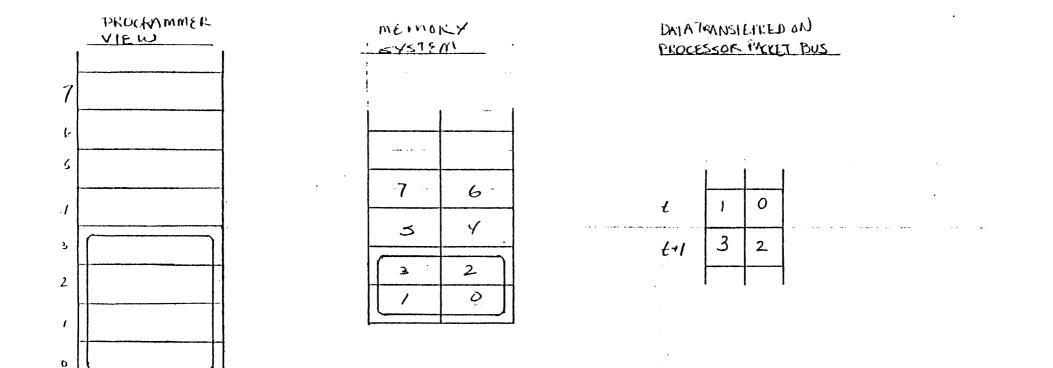

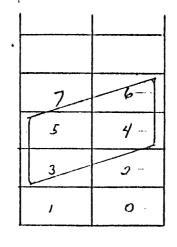

5-8 Byte Swapping for 32-bit Operand

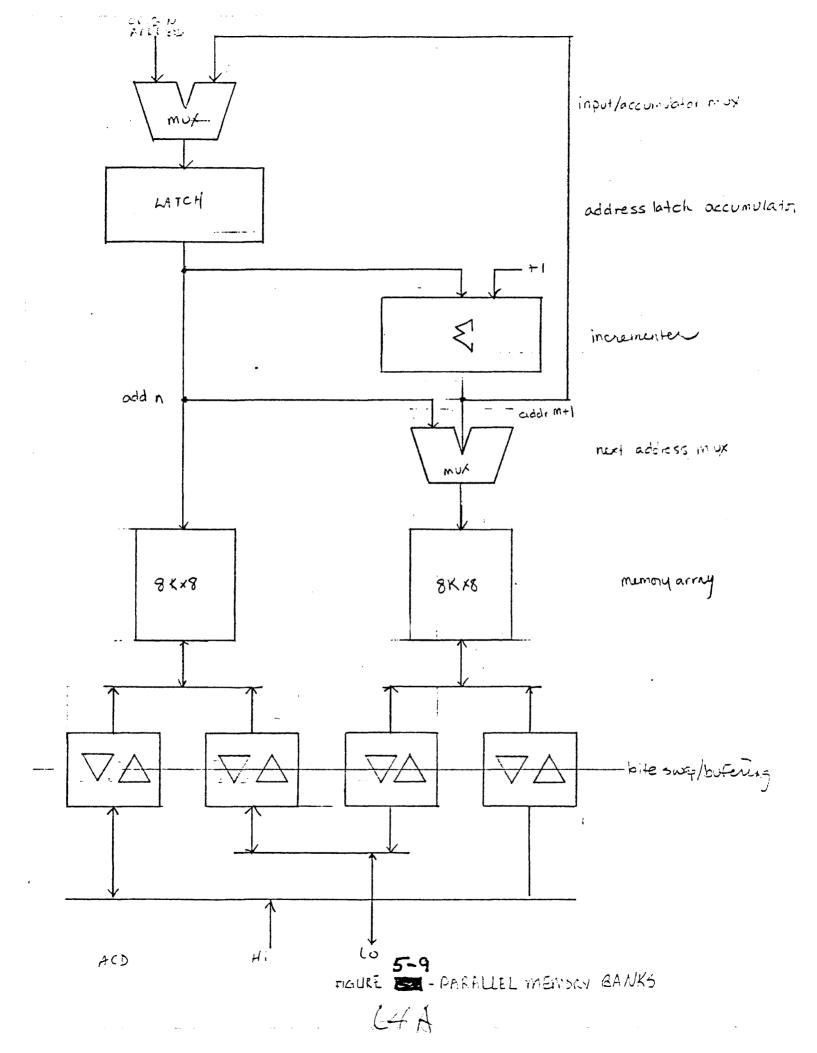

5-9 Parallel Memory Banks

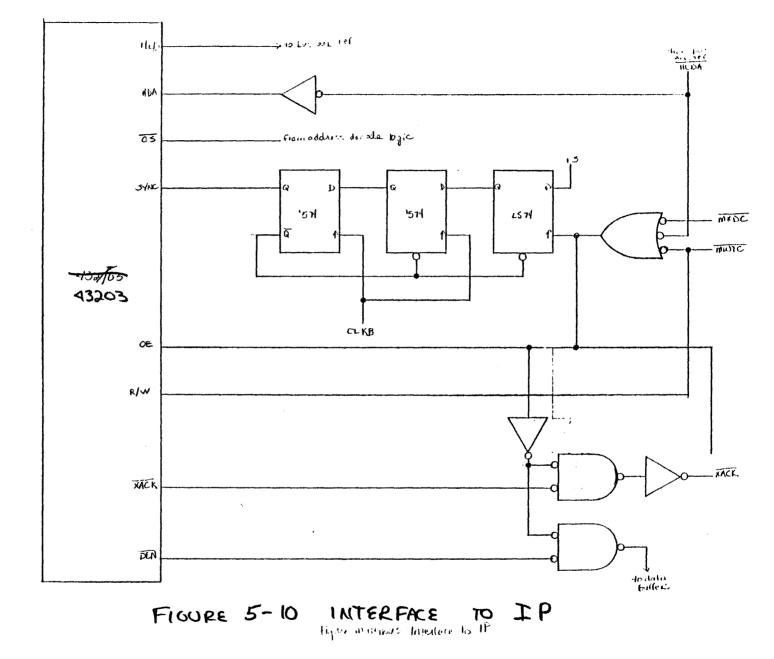

5-10 Interface to IP

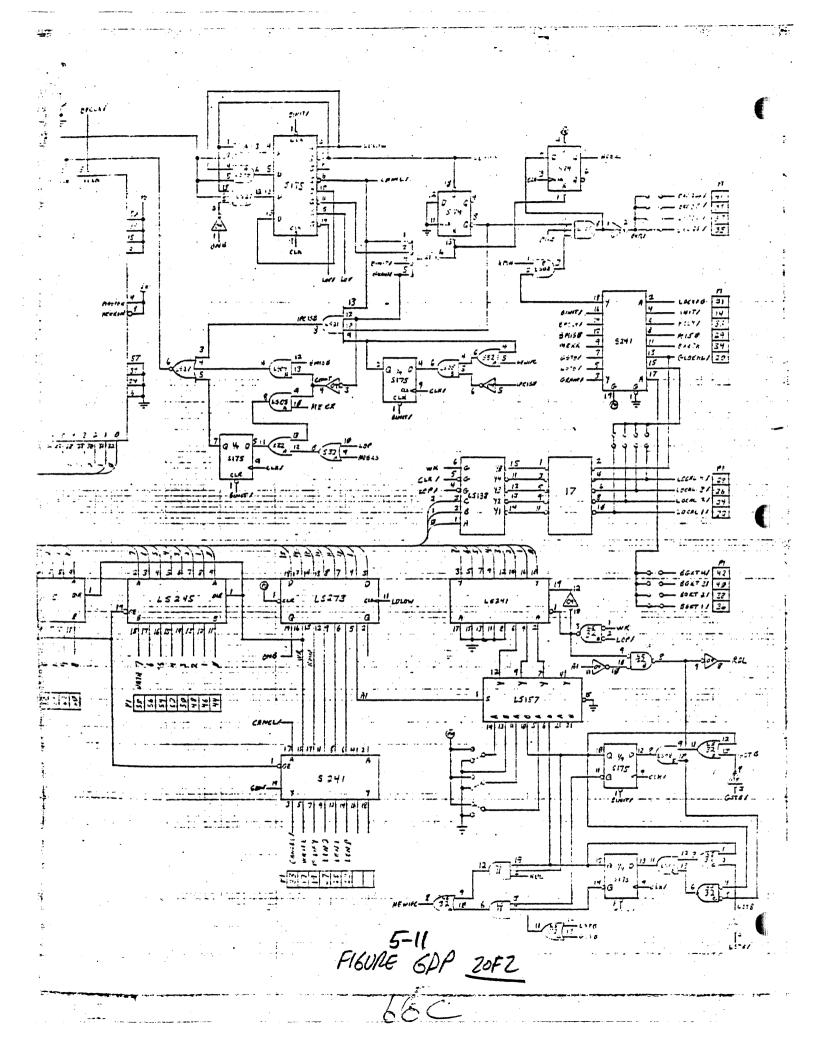

5-11 GDP Schematics

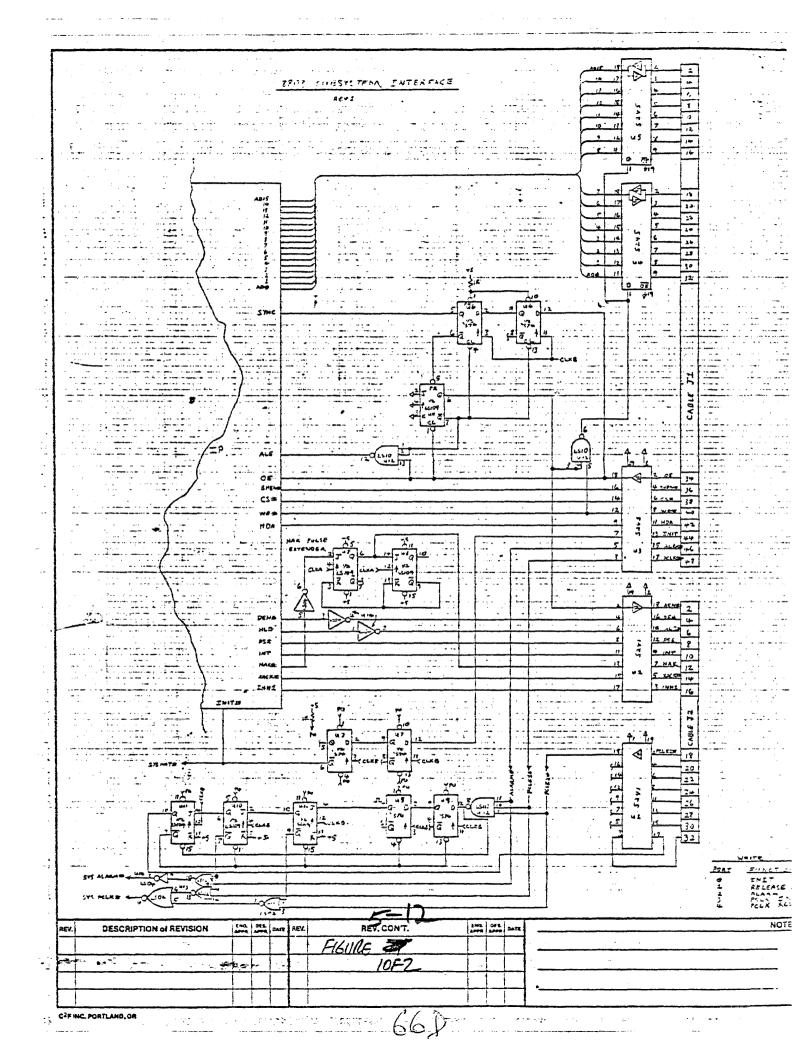

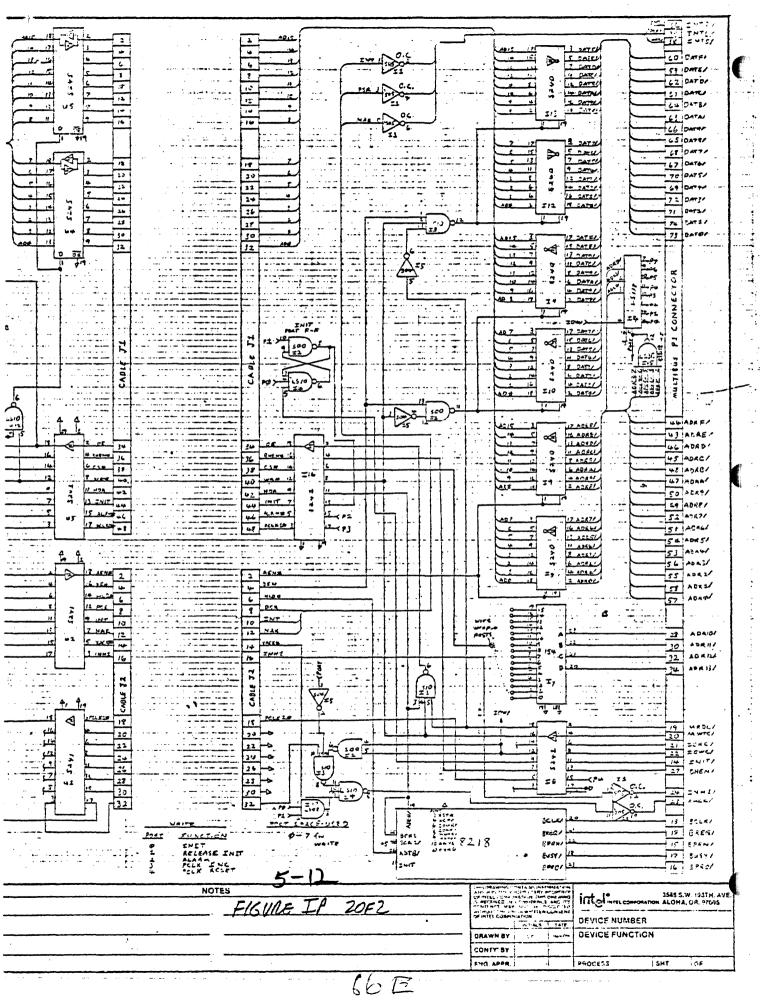

5-12 IP Schematics

## APPENDIX

iAPX 43201/43202 GDP Data Sheets

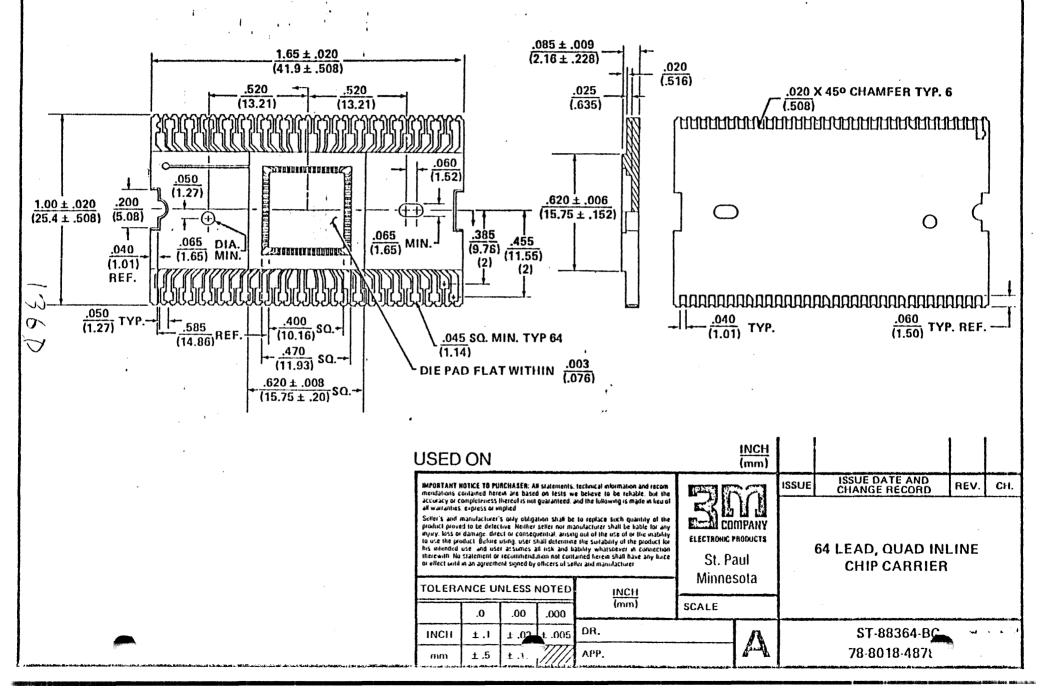

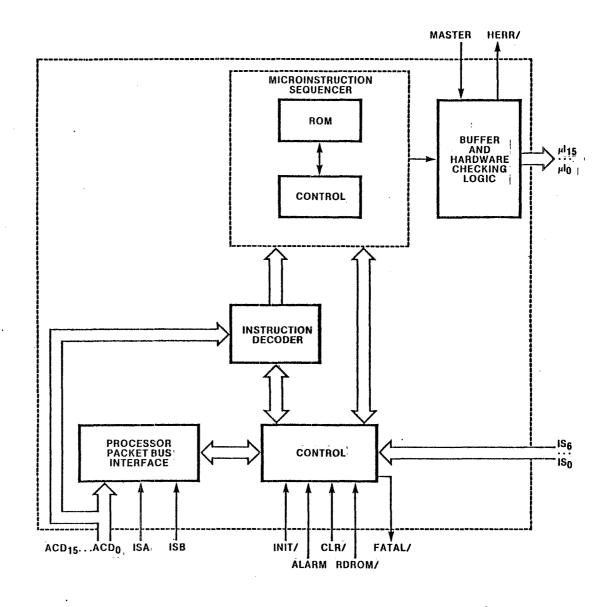

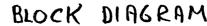

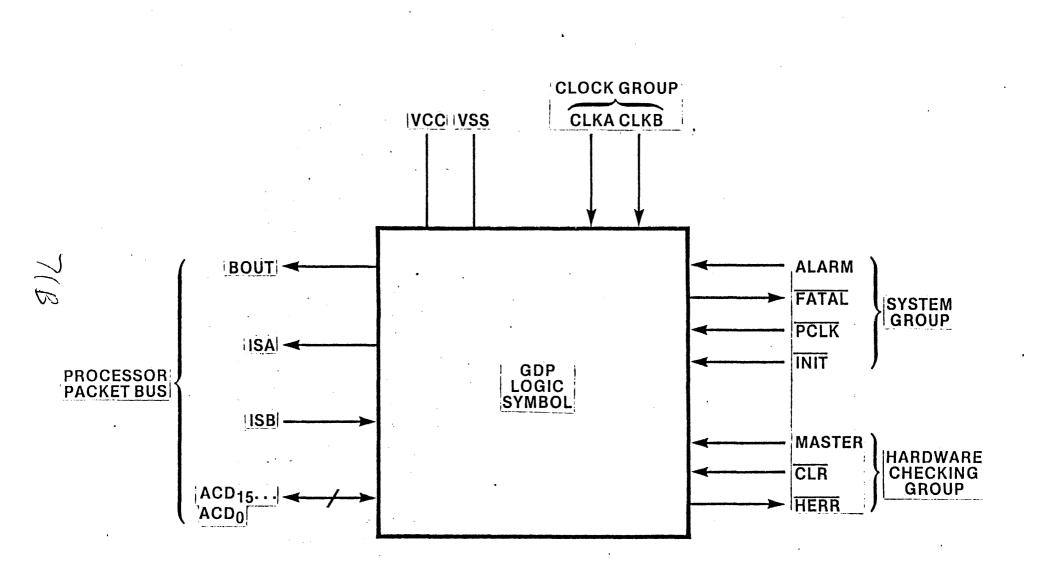

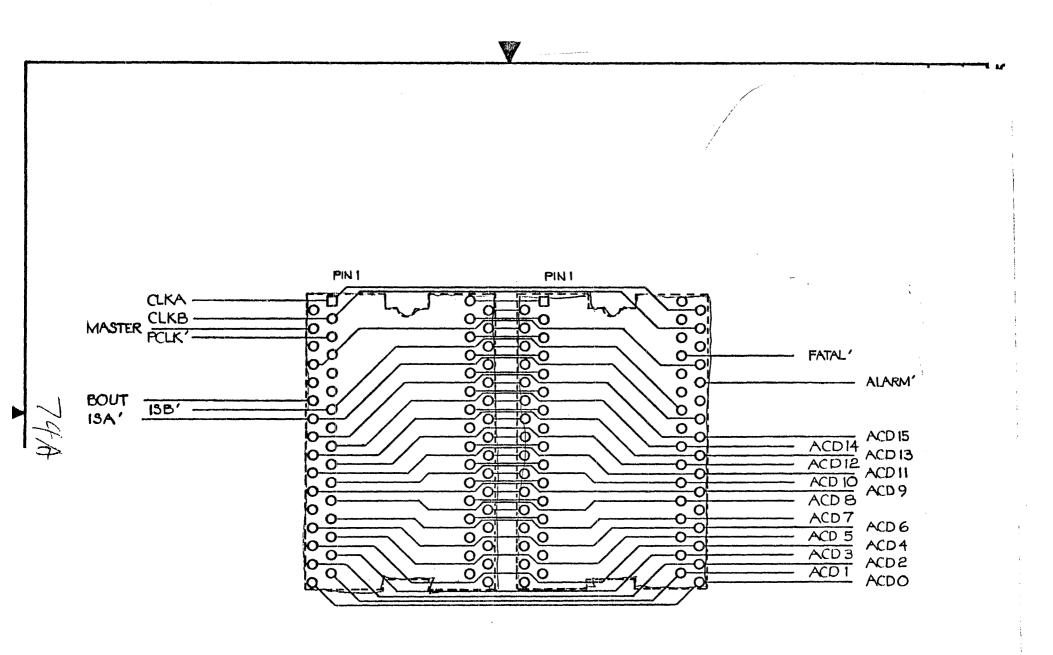

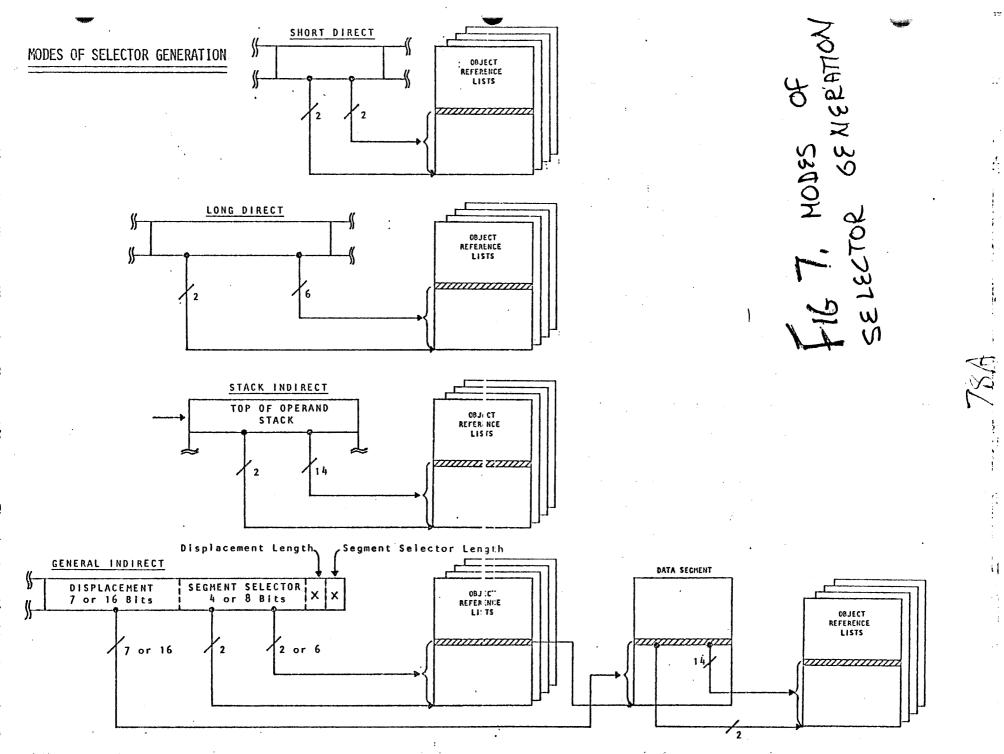

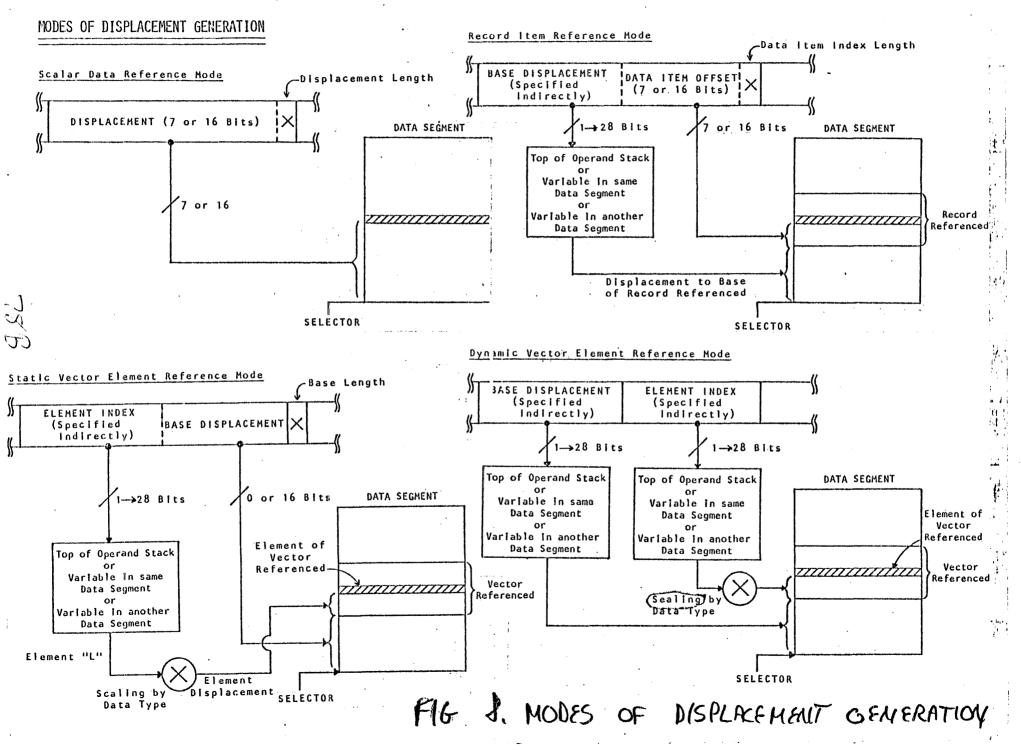

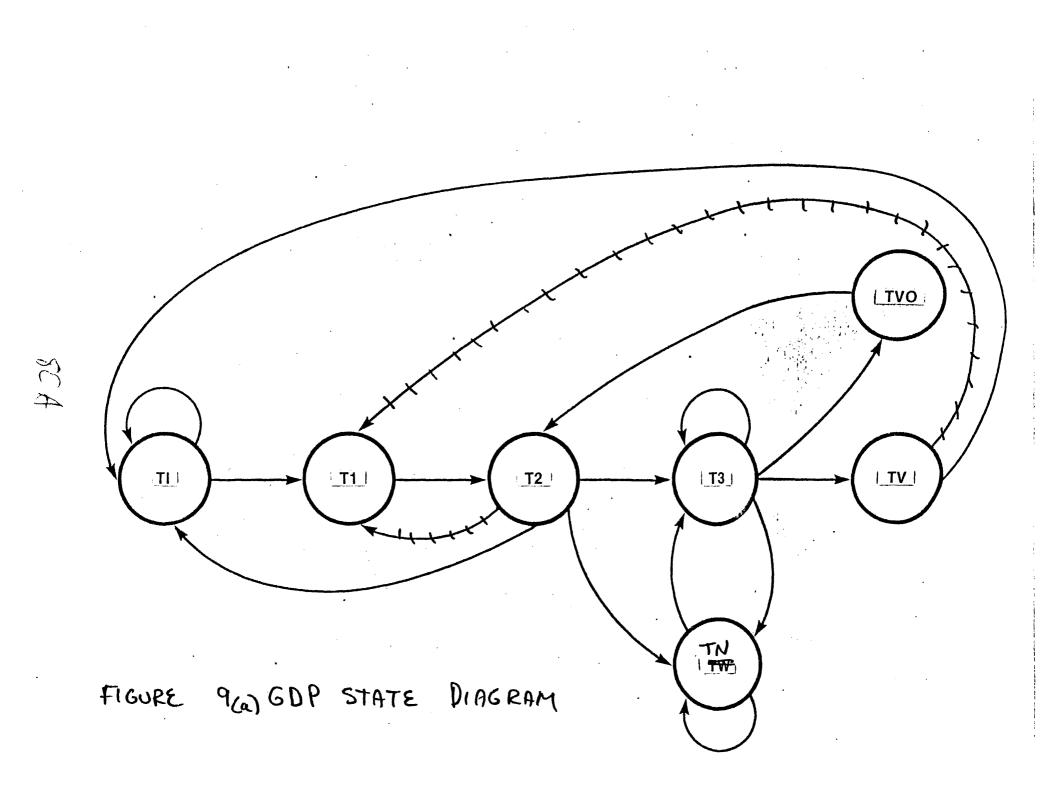

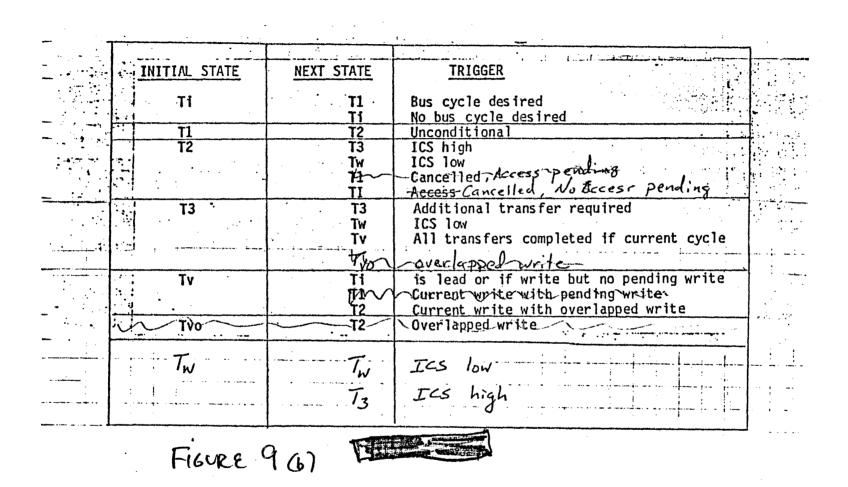

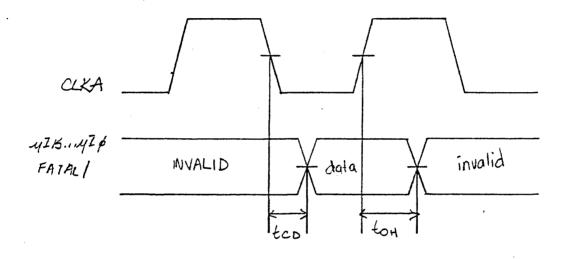

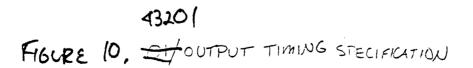

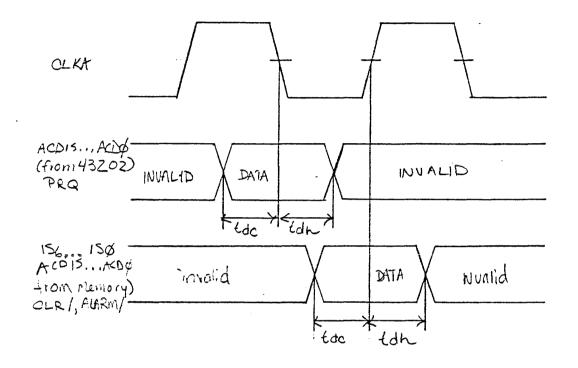

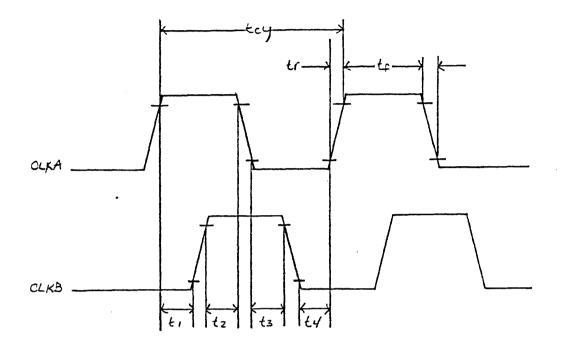

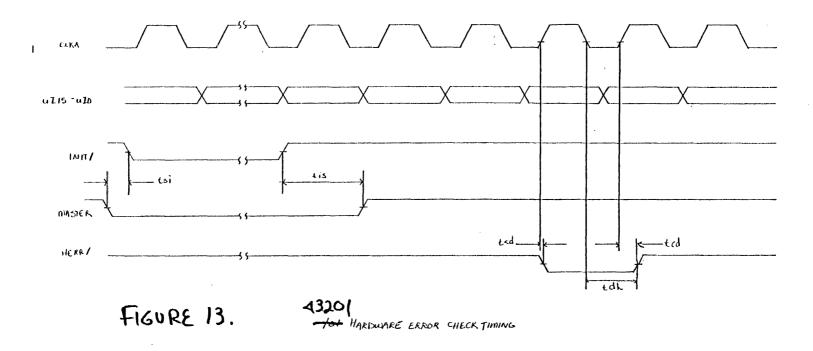

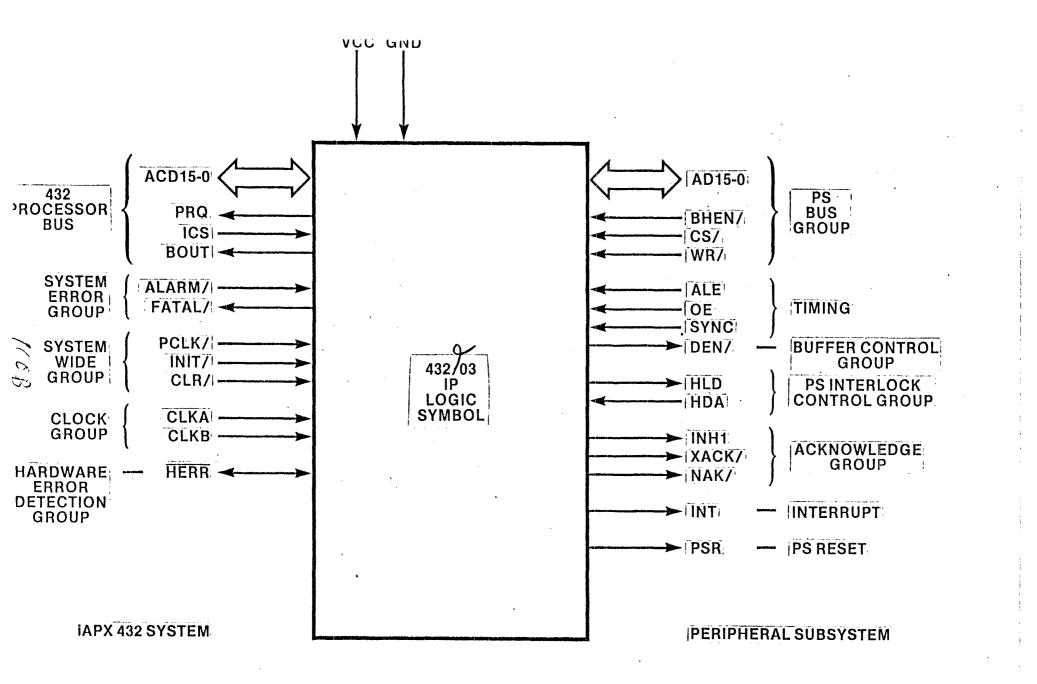

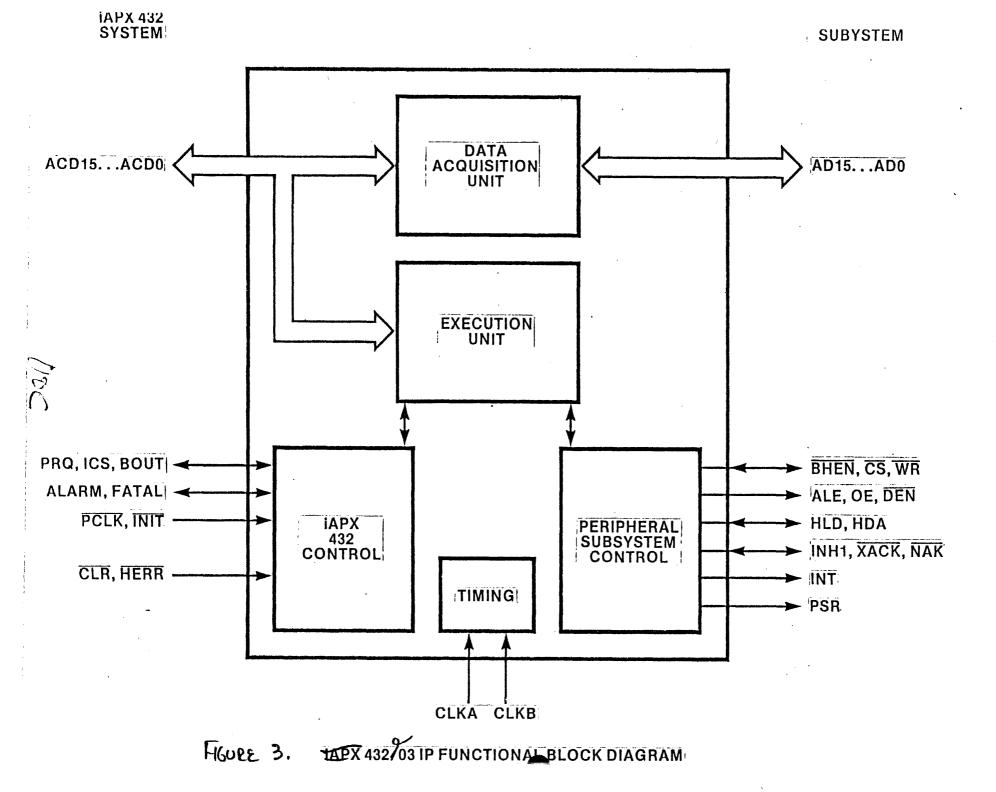

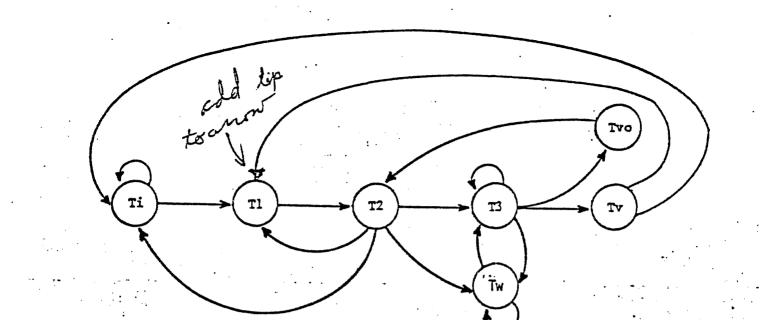

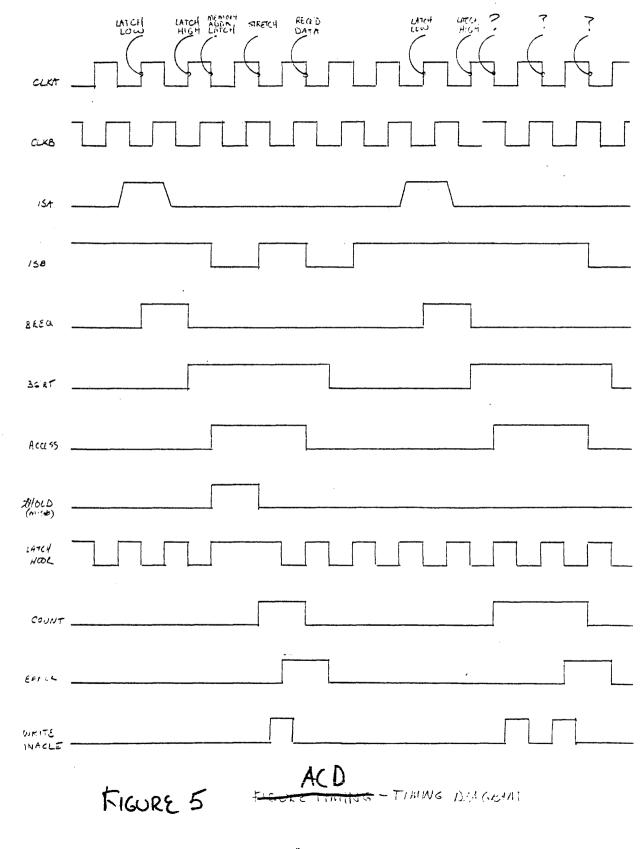

Figure 1. 43201 Pin Assignment 43202 Pin Assignment 2. 3. 43201 Block Diagram 4a. 43202 Block Diagram 4b. GDP Logic Symbol 5. Hardware Error Detection 6. QUIP Layout 7. Modes of Selector Generation 8. Modes of Displacement Generation. 9. GDP Packetbus State Diagram 10. 43201 Output Timing Specification 11. 43201 Input Timing Specification 12. Clock Input Specification 13. 43201 Hardware Error Checking Timing 14. 43201 Initialization Timing 15. 43201 Interrogation Timing 16. 43202 Output Timing Specification 17. 43202 Input Timing Specification iAPX 43203 IP Data Sheets Figure

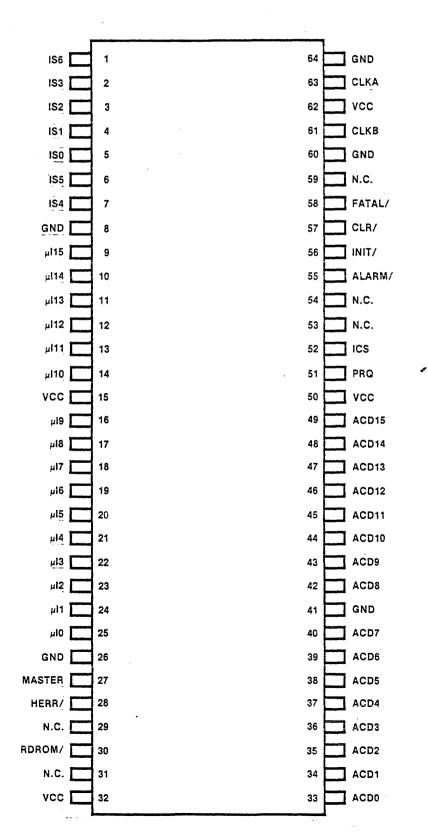

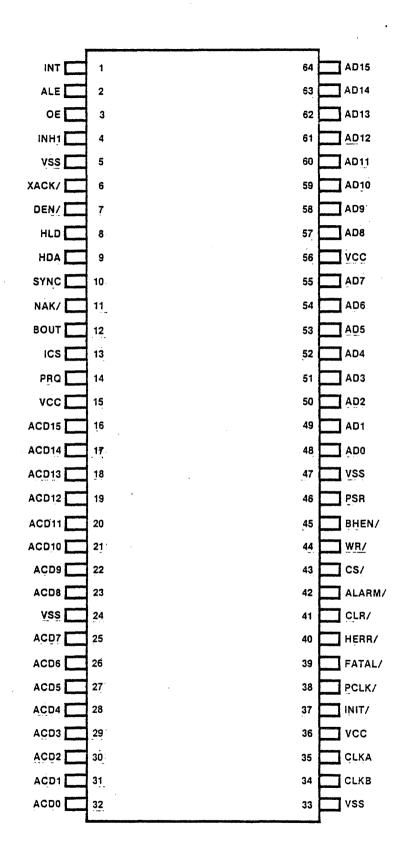

43203 Pinout

43203 Logic Symbol

43203 Functional Block Diagram

43203 Bus State Diagram

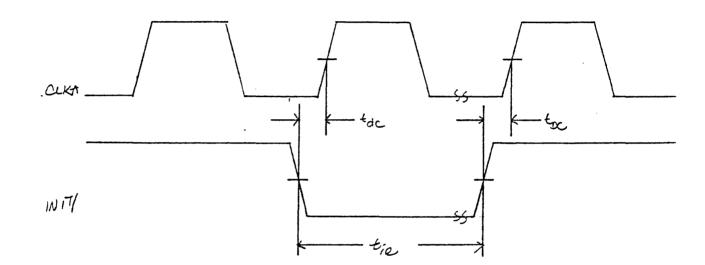

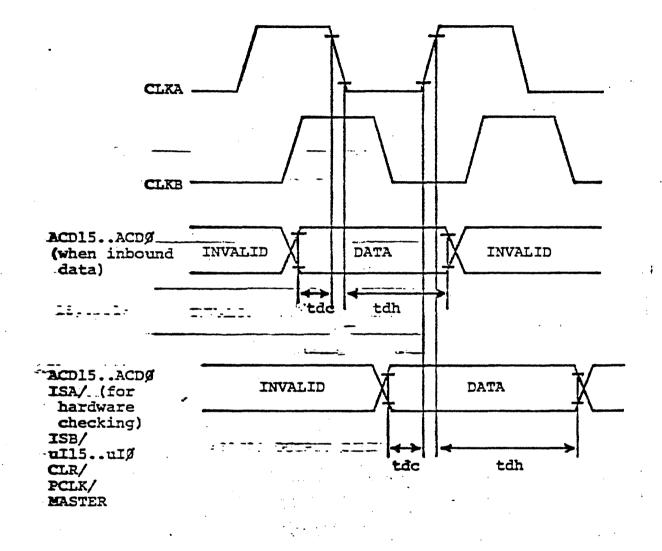

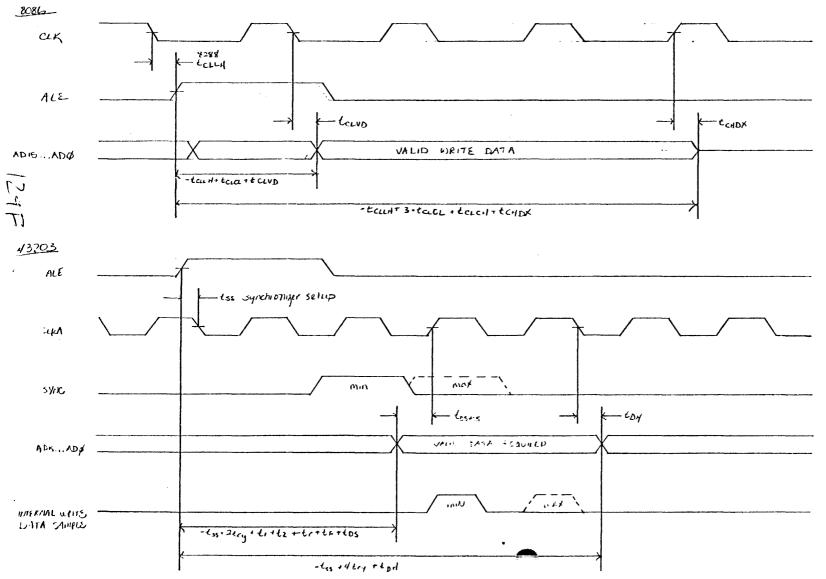

Timing Diagram for ACD Parameters

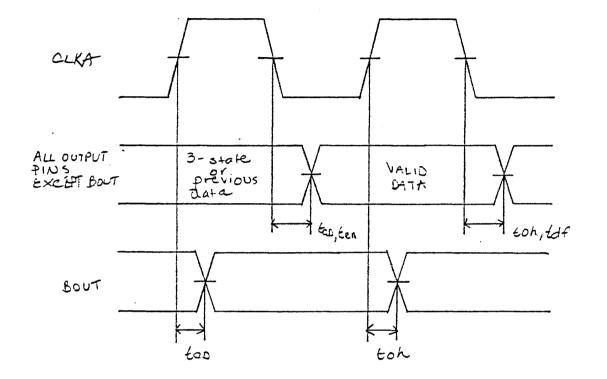

Timing Diagram for Local Processor Bus Timing

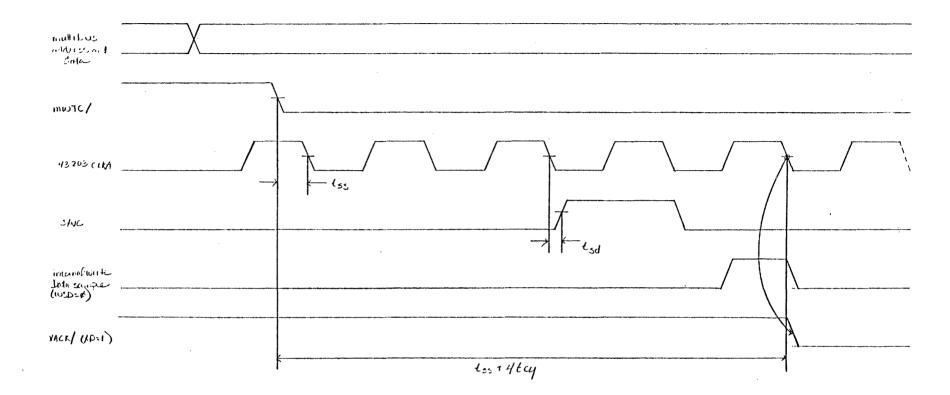

Multibus Interface Timing

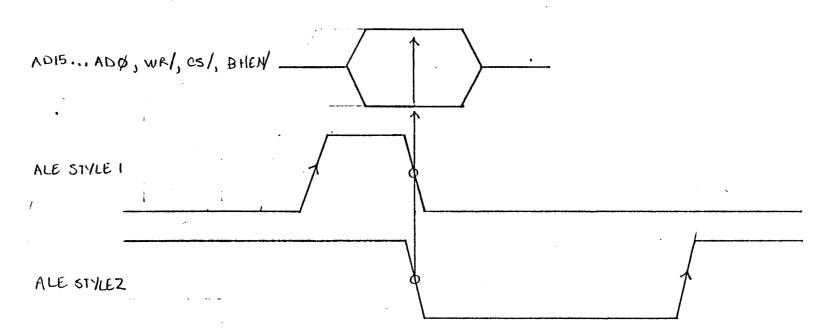

Two Styles of ALE

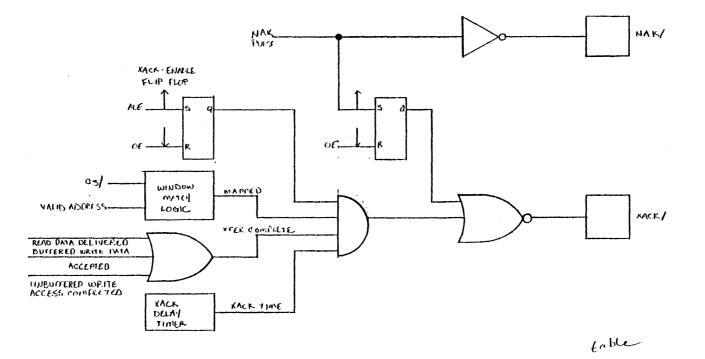

XACK Interface Programmable Timing

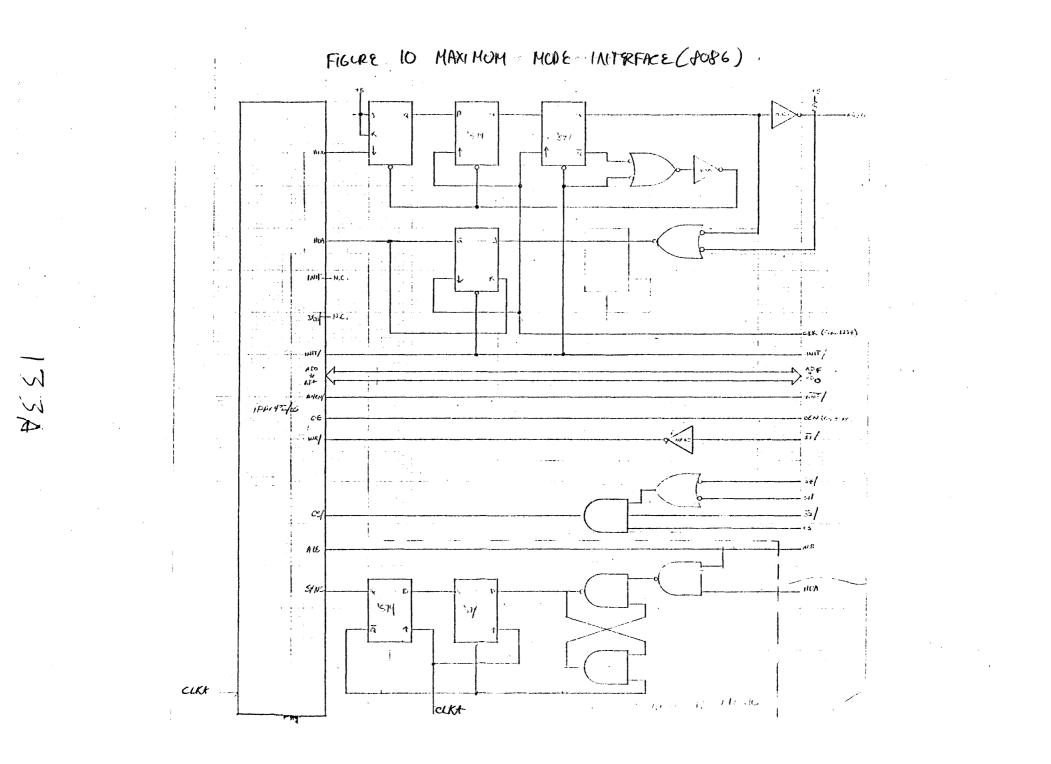

Maximum Mode Interface

MULTIBUS System Interface

## LIST OF TABLES

Chapter 4. 432 Processor Environment Definition

Table

- 4-1 ACD Specification Encoding

- 4-2 ICS Interpretation

- 4-3 PRQ Interpretation

- 4-4 BOUT Interpretation

- 4-5 iAPX 432 Component Signalling Scheme

Chapter 5.An iAPX 432 Multiprocessor System Implementation

Table

5-1 Miscellaneous Pin Connection

5-2 IPC Register Bit Designation

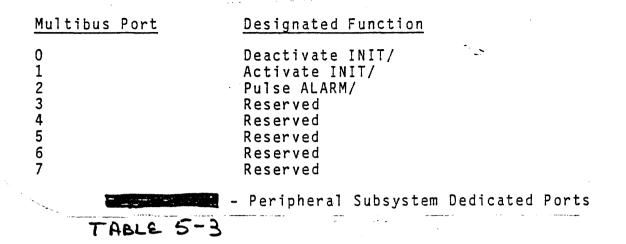

5-3 Peripheral Subsystem Dedicated Ports

#### APPENDIX

18

iAPX 43201/43202 GDP Data Sheets

Table

- 1. GDP Operator Instruction Set

- 2. 43201 DC Characteristics

- 3. 43201 AC Characteristics

- 4. 43201 Capacitance Ratings

- 5. 43202 DC Characteristics

- 6. 43202 AC Characteristics

- 7. 43202 Capacitance Ratings

- 8. GDP Absolute Maximum Ratings

iAPX 43203 IP Data Sheet

Table

- 1. 43203 Interface Pin Summary

- 2. Packetbus signals

- 3. IP Absolute Maximum Ratings

- 4. DC Characteristics

- 5. AC Characteristics

- 6. XACK Timing Parameters

- 7. 8-bit Processor Interface

- 8. 16-bit Processor Interface

- 9. Maximum Mode 8086 System

# iAPX 432 COMPONENT USER'S GUIDE

## CHAPTER 1

## INTRODUCTION

Welcome to Intel's new iAPX 432 family of components. The 432 product line was designed to solve the [existing; growing?] industrial problem of software development. Today's state-of-the-art technology has produced large-scale microprocessors capable of handling tremendous hardware tasks, but has failed to relieve the ever-growing needs of software design. Complex devices, conceptually designed to control this problem have in the end only added more weight to the burden.

## WHAT IS THE PROBLEM?

Today's system applications have evolved into highly complex configurations. Retail business systems, telephone switching systems, laboratory and industrial control systems, communication systems, word processors, and many other large-scale systems have forced the industry to consider alternative

l

methods of handling the extensive requirements of multiple programs, multiple users, and multiple processors. The demands of existing high-level languages, operating system software, and the increased number of peripheral controllers and memory options have produced overwhelming problems for the system designer.

To further compound the problem, tommorrow's applications will increase system complexity by requiring fault-tolerant computing, transparent multiprocessing, distributed operation, networking, and multiple families of programming languages. These system requirements are beyond the scope of today's mini- and mainframe computers. This Component User's Guide presents a hardware discussion of the two components, the 43201 and 43202, that combine to form the General Data Processor (GDP), and the 43203 Interface Processor (IP). Also included in this book are instructions concerning the hardware implementation of the iAPX 432 system concepts. References to additional source documents are given as needed.

## WHAT IS THE SOLUTION?

As you become familiar with the iAPX 432 family members, you will discover an innovative approach to the software development problem. It is not enough to say the 432 family processors have an enhanced architecture with the integra-

tion of over 100,000 silicon gates into 64-pin packages, nor is it enough to promise an increased throughput. What must be understood is that all phases of hardware and software design will be oriented toward safe and efficient control of information with favorable results in development costs.

The solution to complex and growing software demands is the development of the object-oriented machine. Such a machine can provide the important qualities of abstraction and decomposition. Abstraction is one of the inherent qualities of the iAPX432 family, which hides the irrelevant detail of predefined high-level languages, e.g., different number and data types. Decomposition is the quality of breaking up complex problems into manageable units and allows for modular programming. The iAPX 432 hardware provides an architectural structure that defines access limitations to prevent the damage of any established data base. The software designer need only be concerned with the construction of individual, easy-to-understand program modules that are more manageable and capable of working together as a system unit. Refer to Chapter 2 for a discussion of 432 Architecture and its importance to the hardware designer.

HOW IS IT DONE?

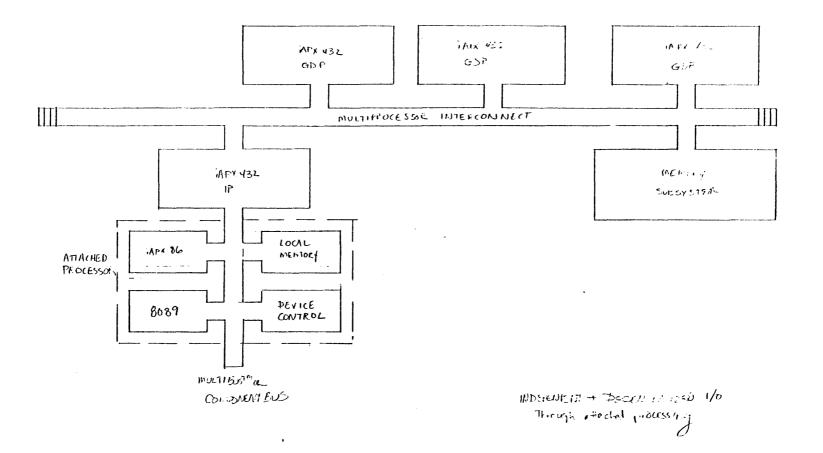

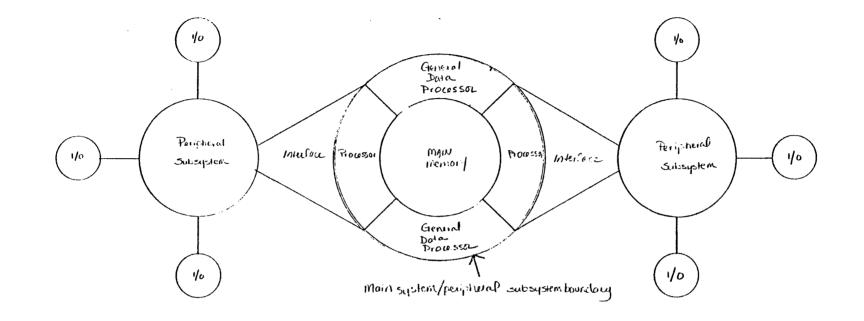

A basic iAPX 432 system consists of one or more Intel

general data processors (GDP's), one or more interface processors (IP's), several independant I/O systems, and a common memory system. Each external I/O system may consist of several I/O devices and microprocessors that may be capable of providing their own complex arbitration schemes, memory interleaving, and dynamic memory configuration. These external processors view memory as a single and continuous byte-addressable sequence, and are not aware of any system interconnection (although that capability does exist). Figure 1-1 illustrates a basic 432 system.

Figure 1-1 432 System Block Diagram

Programs executing in iAPX 432 processors view the memory and the interconnect address spaces quite differently from their attached processors. Programs are hardware-defined as processes, which are controlled by access descriptors; i.e., each process is limited to specific objects that may only be accessed if predefined conditions have been met. After verifying access rights, the hardware automatically computes physical addresses as they are required. The external processors define processes; the interface processor provides access to general data processors and memory resources to run those processes.

432

iapx

4n

Ч Н

Figure

Processor management methodology becomes more important as more subsystems are added. In the iAPX 432 system, processes are scheduled to be executed according to policies, implemented in software, that determine how processes are to share processors. As each process becomes available, i.e., reaches the head of its queue, it is dispatched to the next available processor that can execute the process. Conversely, an idle processer will wait at a dispatching port for a process to appear. Therefore, systems may become as complex as the mind can imagine. Software Engineers are now pleased to discover that the need to develop or redesign new software to handle the complexity of increasing system requirements does not exist! Hardware engineers are pleased to save valuable design effort in increasing the hardware capabilities by simply plugging additional GDP or IP units into their printed circuit boards. Chapters 5 and 6 provide a detailed discussion of the GDP and the IP and their respective roles in implementing these concepts.

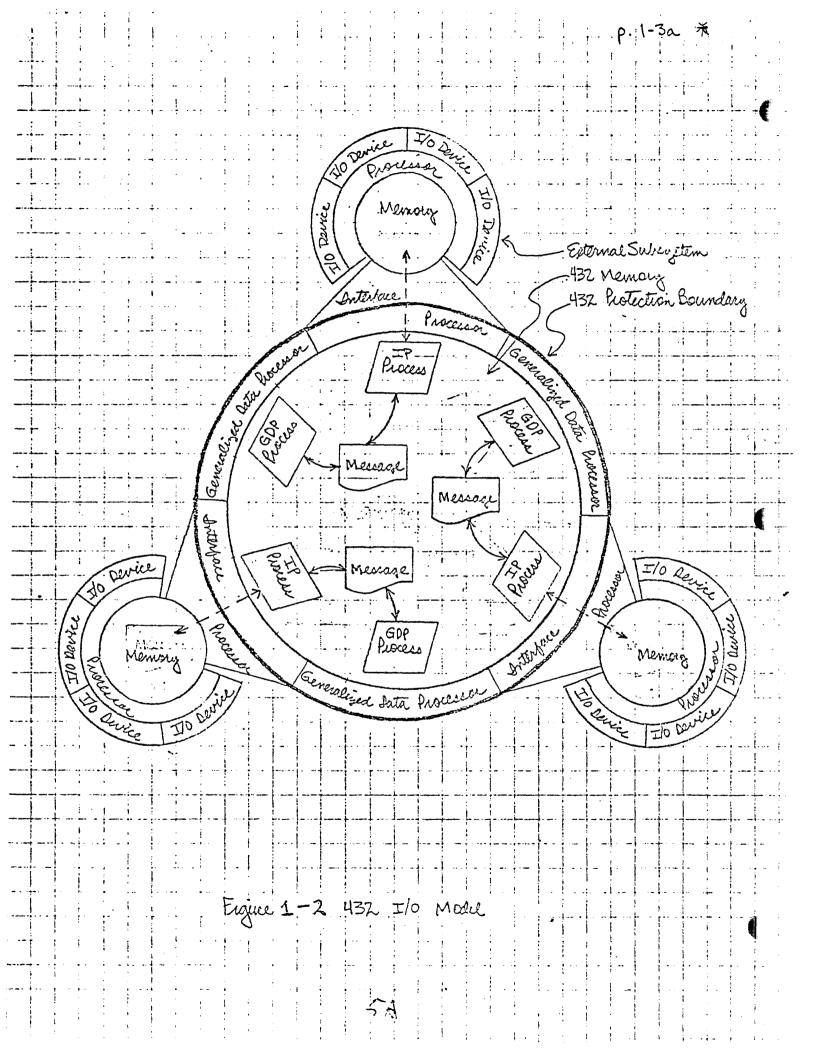

Figure 1-2 represents an iAPX 432 system model complete with three GDP processors (43201 and 43202), three IP processors (43203), and three I/O subsystems. If the external processors were identical, it would be conceivable to use only one IP and several GDP's. The figure illustrates the ease with which information is allocated to available processors. Also shown is the independance of each subsystem as separate tasks are defined without the need for under-

standing tasks for other subsystems. Refer to Chapter 4 for an actual 432 system configuration.

## OBJECT-ORIENTED MACHINE

An object is a data structure that contains information in an organized manner. An object-oriented machine, such as the iAPX 432, is a device that handles data in terms of objects rather than the specific elements within the object. Certain primitive data types (Reals, Integers, Ordinals, etc.) each have a specific structure that may vary from one type to the next. A given binary number might represent a different meaning to each of these data types. In the iAPX 432 architecture, these data structures may be found in a contiguous set of memory locations or possibly a combination of several segments.

A 432 object not only contains organized information but also a basic set of operations defined to directly manipulate the data structure. The 432 hardware inherently ensures manipulation of the data structure by these specific operations only. In this manner, violations to the data structure are prevented. Also, each object can be referenced as one thing; i.e., there is no need to address any of the parts. Therefore, each object has a label to identify it from among the various types.

Notice that objects are manipulated not only by the hardware. Some objects are manipulated by a combination of hardware and software, and some only by software. Frequently used operations have been placed in the 432 structure (hardware implemented) while less frequent operations have been left to the software. Refer to Chapter 2 for a discussion of the following objects: Processor objects, Process objects, Context objects, Instruction objects, and data objects. The coordination of these objects represents the completed picture of the 432 system.

## A FINAL NOTE

The Intel iAPX 432 family of components has been designed specifically to provide a solution to the growing software needs of the 80's. The 432 system should be viewed as a time-saving system, a cost-saving system, and a system to solve design development problems. Welcome to the Object-Oriented world of Intel's iAPX 432 family.

#### CHAPTER 2

## INTRODUCTION TO iAPX 432 ARCHITECTURE

The purpose of this chapter is to familiarize the iAPX 432 hardware designer with the basic object-oriented concepts provided by the 432 system. A solid understanding of the following concepts is essential to the construction of 432 systems (Refer to the iAPX 432 General Data Processor Architectural manual, Order no. 171860, and the iAPX 432 Interface Processor Architectural manual, Order No.171862, for more detailed information on these concepts).

The iAPX 432 system is an object-oriented, capability-based architecture that supports software-transparent multiprocessing and adaptive virtual memory. By including operatingsystem and high-level language functions in hardware, it provides mainframe functionality and performance in a VLSI microcomputer form factor. I/O processing is fully independent and decentralized, allowing other iAPX processors (e.g., 86, 186) to perform I/O as attached processors. The IEEE floating point standard is fully supported in hardware.

The iAPX 432 combines VLSI technology with an architectural

and software design methodology to produce a new computer architecture that will significantly reduce the cost of large-scale software systems and enhance their reliability and security.

Several key concepts are fundamental to an understanding of the iAPX 432 architecture. They are:

- Objects -- data structures having known types that can be either system- or user-defined; moreover, objects are acted upon by a restricted set of operations, which can be individual machine instructions, software package, or hidden hardware functions. In the 432, objects are represented by segments, subsets of segments called refinements, or arbitrarily complex networks of segments and/or refinements.

- Access descriptors -- sometimes called "object references" or "capabilities," these are how objects refer to one another. Each object confers upon its holder access to an object, along with certain rights associated with the object, for instance, read/write or send/receive.

- Segments -- segments form the basis for the physical representation of objects. Each segment is a contiguous block (that is, no gaps) of address space, up to 64K (65,536) bytes long. Each segment has a hardware-

recognized base type, which must be either data segment or access segment.

- Data Segments -- data segments have no inherent structure, but are hardware-recognized. They are variously used to hold instructions and scalar data items, but not object references.

- Access Segments -- each access segment is a hardwarerecognized array of object references, protected by the hardware to ensure that inadvertent or malicious alteration of access rights or addressing information does not occur.

- System Management Objects in addition to a base type (data segment or access segment), each segment is assigned a system type so that objects can be built to represent processors, processes, and storage resources. The hardware-recognized typing of these objects, together with a restricted set of operations defined on each type, facilitates efficient system management as processor management, process management, and storage management.

- Program Environment Objects -- by building "packages" or modules of arbitrarily complex objects, a protected program environment is established wherein access to

instructions, scalar data items, and objects can not only be controlled, but also hidden. Programming abstractions such as "subroutine activation records" and "static access environment" are realized in the hardware as contexts and domains, respectively.

- User-defined Objects -- also called "extended-type" objects, these are objects whose structure and behavior are defined by the user. This extends the concept of hardware typing to include arbitrary objects (and networks of objects) that can only be acted on by a restricted set of operations, which may also be defined by the user.

- Type Management Objects -- in order to manage the arbitrary user-defined types, the objects that are instances of those types, and the operations that act upon them, the 432 architecture provides a hardware-recognized type definition object that can be selectively made available to other users, even though its inner workings are hidden from them.

- **Object Locking** -- objects can be locked by either hardware or software to ensure object integrity in a multiple processor environment.

#### OBJECTS

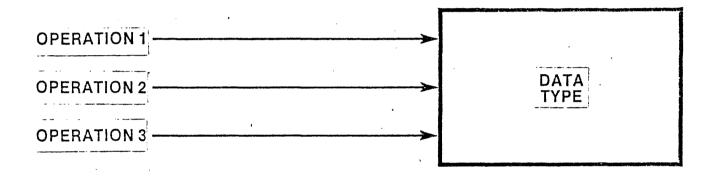

## Operations Defined on Data Types

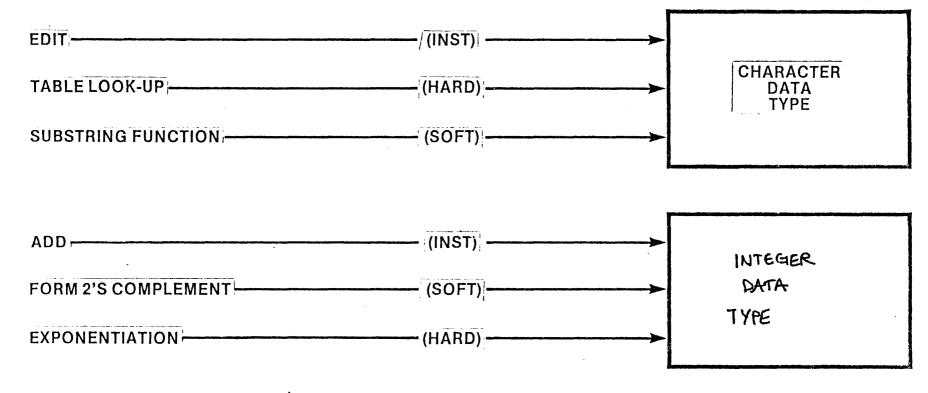

The concept of an object grows out of the natural concept of different data types having different operations that act upon them. Schematically, we depict the situation as shown in Figure 2.1.

Figure 2-1. Operations Defined on a Data Type

# Operations Defined on CHARACTER and INTEGER types

Data types such as CHARACTER and INTEGER are familiar examples of data types. The data items 'A' and 65 are instances of these respective types, which are conceptually different, even though they have the same internal representation, assuming 'A' is represented in ASCII and 65 is represented as a pure binary number in a byte.

These data types may have different operations defined on them by:

Machine instructions (such as an editing instruction for characters, or an arithmetic instruction for integers),

- Hidden hardware functions (such as a table look-up for a character, or forming the 2's complement of an integer),

- Software-implemented functions (such as character substring functions, or exponentiation of integers).

Schematically, we can depict this situation as shown in Figure 2-2.

Figure 2-2. Some Operations Defined on CHARACTER and INTEGER Types.

Characters and integers are not objects, but looking at them this way may help to understand the rationale of objects. Before CHARACTER and INTEGER data types were developed, they existed as abstractions. Programmers coding in octal or binary coded the chartacter 'A' the same as if they were coding the integer 65, and the discipline of choosing the appropriate operations (instructions or subroutines) for the data types they had in mind were left to them.

Programming languages and their translators (assemblers, compilers, and interpreters) introduced formalisms of

2-2 FIGURE 132 SOME OPERATIONS DEFINED ON CHARACTER AND INTEGER TYPES

57 A

subroutines, functions, and procedures into the "art" of programming code: by enforcing declarations of these formerly abstract concepts in programs, language translators could at least ensure that, for instance, a function call was being used as a function call. (An interesting counterexample of this occurred in FORTRAN, in which the statement:

A = F(X)

could be the assignment to A of either:

the value of the function F evaluated using X as an argument, or -

the Xth element of the array F (depending on the declaration of F).

## Software Data Types and Associated Operations

As code abstractions (procedures, functions, and subroutines) demonstrated their merit in enforcing discipline in programming, data abstractions became realized as arrays, vectors, records, and other formal structures. Each essentially different kind of data structure was realized as a data type, and sets of operations were introduced to act upon only certain data types.

For instance, the data type MATRIX was formalized in certain

languages, and the operations DETERMINANT and INVERT, usually implemented in software, could be performed only on a data structure of type MATRIX. If the type did not match the operation, the program would not compile properly.

Compile-time checking ensured that execution time need not be wasted on large programs that would not run properly because a data type did not match the operation applied to it.

# Hardware-Recognized Data Structures and Associated Operations

The software concepts of typed data structures and the operations that can be applied to them are realized in the machine architecture of the iAPX 432. In doing so, the 432 raises the level of the instruction interface from the traditional data computational types of bytes, double bytes, words, etc., to objects.

Just as languages defined operations on primitive data types, the architecture of the 432 (and any language capable of embracing this architecture) defines operations on objects, which are instances of typed data structures. Thus, a machine instruction on the 432 typically specifies as its operands objects that represent:

- o Processors in a multiprocessor environment

- o Processes (tasks) in a concurrent environment

- o Dispatching ports that bind processes to processors

- o Interprocess messages sent from one process to another, and synchronized using communication ports

- Domains (also called type managers) as the static access environments of programs

o Contexts (subprograms)

And many more. These objects are all system objects; they are instances of system types, that is, types built into the system.

# Objects as high level, strongly typed operands

Intuitively, a system object is a high level operand that raises the level of the instruction interface. "High-level" in this sense means that the operand, rather than simply being a byte or word of data, is an organized data structure in memory that is recognized by the hardware as being an instance of a type that can be manipulated only by a select class of operations.

Traditional computer systems implement the abstractions of access environment control, task management, process status, interprocess communication, etc. using a combination of software structures defined by operating systems, utilities, and compilers, and associated supervisor calls.

The 432 implements these concepts as machine-inherent data structures referenced by instructions as strongly typed operands that are validity-checked at run time:

o Each has a type (base and system), and

Each can be used as an operand only as intended, i.e.,

only with a well defined subset of the operator (instruction) set.

Many 432 system objects are highly organized "control blocks" reminiscent of operating task control, message queueing, fault handling, and other mechanisms. These "control block" system object operands do not in and of themselves enforce operating system policy, but rather provide the basic mechanisms from which virtually any operating system can be designed and built. These mechanisms provide functionality needed to design and build clean, fast running software. Indeed, for large, high availability systems, the software development cycle can be shortened

using the 432.

## Extended types

The 432 architecture allows users to define arbitrary data structures as objects, and to define the restricted set of operations that are allowed to act on these objects. These user-defined object types are called extended types, since they extend the set of recognized object types and the operations allowed by each type.

## Example of a 432 object and its associated operations

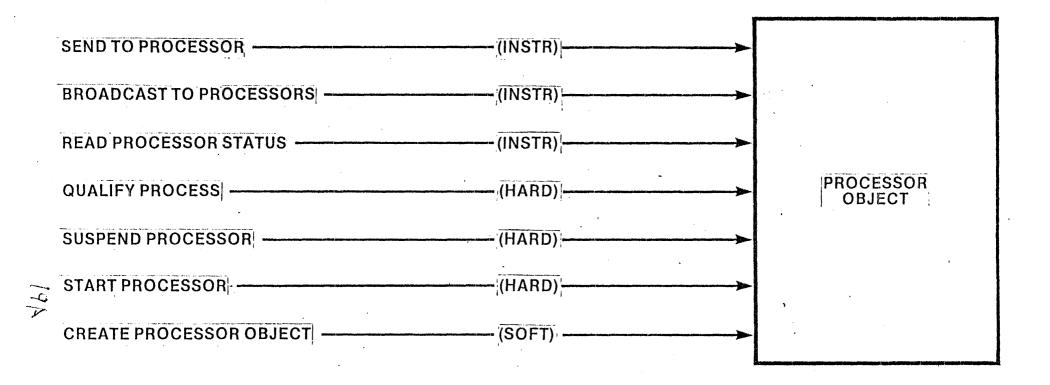

The processor object represents a unit of processing power in the system and as such is an abstraction of the physical processing unit, reflecting its various states (running, queued, assigned, etc.). Processor objects in a given system are in one-to-one correspondence with physical processors in that system.

A processor object thus provides a means of assigning the processor it represents to a particular process set (work stream), and also provides a means of communicating with (sending messages to) a processor.

# Operations

Figure 2-3 indicates a processor object and the operations that act apon it.

Figure 2-3 Operations defined on a procesor object.

# Access descriptors -- "handles" for objects

When several users require access to the same object, at least two problems can arise:

- o Need-to-Know Rights. In a multi-user environment, not all users need to have the same rights to an object; for instance, one user may require only "read" rights to sensitive data, whereas another may require both "read" and "write" rights to that data structure (object); a mechanism is needed whereby different rights can be conferred on different instances of procedures. The solution to this problem is discussed below.

- o Exclusive Access. In a multiprocessor environment, one user of a data structure (object) may require exclusive access to that object for a particular operation, to ensure that no other processor alters the object while the operation proceeds. The solution

to this problem is described at the end of this chapter under "Object Locking."

In the past, problems like the first have been solved by introducing "privileged" and "user" instructions or modes of operation, which have the disadvantage that each user is either "universally privileged" or "universally restricted." Systems that generalize this scheme to three or more levels typically encounter similar problems in their blanket or graduated privilege schemes. Such schemes characteristically do not take individual procedure access requirements into account.

In the object-oriented, capability-based environment of the 432, several privilege and protection abstractions are realized using access descriptors, which act as privilege and protection "handles" for system objects. The 432 approach is to grant a procedure read/write rights to explicit objects on an individual, need-to-know basis. By possessing an access descriptor to an object, a procedure is conferred the read/write rights specified by that access descriptor, and is thus capable of reading/writing the object. An access descriptor is thus sometimes called a capability.

A running procedure context cannot read from or write to an object unless that procedure has an access descriptor for

that object. Moreover, the procedure cannot read to or write from the object accessed by the access descriptor unless that read or write privilege is expressly granted, as indicated in the access descriptor. Furthermore, the procedure cannot delete the access descriptor unless that right is explicitly indicated within the access descriptor itself.

Thus, access descriptors provide:

- o Controlled access to a particular object; if a request to use an object matches the rights specified in the access descriptor for that object, the access descriptor maps a virtual address into a physical address, permitting access.

- Read and/or write protection of the object by an instance of a procedure, independent of other objects, other procedures, and other instances of the same procedure.

- Delete protection of the access descriptor itself.

- O Other object-specific information, such as system

rights, an access descriptor validity check, and an

indication of object storage allocation.

Since an object can be subsetted (using a refiner, as described later in this chapter) to obtain a smaller object, access descriptors provide a granularity of protection not found in "privilege-level" computer systems.

## Access Paths

Many access descriptors can exist for the same object. Each access descriptor belongs to some (but may be copied and/or passed to another) procedure (context), and defines the access rights of the procedure using it to access an object.

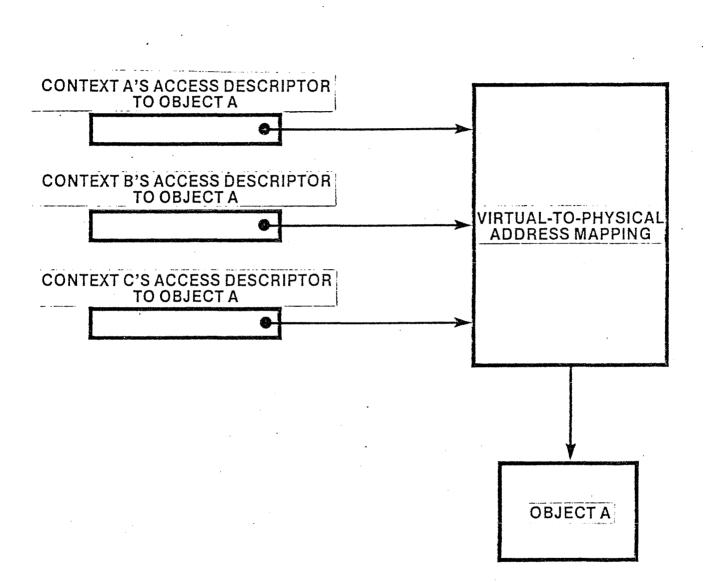

For instance, Figure 2-4 shows three different access descriptors to the same object. Context A can read from Object A, but cannot write into it; Context B can write into Object A, but cannot read from it; and Context C can both read from and write into Object A.

Figure 2-4. Different Access Paths and Rights to the Same Object.

# Segments -- the Representations of Objects

At the machine level, objects are represented by segments. A segment is characterized as being a contiguous block of

memory and having:

o A base address.

o A length, which can be up to 65536 bytes.

A base type and a system type, both of which depend on the intended use of the segment as an object.

Relationship Between System Objects and Segments

Every segment is an object, but the converse does not hold. Every object is either:

o A segment, or

o A subset of a segment (called a refinement), or

o A collection of segments and/or refinements.

Both segments and system objects have these characteristics:

o Each has a base address. If an object is a single segment, the base address is that of the segment. If an object is a group of segments, the base address is that of the "root" segment, i.e. the first in the access path.

- Each has a base type, which must be either of type data segment or type access segment.

- o Each has a system type, which can be generic (data segment or access list), or can be specialized as a transformer, domain, dispatching port, context, operand stack, storage resource, etc.

- Each is represented by, and accessed through, a segment descriptor in a segment table residing in memory. A segment descriptor encodes a segment's base address, length, base type, system type, processor class, and other information.

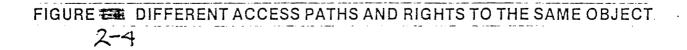

**Object Networks.** As an example of an object that is a collection of segments, consider the access segment (Object O) together with the objects Al, A2, and A3 referenced by its access descriptors. This collection defines a multisegment object. Extending this concept, each of the objects Aj (j = 1, 2, 3) could itself be an access list referencing objects Bjk (k = 1, 2, 3). The resulting network of object: Bll, Bl2, ..., B32, B33, could then be considered an object Figure 2-5 depicts such an object.

Figure 2-5. A Network of Objects as an Object.

FIGURE TER A NETWORK OF OBJECTS AS AN OBJECT

2-5

#### Two-Level Object Typing

Objects defined by the 432 architecture have two levels of typing:

- A base type, which is either data segment or access segment. Data segments cannot contain access descriptors; access segments contain only access descriptors.

- A system type, of which there are several: processor,

process, domain, context, and dispatching port are but

a few system types.

Data Segments

Data segments can contain anything but access descriptors. In fact, they can contain dummy copies of access descriptors for purposes of inspection, but the dummy copies will not "work" as access descriptors; if so referenced, the 432 hardware will not permit the operation to take place.

Data segments are used to hold instructions (as objects of system type instruction segment), scalar data types, and any type of data structure except an access descriptor. In order to access a data segment, a procedure must have an

access descriptor for the data segment.

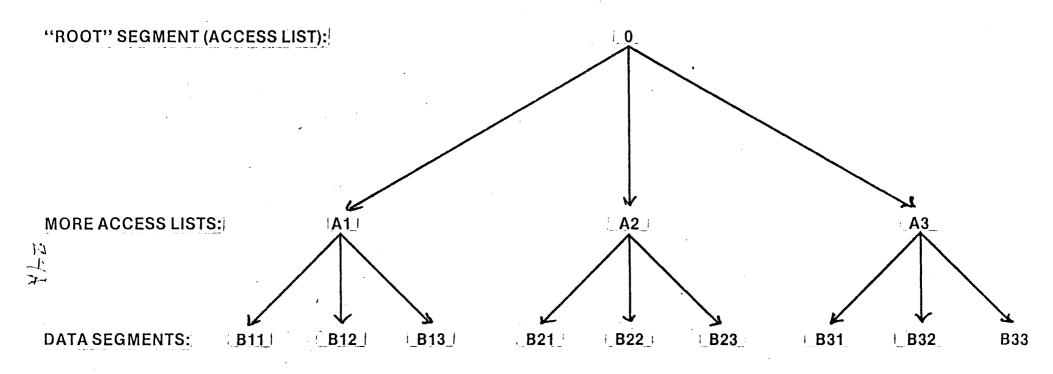

Access Segments

An access segment (sometimes called an "access list") is a hardware-recognized array of access descriptors. In order to access an access segment, a procedure must have an access descriptor for the access segment itself.

Symbology. In this manual, access segments are symbolized as shown in Figure 2-6.

Figure 2-6. Access Segment Symbology.

#### OBJECT LOCKING/EXCLUSION

Object Locking

Either software or hardware can lock (obtain exclusive access to) an object when required by a sequence of instructions or microinstructions. Object can be locked in three ways:

Long-term software lock -- used when a software

operation requires that an object be locked for a

13

FY

FIGURE THE ACCESS SEGMENT SYMBOLOGY

ς.

period of time longer than the duration of one instruction. Accomplished using the Lock Object/Un-lock Object instructions.

- Short-term software lock -- used by a processor when executing an instruction that requires object locking for a period of time less than the duration of an instruction.

- o Short-term hardware lock -- used by a processor when performing an operation on its own behalf that requires an object to be locked.

#### CHAPTER 3

#### INTRODUCTION TO 43203 INTERFACE PROCESSOR

This introduction to the architecture of the Intel 43203 Interface Processor (IP) includes four topics. The first introduces a basic I/O model. The second provides a brief discussion of the 43201 and 43202 General Data Processor (GDP) interface. (Refer to section 2 for a more detailed discussion). The peripheral subsystem/IP interface is the third topic, which provides information concerning the software interface as well as the hardware interface. The final topic introduces the supplementary IP facilities, including the physical reference mode and the interconnect access mode.

For a more detailed presentaion of the following concepts, refer to the iAPX Interface Processor Architecture Reference Manual, Order no. TBS)

A BASIC I/O MODEL

A typical application based on the iAPX 432 microprocessor family consists of a main system and one or more peripheral subsystems. Figure 3-1 illustrates a hypothetical configur-

•

Fig 2017 Main System And Periods Althous systems

FIG. 3-1 MAIN SYSTEM AND PERIPHERAL SUBSYSTEM

ation that employs two peripheral subsystems. The main system hardware is composed of one or more iAPX 432 general data processors (GDPs) and a common memory that is shared by these processors. The main system software is a collection of one or more processes that execute on the GDP(s).

A fundamental principle of the iAPX 432 architecture is that the main system environment is self-contained; neither processors nor processes have any direct contact with the "outside world." Conceptually, the main system is enclosed by a wall that protects objects in memory from possible damage by uncontrolled I/O operations.

Figure 3-1 Main System and Peripheral Subsystems

In an iAPX 432-based system, the bulk of processing required to support input/output operations is delegated to peripheral subsystems; this includes device control, timing, interrupt handling and buffering. A peripheral subsystem is an autonomous computer system with its own local memory, I/O devices and controllers, at least one processor, and software. The number of peripheral subsystems employed in any given application depends on the I/O-intensiveness of the application, and may be varied with changing needs, independent of the number of GDPs in the system.

A peripheral subsystem resembles a mainframe channel in that it assumes responsibility for low-level I/O device support, executing in parallel with main system processor(s). Unlike a simple channel, however, each peripheral subsystem can be configured with a complement of hardware and software resources that precisely fits application cost and performance requirements. In general, any system that can communicate over a standard 8- or 16-bit microcomputer bus such as Intel's Multibus design may serve as an iAPX 432 peripheral subsystem.

A peripheral subsystem is attached to the main system by means of an IP. At the hardware level, the IP presents two separate bus interfaces. One of these is the standard iAPX 432 Packetbus and the other is a very general interface that can be adapted to most traditional 8-and 16-bit microcomputer buses.

To support the transfer of data through the wall that separates a peripheral subsystem from the main system, the IP provides a set of software-controlled windows. A window is used to expose a single object in main system memory so that its contents may be transferred to or from the peripheral subsystem.

The IP also provides a set of functions that are invoked by

software. While the operation of these functions varies considerably, they generally permit objects in main system memory to be manipulated as entities, and enable communication between main system processes and software executing in a peripheral subsystem.

•

It is important to note that both the window and function facilities utilize and strictly enforce the standard iAPX 432 addressing and protection systems. Thus, a window provides protected access to an object, and a function provides a protected way to operate in the main system. The IP permits data to flow across the peripheral subsystem boundary while preserving the integrity of the main system.

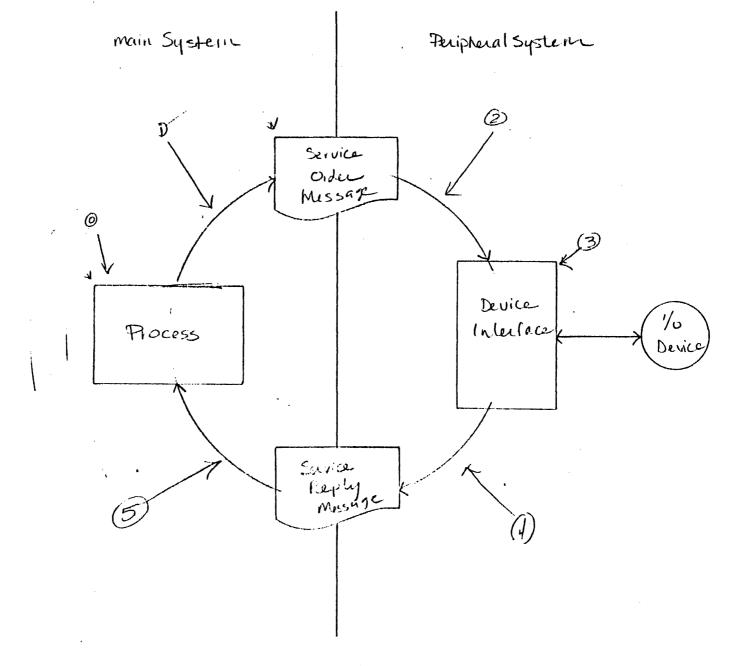

As figure 3-2 illustrates, input/output operations in an iAPX 432 system are based on the notion of passing messages between main system processes and device interfaces located in a peripheral subsystem. A device interface is considered to be the hardware and software in the peripheral subsystem that is responsible for managing an I/O device. An I/O device is considered to be a "data repository," which may be a real device (e.g., a terminal), a file, or a pseudo-device (e.g., a spooler).

A message sent from a process that needs an I/O service contains information that describes the requested operation (e.g., "read file XYZ"). The device interface interprets

FIGURE 3-2 Banc VO Service Cycle

the message and carries out the operation. If an operation requests input data, the device interface returns the data as a message to the originating process. The device interface may also return a message to positively acknowledge completion of a request.

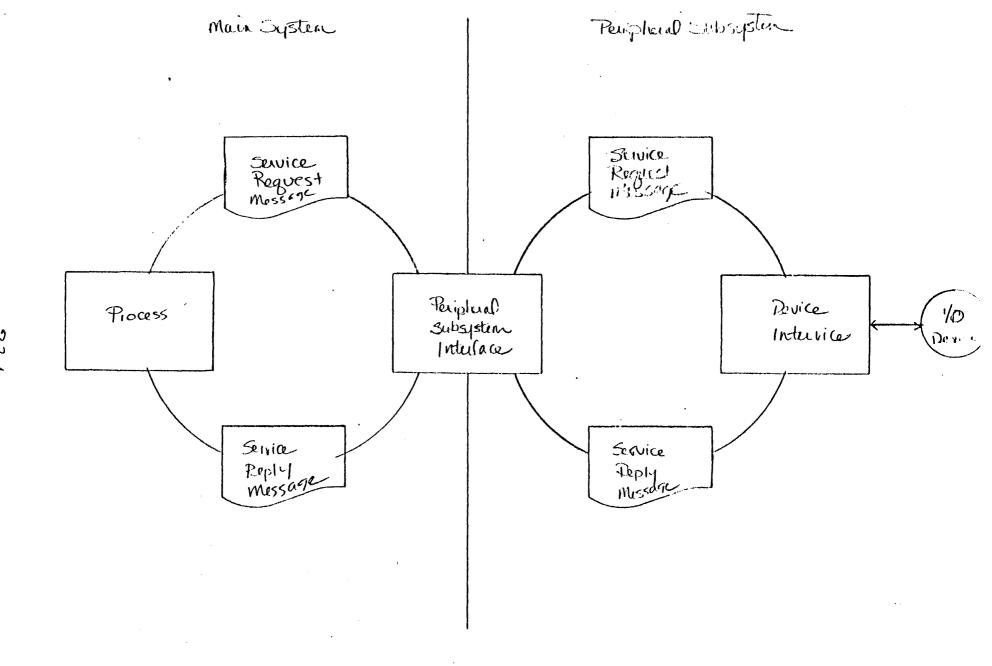

A very general and very powerful mechanism for passing messages between processes is inherent in the iAPX 432 architecture. A given peripheral subsystem may, or may not, have its own message facility, but in any case, such a facility will not be directly compatible with the iAPX 432's. By interposing a peripheral subsystem interface at the subsystem boundary, the standard IP communication system can be made compatible with any device interface (see figure 3-2).

Figure 3-2 Basic I/O Service Cycle

Figure 3-3 Peripheral Subsystem Interface

#### **iAPX 432 INTERFACE**

The IP exists in both the protected environment of the iAPX 432, and the conventional environment of the external

FIG. 3-3 Peripheral Subsystem Hterace

212A

subsystem. Because of this, an IP is able to provide a pathway over which data may flow between the iAPX 432 system and the external subsystem. The IP operates at the boundary between the systems, providing compatibility and protection. In this position, the Interface Processor presents two different views of itself, one to software and processors in the iAPX 432 environment and another to its external processor.

From the iAPX 432 side, an IP looks and behaves very much like any other processor. It attaches to the processor packetbus in the same way as a GDP. Within the iAPX 432 memory, the IP supports an execution environment that is compatible with, and largely identical to, the GDP. Thus, the IP recognizes and manipulates system objects representing processors, processes, ports, etc. It supports and enforces the iAPX 432's access control mechanisms, and provides full interprocess and interprocessor communication facilities.

The principle difference between the two processors is that the GDP manipulates its environment in response to the instruction it fetches, while the IP operates under the direction of its external processor. Indeed, the IP may be said to extend the instruction set of the attached processor (AP) so that it may function in the environment of the iAPX 432 system

#### PERIPHERAL SUBSYSTEM INTERFACE

A peripheral subsystem interface (PSI) is a collection of hardware and software that acts as an adapter that enables message-based communication between a process in the main system and a device interface in a peripheral subsystem (see figure 3-3). Viewed from the iAPX 432 side, the peripheral subsystem interface appears to be a process. The peripheral subsystem interface may be designed to present any desired appearance to a device interface. For example, it may look like a collection of tasks, or like a collection of subroutines.

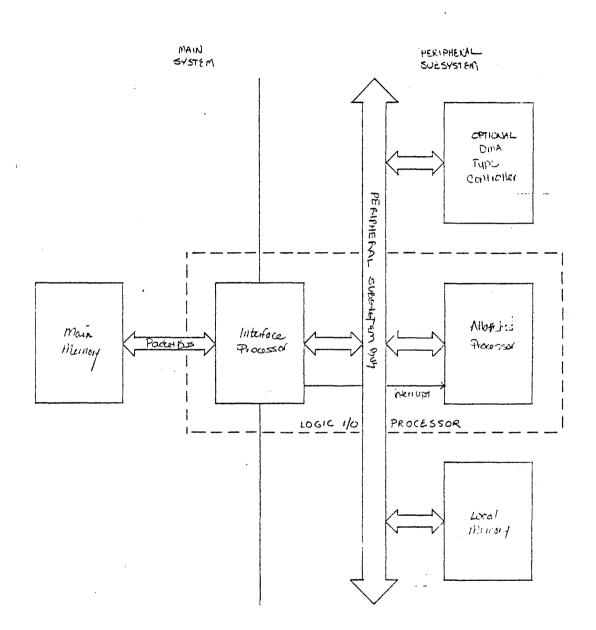

#### Hardware

The PSI hardware consists of an IP, an AP, and local memory (see figure 3-4 ). To improve performance, these may be augmented by a DMA controller. The AP and the IP work together as a team, each providing complementary facilities. Considered as a whole, the AP/IP pair may be thought of as a logical I/O processor that supports software operations in both the main system and the peripheral subsystem.

Attahed Processor -- Almost any general-purpose CPU, such as an 8085, an iAPX 86 or an iAPX 88 can be used as an AP. The AP need not be dedicated exclusively to working with the IP.

FIGURE 3-4 PERIPHERAL SUBSTSTEM INTERFACE HARDWAR BOLD It may, for example, also execute device interface software. Thus, the AP may be the only CPU in the peripheral subsystem, or it may be one of several.

As figure 3-4 shows, the AP is "attached" to the interface processor in a logical sense only. The physical connections are standard bus signals and one interrupt line (which would typically be routed to the AP via an interrupt controller).

Continuing the notion of the logical I/O processor, the AP fetches instructions, and provides the instructions needed to alter the flow of execution, and to perform arithmetic, logic and data transfer operations within the peripheral subsystem.

Figure 3-4 Peripheral Subsystem Interface Hardware

Interface Processor -- The IP completes the logical I/O processor by providing data paths between the peripheral subsystem and the main system, and by providing functions that effectively extend the AP's instruction set so that software running on the logical I/O processor can operate in the main system. Since these facilities are softwarecontrolled, they are discussed in the next section.

As figure 3-4 shows, the IP presents both a peripheral subsystem bus interface and a standard iAPX 432 Packetbus interface. By bridging the two buses, the IP provides the hardware link that permits data to flow under software control between the main system and the peripheral subsystem.

The IP connects to the main system in exactly the same way as a GDP. Thus, in addition to being able to access main memory, the IP supports other iAPX 432 hardware-based facilities, including processor communication, the alarm signal and functional redundancy checking.

On the I/O subsystem side, the IP provides a very general bus interface that can be adapted to any standard 8- or 16bit microprocessor bus, including Intel's Multibus architecture, as well as the component buses of the MCS-85 and iAPX 86 families. The IP is connected to the peripheral subsystem bus as if it were a memory component; it occupies a block of memory addresses up to 64K bytes long. Like a memory, the IP behaves passively within the peripheral subsystem (except as noted below). It is driven by peripheral subsystem memory references that fall within its address range.

While the IP generally responds like a memory component, it also provides an interrupt request signal. The interface

processor uses this line to notify its AP that an event has occurred which requires its attention.

To summarize, the AP and the IP interact with each other by means of address references generated by the AP and interrupt requests generated by the IP. Since the IP responds to memory references, other active peripheral subsystem agents (bus masters), such as DMA controllers, may obtain access to main system memory via the IP.

#### Software

IP Controller -- The peripheral subsystem interface is managed by software, referred to as the IP controller. The IP controller executes on the AP and uses the facilities provided by the AP and the IP to control the flow of data between the main system and the peripheral subsystem.

While there are no actual constraints on the structure of the IP controller, organizing it as a collection of tasks running under the control of a multitasking operating system (such as RMX-80 or iRMX-86) can simplify software development and modification. This type of organization supports asynchronous message-based communication within the IP controller, similar to the iAPX 432's intrinsic interprocessor communication facility. Extending this approach to the device interface as well results in a consistent,

system-wide communication model. However, communication within the IP controller and between the IP controller and device interfaces, is completely application-defined. It may also be implemented via synchronous procedure calls, with "messages" being passed in the form of parameters.

However it is structured, the IP controller interacts with the main system through facilities provided by the interface processor. There are three of these facilities: execution environments, windows, and functions.

Execution Environments -- The IP provides an environment within the main system that supports the operation of the IP controller in that system. This environment is embodied in a set of system objects that are used and manipulated by the IP. At any given time, the IP controller is represented in main memory by a process object and a context object. Like a GDP, the IP itself is represented by a processor object. Representing the IP and its controlling software like this creates an execution environment that is analogous to the environment of a process running on a GDP. This environment provides a standard framework for addressing, protection and communication within the main system.

Like a GDP, an IP actually supports multiple process environments. The IP controller selects the environment in which a function is to be executed. This permits, for

example, the establishment of separate environments corresponding to individual device interface tasks in the peripheral subsystem. If an error occurs while the IP controller is executing a function on behalf of one device interface, that error is confined to the associated process, and processes associated with other device interfaces are not affected.

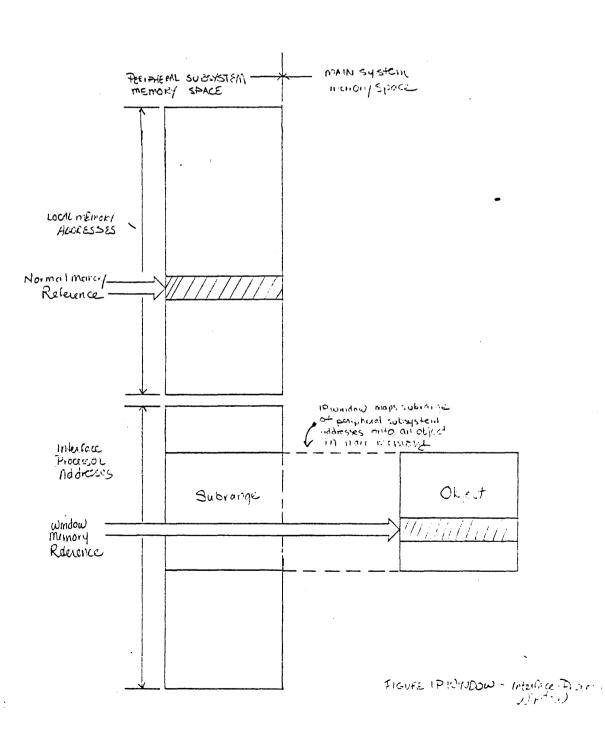

Windows -- Every transfer of data between the main system and a peripheral subsystem is performed with the aid of an IP window. A window defines a correspondence, or mapping, between a subrange of peripheral subsystem memory addresses (within the range of addresses occupied by the IP) and an object in main system memory (see figure 3-5). When an agent in the peripheral subsystem (e.g., the IP controller) reads a local windowed address, it obtains data from the associated object; writing into a windowed address transfers data from the peripheral subsystem to the windowed object. The action of the IP, in mapping the peripheral subsystem address to the main system object, is transparent to the agent making the reference; as far as it is concerned, it is simply reading or writing local memory.

Figure 3-5 Interface Processor Window

34A

Since a window is referenced like local memory, any individual transfer may be between an object and local memory, an object and a processor register, or an object and an I/O device. The latter may be appealing from the standpoint of "efficiency," but it should be considered with caution. Using a window to directly "connect" an I/O device and an object in main memory has the undesirable effect of propogating the real-time constraints imposed by the device beyond the subsystem boundary into the main system. It may seriously complicate error recovery as well. Finally, since there is a finite number of windows, most applications will need to manage them as scarce resources that will not always be instantly available. This means that at least some I/O device transfers will have to be buffered in local memory until a window becomes available. It may be simplest to buffer all I/O device transfers and use the windows to transfer data between local memory and main system memory.

There are four IP windows that may be mapped onto four different objects. The IP controller may alter the windows during execution to map different subranges and objects. References to windowed subranges may be interleaved and may be driven by different processors in the peripheral subsystem. For example, the AP and a DMA controller may be driving transfers concurrently, subject to the same bus arbitration constraints that would apply if they were accessing local memory.

Functions — A fifth window provides the IP controller with access to the IP's function facility. By writing operands and an opcode into predefined locations in this window's subrange, the IP controller requests the IP to execute a function on its behalf. This procedure is very similar to writing commands and data to a memory-mapped peripheral controller (e.g., a floppy disk controller). Upon completion of the function, the IP provides status information that the IP controller can read through the window. The IP can perform transfer requests through the other four windows while it is executing a function.

The IP's function set permits the IP controller to:

- o alter windows;

- exchange messages with GDP processes via the standard

IP communication facility;

o manipulate objects.

These functions may be viewed as instruction set extensions to the AP, which permit the IP controller to operate in the main system. The combination of the IP's function set and windows, the AP's instruction set, and possibly additional facilities provided by a peripheral subsystem operating

system, permits the construction of powerful IP controllers that can relieve the main system of much I/O-related processing. At the same time, by utilizing only a subset of the available IP functions, relatively simple IP controllers can also be built (in cases where this approach is more appropriate).

#### SUPPLEMENTARY INTERFACE PROCESSOR FACILITIES

The preceding sections describe the IP as it is used most of the time. The IP provides two additional capabilities that are typically used less frequently, and only in exceptional circumstances. These are physical reference mode and interconnect access.

#### Physical Reference Mode

The IP normally operates in logical reference mode; this mode is characterized by its object-oriented addressing and protection system. There are times when logical referencing is impossible because the objects used by the hardware to perform logical-to-physical address development are absent (or, less likely, are damaged). In these situations the IP can be used in physical reference mode.

In physical reference mode, the IP provides a reduced set of functions. Its windows operate as in logical reference

mode, except that they are mapped onto memory segments (rather than objects) that are specified directly with 24bit addresses. In this respect, physical reference mode is similar to traditional computer addressing techniques.

Physical reference mode is most often employed during system initialization to load binary images of objects from a peripheral subsystem into main memory. Once the required object images are available, processors can begin normal logical reference mode operations.

#### Interconnect Access

In addition to memory, the iAPX 432 architecture defines a second address space called the processor-memory interconnect. One of the IP windows is software-switchable to either space. In logical reference mode, the interconnect space is addressed in the same object-oriented manner as the memory space, with the IP automatically performing the logical-to-physical address development. In physical reference mode, the interconnect space is addressed as an array of 16-bit registers, with a register selected by a 24-bit physical address.

#### CHAPTER 4

### iAPX 432 PROCESSOR ENVIRONMENT DEFINITION

This chapter describes the requirements placed on the logical structure of the iAPX 432 hardware environment. These requirements are concerned directly with the constraints of local memory, the type of data transferred (address, control, or data), and the structure of the data types.

The first section presents the information structure for an iAPX 432 system and includes a discussion of memory system requirements, physical addressing, data formats, data representation, and hardware error detection. The second section presents the elements of the processor packet bus and includes associated timing diagrams for Read, Write, and Access cycles.

#### **iAPX 432 INFORMATION STRUCTURE**

The iAPX 432 system contains both read/write (RAM) and readonly (ROM) memory. Any attached processor (8 bit or 16 bit) in the system can access all the contents of physical

memory. This section describes how information is represented and accessed.

#### Memory

The iAPX 432 implements a two-level memory structure. The software system exists in a segmented environment in which a logical address specifies the location of a data item. The processor automatically translates this logical address into a physical address for accessing the value in physical memory.

#### Physical Addressing

Logical addresses are translated by the processor into physical addresses. Physical addresses are transmitted to memory by a processor to select the beginning byte of a memory value to be referenced. A physical address is 24 binary bits in length. This results in a physical memory of over 16.5 Megabytes.

#### Data Formats

When a processor executes the instructions of an operation within a context, operands found in the segments of the context may be manipulated. An individual operand may occupy one, two, four, eight, of ten bytes of memory (byte, double

byte, word, double word, or extended word, respectively). All operands are referenced by a logical address as described above. The displacement in such an address is the displacement in bytes from the base address of the data segment to the first byte of the operand. For operands consisting of multiple bytes, the address locates the loworder byte while the higher-order bytes are found at the next higher consecutive addresses.

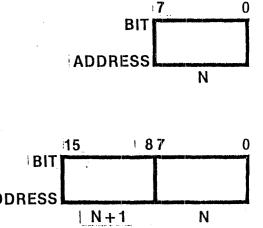

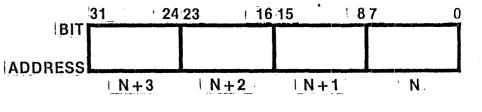

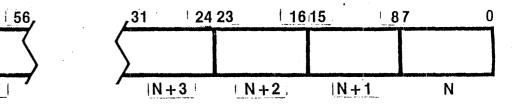

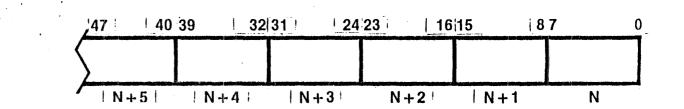

#### Data Representation

An iAPX 432 convention has been adopted for representing data structures stored in memory. The bits in a field are numbered by increasing numeric significance, with the leastsignificant bit shown on the right. Increasing byte addresses are shown from right to left. Examples of the five basic data lengths used in the iAPX 432 system are shown in figure 4-1.

Figure 4-1

#### Data Positioning

The data structures shown in figure 4-1 may be aligned on an arbitrary byte boundary within a data segment. Note that more efficient system operation may be obtained when multibyte data structures are aligned on double-byte boundaries

## BASIC , APX 432 DATA LENGTHS FIGURE 4-1

## BYTE

DOUBLE BYTE

# ALA

WORD

# **DOUBLE WORD**

EXTENDED WORD

63

IN+7

BIT

ADDRESS

79

BIT

ADDRESS

1 72

N + 9 |

ADDRESS

(if the memory system is organized in units of double bytes).

#### Requirements of an iAPX 432 Memory System

The multiprocessor architecture of the iAPX 432 places certain requirements on the operation of the memory system to ensure the integrity of data items that can potentially be accessed simultaneously. Indivisible read-modify-write (RMW) operations to both double-byte and word operands in memory are necessary for manipulating system objects. When an RMW-read is processed for a location in memory, any other RMW-reads from that location must be held off by the memory system until an RMW-write to that location is received (or until an RMW timeout occurs). Note that while the memory system is writing the RMW-write, any other types of reads and writes are allowed. Also, for ordinary reads and writes of double-byte or longer operands, the memory system must ensure the entire operand has been either read or written before beginning to process another access to the same location; e.g., if two simultaneous writes to the same location occurs, the set of locations used to store the operand could contain some interleaved combination of the two written values.

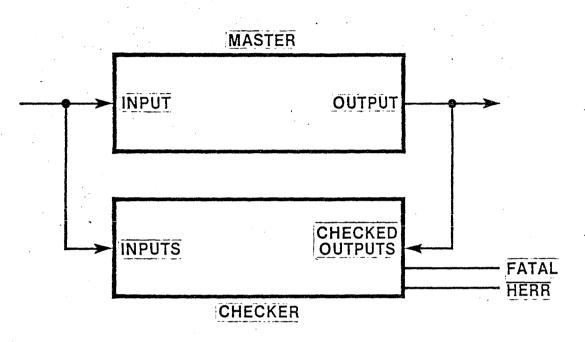

iAPX 432 Hardware Error Detection

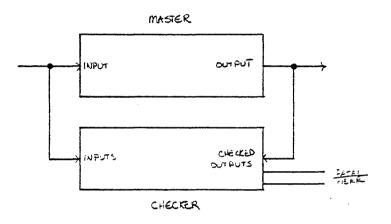

iAPX 432 processors include a facility to support the hardware detection of functional errors. At INIT/ time each iAPX 432 processor is configured to operate as either a master or checker processor. A master operates in the normal manner. A checker places all output pins that are being checked into a high-impedance state. Thus a master and checker processor may be parallel-connected such that the checker is able to compare a master's output pin values to those computed in the checker. Any comparison error causes the checker to assert HERR/, FATAL/, and go idle. No further activity will occur at the disagreeing masterchecker processor.

Figure 4-2 Hardware Error Detection

#### PACKET BUS DEFINITION

This section describes and defines the significance of the 19 signal lines that make up the processor packet bus, and the general scheme by which timing relationships on these lines are derived. Although this section defines all legal bus activities, the processors do not necessarily perform all allowed activities.

The packet bus consists of 3 control lines:

o Packet bus Request (PRQ),

FIGURE 4-2 HARDWARE ERFOR DETECTION

45A

o Enable Buffer Outputs ( BOUT).

o Interconnect Status (ICS),

This bus also includes sixteen 3-state Address-Control-Data lines (ACD15 through ACDO). PRQ has two functions whose use depends upon the application, i.e., PRQ either indicates the first cycle of a transaction on the processor component bus or the cancellation of a transaction initiated in the previous cycle. Of the three control lines, BOUT has the simplest function, serving as a direction control for buffers in large systems requiring more electrical drive than the processor components can provide. The ICS signal has significance pertaining to one of three different system conditions and depends on the state of the processor component bus transaction. The processor interprets the ICS input as an indication of one of the following:

- Whether or not an interprocess communication (IPC) is waiting,

- Whether or not the slave requires more time to service the processors request,

- o Whether or not a bus ERROR has occurred.

The Address/Control/Data lines emit output specification information to indicate the type of cycle being initiated, e.g., addresses, data to be written, or control information. They also receive data returned to the processor during reads. Details of the ACD line operation and the associated control lines are summarized below.

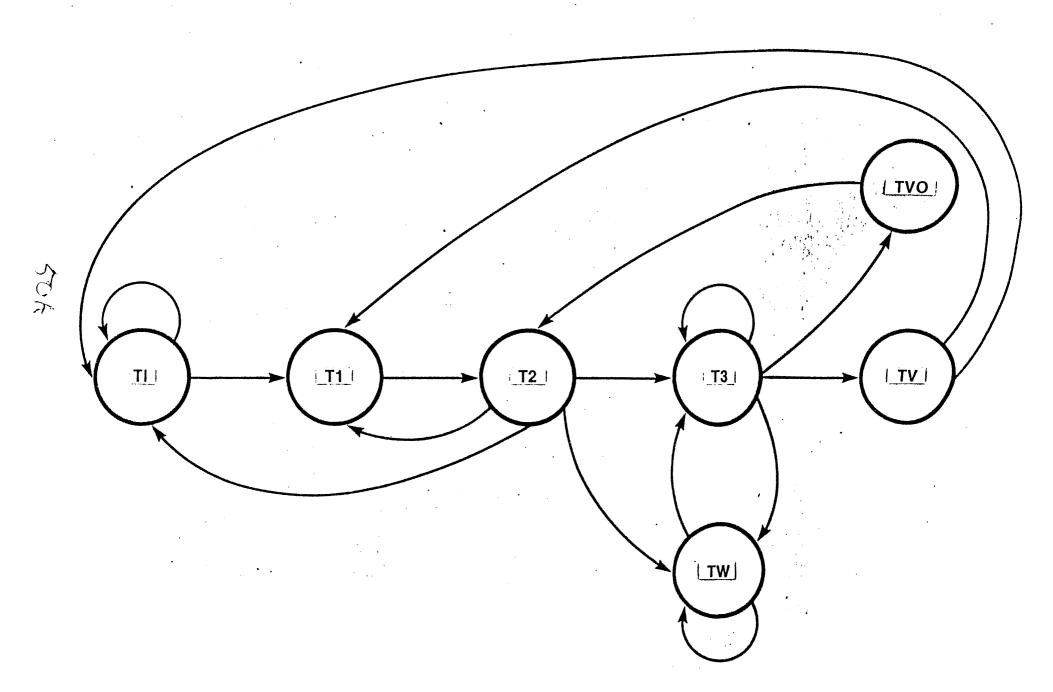

ACD15 - ACDO (Address/Control/Data) -- During the first cycle (Tl or Tvo (See Figure 4-3) of a processor component bus transaction (indicated by the rising edge of PRQ), the high-order 8 ACD bits (ACD15...ACD8) specify the type of the current transaction. In this first cycle, the low-order ACD bits (\*CD7...ACDO) contain the least significant eight bits of the 24 bit physical address.

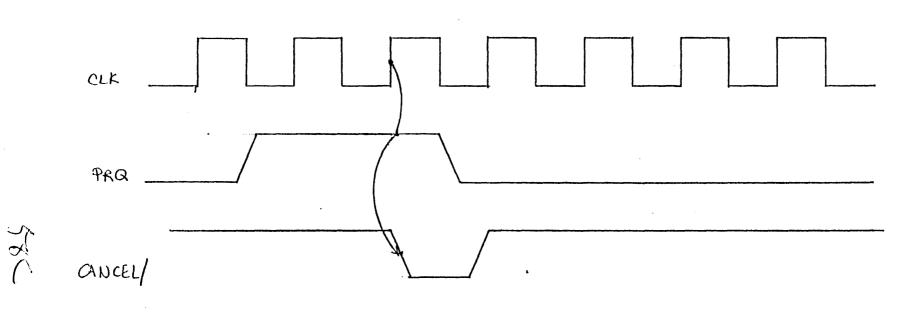

> During the subsequent cycle (T2), the remainder of the address is present on the ACD pins (aligned such that the most significant byte of the address is on ACD15 through ACD8, the mid-significant byte on ACD7 through ACD0). If PRQ is asserted during T2, the access is cancelled and the ACD line is not defined.

> During the third cycle (T3 or Tw) of a processor packet bus transaction the processor presents a high impedance to the ACD lines for read transactions and Tw or T3 asserts write data for write transactions.

FIGURE 4-3 STATE DIAGRAM FOR PROCESSOR PACKET BUS

## Processor Pocket Bus State Diagram

ι

| Ti                                                 | T1 | T2                    | Т3                                                                        | Tv                                |

|----------------------------------------------------|----|-----------------------|---------------------------------------------------------------------------|-----------------------------------|

|                                                    |    |                       |                                                                           |                                   |

|                                                    |    |                       | Tw                                                                        |                                   |

| INITIAL STATE                                      |    | NEXT STATE            | TRIGGER                                                                   |                                   |

| Ti                                                 |    | T1<br>Ti              | Bus cycle desired<br>No bus cycle desire                                  | d                                 |

| T1                                                 |    | T2                    | Unconditional                                                             |                                   |

| Τ2                                                 |    | T3<br>Tw<br>T1<br>Ti  | ICS high<br>ICS low<br>Cancelled, Access P<br>Cancelled, No Accce         |                                   |

| Т3                                                 |    | T3<br>Tw<br>Tv<br>Tvo | Additional transfer<br>ICS low<br>All transfers compl<br>Overlapped write | required<br>eted if current cycle |

| Τ <b>ν</b>                                         |    | Ti<br>T1<br>T2        | If read or if write<br>Current write with<br>Current write with           |                                   |

| Tvo                                                |    | T2                    | Overlapped write                                                          |                                   |

| Тw                                                 |    | Tw<br>T3              | ICS Low<br>ICS High                                                       |                                   |

| Figure Free State Diagram for Processon Backet Ruc |    |                       |                                                                           |                                   |

Figure -3 - State Diagram for Processor Packet Bus (-3)

;

Tvo

★

Once the bus has entered T3 or Tv, the sequence of state transactions depends on the type of cycle requested during the preceding Tl or Tvo. Accesses ranging in length from 1 to 32 bytes may be requested (see Table 4-1). If a transfer of more than one double byte has been requested, it is necessary to enter T3 for every double-byte that is transferred. After any transfer the processor may simply re-enter T3 or it may enter Tw for any number of cycles (as dictated by ICS) and the number of double bytes remaining to be transferred.

After all data is transferred, the processor enters either Tv or Tvo. Tvo can be entered only when the internal state of execution is such that the processor is prepared to accomplish an immediate write transfer (overlapped write). During Tvo, the ACD lines contain address and specification information aligned in the same fashion as in Tl. If the processor does not require an overlapped write, the bus state moves to Tv (the ACD lines will be floating). After Tv, a new bus cycle can be started with Tl, or the processor may enter the idle state(Ti).

ICS (Interconnect Status) -- ICS has three possible interpretations depending on the state of the bus transac-

| ACD<br>15     | ACD<br>14    | ACD<br>13      | ACD<br>12      | ACD<br>11                                                                  | ACD<br>10 | ACD<br>9                                              | ACD<br>8                 |

|---------------|--------------|----------------|----------------|----------------------------------------------------------------------------|-----------|-------------------------------------------------------|--------------------------|

| Access        | Ор           | RMW            |                | Length                                                                     |           | Мо                                                    | difiers                  |

| 0 -<br>Memory | 0 -<br>Read  | 0 -<br>Nominal | 00<br>01<br>01 | 00 - 1 Byte<br>01 - 2 Bytes<br>0 - 4 Bytes<br>11 - 6 Bytes<br>00 - 8 Bytes | 5         | ACD 15<br>00-Ins<br>Acc<br>01-Sta<br>Acc              | t Seg<br>ess<br>ck Seg   |

| 1 -<br>Other  | 1 -<br>Write | 1 -<br>RMW     | 10<br>11       | 01 - 10 Byte<br>10 - 16 Byte<br>11 - 32 Byte                               | es<br>es* |                                                       | text Ctl<br>Access<br>er |

|               |              |                | *              | Not impleme                                                                | ented     | ACD 15<br>00-Res<br>01-Res<br>10-Res<br>11-Int<br>Reg | erved<br>erved<br>erved  |

Table See ACD Specification Encoding

.

.

TABLE 4-2 tion (see Figure ICS). Notice that under most conditions ICS has IPC significance for more than one It is important to note that a valid low cycle. during any cycle with IPC significance will signal the processor that an IPC has been received. An iAPX 432 processor is required to record and service only one IPC at a time. Logic in the interconnect system must record and sequence multiple (possibly simultaneous) IPC occurences to the processor. Thus the logic that forms ICS must accomodate global and local IPC arrivals and requests for reconfiguration as individual events:

- Assert IPC significance on ICS for the arrival of an IPC.

- 2. When the iAPX 432 processor reads interconnect address register 2, it will respond to one of the status bits for the IPC signalled on ICS in the following order:

Bit 2 (l=reconfigure, 0=Do not reconfigure)

Bit 1 (1=global IPC arrived, 0= No global IPC)

Bit 0 (1= Local IPC arrived, 0= No local IPC)

- 3. The logic in the interconnect system must clear the highest order status bit that was serviced by the iAPX 432 processor and if additional IPC information has arrived the interconnect system logic must signal an additional IPC indication to the iAPX 432 processor.

- PRQ (Processor Packet Bus Request) -- PRQ is normally low and can go high only during Tl, T2 and Tvo. High levels during Tvo and Tl indicate the first cycle of an access. A high level during T2 indicates that the TABLE 4-3 current cycle is to be cancelled. See Figure PRQ.

- BOUT (Enable Buffered Outputs) -- BOUT is provided to control external buffers when they are present. Table BOUT and the waveforms show its state under various conditions. Note that high to low transitions of BOUT will occur during T3 (when required) and low to high during Ti (when required). Refer to TABLE 4-4.

figure 4-3 State Diagram for Processor Packet Bus

Table 4-1 ACD Specification Encoding

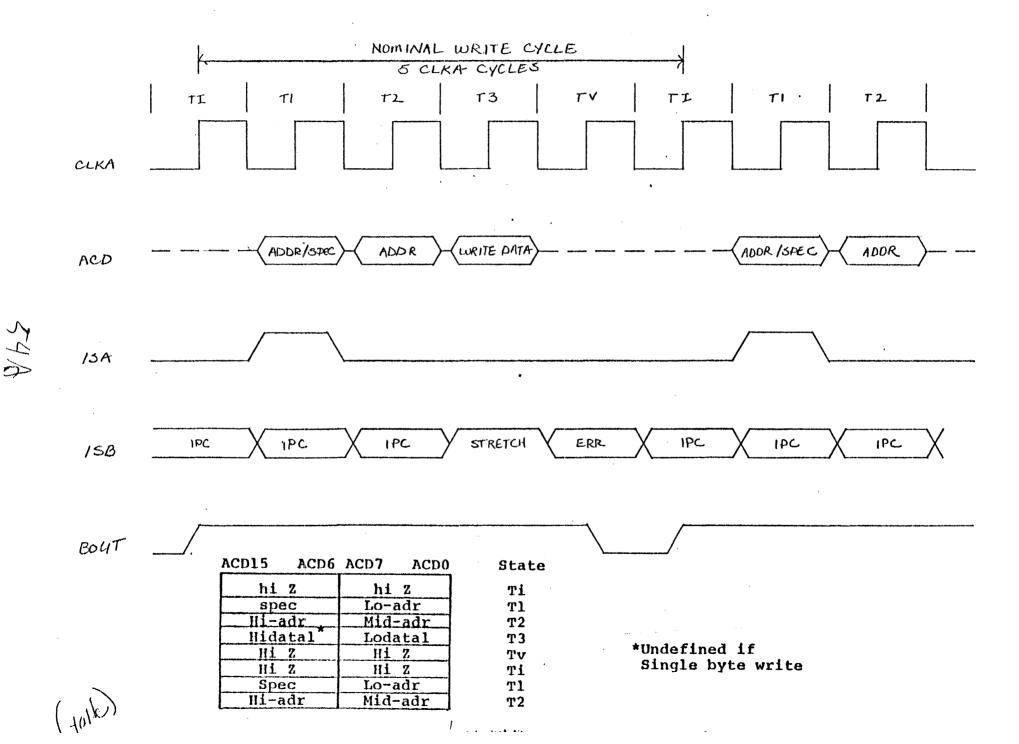

Figure 4-4 Nominal Write Cycle Timing

|                       | LEVEL                                               |                                            |

|-----------------------|-----------------------------------------------------|--------------------------------------------|

| ``                    | HIGH LOW                                            | STATE                                      |

| IPC<br>STRETCH<br>ERR | NONE WAITING<br>DON'T STRETCH<br>BUS ERROR NO ERROR | Ti, T1, T2* See Note.<br>T3, Tw<br>Tv, Tvo |

\*Note: ICS has no significance in a cycle following a T2 where PRQ is asserted (cancelled access) or in any cycle during which HERR/ is asserted.

# TABLE 4-2 - ICS Interpretation

.

| <u>State</u>                      | PRQ                             | <u>Condition</u>                                                                                                  |

|-----------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Ti<br>T1<br>T2<br>T3<br>Tv<br>Tvo | 0<br>1<br>0<br>1<br>0<br>0<br>1 | Always<br>Initiate access<br>Continue access<br>. Cancel access<br>Always<br>Always<br>Initiate overlapped access |

# TABLE 4-3 PRQ Interpretation

| BOUT  | High       | Low        |  |

|-------|------------|------------|--|

| Write | Always     | Never      |  |

| Read  | Ti, T1, T2 | T3, Tv, Tw |  |

# TABLE 4-4 BOUT INTERPRETATION

|                   | PROCESSOR                   |              | SLAV            | 'E           |

|-------------------|-----------------------------|--------------|-----------------|--------------|

| Inputs<br>Sampled | ACD:<br>Others:             | CLKA<br>CLKA | A11:            | CLKB         |

| Outputs<br>Driven | All (except BOUT):<br>BOUT: | CLKA<br>CLKA | ACD:<br>Others: | CLKB<br>CLKB |

iAPX 432 SIGNALLING SCHEME

1

Table iAPX 432 Component Signalling Scheme

Figure 4-5 Stretched Write Cycle Timing

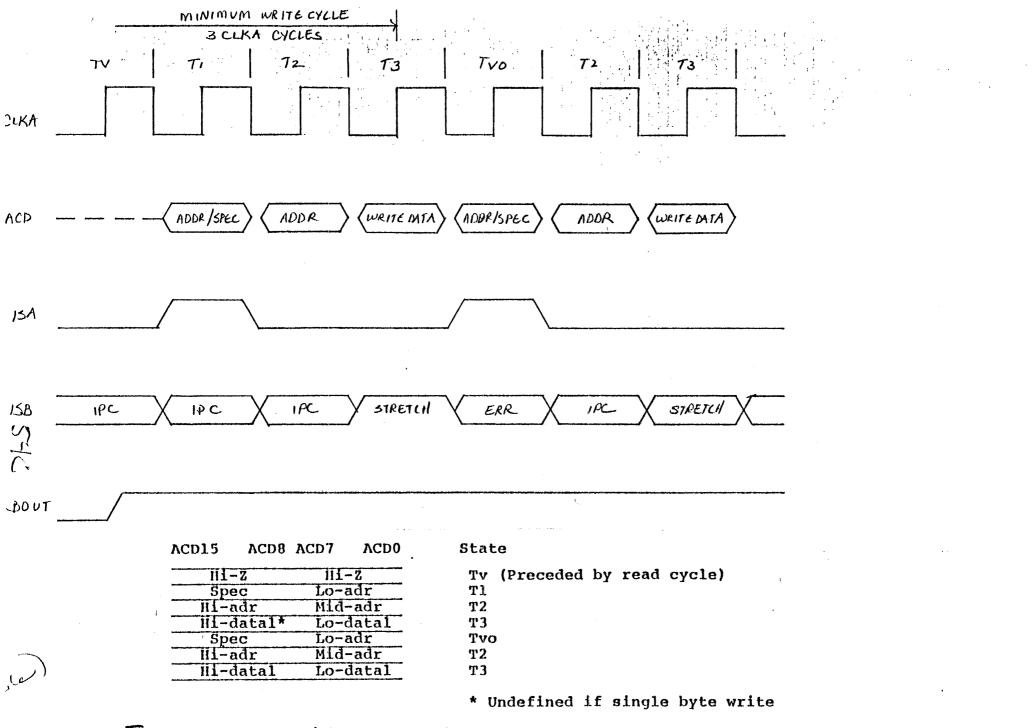

Figure 4-6 Minimum Write Cycle Timing

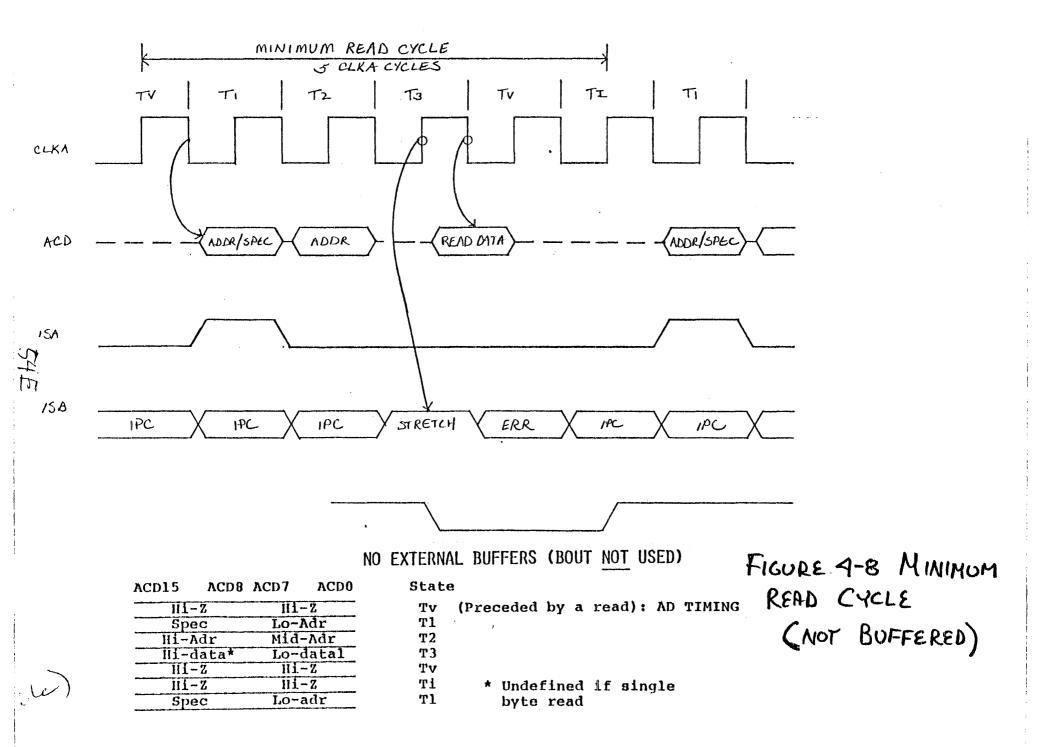

Figure 4-8 Minimum Read Timing/No External Buffers (BOUT not used)

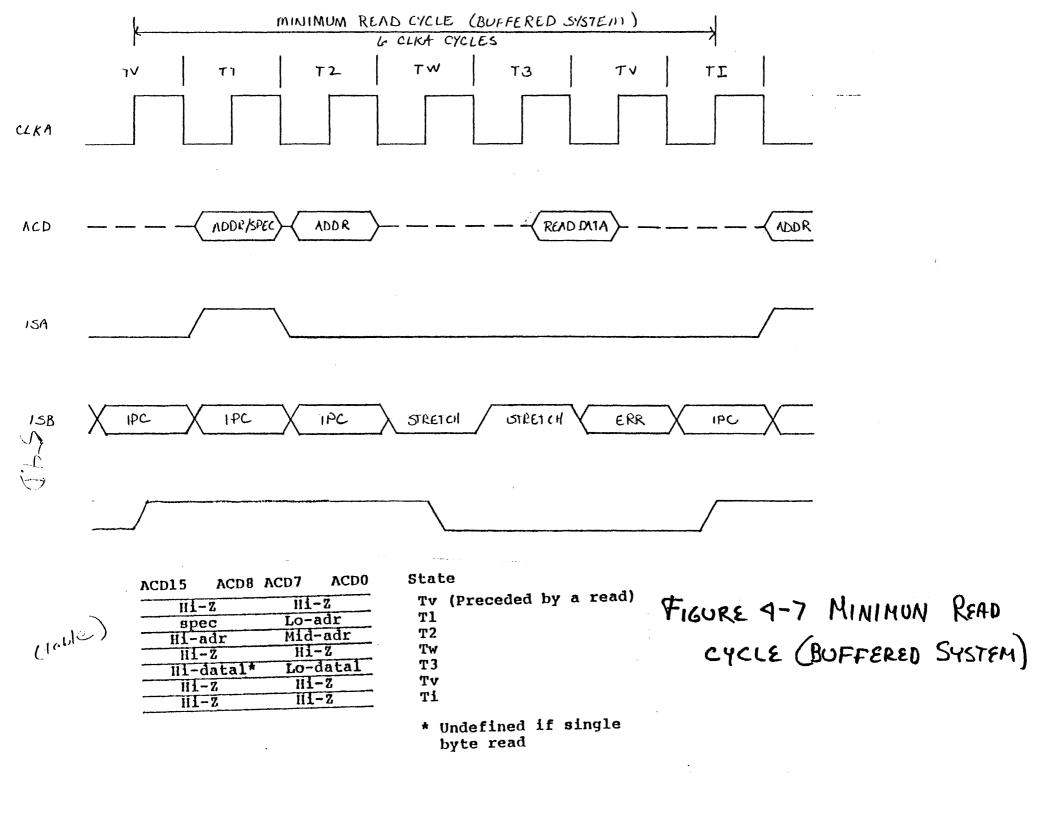

Figure 4-7 Minimum Read Cycle (Buffered System)

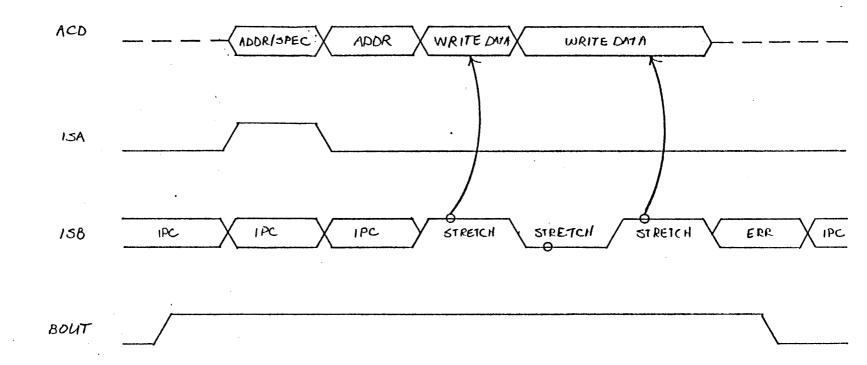

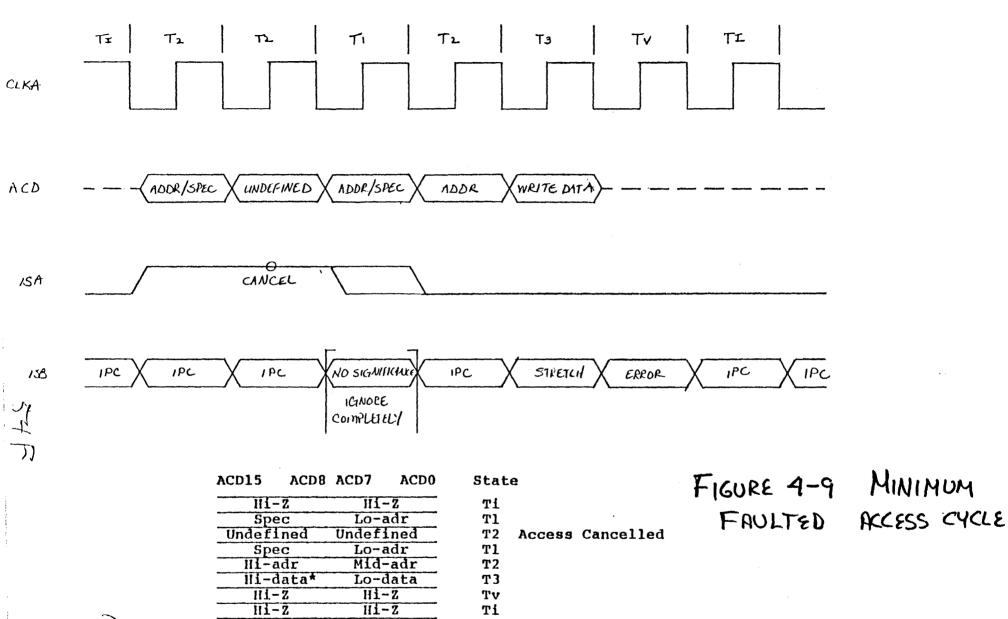

Figure 4-9 Minimum Faulted Access Cycle Timing (PRQ Cancellation)

# Processor Packet Bus Timing Relationships

All timing relationships on the processor packet bus are derived from a simple scheme and related to Figure 4-3. Each timing diagram shown in the following pages provides a separate table illustrating the various system states during the cycle. This approach to transfer timing was designed to allow maximum time for the transfer to occur and yet guarantee hold time.

Any agent connected to the processor packet bus is recognized as either a processor or a slave. Examples of processors are the GDP and the IP. A memory system provides an example of a slave.

FIGURE 4-4 NOMINAL WRITE CYCLE TIMING

| ACD15    | ACD8  | ACD7 | ACD0  |

|----------|-------|------|-------|

| hi-      | ·Z    | hi   |       |

| spe      | C     | Lo-a | adr   |

| Hi-a     |       | Mid  | -adr  |

| H1-d     | latal | Lo-o | latal |

| HI-d     | lata1 | Lo-o | lata2 |

| Hi-data2 |       | Lo-o | lata2 |

| H1-Z     |       | Hi   | -Z    |

| H1-      | 2     | HÍ   | - Z   |

State Ti Tl T2

> T3 Tw T3 Tv

# FIGURE 4-5 STRETCHED WRITE CYCLE TINING

STRETCHED WRITE CYCLE TIMING

FIGURE 4-6 MININUM WRITE CYCLE TIMING

\* Undefined if single > byte write

1

(10 le)

In all tranfers between a processor and a slave, the data to be driven are clocked three-quarters of a cycle before they are to be sampled. The BOUT timing is unique because BOUT is intended as a direction control for external buffers.

Detailed set-up and hold times depend on the processor implementation and can be found in the A.C. characteristics section.

Note that in all transfers between a processor and a slave, data is clocked three quarters of a cycle before it is to be sampled. This allows adequate time for the transfer and ensures sufficient hold time after sampling.

Table 4-2 ICS Interpretation

Table 4-3 PRQ Interpretation

Table 4-4 BOUT

Table 4-5 iAPX 432 Component Signaling Scheme

### CHAPTER 5

# AN iAPX 432 MULTIPROCESSOR SYSTEM IMPLEMENTATION

The prototype system described here is a simple but functional multiprocessor system that demonstrates the major characteristics of iAPX 432 system implementations.

The first section of this Chapter deals with the processor component interconnection and inspects the associated Interconnect Status (ICS) logic, the Processor Request (PRQ) logic, and the Interconnect Processor (IPC) logic of iAPX 432 systems.

The second section describes the memory system logic and includes a discussion of the system clock generator, the PCLK generator, and a static byte-memory system. This section also discusses the important concepts of memory alignment, multibyte sequencing, and peripheral subsystem connections.

# SYSTEM DESCRIPTION

The iAPX 432 demonstration system contains one General Data

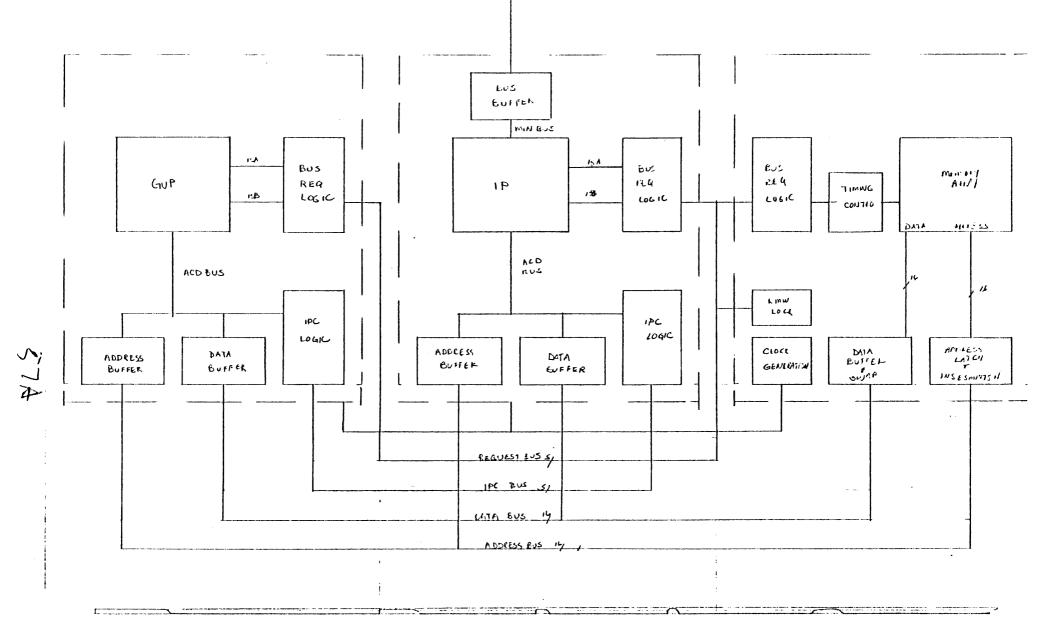

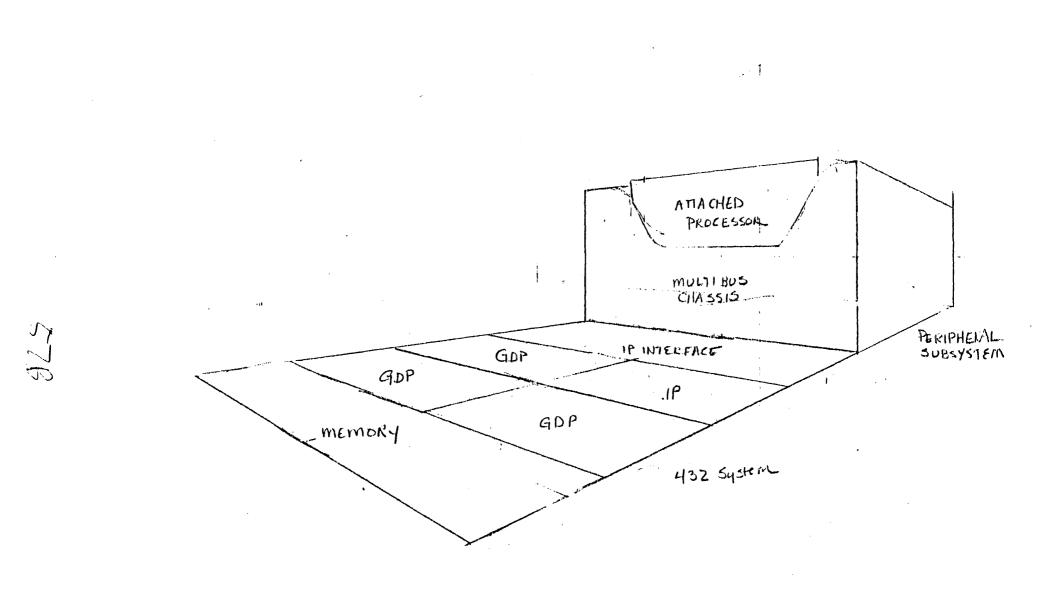

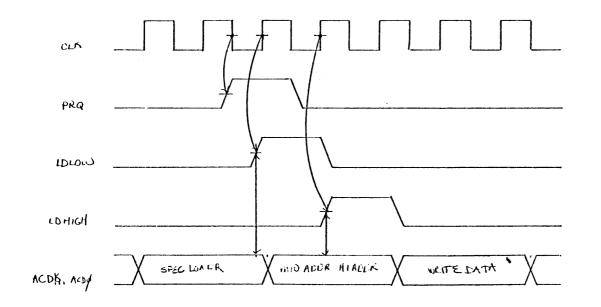

Processor (GDP, consisting of an Intel iAPX 43201/43202 device pair), one Interface Processor (43203 IP device), and a 2147-based static memory system. This system is capable of supporting a total of four attached processors. The IP connects via cabling to the Multibus interface of a peripheral subsystem. Figure 5-1 is a block diagram of the two-processor iAPX 432 system. Figure 5-2 shows the physical partitioning of the system.

Each processor provides demultiplexing and buffering logic for the processor packet bus, IPC logic, and bus request logic. The memory system contains the system clock generator, the bus arbitration unit, the memory array, the memory sequencer, and bus buffering logic.

Figure 5-1 Prototype System Block Diagram

Figure 5-2 Physical System Partitioning

# PROCESSOR COMPONENT INTERCONNECTION

iAPX 432 processor components share some common requirements in the system described. Refer to Figure 5-11 and Figure 5-12 (Appended to this Chapter) for schematics of the two

FIGURE 5-1 BLOCK DIAGRAM (TWO PROCESSOR 432 SYSTEM)