## iAPX 432 INTERCONNECT ARCHITECTURE REFERENCE MANUAL

## iAPX 432 INTERCONNECT ARCHITECTURE REFERENCE MANUAL

Order Number: 172487-001

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication, or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BXP<br>CREDIT                                     | int <sub>e</sub> 1BOS<br>Intelevision | MCS <sup>R</sup><br>Megachassis |

|---------------------------------------------------|---------------------------------------|---------------------------------|

| iR                                                | int <sub>e</sub> ligent Identifier    | MICROMAINFRAME                  |

| ICE                                               | inteligent Programming                | MULTIBUS <sup>R</sup>           |

| iCS                                               | Intellec <sup>R</sup>                 | MULT ICHANNEL                   |

| iDBP                                              | Intellink                             | MULTIMODULE                     |

| idis                                              | i PDS                                 | Plug_A_Bubble                   |

| i <sub>m</sub> <sup>R</sup><br>I <sup>2</sup> ICE | iRMX                                  | PROMPT                          |

| IZICE                                             | iSBC <sup>R</sup>                     | Ripplemode                      |

| ILBX                                              | iSBX                                  | RMX/80                          |

| iMMX                                              | iSDM                                  | System 2000 <sup>R</sup>        |

| Insite                                            | iSXM                                  | UPI                             |

| int <sub>el</sub> R                               | Library Manager                       | RUPI                            |

and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or RMX and a numerical suffix.

Ada is a registered trademark of the Department of Defense (Ada Joint Program Office).

VAX and VMS are registered trademarks of Digital Equipment Corporation.

| REV. | REVISION HISTORY | DATE  |

|------|------------------|-------|

| -001 | Original Issue   | 12/82 |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

|      |                  |       |

This manual describes the iAPX 432 interconnect architecture. It is assumed that the reader is already familiar with other Intel literature related to the iAPX 432 system. A list of references is provided below.

#### Related Publications

For general information about the iAPX 432 system:

<u>iAPX 432 General Data Processor Architecture Reference Manual,</u> Order Number 171860.

iAPX 432 Interface Processor Architecture Reference Manual, Order Nunber 171863.

For detailed information about iAPX 432 processor components that may be used with the interconnect architecture, refer to:

iAPX 43201/43202 General Data Processor Data Sheet, Order Number 171873.

iAPX 43203 Interface Processor Data Sheet, Order Number 171874.

For more information about iAPX 432 interconnect components, refer to:

iAPX 43204/43205 Data Sheet, Order Number 172866, which describes the Bus Interface Unit (BIU) and Memory Control Unit (MCU) interconnect components.

For more information on the general topic of fault tolerance, refer to:

The Theory and Practice of Reliable System Design, Sieworik and Swartz, 1982, Digital Press. This book contains a variety of background information. Chapter 18 is devoted to the iAPX 432: "A Design Method for High-Reliability Systems: The Intel 432", Daniel P. Sieworik and David P. Johnson.

| CHAPTER 1<br>KEY CONCEPTS                                                                                                                                                                                                                                                                                                                    | PAGE                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Introduction<br>Bus Interface Unit<br>Memory Control Unit<br>Memory Bus<br>Interleaving<br>Request/Reply Pairs and Pipelining<br>Interprocessor Communication<br>Interconnect Registers<br>Fault-Tolerant Systems<br>Error Confinement<br>Reporting<br>Recovery<br>Latent Faults<br>Fault-Tolerant System Design Responsibilities<br>Summary | 1-1<br>1-3<br>1-4<br>1-4<br>1-5<br>1-5<br>1-5<br>1-6<br>1-7<br>1-11<br>1-12<br>1-18<br>1-20 |

| CHAPTER 2<br>FUNDAMENTAL FAULT HANDLING CONCEPTS<br>A Model for Fault Handling<br>Philosophy<br>Implementation                                                                                                                                                                                                                               | 2-3                                                                                         |

| CHAPTER 3<br>FUNDAMENTAL SYSTEM STRUCTURES<br>Introduction<br>Error Confinement<br>Reporting<br>Recovery                                                                                                                                                                                                                                     | 3-1<br>3-3<br>3-5                                                                           |

| Memory Confinement Area                                                                                                                                                                                                                                                                                                                      | 4-1<br>4-1<br>4-3<br>4-5<br>4-6<br>4-8<br>4-9                                               |

### GE

| CHAPTER 4 - Continued<br>OVERVIEW OF THE FAULT HANDLING MECHANISMS                             | PAGE         |

|------------------------------------------------------------------------------------------------|--------------|

| Error Reporting<br>Topology of the Reporting Network<br>Error Reporting Protocol<br>Error Logs | 4–10<br>4–11 |

| Recovery                                                                                       | 4-13         |

| Redundant Resources                                                                            |              |

| Optimization                                                                                   |              |

| Lock Step Operation                                                                            |              |

| Graceful Degradation                                                                           |              |

| Recovery                                                                                       | 4-10         |

| Configuration Examples                                                                         |              |

| Example System Operation                                                                       |              |

| A Day in the Life of an FT System                                                              | 4-23         |

#### CHAPTER 5

### CONFINEMENT AREAS/DETECTION MECHANISMS

| Introduction                | 5-1          |

|-----------------------------|--------------|

| GDP Confinement Area        | 5-1          |

| Management and Testing      | 5 <b>-</b> 3 |

| IP Confinement Area         | 5-4          |

| Management and Testing      | 5-5          |

| Memory Confinement Area     | 5-6          |

| Memory Array                | 5-10         |

| Management and Testing      | 5-11         |

| Memory Bus Confinement Area | 5-13         |

| Management and Testing      | 5-18         |

| Component Summary           | 5-20         |

## CHAPTER 6

## REDUNDANCY

| Overview                                   | ,-1 |

|--------------------------------------------|-----|

| Redundancy for Transient Errors            | -2  |

| Retry Buffers                              | -2  |

| Memory Array Correction By Way of ECC Code |     |

| GDP Module Redundancy                      | -2  |

| Startup                                    | -2  |

| Lock Step Operation                        |     |

| Deactivation                               | -5  |

| Management and Testing                     | -6  |

| IP Module Redundancy 6                     |     |

| Startup and Deactivation                   | -7  |

| Lock Step Operation                        |     |

| Management and Testing 6                   |     |

| CHAPTER 6 - Continued<br>REDUNDANCY                                                                                                                                                                   | PAGE                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Memory Module Redundancy<br>Spare Bit<br>Memory Module Shadowing<br>Memory Bus Redundancy<br>Bus Characteristics<br>BIU Characteristics<br>MCU Characteristics<br>Management and Testing              | 6-7<br>6-8<br>6-11<br>6-11<br>6-11<br>6-12                          |

| CHAPTER 7<br>ERROR REPORTING                                                                                                                                                                          |                                                                     |

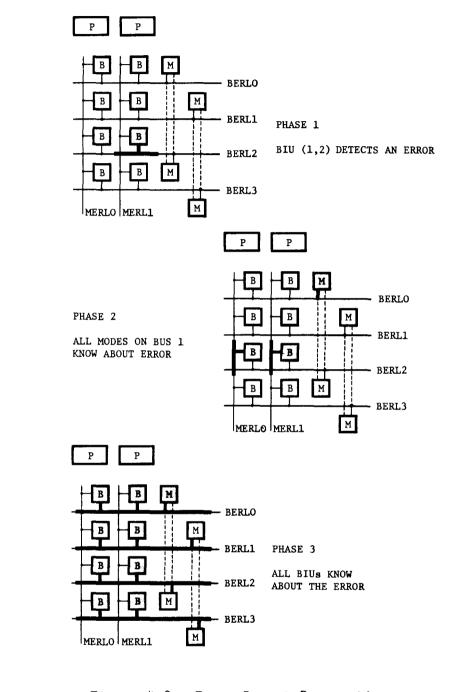

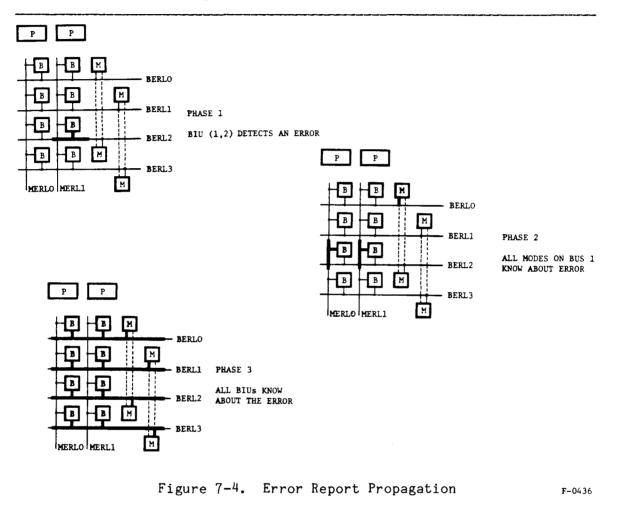

| Overview<br>Topology of the Reporting Network<br>Error Message Format<br>Error Reporting Protocol<br>Phase 1<br>Phase 2<br>Phase 3<br>FIFO Ordering<br>Priority Ordering<br>Definition of Error Types | 7-1<br>7-5<br>7-6<br>7-6<br>7-7<br>7-7<br>7-7<br>7-8<br>7-8<br>7-10 |

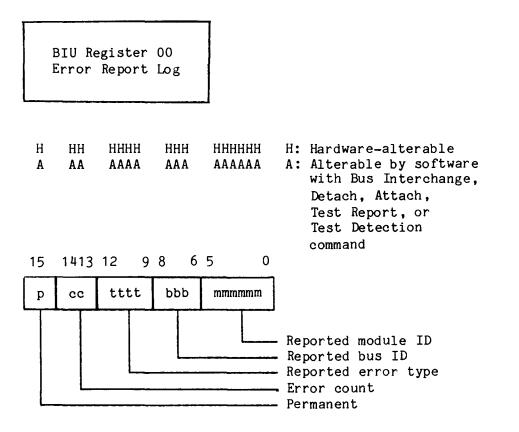

| Error Report Log<br>Array Error Log<br>Management and Testing                                                                                                                                         | 7-14                                                                |

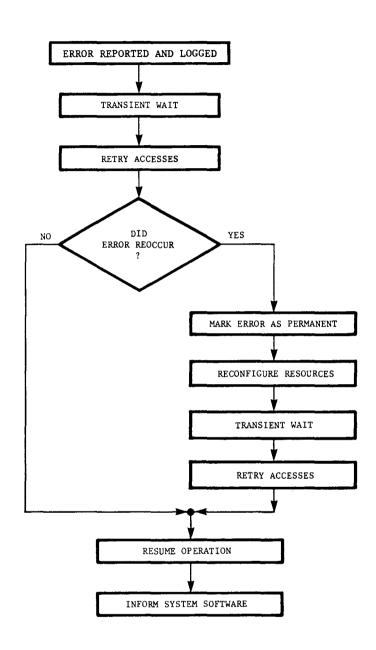

# CHAPTER 8 RECOVERY

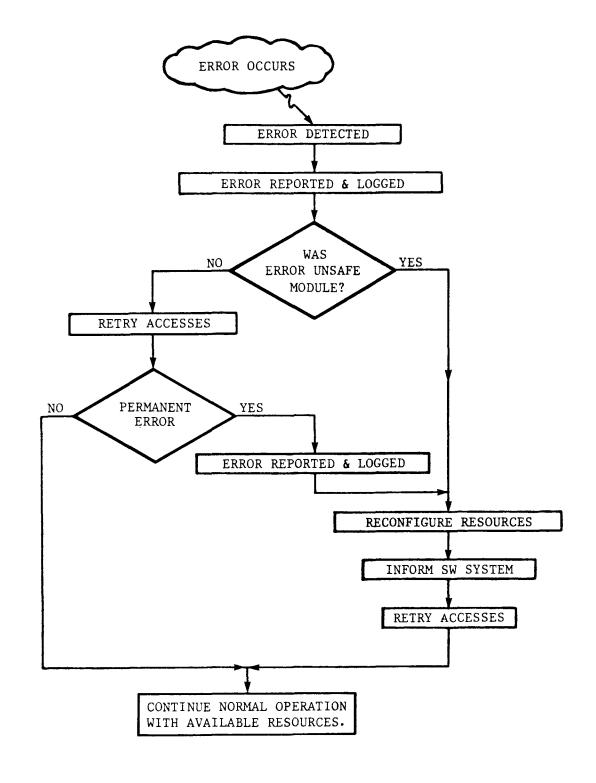

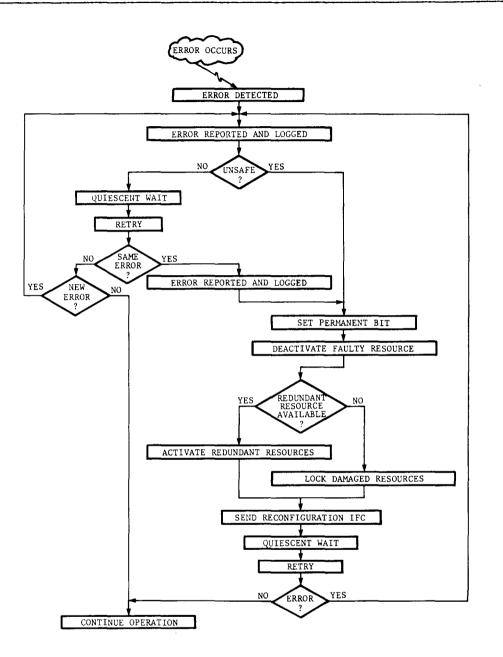

| Overview                                   | 8-1  |

|--------------------------------------------|------|

| Unsafe Module Decision                     | 8–1  |

| Retry Sequence                             | 8-3  |

| Permanent Error Decision                   | 8-6  |

| Isolation of Faulty Confinement Area       | 8-6  |

| GDP or IP Module                           | 8-7  |

| Memory Module                              | 8-7  |

| Memory Bus                                 | 8-7  |

| Resource Reconfiguration                   |      |

| Activate Redundant Resources               | 8-8  |

| GDP, IP, or Memory Module Confinement Area | 8-8  |

| Memory Bus Confinement Area                | 8-8  |

| Lock-Damaged Resources                     | 8-9  |

| Communication with System Software         |      |

| Recovery in the Memory Array               | 8-10 |

| Summary                                    |      |

| Management and Testing                     | 8-12 |

|                                            |      |

|   | CHAPTER 9<br>SPECIAL CASES OF INTEREST                                                                                                      | PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Initialization<br>Interconnect Register Accesses<br>Interprocessor Communication<br>Multiple Module Access<br>Activation of Spare Resources | 9-2<br>9-3<br>9-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | CHAPTER 10<br>SOFTWARE INTERFACE SUMMARY                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | Diagnostic                                                                                                                                  | 10-1<br>10-1<br>10-3<br>10-3<br>10-3<br>10-3<br>10-3<br>10-4<br>10-5<br>10-5<br>10-5<br>10-5<br>10-6<br>10-6<br>10-6<br>10-6<br>10-7<br>10-7<br>10-7<br>10-7<br>10-7<br>10-7<br>10-7<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-8<br>10-10-10-10-10-10-10-10-10-10-10-10-10-1 |

| i | Software Support                                                                                                                            | 10-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                 | PAGE         |

|-------------------------------------------------|--------------|

| APPENDIX A<br>iAPX 43204/43205 REGISTER SUMMARY | A-1          |

| APPENDIX B<br>iAPX 43204 BIU REGISTERS          | B <b>-</b> 1 |

| APPENDIX C<br>iAPX 43205 MCU REGISTERS          | C-1          |

| APPENDIX D<br>EXTERNAL INITIALIZATION           | D <b>-</b> 1 |

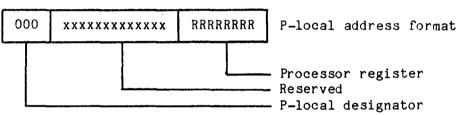

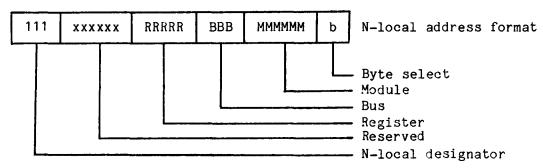

| APPENDIX E<br>ADDRESS FORMATS                   | E-1          |

| APPENDIX F<br>MEMORY BUS                        | F-1          |

•

FIGURE

## TITLE

#### PAGE

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>1-10                                 | Modular Expansion<br>iAPX 432 Interconnect Topology<br>iAPX 432 Confinement Areas<br>FRC Configuration Pairing<br>Confinement Area Operation<br>Three-Phase Error Reporting Mechanism<br>QMR Configuration Pairing<br>Bus Reconfiguration<br>Module Reconfiguration<br>Fault-Tolerant Alternatives                      | 1-2<br>1-3<br>1-8<br>1-9<br>1-10<br>1-12<br>1-14<br>1-15<br>1-16<br>1-17                                 |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| 2 <b>-</b> 1<br>2 <b>-</b> 2                                                                        | Fault Handling Model<br>Separation of HW and SW Layers                                                                                                                                                                                                                                                                  |                                                                                                          |

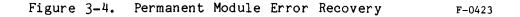

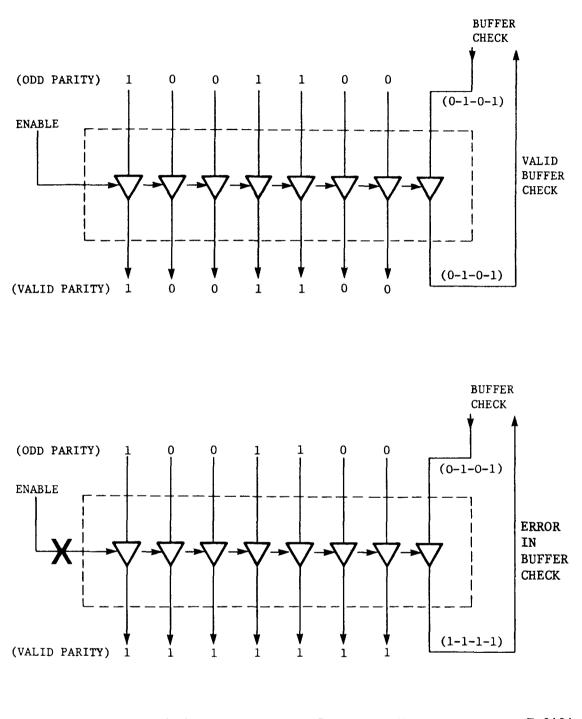

| 3–1<br>3–2<br>3–3<br>3–4                                                                            | iAPX 432 Confinement Areas<br>Confinement Area Operation - An Example<br>Permanent Bus Error Recovery<br>Permanent Module Error Recovery                                                                                                                                                                                | 3 <b>-</b> 4<br>3 <b>-</b> 6                                                                             |

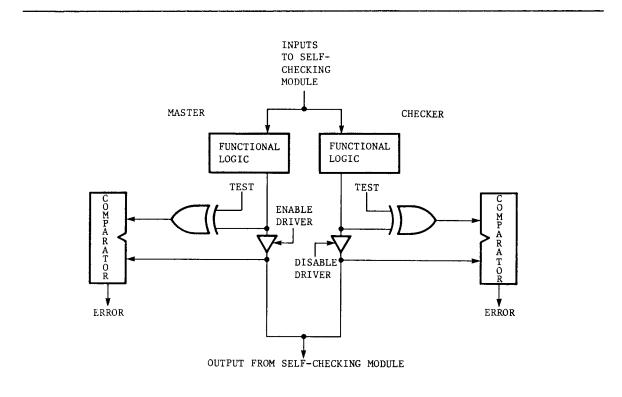

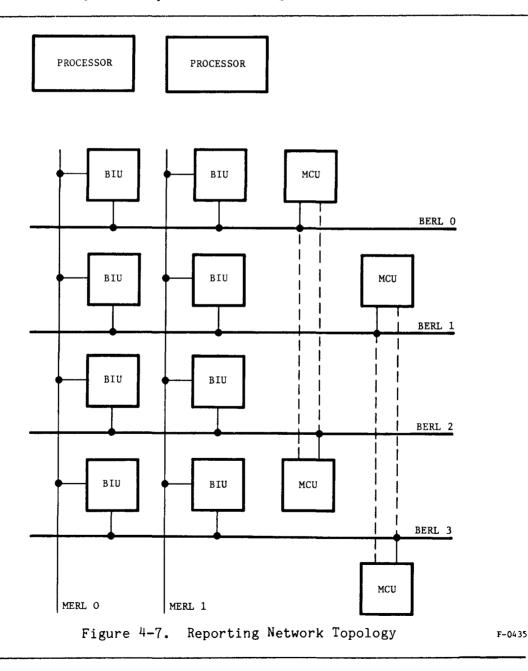

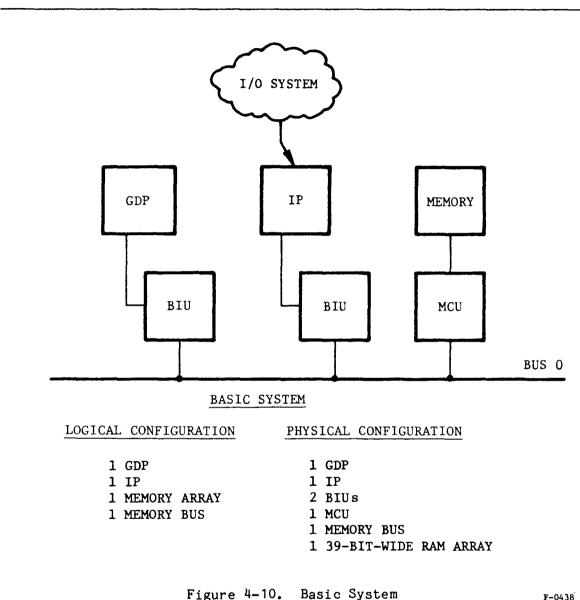

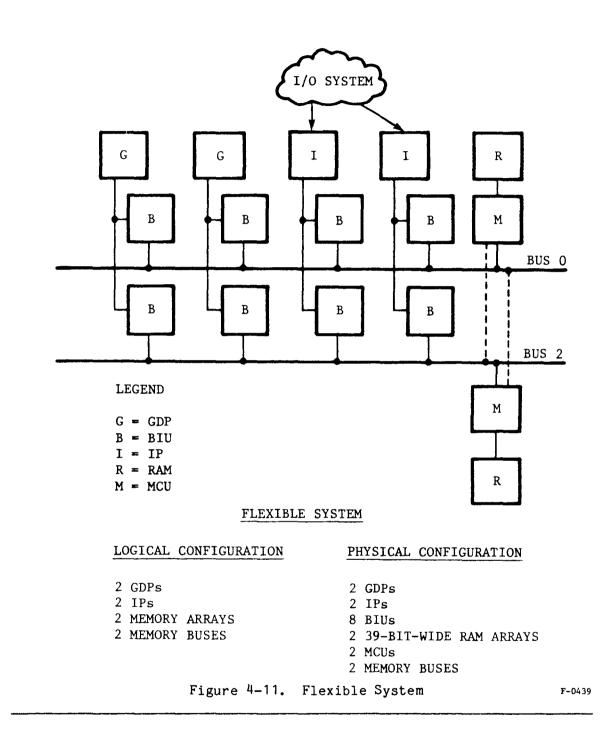

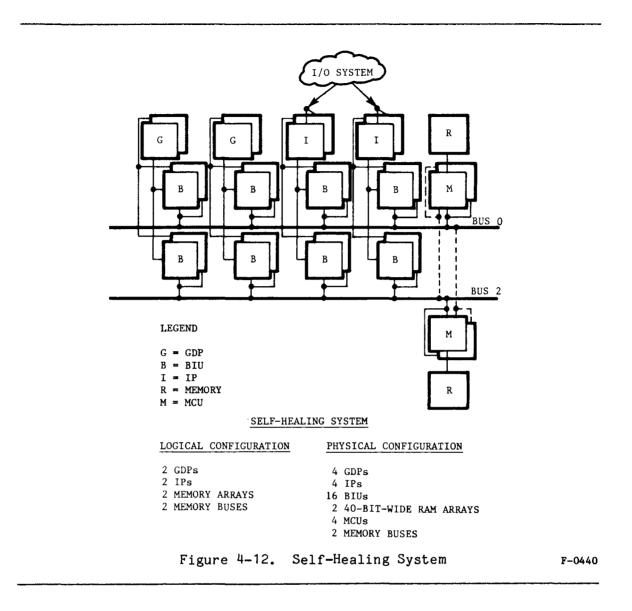

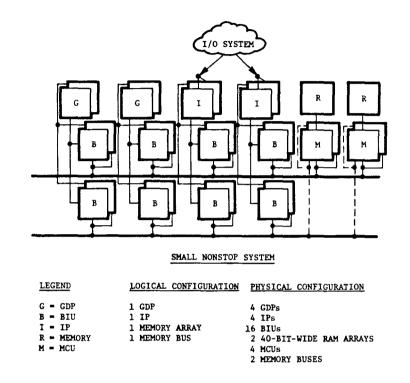

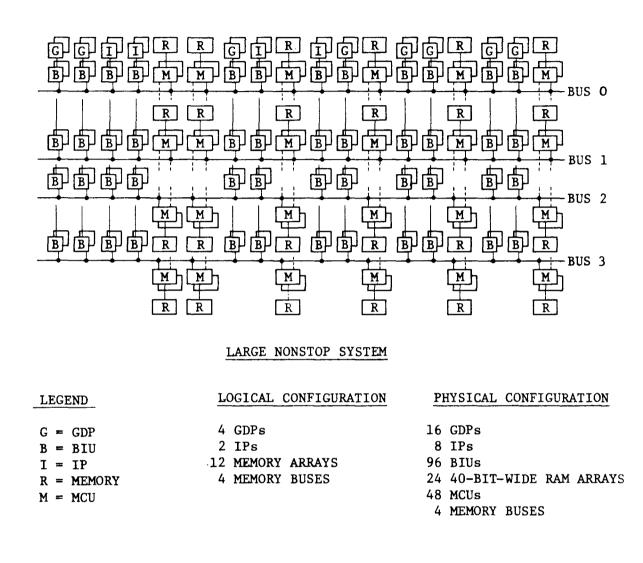

| 4-1<br>4-2<br>4-3<br>4-4<br>4-5<br>4-6<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-13<br>4-14 | Functional Redundancy Checking<br>GDP Confinement Area<br>The IP Confinement Area<br>Memory Confinement Area<br>Memory Bus Confinement Area<br>Reporting Network Topology<br>Error Report Propagation<br>High-Level Recovery Sequence<br>Basic System<br>Flexible System<br>Self-Healing System<br>Small Nonstop System | 4-2<br>4-4<br>4-5<br>4-6<br>4-10<br>4-12<br>4-10<br>4-12<br>4-17<br>4-18<br>4-19<br>4-20<br>4-21<br>4-22 |

| FIGURE                                        | TITLE                                                                                                                                                                                                                                                       | PAGE                            |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

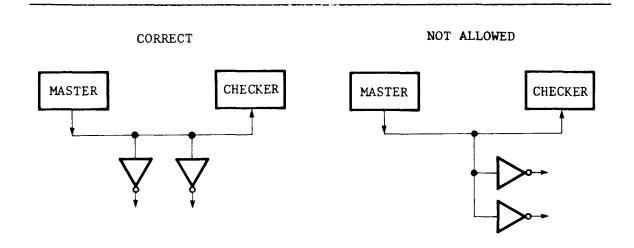

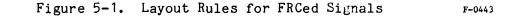

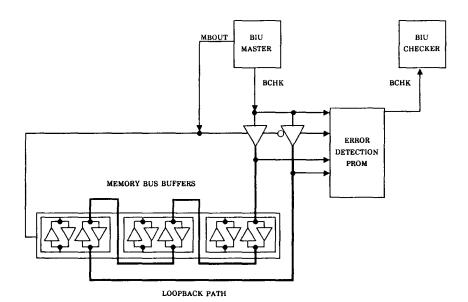

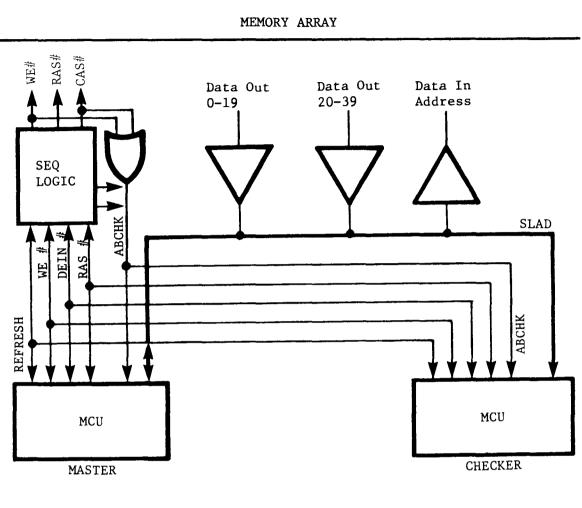

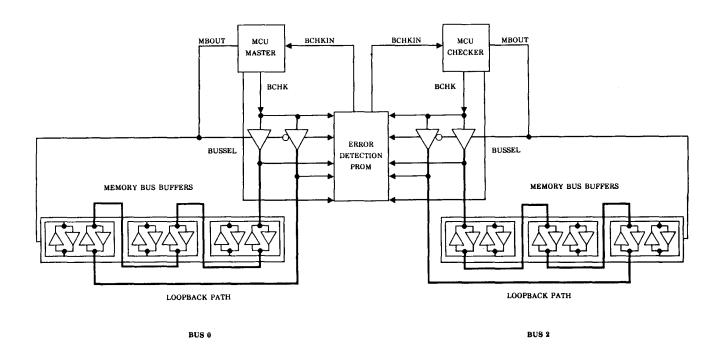

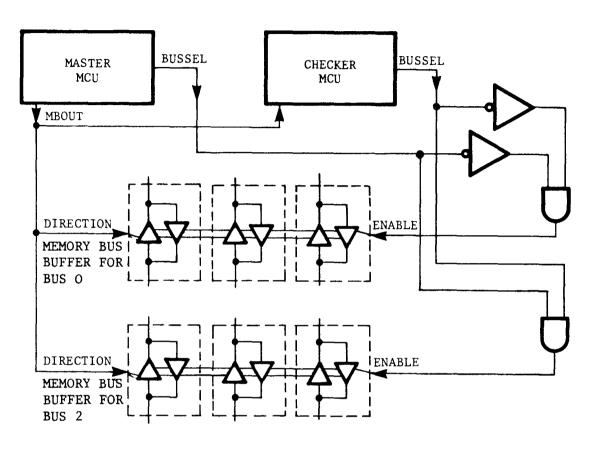

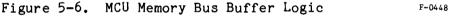

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7 | Layout Rules for FRCed Signals<br>FRC Details for the GDP Confinement Area<br>Buffer Check Detection Mechanism<br>Details of SLAD FRC Detection<br>MCU Buffer Check Connection<br>MCU Memory Bus Buffer Logic<br>Details of Arbitration Detection Mechanism | 5-2<br>5-3<br>5-7<br>5-8<br>5-9 |

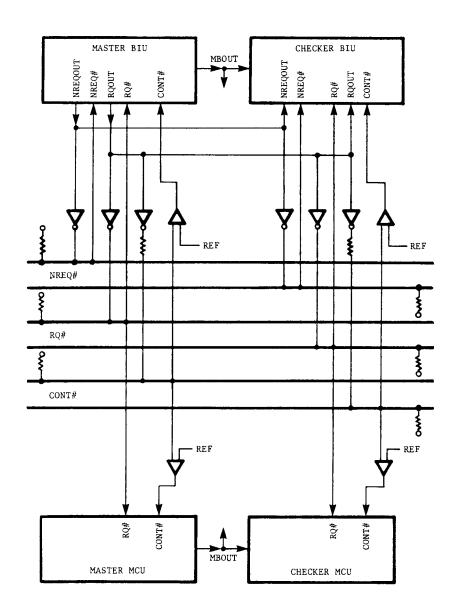

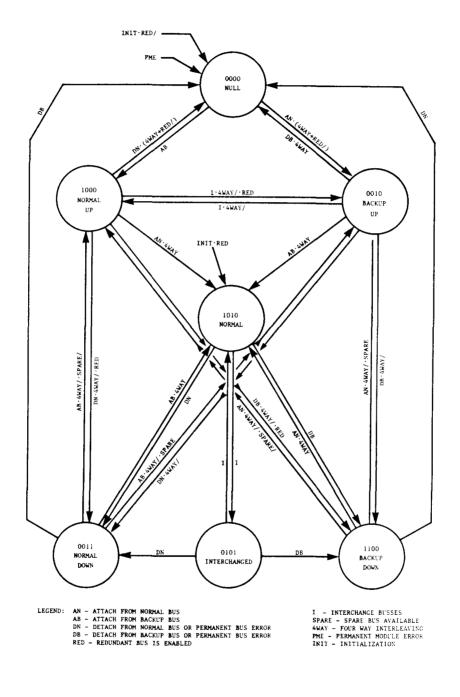

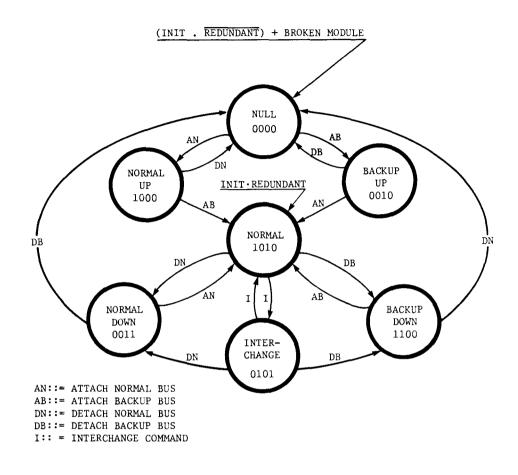

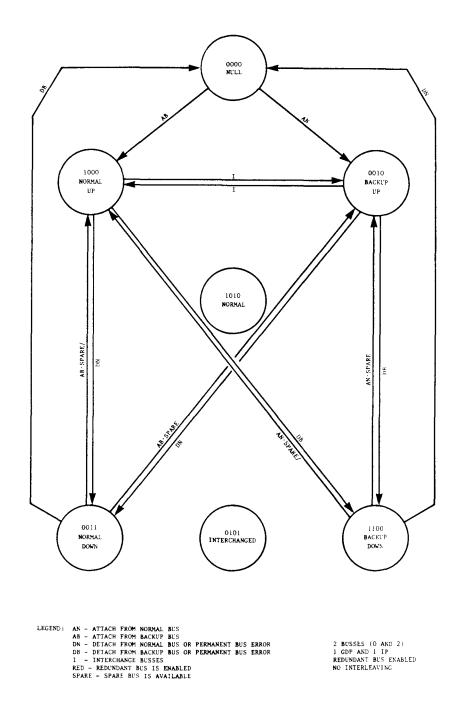

| 6–1                                           | State Diagram for Four-Way Interleaved<br>Bus Recovery                                                                                                                                                                                                      | 6-16                            |

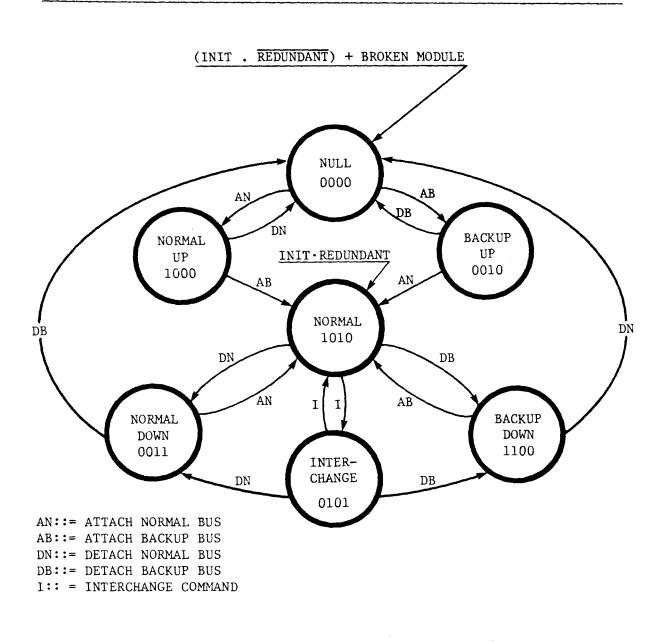

| 6-2                                           | State Diagram for Two-Way Interleaved<br>Bus Recovery                                                                                                                                                                                                       |                                 |

|                                               |                                                                                                                                                                                                                                                             |                                 |

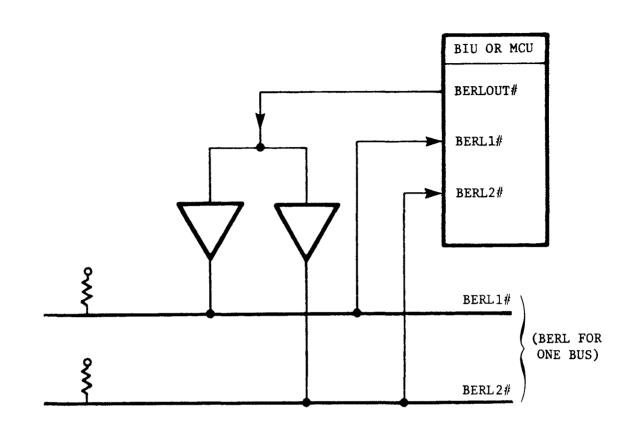

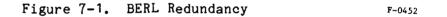

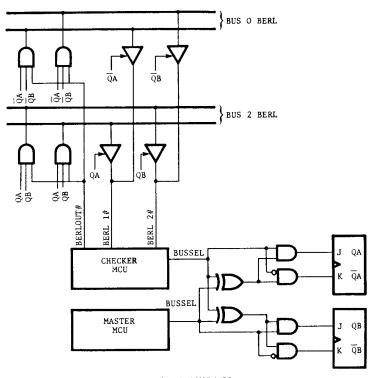

| 7-1<br>7-2                                    | BERL Redundancy<br>BIU Interfaces to Error Reporting Network                                                                                                                                                                                                |                                 |

| 7 <b>-</b> 3<br>7 <b>-</b> 4                  | MCU Interfaces to Error Reporting Network<br>Error Report Propagation                                                                                                                                                                                       |                                 |

| 8–1<br>8–2                                    | Recovery Procedure<br>Detailed Flow Diagram of the Recovery Process                                                                                                                                                                                         |                                 |

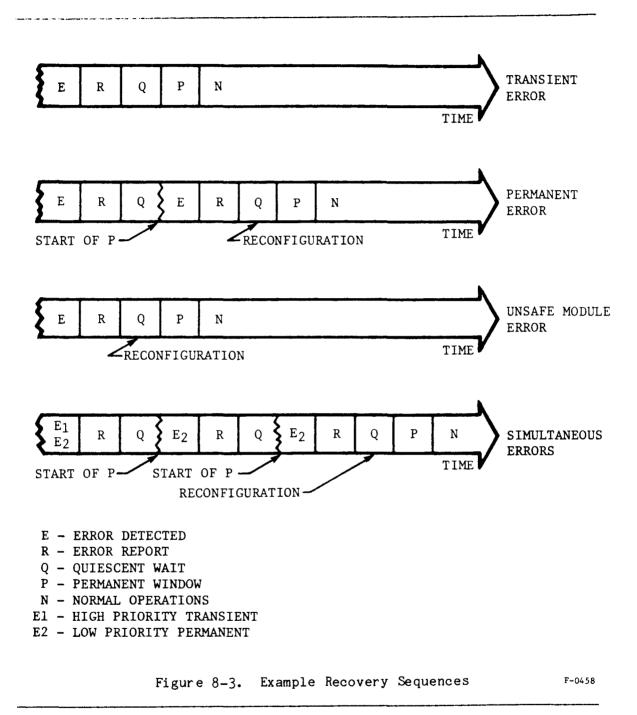

| 8-3                                           | Example Recovery Sequences                                                                                                                                                                                                                                  |                                 |

| 10-1                                          | Software Support                                                                                                                                                                                                                                            | 10–10                           |

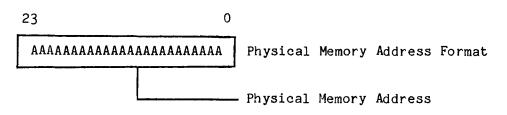

| F-1                                           | State Diagram for MACD Bus<br>Messages/Control Codes                                                                                                                                                                                                        | F-8                             |

| F <b>-</b> 2                                  | General State Machine for Memory<br>Bus Switching                                                                                                                                                                                                           |                                 |

| F-3                                           | State Machine for Large Continuous<br>Processing System                                                                                                                                                                                                     |                                 |

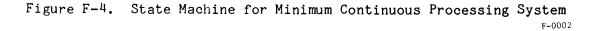

| F-4                                           | State Machine for a Minimum Continuous<br>Processing System                                                                                                                                                                                                 |                                 |

|                                               |                                                                                                                                                                                                                                                             |                                 |

TABLES

| TABLE                           | TITLE                                                                                                                                                | PAGE                           |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 1–1<br>1–2                      | Recovery Mechanisms and Coverage<br>Exercising Latent Faults                                                                                         |                                |

| 5–1                             | GDP Confinement Area Management and<br>Testing Summary                                                                                               | 5-5                            |

| 5-2                             | IP Confinement Area Management and                                                                                                                   |                                |

| 5-3                             | Testing Summary<br>Memory Confinement Area Management and                                                                                            |                                |

| 5-4                             | Testing Summary<br>Bus Confinement Area Management and                                                                                               | 5-13                           |

| 5 <b>-</b> 5                    | Testing Summary<br>Summary of BIU FRC Detection                                                                                                      |                                |

| 5–6<br>5–7                      | Summary of MCU FRC Detection<br>Summary of IP FRC Detection                                                                                          | 5-21                           |

| 6–1<br>6–2                      | Memory Bus Redundancy Options<br>Description of the Bus States                                                                                       |                                |

| 7-1<br>7-2<br>7-3<br>7-4        | Error Type Field Definition<br>Motivation for Error Types<br>Syndrome Bit Mapping<br>Data Field for Test Report Command                              | 7 <b>-</b> 11<br>7 <b>-</b> 16 |

| A-1                             | iAPX 43204 Bus Interface Unit                                                                                                                        |                                |

| A-2                             | Register Summary<br>iAPX 43205 Memory Control Unit                                                                                                   | A-2                            |

|                                 | Register Summary                                                                                                                                     | <b>A-</b> 3                    |

| B-1<br>B-2<br>B-3<br>B-4<br>B-5 | BIU Register Summary<br>BIU Error Report Types<br>BIU Error Recovery Mechanisms<br>Bus State Field Encoding<br>Reordered Addresses with Interleaving | B-4<br>B-5<br>B-12             |

| C-1<br>C-2<br>C-3<br>C-4        | MCU Register Summary<br>MCU Error Report Types<br>MCU Error Recovery Mechanisms<br>Bus State Codes                                                   | C-4<br>C-5                     |

| TABLE         | TITLE                                                                                  | PAGE |

|---------------|----------------------------------------------------------------------------------------|------|

| F-2 Memory Bu | s Request Message Formats<br>s Reply Message Formats<br>s Notification Message Formats | F-6  |

#### INTRODUCTION

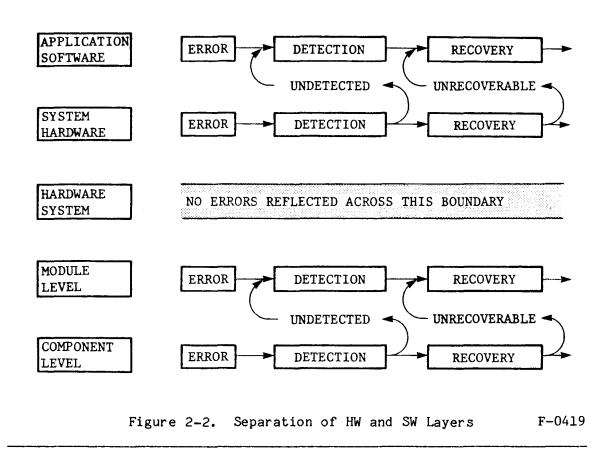

The first phase of the iAPX 432 program introduced two processor types: the General Data Processor (GDP) and the Interface Processor (IP). The GDP was implemented with two VLSI components: iAPX 43201 and iAPX The IP was implemented as a single VLSI component: the iAPX 43202 three VLSI components implement the processor 43203. These architecture for the iAPX 432. System builders have constructed multiple processor systems by surrounding the VLSI processors with discrete logic, which provided the interface to shared memory and the interprocessor communication paths. The method for interconnecting iAPX 432 processors and memories was unique for each for each system. since no standard had been defined.

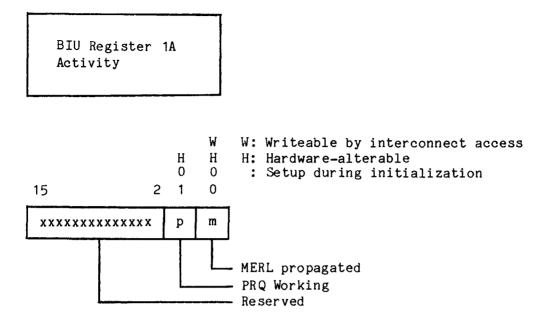

This manual describes a unifying <u>interconnect architecture</u> for building iAPX 432 systems. The interconnect architecture has been implemented in a pair of VLSI components: the iAPX 43204 Bus Interface Unit (BIU) and the iAPX 43205 Memory Control Unit (MCU). Together, these components form the basis for constructing multiple-processor iAPX 432 systems. The BIU performs as an <u>intelligent switch</u>. The MCU acts as an intelligent memory controller.

The iAPX 432 interconnect architecture provides:

- <u>Integrated fault tolerance</u>. The VLSI interconnect components (BIU/MCU) integrate all the detection and recovery logic required to build a system that can tolerate any single component failure.

- <u>Software-transparent fault tolerance</u>. Hardware performs all fault detection and recovery functions transparent to application software. The architecture never dies.

- <u>Configurability</u>. The BIU and MCU support a range of fault tolerance and performance options to meet a diverse set of cost, performance, and reliability needs.

- Standard VLSI solution. Very little external logic is required.

- <u>Reliable software</u>. The iAPX 432 system's "need to know" (capability) addressing confines errors, protecting the system from errant software.

The object-based architecture of the iAPX 432 provides a robust and flexible environment for cooperating, concurrent software systems. The iAPX 432 processors use a cooperating, self-dispatching mechanism to automatically share the workload between the available processors. The number of processors available in the system is transparent to software. The BIU and the MCU extend the logical robustness and flexibility of the iAPX 432 processors into the physical implementation of iAPX 432 systems. The BIU and MCU allow the iAPX 432 hardware to modularly and transparently extend the processing power (from 1 to 63 modules of processors or memories), bus bandwidth (1 to 8 backplane buses), and fault-tolerant capabilities of the system.

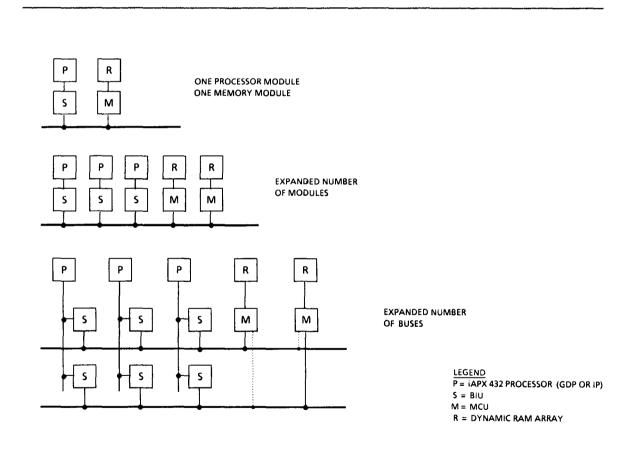

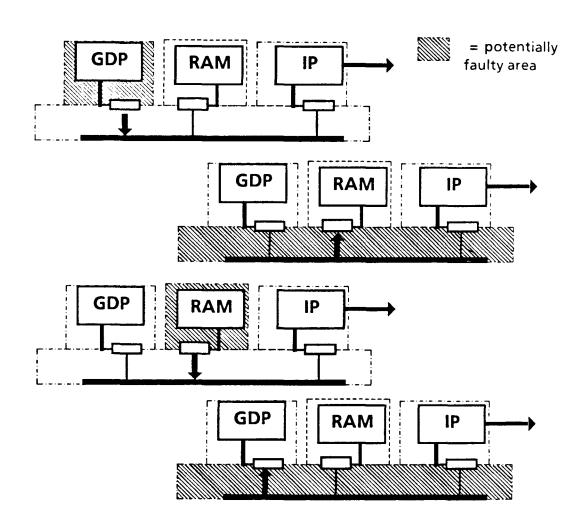

As Figure 1-1 shows, an iAPX 432 system based on the interconnect architecture may be expanded gracefully. A system with one processor and one memory may be built with a single memory bus. Transparent multiprocessing may be achieved by simply adding processor modules. When additional memory is required, memory modules may be added onto the single memory bus. When more memory bandwidth is required, additional memory (bus or buses) can be added. None of these alternative systems require any change to application software.

F-0**396**

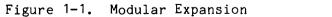

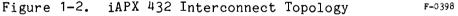

In an iAPX 432 system, each processor is unaware of the manner in which the memory address space is actually implemented. Hardware located in the BIUs determines how processor addresses are mapped to buses and memory systems. Figure 1-2 illustrates how iAPX 432 processors, BIUs, and MCUs are organized into a multiprocessor interconnect system. Each processor and its associated BIUs form a <u>module</u>. Each MCU and its associated storage array form a module. These modules form the basis for detection and confinement of errors. Every BIU and MCU constitutes a <u>node</u> in the interconnect system. A unique BIU or MCU may thus be named in a consistent way by referring to its <u>node address</u>, which consists of the number of the bus to which it is <u>attached</u> and the number of the module in which it is contained. The benefit of the unified, modular design of the iAPX 432 interconnect system is that all modules are alike -- no special backplane slots are required to change the number or mix of processors (GDPs and IPs) and memories in an iAPX 432 system.

#### BUS INTERFACE UNIT

The Bus Interface Unit or BIU provides the switching function of the iAPX 432 interconnect system. That is, it accepts the access requests from an iAPX 432 processor and, based on the physical address, it decides which memory bus(es) will be used to perform the access. The BIU is also responsible for arbitrating the usage of the memory bus.

#### MEMORY CONTROL UNIT

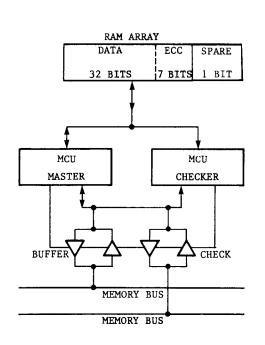

The Memory Control Unit, or MCU, interfaces memory storage arrays to the memory bus. The storage arrays will typically be constructed with high-density dynamic RAM (DRAM) components. All types of DRAMs are supported: 16K, 64K, 256K, even partially good components. The MCU manages the storage array as a logical collection of 32 data bits. 7 bits of error correcting code (ECC), and an optional spare bit. The MCU can automatically refresh the dynamic storage array. In addition. the MCU can scrub single-bit errors from the storage array as a background task. Scrubbing is accomplished by periodically reading the storage array, correcting all single-bit errors, and detecting and reporting all double-bit errors. The MCU accepts variable length data requests from the memory bus and performs the necessary access sequencing to read or write the data into the storage array. A modest amount of external logic is required to interface the MCU to the storage array RAMs -- for simple configurations, as few as 12 external TTL packages are required.

#### MEMORY BUS

The memory bus (sometimes referred to as the MACD bus) provides the principal communication path, carrying all memory access requests and interprocessor communication. The memory bus connects BIUs to MCUs. Each node in the interconnect system tracks each operation on the memory bus to which it is attached. Thus, unlike most bus protocols, each BIU and MCU keeps track all of outstanding requests on the bus -- not just the ones it made. Control for the bus is fully distributed; there is no centralized bus controller.

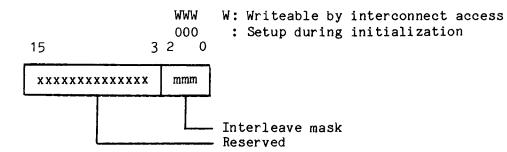

#### INTERLEAVING

When several processors in a shared memory multiprocessor system demand information from a common area of memory (e.g., a shared instruction or data segment), they tend to impede the efforts of one another. All the processors are competing for the same memory bus. The iAPX 432 interconnect system answers this problem by interleaving memory buses. Interleaving spreads the accesses to a common segment of memory across several memory buses. Different memory buses support the alternation of consecutive regions of a processor's address space. On the basis of the mid-order address bits from the processor's physical address, the BIUs control interleaving. A system designer may opt for no interleaving, two-way interleaving, or four-way interleaving under software control. Address bits 6, 7, and 8 may be used to select interleaving on 64-, 128-, or 256-byte boundaries. For example, when two-way interleaving is performed at 64-byte boundaries, a processor's requests for data between addresses 0 and 63 are served by one memory bus and those for data between addresses 64 and 127 are served by a different memory bus.

#### REQUEST/REPLY PAIRS AND PIPELINING

The interconnect system also supports pipelining on each of its memory buses. This allows several processors to issue memory requests before a memory module has performed all its previous requests. Each memory bus in an iAPX 432 interconnect system can queue a maximum of three memory requests. (That is, the maximum memory bus pipeline depth is three.) Pipelining can occur because each request from a processor is separated in time from the corresponding reply from the memory module that supports the request. Each memory access consists of a request/reply pair. Every request deepens the memory bus pipeline by one entry. Each reply removes one entry from the pipeline. All BIUs and MCUs track the state of the memory bus pipeline to which they are attached in order to determine when it is permissible to issue new requests or to return awaited replies. The memory requests are issued to a memory bus as packets of information. Each request also has a data length field. On the memory bus, data requests may be variable length. Access lengths of from 1 to 16 bytes are supported.

#### INTERPROCESSOR COMMUNICATION

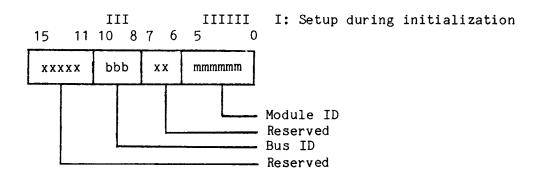

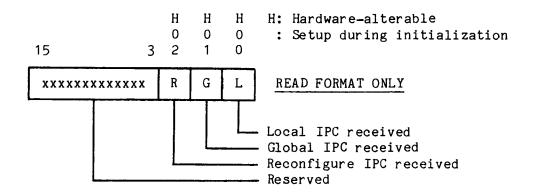

In contrast to standard systems, the iAPX 432 interconnect system also provides a facility for rapid interprocessor communication (IPC). In the iAPX 432, a processor may signal another processor or all other processors of a condition that requires attention (e.g., "stop execution", "flush caches", etc.). The IPC facility is supported in the interconnect system by a special form of memory bus message called a bus notification. Unlike standard memory request/reply pairs, the bus notification is a stand-alone memory bus packet that notifies the processor(s) of an IPC. Each BIU decides if its associated processor should act on the IPC on the basis of whether the processor ID contained in the bus notification matches the processor's unique ID or the global ID. Each processor in the system has a unique processor ID, held in its associated BIU(s), which is established during system initialization.

#### INTERCONNECT REGISTERS

The programmable attributes of BIUs and MCUs in an iAPX 432 interconnect system are contained in registers of the interconnect address space, which is separate from the memory address space. These <u>interconnect registers</u> are accessed with the Move To Interconnect and Move From Interconnect instructions of iAPX 432 processors. Interconnect registers are logically organized by interconnect objects in the iAPX 432 software system. If a processor is given permission to access an interconnect object, it may change the attributes of the interconnect system.

Refinements of interconnect objects may be used to allow a processor a limited view of the total set of interconnect registers, restricted to those the processor has a "need to know": for example, to obtain its processor ID. A programmer can access the interconnect registers of any of the nodes in the interconnect system by node-local addressing (N-local). A node's address is composed of the unique module number and unique bus number that locate the node in the interconnect system. Each BIU and MCU in an interconnect system contains 32 unique interconnect registers.

#### FAULT-TOLERANT SYSTEMS

Three basic principles form the basis for implementation of the iAPX 432 fault handling mechanisms. First, the fault-tolerant functionality is achieved by <u>replication of VLSI components</u>. Second, the machine is partitioned into a set of <u>confinement areas</u>. These areas form the basis for error detection and recovery. Third, only <u>bus-oriented</u> communication paths are used to provide system communication.

VLSI replication is fundamental to achieve effective use of VLSI technology. The iAPX 432 allows the system designer to build a wide range of systems from a small set of VLSI components. These same components provide modular expansion of performance, memory storage, detection, and recovery capabilities. There are no special purpose components aimed solely at fault-tolerant applications.

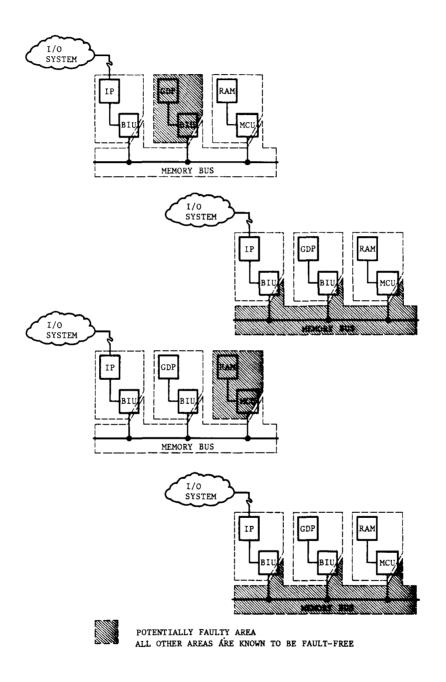

The purpose of a confinement area is to limit damage from error propagation and to localize the faulty area for recovery and repair. A confinement area is defined as a unit (module or memory bus) of the system which has a limited number of tightly controlled interfaces. Detection mechanisms are placed at every interface to ensure that no inconsistent data can leave the area and corrupt other confinements areas. When an error occurs in the system, it is immediately isolated to a confinement area. The error is known to be in that confinement area, and all other confinement areas are known to be error-free.

By defining confinement areas, we provide a conceptual framework for the systematic and coherent placement and definition of the detection mechanisms. The confinement areas also provide a conceptual view of the system under fault conditions. This clarifies the external (software) view of the hardware, and eliminates the need for diagnostic probing as a method of fault isolation.

All communication in the iAPX 432 system is done over buses. There are no point-to-point signals or daisy-chained signals. This makes modular growth possible since no signal definition is dependent on the number of resources in the system. This approach also makes on-line repair possible. The presence or absence of any module cannot prevent communication between any other modules. The memory bus defined by the BIU and MCU provides a uniform and regularly structured communications path that supports the modular expansion of both fault-tolerant and standard system capabilities.

In the iAPX 432 there are three distinct steps in responding to an error. First, the error is detected and localized to a confinement area. Next, the error is reported to all of the modules in the system. This prevents the incorrect data from propagating into another

confinement area and provides all the modules with the information required to perform recovery. Finally, the faulty confinement area is isolated from the system. Recovery occurs through the application of the redundant resources available in the system.

#### ERROR CONFINEMENT

Figure 1-3 shows the four types of confinement areas in a iAPX 432 system. There is a confinement area for each module and each memory bus in a system. These confinement areas were chosen because modules and memory buses are the natural building blocks for iAPX 432 systems. Thus, when an error is detected, it is confined to one of the system building blocks. This allows the recovery and repair strategies to be built around the replacement of system building blocks. When a module or bus has its confinement mechanisms activated, it can be viewed as a <u>self-checking unit</u>. The operation of a self-checking unit is designed so that no inconsistent data will be allowed to leave the unit and corrupt another confinement area. Detection mechanisms reside at every interface, and all data is checked as it flows across the interface between confinement areas.

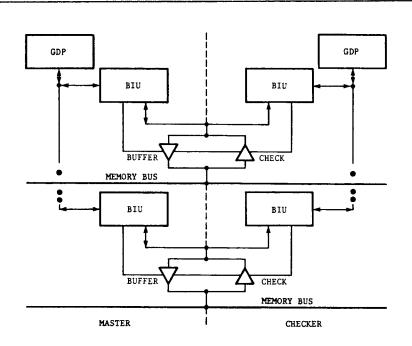

The GDP confinement area includes the GDP and its associated BIUs plus the processor bus and support logic in the module. The only interfaces to a GDP confinement area are the memory buses. The BIUs are responsible for checking all of the information that leaves the GDP module. No information (control, address, or data) can leave a GDP confinement area without first being checked for correctness by one of the BIUs in the module. Error detection is performed by duplicating the GDP module. The duplicate module is built from identical components that are in checker mode. Any disagreement between a master and its checker generates an error signal. A duplicated module thus forms a self-checking module.

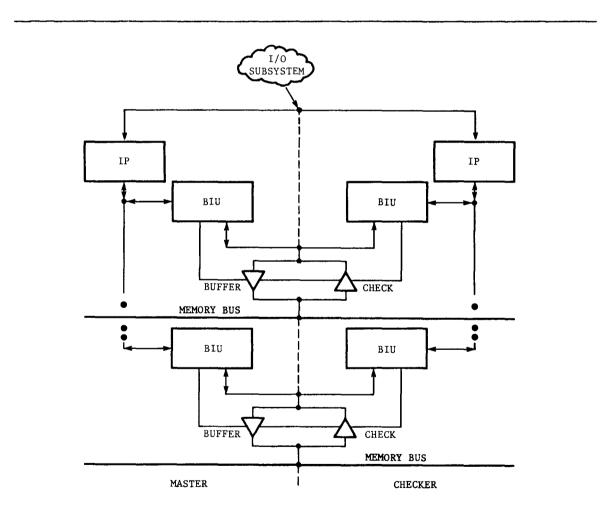

The IP confinement area includes the IP and its associated BIUs plus the processor bus and support logic in the module. An IP module has interfaces to the memory buses in the system, plus an interface to an external I/O subsystem. The interfaces to the memory buses are checked by the BIUs in the same manner that was described for the GDP confinement area. The IP component is responsible for checking any data that leaves the confinement area via the peripheral subsystem (PS) bus. No information can leave an IP confinement area without first being checked for correctness by one of the BIUs or the IP. (The peripheral subsystem is not a confinement area.)

At this time the application hardware or software must apply its own detection mechanisms to this subsystem. The PS bus represents a firewall between the central system and the I/O subsystem. The IP confinement area checks data as it leaves the IP: the application hardware and software must check data that leaves the I/O subsystem and enters the IP module. Error detection is performed by a duplicate checker module, as it was with the GDP module.

Figure 1-3. iAPX 432 Confinement Areas

F-0400

The memory confinement area includes the MCU, the RAM array, and the buses and support logic inside the module. A memory module has interfaces to two of the memory buses in the system. The MCU is responsible for checking all information that leaves the memory confinement area. No information can leave the confinement area without first being checked for correctness by the MCU. Error detection is performed by duplicating the MCU and applying an ECC code to the memory array. Thus, a self-checking memory module has two MCUs but only one memory array.

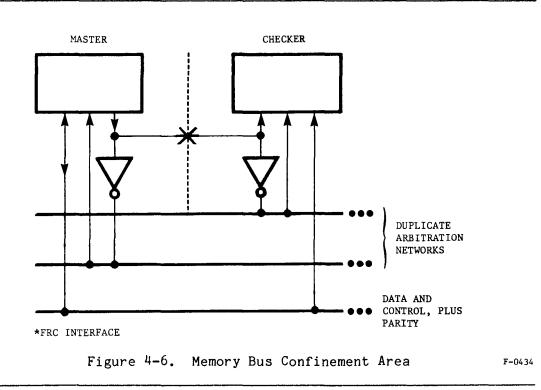

Each memory bus confinement area includes a memory bus and the interface logic residing in the BIUs and MCUs attached to the memory bus. Each memory bus has interfaces to all of the GDP and IP modules plus some of the memory modules. Every node (BIU or MCU) attached to this bus is responsible for checking all of the information that flows off the memory bus and into its module. No information can leave the memory bus and enter a module without first being checked for correctness by either a BIU or an MCU. Error detection is performed by two interlaced parity bits, which cover the control and address/data lines. Error detection for the arbitration lines is achieved by duplication.

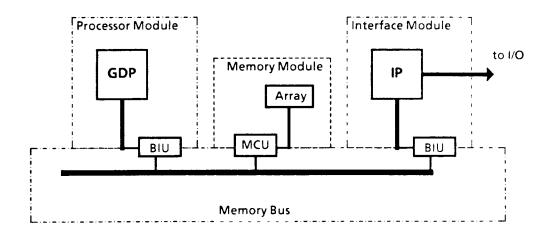

Figure 1-4 illustrates how interconnect components are logically paired to form self-checking units. Functional Redundancy Checking (FRC) provides the logical error detection mechanism. The master processor and its associated BIUs generate memory bus requests. The checker processor and its associated BIUs are functionally redundant elements used for error detection. Logic in the master and checker BIUs compares all information sent to a memory bus by the master. If any disagreement is detected, an error report is generated.

An example of processor-memory operation may help to clarify the operation of the confinement areas. This example is shown graphically in Figure 1-5. Assume that a GDP makes a read request to a memory location. That request will be mapped to a BIU on the addressed memory bus. As the information flows onto the memory bus it will be checked by the BIU. If any failure has occurred in the GDP confinement area (GDP, processor bus, BIUs, etc.) it is detected at this time. The information flows across the memory bus and into the addressed memory module. Before the information is accepted by the module, the MCU checks it for correctness. If a failure is detected, it is confined to the memory bus because the information was valid when it left the GDP confinement area. The MCU performs the memory operation and returns data onto the memory bus. As data flows onto the bus it is checked for correctness by the MCU. As the data flows into the GDP module from the memory bus it is checked for correctness by the BIU before being used by the GDP module.

#### Figure 1-5. Confinement Area Operation F-0401

The confinement area interfaces provide very tight error control and isolate the failure to one of the building blocks present in the system. The only remaining question concerns checking the detection mechanisms. Most of the detection mechanisms are self-checking in that the detection circuits are checked as part of normal operation. Those circuits that are not self-checking can be exercised during normal system operation to flush out any latent faults.

error detection mechanisms are employed in the hardware Four parity, Functional Redundancy Checking interconnect architecture: (FRC), error correcting codes (ECC), and buffer checking. All data, address, and control information that is moved across a memory bus is checked by a pair of parity bits that are interlaced among the signals that they check. FRC is a mechanism that allows identical VLSI components to be connected in parallel so that they may check each other's operation in real time. FRC error detection is an optional mechanism. MCUs perform ECC checks across all the address and data bits that are written to or read from the storage arrays they control. To cover the miscellaneous logic external to BIUs and MCUs, the VLSI components support a method of buffer checking that performs a sanity check to ensure that buffers are operating.

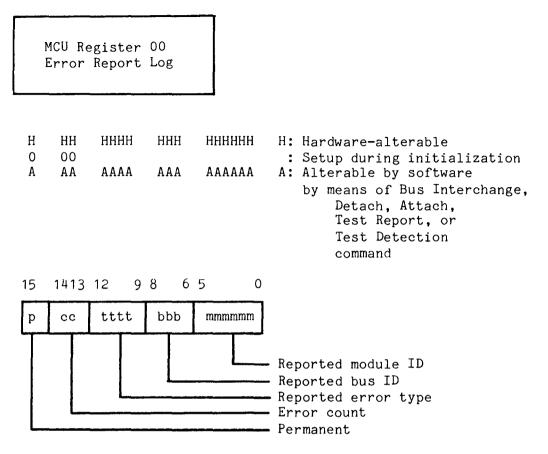

#### REPORTING

Immediately upon detecting an error, a message is broadcast to all the nodes in the system. This error report message identifies the fault confinement area, the type of error that occurred, and whether the error is permanant or transient. There are two reasons for sending this error report. First, it informs the rest of the system that an error has occurred. This prevents other confinement areas from using the inconsistent data. Second, it provides the necessary information for system recovery. After recovery, the error message is recorded in a log register in every node in the system. This log is available to software and is useful in monitoring the health of the system.

The error messages are broadcast over a set of serial buses, which are totally independent from the buses used during normal operation. However, this network of serial buses follows exactly the same topology as the buses used for normal operation. A failure on one of these buses is limited to one of the confinement areas discussed earlier. The error reporting circuitry may be tested during normal operation to uncover any latent faults.

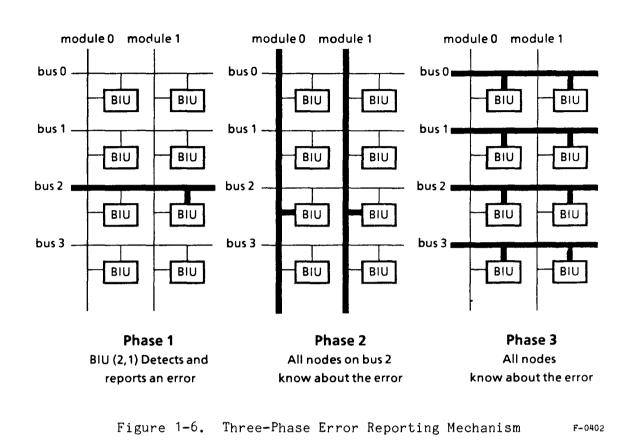

Figure 1-6 illustrates the three-phase flow of error information in the interconnect system. In phase 1, an error is detected at a node in the interconnect system. The example illustrates an an error detected at BIU(2,1); i.e., the BIU on memory bus 2 in processor module 1. The detecting component reports the error to all components attached to the same bus. (A bold line indicates an active error reporting path.) At this point, if all error reporting nodes are intact, all nodes have received the error message. In phase 2, all components that received the phase 1 error message <u>rebroadcast</u> the message along their module paths. Finally, in phase 3, each component that has received an error message rebroadcasts the message along its bus path. This second rebroadcast ensures that all nodes receive the error message even if one module or one bus error report line has failed. At the end of phase 3, all interconnect components in the system have been informed of the error.

The actual error reporting paths are separate from, but run parallel to, the MACD and ACD (Address, Control, and Data) buses so that error reports may propagate even if a bus is inoperative. In addition, the reporting paths may be duplicated to remove any single-point dependency in delivering an error report.

#### RECOVERY

The recovery process begins after an error report message has been broadcast around the system. Recovery is a distributed operation on the iAPX 432. Each node in the system reads the error report message and decides what recovery needs to be taken. For recovery to be successful, there must be redundant resources available in the system. There are five redundancy mechanisms in the iAPX 432: retry buffers, ECC, module shadowing, bus switching, and the spare memory bit. The first two of these mechanisms provide information useful in recovering from transient errors, while the other mechanisms allow recovery from permanent errors in the system. These redundant resources cover the entire system and allow recovery from any detected error. The presence of redundant resources has no impact on system performance.

For transient errors, each BIU maintains an internal buffer that allows outstanding processor requests to be retried if a transient error occurs. A single-bit correcting ECC code is applied to each word in the memory arrays. Although this provides redundancy for both permanent and transient errors, its primary purpose is to correct soft errors, which occur in DRAMs.

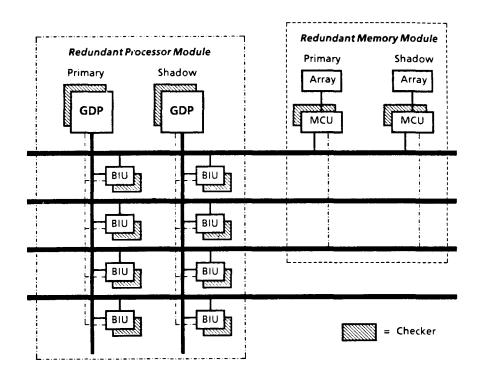

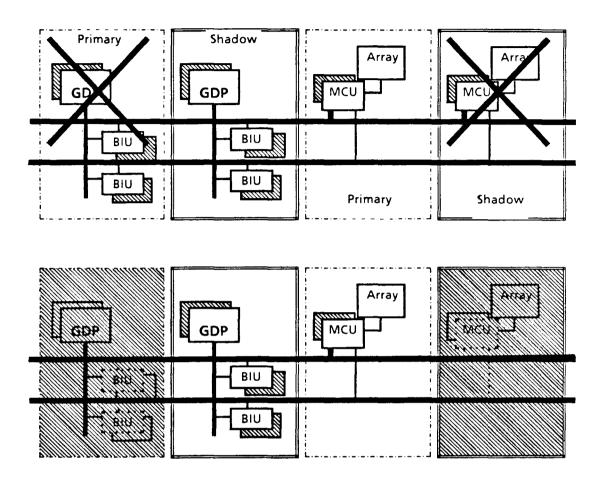

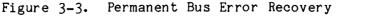

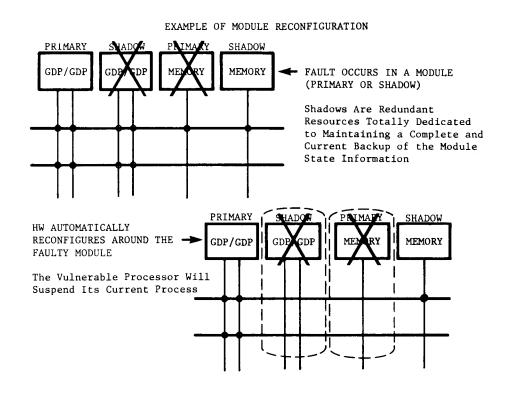

For permanent errors, every module in the system may be paired with another self-checking module of the same type. This pair of self-checking modules operates in lock step and provides a complete and current backup for all state information in the module. This mechanism is known as <u>module shadowing</u> because if one module (the primary) fails, a duplicate module (the shadow) is ready to fill in. A fault-tolerant module is also called a QMR (Quad Modular Redundant) module because most components are replicated four times. There are two self-checking modules and each of these has a master and a checker. See Figure 1-7 for an example of the pairing of QMR modules.

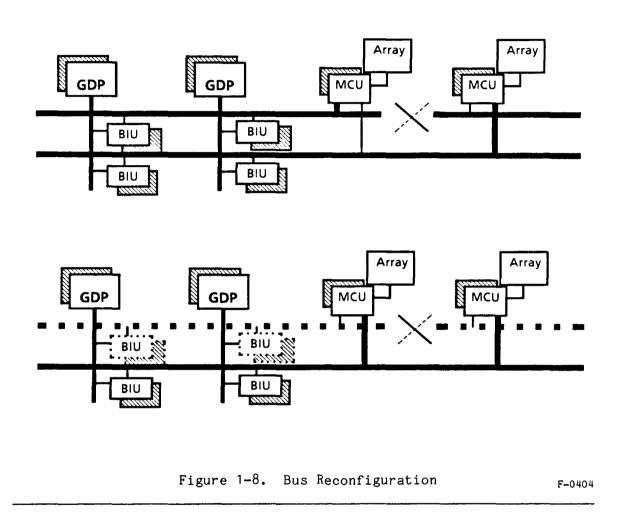

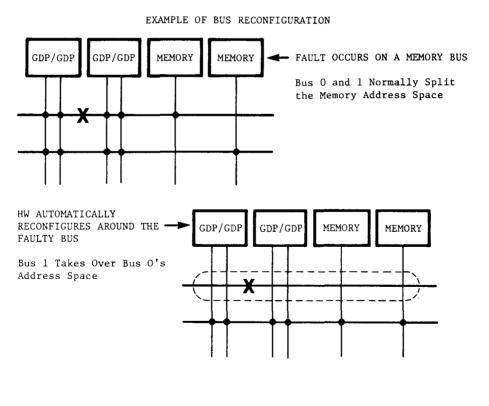

Each memory bus in the system may be paired with another memory bus. During normal operation the buses run independently. Both contribute to the total memory bandwith available in the system. However, if one bus fails, the other bus is capable of handling the bus requests (switching buses and rerouting accesses) that normally would have been handled by the failed bus.

Inside of each memory module, a spare bit may be added to each word in the memory array. If one bit in the array fails, the spare bit can be switched in to replace the failed bit.

For transient errors, all of the outstanding access will be retried, and the MCUs will return corrected data if there are any single-bit errors in the memory arrays.

For permanent errors, the redundant resource is switched in to replace the failed unit. This switch is done on a node-by-node basis; there is no centralized element that controls the switch. Each node knows which module or memory bus it is backing up (shadowing). If the error report identifies its partner as the faulty unit, it then becomes active and takes over operation for the faulty unit. After the resource switch is complete, all of the outstanding accesses are retried. This allows operation to resume at a point before the failure corrupted data.

These reconfiguration and recovery actions are performed by the hardware without any software intervention. After recovery is complete, the hardware informs the system software of the error and System software now makes policy subsequent recovery actions. decisions regarding optimum system configuration, given the resources remaining in the system. Software can elect to continue running with same number of modules but with reduced fault tolerance (because of the failure), or it can remove the module from service, thus reducing performance but retaining the same level of fault tolerance. The "marrying" of primary and shadow modules is under software control, giving the system a great deal of configuration flexibility. These policy decisions are carried out while normal system operation continues.

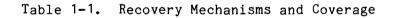

Figures 1-8 and 1-9 show two examples of recovery operation. Table 1-1 lists the recovery mechanisms provided by the interconnect system and the areas of the system which each covers.

Figure 1-9. Module Reconfiguration

F-0405

#### MECHANISM

Retry ECC Spare Bit Memory Bus Pairs Module Shadowing COVERAGE

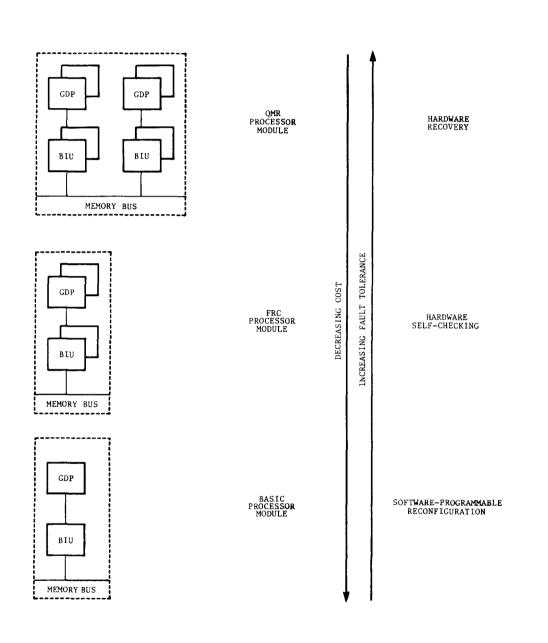

Transient Errors Storage Array Address and Data DRAM Replacement Memory Bus Failure Module Failure, GDP, IP, or Memory Figure 1-10 illustrates the range of alternatives available to system designers when they build iAPX 432 systems. The most fault-tolerant systems are built from a QMR configuration of processors that can tolerate any single component failure without crashing the system.

#### Figure 1-10. Fault-Tolerant Alternatives

F-03**9**7

The lowest cost configurations can be built using basic processor modules without FRC or QMR. This type of configuration will crash if a component fails, but can be made "self-healing" by adding intelligent software to the I/O subsystem. Unlike QMR, self-healing does not protect against the system crashing, but it does allow the system to recover from a failure in a short period of time. The "healing" takes place in three steps. First, a watchdog timer on an I/O subsystem alerts I/O subsystem software that the central system has failed. Second, the I/O subsystem checks BIU/MCU error logging registers and runs diagnostics to identify which resource (e.g., processor, bus, or memory) has failed. Third, the I/O subsystem reinitializes the system using the configuration control within the BIU and MCU to configure out the failed resource. The system is up and running without human intervention after only a short period of down time.

The basic configuration is the lowest cost alternative, but for some applications it is desirable to be able to have a very high degree of confidence that calculations are performed correctly. A QMR system will do this since all components have a checker that alerts the system if a mistake is made. But a QMR configuration may be overkill for some applications that can tolerate an occasional system failure, as long as they are confident that the computations are correct when they do complete. FRC configurations offer an alternative between the basic and QMR approaches. Adding a second set of checker components to each module improves the error detection capabilities of the system, providing "high-confidence" computing. No single hardware failure will go undetected and corrupt the results of a critical computation. FRC insures that any error is caught before it can propagate to another module in the system. FRC alone does not provide automatic hardware recovery like a QMR system, but it does detect errors as soon as they occur so that the system does not become corrupted. It is then the responsibility of system software to implement a "self-healing" strategy where the faulty resource is disabled and the system reinitialized.

The software configurability of a BIU/MCU system allows a system to use a combination of the above strategies. Software can configure a system as a full QMR system in the morning for critical applications, and then switch to an FRC-only system in the afternoon. This doubles the system throughput (twice as many processors are working in parallel) without making any hardware changes.

#### LATENT FAULTS

Earlier sections of this chapter have discussed how hardware faults are detected and handled by the interconnect architecture as it operates. The interconnect system can be used to detect another class of faults known as <u>latent faults</u>. Latent faults can exist in a part of the system which is normally dormant. Under normal operation of the system, it would take a long time before the fault reached an interface where it would be detected by the other mechanisms. The iAPX 432

interconnect system can be used to exercise the normally dormant parts of the system in a strategy to uncover the latent faults. Table 1-2 summarizes some of the areas in which latent faults may exist and the methods used to uncover the faults.

| Table  | 1-2.         | Exercising  | Latent | Faults   |

|--------|--------------|-------------|--------|----------|

| - uore | · <b>-</b> • | DYCI CTDTUR | -uocno | 1 UU1 0D |

| DORMANT AREA         | EXERCISE                                                                                   |  |

|----------------------|--------------------------------------------------------------------------------------------|--|

| Memory Locations     | MCU periodically reads every array location (scrubbing).                                   |  |

| Detection Mechanisms | Software <sup>*</sup> periodically forces error conditions into the detection mechanisms.  |  |

| Reporting Mechanisms | Software <sup>*</sup> periodically initiates and observes error reports.                   |  |

| Recovery Mechanisms  | Software <sup>*</sup> periodically invokes recovery operations.                            |  |

|                      | *Special commands to support exercising<br>dormant areas are provided in BIUs and<br>MCUs. |  |

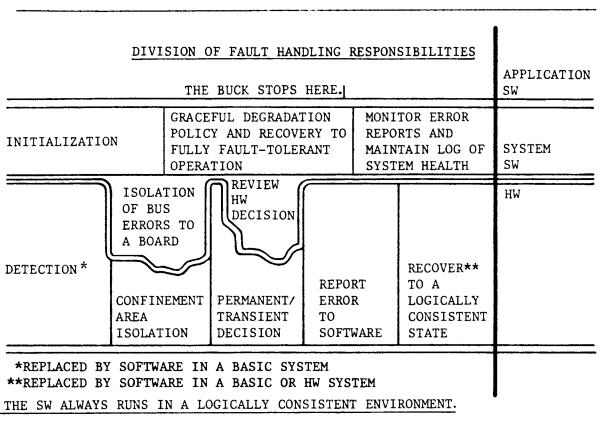

# FAULT-TOLERANT SYSTEM DESIGN RESPONSIBILITIES

The interconnect architecture and the VLSI components provide a stable base for developing fault-tolerant iAPX 432 systems. The iAPX 432 interconnect components address the issues concerning fault tolerance which are encountered when constructing the iAPX 432 central system.

A number of system-wide issues remain the responsibility of the iAPX 432 system designer. These issues include:

- A fault-tolerant I/O system

- Fault-tolerant power supplies and distribution method

- A fault-tolerant method for clock generation and distribution

- The electrical and physical provisions for on-line repair

- Environmental issues, such as system cooling

# SUMMARY

The iAPX 432 interconnect architecture provides a standard VLSI method for constructing multiple processor VLSI computer systems. The iAPX 432 interconnect architecture is implemented by a pair of VLSI components, the Bus Interface Unit (BIU) and the Memory Control Unit (MCU). Together with iAPX 432 processors, these components permit the construction of modular, extensible, multiprocessor computer systems. The components are designed to support the construction of fully fault-tolerant iAPX 432 systems. However, there is no penalty in performance or in cost for those applications that do not require fault tolerance.

The 432 fault-tolerant mechanisms are designed to provide a flexible and complete solution to the problems of fault-tolerant hardware. For basic systems (those without checkers for error detection or QMR for recovery), a user may decide to use only a few detection mechanisms and provide recovery only for transient errors. This functionality comes at no additional charge in the VLSI interconnect system. To reduce maintenance costs and increase system availability, a system may use all of the detection mechanisms (i.e., may add checker components) but may not add any extra recovery capability (i.e., may not marry self-checking modules into a fault-tolerant QMR module). Continuous operation is available to the user who adds the extra recovery capabilities.

None of the fault-tolerant mechanisms reduce system performance. Systems that do not require the highest level of fault tolerance are not penalized in any way (cost, size, or performance) for the unused fault-tolerant capabilities. Increased levels of fault tolerance are achieved by replicating the iAPX 432 VLSI components. The hardware fault tolerance in the iAPX 432 is transparent to application software. The system's fault-tolerant capabilities may be changed without any changes to the application software system.

# A MODEL FOR FAULT HANDLING

To provide a conceptual framework for our thinking, this chapter presents a model for systems under fault conditions. Our first observation is that a fault handling cycle has three phases: a fault is generated, detection of the fault occurs, and then a recovery procedure is activated. Fault generation ranges from hardware errors to software bugs. We define the detection phase to include detection, diagnosis, logging, and reporting of the fault. During this phase, system resources detect the presence and extent of the failure and pass this information on to the recovery mechanisms. After fault detection, recovery mechanisms are employed to mask the effects of the fault from the rest of the system and possibly isolate and repair the faulty subsystem.

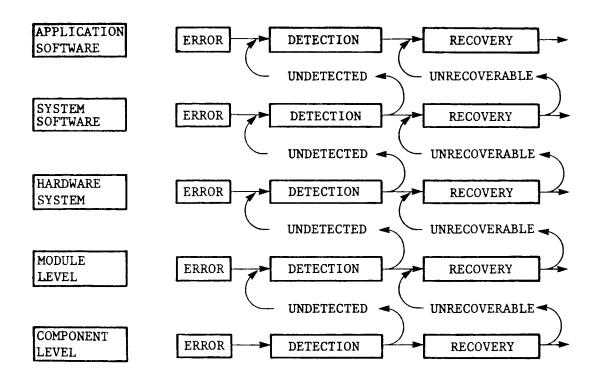

Next, we assume that a system is made up of a hierarchy of these fault handling cycles. Although the definition of the levels varies depending on system design and the technology of implementation, we believe that these levels exist in every system. For clarity, five levels that exist in most current systems are described below:

- 1. Component Level. This is the lowest level of hardware that will be considered in the system. Failures are generated by faults within the component itself. An example of such a failure is the loss of a memory bit within a RAM chip. This could be detected by employing checksums across the internal rows of storage cells in the chip. Recovery might be implemented by an on-board associative memory, which provides back-up storage for bad cells in the normal array. Bv employing fault handling strategies such as the ones mentioned, higher levels in the system may be totally unaware that a fault occurred.

- 2. <u>Module Level</u>. This level is composed of a group of interconnected components (such as a GDP, IP, or memory module). The failures at this level are generated by the components or the signal paths connecting the components. An example of such a failure at this level would be the loss of a memory bit in a 32-bit word of a memory array (e.g., a bad solder joint at a RAM data-out pin). This could be detected by employing parity to cover single failures within a memory word. Recovery could be accomplished by replacing the parity bit with a single error-correcting Hamming code (ECC).

- 3. Hardware System Level. This level consists of a network of Failures may occur when either a interconnected modules. module or the interconnect network fails. An example of such a failure might be an incorrect response from the memory module. This could be detected by duplicating the memory module and comparing the outputs. Recovery is possible if a third memory module is added and majority voting is performed at the outputs.

- 4. System Software Level. The operating system is responsible for providing expanded service to the application software. Failures may occur when defects exist in the algorithms. An example might be allowing a deadlock situation to occur. This can be detected by utilizing some secondary routines which monitor the operation of the system resources. Recovery might be accomplished by changing some of the previous resource allocation decisions.

- Application Level. This level completes the system description. This software may have defects in its algorithms 5. or specifications. The human interface of the system may even be used to detect and recover from application failures.

We also assume that these system levels are connected. Failures that occur at one level may flow up to higher levels if either the detection or recovery at that level is inadequate to handle the fault. Each time a failure is reflected up, the detection mechanisms at the next level will treat the failure as if it were originally generated at the higher level. This treatment causes a loss of information about the fault by potentially masking the true cause of the failure, as well as by increasing the amount of the system which must be considered suspect. An example of fault detection being reflected up is an undetected memory error that appears as an invalid data structure at one of the software levels. An example of recovery being reflected to higher levels is an uncorrectable memory error in an application program segment. It may be possible for the operating system or the user to handle this fault. Recovery can also be reflected up because of improper detection or incorrect operation of the recovery mechanisms. An example of this is a 3-bit memory error that is detected as a single-bit error by the Hamming code and subsequently "corrected."

The model we have constructed is pictured in Figure 2-1.

We deduce from the model several key points about system fault handling. Faults can occur at many different levels in the system. Each level has its own characteristics: different detection and recovery strategies will be appropriate for different levels. Faults not handled at one level will propagate up to the higher levels in the system. Higher levels have more complex environments, which make recovery a more complex and slow task: failure modes increase in complexity, the interaction between subsystems grows, and the original source of the failure becomes more ambiguous. Thus, faults should be handled at the lowest possible level.

# PHILOSOPHY

The goal of the iAPX 432 fault handling approach is to provide general-purpose, adaptable, and software-transparent fault-tolerant capabilities. Our design philosophy has two fundamental principles. First, the number of hardware errors which will be reflected up to the software levels of the system must be minimal. Second, all of the fault handling mechanisms must be designed as independent and orthogonal capabilities.

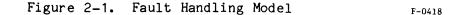

Figure 2-2 shows the location of the barrier that prevents hardware failures from being reflected into higher layers of the system. It is important to note that it is impossible for any system to detect and recover from all failures that might occur. However, the iAPX 432 hardware reduces the rate of failures reflected into the software to such a low level that in virtually every fault-tolerant application the software system can ignore errors reflected up by the hardware. (At this time we do not have enough data to publish an absolute value for the rate of failures reflected into the software. However, we have done enough modeling to confirm that the rate is extremely low.)

The reflection of errors needs to be minimized to prevent information overload at higher levels in the system structure. If all failures are allowed to propagate to the top, the system becomes overloaded and loses its ability to react to the fault conditions. The complexity of the failure modes may make implementation impossible or force a reduction in the completeness of fault coverage or generality of operation.