# intel System 432/600 System Reference Manual

/ . •

·

# SYSTEM 432/600 SYSTEM REFERENCE MANUAL

Order Number: 172098-001

Copyright © 1981 Intel Corporation Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051

# CAUTION

This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A Computing Device pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication, or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| BXP                           | Intelevision          | Micromainframe           |

|-------------------------------|-----------------------|--------------------------|

| CREDIT                        | Intellec <sup>R</sup> | Micromap                 |

| iR                            | IOSP                  | Multibus <sup>R</sup>    |

| ICE                           | 1RMX                  | Multimodule              |

| ics                           | 1SBC                  | Plug-A-Bubble            |

| immx                          | isbx                  | PROMPT                   |

| Insite                        | Library Manager       | RMX/80                   |

| Intel <sup>R</sup>            | MCSR                  | System 2000 <sup>R</sup> |

| int <sub>el<sup>R</sup></sub> | Megachassis           | UPI                      |

and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or RMX and a numerical suffix.

Ada is a trademark of the Department of Defense (Ada Joint Program Office).

VAX and VMS are trademarks of Digital Equipment Corporation.

| . * | REV. | REVISION HISTORY | DATE       |

|-----|------|------------------|------------|

|     | -001 | Original issue   | 12/81      |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     | -    |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     |      |                  |            |

|     | r    |                  |            |

|     |      |                  |            |

|     |      |                  |            |

| -   |      |                  |            |

| -   |      |                  | <i>i</i> . |

|     |      |                  |            |

PREFACE

The objective of this manual is to provide a single definitive reference source for Intel's System 432/600 family of computer products. This manual describes their physical and functional characteristics, hardware and software interfaces, modularity, and configurability in sufficient depth for the reader to select and configure a System 432/600 for a specific application.

Specific items of interest may be located in the Table of Contents.

This manual is divided into six chapters:

Chapter 1 Introduction and General Description

This chapter provides a brief overview of the System 432/600 family of products. It describes the modularity and extensibility of the subsystem modules and briefly covers functional characteristics. It introduces the PC boards, backplanes, card cages, chassis, and the complete OEM computer systems available in the System 432/600 product line.

Chapter 2 Physical Characteristics and Configuration

This chapter gives a brief introduction to module function and extensibility, and lists physical characteristics of the hardware including backplanes and card cages, PC board form factors, keying, and board placement. It defines power and cooling requirements so that requirements for a particular board group may be calculated. It provides pointers on configuration criteria for typical small, medium, and large system configurations.

Chapter 3 System Functional Description

This chapter provides a detailed functional description of each module's operation in the system, and overall system functions. It describes the modularity and extensibility of memory, processor, and I/O boards.

v

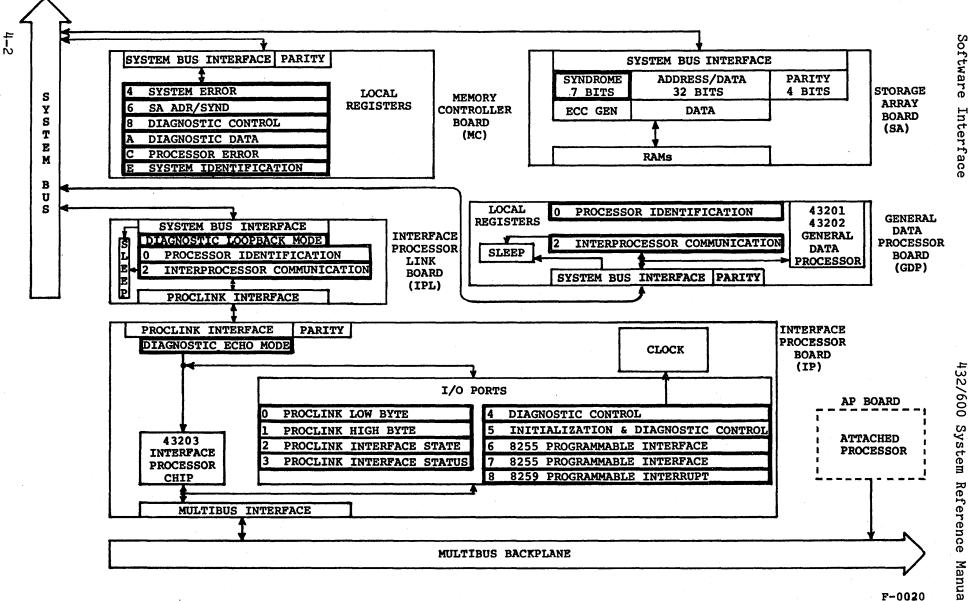

#### Chapter 4 Software Interface

This chapter describes the system reset mechanisms, communication ports, and local registers available to system software, and defines their use in the system. Error logging and diagnostic registers and controls are listed and described.

Chapter 5 System Performance

Factors affecting the performance of multiprocessor systems are discussed, and the System 432/600 is compared to conventional computers.

Chapter 6 Reliability and Maintenance

This chapter provides an overview of System 432/600 diagnostic software and the special hardware it uses to isolate system faults to board level.

Additional related information is available from the following documents:

Introduction to the iAPX 432 Architecture, Order Number: 171821

iAPX 432 Object Primer, Order Number: 171858

iAPX 432 General Data Processor Architecture Reference Manual, Order Number: 171860

iAPX 432 Interface Processor Architecture Reference Manual, Order Number: 171863

System 432/600 Diagnostic Software User's Guide, Order Number: 172099

Intel Multibus Specification, Order Number: 9800683

Intel Multibus Interfacing, Application Note: AP-28

CONTENTS

Page

# CHAPTER 1

| Introduction                      |   |

|-----------------------------------|---|

| General Description 1-1           |   |

| System 432/600 Product Family 1-4 | ł |

| Backplanes 1-5                    |   |

| Processor Subsystem 1-5           | 5 |

| Memory Subsystem 1-6              |   |

| Peripheral Subsystem 1-7          | 7 |

| Card Cages 1-8                    |   |

| Powered and Cooled Chassis 1-8    | 3 |

| Diagnostic Software 1-9           | ) |

| Sample Configurations 1-1         |   |

#### CHAPTER 2

PHYSICAL CHARACTERISTICS AND CONFIGURATION

| Introduction                           | 2-1  |

|----------------------------------------|------|

| Module Function and Extensibility      | 2-1  |

| Backplanes                             | 2-2  |

| Logic Boards                           | 2-5  |

| Logic Board Jumpers                    | 2-6  |

| ProcLink Cables                        | 2-7  |

| Power and Cooling                      | 2-8  |

| Card Cages                             | 2-8  |

| Powered and Cooled Chassis             | 2-10 |

| Configuring a System 432/600           | 2-14 |

| Memory Subsystem Configuration         | 2-14 |

| Memory Size                            | 2-15 |

| Interleave Option                      | 2–15 |

| Future Expansion                       | 2–16 |

| Processor Subsystem Configuration      |      |

| Peripheral Subsystem Configuration     | 2-17 |

| Peripheral Device Functions            | 2-17 |

| Attached Processor                     | 2-17 |

| Peripheral Subsystem Performance Range | 2–18 |

| Backplane Selection                    | 2-18 |

| Configuration Summary                  | 2–19 |

|                                        |      |

| CHAPTER 3<br>SYSTEM FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                         | Page                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Introduction<br>General Description<br>Interface Processor Board<br>Multibus Interface and Diagnostic Support Logic<br>Interface Processor Chip, Support Logic, and Clock<br>ProcLink Control and Data<br>Interface Processor Link Board<br>Data Rotation and Storage Unit<br>DRSU Control<br>Processor Controller | 3-1<br>3-3<br>3-3<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7<br>3-8        |

| Arbitration Logic<br>System Bus Controller<br>System Bus Backplane<br>General Data Processor Board<br>Clock Logic<br>System Bus Control and Buffers<br>Data Rotation and Storage Unit<br>Arbitration Logic<br>Processor State Machine                                                                              | 3-9<br>3-9<br>3-10<br>3-11<br>3-12<br>3-12<br>3-12<br>3-13<br>3-13 |

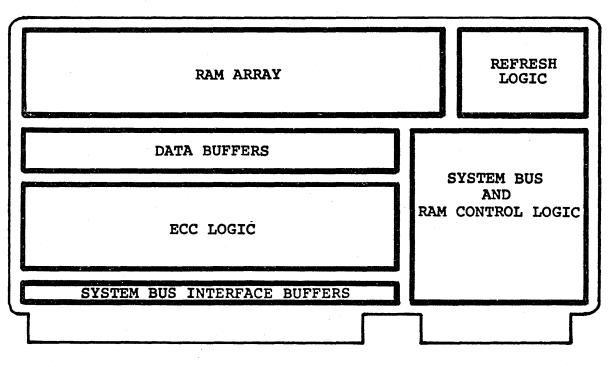

| Memory Controller Board<br>Clock Generator<br>System Bus Interface<br>Memory Controller State Machine<br>Local Registers<br>Error Logging<br>Storage Array Board<br>System Bus and Ram Control Logic<br>Refresh Logic                                                                                              | 3-13<br>3-13<br>3-14<br>3-15<br>3-16<br>3-16<br>3-17               |

| ECC Logic                                                                                                                                                                                                                                                                                                          | 3–18                                                               |

#### CHAPTER 4 SOFTWARE INTERFACE

| Introduction                       | 4-1 |

|------------------------------------|-----|

| General Description                | 4-1 |

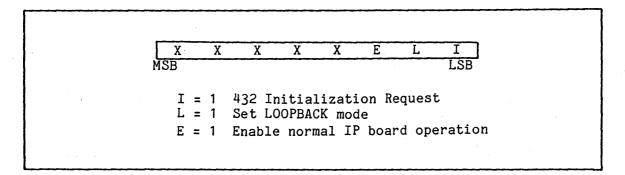

| Initialization                     | 4-3 |

| Error Logging and Retrieval        | 4-4 |

| Diagnostic Operation               | 4-5 |

| Interface Port and Register Tables |     |

| CHAPTER 5<br>SYSTEM PERFORMANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Page                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Introduction<br>Automatic Process Scheduling<br>Transparent Multiprocessing<br>Practical Limitations<br>Efficient Data Transfers                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5–2<br>5–3<br>5–3                                                                                             |

| CHAPTER 6<br>RELIABILITY AND MAINTENANCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                               |

| Introduction<br>Diagnostic Software Overview<br>System Configuration Program<br>Diagnostic Supervisor<br>Test Sequences and Error Messages<br>System Validator<br>Restoring System Operation<br>Diagnostic Board Test Programs<br>Interface Processor Board Diagnostic<br>PASS Mode<br>ECHO Mode<br>IP Board Tests.<br>Interface Processor Link Board Diagnostic<br>Memory Controller Board Diagnostic<br>Storage Array Board Diagnostic<br>General Data Processor Board Diagnostic<br>IPC Send Test for IP<br>Initialization Test<br>Access Test<br>43201/43202 Component Test<br>43203 Component Test | 6-1<br>6-2<br>6-3<br>6-3<br>6-3<br>6-3<br>6-3<br>6-5<br>6-6<br>6-6<br>6-6<br>6-7<br>6-9<br>6-9<br>6-9<br>6-10 |

# Page

ix

ILLUSTRATIONS

| Figure     | e Title                                                         | Page       |

|------------|-----------------------------------------------------------------|------------|

| 1–1<br>1–2 | System 432/600: Simplified Block Diagram<br>Processor Subsystem | 1–6        |

| 1-3<br>1-4 | Memory Subsystem<br>Peripheral Subsystem                        |            |

| 1-5        | iSBC 432/630 Chassis                                            |            |

| 1-6        | System 432/600 Sample Configurations                            |            |

| 2–1        | System Bus Backplane                                            | 2-3        |

| 2-2        | Multibus Backplane                                              | 2-4        |

| 2-3        | PC Board Form Factor                                            | 2-5        |

| 2-4        | External ProcLink                                               | 2-7        |

| 2-5        | Suggested Card Cage and Backplane Combinations<br>Card Cages    | 2-9        |

| 2-6<br>2-7 | iSBC 432/630 Chassis with the System 432/670 Configuration .    | 2-11       |

| 2-8        | Operator's Panel                                                | 2-12       |

| 3-1        | System 432/600 Block Diagram                                    | 3–2        |

| 3-2        | Interface Processor Board Block Diagram                         | 3-4        |

| 3–3        | Interface Processor Link Board Block Diagram                    | 3-7        |

| 3-4        | General Data Processor Board Block Diagram                      | 3-11       |

| 3-5        | Memory Controller Board Block Diagram                           | 3-14       |

| 3-6        | Storage Array Board Block Diagram                               | 3-10       |

| 4-1        | Software Interface Implementation                               | 4-2<br>5-1 |

| 5–1<br>6–1 | Performance Range<br>Interface Processor Board Functions        | 6-4        |

| 6-2        | Interface Processor Link Board Function                         | 6-6        |

| 6-3        | Memory Controller Board Functions                               | 6-7        |

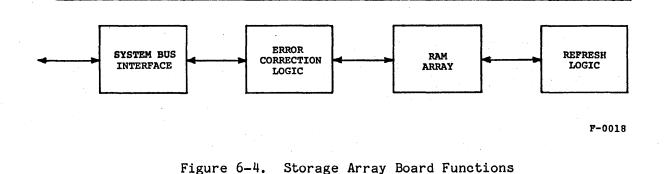

| 6-4        | Storage Array Board Functions                                   | 6-8        |

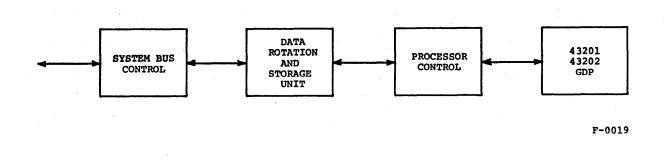

| 6-5        | General Data Processor Board Functions                          | 6-9        |

Х

Table

| intel | TABLES |

|-------|--------|

|       |        |

# Title

Page

| 1-1          | System 432/600 Product Family                     | 1-4 |

|--------------|---------------------------------------------------|-----|

| 2-1          | System Bus Slot Allocations                       |     |

| 2-2          | PC Board Key Slots                                |     |

| 2-3          | ProcLink Cables                                   |     |

| 2-4          |                                                   |     |

|              | Power and Cooling                                 | 2-8 |

| 2-5          | System Memory Sizes                               |     |

| 2-6          | System Bus Backplanes                             |     |

| 4-1          | I/O Ports and Addresses                           |     |

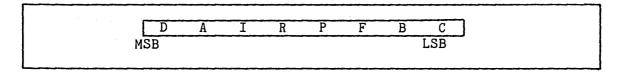

| 4-2          | Port 2, ProcLink Interface State                  | 4-6 |

| 4-3          | Port 3, ProcLink Interface Status                 | 4-7 |

| 4-4          | ProcLink Interface Status Register Bit Definition | 4-7 |

| 4-5          | Port 4, Diagnostic Control                        |     |

| 4-6          | Port 5, Diagnostic and Initialization Control     |     |

| 4-7          | System 432/600 Local Registers                    |     |

| 48           | Local Register 0, Processor Identification        |     |

| 4-9          | Local Register 2, Interprocessor Communication    |     |

| 4-10         | System Error Register and Bit Definition          |     |

| 4-11         | System Error Register Error Code Definition       |     |

| 4-12         | SA Address/Syndrome Register and Field Definition |     |

| 4-13         | Local Register 8, Diagnostic Control              |     |

| 4-14         | Local Register A, Diagnostic Data                 |     |

| 4-14<br>4-15 |                                                   |     |

|              | Local Register C, Processor Error Register        |     |

| 6-1          | Diagnostic I/O Ports                              | 0-4 |

CHAPTER 1 INTRODUCTION AND GENERAL DESCRIPTION

#### INTRODUCTION

This chapter introduces and provides a brief overview of the Intel's System 432/600 family of products. It describes the capability and extensibility of the subsystems and briefly covers the functional characteristics of each module.

System 432/600 computers utilize the advanced architecture of the iAPX 432 Micromainframe VLSI components. The Micromainframe components are the 43201/43202 General Data Processor (GDP) chip-pair and the companion 43203 Interface Processor (IP) chip which unburdens the GDP of all input/output handshakes, synchronization, and data transfers. Through subsystem extensibility, System 432/600 computers offer a wide range of performance, memory capacity, and input/output capability.

The System 432/600 product line includes logic boards, backplanes, cables, card cages, and a powered and cooled chassis. They are offered individually and as integrated 32-bit OEM computer systems.

#### GENERAL DESCRIPTION

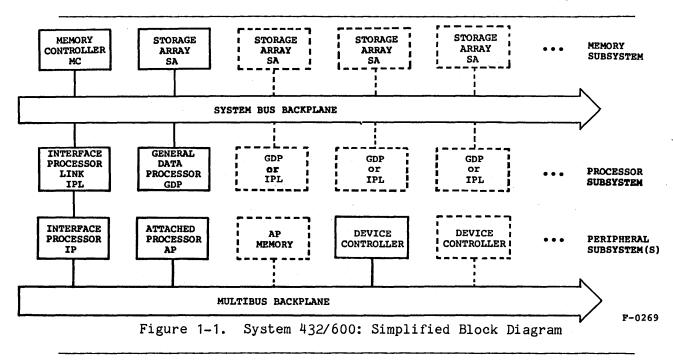

A simplified block diagram of the System 432/600 is shown in Figure 1-1.

A System 432/600 comprises one Processor Subsystem, one Memory Subsystem, and one to five Peripheral Subsystems.

The Processor Subsystem and the Memory Subsystem reside on the System Bus backplane. This portion of the System 432/600, the Processor Subsystem plus the Memory Subsystem, is called the Central System.

Each Peripheral Subsystem resides on a separate Multibus backplane.

The Processor Subsystem contains one General Data Processor (GDP) board and one Interface Processor Link (IPL) board, plus zero to four additional boards which may be any combination of GDP and IPL boards. Each IPL board connects a Peripheral Subsystem to the Central System. Thus, a Processor Subsystem could contain one GDP board and five IPL boards, connecting to five Peripheral Subsystems. At the other extreme, a Processor Subsystem could contain five GDP boards and one IPL board, connecting to one Peripheral Subsystem. The user chooses the mix of data processing capability (GDPs) and input/output capability (Peripheral Subsystems) which best meets his needs.

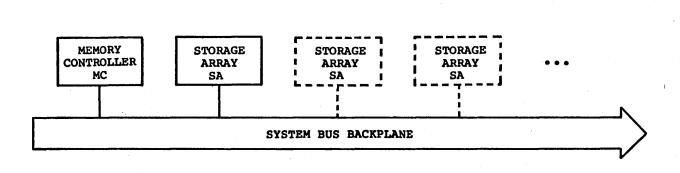

The Memory Subsystem contains one Memory Controller (MC) board plus one to ten Storage Array (SA) boards. Each SA board contains 256K bytes of memory with Error Correction Code (ECC) protection. The user can thus configure a System 432/600 from 256K bytes to 2.5M bytes of memory.

Each Peripheral Subsystem contains one Interface Processor (IP) board and one Attached Processor (AP) board, plus peripheral device controllers and additional AP memory as required. The IP board on the Multibus backplane connects to its companion IPL board on the System Bus backplane via a Processor Link (ProcLink) cable. The Attached Processor (AP) may be any Multibus-compatible single board computer. The combination of the IPL board on the System Bus backplane plus the IP board and the AP board on the Multibus backplane, forms a logical input/output processor.

Each GDP board contains one independent GDP chip-pair. Hardware mechanisms provide for software-transparent multiprocessing, which allow GDPs to be added to an existing system by simply plugging additional GDP boards into the System Bus backplane; there is no effect on application software, system software, or the memory access arbitration logic that controls the access of multiple processors to the Memory Subsystem. Similarly, removing a GDP board from a multiple GDP system (e.g., because of a board malfunction) has no effect beyond the reduced system throughput caused by the reduction of available GDPs. The Memory Subsystem is accessible to all the processors in the System 432/600, where "processors" means both the General Data Processors and the logical input/output processors (IPL/IP/AP combination) described above. Data is stored on modular Storage Array boards which are accessed via the Memory Controller. Only one MC board is necessary in any System 432/600 configuration.

The Memory Controller supports byte addressability and an interleave option to enhance performance. Memory size is expanded by inserting additional SA boards into the System Bus backplane, with no hardware or software changes required. When the interleave option is enabled, SA boards must be added in pairs.

The Peripheral Subsystems relieve the Central System of all general input/output processing, device control, and operator control functions. No switches or other operator controls connect to the Central System; the only way to start, stop, or interrupt the Central System is via programs running on the Attached Processor. Thus, the high speed Central System is never forced to wait during operation for human intervention or response.

Peripheral Subsystems may be added to a System 432/600 by attaching another Multibus backplane. The capability of an existing Peripheral Subsystem may be expanded by adding any Multibus-compatible peripheral device controller board, or by adding Multimodule mini-boards to Multimodule-compatible mother boards.

As outlined above, System 432/600 hardware provides extensible subsystems, each with a high degree of modularity. All logic board types, backplanes, and card cages have been designed to provide mechanically, electrically, and logically independent and decentralized modules. This allows an incremental approach to selecting the modules necessary to achieve a System 432/600 with a desired range of functionality and performance. An additional benefit is the ability to expand subsystems, after a System 432/600 has been configured and installed, by simply inserting additional modules.

In addition to being highly configurable and extensible, the System 432/600 is easily maintained. System 432/600 Diagnostic Software isolates a system malfunction to an individual board. Simply replacing the board specified by the diagnostics returns the system to full operational status.

# General Description

# SYSTEM 432/600 PRODUCT FAMILY

Table 1-1 is a summary of the System 432/600 product family.

# Table 1-1. System 432/600 Product Family

|          |         | NODU P. NAME                    |      |                 |    |

|----------|---------|---------------------------------|------|-----------------|----|

| NUME     | BER     | MODULE NAME                     |      |                 |    |

| iSBC 43  | 32/601  | General Data Processor Board (G | GDP) |                 |    |

| iSBC 43  | 32/602  | Interface Processor Board (IP)  |      |                 |    |

| iSBC 4   | 32/603  | Interface Processor Link Board  | (IPL | .)              |    |

| iSBC 43  | 32/604  | Memory Controller Board (MC)    |      |                 |    |

| iSBC 43  | 32/607  | Storage Array Board (SA)        |      | 256K by         | te |

| iSBC 4   | 32/610  | System Bus Backplane            |      | 6-slo           | ot |

| iSBC 43  | 32/611  | System Bus Backplane            |      | 12 <b>-</b> slo | ot |

| iSBC 43  | 32/612  | System Bus Backplane            |      | 18-sl           | ot |

| iSBC 43  | 32/615  | Multibus Backplane              |      | 6-sle           | ot |

| iSBC 4   | 32/616  | Multibus Backplane              |      | 12-sl           | ot |

| iSBC 43  | 32/620  | Card Cage                       |      | 6-slo           | ot |

| iSBC 43  | 32/621  | Card Cage                       |      | 12-sl           | ot |

| iSBC 43  | 32/622  | Card Cage                       |      | 18-slo          | ot |

| iSBC 4   | 32/630  | 432/600 System Chassis          | 120  | VAC/60 I        | Hz |

| iSBC 4   | 32/631  | 432/600 System Chassis          | 230  | VAC/50 I        | Hz |

| System 4 | 432/670 | Integrated Computer             | 120  | VAC/60          | Hz |

| System 4 | 432/671 | Integrated Computer             | 230  | VAC/50 I        | Hz |

#### BACKPLANES

One System Bus backplane and one Multibus backplane are necessary to configure a System 432/600. A System Bus backplane is used to interconnect General Data Processor, Interface Processor Link, Memory Controller, and Storage Array boards. The System Bus contains various control and error lines, and a system wide Specification/Address/Data (SAD) bus. The SAD bus is 36 bits wide; 32 data bits plus one parity bit for each 8-bit byte.

All communication on the System Bus is synchronous, controlled and synchronized by the 8 MHz clock on the MC board. The MC drives one set of control lines for General Data Processor and Interface Processor Link boards, and another set of control lines to the Storage Array boards. The MC board fits into one dedicated slot position in a System Bus backplane.

A Multibus backplane (as defined by the IEEE-P796 Multibus Standard) interconnects the Interface Processor, Attached Processor, and peripheral device controller boards of a Peripheral Subsystem. A Processor Link (ProcLink) cable connects the IPL board on the System Bus backplane to the IP board on the Multibus backplane to complete the system communications path. The ProcLink cable also allows physical separation of the System Bus and Multibus backplanes, if desired. Mounting dimensions and power connections on the System Bus and Multibus backplanes are similar; either may be mounted easily in the card cages listed in Table 1-1.

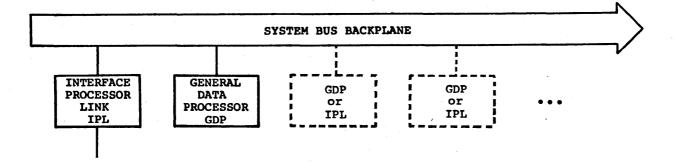

#### PROCESSOR SUBSYSTEM

The Processor Subsystem contains GDP boards and IPL boards. An IPL board is the "agent" on the System Bus backplane for an IP board and AP board on a Multibus backplane.

The Processor Subsystem contains one GDP board and one IPL board, plus up to four additional boards which may be any mix of GDP or IPL.

Each GDP and IP board contains a clock generator for its own internal sequencing. This allows each processor to run at its own clock rate, regardless of other processor rates or the Memory Subsystem clock rate. Each IPL board operates at the clock rate set by its companion IP board, except for interaction with the System Bus, which uses the Memory Controller clock.

A GDP board performs the data manipulations of a typical computational task, communicating with memory and other processors via the System Bus.

A General Data Processor is self-dispatching; it automatically performs the normal cycle of running a process (program unit) until the process completes, blocks (e.g., waiting for input/output), or times out. It then re-schedules the process for subsequent execution, and begins executing the next ready process with no software intervention. System software is not affected by the number of processors in a system or by which processor is executing a particular process.

All processors in a system share memory via the System Bus. A round-robin arbitration scheme allows processors to arbitrate priority for the next memory access. This ensures that each GDP and IP has equal opportunity for access to memory, and prevents memory access conflicts. Since the IP board is physically not on the System Bus, the IPL board contains arbitration logic for the IP. Attached Processor accesses to the Central System use the IPL/IP board-pair as an intermediary.

Adding or removing a processor board from a multiprocessing system does not affect the arbitration logic or system software.

#### MEMORY SUBSYSTEM

The Memory Subsystem for any System 432/600 contains one Memory Controller board. The MC can logically control and access from one to sixteen Storage Array boards. To support Byte Addressability, the MC logic controls 1-, 2-, 4-, 6-, 8-, and 10-byte accesses as requested by system processors. For any Read request, the Memory Subsystem provides the exact number of bytes a processor requests, rather than a fixed length word.

A memory interleave option is available to enhance system performance. This option uses two banks of memory with alternating addresses to provide faster data access by overlapping memory operations. Interleave operation is selected by one jumper on the MC board. This option requires Storage Array boards to be installed in pairs to implement the alternate bank addressing.

Figure 1-3. Memory Subsystem

Each Storage Array board contains logic to generate, check, and store a 7-bit Error Correction Code (ECC) for each 32-bit data word. As data is read from memory, single bit errors are detected and corrected, and double bit errors are detected and logged in a system error register.

The size of an existing Memory Subsystem may be expanded by simply plugging in additional SA boards. Refer to the Interleave Option description in Chapter 2 for memory expansion details.

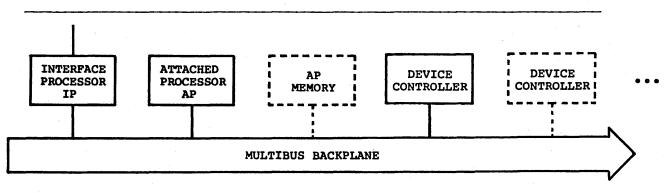

#### PERIPHERAL SUBSYSTEM

Implementation of the Peripheral Subsystem provides for attached processing and peripheral device control to be performed by standard Multibus products. Multibus compatible Single Board Computers may be used as Attached Processors. The Attached Processor for a System 432/600 is selected by the user; information on AP requirements is given in Chapter 2. More than one Peripheral Subsystem with its Attached Processor may be present within a system. Any Multibus compatible peripheral device controller, direct memory access controller, or communications controller may be used in a Peripheral Subsystem. Additional AP memory may be added as required.

1-7

The Peripheral Subsystem is implemented by the Attached Processor, Interface Processor, and Interface Processor Link boards. One IP and one IPL is necessary for each AP in a system. Each Multibus backplane requires one AP and one IP board. The AP and IP reside on a Multibus backplane, and the IPL board on the System Bus backplane.

The Attached Processor manages all peripheral device functions. In general, it coordinates the activity of multiple input/output processes, supports data transfers, and reacts to real-time concerns of the peripheral device controllers. The AP may also function as an additional decentralized data processor. All AP accesses to the System 432/600 main memory are via the Interface Processor chip (43203 VLSI component) on the IP board.

A primary function of the Interface Procesor is to map a portion of the AP's address space through protected windows into the system's main memory. This allows the AP to exploit the object-oriented addressing feature of the iAPX 432 architecture. The IP acts as a slave to the AP, and extends the AP instruction set to include some 432 object oriented instructions. This allows the AP to perform data manipulations within the Central System. The JP board also contains specific hardware to support system diagnostic software which executes on the AP.

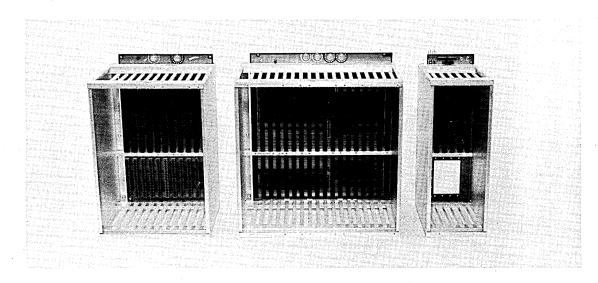

#### CARD CAGES

Three card cages are offered for use with System Bus and Multibus backplanes: 6-slot, 12-slot and 18-slot. System 432/600 backplanes have card connectors on 0.70 inch centers. An 18-slot card cage will accept any mix of backplanes that support a total of 18 boards (e.g., a 12-slot System Bus backplane and a 6-slot Multibus backplane). Card cages do not contain power supplies or cooling fans.

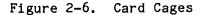

#### POWERED AND COOLED CHASSIS

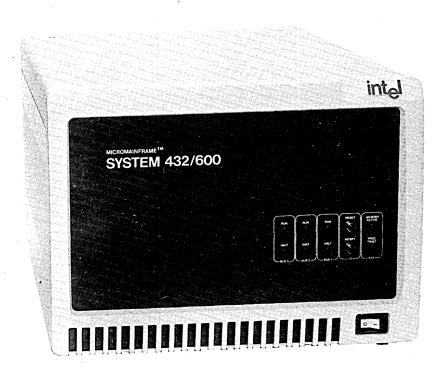

A complete powered and cooled chassis is available which includes an 18-slot card cage. Smaller card cages may also be mounted in the chassis in place of the 18-slot card cage. The chassis may be a table-top unit or be RETMA rack-mounted. A microcomputer-controlled system interface board and an operator switch and light panel is included in the chassis. The chassis power supply provides all necessary voltages and control signals for any combination of System Bus and/or Multibus backplanes containing a maximum of 18 logic boards. Two chassis models are available: one for 120 VAC/60 Hz and the other for 230 VAC/50 Hz.

Figure 1-5. iSBC 432/630 Chassis

#### DIAGNOSTIC SOFTWARE

The System 432/600 Diagnostic Software package is available for System 432/600 users. It is described in the System 432/600 Diagnostic Software User's Guide. All access and data paths, all memory locations, and representative processor instructions are exercised by a series of structured test programs.

The normal sequence of testing is a series of tests starting on the IP board and progressing through the IPL, MC, and SA boards, and finally to the GDP boards. The diagnostic software has been designed to test System 432/600 configurations within the following range:

MINIMUM One each of the five board types: GDP, IP, IPL, MC, and SA.

#### MAXIMUM

Five GDP boards, one IP board, one IPL board, one MC board, and 16 SA boards.

If more than one Peripheral Subsystem is available, the diagnostics may be run on any or all of the APs.

One section of the Diagnostic Software package is the System Validator, which gives a quick confidence check of the System 432/600. The validator is a subset of the Diagnostic Software package. It is a minimal functional test of the entire system, and runs in a much shorter time than the full system diagnostics.

#### SAMPLE CONFIGURATIONS

Figure 1-6 depicts the modularity and expansion capabilities of System 432/600 modules. Sample configurations for entry level, medium, and large systems are shown. System configuration and expansion limits are set by the backplane size and types selected.

Figure 1-6A is an entry level system for a 12-slot card cage with one 6-slot System Bus backplane and one 6-slot Multibus backplane. The Memory Subsystem consists of one MC board and one SA board in a non-interleaved system, or one MC and two SA boards in an interleaved system. One GDP board and one IPL board complete the System Bus population. The Multibus backplane contains one IP board, one AP board, and one device controller board. The AP and device controller boards are selected by the user.

The memory size for the entry level system described above is 256K bytes for the non-interleaved version, or 512K bytes for the interleaved version. The non-interleaved version can be expanded to 512K bytes by adding a second SA board.

This entry level system can also be expanded by plugging one additional GDP board into the remaining System Bus slot. No software changes are needed to utilize the additional GDP board - simply plug it in. The Peripheral Subsystem may be expanded by inserting up to three additional boards (either user-selected device controllers or AP memory) in the Multibus backplane.

Figure 1-6B shows two possible configurations for a medium system utilizing an 18-slot card cage. System B-1 increases processing power, while System B-2 extends input/output capabilities. System B-1 provides over 1.5 million bytes of main system memory, four General Data Processors, and a complete Peripheral Subsystem in one unit. Four GDPs, with their inherent multitasking and concurrent execution capabilities, provide an extremely powerful processing subsystem.

System B-2 provides 512K bytes of main system memory and two complete Peripheral Subsystems in one small package.

432/600 System Reference Manual

Since the ProcLink cable provides all interconnections between Peripheral Subsystems and the 432/600 Central System, a large multiple-chassis system may be configured easily, as shown in Figure 1-6C.

Using an 18-slot System Bus backplane, this system provides a main memory capacity of over 2.5 million bytes, the processing power of four GDP boards, and two complete, powerful Peripheral Subsystems. One option to this system is to exchange one GDP board with an IPL board, and configure the peripheral card cage with three 6-slot Multibus backplanes. With three GDP boards, this configuration still provides a powerful data processing capability, plus maximum main memory and three autonomous Peripheral Subsystems.

More details of system configuration may be found in Chapter 2, Configuration and Physical Characteristics.

A Entry Level System

B Two Medium Systems

C Large Two Card Cage System

Figure 1-6. System 432/600 Sample Configurations

#### INTRODUCTION

This chapter introduces System 432/600 module functions and extensibility, and physical characteristics of the hardware including power and cooling requirements. It provides pointers on configuration criteria for typical small, medium, and large configurations.

#### MODULE FUNCTION AND EXTENSIBILITY

Intel's System 432/600 product line is a family of functional modules that provide expansible subsystem building blocks easily configured into an extensive range of computer systems. The product line includes PC boards, backplanes, cables, card cages, and a powered and cooled chassis which are offered individually or as integrated 32-bit OEM computer systems.

An early procedure in a configuration exercise is to divide the computer system into its constituent subsystems: Processor, Memory, and Peripheral. Each subsystem in the System 432/600 product family is an independent, decentralized entity. The function of each subsystem is distributed over a number of independent boards, which allows an incremental approach to selecting subsystem modules for a particular range of performance.

Processors in a System 432/600 are either a General Data Processor (GDP) or Interface Processor (IP). At least one GDP is necessary to provide data processing capability; one IP is necessary to implement each Peripheral Subsystem interface. An Interface Processor Link (IPL) board is necessary to interface the System Bus backplane to each IP board and its associated Multibus backplane. A Processor Link (ProcLink) cable connects the IPL and IP boards.

The number of processors in a system may vary from two to six. The optional four processors may be any mix of General Data Processors and Interface Processors. For processing intensive applications, adding GDP boards will improve system throughput. No electrical or software considerations are necessary when adding GDP boards to a system.

All peripheral device functions are controlled and coordinated by a user-selected Attached Processor (AP). Peripheral capabilities may be expanded by adding any Multibus-compatible controller or Multimodule board. This allows Peripheral Subsystems to be configured to provide mass storage, DMA functions, data communications, and analog/digital device control, by simply adding boards to the Multibus backplane. The System 432/600 architecture allows adding complete Peripheral Subsystems (additional Multibus backplanes and logic boards) for further input/output enhancement. A maximum of five Multibus backplanes may be configured in one System 432/600 to provide five complete, independent Peripheral Subsystems in a single shared-memory computer system.

The amount of memory in a System 432/600 depends on the number of SA boards installed. The logical addressing capability permits 16 SA boards. Thus, assuming a System Bus backplane with 16 SA board slots, a System 432/600 could be configured with memory sizes ranging from 256K bytes to 4M bytes. The largest System Bus backplane currently offered by Intel, however, is the 18-slot backplane which provides 10 slots for SA boards. This backplane permits a maximum main memory size of 2.5M bytes of ECC-protected RAM memory.

A memory interleave option is available to enhance system performance. This option uses two identical banks of memory with alternate addresses to allow overlapping operations for faster data access.

Only one MC board is used in any system, regardless of the number of SA boards in the system.

#### BACKPLANES

Two types of backplanes are available for System 432/600 modules: System Bus and Multibus. System bus backplanes come in 6-, 12-, and 18-slot sizes. Multibus backplanes come in 6-slot and 12-slot sizes. System Bus and Multibus backplanes of a given size (e.g., 6-slot backplanes) have the same form factor to ensure mechanical compatibility, regardless of the configuration of a particular system. System 432/600 backplanes are four layer boards with internal ground and power planes, and with ground shields between signal lines to provide controlled line impedance. All backplane signal lines are terminated.

Note that two or more backplanes do not connect together to form one larger backplane; each of the five backplanes is an independent unit.

System Bus backplanes accept and interconnect the System 432/600 Memory Controller, Storage Array, General Data Processor, and Interface Processor Link boards. Each System Bus backplane has one dedicated slot for the Memory Controller board. The seventh processor slot of the 18-slot backplane is reserved. System Bus slot allocations are shown in Table 2-1.

A System Bus backplane requires connection only to +5 volts and ground. Two 5/16-inch diameter holes are provided in the backplane to accept bolt-on power lugs.

| Syste | m Bus Backplane<br>Size | Processor<br>Slots<br>(IPL or GDP) | Memory<br>Controller | Storage Array<br>Slots |

|-------|-------------------------|------------------------------------|----------------------|------------------------|

| 6     | Entry Level             | 3                                  | 1                    | 2                      |

| 12    | Medium                  | 5                                  | 1                    | 6                      |

| 18    | Large                   | 6                                  | 1                    | 10                     |

Table 2-1. System Bus Slot Allocations

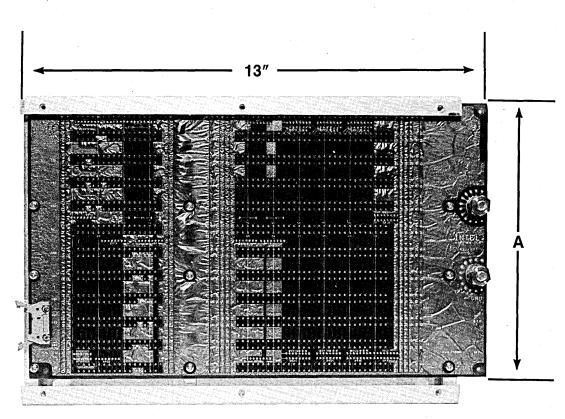

Figure 2-1 shows dimensions and mounting holes of the System Bus backplane.

6 SLOT 4.5" A = 12 SLOT 9" 18 SLOT 13.5"

2-3

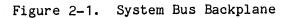

System 432/600 Multibus backplanes accept and interconnect the Interface Processor board, Attached Processor board, and standard Multibus device controllers. The Multibus backplanes (6-slot iSBC 432/615 and 12-slot iSBC 432/616) are compatible with the card spacing, mounting dimensions, and power distribution of the System Bus backplane; either may be mounted in any position of a card cage.

An IP board may occupy any position on the Multibus backplane. For mechanical reasons, P2 of the two outside board positions is not available for external connection. If a Multimodule board is added to a PC board, the combined board thickness will require two adjacent Multibus slot positions. The AP usually occupies the end two slots next to the System Bus and IPL boards. Dimensions for Multibus backplanes are shown in Figure 2-2.

$A = \frac{6 \text{ SLOT } 4.5''}{12 \text{ SLOT } 9''}$

#### LOGIC BOARDS

| The | five | types of logic boards in the System 432/600 set are: |  |

|-----|------|------------------------------------------------------|--|

|     |      | General Data Processor board GDP                     |  |

|     |      | Interface Processor board IP                         |  |

|     |      | Interface Processor Link board IPL                   |  |

|     |      | Memory Control board MC                              |  |

|     |      | Storage Array board SA                               |  |

|     |      |                                                      |  |

The following additional board is necessary to complete a System 432/600 configuration:

Attached Processor board ..... AP

An example is the Intel System 432/670 Integrated Computer System, which uses an iSBC 86/12A as the Attached Processor.

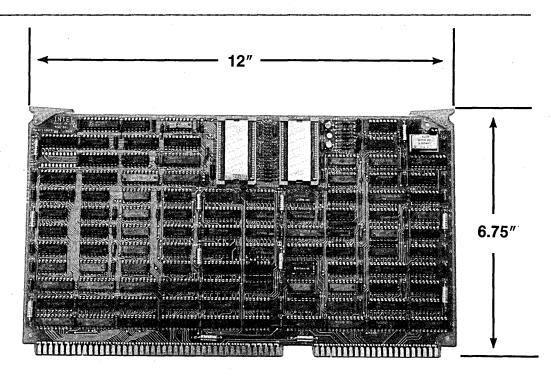

#### Figure 2-3. PC Board Form Factor

Key slots are cut in each System 432/600 board connector to correspond to physical position areas on the System Bus backplane, preventing boards from being installed incorrectly. Slots are cut between pins on both P1 and P2 connectors, as shown in Table 2-2.

| PCB | P1           | P2           |

|-----|--------------|--------------|

|     | between pins | between pins |

| GDP | 15-17        | 5-7          |

| IPL | 15-17        | 5-7          |

| MC  | 29-31        | 13–15        |

| SA  | 71–73        | 37-39        |

Table 2-2. PC Board Key Slots

Clock generators reside on IP, GDP, and MC boards. The MC clock synchronizes all System Bus transfers and Storage Array transfers. The GDP clock synchronizes functions on the GDP board itself. The IP clock synchronizes functions on the IP board, and all data transfers between the IP board and the IPL board. Since each processor has its own clock, processor boards may function at different clock rates. The IP clock rate is determined during configuration as a result of ProcLink cable length.

#### LOGIC BOARD JUMPERS

The Memory Controller board and the Interface Processor board require jumpers to set configuration options. One jumper on the MC board is used to select interleaved or non-interleaved memory operation of all Storage Array board slots on the System Bus backplane.

Jumpers on the IP board are used to select:

- 1. 16 IP window page addresses out of the possible 64K pages of Multibus memory address space

- 2. The I/O base port address

- 3. One of eight interrupt lines to be used by the IP interrupt

- 4. One Multibus driver is jumpered ON or OFF so the IP initializes the Multibus system or simply generates an interrupt

#### PROCLINK CABLES

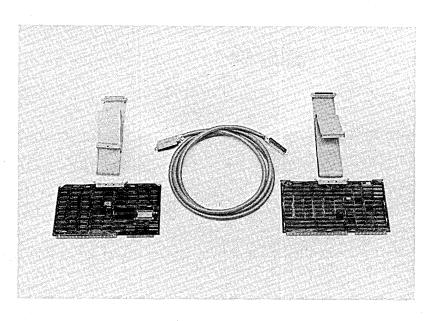

If IP/IPL board-pairs are completely enclosed in a metal cabinet, ribbon type ProcLink cables are used. If a connection outside of a cabinet is necessary (e.g., connecting boards in two separate cabinets) the shielded ProcLink cable is necessary to prevent interference problems. The additional line capacitance of shielded cable affects data transfer rates, and leads to length restrictions or lowering the IP clock rate.

A typical ProcLink configuration is a 20-inch ribbon cable (board to rear connector plate), 10-foot shielded cable (chassis to chassis), and another 20-inch ribbon cable as shown in Figure 2-4. A 36-inch external cable with two 20-inch internal cables is the maximum length usable with an 8 MHz IP clock rate. If the external cable length is increased, the IP clock rate must be set to 5 MHz. Table 2-3 is a matrix of cable types, lengths, and clock rates for different internal and external combinations.

#### Table 2-3. ProcLink Cables

| INT                                                    | ERNAL             | EXTERNAL                        |                    |

|--------------------------------------------------------|-------------------|---------------------------------|--------------------|

| Length<br>20"                                          | IP Clock<br>8 MHz | Length<br>36"                   | IP Clock<br>*8 MHz |

| 72"                                                    | 8 MHz             | 72"                             | 5 MHz              |

| 120"                                                   | 8 MHz             | 120"                            | 5 MHz              |

| The 36-inch ext<br>internal cables<br>increase in eith | may be operated   | with an 8 MHz<br>external cable | clock. Any         |

#### POWER AND COOLING

Power and cooling requirements for System 432/600 PC boards are given in Table 2-4 at the maximum DC voltage of +5.0V plus 5.0%.

| BOARD | Max Amps @ +5.25 volts | Cooling                      |

|-------|------------------------|------------------------------|

| GDP   | 7.0                    |                              |

| IP    | 5.5                    | 300 LFPM or 10 cfm per board |

| IPL   | 6.5                    | at 0 to 40 degrees C.        |

| MC    | 6.5                    |                              |

| SA    | 7.0                    |                              |

Table 2-4. Power and Cooling

#### CARD CAGES

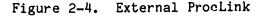

Three card cages are available, in 6-, 12-, and 18-slot sizes. Card cages do not contain power supplies or cooling fans. Mounting holes in the bottom of the large card cages will accept 6-, 12-, or 18-slot backplanes. Holes in the side rails contain nylon card guides, and are on 0.7 inch centers to match backplane connector spacing.

Since mounting dimensions are standard on iSBC 432/610, 432/611, and 432/612 System Bus and iSBC 432/615 and 432/616 Multibus backplanes, they may be mounted in any position in a larger card cage to allow maximum configuration freedom. Card cage configurations are shown in Figure 2-5.

More than one card cage may be used in a single system, and card cage sizes may be intermixed in a system.

#### POWERED AND COOLED CHASSIS

The iSBC 432/630 chassis is a versatile and compact enclosure for System 432/600 modules. It powers and supports any combination of up to 18 System Bus and/or Multibus PC boards, and provides a microcomputer-controlled Switch and Light panel interface for operator use.

The chassis is approximately 12 inches high, 17 inches wide and 22 inches deep. In this discussion, right and left are determined by looking at the front of the chassis.

This universally-styled package may be used as a table top unit or be RETMA rack-mounted. Two AC source power options are available. The iSBC 432/630 uses 120 VAC/60 Hz line power; the iSBC 432/631 operates from 230 VAC/50 Hz.

Figure 2-7 shows the iSBC 432/630 chassis.

# Figure 2-7. iSBC 432/630 Chassis with the System 432/670 Configuration

Modules constituting an iSBC 432/630 chassis are:

- a rigid aluminum support frame

- an 18-slot card cage

- three cooling fans for logic boards in the card cage

- a 750 watt 4-level switching power supply (+5, -5, +12, and -12 volts)

- an AC circuit breaker ON/OFF switch and AC line filter

- a programmable operator's switch and light panel on the front of the chassis

- removable external connector plates on the rear panel

- metal cover panels on the frame that provide EMI/ESD shielding

The microcomputer-controlled Switch and Light (SL) logic board associated with the operator's panel provides support for up to four subsystems, and remote control capability. The control component for the board is an Intel 8748 MCS 48 microcomputer. The 8748 has a user-programmable and erasable EPROM program memory. Jumpers on the board select the 4-bit address for the 8748. These may be wired to a remote cable to allow remote selection of the unit, if desired. The remote interface is an RS-232C serial data communication port that transfers command and status information to and from the board.

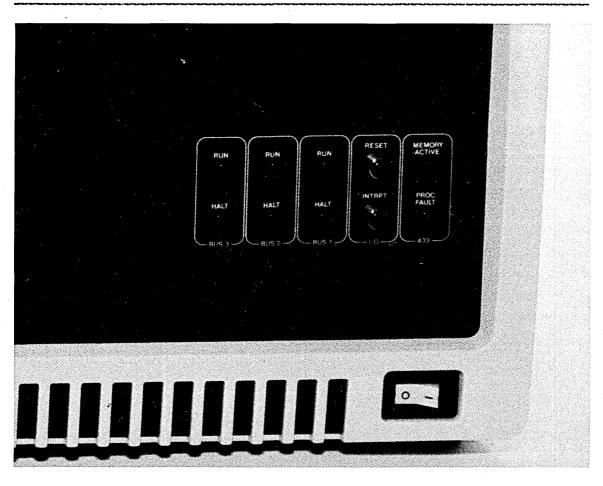

Figure 2-8 shows the operator's panel.

Figure 2-8. Operator's Panel

In configurations with more than one Peripheral Subsystem (more than one Multibus backplane), the Attached Processor in one Peripheral Subsystem must be designated as the controlling AP. The controlling AP is connected to Port 2 of the SL board, from which it receives reset, interrupt, and power fail signals. Operator switches and indicators are on the SL board which is mounted on the front of the chassis. Holes in the front panel of the chassis allow the lights and switches to protrude for operator indication and access. Status indicators show MEMORY ACTIVE and PROCESSOR FAULT conditions for a System 432/600 Central System, and RUN or HALT conditions for one, two, or three Peripheral Subsystems. Switches allow resetting or interrupting the controlling Attached Processor via firmware in the 8748 microcomputer.

Power fail logic on the SL board monitors both AC and DC valid conditions. If the DC valid condition fails, the SL board sends a Reset signal to the Central System and all three Peripheral Subsystems. If the AC valid condition fails, the Multibus Power Fail signal (PFIN) is asserted for 5 MS, then an initiate signal (INIT) will be sent to the controlling Attached Processor of the system.

Six cable connectors are located on the SL board:

- 1. Port 1, System 432/600 Central System (System Bus backplane)

- 2. Port 2, Peripheral Subsystem (Multibus backplane)

- 3. Port 3. Peripheral Subsystem (Multibus backplane)

- 4. Port 4. Peripheral Subsystem (Multibus backplane)

- 5. AC/DC power sense for power fail reset/interrupt control

- 6. RS-232C Remote Port

Flexibility in backplane selection for the card cage provides a wide range of system configurations within the chassis. System Bus backplane selections are 6-, 12-, and 18-slot, with 6- or 12-slot Multibus backplanes available. Within the 18-slot size limit, any backplane type, size or position mix may be selected for the card cage.

Three cooling fans on the left side of the chassis blow room air across the logic boards. System logic boards and the chassis are designed to operate through an ambient temperature range of 0 degrees to 40 degrees Celsius.

The power supply is a regulated, protected switching type that provides four voltages: +5, -5, +12, and -12 volts. Maximum combined power output of the supply is 750 watts. This is sufficient for any combination of System Bus and/or Multibus backplanes and 18 logic boards. The power supply has its own internal cooling fan. A series AC line filter reduces the effect of line noise on system logic boards, and reduces external radiation by the chassis. There are three cable connector cut-outs in the rear panel of the chassis. The cut-out covers may be removed, installed with bulkhead connectors, and replaced on the rear panel. This provides a simple means of connecting cable shields to chassis ground, and retains the EMI/ESD shielding integrity of the chassis. Because of the shielding and line filter, the iSBC 432/630 chassis surpasses the FCC standard for conductive radiated noise.

### CONFIGURING A SYSTEM 432/600

Configuring a System 432/600 is a simple process of selecting building blocks for each subsystem in turn. No effort is necessary to forge the subsystems into a complete functional system; that is automatic as a result of the System 432/600 architecture. Configuring a System 432/600 is a four-step process of determining and selecting:

- 1. Memory size, Interleave option, and future expansion needs

- 2. Processing needs

- 3. Input/Output needs

- 4. Backplanes, ProcLink cables, card cages, and power requirements

Pointers on configuration criteria are given in the above order.

The largest System Bus backplane offered by Intel contains six slots for processor boards, one Memory Controller board slot, and slots for 10 SA boards.

#### MEMORY SUBSYSTEM CONFIGURATION

Four items should be considered in configuring a Memory Subsystem:

- 1. Memory size

- 2. Interleave or non-interleave option

- 3. Future expansion

### MEMORY SIZE

The first consideration in determining memory size is the operating system to be used and the amount of memory it requires. Other system software such as compilers and basic utilities must also be considered, as must the space required for application programs. Input/Output needs must also be included, although these needs are minimal in Central System memory since the Attached Processor uses AP memory in the Peripheral Subsystem as it performs real-time device control and input/output management.

When the needed memory size is known, the number of SA boards can be calculated. Each SA board contains 256K bytes.

Although the Memory Controller can logically address 16 SA boards, the 18-slot System Bus backplane contains a maximum of 10 SA boards. Thus, the maximum memory size currently offered on a System 432/600 is 2.5M bytes.

The physical address of an SA board is established simply by its slot position in the System Bus backplane. There are no operational jumpers on an SA board and no changeable PROMs. The expansion increments in memory size depend only on interleaved or non-interleaved operation. Table 2-5 shows the minimum and maximum memory sizes and the memory expansion increments.

## INTERLEAVE OPTION

Only one Memory Controller board is necessary in any system, regardless of the number of Storage Array boards. One jumper exists on the MC non-interleaved operation. board to select interleaved or The interleave option will provide an approximate 10% increase in single GDP performance and a 25% to 30% increase in the system's multiprocessor performance range. If the interleave option is selected, Storage Array boards must be installed in pairs to provide for the alternate bank addressing used in interleaved operation.

To change an existing system from non-interleaved to interleaved operation, the MC board jumper must be changed and an even number of SA boards installed.

| RAM Size        | Minimum<br>Memory Size | Maximum<br>Memory Size | Expansion<br>Increment |

|-----------------|------------------------|------------------------|------------------------|

| Interleaved     |                        |                        |                        |

| 64K RAM         | 512K Bytes             | 2.5M Bytes             | 512K Bytes             |

| Non-Interleaved |                        |                        |                        |

| 64K RAM         | 256K Bytes             | 2.5M Bytes             | 256K Bytes             |

## Table 2-5. System Memory Sizes

## FUTURE EXPANSION

The simplicity of System 432/600 memory size expansion should be kept in mind while configuring the Memory Subsystem, and when determining System Bus backplane and card cage size. If backplane slots are available, memory size may be expanded by simply plugging in additional SA boards. No change is necessary to systems or applications software when adding SA boards to a system.

#### PROCESSOR SUBSYSTEM CONFIGURATION

In a System 432/600, a "processor" is either a General Data Processor board or an Interface Processor board. An IP board physically resides on the Multibus backplane and is logically a slave to the AP. GDP and IPL boards reside on the System Bus backplane. Each IP board requires one Interface Processor Link board to complete the communications path from the System Bus backplane to the Multibus backplane. There are a maximum of six processor positions in a System Bus. There must be one GDP board and one IPL board. The remaining processor positions may contain any mix of GDP and IPL boards.

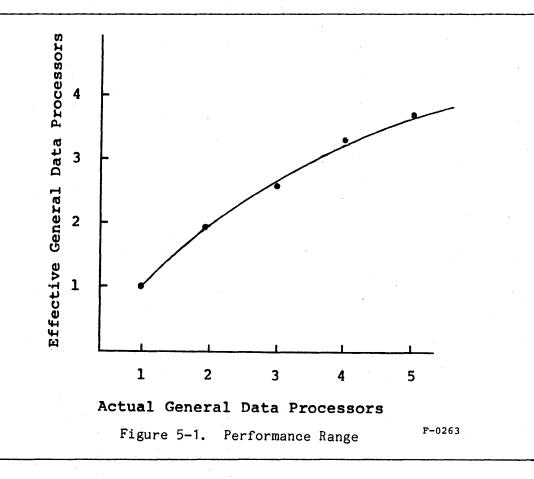

A System 432/600 will typically provide a four-times performance increase between the entry level system with one GDP board and non-interleaved memory, and the maximum system with five GDP boards and interleaved memory.

Ideally, the Memory Subsystem can support as many processors as it takes to consume 100% of the available memory bandwidth. This number varies with the application, depending on how often a typical GDP initiates a memory access. In a processing-intensive application, GDPs typically consume more time between memory access requests. In this case, adding GDP boards will improve system throughput. The memory bandwidth will always support at least three GDPs; if the instruction mix is at least moderately processing-intensive, the system throughput will increase when the fourth and fifth GDPs are added.

If slot positions are available in the System Bus backplane, GDPs may be added to an existing system by plugging in GDP boards. No changes are necessary to system or applications software.

2-16

Similarly, removing a GDP board from a multiprocessor system does not affect system software. Full system operation and capability is retained after removing a GDP board (e.g., because of a malfunction), with some reduction in system throughput.

GDP and IP boards are available with either a 5 MHz or 8 MHz clock rate. Processors operate-asynchronously, and processor clock rates may be intermixed in a system.

#### PERIPHERAL SUBSYSTEM CONFIGURATION

Peripheral Subsystem modules reside in a System 432/600 Multibus backplane. In general, any Multibus-compatible module may be used in a System 432/600 Peripheral Subsystem. For a listing of typical Multibus modules available, refer to the Intel Systems Data Catalog.

A System 432/600 may contain from one to five Peripheral Subsystems. Each Peripheral Subsystem must contain one Interface Processor board and one Attached Processor board. Each IP board must have a ProcLink cable to connect it to its companion IPL board on the System Bus backplane. The cable type and length will limit the maximum ProcLink data rate, and thereby the IP clock rate. Refer to the PROCLINK CABLES paragraph for details.

Three general areas must be considered in configuring a System 432/600 Peripheral Subsystem: peripheral device functions, the Attached Processor, and the performance range.

#### PERIPHERAL DEVICE FUNCTIONS

The System 432/600 Diagnostic Software package requires a CRT and keyboard (or teletype), and one floppy disk unit to run the diagnostic package. Besides typical operator interface devices such as these, additional mass storage devices and communication units may be configured. When the peripheral device requirements have been defined, Multibus-compatible controller boards and Multimodule boards may be selected for those devices.

#### ATTACHED PROCESSOR

One Attached Processor is necessary in each Peripheral Subsystem of a System 432/600. Any Multibus-compatible computer may be used as the Attached Processor. The AP may be either an 8-bit or 16-bit device. The System 432/600 Diagnostic Software package was written for an iSBC 86/12A Attached Processor.

The Interface Processor chip on the IP board recognizes five "windows" in one specific 64K-byte page of Multibus system memory. This 64K-byte page is the AP's communication path to Central System memory. The base address of the specific page is selected by jumpers on the IP board. The number and operating speed of peripheral devices selected will affect the choice of an AP. In a system with more than one Peripheral Subsystem, it is possible to use different types of Attached Processors, depending on the needs of the different Peripheral Subsystems.

When the AP has been selected, the AP operating system to be used and the necessary device control routines should be analyzed to determine AP memory requirements. Additional AP memory boards may be needed on the Multibus backplane.

## PERIPHERAL SUBSYSTEM PERFORMANCE RANGE

Many applications will utilize both a large number of low speed devices and one or more high data-rate devices. In these instances, it may be desirable to configure more than one Peripheral Subsystem in a System 432/600.

The maximum number of Peripheral Subsystems in a System 432/600 is five. In an input/output intensive application, one or more subsystems may be devoted to low speed terminals, and one or more to high data-rate devices. These options should be considered when making the choice of the AP to be used.

Complete Peripheral Subsystems may be added to an existing system by adding an IPL board to the System Bus, and an additional Multibus backplane with IP, AP, and device controller boards. The only limitation is the number of empty processor slots in the System Bus backplane, since an IPL board is necessary for each Peripheral Subsystem in the configuration.

### BACKPLANE SELECTION

When board requirements of a configuration have been determined, backplane type and size must be selected. Future growth and the simplicity of expansion of all three subsystems should be considered when selecting backplane sizes.

Each System Bus backplane contains one dedicated slot for a Memory Controller board. SA boards reside on one side of the Memory Controller; GDP and IPL boards reside on the other. System Bus backplanes are available in 6-, 12-, or 18-slot sizes. Table 2-6 shows the number of processor board slots and SA board slots in each backplane size.

Multibus backplanes are available in 6- or 12-slot sizes. For mechanical reasons, P2 of the outside slot positions is not available for connection on Multibus boards.

| Backplane Size | Processor slots | SA Slots |

|----------------|-----------------|----------|

| 6 slot         | 3               | 2        |

| 12 slot        | 5               | 6        |

| 18 slot        | 6               | 10       |

Table 2-6. System Bus Backplanes

### CONFIGURATION SUMMARY

Decision steps in a configuration exercise are:

- 1. Memory size (consider future expansions)

- 2. Interleave versus non-interleave memory option

- 3. Number of General Data Processors (consider future expansions)

- 4. Number of Peripheral Subsystems (consider future expansions)

A. Number of IP/IPL boards

B. Number and type of Attached Processors

- C. Number and type of peripheral device controllers

- D. Number and type of AP memory boards

5. Type, length, and number of ProcLink cables

- 6. Type and size of backplanes

- 7. Size and number of card cages

- 8. Power supply and cooling requirements

CHAPTER 3 SYSTEM FUNCTIONAL DESCRIPTION

#### INTRODUCTION

This chapter provides a detailed functional description of overall system operation and each module's operation in the system. It describes the modularity and extensibility of memory, processor, and peripheral subsystems at a block diagram level.

### GENERAL DESCRIPTION

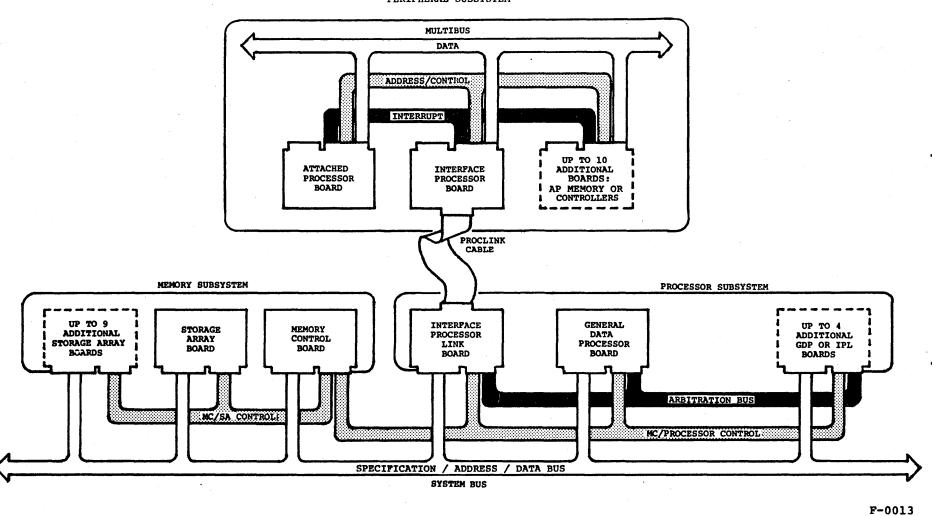

The following discussion refers to Figure 3-1, System 432/600 Block Diagram. As shown in Figure 3-1, the system is divided into three separate subsystems: Memory, Processor, and Peripheral.

The user-selected Attached Processor coordinates the activity of all peripheral processes. It reacts to real-time concerns of peripheral devices and controllers, and supports input/output data transfers and operator control devices. The only human control and interface to the 432/600 Central System is via software running on the AP.

Any Multibus-compatible peripheral device controller or Multimodule board may be used with the Multibus backplane and controlled by software running on the AP.

All communication with System 432/600 memory and General Data Processors is through the Interface Processor board. In performing these functions, the IP is an intelligent adaptor or slave to the AP.

A major function of the iAPX 43203 Interface Processor chip is to map a portion of the AP memory address space into areas of 432/600 main memory. The IP chip does this by providing five "windows" into memory for AP use; a window is simply a range of sequential AP memory addresses. To communicate with 432/600 main memory, the AP simply reads or writes to the IP as it would to AP memory. The IP provides the same hardware protection of all data structures in 432 memory as GDPs provide. All memory mapping, fault detection, handling, and reporting functions are internal to the IP chip.

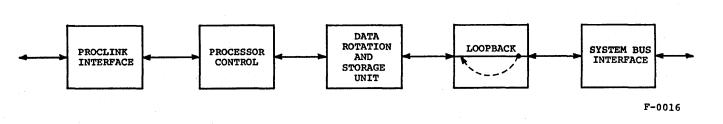

The physical communication path from the Multibus backplane to the System Bus backplane is via the ProcLink cable connected from the IP board to the Interface Processor Link board. Data transfer occurs two bytes at a time over 16 lines in the cable. A Block Mode 8-byte burst transfer is used to meet requirements of high-speed peripheral devices.

#### PERIPHERAL SUBSYSTEM

System Functional Description

432/600 System Reference Manual

3-2 2-2 432/600 System Reference Manual

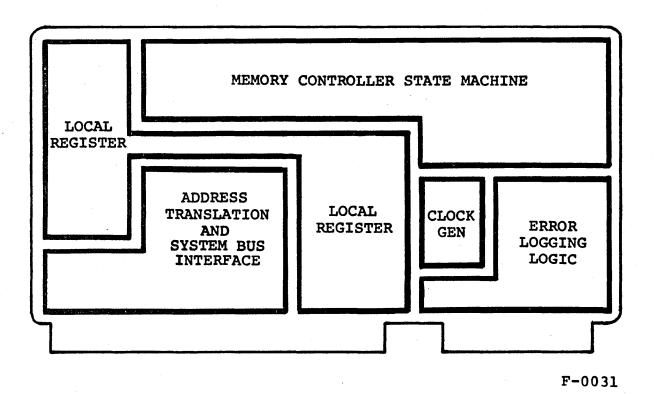

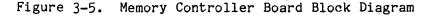

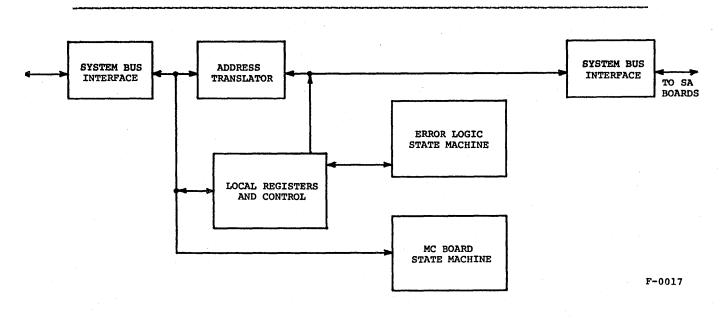

The Memory Subsystem consists of one Memory Controller board and one to 16 Storage Array boards. Note, however, that the largest System Bus backplane currently offered by Intel supports a maximum of 10 SA boards. One common bus for access Specification, Address, and Data interconnects all PC boards on the System Bus. This SAD bus is 36-bits wide, four 8-bit bytes plus one parity bit for each byte. The System Bus provides one set of control/status lines from the Memory Controller to SA boards, and a separate set of control/status lines to General Data Processor and Interface Processor Link boards. A separate group of lines on the backplane are used by processor boards to arbitrate priority for the next memory access.

The Memory Controller performs 1-, 2-, 4-, 6-, 8-, and 10-byte accesses as requested by system processors. The byte address is accepted from a processor, mapped to the proper SA address format, and transferred to the SA board. The Memory Controller also supports local registers, local register accesses, and Interprocessor Communications (IPCs) for the system.

Storage Array boards store data in word organized 39-bit wide banks. Each four-byte (32-bit) data word is stored with a seven-bit Error Correction Code. This allows SA boards to detect and correct single bit errors, and detect double bit error conditions. Error condition information is stored in local registers on the MC board.

All processors (GDPs and IP/IPLs) use a common protocol for requests to the Memory Controller to access memory, system local registers, or perform IPC operations. The Memory Controller accepts these access requests and provides the appropriate response.

Each processor gets its identification number from its physical position in the backplane. The processor ID is used in IPC and self-dispatching procedures.

The processors use the Arbitration Bus on the backplane to determine which processor has the right to make the next memory access. The arbitration is under automatic hardware control, and is transparent to the number of processors in a system. Since the IP resides on the Multibus backplane, each IPL board contains arbitration logic for its companion IP.

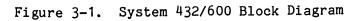

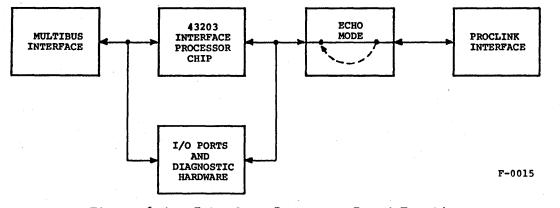

#### INTERFACE PROCESSOR BOARD

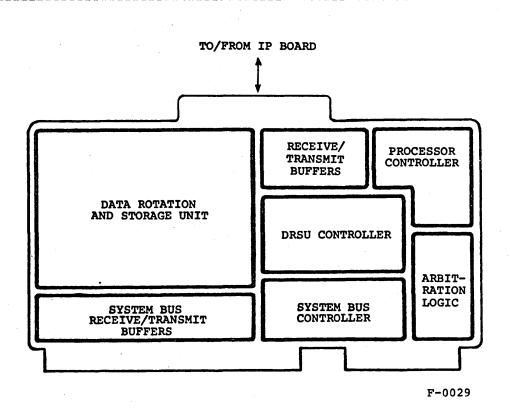

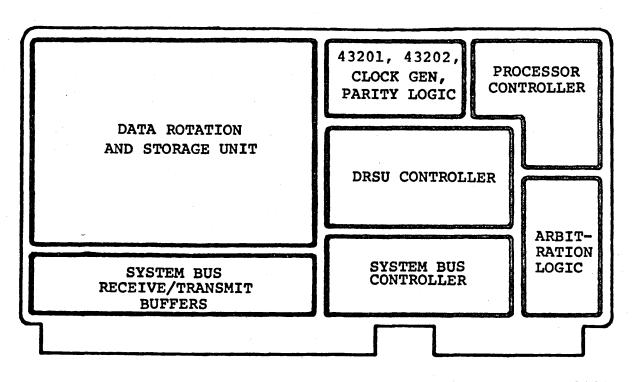

Figure 3-2 shows a functional block diagram of the IP board. The blocks show the approximate location and physical area of components used for particular logical functions on the board.

#### MULTIBUS INTERFACE AND DIAGNOSTIC SUPPORT LOGIC

The Multibus block provides the standard Multibus address, data, control, and interrupt interface. IP board logic allows the use of either an 8-bit or 16-bit Attached Processor in a System 432/600.

Jumpers on the IP board allow selection of one of eight interrupt lines to be driven to the Multibus backplane and the AP.

Logic on the IP board provides 16 eight-bit I/O ports (registers) accessible to AP software. Nine of these are used; the others are duplicates or undefined. The base address of these ports is selected by jumpers on the IP board. Ports 0 and 1 are used for all data transfers between the AP and the 432/600 Central System during PASS mode in diagnostic operation. The remaining seven ports are used for initialization, control, and diagnostic functions for the System 432/600.

Central System communication with the AP is done through a 64K-byte "page" of AP memory. The IP board provides 16 possible base addresses, or 16 possible 64K-byte pages, for this purpose. One of the 16 possible pages is selected by jumpers on the IP board.

The IP recognizes five non-overlapping spaces or "windows" in the jumper-selected 64K-byte page of AP memory. Each window (via the IP chip) has its own address mapping function. The AP simply accesses its memory window space to transfer data to/from 432/600 main memory.

In Random Mapping Mode, each transfer is an independent 2-byte transfer across the ProcLink cable. By contrast, Block Mode provides a buffered 8-byte block transfer for high-speed peripheral devices. Windows 0, 2, and 3 open only to data segments in main memory, and Window 4 opens only to the Interface Processor Data Segment in main memory. Window 1 opens to data segments or interconnect space. Window uses are:

- Window 0 may be set by software to Random Mapping Mode or Block Mode transfers. (Initialization forces Window 0 to open in Block Mode.)

- 1 Window 1 is always in Random Mapping Mode. Software may set Window 1 to access either 432/600 main memory or the Interconnect address space. In the System 432/600, Interconnect access space is used to access system local registers. (Initialization closes Windows 1, 2, and 3.)

- 2,3 Windows 2 and 3 may be used only for Random Mapping Mode.

- Window 4 is the Context Control window, and always accesses the Interface Processor Data Segment. This window allows the AP to access the IP function request facility. The AP writes operands and operation codes into predefined locations of Window 4. The AP may alter window modes, utilize IPCs, and manipulate 432 system objects in this manner.

The preceding description relates to Logical Reference Mode operation of the IP chip. Initialization or an Enter Physical Reference Mode IPC to the Interface Processor will change its operational characteristics to Physical Reference Mode. In this mode, 24-bit addresses from the AP go directly to 432/600 main memory, with no IP address mapping function. Care should be exercised when using Physical Reference Mode, since automatic fault detection is not performed.

Initialization forces the IP chip into Physical Reference Mode with Windows 1, 2, and 3 closed, Window 0 open in Block Mode, and Window 4 open. Window 0 is normally used in Physical Reference Mode to establish an initial object table directory, objects, tables, and initial program instructions in main memory. Window 4 is normally used in Physical Reference Mode to load the proper Processor Object image for the Interface Processor. A "startup IPC" may then be issued to the IP or a GDP. The first IPC to the Interface Processor after initialization will cause it to change to Logical Reference Mode, where logical address mapping is performed and all accesses and mapping functions have automatic fault protection.

## INTERFACE PROCESSOR CHIP, SUPPORT LOGIC, AND CLOCK

Window functions, logical and physical reference modes, data handling, checking, and mapping described previously are controlled by the IP chip. The IP chip checks for three classes of faults: context level, process level, and processor level. Refer to the <u>iAPX 432 Interface</u> <u>Processor Architecture Reference Manual</u> for details on IP chip functions. A fault condition may be detected while the IP is attempting to execute a function for the AP, or while moving data through a window. When a fault is detected, the IP records information about the fault in a fault information area, then interrupts the AP to inform it of the fault condition.

Clock generation on the board provides timing for IP board functions, the ProcLink interface, and the Interface Processor Link board. All transfers to and from the IPL board are synchronized by the IP clock.