# COMMUNICATION SYSTEMS

McGraw-Hill

PRACTICAL GUIDE TO INTEL'S CONNECTIVITY DESIGNS

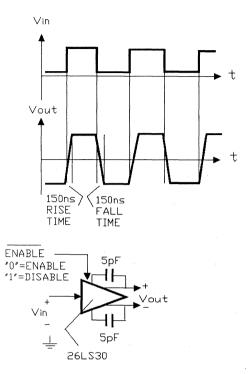

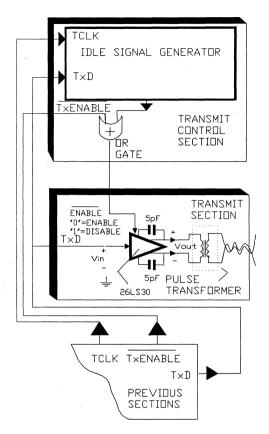

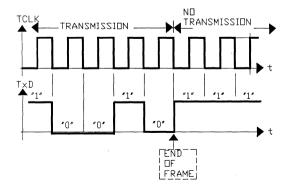

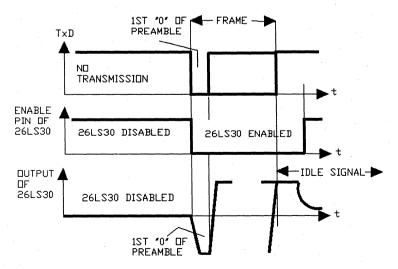

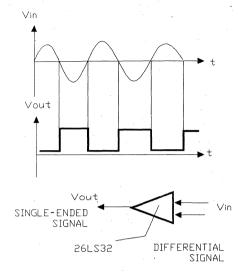

# NATHAN GUREWICH

## Communication Systems

#### Intel/McGraw-Hill Series

#### Published

BABBAR/STECIAK • The Official Intel 386SL Portable Computer Book BUNZEL/MORRIS • Multimedia Applications Development: Using DVI Technology

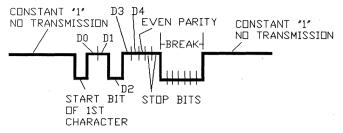

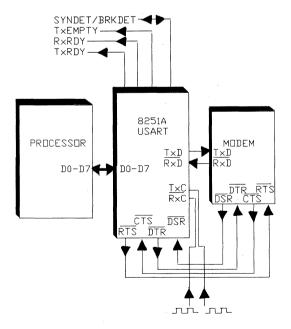

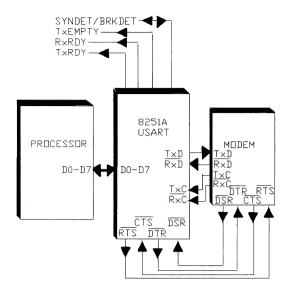

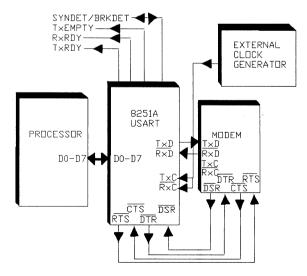

EDELHART • Intel's Official Guide to 386 Computing

INTEL • Intel386 Family Binary Compatibility Specification 2

INTEL • i486 Microprocessor Programming Reference Manual

LUTHER • Digital Video in the PC Environment

MARGULIS • i860 Microprocessor Architecture

RAGSDALE • Parallel Programming

## Communication Systems

Practical Guide to Intel's Connectivity Designs

### **Nathan Gurewich**

#### McGraw-Hill, Inc.

New York St. Louis San Francisco Auckland Bogotá Caracas Lisbon London Madrid Mexico Milan Montreal New Delhi Paris San Juan São Paulo Singapore Sydney Tokyo Toronto

#### Library of Congress Cataloging-in-Publication Data

Gurewich, Nathan

Communication systems : practical guide to Intel's connectivity designs / Nathan Gurewich.

p. cm. — (Intel/McGraw-Hill series)

Includes index.

ISBN 0-07-025234-3

1. Local area networks (Computer networks).2. Electronic digitalcomputers—Circuits.3. Computer network protocols.I. Title.II. Series.TK5105.7.G871992004.6'8—dc2091-46677

91-46677 CIP

Copyright © 1992 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. Except as permitted under the United States Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a data base or retrieval system, without the prior written permission of the publisher.

1 2 3 4 5 6 7 8 9 0 DOC/DOC 9 8 7 6 5 4 3 2

#### ISBN 0-07-025234-3

The sponsoring editor for this book was Daniel A. Gonneau, the editing supervisor was Martha W. Gleason, and the production supervisor was Suzanne W. Babeuf. This book was set in Century Schoolbook. It was composed by North Market Street Graphics.

Printed and bound by R. R. Donnelley & Sons Company.

Information contained in this work has been obtained by McGraw-Hill, Inc. from sources believed to be reliable. However, neither McGraw-Hill nor its authors guarantee the accuracy or completeness of any information published herein and neither McGraw-Hill nor its authors shall be responsible for any errors, omissions, or damages arising out of use of this information. This work is published with the understanding that McGraw-Hill and its authors are supplying information but are not attempting to render engineering or other professional services. If such services are required, the assistance of an appropriate professional should be sought.

## Contents

Foreword ix Preface xiii

| Cha  | oter 1. Introduction to Local Area Networks (LANs)      | 1   |

|------|---------------------------------------------------------|-----|

| 1.1  | The Need for Local Area Networks                        | . 1 |

| 1.2  | Space Division Multiplexing                             | 2   |

| 1.3  | Sharing the Network Cable                               | 4   |

| 1.4  | Central Controller                                      | 6   |

| 1.5  | Cables                                                  | 7   |

| 1.6  | The Node Board                                          | . 8 |

| 1.7  | A Quick Review of the ISO Seven Layers Model            | 9   |

| 1.8  | Equating the LAN Protocol to the ISO Seven Layers Model | 11  |

| 1.9  | The IEEE 802 LAN Protocols                              | 14  |

| 1.10 | The Various LANs in the IEEE 802.3 LAN Protocols        | 15  |

| 1.11 | CSMA/CD Access Method                                   | 17  |

| 1.12 | A Quick Review of Manchester Format                     | 18  |

| 1.13 | The Frame                                               | 19  |

| 1.14 | The Address of a Node                                   | 21  |

| 1.15 | Principle of Operation of an 802.3 LAN                  | 22  |

| 1.16 | Reception of Frames by the Node                         | 22  |

| 1.17 | Transmission of Frames by the Node                      | 24  |

| 1.18 | How Could a Collision Occur?                            | 26  |

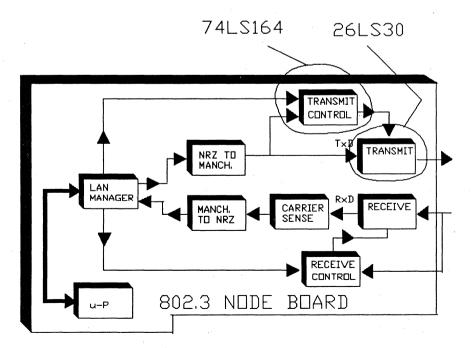

| 1.19 | The Different Sections of the 802.3 Node Board          | 27  |

| 1.20 | Summary                                                 | 30  |

| Cha  | oter 2. The Principle of 1BASE5 (Starlan)               | 31  |

| 2.1  | Introduction to Starlan                                 | 31  |

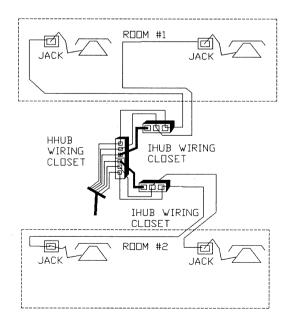

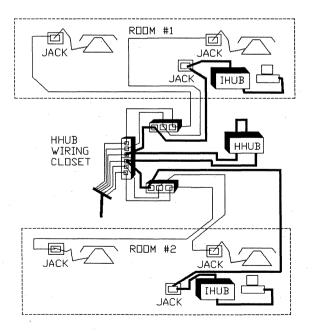

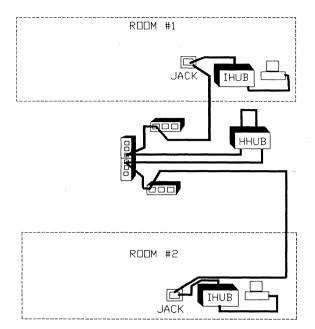

| 2.2  | Connecting Node Boards to the Hub Board                 | 32  |

| 2.3  | Upstream and Downstream Sections of the Hub             | 37  |

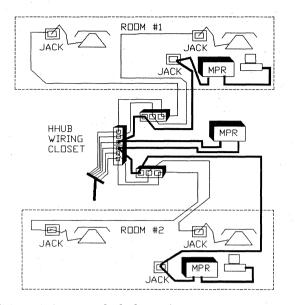

| 2.4  | The Header Hub (HHUB)                                   | 40  |

| 2.5  | Principle of Operation of Starlan                       | 40  |

| 2.6  | The Telephone Wires and Starlan                         | 42  |

| vi                                                            | Contents                                                                                                                                                                                                                                                                           |                     |

|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 2.7                                                           | Using Existing Telephone Wiring for Starlan                                                                                                                                                                                                                                        | 4                   |

| 2.8                                                           | Summary                                                                                                                                                                                                                                                                            | . 4                 |

| Cha                                                           | pter 3. The Transmitter and Receiver of a 1BASE5 (Starlan) Node                                                                                                                                                                                                                    | 4                   |

| 3.1                                                           | Introduction                                                                                                                                                                                                                                                                       | 4                   |

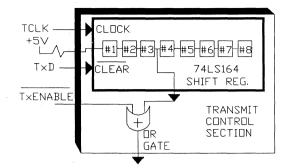

| 3.2                                                           | The Transmit Control Circuit                                                                                                                                                                                                                                                       | 5                   |

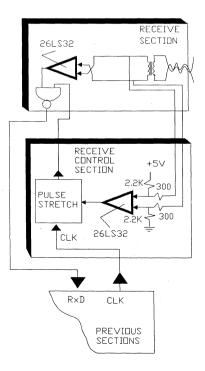

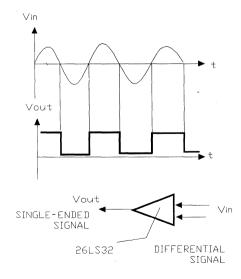

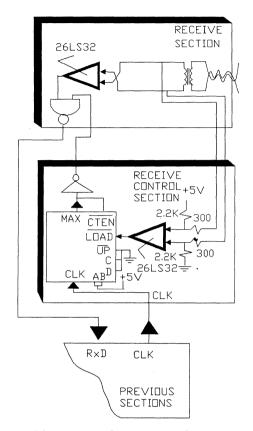

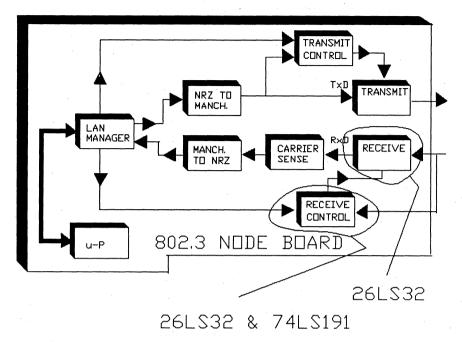

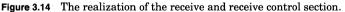

| 3.3                                                           | The Receive and Receive Control Sections                                                                                                                                                                                                                                           | 5                   |

| 3.4                                                           | Squelching the Incoming Signal                                                                                                                                                                                                                                                     | 5                   |

|                                                               | The Receive Control Circuit                                                                                                                                                                                                                                                        | 5                   |

| 3.6                                                           | Summary                                                                                                                                                                                                                                                                            | 6                   |

| Cha                                                           | pter 4. The LAN Manager Section of a Node in 1BASE5 LAN                                                                                                                                                                                                                            | 6                   |

| 4.1                                                           | The Manchester Decoder-Encoder and the Carrier Sense Sections                                                                                                                                                                                                                      | 6                   |

| 4.2                                                           | A Quick Review of the Intel 80188 Processor                                                                                                                                                                                                                                        | 6                   |

| 4.3                                                           | Connecting ROM and RAM Chips to the 80188                                                                                                                                                                                                                                          | 6                   |

| 4.4                                                           | A Quick Review of the On-Chip DMA Controllers of the 80188                                                                                                                                                                                                                         | 6                   |

| 4.5                                                           | The Rest of the 80188 Pins                                                                                                                                                                                                                                                         | 6                   |

| 4.6                                                           | ······································                                                                                                                                                                                                                                             | 6                   |

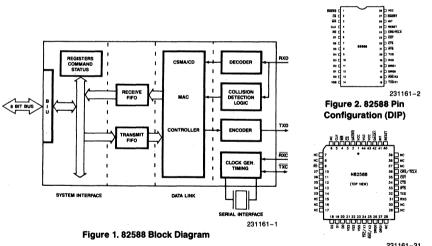

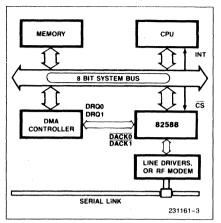

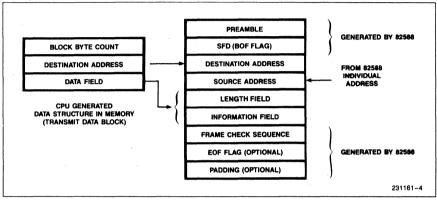

| 4.7                                                           | The 82588-80188 interface                                                                                                                                                                                                                                                          | 6                   |

| 4.8                                                           |                                                                                                                                                                                                                                                                                    | 7                   |

| 4.9                                                           | Summary                                                                                                                                                                                                                                                                            | 7                   |

| Cha                                                           | pter 5. The Software of the 1BASE5 Node Board                                                                                                                                                                                                                                      | 7                   |

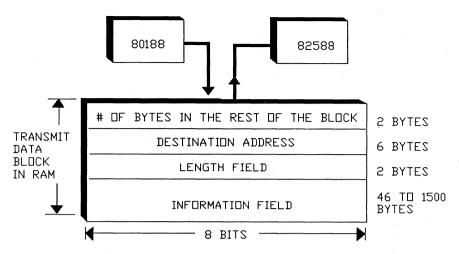

| 5.1                                                           | Transmitting a Frame                                                                                                                                                                                                                                                               | 7                   |

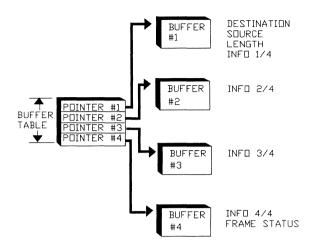

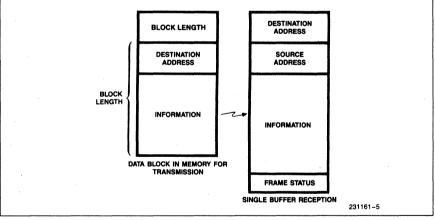

| 5.2                                                           | Preparing Data for Transmission in the RAM Chips                                                                                                                                                                                                                                   | 7                   |

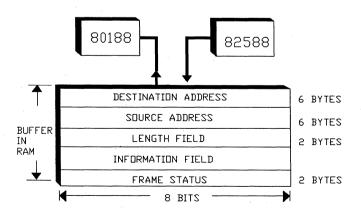

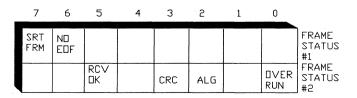

| 5.3                                                           | Storing the Received Data in RAM Chips                                                                                                                                                                                                                                             | 7                   |

| 5.4                                                           |                                                                                                                                                                                                                                                                                    | 7                   |

| 5.5                                                           | The Amount of RAM Buffer Required for Storing Incoming Frames                                                                                                                                                                                                                      | 8                   |

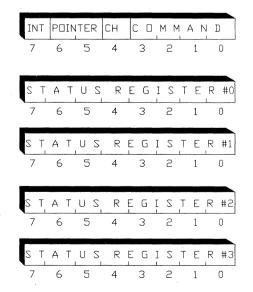

| 5.6                                                           | The Command Register of the 82588                                                                                                                                                                                                                                                  | 8                   |

| 5.7                                                           | ······································                                                                                                                                                                                                                                             | 8                   |

| 5.8                                                           | The FIX POINTER and RELEASE POINTER Commands                                                                                                                                                                                                                                       | 8                   |

| 5.9                                                           |                                                                                                                                                                                                                                                                                    | 8                   |

| 5.10                                                          | The Channel Bit of the Command Byte                                                                                                                                                                                                                                                | ę                   |

|                                                               |                                                                                                                                                                                                                                                                                    | ę                   |

| 5.11                                                          | The Program of the 80188                                                                                                                                                                                                                                                           | 9                   |

| 5.12                                                          | Summary                                                                                                                                                                                                                                                                            | 9                   |

|                                                               |                                                                                                                                                                                                                                                                                    | ę                   |

| 5.12<br>5.13                                                  | pter 6. 10BASE5 (Ethernet) and 10BASE2 (Cheapernet)                                                                                                                                                                                                                                |                     |

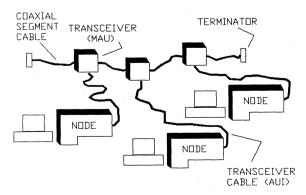

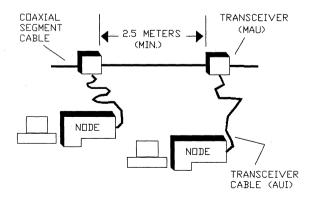

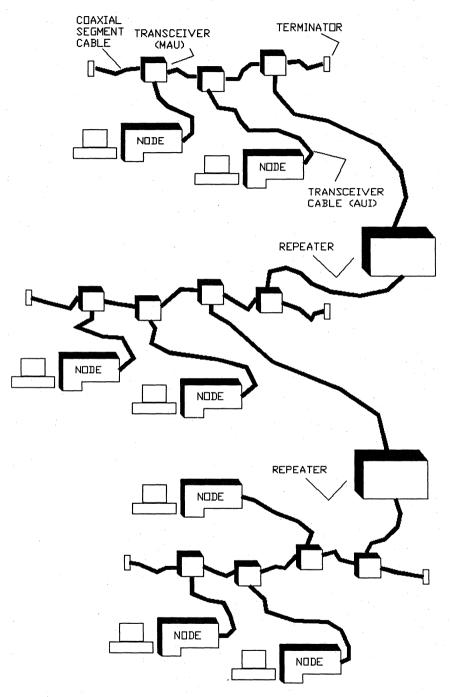

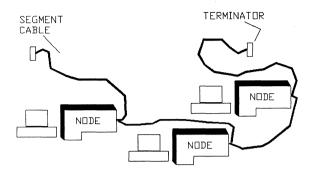

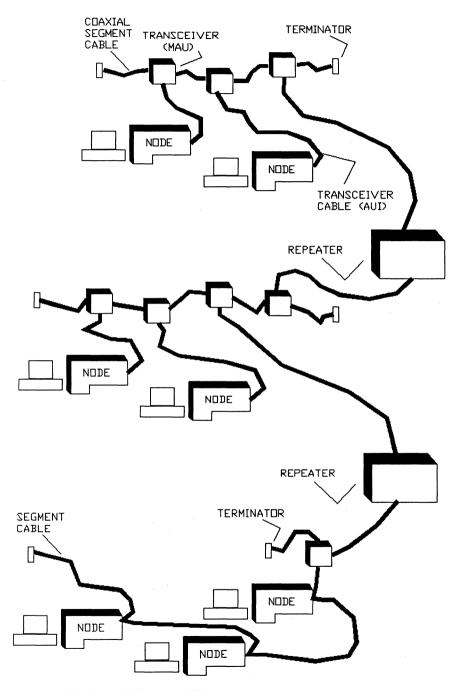

| 5.12<br>5.13<br>Cha<br>6.1                                    | pter 6. 10BASE5 (Ethernet) and 10BASE2 (Cheapernet)<br>The Topology and Components of Ethernet                                                                                                                                                                                     |                     |

| 5.12<br>5.13<br>Cha                                           | The Topology and Components of Ethernet<br>The Topology and Components of Cheapernet                                                                                                                                                                                               |                     |

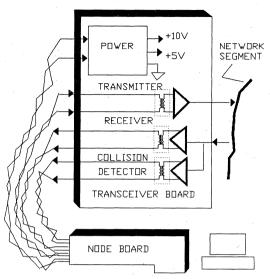

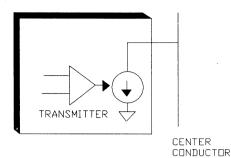

| 5.12<br>5.13<br>Cha<br>6.1<br>6.2<br>6.3                      | The Topology and Components of Ethernet<br>The Topology and Components of Cheapernet<br>The Transceiver Circuit in Ethernet                                                                                                                                                        | 9                   |

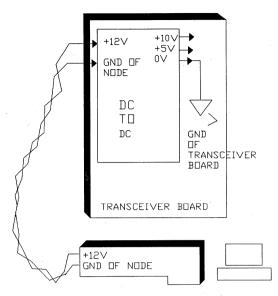

| 5.12<br>5.13<br>Cha<br>6.1<br>6.2<br>6.3<br>6.4               | The Topology and Components of Ethernet<br>The Topology and Components of Cheapernet<br>The Transceiver Circuit in Ethernet<br>Supplying Power to the Transceiver Board                                                                                                            | (                   |

| 5.12<br>5.13<br>Cha<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5        | The Topology and Components of Ethernet<br>The Topology and Components of Cheapernet<br>The Transceiver Circuit in Ethernet<br>Supplying Power to the Transceiver Board<br>Transceiver Chips                                                                                       | 9<br>9<br>10        |

| 5.12<br>5.13<br>Cha<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | The Topology and Components of Ethernet<br>The Topology and Components of Cheapernet<br>The Transceiver Circuit in Ethernet<br>Supplying Power to the Transceiver Board<br>Transceiver Chips<br>The Transceiver Circuit in Cheapernet                                              | 9<br>10<br>10<br>10 |

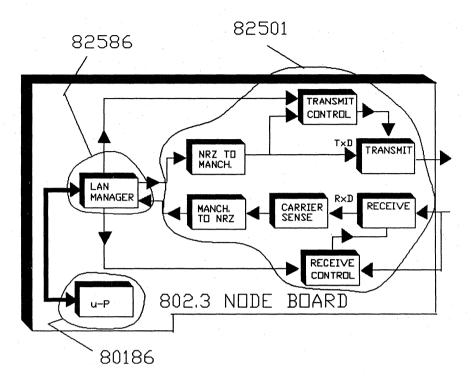

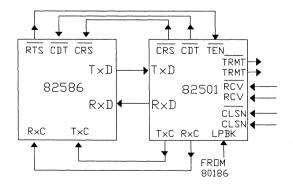

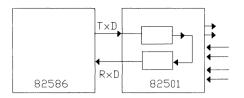

| 5.12<br>5.13<br>Cha<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5        | The Topology and Components of Ethernet<br>The Topology and Components of Cheapernet<br>The Transceiver Circuit in Ethernet<br>Supplying Power to the Transceiver Board<br>Transceiver Chips<br>The Transceiver Circuit in Cheapernet<br>The Node Board in Ethernet and Cheapernet | 9                   |

| 6.9  | Receiving Frames from the Transceiver                                 | 107 |

|------|-----------------------------------------------------------------------|-----|

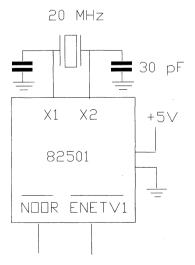

| 6.10 | The Clock of the 82501                                                | 108 |

| 6.11 | Informing the 82586 about Collision                                   | 109 |

| 6.12 | The Loop-Back Concept                                                 | 110 |

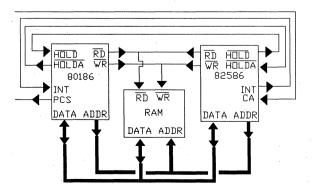

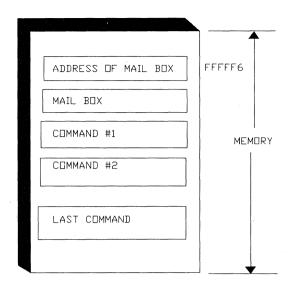

| 6.13 | The Shared Memory Concept                                             | 111 |

| 6.14 | The Operation                                                         | 113 |

| 6.15 | Writing the Program for the 80186                                     | 114 |

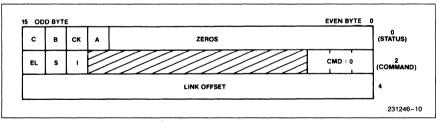

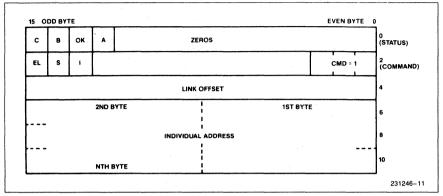

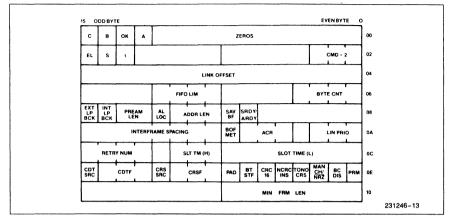

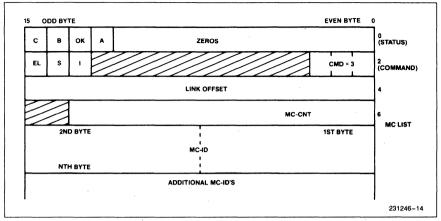

| 6.16 | Command Example                                                       | 115 |

| 6.17 | The High Performance 32-Bit LAN Coprocessors                          | 119 |

| 6.18 | Summary                                                               | 121 |

| Chaj | oter 7. Twisted Pair Ethernet                                         | 123 |

| 7.1  | The Need for an Additional 802.3 LAN                                  | 123 |

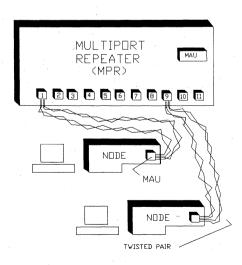

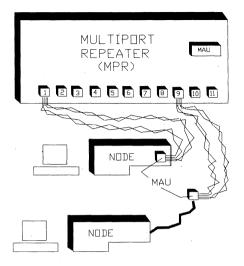

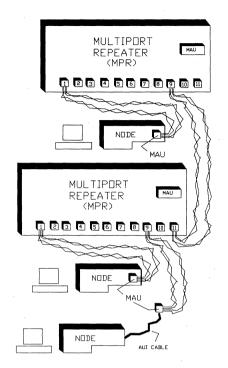

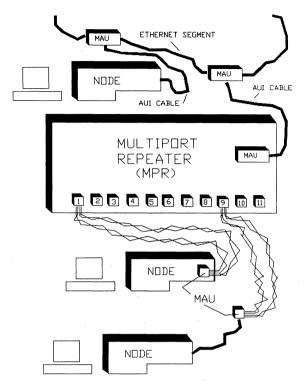

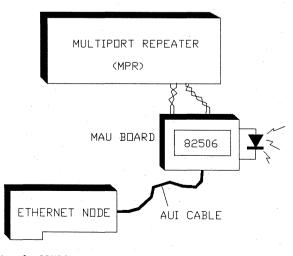

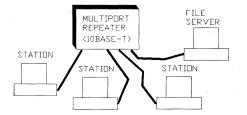

| 7.2  | Connecting Nodes to the Multiport Repeater Board                      | 124 |

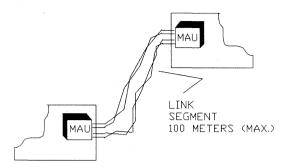

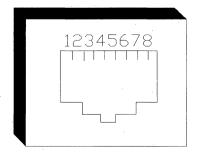

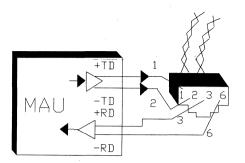

| 7.3  | The Medium Dependent Interface Connector                              | 128 |

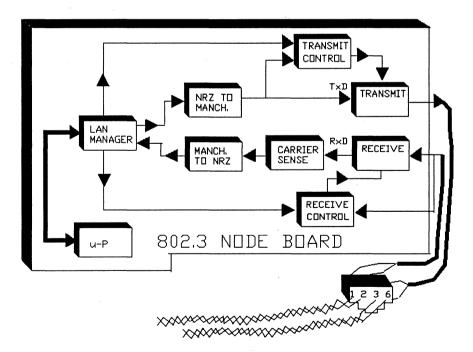

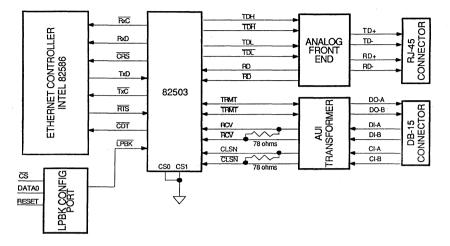

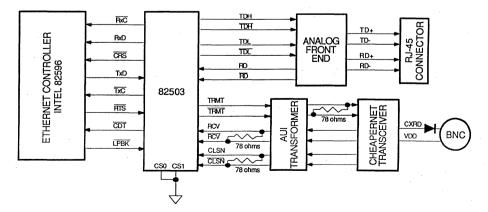

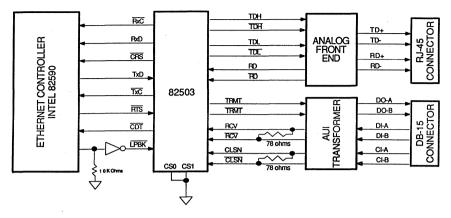

| 7.4  | The Node Board in a Twisted Pair Ethernet                             | 130 |

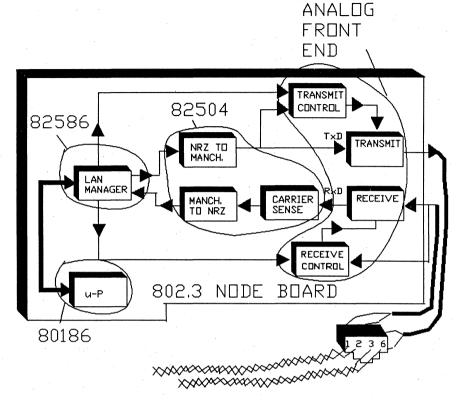

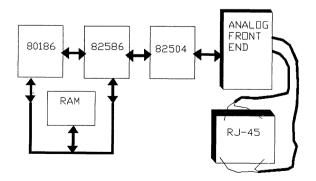

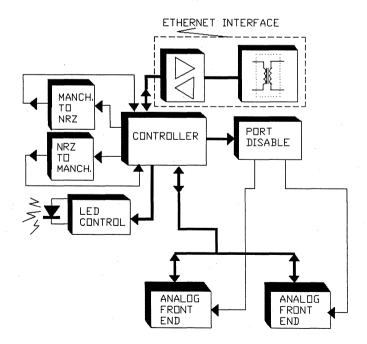

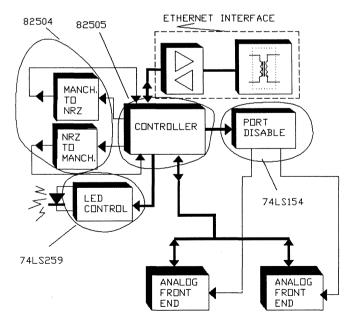

| 7.5  | Design of a Twisted Pair Ethernet Node Board with an Analog Front End | 130 |

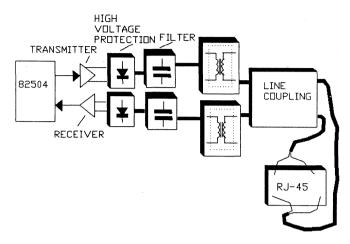

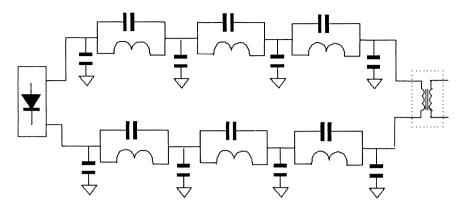

| 7.6  | The Analog Front End                                                  | 132 |

| 7.7  | The Transceiver Serial Interface                                      | 134 |

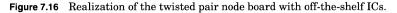

| 7.8  | A Twisted Pair Ethernet Serial Supercomponent                         | 135 |

| 7.9  | No Change to the Existing Software of an Ethernet Node                | 136 |

| 7.10 | The Multiport Repeater (MPR)                                          | 136 |

| 7.11 | Implementing a Multiport Repeater Board                               | 140 |

| 7.12 | Implementing the Twisted Pair MAU                                     | 140 |

| 7.13 | The 82503                                                             | 141 |

| 7.14 | Summary                                                               | 144 |

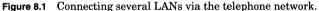

| Chaj | oter 8. Serial Communication                                          | 145 |

| 8.1  | Connecting LANs with WANs                                             | 145 |

| 8.2  | Serial Communication Circuitry                                        | 146 |

| 8.3  | Modems                                                                | 147 |

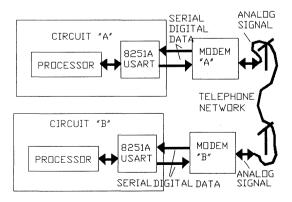

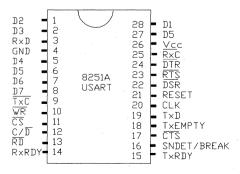

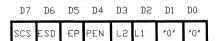

| 8.4  | USART                                                                 | 148 |

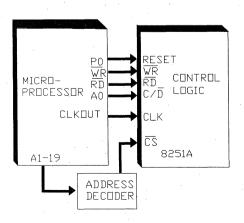

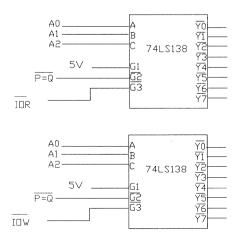

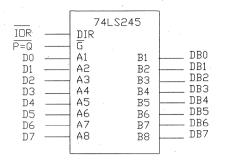

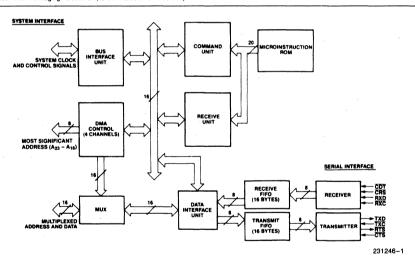

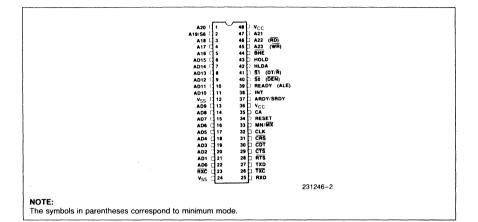

| 8.5  | USART-Processor Interface, Hardware Design                            | 149 |

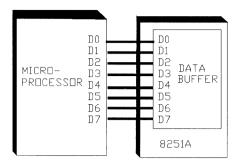

| 8.6  | The Data Buffer Block of the 8251A                                    | 150 |

| 8.7  | The Control Logic Block of the USART                                  | 152 |

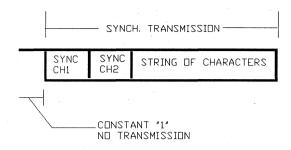

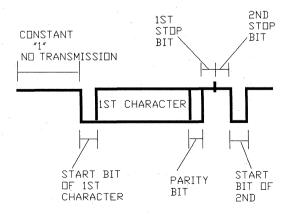

| 8.8  | Protocols                                                             | 155 |

| 8.9  | Transmitter, Hardware Design                                          | 159 |

| 8.10 | Receiver, Hardware Design                                             | 161 |

| 8.11 | Synchronous Modems and Asynchronous Modems                            | 162 |

| 8.12 | The SYNDET/BRKDET Pin of the 8251A                                    | 165 |

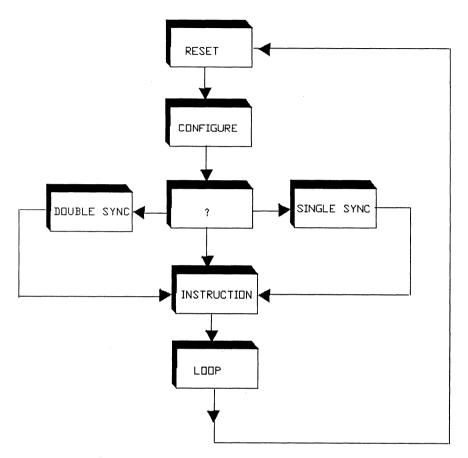

| 8.13 | Software Implementation                                               | 167 |

| 8.14 | Sending the Mode Instruction to the 8251A                             | 170 |

| 8.15 | Sending Instructions to the 8251A                                     | 172 |

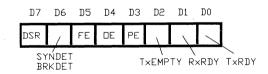

| 8.16 | Monitoring the Operation of the 8251A                                 | 175 |

| 8.17 | The Read Status Byte                                                  | 177 |

| 8.18 | Fetching Received Characters from the 8251A                           | 177 |

| 8.19 | Writing Characters to Be Transmitted to the 8251A                     | 178 |

|      |                                                                       |     |

#### viii Contents

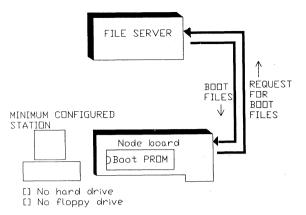

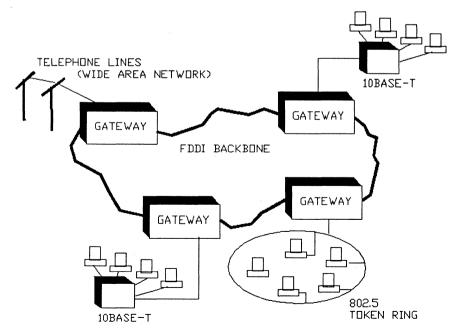

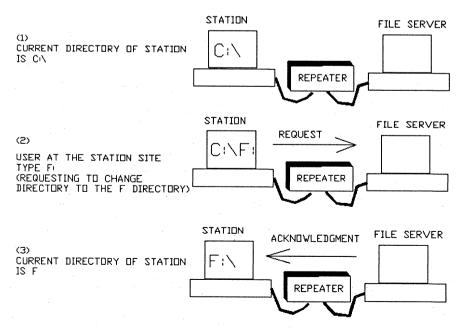

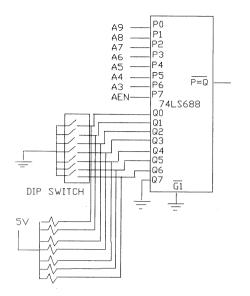

#### Appendix A 183 A.1 **Choosing the Right Network** 183 A.2 The Line Integrity Test Feature of the 10BASE-T 183 A.3 **Minimally Configured Station** 184 A.4 The File Server 184 A.5 Intelligent Repeaters 186 A.6 Combining Several Networks 187 A.7 **Node Drivers** 188 A.8 Interfacing to the I/O of the PC 189 Appendix B. 82586 1EEE 802.3 Ethernet LAN Coprocessor 193 Appendix C. 82596CA High-Performance 32-Bit LAN Coprocessor 231 Appendix D. 82588 High-Integration LAN Controller 305

Glossary 333 Index 343

## Foreword

In the old days, when I owned a 286 microprocessor-based personal computer, I used my PC to do two things, word processing and spreadsheet number crunching. Some of my colleagues got more adventurous and ran database applications as well. I was one of the lucky ones in our department in that I had my own dedicated dot matrix printer. Do you remember the times when people used to bring you their floppy disks so that you could print out a letter or a table for them?

#### Today's PC

Today I have an Intel 486SX\* microprocessor-based personal computer. Under Microsoft Windows<sup>†</sup> 3.0, I run numerous applications programs simultaneously. I have added a graphics presentation program to my original word processor and spreadsheet. I no longer have my own dedicated dot-matrix printer; instead I share a number of printers with other people in my office. Since I am in marketing, I generate numerous presentations. Having the capability to generate and print presentation-ready black and white or color slides right from my PC saves me a great deal of time and money. Today, I print impressive presentations via an Ethernet<sup>‡</sup> local area network on a Hewlett-Packard laser printer, or even a Tektronix color printer.

Two years ago I was introduced to electronic mail, and have been addicted ever since. Twice a day I *read* my *inbox*, *send* a *reply*, *forward* messages, *create* reports or memos, and *copy* them to other email users around the globe. Unlike faxes, email transmission is almost instantaneous, error-free and 100 percent reliable. Since most of the people I deal with are on email, I hardly ever use a fax machine these days.

<sup>†</sup>Windows is a trademark of Microsoft Corporation.

<sup>\*</sup>Intel 486SX and Intel 386 are trademarks of Intel Corporation.

<sup>&</sup>lt;sup>‡</sup>Ethernet is a trademark of Xerox Corporation.

#### x Foreword

Local area networks now permeate over one-third of corporations around the world, allowing companies to share expensive peripheral devices. "Sneakernet" (walking a floppy disk from one PC to another to transport data) is a thing of the past. Electronic mail is becoming the third power application that every user wants to have, made possible by local and wide area networks.

Bob Metcalfe, founder of 3Com Corporation, co-invented Ethernet at Xerox's Parc laboratories in the early 1970s. Digital Equipment, Xerox, and Intel commercialized Ethernet in the early 1980s. Today, Ethernet is *the* local area networking standard, with over 50 percent market share. It is a multibillion dollar business, with 3 million personal computer adapter cards alone being sold in 1991. The local area networking industry continues to grow faster than the personal computer industry as a whole; after all, there are over 50 million PCs still to be networked!

#### A Look into the Future

In 1981, after the original IBM PC was announced, a number of smaller companies started selling expensive serial and parallel port adapters. In the middle 1980s, both serial and parallel port add-in cards became very affordable. A few years later, personal computer manufacturers started integrating both ports into the PC. Today, Intel's newest microprocessor, the high-integration Intel 386 SL microprocessor superset, contains two serial and one parallel port *on-chip*. As future transistors become smaller, cheaper, and more powerful, more I/O functions will be integrated into the CPU. By the turn of the century, it is very likely that Intel's high-integration microprocessors will integrate Ethernet directly into the CPU.

Ethernet adapter cards will constitute the lion's share of the LAN market for quite a number of years. However, as the need for networking grows, personal computer manufacturers will start integrating the Ethernet chipset directly onto the personal computer motherboard. Today, in late 1991, the first network-ready PCs are starting to appear. In 1992, many more Ethernet-ready PCs will be introduced.

Intel has sold more than 9 million Ethernet VLSI (very large scale integration) components in the last 8 years, with 2 million more being forecast for 1991 alone. During those 8 years, Intel has introduced more than a dozen Ethernet components, two new chips in 1991 alone. As one of the technological leaders in the personal computer connectivity business, we will continue to bring out leading-edge connectivity components in the future too. Ethernet is not an easy technology. I am positive that this book will go a long way in helping design engineers build better adapter cards or PC motherboards, so that the next time around I can send you the foreword via video-mail.

> ROBERT BREYER Product Marketing Engineer Intel Corporation

## Preface

Local area network (LAN) equipment includes products that are procured by virtually all segments of industry: small, medium, and large corporations; manufacturers; law and accounting firms; schools and universities; banks; mail order businesses; and other organizations that require establishing data communication between several personal computers (PCs). The number of PCs connected via a LAN varies as well. Some networks consist of three to four PCs connected in small offices to form a tiny LAN for the purpose of sharing a laser printer, databases, and other resources. Other networks consist of hundreds of stations.

To be able to design LAN equipment, the designer must fully understand the principle of operation of the equipment. Chapter 1 introduces the terms and definitions and explains how LANs work. The chapter discusses the difference between the probabilistic and deterministic type of LANs, the ISO seven layers model, and the various IEEE 802 LAN protocols. It includes an elaborate discussion of the CSMA/CD access method, Manchester decoding-encoding, the 802.3 frame, the collision concept, and other topics that are prerequisites to understanding the material presented in subsequent chapters. Since Chap. 1 presents the theory of local area networks, it serves as the base for all subsequent chapters.

To provide the reader with a full understanding of LAN design problems and their solutions, the book presents LAN design circuitries in the same order as they occurred historically. The reason for this particular approach is not to teach the history of LAN, but rather to present the reader with the various stages that the art of LAN design experienced. By following this route, the reader will gain insight into current design challenges as well as future design challenges that are involved in LAN equipment design.

One of the earlier LANs was the Starlan. This LAN is at least 10 times slower than current LANs and is becoming obsolete. Yet, by

studying this particular LAN, the reader will gain a full understanding of the degree of complexity (hardware and software) that is required in LAN implementation: the off-the-shelf LAN controller chip, the required magnetic components, the logic "glue" chips, and the various cable considerations and LAN topology. Chapter 2 discusses the topology and cable requirements of the Starlan, Chaps. 3 and 4 discuss the hardware node design, and Chap. 5 discusses the software of the implementation of the node. Although the Starlan itself became obsolete, the reader will find that most of the information presented in these chapters is still valid for current LANs.

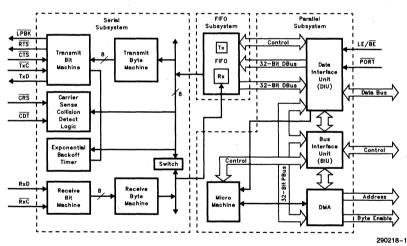

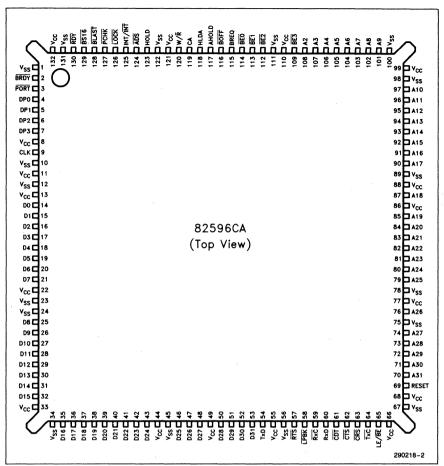

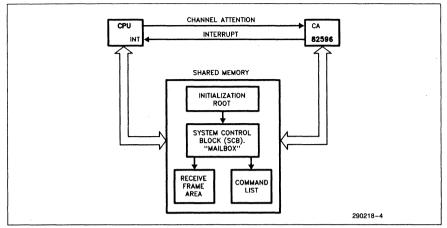

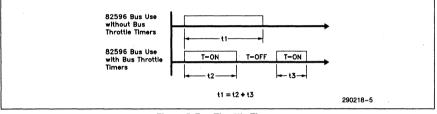

The next stage of LAN evolution was the introduction of Ethernet and Cheapernet. These LANs utilize different LAN topologies and different types of cables. More important, these LANs are 10 times faster than the Starlan. Chapter 6 is devoted to the implementation of these LANs by using the next generation LAN controller chip, the Intel 82586 LAN controller. The 82586 is a more complex chip that requires more programming than the 82588. However, the experience gained by studying the 82588 will enable an easy transition to the more advanced 82586 LAN controller, since at that point, the reader already understands the performance requirements and what is expected from a LAN controller. The last section of Chap. 6 includes a discussion of the most up-to-date LAN controllers. The Intel 82596 LAN controller is currently the most advanced controller available, and its advanced performances should be obvious to the reader who masters the 82586.

Chapter 7 presents the next stage of LAN evolution, the most current 802.3 LAN protocol (the newly announced 10BASE-T LAN protocol). This LAN is as fast as the Ethernet/Cheapernet, and while its main component (the LAN controller) is the same controller as the one used by the Ethernet and Cheapernet (e.g., 82586, 82596), its topology and the types of cables that it uses resemble the Starlan. Chapter 7 discusses the various off-the-shelf 10BASE-T components, including the Intel 82503. Finally, Chap. 8 discusses serial communication.

The field of designing and manufacturing LAN equipment is dynamic and depends on several factors. One factor that determines the destiny and direction of LANs is the consumers who require inexpensive, reliable equipment. The other factor is the constant improvement of integrated circuits technology. As this technology keeps progressing, the integrated circuits manufacturers are able to announce new chips which may be used as the building blocks for future LAN equipment that will be able to reliably transfer data at higher data rates. Indeed, in many cases it is the integrated circuits manufacturers who introduce and contribute ideas to new LAN protocols.

An example of the dynamic nature of the LAN market is the introduction of the 10BASE-T LAN, the latest IEEE 802.3 protocol. This new protocol is expected to replace the popular 10BASE5/10BASE2 LANs. It contains all the "good" features of these LANs. That is, it uses the same CSMA/CD access method which proved itself to be very reliable during the last several years, and it has the same high data rate capability (10 Mbit/s). Yet this new protocol introduces an improvement: it does not require coaxial cables, but rather it uses inexpensive twisted pairs of wires.

The purpose of this book is to introduce hardware and firmware design know-how of local area network circuits to engineers, technicians, students, and anybody else who is interested in gaining such knowledge. Although the book includes a discussion of all the current IEEE 802.X LAN protocols, the book specifically concentrates on the CSMA/CD type of LANs: the IEEE 802.3 protocols: 1BASE5 (Starlan\*), 10BASE5 (Ethernet<sup>†</sup>), 10BASE2 (Cheapernet), and the newly evolved 10BASE-T (Twisted Pair Ethernet). The book teaches the theory and principle of operation of these LANs and then illustrates how to implement a design of such LAN circuits (hardware and firmware) by using off-the-shelf reliable components.

#### NATHAN GUREWICH

<sup>\*</sup>Starlan is a registered trademark of AT&T.

<sup>&</sup>lt;sup>†</sup>Ethernet is a registered trademark of Xerox Corporation.

## Communication Systems

# 1

## Introduction to Local Area Networks

#### 1.1 The Need for Local Area Networks

As the number of personal computers (PCs) utilized in various industries increases, there is a growing demand for establishing data communication between PCs by connecting them together.

A *network* is the tool by which the PCs are connected. The network consists of hardware components (boards, cables, connectors, etc.) and software components.

The network enables a user of one PC in the network to transfer data to any other PC in the network. When the network cables are limited to short distances, the network is called a *local area network*, or *LAN* for short. Among other things, the LAN protocol specifies the maximum allowed cable length and the type of cables to be used.

The major reasons for demanding the ability to connect several PCs together are

- *Electronic transmission.* By networking several PCs together, there is no need to transfer data from one PC to another by physically transferring diskettes. Rather, the data can be transmitted electronically over the network cables.

- Sharing peripherals. By networking several PCs together, costly peripheral devices such as plotters can be shared among several users.

#### 1.1.1 Types of LANs

There are many types of LANs, each suitable for a particular type of application. Some LANs are oriented toward noisy environments. In

these LANs, the prime concern is to be able to establish communication despite the large noise generated by the environment. Such LANs are used, for example, in manufacturing environments. In other LAN applications, the ability to transfer data as fast as possible is the prime concern. Yet in other applications, the prime concern is the cost of the LAN.

#### 1.1.2 The need for standard protocols

As the demand for LANs increased, various industries realized the need of establishing standard protocols for LANs.

A standard protocol is a set of rules and specifications that fully defines and specifies the LAN. A standard LAN is one that is built from several components, where each component is assumed to comply with the specifications mentioned in the standard protocol.

By having a standard protocol, the end user is able to construct a LAN by purchasing different components of the LAN from different vendors based on cost, service, and product reliability. The network should not experience any problem when using components from different vendors, as long as the LAN components were designed in strict compliance with the protocol. It is therefore important to design the LAN equipment in accordance with the protocol.

Another important advantage of having standard protocols for LANs is that once a standard protocol is accepted and recognized, there is a large demand by LAN designers for chips that are capable of implementing portions of the hardware and software tasks dictated by the protocol. As the demand for these chips increases, chip manufacturers have the incentive to invest in the design, manufacturing, and marketing of these chips, since the expected sales justify the investment. The availability of inexpensive LAN chips to the LAN designers reduces development time and yields more reliable products.

In many cases, the chip manufacturers are the major contributors for drafting the specifications of the standard protocols. Of course, having the integrated circuit (IC) manufacturers contribute their ideas to the standard protocols makes sense, since they are the ones who know best what can and cannot be integrated on silicon chips.

#### **1.2 Space Division Multiplexing**

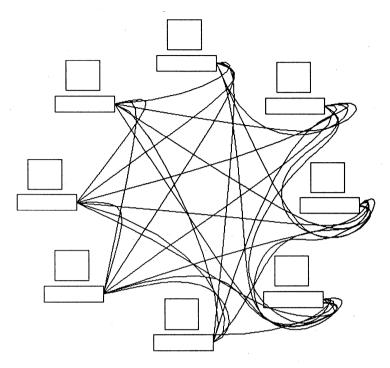

One method of connecting several PCs together to form a network is shown in Fig. 1.1. As shown, each PC has a cable connecting it to all the other PCs in the network. This method is called *space division multiplexing* since the space is divided so that each portion of the space carries a cable.

One of the major drawbacks of the space division multiplexing technique is the fact that it requires too many cables compared to other

Introduction to Local Area Networks

Figure 1.1 Space division multiplexing.

available multiplexing techniques. Stretching cables between rooms, floors, and buildings is expensive. Major contributors to the incurred cost are the cost of the network cables and the cost of the labor to install the cables. Another drawback of the space division multiplexing method is the lack of flexibility. Adding a new PC to the network requires the installation of cables from the new added PC to all the rest of the PCs in the network.

Example 1.1 Assume that 100 PCs are to be networked using the same technique shown in Fig. 1.1. How many cables are needed?

Solution When N is the number of PCs to be connected using the technique shown in Fig. 1.1, the total number of cables required is

Total number of cables required =

$$\frac{N \times (N-1)}{2}$$

For 100 PCs,

Number of cables required =

$$\frac{100 \times 99}{2}$$

= 4950 cables

Obviously, a better technique for connecting PCs is needed.

3

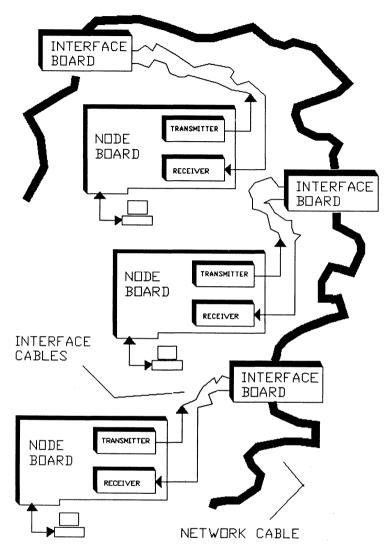

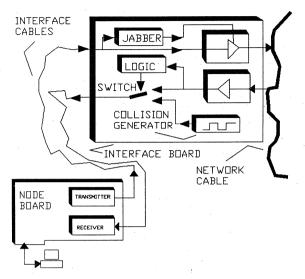

#### 1.3 Sharing the Network Cable

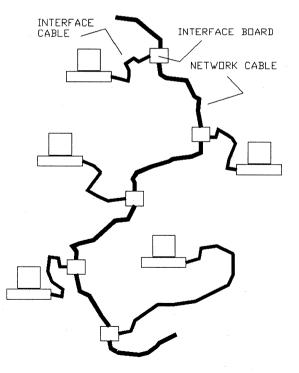

A less expensive method that uses fewer cables is shown in Fig. 1.2. In this technique, a single cable is used to connect all the PCs. While in the network shown in Fig. 1.1 a few PCs may converse with each other simultaneously, in the network shown in Fig. 1.2 only one PC is permitted to transfer data at any given time. The network cable is shared by all the PCs and may carry a single transmission at any given time. As might be expected, to connect a PC to the network cable, some type of connection board is required. In Fig. 1.2, this board is denoted as the *interface board*.

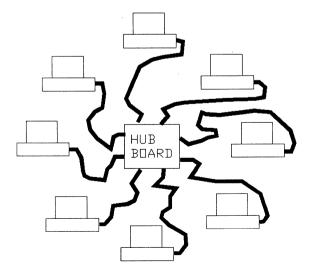

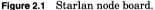

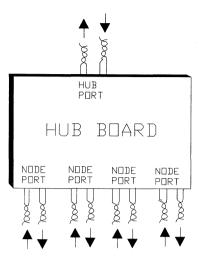

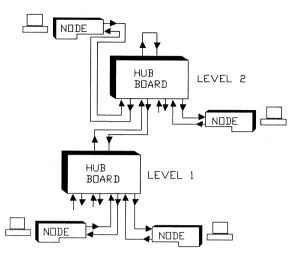

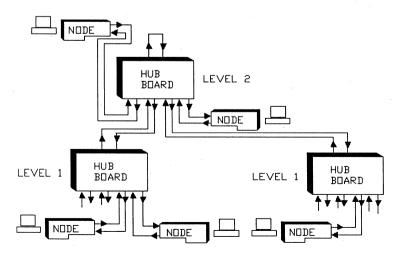

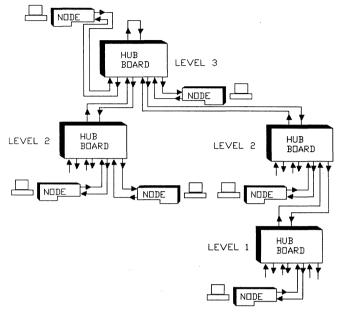

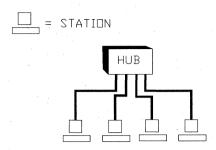

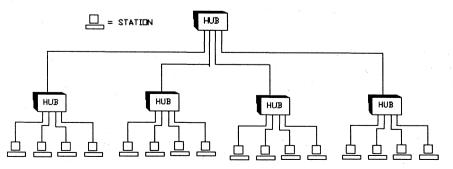

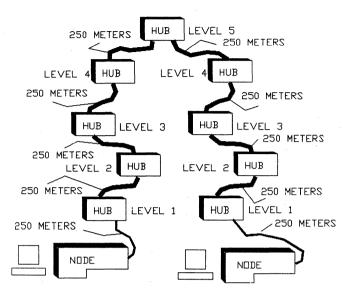

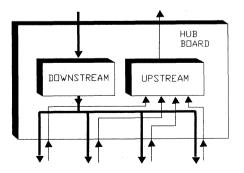

Figure 1.3 is another example of a network in which only a single PC is permitted to transmit at any given time. Again, as might be expected, the cables are not just tied up at the center, but rather an electronic board called a *hub board* is required.

#### 1.3.1 LAN topologies

Different LANs have different topologies. The LAN topology defines the way by which the PCs are connected together. Examples of some of

Figure 1.2 Sharing the cable, bus topology.

the common topologies are the *bus topology* shown in Fig. 1.2 and the *star topology* shown in Fig. 1.3. The LAN topology is specified in the LAN protocol.

## 1.3.2 Access method, deferring procedure, and collision

When the PCs in a LAN share a single cable, certain sharing rules and procedures must be established in order to avoid chaos on the cable.

When a PC wishes to access the network cable for the purpose of transferring data to another PC, it must verify first that the network cable is free. This access verification process is called the *access method*. In some LANs, each of the transmitting PCs is responsible for finding whether or not the network cable is free. In other LANs, the PC is told by a special LAN circuitry called a *central controller*, whether or not the network is free.

If the PC concludes that the network is not free, it defers its transmission for a later time. Deferring the transmission for a later time is called the *deferring procedure*.

If it happens that more than one PC is transmitting at the same time, the network is in a *collision*. In a collision, the network cable carries a signal that is a mixture of data from more than one PC. This signal is useless, and the PCs in the network should be able to recognize such a signal and ignore it.

Figure 1.3 Sharing the cable, star topology.

Although the access method is equipped with enough access rules to avoid collisions, collisions do occur. The LAN protocol specifies how to detect collisions and what to do in the event a collision is detected.

#### 1.4 Central Controller

Some LANs are designed to operate with a central controller, while other LANs are designed to operate without a central controller. A central controller is an intelligent electronic circuit that has the responsibility of managing the whole network. A PC in a LAN that utilizes a central controller is not permitted to transmit unless granted a permission to do so by the central controller. Once a PC is granted the permission to transmit, it may transmit only for the amount of time dictated by the central controller.

The advantage of using a central controller in a LAN is that the central processor can be programmed to favor a group of PCs in the network, granting these PCs more permissions to transmit than other PCs in the network.

A LAN that utilizes a central controller is categorized as a *deterministic* type, since the central controller can be programmed in such a way that it is possible to determine in advance which PC is allowed to transmit, for how long, and at what sequence.

The major disadvantages of a using central controller in a LAN are

- If the central controller circuit fails, the LAN is useless, since this type of LAN cannot operate without its central controller.

- Adding and deleting PCs from the network requires reprogramming the central controller.

- A LAN that utilizes a central controller has the additional cost of the central controller equipment.

#### 1.4.1 Modulation

Some LANs utilize the *frequency division modulation* technique. This technique is similar in concept to the technique used in cable television, where simultaneous transmissions over a single network cable are permitted. Each transmission is assigned to a different frequency channel. This technique requires the use of both transmitter circuits that modulate the data to the required frequency channel and receiver circuits that demodulate the data back to the baseband (original) frequency of the data.

**Example 1.2** In a baseband transmission the entire bandwidth of the network cable is dedicated for a single transmission.

#### 1.5 Cables

There are various types of cables used in LANs. The most common types of cables used in LANs are

- Coaxial cables. These are well-shielded cables, designed to carry data at rate of 10 Mbit/s for distances ranging from 200 to 500 m without distorting the data. These cables are available as single-shielded or as double-shielded cables. High-quality coaxial cables are expensive.

- Unshielded twisted pair. This is the type of wire used by telephone companies to install telephone services. These wires are very inexpensive, probably the most inexpensive wires that one can purchase. These cables are purchased in *bundles*; typically each bundle is composed of 25 pairs of twisted wires.

- *Fiber optics.* Currently, these cables are expensive since there is not yet a great demand for them. As demand increases, prices are expected to decrease.

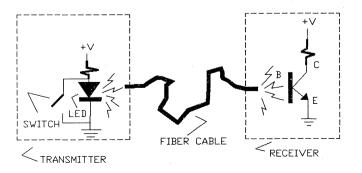

**Example 1.3** Explain the principle of transmitting and receiving data by using fiber optic cables.

**Solution** The principle of transmitting and receiving data by using fiber-optic cables is illustrated in Fig. 1.4. The electronic switch shown in the figure is opened and closed in accordance with the data to be transmitted.

When a 0 is to be transmitted, that 0 causes the switch to open and current flows through the LED, causing it to emit light into the fiber cable.

When a 1 is to be transmitted, that 1 causes the switch to close (shorting out the LED); thus no current is flowing through the LED, and therefore no light is emitted to the fiber cable.

Thus, a flow of light through the cable represents a 0, and the absence of light represents a 1. The light is then propagated through the cable. The cable is flexible and can be routed from one place to another easily. The amazing characteristic of the fiber cable is that light is transmitted from one end of the cable to the

Figure 1.4 The principle of fiber optics transmission.

other end even if the cable is not positioned in a straight line. However, being made of glass or plastic, too much bending of the cable would break it.

Being a light, the transmission has the following major advantages:

- *No interference.* The transmission of the light causes no interference to nearby cables and nearby electronic instruments. Also, external electrical noise cannot distort the transmission of the light.

- *No distortion due to cable characteristics.* Since the data are transferred as light, the transmission is not affected by the resistance, capacitance, and inductance of the cable.

- *High speed of transmission.* The data are traveling at the highest speed that one could hope for, the speed of light.

On the other end of the fiber cable, there is an optical transistor. The fiber cable emits the light into the base of the transistor.

The optical transistor is turned ON when light is applied to its base, causing a low voltage at its collector, which is then interpreted as 0. When light is not applied to its base, the transistor is OFF and the collector is at high voltage, which is then interpreted as 1.

The limiting factor for the speed at which data can be transmitted is the ability of the LED and the optical transistor to switch on and off. A typical rate of transmission is 100 Mbit/s.

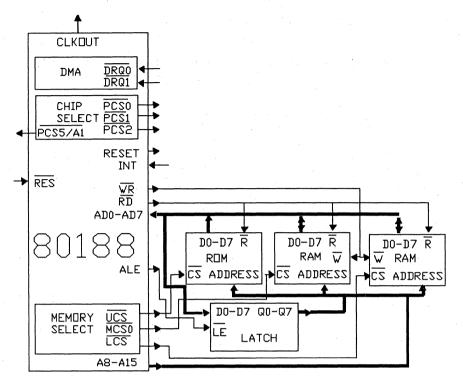

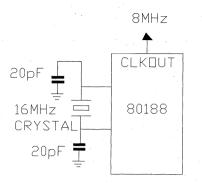

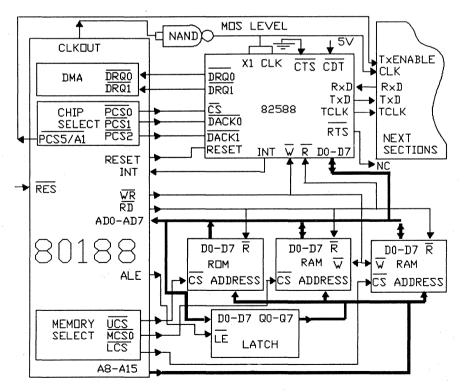

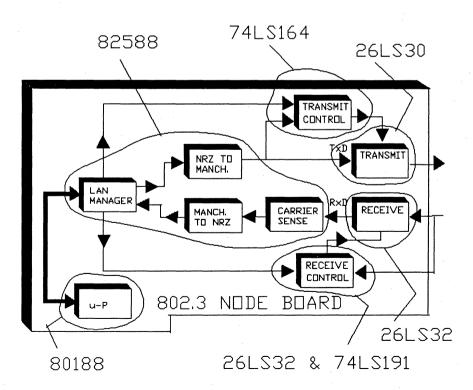

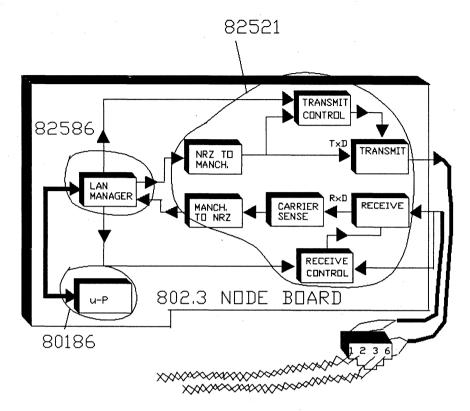

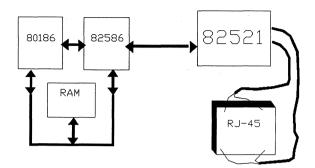

#### 1.6 The Node Board

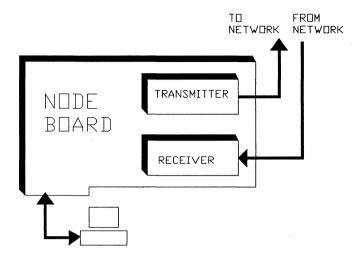

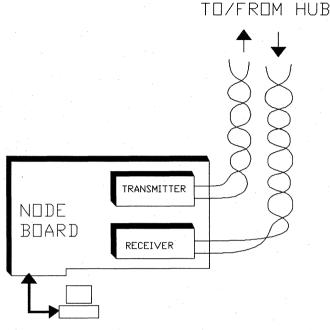

In order to connect PCs to a LAN, electronic boards called *node boards* are required. In many cases, the node boards are designed to be plugged into one of the I/O slots of the motherboard of the PC. A simplified logic block diagram of a node board is shown in Fig. 1.5. The node board is responsible for accepting data from the PC and transmitting the data to the network via its transmitter. The node board is also responsible for receiving data from the network via its receiver and transferring the received data to its PC.

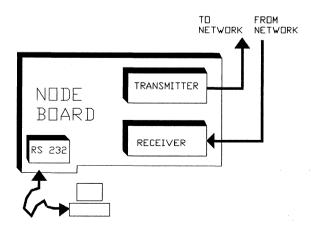

The device connected to the node board is called *data terminal equipment*, or DTE for short. The DTE may be a PC (as shown in Fig. 1.5) or any other device. No matter what type of DTE is connected to the node and no matter how the DTE is connected to the node, the node always communicates with the network in exactly the same way, as prescribed in the network protocol. The node board shown in Fig. 1.6 is shown to be connected to the serial port (RS-232) of the PC. Nevertheless, the nodes of Figs. 1.5 and 1.6 are identical as far as the network is concerned. Of course, the node must contain the appropriate interface circuitry that enables the interface between the node and its DTE.

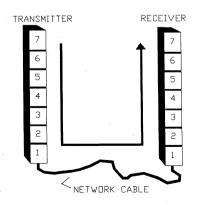

#### **1.6.1** Connecting a node to the network

The network protocol completely defines and specifies the cables that connect the node to the network. Included within the specification are

Figure 1.5 Connecting a node board to a DTE.

the number of wires in the cable, the type of wires, and the maximum length of the wires.

A DTE together with its node is called a *station*.

## 1.7 A Quick Review of the ISO Seven Layers Model

ISO is the abbreviation of *International Standards Organization*. This organization took upon itself the tasks of developing and publishing various standards which are accepted worldwide. The organization has representatives from most of the countries in the world, and it is an agency of the United Nations.

Figure 1.6 Connecting a node board to a DTE via RS 232.

The seven layers model, which was adapted by the ISO, is a recommended model to be used when developing and implementing networks. The concept of the model is to divide the network into seven distinct sections (layers), as follows:

Layer 1: Physical layer Layer 2: Data link layer Layer 3: Network layer Layer 4: Transport layer Layer 5: Session layer Layer 6: Presentation layer Layer 7: Application layer

The ISO seven layers model is recommended for the implementation not only of LANs but also of wide area networks (networks that utilize the telephone lines), as well as other types of communication networks. However, our discussion is restricted to the relations between the ISO model and LANs.

The seven layers are implemented in hardware and software and are installed on both sides of the communication link, the transmitter side, and the receiver side. Figure 1.7 is a pictorial representation of the model.

Each layer is responsible for performing a specific task in the network. When the transmitter wishes to transmit, the process starts at layer 7. Layer 7 prepares the data to be transmitted, and once layer 7 completes its task, it transfers the data to layer 6. Layer 6 also "works" on the data and passes the data to layer 5. The data keep propagating

Figure 1.7 The ISO seven layers model.

downward, until thus reach layer 1, the physical layer. Layer 1 is the layer that actually transmits the data. By the time the data reach layer 1, there are several control bytes attached to data. These control bytes are added by the different layers.

On the receiver side, data are being received by layer 1, and then passed to layer 2. Layer 2 analyzes the control bytes that are related to the task assigned to it, strips off these control bytes, and passes the data upward to the next upper layer. Data keep propagating upward and eventually reach layer 7.

**Example 1.4** As an example of one of the control bytes that is added to the data by the layers, consider the case where a large data file is to be transmitted.

In LANs, only one PC is allowed to transmit at any given time. To avoid monopolization of the network cable by a single PC, long transmissions are not allowed.

The transmitting PC must divide the large data file into several small segments. This breaking of the data files into several small segments is a task performed by one of the layers on the transmitter side. That layer breaks the large file into several small segments and attaches control bytes to each of the segments indicating the sequential segment number. Each segment propagates downward, eventually reaches layer 1, and is transmitted separately.

One of the layers on the receiver side has the task of reassembling the segments (in the right sequence) to reconstruct the original large data file. That layer is able to do so, since the segment numbers are attached to the segments as control bytes. If, for some reason, one of the segments does not reach the receiver, the layer has the ability to detect that it is missing a segment by simply keeping track of the segment numbers.

The advantage of developing a network that follows the ISO seven layers model is the ability to upgrade, change, or modify any of the layers without the need to change or modify the other layers. That is, a layer can be "unplugged" from the network, modified, and then "plugged" back to the network.

The tasks assigned to each of the seven layers are based on experience that was accumulated by a variety of network designers through the years.

## 1.8 Equating the LAN Protocol to the ISO Seven Layers Model

Figure 1.8 illustrates the seven layers of a LAN protocol as viewed by the Institute of Electrical and Electronics Engineers (IEEE). This organization, just like the ISO organization, took upon itself the tasks of developing and publishing standard protocols.

The committees that are responsible for developing LAN protocols are the 802 group of committees. The 802 group is divided into eight committees, each responsible for dealing with a different LAN subject.

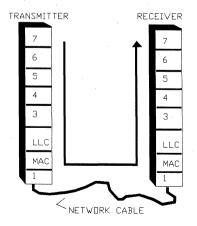

#### 12 Chapter One

As shown in Fig. 1.8, the IEEE deviates somehow from the original ISO seven layers model by further dividing layer 2 into two layers: the *logical link control* layer, or LLC for short, and the *media access control* layer, or MAC for short.

#### 1.8.1 Layer 1, the physical layer

Layer 1, the physical layer, has the task of defining and implementing the physical connection. Included in this layer protocol are the specifications for the type of cable, connector specifications, and everything else that is directly related to the physical connection.

## 1.8.2 The media access control (MAC) layer

The media access control (MAC) layer at the transmitter side has the task of receiving data from a higher level layer (i.e., the LLC layer) in accordance with an agreed upon set of rules. The MAC layer is then responsible for executing the access method, deciding whether the network is free and ready for its transmission. Once this layer decides that it is time to transmit, it adds certain control bytes to the data, formats the data to a certain format (called a *frame*), and hands over the data to the physical layer for transmission.

On the receiver side, the MAC layer receives data from layer 1, checks that the control bytes of the data (which were attached by the MAC layer on the transmitter side) conform to the set of rules, and decides whether or not the data were corrupted during its transmis-

Figure 1.8 Equating the IEEE 800 LAN models to the ISO model.

sion due to noise and other misfortunes. The layer then removes the control bytes from the data and transfers the data (without the control bytes) to the next higher layer level, the LLC layer.

The tasks assigned to the MAC at the transmitter side are

- Receiving data from its LLC layer.

- Making a decision when to transmit (executing the access method).

- Formatting the data and attaching control bytes (constructing a frame).

- Handing over the frame to layer 1 for transmission.

The tasks assigned to the MAC at the receiver side are

- Receiving the data from layer 1.

- Examining the control bytes for the purpose of making the decision whether the data were corrupted on their way.

- Stripping off the control bytes and handing over the data upward to the next higher level.

**Example 1.5** The commercial LAN software known as Netware (manufactured by Novell) is a software package that implements the LLC layer, layer 3, layer 4, and layer 5.

The following examples illustrate how the seven layer model distributes different network tasks among the different layers.

**Example 1.6** Suppose that a PC wishes to receive a data file from another PC in the network. The request is prepared by the upper layers and passed to the MAC layer for transmission. The MAC layer constructs a frame, transmits the frame, and reports back to the upper layers that the transmission was successful.

After a few minutes, the PC program notices that the requested file still has not been received. Which group of layers is responsible for retransmitting the request?

**Solution** The upper layers are responsible for generating the request again. The MAC layer has no means to examine the intelligent content of the data that it is transmitting to the network.

By reporting back to the upper layers that the transmission was successful, the MAC layer merely indicates that no collision was detected during the transmission.

**Example 1.7** Suppose that the MAC layer receives data (from its upper layers) for transmission. The MAC layer constructs a frame and transmits the data. However, at the middle of the transmission, the MAC layer discovers that it is transmitting together with another PC in the network at the same time (i.e., the MAC layer is transmitting into a collide network cable).

MAC protocols require the MAC layer to automatically retransmit the frame again. The MAC protocol also specifies that if the MAC layer keeps retransmitting the frame and keeps encountering collisions one time after the other, the MAC layer should abort the transmission and report the situation back to its upper layers. The MAC protocol specifies the number of consecutive collisions that must occur before the MAC layer should give up on the transmission of that frame.

#### 1.9 The IEEE 802 LAN Protocols

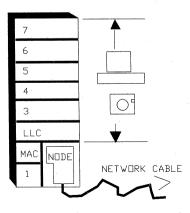

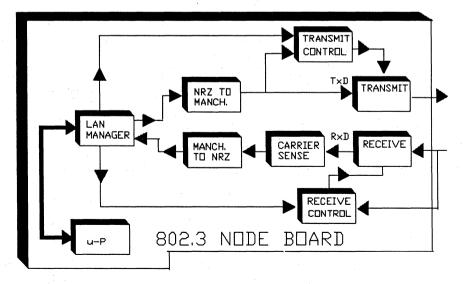

Figure 1.9 illustrates the approach we take to implement layer 1 and the MAC layer. As shown, we choose to implement these layers in hardware and firmware on a separate board, the node board. The rest of the layers are implemented as software executed by the PC.

There are several IEEE standard LAN protocols available for implementing layer 1 and the MAC layer. These protocols are specified as a set of protocols called the IEEE 802 standard LAN protocols.

## 1.9.1 The IEEE 802.3 standard LAN protocols

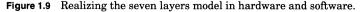

The IEEE 802.3 is a set of LAN protocols for the implementation of layer 1 and the MAC layer. Each of the LANs specified in the 802.3 group has a different set of physical specifications (cable type, cable length, topology, etc.). However, all LANs within this group of protocols utilize the same access method, the CSMA/CD access method. The model representation for these LANs is shown in Fig. 1.10*a*.

## 1.9.2 The IEEE 802.4 standard LAN protocol

Figure 1.10*b* is a representation of a different LAN, the 802.4 LAN. This protocol specifies the *token bus* as the access method.

#### 1.9.3 The IEEE 802.5 LAN protocol

Figure 1.10c is a representation of yet a different LAN, the 802.5 LAN. This protocol specifies the *token ring* as the access method.

#### 1.9.4 The IEEE 802.6 LAN protocol

Another standard LAN protocol is the LAN that conforms to the IEEE 802.6 standard LAN protocol. This LAN is called the *metropolitan area network*, or MAN for short. Although we refer to this as a "LAN" protocol, this LAN may have a network fiber-optic cable that may be up to 50,000 m long.

## 1.9.5 The advantages of using the ISO seven-layers models

Figures 1.9 and 1.10 illustrate the advantage of using the ISO seven layers model. That is, no matter what node board (MAC layer plus layer 1) is used, the upper layers remain the same. Of course, proper interfacing must be incorporated in the design to allow the interface between the node board and its upper layers.

## 1.10 The Various LANs in the IEEE 802.3 LAN Protocols

As mentioned, the 802.3 protocol defines different LANs, each with a different set of specifications for the cable type, cable length, LAN

Figure 1.10 Models of the various IEEE 800 LAN protocols.

topology, and others. However, the access method for all the LANs in the 802.3 group is the same, the CSMA/CD access method.

#### 1.10.1 The xTYPEy LAN name

Each of the LANs within the 802.3 group is identified by its designation name. The LANs have the following designation format:

xTYPEy Name

where

- x = the data rate in megabits per second (Mbit/s) at which data are transferred over the network cable.

- TYPE = indicates the type of modulation used in the transmission of the data over the network cables.

- y = indicates one of the major characteristics of the network cable.

Name = the name of the LAN.

Usually there is no space separating the "x" from the "TYPE" and no space separating the "TYPE" from the "y." The designation name is not intended to fully describe the particular LAN, but simply to indicate some of the special characteristics that make the LAN different from the other LANs in the group.

**Example 1.8** The IEEE 802.3 10BASE5 (Ethernet) is the designation of a LAN with the following main characteristics:

- The "10" represents the fact that data are transmitted over the network cable at a rate of 10 Mbit/s.

- The "BASE" represents the fact that data are being transmitted in baseband transmission.

- The "5" represents 500 m, the maximum permitted length of network cable when the network is configured in a minimum configuration.

Note that Ethernet is a registered trademark of Xerox Corporation.

**Example 1.9** The IEEE 802.3 1BASE5 (Starlan) is the designation of a LAN with the following main characteristics:

- The "1" represents the fact that data are transmitted over the network cable at a rate of 1 Mbit/s.

- The "BASE" represents the fact that data are being transmitted in baseband transmission.

- The "5" represents 500 m, the maximum permitted length of network cable when the network is configured in a minimum configuration.

Note that Starlan is a registered trademark of AT&T.

**Example 1.10** The IEEE 802.3 10BASE2 Cheapernet is the designation for a LAN called Cheapernet:

• The "10" represents the fact that data are transmitted over the network cable at a rate of 10 Mbit/s.

- The "BASE" represents the fact that data are being transmitted in baseband transmission.

- The "2" represents 200 m, the maximum permitted length of network cable when the network is configured in a minimum configuration.

**Example 1.11** The IEEE 802.3 10BROAD36 Broadband Ethernet is the designation for a LAN called Broadband Ethernet:

- The "10" represents the fact that data are transmitted over the network cable at a rate of 10 Mbit/s.

- The "BROAD" represents the fact that data are being transmitted as a broadband transmission.

- The "36" represents 3600 m, the maximum permitted length of network cable when the network is configured in a minimum configuration.

**Example 1.12** The IEEE 802.3 10BASE-T is the designation for a LAN called 10BASE-T:

- The "10" represents the fact that data are transmitted over the network cable at a rate of 10 Mbit/s.

- The "BASE" represents the fact that data are being transmitted as a baseband transmission.

- The "T" represents the type of network cable, a twisted pair wire for this LAN.

#### 1.11 CSMA/CD Access Method

The access method specified in the IEEE 802.3 protocols is called the CSMA/CD access method (Fig. 1.10a).

The "CS" in CSMA/CD is the abbreviation of *carrier sense*. While data are traveling over the network cable, the cable is said to contain a carrier. Each node must sense the cable prior to transmission and decide if the cable carries a carrier. If the node senses no carrier, it can start transmitting.

If, however, the node senses a carrier, the node starts to execute the *deferring* procedure. The deferring procedure is the procedure whereby the node waits for a certain amount of time and then senses the cable again. It is quite possible that on its next try, the node again finds a busy network, while another, luckier node might find a free network on its first attempt. The CSMA/CD access method protocol is a probabilistic type, since there is no guarantee of when a node might be able to access the network. Thus, the CSMA/CD access method does not implement any priority mechanism; every node in the network has the same chance to access the network.

The "MA" in CSMA/CD is the abbreviation of *multiple access*. This term refers to the fact that after completing its transmission, a node can sense the cable again, and if it finds a free network, it may transmit again. Thus, the CSMA/CD access method does not implement a fairness mechanism (i.e., it is not fair that a node accesses the cable numerous times while other nodes are still waiting for a free network).

**Example 1.13** Other access methods specified in other protocols might not permit multiple access. In a non-multiple-access protocol, each node waits for its turn to transmit. Once a node completes its transmission, it waits for its next turn to transmit again. Thus, these access methods implement a fairness mechanism.

The "CD" in CSMA/CD is the abbreviation of *collision detect*. This term refers to the fact that the node must have the capability to detect collisions on the cable. That is, if it happens that more than one node is transmitting at the same time, the node must be able to detect that there are no valid data on the cable, but a "mixed" signal that was generated due to a collision. Naturally, the node should regard that signal as useless data. The 802.3 protocols specify an elaborately detailed list of actions that the node should take upon discovering a collision. We shall soon see what the actions are to be taken and how these actions are implemented in hardware and software by the node.

#### 1.12 Quick Review of Manchester Format

The 802.3 protocols specify that data must be transmitted over the network cable in *Manchester format*. When a PC in the network wishes to send data to another PC in the network, it transfers the data to its node in a parallel form, byte after byte. The node serializes the data, processes the data, and sends the processed data in a Manchester format, bit after bit to the network. Thus, the data present on the wires of the network are in a Manchester format.

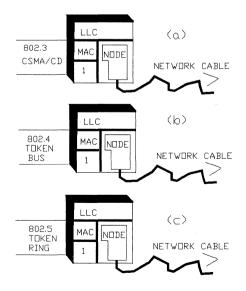

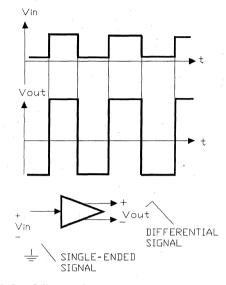

A *nonreturn to zero* signal, or NRZ for short, is a signal in which 1 is represented by a high voltage and a 0 is represented by a low voltage.

Figure 1.11 shows how an NRZ format can be converted to a Manchester format by using an exclusive OR gate. One of the inputs to the exclusive OR gate is the NRZ signal to be converted, the second input to the gate is a clock. The output of the gate is the Manchester signal. The clock is a 50 percent duty-cycle square wave, and its frequency is such that it completes a cycle during the duration of a single 0 or 1 of the NRZ signal.

Since the data have to be transmitted in Manchester format, the node must have the capability of converting NRZ (supplied to it by its PC) to a Manchester format. The node must also have the capability to convert a Manchester signal (supplied to it by the network) to an NRZ signal.

The Manchester format has the characteristic that no matter what the original NRZ signal was, the Manchester format always has a transition from 0 to 1 or from 1 to 0 at least every two half-cycles of the clock.

The advantage of using the Manchester format for transmission is that the receiving node can examine the incoming bits (which are coming in a Manchester format), and if it sees a Manchester code violation,

Figure 1.11 Generating Manchester signals.

it concludes that "something wrong" happened during the transmission. The code violation is easy enough to detect. If the incoming bits do not make a transition from 0 to 1 or from 1 to 0 during two half-cycles of the clock, there is a code violation.

**Example 1.14** What method could be employed by the receiving node to convert the incoming Manchester data back to NRZ format?

**Solution** To convert the incoming Manchester format back to an NRZ format, an exclusive OR could be utilized again. That is, if one input to the gate is the same clock that is used to generate the Manchester code and the other input is the incoming Manchester signal, the output of the gate is the original NRZ signal. This can be verified from Figure 1.11 by exclusive-ORing the clock and the Manchester signals and obtaining the NRZ signal of Fig. 1.11.

Of course the trick is to be able to use the same exact clock that was used to generate the Manchester, which is the reason for also calling the process of converting a Manchester signal back to an NRZ signal the *clock recovery* process.

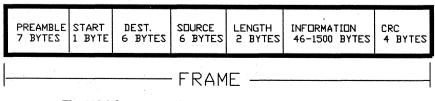

#### 1.13 The Frame

Prior to transmission, the node formats the data in accordance with a specific frame format. The format of the frame in the IEEE 802.3 protocols is shown in Fig. 1.12. The first 7 bytes of the frame are called the *preamble field*. These 7 bytes consist of alternating 0s and 1s (101010...10). When a node in the network receives the preamble bytes, it knows that a frame is coming. The reason for having the preamble bits in the frame is to enable the node to prepare its clock recovery circuitry, which is the reason for also calling these the *training* bits.

The next field of the frame is a 1-byte *start of frame* field, which always contains the byte AB hex (10101011). This byte is an indication to the receiving node that following this field are actual useful data.

The next field of the frame is a 6-byte *destination address* field. During the setup of the network, each node is assigned an identification (ID) number. The destination address is the ID number of the node for which the frame is intended.

The next field in the frame is a 6-byte *source address* field. This field contains the ID number of the node that transmits the frame. Thus, the receiving node is able to tell who sent it the frame.

The next field of the frame is a 2-byte *length* field. This field contains the number of real data in the next field.

The next field of the frame is the *information* field. This field must have a minimum of 46 bytes and a maximum of 1500 bytes. It contains the data information. The whole objective of sending the frame is to send this field.

Following is a 4-byte CRC field. This field contains the CRC number that is generated based on the destination address field, source address field, length field, and information field. A CRC number is similar in concept to a parity bit. That is, the receiving node calculates the CRC of the data that it receives, and if it finds that the value is different from the CRC transmitted to it, it concludes that there is a transmission error. Unlike the parity bit, the CRC is more complicated to generate (requires more mathematical manipulations); however, it is unlikely (with regard to probability) that transmission errors occurred if the CRC calculated by the receiving node matches the CRC in the received frame.

### 1.13.1 Who is responsible for generating the fields of the frame?

Upon initialization, the PC assigns the node with the source address. Thereafter, the only fields that the node receives from the PC are the destination address field and the information field. All the rest of the frame fields are generated and inserted by the node.

As mentioned above, the information field is required to have a minimum of 46 bytes. If the PC instructs the node to transmit information that is less than 46 bytes, the node must insert dummy bytes to make the information field 46 bytes long. This process is called *padding*.

Figure 1.12 The 802.3 frame.

**Example 1.15** Suppose that the PC instructs the node to transmit 150 bytes of information. What should the length field be?

**Solution** In this case, the length field should be 150, indicating that the information field contains 150 bytes of real data.

**Example 1.16** Suppose that the PC instructs the node to transmit 40 bytes of information. What should the length field be?

**Solution** In this case, the length field should be 40, indicating that the information field contains 40 bytes of real data.

The transmitting node must pad the information field with 6 padding bytes to make the information field 46 bytes long. Upon receiving the frame, the receiving node examines the length field and realizes that real data are contained only within the first 40 bytes of the information field.

#### 1.14 The Address of a Node

An *address* of a node is composed of 6 bytes. Upon booting up the node, the PC assigns its node with an address. Each node in the network is assigned a unique address.

In addition to assigning a unique address to the node, the PC could also assign a *group address* to its node. A group address is an address that is assigned to several nodes in the network.

When a node transmits data to another node, it inserts the unique address of the destination node in the destination address field of the frame. The frame is then transferred over the network cable and reaches all the nodes in the network. The destination address field enables the destination node to compare the content of the destination address field to the address that was assigned to it upon booting and to decide if the frame is intended for itself.

There are instances when a PC wishes to transmit the same data to all the other PCs in the network. In these cases, instead of transmitting the same frame separately time after time to each of the nodes in the network, the transmitting node sends the frame only once with a destination address equal to all 1s. When a node in the network sees an incoming frame that has all 1s in the destination address field, it realizes that this frame is intended for all the nodes in the network and therefore accepts the frame. This type of transmission is called *broadcasting*.

Another scenario that occurs frequently (and therefore is specified in the 802.3 protocols) is the case in which a PC wishes to send the same data to a special group of PCs in the network. Instead of transmitting the same frame separately time after time to each of the nodes of the group, the node transmits the frame only once with the destination address field containing the address of the group. A group address must have a 1 in the LSB of the address. When a node sees a 1 in the LSB of an incoming frame, it realizes that the frame is intended to a group of nodes. The node then examines to see if the group address specified in the frame matches its own group address that was assigned to it upon booting. If so, it accepts the frame. This type of transmission is called *multicasting*.

#### 1.15 Principle of Operation of an 802.3 LAN

We can now turn to Fig. 1.13 and explain how an IEEE 802.3 LAN operates. The operations discussed below do not describe any particular existing LAN. It is presented merely for the purpose of describing and defining additional procedures and terms specified in the 803.2 protocols. Subsequent chapters discuss the operation of some particular 802.3 LANs.

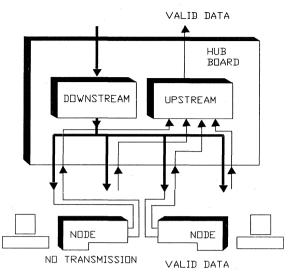

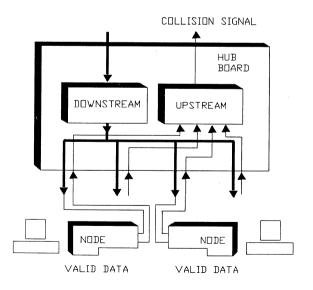

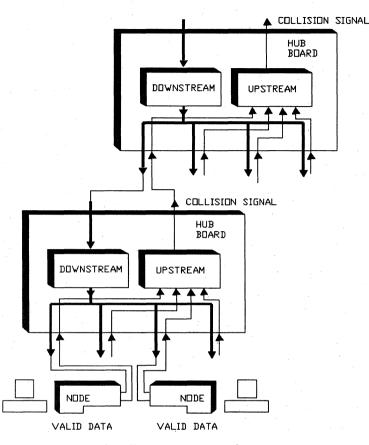

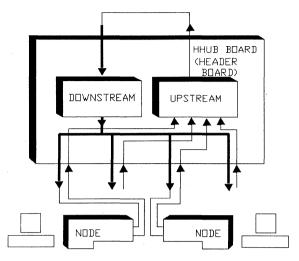

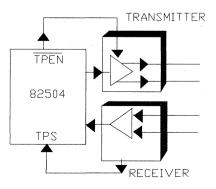

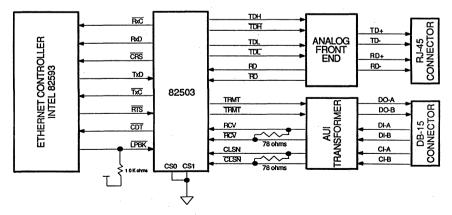

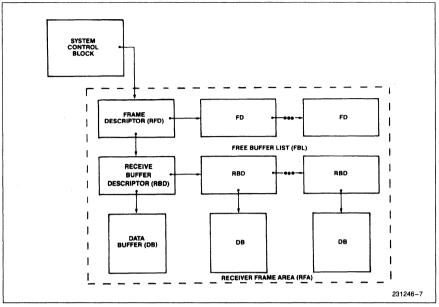

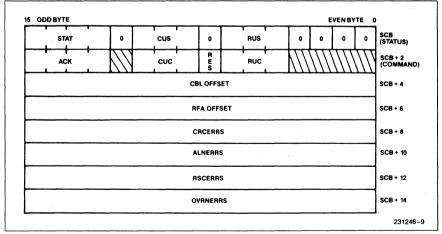

As shown in Fig. 1.13, each node is connected to the network cable via an *interface board*. The number of wires that connect the node to its interface board depends on the particular LAN. Also, the number of wires in the network cable depends on the particular LAN. Since the description below does not pertain to any particular LAN, Fig. 1.13 does not specify the number of wires in the network cable.