# DVI<sup>®</sup> Technology i750<sup>®</sup> Video Processor Technical Specifications

# The i750<sup>®</sup> Video Processor Technical Specifications

# **Contents:**

- 82750PB Video Processor Data Sheet section 1 pages 1 to 63

- 82750DB Display Processor Data Sheet section 2 pages 1 to 55

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

287, 376, 386, 387, 486, 4-SITE, Above, ACE51, ACE96, ACE186, ACE196, ACE960, ActionMedia, BITBUS, COMMputer, CREDIT, Data Pipeline, DVI, ETOX, FaxBACK, Genius, i, <sup>1</sup>, i486, i750, i860, ICE, iCEL, ICEVIEW, ICS, iDBP, IDIS, I<sup>2</sup>ICE, iLBX, iMDDX, IMMX, Inboard, Insite, Intel, Intel, Intel386, int<sub>e</sub>IBOS, Intel Certified, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPAT, iPDS, iPSC, iRMK, iRMX, iSBC, iSBX, ISDM, iSXM, Library Manager, MAPNET, MCS, Megachassis, MICROMAINFRAME, MULTICHANNEL, MULTIMODULE, MultiSERVER, ONCE, OpenNET, OTP, Pro750, PROMPT, Promware, QUEST, QueX, Quick-Erase, Quick-Pulse Programming, READY LAN, RMX/80, RUPI, Seamless, SLD, SugarCube, TooITALK, UPI, VAPI, Visual Edge, VLSiCEL, and ZapCode, and the combination of ICE, iCS, iRMX, ISBC, iSBX, iSXM, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

©INTEL CORPORATION 1990

# 82750PB PIXEL PROCESSOR

- 25 MHz Clock with Single Cycle Execution

- Zero Branch Delay

- Wide Instruction Word Processor

- 512 x 48-Bit Instruction RAM

- 512 x 16-Bit Data RAM

- Two Internal 16-Bit Buses

- ALU with Dual-Add-With-Saturation Mode

- Variable Length Sequence Decoder

- Pixel Interpolator

- High Performance Memory Interface

32-Bit Memory Data Bus

- 50 MBytes per Second Maximum

- 25 MBytes per Second with Standard VRAMs or DRAMs

- 16 General-Purpose Registers

- 4 Gbyte Linear Address Space

- 132-Pin PQFP

- Compatible with the 82750PA

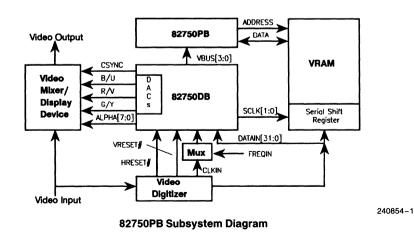

The 82750PB is a 25 MHz wide instruction processor that generates and manipulates pixels. When paired with its companion chip, the 82750DB, and used to implement a DVI Technology video subsystem, the 82750PB provides real time (30 images/sec) pixel processing, real time video compression, interactive motion video playback and real time video effects.

Real time pixel manipulations, including 30 images/sec video compression, are supported by the 25 MHz instruction rate. On-chip instruction RAM provides programmability for execution of a wide range of algorithms that support motion video decompression, text, and 2D and 3D graphics. Inner loops are optimized with the integration of sixteen 16-bit quad ported registers, on-chip DRAM, and two loop counters that provide zero delay two-way branching "free" in any instruction. Two, 16-bit internal buses enable two parallel register transfers on each 82750PB instruction, contributing to the real time performance of the video processing. Another feature that adds to the processing power of the 82750PB is the 16-bit ALU, which includes an 8-bit dual-add-with-saturate operation critical for pixel arithmetic. Other specialized features for pixel processing include a 2D pixel interpolator for image processing functions and a variable length sequence decoder for decoding compressed data.

The 82750PB is implemented using Intel's low-power CHMOS IV Technology and is packaged in a 132-lead space-saving, plastic quad flat pack (PQFP) package.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied. Information contained herein supersedes previously published specifications on these devices from Intel. October 1990 © INTEL CORPORATION, 1990 Order Number: 240854-001

# 82750PB Pixel Processor

| CONTENTS                                         | PAGE |

|--------------------------------------------------|------|

| 1.0 82750PB PIN DESCRIPTION                      | 5    |

| Pinout                                           | 5    |

| Quick Pin Reference                              | 6    |

| 2.0 ARCHITECTURE                                 | 12   |

| Overview                                         | 12   |

| Registers                                        | 13   |

| ALU                                              | 13   |

| Barrel Shifter                                   | 14   |

| Data RAM                                         | 14   |

| Loop Counters                                    | 14   |

| Microcode RAM                                    | 14   |

| Horizontal Line Counter                          | 16   |

| Input FIFOs                                      | 16   |

| Output FIFOs                                     | 17   |

| Statistical Decoder                              | 18   |

| Pixel Interpolator                               | 23   |

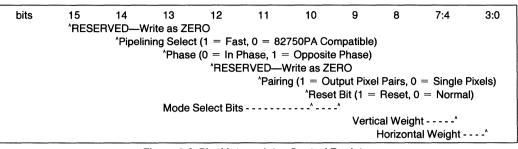

| Mode Select                                      | 24   |

| Reset                                            | 24   |

| Pairing                                          | 24   |

| Phase                                            | 24   |

| Pipelining                                       | 24   |

| Reserved                                         | 25   |

| Signature Register                               | 25   |

| Display Format Registers                         | 25   |

| 3.0 HARDWARE INTERFACE                           | 26   |

| VRAM Interface                                   | 26   |

| VRAM Accesses                                    | 27   |

| Fast VRAM Cycles                                 | 28   |

| VBUS Codes                                       | 28   |

| Method for Calculating TC <sub>VBTR</sub> Cycles | 29   |

| Priority                                         | 29   |

| VRAM Pointers                                    | 30   |

| Shadow Copy                                      | 30   |

| Host Interface                                   | 31   |

| Host Register Access                             | 32   |

| CONTENTS                                          | PAGE |

|---------------------------------------------------|------|

| Host VRAM Access                                  |      |

| Host External Access                              |      |

| Host Register Address Mapping                     |      |

| Initializing the 82750PB                          |      |

| Performance Monitoring                            |      |

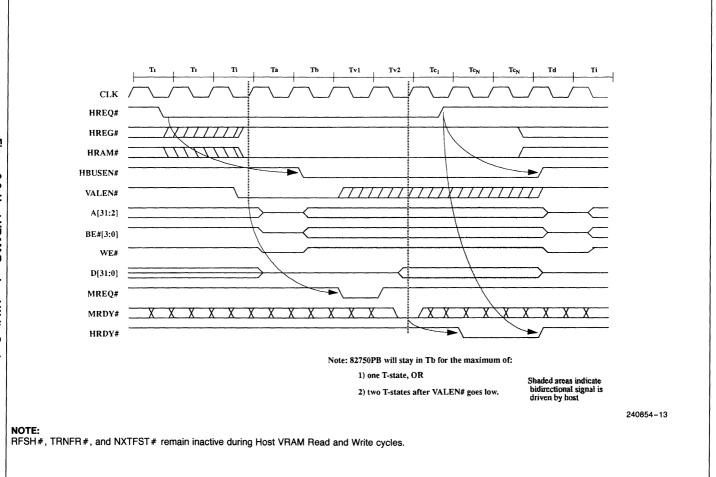

| Host/VRAM Timing Diagrams                         | 37   |

| 4.0 MICROCODE INSTRUCTION<br>FORMAT               | 42   |

| Overview                                          |      |

| Instruction Sequencing                            |      |

| Instruction Word Field Descriptions               |      |

| NADDR—Next Instruction Address<br>Field           |      |

| CFSEL—Condition Flag Select<br>Field              |      |

| ASRC—A Bus Source Select Field                    |      |

| ADST—A Bus Destination Select<br>Field            |      |

| BSRC—B Bus Source Select Field .                  |      |

| BDST—B Bus Destination Select<br>Field            |      |

| CNT—Decrement Loop Counter Bit                    |      |

| LIT—Literal Select Bit                            |      |

| SHFT—Shift Control Field                          |      |

| ALUSS—ALU Source Select Bits                      |      |

| ALUOP—ALU Operation Code                          |      |

| Field                                             |      |

| LC—Loop Counter Select Bit                        | 44   |

| 5.0 HOW MICROCODE EXECUTES                        | 44   |

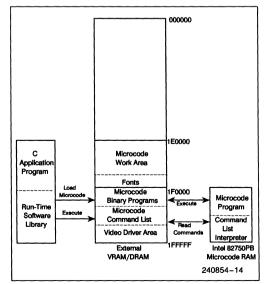

| DVI Technology Microcode Execution .              |      |

| Command List Interpreter                          | 45   |

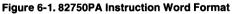

| 6.0 82750PA DIFFERENCES                           | 45   |

| 82750PA/82750PB Compatibility<br>Issues           | 45   |

| 82750PA and 82750PB Source/<br>Destination Coding |      |

| 82750PA and 82750PB Instruction Word              |      |

| Format                                            | 50   |

## 82750PB Pixel Processor

| CONTENTS                                              | PAGE |

|-------------------------------------------------------|------|

| 7.0 ELECTRICAL DATA                                   | 54   |

| D.C. Characteristics                                  | 54   |

| A.C. Characteristics                                  | 55   |

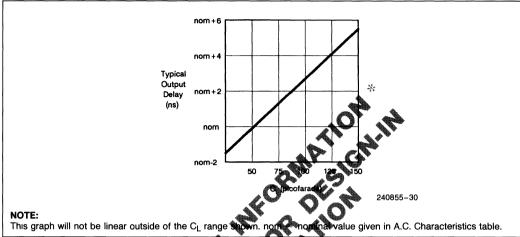

| Output Delay and Rise Time Versus Load<br>Capacitance |      |

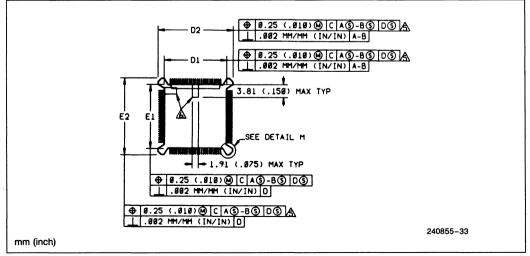

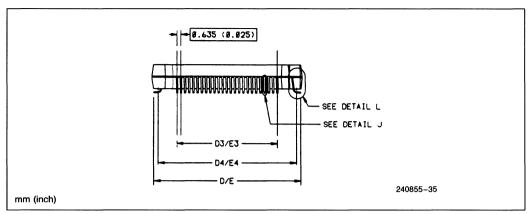

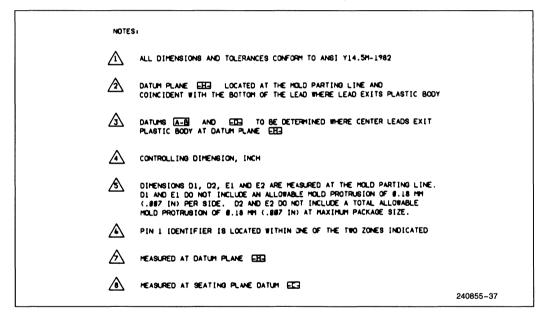

| 8.0 MECHANICAL DATA                                   | 58   |

| Packaging Outlines and Dimensions                     | 58   |

| Package Thermal Specifications                        | 62   |

| FIGURES                                               |      |

| Figure 1-1. 82750PB Pinout                            | 5    |

| Figure 1-2. 82750PB Functional Signal<br>Groupings    | 8    |

| Figure 2-1. 82750PB Block Diagram                     |      |

| Figure 2-2. Input FIFO Control Register               | 16   |

| Figure 2-3. Output FIFO Control<br>Register           | 17   |

| Figure 1-1. | 82750PB Pinout                                         | 5 |

|-------------|--------------------------------------------------------|---|

| Figure 1-2. | 82750PB Functional Signal<br>Groupings                 | 8 |

| Figure 2-1. | 82750PB Block Diagram 12                               | 2 |

| Figure 2-2. | Input FIFO Control Register 16                         | 6 |

| Figure 2-3. | Output FIFO Control<br>Register 12                     | 7 |

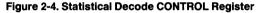

| Figure 2-4. | Statistical Decode CONTROL<br>Register 2               | 1 |

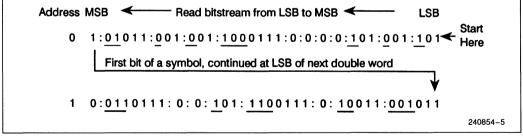

| Figure 2-5. | VRAM Bitstream Decoding<br>Addresses 22                | 2 |

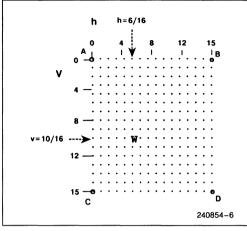

| Figure 2-6. | Pixel Interpolation 23                                 | 3 |

| Figure 2-7. | Sequential-2D Pixel<br>Interpolation                   | 3 |

| Figure 2-8. | Pixel Interpolator Control<br>Register                 | 4 |

| Figure 2-9. | Pixel Pair Phases 24                                   | 4 |

| Figure 3-1. | Access State Diagram 27                                | 7 |

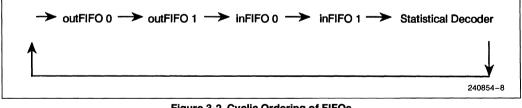

| Figure 3-2. | Cyclic Ordering of FIFOs 30                            | 0 |

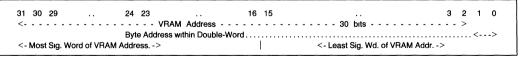

| Figure 3-3. | VRAM Addressing 30                                     | 0 |

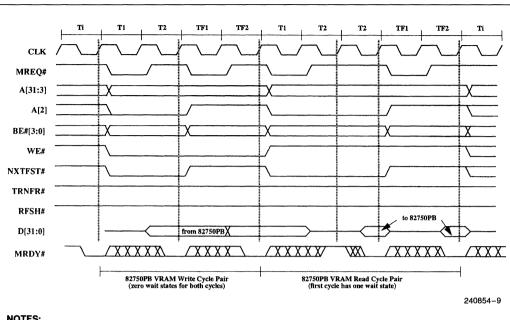

| -           | VRAM Read and Write<br>Cycles 34                       | 8 |

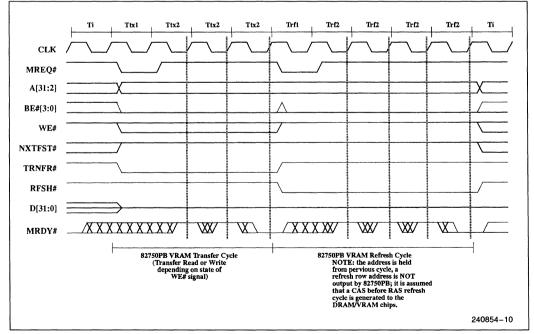

| Figure 3-5. | VRAM Transfer and Refresh<br>Cycles                    | 8 |

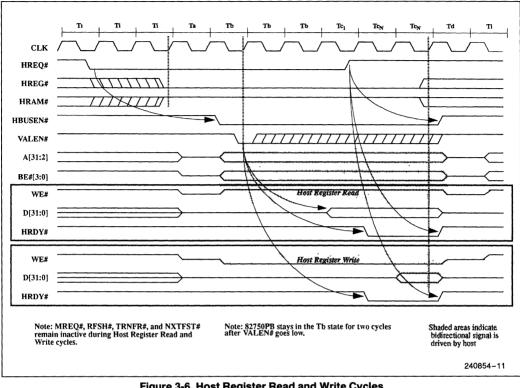

| Figure 3-6. | Host Register Read and Write<br>Cycles                 | 9 |

| Figure 3-7. | Host VRAM Read and Write<br>Cycles 44                  | 0 |

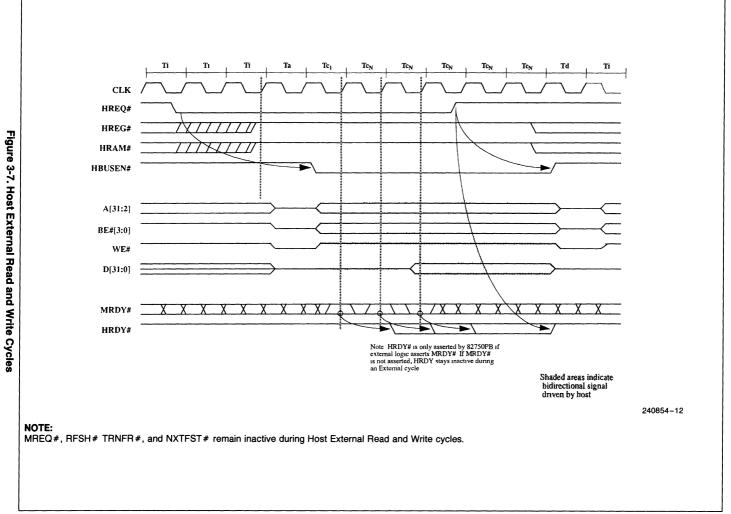

| Figure 3-8. | Host External Cycles 4                                 | 1 |

| -           | Literal Field Mapping onto a<br>Bus 44                 | 4 |

| Figure 5-1. | Execution of an Intel 82750PB<br>Microcode Function 44 | 4 |

| CONTENTS                                                                                            | PAGE |

|-----------------------------------------------------------------------------------------------------|------|

| Figure 6-1. 82750PA Instruction Word<br>Format                                                      | 50   |

| Figure 6-2. 82750PB Instruction Word<br>Format                                                      | 52   |

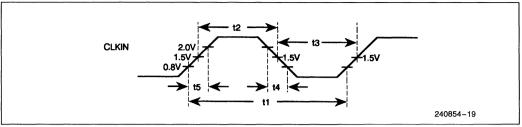

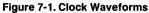

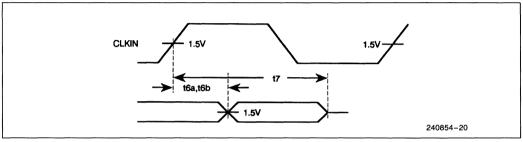

| Figure 7-1. Clock Waveforms                                                                         | 56   |

| Figure 7-2. Output Waveforms                                                                        | 56   |

| Figure 7-3. Input Waveforms                                                                         | 56   |

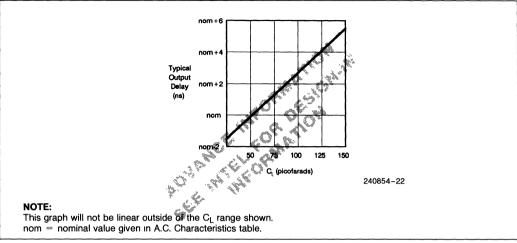

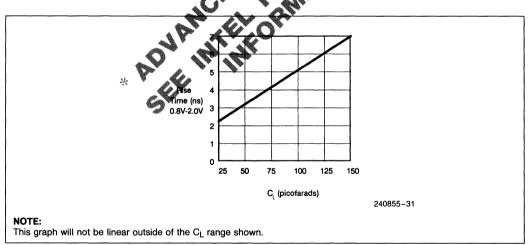

| Figure 7-4. Typical Output Valid Delay<br>Versus Load Capacitance<br>under Worst Case<br>Conditions | 57   |

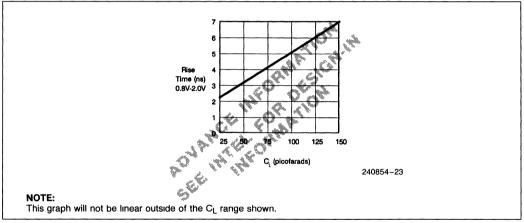

| Figure 7-5. Typical Output Rise Time<br>Versus Load Capacitance<br>under Worst Case<br>Conditions   | 57   |

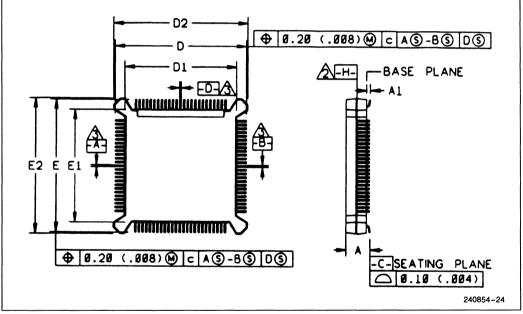

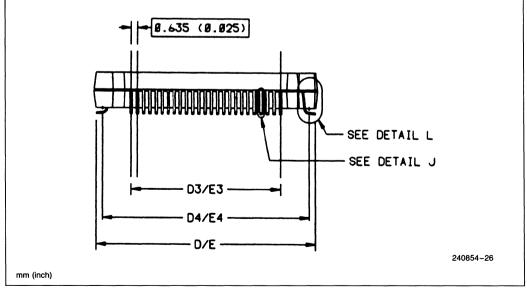

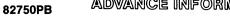

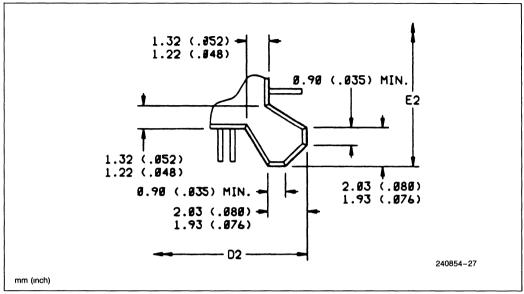

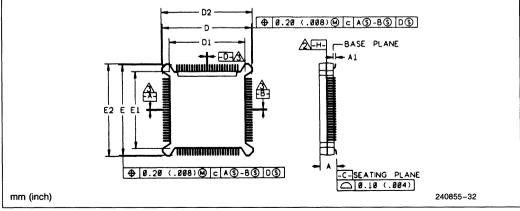

| Figure 8-1. Principal Dimensions and Datums                                                         | 59   |

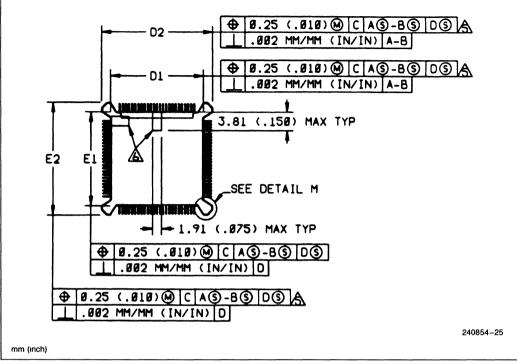

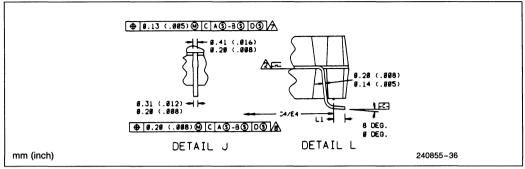

| Figure 8-2. Molding Details                                                                         | 60   |

| Figure 8-3. Terminal Details                                                                        | 60   |

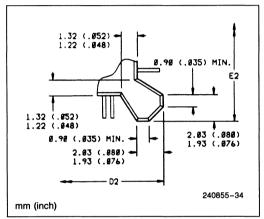

| Figure 8-4. Typical Lead                                                                            | 61   |

| Figure 8-5. Bumper (Detail M)                                                                       | 61   |

|                                                                                                     |      |

## TABLES

| Table 1-1. | Pin Cross Reference by Pin Name6    |

|------------|-------------------------------------|

| Table 1-2. | Pin Cross Reference by Location7    |

| Table 1-3. | Pin Descriptions9                   |

| Table 1-4. | Output Pins 11                      |

| Table 1-5. | Input Pins 11                       |

| Table 1-6. | Input/Output Pins 11                |

| Table 2-1. | Bit Assignment for cc<br>Register13 |

| Table 2-2. | Sample Code Description Table       |

| Table 2-3. | Decoded Values 19                   |

| Table 2-4. | END Mode Decoded<br>Values 19       |

| Table 2-5. | END Flag Decoded Values 20          |

| Table 2-6. | Packed 3-Bit Field Decoded Values   |

| Table 2-7. | VRAM Bitstream Decoded<br>Values 22 |

| Table 2-8. | Decoding Symbols 22                 |

|            |                                     |

## 82750PB Pixel Processor

| CONTEN      | NTS P                                                          | AGE |

|-------------|----------------------------------------------------------------|-----|

| Table 2-9.  | Mode Select Operating<br>Modes                                 | 25  |

| Table 2-10. | Pipelining Delay for<br>Sequential-2D NON-PAIR<br>Mode         | 25  |

| Table 2-11. | Signature Values                                               | 25  |

| Table 2-12. | Display Registers                                              | 26  |

| Table 3-1.  | VRAM Interface Signals                                         | 26  |

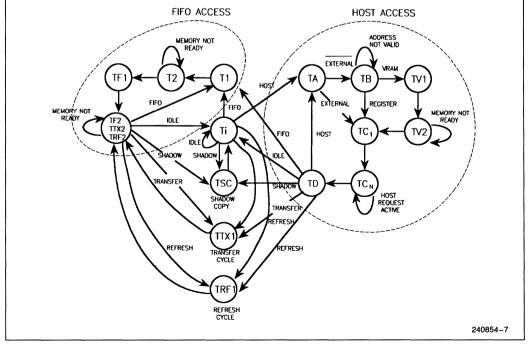

| Table 3-2.  | 82750PB VRAM Access<br>States                                  | 27  |

| Table 3-3.  | VBUS Codes                                                     | 28  |

| Table 3-4.  | Priority of VRAM<br>Operations                                 | 29  |

| Table 3-5.  | Host Interface Signals                                         | 31  |

| Table 3-6.  | Host, VRAM and External Device Signals                         | 31  |

| Table 3-7.  | 82750PB Host Transaction<br>States                             | 32  |

| Table 3-8.  | Host Cycle Types                                               | 32  |

| Table 3-9.  | Host Address Mapping                                           |     |

| Table 3-10. | Bit Assignments for<br>Microcode Processor<br>CONTROL Register | 34  |

| Table 3-11. | Bit Assignments for<br>INTERRUPT FLAG<br>Register              | 35  |

| Table 3-12. | Bit Assignments for<br>PROCESSOR STATUS<br>Register            | 35  |

| CONTEN      | ITS                                                            | PAGE |

|-------------|----------------------------------------------------------------|------|

| Table 3-13. | VRAM Pointer RAM<br>Mapping                                    | 36   |

|             | Mirocode Next Instruction Selection                            | 42   |

| Table 4-2.  | PC Load Example                                                | 43   |

| Table 4-3.  | Condition Flag Select Field<br>Assignments                     | 43   |

| Table 4-4.  | SHIFT Control Field<br>Coding                                  | 44   |

| Table 6-1.  | 82750PB/82750PA<br>Functionality Differences                   | 45   |

| Table 6-2.  | 82750PA Source/Destination                                     |      |

| Table 6-3.  | 82750PB Source/Destination                                     |      |

| Table 7-1.  | Absolute Maximum<br>Requirements                               | 54   |

| Table 7-2.  | D.C. Characteristics                                           |      |

| Table 7-3.  | A.C. Characteristics at 25 MHz                                 | 55   |

| Table 8-1.  | PQFP Symbol List                                               | 58   |

| Table 8-2.  | Intel Case Outline Drawings<br>for PQFP at 0.025-Inch<br>Pitch | 59   |

| Table 8-3.  | Thermal Resistances<br>(°C/W)                                  | 63   |

| Table 8-4.  | Maximum T <sub>A</sub> at Various<br>Airflows                  | 63   |

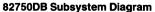

## 1.0 82750PB PIN DESCRIPTION

## Pinout

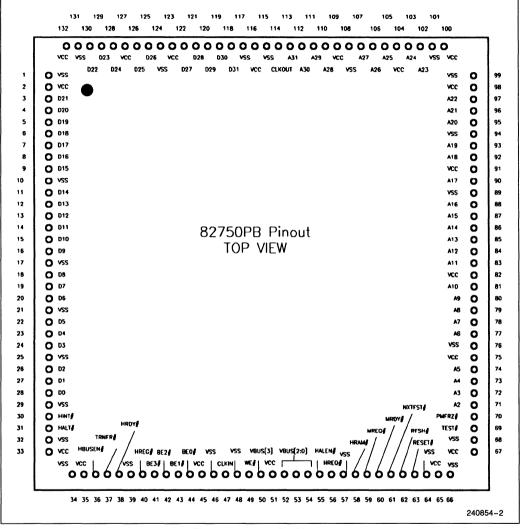

Figure 1-1. 82750PB Pinout

| Pin<br>Name | Location | Pin<br>Name | Location | Pin<br>Name     | Location | Pin<br>Name     | Location |

|-------------|----------|-------------|----------|-----------------|----------|-----------------|----------|

| A2          | 71       | BE3\        | 41       | D30             | 119      | V <sub>CC</sub> | 100      |

| A3          | 72       | CLKIN       | 47       | D31             | 118      | V <sub>CC</sub> | 104      |

| A4          | 73       | CLKOUT      | 114      | HALEN#          | 55       | V <sub>SS</sub> | 94       |

| A5          | 74       | D0          | 28       | HALT#           | 31       | V <sub>CC</sub> | 109      |

| A6          | 77       | D1          | 27       | HBUSEN#         | 36       | V <sub>CC</sub> | 116      |

| A7          | 78       | D2          | 26       | HINT#           | 30       | V <sub>CC</sub> | 123      |

| A8          | 79       | D3          | 24       | HRAM#           | 58       | V <sub>CC</sub> | 127      |

| A9          | 80       | D4          | 23       | HRDY#           | 38       | V <sub>CC</sub> | 132      |

| A10         | 81       | D5          | 22       | HREG #          | 40       | V <sub>SS</sub> | 1        |

| A11         | 83       | D6          | 20       | HREQ#           | 56       | V <sub>SS</sub> | 32       |

| A12         | 84       | D7          | 19       | MRDY#           | 60       | VSS             | 34       |

| A13         | 85       | D8          | 18       | MREQ#           | 59       | V <sub>SS</sub> | 39       |

| A14         | 86       | D9          | 16       | NXTFST#         | 61       | V <sub>SS</sub> | 48       |

| A15         | 87       | D10         | 15       | PMFRZ#          | 70       | V <sub>SS</sub> | 57       |

| A16         | 88       | D11         | 14       | RESET#          | 63       | V <sub>SS</sub> | 66       |

| A17         | 90       | D12         | 13       | RFSH#           | 62       | V <sub>SS</sub> | 68       |

| A18         | 92       | D13         | 12       | TEST#           | 69       | V <sub>SS</sub> | 76       |

| A19         | 93       | D14         | 11       | TRNFR#          | 37       | V <sub>SS</sub> | 89       |

| A20         | 95       | D15         | 9        | VBUS[0]         | 54       | V <sub>SS</sub> | 99       |

| A21         | 96       | D16         | 8        | VBUS[1]         | 53       | Vss             | 101      |

| A22         | 97       | D17         | 7        | VBUS[2]         | 52       | V <sub>SS</sub> | 108      |

| A23         | 102      | D18         | 6        | VBUS[3]         | 50       | V <sub>SS</sub> | 115      |

| A24         | 103      | D19         | 5        | Vcc             | 2        | V <sub>SS</sub> | 117      |

| A25         | 105      | D20         | 4        | V <sub>CC</sub> | 33       | V <sub>SS</sub> | 124      |

| A26         | 106      | D21         | 3        | V <sub>CC</sub> | 35       | V <sub>SS</sub> | 131      |

| A27         | 107      | D22         | 130      | Vcc             | 45       | V <sub>SS</sub> | 10       |

| A28         | 110      | D23         | 129      | Vcc             | 51       | V <sub>SS</sub> | 17       |

| A29         | 111      | D24         | 128      | V <sub>CC</sub> | 65       | V <sub>SS</sub> | 21       |

| A30         | 112      | D25         | 126      | V <sub>CC</sub> | 67       | V <sub>SS</sub> | 25       |

| A31         | 113      | D26         | 125      | V <sub>CC</sub> | 75       | V <sub>SS</sub> | 29       |

| BE0\        | 44       | D27         | 122      | Vcc             | 82       | V <sub>SS</sub> | 46       |

| BE1\        | 43       | D28         | 121      | Vcc             | 91       | V <sub>SS</sub> | 64       |

| BE2\        | 42       | D29         | 120      | V <sub>CC</sub> | 98       | WE#             | 49       |

Table 1-1. Pin Cross Reference by Pin Name

| <b></b>  |                 |          |                 |  |          |                 |          |                 |

|----------|-----------------|----------|-----------------|--|----------|-----------------|----------|-----------------|

| Location | Pin<br>Name     | Location | Pin<br>Name     |  | Location | Pin<br>Name     | Location | Pin<br>Name     |

| 1        | V <sub>SS</sub> | 34       | V <sub>SS</sub> |  | 67       | V <sub>CC</sub> | 100      | V <sub>CC</sub> |

| 2        | Vcc             | 35       | Vcc             |  | 68       | V <sub>SS</sub> | 101      | V <sub>SS</sub> |

| 3        | D21             | 36       | HBUSEN#         |  | 69       | TEST#           | 102      | A23             |

| 4        | D20             | 37       | TRNFR#          |  | 70       | PMFRZ#          | 103      | A24             |

| 5        | D19             | 38       | HRDY#           |  | 71       | A2              | 104      | V <sub>CC</sub> |

| 6        | D18             | 39       | V <sub>SS</sub> |  | 72       | A3              | 105      | A25             |

| 7        | D17             | 40       | HREG#           |  | 73       | A4              | 106      | A26             |

| 8        | D16             | 41       | BE3#            |  | 74       | A5              | 107      | A27             |

| 9        | D15             | 42       | BE2#            |  | 75       | V <sub>CC</sub> | 108      | V <sub>SS</sub> |

| 10       | V <sub>SS</sub> | 43       | BE1#            |  | 76       | V <sub>SS</sub> | 109      | V <sub>CC</sub> |

| 11       | D14             | 44       | BE0#            |  | 77       | A6              | 110      | A28             |

| 12       | D13             | 45       | V <sub>CC</sub> |  | 78       | A7              | 111      | A29             |

| 13       | D12             | 46       | V <sub>SS</sub> |  | 79       | A8              | 112      | A30             |

| 14       | D11             | 47       | CLKIN           |  | 80       | A9              | 113      | A31             |

| 15       | D10             | 48       | V <sub>SS</sub> |  | 81       | A10             | 114      | CLKOUT          |

| 16       | D9              | 49       | WE#             |  | 82       | V <sub>CC</sub> | 115      | V <sub>SS</sub> |

| 17       | V <sub>SS</sub> | 50       | VBUS[3]         |  | 83       | A11             | 116      | V <sub>CC</sub> |

| 18       | D8              | 51       | V <sub>CC</sub> |  | 84       | A12             | 117      | V <sub>SS</sub> |

| 19       | D7              | 52       | VBUS[2]         |  | 85       | A13             | 118      | D31             |

| 20       | D6              | 53       | VBUS[1]         |  | 86       | A14             | 119      | D30             |

| 21       | V <sub>SS</sub> | 54       | VBUS[0]         |  | 87       | A15             | 120      | D29             |

| 22       | D5              | 55       | HALEN#          |  | 88       | A16             | 121      | D28             |

| 23       | D4              | 56       | HREQ#           |  | 89       | V <sub>SS</sub> | 122      | D27             |

| 24       | D3              | 57       | V <sub>SS</sub> |  | 90       | A17             | 123      | V <sub>CC</sub> |

| 25       | V <sub>SS</sub> | 58       | HRAM#           |  | 91       | V <sub>CC</sub> | 124      | V <sub>SS</sub> |

| 26       | D2              | 59       | MREQ#           |  | 92       | A18             | 125      | D26             |

| 27       | D1              | 60       | MRDY#           |  | 93       | A19             | 126      | D25             |

| 28       | D0              | 61       | NXTFST#         |  | 94       | V <sub>SS</sub> | 127      | V <sub>CC</sub> |

| 29       | V <sub>SS</sub> | 62       | RFSH#           |  | 95       | A20             | 128      | D24             |

| 30       | HINT#           | 63       | RESET#          |  | 96       | A21             | 129      | D23             |

| 31       | HALT#           | 64       | V <sub>SS</sub> |  | 97       | A22             | 130      | D22             |

| 32       | V <sub>SS</sub> | 65       | V <sub>CC</sub> |  | 98       | V <sub>CC</sub> | 131      | V <sub>SS</sub> |

| 33       | V <sub>CC</sub> | 66       | V <sub>SS</sub> |  | 99       | V <sub>SS</sub> | 132      | V <sub>CC</sub> |

Table 1-2. Pin Cross Reference by Location

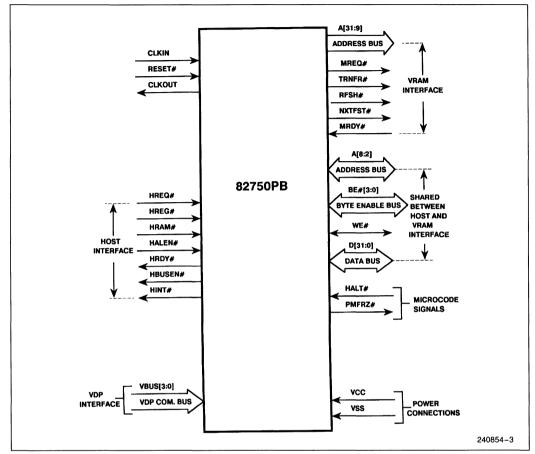

Figure 1-2. 82750PB Functional Signal Groupings

## **Quick Pin Reference**

Table 1-3 provides descriptions of 82750PB pins.

| 0                 | <b>T</b> | Table 1-3. Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol            | Туре     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CLKIN             | 1        | CLKIN is a <b>1X CLOCK INPUT</b> that provides the fundamental timing for the 82750PB. One cycle of CLKIN is denoted as one T-cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RESET#            | 1        | The 82750PB is reset and initialized by holding this signal active for at least ten T-cycles. Refer to page 36.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HREQ#             | I        | The <b>HOST REQUEST</b> signal is a request from the host CPU to perform a read<br>or write access to either registers on the 82750PB, an external device, or to<br>VRAM shared by the 82750PB and the host. The type of access that is<br>requested is determined by the host access definition signals: HREG #,<br>HRAM #, and WE #.                                                                                                                                                                                                                                                                                                                                  |

| HREG,#<br>HRAM#   | I        | The <b>HOST REGISTER</b> and <b>HOST RAM</b> signals, when validated by HREQ#, are used to define three host access cycles. HRAM# active indicates the host is requesting a VRAM read or write cycle. HREG# active indicates that the host is requesting a 82750PB register read or register write cycle. When both signals are inactive, a host external cycle is requested.                                                                                                                                                                                                                                                                                           |

| HBUSEN#           | 0        | <b>HOST BUS ENABLE</b> is asserted by the 82750PB at the start of a host access to indicate that the 82750PB Address and Data buses (A[31:2], BE $\#$ [3:0], and D[31:0]) have been tri-stated. This allows the host to drive the same buses either for accessing shared VRAM or the 82750PB internal registers.                                                                                                                                                                                                                                                                                                                                                        |

| HALEN#            | I        | The <b>HOST ADDRESS LATCH ENABLE</b> signal is used to indicate to the 82750PB that the host has asserted a valid address (A[31:2], BE $#$ [3:0]) and write enable (WE $#$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HRDY#             | 0        | <b>HOST READY</b> is asserted by the 82750PB at the end of a host access to indicate that the access cycle is ready for data transfer. For a host write cycle, HRDY # indicates that the 82750PB is ready to accept data from the host. For a host VRAM write cycle, HRDY # indicates that the VRAM has latched the data from the host. For a host read cycle, HRDY # indicates that output data from the 82750PB or VRAM is ready to be latched by the host.                                                                                                                                                                                                           |

| HINT #            | 0        | <b>HOST INTERRUPT:</b> This output is asserted when an interrupt condition is detected by the 82750PB, and the enable bit in the PROCESSOR CONTROL register corresponding to that interrupt condition is set to a ONE. HINT# stays active until the host CPU reads the INTERRUPT STATUS register. If an interrupt condition that is enabled occurs during the same cycle that the INTERRUPT STATUS register is being read, HINT# remains active.                                                                                                                                                                                                                        |

| D[31:0]           | 1/0      | The <b>DATA BUS</b> is used to transfer data between:<br>1. The 82750PB and VRAM, and<br>2. The Host CPU and internal 82750PB registers. During host VRAM accesses,<br>this bus is tri-stated to allow the host to share the same VRAM data bus. During<br>host accesses to internal 82750PB registers all 32 bits are used for data<br>transfer.                                                                                                                                                                                                                                                                                                                       |

| A[31:9]<br>A[8:2] | 0<br>1/0 | The <b>ADDRESS BUS</b> is shared between the 82750PB and the host for<br>addressing VRAM. This 30-pin bus addresses 32-bit double words in VRAM.<br>Byte Enable signals are used to address individual bytes or words within a<br>double word in VRAM. In addition, the address for host accesses to internal<br>82750PB registers are communicated to the 82750PB using the lower seven<br>pins, A[8:2], and the BE# pins. During host access cycles to either VRAM or<br>82750PB internal registers, A[31:2] are tri-stated. For internal register<br>accesses, as indicated by HREG# being low, the lower seven bits, A[8:2], are<br>used as the host address input. |

| CLKOUT            | 0        | The <b>CLOCK OUTPUT</b> signal is one of the two internal clocks and is synchronized with CLKIN. It is always driven and will have a 50% duty cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

7

82750PB

Table 1-3. Pin Descriptions (Continued)

| Symbol           | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BE#[3:0]         | 1/0  | The <b>BYTE ENABLE BUS</b> is shared by the 82750PB and the host for addressing VRAM down to the byte level. The correspondence between the four Byte Enable pins and the D[31:0] pins is: BE # [3] – D[31:24], BE # [2] – D[23:16], BE # [1] – D[15:8], and BE # [0] – D[7:0]. During VRAM read cycles, the 82750PB enables all four bytes. During write cycles the 82750PB only enables those bytes that are to be written. Bytes that are not enabled are not to be altered in VRAM. During host accesses to 82750PB on-chip registers, the BE # [0] pin is used as an input to select whether the even or odd word is being accessed; the double word address is provided by the host on the A[8:2] pins. BE # [0] = 0 indicates that data is transferred on D[15:0]. BE # [0] = 1 indicates that data is transferred on D[31:16]. |

| MREQ#            | 0    | <b>MEMORY REQUEST</b> is asserted for the first cycle, T1, of each VRAM cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TRNFR#,<br>RFSH# | 0    | The <b>MEMORY CYCLE DEFINITION SIGNALS:</b> Transfer, Refresh and<br>Write Enable are asserted at the same time as MREQ#, but stay active<br>for the entire VRAM cycle. TRNFR# active indicates a VRAM transfer<br>cycle. RFSH# active indicates a VRAM refresh cycle. If neither TRNFR#<br>nor RFSH# are active, a VRAM data read or write cycle is requested.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| WE#              | 1/0  | The <b>WRITE ENABLE</b> pin is used as an output during a 82750PB/VRAM cycle to drive the WE # signal, which defines the access as a VRAM read cycle (when inactive) or write cycle (when active). During Host/VRAM and Host External cycles, the 82750PB tri-states this pin to allow the host to drive the VRAM write enable signals directly. During Host/register cycles, this pin is used as an input for the Host Write Enable signal to determine whether the host is reading or writing the 82750PB register.                                                                                                                                                                                                                                                                                                                  |

| NXTFST#          | Ο    | The <b>NEXT FAST</b> signal indicates that the following vram cycle can be performed with a page-mode or bank-interleaved access. This signal is asserted during the first of a pair of VRAM cycles that is guaranteed to be within the same VRAM page and in opposite banks—a pair of accesses to two sequential double words in VRAM at addresses Even Address and Even Address $+$ 1. In other words, A[2] is a zero for the first cycle and a one for the second cycle.                                                                                                                                                                                                                                                                                                                                                            |

| MRDY#            | I    | The <b>MEMORY READY</b> input indicates that the VRAM cycle has<br>progressed to the point where it is ready to perform the data transfer. For<br>a VRAM read cycle, the VRAM data can be latched by the transition of<br>MRDY# to an active state. For a VRAM write cycle, MRDY# indicates<br>that the data has been latched into the VRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VBUS[3:0]        | Ι    | The <b>VDP COMMUNICATION BUS</b> is used to communicate from the 82750DB to the 82750PB. Codes sent over this bus indicate interrupt requests, transfer requests, and status information. Since the 82750DB and 82750PB run asynchronously, the VBUS signals are sampled on the falling edge of CLKIN and compared with the previous sample. For a VBUS code to be detected by the 82750PB, it must be valid for two successive samples.                                                                                                                                                                                                                                                                                                                                                                                               |

| HALT#            | I    | The <b>HALT</b> signal causes the microcode processor on the 82750PB to halt prior to executing the next instruction. This signal does not halt the VRAM interface. The Halt signal will allow the design of a hardware emulator for the 82750PB based on an 82750PB chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TEST#            | I    | The <b>TEST</b> signal is used for test purposes only and must remain high for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Symbol          | Туре | Name and Function                                                                                                                                                                                |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMFRZ#          | 0    | The <b>PERFORMANCE MONITORING AND FREEZE</b> signal is toggled by<br>specific microcode instructions and can be used to determine the time<br>required to execute certain sections of microcode. |

| V <sub>CC</sub> | 1    | <b>POWER</b> pins provide the +5V D.C. supply input.                                                                                                                                             |

| V <sub>SS</sub> | I    | GROUND pins provide the 0V connection to which all inputs and outputs<br>are referenced.                                                                                                         |

## Table 1-3. Pin Descriptions (Continued)

## Table 1-4. Output Pins

| Name             | Active<br>Level | When<br>Floated    |

|------------------|-----------------|--------------------|

| CLKOUT           | High            | Always Driven      |

| A[31:9]          | High            | Reset*, Host Cycle |

| HBUSEN#          | Low             | Reset*             |

| HRDY#            | Low             | Reset*             |

| HINT#            | Low             | Reset*             |

| MREQ#            | Low             | Reset*             |

| TRNFR#,<br>RFSH# | Low             | Reset*             |

| NXTFST#          | Low             | Reset*             |

| PMFRZ#           | Low             | Reset*             |

## Table 1-5. Input Pins

| Name      | Active<br>Level | Synchronous/<br>Asynchronous |

|-----------|-----------------|------------------------------|

| CLKIN     | High            | Synchronous                  |

| RESET#    | Low             | Asynchronous                 |

| HREQ#     | Low             | Asynchronous                 |

| HREG#     | Low             | Synchronous                  |

| HRAM#     | Low             | Synchronous                  |

| MRDY #    | Low             | Synchronous                  |

| VBUS[3:0] | High            | Asynchronous                 |

| HALT#     | Low             | Synchronous                  |

| HALEN#    | Low             | Asynchronous                 |

\*The reset state is caused by RESET# being active low.

## Table 1-6. Input/Output Pins

| Name     | Active Level | When Floated       | Synch/Async |

|----------|--------------|--------------------|-------------|

| D[31:0]  | High         | Reset*, Host Cycle | Synchronous |

| A[8:2]   | High         | Reset*, Host Cycle | Synchronous |

| BE#[3:0] | Low          | Reset*, Host Cycle | Synchronous |

| WE#      | Low          | Reset*, Host Cycle | Synchronous |

\*The reset state is caused by RESET# being active low.

All output pins are floated when RESET is active low.

## 2.0 ARCHITECTURE

## **Overview**

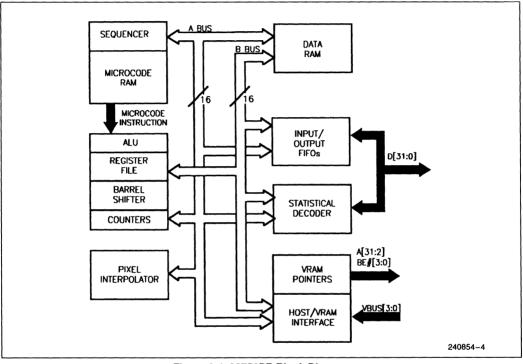

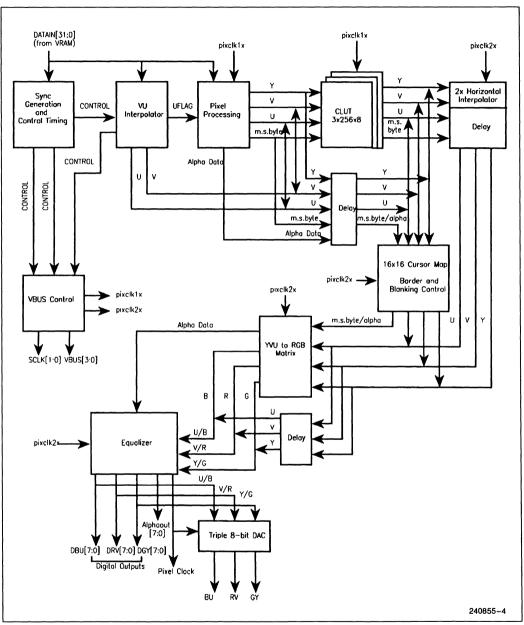

The 82750PB includes a wide instruction word processor that comprises a number of processing, storage, and input/output elements. The wide instruction word architecture allows a number of these elements to operate in parallel. The 82750PB executesone instruction every internal clock cycle or T-cycle. The various elements are connected via two 16-bit buses, the A bus and B bus, as shown in Figure 2-1. During each instruction execution cycle, data can be transferred from a bus source to a bus destination element on both buses.

Figure 2-1. 82750PB Block Diagram

## Registers

$\{rN; N = 0 - 15\}$

There are 16 general-purpose data registers, each 16 bits wide, that are connected to both the A bus and B bus as both sources and destinations. These registers are designated rO-r15. All the registers are functionally identical except r0, which also includes logic for bit shifting and byte swapping. A register can source both the A bus and the B bus in the same cycle. A register cannot be the destination of both the A bus and the B bus in a single instruction. Because the registers are doubly latched, the same register may be both a source and destination in the same cycle. The result is that the data in the register prior to the current cycle will be driven on the source bus, and the data on the destination bus will be latched into the register at the end of the cycle.

Register *r0* has additional logic to allow bit shifting and byte swapping. The value in *r0* can be shifted left or right one bit position per instruction cycle. For a right shift, the new MSB is equal to the old MSB; in other words, the value is sign-extended. For left shifting, the new LSB is equal to zero. *R0* can not be shifted and loaded in the same instruction. Byte swapping, on the other hand, only occurs when *r0* is being loaded with a value from the A bus or B bus. Byte swapping causes the most significant byte and the least significant byte of the 16-bit value being loaded into *r0* to be interchanged. Refer to Chapter 4 for a description of the SHFT microcode field that controls the shifting and swapping operations in *r0*.

## ALU

#### {alu, cc}

The ALU performs 16-bit arithmetic and logic operations, and can also be operated as two independent 8-bit ALUs for the Dual-Add-with-Saturate operation. There are two fields in the microcode instruction that affect the operation of the ALU: the ALUOP field specifies the operation to be performed, and the ALUSS field specifies the source of the two ALU inputs. Refer to Chapter 4 for further information on these fields.

The two ALU operands either come from values held in the ALU input latches or from "eavesdropping" on the A or B buses. The result of any ALU operation is latched in the ALU output register, *alu*. In a following instruction this result can be transferred to any A or B destination. The ALU has four condition flag outputs: CarryOut, Sign, Overflow, and Zero. CarryOut is the carry out of the most significant bit position. Sign is equal to the value of the most significant bit of the result. Overflow is the exclusive-OR of CarryOut and the CarryIn to the most significant bit position of the result. Zero is true (a value of 1) if all 16 bits of the ALU result are equal to zero. CarryOut and Overflow are defined as equal to Zero for all logical operations. For must ALU operations, the state of these four condition flags are latched when the operation is complete. There are six operations (NOP, A\*, B\*, ZERO, PMON, and INT) that are exceptions. These operations are performed without disturbing the condition state of the previous ALU operation.

Microcode routines can read and write the ALU condition flag register, *cc*. This can be used to save and restore the state of these flags. The bit ordering of the ALU condition flags within *cc* are given in Table 2-1.

| Bit      | Condition                    |

|----------|------------------------------|

| DIL      | Condition                    |

| Bit 0    | False (This bit of the cc is |

|          | always read as a zero.)*     |

| Bit 1    | ALU Carry Out                |

| Bit 2    | ALU Overflow                 |

| Bit 3    | ALU Sign                     |

| Bit 4    | ALU Zero                     |

| Bit 5    | Loop Counter Zero*           |

| Bit 6    | R0 LSB*                      |

| Bit 7    | R0 MSB*                      |

| Bit 15:8 | RESERVED. The state of these |

|          | bits is undefined when       |

|          | read; write as zeros.        |

\*These are read-only values and are not affected by writes to the cc register.

The Dual-Add-with-Saturate operation performs independent 8-bit ADDs on the upper and lower bytes of the two ALU operands. The two bytes of the A operand are treated as unsigned binary numbers (00:FF<sub>16</sub> corresponds to 0:255<sub>10</sub>). The two bytes of the B operand are treated as offset binary numbers with an offset of +128 (00:FF<sub>16</sub> corresponds to  $-128_{10}$ :127<sub>10</sub>). The upper and lower byte results are treated as 9-bit offset binary, including the carry output of each byte, with a + 128 offset (000:1FF<sub>16</sub> corresponds to  $-128_{10}$ :383<sub>10</sub>) and are saturated to a range of 0-255<sub>10</sub>. A result that is less than zero is set equal to zero or 00<sub>16</sub> and a result that is greater than +255 is set equal to +255 or FF<sub>16</sub>. In fact, this operation is symmetric. Either the A operand or the B operand can be defined as the unsigned binary value, and the other operand will be treated as the offset signed binary value. The four ALU condition flags are latched after a Dual-Addwith-Saturate operation, but only the ALU ZERO flag has a defined value. It is set to ONE if the two 8-bit results are both zero, otherwise it is set to ZERO. The other three ALU flags are undefined after a Dual-Add-with-Saturate operation.

The ALU opcode INT generates the MCINT (microcode interrupt) condition. When this condition is detected by interrupt logic in the host CPU interface, and if the Enable MCINT bit in the PROCESSOR CONTROL register is set to a ONE, the host interrupt output, HINT #, will be asserted. Refer to Chapter 3 for further information.

## **Barrel Shifter**

#### {shift, shift-r, shift-rl, shift-l}

The barrel shifter performs a single cycle, n-bit left or right shift. The barrel shifter operates independent of the ALU. The three barrel shifter operations are: *Shift-r* for a right shift with sign extend; *Shift-rl* for right shift with zero fill; and *Shift-l* for a left shift with zero fill. The shift operation is invoked by writing a 4-bit value (the shift amount) to one of three A bus registers, depending on which of the three operations is to be performed. The operand is taken from the B bus, and the result is stored in the barrel shift-er output register, *Shift*. Like the ALU result register, the value in *Shift* can be read onto the A bus or B bus in the following instruction cycle.

A barrel shifter operation does not affect any of the condition flags.

## Data RAM

$\{dramN, *dramN, ++, --; N = 1-4\}$

The Data RAM holds 512, 16-bit words that are accessed using four pointers. To access a value in a particular location, the microcode routine must first load a pointer with the address to be accessed, and then perform a read or write using the same pointer. In parallel with the data RAM access, the pointer can optionally be post-incremented or post-decremented. The four pointers, referred to as *dram1-dram4*, can be written and read via the A bus. When a dram pointer, which is only 9 bits wide, is read onto the A bus, its upper seven bits are set to zeros.

#### CAUTION:

The width of the dram pointers may change in later versions of the 82750PB. Software should not rely on the width of a pointer to, for example, mask the upper seven bits of a value to zero.

All four pointers can be used to read or write the Data RAM from either the A or B bus. Only one Data RAM access can be performed in any cycle. A Data RAM access is referred to, using C language syntax, as \**dram1*. The \* means "the value pointed to by". As another example, \**dram3* + means access the Data RAM using the pointer *dram3* and increment *dram3*. The symbol -- in place of the ++ would indicate autodecrement.

## **Loop Counters**

82750PB

#### {cnt,cnt2}

Two 16-bit loop counters are available to microcode programs for automatically counting iterations of a microcode loop. In parallel with other operations performed in an instruction, either loop counter can be decremented, and a conditional branch can be made based on the loop counter value being equal or not equal to zero. Since the two loop counters can be written and read on the A bus, as *cnt* and *cnt2* respectively, they can also be used for variable storage when not being used as loop counters. The loop counters can be written to and decremented during the same instruction cycle. The value in the counter at the start of the next cycle will be the value written to the counter minus one.

The LC microcode bit determines the loop counter that is selected for decrementing and/or branching in an instruction. The LC microcode bit does not affect the loop counter that is written or read over the A bus, since each loop counter is separately addressable as a A bus source or destination. Refer to Chapter 4 for a description of the CNT - microcode bit that causes the select loop counter to be decremented, and for a description of the CFSEL microcode field that is used to perform a conditional branch based on the selected loop counter's value.

## **Microcode RAM**

#### {mcode1-3, maddr, pc}

The 82750PB executes instructions stored in an onchip microcode RAM. This RAM holds 512 instructions and each instruction is 48 bits wide. Normally, to start the microcode processor, the host CPU will load a microcode program into the microcode RAM, point the program counter, *pc*, to the start of the program, and then release the HALT bit to start executing the microcode program. The microcode processor can also load its own microcode RAM to overlay new routines and therefore, does not require constant intervention by the host to perform multiple operations. Writing an instruction into Microcode RAM is done by first loading the three registers *mcode3*, *mcode2*, and *mcode1* with the three 16-bit words of the instruction (the most significant word goes into *mcode1*), and then loading the address where the instruction should be written into *maddr*.

#### NOTE:

In the 82750PA mode, only the lower eight bits of *maddr* are used. The upper eight bits are forced to zeros in order to accurately emulate the 82750PA.

The host CPU can also read the Microcode RAM by first loading the *pc* with the address of the instruction to be read and then reading the three 16-bit words of the instruction from the *mcode1-mcode3* registers. Normally, this would be done by the Host CPU while the 82750PB is halted. Since *mcode1-mcode3* hold the instruction pointed to by the *pc* (i.e. the instruction that is about to be executed), normally reading these three registers from a microcode routine is not useful.

#### CAUTION:

The read registers named mcode1-mcode3 and the write registers also named mcode1-mcode3 are in fact different registers. Writing values into mcode1-mcode3 and then reading the values of mcode1-mcode3 will not read back the same values just written. The read registers hold the instruction stored in the instruction latch (the instruction to be executed). The write registers hold an instruction that is about to be written into microcode RAM.

#### **CAUTION:**

In the 82750PA mode, the bit positions of the microcode fields are scrambled. As a result, data written to microcode RAM via the mcode1-mcode3 registers in the 82750PA mode will not be read as the same values from the mcode1-mcode3 registers. In the 82750PB mode, data written to the microcode RAM will be read back without any bit scrambling. Therefore, testing of the microcode RAM is less difficult in the 82750PB mode.

After writing to *maddr* to load an instruction into microcode RAM, a one cycle freeze occurs and during the freeze a write to the microcode RAM takes place. The instruction following the write to *maddr* can either jump to the address just loaded or start loading the *mcode1-mcode3* registers with the next instruction to be written.

#### CAUTION:

The 82750PB requires at least one instruction between the write to maddr and the execution of the instruction that is loaded by the write to maddr.

Here are two examples:

## Example 1:

| maddr = ADDR1<br>jmp addr1 | * load instruction */<br>* jump to it, this is the extra inst. required bet<br>* writing to maddr and executing the loaded inst. | • |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------|---|

| ADDR1:<br>???????????      | * here's where new instruction gets loaded */                                                                                    |   |

#### Example 2:

| maddr = INST<br>nop  | /* | extra instruct | tion | . */   |      |    |

|----------------------|----|----------------|------|--------|------|----|

| INST:<br>??????????? | /* | instruction ge | ets  | loaded | here | */ |

When a microcode routine writes to *pc*, one more instruction is executed before the jump to the new address takes effect. For example:

| <pre>pc = ADDR1 r0 = r1 jmp ADDR2</pre> | /* this instruction gets executed but */<br>/* its jump to ADDR2 is ignored. */ |

|-----------------------------------------|---------------------------------------------------------------------------------|

| ADDR1:<br>r3 = r0                       | /* after this instruction executes $r3 = r0 = r1 */$                            |

intel

When the host CPU writes to the pc, the instruction at the address that was written is loaded into the *mcode1-mcode3* registers and, when the microcode processor is released from its Halt condition, this is the first instruction that will be executed.

When the host CPU reads the pc, the result returned is the address of the instruction that will be executed when Halt is released, that is, the address of the instruction held in the *mcode1-mcode3* registers.

## **Horizontal Line Counter**

#### {*lcnt*}

The Horizontal Line Counter is updated by VBUS codes from the 82750DB to track the horizontal display line that is currently being scanned by the 82750DB. The counter is reset by a VODD code and incremented each time an HLINE code is received. A value can also be written into a Horizontal Line Counter but this is used primarily for testing the 82750PB.

## **Input FIFOs**

#### $\{inN-lo, inN-hi, inN-c, *inN; N = 1, 2\}$

There are two input channels, referred to as input FIFOs, through which the processor can read pixels or data from VRAM. Each channel automatically fetches 64-bit quad words from VRAM and breaks them into 8-bit bytes or 16-bit words that are read by microcode. Each FIFO operates independently and can be programmed to automatically increment or decrement through bytes or words in VRAM. The FIFOs are double buffered so that while values are being extracted from one quad word (64 bits), the next quad word is being prefetched from VRAM.

The mode control register for each input FIFO, designated *in1-c* or *in2-c*, contains four mode bits as seen in Figure 2-2. The WORD/BYTE bit (bit 0) determines whether the input FIFO is in word mode (WORD/BYTE = 0) or byte mode (WORD/BYTE = 1). In byte mode, the FIFO can start reading on any byte boundary and in word mode on any word boundary.

The INC/DEC bit (bit 1) determines the order that bytes or words are read from VRAM. In INCRE-MENT mode, with INC/DEC = 0, the FIFO reads from the least significant byte or word to the most

significant byte or word of each double word and increments through double words in VRAM. In DEC-REMENT mode, with INC/DEC = 1, the FIFO reads from most significant byte or word to least significant byte or word within a double word and decrements through double words in VRAM.

The PREFETCH OFF bit (bit 2) specifies whether the FIFO will automatically prefetch successive quad words from VRAM or will only fetch a new quad word when a value from that quad word is requested. In PREFETCH-ON mode, bit 2 = 0, the input FIFO prefetches successive quad words from VRAM as necessary to keep its buffer full (either from ascending or descending addresses, depending on the state of the INC/DEC bit). In PREFETCH-OFF mode, the FIFO will still prefetch the first two quad words to fill its buffer (when started at a new address location), but will only fetch a new quad word when a read request is made to the FIFO for a value in the next unfetched quad word.

In "BY-32" MODE (bit 3), the pointer increments or decrements by 32 bits, independent of whether the FIFO is in 8-bit pixel mode or 16-bit pixel mode. This mode was added to facilitate microcode that operates on one component of a 32-bit per pixel image.

The standard sequence for initializing an input FIFO is to write to the control register *(in-c)*, the high address *(in-hi)*, and then the low address *(in-lo)* of the appropriate FIFO. Refer to the access state diagram in Chapter 3. The write to *in-lo* causes the FIFO to start reading from VRAM. A byte or word is then read from *\*in*. Successive reads from *\*in* will read sequential bytes or words from VRAM. Writing to the control register each time the FIFO is started at a new address is not necessary, except to change the FIFO's mode. Also, if the new address is within the same 64 kByte page of VRAM, only the lo-address needs to be written in order to start the FIFO reading from the new address.

If microcode attempts to read a value from an empty input FIFO, the processor is frozen prior to the execution of the instruction, until the FIFO's control logic has fetched another double word from VRAM and extracted the next value. At this point, the processor is released from the frozen state, and the instruction that reads the value is executed. When the processor is frozen waiting for a particular FIFO that isn't yet ready, that FIFO's VRAM access priority is raised above all other FIFOs.

| bits: | 154          | 3          | 2      | 1       | 0         |

|-------|--------------|------------|--------|---------|-----------|

|       | Set to Zeros | BY-32 MODE | PF OFF | INC/DEC | WORD/BYTE |

Figure 2-2. Input FIFO Control Register

## **Output FIFOs**

{outN-lo, outN-hi, outN-c, \*outN, outN++; N = 1, 2}

There are two output channels, referred to as output FIFOs, through which the graphics processor writes pixels or data to VRAM. Each channel automatically collects bytes or words into 64-bit quad words and writes the quad words to VRAM. Each output FIFO operates independently and can be programmed to write bytes or words into sequential addresses in VRAM (either incrementing or decrementing). The FIFOs are double buffered so that while one quad word is waiting to be written to VRAM, the next quad word can be assembled from individual bytes or words.

The mode control register for each output FIFO, designated *out1-c* or *out2-c*, contains six mode bits as shown in the Figure 2-3. The WORD/BYTE bit (bit 0) determines whether the output FIFO is in word mode (WORD/BYTE = 0) or byte mode (WORD/BYTE = 1). In byte mode the FIFO can start writing on any byte boundary in VRAM and in word mode on any word boundary.

The INC/DEC bit (bit 1) determines the order that bytes or words are written to VRAM. In INCREMENT mode, with INC/DEC = 0, the FIFO writes from the least significant byte or word to the most significant byte or word and increments through double words in VRAM. In DECREMENT mode, with INC/DEC = 1, the FIFO writes from most significant byte or word to least significant byte or word within a double word and decrements through double words in VRAM.

When the DISABLE INC/DEC bit (bit 2) is set, the output FIFO quad word address is not incremented or decremented. In this mode, the FIFO continues to output to a single quad word in VRAM.

The FORCE-LSB bits (bits 3 and 4) are used to force the least significant bit of each byte written to VRAM to either a zero or a one. This can be used, for example, to force the LSB to the correct polarity when writing to the U bitmap during motion video decompression. In certain display modes for the 82750DB, the LSB of the 8-bit samples in the U or Y bitmap are used to select VIDEO or GRAPHICS display mode for the n x n group of display pixels corresponding to the particular U or Y sample. A one in the FORCE-LSB ENABLE bit (bit 4) enables the forcing; a zero results in normal operation. The FORCE-LSB VAL-UE bit (bit 3) is used as the value to which the LSB is forced. Whether in byte mode or word mode, the LSB of *each byte* is forced to the FORCE-LSB value.

In "BY-32" MODE (bit 5), the pointer increments or decrements by 32 bits, independent of whether the FIFO is in 8-bit pixel mode or 16-bit pixel mode. This mode is used to facilitate microcode that operates on one component of a 32-bit per pixel image. The bytes or words that are skipped over will be unchanged in VRAM.

The standard sequence for initializing an output FIFO is to write to the control register *(out-c)*, the low address *(out-lo)*, and then the high address *(out-hi)* of the appropriate FIFO. A series of bytes or words is then written to *\*out*. Refer to the access state diagram in Chapter 3.

In order to flush any remaining data in an output FIFO before changing its VRAM pointer, it is necessary to write to the control register. When pointing to a new location in VRAM, if the new address is within the same 64 kByte page of VRAM, only the lo-address needs to be written.

| bits: | 15–6         | 5          | 4         | 3         | 2       | 1       | 0         |

|-------|--------------|------------|-----------|-----------|---------|---------|-----------|

|       | Set to Zeros | BY-32 MODE | FORCE-LSB | FORCE-LSB | DISABLE | INC/DEC | WORD/BYTE |

|       |              |            | ENABLE    | VALUE     | INC/DEC |         |           |

Figure 2-3. Output FIFO Control Register

## CAUTION:

There must be one instruction between the write to the output FIFOs low address and the first write to \*outN. Therefore, it is recommended that outN-lo be written before outN-hi. The write to outN-hi insures that this requirement is met. If only the outNlo value is being changed, it is still necessary to have one additional instruction before the first write to \*outN.

When writing bytes or words to VRAM through an output FIFO, a byte or word can be skipped over by writing to outN + + instead of \*outN. When the values are written to VRAM, any byte or word that was skipped will retain its original value in VRAM, and its value is not altered by the VRAM write. This can be used when writing a series of pixels, some of which are "transparent", allowing whatever was behind them to show through.

If the microcode routine attempts to write a value to a full output FIFO, the processor is frozen prior to the execution of the instruction. The processor remains frozen until the FIFO has a chance to write one of the buffered quad words to VRAM. At that point, the processor is released from the frozen state, and the instruction that writes the value is executed. When the processor is frozen, waiting for a particular FIFO that isn't yet ready, that FIFO's VRAM access priority is raised above all other FIFOs.

## **Statistical Decoder**

{stat-lo, stat-hi, stat-c, stat-ram, \*stat, \*stat#}

The Statistical Decoder (also referred to as the Huffman Decoder) is a specialized input channel that can read a variable-length bit sequence from VRAM and convert it into a fixed-length bit sequence that is read by the microcode processor. In image compression, as well as in other applications such as text compression, certain values occur more frequently than others. A means of compressing this data is to use fewer bits to encode more frequently occurring values and more bits to encode less frequently occurring values. This type of encoding results in a variable-length sequence in which the length of a symbol (the group of bits used to encode a single value) can range for example, from one bit to sixteen bits. The statistical code that the statistical decoder can decode is of either of the two forms:

| 0x              |    | 1x             |

|-----------------|----|----------------|

| 10x             |    | 01x            |

| 110xxx          |    | 001xxx         |

| 1110xxxxx       |    | 0001xxxxx      |

|                 | or |                |

| 11111110xxxxxx  |    | 00000001xxxxxx |

| 111111110xxxxxx |    | 00000001xxxxxx |

| •••             |    | •••            |

Each symbol of a given length (one per line as shown here) consists of a run-in sequence followed by some number of x-bits. The run-in sequence is defined as a series of zero or more ONEs followed by a ZERO or, as in the code on the right above, zero or more ZEROs followed by a ONE. The remainder of this description will use examples of the code on the left. A bit in the decoder's control register determines the polarity of the run-in sequence bits.

In the example on the left, there would be two symbols of length two: 00 and 01. Each x-bit can take on a ZERO or ONE value. The number of x-bits following a run-in sequence can range from zero to six. Since the goal, in general, is to have a few short codes and a larger number of long codes, typically, codes with fewer run-in bits will have fewer x's following. However, this is not a hardware constraint. A code of this form is completely described by a code description table indicating: for each length of run-in sequence. R = the number of ONEs in the run-in. and how many x-bits follow the ZERO. The value of R is used as an index into the code description table. Due to the hardware implementation, the number actually stored in the table is 2x, where x is the number of x-bits.

For the example above, the corresponding code description values are given in Table 2-2.

| Table | 2-2. | Sample | Code | Description | Table |

|-------|------|--------|------|-------------|-------|

|-------|------|--------|------|-------------|-------|

| R | X | 2 <sup>x</sup> (dec.) | 2×(bin.) |

|---|---|-----------------------|----------|

| 0 | 1 | 2                     | 000 0010 |

| 1 | 1 | 2                     | 000 0010 |

| 2 | 3 | 8                     | 000 1000 |

| 4 | 5 | 32                    | 010 0000 |

|   |   |                       |          |

| 7 | 6 | 64                    | 100 0000 |

Note that the table only goes up to symbols with seven ONEs in the run-in. For symbols with more than seven ONEs, the value of X and 2<sup>x</sup> for seven ONEs is used for all symbols having seven or more ONEs in the run-in sequence. For example, in the code above a symbol with eight or more ONEs in the run-in sequence has six x-bits following the ZERO, which is the same as symbols having seven ONEs.

For each different symbol, including all symbols of the same run-in length with different x-bit values, the decoder generates a unique fixed-length, 16-bit value. Some of the decoded values for the sample code given above are provided in Table 2-3.

| Symbol*           | Decoded Value |

|-------------------|---------------|

| 00                | 0             |

| 01                | 1             |

| 10 <b>0</b>       | 2             |

| 101               | 3             |

| 110 <b>000</b>    | 4             |

| 110 <b>001</b>    | 5             |

| 110 <b>010</b>    | 6             |

|                   |               |

| 110 <b>111</b>    | 11            |

| 1110 <b>00000</b> | 12            |

|                   |               |

| 1110 <b>11111</b> | 43            |

|                   |               |

Table 2-3. Decoded Values

\*The x-bits of the symbol are in boldface for clarity

The algorithm for generating a decoded value from a symbol is as follows: all symbols of a given run-in length are assigned a base value, B; the value corresponding to a particular symbol is equal to B plus the binary value of the x-bits in the symbol. The base value B for a symbol with a run-in length of R is calculated by:

$B(R) = SUM[2^{X(r)}]$  with r = 0 to R - 1,

where X(r) corresponds to the X value in the table entry corresponding to R = r.

For example, in the above code: B(0) = 0, B(0) is always zero B(1) = 0 + 2 = 2 B(2) = 0 + 2 + 2 = 4 B(3) = 0 + 2 + 2 + 8 = 12B(4) = 0 + 2 + 2 + 8 + 32 = 44

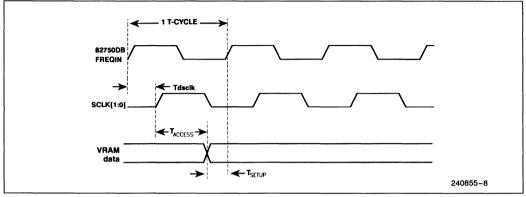

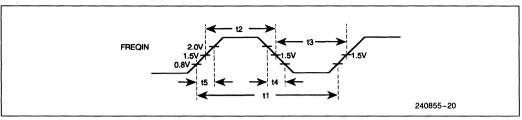

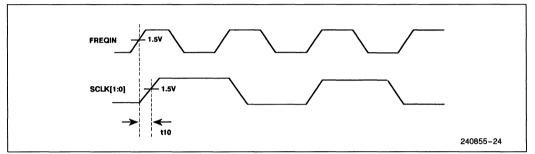

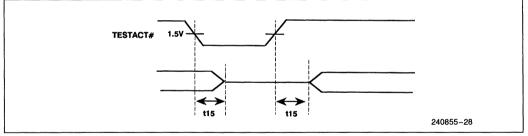

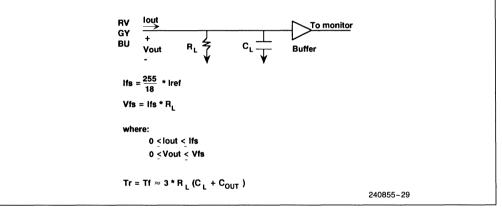

This is one of the reasons that the table holds  $2^X$  instead of X. The calculation of B(R) are easier to implement in logic.