# **Memory Products**

int<sub>el</sub>.

Founded in 1968 to pursue the integration of large numbers of transistors onto tiny silicon chips, Intel's history has been marked by a remarkable number of scientific breakthroughs and innovations. In 1971, Intel introduced the 4004, the first microprocessor. Containing 2300 transistors, this first commercially-available computer on a chip is considered primitive compared with today's million-plus transistor products.

Innovations such as the microprocessor, the erasable programmable read-only memory (EPROM) and the dynamic random access memory (DRAM) revolutionized electronics by making integrated circuits the mainstay of both consumer and business computing products.

Over the last two and a half decades, Intel's business has evolved and today the company's focus is on delivering an extensive line of component, module and system-level building block products to the computer industry. The company's product line covers a broad spectrum, and includes microprocessors, flash memory, microcontrollers, a broad line of PC enhancement and local area network products, multimedia technology products, and massively parallel supercomputers. Intel's 32-bit X86 architecture, represented by the Intel386™ and Intel486™ microprocessor families, are the de facto standard of modern business computing and installed in millions of PCs worldwide.

Intel has over 25,000 employees located in offices and manufacturing facilities around the world. Today, Intel is the largest semiconductor company in the United States and the second largest in the world.

## **U.S. and CANADA LITERATURE ORDER FORM**

| NAME:                                                              |                                                                               |                                               |                                |                            |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------|----------------------------|

| COMPANY:                                                           |                                                                               |                                               |                                | •                          |

| ADDRESS:                                                           |                                                                               |                                               |                                |                            |

| CITY:                                                              | 8                                                                             | STATE:                                        | ZIP: _                         |                            |

| COUNTRY:                                                           |                                                                               |                                               |                                |                            |

| PHONE NO.: _(                                                      | <b>)</b> · .                                                                  |                                               |                                |                            |

| ORDER NO.                                                          | TITLE                                                                         | QTY.                                          | PRICE                          | TOTAL                      |

|                                                                    |                                                                               | ×                                             |                                |                            |

|                                                                    |                                                                               |                                               | =                              | =                          |

|                                                                    |                                                                               |                                               | =                              | =                          |

|                                                                    |                                                                               |                                               | =                              | =                          |

| f,                                                                 |                                                                               | ×                                             | · .                            | <b>=</b>                   |

|                                                                    |                                                                               | ×                                             |                                | =                          |

|                                                                    |                                                                               | ×                                             | =                              |                            |

|                                                                    |                                                                               | ×                                             | =                              | =                          |

|                                                                    |                                                                               | ×                                             | :                              | =                          |

|                                                                    |                                                                               | ×                                             |                                | =                          |

|                                                                    |                                                                               |                                               | Subtotal                       |                            |

|                                                                    |                                                                               | Must<br>Local                                 | Add Your<br>Sales Tax          |                            |

| Include postage: Must add 15% of Subtotal and Canada postage. (20% | to cover U.S.                                                                 | <del></del>                                   | Postage _                      |                            |

|                                                                    | <del></del>                                                                   | :                                             |                                | <del> </del>               |

| Pay by check, money ord<br>accept VISA, MasterCard<br>delivery.    | der, or include company purchase orde<br>or American Express. Make payment to | er with this form (\$<br>o Intel Literature S | 6200 minimur<br>ales. Allow 2- | n). We also<br>3 weeks for |

| ☐ VISA ☐ MasterCard                                                | ☐ American Express Expiration Dat                                             | e                                             |                                |                            |

| Account No                                                         |                                                                               |                                               |                                |                            |

| Signature                                                          | ; · · · · · · · · · · · · · · · · · · ·                                       |                                               |                                |                            |

| Mail To: Intel Literature S<br>P.O. Box 7641                       | should use the In                                                             | ustomers outside<br>iternational order for D  | orm on the n                   |                            |

For phone orders in the U.S. and Canada Call Toll Free: (800) 548-4725

Prices good until 12/31/93. Source HB

## INTERNATIONAL LITERATURE ORDER FORM

| NAME:        |       |        |                           |                                       |

|--------------|-------|--------|---------------------------|---------------------------------------|

| COMPANY:     |       |        |                           |                                       |

| ADDRESS:     |       |        |                           |                                       |

| CITY:        |       | STATE: | ZIP:                      |                                       |

| COUNTRY:     |       |        |                           |                                       |

| PHONE NO.: ( |       |        |                           | · · · · · · · · · · · · · · · · · · · |

| ORDER NO.    | TITLE | QTY.   | PRICE                     | TOTAL                                 |

|              |       | ×      |                           |                                       |

|              |       | ×      |                           | =                                     |

|              |       | ×      |                           | =                                     |

|              |       | ×      | 1 .                       | =                                     |

|              | •     | ×      |                           | =                                     |

|              |       | ×      |                           | <b>=</b>                              |

|              |       | ×      |                           | =                                     |

|              |       | ×      | 2                         | =                                     |

|              |       | ×      |                           | =                                     |

|              |       | ×      |                           | =                                     |

|              |       |        | Subtotal _                |                                       |

| 7 - 4        | 1     |        | t Add Your<br>Sales Tax _ |                                       |

|              |       |        | Total _                   | · · · · · · · · · · · · · · · · · · · |

#### **PAYMENT**

Cheques should be made payable to your *local* Intel Sales Office (see inside back cover).

Other forms of payment may be available in your country. Please contact the Literature Coordinator at your *local* Intel Sales Office for details.

The completed form should be marked to the attention of the LITERATURE COORDINATOR and returned to your *local* Intel Sales Office.

# **MEMORY PRODUCTS**

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

| 376™             | i750®         | MAPNET™                     |

|------------------|---------------|-----------------------------|

| Above™           | i860™         | Matched™                    |

| ActionMedia®     | i960®         | MCS®                        |

| BITBUS™          | Intel287™     | Media Mail™                 |

| Code Builder™    | Intel386™     | NetPort™                    |

| DeskWare™        | Intel387™     | NetSentry™                  |

| Digital Studio™  | Intel486™     | OpenNET™                    |

| DVI®             | Intel487™     | OverDrive™                  |

| EtherExpress™    | Intel®        | Paragon™                    |

| ETOX™            | intel inside® | Pentium™                    |

| ExCA™            | Intellec®     | ProSolver™                  |

| Exchange and Go™ | iPSC®         | RapidCAD™                   |

| FaxBACK™         | iRMX®         | READY-LAN™                  |

| FlashFile™       | iSBC®         | Reference Point®            |

| Grand Challenge™ | iSBX™         | RMX/80™                     |

| j®               | iWARP™        | RxServer™                   |

| ICE™             | LANDesk™      | SatisFAXtion®               |

| iLBX™            | LANPrint®     | Snapln 386™                 |

| Inboard™         | LANProtect™   | Storage Broker <sup>™</sup> |

| i287™            | LANSelect®    | SugarCube™                  |

| i386™            | LANShell®     | The Computer Inside™        |

| i387™            | LANSight™     | TokenExpress™               |

| i486™            | LANSpace®     | Visual Edge™                |

| .1487™           | LANSpool®     | WYPIWYF®                    |

|                  |               |                             |

MDS is an ordering code only and is not used as a product name or trademark. MDS is a registered trademark of Mohawk Data Sciences Corporation.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

## **DATA SHEET DESIGNATIONS**

Intel uses various data sheet markings to designate each phase of the document as it relates to the product. The marking appears in the upper, right-hand corner of the data sheet. The following is the definition of these markings:

| Data Sheet Marking   | Description                                                                                                                                                                                    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview      | Contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product becomes available. |

| Advanced Information | Contains information on products being sampled or in the initial production phase of development.*                                                                                             |

| Preliminary          | Contains preliminary information on new products in production.*                                                                                                                               |

| No Marking           | Contains information on products in full production *                                                                                                                                          |

<sup>\*</sup>Specifications within these data sheets are subject to change without notice. Verify with your local Intel sales office that you have the latest data sheet before finalizing a design.

# intel<sub>®</sub>

| Memory | Technologies |

|--------|--------------|

|        |              |

Flash Overview

**Flash Memory Components**

Flash Memory Systems

**Automotive Memory**

)

3

5

## **Table of Contents**

| Alphanumeric Index                                                         | xiii          |

|----------------------------------------------------------------------------|---------------|

| CHAPTER 1                                                                  |               |

| Memory Technologies                                                        |               |

| Intel Memory Technologies                                                  | 1-1           |

| CHAPTER 2                                                                  |               |

| Flash Overview                                                             |               |

| Flash Overview                                                             | 2-1           |

|                                                                            | 2-1           |

| CHAPTER 3                                                                  |               |

| Flash Memory Components                                                    |               |

| DATA SHEETS                                                                |               |

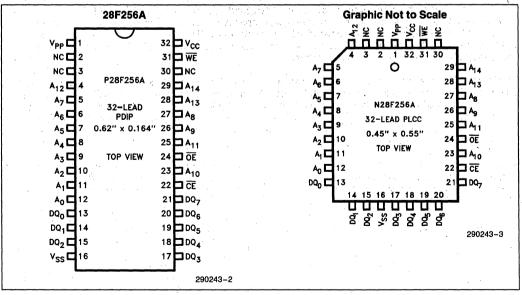

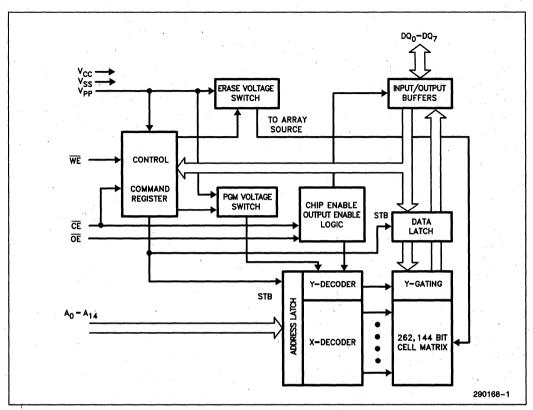

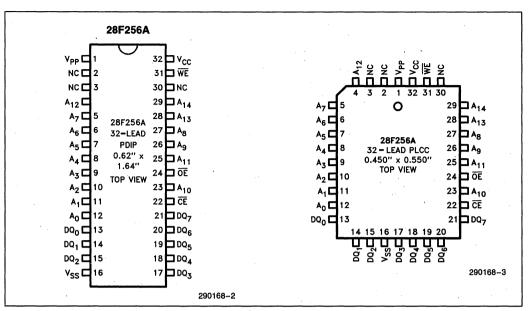

| 28F256A 256K (32K x 8) CMOS Flash Memory                                   | 3-1           |

| 28F512 512K (64K x 8) CMOS Flash Memory                                    | 3-26          |

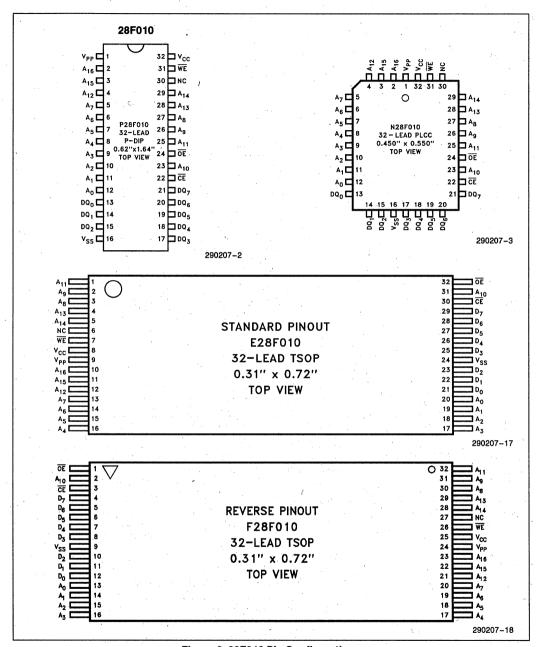

| 28F010 1024K (128K x 8) CMOS Flash Memory                                  | 3-54          |

| 28F020 2048K (256K x 8) CMOS Flash Memory                                  | 3-84<br>3-117 |

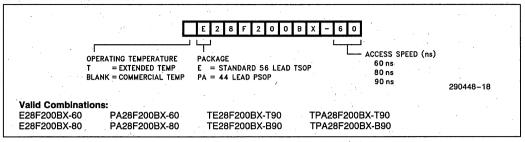

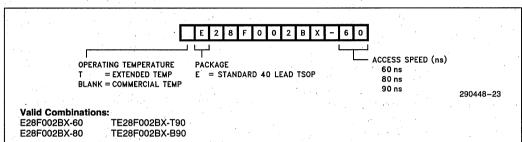

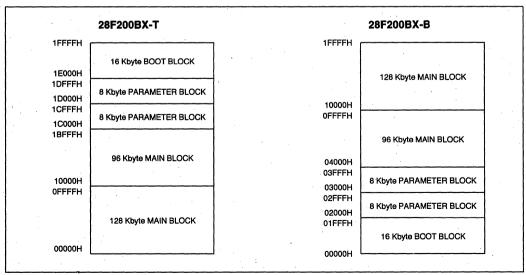

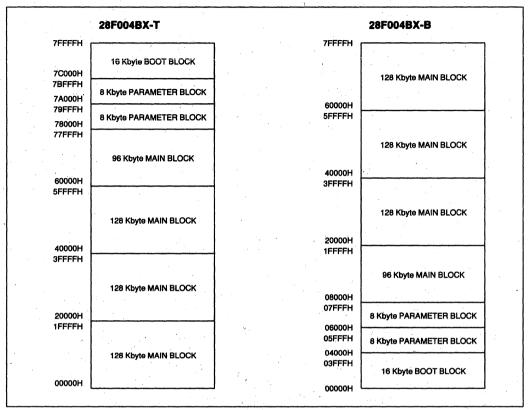

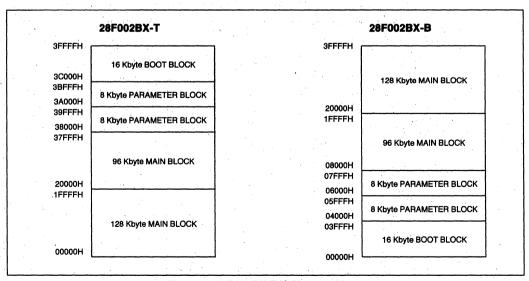

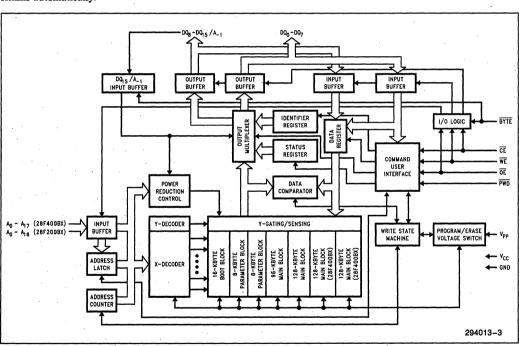

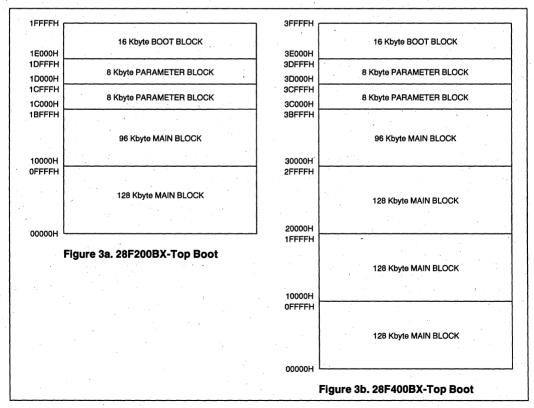

| 28F200BX-T/B, 28F002BX-T/B 2 Mbit (128K x 16, 256K x 8) Boot Block Flash   | 3-117         |

| Memory Family                                                              | 3-146         |

| 28F200BX-TL/BL, 28F002BX-TL/BL 2 Mbit (128K x 16, 256K x 8) Low Power Boot | J-140         |

| Block Flash Memory Family                                                  | 3-192         |

| 28F400BX-T/B, 28F004BX-T/B 4 Mbit (256K x 16, 512K x 8) Boot Block Flash   | 0 102         |

| Memory Family                                                              | 3-233         |

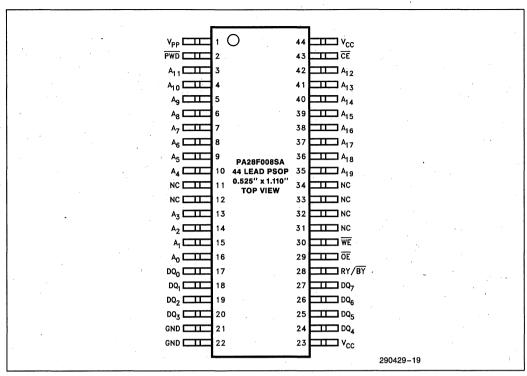

| 28F008SA 8 Mbit (1 Mbit x 8) Flash Memory                                  | 3-281         |

| APPLICATION NOTÈS                                                          |               |

| AP-316 Using Flash Memory for In-System Reprogrammable Nonvolatile Storage | 3-309         |

| AP-341 Designing an Updatable BIOS Using Flash Memory                      | 3-354         |

| AP-357 Power Supply Solutions for Flash Memory                             | 3-397         |

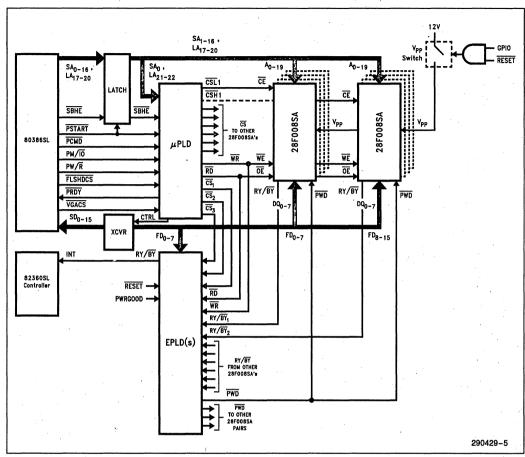

| AP-359 28F008SA Hardware Interfacing                                       | 3-432         |

| AP-360 28F008SA Software Drivers                                           | 3-443         |

| AP-363 Extended Flash Bios Design For Portable Computers                   | 3-465         |

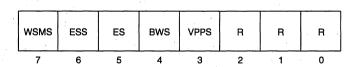

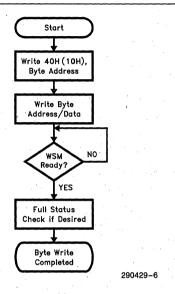

| AP-364 28F008SA Automation and Algorithms                                  | 3-494         |

| AP-371 Designing Flash Card Readiness Into Today's System                  | 3-508         |

| AB-29 Flash Memory Applications in Laser Printers                          | 3-516         |

| ENGINEERING REPORTS ER-20 ETOX™ II Flash Memory Technology                 | 3-523         |

|                                                                            | 3-528         |

| ER-26 The Intel 28F001BX-T and 28F001BX-B Flash Memories                   | 3-551         |

| ER-27 The Intel 28F008SA Flash Memory                                      | 3-566         |

| ER-28 ETOXTM III Flash Memory Technology                                   | 3-591         |

| ER-29 The Intel 2/4 Mbit Boot Block Flash Memory Family                    |               |

| RELIABILITY REPORTS                                                        |               |

| RR-60 ETOX™ II Flash Memory Reliability Data Summary                       | 3-633         |

| RR-69 28F008SA Reliability Summary                                         | 3-670         |

| ARTICLE REPRINTS                                                           |               |

| AR-470 A 90 ns 100K Erase/Program Cycle Megabit Flash Memory               | 3-678         |

| AR-472 The Memory Driver                                                   | 3-682         |

| AR-478 Flash Memories: The Best of Two Worlds                              | 3-683         |

| AR-486 Flash Outshines ROM & EPROM                                         |               |

| AR-491 Memory Breakthrough Drives Miniaturization                          | 3-694         |

| AR-493 Look Out EPROMs, Here Comes Flash                                   | 3-696         |

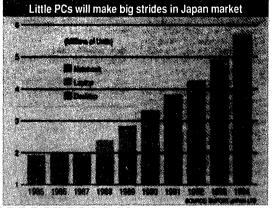

| AR-494 Laptop Vendors Join the Flash Bandwagon                             | 3-700         |

| AR-495 Store Data in a Flash                                               | 3-702         |

# Table of Contents (Continued)

| AR-497 Designing with Flash MemorySUPPORT TOOLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-708 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Boot Block Flash: The Next Generation White Paper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-718 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| Intel FlashFile™ Memory-The Key to Diskless Mobile PCs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-722 |

| SOP Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-728 |

| Intel Blocked Flash Memory 28F001BX-B/28F001BX-T Product Brief Intel 2 Megabit Boot Block Flash Memory 28F200BX-T/B, 28F002BX-T/B Product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-734 |

| Brief                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-736 |

| Intel 4 Megabit Boot Block Flash Memory 28F400BX-T/B, 28F004BX-T/B Product Brief                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-738 |

| Intel 28F008SA (8 Mbit) FlashFile™ Memory Product Brief                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3-740 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3-740 |

| Intel Flash Memory Evaluation Kit II Product BriefIntel 28F008SA FlashFile Memory Evaluation Module (D,FLASHEVAL4) Product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| Brief                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-743 |

| Intel 28F400BX/28F004BX Flash Memory Evaluation Module (D,FLASHEVAL5) Product Brief                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-744 |

| CHAPTER 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| Flash Memory Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| DATA SHEETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

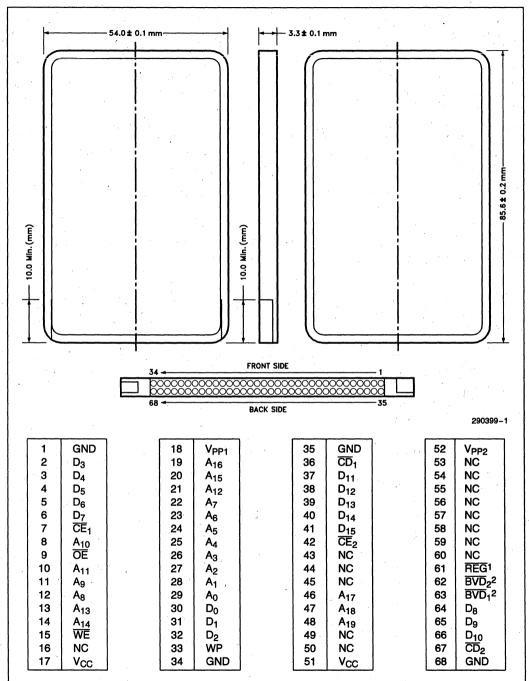

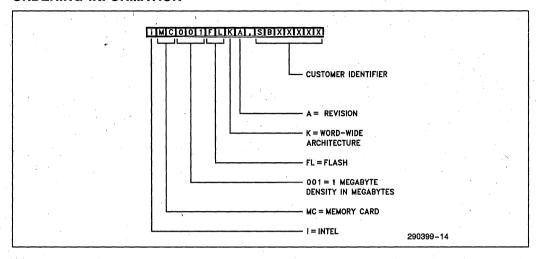

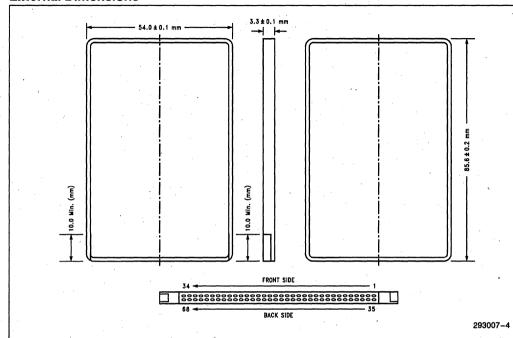

| iMC001FLKA 1-Megabyte Flash Memory Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1   |

| iMC002FLKA 2-Mbyte Flash Memory Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-31  |

| iMC004FLKA 4-Megabyte Flash Memory Card                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-61  |

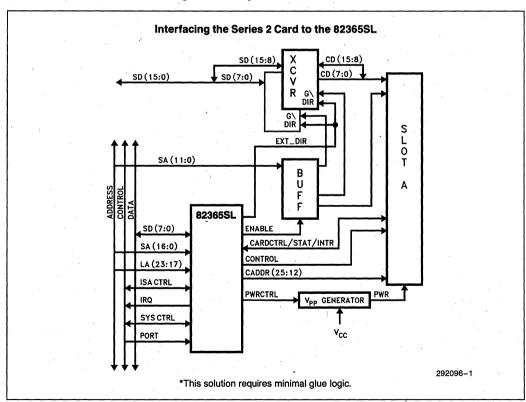

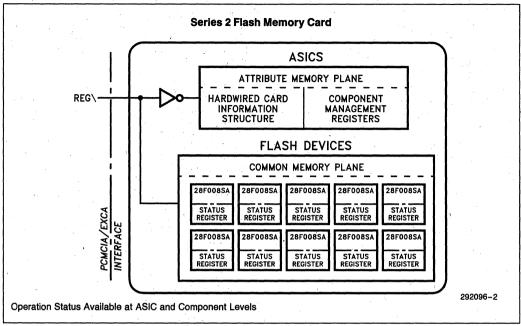

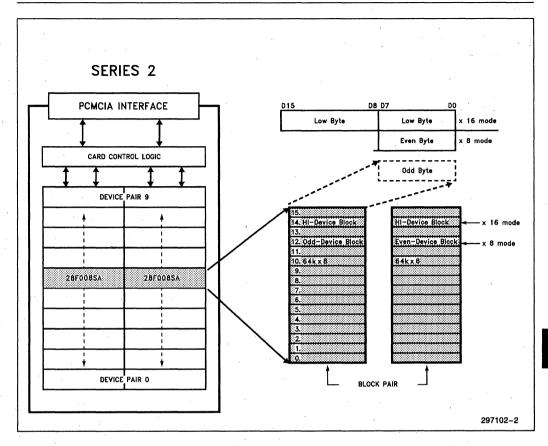

| Series 2 Flash Memory Cards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-91  |

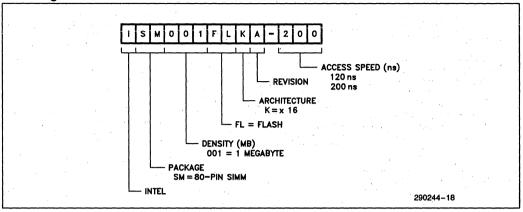

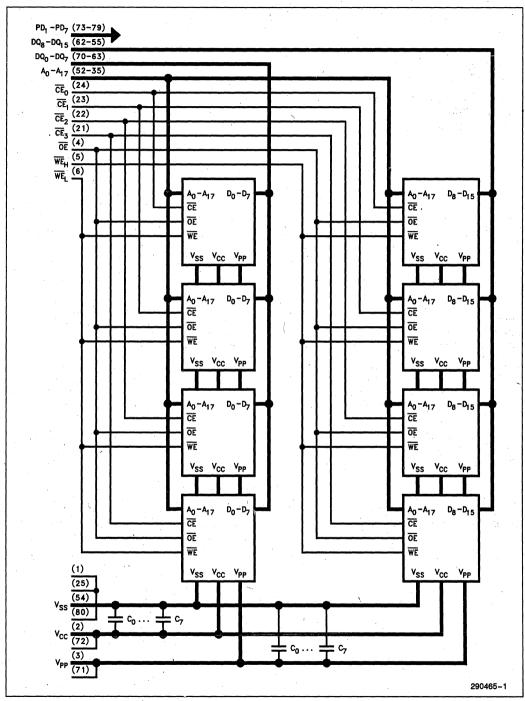

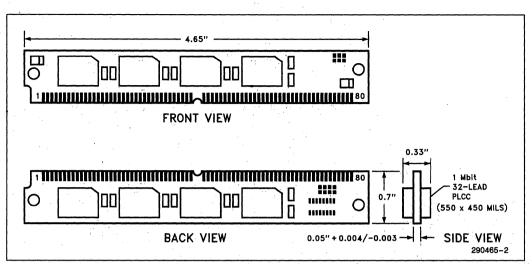

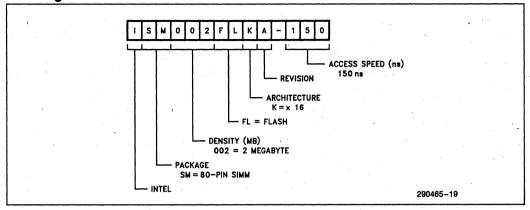

| iSM001FLKA 1 Mbyte (512K x 16) CMOS Flash SIMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-129 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-129 |

| iSM002FLKA 2 Mbyte (1024K x 16) CMOS Flash SIMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-103 |

| APPLICATION NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4 400 |

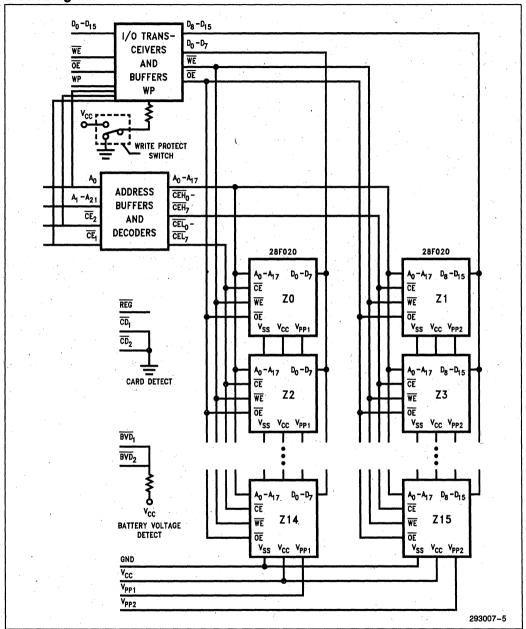

| AP-343 Solutions for High Density Applications Using Intel Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-199 |

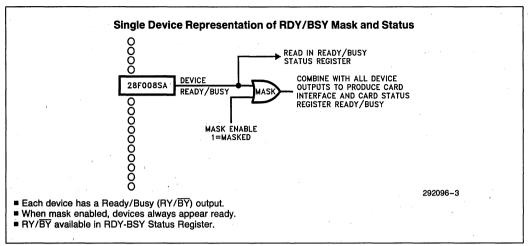

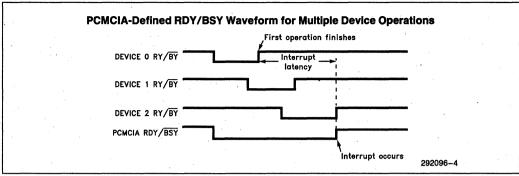

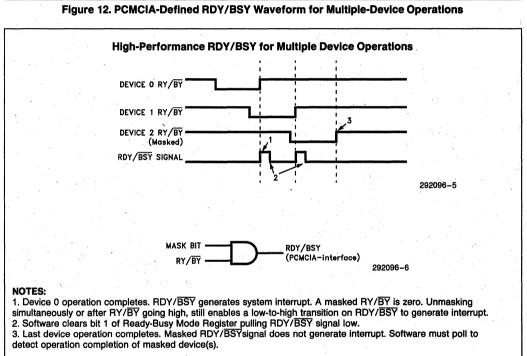

| AP-361 Implementing the Integrated Registers of the Series 2 Flash Memory Card.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-267 |

| RELIABILITY REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |