# intel Multimedia and Supercomputing Processors

Intel Corporation is a leading supplier of microcomputer components, modules and systems. When Intel first introduced the microprocessor in 1971, it created the era of the microcomputer. Today, Intel architectures are considered world standards. Intel products are used in a wide variety of applications including, embedded systems such as automobiles, avionics systems and telecommunications equipment, and as the CPU in personal computers, network servers and supercomputers. Others bring enhanced capabilities to systems and networks. Intel's mission is to deliver quality products through leading-edge technology.

# MULTIMEDIA AND SUPERCOMPUTING PROCESSORS

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

376, Above, ActionMedia, BITBUS, Code Builder, DeskWare, Digital Studio, DVI, EtherExpress, ETOX, FaxBACK, Grand Challenge, i, i287, i386, i387, i486, i487, i750, i860, i960, ICE, iLBX, Inboard, Intel, Intel287, Intel386, Intel387, Intel486, Intel487, intel inside., Intellec, iPSC, iRMX, iSBC, iSBX, iWARP, LANPrint, LANSelect, LANShell, LANSight, LANSpace, LANSpool, MAPNET, Matched, MCS, Media Mail, NetPort, NetSentry, OpenNET, PRO750, ProSolver, READY-LAN, Reference Point, RMX/80, SatisFAXtion, SnapIn 386, Storage Broker, SugarCube, The Computer Inside., TokenExpress, Visual Edge, and WYPIWYF.

MDS is an ordering code only and is not used as a product name or trademark. MDS is a registered trademark of Mohawk Data Sciences Corporation.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect. IL 60056-7641

## **INTEL SERVICE**

#### INTEL'S COMPLETE SUPPORT SOLUTION WORLDWIDE

Intel Service is a complete support program that provides Intel customers with hardware support, software support, customer training, and consulting services. For detailed information contact your local sales offices.

Service and support are major factors in determining the success of a product or program. For Intel this support includes an international service organization and a breadth of service programs to meet a variety of customer needs. As you might expect, Intel service is extensive. It can start with On-Site Installation and Maintenance for Intel and non-Intel systems and peripherals, Repair Services for Intel OEM Modules and Platforms, Network Operating System support for Novell NetWare and Banyan VINES software, Custom Integration Services for Intel Platforms, Customer Training, and System Engineering Consulting Services. Intel maintains service locations worldwide. So wherever you're using Intel technology, our professional staff is within close reach.

#### ON-SITE INSTALLATION AND MAINTENANCE

Intel's installation and maintenance services are designed to get Intel and Intel-based systems and the networks they use up and running—fast. Intel's service centers are staffed by trained and certified Customer Engineers throughout the world. Once installed, Intel is dedicated to keeping them running at maximum efficiency, while controlling costs.

#### REPAIR SERVICES FOR INTEL OEM MODULES AND PLATFORMS

Intel offers customers of its OEM Modules and Platforms a comprehensive set of repair services that reduce the costs of system warranty, maintenance, and ownership. Repair services include module or system testing and repair, module exchange, and spare part sales.

#### NETWORK OPERATING SYSTEM SUPPORT

An Intel software support contract for Novell NetWare or Banyan VINES software means unlimited access to troubleshooting expertise any time during contract hours—up to seven days per week, twenty-four hours per day. To keep networks current and compatible with the latest software versions, support services include access to minor releases and "patches" as made available by Novell and Banyan.

#### **CUSTOM SYSTEM INTEGRATION SERVICES**

Intel Custom System Integration Services enable resellers to order completely integrated systems assembled from a list of Intel386™ and Intel486™ microcomputers and validated hardware and software options. These services are designed to complement the reseller's own integration capabilities. Resellers can increase business opportunities, while controlling overhead and support costs.

#### **CUSTOMER TRAINING**

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to five days a limited number of individuals learn more in a single workshop than in weeks of self-study. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, BITBUS<sup>TM</sup>, and LAN applications.

#### SYSTEM ENGINEERING CONSULTING

Intel provides field system engineering consulting services for any phase of your development or application effort. You can use our system engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training and customizing an Intel product to providing technical and management consulting. Working together, we can help you get a successful product to market in the least possible time.

# **DATA SHEET DESIGNATIONS**

Intel uses various data sheet markings to designate each phase of the document as it relates to the product. The marking appears in the upper, right-hand corner of the data sheet. The following is the definition of these markings:

| Data Sheet Marking   | Description                                                                                                                                                                                    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Preview      | Contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product becomes available. |

| Advanced Information | Contains information on products being sampled or in the initial production phase of development.*                                                                                             |

| Preliminary          | Contains preliminary information on new products in production.*                                                                                                                               |

| No Marking           | Contains information on products in full production.*                                                                                                                                          |

<sup>\*</sup>Specifications within these data sheets are subject to change without notice. Verify with your local Intel sales office that you have the latest data sheet before finalizing a design.

angten det formålet i signikkligteten med egt. In storre fing bli der flatt av ørett mede middels det signikkl I meden storrad med ett skalet ett skalet flatt og det finn her ett eftet bestindt flatt i med med ett skalet I flatt skalet finn her klim i film ett skalet here på det ett skalet skalet ett kjelle ett skalet bestind dem I fan det flatt skalet skalet skalet ett skalet skalet skalet skalet skalet skalet skalet skalet ett skalet skalet

i750<sup>TM</sup> Microprocessor Family

1

i860<sup>TM</sup> Microprocessor Family

i960<sup>TM</sup> Microprocessor Family

Memories and Peripherals

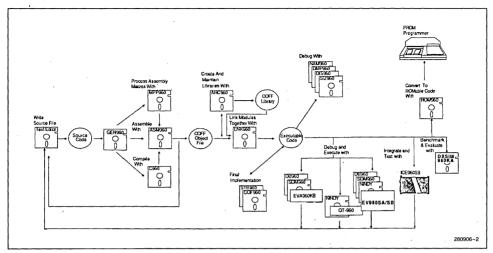

**Development Support Tools**

# **Table of Contents**

| Alphanumeric Index                                                             | X              |

|--------------------------------------------------------------------------------|----------------|

| i750TM MICROPROCESSOR FAMILY                                                   |                |

| Chapter 1                                                                      |                |

| i750™ PROCESSOR DATA SHEETS                                                    |                |

| 82750DB Display Processor                                                      | 1-1            |

| 82750PB Pixel Processor                                                        | 1-57           |

| 1860™ MICROPROCESSOR FAMILY                                                    |                |

| Chapter 2                                                                      | **             |

| i860™ PROCESSOR DATA SHEETS AND APPLICATION NOTES                              |                |

| i860 XP Microprocessor                                                         | 2-1            |

| i860 XR 64-Bit Microprocessor                                                  | 2-164          |

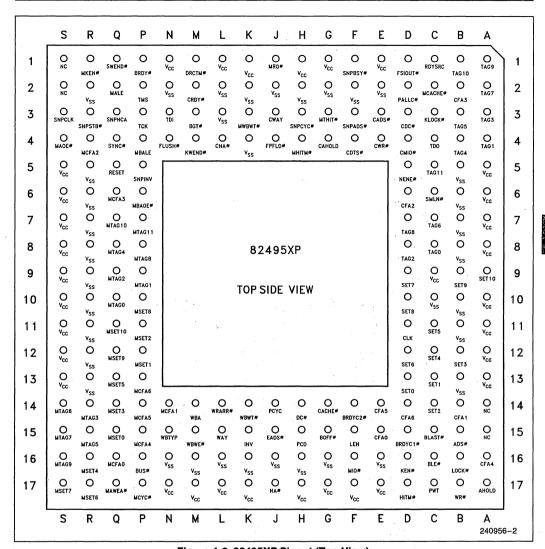

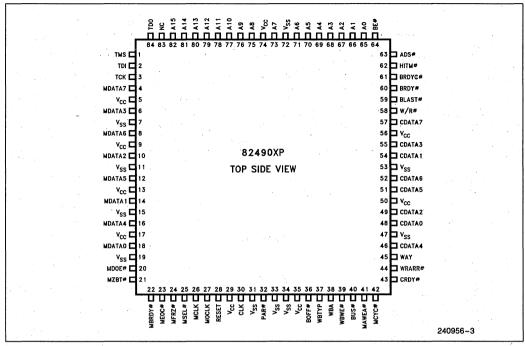

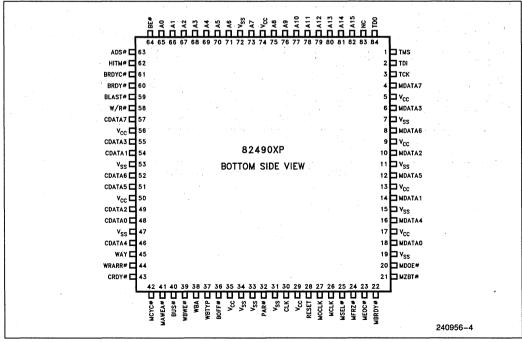

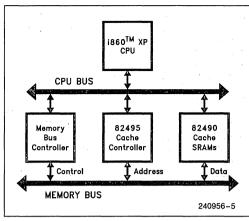

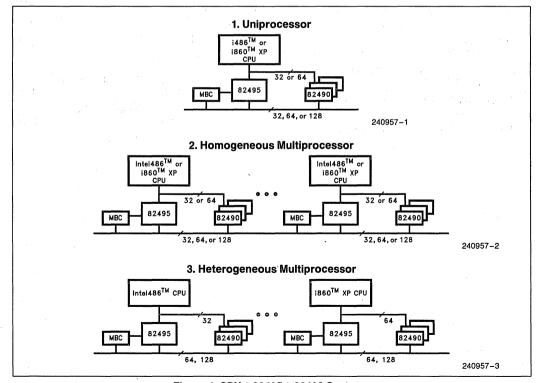

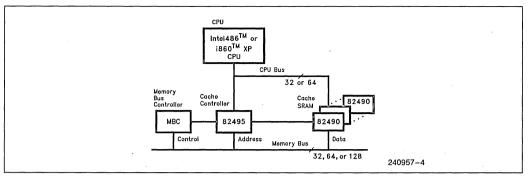

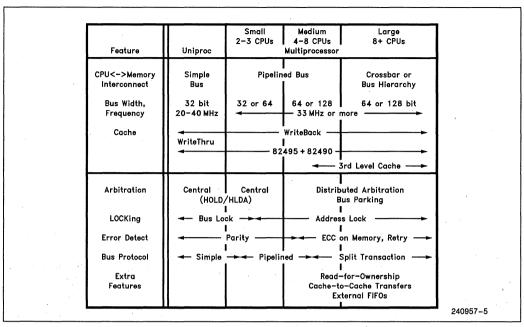

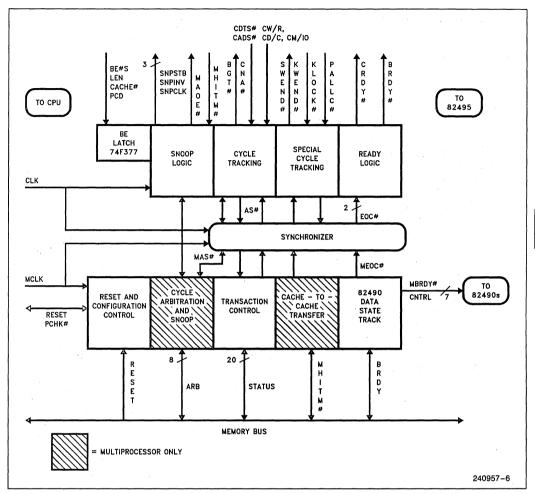

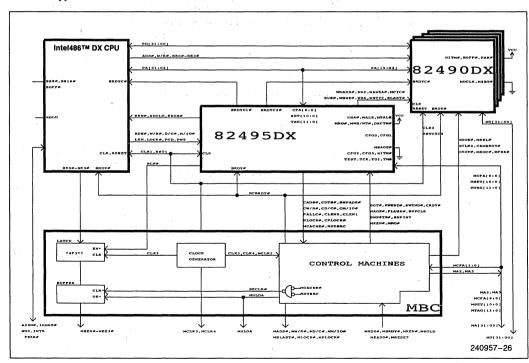

| 82495XP Cache Controller/82490XP Cache RAM                                     | 2-243          |

| AP-434 Using i860 Microprocessor Graphics Instructions for 3-D Rendering       | 2-378          |

| AP-435 Fast Fourier Transforms on the i860 Microprocessor                      | 2-393          |

| AP-452 Designing a Memory Bus Controller for the 82495/82490 Cache             | 2-447          |

| i960™ MICROPROCESSOR FAMILY                                                    |                |

| Chapter 3                                                                      |                |

| i960™ PROCESSOR PRODUCT OVERVIEWS AND DATA SHEETS                              |                |

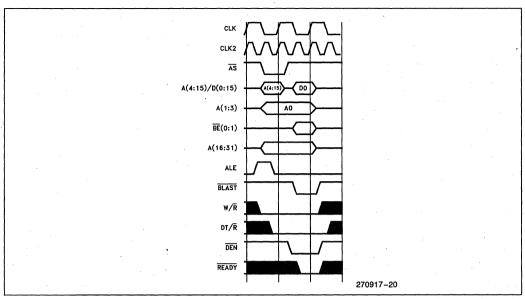

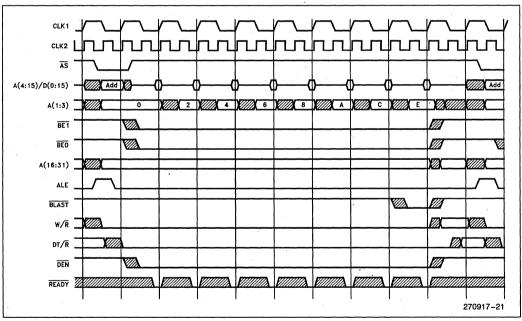

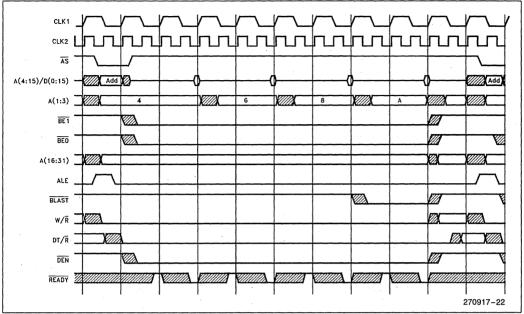

| 80960SA/80960SB Embedded 32-Bit Processors with 16-Bit Burst Data Bus          | 3-1            |

| i960 KA/KB Processor Product Overview                                          | 3-29           |

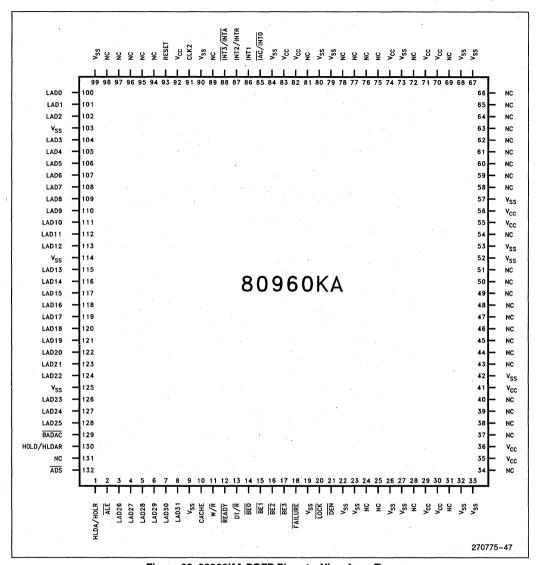

| 80960KA Embedded 32-Bit Processor                                              | 3-34           |

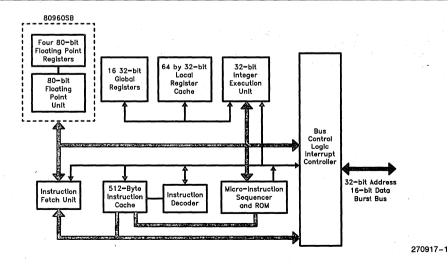

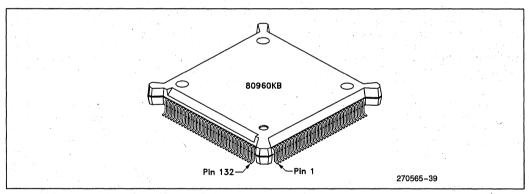

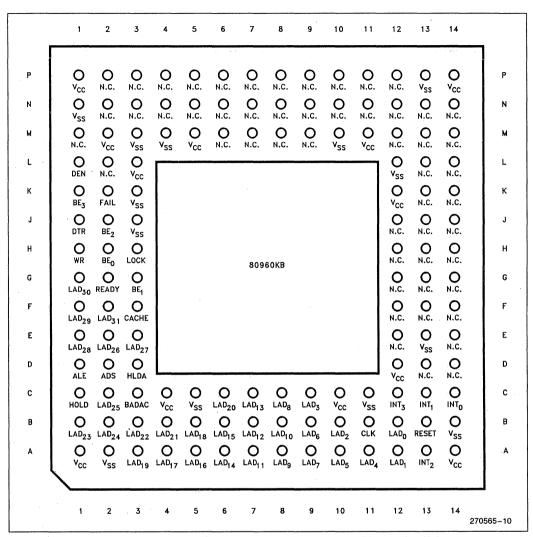

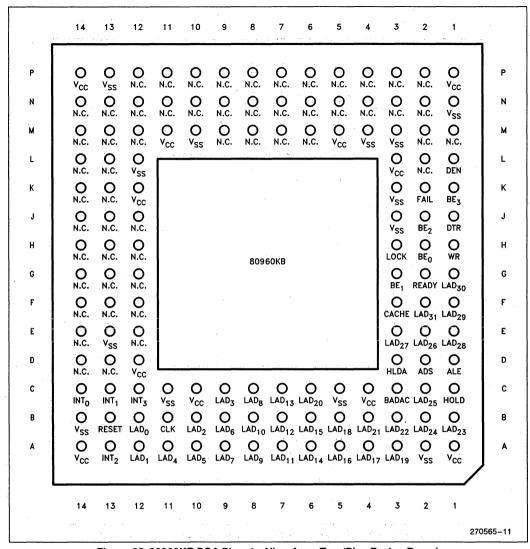

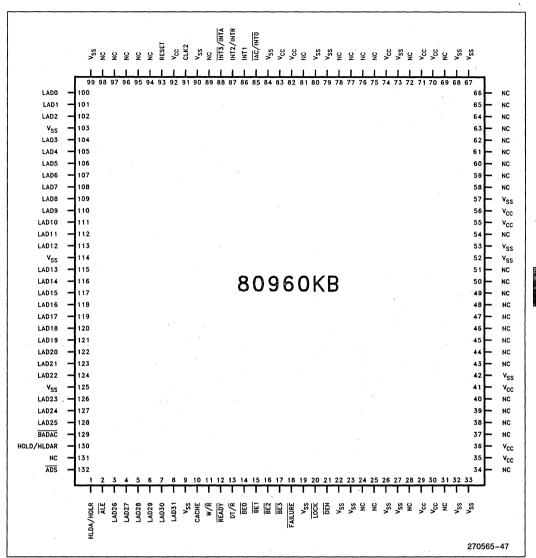

| 80960KB Embedded 32-Bit Processor with Integrated Floating-Point Unit          | 3-81           |

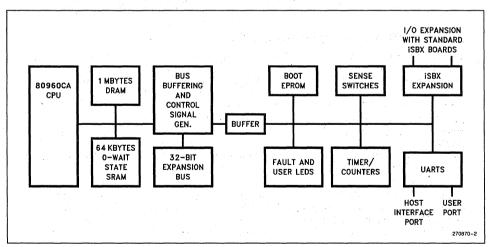

| 80960CA Product Overview                                                       | 3-128          |

| 80960CA-33, -25, -16, 32-Bit High Performance Embedded Processor               | 3-166          |

| i960™ MC Processor Product Overview                                            | 3-233          |

| 80960MC Embedded 32-Bit Microprocessor with Integrated Floating-Point Unit and |                |

| Memory Management Unit                                                         | 3-238<br>3-276 |

|                                                                                | 3-270          |

| MEMORIES AND PERIPHERALS                                                       |                |

| Chapter 4                                                                      |                |

| DATA SHEETS                                                                    |                |

| 85C960 1-Micron CHMOS 80960 K-Series Bus Control microPLD                      | 4-1<br>4-19    |

| 27960CX Pipelined Burst Access 1M (128K x 8) CHMOS EPROM                       | 4-19<br>4-40   |

| 82596CA High-Performance 32-Bit Local Area Network Coprocessor                 | 4-40           |

| · · · · · · · · · · · · · · · · · · ·                                          | 4-55           |

| DEVELOPMENT SUPPORT TOOLS                                                      |                |

| Chapter 5                                                                      |                |

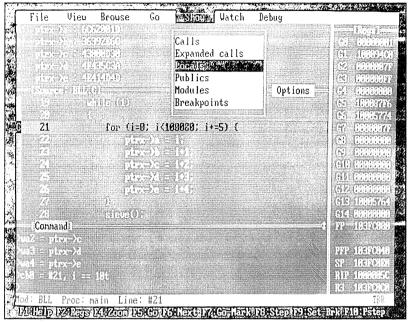

| i960 Family of Software Debuggers                                              | 5-1            |

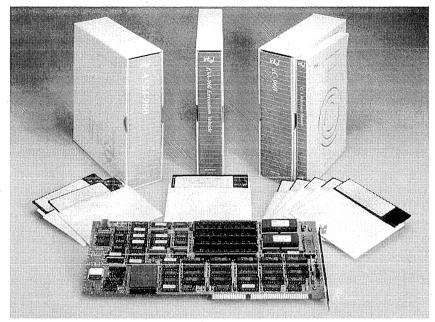

| EXV960MC Execution Vehicle                                                     | 5-6<br>5-8     |

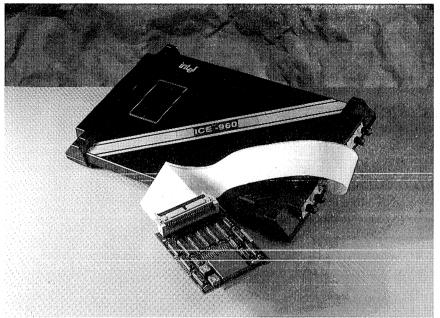

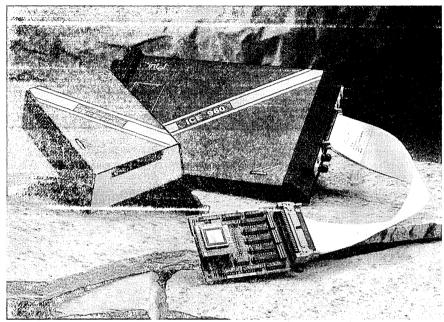

| ICE-960SB and ICE-960KB In-Circuit Emulators                                   | 5-15           |

| ICE-960MC In-Circuit Emulator                                                  | 5-25           |

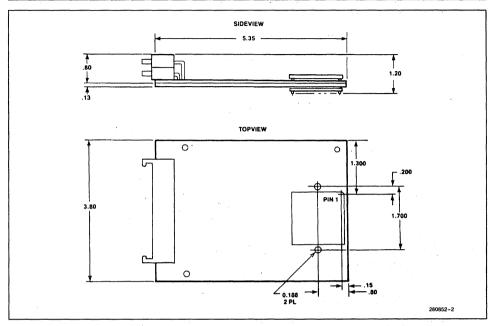

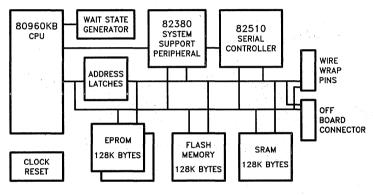

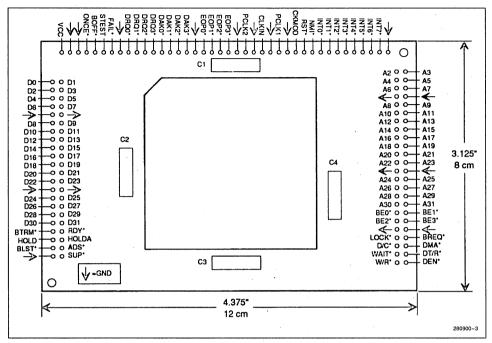

| QT960 Evaluation and Prototyping Board                                         | 5-33           |

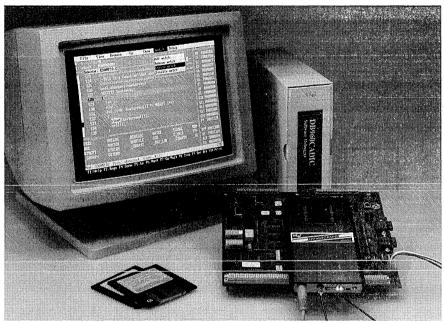

| DB960CADIC In-Circuit Debugger                                                 | 5-36           |

| Intel Development Tools Software Services                                      | 5-41           |

| iRMK 960 Real-Time Kernel                                                      | 5-43           |

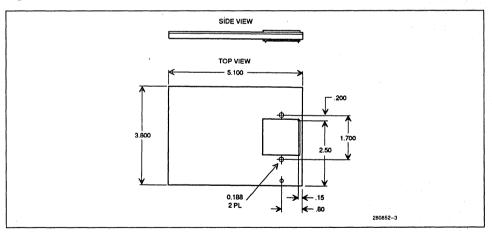

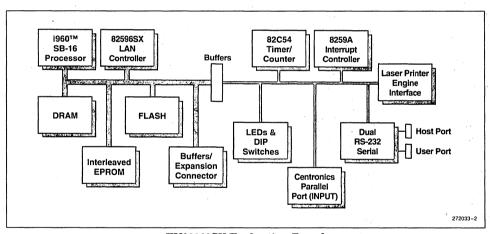

| EV80960CA Evaluation Board                                                     | 5-49           |

| i960 SA/SB Evaluation Board                                                    | 5-52           |

|                                                                                |                |

# **Alphanumeric Index**

| 27960CX Pipelined Burst Access 1M (128K x 8) CHMOS EPROM                       | 4-19  |

|--------------------------------------------------------------------------------|-------|

| 27960KX Burst Access 1M (128K x 8) CHMOS EPROM                                 | 4-40  |

| 80960CA Product Overview                                                       | 3-128 |

| 80960CA-33, -25, -16, 32-Bit High Performance Embedded Processor               | 3-166 |

| 80960KA Embedded 32-Bit Processor                                              | 3-34  |

| 80960KB Embedded 32-Bit Processor with Integrated Floating-Point Unit          | 3-81  |

| 80960MC Embedded 32-Bit Microprocessor with Integrated Floating-Point Unit and |       |

| Memory Management Unit                                                         | 3-238 |

| 80960SA/80960SB Embedded 32-Bit Processors with 16-Bit Burst Data Bus          | 3-1   |

| 80960SA/SB Development Support                                                 | 5-8   |

| 82495XP Cache Controller/82490XP Cache RAM                                     | 2-243 |

| 82596CA High-Performance 32-Bit Local Area Network Coprocessor                 | 4-59  |

| 82750DB Display Processor                                                      | 1-1   |

| 82750PB Pixel Processor                                                        | 1-57  |

| 85C960 1-Micron CHMOS 80960 K-Series Bus Control microPLD                      | 4-1   |

| AP-434 Using i860 Microprocessor Graphics Instructions for 3-D Rendering       | 2-378 |

| AP-435 Fast Fourier Transforms on the i860 Microprocessor                      | 2-393 |

| AP-452 Designing a Memory Bus Controller for the 82495/82490 Cache             | 2-447 |

| DB960CADIC In-Circuit Debugger                                                 | 5-36  |

| EV80960CA Evaluation Board                                                     | 5-49  |

| EXV960MC Execution Vehicle 2.44                                                | 5-6   |

| i860 XP Microprocessor                                                         | 2-1   |

| i860 XR 64-Bit Microprocessor                                                  | 2-164 |

| i960 Family of Software Debuggers                                              | 5-1   |

| i960 KA/KB Processor Product Overview                                          | 3-29  |

| i960™ MC Processor Product Overview                                            | 3-233 |

| i960 SA/SB Evaluation Board                                                    | 5-52  |

| ICE-960MC In-Circuit Emulator                                                  | 5-25  |

| ICE-960SB and ICE-960KB In-Circuit Emulators                                   | 5-15  |

| Intel Development Tools Software Services                                      | 5-41  |

| iRMK 960 Real-Time Kernel                                                      | 5-43  |

|                                                                                |       |

| QT960 Evaluation and Prototyping Board                                         | 5-33  |

# 82750DB DISPLAY PROCESSOR

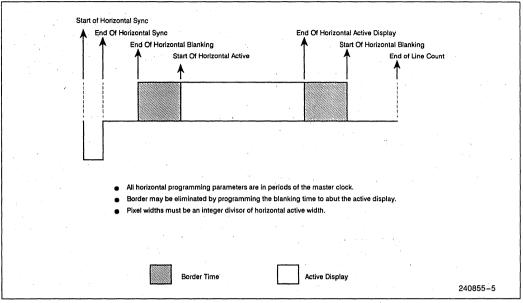

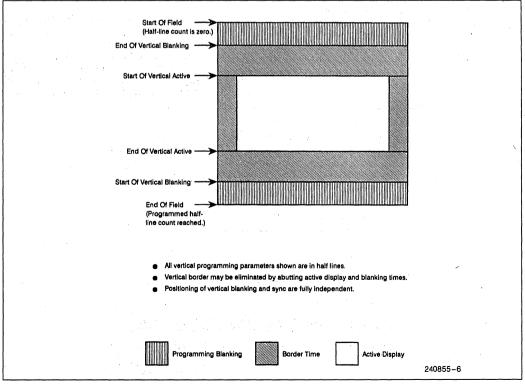

- Programmable Video Timing

- 28 MHz and 45MHz Operating Frequency

- Pixel/Line Address Range to 4096

- Fully Programmable Sync, Equalization, and Serration Components

- Fully Programmable Blanking and Active Display Start and Stop Times

- Genlocking Capability

- Flexible Display Characteristics

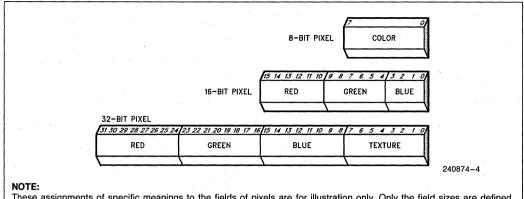

- -8-, Pseudo 16-, 16-, and 32-Bit/Pixel Modes

- Selectable Pixel Widths of 1.0, 1.5, 2.0, 2.5, through 14 Periods of the Input Frequency

- Support Popular Display Resolutions:

VGA, XGA, NTSC, PAL, and SECAM

- On-Chip Triple DAC for Analog RGB/ YUV Output

- Mix Graphics and Video Images on a Pixel by Pixel Basis

- Real Time Expansion of the Reduced Sample Density Video Color Components (U, V) to Full Resolution

- Three Independently Addressable Color Palettes

- Programmable 2X Horizontal Interpolation of Y Channel

- 16 x 16 x 2-Bit Cursor Map with Independently Programmable 2X Expansion Factors in X and Y Dimensions

- YUV to RGB Color Space Conversion

- 2X Vertical Replication of Y, U, and V Data for Displaying Full Motion Video on VGA Monitor

- Register and Function Compatible with the 82750DA

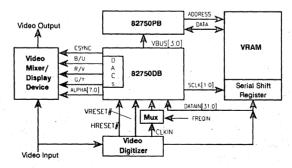

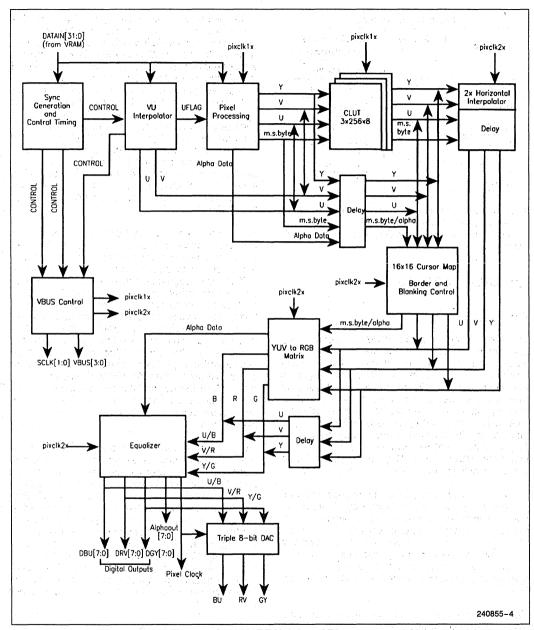

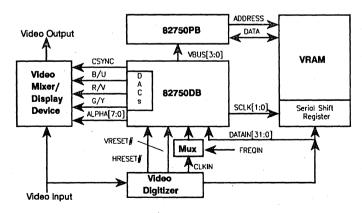

Intel's 82750DB is a custom designed VLSI chip used for processing and displaying video graphic information. It is register and function compatible with the 82750DA.

Reset inputs allow the 82750DB to be genlocked to an external sync source. By programming internal control registers, this sync can be modified to accommodate a wide variety of scanning frequencies. A large selection of bits/pixel, pixels/line, and pixel widths are programmable, allowing a wide latitude in trading-off image quality vs update rate and VRAM requirements.

The 82750DB can operate in a digitizing mode, wherein it generates timing and control signals to the 82750PB and VRAM, but does not output display information. Besides digitizer support signals and video synchronization, the 82750DB outputs digital and analog RGB or YUV information and an 8-bit digital word of alpha data. This alpha channel data may be used to obtain a fractional mix of 82750DB outputs with another video source.

82750DB Subsystem Diagram

240855-1

# 82750DB Display Processor

| <b>CONTENTS</b> PAGE                                                                                                                                                                                                 | <b>CONTENTS</b> PAGE                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 82750DB PIN DESCRIPTION         Pinout       1-4         Quick Pin Reference       1-8                                                                                                                           | 4.0 PROGRAMMING THE 82750DB         Overview       1-33         Pipeline Delay through the 82750DB       1-33                                                                                                   |

| 2.0 ARCHITECTURE  Overview 1-11  Sync Generation and Timing 1-11  VBUS Control 1-14  VBUS Code Description 1-16  Pixel Processing Path 1-19  VU Interpolation 1-19  Colormap Lookup Table (CLUT)                     | Programming Considerations 1-34 Cursor Registers 1-34 Display Timing Registers 1-35 VBUS Code Registers 1-37 Color Registers 1-38 Control Registers 1-38 Color Map Registers 1-42 82750DB Register Summary 1-43 |

| Operation 1-20 8-Bit/Pixel Graphics Mode 1-21 8-Bit/Pixel Video Mode 1-21 8-Bit/Pixel Mixed Mode 1-21 Pseudo 16-Bit/Pixel Graphics Mode 1-21 Pseudo 16-Bit/Pixel Video Mode 1-21 Pseudo 16-Bit/Pixel Wixed Mode 1-22 | 5.0 ELECTRICAL DATA  D.C. Characteristics                                                                                                                                                                       |

| 16-Bit/Pixel Graphics Mode 1-22 16-Bit/Pixel Video Mode 1-22 16-Bit/Pixel Mixed Mode 1-22 32-Bit/Pixel Graphics Mode 1-22                                                                                            | 6.0 MECHANICAL DATA Packaging Outlines and Dimensions 1-53 Package Thermal Specifications 1-56 FIGURES                                                                                                          |

| 32-Bit/Pixel Video Mode       1-22         32-Bit/Pixel Mixed Mode       1-22         Y Interpolator       1-23         Cursor       1-23                                                                            | Figure 1-1       82750DB Pinout       1-4         Figure 1-2       82750DB Functional Signal Groupings       1-7                                                                                                |

| YUV to RGB Converter                                                                                                                                                                                                 | Figure 2-1 82750DB Unit Level Diagram                                                                                                                                                                           |

| <b>3.0 HARDWARE INTERFACE</b> 82750DB Reset Operations                                                                                                                                                               | Parameters                                                                                                                                                                                                      |

| Genlocking on the 82750DB                                                                                                                                                                                            | Figure 2-5 82750DB 1X Shift Clock Operation                                                                                                                                                                     |

|                                                                                                                                                                                                                      | Figure 2-7 82750DB 1/3X Shift Clock<br>Operation                                                                                                                                                                |

| ngar kanalang meneralah di Sebagai Sebagai Anggarapan kanalan Sebagai Sebagai Sebagai Sebagai Sebagai Sebagai                                                                                                        | 1                                                                                                                                                                                                               |

| CONTEN         | I <b>TS</b> PA                                        | AGE  | CONTE     | <b>NTS</b> PAGE                                               |

|----------------|-------------------------------------------------------|------|-----------|---------------------------------------------------------------|

| Figure 2-9     | Divide by 2.5 Pixel Clock                             | 1-27 | TABLES    |                                                               |

| Figure 3-1     | Horizontal and Vertical Reset Timing                  | 1-30 |           | Pin Cross Reference by Pin<br>Name                            |

| Figure 3-2     | Digitizing Example                                    | 1-31 | Table 1-2 | Pin Cross Reference by                                        |

| Figure 3-3     | Digitizing Example with Line                          | 4.00 |           | Location 1-6                                                  |

| <b>-</b> : 4.4 | Replicate                                             | 1-32 | Table 1-3 | Pin Descriptions 1-8                                          |

| Figure 4-1     | Programming the Video Sync Outputs                    | 1-36 | Table 1-4 | Input Pins 1-11                                               |

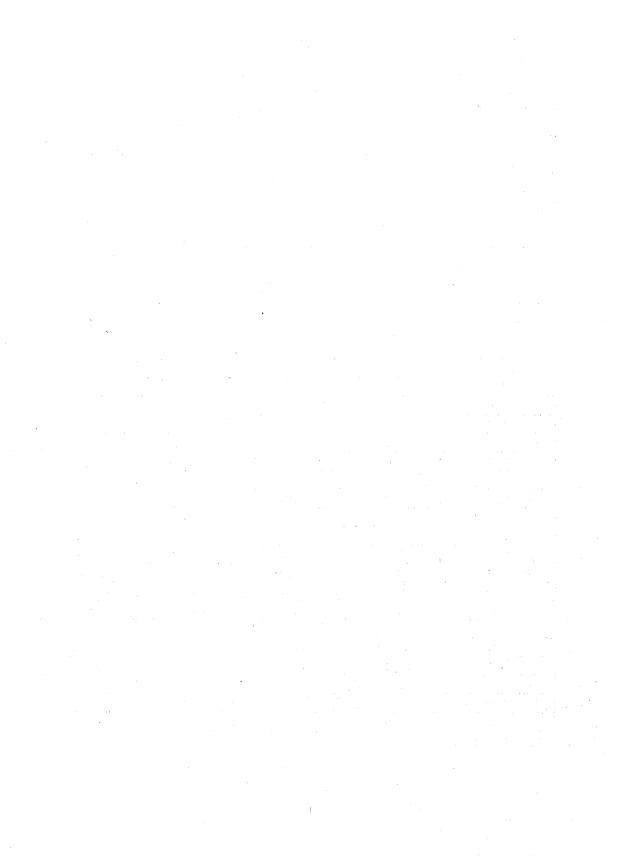

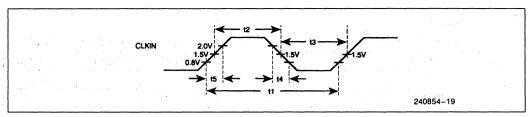

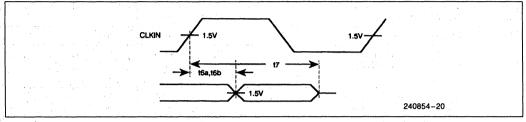

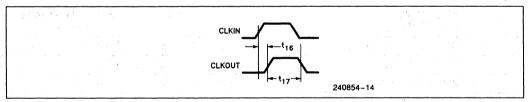

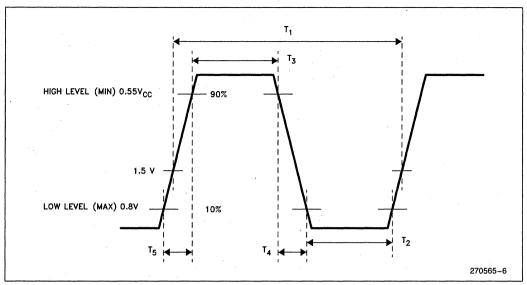

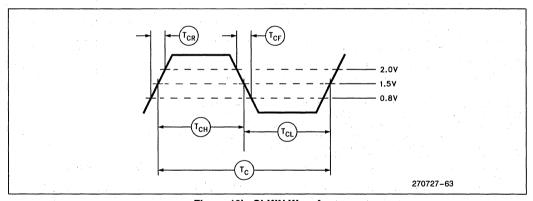

| Figure 5-1     | Clock Waveforms                                       |      | Table 2-1 | VU Transfer Request Patterns 1-17                             |

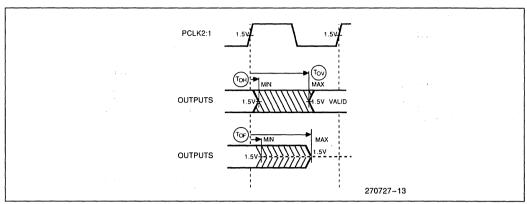

| Figure 5-2     | Output Waveforms                                      | 1-47 | Table 2.2 | VU Transfer Request Patterns                                  |

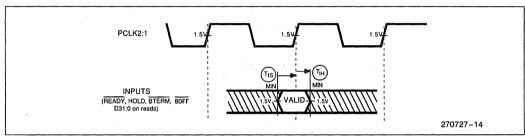

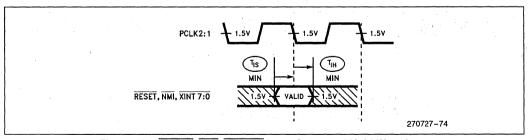

| Figure 5-3     | Input Waveforms                                       | 1-47 | Table 2-2 | with Line Replicate 1-17                                      |

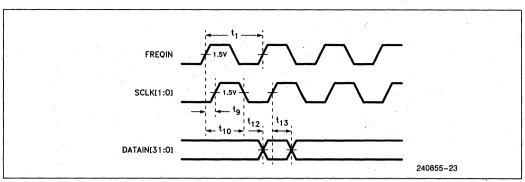

| Figure 5-4     | 1X SCLK Mode                                          | 1-48 | Table 2-3 | CLUT Modes 1-20                                               |

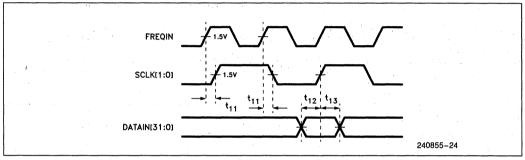

| Figure 5-5     | 1/2X SCLK Mode                                        | 1-48 |           | Control Bit Settings and                                      |

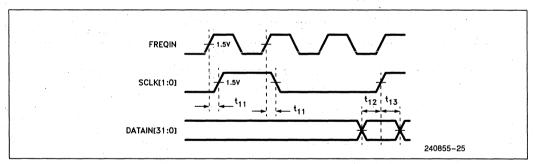

| Figure 5-6     | 1/3X SCLK Mode                                        | 1-48 |           | Resulting Interpolator Output                                 |

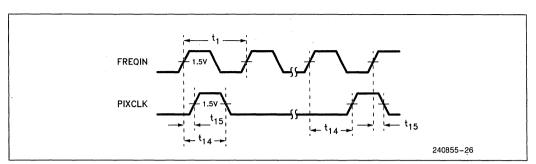

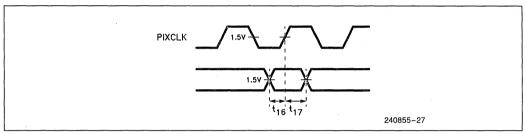

| Figure 5-7     | PIXCLK Waveforms                                      | 1-49 | Table 2-5 | Cursor Color Registers 1-24                                   |

| Figure 5-8     | Output Setup and Hold $\ \ldots \ .$                  | 1-49 |           | Cursor Sizes 1-24                                             |

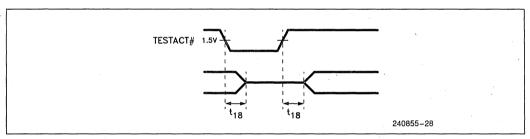

| Figure 5-9     | TESTACT# Float Delay                                  | 1-49 |           | 82750DB Active T-Cycle                                        |

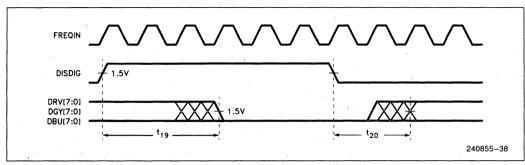

| Figure 5-10    | DISDIG to Digital Output Delay                        | 1-50 |           | Patterns 1-26                                                 |

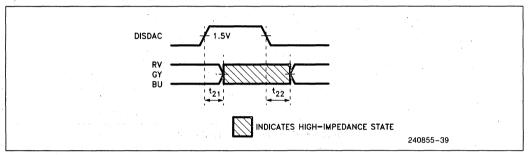

| Figure 5-11    | DISDAC to Analog Output                               | 1-30 | Table 2-8 | Digital to Analog Converter                                   |

| riguic 5-11    | Delay                                                 | 1-50 | Table 2.1 | Pins 1-27                                                     |

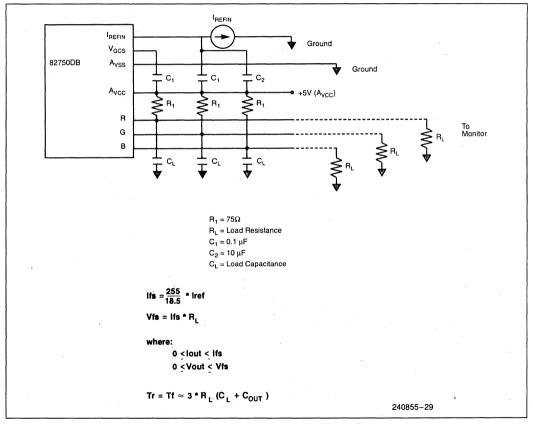

| Figure 5-12    | Typical Output                                        |      |           | Selecting Alpha Outputs 1-29<br>VU Sampling 1-39              |

| =: =           | Configuration                                         | 1-51 |           | Pixel Times 1-39                                              |

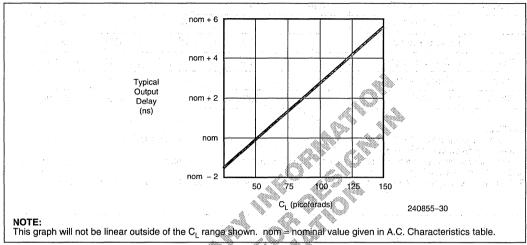

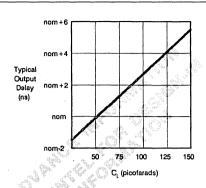

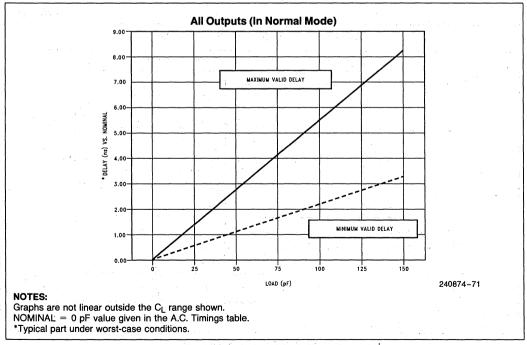

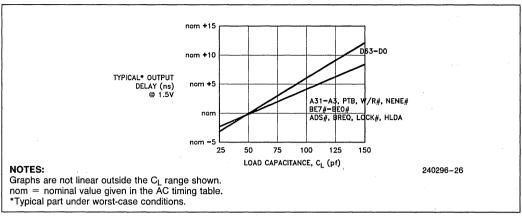

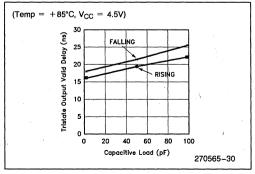

| Figure 5-13    | Typical Output Valid Delay<br>Versus Load Capacitance |      |           | Number of Bits/Pixel 1-40                                     |

|                | under Worst Case<br>Conditions                        | 1 50 |           | Test Mode Select Coding 1-40                                  |

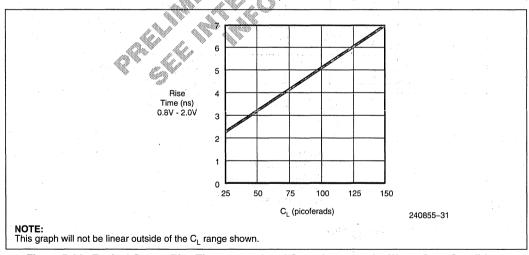

| Ciauro E 14    |                                                       | 1-52 |           | Coding of Transfer Timing                                     |

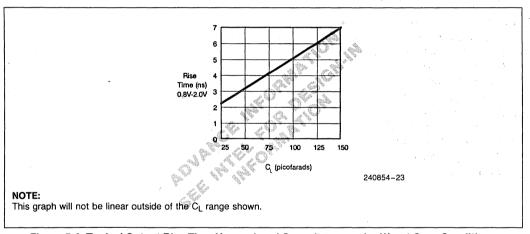

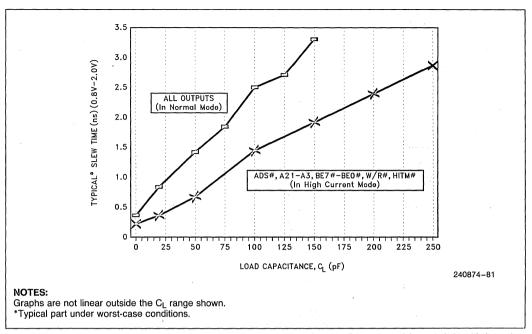

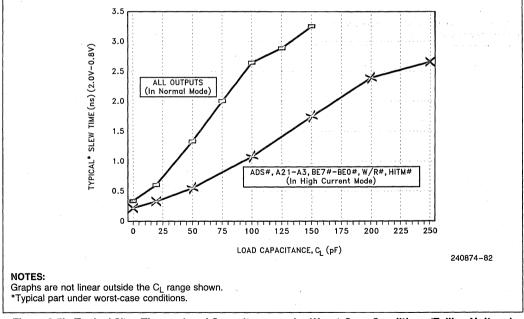

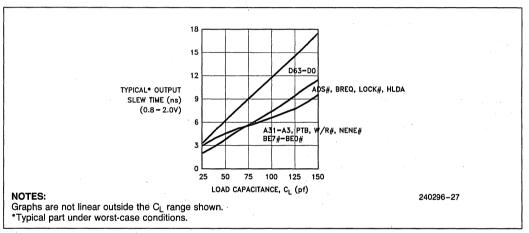

| rigure 5-14    | Typical Output Rise Time Versus Load Capacitance      |      |           | Select Bits 1-42                                              |

|                | under Worst Case                                      | 1 50 |           | 82750DB Register Space 1-43                                   |

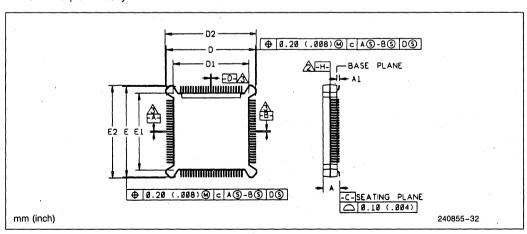

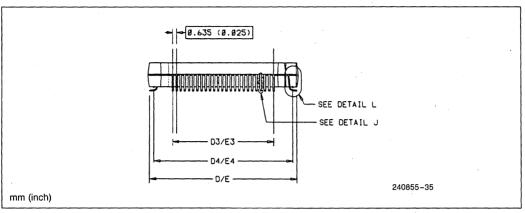

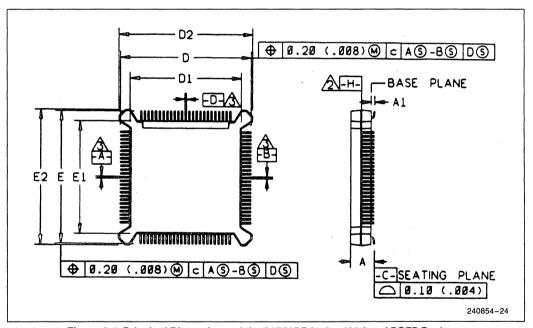

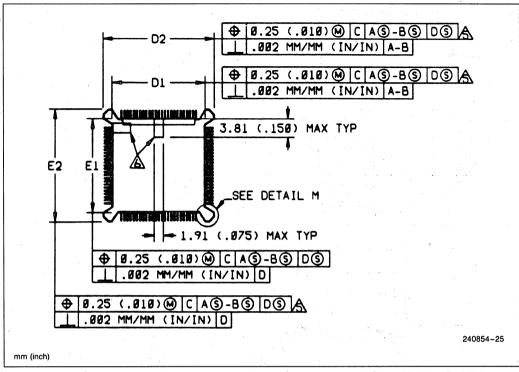

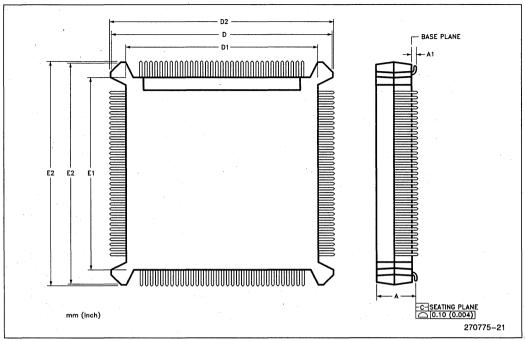

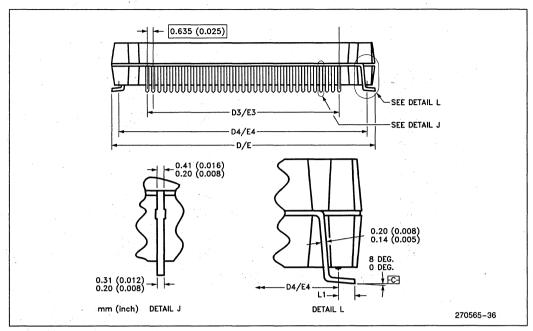

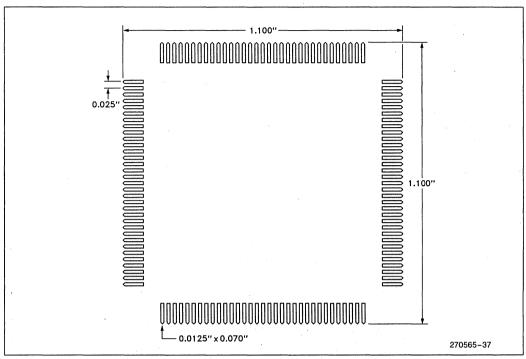

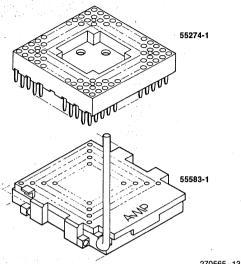

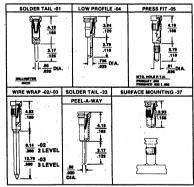

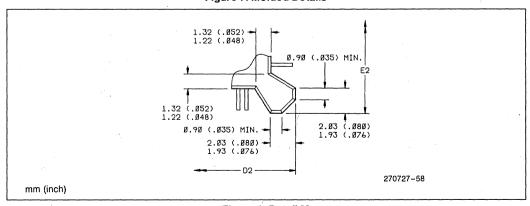

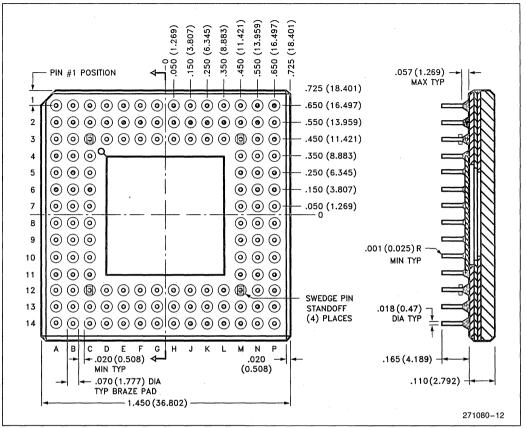

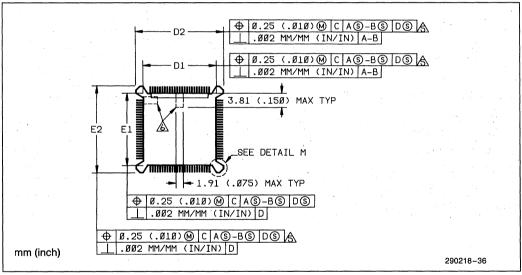

| Figure 6-1     | Conditions  Principle Dimensions of the               | 1-52 | Table 5-1 | Absolute Maximum                                              |

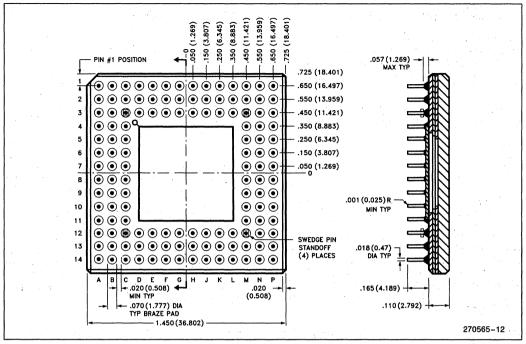

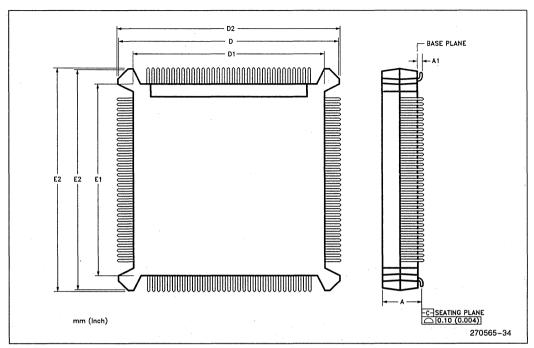

| rigule 0-1     | 82750DB in the 132-Lead PQF                           | Р    | Table 5.2 | Requirements 1-44  D.C. Characteristics 1-44                  |

|                | Package                                               | 1-53 |           | A.C. Characteristics at                                       |

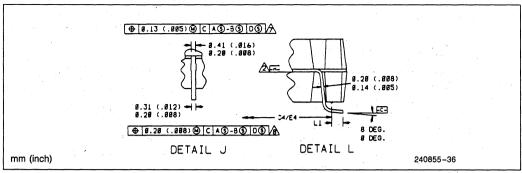

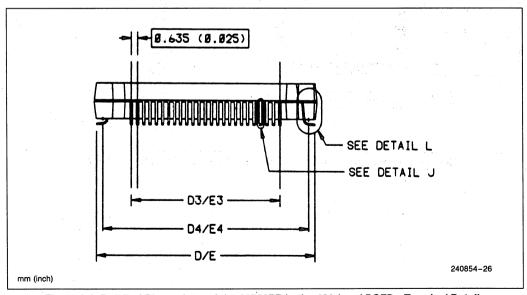

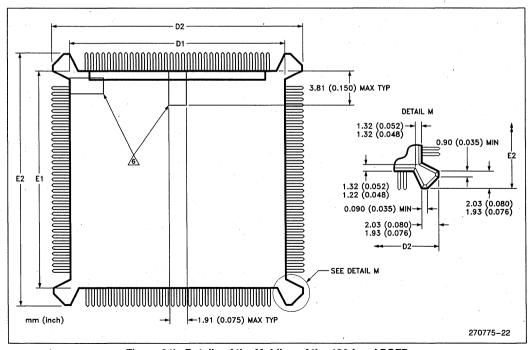

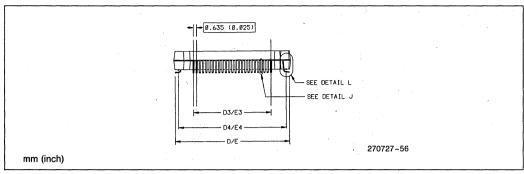

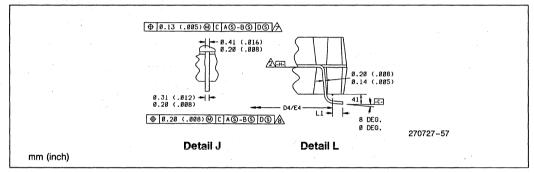

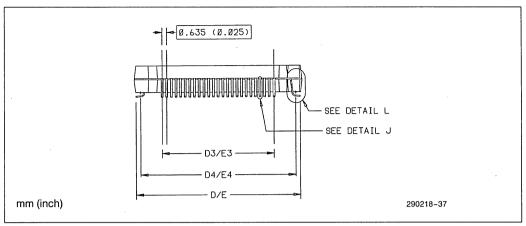

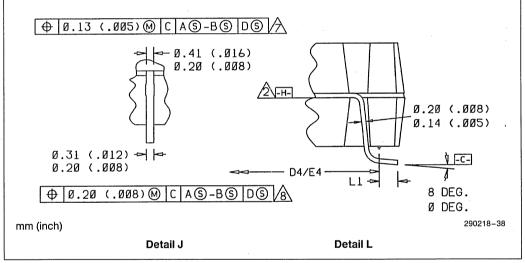

| Figure 6-2     | 132-Lead PQFP Mechanical Package Detail—Typical       |      | Table 3-3 | 28 MHz1-45                                                    |

|                | Lead                                                  | 1-54 | Table 5-4 | A.C. Characteristics at                                       |

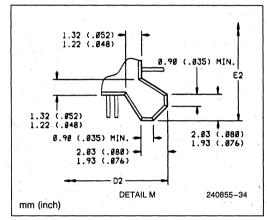

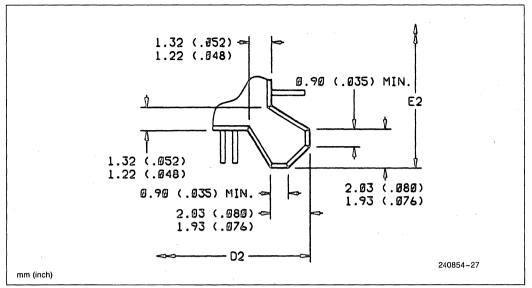

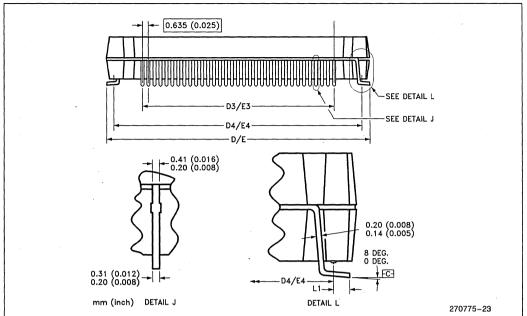

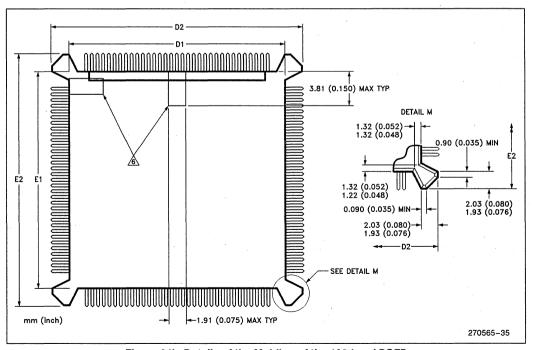

| Figure 6-3     | 132-Lead PQFP Mechanical                              |      |           | 45 MHz1-46                                                    |

|                | Package Detail—Protective                             | 1.54 |           | DAC D.C. Characteristics 1-50                                 |

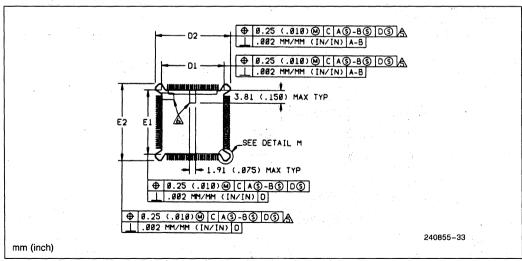

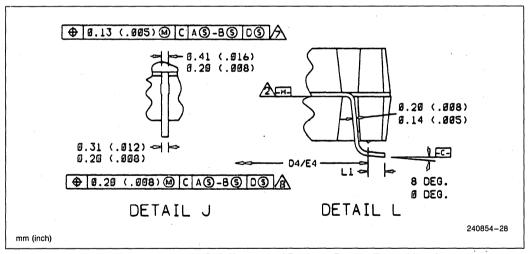

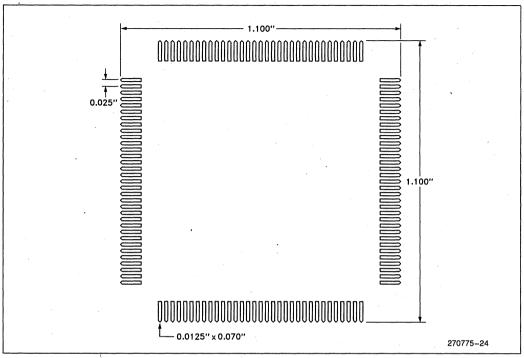

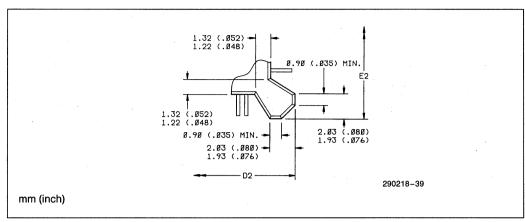

| Figure 6-4     | Detailed Dimensions of the                            | 1-54 |           | DAC A.C. Characteristics 1-51                                 |

| riguic o-4     | 82750DB in the 132-Lead                               |      |           | PQFP Symbol List1-53                                          |

|                | PQFP Package—Molded Details                           | 1-54 | Table 6-2 | Intel Case Outline Drawings for PQFP at 0.025 Inch Pitch 1-53 |

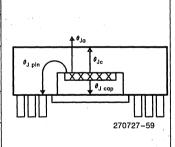

| Figure 6-5     | Detailed Dimensions of the 82750DB in the 132-Lead    |      | Table 6-3 | Thermal Resistances (°C/W)1-56                                |

|                | PQFP Package—Terminal Details                         | 1-55 | Table 6-4 | Maximum T <sub>A</sub> at Various Airflows                    |

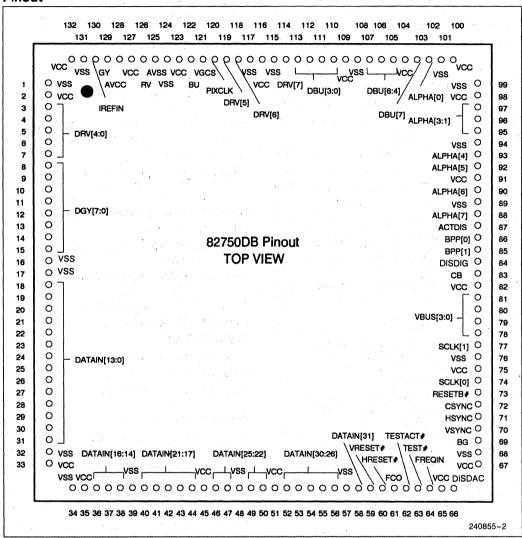

#### 1.0 82750DB PIN DESCRIPTION

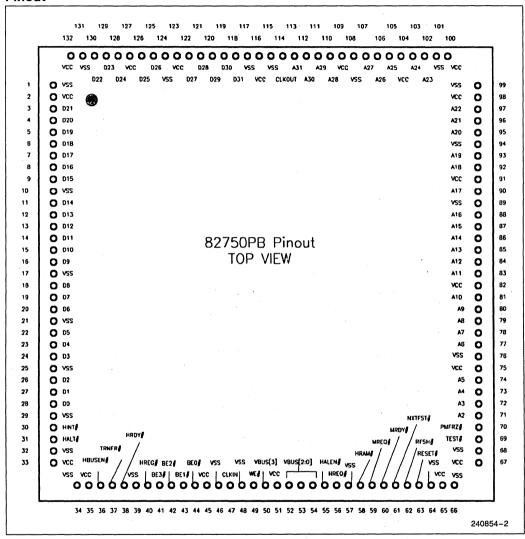

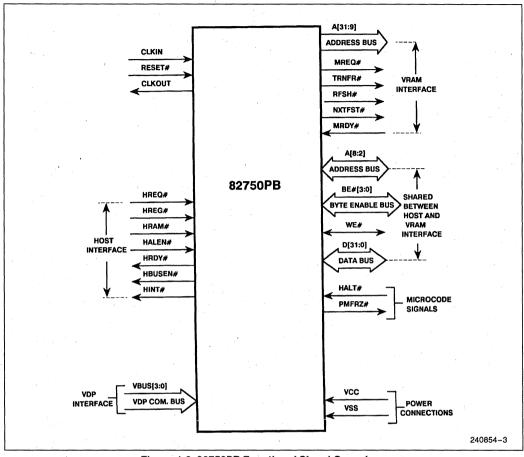

#### **Pinout**

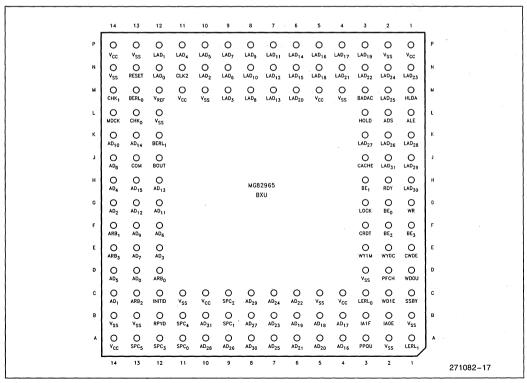

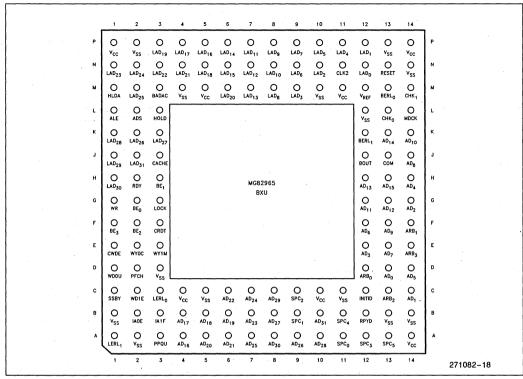

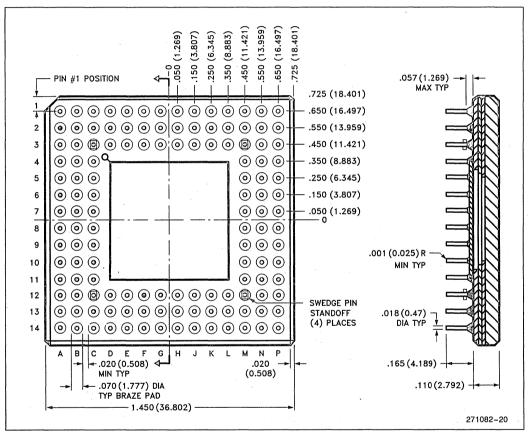

Figure 1-1. 82750DB Pinout

Table 1-1. Pin Cross Reference by Pin Name

| Pin Name   | Location |

|------------|----------|

| ACTDIS     | 87       |

| ALPHA[7]   | 88       |

| ALPHA[6]   | 90       |

| ALPHA[5]   | 92       |

| ALPHA[4]   | 93       |

| ALPHA[3]   | 95       |

| ALPHA[2]   | 96       |

| ALPHA[1]   | 97       |

| ALPHA[0]   | 102      |

| AVCC       | 128      |

| AVSS       | 125      |

| BG         | 69       |

| BPP[1]     | 85       |

| BPP[0]     | 86       |

| BU         | 122      |

| СВ         | 83       |

| CSYNC      | 72       |

| DATAIN[31] | 58       |

| DATAIN[30] | 56       |

| DATAIN[29] | 55       |

| DATAIN[28] | 54       |

| DATAIN[27] | 53       |

| DATAIN[26] | 52       |

| DATAIN[25] | 50       |

| DATAIN[24] | 49       |

| DATAIN[23] | 47       |

| DATAIN[22] | 46       |

| DATAIN[21] | 44       |

| DATAIN[20] | 43       |

| DATAIN[19] | 42       |

| DATAIN[18] | 41       |

| DATAIN[17] | 40       |

| DATAIN[16] | 38       |

| Table 1-1. | Pin Cross I |

|------------|-------------|

| Pin Name   | Location    |

| DATAIN[15] | 37          |

| DATAIN[14] | 36          |

| DATAIN[13] | 31          |

| DATAIN[12] | 30          |

| DATAIN[11] | 29          |

| DATAIN[10] | 28          |

| DATAIN[9]  | 27          |

| DATAIN[8]  | 26          |

| DATAIN[7]  | 25          |

| DATAIN[6]  | 24          |

| DATAIN[5]  | 23          |

| DATAIN[4]  | 22          |

| DATAIN[3]  | 21          |

| DATAIN[2]  | 20          |

| DATAIN[1]  | 19          |

| DATAIN[0]  | 18          |

| DBU[7]     | 103         |

| DBU[6]     | 105         |

| DBU[5]     | 106         |

| DBU[4]     | 107         |

| DBU[3]     | 110         |

| DBU[2]     | 111         |

| DBU[1]     | 112         |

| DBU[0]     | 113         |

| DGY[7]     | 8           |

| DGY[6]     | 9           |

| DGY[5]     | 10          |

| DGY[4]     | 11          |

| DGY[3]     | 12          |

| DGY[2]     | 13          |

| DGY[1]     | 14          |

| DGY[0]     | 15          |

| DISDAC     | 66          |

| DISDIG     | 84          |

| refere by Pili Name |         |  |

|---------------------|---------|--|

| Pin Name            | Locatio |  |

| DRV[7]              | 114     |  |

| DRV[6]              | 118     |  |

| DRV[5]              | 119     |  |

| DRV[4]              | 3       |  |

| DRV[3]              | 4       |  |

| DRV[2]              | 5       |  |

| DRV[1]              | 6       |  |

| DRV[0]              | 7       |  |

| FCO .               | 61      |  |

| FREQIN              | 64      |  |

| GY                  | 129     |  |

| HRESET#             | 60      |  |

| HYSNC               | 71      |  |

| IREFIN              | 130     |  |

| PIXCLK              | 120     |  |

| RESETB#             | 73      |  |

| RV                  | 126     |  |

| SCLK[1]             | 77      |  |

| SCLK[0]             | 74      |  |

| TEST#               | 63      |  |

| TESTACT#            | 62      |  |

| VBUS[3]             | 81      |  |

| VBUS[2]             | 80      |  |

| VBUS[1]             | 79      |  |

| VBUS[0]             | 78      |  |

| V <sub>CC</sub>     | 2       |  |

| V <sub>CC</sub>     | 33      |  |

| V <sub>CC</sub>     | 35      |  |

| V <sub>CC</sub>     | 45      |  |

| V <sub>CC</sub>     | 51      |  |

| V <sub>CC</sub>     | 65      |  |

| V <sub>CC</sub>     | 67      |  |

| V <sub>CC</sub>     | 75      |  |

| Pin Name        | Location |

|-----------------|----------|

| V <sub>CC</sub> | 82       |

| $V_{CC}$        | 91       |

| V <sub>CC</sub> | 98       |

| V <sub>CC</sub> | 100      |

| V <sub>CC</sub> | 104      |

| V <sub>CC</sub> | 109      |

| V <sub>CC</sub> | 116      |

| V <sub>CC</sub> | 123      |

| V <sub>CC</sub> | 127      |

| V <sub>CC</sub> | 132      |

| VGCS            | 121      |

| VRESET#         | 59       |

| V <sub>SS</sub> | 1        |

| V <sub>SS</sub> | 16       |

| $V_{SS}$        | 17       |

| $V_{SS}$        | 32       |

| V <sub>SS</sub> | 34       |

| V <sub>SS</sub> | 39       |

| V <sub>SS</sub> | 48       |

| V <sub>SS</sub> | 57       |

| V <sub>SS</sub> | 66       |

| V <sub>SS</sub> | 68       |

| V <sub>SS</sub> | 76       |

| V <sub>SS</sub> | 89       |

| V <sub>SS</sub> | 94       |

| V <sub>SS</sub> | 99       |

| V <sub>SS</sub> | 101      |

| V <sub>SS</sub> | 108      |

| V <sub>SS</sub> | 115      |

| $V_{SS}$        | 117      |

| $V_{SS}$        | 124      |

| V <sub>SS</sub> | 131      |

| VSYNC           | 70       |

Table 1-2. Pin Cross Reference by Location

| Location | Pin Name        |

|----------|-----------------|

| 1        | V <sub>SS</sub> |

| 2        | V <sub>CC</sub> |

| 3        | DRV[4]          |

| 4        | DRV[3]          |

| 5        | DRV[2]          |

| 6        | DRV[1]          |

| . 7      | DRV[0]          |

| 8        | DGY[7]          |

| 9        | DGY[6]          |

| 10       | DGY[5]          |

| 11       | DGY[4]          |

| 12       | DGY[3]          |

| 13       | DGY[2]          |

| 14       | DGY[1]          |

| 15       | DGY[0]          |

| 16       | V <sub>SS</sub> |

| 17       | $V_{SS}$        |

| 18       | DATAIN[0]       |

| 19       | DATAIN[1]       |

| 20       | DATAIN[2]       |

| 21       | DATAIN[3]       |

| 22       | DATAIN[4]       |

| 23       | DATAIN[5]       |

| 24       | DATAIN[6]       |

| 25       | DATAIN[7]       |

| 26       | DATAIN[8]       |

| 27       | DATAIN[9]       |

| 28       | DATAIN[10]      |

| 29       | DATAIN[11]      |

| 30       | DATAIN[12]      |

| 31       | DATAIN[13]      |

| 32       | V <sub>SS</sub> |

| 33       | V <sub>CC</sub> |

| Location         Pin Name           34         V <sub>SS</sub> 35         V <sub>CC</sub> 36         DATAIN[1           37         DATAIN[1           38         DATAIN[1           39         V <sub>SS</sub> 40         DATAIN[1           41         DATAIN[1           42         DATAIN[1           43         DATAIN[2           44         DATAIN[2           45         V <sub>CC</sub> 46         DATAIN[2 | 4]<br> 5]<br> 6]<br> 17]<br> 8] |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 35 V <sub>CC</sub> 36 DATAIN[1  37 DATAIN[1  38 DATAIN[1  39 V <sub>SS</sub> 40 DATAIN[1  41 DATAIN[1  42 DATAIN[1  43 DATAIN[2  44 DATAIN[2  45 V <sub>CC</sub>                                                                                                                                                                                                                                                    | 5]<br> 6]<br> 7]<br> 8]         |

| 35 V <sub>CC</sub> 36 DATAIN[1  37 DATAIN[1  38 DATAIN[1  39 V <sub>SS</sub> 40 DATAIN[1  41 DATAIN[1  42 DATAIN[1  43 DATAIN[2  44 DATAIN[2  45 V <sub>CC</sub>                                                                                                                                                                                                                                                    | 5]<br> 6]<br> 7]<br> 8]         |

| 37 DATAIN[1 38 DATAIN[1 39 V <sub>SS</sub> 40 DATAIN[1 41 DATAIN[1 42 DATAIN[1 43 DATAIN[2 44 DATAIN[2 45 V <sub>CC</sub>                                                                                                                                                                                                                                                                                           | 5]<br> 6]<br> 7]<br> 8]         |

| 38 DATAIN[1 39 V <sub>SS</sub> 40 DATAIN[1 41 DATAIN[1 42 DATAIN[1 43 DATAIN[2 44 DATAIN[2 45 V <sub>CC</sub>                                                                                                                                                                                                                                                                                                       | 6]<br> 7]<br> 8]                |

| 39 V <sub>SS</sub> 40 DATAIN[1 41 DATAIN[1 42 DATAIN[1 43 DATAIN[2 44 DATAIN[2 45 V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                   | 17]<br>18]<br>19]               |

| 40 DATAIN[1 41 DATAIN[1 42 DATAIN[1 43 DATAIN[2 44 DATAIN[2 45 V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                      | 18]<br>19]                      |

| 41 DATAIN[1 42 DATAIN[1 43 DATAIN[2 44 DATAIN[2 45 V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                  | 18]<br>19]                      |

| 42 DATAIN[1 43 DATAIN[2 44 DATAIN[2 45 VCC                                                                                                                                                                                                                                                                                                                                                                          | 9]                              |

| 43 DATAIN[2<br>44 DATAIN[2<br>45 V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                    |                                 |

| 44 DATAIN[2<br>45 Vcc                                                                                                                                                                                                                                                                                                                                                                                               | 20]                             |

| 45 V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                     | 21]                             |

| 46 DATAIN[2                                                                                                                                                                                                                                                                                                                                                                                                         |                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                     | 22]                             |

| 47 DATAIN[2                                                                                                                                                                                                                                                                                                                                                                                                         | 23]                             |

| 48 V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

| 49 DATAIN[2                                                                                                                                                                                                                                                                                                                                                                                                         | 24]                             |

| 50 DATAIN[2                                                                                                                                                                                                                                                                                                                                                                                                         | 25]                             |

| 51 V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

| 52 DATAIN[2                                                                                                                                                                                                                                                                                                                                                                                                         | 26]                             |

| 53 DATAIN[2                                                                                                                                                                                                                                                                                                                                                                                                         | 27]                             |

| 54 DATAIN[2                                                                                                                                                                                                                                                                                                                                                                                                         | 28]                             |

| 55 DATAIN[2                                                                                                                                                                                                                                                                                                                                                                                                         | 29]                             |

| 56 DATAIN[                                                                                                                                                                                                                                                                                                                                                                                                          | 30]                             |

| 57 V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

| 58 DATAIN[                                                                                                                                                                                                                                                                                                                                                                                                          | 31]                             |

| 59 VRESET                                                                                                                                                                                                                                                                                                                                                                                                           | #                               |

| 60 HRESET                                                                                                                                                                                                                                                                                                                                                                                                           | #                               |

| 61 FCO                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |

| 62 TESTACT                                                                                                                                                                                                                                                                                                                                                                                                          | #                               |

| 63 TEST#                                                                                                                                                                                                                                                                                                                                                                                                            |                                 |

| 64 FREQIN                                                                                                                                                                                                                                                                                                                                                                                                           |                                 |

| 65 V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                  |                                 |

| 66 DISDAC                                                                                                                                                                                                                                                                                                                                                                                                           |                                 |

| Location | Pin Name        |

|----------|-----------------|

| 67       | V <sub>CC</sub> |

| 68       | V <sub>SS</sub> |

| 69       | BG              |

| 70       | VSYNC           |

| 71       | HSYNC           |

| 72       | CSYNC           |

| 73       | RESETB#         |

| 74       | SCLK[0]         |

| 75       | V <sub>CC</sub> |

| 76       | V <sub>SS</sub> |

| 77       | SCLK[1]         |

| 78       | VBUS[0]         |

| 79       | VBUS[1]         |

| 80       | VBUS[2]         |

| 81       | VBUS[3]         |

| 82       | V <sub>CC</sub> |

| 83       | СВ              |

| 84       | DISDIG          |

| 85       | BPP[1]          |

| 86       | BPP[0]          |

| 87       | ACTDIS          |

| 88       | ALPHA[7]        |

| 89       | V <sub>SS</sub> |

| 90       | ALPHA[6]        |

| 91       | V <sub>CC</sub> |

| 92       | ALPHA[5]        |

| 93       | ALPHA[4]        |

| 94       | V <sub>SS</sub> |

| 95       | ALPHA[3]        |

| 96       | ALPHA[2]        |

| 97       | ALPHA[1]        |

| 98       | V <sub>CC</sub> |

| 99       | V <sub>SS</sub> |

|          |                 |

| Location | Pin Name         |

|----------|------------------|

| 100      | V <sub>CC</sub>  |

| 101      | V <sub>SS</sub>  |

| 102      | ALPHA[0]         |

| 103      | DBU[7]           |

| 104      | V <sub>CC</sub>  |

| 105      | DBU[6]           |

| 106      | DBU[5]           |

| 107      | DBU[4]           |

| 108      | V <sub>SS</sub>  |

| 109      | V <sub>CC</sub>  |

| 110      | DBU[3]           |

| 111      | DBU[2]           |

| 112      | DBU[1]           |

| 113      | DBU[0]           |

| 114      | DRV[7]           |

| 115      | V <sub>SS</sub>  |

| 116      | V <sub>CC</sub>  |

| 117      | V <sub>SS</sub>  |

| 118      | DRV[6]           |

| 119      | DRV[5]           |

| 120      | PIXCLK           |

| 121      | VGCS             |

| 122      | BU               |

| 123      | V <sub>CC</sub>  |

| 124      | V <sub>SS</sub>  |

| 125      | AV <sub>SS</sub> |

| 126      | RV               |

| 127      | V <sub>CC</sub>  |

| 128      | AV <sub>CC</sub> |

| 129      | GY               |

| 130      | IREFIN           |

| 131      | V <sub>SS</sub>  |

| 132      | V <sub>CC</sub>  |

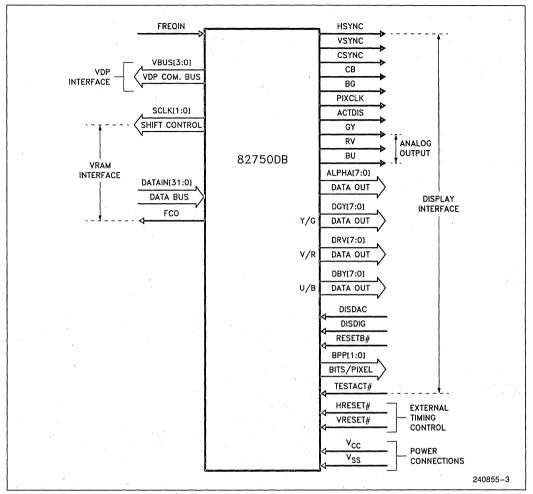

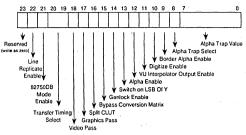

Figure 1-2. 82750DB Functional Signal Groupings

# **Quick Pin Reference**

Table 1-3. Pin Descriptions

| Symbol       | Туре     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

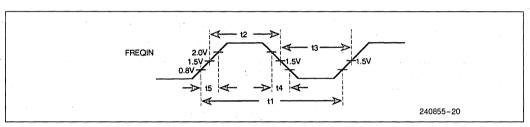

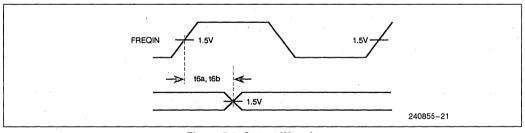

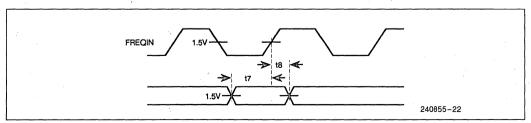

| FREQIN       | <b>.</b> | FREQUENCY INPUT CLOCK: In normal use, the 82750DB supplies refresh timing for an associated VRAM through the 82750PB. This places a lower limit on the line frequency, which is a programmed multiple of FREQIN. It must generate enough refresh cycles, so a minimum line rate of 4 kHz is required. Furthermore, the 82750PB may run no less than ½ the speed of the 82750DB, since the 82750PB samples the timing and control signals generated by the 82750DB. The period of FREQIN is known as a "T" cycle.                                                                                                                                                                                                                |

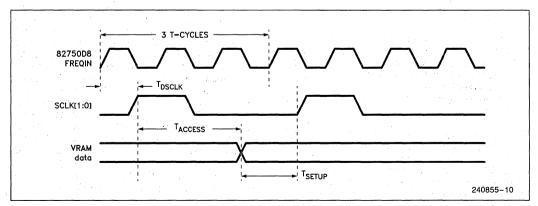

| RESETB#      | _        | <b>EXTERNAL RESET:</b> Input signal which places all units in the 82750DB into an initialized state, and sets the transfer rate to a default value of 1/3X the operating frequency. It is an edge sensitive iniput which must be held low for a minimum of ten T-cycles. The slowest transfer rate is selected to ensure that the 82750DB will read the register information correctly during the first register transfer, independent of the speed of the VRAMs. During the reset state, the analog video outputs and digital outputs are set to the black level. This will occur a maximum of four cycles after RESETB# is set to a zero. This signal is also used in conjunction with the TESTACT# input to disable outputs. |

| VRESET#      | <b>-</b> | VERTICAL RESET: By programming a bit in an internal register, the 82750DB may be placed in the Genlock mode. If this mode is selected, assertion of VRESET# resets all vertical timing to the first line of the next field. It does not affect the horizontal timing, but does generate the on-chip end of field signals. It is an edge sensitive input that is sampled in the 82750DB at the internal time corresponding to the rising edge of FREQIN. If the Genlock mode has not been enabled, this signal will have no effect on the sync timing. The 82750DB will then operate in a free-running mode. Refer to Chapter 3 for a detailed description of genlocking the 82750DB.                                            |

| HRESET#      |          | HORIZONTAL RESET: When in the Genlock mode, this input will reset all of the horizontal timing to the start of the line (beginning of horizontal sync). HRESET# does not affect vertical timing (except for an up-to one-line delay) or any other 82750DB registers. This signal is an edge sensitive input that is sampled in the 82750DB at that internal time corresponding to the rising edge of FREQIN. As was the case with the VRESET# signal, this input will be ignored when not in the Genlock mode.                                                                                                                                                                                                                  |

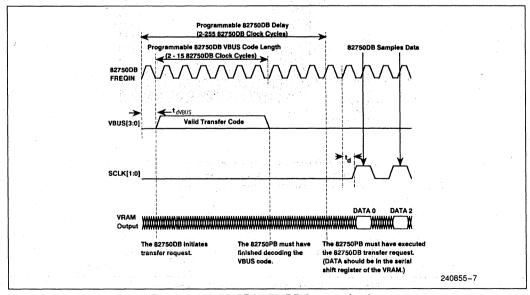

| VBUS[3:0]    | 0        | VDP COMMUNICATION BUS: The 82750DB outputs status and VRAM transfer requests over these lines to the 82750PB, for 2 to 16 T-cycles (as programmed by the user). Transfer requests can tie up the 82750DB/VRAM, 82750PB/VRAM, or 82750PB/82750DB (VBUS) interfaces for a longer period due to VRAM arbitration. When signals are not being sent out, the VBUS has value 1111, the "null command."                                                                                                                                                                                                                                                                                                                                |

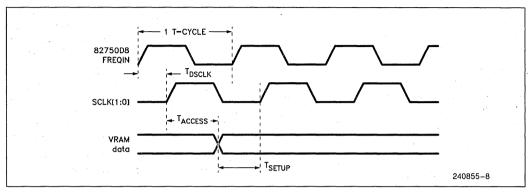

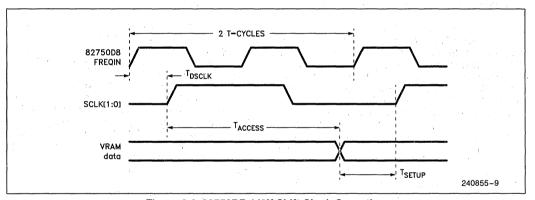

| SCLK[1:0]    | 0        | VRAM SHIFT CLOCKS: Transfer requests to the 82750PB cause a VRAM address to be set up, and the VRAM serial registers loaded (in the case of displaying) or unloaded (in the case of digitizing). These signals are used to shift data out of and into the VRAMs. Both signals are identical, and run at a maximum rate of 1X of the pixel frequency, except during transfer requests, at which time they run at 1X, 1/2X, or 1/3X of the operating frequency of the 82750DB, as programmed by the user.                                                                                                                                                                                                                         |

| DATAIN[31:0] | 1        | DATA INPUT BUS: This is the input data clocked in from VRAM by the SCLK[1:0] signals. The format of the input data is a function of the programmed number of bits/pixel and of the type of transfer cycle being executed. Data will be sampled internally on the rising edge of FREQIN.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 1-3. Pin Descriptions (Continued)

| Symbol                             | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Nar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ne and i  | unction    |        |                       |

|------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|--------|-----------------------|

| FCO                                | Ο    | FRAME CAPTURE ON: This is the output signal which indicates to the digitizer that the VRAM serial port has been turned from read mode to write mode. The digitizer may then drive the (common) VRAM serial register data I/O pins. FCO will be asserted after the programmer specifies digitization, five lines after the start of the active vertical display, at the time of HSYNC. This gives the external logic time to switch directions of the VRAM serial data bus. This signal will end four lines after vertical active stops, at the next HSYNC, to make sure the digitizer is off before the next beginning-of-field register transfer. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |            |        |                       |

| HSYNC                              | 0    | asserted at the beginni                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | HORIZONTAL SYNCHRONIZATION: Video synchronization signal which is asserted at the beginning of every line and ends a programmed time later. (The duration of this signal is specified in T-cycles.)                                                                                                                                                                                                                                                                                                                                                                                          |           |            |        |                       |

| VSYNC                              | 0    | VERTICAL SYNCHRO<br>programmed to start (o<br>position may be specifi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | nce) and e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nd (once  | ) in every |        |                       |

| CSYNC                              | 0    | COMPOSITE SYNCHR<br>vertical serration and e<br>synchronization pulses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | qualization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |            |        |                       |

| СВ                                 | 0    | COMPOSITE BLANKI<br>once in each line, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |            |        | to end once and start |

| BG                                 | 0    | positions in each line, i<br>of this signal is to provi<br>inserted to generate a<br>integer divisor (0–31) a<br>effectively, the 82750D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BURST GATE: This signal starts and stops at user-programmable horizontal positions in each line, in a programmable vertical group of lines. The primary use of this signal is to provide a "window" during which the BURST output should be inserted to generate a baseband NTSC signal. The output frequency is set by an integer divisor (0–31) and the rate of the FREQIN clock input. To use this effectively, the 82750DB must operate at an integer multiple of the NTSC 3.58 MHz color subcarrier. The number is programmed in two's complement form in the General Control register. |           |            |        |                       |

| PIXCLK                             | 0    | PIXEL CLOCK: This output signals valid data on the DGY, DRV, DBU, GY, RV, and BU lines. PIXCLK becomes active one-half of a T-cycle after valid data appears on DGY, DRV, or DBU, and coincident with GY, RV, and BU. During active display time it is issued at a steady rate of 1/(T-cycles/pixel) times per T-cycle, and otherwise at a steady rate of once per T-cycle. Its duration is one-half of a T-cycle, and its rising edge may synchronize with either rising or falling edges of FREQIN depending on the pixel frequency. This signal may be used to synchronize off-chip processing of the pixel data outputs.                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |            |        |                       |

| GY, RV, BU                         | 0    | ANALOG PIXEL OUT<br>82750DB in analog for<br>output pixel data in eith                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | m. During th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ne displa | y, these s |        |                       |

|                                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Output<br>Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DGY       | DRV        | DBU    |                       |

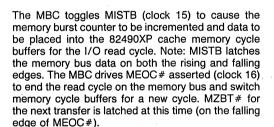

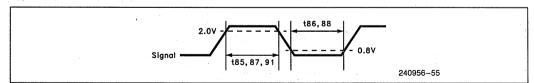

|                                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | YUV<br>RGB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Y<br>G    | V<br>R     | U<br>B |                       |