Volume II—Peripherals Microprocessor and Peripheral Handbook intel

# Microprocessor and Peripheral Handbook

Volume II - Peripheral

## LITERATURE

To order Intel Literature or obtain literature pricing information in the U.S. and Canada call or write Intel Literature Sales. In Europe and other international locations, please contact your local sales office or distributor.

INTEL LITERATURE SALES P.O. BOX 58130 SANTA CLARA, CA 95052-8130 In the U.S. and Canada call toll free (800) 548-4725

#### **CURRENT HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| TITLE                                                                                    | LITERATURE<br>ORDER NUMBER |

|------------------------------------------------------------------------------------------|----------------------------|

| COMPLETE SET OF HANDBOOKS (Available in U.S. and Canada only)                            | 231003                     |

| AUTOMOTIVE PRODUCTS HANDBOOK (Not included in handbook set)                              | 231792                     |

| COMPONENTS QUALITY/RELIABILITY HANDBOOK                                                  | 210997                     |

| EMBEDDED CONTROL APPLICATIONS HANDBOOK                                                   | 270648                     |

| 8-BIT EMBEDDED CONTROLLER HANDBOOK                                                       | 270645                     |

| 16-BIT EMBEDDED CONTROLLER HANDBOOK                                                      | 270646                     |

| 32-BIT EMBEDDED CONTROLLER HANDBOOK                                                      | 270647                     |

| MEMORY COMPONENTS HANDBOOK                                                               | 210830                     |

| MICROCOMMUNICATIONS HANDBOOK                                                             | 231658                     |

| MICROCOMPUTER PROGRAMMABLE LOGIC HANDBOOK                                                | 296083                     |

| MICROPROCESSOR AND PERIPHERAL HANDBOOK (2 volume set)                                    | 230843                     |

| MILITARY PRODUCTS HANDBOOK (2 volume set. Not included in handbook set)                  | 210461                     |

| OEM BOARDS AND SYSTEMS HANDBOOK                                                          | 280407                     |

| PRODUCT GUIDE (Overview of Intel's complete product lines)                               | 210846                     |

| SYSTEMS QUALITY/RELIABILITY HANDBOOK                                                     | 231762                     |

| INTEL PACKAGING OUTLINES AND DIMENSIONS (Packaging types, number of leads, etc.)         | 231369                     |

| LITERATURE PRICE LIST (U.S. and Canada) (Comprehensive list of current Intel Literature) | 210620                     |

| INTERNATIONAL LITERATURE GUIDE                                                           | E00029                     |

CG/LIT/100188

About Our Cover:

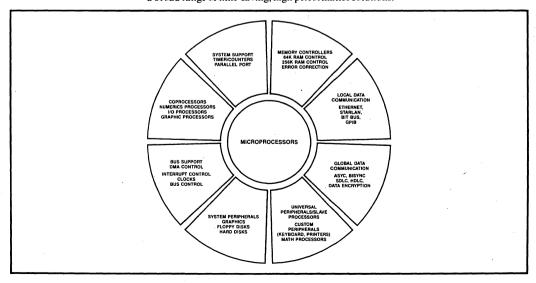

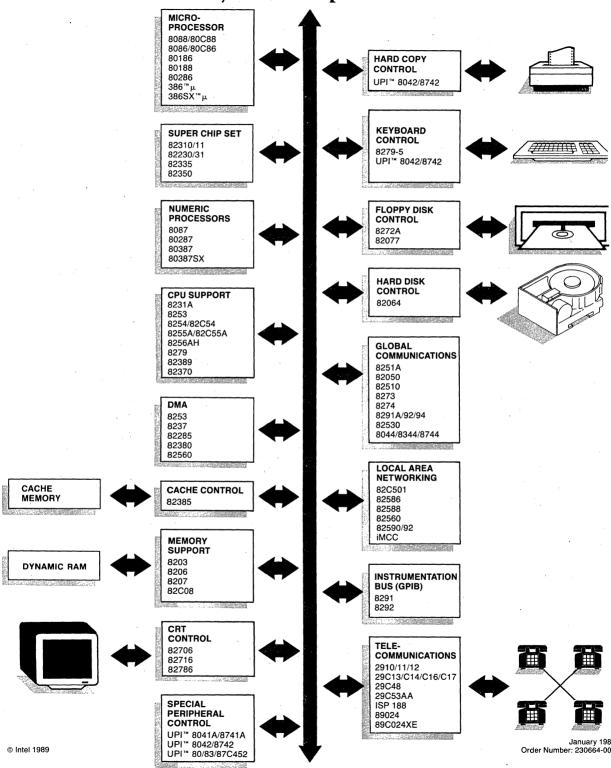

The microprocessor has been the integral device in translating unlimited ideas into solid reality. Our microprocessors work in close conjunction with our family of peripherals to form complete microcomputer chip set solutions that will help you develop and build tomorrow's electronic systems.

## U.S. and CANADA LITERATURE ORDER FORM

| NAME:                                                                                                                                    |                                       |                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------|

| COMPANY:                                                                                                                                 |                                       |                                                               |

| ADDRESS:                                                                                                                                 |                                       |                                                               |

| CITY:                                                                                                                                    | STATE: _                              | ZIP:                                                          |

| COUNTRY:                                                                                                                                 |                                       |                                                               |

| PHONE NO.: ( )                                                                                                                           |                                       | •                                                             |

|                                                                                                                                          | TITLE                                 | QTY. PRICE TOTAL                                              |

|                                                                                                                                          |                                       | X=                                                            |

|                                                                                                                                          |                                       |                                                               |

|                                                                                                                                          |                                       | X=                                                            |

|                                                                                                                                          |                                       | ×=                                                            |

|                                                                                                                                          |                                       | =                                                             |

|                                                                                                                                          | · · · · · · · · · · · · · · · · · · · | X=Subtotal                                                    |

|                                                                                                                                          |                                       | Must Add Your<br>Local Sales Tax                              |

| Postage: add 10% of subtotal                                                                                                             |                                       | Postage                                                       |

| Pay by check, money order, or include compaccept VISA, MasterCard or American Exprefor delivery.  ☐ VISA ☐ MasterCard ☐ American Express | ess. Make payment to Intel Lit        | erature Sales. Allow 2-4 weeks                                |

| Account No.                                                                                                                              |                                       |                                                               |

| Signature                                                                                                                                |                                       |                                                               |

| Mail To: Intel Literature Sales<br>P.O. Box 58130<br>Santa Clara, CA 95052-8130                                                          |                                       | outside the U.S. and Canada order form or contact their local |

For phone orders in the U.S. and Canada Call Toll Free: (800) 548-4725

Prices good until 12/31/89. Source HB

## INTERNATIONAL LITERATURE ORDER FORM

| NAME:           | <u></u>                               |

|-----------------|---------------------------------------|

| COMPANY:        |                                       |

| ADDRESS:        |                                       |

| CITY: ST        | ATE: ZIP:                             |

| COUNTRY:        |                                       |

| PHONE NO.: ( )  | · · · · · · · · · · · · · · · · · · · |

| ORDER NO. TITLE | QTY. PRICE TOTAL                      |

|                 |                                       |

|                 |                                       |

|                 | X=                                    |

|                 | X=                                    |

|                 | ×=                                    |

|                 | X=                                    |

|                 | X=                                    |

|                 | ×=                                    |

|                 |                                       |

|                 | Subtotal                              |

|                 | Must Add Your<br>Local Sales Tax      |

|                 | Total                                 |

#### **PAYMENT**

Cheques should be made payable to your local Intel Sales Office (see inside back cover.)

Other forms of payment may be available in your country. Please contact the Literature Coordinator at your local Intel Sales Office for details.

The completed form should be marked to the attention of the LITERATURE COORDINATOR and returned to your local Intel Sales Office.

Intel the Microcomputer Company:

When Intel invented the microprocessor in 1971, it created the era of microcomputers. Whether used as microcontrollers in automobiles or microwave ovens, or as personal computers or supercomputers, Intel's microcomputers have always offered leading-edge technology. In the second half of the 1980s, Intel architectures have held at least a 75% market share of microprocessors at 16 bits and above. Intel continues to strive for the highest standards in memory, microcomputer components, modules, and systems to give its customers the best possible competitive advantages.

## MICROPROCESSOR AND PERIPHERAL HANDBOOK VOLUME II PERIPHERAL

1989

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

Above, BITBUS, COMMputer, CREDIT, Data Pipeline, ETOX, FASTPATH, Genius, i,  $\hat{i}$ , ICE, iCEL, iCS, iDBP, iDIS, I2ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Inboard, Insite, Intel, int<sub>e</sub>l, Intel376, Intel386, Intel486, int<sub>e</sub>IBOS, Intel Certified, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iPSC, iRMK, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MAPNET, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, ONCE, OpenNET, OTP, PC BUBBLE, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Quick-Erase, Quick-Proseprogramming, Ripplemode, RMX/80, RUPI, Seamless, SLD, SugarCube, UPI, and VLSiCEL, and the combination of ICE, iCS, iRMX, iSBC, iSBX, iSXM, MCS, or UPI and a numerical suffix. 4-SITE, 376, 386, 486.

MDS is an ordering code only and is not used as a product name or trademark. MDS® is a registered trademark of Mohawk Data Sciences Corporation.

\*MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales F.O. Box 58130 Santa Clara, CA 95052-8130

### CUSTOMER SUPPORT

#### INTEL'S COMPLETE SUPPORT SOLUTION WORLDWIDE

Customer Support is Intel's complete support service that provides Intel customers with hardware support, software support, customer training, consulting services and network management services. For detailed information contact your local sales offices.

After a customer purchases any system hardware or software product, service and support become major factors in determining whether that product will continue to meet a customer's expectations. Such support requires an international support organization and a breadth of programs to meet a variety of customer needs. As you might expect, Intel's customer support is quite extensive. It can start with assistance during your development effort to network management. 100 Intel sales and service offices are located worldwide — in the U.S., Canada, Europe and the Far East. So wherever you're using Intel technology, our professional staff is within close reach.

#### HARDWARE SUPPORT SERVICES

Intel's hardware maintenance service, starting with complete on-site installation will boost your productivity from the start and keep you running at maximum efficiency. Support for system or board level products can be tailored to match your needs, from complete on-site repair and maintenance support economical carry-in or mail-in factory service.

Intel can provide support service for not only Intel systems and emulators, but also support for equipment in your development lab or provide service on your product to your end-user/customer.

#### SOFTWARE SUPPORT SERVICES

Software products are supported by our Technical Information Phone Service (TIPS) that has a special toll free number to provide you with direct, ready information on known, documented problems and deficiencies, as well as work-arounds, patches and other solutions.

Intel's software support consists of two levels of contracts. Standard support includes TIPS (Technical Information Phone Service), updates and subscription service (product-specific troubleshooting guides and; *COMMENTS Magazine*). Basic support consists of updates and the subscription service. Contracts are sold in environments which represent product groupings (e.g., iRMX® environment).

#### CONSULTING SERVICES

Intel provides field system engineering consulting services for any phase of your development or application effort. You can use our system engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training and customizing an Intel product to providing technical and management consulting. Systems Engineers are well versed in technical areas such as microcommunications, real-time applications, embedded microcontrollers, and network services. You know your application needs; we know our products. Working together we can help you get a successful product to market in the least possible time.

#### **CUSTOMER TRAINING**

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to ten days a limited number of individuals learn more in a single workshop than in weeks of self-study. For optimum convenience, workshops are scheduled regularly at Training Centers worldwide or we can take our workshops to you for on-site instruction. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, BITBUS<sup>TM</sup> and LAN applications.

#### **NETWORK MANAGEMENT SERVICES**

Today's networking products are powerful and extremely flexible. The return they can provide on your investment via increased productivity and reduced costs can be very substantial.

Intel offers complete network support, from definition of your network's physical and functional design, to in plementation, installation and maintenance. Whether installing your first network or adding to an existing one, Intel's Networking Specialists can optimize network performance for you.

## Table of Contents

| Alphanumeric Index                                                                  | ix    |

|-------------------------------------------------------------------------------------|-------|

| CHAPTER 1                                                                           |       |

| Overview                                                                            |       |

| Introduction                                                                        | 1-1   |

|                                                                                     |       |

| CHAPTER 2                                                                           |       |

| 8086 Microprocessor Family                                                          |       |

| DATA SHEETS                                                                         |       |

| 8086 16-Bit HMOS Microprocessor                                                     | 2-1   |

| 80C86A 16-Bit CHMOS Microprocessor                                                  | 2-31  |

| 80C86AL 16-Bit CHMOS Microprocessor                                                 | 2-60  |

| 8088 8-Bit HMOS Microprocessor                                                      | 2-89  |

|                                                                                     | 2-119 |

| 80C88AL 8-Bit CHMOS Microprocessor                                                  | 2-151 |

|                                                                                     | 2-183 |

| 82C84A CHMOS Clock Generator and Driver for 80C86, 80C88 Processors                 | 2-205 |

| 82C88 CHMOS Bus Controller                                                          | 2-214 |

| 8237A High Performance Programmable DMA Controller                                  | 0.000 |

| (8237A, 8237A-4, 8237A-5)                                                           | 2-222 |

| 82C37A-5 CHMOS High Performance Programmable DMA Controller                         |       |

| 8259A/8259A-2/8259A-8 Programmable Interrupt Controller                             |       |

| 82C59A-2 CHMOS Programmable Interrupt Controller                                    | 2-203 |

| CHAPTER 3                                                                           |       |

| 80286 Microprocessor Family                                                         |       |

| DATA SHEETS                                                                         |       |

| 80286 High Performance Microprocessor with Memory Management and                    |       |

| Protection                                                                          | 3-1   |

| 80287 80-Bit HMOS Numeric Processor Extention                                       | 3-56  |

| 82258 Advanced Direct Memory Access Coprocessor                                     | 3-82  |

| 82288 Bus Controller for 80286 Processor                                            |       |

| (82288-12, 82288-10, 82288-8)                                                       | 3-141 |

| 82C288 Bus Controller for 80286 Processors                                          |       |

| (82C288-12, 82C288-10, 82C288-8)                                                    | 3-161 |

| 82C284 Clock Generator and Ready Interface for 80286 Processors                     |       |

| (82C284-12, 82C284-10, 82C284-8)                                                    | 3-182 |

| CHAPTER 4                                                                           |       |

| INTEL386™ Family                                                                    |       |

| DATA SHEETS                                                                         |       |

| 386 <sup>TM</sup> High Performance Microprocessor with Integrated Memory Management | 4-1   |

| 80387 80-Bit CHMOS III Numeric Processor Extension                                  | 4-133 |

| 82380 High Performance 32-Bit DMA Controller w/Integrated System                    |       |

| Support Peripherals                                                                 | 4-171 |

| 82385 High Performance 32-Bit Cache Controller                                      |       |

| 386SXTM Microprocessor                                                              |       |

| 80387SX 80-Bit Numeric Processor Extension                                          | 4-450 |

| 82310/82311 Micro Channel Compatible Peripheral Family                              | 4-488 |

| 82303 I/O Support Chip                                                              | 4-509 |

| 82304 I/O Support Chip                                                              | 4-519 |

| 82306 Local Channel Support Chip                                                    | 4-534 |

| 82307 DMA/Micro Channel Arbitration Controller                                      | 4-545 |

| 82308 Micro Channel Bus Controller (BC)                                             | 4-557 |

| 82309 Address Bus Controller (ABC)                                                  | 4-588 |

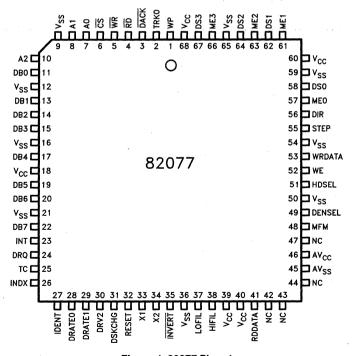

| 82077 Floppy Disk Controller                                                        | 4-617 |

| ***                                                                                 |       |

## Table of Contents (Continued)

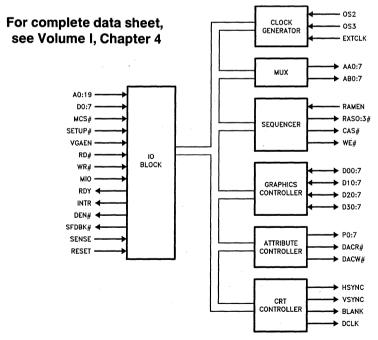

| 82706 Intel Video Graphics Array82335 High Integration Interface Device for 386SX™ Microprocessor Based | 4-618        |

|---------------------------------------------------------------------------------------------------------|--------------|

| PC-AT System                                                                                            |              |

| 82230/82231 High Integration AT*-Compatible Chip Set                                                    | 4-667        |

| 376™ High Performance 32-Bit Embedded Processor                                                         |              |

| CHAPTER 5                                                                                               |              |

| Memory Controllers                                                                                      |              |

| DATA SHEETS                                                                                             |              |

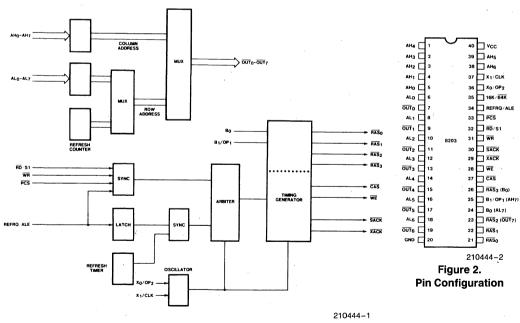

| 8203 64K Dynamic RAM Controller                                                                         | 5-1          |

| 8206 Error Detection and Correction Unit                                                                | 5-17<br>5-39 |

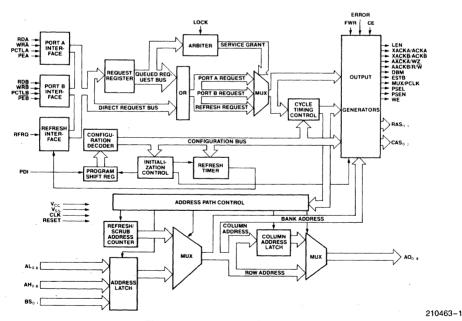

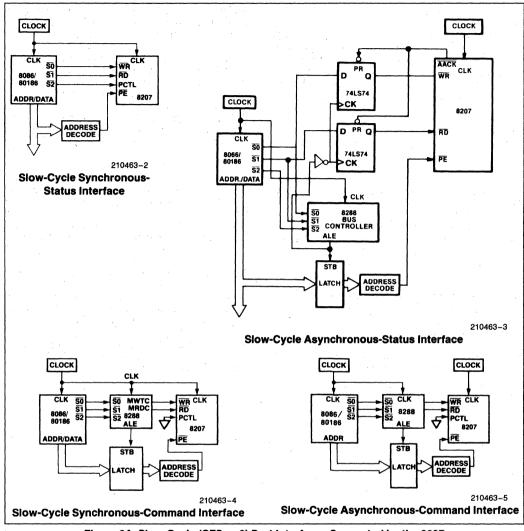

| 8207 Dual-Port Dynamic RAM Controller                                                                   | 5-39<br>5-86 |

| APPLICATION NOTES                                                                                       | 3-00         |

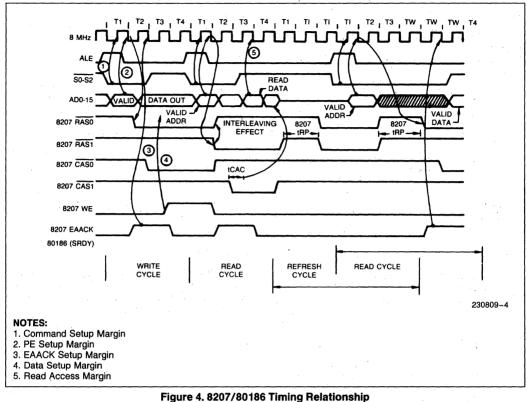

| Interfacing the 8207 Dynamic RAM Controller to the 80186 AP-167                                         | 5-115        |

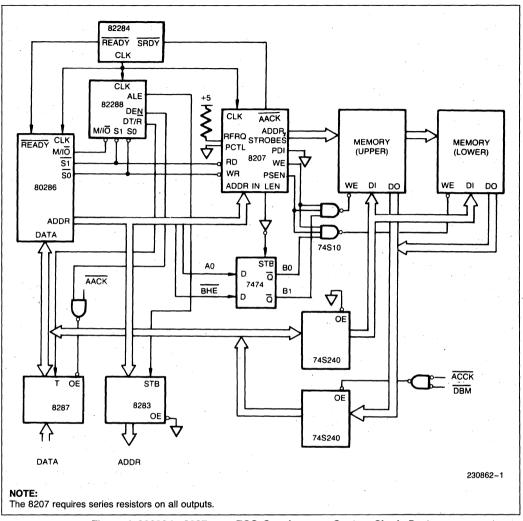

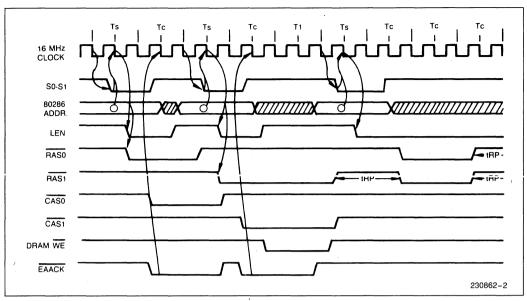

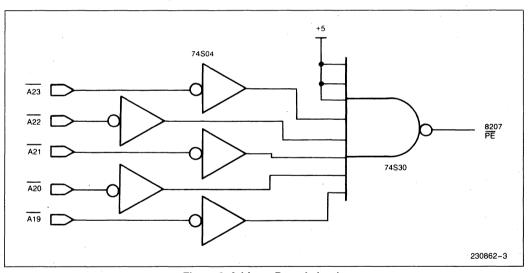

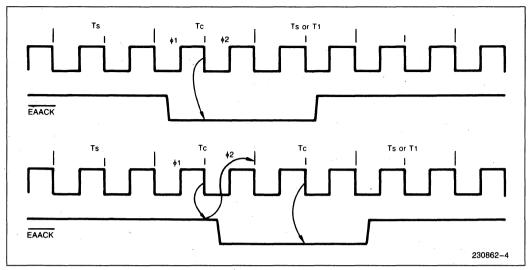

| Interfacing the 8207 Advanced Dynamic RAM Controller to the 80286 AP-168                                |              |

| CHAPTER 6                                                                                               |              |

| Support Peripherals                                                                                     |              |

| DATA SHEETS                                                                                             |              |

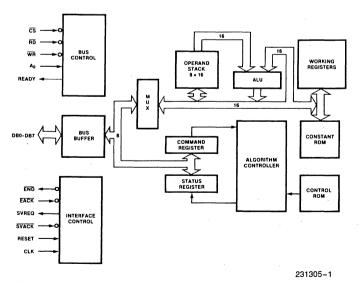

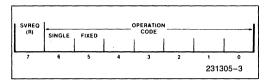

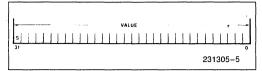

| 8231A Arithmetic Processing Unit                                                                        | 6-1          |

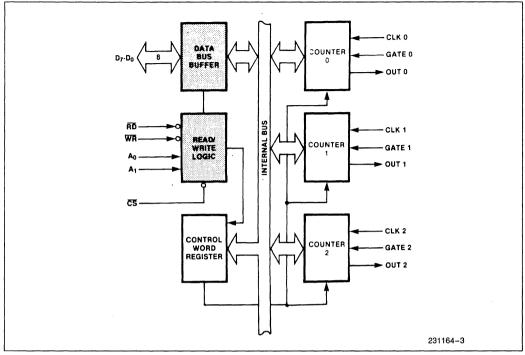

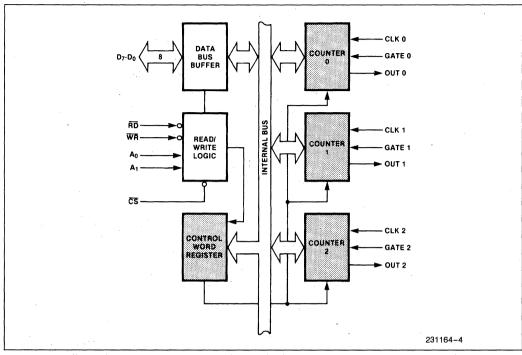

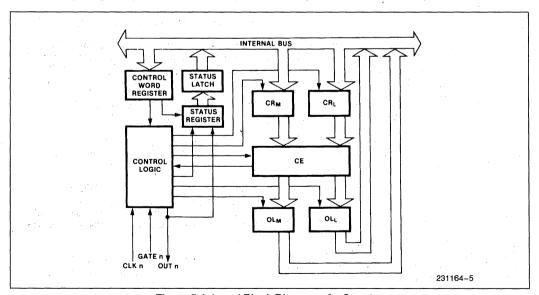

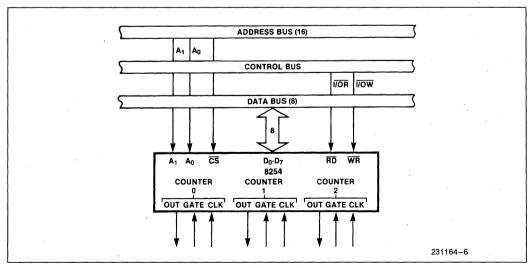

| 8253/8253-5 Programmable Interval Timer                                                                 | 6-14<br>6-25 |

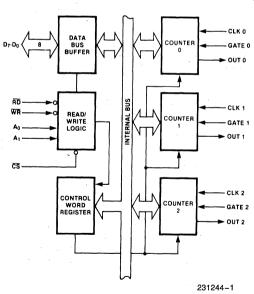

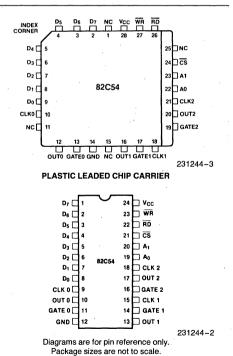

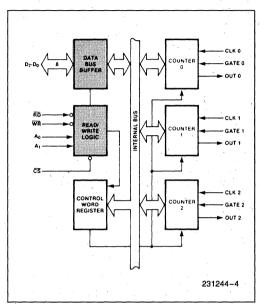

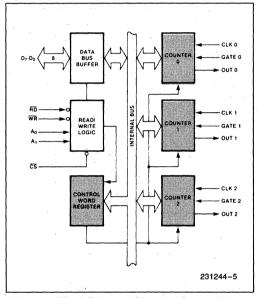

| 82C54 CHMOS Programmable Interval Timer                                                                 | 6-46         |

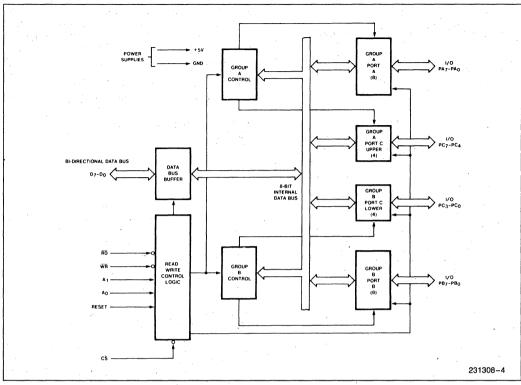

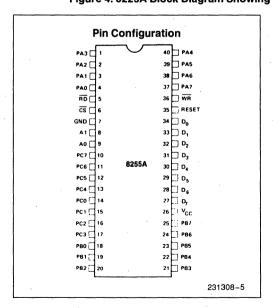

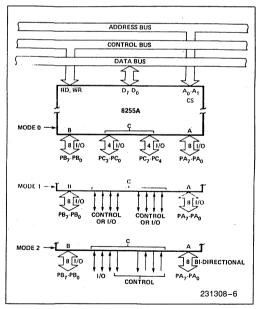

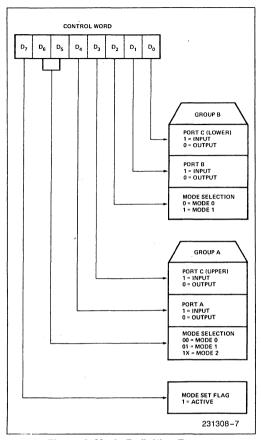

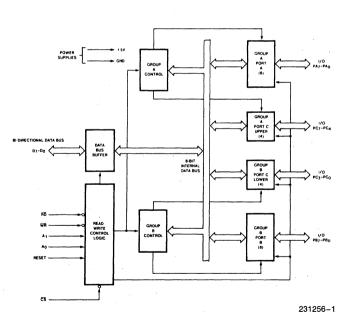

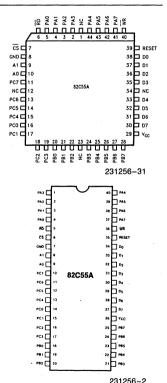

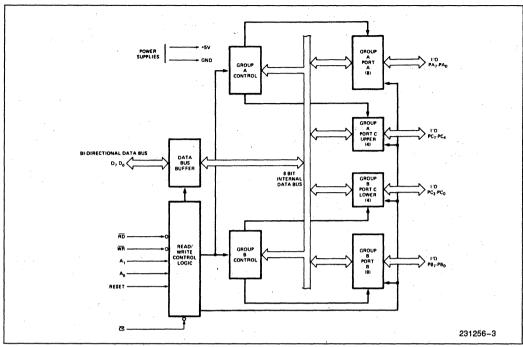

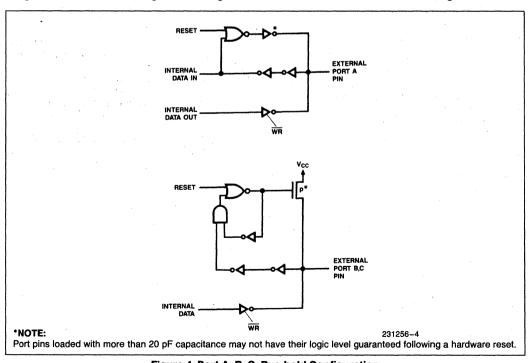

| 8255A/8255A-5 Programmable Peripheral Interface                                                         | 6-63         |

| 82C55A CHMOS Programmable Peripheral Interface                                                          | 6-87         |

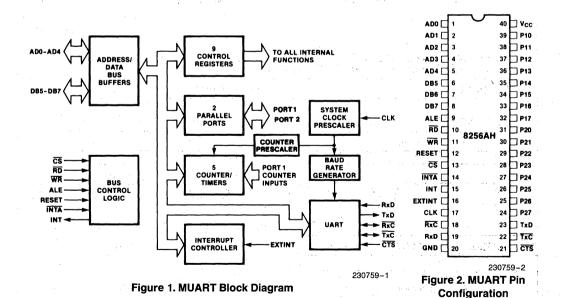

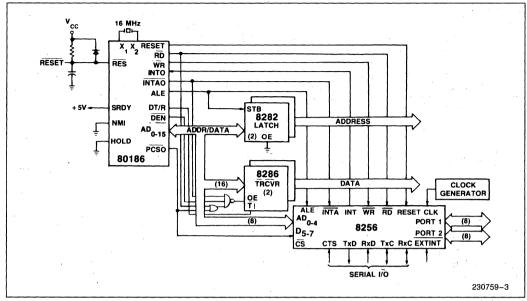

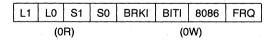

| 8256AH Multifunction Microprocessor Support Controller                                                  | 6-110        |

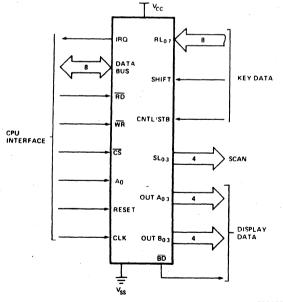

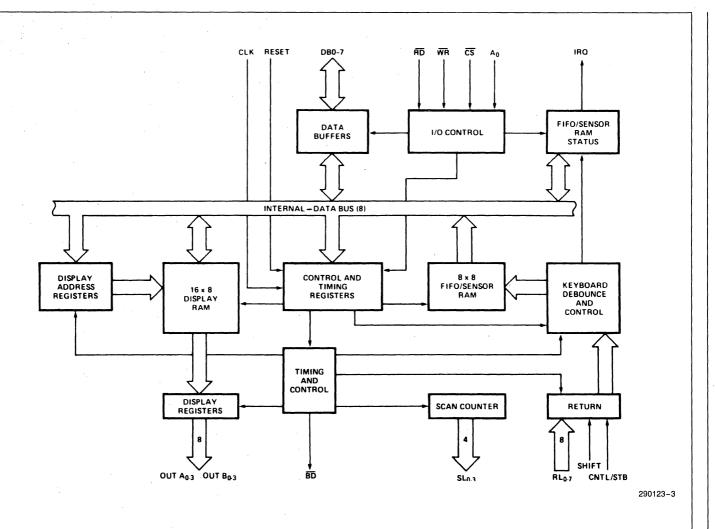

| 8279/8279-5 Programmable Keyboard/Display Interface                                                     | 6-134        |

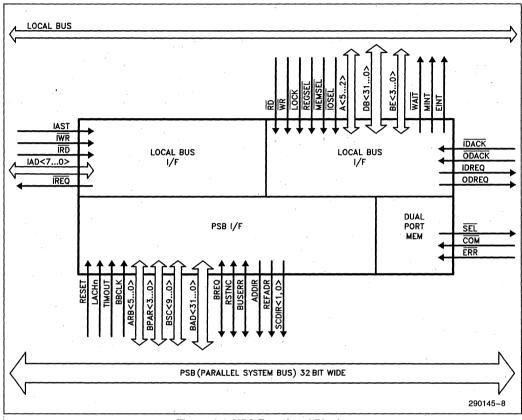

| 82389 Message Passing Coprocessor, A MULTIBUS™ II Bus Interface Controller .                            | 6-150        |

| CHAPTER 7                                                                                               |              |

| Floppy Disk Controllers                                                                                 |              |

| DATA SHEETS                                                                                             | 7.4          |

| 8272A Single/Double Density Floppy Disk Controller                                                      | 7-1<br>7-32  |

| APPLICATION NOTES                                                                                       | 7-32         |

| An Intelligent Data Base System Using the 8272 AP-116                                                   | 7-87         |

| Software Design and Implementation of Floppy Disk Systems AP-121                                        |              |

| CHAPTER 8                                                                                               |              |

| Hard Disk Controllers                                                                                   |              |

| DATA SHEET                                                                                              |              |

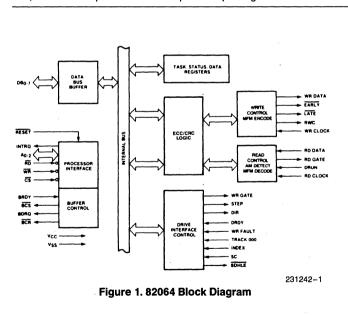

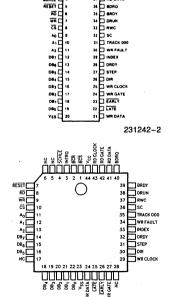

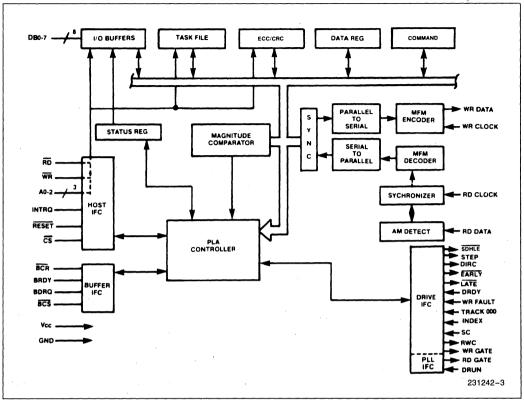

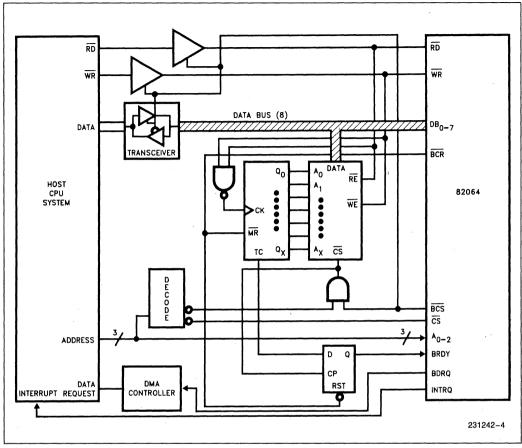

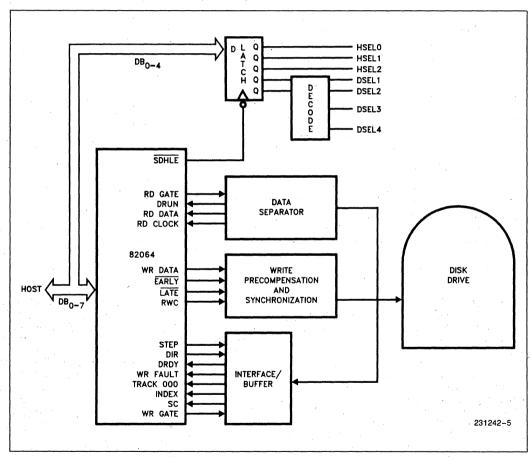

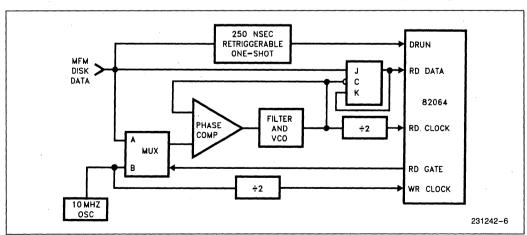

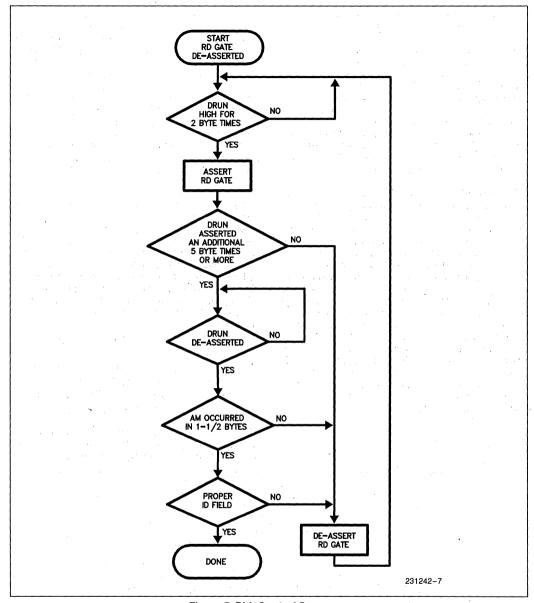

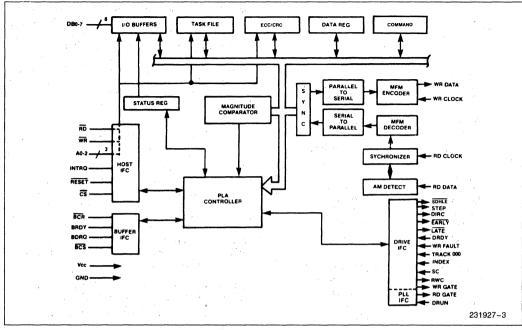

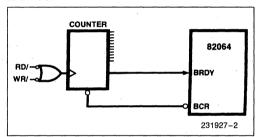

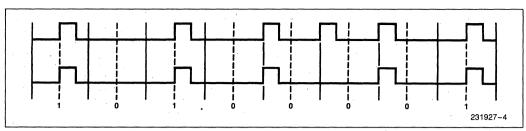

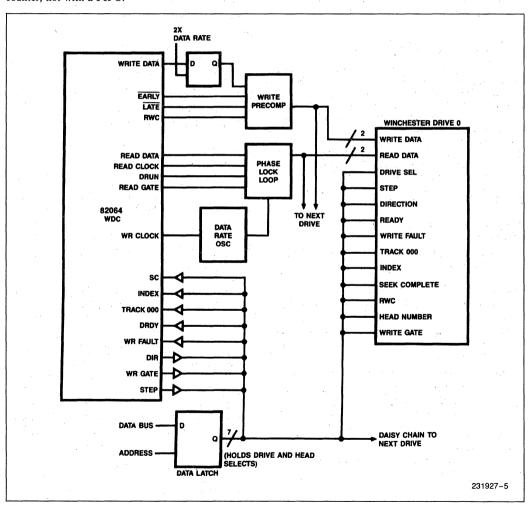

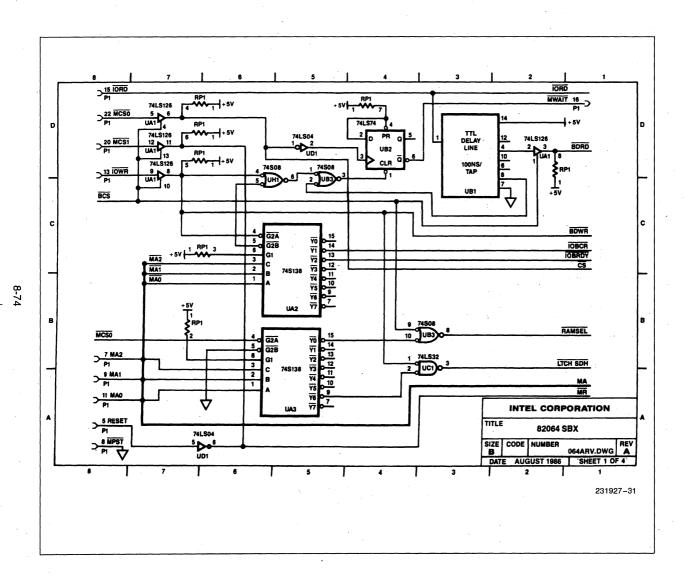

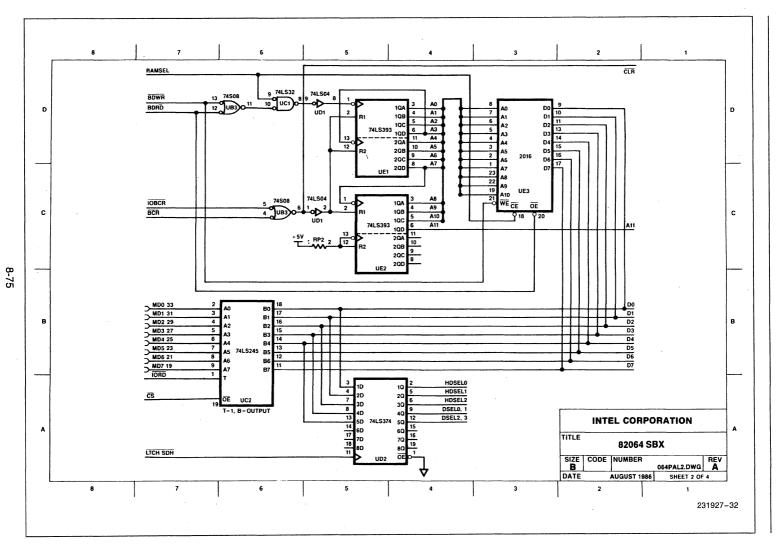

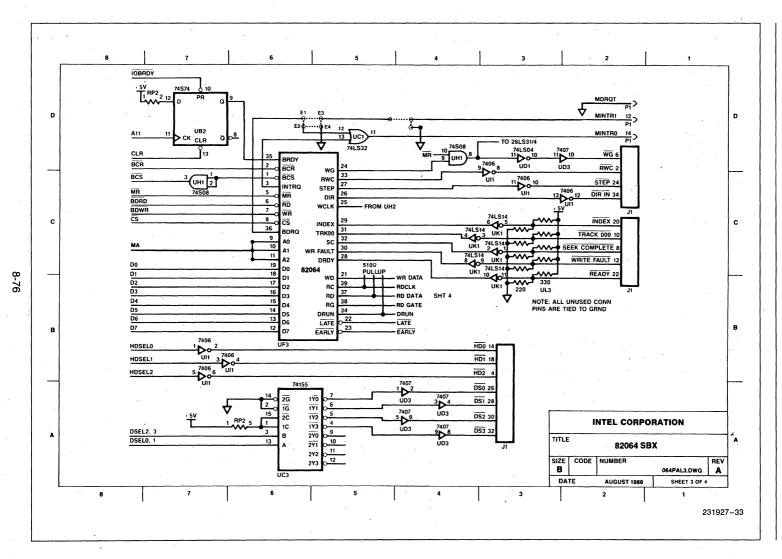

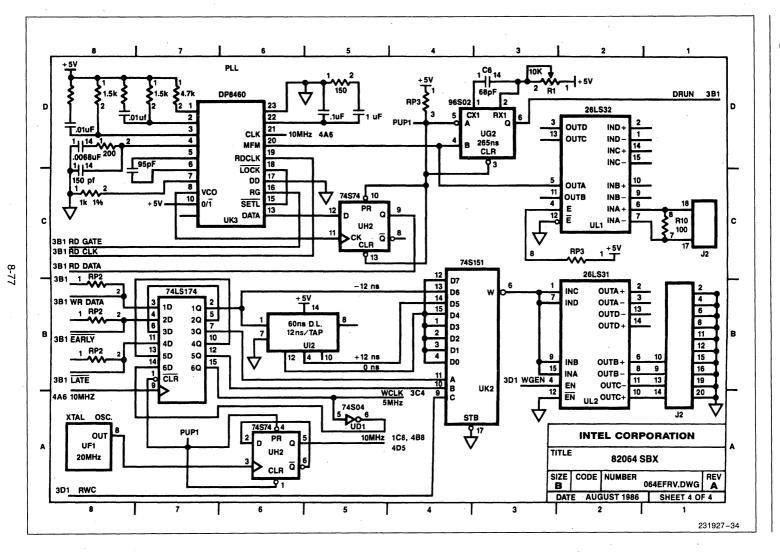

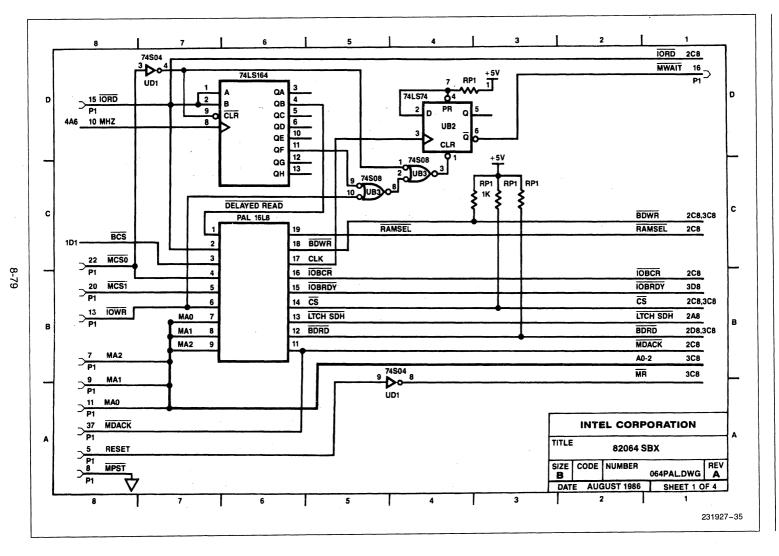

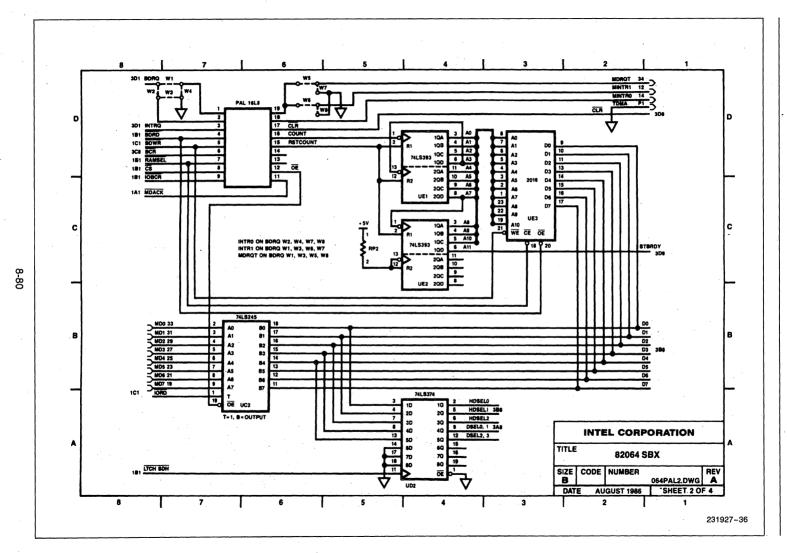

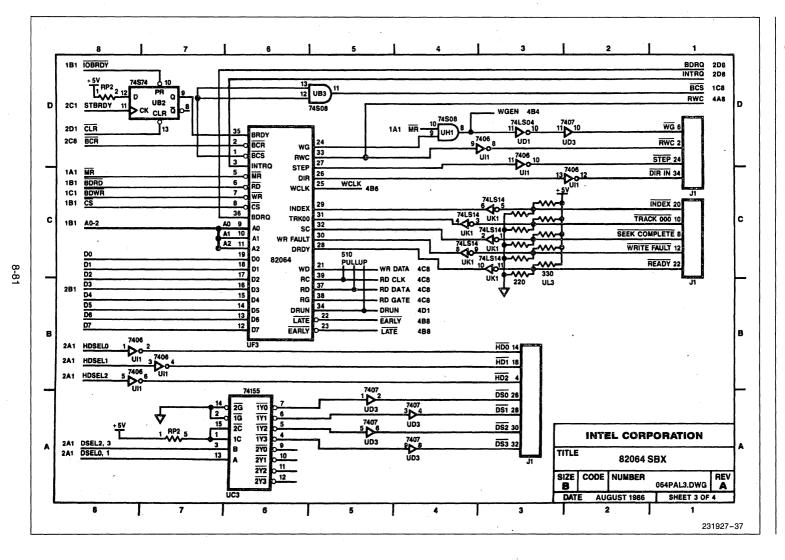

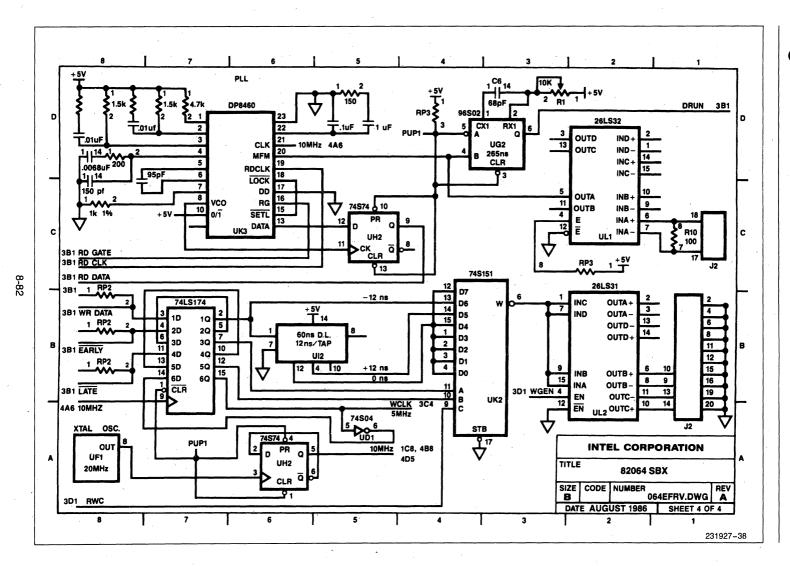

| 82064 CHMOS Winchester Disk Controller with On-Chip Error Detection and                                 |              |

| Correction APPLICATION NOTE                                                                             | 8-1          |

| Multimode™ Winchester Controller Using the CHMOS 82064 AP-402                                           | 8-33         |

| CHAPTER 9                                                                                               | 0 00         |

| Universal Peripheral Interface Slave Microcontrollers                                                   |              |

| DATA SHEETS                                                                                             |              |

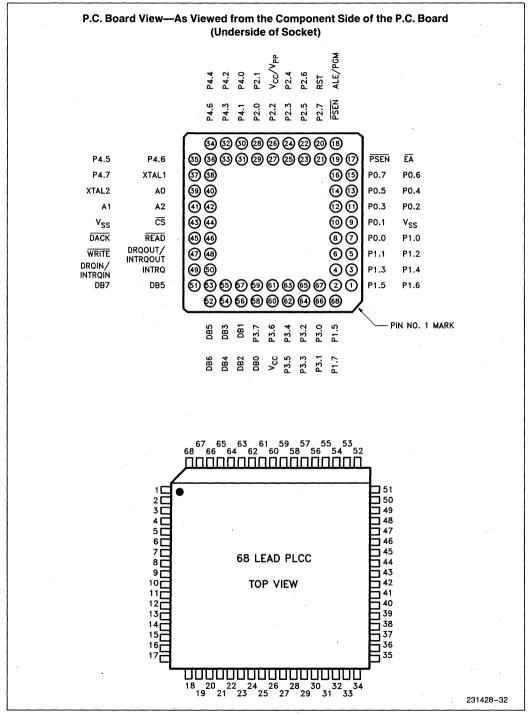

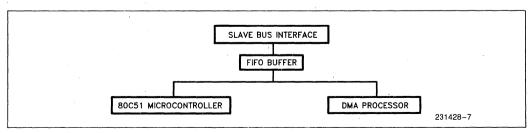

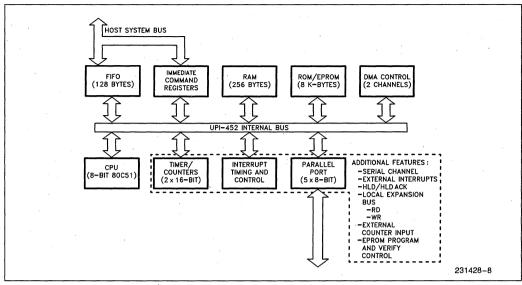

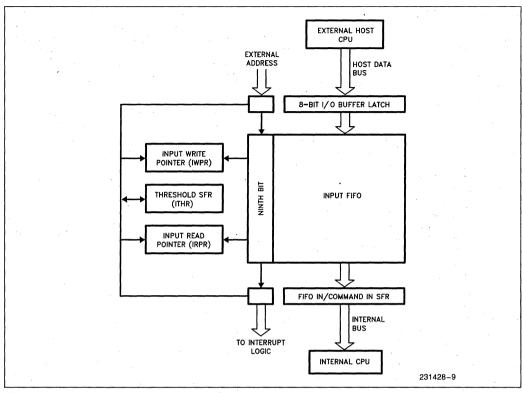

| UPITM-452 CHMOS Programmable I/O Processor (80/83/87452)                                                | 9-1          |

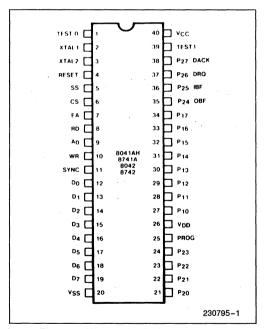

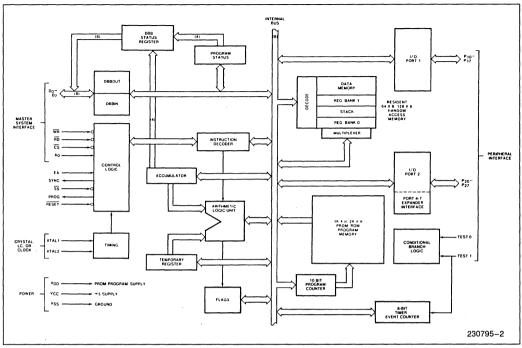

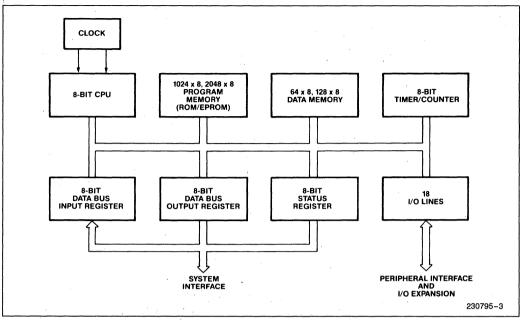

| UPI™-41, 42: 8041AH/8042AH/8741AH/8742AH Universal Peripheral Interface                                 |              |

| 8-Bit Slave Microcontroller                                                                             | 9-54         |

## Table of Contents (Continued)

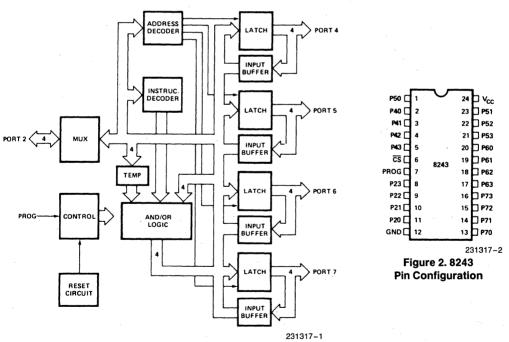

| 8243 MCS®-48 Input/Output Expander                                                        | 9-73            |

|-------------------------------------------------------------------------------------------|-----------------|

| APPLICATION NOTES Applications Using the 8042 UPI™ Microcontroller                        | 9-79            |

| Complex Peripheral Control with the UPITM-42 AP-161                                       | 9-83            |

| An 8741AH/8041A Digital Cassette Controller AP-90                                         |                 |

| UPITM-452 Accelerates iAPX 286 Bus Performance AP-281                                     | 9-145           |

| SYSTEM SUPPORT                                                                            |                 |

| ICETM-42 8042 In-Circuit Emulator                                                         | 9-165           |

| iUP-200A/iUP-201A Universal PROM Programmers                                              | 9-173           |

| CHAPTER 10                                                                                |                 |

| Graphics Coprocessor Family                                                               |                 |

| DATA SHEETS                                                                               |                 |

| 82706 Intel Video Graphics Array                                                          | 10-1            |

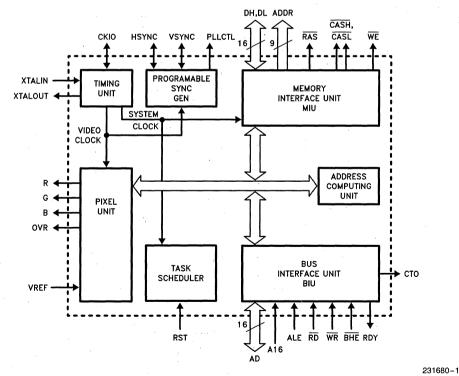

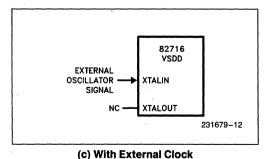

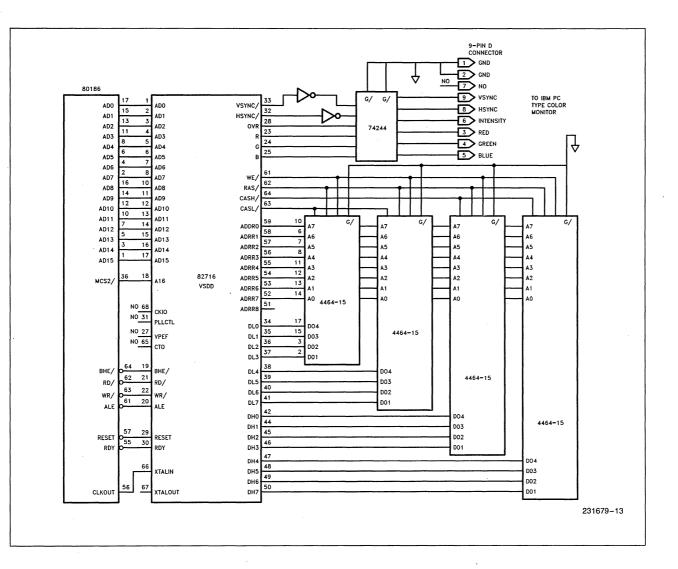

| 82716/VSDD Video Storage and Display Device                                               | 10-2            |

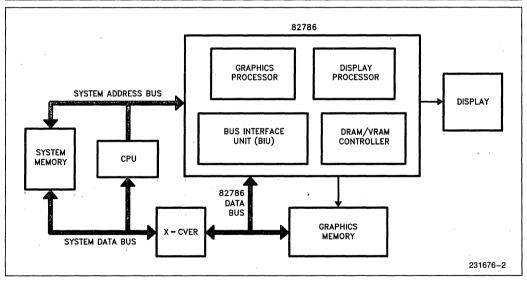

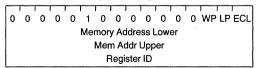

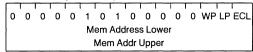

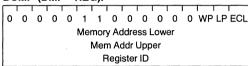

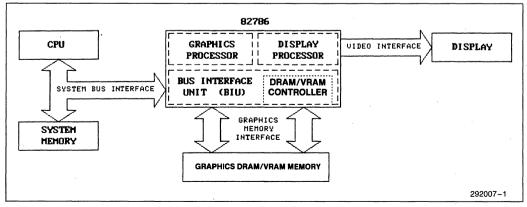

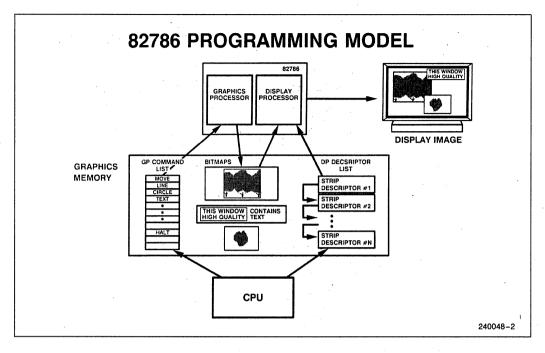

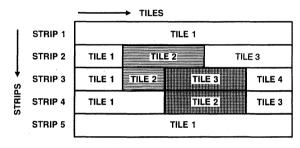

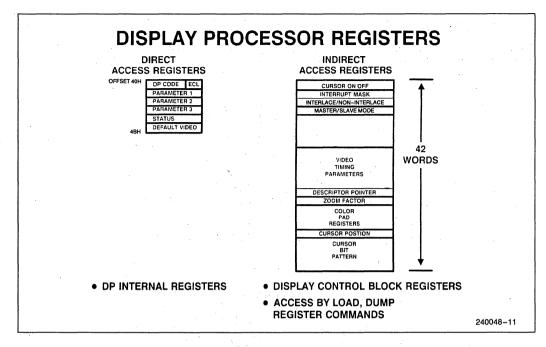

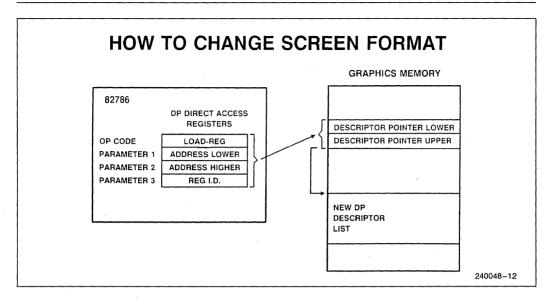

| 82786 CHMOS Graphics Coprocessor                                                          | 10-4            |

| APPLICATION NOTES                                                                         |                 |

| A Low Cost and High Integration Graphics System Using 82716 AP-268                        | 10-49           |

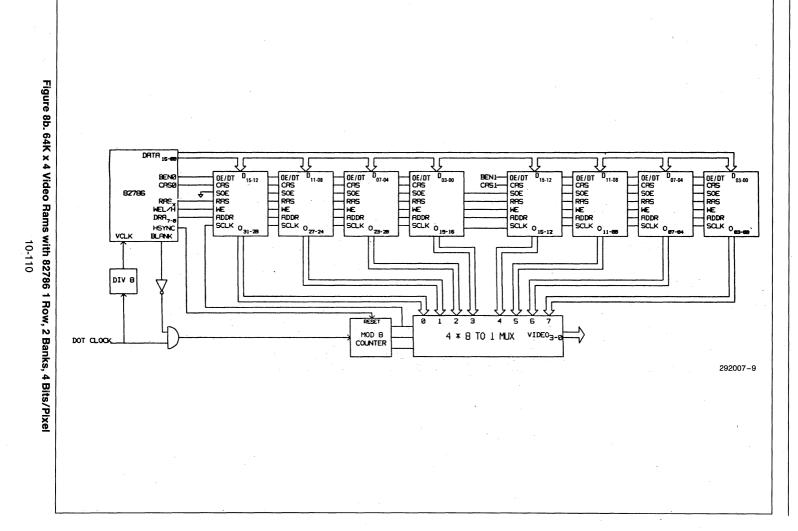

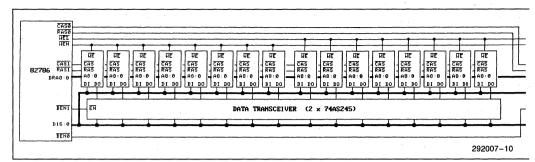

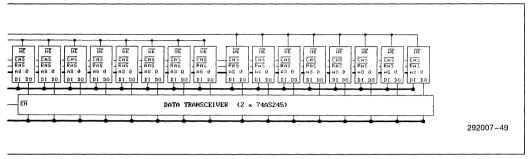

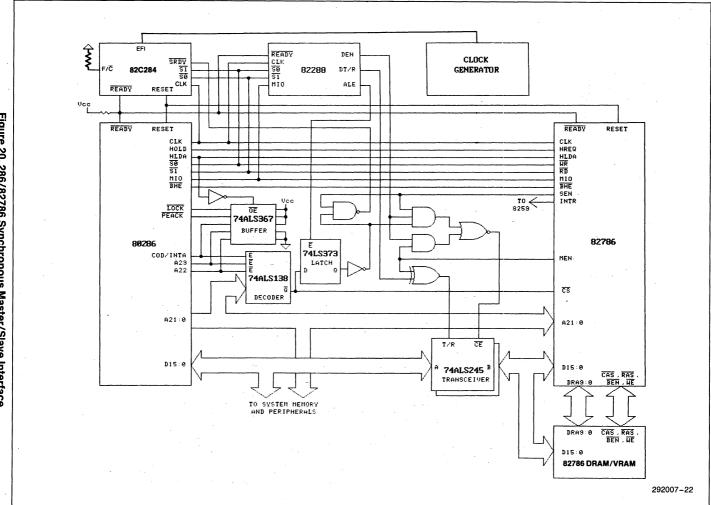

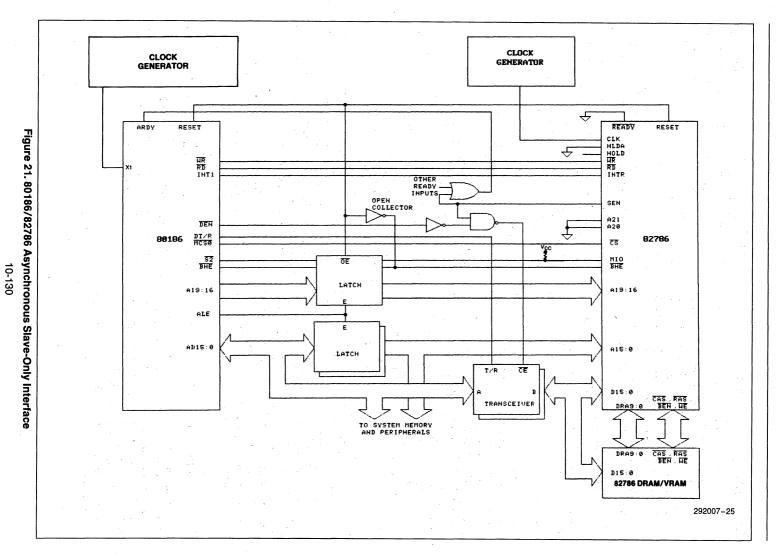

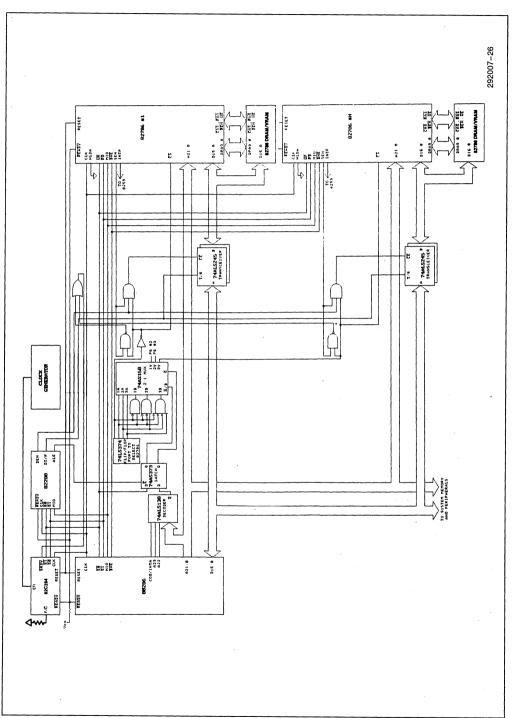

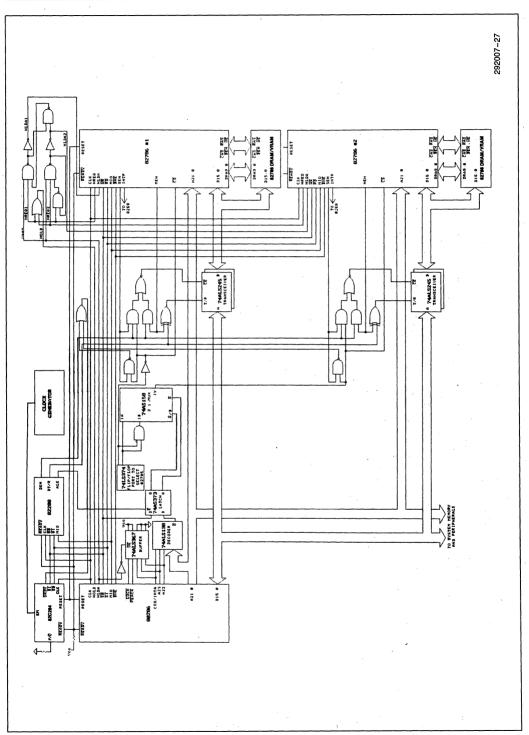

| 82786 Hardware Configuration AP-270                                                       | 10-101          |

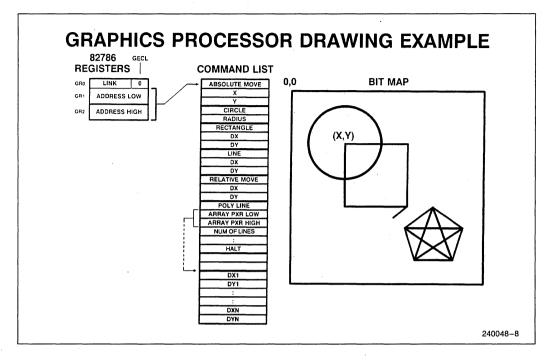

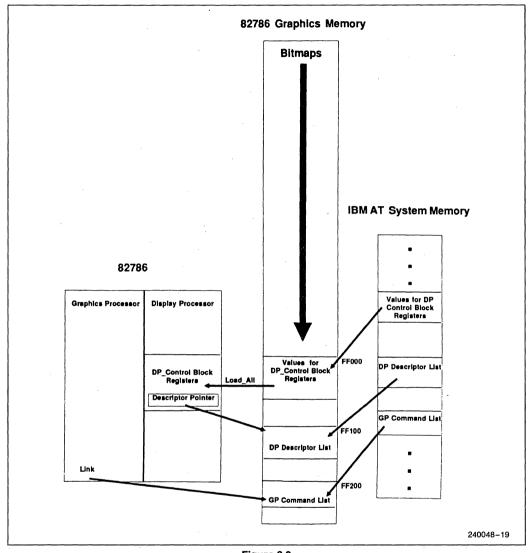

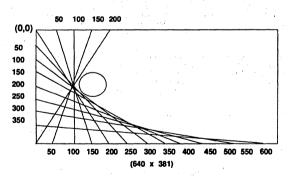

| An Introduction to Programming the 82786 Graphics Coprocessor AP-408                      | 10-162          |

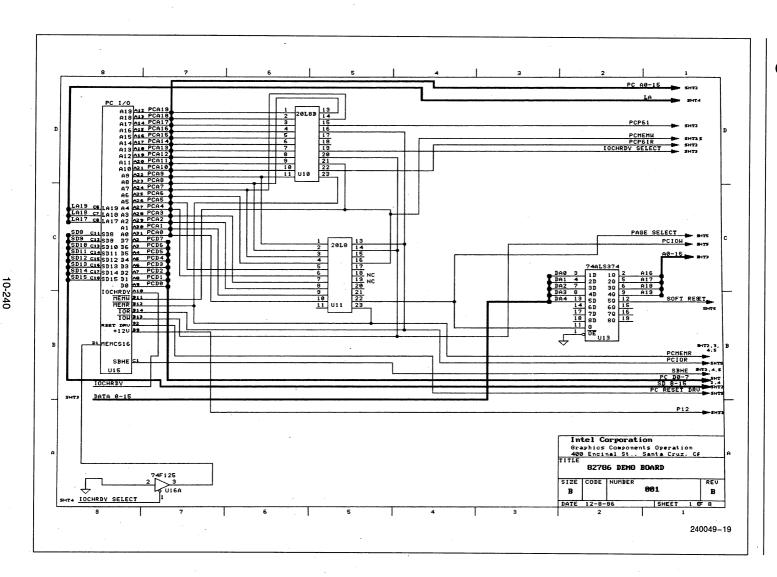

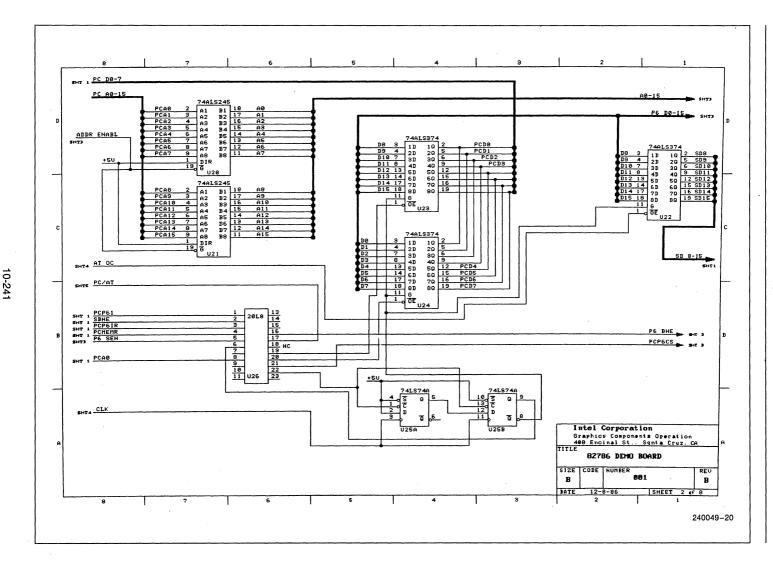

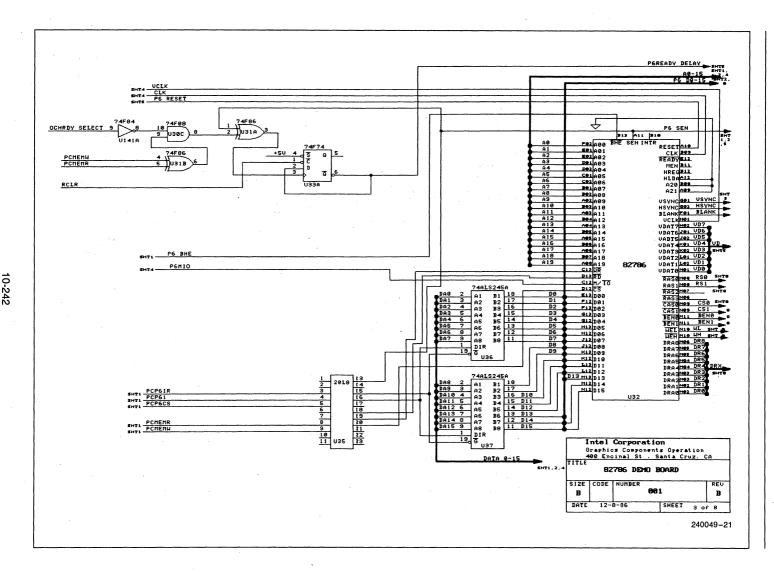

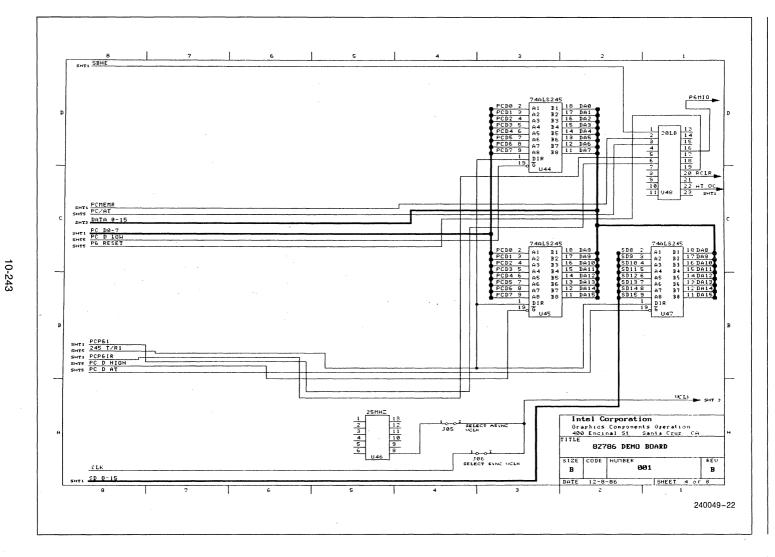

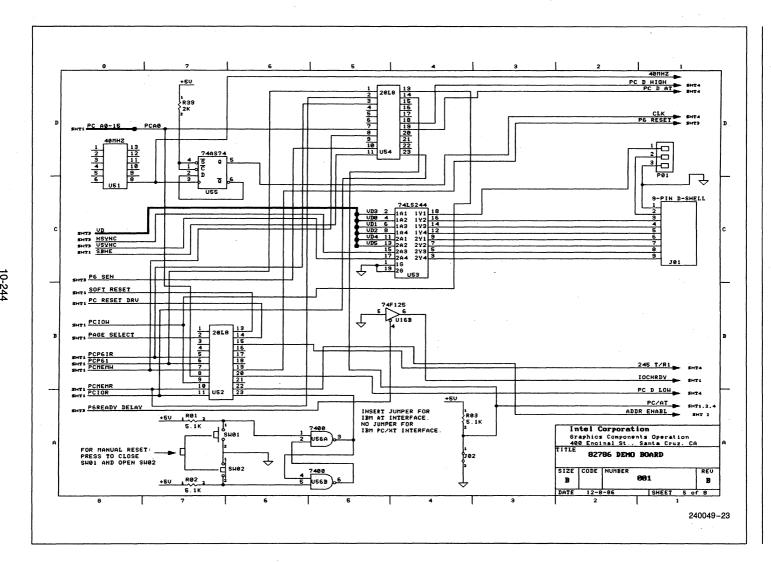

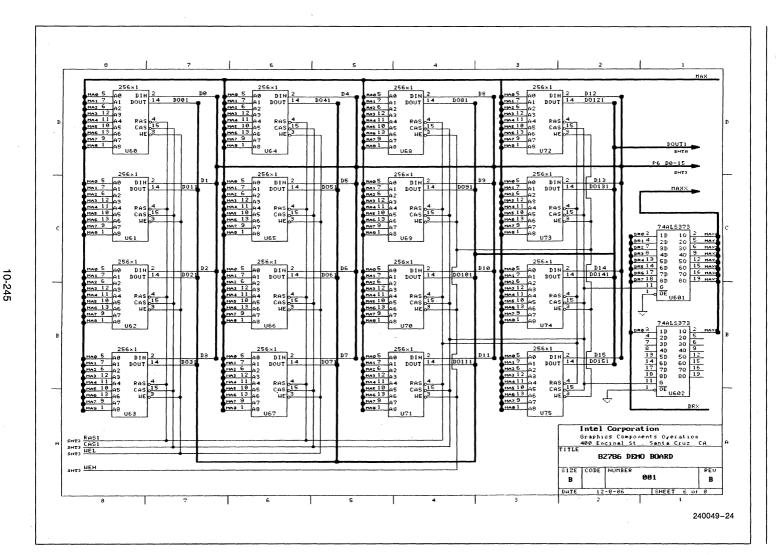

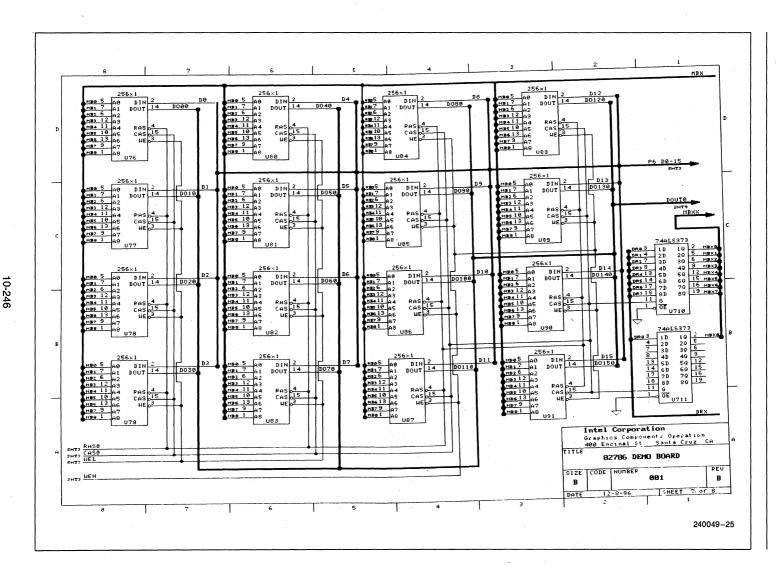

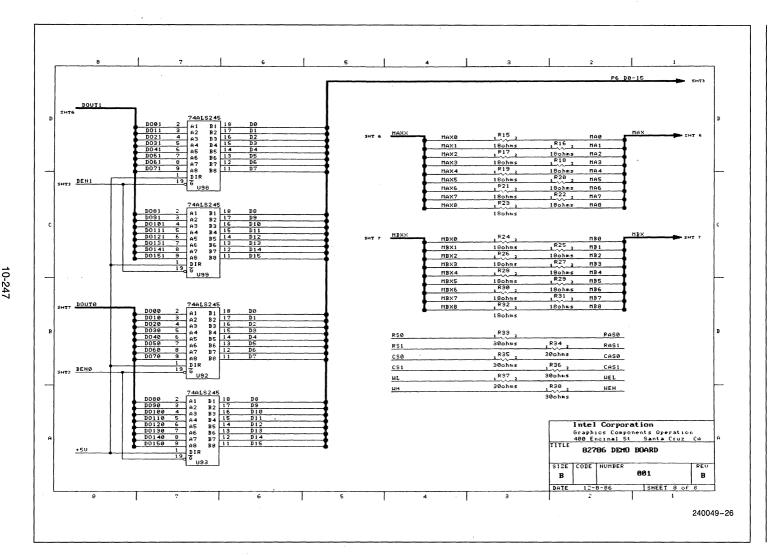

| 82786 Design Example Interfacing to the IBM PC/AT Computer AP-409                         | 10-222          |

| CHAPTER 11                                                                                |                 |

| Development Tools for the 8051, 8096, 8086/186/188, 80286, and 80386                      |                 |

| LANGUAGES AND SOFTWARE DEVELOPMENT TOOLS                                                  |                 |

| 8051 Software Packages Fact Sheet                                                         | 11-1            |

| 8096 Software Development Packages Fact Sheet                                             | 11-4            |

| VAX/VMS Resident Software Development Packages Data Sheet                                 |                 |

| 8086/80186 Software Development Packages Fact Sheet                                       |                 |

| 8087 Support Library Data Sheet                                                           | 11-19           |

| PSCOPE-86 for DOS High-Level Application Program Debugger Data Sheet                      | 11-23           |

| iC-86 C Compiler Fact Sheet                                                               | 11-30<br>11-33  |

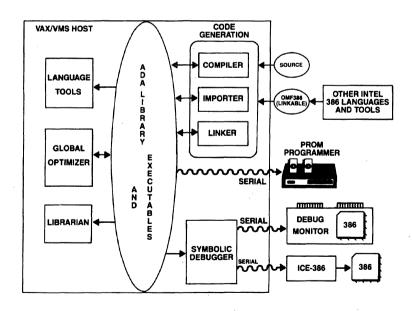

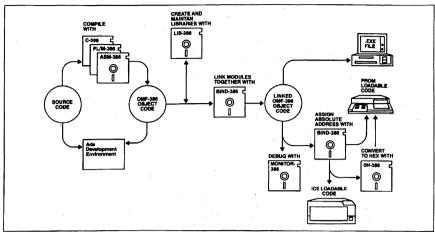

| Ada-386 Cross Development for the 386 <sup>TM</sup> Fact Sheet                            | 11-53           |

| Intel386™ Development Support Family Fact Sheet                                           | 11-55           |

| AEDIT Source Code and Text Editor Fact Sheet                                              |                 |

| iPATTM Performance Analysis Tool Fact Sheet                                               | 11-61           |

| IN-CIRCUIT EMULATORS                                                                      |                 |

| ICE™ 5100/452 In-Circuit Emulator Fact Sheet                                              | 11-65           |

| ICETM 5100/044 In-Circuit Emulator Fact Sheet                                             | 11-69           |

| ICE™ 5100/252 In-Circuit Emulator Fact Sheet                                              | 11-73           |

| ICE™ 5100/451 In-Circuit Emulator Fact Sheet                                              | 11-77           |

| VLSiCE™-96 In-Circuit Emulator Fact Sheet                                                 | 11-81           |

| Real-Time Transparent 80C196 In-Circuit Emulator Fact Sheet                               | 11-84           |

| ICE™-196KB/xX In-Circuit Emulators Fact Sheet                                             |                 |

| ICE™-186 In-Circuit Emulator Fact Sheet                                                   |                 |

| ICETM-188 In-Circuit Emulator Fact Sheet                                                  | 11-94           |

| I <sup>2</sup> ICE™ In-Circuit Emulation System Fact Sheet                                |                 |

|                                                                                           | 11-98           |

| ICETM-286 In-Circuit Emulator Fact Sheet Intel386TM Family Development Support Fact Sheet | 11-98<br>11-101 |

## Alphanumeric Index

| 286 Software Development Packages Data Sheet                                       | 11-33 |

|------------------------------------------------------------------------------------|-------|

| 376™ High Performance 32-Bit Embedded Processor                                    | 4-705 |

| 386SX <sup>TM</sup> Microprocessor                                                 | 4-354 |

| 386™ High Performance Microprocessor with Integrated Memory Management             | 4-1   |

| 80286 High Performance Microprocessor with Memory Management and Protection        | 3-1   |

| 80287 80-Bit HMOS Numeric Processor Extention                                      | 3-56  |

| 80387 80-Bit CHMOS III Numeric Processor Extension                                 | 4-133 |

| 80387SX 80-Bit Numeric Processor Extension                                         | 4-450 |

| 8051 Software Packages Fact Sheet                                                  | 11-1  |

| 8086 16-Bit HMOS Microprocessor                                                    | 2-1   |

| 8086/80186 Software Development Packages Fact Sheet                                | 11-15 |

| 8087 Support Library Data Sheet                                                    | 11-19 |

| 8087/8087-2/8087-1 Numeric Data Coprocessor                                        | 2-183 |

| 8088 8-Bit HMOS Microprocessor                                                     | 2-89  |

| 8096 Software Development Packages Fact Sheet                                      | 11-4  |

| 80C86A 16-Bit CHMOS Microprocessor                                                 | 2-31  |

| 80C86AL 16-Bit CHMOS Microprocessor                                                | 2-60  |

| 80C88A 8-Bit CHMOS Microprocessor                                                  | 2-119 |

| 80C88AL 8-Bit CHMOS Microprocessor                                                 | 2-151 |

| 8203 64K Dynamic RAM Controller                                                    | 5-1   |

| 8206 Error Detection and Correction Unit                                           | 5-17  |

| 82064 CHMOS Winchester Disk Controller with On-Chip Error Detection and Correction | 8-1   |

| 8207 Dual-Port Dynamic RAM Controller                                              | 5-39  |

| 82077 Floppy Disk Controller                                                       | 4-617 |

| 82077 Single Chip Floppy Disk Controller                                           | 7-32  |

| 82230/82231 High Integration AT*-Compatible Chip Set                               | 4-667 |

|                                                                                    | 3-82  |

| 82258 Advanced Direct Memory Access Coprocessor                                    | 3-141 |

|                                                                                    | 4-509 |

| 82303 I/O Support Chip                                                             | 4-509 |

| 82304 I/O Support Chip                                                             | 4-519 |

| 82306 Local Channel Support Chip                                                   |       |

| 82307 DMA/Micro Channel Arbitration Controller                                     | 4-545 |

| 82308 Micro Channel Bus Controller (BC)                                            | 4-557 |

| 82309 Address Bus Controller (ABC)                                                 | 4-588 |

| 82310/82311 Micro Channel Compatible Peripheral Family                             | 4-488 |

| 8231A Arithmetic Processing Unit                                                   | 6-1   |

| 82335 High Integration Interface Device for 386SX™ Microprocessor Based PC-AT      |       |

| System                                                                             | 4-636 |

| 82370 Integrated System Peripheral                                                 | 4-796 |

| 8237A High Performance Programmable DMA Controller (8237A, 8237A-4, 8237A-5)       | 2-222 |

| 82380 High Performance 32-Bit DMA Controller w/Integrated System                   |       |

| Support Peripherals                                                                | 4-171 |

| 82385 High Performance 32-Bit Cache Controller                                     | 4-292 |

| 82389 Message Passing Coprocessor, A MULTIBUS™ II Bus Interface Controller         | 6-150 |

| 8243 MCS®-48 Input/Output Expander                                                 | 9-73  |

| 8253/8253-5 Programmable Interval Timer                                            | 6-14  |

| 8254 Programmable Interval Timer                                                   | 6-25  |

| 8255A/8255A-5 Programmable Peripheral Interface                                    | 6-63  |

| 8256AH Multifunction Microprocessor Support Controller                             | 6-110 |

| 8259A/8259A-2/8259A-8 Programmable Interrupt Controller                            | 2-259 |

| 82706 Intel Video Graphics Array                                                   | 4-618 |

| 82706 Intel Video Graphics Array                                                   | 10-1  |

| 82716/VSDD Video Storage and Display Device                                        | 10-2  |

| 8272A Single/Double Density Floppy Disk Controller                                 | 7-1   |

## Alphanumeric Index (Continued)

| 82786 CHMOS Graphics Coprocessor                                               | 10-4    |

|--------------------------------------------------------------------------------|---------|

| 82786 Design Example Interfacing to the IBM PC/AT Computer AP-409              | 10-222  |

| 82786 Hardware Configuration AP-270                                            | 10-101  |

| 8279/8279-5 Programmable Keyboard/Display Interface                            | 6-134   |

| 82C08 CHMOS Dynamic RAM Controller                                             | 5-86    |

| 82C284 Clock Generator and Ready Interface for 80286 Processors                |         |

| (82C284-12, 82C284-10, 82C284-8)                                               | 3-182   |

| 82C288 Bus Controller for 80286 Processors (82C288-12, 82C288-10, 82C288-8)    | 3-161   |

| 82C37A-5 CHMOS High Performance Programmable DMA Controller                    |         |

| 82C54 CHMOS Programmable Interval Timer                                        | 6-46    |

| 82C55A CHMOS Programmable Peripheral Interface                                 | 6-87    |

| 82C59A-2 CHMOS Programmable Interrupt Controller                               | 2-283   |

| 82C84A CHMOS Clock Generator and Driver for 80C86, 80C88 Processors            | 2-205   |

| 82C88 CHMOS Bus Controller                                                     | 2-214   |

| A Low Cost and High Integration Graphics System Using 82716 AP-268             | 10-49   |

| Ada-386 Cross Development for the 386 <sup>TM</sup> Fact Sheet                 |         |

| AEDIT Source Code and Text Editor Fact Sheet                                   | 11-59   |

| An 8741AH/8041A Digital Cassette Controller AP-90                              | 9-138   |

| An Intelligent Data Base System Using the 8272 AP-116                          |         |

| An Introduction to Programming the 82786 Graphics Coprocessor AP-408           | 10-162  |

| Applications Using the 8042 UPITM Microcontroller                              | 9-79    |

| Applications Using the 8042 UPITM Microcontroller                              | 9-83    |

| iC-86 C Compiler Fact Sheet                                                    | 11-30   |

| ICETM 5100/044 In-Circuit Emulator Fact Sheet                                  | 11-69   |

| ICETM 5100/252 In-Circuit Emulator Fact Sheet                                  |         |

| ICETM 5100/451 In-Circuit Emulator Fact Sheet                                  |         |

| ICE™ 5100/452 In-Circuit Emulator Fact Sheet                                   |         |

| ICETM-186 In-Circuit Emulator Fact Sheet                                       | 11-90   |

| ICETM-188 In-Circuit Emulator Fact Sheet                                       |         |

| ICETM-196KB/xX In-Circuit Emulators Fact Sheet                                 | 11-86   |

| ICETM-286 In-Circuit Emulator Fact Sheet                                       |         |

| ICETM-42 8042 In-Circuit Emulator                                              |         |

| Intel386TM Development Support Family Fact Sheet                               | 11-55   |

| Intel386™ Family Development Support Fact Sheet                                | .11-104 |

| Interfacing the 8207 Advanced Dynamic RAM Controller to the 80286 AP-168       | 5-121   |

| Interfacing the 8207 Dynamic RAM Controller to the 80186 AP-167                | 5-115   |

| iPAT™ Performance Analysis Tool Fact Sheet                                     | 11-61   |

| iUP-200A/iUP-201A Universal PROM Programmers                                   | 9-173   |

| I <sup>2</sup> ICE™ In-Circuit Emulation System Fact Sheet                     | 11-98   |

| Multimode™ Winchester Controller Using the CHMOS 82064 AP-402                  |         |

| PSCOPE-86 for DOS High-Level Application Program Debugger Data Sheet           |         |

| Real-Time Transparent 80C196 In-Circuit Emulator Fact Sheet                    |         |

| Software Design and Implementation of Floppy Disk Systems AP-121               |         |

| UPITM-41, 42: 8041AH/8042AH/8741AH/8742AH Universal Peripheral Interface 8-Bit | 7-120   |

|                                                                                | 0.54    |

| Slave Microcontroller                                                          | 9-54    |

| UPITM-452 CHMOS Programmable I/O Processor (80/83/87452)                       |         |

| VAX/VMS Resident Software Development Packages Data Sheet                      |         |

| VAA/ VIVIO Resident Software Development Packages Data Sheet                   | 11-/    |

| VLSiCE™-96 In-Circuit Emulator Fact Sheet                                      | 11-81   |

Any of the following products may appear in this publication. If so, it must be noted that such products have counterparts manufactured by Intel Puerto Rico, Inc., Intel Puerto Rico II, Inc., and/or Intel Singapore, Ltd. The product codes/part numbers of these counterpart products are listed below next to the corresponding Intel Corporation product codes/part numbers.

| Intel Corporation<br>Product Codes/<br>Part Numbers | Intel Puerto Rico, Inc.<br>Intel Puerto Rico II, Inc.<br>Product Codes/<br>Part Numbers | Intel Singapore, Ltd.<br>Product Codes/<br>Part Numbers | Intel Corporation<br>Product Codes/<br>Part Numbers | Intel Puerto Rico, Inc.<br>Intel Puerto Ríco II, Inc.<br>Product Codes/<br>Part Numbers | Intel Singapore, Ltd.<br>Product Codes/<br>Part Numbers |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------|

| 376SKIT                                             | p376SKIT                                                                                |                                                         | KM2                                                 | pKM2                                                                                    |                                                         |

| 903                                                 | p903                                                                                    |                                                         | KM4                                                 | pKM4                                                                                    |                                                         |

| 904                                                 | p904                                                                                    |                                                         | KM8                                                 | pKM8                                                                                    |                                                         |

| 913                                                 | p913                                                                                    |                                                         | KNLAN                                               | pKNLAN                                                                                  |                                                         |

| 914                                                 | p914                                                                                    |                                                         | KT60                                                | pKT60                                                                                   |                                                         |

| 923                                                 | p923                                                                                    |                                                         | KW140                                               | pKW140                                                                                  |                                                         |

| 924                                                 | p924                                                                                    |                                                         | KW40                                                | pKW40                                                                                   |                                                         |

| 952                                                 | p952                                                                                    |                                                         | KW80                                                | pKW80                                                                                   |                                                         |

| 953                                                 | p953                                                                                    |                                                         | M1                                                  | pM1                                                                                     |                                                         |

| 954<br>ADAICE                                       | p954                                                                                    |                                                         | M2<br>M4                                            | pM2                                                                                     |                                                         |

| B386M1                                              | pADAICE<br>pB386M1                                                                      |                                                         | M8                                                  | pM4<br>pM8                                                                              |                                                         |

| B386M2                                              | pB386M2                                                                                 |                                                         | MDS610                                              | pMDS610                                                                                 |                                                         |

| B386M4                                              | pB386M4                                                                                 |                                                         | MDX3015                                             | pMD3010<br>pMDX3015                                                                     |                                                         |

| B386M8                                              | pB386M8                                                                                 |                                                         | MDX3015                                             | pMDX3015                                                                                |                                                         |

| C044KIT                                             | pC044KIT                                                                                |                                                         | MDX3015<br>MDX3016                                  | pMDX3015                                                                                |                                                         |

| C252KIT                                             | pC252KIT                                                                                |                                                         | MDX3016                                             | pMDX3016                                                                                |                                                         |

| C28                                                 | pC28                                                                                    |                                                         | MDX457                                              | pMDX457                                                                                 |                                                         |

| C32                                                 | pC32                                                                                    | ,                                                       | MDX457                                              | pMDX457                                                                                 |                                                         |

| C452KIT                                             | pC452KIT                                                                                |                                                         | MDX458                                              | pMDX458                                                                                 |                                                         |

| D86ASM                                              | pD86ASM                                                                                 |                                                         | MDX458                                              | pMDX458                                                                                 |                                                         |

| D86C86                                              | pD86C86                                                                                 |                                                         | MSA96                                               | pMSA96                                                                                  |                                                         |

| D86EDI                                              | pD86EDI                                                                                 |                                                         | NLAN                                                | pNLAN                                                                                   |                                                         |

| DCM9111                                             | pDCM9111                                                                                |                                                         | PCLINK                                              |                                                                                         | sPCĻINK                                                 |

| DOSNET                                              | pDOSNET                                                                                 |                                                         | PCX344A                                             | pPCX344A                                                                                |                                                         |

| F1                                                  | pF1                                                                                     |                                                         | R286ASM                                             | pR286ASM                                                                                |                                                         |

| GUPILOGICIID                                        | pGUPILOGICIID                                                                           |                                                         | R286EDI                                             | pR286EDI                                                                                |                                                         |

| H4                                                  | pH4                                                                                     |                                                         | R286PLM                                             | pR286PLM                                                                                |                                                         |

| I044<br>I252KIT                                     | pI044<br>pI252KIT                                                                       |                                                         | R286SSC                                             | pR286SSC                                                                                |                                                         |

| 1452KIT                                             | pI452KIT                                                                                |                                                         | R86FOR<br>RCB4410                                   | pR86FOR                                                                                 | sRCB4410                                                |

| I86ASM                                              | pI86ASM                                                                                 |                                                         | RCX920                                              | pRCX920                                                                                 | SRCD4410                                                |

| ICE386                                              | pICE386                                                                                 |                                                         | RMX286                                              | pRMX286                                                                                 |                                                         |

| III010                                              | pIII010                                                                                 |                                                         | RMXNET                                              | pRMXNET                                                                                 |                                                         |

| III086                                              | pIII086                                                                                 |                                                         | S301                                                | pS301                                                                                   |                                                         |

| III086                                              | TIII086                                                                                 |                                                         | S386                                                | pS386                                                                                   |                                                         |

| III111                                              | pIII111                                                                                 |                                                         | SBC010                                              | pSBC010                                                                                 |                                                         |

| III186                                              | pIII186                                                                                 |                                                         | SBC012                                              | pSBC012                                                                                 | sSBC012                                                 |

| III186                                              | TIII186                                                                                 |                                                         | SBC020                                              | pSBC020                                                                                 |                                                         |

| III198                                              | pIII198                                                                                 |                                                         | SBC028                                              | pSBC028                                                                                 |                                                         |

| III212                                              | pIII212                                                                                 | •                                                       | SBC040                                              | pSBC040                                                                                 |                                                         |

| III286                                              | pIII286                                                                                 |                                                         | SBC056                                              | pSBC056                                                                                 |                                                         |

| III286                                              | TII1286                                                                                 |                                                         | SBC108                                              | pSBC108                                                                                 |                                                         |

| III515                                              | pIII515                                                                                 |                                                         | SBC116                                              | pSBC116                                                                                 |                                                         |

| III520                                              | TIII520                                                                                 |                                                         | SBC18603                                            | pSBC18603                                                                               | sSBC18603                                               |

| III520                                              | pIII520                                                                                 |                                                         | SBC186410                                           | pSBC186410                                                                              | CDC10/f1                                                |

| III531                                              | pIII531                                                                                 |                                                         | SBC18651                                            | pSBC18651                                                                               | sSBC18651                                               |

| III532<br>III533                                    | pIII532<br>pIII533                                                                      |                                                         | SBC186530<br>SBC18678                               | pSBC186530                                                                              |                                                         |

| III621                                              | pIII621                                                                                 |                                                         | SBC18848                                            | pSBC18678<br>pSBC18848                                                                  | sSBC18848                                               |

| III707                                              | pIII021<br>pIII707                                                                      |                                                         | SBC18856                                            | pSBC18856                                                                               | sSBC18856                                               |

| III707<br>III707                                    | TIII707                                                                                 |                                                         | SBC208                                              | pSBC208                                                                                 | sSBC18830<br>sSBC208                                    |

| III815                                              | pIII815                                                                                 |                                                         | SBC208<br>SBC214                                    | pSBC214                                                                                 | 3020200                                                 |

| INA961                                              | pINA961                                                                                 |                                                         | SBC214<br>SBC215                                    | pSBC214<br>pSBC215                                                                      |                                                         |

| IPAT86                                              | pIPAT86                                                                                 |                                                         | SBC220                                              | pSBC220                                                                                 | sSBC220                                                 |

| KAS                                                 | pKAS                                                                                    |                                                         | SBC221                                              | pSBC221                                                                                 |                                                         |

| KC                                                  | pKC                                                                                     |                                                         | SBC28610                                            | pSBC28610                                                                               | sSBC28610                                               |

| KH                                                  | pKH                                                                                     |                                                         | SBC28612                                            | pSBC28612                                                                               | -                                                       |

| KM1                                                 | pKM1                                                                                    |                                                         | SBC28614                                            | pSBC28614                                                                               |                                                         |

| Intel Corporation<br>Product Codes/<br>Part Numbers | Intel Puerto Rico, Inc.<br>Intel Puerto Rico II, Inc.<br>Product Codes/<br>Part Numbers | Intel Singapore, Ltd.<br>Product Codes/<br>Part Numbers | Intel Corporation<br>Product Codes/<br>Part Numbers | Intel Puerto Rico, Inc.<br>Intel Puerto Rico II, Inc.<br>Product Codes/<br>Part Numbers | Intel Singapore, Ltd<br>Product Codes/<br>Part Numbers |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|

| SBC28616                                            | pSBC28616                                                                               |                                                         | SBCMEM310                                           | pSBCMEM310                                                                              |                                                        |

| SBC300                                              | pSBC300                                                                                 |                                                         | SBCMEM312                                           | pSBCMEM312                                                                              |                                                        |

| SBC301                                              | pSBC301                                                                                 |                                                         | SBCMEM320                                           | pSBCMEM320                                                                              |                                                        |

| SBC302                                              | pSBC302                                                                                 |                                                         | SBCMEM340                                           | pSBCMEM340                                                                              |                                                        |

| SBC304                                              | pSBC304                                                                                 |                                                         | SBE96                                               | pSBE96                                                                                  |                                                        |

| SBC307                                              | pSBC307                                                                                 |                                                         | SBX217                                              | pSBX217                                                                                 |                                                        |

| SBC314                                              | pSBC314                                                                                 |                                                         | SBX218                                              | pSBX218                                                                                 |                                                        |

| SBC322                                              | pSBC322                                                                                 |                                                         | SBX270                                              | pSBX270                                                                                 |                                                        |

| SBC324                                              | pSBC324                                                                                 |                                                         | SBX311                                              | pSBX311                                                                                 |                                                        |

| SBC337                                              | pSBC337                                                                                 |                                                         | SBX328                                              | pSBX328                                                                                 |                                                        |

| SBC341                                              | pSBC341                                                                                 |                                                         | SBX331                                              | pSBX331                                                                                 |                                                        |

| SBC386                                              | pSBC386                                                                                 | sSBC386                                                 | SBX344                                              | pSBX344                                                                                 |                                                        |

| SBC386116                                           | pSBC386116                                                                              |                                                         | SBX350                                              | pSBX350                                                                                 |                                                        |

| SBC386120                                           | pSBC386120                                                                              |                                                         | SBX351                                              | pSBX351                                                                                 |                                                        |

| SBC38621                                            | pSBC38621                                                                               |                                                         | SBX354                                              | pSBX354                                                                                 |                                                        |

| SBC38622                                            | pSBC38622                                                                               |                                                         | SBX488                                              | pSBX488                                                                                 |                                                        |

| SBC38624                                            | pSBC38624                                                                               |                                                         | SBX586                                              |                                                                                         | sSBX586                                                |

| SBC38628                                            | pSBC38628                                                                               | •                                                       | SCHEMAIIPLD                                         | pSCHEMAIIPLD                                                                            |                                                        |

| SBC38631                                            | pSBC38631                                                                               |                                                         | SCOM                                                | pSCOM                                                                                   |                                                        |

| SBC38632                                            | pSBC38632                                                                               |                                                         | SDK51                                               | pSDK51                                                                                  |                                                        |

| SBC38634                                            | pSBC38634                                                                               |                                                         | SDK85                                               | pSDK85                                                                                  |                                                        |

| SBC38638                                            | pSBC38638                                                                               |                                                         | SDK86                                               | pSDK86                                                                                  |                                                        |

| SBC428                                              | pSBC428                                                                                 | sSBC428                                                 | SXM217                                              | pSXM217                                                                                 |                                                        |

| SBC464                                              | pSBC464                                                                                 |                                                         | SXM28612                                            | pSXM28612                                                                               | ,                                                      |