**CHMOS Components Handbook**

intel

# CHMOS Components Handbook

# LITERATURE

In addition to the product line handbooks listed below, the INTEL PRODUCT GUIDE (no charge, Order No. 210846-003) provides an overview of Intel's complete product lines and customer services.

Consult the INTEL LITERATURE GUIDE (Order No. 210620) for a listing of Intel literature. TO ORDER literature in the U.S., write or call the INTEL LITERATURE DEPARTMENT, 3065 Bowers Avenue, Santa Clara, CA 95051, (800) 538-1876, or (800) 672-1833 (California only). TO ORDER literature from international locations, contact the nearest Intel sales office or distributor (see listings in the back of most any Intel literature).

Use the order blank on the facing page or call our TOLL FREE number listed above to order literature. Remember to add your local sales tax.

# **1985 HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information.

| QUALITY/RELIABILITY HANDBOOK (Order No. 210997-001)<br>Contains technical details of both quality and reliability programs and principles.            | *U.S. PRICE<br>\$15.00 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| CHMOS HANDBOOK (Order No. 290005-001)<br>Contains data sheets only on all microprocessor, peripheral, microcontroller and<br>memory CHMOS components. | \$12.00                |

| MEMORY COMPONENTS HANDBOOK (Order No. 210830-004)                                                                                                     | \$18.00                |

| TELECOMMUNICATION PRODUCTS HANDBOOK (Order No. 230730-003)                                                                                            | \$12.00                |

| MICROCONTROLLER HANDBOOK (Order No. 210918-003)                                                                                                       | \$18.00                |

| <b>MICROSYSTEM COMPONENTS HANDBOOK (Order No. 230843-002)</b><br>Microprocessors and peripherals—2 Volume Set                                         | \$25.00                |

| DEVELOPMENT SYSTEMS HANDBOOK (Order No. 210940-003)                                                                                                   | \$15.00                |

| OEM SYSTEMS HANDBOOK (Order No. 210941-003)                                                                                                           | \$18.00                |

| SOFTWARE HANDBOOK (Order No. 230786-002)                                                                                                              | \$12.00                |

| MILITARY HANDBOOK (Order No. 210461-003)<br>Not available until June.                                                                                 | \$15.00                |

| <b>COMPLETE SET OF HANDBOOKS (Order No. 231003-002)</b><br>Get a 25% discount off the retail price of \$160.                                          | \$120.00               |

# **U.S. LITERATURE ORDER FORM**

| NAME:                                                                                                             | TITLE:                                                                                                        |                                        |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------|

| COMPANY:                                                                                                          |                                                                                                               |                                        |

| ADDRESS:                                                                                                          |                                                                                                               |                                        |

| CITY:                                                                                                             | STATE: ZIP: .                                                                                                 |                                        |

| COUNTRY:                                                                                                          |                                                                                                               |                                        |

| PHONE NO.: ()                                                                                                     |                                                                                                               |                                        |

| ORDER NO.                                                                                                         | TITLE     QTY.     PRICI                                                                                      | - =<br>- =<br>- =<br>- =<br>- =<br>- = |

| Allow 4–6 weeks for delivery                                                                                      | Total                                                                                                         |                                        |

| Pay by Visa, MasterCard, Check or N<br>have a \$50.00 minimum.                                                    | Money Order, payable to Intel Literature. Purc                                                                | hase Orders                            |

| Visa Account No MasterCard                                                                                        | Expiration Date                                                                                               |                                        |

| Signature:                                                                                                        |                                                                                                               |                                        |

| Mail To: Intel Literature Distribution<br>Mail Stop SC6-714<br>3065 Bowers Avenue<br>Santa Clara, CA 95051.       | Customers outside the U.S. and Canad<br>tact the local Intel Sales Office or Distri<br>the back of this book. |                                        |

| For information on quantity discour<br>TOLL-FREE NUMBER: (800) 548-47<br>Prices good until 12/31/85.<br>Source HB |                                                                                                               |                                        |

intel®

Mail To: Intel Literature Distribution Mail Stop SC6-714 3065 Bowers Avenue Santa Clara, CA 95051.

intط

# CHMOS COMPONENTS HANDBOOK

1985

About Our Cover: The design on our front cover is an abstract portrayal of the state-of-the-art technology provided by Intel's CHMOS Components to the low power, high performance kit solution. Intel has a complete kit, advanced technology, high performance and reliability, low power and open-ended access. Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BITBUS, COMMputer, CREDIT, Data Pipeline, GENIUS, i, <sup>1</sup>/<sub>1</sub>, ICE, iCS, iDBP, iDIS, I<sup>2</sup>ICE, iLBX, i<sub>m</sub>, iMDDX, iMMX, Insite, Intel, int<sub>e</sub>l, int<sub>e</sub>lBOS, Intelevision, int<sub>e</sub>ligent Identifier, int<sub>e</sub>ligent Programming, Intellec, Intellink, iOSP, iPDS, iRMX, iSBC, iSBX, iSDM, iSXM, KEPROM, Library Manager, MCS, Megachassis, MICROMAINFRAME, MULTIBUS, MULTICHANNEL, MULTIMODULE, OpeNET, Plug-A-Bubble, PROMPT, Promware, QUEST, QueX, Ripplemode, RMX/80, RUPI, Seamless, SLD, SYSTEM 2000, and UPI, and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

HMOS and CHMOS are patented processes of Intel Corporation.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Department 3065 Bowers Avenue Santa Clara, CA 95051

©INTEL CORPORATION 1984

# **Table of Contents**

| Alphanumeric Index                                                                                                                                                                                                                                                                                                                                                             |                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| CHAPTER 1<br>CHMOS Technology Overview                                                                                                                                                                                                                                                                                                                                         | 1-1                          |

| CHAPTER 2<br>Memory Components<br>DRAMs (Dynamic Random Access Memories)                                                                                                                                                                                                                                                                                                       |                              |

| 51C64H, High Performance Ripplemode 64K x 1 CHMOS Dynamic RAM<br>51C64L, Low Power 64K x 1 CHMOS Dynamic RAM<br>51C64HL, High Performance Low Power Ripplemode 64K x 1                                                                                                                                                                                                         | 2-1<br>2-21                  |

| CHMOS Dynamic RAM<br>51C256H, High Performance Ripplemode 256K x 1 CHMOS Dynamic RAM<br>51C256L, Low Power 256K x 1 CHMOS Dynamic RAM<br>51C256HL, High Performance Low Power Ripplemode 256K x 1                                                                                                                                                                              | 2-55                         |

| CHMOS Dynamic RAM<br>51C259H, High Performance Static Column 64K x 4 CHMOS Dynamic RAM<br>51C259L, Low Power 64K x 4 CHMOS Dynamic RAM<br>51C259HL, High Performance Low Power Static Column 64K x 4                                                                                                                                                                           | 2-103                        |

| CHMOS Dynamic RAM                                                                                                                                                                                                                                                                                                                                                              | 2-132                        |

| 51C67, High Speed CHMOS 16,384 x 1-Bit Static RAM<br>81C28 Family, 2048 x 8-Bit Low Power, High Integration Static RAM<br>EPROMs (Erasable Programmable Read Only Memories)                                                                                                                                                                                                    | 2-154                        |

| 27C64/87C64 64K (8K x 8) CHMOS UV Erasable PRÓM                                                                                                                                                                                                                                                                                                                                | 2-160                        |

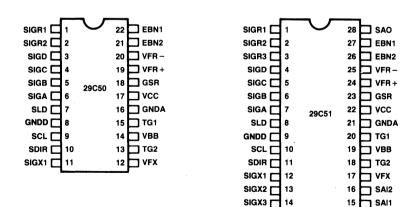

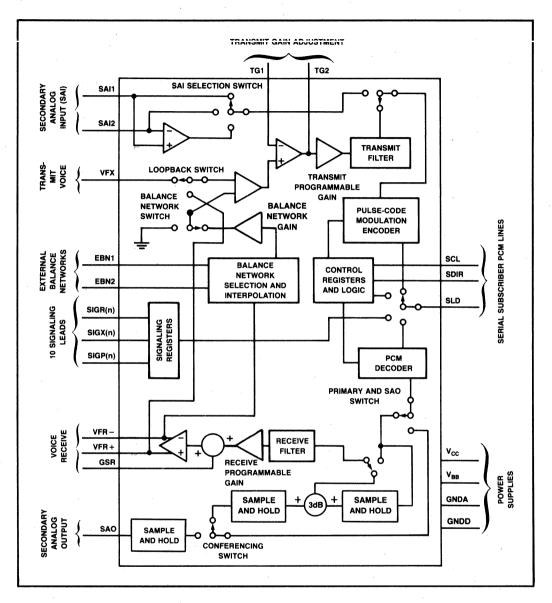

| Telecommunications Components         iATC 29C50 and 29C51, Feature Control Combo         29C13 and 29C14, CHMOS Combined Single-Chip PCM Codec and Filter         29C16 and 29C17, 16 Pin CHMOS Single-Chip PCM Codec and Filter                                                                                                                                              |                              |

| CHAPTER 4                                                                                                                                                                                                                                                                                                                                                                      |                              |

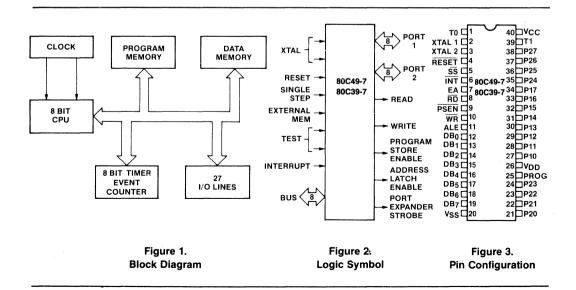

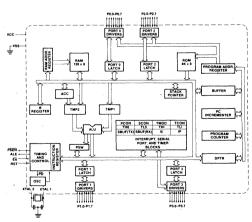

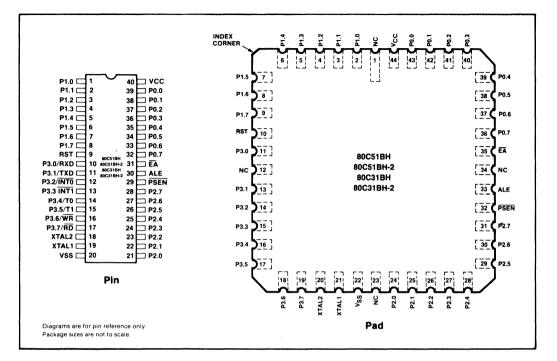

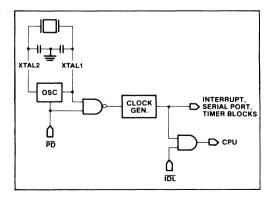

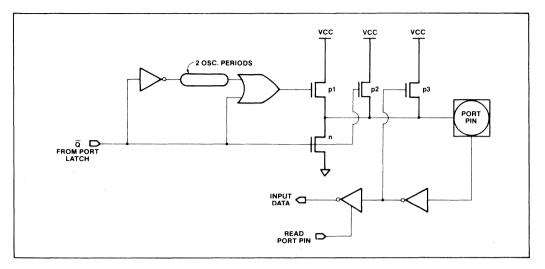

| Microcontrollers<br>80C49-7/80C39-7, CHMOS Single-Component 8-Bit Microcomputer<br>80C51BH/80C51BH-2 80C31BH/80C31BH-2, CHMOS Single-Component 8-Bit<br>Microcontroller                                                                                                                                                                                                        |                              |

| CHAPTER 5                                                                                                                                                                                                                                                                                                                                                                      | 4-10                         |

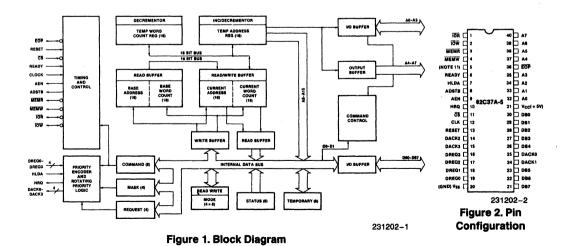

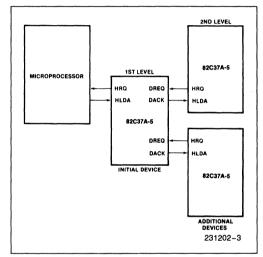

| Microprocessors<br>80C86/80C86-2, 16-Bit CHMOS Microprocessor<br>80C88/80C88-2, 8-Bit CHMOS Microprocessor<br>82C37A-5, CHMOS High Performance Programmable DMA Controller<br>82C59A-2, CHMOS Programmable Interrupt Controller<br>82C84A/82C84A-5, CHMOS Clock Generator and Driver for<br>80C86, 80C88 Processors<br>82C88, CHMOS Bus Controller for 80C86, 80C88 Processors | 5-28<br>5-57<br>5-67<br>5-87 |

| CHAPTER 6                                                                                                                                                                                                                                                                                                                                                                      | 0.00                         |

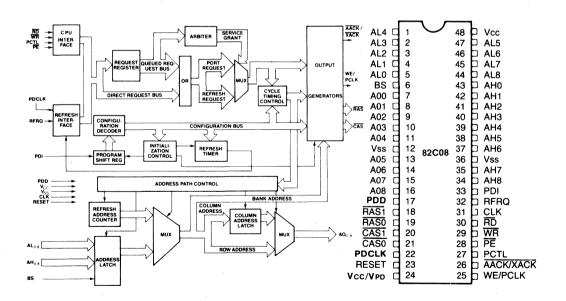

| Peripherals<br>82C08, CHMOS Dynamic RAM Controller<br>82C54, CHMOS Programmable Interval Timer<br>82C55A, CHMOS Programmable Peripheral Interface                                                                                                                                                                                                                              | 6-1<br>6-7<br>6-24           |

| CHAPTER 7<br>Additional References                                                                                                                                                                                                                                                                                                                                             | 7-1                          |

# Alphanumeric Index

| iATC 29C50 and 29C51, Feature Control Combo3-127C64/87C64, 64K (8K x 8) CHMOS UV Erasable PROM2-16029C13 and 29C14, CHMOS Combined Single-Chip PCM Codec and Filter3-2029C16 and 29C17, 16 Pin CHMOS Single-Chip PCM Codec and Filter3-3951C64H, High Performance Ripplemode 64K x 1 CHMOS Dynamic RAM2-151C64L, Low Power 64K x 1 CHMOS Dynamic RAM2-2151C64HL, High Performance Low Power Ripplemode 64K x 1 CHMOS Dynamic RAM2-3551C67, High Speed CHMOS 16,384 x 1-Bit Static RAM2-149 | )<br>)<br> <br> <br>5 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 51C256H, High Performance Ripplemode 256K x 1 CHMOS Dynamic RAM 2-55                                                                                                                                                                                                                                                                                                                                                                                                                       | ;                     |

| 51C256L, Low Power 256K x 1 CHMOS Dynamic RAM 2-73                                                                                                                                                                                                                                                                                                                                                                                                                                         | \$                    |

| 51C256HL, High Performance Low Power Ripplemode 256K x 1                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |

| CHMOS Dynamic RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | )                     |

| 51C259H, High Performance Static Column 64K x 4 CHMOS Dynamic RAM 2-103                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |

| 51C259L, Low Power 64K x 4 CHMOS Dynamic RAM 2-120                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                     |

| 51C259HL, High Performance Low Power Static Column 64K x 4                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |

| CHMOS Dynamic RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |

| 80C49-7/80C39-7, CHMOS Single-Component 8-Bit Microcomputer 4-1                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

| 80C51BH/80C51BH-2 80C31BH/80C31BH-2, CHMOS Single-Component                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |

| 8-Bit Microcontroller 4-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                     |

| 80C86/80C86-2, 16-Bit CHMOS Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |

| 80C88/80C88-2, 8-Bit CHMOS Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |

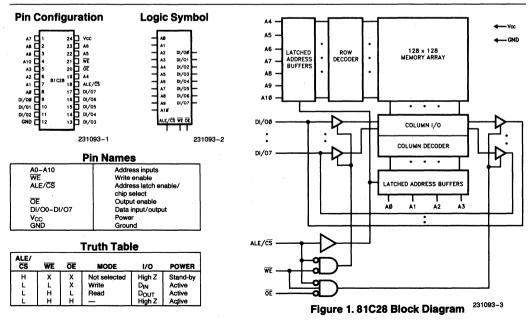

| 81C28 Family, 2048 x 8-Bit Low Power, High Integration Static RAM 2-154                                                                                                                                                                                                                                                                                                                                                                                                                    |                       |

| 82C08, CHMOS Dynamic RAM Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

| 82C37A-5, CHMOS High Performance Programmable DMA Controller 5-57                                                                                                                                                                                                                                                                                                                                                                                                                          |                       |

| 82C54, CHMOS Programmable Interval Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |

| 82C55A, CHMOS Programmable Peripheral Interface                                                                                                                                                                                                                                                                                                                                                                                                                                            |                       |

| 82C59A-2, CHMOS Programmable Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,                     |

| 82C84A/82C84A-5, CHMOS Clock Generator and Driver for 80C86,                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

| 80C88 Processors                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       |

| 82C88,CHMOS Bus Controller for 80C86, 80C88 Processors 5-96                                                                                                                                                                                                                                                                                                                                                                                                                                | )                     |

# INTRODUCTION

v

This handbook introduces products on a new generation of VLSI semiconductor technology from Intel. CHMOS (Complementary High-performance Metal Oxide Semiconductor) combines the best processing techniques used on Intel's high performance HMOS processes with a new set of performanceoriented design rules. CHMOS improves the industry's best speed-power performance to achieve highspeed products with an order of magnitude less power usage. Additionally, on some products (like the new series of CHMOS Random Access Memories), CHMOS is utilized to attain higher speed versions than previously available.

These CHMOS product specifications are brought together to give designers a common reference for information on Intel's complete VLSI CHMOS product line. Represented are components from the microprocessor, peripheral, microcontroller, telecommunication, non-volatile memory, and volatile memory areas. In each case, optimized CHMOS versions of industry-standard architectures are included. This complete set of CHMOS products enables designers to utilize their software and hardware expertise gained with HMOS and quickly take advantage of CHMOS benefits for their systems.

#### **USING THIS HANDBOOK:**

Primarily, this book contains a compilation of Intel's CHMOS data sheets organized by product type.

Each data sheet highlights those aspects of each product which the designer will find most useful. Complete parametric specifications follow the product descriptions.

A summary of Intel's unique approach to building CHMOS product line has been inserted at the outset. The opening chapter discusses the key issues addressed in designing CHMOS — namely latchup prevention, soft-error prevention, interconnections, and logic design techniques. The approach used to resolve these issues and create a complete set of VLSI components is then outlined.

This handbook should be used in combination with other Intel design aids. Additional specifications, application materials, design support tools, or instructional classes are available to supplement design efforts. These items can be obtained from your local Intel representative.

## **ABOUT THE FUTURE:**

Specifications of Intel's initial CHMOS products are contained in this handbook. More VLSI CHMOS components will be added as Intel continues to improve its technologies, the products they make up, and ultimately the systems they go into. With these new products will come an expanding set of documentation to keep designers abreast of advanced semiconductor capabilities and their applications.

# CHMOS Technology Overview

# Modular approach to C-MOS technology tailors process to application

Despite the proliferation of applications, a few C-MOS process variations can address the functional requirements of many different products

by Kim Kokkonen and Richard Pashley, Intel Corp., Santa Clara, Calif.

□ In the past few years, the interest in complementary-MOS technology and its applications to new products has exploded. Traditional arguments for C-MOS center on its low power dissipation, the large noise margins of complementary logic, and its simple ratioless design. With the advent of very large-scale integration, these arguments are taking on new meaning and importance.

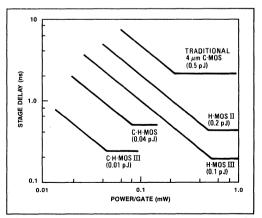

As an example, Fig. 1 compares the performance of H-MOS (high-performance n-channel MOS ) inverters with their equivalent in Intel's C-H-MOS (complementary high-performance MOS) technology. Though H-MOS's speed continues to improve with further scaling, its delay-power product is more than an order of magnitude higher than a C-H-MOS implementation with identical n-channel transistors. In a VLSI part with 50,000 gates, C-H-MOS could mean the difference between 1 and 10 watts of power dissipation, which might save the expense and difficulty of a sophisticated cooling system or extend a portable system's operating time by a factor of 10.

That C-MOS performance is now on a par with n-MOS technology has also accelerated its popularity. In addition, the density of C-MOS circuitry has improved dramatically with advances in technology. Finally, the number of process alternatives has grown so large that almost any integrated-circuit design can be supported with available C-MOS technology.

Unfortunately, the wave of enthusiasm for C-MOS and the needs of different applications have multiplied the number of approaches that C-MOS developers are taking. Several major issues remain in VLSI C-MOS design—namely latchup and soft-error prevention, interconnections, and logic-design techniques. A building-block approach with a limited number of basic process modules can be used to create a close-knit family of technologies that squarely addresses these issues and simultaneously supports a wide range of applications.

#### The basis for C-H-MOS

A firm foundation in n-MOS-transistor physics will support the advancement of C-MOS technology. As channel lengths approach 1 micrometer, n-channel transistors become more difficult to optimize because the standard 5-volt power supply causes problems with high-intensity fields. Improperly designed transistors may be unreliable as a result of hot-carrier injection into gate oxides, or they may cause less localized problems by injecting carriers into the MOS substrate—there to bleed charge from storage nodes or even trigger a destructive latchup.

The resources to develop and verify the reliability of a  $1-\mu m$  n-channel transistor are well established and substantial. In Intel's C-H-MOS process, the basic design of the n-channel transistor is identical to its H-MOS counterpart, as shown in the table. Even at the more detailed levels of doping profiles, the H-MOS and C-H-MOS transistors are nearly identical.

Thus a high-performance C-MOS technology may be born out of an established n-MOS line. The relatively simple addition of an n-well in the same high-resistivity substrate results in a C-MOS process that serves as the basis for several optimized technologies. This is just a start, however, as other important issues remain.

Latchup has been the traditional nemesis of C-MOS. Given the presence of parasitic silicon controlled rectifiers within every bulk C-MOS chip, a current pulse of sufficient magnitude either inside or outside the chip may cause a catastrophic latchup. Many schemes have been proposed to combat latchup, ranging from carefully scrutinizing the layout (which imposes no burden on the technology) to a buried layer (which significantly in-

**1. Power down.** Despite the continuous improvement of H-MOS (high-performance MOS) by scaling, the delay-power product for C-H-MOS (complementary-MOS H-MOS) is more than an order of magnitude lower in the typical integrated circuit.

| n-CHANNEL TRANSISTOR COMPARISON |                  |                             |                        |                          |                         |  |  |  |  |  |

|---------------------------------|------------------|-----------------------------|------------------------|--------------------------|-------------------------|--|--|--|--|--|

| Tec<br>n•MOS                    | hnology<br>C-MOS | Gate-oxide<br>thickness (Å) | Channel<br>length (μm) | Threshold<br>voltage (V) | Graded drain<br>profile |  |  |  |  |  |

| H-MOS I                         |                  | 700                         | 3.0                    | 0.7                      | no                      |  |  |  |  |  |

| H-MOS II                        | C-H-MOS          | 400                         | 2.0                    | 0.7                      | no                      |  |  |  |  |  |

| H-MOS II                        | C-H-MOS III      | 250                         | 1.0                    | 0.7                      | yes                     |  |  |  |  |  |

creases complexity and processing cost). All have some degree of effectiveness.

A modular approach to a broad-based line of C-MOS technologies requires other measures besides mere physical latchup resistance. The latchup spoiler must be applicable to dynamic random-access memories, erasable programmable ready-only memories, and static RAMs, as well as to microprocessors and controllers. In order to improve latchup resistance, it cannot increase the distance between n- and p-channel transistors (this constraint is most significant in random logic and full C-MOS six-transistor static-RAM cells). The technique must be compatible with low-cost and large-volume manufacturing. Finally, the approach must be consistent with the use of an automated checking algorithm, so that every gate of a large semirandom logic design need not be scrutinized for latchup susceptibility.

#### **Epitaxial benefits**

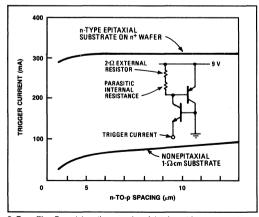

Figure 2 shows the margin gained in latchup trigger current when an epitaxial substrate is used. The epitaxial substrate brings the same latchup benefits to all product lines, and in many cases provides additional advantages such as improved surface lifetimes (for dynamic RAMS) and reduced dc resistance (for E-PROMs and logic). Epitaxial substrates are now available in volume from commercial silicon vendors, adding less than 5% to the cost of a finished wafer. No additional or exotic fabrication equipment needs to be installed. Because the epitaxial

2. Benefits. By raising the margin of latchup trigger current, an epitaxial substrate effects a dramatic improvement in combatting latchup, a major concern in complementary-MOS chip design.

substrate's heavily doped bulk effectively eliminates the vertically triggered latchup mode, it is possible to develop a set of computer-aided-design tools that can flag latchup-sensitive layouts on the largest VLSI chips.

Since grasping the phenomenon of upsets induced by alpha particles, in 1977, memory designers have taken care to ensure that enough charge is stored within each cell to minimize

the problem. As critical chip dimensions are reduced, this problem becomes more severe, however, since both parasitic and storage capacitances are naturally reduced. For the latest 1.5- $\mu$ m n-MOS process, stored charge is low enough to caution even microprocessor designers to guard against random storage nodes suffering from soft errors. Fortunately, C-MOS provides a natural barrier against soft errors if the storage node is located within the C-MOS well.

The well junction is reverse-biased by the power-supply voltage. The electric field at this junction naturally repels any carriers generated outside the well that might otherwise diffuse up to surface storage nodes. The combination of the well structure and an epitaxial substrate is even more effective. Here the funneling mechanism that usually collapses local electric fields during the passage of an alpha particle is also minimized. By using epitaxial substrates and the protection of a C-MOS well, the amount of charge collected during an alpha event can be reduced by an order of magnitude.

Of course, the designer must arrange for the storage node to reside within the well. This constraint, combined with other performance issues, leads to different choices of well and substrate polarities, depending on application. For example, in a C-MOS technology that is optimized for dynamic RAM, the ideal memory cell should have a pchannel pass gate and a p-channel capacitor located within an n-well in a p-type substrate. The p-channel transistor is chosen because it injects far fewer spurious carriers into the substrate and thus does not by itself disturb the state of neighboring cells.

The conductance of the p-channel device, while lower than that of an n-channel device of the same size, does not degrade the RAM's performance, since dynamic-RAM sensing is limited primarily by the amount of stored charge. Experimental results with C-H-MOS dynamic RAMs based on these principles show a soft-error rate of less than 300 FIT (failures in time, or device failures per billion hours) at a power supply of only 3 v. This is an improvement of more than three orders of magnitude over traditional n-MOS dynamic-RAM technology and offers the possibility of dynamic-RAM systems that require no error correction and that are compatible with lowvoltage battery backup.

High-density, high-performance static RAMs present the other side of the coin. The smallest static-RAM cells today are built using polysilicon-load resistors that sustain the stored-node voltage. On the time scale of an alpha event, however, these resistors in effect do not exist. Because the storage node's RC time constant is on the order of milliseconds and the alpha event's time scale is nanoseconds, the cell appears dynamic. In this sense, polysilicon-load static-RAM cells are very similar to dynamic-RAM cells. The major difference arises in the way the cells sense the cell's information. The static-RAM cell provides a direct current, and to maximize the cell's performance, that current must be as large as possible while contained in a minimum area. Thus the chip designer must use high-gain n-channel transistors for the cell's pass gates and pulldowns. For good soft-error protection, then, the cell must be located in a p-well within an n-type substrate.

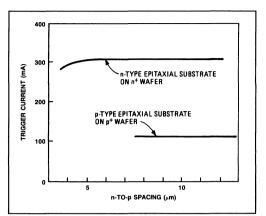

The p-well approach benefits even full C-MOS six-transistor static-RAM cells. The area of such cells depends strongly on the distance allowed between n- and p-channel devices. Using a straightforward implementation of epitaxial C-MOS, the p-well approach provides more margin against latchup at small n-to-p spacings (Fig. 3). This phenomenon occurs because of the differing diffusion properties of n- and p-type dopants. The heavy doping in the n-type substrate is less mobile than is the p-type dopant, resulting in less outdiffusion during thermal processing and thus minimizing the shunt resistance that controls latchup.

#### Hooking it up

One of the challenges of C-MOS in logic applications is interconnection. Designers of n-MOS chips are accustomed to buried contacts, which directly connect n-type polysilicon and n-type transistor source or drain regions. Because C-MOS requires contact to both p and n regions, the traditional n-type buried contact becomes much less useful, and a version suitable for both diffusion polarities is quite difficult to implement. This increases the burden on contact and metallization modules.

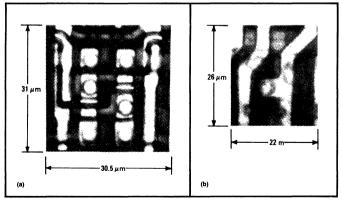

For high-density C-MOS logic, the first level of metal is all but consumed by local connections between p and n transistors. The payback from adding a second level of metal for longer-distance routing is very high. A good example exists for the six-transistor static-RAM cell commonly used by logic designers. Figure 4 compares single- and double-metal versions of this cell, both imple-

mented with 1.5- $\mu$ m design rules. Here the second-metal layer provides the bit lines for the cell. Similar arguments justify the use of second metal in global power, clock, and data routing in complex microprocessor chips.

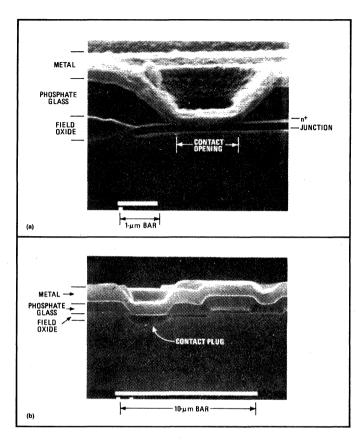

Contacts themselves are more difficult to build in C-MOS. N-MOS technology accustomed process engineers to adding a phosphorus contact plug after the contacts have been etched. This plug brought several advantages: the phosphorus gettered metallic contaminants from the wafer, reducing junction leakage; and the high-temperature diffusion rounded the profile of the contact sidewall, easing the step coverage of the metal subsequently deposited. Further, the plug had self-aligning features. If the

3. P-well margin. With an epitaxial substrate, a p-well structure (upper curve) yields a greater margin against latchup than n-well at smaller n- and p-device spacings.

contact etch attacked the silicon substrate or if the contact was misaligned toward the field-oxide edge, the plug would rejuvenate the resulting weakened junctions. In C-MOS, these same attributes must be obtained differently, through improved fabrication, cleanliness, new gettering techniques, improved dielectrics, and tightly controlled contact etching. Figure 5 shows the difference in implementing a 1.5- $\mu$ m contact structure in n-MOS and C-MOS.

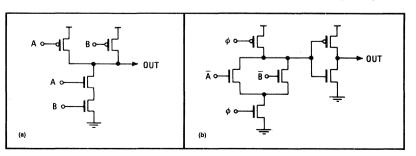

Along with the proliferation of C-MOS technologies has come a wave of innovation in C-MOS design techniques. For digital logic, the major contenders for broad use are full complementary design and domino logic, first proposed by AT&T Bell Laboratories (Fig. 6). For many applications, traditional C-MOS logic is a winner. It requires no clocks, has larger operating margins, and uses fewer transistors for simple gates. For more complex gates, however, domino logic uses fewer transistors and runs faster. The speed results from connecting fewer transistors in series and reducing gate-fanout loading by

4. Payback. The use of double-metal layers for a six-transistor static-RAM cell can produce a large savings in real-estate. In two cells implemented with a 1.5-µm design rules, the savings can amount to one third of the total area. The cell at right uses second-layer metal for bit lines.

up to a factor of two compared with full C-MOS.

Interestingly, the choice of design style influences the optimal type of C-MOS well. The speed of full C-MOS is limited by the slower of the two transistor polarities. Since the trip point is quite close to half the power supply, the time required for either transistor type to discharge its load capacitance by about 2.5 v sets the gate's speed. Since the p-channel device is the weaker one, it pays to choose a well type that improves the p-channel's conductance. P-well does this because the p-device is fabricated in an uncompensated substrate and thus has maximum mobility. Comparisons between n

6. Logic. Two major contenders for digital logic design are full complementary (a) and domino logic (b). The former requires no clocks and is simpler for many applications. Domino logic, which performs best in an n-well technology, is faster and simpler for more complex circuits.

5. Making contact. Contacts are more difficult to build in C-MOS than in conventional n-MOS. The phosphorous contact plug used in n-MOS after contact etching (a) adds desirable features such as reduced junction leakage and improved step coverage by the metal layer. To gain the same advantages in C-MOS requires greater process control (b).

and p-well construction show that the p-channel's conductance may be improved by as much as 10% with the proper well type.

By contrast, domino logic is at its best in an n-well technology. Here, the n-channel transistor dominates both performance and transistor count. Placing the n-channel device outside the well improves its conductance and reduces the dominant parasitic junction capacitance. Density also increases because no well contacts are required for the majority of the transistors.

The twin-well approach to C-MOS blurs these distinctions. In this approach, a high-resistivity epitaxial layer is grown on a heavily doped starting wafer. Then the doping for each transistor polarity may be independently optimized without need for doping compensation. Performance arguments based on mobility or junction capacitance thus become moot. Nonetheless, domino logic will still be best on a p-type substrate (equivalent to n-well) because it does

not require well contacts to collect the large parasitic substrate currents from the n-channel transistors, thus improving packing density.

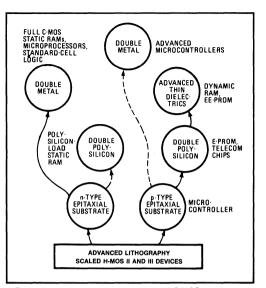

#### Matching process to product

These and other technical arguments may be combined into a consistent strategy (Fig. 7) for creating a line of C-MOS processes serving a broad marketplace. For at least the next several years, a complete technology line must include C-MOS based on both p- and n-type substrates. Fortunately, choosing epitaxial-latchup control minimizes the development cost of running both processes. Dynamic RAMs are supported on the n-well side to minimize pattern sensitivities induced by substrate currents while protecting the p-channel cell from soft errors. E-PROMs are built in a similar n-well C-H-MOS process. Placing Intel's n-MOS E-PROM cell in an epitaxial p-type substrate eliminates parasitic effects caused by high substrate currents flowing during cell programming.

Microcontrollers land on the n-well side also, so that they may incorporate on-chip E-PROM cells. Most microcontroller products come in two versions, one with onchip E-PROM for system-development and manufacturing flexibility, and another with on-chip ROM for lowest cost. Using n-well C-MOS, a single core design can support both versions. Telecommunications and signal-processing products can also take advantage of the n-well E-PROM process, both for its high-quality polysilicon-polysilicon capacitors and for the E-PROM cell's programmable features. High-performance static RAMS, whether six-transistor or polysilicon-load, can take advantage of a p-well C-H-MOS process. High-end microprocessors can key off the dense n-to-p packing and double-metal capability offered by the six-transistor static-RAM process.

Because these processes are modular, development is simplified and manufacturing overhead is minimized. Just as all the 1.5- $\mu$ m C-H-MOS III technologies share a common transistor module, the difficult contact module was developed once to be shared among all. Specialized features such as double polysilicon or double metal are extensions of the common base.

#### The future

C-MOS technology is still developing at a frenetic pace. Surprisingly, the application of some newer techniques and the demands of next-generation circuits may bring the various forms of C-MOS closer together, rather than further splitting the number of integrated processes.

One example of this trend is the development of a trench-isolation technique for separating n and p devices. When this module is perfected, there will be no reason to develop six-transistor static-RAM cells on p-well technology. The near-ideal trench isolation will prevent latchup on either substrate type. Similarly, if stacked C-MOS static-RAM cells can be perfected, there will be no need for polysilicon loads. The stacked C-MOS cell will have the same density but with improved performance and softerror immunity. At that time, twin-well C-MOS on a p-type substrate, augmented by specialized features for specific product lines, will become the one approach to a broad line of C-MOS processes.

Another factor affecting future C-MOS integration is the continued scaling of transistors. It is well known that the weaker p-channel transistor is gradually catching up on the n-channel device as channel lengths enter the submicrometer region. Eventually, the performance differences may become so small that p- and n-channel devices will be used interchangeably. Before this level is reached, however, the 5-v power-supply standard must be reduced. Because of the large base of TTL-compatible designs and the impossibility of converting the world to a new standard overnight, components operating from the new reduced supply will need to maintain TTL compatibility and also be able to operate in a system that mixes

7. Technology tree. A relatively small line of C-MOS process variations, or modules, can be matched to a wide variety of products to serve a broad marketplace. The broken lines indicate directions of potential future growth.

older 5-v components with lower-voltage ones. An onchip 5-to-3-v converter may be one way to solve the problem. This technique, however, will waste up to 40% of the total chip power within the voltage regulator.

C-MOS technology provides an elegant solution because it can drive TTL-compatible output levels from a system power supply as low as 3 V. Since TTL levels are referenced to the negative (ground) rail, the grounded substrate offered by n-well C-MOS is a much-preferred means of integrating submicrometer transistors into such a system. This will be a strong motive to standardize on psubstrate C-MOS.

A final factor that tends to drive future C-MOS processes toward commonality is the growing importance of RC delays in overall chip performance. The latest high-performance static RAMs use an aluminum strap in parallel with the polysilicon word line because the RC delay induced by even the best refractory metal polycides is several nanoseconds too long. Studies of dynamic RAMs larger than 1 megabit similarly indicate that refractory word lines will probably be inadequate, forcing the technology to support two layers of metal. Combining these observations with those made previously regarding the evolution of static-RAM cells leads to the conclusion that most future C-MOS technologies will have two layers of polysilicon as well as two layers of metal.

The development of silicon-on-insulator technology is the one major factor that could renew the divergence of C-MOS approaches in the future. However, until the quality of SOI substrates is adequate to support dynamic RAM and E-PROM cells, and not just static logic, it will not play a major role in a broad-based and modular technology strategy.

# Memory Components

2

# 51C64H HIGH PERFORMANCE RIPPLEMODE™ 64K X 1 CHMOS DYNAMIC RAM

|                                         | 51C64H-8 | 51C64H-10 | 51C64H-12 |

|-----------------------------------------|----------|-----------|-----------|

| Maximum Access Time (ns)                | 80       | 100       | 120       |

| Maximum Column Address Access Time (ns) | 45       | 55        | 65        |

| Ripplemode Cycle Time (ns)              | 55       | 65        | 75        |

- Ripplemode Operation

- Continuous data rate over 18 MHz

- Random access within a row

- Flow through column latch for pipelining

- Low Operating Current 45 mA

- Low Input/Output Capacitance

## ■ Fast "Usable Speed"

- $t_{RC} = 140 \text{ ns}$

- $t_{CAC} = 20 \text{ ns}$

$- t_{RCD} = 30$  ns min./60 max.

- Fully TTL Compatible

- High Reliability Plastic 16 Pin DIP

The Intel®51C64H is a high speed 65,536 × 1 dynamic Random Access Memory. Fabricated on Intel's CHMOS III-D technology, the 51C64H offers features not provided by an NMOS dynamic RAM: Ripplemode for high data bandwidth and fast usable speed. All inputs and outputs are fully TTL compatible and the input and output capacitances are significantly lowered to allow increased system performance.

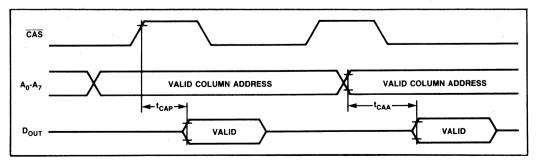

Ripplemode operation allows random or sequential access of up to 256 bits within a row, with cycle times as fast as 55 ns. Because of static column circuitry, the CAS clock is no longer in the critical timing path. The flow through column latch allows address pipelining while relaxing many critical system timing requirements for fast usable speed. These features make the 51C64H ideally suited for cache based mainframe and mini computers, graphics, digital signal processing, and high performance microprocessor systems.

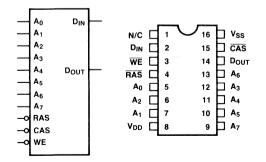

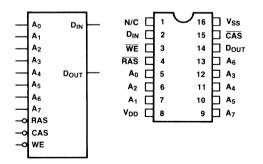

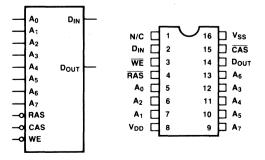

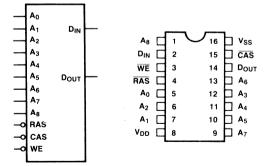

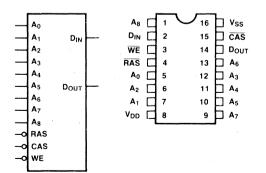

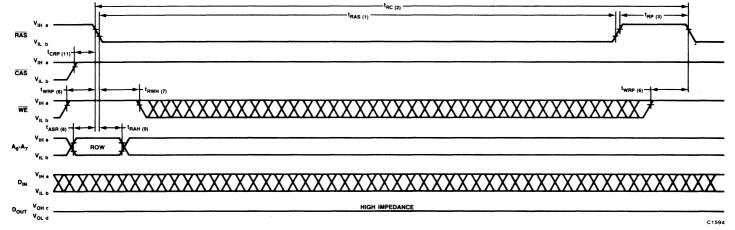

LOGIC SYMBOL

PIN CONFIGURATION

**PIN NAMES**

| RAS                            | ROW ADDRESS STROBE    |

|--------------------------------|-----------------------|

| CAS                            | COLUMN ADDRESS STROBE |

| WE                             | WRITE ENABLE          |

| A <sub>0</sub> -A <sub>7</sub> | ADDRESS INPUTS        |

| DIN                            | DATA IN               |

| DOUT                           | DATA OUT              |

| V <sub>DD</sub>                | POWER (+5V)           |

| V <sub>SS</sub>                | GROUND                |

|                                |                       |

Intel Corporation Assumes No Responsibility for the Use of Any Circuitry Other Than Circuitry Embodied in an Intel Product. No Other Circuit Patent Licenses are Implied.

# **ABSOLUTE MAXIMUM RATINGS†**

Ambient Temperature Under

| Bias + 80°C                                                           |

|-----------------------------------------------------------------------|

| Storage Temperature Plastic - 55 to + 125°C                           |

| Voltage on Any Pin except V <sub>DD</sub> and D <sub>OUT</sub>        |

| Relative to V <sub>SS</sub> – 2.0V to 7.5V                            |

| Voltage on V <sub>DD</sub> Relative to V <sub>SS</sub> – 1.0V to 7.5V |

| Voltage on DOUT                                                       |

| Relative to V <sub>SS</sub> – 2.0V to V <sub>DD</sub> + 1V            |

| Data Out Current                                                      |

| Power Dissipation1.0W                                                 |

#### **†COMMENT**

Stresses above those listed under "Absolute Maximum Rating" may cause damage to the device. This is a stress rating only and functional operation of the device at these or at any other conditions above or below those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

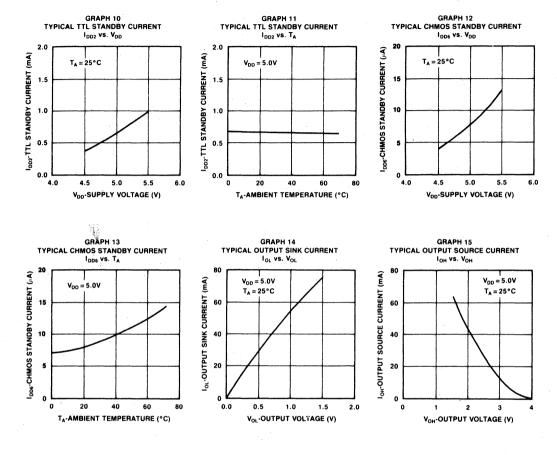

# D.C. CHARACTERISTICS<sup>1</sup>

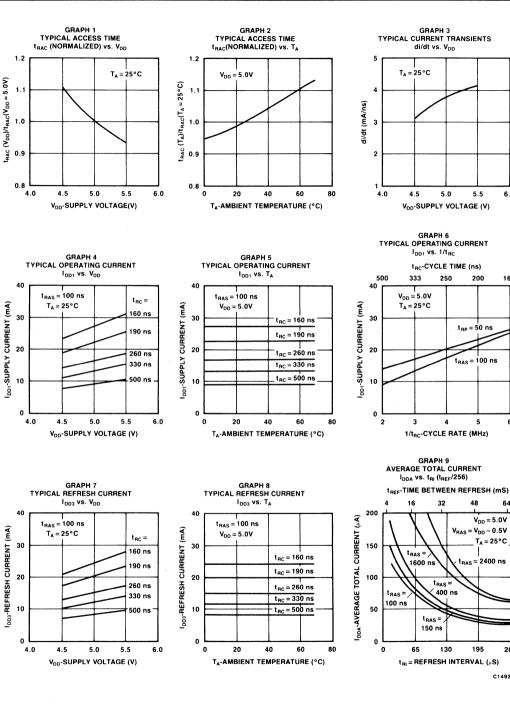

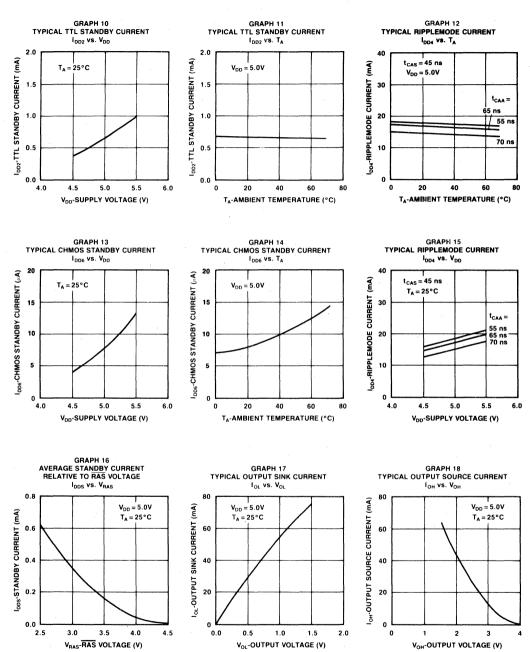

$T_A = 0$  °C to 70 °C,  $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

| Symbol            | Parameter                                                  |       | 51C64H | 1                   | Unit | Test Conditions                                                                                                                 | Notes |

|-------------------|------------------------------------------------------------|-------|--------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------|-------|

| Symbol            | Parameter                                                  | Min.  | Typ.2  | Max.                | Unit | rest conditions                                                                                                                 | NOLES |

|                   | V <sub>DD</sub> Supply Current,                            |       | 33     | 45                  | mA   | $t_{RC} = t_{RC}(min)$ , for -8 specification                                                                                   |       |

| I <sub>DD1</sub>  | Operating                                                  |       | 27     | 37                  | mA   | $t_{RC} = t_{RC}(min)$ , for $-10$ specification                                                                                | 3,4   |

|                   |                                                            |       | 23     | 35                  | mA   | $t_{RC} = t_{RC}(min)$ , for $-12$ specification                                                                                |       |

| I <sub>DD2</sub>  | V <sub>DD</sub> Supply Current, TTL<br>Standby             |       |        | 4                   | mA   | RAS and CAS at V <sub>IH</sub> , all other inputs and output ≥ V <sub>SS</sub>                                                  |       |

|                   | V <sub>DD</sub> Supply Current, TTL                        |       | 28     | 45                  | mA   | $t_{RC} = t_{RC}(min)$ , for -8 specification                                                                                   |       |

| I <sub>DD3</sub>  | RAS-Only Refresh                                           |       | 24     | 37                  | mA   | $t_{RC} = t_{RC}(min)$ , for $-10$ specification                                                                                | 4     |

|                   |                                                            |       | 20     | 35                  | mA   | $t_{RC} = t_{RC}(min)$ , for $-12$ specification                                                                                |       |

|                   | V <sub>DD</sub> Supply Current,                            |       | 20     | 45                  | mA   | $t_{PC} = t_{PC}(min)$ , for -8 specification                                                                                   |       |

| I <sub>DD4</sub>  | Ripplemode™                                                |       | 18     | 37                  | mA   | $t_{PC} = t_{PC}(min)$ , for -10 specification                                                                                  | 3,4   |

|                   |                                                            |       | 17     | 35                  | mA   | $t_{PC} = t_{PC}(min)$ , for $-12$ specification                                                                                |       |

| I <sub>DD 5</sub> | V <sub>DD</sub> Supply Current,<br>Standby, Output Enabled |       | 3      | 6                   | mA   | RAS at V <sub>IH</sub> , CAS at V <sub>IL</sub> , all other inputs and output≥V <sub>SS</sub>                                   | 3     |

| 1_1               | Input Load Current<br>(any pin)                            |       |        | 10                  | μA   | $V_{IN} = V_{SS}$ to $V_{DD}$                                                                                                   |       |

| I <sub>LO</sub>   | Output Leakage Current for T<br>High Impedance State       |       |        | 10                  | μA   | $\overrightarrow{RAS}$ and $\overrightarrow{CAS}$ at V <sub>IH</sub> ,<br>D <sub>OUT</sub> = V <sub>SS</sub> to V <sub>DD</sub> |       |

| VIL               | Input Low Voltage<br>(all inputs)                          | - 1.0 |        | 0.8                 | v    |                                                                                                                                 | 5     |

| V <sub>IH</sub>   | Input High Voltage<br>(all inputs)                         | 2.4   |        | V <sub>DD + 1</sub> | v    |                                                                                                                                 | 5     |

| Vol               | Output Low Voltage                                         |       |        | 0.4                 | V    | I <sub>OL</sub> = 4.2 mA                                                                                                        | 6     |

| V <sub>OH</sub>   | Output High Voltage                                        | 2.4   |        |                     | ٧    | I <sub>OH</sub> = -5 mA                                                                                                         | 6     |

#### NOTES:

- 1. All voltages referenced to V<sub>SS</sub>.

- 2. Typical values are at  $T_A = 25^{\circ}C$  and  $V_{DD} = +5V$ .

- I<sub>DD</sub> is dependent on output loading when the device output is selected. Specified I<sub>DD</sub> (max) is measured with the output open.

I<sub>DD</sub> is dependent upon the number of address transitions while CAS is at V<sub>IH</sub>. Specified I<sub>DD</sub> (max) is measured with a maximum of two transitions per address input per random cycle, one transition per access cycle in Ripplemode.

5. Specified V<sub>IL</sub> (min) is steady state operation. All A.C. parameters are measured with V<sub>IL</sub> (min)≥V<sub>SS</sub> and V<sub>IH</sub> (max)≤V<sub>DD</sub>.

6. Test conditions apply only for D.C. Characteristics. All A.C. parameters are measured with a load equivalent to two TTL loads and 50 pF.

# intel®

# **CAPACITANCE<sup>†</sup>**

$T_{A}$  = 25°C,  $V_{DD}$  = 5V  $\pm$  10%,  $V_{SS}$  = 0V, unless otherwise noted.

| Symbol           | Parameter                | Тур. | Max | Unit |

|------------------|--------------------------|------|-----|------|

| C <sub>IN1</sub> | Address, D <sub>IN</sub> | 3    | 4   | рF   |

| C <sub>IN2</sub> | RAS, CAS, WE             | 4    | 5   | рF   |

| COUT             | Dout                     | 4    | 6   | рF   |

# A.C. CHARACTERISTICS 1,2,3

$T_A = 0^{\circ}C$  to 70°C,  $V_{DD} = 5V \pm 10\%$ ,  $V_{SS} = 0V$ , unless otherwise noted.

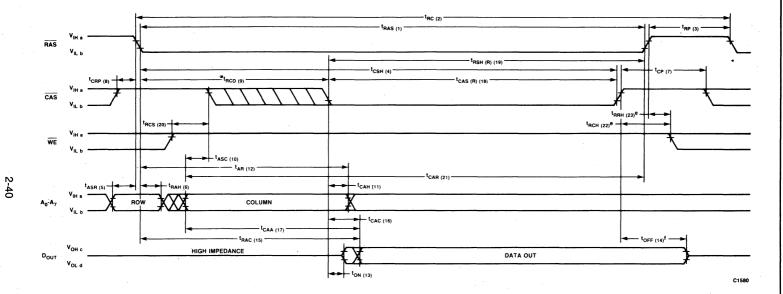

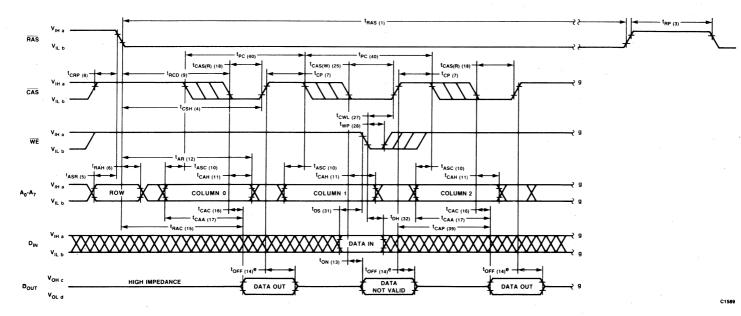

# Read, Write, Read-Modify-Write and Refresh Cycles

|    | JEDEC               |                  |                                   | 51C6 | 51C64H-8 |      | 51C64H-10 |      | 51C64H-12 |      |       |

|----|---------------------|------------------|-----------------------------------|------|----------|------|-----------|------|-----------|------|-------|

| #  | Symbol              | Symbol           | Parameter                         | Min. | Max.     | Min. | Max.      | Min. | Max.      | Unit | Notes |

| 1  | t <sub>RL1RH1</sub> | t <sub>RAS</sub> | RAS Pulse Width                   | 80   | 75000    | 100  | 75000     | 120  | 75000     | ns   |       |

| 2  | t <sub>RL2RL2</sub> | t <sub>RC</sub>  | Random Read or Write Cycle Time   | 140  |          | 160  |           | 190  |           | ns   |       |

| 3  | t <sub>RH2RL2</sub> | t <sub>RP</sub>  | RAS Precharge Time                | 50   |          | 50   |           | 60   |           | ns   |       |

| 4  | t <sub>RL1CH1</sub> | t <sub>CSH</sub> | CAS Hold Time                     | 80   |          | 100  |           | 120  |           | ns   |       |

| 5  | t <sub>AVRL2</sub>  | t <sub>ASR</sub> | Row Address Set-up Time           | 0    |          | 0    |           | 0    |           | ns   |       |

| 6  | t <sub>RL1AX</sub>  | t <sub>RAH</sub> | Row Address Hold Time             | 15   |          | 15   |           | 15   |           | ns   |       |

| 7  | t <sub>CH2CL2</sub> | t <sub>CP</sub>  | CAS Precharge Time                | 10   |          | 10   |           | 15   |           | ns   |       |

| 8  | t <sub>CH2RL2</sub> | t <sub>CRP</sub> | CAS to RAS Precharge Time         | - 20 |          | - 20 |           | - 20 |           | ns   |       |

| 9  | t <sub>RL1CL2</sub> | t <sub>RCD</sub> | RAS to CAS Delay                  | 30   | 60       | 30   | 80        | 35   | 95        | ns   | 4     |

| 10 | t <sub>AVCL2</sub>  | t <sub>ASC</sub> | Column Address Set-up Time        | 0    |          | 0    |           | 0    |           | ns   |       |

| 11 | t <sub>CL1AX</sub>  | t <sub>CAH</sub> | Column Address Hold Time          | 10   |          | 10   |           | 15   |           | ns   |       |

| 12 | t <sub>RL1AX</sub>  | t <sub>AR</sub>  | Column Address Hold Time From RAS | 40   |          | 40   |           | 50   |           | ns   |       |

|    | t <sub>RVRV</sub>   | t <sub>REF</sub> | Time Between Refresh              |      | 4        |      | 4         |      | 4         | ms   |       |

|    | t <sub>T</sub>      | t <sub>T</sub>   | Transition Time (Rise and Fall)   | 3    | 50       | 3    | 50        | 3    | 50        | ns   | 5     |

| 13 | t <sub>CL1QX</sub>  | t <sub>ON</sub>  | Output Buffer Turn On Delay       | 0    | 20       | 0    | 20        | 0    | 25        | ns   |       |

| 14 | t <sub>CH2QZ</sub>  | t <sub>OFF</sub> | Output Buffer Turn Off Delay      | 0    | 20       | 0    | 20        | 0    | 25        | ns   |       |

## NOTES:

- 1. All voltages referenced to  $V_{\mbox{\scriptsize SS}}.$

- An initial pause of 100 microseconds is required after power up followed by a minimum of eight initialization cycles (any combination of cycles containing a RAS clock such as RAS-Only refresh). Eight initialization cycles are required after extended periods of bias without clocks (greater than 4 ms).

- A.C. Characteristics assume t<sub>T</sub> = 5 ns. All A.C. parameters are measured with a load equivalent to two TTL loads and 50 pF, V<sub>IL</sub> (min)≥V<sub>SS</sub> and V<sub>IH</sub> (max)≤V<sub>DD</sub>.

- 4. t<sub>RCD</sub> (max) is specified for reference only.

- 5.  $t_{T}$  is measured between  $V_{IH}$  (min) and  $V_{IL}$  (max).

TNOTE:

Capacitance is measured at worst case voltage levels with a programmable capacitance meter.

# A.C. CHARACTERISTICS (Con't.)

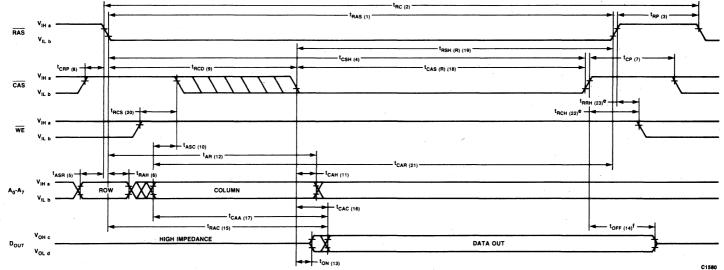

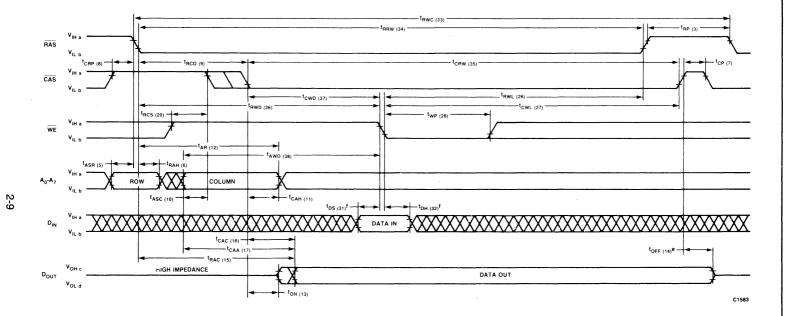

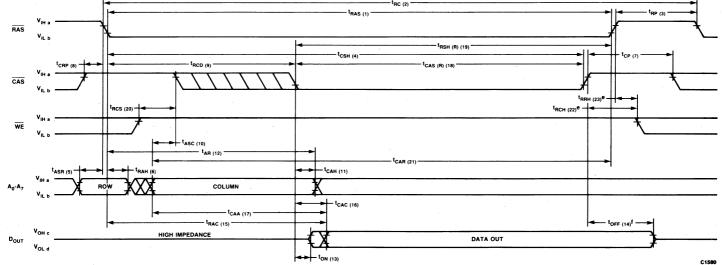

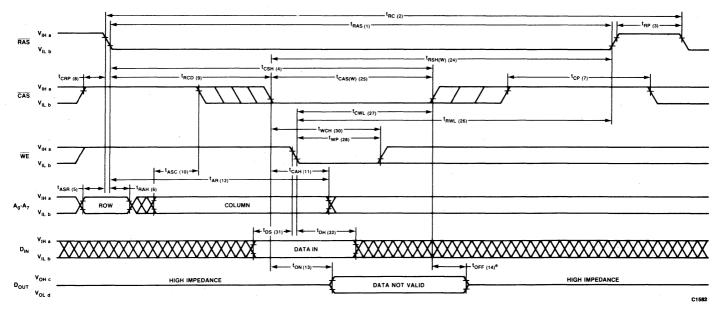

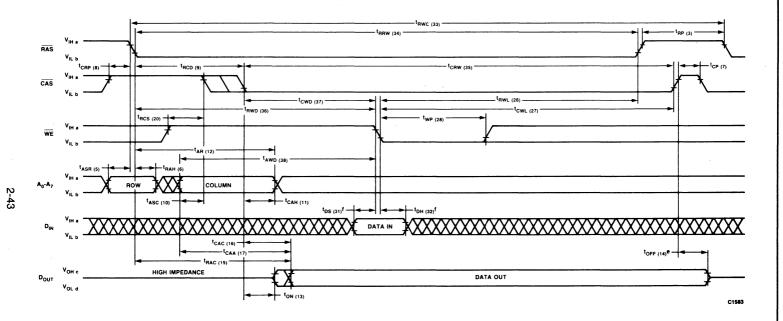

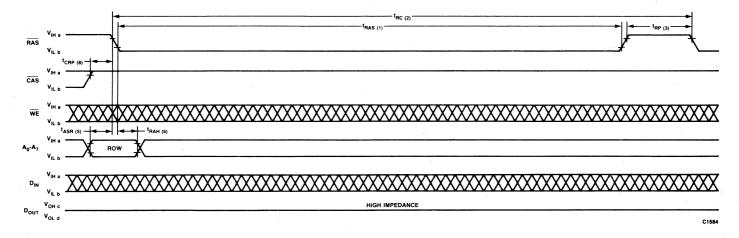

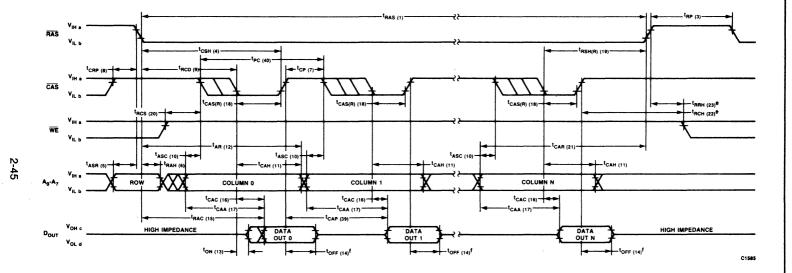

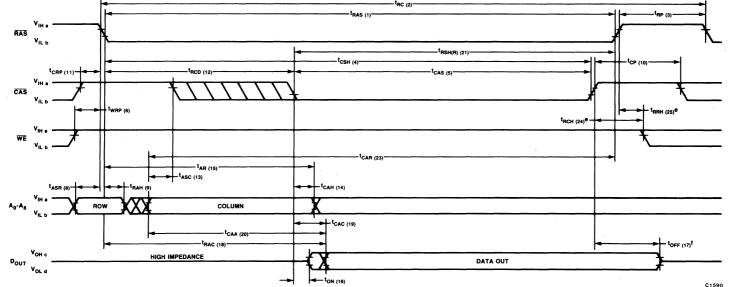

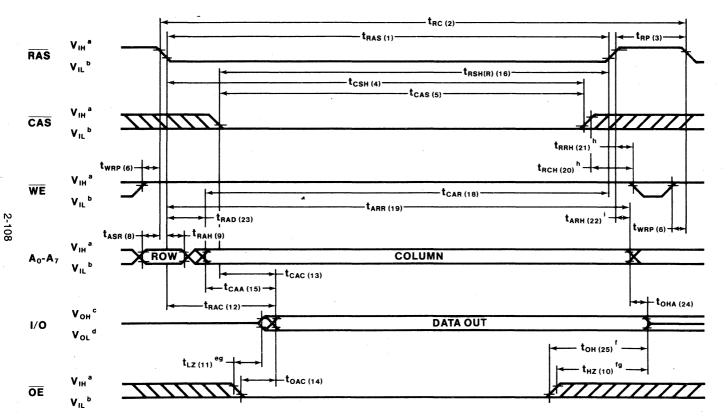

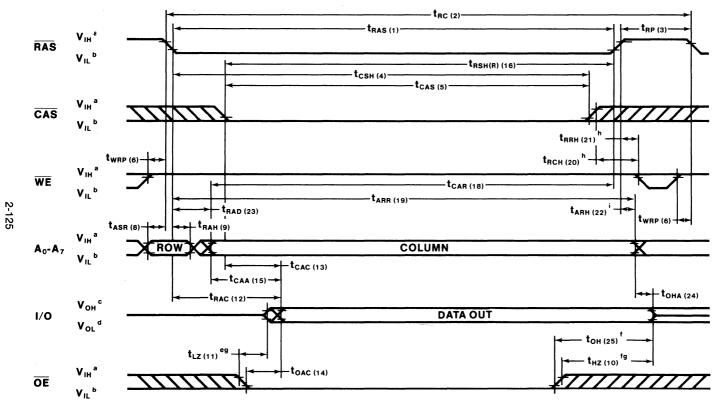

# **Read Cycle**

|    | " JEDEC                | JEDEC Durate Company |                                   | 51C64H-8 |       | 51C64H-10 |       | 51C64H-12 |       |      |       |

|----|------------------------|----------------------|-----------------------------------|----------|-------|-----------|-------|-----------|-------|------|-------|

| #  | Symbol                 | Symbol               | Parameter                         | Min.     | Max.  | Min.      | Max.  | Min.      | Max.  | Unit | Notes |

| 15 | t <sub>RL1QV</sub>     | t <sub>RAC</sub>     | Access Time From RAS              |          | 80    |           | 100   |           | 120   | ns   | 6     |

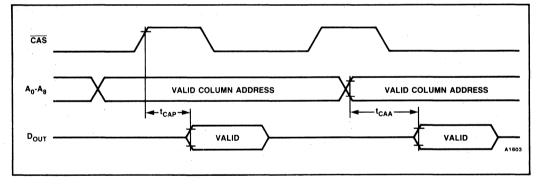

| 16 | t <sub>CL1QV</sub>     | t <sub>CAC</sub>     | Access Time From CAS              |          | 20    |           | 20    |           | 25    | ns   | 7,8   |

| 17 | t <sub>AVQV</sub>      | t <sub>CAA</sub>     | Access Time From Column Address   |          | 45    |           | 55    |           | 65    | ns   | 8,9   |

| 18 | t <sub>CL1CH1(R)</sub> | t <sub>CAS(R)</sub>  | CAS Pulse Width (Read Cycle)      | 15       | 75000 | 20        | 75000 | 25        | 75000 | ns   |       |

| 19 | t <sub>CL1RH1(R)</sub> | t <sub>RSH(R)</sub>  | RAS Hold Time (Read Cycle)        | 10       |       | 10        |       | 10        |       | ns   |       |

| 20 | twH2CL2                | t <sub>RCS</sub>     | Read Command Set-up Time          | 0        |       | 0         |       | 0         |       | ns   |       |

| 21 | t <sub>AVRH1</sub>     | t <sub>CAR</sub>     | Column Address to RAS Set-up Time | 45       |       | 55        |       | 65        |       | ns   |       |

| 22 | t <sub>CH2WX</sub>     | t <sub>RCH</sub>     | Read Com. Hold Time Ref. to CAS   | 0        |       | 0         |       | 0         |       | ns   | 10    |

| 23 | t <sub>RH2WX</sub>     | t <sub>RRH</sub>     | Read Com. Hold Time Ref. to RAS   | 10       |       | 10        |       | 10        |       | ns   | 10    |

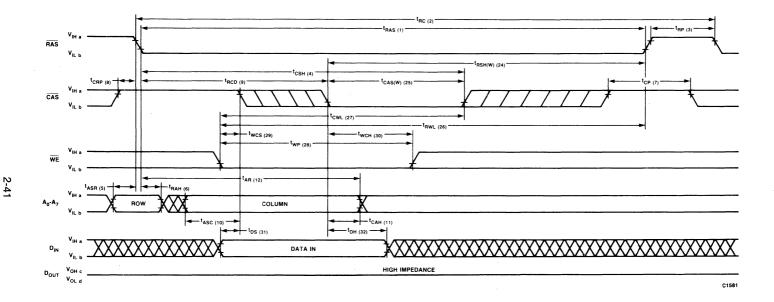

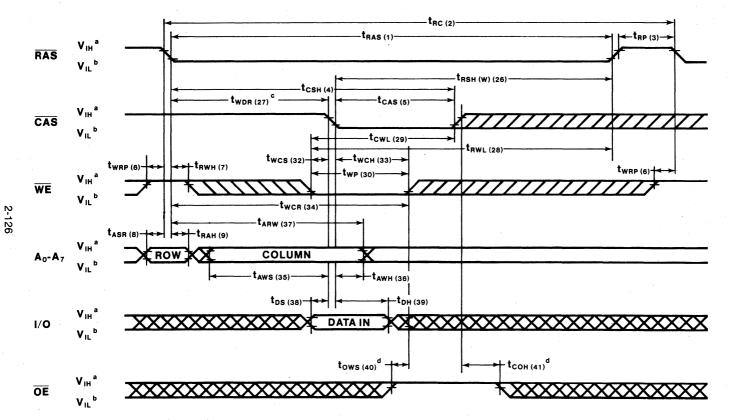

### Write Cycle

| #  | JEDEC<br>Symbol        | Symbol              | Parameter                      | 51C64H-8 |       | 51C64H-10 |       | 51C64H-12 |       |      |       |

|----|------------------------|---------------------|--------------------------------|----------|-------|-----------|-------|-----------|-------|------|-------|

|    |                        |                     |                                | Min.     | Max.  | Min.      | Max.  | Min.      | Max.  | Unit | Notes |

| 24 | t <sub>CL1RH1(W)</sub> | t <sub>RSH(W)</sub> | RAS Hold Time (Write Cycle)    | 35       |       | 35        |       | 40        |       | ns   |       |

| 25 | t <sub>CL1CH1(W)</sub> | tcas(w)             | CAS Pulse Width (Write Cycle)  | 25       | 75000 | 30        | 75000 | 35        | 75000 | ns   |       |

| 26 | t <sub>WL1RH1</sub>    | t <sub>RWL</sub>    | Write Command to RAS Lead Time | 25       |       | 30        |       | 35        |       | ns   |       |

| 27 | t <sub>WL1CH1</sub>    | t <sub>CWL</sub>    | Write Command to CAS Lead Time | 25       |       | 30        |       | 35        |       | ns.  |       |

| 28 | twL1WH1                | twp                 | Write Command Pulse Width      | 20       |       | 20        |       | 25        |       | ns   |       |

| 29 | twL1CL2                | twcs                | Write Command Set-up Time      | 0        |       | 0         |       | 0         |       | ns   | 11    |

| 30 | t <sub>CL1WH1</sub>    | twcн                | Write Command Hold Time        | 25       |       | 30        |       | 35        |       | ns   |       |

| 31 | t <sub>DVCL2</sub>     | t <sub>DS</sub>     | Data-In Set-up Time            | 0        |       | 0         |       | 0         |       | ns   |       |

| 32 | t <sub>CL1DX</sub>     | t <sub>DH</sub>     | Data-In Hold Time              | 20       |       | 20        |       | 25        |       | ns   |       |

#### NOTES:

6. Assumes that t<sub>RCD</sub> ≤ t<sub>RCD</sub> (max). If t<sub>RCD</sub> > t<sub>RCD</sub> (max), then t<sub>RAC</sub> will increase by the amount that t<sub>RCD</sub> exceeds t<sub>RCD</sub> (max).

7. Assumes  $t_{RCD} \ge t_{RCD}$  (max).

8. If  $t_{ASC} < (t_{CAA} (max) - t_{CAC} (max) - t_T)$ , then access time is defined by  $t_{CAA}$  rather than by  $t_{CAC}$ .

9. When a Ripplemode read cycle immediately follows a Ripplemode write cycle, the specification must be increased by 10 ns.

10. Either t<sub>BCH</sub> or t<sub>BBH</sub> must be satisfied.

11. twCS, tRWD, tCWD and tAWD are specified as reference points only. If twCS ≥ twCS (min), the cycle is a CAS controlled write cycle (early write cycle) and the data out pin will remain in high impedence throughout the entire cycle. If t<sub>CWD</sub> ≥ t<sub>CWD</sub> (min) and t<sub>RWD</sub> ≥ t<sub>RWD</sub> (min) and t<sub>AWD</sub> ≥ t<sub>AWD</sub>(min), then the cycle is a read-modify-write cycle and the data out will contain the data read from the selected address. If any of the above conditions are not satisfied, the condition of the data out is indeterminate.

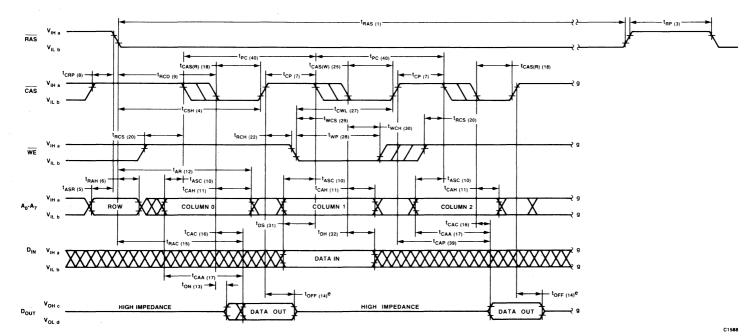

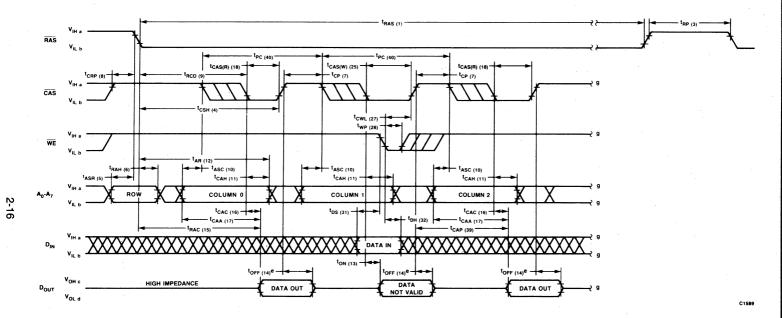

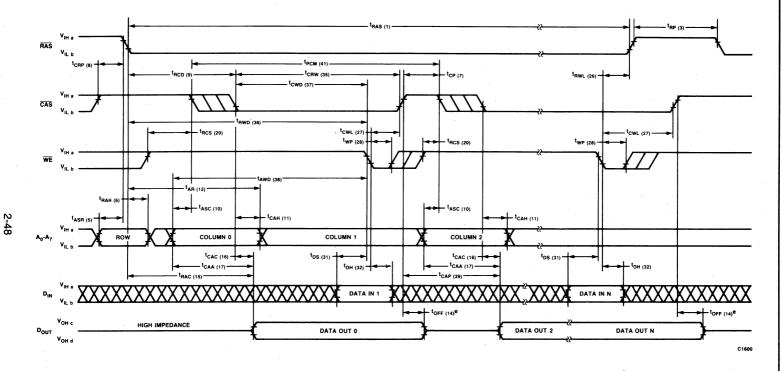

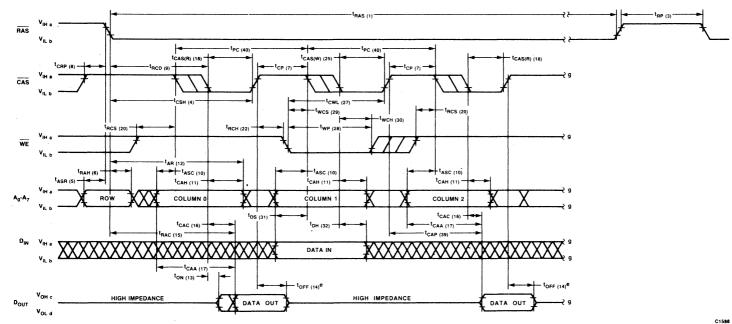

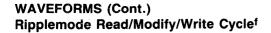

# A.C. CHARACTERISTICS (Con't.) Read-Modify-Write Cycle 12

| #  | JEDEC                    |                  | Parameter                          | 51C64H-8 |       | 51C64H-10 |       | 51C64H-12 |       |      |       |

|----|--------------------------|------------------|------------------------------------|----------|-------|-----------|-------|-----------|-------|------|-------|

|    | Symbol                   | Symbol           |                                    | Min.     | Max.  | Min.      | Max.  | Min.      | Max.  | Unit | Notes |

| 33 | t <sub>RL2RL2(RMW)</sub> | t <sub>RWC</sub> | Read-Modify-Write (RMW) Cycle Time | 170      |       | 195       |       | 230       |       | ns   |       |

| 34 | t <sub>RL1RH1(RMW)</sub> | t <sub>RRW</sub> | RMW Cycle RAS Pulse Width          | 110      | 75000 | 135       | 75000 | 160       | 75000 | ns   |       |

| 35 | t <sub>CL1CH1(RMW)</sub> | t <sub>CRW</sub> | RMW Cycle CAS Pulse Width          | 50       | 75000 | 55        | 75000 | 65        | 75000 | ns   |       |

| 36 | t <sub>RL1WL2</sub>      | t <sub>RWD</sub> | RAS to WE Delay                    | 80       |       | 100       |       | 120       |       | ns   | 13    |

| 37 | t <sub>CL1WL2</sub>      | t <sub>CWD</sub> | CAS to WE Delay                    | 20       |       | 20        |       | 25        |       | ns   | 13    |

| 38 | t <sub>AVWL2</sub>       | t <sub>AWD</sub> | Column Address to WE Delay         | 45       |       | 55        |       | 65        |       | ns   | 13    |

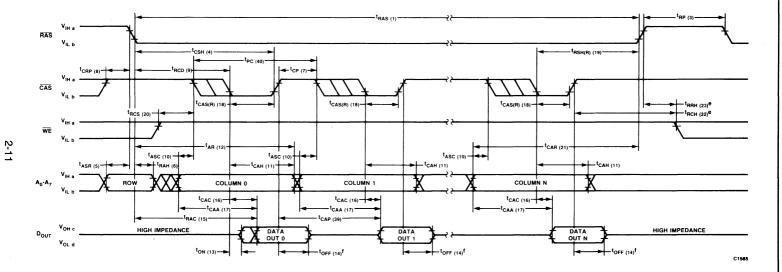

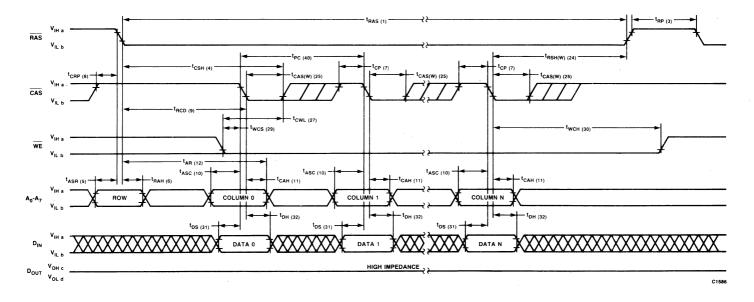

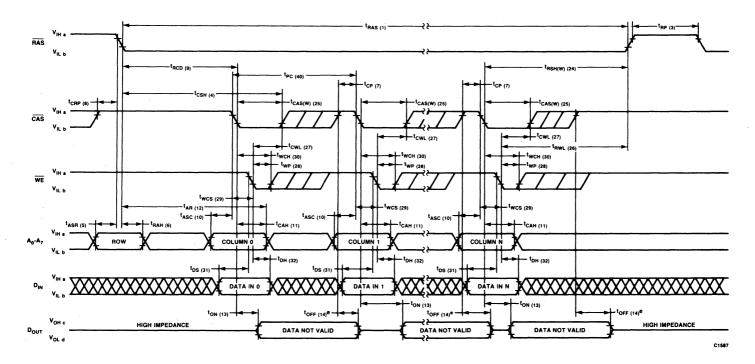

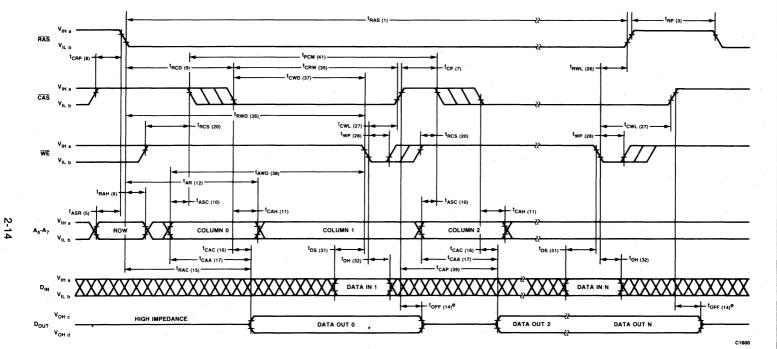

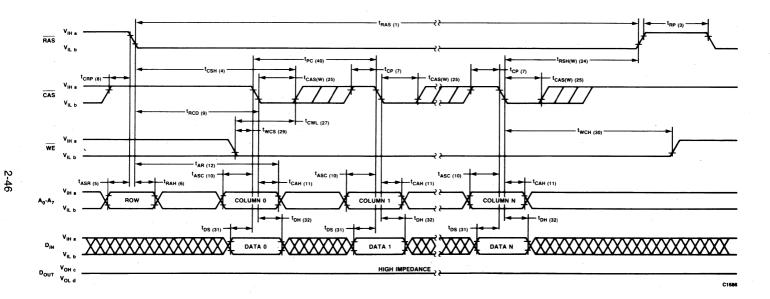

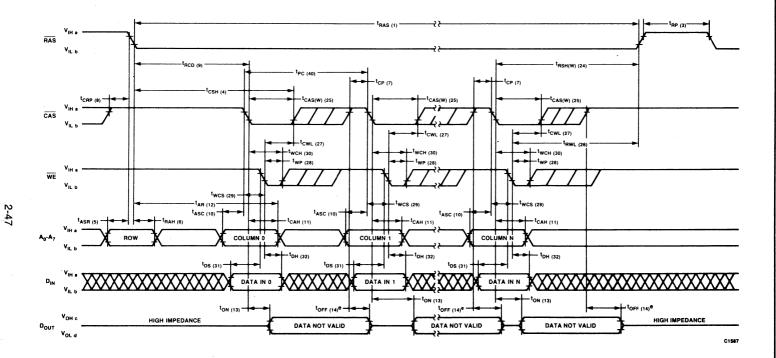

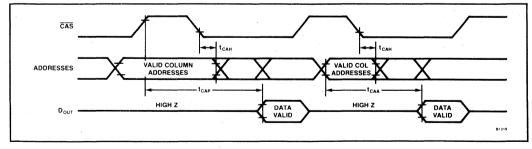

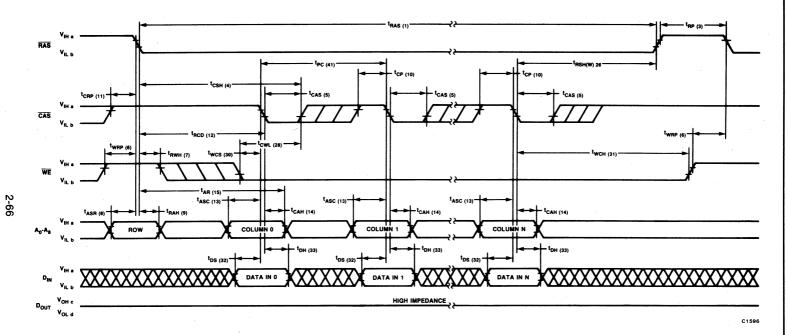

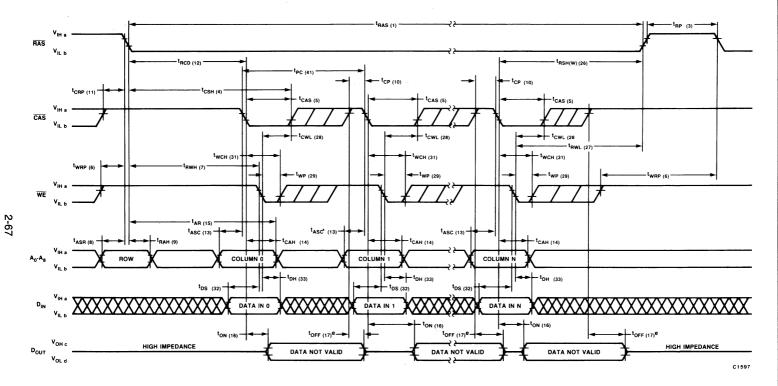

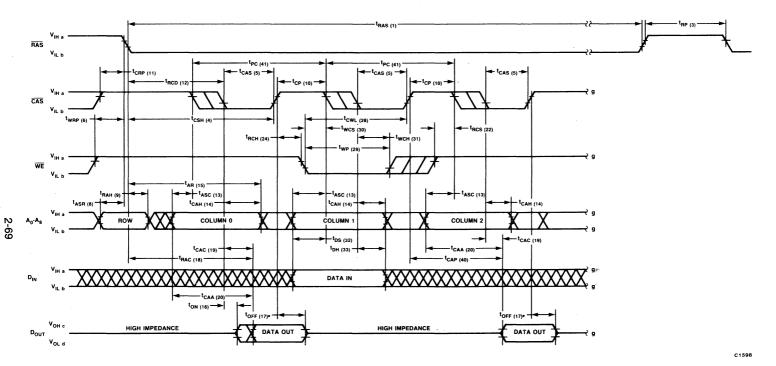

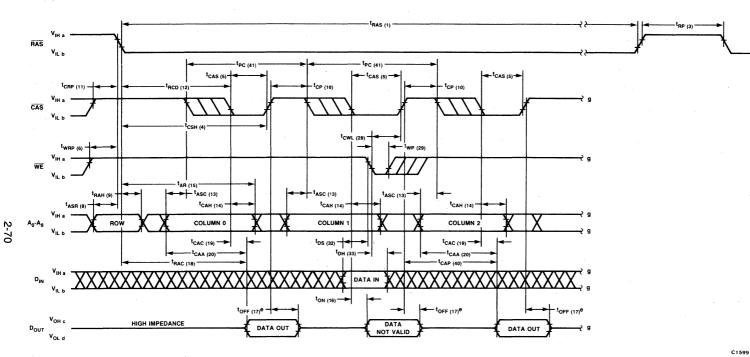

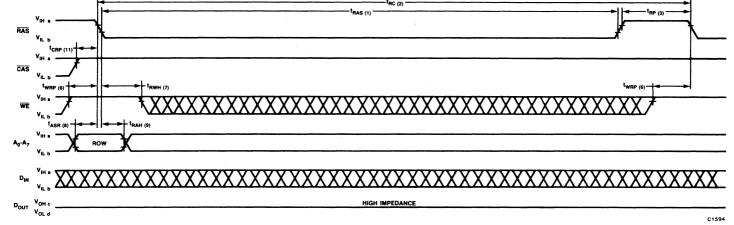

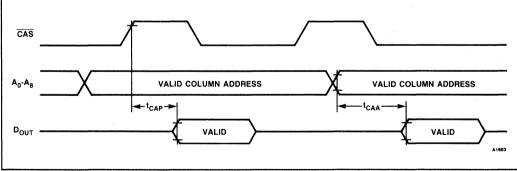

## **Ripplemode Cycle 14**

| #  | JEDEC                      |                  |                                   | 51C64H-8 |      | 51C64H-10 |      | 51C64H-12 |      |      |       |

|----|----------------------------|------------------|-----------------------------------|----------|------|-----------|------|-----------|------|------|-------|

|    | Symbol                     | Symbol           | Parameter                         | Min.     | Max. | Min.      | Max. | Min.      | Max. | Unit | Notes |

| 39 | t <sub>CH2QV</sub>         | t <sub>CAP</sub> | Access Time From Column Precharge |          | 50   |           | 60   |           | 70   | ns   | 15,16 |

| 40 | t <sub>CL2CL2(R)</sub>     | t <sub>PC</sub>  | Ripplemode Read or Write Cycle    | 55       |      | 65        |      | 75        |      | ns   | 15,16 |

| 41 | t <sub>CL2CL2</sub> (RRMW) | t <sub>РСМ</sub> | Ripplemode RMW Cycle Time         | 80       |      | 95        |      | 110       |      | ns   |       |

## NOTES:

- 12. The parameters shown in the Read-Modify-Write timing diagrams which are not listed in the table are previously specified.

- 13. t<sub>WCS</sub>, t<sub>RWD</sub>, t<sub>CWD</sub> and t<sub>AWD</sub> are specified as reference points only. If t<sub>WCS</sub>≥t<sub>WCS</sub> (min), the cycle is a CAS controlled write cycle (early write cycle) and the data out pin will remain in high impedance throughout the entire cycle. If t<sub>CWD</sub>≥t<sub>CWD</sub> (min) and t<sub>RWD</sub>≥t<sub>RWD</sub> (min) and t<sub>AWD</sub>≥t<sub>AWD</sub> (min), then the cycle is a read-modify-write cycle and the data out will contain the data read from the selected address. If any of the above conditions are not satisfied, the condition of data out is indeterminate.

14. All previously specified A.C. Characteristics are applicable.

- 15. Access time is determined by the longer of  $t_{\text{CAA}}$  or  $t_{\text{CAC}}$  or  $t_{\text{CAP}}.$

- 16. When a Ripplemode read cycle immediately follows a Ripplemode write cycle, the specification must be increased by 10 ns.

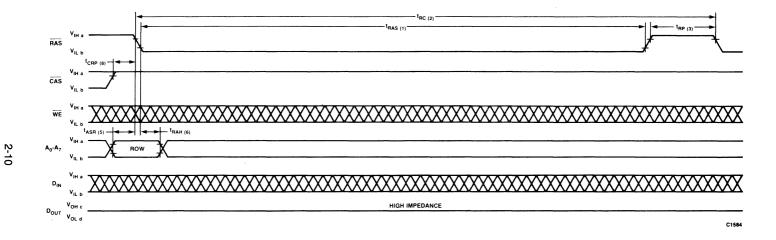

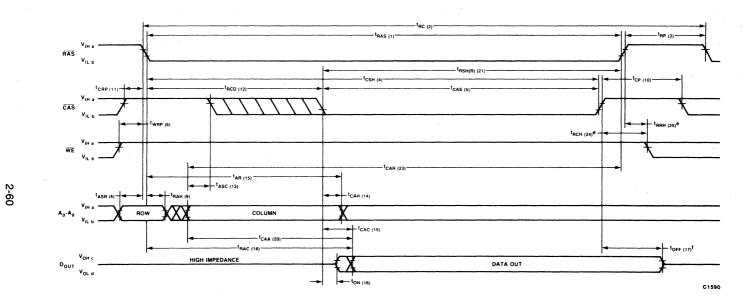

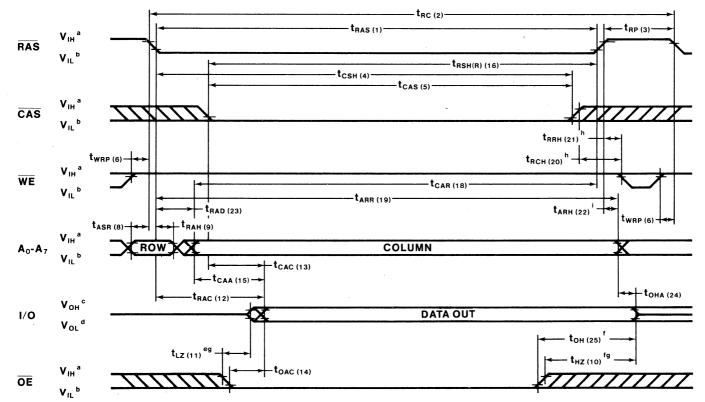

#### NOTES:

2-6

- a., b. V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals.

- c., d. V<sub>OH</sub> (min) and V<sub>OL</sub> (max) are reference levels for measuring timing of D<sub>OUT</sub>.

- e. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied.

- f.  $t_{OFF}$  is measured to  $l_{OUT} \le |l_{LO}|$ .

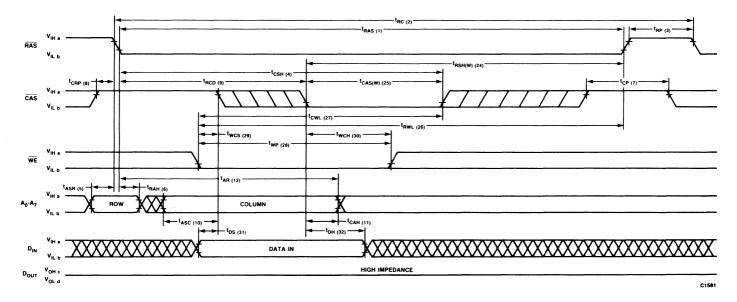

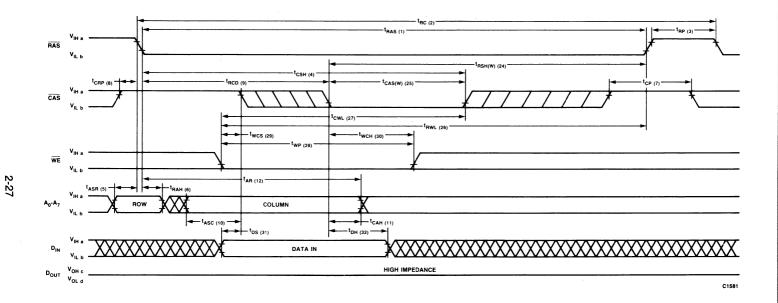

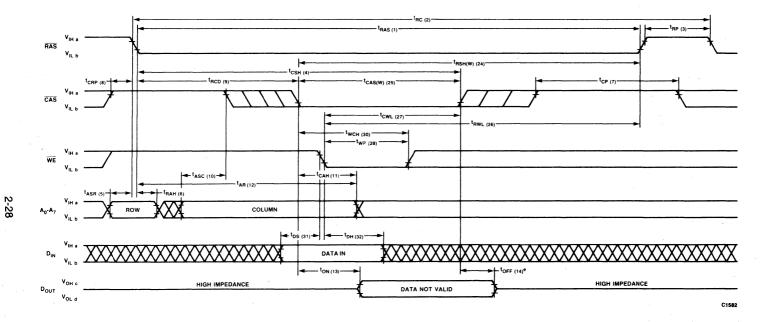

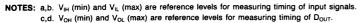

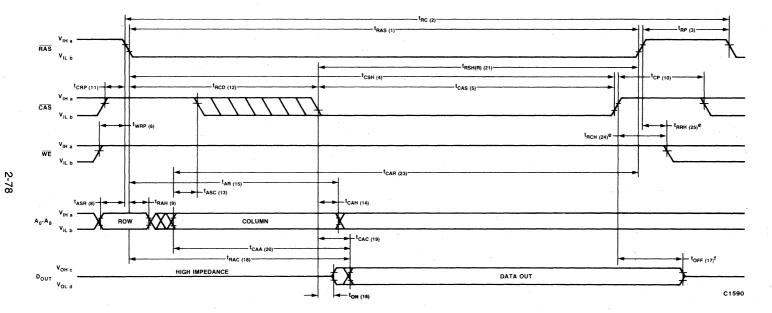

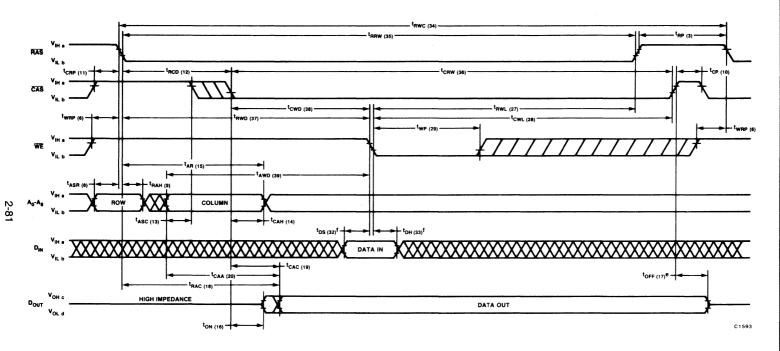

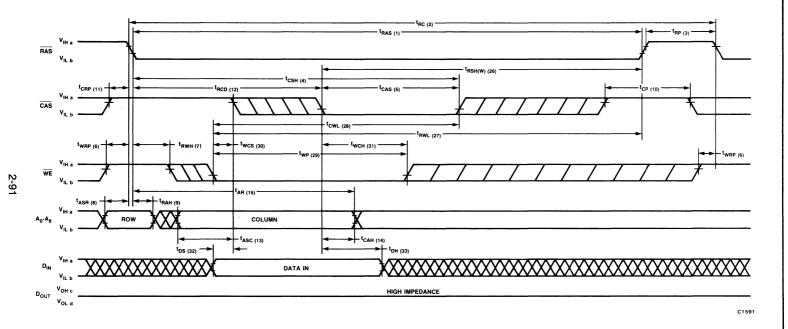

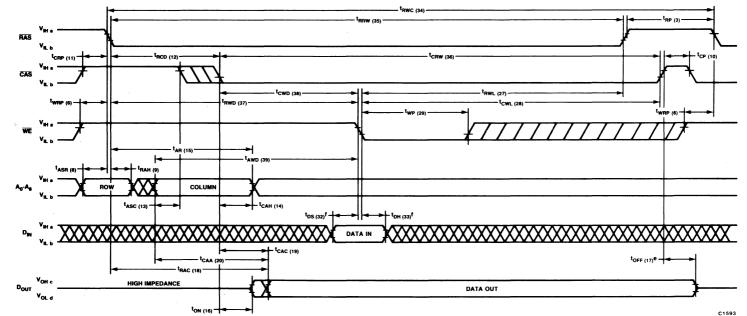

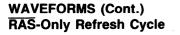

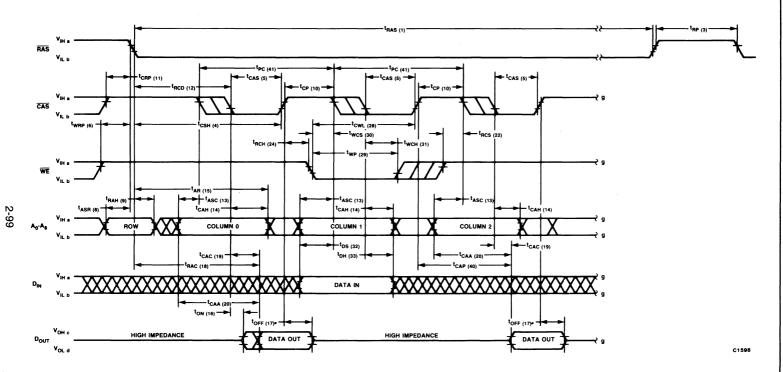

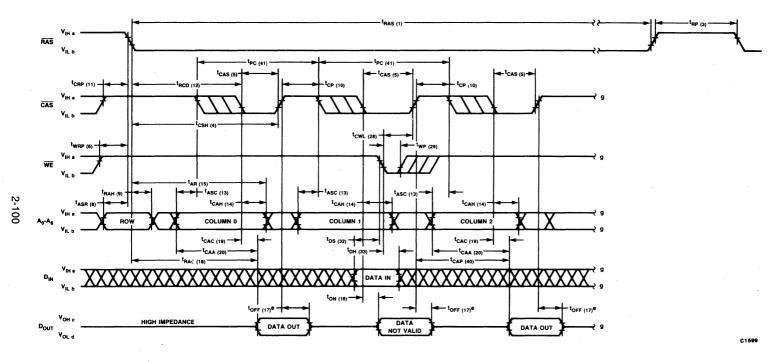

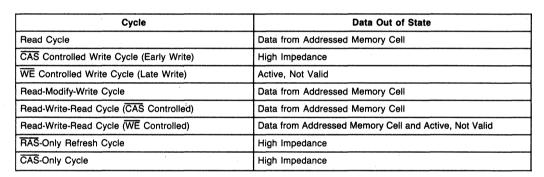

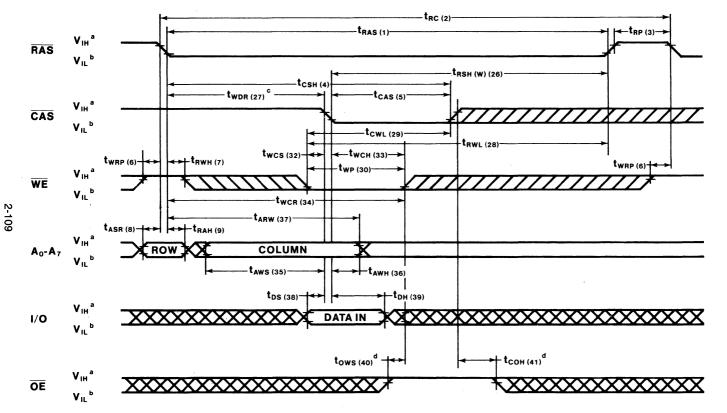

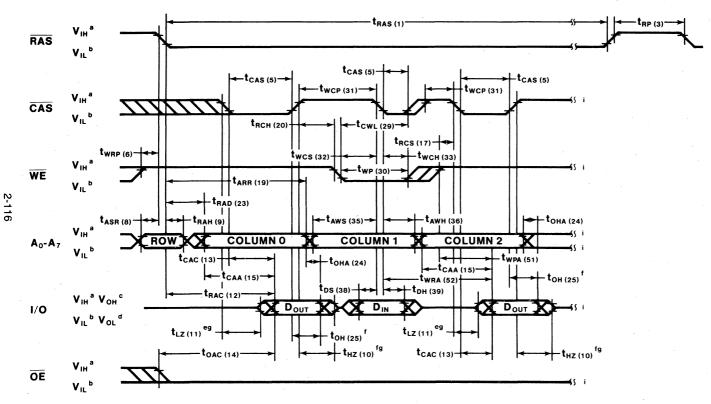

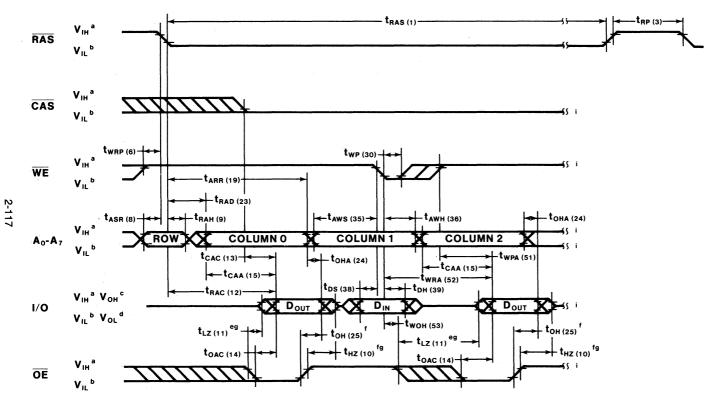

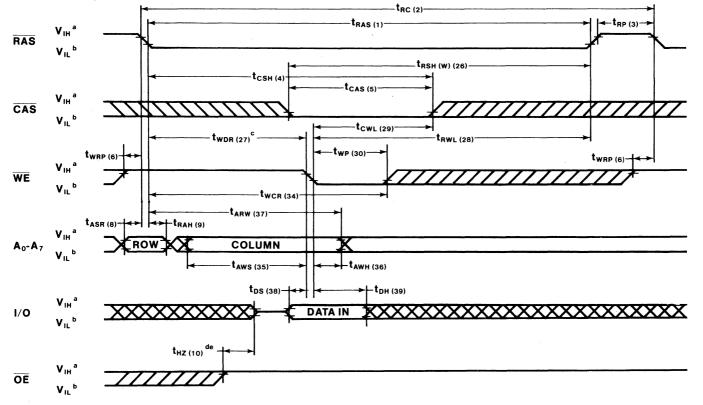

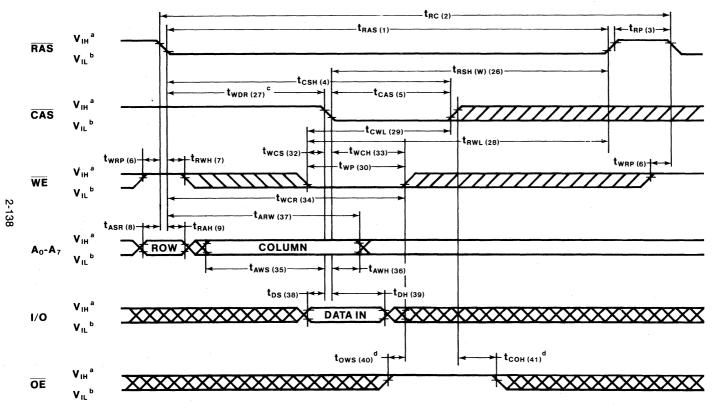

# WAVEFORMS (Cont.) Write Cycle (CAS Controlled)<sup>e</sup>

#### NOTES:

a., b. V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals.

c., d. V<sub>OH</sub> (min) and V<sub>OL</sub> (max) are reference levels for measuring timing of D<sub>OUT</sub>.

e. WE is low prior to or simultaneously with CAS low transition. CAS latches column address and data-in.

51C64H

2-7

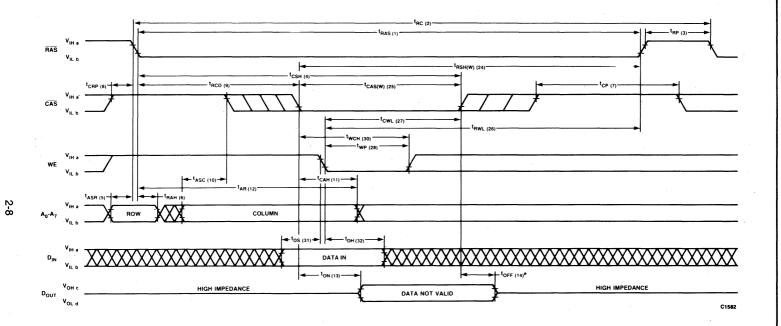

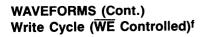

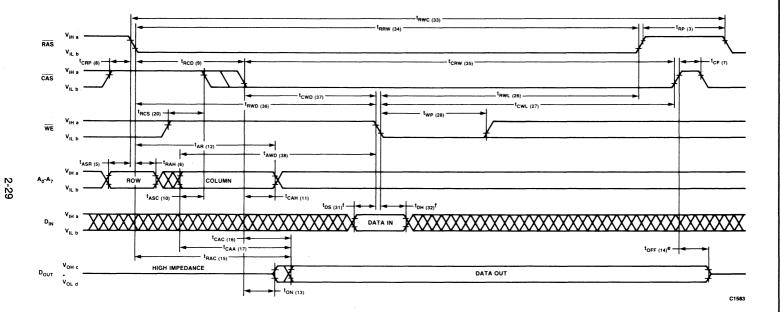

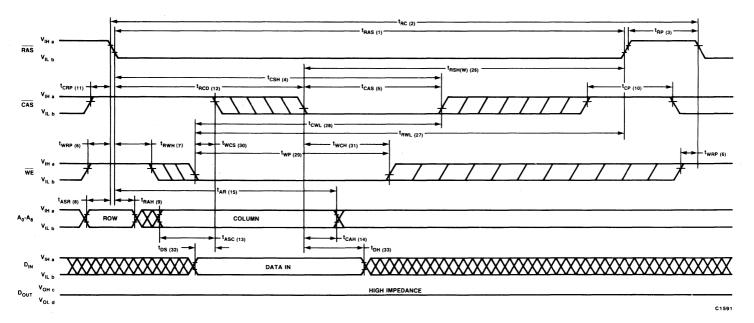

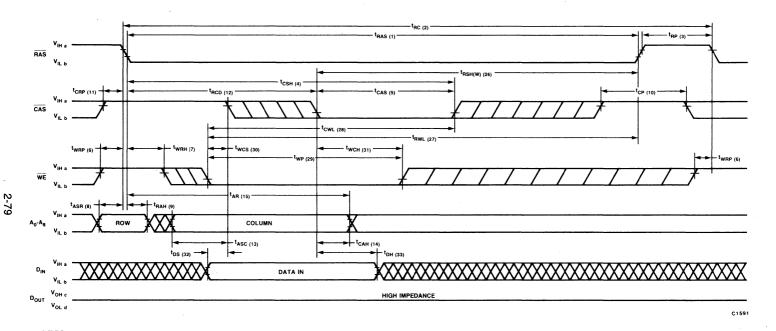

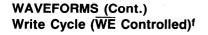

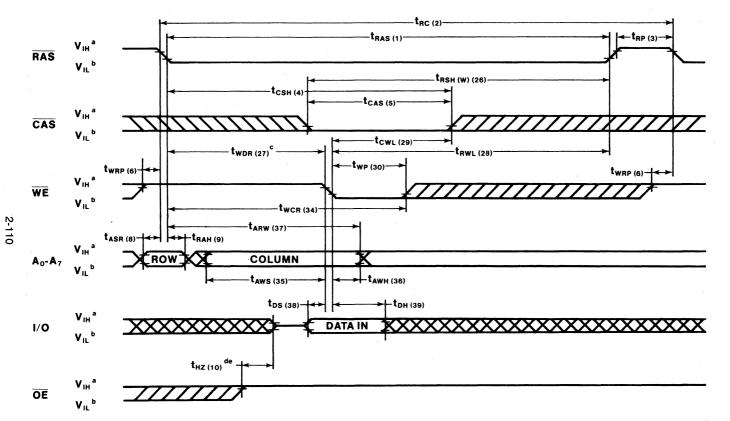

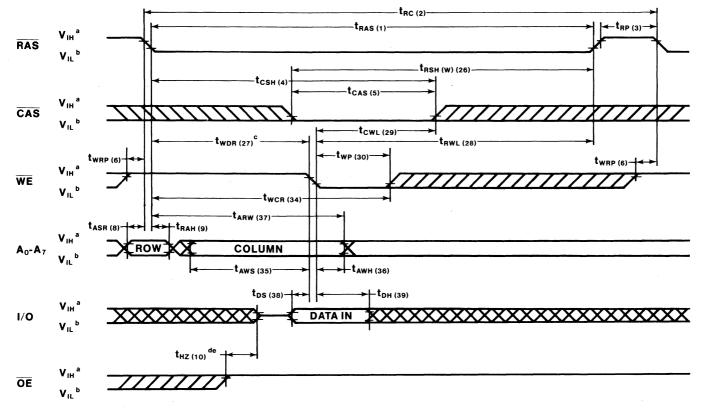

WAVEFORMS (Cont.) Write Cycle (WE Controlled)<sup>f</sup>

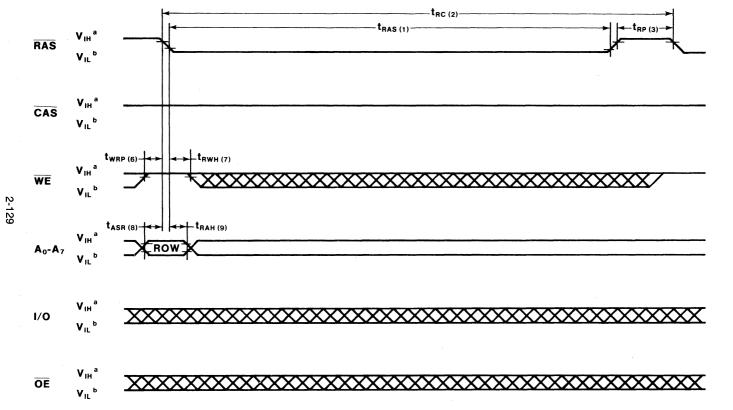

#### NOTES:

- a., b. V<sub>IH</sub> (min) and V<sub>IL</sub> (max) are reference levels for measuring timing of input signals.

- c., d. V<sub>OH</sub> (min) and V<sub>OL</sub> (max) are reference levels for measuring timing of D<sub>OUT</sub>.

- e. Tore is measured to  $|_{0ur} \le |l_{LO}|$ . f. CAS is low prior to the WE low transition. CAS latches the column address while WE latches the data-in.

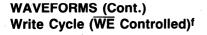

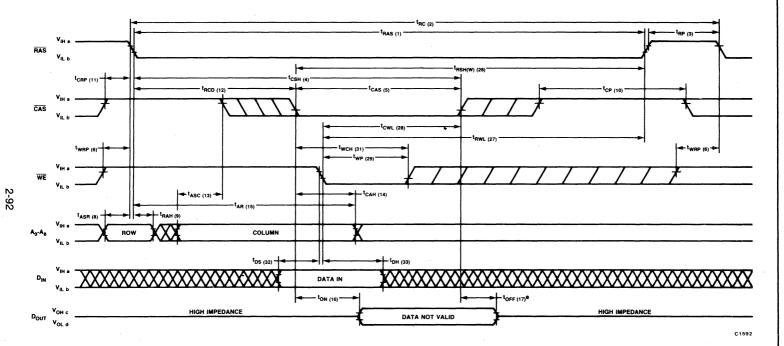

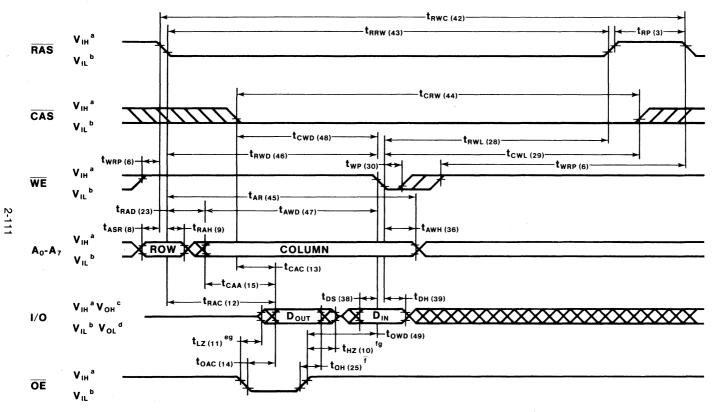

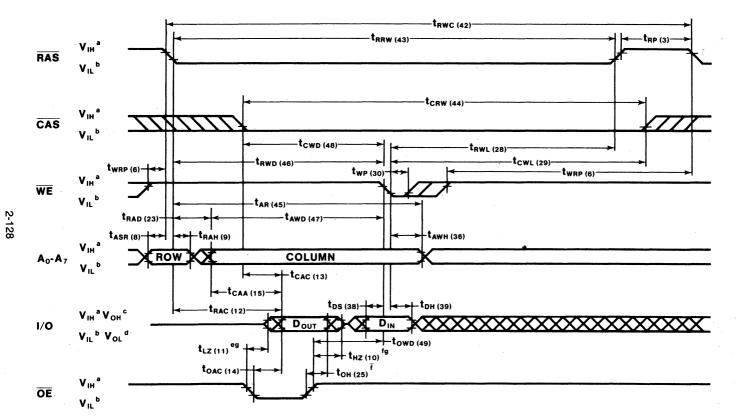

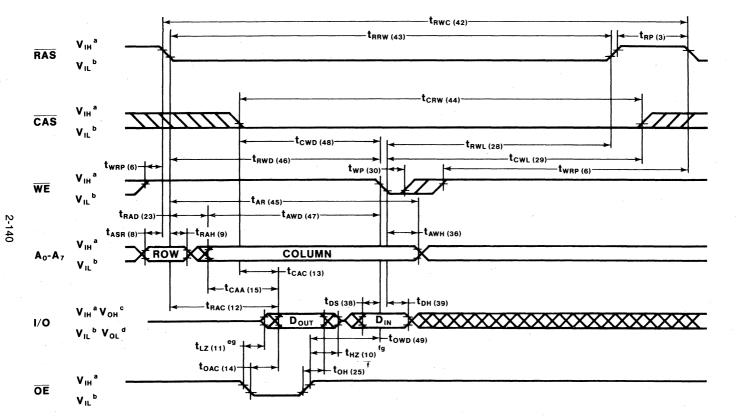

WAVEFORMS (Cont.) Read/Modify/Write Cycle

#### NOTES:

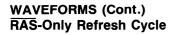

- a., b.  $V_{IH}$  (min) and  $V_{IL}$  (max) are reference levels for measuring timing of input signals.