### THE QUIET REVOLUTION AT INTEL

There's a quiet revolution going on at Intel every day, where new products are being introduced that are changing the face of electronic systems the world over, whether they be in computers, consumer products, industrial systems, or in new applications that have never been attacked before. On the pages of this catalog you will find some of these products. Why not join the revolution yourself!

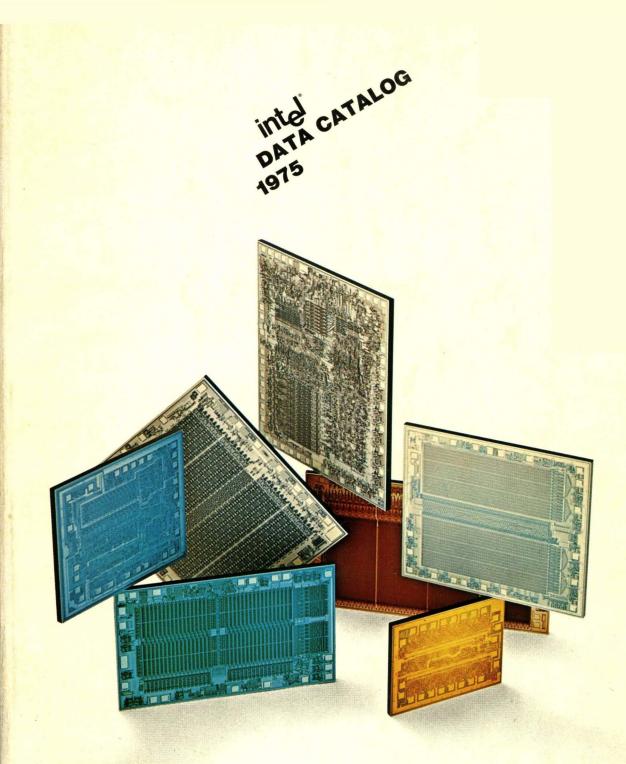

### On the cover:

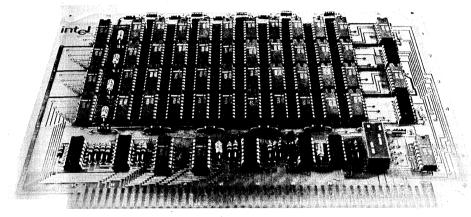

Pictured on the cover of this 1975 edition of the Intel Data Catalog are seven recently introduced Intel products. Each represents the state of the semiconductor art in its area of application.

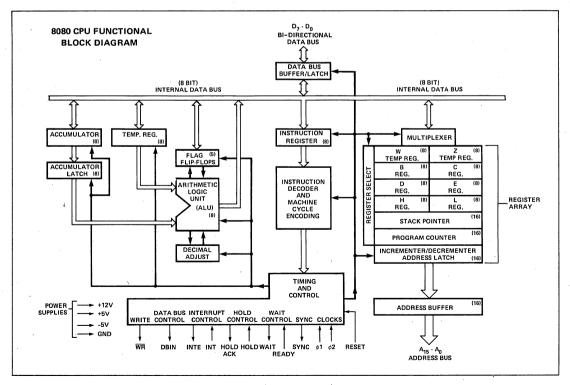

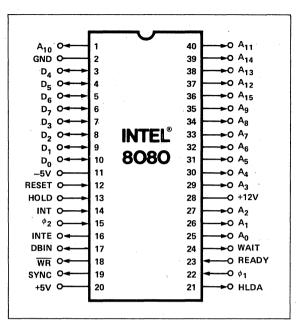

- 1. Intel® 8080. Intel Microcomputers have revolutionized the design of logic systems. This 8-bit CPU is Intel's third generation Microcomputer. It has a repertoire of 78 instructions and an instruction cycle time of 2  $\mu$ sec. The 8080 is manufactured with N-channel silicon-gate technology. Further information on the 8080 may be found on page 6-25.

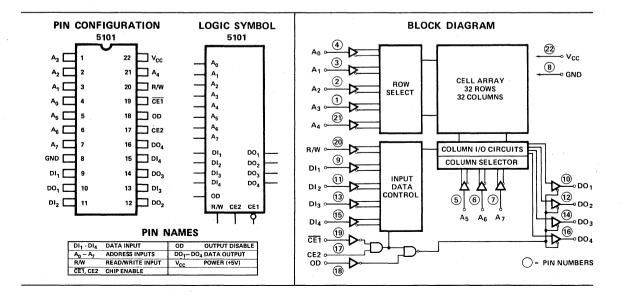

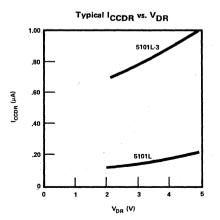

- 2. Intel<sup>®</sup> 5101. This 1024 bit CMOS RAM dissipates only 15 μw per bit when active and only 0.28 nw per bit when in power-down standby. It is organized as 256 words by 4 bits and has an access time of 650 nsec. Four versions are available now and extended temperature range options for military applications will be offered beginning in March 1975. Specifications on the 5101 begin on page 2-115.

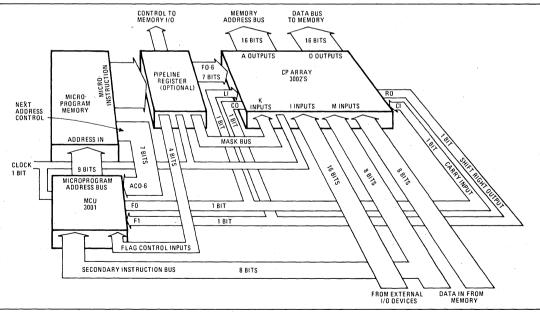

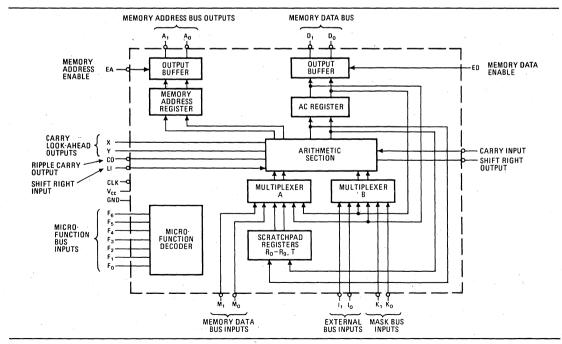

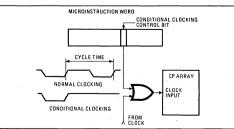

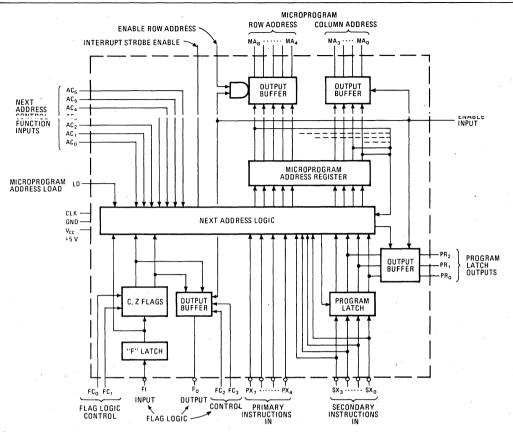

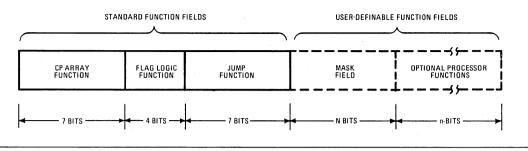

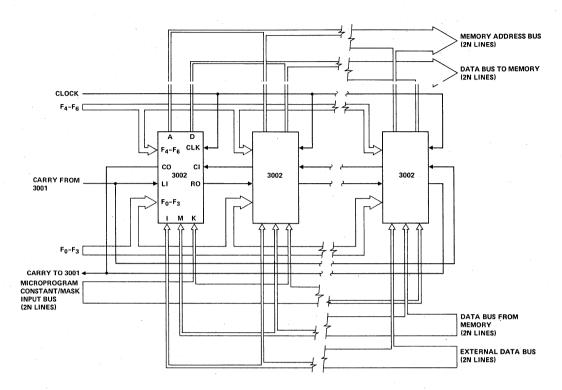

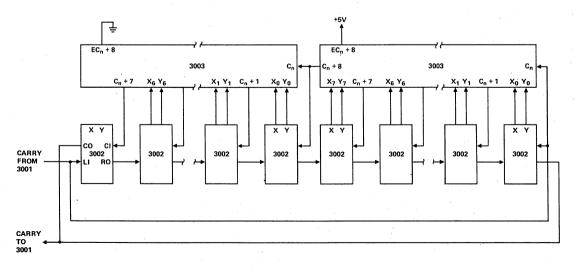

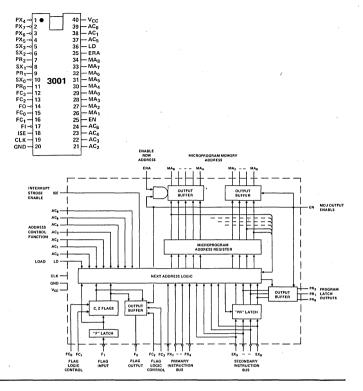

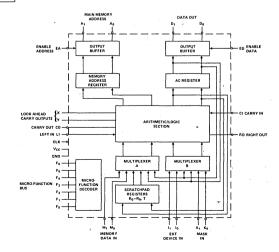

- 3. Intel® 3002. This Schottky Bipolar 2 bit Central Processing Element contains all of the Central Processing Unit circuits of a 2 bit wide slice of a digital computer. An array of 3002's used in conjunction with other members of the Bipolar Microcomputer Set allows the construction of extremely powerful Microprogrammed High Speed Central Processors. Information on the Intel Bipolar Microcomputer Set begins on page 6-53.

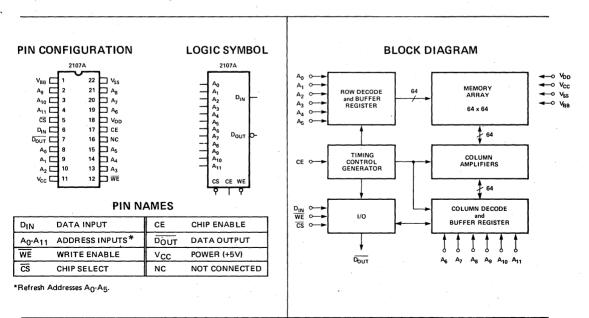

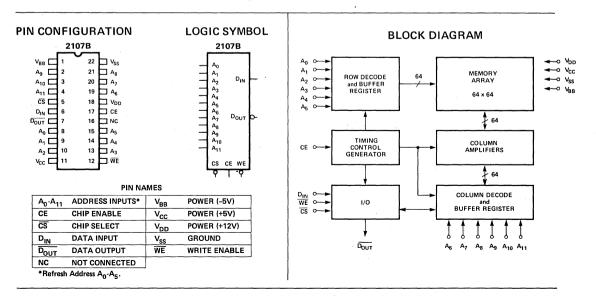

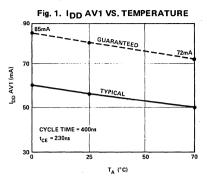

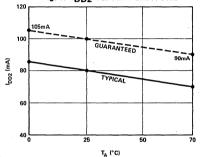

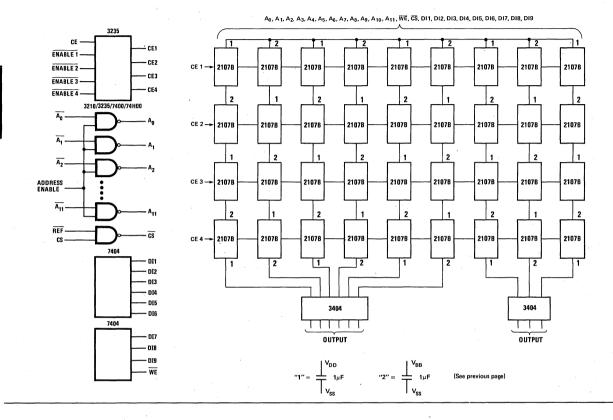

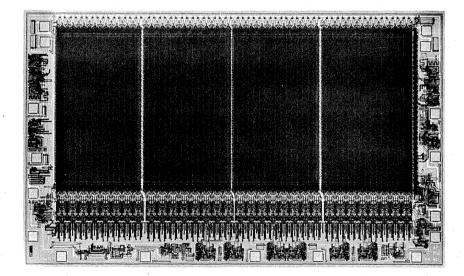

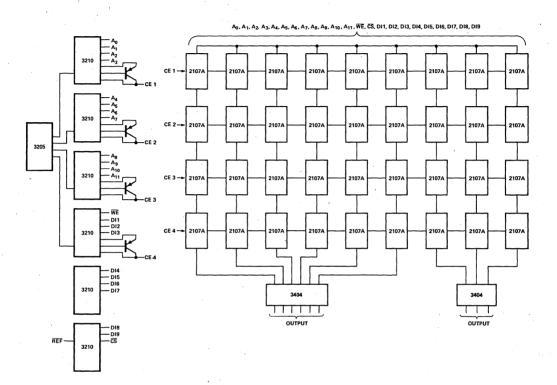

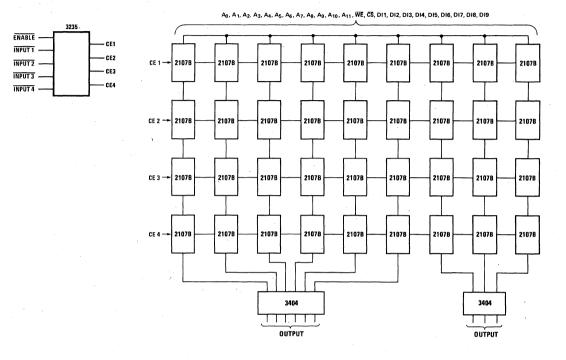

- 4. Intel<sup>®</sup> 2107B. The 2107B 4K N-channel RAM is expected to be the industry's workhorse memory. The 2107B accesses in 200 ns, cycles in 400 ns and is low in cost due to its single transistor cell design and small chip size. Specifications begin on page 2-81.

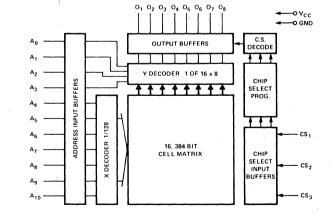

- 5. Intel<sup>®</sup> 2416. This unique new semiconductor memory is a 16,384 bit CCD Memory, organized as 64 registers of 256 bits each. Each register is accessed through a decoding network allowing an average latency time of 100  $\mu$ s and data transfer rates of up to 64 megabits per second. Information on the 2416 is on page 4-19.

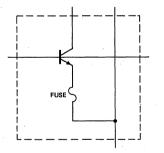

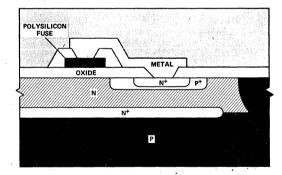

- 6. Intel® 3604. This High Speed 4096 bit PROM is electrically programmed by selectively blowing a unique polysilicon fuse through the application of the appropriate programming pulses. The 3604 is one product of a 28 member family of High Speed Schottky Bipolar 1K, 2K, and 4K PROMS and ROMS. Specifications are on page 3-36.

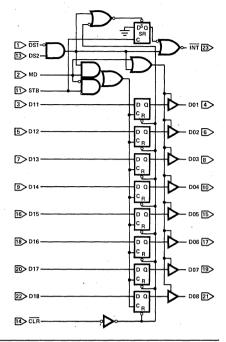

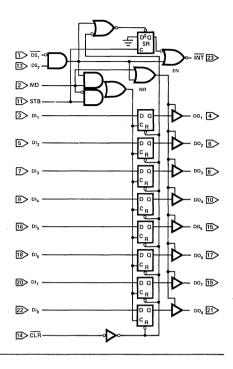

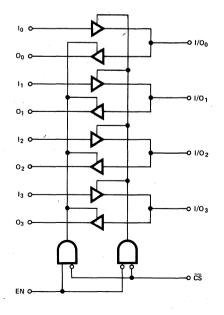

- 7. Intel® 8212. This Schottky Bipolar circuit is an input/output port consisting of an 8-bit latch with three-state output buffers along with control and device selection logic. Because of their multimode capability 8212's can be used to implement latches, buffers, multiplexers, bi-directional bus drivers, or interrupting input/output ports. Information on the 8212 is on page 6-63.

# intel data catalog

Intel Corporation 3065 Bowers Ave. Santa Clara, CA 95051 Tel: 408/246-7501, TWX: 910-338-0026, Telex: 34-6372

# contents

|    |                                                                                                                                                                    | rage                               |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| 1. | Indexes and General Information                                                                                                                                    | 1-1                                |

|    | Functional Index<br>Numerical Index<br>Standard Product Processing and                                                                                             | 1-2<br>1-4                         |

|    | 100% Screening         Packaging Information         Ordering Instructions         Literature Guide         Distributors                                           | 1-6<br>1-8<br>1-12<br>1-13<br>1-14 |

| 2  | · · ·                                                                                                                                                              | 2-1                                |

| 2. | Random Access Memories (RAMs)         RAM Selection Guide         Silicon Gate MOS         Schottky Bipolar         CMOS Silicon Gate                              | 2-2<br>2-3<br>2-101                |

| 3. | Read Only Memories (ROMs)          ROM and PROM Selection Guide          Silicon Gate MOS          Schottky Bipolar          ROM and PROM Programming Instructions | 3-1<br>3-2<br>3-3<br>3-21<br>3-41  |

| 4. | Shift Registers                                                                                                                                                    | 4-1<br>4-2                         |

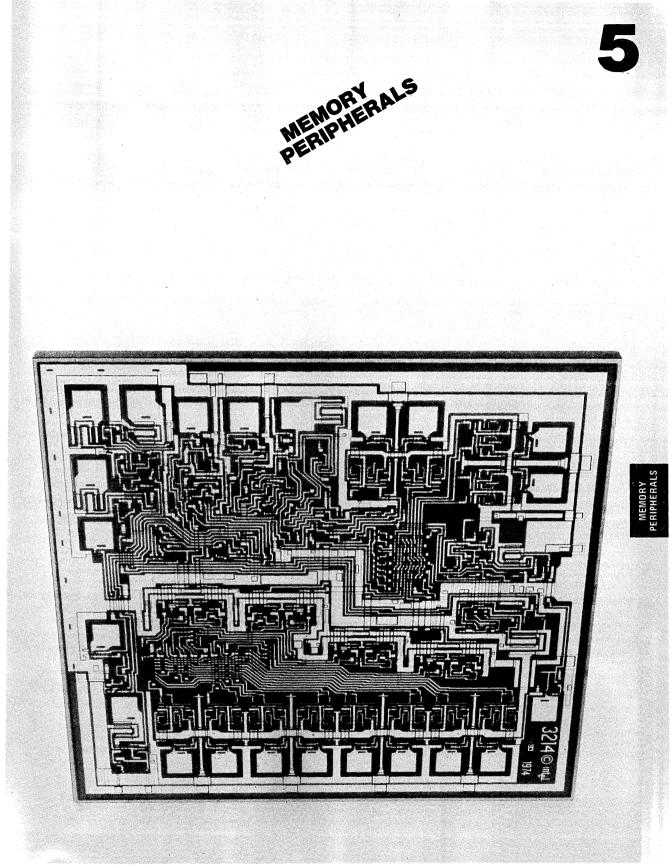

| 5. | Memory Peripherals                                                                                                                                                 | 5-1<br>5-2                         |

| 6. | Microcomputers<br>MCS-4/40 <sup>™</sup><br>MCS-8/80 <sup>™</sup><br>WF 3000                                                                                        | 6-1<br>6-5<br>6-25<br>6-53         |

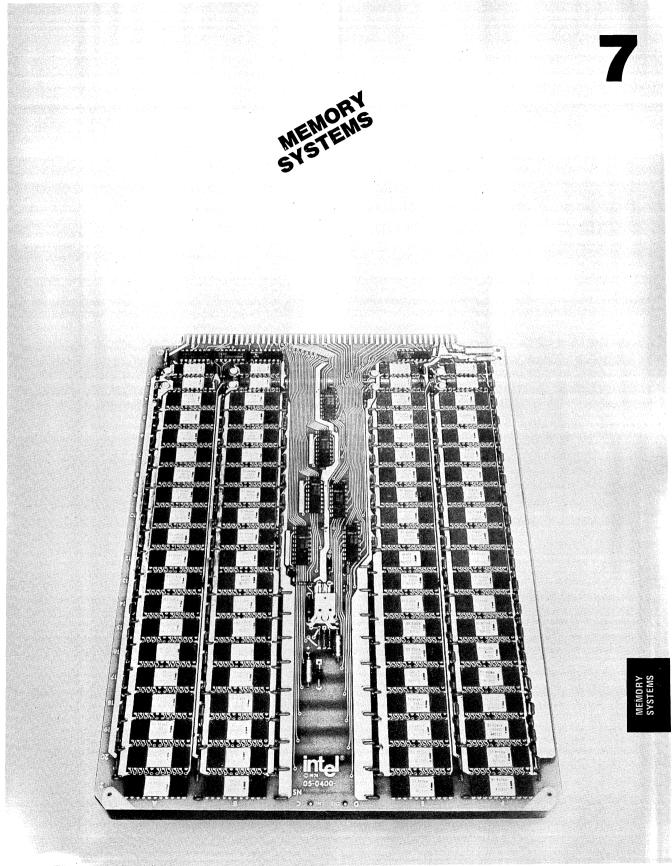

| 7. | Memory Systems                                                                                                                                                     | 7-1                                |

| 8. | Timekeeping Circuits                                                                                                                                               | 8-1<br>8-2                         |

-

1. **INDEXES** & GENERAL **INFORMATION** 2. RAMs RANDOM ACCESS **MEMORIES** 3. ROMs **READ ONLY MEMORIES** 4. SHIFT REGISTERS 5. MEMORY PERIPHERALS 6. **MICRO COMPUTERS** 7. **MEMORY SYSTEMS**

8. TIMEKEEPING CIRCUITS

# intel<sup>®</sup> corporation

Housed today in approximately 500,000 square feet of facilities, Intel is the world's leading supplier of semiconductor memory components. Process technologies used in production by Intel are p-channel, n-channel, and complementary silicon gate MOS and SCHOTTKY Bipolar. This breadth of process technology allows Intel to make the optimum cost-performance trade off for a particular memory application.

Santa Clara Corporate Headquarters

intel facilities

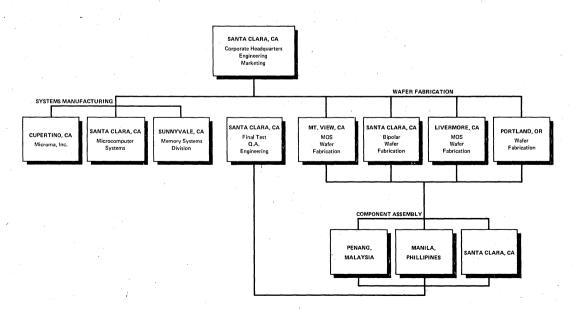

World-wide facilities: Intel manufacturing facilities are located world-wide. Santa Clara, California serves as corporate headquarters. Wafer fabrication plants are located in Mountain View, Santa Clara, and Livermore, California and Portland, Oregon. Assembly operations are performed in Penang, Malaysia; Manila, Philippines; and Santa Clara, California. Marketing offices are located throughout the U.S., in Europe and Japan. New facilities for our Memory Systems Division, Microma and Micro Computer Systems give Intel a total of approximately 500,00 square feet.

# FUNCTIONAL INDEX

INDEXES AND General Information

| -                    |                                                              | PAGE  |             |                                                | Ē |

|----------------------|--------------------------------------------------------------|-------|-------------|------------------------------------------------|---|

| RANDOM A             | CCESS MEMORIES (RAMS)                                        | 2-1   |             |                                                |   |

| SILICON GAT          | E MOS                                                        |       | SILICON GAT | E CMOS                                         |   |

| 1101A                | 256-bit (256w x 1b) Static                                   | 2-3   | 5101        | 1024-bit (256w x 4b) Static Low Power          |   |

| 1101A1               | 256-bit (256w x 1b) Static                                   | 2-3   | 5101-3      | 1024-bit (256w x 4b) Static Low Power          |   |

| 1103                 | 1024-bit (1024w x 1b) Dynamic                                | 2-7   | 5101L       | 1024-bit (256w x 4b) Static Low Power          |   |

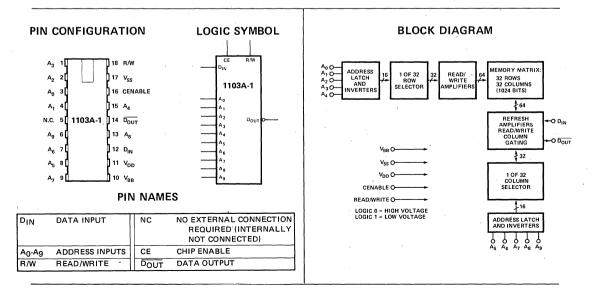

| 1103-1               | 1024-bit (1024w x 1b) Dynamic                                | 2-12  | 5101L-3     | 1024-bit (256w x 4b) Static Low Power          |   |

| 1103A                | 1024-bit (1024w x 1b) Dynamic                                | 2-15  |             |                                                |   |

| 1103A-1              | 1024-bit (1024w x 1b) Dynamic                                | 2-20  |             | Y MEMORIES (ROMs and PROMs)                    |   |

| 1103A-2              | 1024-bit (1024w x 1b) Dynamic                                | 2-25  | ILAD ONL    |                                                |   |

| 2101                 | 1024-bit (256w x 4b) Static                                  | 2-29  | SILICON GAT | E MOS                                          |   |

| 2101-1               | 1024-bit (256w x 4b) Static                                  | 2-29  | 1202        |                                                |   |

| 2101-2               | 1024-bit (256w x 4b) Static                                  | 2-29  | 1302        | 2048-bit (256w x 8b) Mask Programmable         |   |

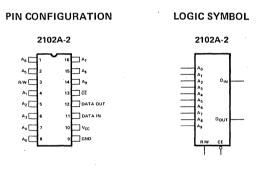

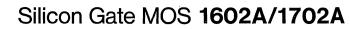

| 2102                 | 1024-bit (1024w x 1b) Static                                 | 2-33  | 1602A       | 2048-bit (256w x 8b) Electrically Programmable |   |

| 2102-1               | 1024-bit (1024w x 1b) Static                                 | 2-37  | 1602A-6     | 2048-bit (256w x 8b) Electrically Programmable |   |

| 2102-2               | 1024-bit (1024w x 1b) Static                                 | 2-29  | 1702A       | 2048-bit (256w x 8b) Erasable and              |   |

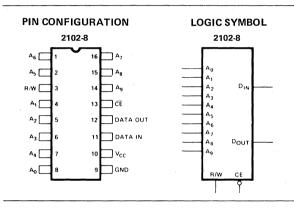

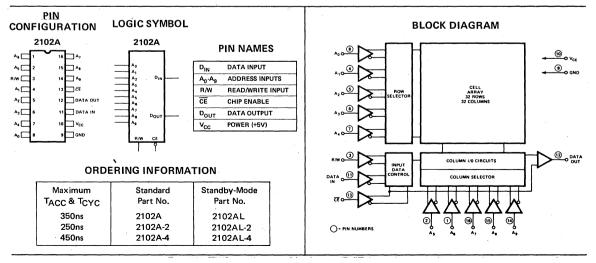

| 2102-8               | 1024-bit (1024w x 1b) Static                                 | 2-41  | 17004.0     | Electrically Programmable                      |   |

| 2102A                | 1024-bit (1024w x 1b) Static                                 | 2-43  | 1702A-6     | 2048-bit (256w x 8b) Erasable and              |   |

| 2102AL               | 1024-bit (1024w x 1b) Static                                 | 2-43  |             | Electrically Programmable                      |   |

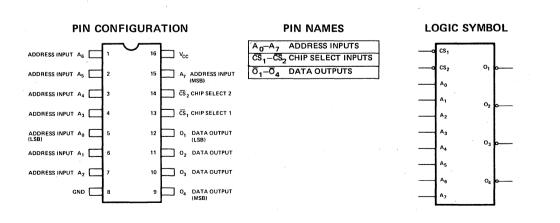

| 2102A-2              | 1024-bit (1024w x 1b) Static                                 | 2-43  | 2308        | 8192-bit (1024w x 8b) Mask Programmable        |   |

| 2102AL-2             | 1024-bit (1024w x 1b) Static                                 | 2-47  | 2316A       | 16384-bit (2048w x 8b) Mask Programmable       |   |

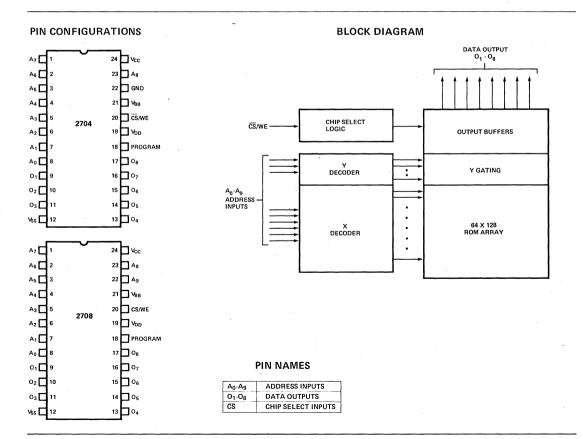

| 2102A-4              | 1024-bit (1024w x 1b) Static                                 | 2-47  | 2704        | 4096-bit (512w x 8b) Erasable and              |   |

| 2102AL-4             | 1024-bit (1024w x 1b) Static                                 | 2-49  |             | Electrically Programmable                      |   |

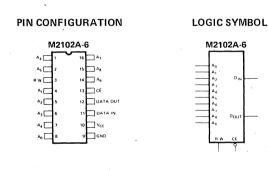

| M2102A-4             | 1024-bit (1024w x 1b) Static                                 | 2-43  | 2708        | 8192-bit (1024w x 8b) Erasable and             |   |

| M2102A-4<br>M2102A-6 | 1024-bit (1024w x 1b) Static                                 | 2-51  |             | Electrically Programmable                      |   |

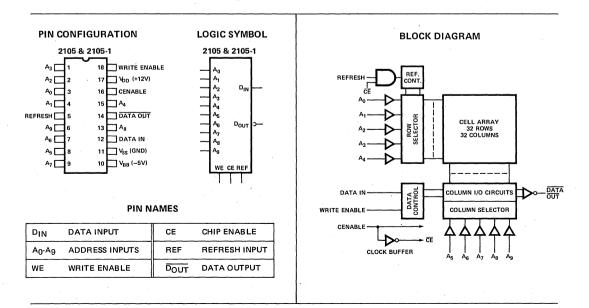

| 2105                 | 1024-bit (1024w x 1b) State<br>1024-bit (1024w x 1b) Dynamic | 2-55  | SCHOTTKY В  |                                                |   |

| 2105                 | 1024-bit (1024-w x 1b) Dynamic                               | 2-55  |             |                                                |   |

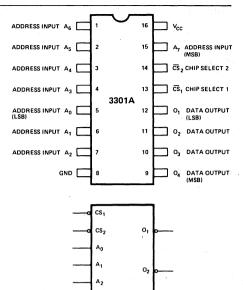

| 2105-2               | 1024-bit (1024w x 1b) Dynamic                                | 2-55  | 3301A       | 1024-bit (256w x 4b) Mask Programmable         |   |

| 2103-2<br>2107A      | 4096-bit (4096w x 1b) Dynamic                                | 2-63  | M3301A      | 1024-bit (256w x 4b) Mask Programmable         |   |

| 2107A                | 4096-bit (4096w x 1b) Dynamic                                | 2-07  | 3302        | 2048-bit (512w x 4b) Mask Programmable         |   |

| 2107A-1<br>2107A-4   |                                                              | 2-75  | 3302-4      | 2048-bit (512w x 4b) Mask Programmable         |   |

|                      | 4096-bit (4096w x 1b) Dynamic                                |       | 3302-6      | 2048-bit (512w x 4b) Mask Programmable         |   |

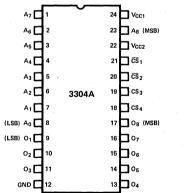

| 2107A-5              | 4096-bit (4096w x 1b) Dynamic                                | 2-77  | 3304A       | 4096-bit (512w x 8b) Mask Programmable         |   |

| 2107A-8              | 4096-bit (4096w x 1b) Dynamic                                | 2-79  | 3304A-4     | 4096-bit (512w x 8b) Mask Programmable         |   |

| 2107B                | 4096-bit (4096w x 1b) Dynamic                                | 2-81  | 3304A-6     | 4096-bit (512w x 8b) Mask Programmable         |   |

| 2107B-4              | 4096-bit (4096w x 1b) Dynamic                                | 2-89  | 3322        | 2048-bit (512w x 4b) Mask Programmable         |   |

| 2107B-6              | 4096-bit (4096w x 1b) Dynamic                                | 2-91  | 3322-4      | 2048-bit (512w x 4b) Mask Programmable         |   |

| 2111                 | 1024-bit (256w x 4b) Static                                  | 2-93  | 3322-6      | 2048-bit (512w x 4b) Mask Programmable         |   |

| 2111-1               | 1024-bit (256w x 4b) Static                                  | 2-93  | 3324A       | 4096-bit (512w x 8b) Mask Programmable         |   |

| 2111-2               | 1024-bit (256w x 4b) Static                                  | 2-93  | 3324A-4     | 4096-bit (512w x 8b) Mask Programmable         | • |

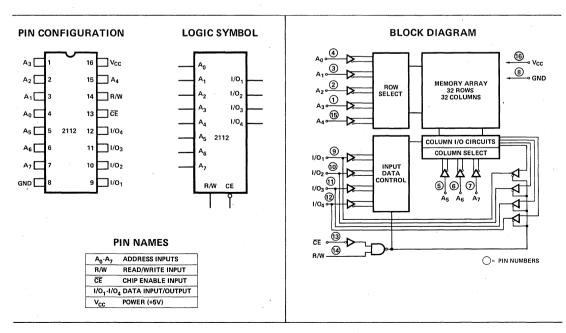

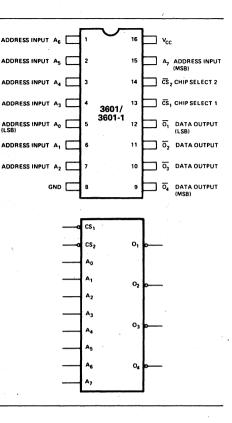

| 2112                 | 1024-bit (256w x 4b) Static                                  | 2-97  | 3601        | 1024-bit (256w x 4b) Electrically Programmable |   |

| 2112-2               | 1024-bit (256w x 4b) Static                                  | 2-97  | 3601-1      | 1024-bit (256w x 4b) Electrically Programmable |   |

| <b>SCHOTTKY</b> В    |                                                              |       | M3601       | 1024-bit (256w x 4b) Electrically Programmable |   |

|                      |                                                              | 1     | 3602        | 2048-bit (512w x 4b) Electrically Programmable |   |

| 3101                 | 64-bit (16w x 4b) Fully Decoded                              | 2-101 | 3602-4      | 2048-bit (512w x 4b) Electrically Programmable |   |

| 3101A                | 64-bit (16w x 4b) Fully Decoded                              | 2-101 | 3602-6      | 2048-bit (512w x 4b) Electrically Programmable |   |

| M3101                | 64-bit (16w x 4b) Fully Decoded                              | 2-105 | 3604        | 4096-bit (512w x 8b) Electrically Programmable |   |

| M3101A               | 64-bit (16w x 4b) Fully Decoded                              | 2-105 | 3604-4      | 4096-bit (512w x 8b) Electrically Programmable |   |

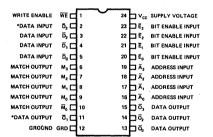

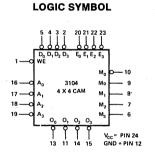

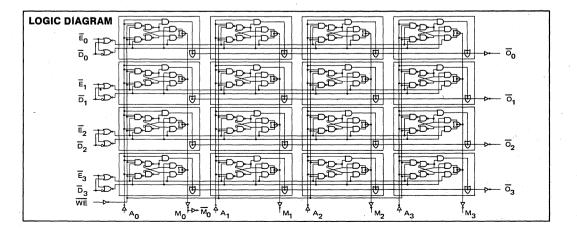

| 3104                 | 16-bit (4w x 4b) Content Addressable                         | 2-107 | 3604-6      | 4096-bit (512w x 8b) Electrically Programmable |   |

| 3106                 | 256-bit (256w x 1b) Fully Decoded                            | 2-111 | 3622        | 2048-bit (512w x 4b) Electrically Programmable |   |

| 3106A                | 256-bit (256w x 1b) Fully Decoded                            | 2-111 | 3622-4      | 2048-bit (512w x 4b) Electrically Programmable |   |

| 3106-8               | 256-bit (256w x 1b) Fully Decoded                            | 2-111 | 3622-6      | 2048-bit (512w x 4b) Electrically Programmable |   |

| 3107                 | 256-bit (256w x 1b) Fully Decoded                            | 2-111 | 3624        | 4096-bit (512w x 8b) Electrically Programmable |   |

| 3107A                | 256-bit (256w x 1b) Fully Decoded                            | 2-111 | 3624-4      | 4096-bit (512w x 8b) Electrically Programmable |   |

| 3107-8               | 256-bit (256w x 1b) Fully Decoded                            | 2-111 |             |                                                |   |

|                      |                                                              |       | 1           |                                                |   |

PAGE

2-115 2-115 2-115 2-115

3-1

3-3

3-7

3-14 3-7 3-14 3-17

3-17 3-18 3-18

3-19

3-23

3-31

3-31 3-31

3-33

3-33

3-33

3-31 3-31

3-31 3-33

3-33

3-25 3-25

3-29

3-32

3-32 3-32

3-34

3-34

3-34

3-32 3-32

3-32

3-38 3-38

# **FUNCTIONAL INDEX**

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                 | PAGE                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SHIFT REGI                                                                               | STERS                                                                                                                                                                                                                                                                                                                                                                                           | 4-1                                                                               | MEMORY SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                    |

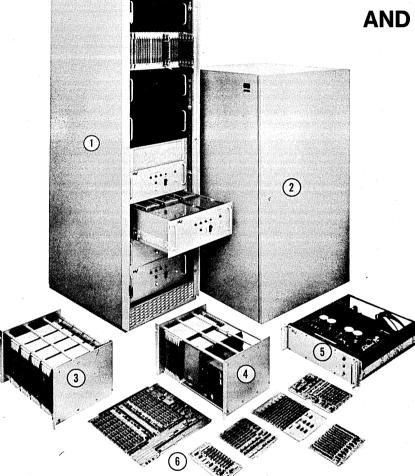

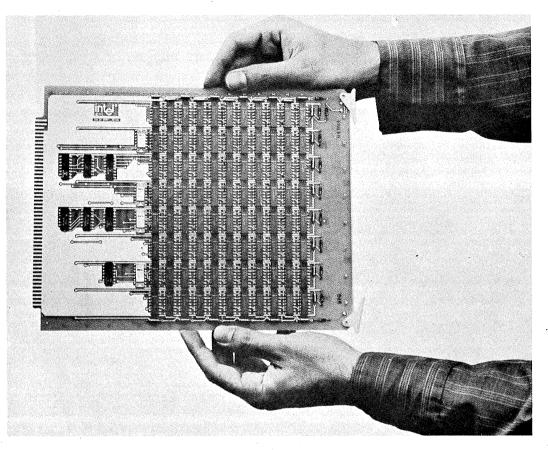

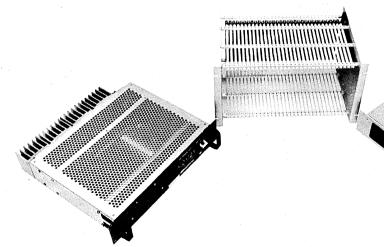

| 1402A<br>1403A<br>1404A<br>1405A<br>1406<br>1407<br>1506<br>1507<br>2401<br>2405<br>2416 | 1024-bit (Quad 256) Dynamic<br>1024-bit (Dual 512) Dynamic<br>1024-bit (Single 1024) Dynamic<br>512-bit Dynamic Recirculating<br>200-bit (Dual 100) Dynamic<br>200-bit (Dual 100) Dynamic<br>200-bit (Dual 100) Dynamic<br>200-bit (Dual 100) Dynamic<br>2048-bit (Dual 1024) Dynamic Recirculating<br>1024-bit Dynamic Recirculating<br>16,384-bit (64 Registers of 256 bits)<br>Dynamic CCD   | 4.3<br>4.3<br>4.7<br>4.11<br>4.11<br>4.11<br>4.11<br>4.11<br>4.15<br>4.15<br>4.19 | in-104K x 18 (or 8K x 9) RAM Memory Boardin-124K x 18 (or 8K x 9) RAM Memory Boardin-144K x 18 (or 8K x 9) RAM Memory Boardin-264K x 9 RAM Memory Boardin-264K x 9 RAM Memory Boardin-304K x 9 RAM Memory Boardin-404K x 9 RAM Memory Boardin-41E4K x 9 RAM Memory Boardin-501K x 10 RAM Memory Boardin-6020K x 10 Serial Memory Boardin-6288K x 1 Serial Memory Boardin-64Memory Cabinetsin-CABMemory Cabinetsin-CHSCard Chassis |

| MEMORY PE                                                                                | RIPHERALS                                                                                                                                                                                                                                                                                                                                                                                       | 5-1                                                                               | in-PS Power Supplies<br>in-Series Accessories                                                                                                                                                                                                                                                                                                                                                                                     |

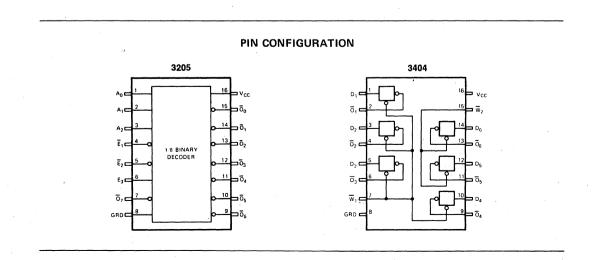

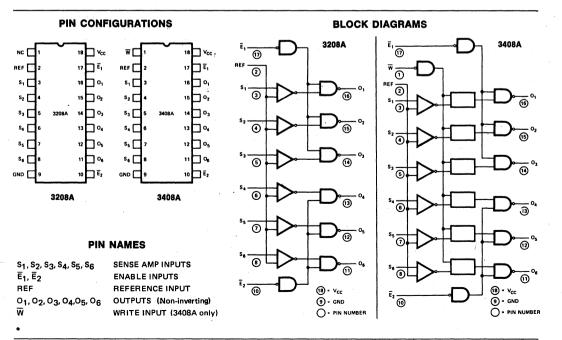

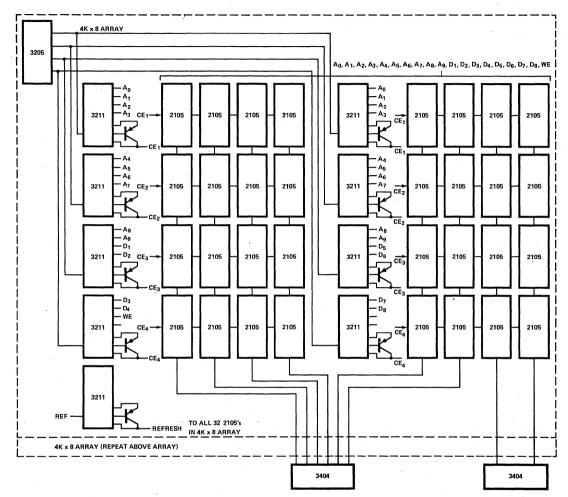

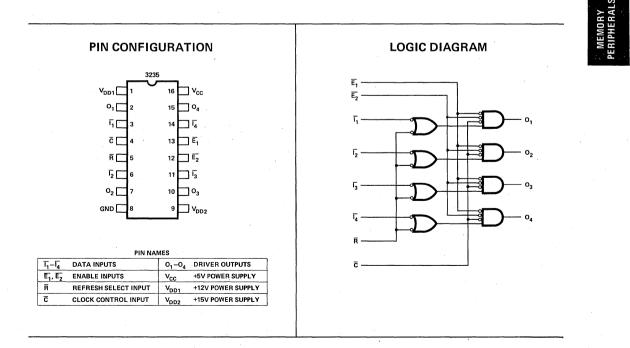

| 3205<br>3207A<br>3207A-1<br>3208A<br>3210<br>3211<br>3235<br>3404<br>3408A               | One-of-Eight Binary High Speed Decoder<br>Quad Bipolar-to-MOS Level Shifter and Driver<br>Quad Bipolar-to-MOS Level Shifter and Driver<br>Hex Sense Amplifier<br>TTL-to-MOS Level Shifter and<br>High Voltage Clock Driver<br>ECL-to-MOS Level Shifter and<br>High Voltage Clock Driver<br>Quad Bipolar-to-MOS Level Shifter and Driver<br>6-bit High Speed Latch<br>Hex Sense Amp with Latches | 5-3<br>5-7<br>5-11<br>5-13<br>5-19<br>5-23<br>5-23<br>5-27<br>5-3<br>5-13         | CMOS TIMEKEEPING CIRCUITS5201LCD Hours/Minutes/Seconds Decoder-Driver5201-2LCD Hours/Minutes/Seconds Decoder-Driver5202LCD Hours and Minutes Decoder-Driver5202-2LCD Hours and Minutes Decoder-Driver5204LCD Time/Seconds/Date Decoder-Driver580132.768 kHz Oscillator-Divider                                                                                                                                                    |

| MICROCOMI                                                                                | PUTER SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                   | 6-1                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MCS 4/40<br>MCS 8/80<br>WF 3000                                                          | 4-bit Microcomputer Set<br>8-bit Microcomputer Set<br>• Bipolar Microprocessor Set                                                                                                                                                                                                                                                                                                              | 6-5<br>6-25<br>6-53                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                   |

1-3

PAGE 7-1 9 8

7-6 7-6 7-8 7-10 7-12 7-14 7-16 7-18 7-20 7-22 7-23 7-24 7-25

8-1 8-3 8-3 8-3 8-3 8-7 8-11

# NUMERICAL INDEX

| 2   |          |                                               | PAGE   |         |                                               | PAGE  |

|-----|----------|-----------------------------------------------|--------|---------|-----------------------------------------------|-------|

|     | 1101A    | 256-bit (256w x 1b) Static RAM                | 2-3    | 2401    | 2048-bit (Dual 1024) Dynamic Recirculating    | 4-15  |

| A   | 1101A1   | 256-bit (256w x 1b) Static RAM                | 2-3    |         | Shift Register                                |       |

| N N | 1103     | 1024-bit (1024w x 1b) Dynamic RAM             | 2-7    | 2405    | 1024-bit Dynamic Recirculating Shift Register | 4-15  |

| Į.  | 1103-1   | 1024-bit (1024w x 1b) Dynamic RAM             | 2-12   | 2416    | 16,384-bit (64 Registers of 256 bits)         | 4-19  |

| É   | 1103A    | 1024-bit (1024w x 1b) Dynamic RAM             | 2-15   |         | CCD Register                                  |       |

|     | 1103A-1  | 1024-bit (1024w x 1b) Dynamic RAM             | 2-20   | 2704    | 4096-bit (512 x 8) PROM                       | 3-18  |

|     | 1103A-2  | 1024-bit (1024w x 1b) Dynamic RAM             | 2-25   | 2708    | 8192-bit (1024 x 8) PROM                      | 3-18  |

|     | 1302     | 2048-bit (256w x 8b) ROM                      | 3-3    | 3001    | Microprogram Control Unit                     | 6-59  |

|     | 1402A    | 1024-bit (Quad 256) Dynamic Shift Register    | 4-3    | 3002    | Central Processing Element                    | 6-59  |

|     | 1403A    | 1024-bit (Dual 512) Dynamic Shift Register    | 4-3    | 3003    | Look-ahead Carry Generator                    | 6-60  |

|     | 1404A    | 1024-bit (Single 1024) Dynamic Shift Register | 4-3    | 3101    | 64-bit (16w x 4b) RAM                         | 2-101 |

|     | 1405A    | 512-bit Dynamic Recirculating Shift Register  | 4-7    | 3101A   | 64-bit (16w x 4b) RAM                         | 2-101 |

|     | 1406     | 200-bit (Dual 100) Dynamic Shift Register     | 4-11   | M3101   | 64-bit (16w x 4b) RAM                         | 2-105 |

|     | 1407     | 200-bit (Dual 100) Dynamic Shift Register     | 4-11   | M3101A  | 64-bit (16w x 4b) RAM                         | 2-105 |

|     | 1506     | 200-bit (Dual 100) Dynamic Shift Register     | 4-11   | 3104    | 16-bit (4w x 4b) Content Addressable RAM      | 2-107 |

|     | 1507     | 200-bit (Dual 100) Dynamic Shift Register     | 4-11   | 3106    | 256-bit (256w x 1b) RAM                       | 2-111 |

|     | 1602A    | 2048-bit (256w x 8b) PROM                     | 3-7    | 3106A   | 256-bit (256w x 1b) RAM                       | 2-111 |

|     | 1602A-6  | 2048-bit (256w x 8b) PROM                     | 3-14   | 3106-8  | 256-bit (256w x 1b) RAM                       | 2-111 |

|     | 1702A    | 2048-bit (256w x 8b) PROM                     | 3-7    | 3107    | 256-bit (256w x 1b) RAM                       | 2-111 |

|     | 1702A-6  | 2048-bit (256w x 8b) PROM                     | 3-14   | 3107A   | 256-bit (256w x 1b) RAM                       | 2-111 |

|     | 2101     | 1024-bit (256w x 4b) Static RAM               | 2-29   | 3107-8  | 256-bit (256w x 1b) RAM                       | 2-111 |

|     | 2101-1   | 1024-bit (256w x 4b) Static RAM               | 2-29   | 3205    | One-of-Eight Binary High Speed Decoder        | 5-3   |

|     | 2101-2   | 1024-bit (256w x 4b) Static RAM               | 2-29   | 3207A   | Quad Bipolar-to-MOS Level Shifter and Driver  | 5-7   |

|     | 2102     | 1024-bit (1024w x 1b) Static RAM              | 2-33   | 3207A-1 | Quad Bipolar-to-MOS Level Shifter and Driver  | 5-11  |

|     | 2102-1   | 1024-bit (1024w x 1b) Static RAM              | 2-37   | 3208A   | Hex Sense Amplifier for MOS Memories          | 5-13  |

|     | 2102-2   | 1024-bit (1024w x 1b) Static RAM              | 2-39   | 3210    | TTL-to-MOS Level Shifter and High Voltage     | 5-19  |

|     | 2102-8   | 1024-bit (1024w x 1b) Static RAM              | 2-41   |         | Clock Driver                                  |       |

|     | 2102A    | 1024-bit (1024w x 1b) Static RAM              | 2-43   | 3211    | ECL-to-MOS Level Shifter and High Voltage     | 5-23  |

|     | 2102AL   | 1024-bit (1024w x 1b) Static RAM              | 2-43   |         | Clock Driver                                  |       |

|     | 2102A-2  | 1024-bit (1024w x 1b) Static RAM              | 2-47   | 3212    | Multi-Mode Latch Buffer                       | 6-63  |

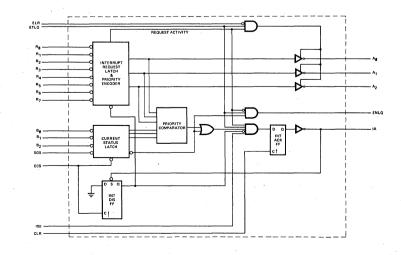

|     | 2102AL-2 | 1024-bit (1024w x 1b) Static RAM              | 2-47   | 3214    | Priority Interrupt Control Unit               | 6-60  |

|     | 2102A-4  | 1024-bit (1024w x 1b) Static RAM              | 2-49   | 3216    | Non-Inverting Bi-Directional Bus Driver       | 6-63  |

|     | 2102AL-4 | 1024-bit (1024w x 1b) Static RAM              | 2-49   | 3226    | Inverting Bi-Directional Bus Driver           | 6-63  |

|     | M2102A-4 | 1024-bit (1024w x 1b) Static RAM              | 2-51   | 3235    | Quad Bipolar-to-MOS Driver                    | 5-27  |

|     | M2102A-6 | 1024-bit (1024w x 1b) Static RAM              | 2-53   | 3301A   | 1024-bit (256w x 4b) Schottky Bipolar ROM     | 3-19  |

|     | 2105     | 1024-bit (1024w x 1b) Dynamic RAM             | 2-55   | M3301A  | 1024-bit (256w x 4b) Schottky Bipolar ROM     | 3-23  |

|     | 2105-1   | 1024-bit (1024w x 1b) Dynamic RAM             | 2-55   | 3302    | 2048-bit (512w x 4b) Schottky Bipolar ROM     | 3-31  |

|     | 2105-2   | 1024-bit (1024w x 1b) Dynamic RAM             | 2-63   | 3302-4  | 2048-bit (512w x 4b) Schottky Bipolar ROM     | 3-31  |

|     | 2107A    | 4096-bit (4096w x 1b) Dynamic RAM             | 2-67   | 3302-6  | 2048-bit (512w x 4b) Schottky Bipolar ROM     | 3-31  |

|     | 2107A-1  | 4096-bit (4096w x 1b) Dynamic RAM             | 2-73   | 3304A   | 4096-bit (512w x 8b) Schottky Bipolar ROM     | 3-33  |

|     | 2107A-4  | 4096-bit (4096w x 1b) Dynamic RAM             | 2-75   | 3304A-4 | 4096-bit (512w x 8b) Schottky Bipolar ROM     | 3-33  |

|     | 2107A-5  | 4096-bit (4096w x 1b) Dynamic RAM             | 2-77   | 3304A-6 | 4096-bit (512w x 8b) Schottky Bipolar ROM     | 3-33  |

|     | 2107A-8  | 4096-bit (4096w x 1b) Dynamic RAM             | 2-79   | 3322    | 2048-bit (512w x 4b) Schottky Bipolar ROM     | 3-31  |

|     | 2107B    | 4096-bit (4096w x 1b) Dynamic RAM             | 2-81   | 3322-4  | 2048-bit (512w x 4b) Schottky Bipolar ROM     | 3-31  |

|     | 2107B-4  | 4096-bit (4096w x 1b) Dynamic RAM             | 2-89   | 3322-6  | 2048-bit (512w x 4b) Schottky Bipolar ROM     | 3-31  |

|     | 2107B-6  | 4096-bit (4096w x 1b) Dynamic RAM             | 2-91   | 3324A   | 4096-bit (512w x 8b) Schottky Bipolar ROM     | 3-33  |

|     | 2111     | 1024-bit (256w x 4b) Static RAM               | 2-93   | 3324A-4 | 4096-bit (512w x 8b) Schottky Bipolar ROM     | 3-33  |

|     | 2111-1   | 1024-bit (256w x 4b) Static RAM               | 2-93   | 3404    | 6-bit High Speed Latch                        | 5-3   |

|     | 2111-2   | 1024-bit (256w x 4b) Static RAM               | 2-93   | 3408A   | Hex Sense Amp with Latches                    | 5-13  |

|     | 2112     | 1024-bit (256w x 4b) Static RAM               | × 2-97 | 3601    | 1024-bit (256w x 4b) Schottky Bipolar PROM    | 3-25  |

|     | 2112-2   | 1024-bit (256w x 4b) Static RAM               | 2-97   | 3601-1  | 1024-bit (256w x 4b) Schottky Bipolar PROM    | 3-25  |

|     | 2308     | 8192-bit (1024w x 8b) ROM                     | 3-17   | M3601   | 1024-bit (256w x 4b) Schottky Bipolar PROM    | 3-29  |

|     | 2316A    | 16,384-bit (2048w x 8b) ROM                   | 3-18   | 3602    | 2048-bit (512w x 8b) Schottky Bipolar PROM    | 3-32  |

|     |          |                                               |        | 1       |                                               |       |

DEXES AN General Formatio

|         |                                                  | PAGE  |

|---------|--------------------------------------------------|-------|

| 3602-4  | 2048-bit (512w x 8b) Schottky Bipolar PROM       | 3-32  |

| 3602-6  | 2048-bit (512w x 8b) Schottky Bipolar PROM       | 3-32  |

| 3604    | 4096-bit (512w x 8b) Schottky Bipolar PROM       | 3-34  |

| 3604-4  | 4096-bit (512w x 8b) Schottky Bipolar PROM       | 3-34  |

| 3604-6  | 4096-bit (512w x 8b) Schottky Bipolar PROM       | 3-34  |

| 3622    | 2048-bit (512w x 4b) Schottky Bipolar PROM       | 3-32  |

| 3622-4  | 2048-bit (512w x 4b) Schottky Bipolar PROM       | 3-32  |

| 3622-6  | 2048-bit (512w x 4b) Schottky Bipolar PROM       | 3-32  |

| 3624    | 4096-bit (512w x 4b) Schottky Bipolar PROM       | 3-38  |

| 3624-4  | 4096-bit (512w x 4b) Schottky Bipolar PROM       | 3-38  |

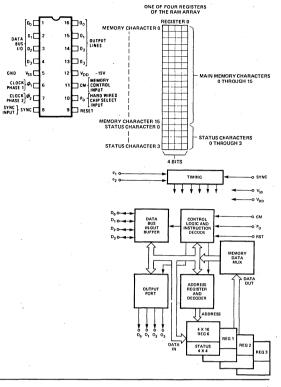

| 4001    | 2048-bit (256w x 8b) ROM and                     | 6-13  |

|         | 4-bit I/O Port                                   | 0.10  |

| 4002    | 320-bit RAM and 4-bit I/O Port                   | 6-16  |

| 4003    | 10-bit Serial-in/Parallel-out,                   | 6-17  |

|         | Serial-out Shift Register                        |       |

| 4004    | 4-bit Central Processor Unit                     | 6-5   |

| 4008    | Address Latch for MCS <sup>™</sup> 4/40          | 6-19  |

| 4009    | I/O Device for MCS <sup>™</sup> 4/40             | 6-19  |

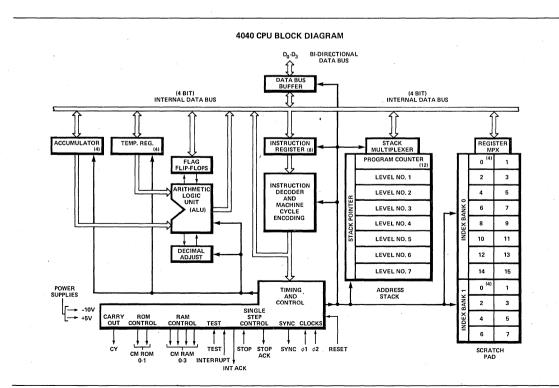

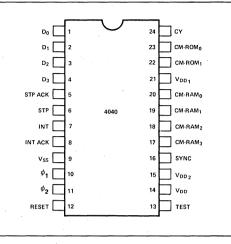

| 4040    | 4-bit Central Processor Unit                     | 6-9   |

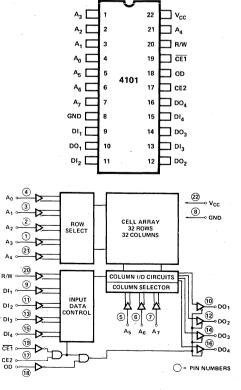

| 4101    | 1024-bit (256w x 4b) Static RAM                  | 6-16  |

| 4201    | Clock Generator for MCS 4/40                     | 6-20  |

| 4207    | General Purpose Input/Output                     | 6-18  |

| 4209    | General Purpose Input/Output                     | 6-18  |

| 4211    | General Purpose Input/Output                     | 6-18  |

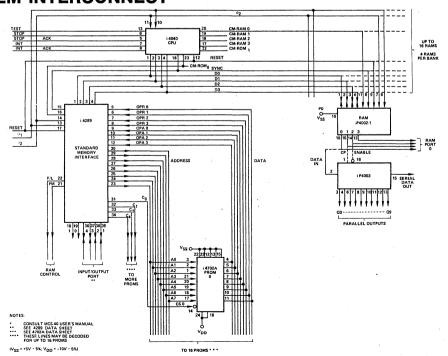

| 4289    | Standard Memory and I/O Interface                | 6-20  |

| 4308    | 8192-bit (1024w x 8b) ROM                        | 6-13  |

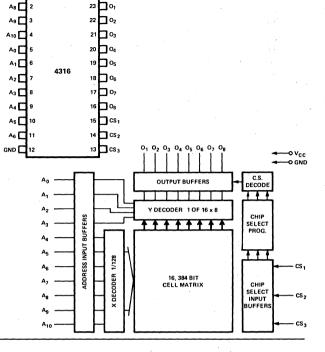

| 4316    | 16,384-bit (2048w x 8b) ROM                      | 6-14  |

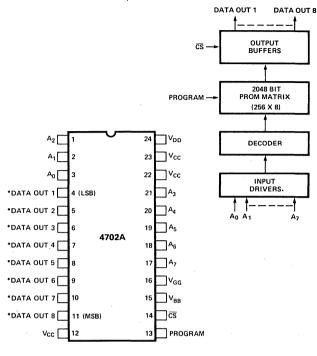

| 4702A   | 2048-bit (256w x 8b) PROM                        | 6-15  |

| 5101    | 1024-bit (256w x 4b) CMOS Low Power RAM          | 2-115 |

| 5101-3  | 1024-bit (256w x 4b) CMOS Low Power RAM          | 2-115 |

| 5101L   | 1024-bit (256w x 4b) CMOS Low Power RAM          | 2-115 |

| 5101L-3 | 1024-bit (256w x 4b) CMOS Low Power RAM          | 2-115 |

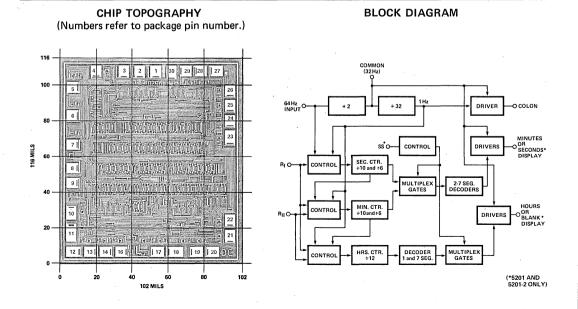

| 5201    | CMOS LCD Hours/Minutes/Seconds<br>Decoder-Driver | 8-3   |

| 5201-2  | CMOS LCD Hours/Minutes/Seconds                   | 8-3   |

|         | Decoder-Driver                                   |       |

| 5202    | CMOS LCD Hours and Minutes Decoder-Driver        | 8-3   |

| 5202-2  | CMOS LCD Hours and Minutes Decoder-Driver        | 8-3   |

| 5204    | CMOS LCD Time/Seconds/Date Decoder-Driver        | 8-7   |

| 5801    | CMOS 32.768 kHz Oscillator-Divider               | 8-11  |

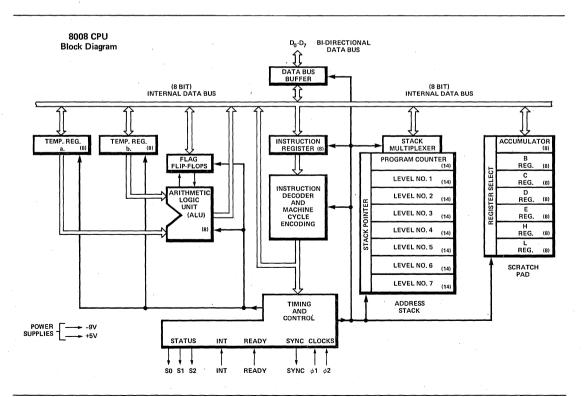

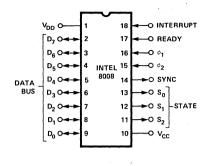

| 8008    | 8-bit Central Processor Unit                     | 6-25  |

| 8008-1  | 8-bit Central Processor Unit                     | 6-25  |

| 8080    | 8-bit Central Processor Unit                     | 6-29  |

|         |                                                  |       |

|         |                                         | PAGE |

|---------|-----------------------------------------|------|

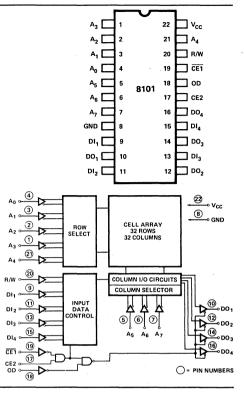

| 8101    | 1024-bit (256w x 4b) RAM                | 6-35 |

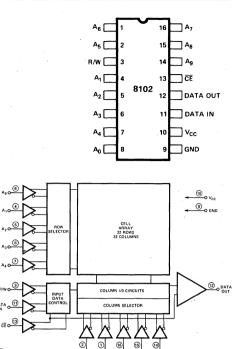

| 8102    | 1024-bit (1024w x 1b) RAM               | 6-36 |

| 8102-2  | 1024-bit (1024w x 1b) RAM               | 6-36 |

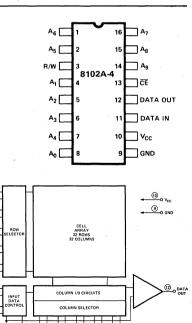

| 8102A-4 | 1024-bit (1024w x 1b) RAM               | 6-36 |

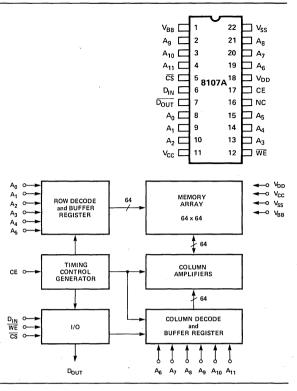

| 8107A   | 4096-bit (4096w x 1b) RAM               | 6-37 |

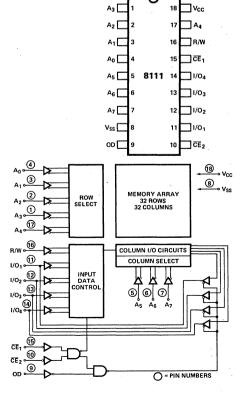

| 8111    | 1024-bit (256w x 4b) RAM                | 6-35 |

| 8201    | Clock Generator for MCS-8™              | 6-41 |

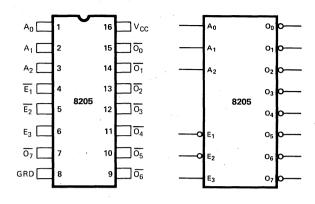

| 8205    | High Speed One-of-Eight Binary Decoder  | 6-40 |

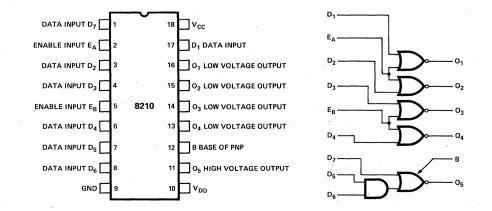

| 8210    | TTL to MOS Level Shifter and            | 6-40 |

|         | High Voltage Clock Driver               |      |

| 8212    | 8-bit Input/Output Port                 | 6-38 |

| 8214    | Priority Interrupt Control Unit         | 6-42 |

| 8216    | Non-inverting Bi-Directional Bus Driver | 6-38 |

| 8224    | 8080 Clock Generator                    | 6-41 |

| 8228    | System Controller for 8080              | 6-42 |

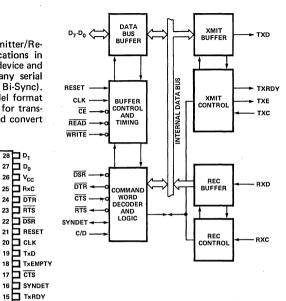

| 8251    | Universal Communications Interface      | 6-39 |

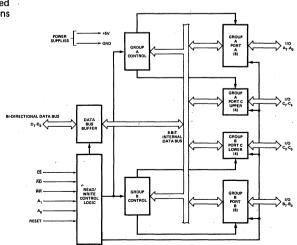

| 8255    | Programmable Peripheral Interface       | 6-39 |

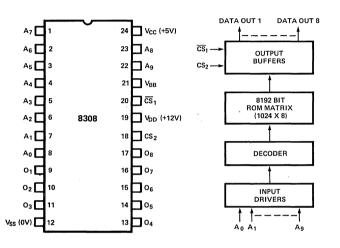

| 8308    | 8192-bit (1024w x 8b) ROM               | 6-33 |

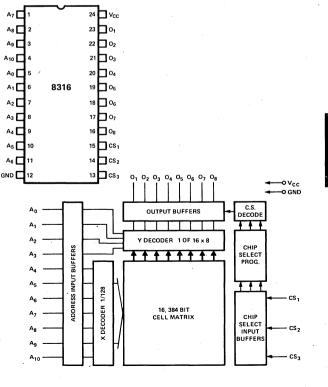

| 8316    | 16,384-bit (2048w x 8b) ROM             | 6-33 |

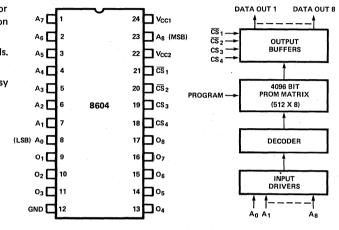

| 8604    | 4096-bit (512w x 8b) PROM               | 6-34 |

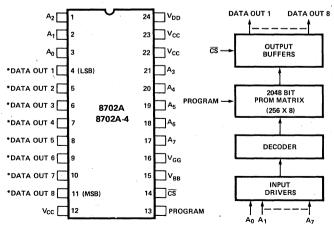

| 8702A   | 2048-bit (256w x 8b) PROM               | 6-34 |

| 8702A-4 | 2048-bit (256w x 8b) PROM               | 6-34 |

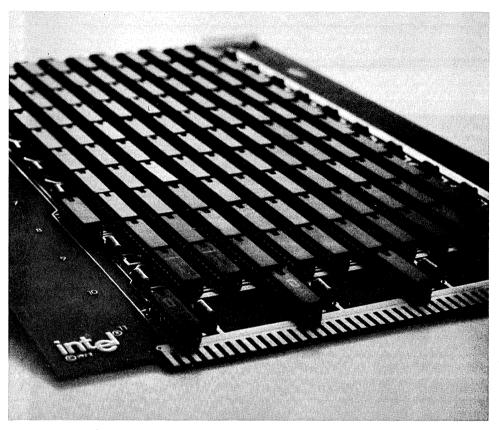

# INTEL MEMORY SYSTEMS

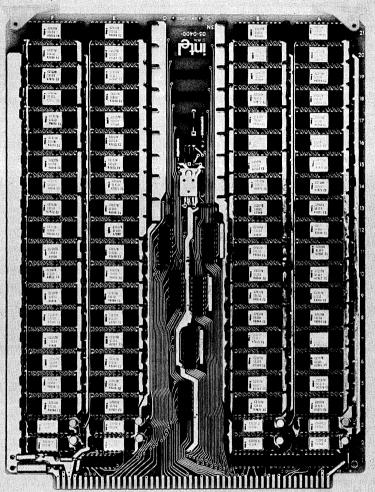

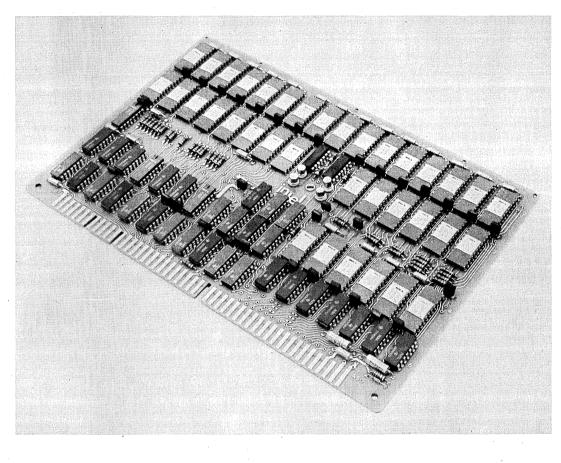

| in-10     | 4K x 18 (or 8K x 9) RAM Memory Board | 7-6  |

|-----------|--------------------------------------|------|

| in-12     | 4K x 18 (or 8K x 9) RAM Memory Board | 7-6  |

| in-14     | 4K x 18 (or 8K x 9) RAM Memory Board | 7-6  |

| in-26     | 4K x 9 RAM Memory Board              | 7-8  |

| in-30     | 4K x 9 RAM Memory Board              | 7-10 |

| in-40     | 4K x 9 RAM Memory Board              | 7-12 |

| in-41E    | 4K x 9 RAM Memory Board              | 7-14 |

| in-50     | 1K x 10 RAM Memory Board             | 7-16 |

| in-60     | 20K x 10 Serial Memory Board         | 7-18 |

| in-62     | 88K x 1 Serial Memory Board          | 7-20 |

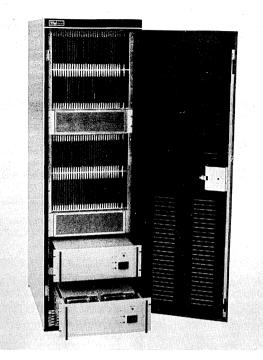

| in-CAB    | Memory Cabinets                      | 7-22 |

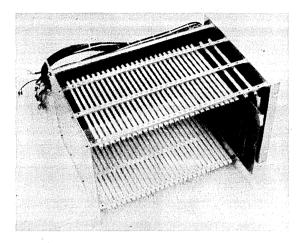

| in-CHS    | Card Chassis                         | 7-23 |

| in-PS     | Power Supplies                       | 7-24 |

| in-Series | Accessories                          | 7-25 |

## **STANDARD PRODUCT PROCESSING AND 100% SCREENING -**

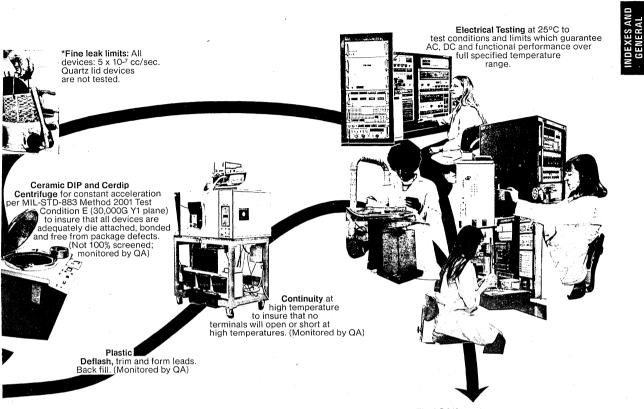

Optical inspection of sorted dice per MIL-STD-883 Method 2010.1B to insure that all devices are free from internal defects which could lead to failure in normal applications. (Monitored by QA)

Die Attach (Monitored by QA)

Lead Bonding (Monitored by QA per MIL-STD-883 Method 2011 Test Condition D.)

Hermeticity Testing to eliminate devices which show insufficient hermeticity. (Monitored by QA) Fine leak C DIPs, CERDIPs, and Metal cans (MIL-STD-883 Method 1014A)\* Gross Leak C DIPs and Cerdips only (Method 1014C; vacuum omitted and 2 hour pressurization).

Metal Can

Pneupactor for constant acceleration and mechanical shock (15,000G for 0.5 msec) to insure that all devices are adequately die attached, bonded and free from package defects. (Not 100% screened. Monitored by QA)

> Temperature Cycling per MIL-STD-883 Method 1010 Test Condition C (10 Cycles: -65°C to +150°C) to insure that all devices are free from metalization, bonding or packaging defects. (Monitored by QA)

Inspection per MIL-STD-883 Method 2010.1B to insure that after assembly all devices are free from defects which could lead to failure in normal applications. (Each lot must pass a QA acceptance)

Precap Visual

MIL-STD-883 100% screens for class B devices which are performed on a "Customer Special" basis are: Stabilization Bake (Method 1008)

(Method 1015, conditions A, B, or C) Burn-in

MIL-STD-883 Group A Electrical Tests of Method 5005 at maximum and minimum operating temperatures are performed on a "Cus-tomer Special" basis.

MIL-STD-883 Group B and C tests are performed periodically to provide generic data. Reprints of the reports on these tests are available from:

Product Marketing Intel Corporation 3065 Bowers Avenue Santa Clara, California 95051

## **COMPUTER GRADE PRODUCTS\***

Final QA Acceptance per MIL-STD-883 Method 2009 External Visual (LTPD 7, Max. Acc. 3), and Electrical AC, DC, Functional Tests at 25°C with correlated limits to guarantee performance over full specified temperature range (LTPD 7, Max. Acc. 2)

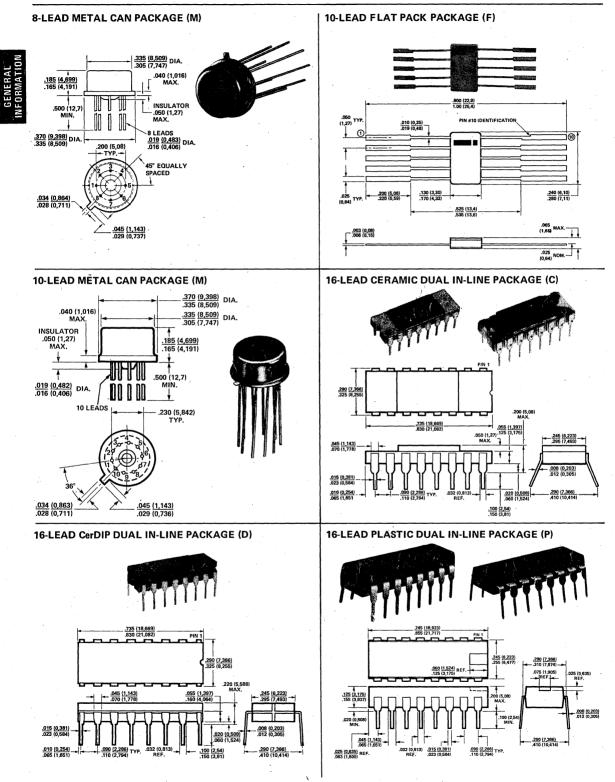

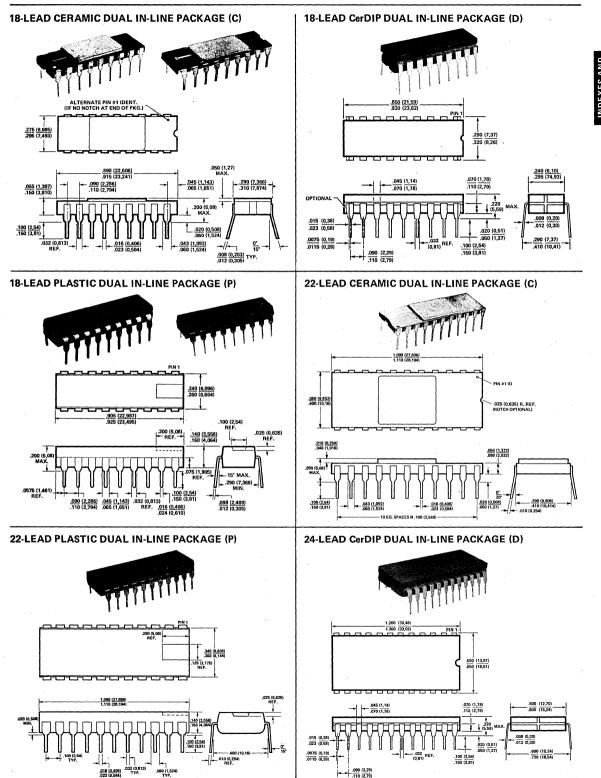

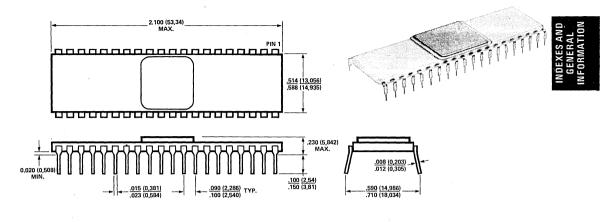

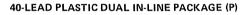

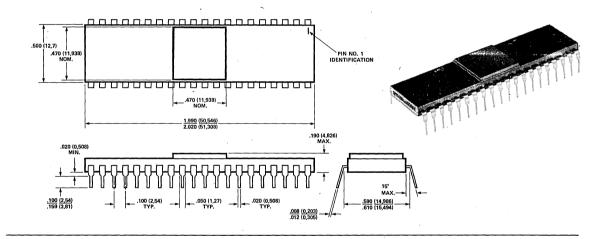

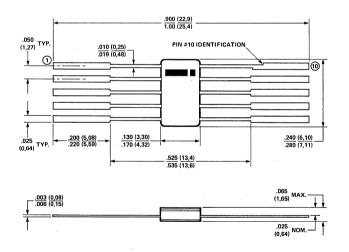

Dimensions in inches and (millimeters).

1-8

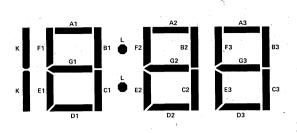

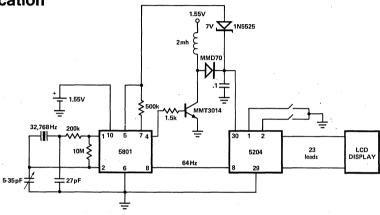

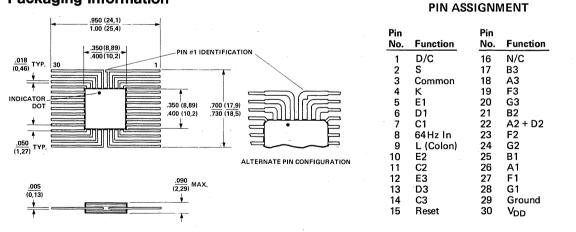

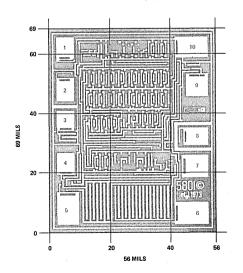

#### 24-LEAD CERAMIC DUAL IN-LINE PACKAGE (C) 1.200 (30,48) PIN оте 1105 NOTE 1 0.125 (3,175) MAX. FOR 1602A 0.150 (3.810) MAX, FOR 1702A OPTIONAL WINDOW LID THICKNESS 0.050 (1,270) MAX. FOR 1602A 0.075 (1,905) MAX. FOR 1702A AFTA NOTE 2 490 (12,446) TRANS. WINDOW FOR ERASABLE .550 (13,97) PIN NOTE 1 .070 (1,78) .045 (1,14) 500 (12,70 600 (15,24 .050 (1,270) 120 (3,048) REF. 1.175 (29,845) 1.300 (33.020) .040 (1,016) REF. ,220 M. Ŧ .015 (0,38) .008 (0,20) TE 2 .100 (2,54) 150 (3,81) .020 (0,51) .600 (15,24) .0075 (0,19) 100 (2,54) .590 (14,986) 610 (15,494) .008 (0,203) 090 (2,29) 110 (2,79) TYP .090 (2,286) 110 (2,794) TYP. .015 (0.381) .022 (0.559) TYP. 24-LEAD PLASTIC DUAL IN-LINE PACKAGE (P) 28-LEAD CERAMIC DUAL IN-LINE PACKAGE (C) PPPPPPPPPPP 1.230 (31,242) 1.250 (31,750) PIN 1 o 4 .190 (4,826) REF. PIN 1 50 (3,81) BEE .514 (13,056) .588 (14,735) .250 (6,35) REF. .530 (13,462) .550 (13,970) .070 (1,778) REF. + 7° REF. .145 (3,683) .165 (4,191) .230 (5,842) MAX. П .030 (0,762 REF. 0° 15' .590 (14,986) .610 (15,494) BEND LINE <u>.000 (2,540)</u> .150 (3,810) .100 (2,540) TYP. .100 016 (0,406) .008 (0,203) 015 (0,381) .590 (14,986) 28-LEAD PLASTIC DUAL IN-LINE PACKAGE (P) **30-LEAD FLAT PACK PACKAGE (F)** חן וני .950 (24,1) 1.00 (25,4) 250 (6.35) .240 (6,096) .075 (1.905) .350 (8,89) PIN #1 IDENTIFICATION .018 (0,46) TYP. ÷ .270 7111 G .190 (4,83) .540 (13,716) .150 (3,81)---INDICATOR DOT 350 (8.89) .700 (17.9) (1,905) REF. 400 (10,2) 1 TTUTTTTTTTTT Ŧ .100 (2,54) TYP. .005 + (0,127) -NON ACCUM. .075 (1,905) REF. .050 (1.27) TYP ALTERNATE PIN CONFIGURATION .155 (3,937) 4 ΠΠΠ (2,29) MAX. .005 (0,13) .125 3,175 .010 (0,254) + H N. ł 1 U U .060 (1.524) 2 (0,8 18 (0,457) TYP. 630 (16,0 ł

### 40-LEAD CERAMIC DUAL IN-LINE PACKAGE (C)

### I. MEMORY COMPONENTS (Products in Sections 2, 3, 4, 5, and 8)

The following list indicates the basic package type(s) available for each Intel product. To order, place the appropriate package designation letter before the Intel product number. (For example, when ordering Intel's standard 1103 in a plastic dual in-line package, it should be ordered as P 1103.)

| Package Designation Letter | Basic Package Type Description                      |

|----------------------------|-----------------------------------------------------|

| C                          | Ceramic (Metal Lid) Dual In-line Package (Hermetic) |

| D                          | CerDIP (Glass Seal) Dual In-line Package (Hermetic) |

| P                          | Plastic Dual In-line Package                        |

| Μ                          | Metal Can Package (Hermetic)                        |

| F .                        | Flat Package                                        |

Within each basic package type there are various outlines corresponding to the different number of leads. (See the package outline on page 1-8.)

| Intel Product Type                           | P | acka | indai<br>ige T<br>ailab | ype | No.<br>Of<br>Leads | Intel Product Type                 | Pa | icka | ndard<br>ge Ty<br>ilable | oe C | No<br>Of<br>eac |

|----------------------------------------------|---|------|-------------------------|-----|--------------------|------------------------------------|----|------|--------------------------|------|-----------------|

| 1101A, 1101A-1                               | Ρ | С    |                         |     | 16                 | 3101, 3101A                        | Ρ  | С    | D                        | 1    | 16              |

| 1103, 1103-1, 1103A, 1103A,<br>1103A-2       | Ρ | с    | D                       |     | 18                 | 3104<br>3106, 3106A, 3106-8, 3107, |    | С    | _                        |      | 24              |

| 1302                                         | Ρ | С    |                         |     | 24                 | 3107A, 3107-8                      | Ρ  | С    | D                        | 1    | 16              |

| 1402A                                        |   | С    |                         |     | 16                 | 3205                               | Р  | С    | D                        | . 1  | 16              |

| 1403A                                        |   |      |                         | М   | 8                  | 3207A, 3207A-1                     |    |      | D                        | 1    | 16              |

| 1404A                                        |   |      |                         | М   | 8                  | 3208A                              | Р  |      | D                        | 1    | 18              |

| 1405A                                        |   |      |                         | М   | 10                 | 3210                               |    |      | D                        | 1    | 18              |

| 1406, 1407, 1506, 1507                       |   |      |                         | М   | 8                  | 3211                               |    |      | D                        | 1    | 18              |

| 1602A, 1602A-6                               |   | С    |                         |     | 24                 | 3235                               |    |      | D                        | 1    | 16              |

| 1702A, 1702A-6                               |   | С    |                         |     | 24                 | 3301A                              | Р  | С    | D                        | . 1  | 16              |

| 2101, 2101-1, 2101-2                         | Ρ | С    | D                       |     | 22                 | M3301A                             |    | С    | D                        | 1    | 10              |

| 2102, 2102-1, 2102-2, 2102-8                 | Ρ | С    |                         |     | 16                 | 3302, 3302-4, 3302-6               | Ρ  | С    | D                        | 1    | 16              |

| 2102A, 2102AL, 2102A-2,                      |   |      |                         |     |                    | 3304A, 3304A-4, 3304A-6            |    | С    | D                        | 2    | 24              |

| 2102AL-2, 2102A-4,                           | Ρ | С    | D                       |     | 16                 | 3322, 3322-4, 3322-6               | P  | С    | D                        |      | 16              |

| 2102AL-4                                     |   | ~    |                         |     | 10                 | 3324A, 3324A-4                     |    | С    | ; D                      |      | 24              |

| M2102A-4, M2102A-6                           | - | С    |                         |     | 16                 | 3404                               | Р  | С    | D                        |      | 16              |

| 2105, 2105-1, 2105-2                         | Ρ | С    |                         |     | 18                 | 3408A                              | Р  |      | D                        | 1    | 18              |

| 2107A, 2107A-1, 2107A-4,<br>2107A-5, 2107A-8 | Ρ | С    | D                       |     | 22                 | 3601, 3601-1                       |    |      | D                        |      | 16              |

| 2107B, 2107B-4, 2107B-6                      | Р | с    | D                       |     | 22                 | M3601                              |    |      | D                        |      | 16              |

| 2111, 2111-1, 2111-2                         | P | č    | D                       |     | 18                 | 3602, 3602-4, 3602-6               |    |      | D                        |      | 16              |

| 2112, 2112-2                                 | P | c    | D                       |     | 16                 | 3604, 3604-4, 3604-6               |    |      | D                        |      | 24              |

| 2308                                         | P | c    | D                       |     | 24                 | 3622, 3622-4, 3622-6               |    |      | D                        |      | 1               |

| 2316A                                        | P | c    |                         |     | 24                 | 3624, 3624-4                       |    |      | D                        |      | 24              |

| 2401, 2405                                   | P | c    |                         |     | 24<br>16           | 5101, 5101-3, 5101L, 5101L-3       | Ρ  | С    | D                        |      | 2:              |

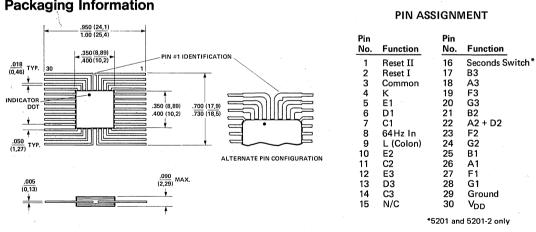

| C2416                                        | F | c    |                         |     | 22                 | 5201, 5201-2                       |    |      |                          |      | 3(              |

| -2416<br>P2416                               | Р | U    |                         |     | 22<br>18           | 5202, 5202-2                       |    |      |                          |      | 3               |

| 2704                                         | ٢ | ~    |                         |     |                    | 5204                               |    |      | 1                        | = ;; | 3               |

| ////4                                        |   | С    |                         |     | 24                 | 5801                               |    |      |                          | = '  | 1               |

NOTE: The data sheets in this catalog are subject to change without notice. You can insure your specification is the current revision by contacting your local Intel sales office.

# LITERATURE GUIDE

The following literature guide provides further information on many products described in this data catalog. The list includes only a few of our major pieces of literature. If you have specific requirements for more detailed information on one or more of our products, contact your local Intel sales office or Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051. If you wish to receive literature on a continuing basis, please fill our the card at the front of this book.

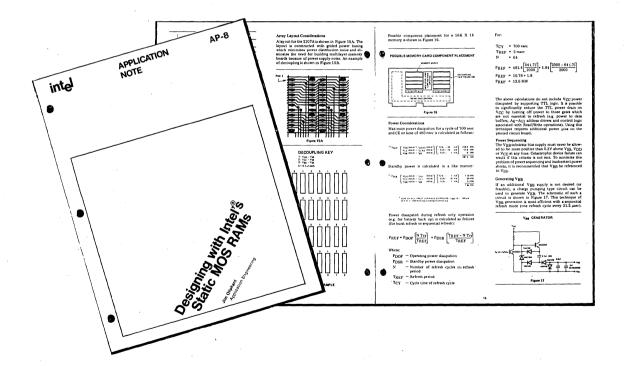

### APPLICATION NOTES AND ARTICLE REPRINTS

- AP4 Designing Memory Systems with the Intel<sup>®</sup> 2107A 4K RAM

- AP5 Designing High Speed, Low Cost Memory Systems with the Intel<sup>®</sup> 2105

- AP6 Designing with Intel® PROMs & ROMs

- AP8 Designing with Intel®s Static MOS RAMs

- AP10 Memory System Design with the Intel® 2107B 4K RAM

- AR12 Semiconductor Memory Costs Present and Future

- AR14 1024 Bit Bipolar RAM

### MICROCOMPUTER LITERATURE

AR3 Microcomputers, What they mean to your Company MCS-40<sup>™</sup> User's Manual MCS-80<sup>™</sup> User's Manual MCS-80<sup>™</sup> Systems Manual

# INTEL DISTRIBUTORS

### U.S. DISTRIBUTORS

### WEST

INDEXES AND GENERAL

NFORMATION

ARIZONA Cramer/Arizona 2643 East University Drive Phoenix 85034 Tel: (602) 263-1112 Hamilton/Avnet Electronics 2615 South 21st Street Phoenix 85034 Tel: (602) 275-7851

### CALIFORNIA

Hamilton/Avnet Electronics 575 E. Middlefield Road Mountain View 94040 Tel: (415) 961-7000 Hamilton/Avnet Electronics 8917 Complex Drive San Diego 92123 Tel: (714) 279-2421 Tel: (174) 279-2421 Hamilton Electro Sales 10912 W. Washington Boulevard Culver City 90230 Tel: (213) 558-2121 Cramer/San Francisco 720 Palomar Avenue Sunnyvale 94086 Tel: (400) 709-3011 Cramer/Los Angeles 17201 Daimler Street Irvine 92705 Tel: (714) 979-3000 Cramer/San Diego 8975 Complex Drive San Diego 92123 Tel: (714) 565-1881

#### COLORADO

Cramer/Denver 5465 E. Evans PI. at Hudson Denver 80222 Tel: (303) 758-2100 Hamilton/Avnet Electronics 5921 No. Broadway Denver 80216 Tel: (303) 534-1212

#### NEW MEXICO

Hamilton/Avnet Electronics 2450 Baylor Drive, S.E. Albuquerque 87119 Tel: (505) 765-1500 Cramer/New Mexico 137 Vermont, N.E. Albuquerque 87108 Tel: (505) 265-5767

### OREGON

Almac/Stroum Electronics 4475 S.W. Scholls Ferry Rd. Portland 97225 Tel: (503) 292-3534

### UTAH

Cramer/Utah 391 W. 2500 South Salt Lake City 84115 Tel: (801) 487-4131 Hamilton/Avnet Electronics 647 W. Billinis Road Salt Lake City 84119 Tel: (801) 262-8451

#### WASHINGTON

Hamilton/Avnet Electronics 13407 Northrup Way Bellevue 98005 Tel: (206) 746-8750 Almac/Stroum Electronics 5811 Sixth Ave. South Seattle 98108 Tel: (206) 763-2300 Cramer/Seattle 5602 Sixth Ave. South Seattle 98108 Tel: (206) 762-5755

MID-AMERICA

оню

Hamilton/Avnet Electronics 118 Westpark Road Dayton 45459 Tel: (513) 433-0610 TWX: 810-450-2531

Sheridan Sales Co. 10 Knollcrest Drive

Cramer/Cleveland 5835 Harper Road Cleveland 44139 Tel: (216) 248-8400 TWX: 810-427-9407

Cleveland 44143 Tel: (216) 461-1400

Beachwood 44122 Tel: (216) 831-0130

TEXAS

Cramer/Tri States, Inc. 666 Redna Terrace Cincinnati 45215 Tel: (513) 771-6441 TWX: 810-461-2882

Sheridan Sales Co. 23224 Commerce Park Road

Sheridan Sales Co. Shiloh Building, Suite 250 5045 North Main Street Dayton 45405 Tel: (513) 277-8911

TEXAS Cramer Electronics 2970 Blystone Dallas 75220 Tel: (214) 350-1355 Hamilton/Avnet Electronics 4445 Sigma Road Dallas 75240 Tel: (214) 661-8661

Hamilton/Avnet Electronics 1216 W. Clay Houston 77019 Tel: (713) 526-4661

Component Specialties, Inc. 10907 Shady Trail, Suite 101 Dallas 75220 Tel: (214) 357-4576

Tel: (214) 357-4576 Component Specialties, Inc. 7313 Ashcroft Street Houston 77036 Tel: (713) 771-7237

Hamilton/Avnet Electronics 761 Beta Drive

Cincinnati 45222 Tel: (513) 761-5432 TWX: 810-461-2670

Cramer/Chicago 1911 So. Busse Rd Mt. Prospect 60056 Tel: (312) 593-8230 Hamilton/Avnet Electronics 3901 No. 25th Ave. Schiller Park 60176 Tel: (312) 678-6310

### KANSAS Hamilton/Avnet Electronics 37 Lenexa Industrial Center 9900 Pflumm Road Lenexa 66215 Tel: (913) 888-8900

### MICHIGAN

ILLINOIS

Sheridan Sales Co. 24543 Indoplex Drive Farmington Hills 48024 Tel: (313) 477-3800 Cramer/Detroit 13193 Wayne Road Livonia 48150 Tel: (313) 425-7000 TWX: 810-242-2985 Hamilton/Avnet Electronics 12870 Farmington Road Livonia 48150 Tel: (313) 522-4700 TWX: 810-242-8775

### MINNESOTA

Industrial Components, Inc. 5280 West 74th Street Minneapolis 55435 Tel: (612) 831-2666 Cramer/Bonn 7275 Bush Lake Road Edina 55435 Tel: (612) 835-7811 Hamilton/Avnet Electronics 7683 Washington Avenue, So. Edina 55435 Tel: (612) 941-3801

### MISSOURI

Hamilton/Avnet Electronics 364 Brookes Lane Hazelwood 63042 Tel: (314) 731-1144 Sheridan Sales Co. 110 South Highway 140, Suite 10 Florissant 63033 Tel: (314) 837-5200

#### WISCONSIN

Cramer/Wisconsin 430 West Rawson Avenue Oak Creek 53154 Tel: (414) 764-1700

### NORTHEAST

CONNECTICUT Cramer/Connecticut 35 Dodge Avenue North Haven 06473 Tel: (203) 239-5641 Hamilton/Avnet Electronics 643 Danbury Road Georgetown 06829 Tel: (203) 762-0361

MARYLAND Cramer/EW Baltimore 7255 Standard Drive Hanover 21076 Tel: (301) 796-5790 Cramer/EW Washington 16021 Industrial Drive Gaithersburg 20760 Tel: (301) 948-0110 Hamilton/Avnet Electronics 7255 Standard Drive Hanover 21076 Tel: (301) 796-5000

MASSACHUSETTS Cramer Electronics Inc. 85 Wells Avenue Newton 02159 Tel: (617) 969-7700 Hamilton/Avnet Electronics Hamilton/Avnet Elec 185 Cambridge Stree Burlington 01803 Tel: (617) 273-2120

### NEW JERSEY

NEW JERSEY Cramer/Pennsylvania, Inc. 12 Springdale Road Cherry Hill Industrial Center Cherry Hill 08033 Tol: (080) 424-993 Tol: (080) 424-993 Hamilton/Avnet Electronics 218 Little Falls Road Cedar Grove 07009 Tel: (201) 239-0600 TWX: 710-994-5787 Cramer/New Jersey No. 1 Barrett Avenue Moonachie 07074 Tel: (201) 935-5600 Hamilton/Avnet Electronics Hamilton/Avnet Electronics 113 Gaither Drive East Gate Industrial Park Mt. Laurel 08057 Tel: (609) 234-2133 TWX: 710-897-1405

### NEW YORK

Cramer/Binghamton 3220 Watson Boulevard Endwell 13760 Tel: (607) 754-6661 Cramer/Rochester 3000 Winton Road South Rochester 14623 Tel: (716) 275-0300 Hamilton/Avnet Electronics 167 Clay Road Rochester 14623 Tel: (716) 442-7820 161: (/16) 442-7820 Cramer/Syracuse 6716 Joy Road East Syracuse 13057 Tel: (315) 437-6671 Hamilton/Avnet Electronics 6500 Joy Road E. Syracuse 13057 Tel: (315) 437-2642 Cramer/Long Island 29 Oser Avenue Hauppauge, L.I. 11787 Tel: (516) 231-5600 TWX: 510-227-9863 Hamilton/Avnet Electronics 70 State Street Westbury, L.I. 11590 Tel: (516) 333-5800 TWX: 510-222-8237

### PENNSYLVANIA

Sheridan Sales Co. 1717 Penn Avenue, Suite 5009 Pittsburgh 15221 Tel: (412) 244-1640 Cramer Electronics 616 Beatty Drive Monroeville 15146 Tel: (412) 242-7410

### SOUTHEAST

ALABAMA Cramer/EW Huntsville, Inc. 2310 Bob Wallace Avenue, S.W. Huntsville 35805 Tel: (205) 539-5722 Hamilton/Avnet Electronics 805 Oster Drive NW Huntsville 35805 Tel: (205) 533-1170

FLORIDA Cramer/E.W. Hollywood 4035 No. 29th Avenue Hollywood 33020 Tel: (305) 923-8181 Hamilton/Avnet Electronics 4020 No. 29th Ave. Hollywood 33021 Tel: (305) 925-5401 Cramer/E.W. Orlando 345 No. Graham Ave. Orlando 32814 Tel: (305) 894-1511

GEORGIA Cramer/EW Atlanta 3923 Oakcliff Industrial Center Atlanta 30340 Tel: (404) 448-9050 Hamilton/Avnet Electronics 6700 I 85, Access Road, Suite 2B Norcross 30071 Tel: (404) 448-0800

NORTH CAROLINA Cramer Electronics 938 Burke Street Winston-Salem 27102 Tel: (919) 725-8711

### CANADA

BRITISH COLUMBIA L. A. Varah Ltd. 2077 Alberta Street Vancouver 10 Tel: (604) 873-3211

ONTARIO Cramer/Canada 920 Alness Avenue, Unit No. 9 Downsview Toronto 392 Tel: (416) 661-9222 TWX: 610-492-6210 Hamilton/Avnet Electronics 6291-16 Dorman Road Mississauga L4V 1H2 Tel: (416) 677-7432 TWX: 610-492-8867 Hamilton/Avnet Electronics 1735 Courtwood Cresc. Ottawa K2C 2B4 Tel: (613) 226-1700 TWX: 610-562-1906

### QUEBEC

Hamilton/Avnet Electronics 2670 Paulus St. Laurent H45 1G2 Tel: (514) 331-6443 TWX: 610-421-3731

# RANDOM ACCESS MEMORIES

|                      |                    |                |                                                                                          |                      | Electrical Characteristics Over Temperature |                    |                                                   |                   |                |  |  |

|----------------------|--------------------|----------------|------------------------------------------------------------------------------------------|----------------------|---------------------------------------------|--------------------|---------------------------------------------------|-------------------|----------------|--|--|

|                      | Түре               | No. of<br>Bits | Description                                                                              | Organization         | Access Time<br>Max.                         | Cycle Time<br>Max. | Power<br>Dissipation Max.[1]<br>Operating/Standby | Supplies [V]      | Page No.       |  |  |

|                      | 1101A              | 256            | Static Fully Decoded                                                                     | 256 x 1              | 1500 ns                                     | 1500 ns            | 685mW/340mW                                       | +5, -9            | 2-3            |  |  |

|                      | 1101A1             | 256            | Hi-Speed Static Fully Decoded                                                            | 256 x 1              | 1000 ns                                     | 1000 ns            | 685mW/340mW                                       | +5, -9            | 2-3            |  |  |

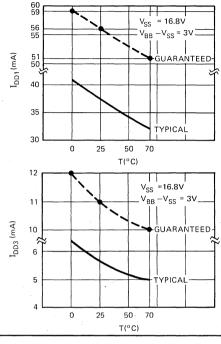

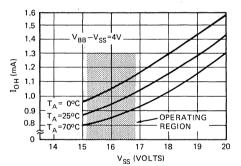

|                      | 1103               | 1024           | Dynamic Fully Decoded                                                                    | 1024 x 1             | 300 ns                                      | 580 ns             | 400 mW/67 mW                                      | +16, +19          | 2-7            |  |  |

|                      | 1103-1             | 1024           | Dynamic Fully Decoded                                                                    | 1024 x 1             | 150 ns                                      | 340 ns             | 400 mW/76 mW                                      | +19, +22          | 2-12           |  |  |

|                      | 1103A              | 1024           | Dynamic Fully Decoded                                                                    | 1024 x 1             | 205ns                                       | 580 ns             | 400 mW/64 mW                                      | +16, +19          | 2-15           |  |  |

|                      | 1103A-1            | 1024           | Dynamic Fully Decoded                                                                    | 1024 x 1             | 145ns                                       | 340 ns             | 625mW/10mW                                        | +19, +22          | 2-20           |  |  |

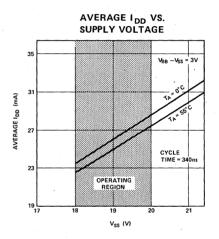

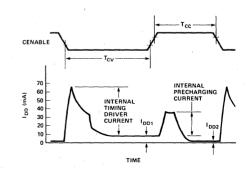

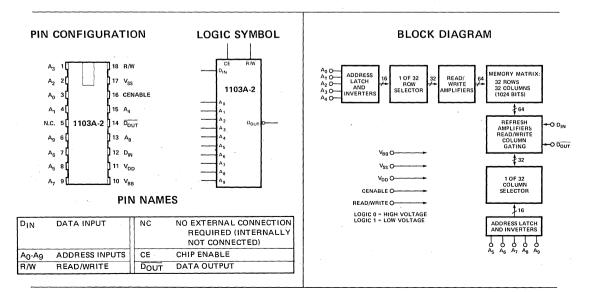

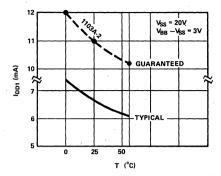

|                      | 1103A-2            | 1024           | Dynamic Fully Decoded                                                                    | 1024 x 1             | 145 ns                                      | 400 ns             | 570 mW/10 mW                                      | +19, +22          | 2-25           |  |  |

|                      | 2101               | 1024           | Static, Separate I/O                                                                     | 256 x 4              | 1000 ns                                     | 1000 ns            | 350 mW                                            | +5                | 2-29           |  |  |

|                      | 2101-1             | 1024           | Static, Separate I/O                                                                     | 256 x 4              | 500 ns                                      | 500 ns             | 350 mW                                            | +5                | 2-29           |  |  |

|                      | 2101-2             | 1024<br>1024   | Static, Separate 1/0<br>Static Fully Decoded                                             | 256 x 4<br>1024 x 1  | 650 ns                                      | 650 ns<br>1000 ns  | 350 mW                                            | +5                | 2-29           |  |  |

|                      | 2102               | 1024           | Hi-Speed Static Fully Decoded                                                            | 1024 x 1             | 500 ns                                      | 500 ns             | 350 mW<br>350 mW                                  | +5                | 2.33           |  |  |

|                      | 2102-1             | 1024           | Static Fully Decoded                                                                     | 1024 x 1<br>1024 x 1 | 650 ns                                      | 650 ns             | 350 mW                                            | +5                | 2.37           |  |  |

|                      | 2102-2             | 1024           | Static Fully Decoded                                                                     | 1024 x 1             | 1500 ns                                     | 1500 ns            | 350 mW                                            | +5                | 2-39           |  |  |

|                      | 2102-0<br>2102A    | 1024           | Very High Speed Static                                                                   | 1024 x 1             | 350 ns                                      | 350 ns             | 350 mW/42 mW                                      | +5                | 2-41<br>2-43   |  |  |

|                      | 2102A              | 1024           | Very High Speed Static                                                                   | 1024 x 1             | 250 ns                                      | 250 ns             | 350 mW/42 mW                                      | +5                | 2-43           |  |  |

|                      | 2102A-2<br>2102A-4 | 1024           | Very High Speed Static                                                                   | 1024 x 1             | 450 ns                                      | 450 ns             | 350 mW/42 mW                                      | +5                | 2.47           |  |  |

| s                    | M2102A-4           | 1024           | Static, T <sub>A</sub> = 55°C to +125°C                                                  | 1024 x 1             | 450 ns                                      | 450 ns             | 350 mW                                            | +5                | 2.49           |  |  |

| WO:                  | M2102A-6           | 1024           | Static, T <sub>A</sub> = 55°C to +125°C                                                  | 1024 x 1             | 650 ns                                      | 650 ns             | 350 mW                                            | +5                | 2.53           |  |  |

| SILICON GATE MOS     | 2105               | 1024           | Hi-Speed Dynamic Fully<br>Decoded                                                        | 1024 x 1             | 95ns                                        | 200 ns             | 460 mW/97 mW                                      | +12, -5.2         | 2-55           |  |  |

| LICON                | 2105-1             | 1024           | Very High Speed Dynamic<br>Fully Decoded                                                 | 1024 x 1             | 80 ns                                       | 180 ns             | `513 mW/97 mW                                     | +12, -5.2         | 2-55           |  |  |

| S                    | 2105-2             | 1024           | High Speed Dynamic with<br>Invisible Refresh                                             | 1024 x 1             | 85ns                                        | 190 ns             | 540 mW/97 mW                                      | +12, -5.2         | 2-63           |  |  |

|                      | 2107A              | 4096           | Dynamic Fully Decoded                                                                    | 4096 x 1             | 300 ns                                      | 700 ns             | 458 mW/10 mW                                      | +12, +5,5         | 2-67           |  |  |

|                      | 2107A-1            | 4096           | Dynamic Fully Decoded                                                                    | 4096 x 1             | 280 ns                                      | 550 ns             | 516 mW/16 mW                                      | +12, +5, -5       | 2-73           |  |  |

|                      | 2107A-4            | 4096           | Dynamic Fully Decoded                                                                    | 4096 x 1             | 350 ns                                      | 840 ns             | 405 mW/10 mW                                      | +12, +5, -5       | 2-75           |  |  |

|                      | 2107A-5            | · 4096         | Dynamic Fully Decoded                                                                    | 4096 x 1             | 420 ns                                      | 970 ns             | 376 mW/11 mW                                      | +12, +5, -5       | 2.77           |  |  |

|                      | 2107A-8            | 4096           | Dynamic Fully Decoded                                                                    | 4096 x 1             | 420 ns                                      | 970ns              | 376 mW/11 mW                                      | +12, +5, -5       | 2.79           |  |  |

|                      | 2107B              | 4096           | Dynamic Fully Decoded                                                                    | 4096 x 1             | 200 ns                                      | 400 ns             | 960 mW/16 mW                                      | +12, +5,5         | 2-81           |  |  |

|                      | 2107B-4            | 4096           | Dynamic Fully Decoded                                                                    | 4096 x 1             | 270 ns                                      | 470 ns             | 960 mW/18 mW                                      | +12, +5, -5       | 2-89           |  |  |

|                      | 2107B-6<br>2111    | 4096<br>1024   | Dynamic Fully Decoded<br>Static, Common I/O with<br>Output Deselect                      | 4096 x 1<br>256 x 4  | 350 ns<br>1000 ns                           | 800 ns<br>1000 ns  | 840 mW/25 mW<br>350 mW                            | +12, +5, -5<br>+5 | 2-91<br>2-93   |  |  |

|                      | 2111-1             | 1024           | Static, Common I/O with<br>Output Deselect                                               | 256 x 4              | 500 ns                                      | 500 ns             | 350 mW                                            | +5                | 2-93           |  |  |

|                      | 2111-2             | 1024           | Static, Common I/O with<br>Output Deselect                                               | 256 x 4              | 650 ns                                      | 650 ns             | 350 mW                                            | +5                | 2-93           |  |  |

|                      | 2112               | 1024           | Static, Common 1/0 without<br>Output Deselect                                            | 256 x 4              | 1000 ns                                     | 1000 ns            | 350 mW                                            | +5                | 2-97           |  |  |

|                      | 2112-2             | 1024           | Static, Common I/O without<br>Output Deselect                                            | 256 x 4              | 650 ns                                      | 650 ns             | 350 mW                                            | +5                | 2-97           |  |  |

|                      | 3101               | 64             | Fully Decoded                                                                            | 16 x 4               | 60 ns                                       | 60 ns              | 525 mW                                            | +5                | 2-101          |  |  |

|                      | 3101A              | 64             | High Speed Fully Decoded                                                                 | 16 x 4               | 35 ns                                       | 35 ns              | 525 mW                                            | +5                | 2-101          |  |  |

|                      | M3101              | 64             | Fully Decoded (-55°C to<br>+125°C                                                        | 16 x 4               | 75 ns                                       | 75 ns              | 546 mW                                            | +5                | 2-105          |  |  |

| ILAR                 | M3101A             | 64             | High Speed Fully Decoded<br>(-55°C to +125°C)                                            | 16 x 4               | 45 ns                                       | 45 ns              | 546 mW                                            | +5                | 2-105          |  |  |

|                      | 3104               | 16<br>256      | Content Addressable Memory                                                               | 4 x 4                | 30 ns                                       | 40 ns              | 625mW                                             | +5                | 2.107          |  |  |

| KY BIP               | 3106<br>3106A      | 256            | High Speed Fully Decoded<br>(With 3-State Output)<br>High Speed Fully Decoded            | 256 x 1              | 80 ns                                       | 80 ns              | 650 mW                                            | +5                | 2·111<br>2·111 |  |  |

| SCHOTTKY BIP         | 3106-8             | 256            | (With 3-State Output)<br>High Speed Fully Decoded                                        | 256 x 1              | 80 ns                                       | 80 ns              | 650 mW                                            | +5                | 2.111          |  |  |

| SC                   | 3107               | 256            | (With 3-State Output)<br>High Speed Fully Decoded                                        | 256 x 1              | 80 ns                                       | 80 ns              | 650 mW                                            | +5                | 2.111          |  |  |

|                      | 3107A              | 256            | (With Open Collector Output)<br>High Speed Fully Decoded                                 | 256 × 1              | 60 ns                                       | 70ns               | 650 mW .                                          | +5                | 2-111          |  |  |

|                      | 3107-8             | 256            | (With Open Collector Output)<br>High Speed Fully Decoded<br>(With Open Collector Output) | 256 x 1              | 60 ns                                       | 70ns               | 650 mW                                            | +5                | 2-111          |  |  |

|                      | 5101               | 1024           | (With Open Collector Output)<br>Static CMOS RAM                                          | 256 x 4              | 650                                         | 650                | 142 mW/75 µW                                      | +5                | 2115           |  |  |

| SILICON<br>GATE CMOS | 5101<br>5101-3     | 1024           | Static CMOS RAM                                                                          | 256 x 4<br>256 x 4   | 650 ns<br>650 ns                            | 650 ns             |                                                   | +5                | 2-115          |  |  |

| 20                   |                    | 1024           | Static CMOS RAM                                                                          | 256 x 4<br>256 x 4   | 650 ns                                      | 650 ns             | 142 mW/1 mW<br>142 mW/30 µW                       | +5                | 2-115<br>2-115 |  |  |

| Ξw                   | 5101L              |                |                                                                                          |                      |                                             |                    |                                                   |                   |                |  |  |

RAMs

Note 1: Power Dissipation calculated with maximum power supply current and nominal supply voltages.

# Silicon Gate MOS 1101A, 1101A1

# 256 BIT FULLY DECODED RANDOM ACCESS MEMORY

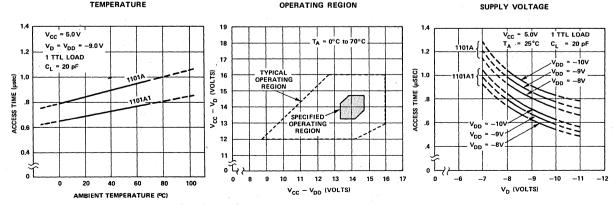

- Access Time -- Typically Below 650 nsec - 1101A1, 850 nsec - 1101A

- Low Power Standby Mode

- Low Power Dissipation -- Typically less than 1.5 mW/bit during access

- Directly DTL and TTL Compatible

- Three-state Output --OR-tie Capability

- Simple Memory Expansion --Chip Select Input Lead

- Fully Decoded --On Chip Address Decode and Sense

- Inputs Protected -- All Inputs Have Protection Against Static Charge

- Ceramic and Plastic Package --16 Pin Dual In-Line Configuration

The 1101A is an improved version of the 1101 which requires only two power supplies (+5V and -9V) for operation. The 1101A is a direct pin for pin replacement for the 1101.

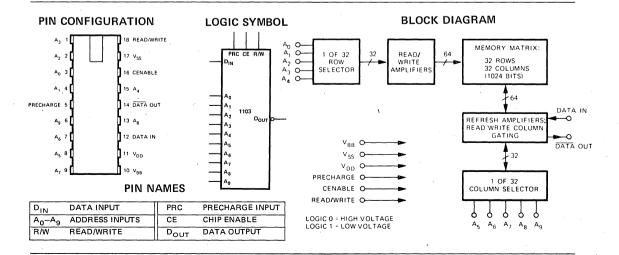

The Intel<sup>®</sup>1101A is a 256 word by 1 bit random access memory element using normally off P-channel MOS devices integrated on a monolithic array. It uses fully dc stable (static) circuitry and therefore requires no clocks to operate.

The 1101A is designed primarily for small buffer storage applications where high performance, low cost, and ease of interfacing with other standard logic circuits are important design objectives. The unit will directly interface with standard bipolar integrated logic circuits (TTL, DTL, etc.) The data output buffers are capable of driving TTL loads **directly**. A separate chip select ( $\overline{CS}$ ) lead allows easy selection of an individual package when outputs are OR-tied.

For applications requiring a faster access time we recommend the 1101A1 which is a selection from the 1101A and has a guaranteed maximum access time of 1.0 µsec.

The Intel 1101A is fabricated with silicon gate technology. This low threshold technology allows the design and production of higher performance MOS circuits and provides a higher functional density on a monolithic chip than conventional MOS technologies.

Intel's silicon gate technology also provides excellent protection against contamination. This permits the use of low cost silicone packaging.

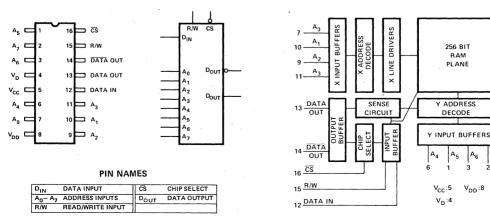

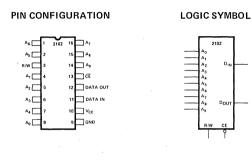

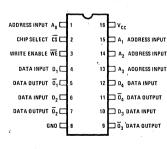

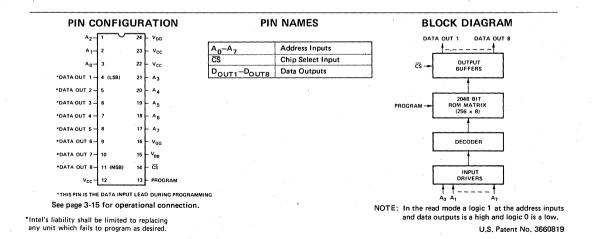

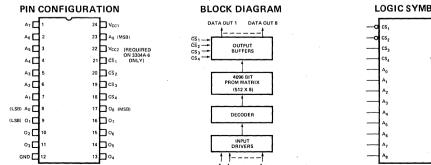

**PIN CONFIGURATION**

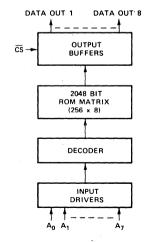

**BLOCK DIAGRAM**