# LITERATURE

To order Intel Literature or obtain literature pricing information in the U.S. and Canada call or write Intel Literature Sales. In Europe and other international locations, please contact your *local* sales office or distributor.

INTEL LITERATURE SALES P.O. BOX 7641 Mt. Prospect, IL 60056-7641 In the U.S. and Canada call toll free (800) 548-4725 This 800 number is for external customers only.

LITINCOV/091790

# **CURRENT HANDBOOKS**

Product line handbooks contain data sheets, application notes, article reprints and other design information. All handbooks can be ordered individually, and most are available in a pre-packaged set in the U.S. and Canada.

| TITLE                                                         | INTEL<br>ORDER NUMBER | ISBN          |

|---------------------------------------------------------------|-----------------------|---------------|

| SET OF THIRTEEN HANDBOOKS<br>(Available in U.S. and Canada)   | 231003                | N/A           |

| CONTENTS LISTED BELOW FOR INDIVIDUAL                          | ORDERING:             |               |

| COMPONENTS QUALITY/RELIABILITY                                | 210997                | 1-55512-132-2 |

| EMBEDDED APPLICATIONS                                         | 270648                | 1-55512-123-3 |

| 8-BIT EMBEDDED CONTROLLERS                                    | 270645                | 1-55512-121-7 |

| 16-BIT EMBEDDED CONTROLLERS                                   | 270646                | 1-55512-120-9 |

| 16/32-BIT EMBEDDED PROCESSORS                                 | 270647                | 1-55512-122-5 |

| MEMORY PRODUCTS                                               | 210830                | 1-55512-117-9 |

| MICROCOMMUNICATIONS                                           | 231658                | 1-55512-119-5 |

| MICROCOMPUTER PRODUCTS                                        | 280407                | 1-55512-118-7 |

| MICROPROCESSORS                                               | 230843                | 1-55512-115-2 |

| PACKAGING                                                     | 240800                | 1-55512-128-4 |

| PERIPHERAL COMPONENTS                                         | 296467                | 1-55512-127-6 |

| PRODUCT GUIDE<br>(Overview of Intel's complete product lines) | 210846                | 1-55512-116-0 |

| PROGRAMMABLE LOGIC                                            | 296083                | 1-55512-124-1 |

| ADDITIONAL LITERATURE:<br>(Not included in handbook set)      |                       |               |

| AUTOMOTIVE HANDBOOK                                           | 231792                | 1-55512-125-x |

| INTERNATIONAL LITERATURE GUIDE<br>(Available in Europe only)  | E00029                | N/A           |

| CUSTOMER LITERATURE GUIDE                                     | 210620                | N/A           |

| MILITARY HANDBOOK<br>(2 volume set)                           | 210461                | 1-55512-126-8 |

| SYSTEMS QUALITY/RELIABILITY                                   | 231762                | 1-55512-046-6 |

intel®

| NAME:                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMPANY:                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADDRESS:                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CITY:                                                                                                                    | STATE: ZIP:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| COUNTRY:                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PHONE NO.: ( )                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ORDER NO. TITLE                                                                                                          | QTY. PRICE TOTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                          | × =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                          | × =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                          | × =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                          | × =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                          | (a) A set of the se |

|                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                          | × =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                          | × =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                          | Subtotal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                          | Must Add Your                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Include postage:                                                                                                         | Local Sales Tax                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Must add 15% of Subtotal to cover U.S.                                                                                   | > Postage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| and Canada postage. (20% all other.)                                                                                     | Total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pay by check, money order, or include company purch<br>accept VISA, MasterCard or American Express. Make pa<br>delivery. | nase order with this form (\$100 minimum). We also<br>ayment to Intel Literature Sales. Allow 2-4 weeks for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| UISA 🗌 MasterCard 🗌 American Express Expira                                                                              | ation Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Account No.                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Signature                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Mail To: Intel Literature Sales Internation P.O. Box 7641 should us                                                      | ional Customers outside the U.S. and Canada<br>use the International order form on the next page or<br>their local Sales Office or Distributor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| For phone orders in the U.S. and Canada Call Toll Free: (800) 548-4725                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

**U.S. and CANADA LITERATURE ORDER FORM**

Prices good until 12/31/91. Source HB

CG/LOF1/091790

# INTERNATIONAL LITERATURE ORDER FORM

| NAME:           |                                        |                       |        |

|-----------------|----------------------------------------|-----------------------|--------|

| COMPANY:        |                                        |                       |        |

| ADDRESS:        |                                        |                       |        |

| CITY: S         | TATE:                                  | ZIP:                  | -<br>- |

| COUNTRY:        |                                        |                       |        |

| PHONE NO.: ( )  | ······································ |                       |        |

| ORDER NO. TITLE | QTY.                                   | PRICE                 | TOTAL  |

|                 | ×                                      |                       | =      |

|                 | ×                                      |                       | =      |

|                 | ×                                      |                       | =      |

|                 | <u> </u>                               | ,<br>                 | =      |

|                 | ×                                      |                       | =      |

|                 | ×                                      | -                     | =      |

|                 | ×                                      |                       |        |

|                 |                                        |                       | =      |

|                 | ×                                      |                       | =      |

|                 | ×                                      | · · · ·               | =      |

|                 |                                        | Subtotal              |        |

|                 |                                        | Add Your<br>Sales Tax | а<br>  |

|                 | 2004                                   | Total                 |        |

#### PAYMENT

Cheques should be made payable to your *local* Intel Sales Office (see inside back cover).

Other forms of payment may be available in your country. Please contact the Literature Coordinator at your *local* Intel Sales Office for details.

The completed form should be marked to the attention of the LITERATURE COORDINATOR and returned to your *local* Intel Sales Office.

CG/091790

intel®

# Intel386<sup>™</sup> DX MICROPROCESSOR HARDWARE REFERENCE MANUAL

1991

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel products:

376, Above, ActionMedia, BITBUS, Code Builder, DeskWare, Digital Studio, DVI, EtherExpress, ETOX, FaxBACK, Grand Challenge, i, i287, i386, i387, i486, i487, i750, i860, i960, ICE, iLBX, Inboard, Intel, Intel/287, Intel/386, Intel/387, Intel/486, Intel/487, intel inside., Intellec, iPSC, iRMX, iSBC, iSBX, iWARP, LANPrint, LANSelect, LANShell, LANSight, LANSpace, LANSpool, MAPNET, Matched, MCS, Media Mail, NetPort, NetSentry, OpenNET, PRO750, ProSolver, READY-LAN, Reference Point, RMX/80, SatisFAXtion, SnapIn 386, Storage Broker, SugarCube, The Computer Inside., TokenExpress, Visual Edge, and WYPIWYF.

MDS is an ordering code only and is not used as a product name or trademark. MDS is a registered trademark of Mohawk Data Sciences Corporation.

CHMOS and HMOS are patented processes of Intel Corp.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

Micro Channel, OS/2 and PS/2 are trademarks of International Business Machines Corporation.

UNIX is a registered trademark of UNIX System Laboratories, Inc.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641

©INTEL CORPORATION 1986, 1990, 1991

# **CUSTOMER SUPPORT**

#### **INTEL'S COMPLETE SUPPORT SOLUTION WORLDWIDE**

Customer Support is Intel's complete support service that provides Intel customers with hardware support, software support, customer training, consulting services and network management services. For detailed information contact your local sales offices.

After a customer purchases any system hardware or software product, service and support become major factors in determining whether that product will continue to meet a customer's expectations. Such support requires an international support organization and a breadth of programs to meet a variety of customer needs. As you might expect, Intel's customer support is extensive. It can start with assistance during your development effort to network management. 100 Intel sales and service offices are located worldwide – in the U.S., Canada, Europe and the Far East. So wherever you're using Intel technology, our professional staff is within close reach.

#### HARDWARE SUPPORT SERVICES

Intel's hardware maintenance service, starting with complete on-site installation will boost your productivity from the start and keep you running at maximum efficiency. Support for system or board level products can be tailored to match your needs, from complete on-site repair and maintenance support to economical carry-in or mail-in factory service.

Intel can provide support service for not only Intel systems and emulators, but also support for equipment in your development lab or provide service on your product to your end-user/customer.

#### SOFTWARE SUPPORT SERVICES

Software products are supported by our Technical Information Service (TIPS) that has a special toll free number to provide you with direct, ready information on known, documented problems and deficiencies, as well as work-arounds, patches and other solutions.

Intel's software support consists of two levels of contracts. Standard support includes TIPS (Technical Information Phone Service), updates and subscription service (product-specific troubleshooting guides and *COMMENTS Magazine*). Basic support consists of updates and the subscription service. Contracts are sold in environments which represent product groupings (e.g., iRMX<sup>®</sup> environment).

#### **NETWORK SERVICE AND SUPPORT**

Today's broad spectrum of powerful networking capabilities are only as good as the customer support provided by the vendor. Intel offers network services and support structured to meet a wide variety of end-user computing needs. From a ground up design of your network's physical and logical design to implementation, installation and network wide maintenance. From software products to turn-key system solutions; Intel offers the customer a complete networked solution. With over 10 years of network experience in both the commercial and Government arena; network products, services and support from Intel provide you the most optimized network offering in the industry.

#### CONSULTING SERVICES

Intel provides field system engineering consulting services for any phase of your development or application effort. You can use our system engineers in a variety of ways ranging from assistance in using a new product, developing an application, personalizing training and customizing an Intel product to providing technical and management consulting. Systems Engineers are well versed in technical areas such as microcommunications, real-time applications, embedded microcontrollers, and network services. You know your application needs; we know our products. Working together we can help you get a successful product to market in the least possible time.

#### CUSTOMER TRAINING.

Intel offers a wide range of instructional programs covering various aspects of system design and implementation. In just three to ten days a limited number of individuals learn more in a single workshop than in weeks of self-study. For optimum convenience, workshops are scheduled regularly at Training Centers worldwide or we can take our workshops to you for on-site instruction. Covering a wide variety of topics, Intel's major course categories include: architecture and assembly language, programming and operating systems, BITBUS<sup>™</sup> and LAN applications.

# PREFACE

The Intel386<sup>™</sup> DX microprocessor is a high-performance 32-bit microprocessor. This manual provides complete hardware reference information for Intel386 DX microprocessor system designs. It is written for system engineers and hardware designers who understand the operating principles of microprocessors and microcomputer systems. Readers of this manual should be familiar with the information in the *Introduction to the* 80386 (Intel publication Order Number 231252).

# **RELATED PUBLICATIONS**

In this manual, the Intel386 DX microprocessor is presented from a hardware perspective. Information on the software architecture, instruction set, and programming of the Intel386 DX microprocessor can be found in these related Intel publications:

- 386<sup>™</sup> DX Microprocessor Programmer's Reference Manual, Order Number 230985

- 80386 System Software Writer's Guide, Order Number 231499

- 386<sup>™</sup> DX Microprocessor Data Sheet, Order Number 231630

The 386<sup>™</sup> DX Microprocessor Data Sheet contains device specifications for the Intel386 DX microprocessor. Always consult the most recent version of this publication for specific Intel386 DX microprocessor parameter values.

Detailed device specifications on Intel386 DX microprocessor family components can be found in the following publications:

- 387<sup>™</sup> DX Math Coprocessor Data Sheet, Order Number 240448

- 82380 Data Sheet, Order Number 290128

- 82385 Data Sheet, Order Number 290143

- 82310/11 Data Sheet, Order Number 290167

- *82350 Data Sheet*, Order Number 290220

- 82596DX Data Sheet, Order Number 290219

Together with the Intel386<sup>TM</sup> DX Microprocessor Hardware Reference Manual, these publications provide a complete description of the Intel386 DX microprocessor system for hardware designers, software engineers, and all users of Intel386 DX microprocessor systems.

The Intel386 DX microprocessor is object-code compatible with 3 other processors: the Intel486<sup>TM</sup>, the Intel386 SX and the  $376^{TM}$  microprocessors.

The Intel486 DX processor integrates cache memory, floating point hardware and memory management on-chip while retaining binary compatibility with previous members of the 86 architectural family. Related documentation includes:

- *i486™ Microprocessor Data Sheet*, Order Number 240440

- i486<sup>™</sup> Microprocessor Programmer's Reference Manual, Order Number 240486

The Intel386 SX processor (16-bit data bus) - The Intel386 DX processor adapted for mid-range personal computers, which are sensitive to the higher system cost of a 32-bit bus. Related documentation includes:

- 386<sup>™</sup> SX Microprocessor Data Sheet, Order Number 240187

- 386<sup>™</sup> SX Microprocessor Hardware Reference Manual, Order Number 240332

The 376 embedded processor (16-bit data bus) - A reduced form of the Intel386 processor, optimized for embedded applications. Related documentation includes:

- 376<sup>™</sup> Microprocessor Data Sheet, Order Number 240182

- 376<sup>™</sup> Embedded Processor Programmer's Reference Manual, Order Number 240314

# **ORGANIZATION OF THIS MANUAL**

into

The information in this manual is divided into 12 chapters and three appendices. The material begins with a description of the Intel386 DX microprocessor and continues with discussions of hardware design information needed to implement Intel386 DX microprocessor system designs.

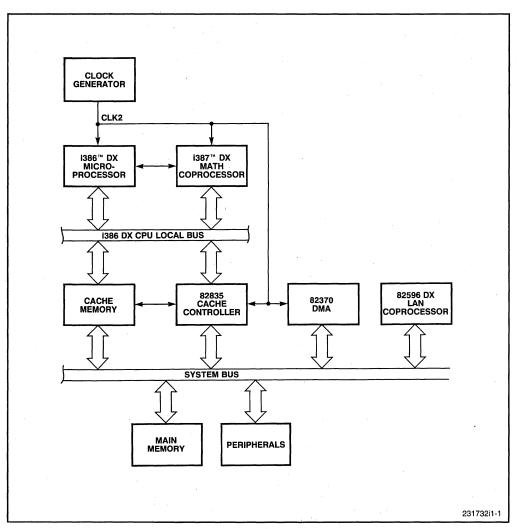

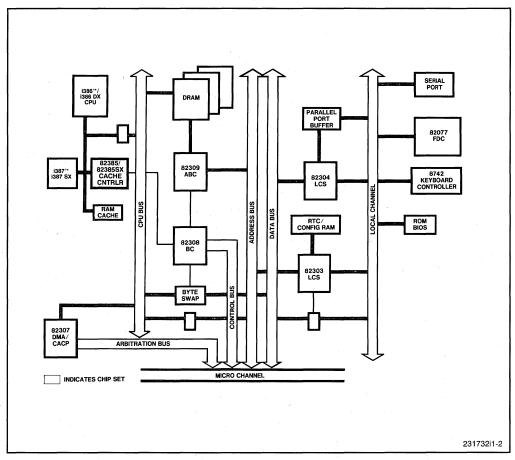

- Chapter 1, "System Overview." This chapter provides an overview of the Intel386 DX microprocessor and its supporting devices.

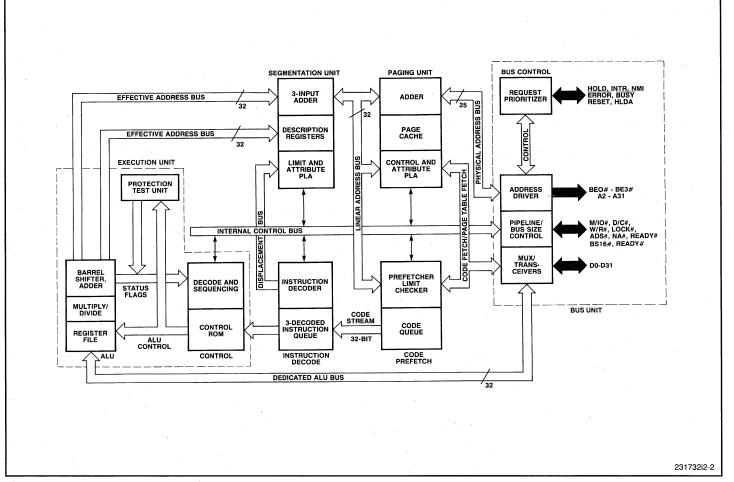

- Chapter 2, "Internal Architecture." This chapter describes the internal architecture of the Intel386 DX microprocessor.

- Chapter 3, "Local Bus Interface." This chapter discusses the Intel386 DX microprocessor local bus interface. This chapter includes Intel386 DX microprocessor signal descriptions, memory and I/O organization, and local bus interface guidelines.

- Chapter 4, "Performance Considerations." This chapter explores the factors that affect the performance of an Intel386 DX microprocessor system.

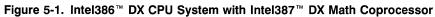

- Chapter 5, "Coprocessor Hardware Interface." This chapter describes the interface between the Intel386 DX microprocessor and the Intel387<sup>™</sup> Numeric Coprocessors. This coprocessor expands the floating-point numerical processing capabilities of the Intel386 DX microprocessor.

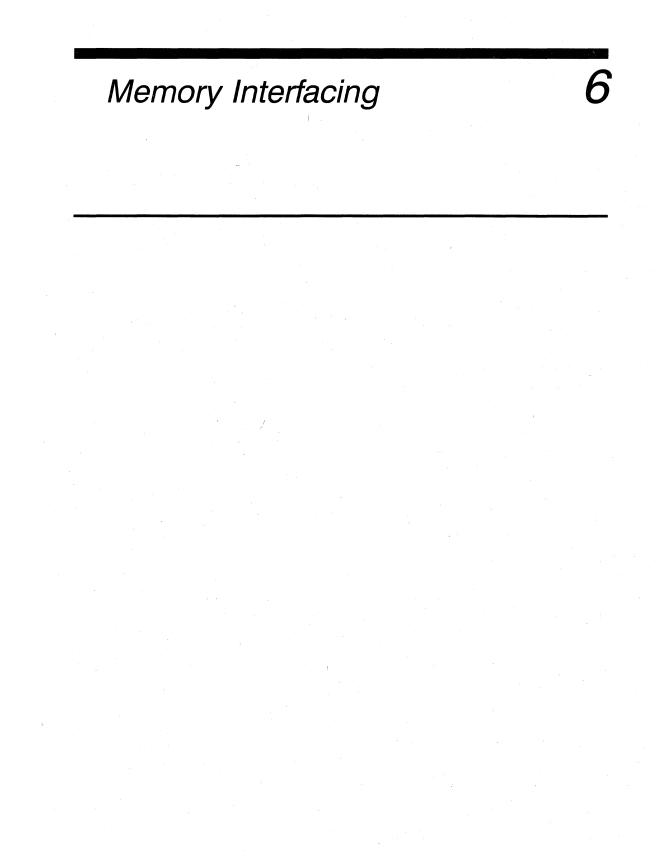

- Chapter 6, "Memory Interfacing." This chapter discusses techniques for designing memory subsystems for the Intel386 DX microprocessor.

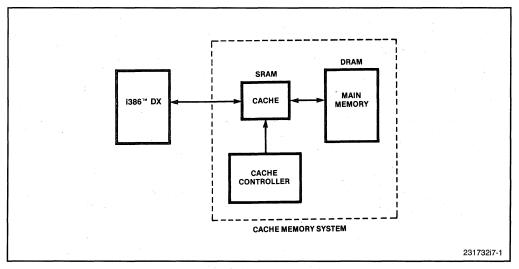

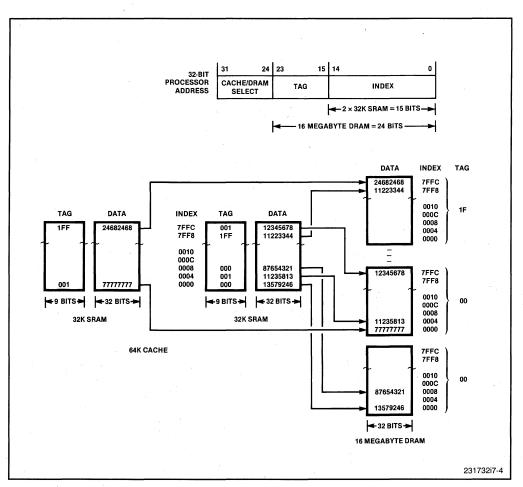

- Chapter 7, "Cache Subsystems." This chapter describes cache memory subsystems, which provide higher performance at lower relative cost.

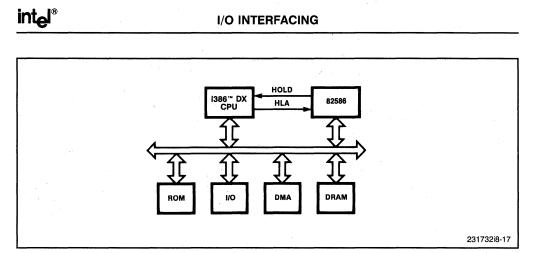

- Chapter 8, "I/O Interfacing." This chapter discusses techniques for connecting I/O devices to an Intel386 DX microprocessor system.

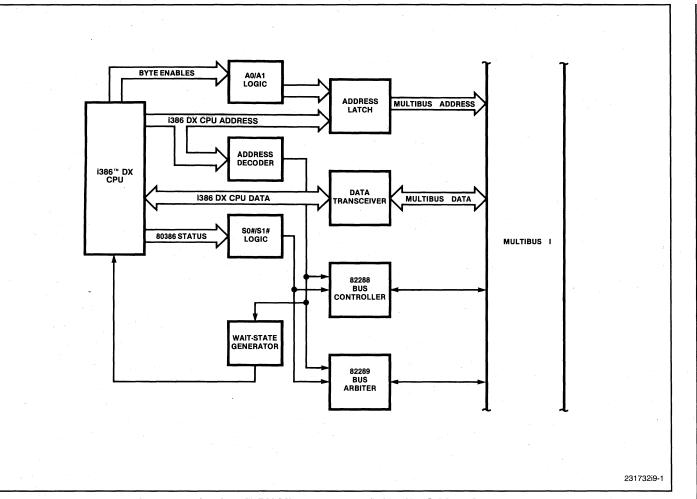

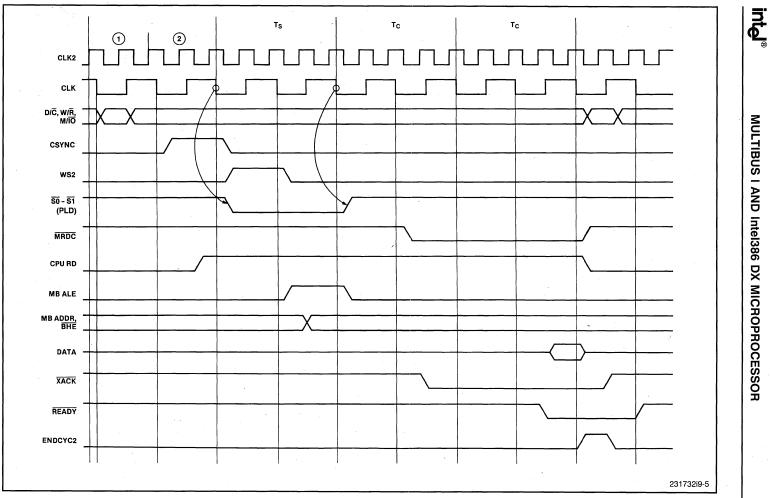

- Chapter 9, "MULTIBUS I and Intel386 DX Microprocessor." This chapter describes the interface between an Intel386 DX microprocessor system and the Intel MULTIBUS I multi-master system bus.

- Chapter 10, "MULTIBUS II and Intel386 DX Microprocessor." This chapter describes the interface between an Intel386 DX microprocessor system and the Intel MULTIBUS II multi-master system bus.

# intel®

- Chapter 11, "Physical Design and Debugging." This chapter contains recommendations for constructing and debugging Intel386 DX microprocessor systems.

- Chapter 12, "Test Capabilities." This chapter describes Intel386 DX microprocessor test procedures.

- Appendix A contains descriptions of the components of the basic memory interface described in Chapter 6.

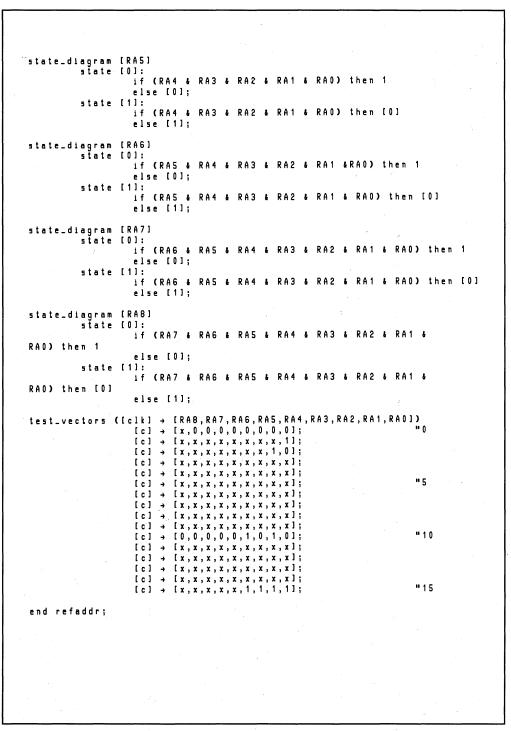

- Appendix B contains descriptions of the components of the dynamic RAM subsystem described in Chapter 6.

# TABLE OF CONTENTS

#### **CHAPTER 1** Page SYSTEM OVERVIEW 1.1 MICROPROCESSOR ..... 1-1 1.2 COPROCESSORS ..... 1-4 1.3 INTEGRATED SYSTEM PERIPHERAL ...... 1-4 1.5 EISA CHIP SET ..... 1-6 1.6 MCA CHIP SET ..... 1-6 1.7 LAN COPROCESSOR ...... 1-7 1.9 8086/80286 FAMILY COMPONENTS 1-7

# CHAPTER 2

# INTERNAL ARCHITECTURE

| 2.1 | BUS INTERFACE UNIT      | 2-2 |

|-----|-------------------------|-----|

|     | CODE PREFETCH UNIT      |     |

| 2.3 | INSTRUCTION DECODE UNIT | 2-2 |

|     | EXECUTION UNIT          |     |

| 2.5 | SEGMENTATION UNIT       | 2-4 |

| 2.6 | PAGING UNIT             | 2-4 |

#### CHAPTER 3

# LOCAL BUS INTERFACE

| 3.1 BUS OPERATIONS              | 3-2 |

|---------------------------------|-----|