# intel iAPX 286 Operating Systems Writer's Guide

#### LITERATURE

1983 will be a year of transition for Intel's catalog program. In order to better serve you, our customers, we are reorganizing many of our catalogs to more completely reflect product groups.

In addition to the new product line handbooks listed below, an INTEL PRODUCT GUIDE (Order No. 210846) will be available free of charge in March. This GUIDE will contain a listing of Intel's complete product line along with information on quality/reliability, packaging and ordering, customer training classes and product services.

Consult the Intel Literature Guide (no charge, Order No. 210620) for a complete listing of Intel literature. Literature is presently available in other forms for those handbooks that will not be published until later in the year. Write or call the Intel Literature Department, 3065 Bowers Avenue, Santa Clara, CA 95051, (800) 538-1876, or (800) 672-1833 (California only).

#### **HANDBOOKS**

#### Memory Components Handbook (Order No. 210830)

Contains all application notes, article reprints, data sheets and other design information on RAMs, DRAMs, EPROMs, E<sup>2</sup>PROMs, Bubble Memories.

#### Microcontroller Handbook (Available in May)

Contains all application notes, article reprints, data sheets, and other user information on the MCS-48, MCS-51 (8-bit) and the new MCS-96 (16-bit) product families.

#### Military Handbook (Order No. 210461)

Contains complete data sheets on all military products.

#### Microprocessor and Peripherals Handbook (Order No. 210844)

Contains data sheets on all microprocessors and peripherals. (Individual User Manuals are also available on the 8085, 8086, 8088, 186, 286, etc.)

#### **Development Systems Handbook (Available in April)**

Contains data sheets on development systems and supporting software.

#### **OEM Systems Handbook (Available in May)**

Contains all application notes, article reprints and data sheets for OEM boards and systems.

#### Software Handbook (Available in May)

Contains software product overview as well as data sheets for all Intel software.

#### Quality/Reliability Standards Handbook (Available in April)

## iAPX 286 OPERATING SYSTEMS WRITER'S GUIDE

1983

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and may only be used to identify Intel Products:

BXP, CREDIT, i, ICE, I<sup>2</sup>ICE, ICS, iDBP, iDIS, iLBX, i<sub>m</sub>, iMMX, Insite, INTEL, int<sub>e</sub>l, Intelevision, Intellec, int<sub>e</sub>ligent Identifier™, int<sub>e</sub>lBOS, int<sub>e</sub>ligent Programming™, Intellink, iOSP, iPDS, iRMS, iSBC, iSBX, iSDM, iSXM, Library Manager, MCS, Megachassis, Micromainframe, MULTIBUS, Multichannel™ Plug-A-Bubble, MULTIMODULE, PROMPT, Ripplemode, RMX/80, RUPI, System 2000, and UPI, and the combination of ICE, iCS, iRMX, iSBC, MCS, or UPI and a numerical suffix.

MDS is an ordering code only and is not used as a product name or trademark. MDS\* is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Additional copies of this manual or other Intel literature may be obtained from:

Intel Corporation Literature Department 3065 Bowers Avenue Santa Clara, CA 95051

#### **PREFACE**

This book is written for systems designers and operating system designers and programmers who plan to use the Intel iAPX 286 microprocessor in its protected, virtual-address mode. The protected-mode iAPX 286 is designed for multitasking systems: systems that serve many users or that simultaneously run several programs.

This book analyzes operating system functions that are appropriate for the iAPX 286 when used in a variety of multitasking applications, including

- · Communications, such as automated PBXs

- Real-time, such as instrumentation or process control

- Multi-user, such as time-sharing or office systems

Many of the features of the iAPX 286 are intended for use by an operating system. This book identifies and explains those features and gives examples of how they can be used in an operating system.

#### **AUDIENCE**

This book assumes that you have a knowledge of multitasking operating systems at least equivalent to that presented in introductory undergraduate textbooks on the subject. It also assumes that you have had some exposure to the architecture of the iAPX 286 through attending an introductory course or reading introductory literature such as *Introduction to the iAPX 286*.

#### **RELATED PUBLICATIONS**

#### Intel Literature

The following manuals contain additional information of use to operating-system designers and programmers:

- ASM286 Assembly Language Reference Manual, 121924

- Component Data Catalog, 210298

- iAPX 286 Architecture Extension Kernel (K286) User's Guide, 121961

- iAPX 286 Programmer's Reference Manual, 210498

- iAPX 286 System Builder User's Guide, 121935

- iAPX 286 Utilities User's Guide, 121934

- iAPX 286/10 High Performance Microprocessor with Memory Management and Protection (Data Sheet), 210253

- Introduction to the iAPX 286, 210308

- PL/M-286 User's Guide, 121945

iii 121960-001

#### **External Literature**

Many aspects of operating system construction for the iAPX 286 are the same as for other processors. The following are sources of generally applicable theories and algorithms referred to in the text of this book.

- Coffman, E.G., Jr., and Peter J. Denning, *Operating Systems Theory* (Englewood Cliffs, N.J.: Prentice-Hall, 1973)

- Denning, Peter J., "Virtual Memory," Computing Surveys, Vol. 2, No. 3 (September 1970)

- Knuth, Donald E., Fundamental Algorithms, Vol. 1 (Reading, Mass.: Addison-Wesley, 1973)

- Peterson, James L., Petri Net Theory and the Modeling of Systems (Englewood Cliffs, N.J.: Prentice-Hall. 1981)

#### **RELATED PRODUCTS**

Designers interested in operating systems for the protected-mode iAPX 286 should also be aware of Intel's iAPX 286 Architecture Extension Kernel K28. K286 is an operating-system kernel designed for a wide variety of applications, including real-time, communications, business systems, and time-sharing. K286 provides

- Short-term, priority scheduling and management of multiple tasks

- Interrupt management

- Multiprocessor support

- Virtual memory support

- Data sharing among tasks with synchronization

- Intertask signals and messages

- Extended protection

Whether you use K286 "as is," for greatest possible efficiency, or whether you add layers of software to more fully support your applications, K286 can significantly reduce your system development time. Since K286 has been designed by the architects of the iAPX 286 and implemented and tested by Intel's software engineers, using K286 can make your system more reliable.

K286 implements many of the concepts discussed in this book, which can therefore give you additional understanding of why and how to use K286.

#### HOW TO USE THIS MANUAL

This manual has two related objectives:

- To identify features of the iAPX 286 architecture that are unique when applied to the implementation of an operating system

- To show how you can effectively use these unique features in the design of familiar operating system functions

In pursuit of these objectives, Chapters 2 thru 13 share a general, three-part structure:

- 1. Identifing an operating system function (or class of functions). The functions chosen are those with which you might already be familiar, since they are similar to those used in state-of-the-art operating systems such as iRMX 86 (from Intel Corporation) or UNIX (from Bell Laboratories).

- 2. Reviewing the iAPX 286 features that support that function. While this portion of each chapter may cover some material available in other Intel literature, it provides added value by discussing in one place all the iAPX 286 features that bear on a given operating system function and by identifying relationships among those features.

- 3. Outlining some examples of how to use those iAPX 286 features in an implementation of the identified function. It is, of course, impossible to illustrate all the ways to design any given function, but these examples serve to illustrate a few of the ways that the designers of the iAPX 286 architecture intended for it to be applied.

Chapter 1 introduces the iAPX 286 architecture; identifies the role of an operating system in a protected, multitasking environment; and shows how Intel's Binder and Builder utilities aid in the construction of an operating system. You may skip Chapter 1 if you are already familiar with multitasking operating systems and with the Binder and the Builder.

Both Chapter 2 and Chapter 5 contain key information about manipulating the protection features of the iAPX 286. Be sure not to omit these chapters when scanning the contents of the book.

For the remaining chapters, you may turn directly to the subjects that interest you most. You will find the reading easier, however, if you observe the partial orderings outlined in table 0-1.

#### NOTATIONAL CONVENTIONS

UPPERCASE

Characters shown in uppercase must be entered in the order shown. You may enter the characters in uppercase or lowercase.

Italic

Italic indicates a meta symbol that may be replaced with an item that fulfills the rules for that symbol. The actual symbol may be any of the following:

system-id

Is a generic label placed on sample listings where an operating system-dependent name would actually be printed.

Vx.y

Is a generic label placed on sample listings where the version number of the product that produced the listing would actually be printed.

Table 0-1. Prerequisites by Chapter

| Target Chapter | Prerequisites |

|----------------|---------------|

| 6              | 4             |

| 7              | 6             |

| 8              | 4, 6          |

| 9              | 6, 7          |

| 12             | 4, 6, 7       |

121960-001

#### **Table of Contents**

|                    | PROTECTED MULTITASKING ON THE IAPX 286 |

|--------------------|----------------------------------------|

|                    |                                        |

|                    | ıram                                   |

|                    | ´у                                     |

| •                  |                                        |

|                    |                                        |

|                    | s                                      |

| •                  |                                        |

|                    | ucture                                 |

|                    | System                                 |

|                    | ctions                                 |

|                    | Dynamic Environment                    |

|                    | al Run-Time Environment                |

|                    | /stem                                  |

| building a Dynamic | : System                               |

|                    |                                        |

|                    |                                        |

|                    |                                        |

| LARTER A           |                                        |

| IAPTER 2           | DOTEOTION EE ATUDEO                    |

|                    | ROTECTION FEATURES                     |

| <u> </u>           | sm                                     |

|                    |                                        |

| •                  |                                        |

|                    | r                                      |

|                    | Landa and Canada                       |

|                    | echanisms                              |

|                    | Gated Intersegment Transfers           |

| •                  |                                        |

|                    | able                                   |

|                    | Table                                  |

| ·                  | r Table                                |

|                    |                                        |

|                    |                                        |

|                    |                                        |

|                    | f Time                                 |

|                    | f Type                                 |

|                    |                                        |

|                    | among Tasks                            |

|                    | grity with Aliasing                    |

|                    | or Manipulation                        |

| Sint Management    |                                        |

| CHAPTER 3                                       | Page |

|-------------------------------------------------|------|

| REAL MEMORY MANAGEMENT                          | _    |

| Memory Management Functions                     | 3-1  |

| Example of a Memory Manager                     | 3-1  |

| Data Structures                                 | 3-2  |

| PL/M-286 Code                                   | 3-6  |

| Protection Structure                            | 3-7  |

| Advanced Memory Management                      | 3-10 |

| , ,                                             |      |

| CHAPTER 4                                       |      |

| TASK MANAGEMENT                                 |      |

| Hardware Task-Management Features               | 4-1  |

| Storing Task State                              | 4-1  |

| Switching Tasks                                 | 4-3  |

| Role of Operating System in Task Management     | 4-4  |

| State Model of Task Scheduling                  | 4-5  |

| Interfacing with the Hardware Scheduler         | 4-6  |

| Changing Scheduling State                       | 4-7  |

| Structuring Task Information                    | 4-10 |

| Example of a Dispatcher                         | 4-13 |

|                                                 |      |

| CHAPTED 5                                       |      |

| CHAPTER 5                                       |      |

| DATA SHARING, ALIASING, AND SYNCHRONIZATION     | E 1  |

| Data-Sharing Techniques                         | 5-1  |

| Sharing via the GDT                             | 5-1  |

| Sharing via Common LDT                          | 5-1  |

| Sharing via Aliases                             | 5-2  |

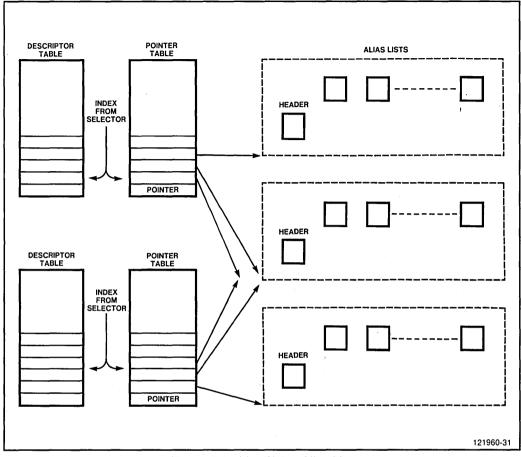

| Alias Management                                | 5-3  |

| Alias Database                                  | 5-3  |

| Alias Procedures                                | 5-3  |

| Synchronization                                 | 5-4  |

| Low-Level Mutual Exclusion                      | 5-5  |

| High-Level Mutual Exclusion                     | 5-6  |

| Message Passing                                 | 5-10 |

| Message-Passing Example                         | 5-10 |

| Variations on the Mailbox Theme                 | 5-16 |

|                                                 |      |

| CHAPTER 6                                       |      |

| SIGNALS AND INTERRUPTS                          |      |

| Interrupt Features of the iAPX 286 Architecture | 6-1  |

| Vectoring                                       | 6-1  |

| Enabling and Disabling Interrupts               | 6-2  |

| Interrupt Descriptor Table                      | 6-2  |

| Interrupt Tasks and Interrupt Procedures        | 6-2  |

| intorrupt rubito und intorrupt ribodudies       | 0-2  |

### intel

|                                                    | P |

|----------------------------------------------------|---|

| Operating System Responsibilities                  |   |

| Manage IDT                                         |   |

| Switch Scheduling Modes                            |   |

| Manage Interrupt Controller                        |   |

| Provide Task-Level Interrupt Procedures            |   |

| Provide Software Signals                           |   |

|                                                    |   |

|                                                    |   |

| CHAPTER 7                                          |   |

| HANDLING EXCEPTION CONDITIONS                      |   |

| Fault Mechanism                                    |   |

| Fault Recovery                                     |   |

| Locating the Faulting Instruction                  |   |

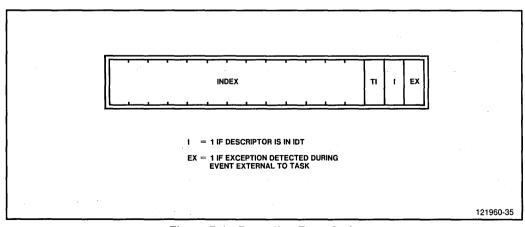

| Error Code                                         |   |

| Application Interface                              |   |

| Exception Conditions                               |   |

| Interrupt 0—Divide Error                           |   |

| Interrupt 1—Single Step                            |   |

| Interrupt 3—Breakpoint                             |   |

| Interrupt 4—Overflow                               |   |

| Interrupt 5—Bound Check                            |   |

| Interrupt 6—Undefined Opcode (UD)                  |   |

| Interrupt 7—Processor Extension Not Available (NM) |   |

| Interrupt 8—Double Fault (DF)                      |   |

| Interrupt 9—Processor Extension Segment Overrun    |   |

| Interrupt 10—Invalid TSS (TS)                      |   |

| Interrupt 11—Segment Not Present (NP)              |   |

| Interrupt 12—Stack Exception (SS)                  |   |

| Interrupt 13—General Protection Exception (GP)     |   |

| Interrupt 16—Processor Extension Error (MF)        |   |

| Interrupt 17—Run-Time Exceptions                   |   |

|                                                    |   |

| Restartability Summary                             |   |

|                                                    |   |

| CHAPTER 8                                          |   |

| INPUT/OUTPUT                                       |   |

| I/O and Protection                                 |   |

| I/O Privilege Level (IOPL)                         |   |

| Controlling I/O Addresses                          |   |

| I/O and Memory Management                          |   |

| Partitioning I/O Functions                         |   |

| Requirements for Parallelism and Synchronization   |   |

| ·                                                  |   |

| Requirements for Protection                        |   |

| Implementation Alternatives                        |   |

| CHAPTER 9                           | Page           |

|-------------------------------------|----------------|

| VIRTUAL MEMORY                      |                |

| Hardware Mechanisms                 | 9-1            |

| Accessed Bit                        | 9-1            |

| Present Bit                         | 9-1            |

| Software Mechanisms                 | 9-2            |

| Secondary Storage Management        | 9-2            |

| Level Zero Support Procedures       | 9-3            |

| Swapping Managers                   | 9-4            |

| Software Policies                   | 9-6            |

| Fetch                               | 9-6            |

| Placement                           | 9-6            |

| Replacement                         | 9-7            |

| Thrashing                           | 9-8            |

| CHAPTER 10                          |                |

| SYSTEM INITIALIZATION               |                |

| Initial State                       | 10-1           |

| Switching to Protected Mode         | 10-1           |

| Initializing for Protected Mode     | 10-2           |

| Interrupt Vector                    | 10-2           |

| Stack                               | 10-2           |

| Global Descriptor Table             | 10-2           |

| Starting First Task                 | 10-2           |

| Example of Initialization           | 10-3           |

| Initialization Module ENTP          | 10-3           |

| CHAPTER 11                          |                |

| BINDING AND LOADING                 |                |

| Binding Model                       | 11-1           |

| Modules                             | 11-1           |

| Segmentation                        | 11-2           |

| Interfaces                          | 11-2           |

| Naming                              | 11-3           |

| Timing                              | 11-3           |

| Implementing According to the Model | 11-3           |

| ·                                   | 11-4           |

| Source Code                         | 11-4           |

| Binding Utilities                   | 11-5           |

|                                     | 11-8           |

| Overview of Loading                 | 11-8           |

| iAPX 286 Object Module Format       | 11-10          |

|                                     |                |

| Flow of Loader                      | 11-11<br>11-12 |

| Load-Time Binding                   | 11-12          |

| Example Loader                      | 11-12          |

#### 'لطnt

#### **TABLE OF CONTENTS**

|       | TER 12 IERICS PROCESSOR EXTENSION                   | Page |

|-------|-----------------------------------------------------|------|

|       |                                                     | 12-1 |

|       | PX 286/20 Numerics Processing Features              | 12-1 |

|       |                                                     | 12-1 |

|       | Emulation Mode Flag (EM)                            | 12-1 |

|       | Math Present Flag (MP)                              |      |

|       | Task Switched Flag (TS)                             | 12-2 |

|       | WAIT Instruction                                    | 12-2 |

|       | Summary                                             | 12-2 |

|       | ialization                                          | 12-2 |

|       | sk State                                            | 12-3 |

|       | merics Exceptions                                   | 12-3 |

|       | nterrupt 7—Processor Extension Not Available (NM)   | 12-3 |

|       | nterrupt 9—Processor Extension Segment Overrun (MP) | 12-4 |

| ١     | nterrupt 16—Processor Extension Error (MF)          | 12-5 |

|       |                                                     |      |

| CHAP1 | ER 13 ENDED PROTECTION                              |      |

|       | tended Type                                         | 13-1 |

|       | Type Extension Code with Descriptor                 | 13-1 |

|       | Type Extension Code with Descriptor                 | 13-1 |

|       | •••                                                 | 13-1 |

|       | ,                                                   | 13-2 |

|       | rameter Validation                                  |      |

|       | Defensive Use of ARPL                               | 13-2 |

|       | Point-of-Entry Scrutiny                             | 13-3 |

|       | age Privilege Level                                 | 13-4 |

|       | nd Privilege Level                                  | 13-5 |

| Co    | nstructing Shared Objects                           | 13-5 |

| GLOSS | SARY                                                |      |

| INDEX |                                                     |      |

|       | LIST OF TABLES                                      |      |

| Table | Title                                               | Page |

| 0-1   | Prerequisites by Chapter                            | ٧    |

| 2-1   | Categories of Control Flow Transfer                 | 2-7  |

| 2-2   | Control Transfer Mechanisms                         | 2-10 |

| 3-1   | Actions for Combining Segments                      | 3-9  |

| 4-1   | Task Switching Operations                           | 4-3  |

| 6-1   | Interrupt Response Time                             | 6-5  |

| 7-1   | Restart Conditions                                  | 7-8  |

| 12-1  | Interpretation of MP and EM Flags                   | 12-3 |

| 13-1  |                                                     | 13-2 |

| 10-1  | Access Checking Instructions                        | 10-2 |

#### **LIST OF FIGURES**

| Figure | Title                                                | Page |

|--------|------------------------------------------------------|------|

| 1-1    | Segregation of Segments by Tasks with Private LDTs   | 1-2  |

| 1-2    | Global Segments in System                            | 1-3  |

| 1-3    | Segment Segregation by Privilege Level within a Task | 1-4  |

| 1-4    | A Four-Level Protection Structure                    | 1-6  |

| 1-5    | A Two-Level Protection Structure                     | 1-7  |

| 1-6    | A One-Level Unprotected Structure                    | 1-8  |

| 1-7    | Independent Operating-System Tasks                   | 1-9  |

| 1-8    | Building a Static System                             | 1-10 |

| 1-9    | Building a Dynamic System                            | 1-11 |

| 2-1    | Abstraction of Addressing Mechanism                  | 2-1  |

| 2-2    | Data Segment Descriptor                              | 2-3  |

| 2-3    | Executable Segment Descriptor                        | 2-4  |

| 2-4    | System Segment Descriptor                            | 2-5  |

| 2-5    | Calling a Conforming Segment                         | 2-6  |

| 2-6    | Gate Descriptor                                      | 2-9  |

| 2-7    | Intralevel Control Transfers                         | 2-11 |

| 2-8    | Gated Interlevel Call and Return                     | 2-12 |

| 2-9    | Valid and Invalid Interlevel Transfers               | 2-13 |

| 2-10   | Format of a Selector                                 | 2-16 |

| 2-11   | Aliasing for Debugger                                | 2-17 |

| 2-12   | Aliases for System Tables                            | 2-18 |

| 2-13   | Aliases with Differing Limit                         | 2-19 |

| 2-14   | Application of Segment Sharing                       | 2-20 |

| 2-15   | Aliases for Segment Sharing                          | 2-21 |

| 2-16   | Descriptor Manipulation Example                      | 2-23 |

| 2-17   | Available Slot List                                  | 2-26 |

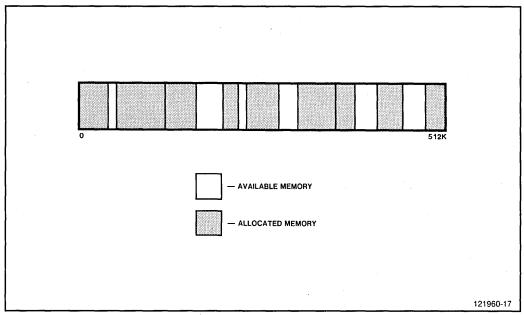

| 3-1    | Memory Fragmentation                                 | 3-2  |

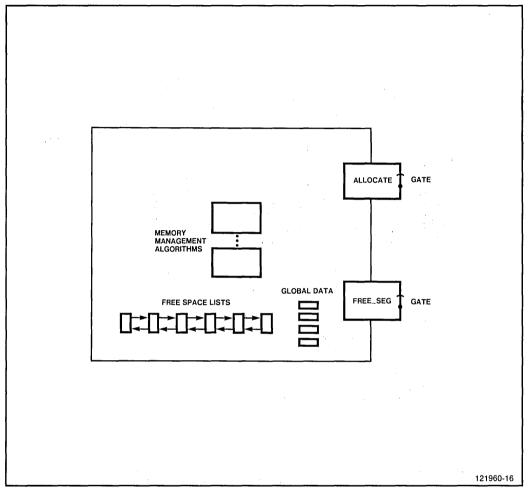

| 3-2    | Information Hiding in Memory-Management Example      | 3-3  |

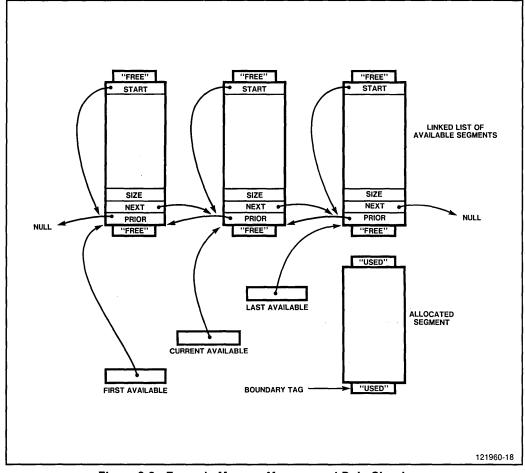

| 3-3    | Example Memory-Management Data Structures            | 3-4  |

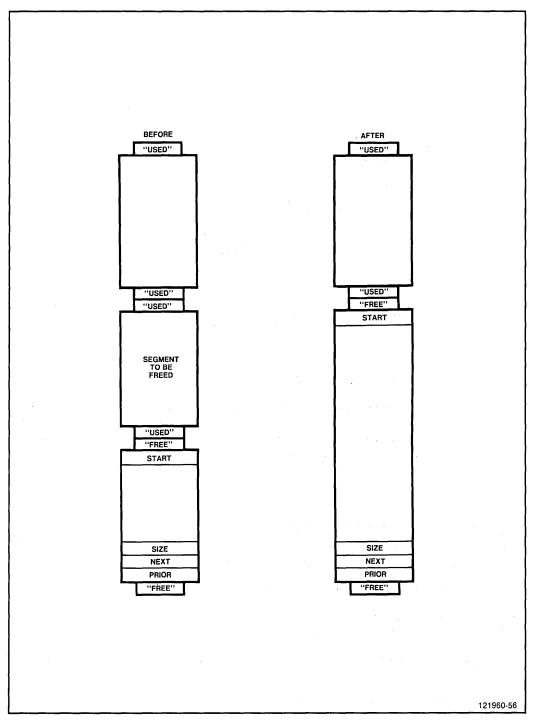

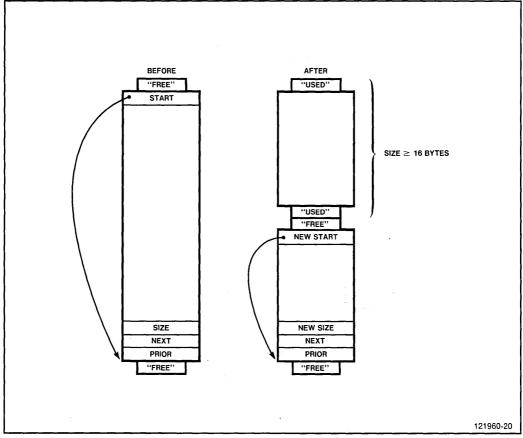

| 3-4    | Using Boundary Tags                                  | 3-5  |

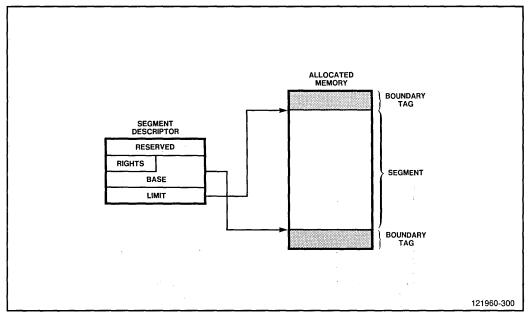

| 3-5    | Hiding Boundary Tags                                 | 3-6  |

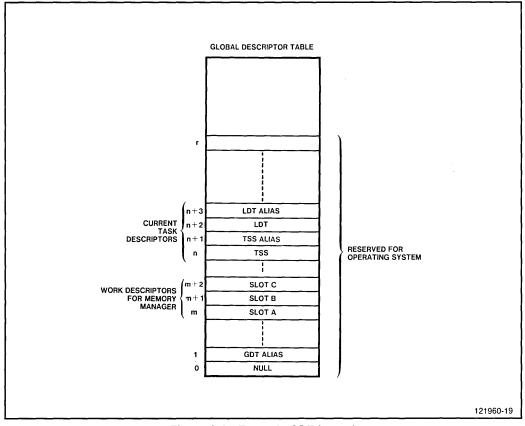

| 3-6    | Example GDT Layout                                   | 3-7  |

| 3-7    | Splitting an Available Block of Memory               | 3-8  |

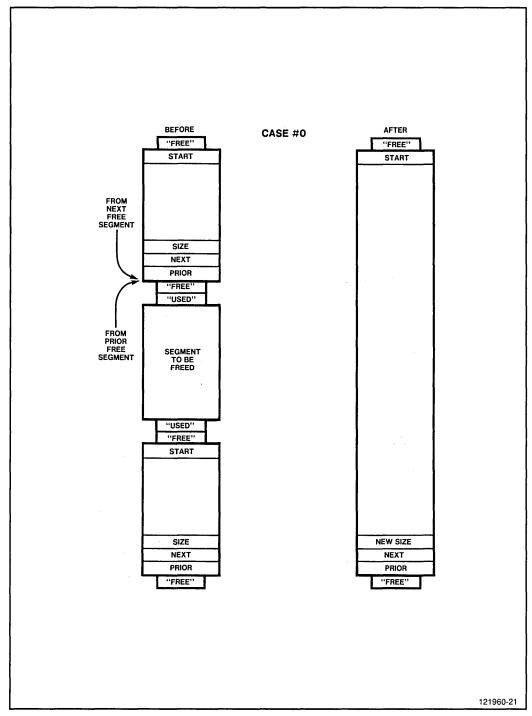

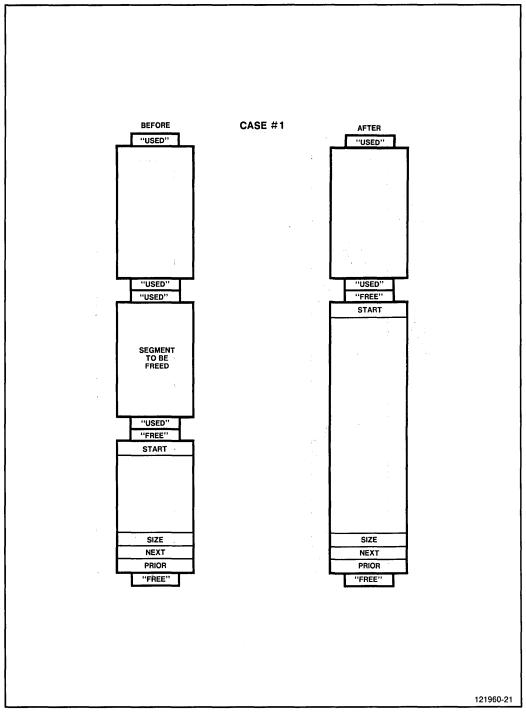

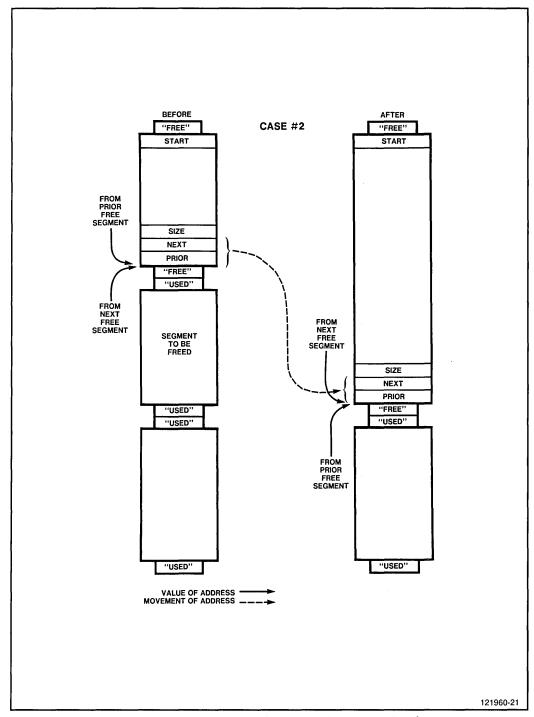

| 3-8    | Possibilities for Combining Segments                 | 3-11 |

| 3-9    | Code for Memory-Management Example                   | 3-15 |

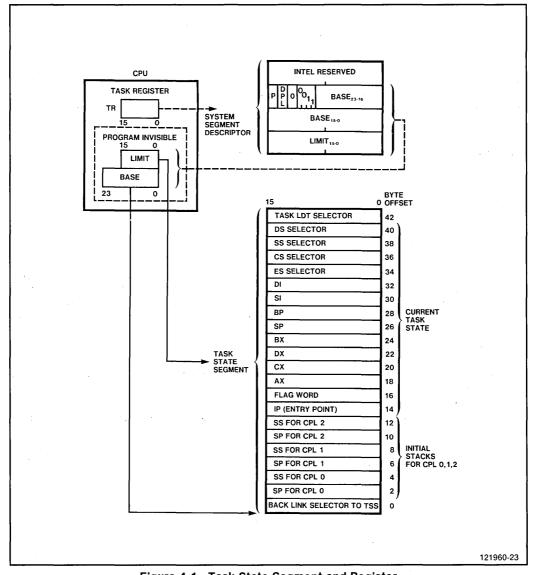

| 4-1    | Task State Segment and Register                      | 4-2  |

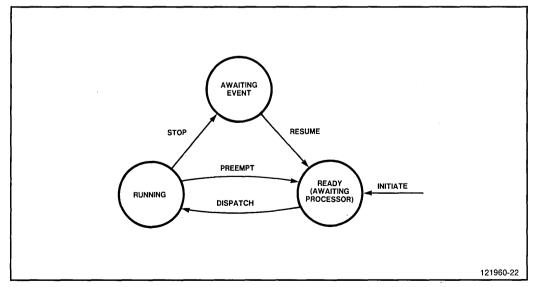

| 4-2    | Scheduling State Transition Diagram                  | 4-5  |

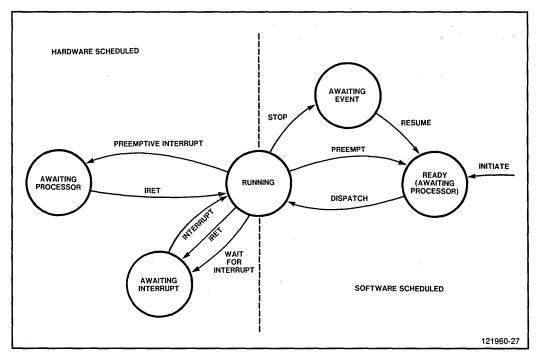

| 4-3    | Expanded Scheduling State Transition Diagram         | 4-6  |

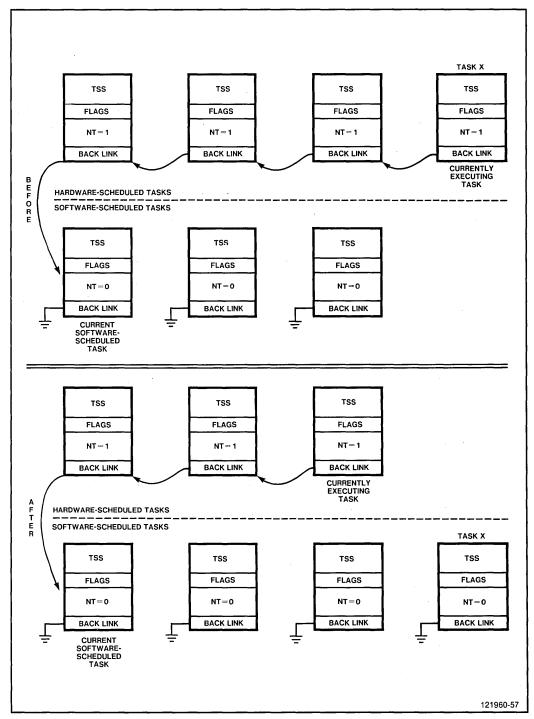

| 4-4    | Changing Scheduling Mode                             | 4-8  |

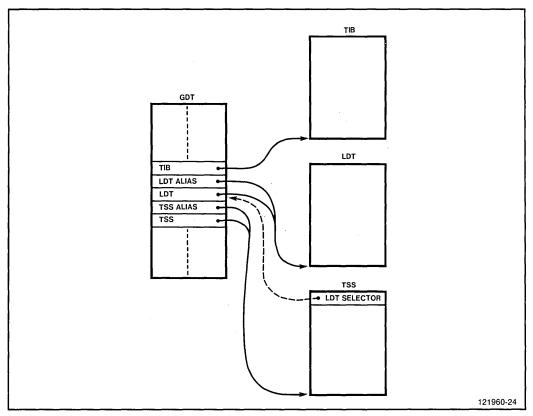

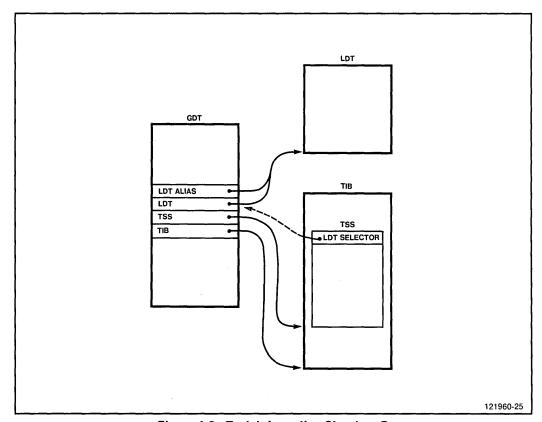

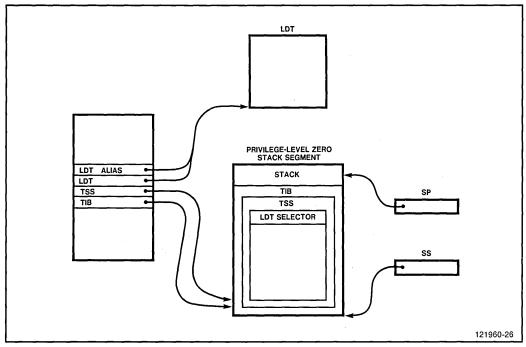

| 4-5    | Task Information Structure A                         | 4-11 |

| 4-6    | Task Information Structure B                         | 4-12 |

| Figure | Title                                       | Page  |

|--------|---------------------------------------------|-------|

| 4-7    | Task Information Structure C                | 4-13  |

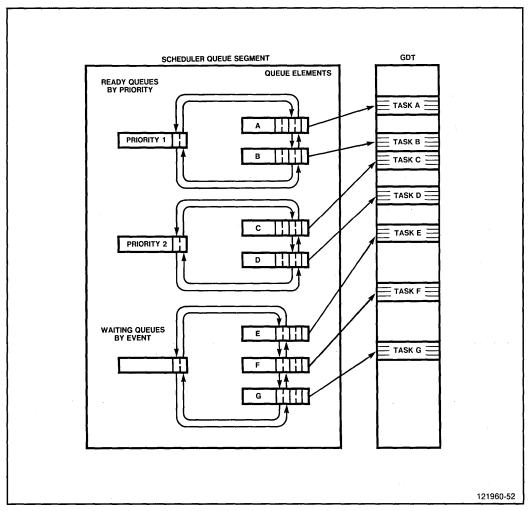

| 4-8    | Scheduler Queue Segment                     | 4-14  |

| 4-9    | Dispatcher Example                          | 4-15  |

| 5-1    | Segment via Common LDT                      | 5-2   |

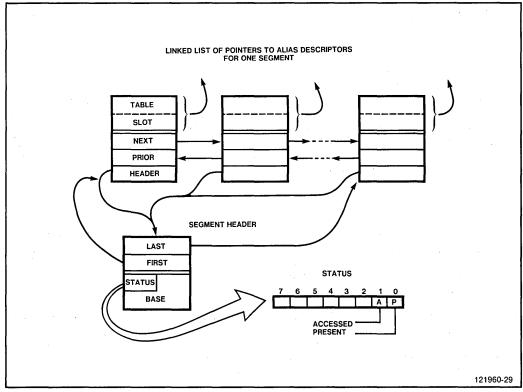

| 5-2    | Alias List                                  | 5-4   |

| 5-3    | Identifying Alias List                      | 5-5   |

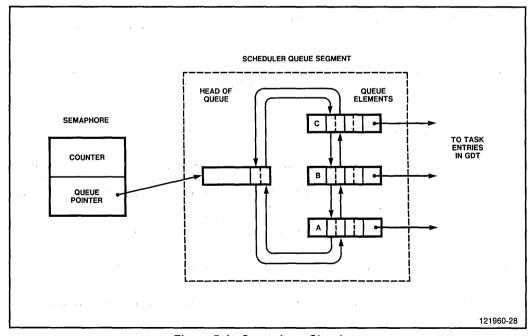

| 5-4    | Semaphore Structure                         | 5-6   |

| 5-5    | Semaphore Example                           | 5-8   |

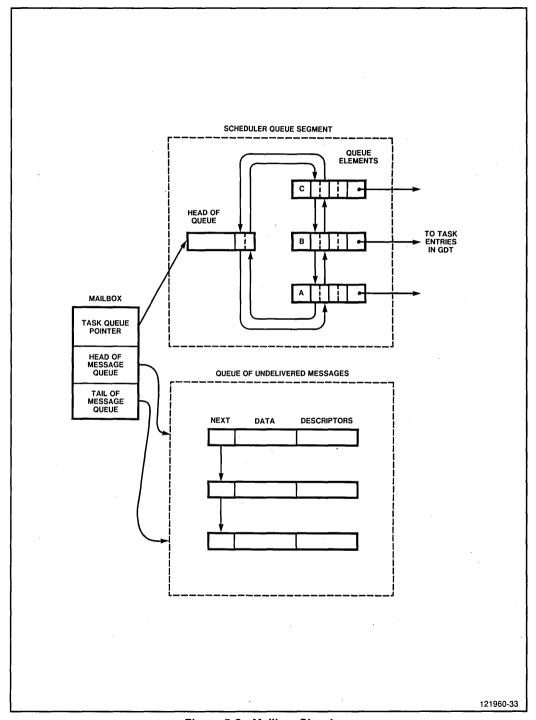

| 5-6    | Mailbox Structure                           | 5-11  |

| 5-7    | Example of Mailbox Procedures               | 5-13  |

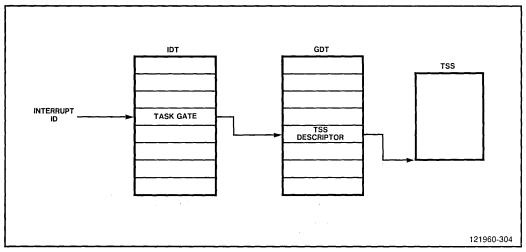

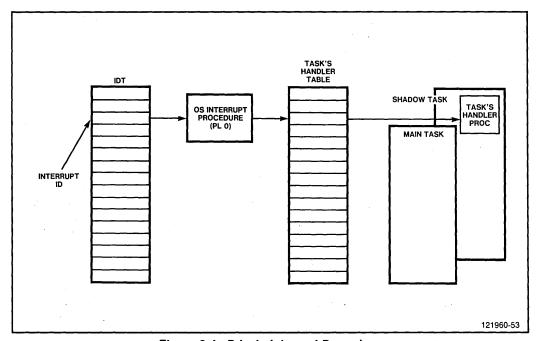

| 6-1    | Interrupt Vectoring for Tasks               | 6-3   |

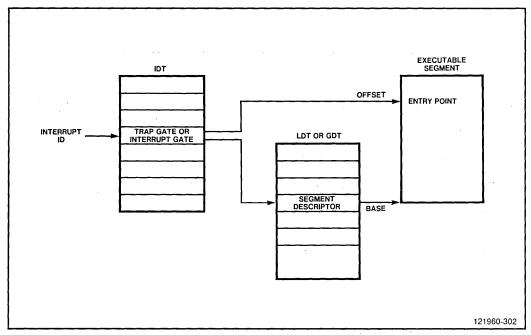

| 6-2    | Interrupt Vectoring for Procedures          | 6-3   |

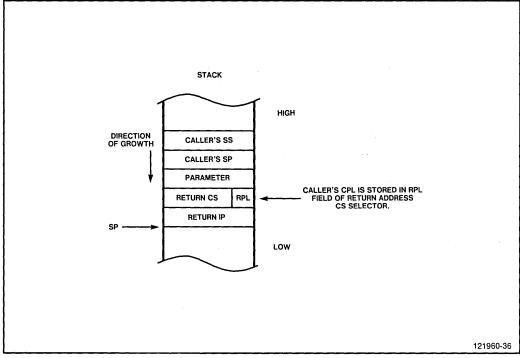

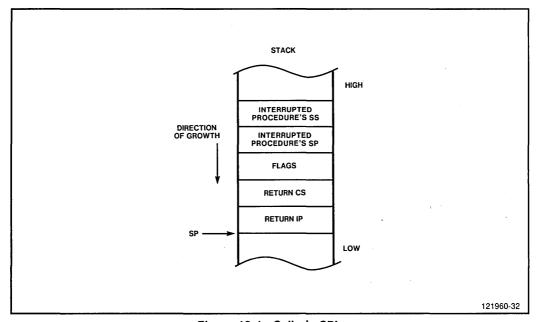

| 6-3    | Interrupt Procedure's Stack                 | 6-4   |

| 6-4    | Private Interrupt Procedure                 | 6-8   |

| 7-1    | Exception Error Code                        | 7-2   |

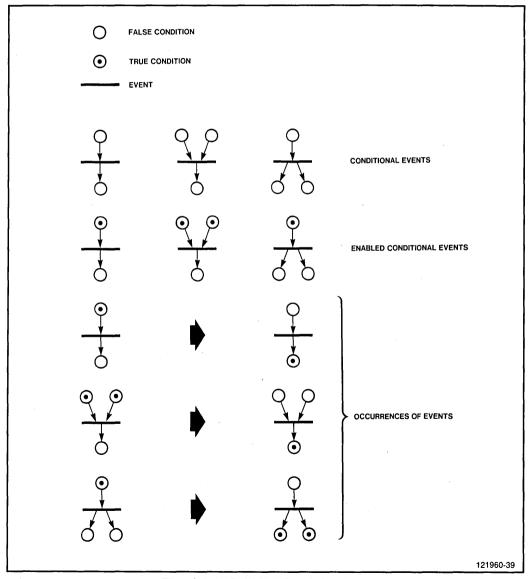

| 8-1    | Petri Net Graph Symbols                     | 8-5   |

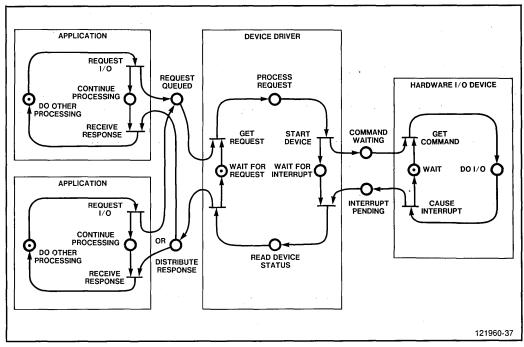

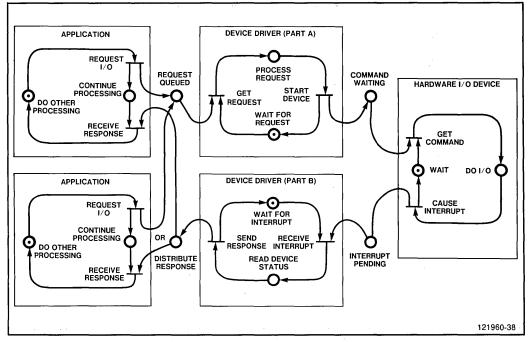

| 8-2    | Synchronization with Simple Device Driver   | 8-6   |

| 8-3    | Synchronization with Two-Part Device Driver | 8-6   |

| 10-1   | Initialization Module ENTP                  | 10-4  |

| 10-2   | Dummy Segments for ENTP                     | 10-14 |

| 10-3   | Initial Task INIT                           | 10-15 |

| 11-1   | Subsystem for Kernel Exports                | 11-5  |

| 11-2   | Binder Specifications for XOS Kernel        | 11-6  |

| 11-3   | Builder Specifications for XOS              | 11-7  |

| 11-4   | Specifying Dummy Gate Exports               | 11-13 |

| 11-5   | Strategy for Load-Time Binding              | 11-14 |

| 11-6   | Binding Loader                              | 11-15 |

| 11-7   | BOND Module of Binding Loader               | 11-24 |

| 13-1   | Caller's CPI                                | 13-3  |

# Introduction to Protected Multitasking on the iAPX 286

1

# CHAPTER 1 INTRODUCTION TO PROTECTED MULTITASKING ON THE IAPX 286

The iAPX 286 architecture views the software system (the operating system as well as applications) as a number of asynchronous tasks, each task possibly consisting of levels of procedures deserving different degrees of "trust." An operating system for the iAPX 286 must (with the help of the hardware) coordinate the activities of multiple tasks and administer protection among tasks and among levels of procedures within tasks.

#### **TASKS**

A task is the execution of a sequence of steps. A program is a logical entity that can have many representations: for example, source code file or object program file. A program becomes a task when it is actually available for execution. This is achieved by converting source (with a compiler and program loader, for example) to a representation suitable for execution and notifying the operating system that the task is ready for installation and execution.

The distinction between programs and tasks is most clear in a multitasking system, where it is possible for two or more tasks to use one program simultaneously. The line editor program in a timesharing system is a common example. Even though each line editor task uses the same program, each task produces different results, since it receives different inputs.

#### Structure of a Program

Each program is formed from modules created by language translators and bound together into a single executable unit. The translators (for example, ASM286, PL/M-286, Pascal-286, and FORTRAN-286) and the object program utilities (for example, Intel's Builder and Binder) support the concept of *logical segments*. A logical segment is a contiguous block of either instructions or data. Each logical segment can contain up to 64K bytes of code or data. Logical segments are the units that may be combined when a program comprises more than one module.

#### **Segmented Memory**

The iAPX 286 structures the address space of a task into *physical segments* of variable length. A physical segment is a contiguous block of memory that does not (normally) overlap another physical segment. Each physical segment may contain up to 64K bytes of either instructions or data. Each physical segment contains one or more logical segments of a task. The segments reflect how tasks are organized into code, data, and stack areas.

#### Multitasking

One of the most important features of the iAPX 286 is its ability to switch rapidly from executing one task to executing another task. This gives the appearance that the processor is executing more than one task at a time.

1–1 121960-001

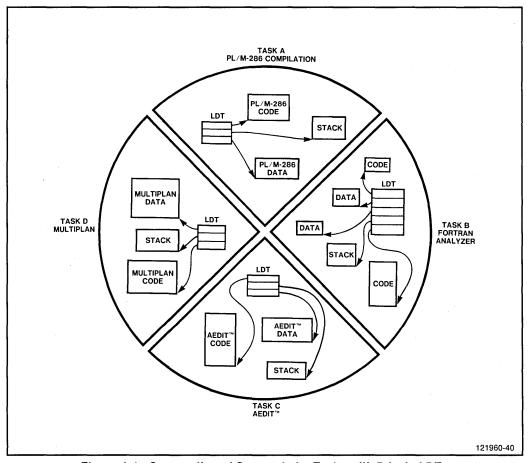

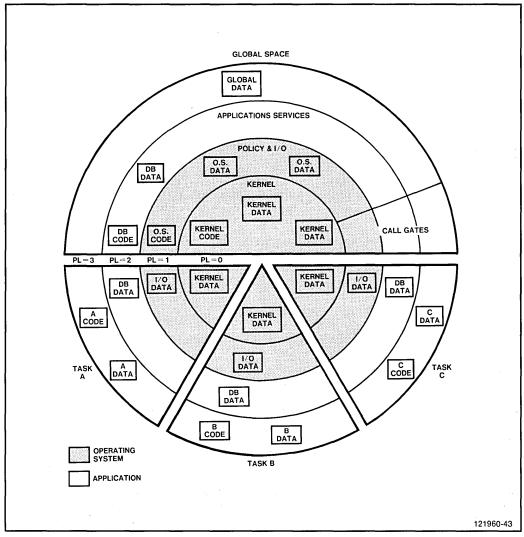

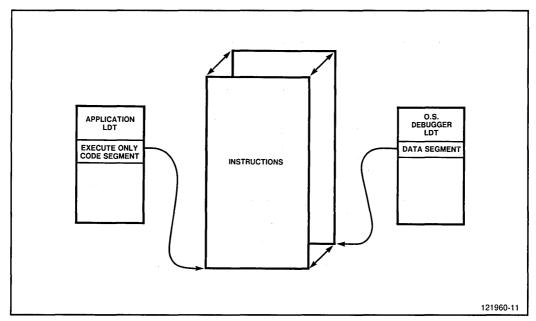

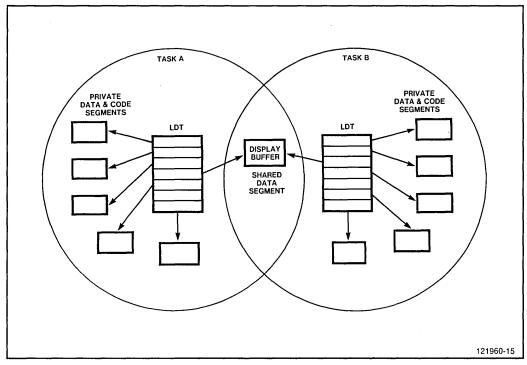

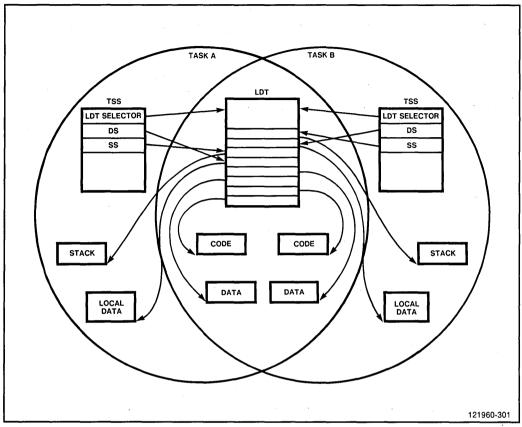

Hardware system tables enable both the hardware and the operating system to distinguish between the physical segments of individual tasks. Figure 1-1 shows how physical segments of one task are logically separate from those of other tasks. Since references to physical segments are always relative to system descriptor tables, the actual locations of physical segments in physical memory are not significant to the tasks and therefore are not illustrated.

Descriptor tables serve not only to identify the segments that belong to a task but also to *isolate* the address space of one task from that of another, so that one task cannot inadvertently affect the operations of another.

Multitasking works through close interaction of the operating system with hardware features. When the executing task needs to wait for some event (such as the arrival of data from some I/O device), it notifies the operating system. The operating system determines which other task should execute next, and then causes the processor to store the state of the current task, retrieve the state of the next task, and begin executing the next task at the point where its processing last halted. The processor then executes that task until the task needs to wait for some event. (This is a somewhat oversimplified

Figure 1-1. Segregation of Segments by Tasks with Private LDTs

1-2 121960-001

description of what can be a complex operating system function. Chapter 4 covers the subject of task switching in more detail.)

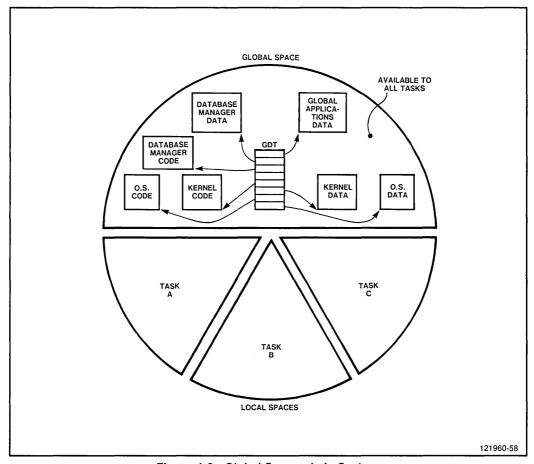

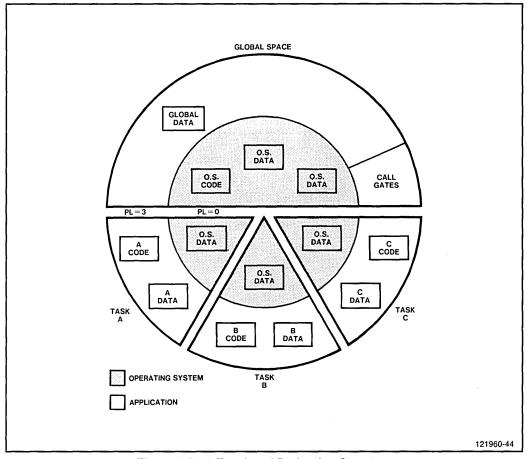

Figure 1-2 illustrates how the global descriptor table defines an address space that is accessible to all tasks in the system. This global space is useful for translation tables, run-time libraries, operating-system code and data, and the like.

#### PRIVILEGE LEVELS

The iAPX 286 architecture uses the concept of *privilege levels* to protect critical procedures within a task from less trusted procedures in the same task. For example, with previous generations of microprocessors, applications code could access and possibly destroy tables used by the operating system. An error of this sort could cause the operating system to incorrectly service a subsequent request from another unrelated task. With the iAPX 286, such situations are prevented by hardware-enforced barriers between different levels of procedures.

Figure 1-2. Global Segments in System

1-3

121960-001

Applied to procedures, privilege level is a measure of the degree to which you trust a procedure not to make a mistake that might affect other procedures or data. Applied to data, privilege level is a measure of the protection you think a data structure should have from less trusted procedures.

Privilege level also applies to instructions. Certain instructions (those that deal with system tables, interrupts, and I/O, for example) have such an effect on the system as a whole that only highly trusted procedures should have the right to use them.

#### Levels of Segments

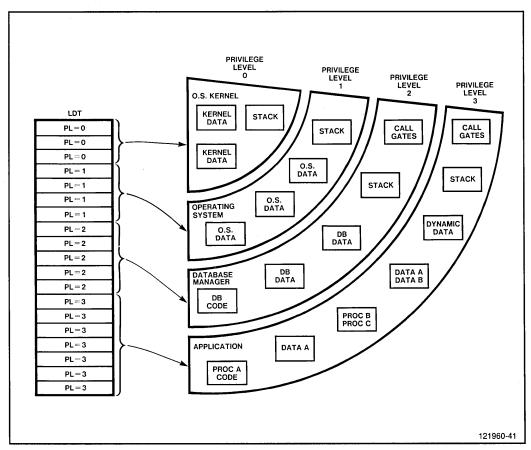

With regard to privilege, you can view the segments of a task as being grouped into four levels. Level zero is for the most privileged procedures and the most private data; level three is for the least trusted procedures and the most public data. You (or your operating system) associate each segment of each task with one of these four levels of privilege. The privilege level of a segment applies to all the procedures or all the data in that segment. Figure 1-3 illustrates the logical segregation of segments into privilege levels. (Later chapters explain why operating-system segments are included within the task.)

Figure 1-3. Segment Segregation by Privilege Level within a Task

1-4 121960-001

#### **Rules of Privilege**

The 80286 processor controls access to both data and procedures between levels of a task. These rules define access rights:

- Data can be accessed only from the same or a more privileged level.

- A procedure can be called only from the same level (or from a less privileged level, if the service is deliberately "exported" to that level. Refer to gates in Chapter 2.).

#### SOFTWARE SYSTEM STRUCTURE

The way you choose to distribute software and data among tasks and privilege levels affects the reliability, efficiency, and flexibility of your system. Operating-system modules may be segregated into their own tasks or may be distributed among and shared by every task. Some advantages of placing operating-system modules in separate tasks are

- Finer granularity of protection is achieved by using task separation as well as privilege levels.

- Operating-system functions can execute in parallel with the caller.

- When only one task at a time can perform the function (for example, reading from a keyboard), serialization of requests is automatic; you do not need to synchronize among requesting tasks.

Some advantages of distributing operating-system functions are

- The communication between application and operating system is faster.

- It may be possible for all tasks to execute the same operation-system function in parallel. (You must ensure reentrancy and provide for synchronization, however.)

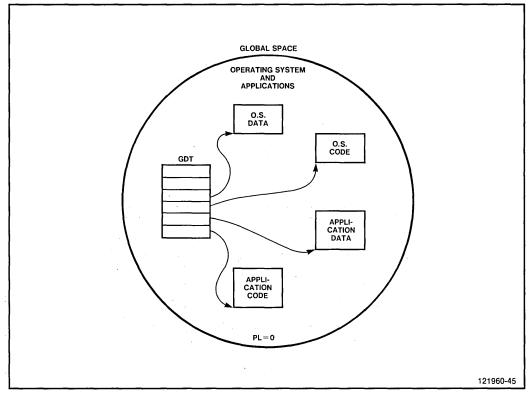

Figures 1-4 through 1-7 illustrate some general approaches that you may consider.

The approach shown in figure 1-4 takes maximum advantage of the four privilege levels. The critical procedures and data of the operating system kernel (for example, memory allocation tables and procedures, information about tasks) are protected from all other procedures in the system. Those parts of the operating system that are less reliable, either due to inherent complexity (for example, the I/O subsystem) or due to occasional changes (for example, policies designed to increase overall throughput), are at a lower level but are still protected from application levels. Application logic has two levels so that application services (such as database management) can be protected from less trusted application code, yet application services cannot affect the integrity of the operating system. Operating-system procedures and application services are shared among all the tasks in the system.

Figure 1-5 illustrates that you do not need to use all four privilege levels. You may prefer this two-level approach if you are converting from a traditional multitasking system that offers protection only between the two levels defined by application and operating system.

The iAPX 286 can also emulate one-level systems, as illustrated in figure 1-6. This approach may be useful in the initial stages of converting from an unprotected system, but it does not take advantage of many of the protection features offered by the iAPX 286. It does isolate tasks from one another, but it does not protect the operating system from applications software.

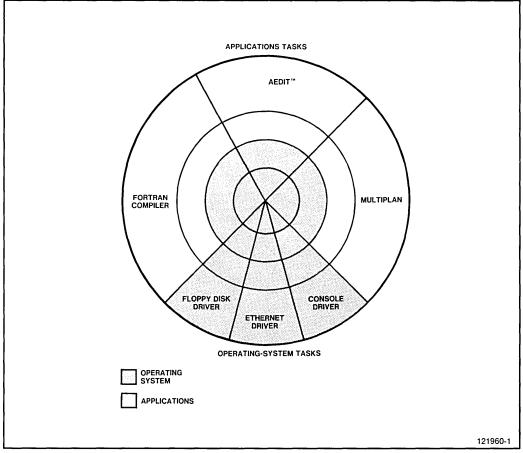

Some operating system functions are better structured as independent operating-system tasks, not as privileged procedures within a task. Certain I/O functions are suited to this treatment. Because of the complexity of I/O code, the extra protection offered by a task boundary contributes to the reliability

1–5 121960-001

Figure 1-4. A Four-Level Protection Structure

of the system. Because many I/O functions involve waiting for responses from I/O devices, it is most convenient to treat these functions as a separate task that can run asynchronously with respect to the tasks that invoke them. Figure 1-7 illustrates a structure with independent operating-system tasks.

#### ROLE OF THE OPERATING SYSTEM

The role that an operating system may play in managing a multitasking execution environment depends on the nature of the application. Applications can be classified according to the volatility of tasks

1–6 121960-001

Figure 1-5. A Two-Level Protection Structure

executing over a period of time. Applications in which tasks frequently begin and end (for example, time-sharing systems or multi-user business systems) are called *dynamic systems*. Applications in which the mix of tasks does not change (for example, process control systems in which tasks service a fixed number of sensors and effectors) are called *static systems*.

#### Common O.S. Functions

The operating-system roles common to both static and dynamic applications are

- Allocation of the processor or processors to tasks

- · Coordination and communication among cooperating tasks

- Processing of interrupts and exception conditions

- Standardization of interfaces to I/O devices

- Control of the numerics processor extension

1–7 121960-001

Figure 1-6. A One-Level Unprotected Structure

#### O.S. Functions in a Dynamic Environment

Even though many of the duties of an operating system in a dynamic environment resemble those in a static environment, the dynamic environment often introduces new complexities. Some additional functions that a dynamic system may require include

- · Real memory management

- · Program loading

- · Command language interface

- Virtual memory management

- Load-time binding

#### CONSTRUCTING THE INITIAL RUN-TIME ENVIRONMENT

Intel's System Builder program helps you create the initial executable system. The Builder program collects object modules into one module, assigns physical addresses, creates system tables, and assigns privilege levels. A specification language gives you the ability to control precisely what the Builder does.

1-8 121960-001

Figure 1-7. Independent Operating-System Tasks

#### **Building a Static System**

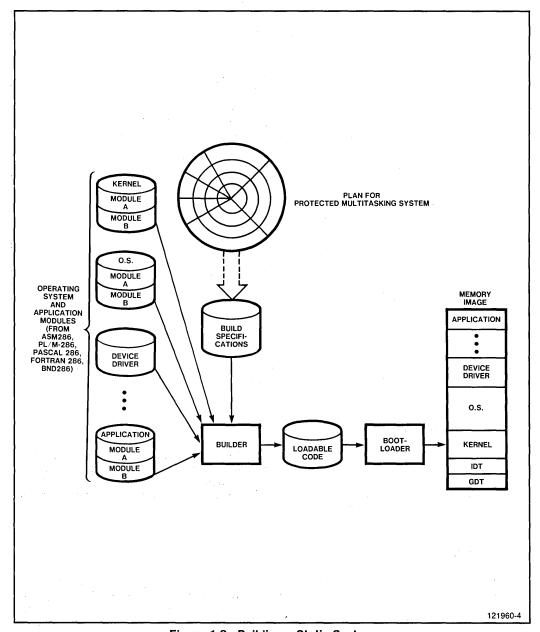

In the case of static systems, the Builder does nearly all the work in constructing a running system. Refer to figure 1-8 for an illustration of the building process. The output of the Builder is a single module that contains all the tasks, both for the operating system and for applications, as well as all system tables and protection information. The Builder's output file has a format that simplifies creation of a bootstrap loader for the system.

#### **Building a Dynamic System**

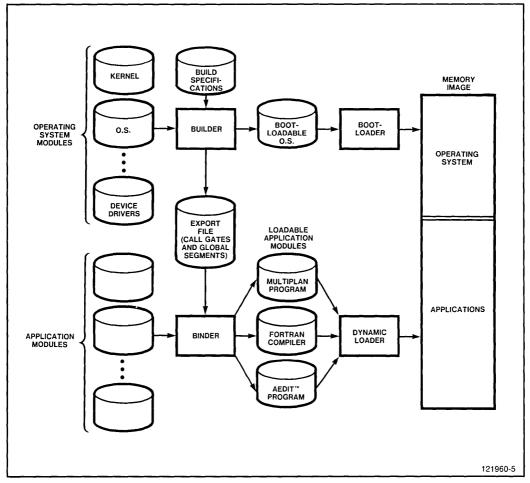

With dynamic systems, the Builder constructs as much of the final system as you can specify in advance, but the nature of dynamic systems is such that the operating system must do at run-time many of the operations that the Builder does for static systems (for example, allocation of memory and assignment of physical addresses). The operating system must update system tables and administer the protection mechanisms as the running environment changes.

1-9 121960-001

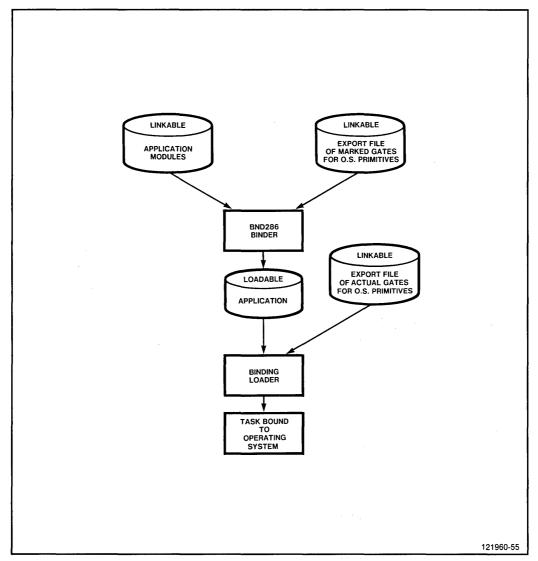

Figure 1-9 illustrates the process of constructing a dynamic system. The Builder creates a loadable module containing those operating-system functions that permanently reside in the running operating system, and it also creates a file that contains information about linking to operating-system primitives. Either a static linker (such as Intel's Binder) or a dynamically linking loader can use this information to help dynamically loaded tasks use operating-system functions.

Figure 1-8. Building a Static System

Figure 1-9. Building a Dynamic System

1–11 121960-001

## CHAPTER 2 USING HARDWARE PROTECTION FEATURES

The architecture of the iAPX 286 enables you to organize software systems so that each task is protected from inadvertent or malicious damage by other tasks and so that privileged procedures are protected from lower-level procedures. You control the degree of protection in your system by the way you set up protection parameters through the Builder or through operating system procedures. The processor interprets the protection parameters and automatically performs all the checking necessary to implement protection.

#### ADDRESSING MECHANISM

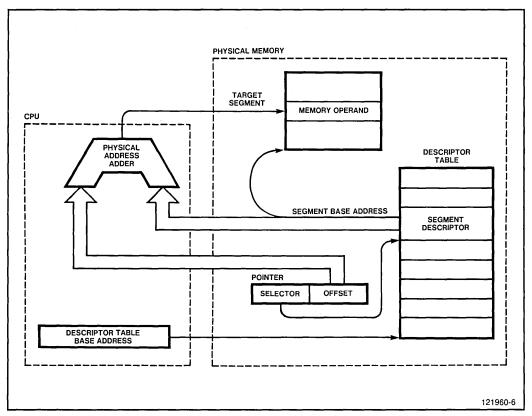

The protection mechanism of the iAPX 286 is embedded in the addressing mechanism. For an introduction to the addressing mechanism, refer to figure 2-1, which shows those portions of the addressing mechanism that are not concerned with protection features. From the point of view of the applications programmer, an address is a pointer. A pointer consists of two parts: a selector and an offset. The

Figure 2-1. Abstraction of Addressing Mechanism

2-1 121960-001

#### **USING HARDWARE PROTECTION FEATURES**

selector portion identifies a segment of the address space and the offset addresses an item within the segment relative to the beginning of the segment.

A selector identifies a segment by reference to a descriptor table. Each entry in a descriptor table is a descriptor. A selector contains an index that identifies a particular descriptor in a particular descriptor table. The descriptor contains the physical address and access rights of the segment.

Both selectors and descriptors contain additional information that relates to the protection features of the iAPX 286.

#### **DESCRIPTORS**

A reference from one segment to another is realized indirectly through a *descriptor*, which contains information about the referenced segment. All descriptors reside in a descriptor table. Every segment must have at least one descriptor; otherwise there is no means to address the segment.

Descriptors are strictly under your control via the Builder or operating system procedures. The existence and function of descriptors is completely invisible to the applications programmer.

#### **Descriptor Format**

There are four variations in descriptor format, corresponding to the four classes of descriptor:

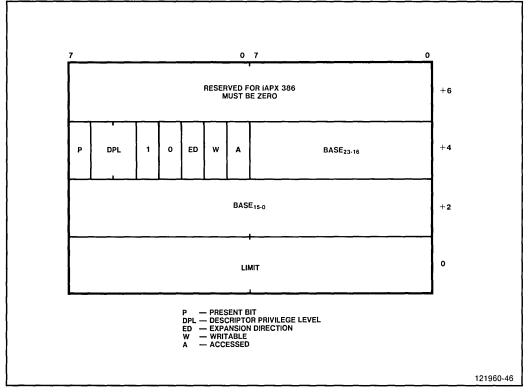

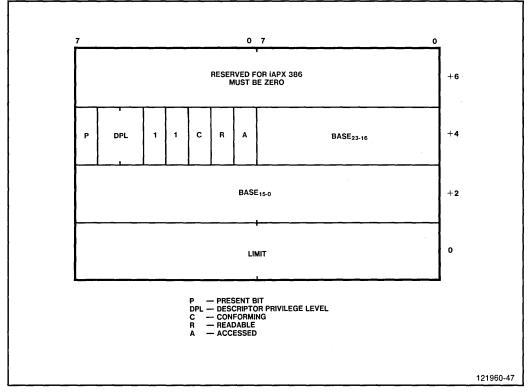

- 1. Data segment descriptors refer only to segments that contain system or application data, including stacks (see figure 2-2).

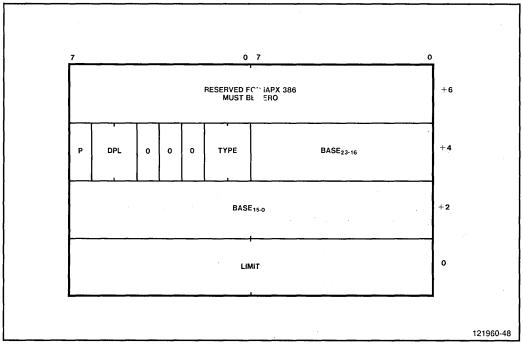

- 2. Executable segment descriptors refer only to segments that contain executable instructions (see figure 2-3).

- 3. System segment descriptors refer only to segments that contain special hardware-recognized data structures, such as descriptor tables (see figure 2-4).

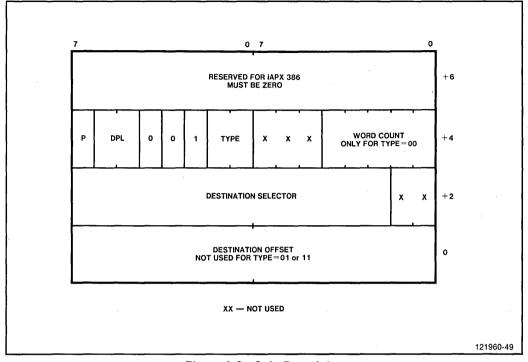

- 4. Gate descriptors define entry points for control transfers. A gate descriptor does not directly address a memory segment; instead it provides a protected pointer to an exported entry point. (Refer to the section "Gate Descriptors" later in this chapter.)

The first two types of descriptor hold information that any operating system must maintain. The iAPX 286, however, requires that such information be in a fixed format so the CPU can interpret it directly. These descriptors are often created dynamically while a program executes (for example, a data-segment descriptor may be created when a task needs additional memory to store an expanding data structure).

The second two types of descriptor are unique to the iAPX 286. They are constructed either once when the system is built or once when a task is created. Code to manipulate these descriptors is limited to the procedures of a dynamic operating system that create new tasks.

Several of the descriptor formats have common fields. These fields are listed first in the following discussions of descriptor contents.

#### PRESENT BIT

This Boolean is set if the segment addressed by the descriptor is actually present in memory, reset if not present. Operating systems for dynamic applications that implement virtual memory must set and

Figure 2-2. Data Segment Descriptor

reset this bit as program segments are brought into or eliminated from memory. Reference to a segment whose present bit is reset causes a fault, providing an opportunity for the operating system to load the segment from virtual store. (Chapter 9 takes up implementation of virtual memory systems.) In systems that do not implement virtual memory, this bit is always set for allocated segments.

#### **DESCRIPTOR PRIVILEGE LEVEL**

The value of this item defines the privilege level of the segment addressed by this descriptor. You control the values in the descriptor privilege level (DPL) by the parameters you give to the builder when creating a static system or the resident portion of a dynamic system, or by the procedures your operating system uses when loading segments dynamically.

#### **INTEL RESERVED**

This portion of the descriptor is reserved by Intel and should always be initialized with zeros. Other use of this field in a valid descriptor will prevent compatability with the iAPX 386 and other additions to Intel's family of processors.

Figure 2-3. Executable Segment Descriptor

#### SEGMENT BASE

This field contains the physical address of the beginning of the memory segment referred to by this descriptor. The 24 bits of this address give the 80286 a 16-megabyte range of real addresses. This is the only place that physical addresses are used. All other addresses are relative to the physical addresses stored in descriptors, making it possible to relocate executable and data segments without making any changes to the relocated segments or to code that refers to the segments. The only changes necessary to relocate segments are changes to the physical addresses stored in descriptor tables.

You can control the actual location of segments by means of specifications to the Builder or by means of the algorithms your operating system uses to allocate memory to segments that are loaded dynamically.

#### **SEGMENT LIMIT**

Segment limits prevent accidental reading or writing beyond the space allocated to a segment. The value of this field is one less than the length of the segment (in bytes) relative to the beginning of the segment. The 16 bits of this field make it possible to have segments up to 64K bytes long. The hardware automatically checks all addressing operations to ensure that they do not exceed the segment limit of the segment to which they refer. This protects other segments from such common programming errors as runaway subscripts.

Figure 2-4. System Segment Descriptor

Note that the segment limit field has a different meaning for "expand down" data segments. Refer to the "expansion direction" bit later in this chapter.

#### **SEGMENT TYPE**

For system segments, the type field distinguishes between kinds of system segments. System segment types are

- 1 and 3 Task state segment, a segment used for storing the context of a task. Chapter 4 discusses task state segments more fully.

- 2 Local descriptor table. The three kinds of descriptor tables are explained later in this chapter.

The processor interprets the type field to ensure that each segment is actually used as intended; for example, an attempt to jump to a local descriptor table is obviously a mistake, and the processor detects this error while examining the target segment's descriptor during the JMP instruction.

#### **EXPANSION DIRECTION**

Data segments may contain stacks as well as other data structures. Stacks expand toward lower addresses while most other data structures expand toward greater (higher) addresses. This field indicates the growth pattern for the segment. A value of zero in this field indicates that the segment expands upward

(from the base address toward the segment limit value that is also contained in the descriptor). A value of one indicates that the segment expands downward (from offset FFFFH toward the limit).

#### WRITABLE

This field applies only to data segment descriptors. A value of one permits the CPU to write into the segment; a value of zero protects the segment from attempts to write into it. Translation tables are but one example of data that deserve the extra protection afforded by storage in a read-only segment.

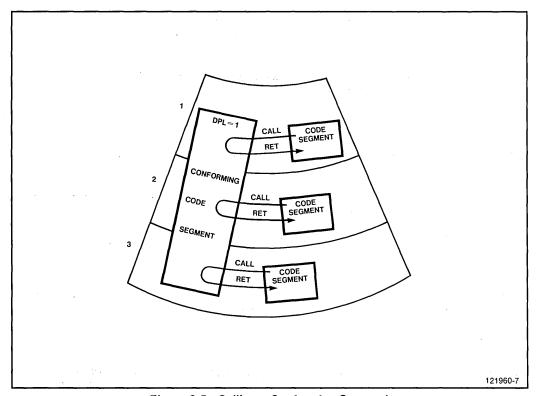

#### CONFORMING

This field applies to executable-segment descriptors only. Ordinarily (when the conforming bit is zero) a called procedure executes at the privilege level defined by the DPL in the descriptor of the segment in which the procedure resides. When the conforming bit of the called segment is set, however, the called procedure executes at the calling procedure's privilege level. This feature cannot be used to decrease (numerically) a segment's privilege level below that defined by it's DPL. Figure 2-5 shows graphically how a conforming segment works. This feature is useful when you want to make procedures (mathematical subroutines or run-time support procedures, for example) available to a number of other procedures running at different privilege levels, but when you do not want to provide increased privilege while the subroutine is executing.

Figure 2-5. Calling a Conforming Segment

2-6 121960-001

#### READABLE

This field applies only to executable-segment descriptors. When reset, it prevents procedures in other segments from reading this code segment; the contents of the segment can be executed only. It is common, however, for executable segments to contain read-only data, in which case this bit must be set.

## **ACCESSED**

The processor sets this bit when the descriptor is accessed (that is, loaded into a segment register or used by a selector test instruction). Operating systems that implement virtual memory may, by periodically testing and resetting this bit, monitor frequency of segment usage. This bit also indicates whether a segment should be written to secondary storage before the RAM space it occupies is reused.

# CONTROL FLOW TRANSFER

Transfers of control are also subject to protection rules. Within the application-oriented part of a task, the protection rules allow unlimited access to code and data. Control transfers to privileged operating-system functions and to other tasks, however, are controlled by gate descriptors. With gate descriptors, the iAPX 286 architecture can perform functions in hardware that operating systems on other processors must do in software. These functions are invoked directly by ordinary CALL and JMP instructions, not by special interrupt or trap instructions.

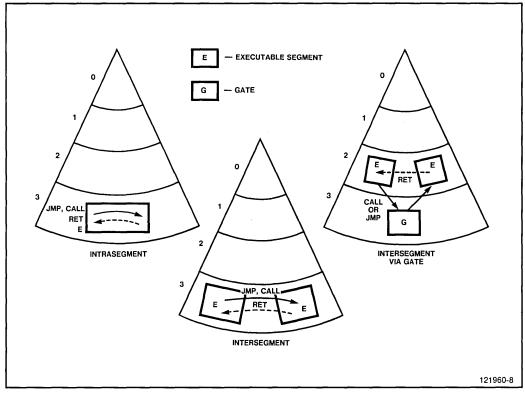

As table 2-1 illustrates, transfers of control can be classified into four categories, depending on whether control passes to another segment, another privilege level, or another task. This classification can help clarify how privilege levels, descriptor tables, and tasks are used.

Processor functions that cause a change in the flow of control are

- Jump instruction (JMP)

- Procedure call instruction (CALL)

- Procedure return instruction (RET)

- Software interrupt instruction (INT)

- External interrupt

Table 2-1. Categories of Control Flow Transfer

| Category     | Segment                 | Privilege<br>Level      | Task      |

|--------------|-------------------------|-------------------------|-----------|

| Intrasegment | same                    | same                    | same      |

| Intersegment | different               | same                    | same      |

| Interlevel   | different               | different               | same      |

| Intertask    | same<br>or<br>different | same<br>or<br>different | different |

# **USING HARDWARE PROTECTION FEATURES**

- Processor-detected exception condition

- Interrupt return instruction (IRET)

Control transfers within the same privilege level may be either short (within same segment) or long (to another segment). A short transfer simply specifies the offset of the instruction to which control is transferred in the same segment. A long transfer also uses a selector to identify the segment to which control is transferred.

For control transfer to a different privilege level or different task, the iAPX 286 introduces gate descriptors.

# Gate Descriptors

A gate descriptor is a type of descriptor used only for transferring control flow to instructions in another segment. Gates provide an indirect reference that is useful for binding and protection purposes. By requiring interlevel and intertask control transfers to reference gate descriptors, the iAPX 286 provides two additional protection features:

- 1. You can hide a procedure by not providing a gate for its entry point.

- 2. You can control access to a procedure via the privilege assigned to the gate. This allows hiding critical procedures from untrusted software.

Figure 2-6 illustrates the format of a gate descriptor.

## DESTINATION SELECTOR

For call, interrupt, and trap gates, this field contains a selector for the segment descriptor of the destination executable segment. For task gates, the selector in this field points to a descriptor for a task state segment, and the RPL field is not used.

#### **DESTINATION OFFSET**

For call, interrupt, and trap gates, this field contains the offset of the entry point within the destination executable segment (not used with task gates).

## WORD COUNT

For each privilege level within a task, there is a separate stack. For calls through a call gate, the processor automatically copies parameters from the stack for the calling procedure's privilege level to the stack for the destination's privilege level. In this field, you specify the number of words to copy.

## **GATE TYPE**

For gate descriptors, the type field distinguishes among the four kinds of gates:

- 0 Call gate

- 1 Task gate

- 2 Interrupt gate

- 3 Trap gate

2-8 121960-001

Figure 2-6. Gate Descriptor

#### PRESENT BIT

Since a gate descriptor does not refer directly to a segment, the present bit in a gate descriptor does not necessarily indicate whether a segment is present. It can be used for other purposes, however. Refer to Chapter 11 for an example of using the present bit to facilitate late binding.

# **Control Transfer Mechanisms**

Table 2-2 summarizes the mechanisms for each class of control flow transfer.

Control transfers within a segment function similarly to intrasegment transfers on the iAPX 86,88, except that the processor checks that the destination address does not exceed the segment limit.

Figure 2-7 illustrates a change in control flow between segments at the *same* privilege level. Any of the following instructions can effect such a transfer:

```

JMP offset selector

CALL offset selector

RET; (offset and selector taken from stack)

```

The selector selects a descriptor for an executable segment. The DPL in the target segment's descriptor must be the same as the privilege level under which the calling segment is running. A CALL or

121960-001

| Table | 2-2 | Control | Transfer | Mechanisms |

|-------|-----|---------|----------|------------|

|       |     |         |          |            |

| Transfer<br>Type | Operation                                               | Descriptor<br>Referenced               | Table   |

|------------------|---------------------------------------------------------|----------------------------------------|---------|

| Intrasegment     | JMP, CALL, RET                                          | (none)                                 |         |

| Intersegment     | JMP, CALL, RET, IRET                                    | code segment                           | GDT/LDT |

| (*)              | CALL, JMP                                               | call gate<br>(same PL)                 | GDT/LDT |

|                  | INT instruction,<br>external interrupt,<br>or exception | trap or<br>interrupt<br>gate (same PL) | ТОТ     |

| Interlevel       | CALL                                                    | call gate                              | GDT/IDT |

|                  | INT instruction,<br>external interrupt,<br>or exception | trap or<br>interrupt<br>gate           | IDT     |

|                  | RET, IRET                                               | code segment                           | GDT/IDT |

| Intertask        | CALL, JMP, IRET                                         | task state<br>segment                  | GDT     |

|                  | CALL, JMP                                               | task gate                              | GDT/LDT |

|                  | INT instruction,<br>external interrupt,<br>exception    | task gate                              | IDT     |

<sup>\*</sup> Includes cases in which the target segment is incidentally the same as the calling segment.

JMP instruction may also reference a call gate. If the target executable segment is at the same privilege level, no level change occurs.

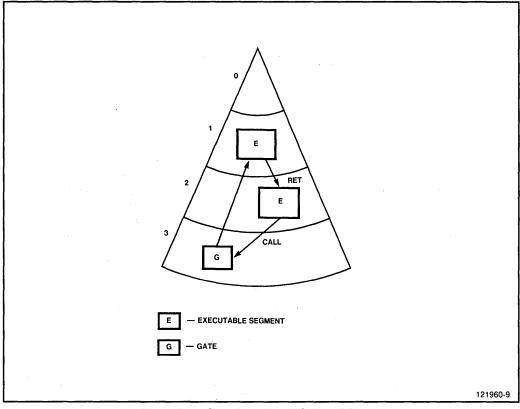

For transfers of control between segments at different privilege levels (as illustrated in figure 2-8) there are three differences:

• Only the following instructions can be used:

CALL offset selector RET

Jumps between privilege levels within a task are not allowed.

- The selector does not select the descriptor of an executable segment but rather selects a gate descriptor.

- The offset operand must be present but is ignored.

Figure 2-7. Intralevel Control Transfers

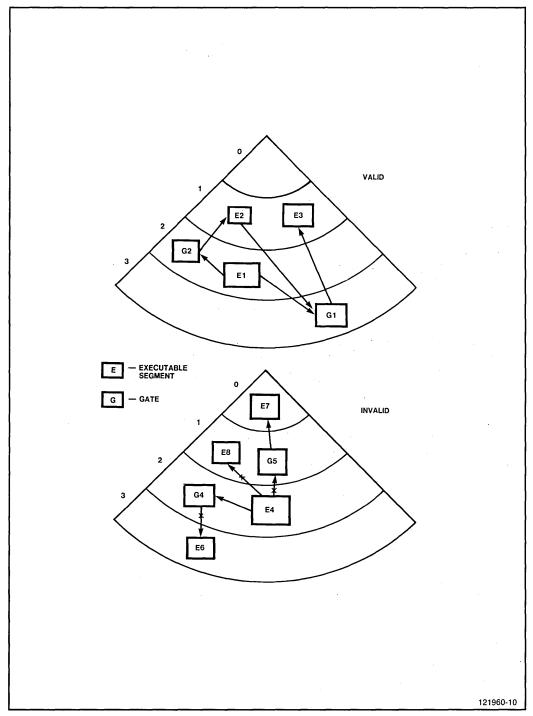

# **Privilege Rules for Gated Intersegment Transfers**

An intersegment transfer through a gate involves four privilege level fields:

- The current privilege level (CPL) of the currently executing segment

- The requested privilege level (RPL) in the selector used in the CALL

- The DPL in the gate descriptor

- The DPL in the segment descriptor of the target executable segment

A transfer is valid only if the following relationships among privilege level numbers both hold:

Figure 2-9 illustrates both valid and invalid attempts to perform an interlevel transfer. Path E4,G5,E7 is not valid because the privilege level of gate G5 is numerically less than that of segment E4. Path E4,E8 is not valid because all interlevel transfers must pass through a gate. Path E4,G4,E6 is not valid because the privilege level of E6 is numerically greater than that of G4. Only paths E1,G2,E2; E1,G1,E3; and E2,G1,E3 satisfy the privilege rule above.

Figure 2-8. Gated Interlevel Call and Return

# **DESCRIPTOR TABLES**

A descriptor table is simply a segment containing an array of eight-byte entries, where each entry is a descriptor. Descriptors are stored in one of three classes of descriptor table:

- Local descriptor table (LDT)

- Global descriptor table (GDT)

- Interrupt descriptor table (IDT)

The descriptors in these tables define *all* the segments in the system. Each table has a variable upper limit, so the size of the table need be no larger than required for the actual number of segments used.

You define the initial contents of descriptor tables through the Builder. An operating system for dynamic applications may change the contents of descriptor tables and may create and delete LDT's as tasks come and go. Correct management of descriptors is the heart of protection on the iAPX 286.

Figure 2-9. Valid and Invalid Interlevel Transfers

# **Local Descriptor Table**

An LDT contains the descriptors that are private to a task. Each task may have an LDT. The LDT keeps the descriptors private to one task separate from those private to other tasks. A task cannot normally gain access to the segments defined by another task. A local descriptor table may contain any of the following types of descriptor:

- Data segment

- Executable segment

- Call gate

- · Task gate

The executable segment and data segment descriptors in an LDT normally refer to segments private to a task. Call gates and task gates in an LDT provide private entry points to other procedures and programs.

The processor uses a task's LDT automatically for certain addressing operations. The base address and limit of the LDT segment of the executing task are kept in the LDT register. Only two operations are available to programmatically change the contents of the LDT register:

- During a task switch operation, the processor loads the LDT register from the task state segment (TSS).

- The LLDT instruction loads the LDT register directly. The LLDT instruction can be executed only at privilege level 0 (PL 0). Initialization procedures use LLDT to give the LDT register its initial value. Note that if you change the LDT register you must also change the LDT selector in the TSS (refer to Chapter 4). An operating system may need to change the LDT register temporarily to gain access to the address space of another task when passing information between tasks.

You can use the SLDT instruction to read the contents of the LDT register. Operating-system procedures that operate on LDTs may usually be called from any task. These procedures may use the SLDT instruction to find which LDT belongs to the current task. In PL/M-286, the built-in variable LOCAL\$TABLE gives access to the LDT register.

An LDT may contain up to 8,192 descriptors (the number of 8-byte descriptors that fit into a maximum-sized segment of 65,536 bytes).

# **Global Descriptor Table**

Descriptors that are shared among tasks reside in the GDT. There is only one GDT for the entire system. The GDT can contain any of the following types of descriptor:

- Data segment

- Executable segment

- Task state segment

- Local descriptor table segment

- Call gate

- Task gate

## **USING HARDWARE PROTECTION FEATURES**

Since the GDT is shared among all tasks, its entries are usually protected. The privilege-level field in each descriptor provides this function. When operating-system functions are distributed among and shared by all tasks, the executable segments and data segments of the operating system are normally kept in the GDT. Call gates then provide controlled access to privileged operating system functions.

The processor uses the GDT automatically for certain addressing operations. The base address and limit of the GDT are kept in the processor's GDT register. Only the LGDT instruction (RESTORE\$GLOBAL\$TABLE in PL/M-286) can alter the contents of the GDT register, and the LGDT instruction can be executed only at PL 0 (i.e., by the operating system).

The SGDT instruction (SAVE\$GLOBAL\$TABLE in PL/M-286) reads the contents of the GDT register.

A GDT may contain up to 8,191 descriptors (the number of 8-byte descriptors that fit into a maximumsized segment of 65,536 bytes). The first entry cannot be used as a descriptor. (A null selector is identified by the fact that it refers to this first entry in the GDT.)

# **Interrupt Descriptor Table**

When processing an interrupt, the processor refers to the IDT to determine what interrupt-handling code to execute. Each interrupt is associated with an interrupt identifier, an integer that ranges from 0-255. The interrupt identifier is supplied either by the INT instruction or externally by the processor's INTA cycles. The interrupt identifier indexes an entry in the IDT. An IDT entry may be

- An interrupt gate

- A trap gate

- · A task gate

In a manner similar to executable segment and data segment descriptors, each gate descriptor has a descriptor privilege level. The DPL of a descriptor in the IDT determines the privilege required to execute an INT n instruction (where n is the interrupt indentifier that corresponds to the descriptor). This use of privilege levels prevents unauthorized programs from invoking interrupt handlers.

The processor locates the IDT by way of the IDT register. The IDT register can be changed only by the LIDT (load IDT) instruction (RESTORE\$INTERRUPT\$TABLE in PL/M-286). Only PL-0 procedures (i.e., the operating system) can execute an LIDT instruction.

The SIDT instruction (SAVE\$INTERRUPT\$TABLE in PL/M-286) reads the contents of the IDT register.

Refer to Chapters 6 and 7 for more detailed information on how the IDT is used.

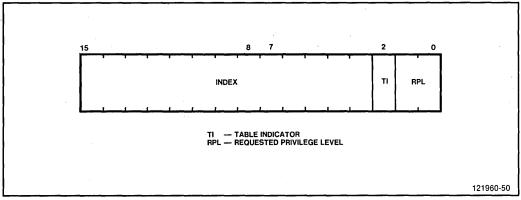

# **SELECTORS**

A selector references a segment indirectly by identifying the location in a descriptor table where a descriptor for that segment is stored.

## Format of Selector

See figure 2-10 for the format of a selector.

Figure 2-10. Format of a Selector

#### INDEX

The index field of a selector specifies a descriptor in either the GDT or the task's LDT. The index field may take on values from 0 through n-1, where n is the number of descriptors in the table. The processor compares the index with the limit of the descriptor table to ensure that the index refers to a defined descriptor.

## **TABLE INDICATOR**

This bit item tells which descriptor table is indexed by the selector. A value of zero specifies the GDT; one specifies the LDT. (The IDT cannot be referenced via a selector; only via an interrupt identifier.)

#### REQUESTED PRIVILEGE LEVEL

Selector privilege is specified in the RPL field of a selector. Selector RPL may establish a less trusted privilege level than the current privilege level for the use of that selector. RPL cannot effect an increase in privilege. A task's effective privilege level is the numeric maximum of the RPL and the current privilege level. For example, if a task is executing at PL = 2, an RPL = 3 reduces the task's effective privilege to level 3 for access to that segment. On the other hand, if RPL = 1, the task's effective privilege level remains at 2.

RPL is generally used by an operating system to ensure that selector parameters passed to the more privileged levels of the operating system do not give access to data at a level more privileged than the calling procedure. The RPL field is a convenient place to store the privilege level of the procedure that originated the selector. Any use of the selector can be restricted to the usage allowed its originator.

The ARPL instruction (ADJUST\$RPL built-in function in PL/M-286) allows the operating system to set the RPL of a selector either to CPL or to the privilege level of the originator, whichever is (numerically) larger. Refer to Chapter 13 for more information on the use of RPL.

#### **Null Selector**

A selector that has a value of zero in both the index and table indicator fields (i.e., appears to point to the first entry of the GDT) is a null selector. You can load such a selector into the DS or ES register, but any attempt to reference memory via that register causes an exception condition.

#### ALIAS DESCRIPTORS

The need arises in dynamic applications for the operating system to maintain more than one descriptor for a segment; however, care must be taken to preserve system integrity and protection.

As an example of the need for an alternate descriptor, consider the case of an executable segment. Ordinarily, the processor fetches instructions from an executable segment that is typed execute-only. However, if the operating system supports a debugger, the debugger needs to read the executable segment in order to display its contents. The debugger may also need to write to the executable segment in order to set breakpoints. If the debugger tries to use an execute-only segment descriptor to read from or write to the segment, the processor detects a protection exception. To properly use that segment, the debugger must use another descriptor that identifies the segment as a data segment. Figure 2-11 illustrates this situation.

The use of more than one descriptor for a segment is known as *aliasing*. Descriptors used in this way are known as *aliases*, because they provide alternate names for segments.

Figure 2-11. Aliasing for Debugger

# **Explicit Variation of Type**

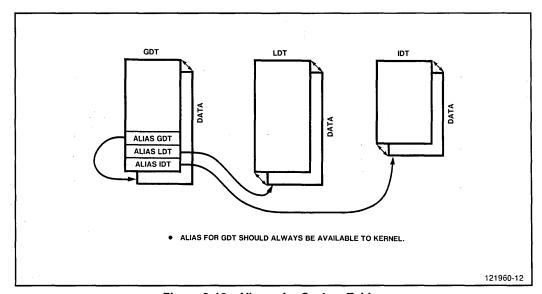

Figure 2-11 illustrates one kind of need for aliasing: the need for a different type specification for a segment. Figure 2-12 shows another example of the same need. In a dynamic application, the operating system may need to modify the GDT, the IDT, TSSs, and LDTs. Changing the interrupt handler for a specific interrupt vector requires changing the IDT. When the operating system places a new segment into the address space of a task (as, for example, when transferring an I/O buffer from an I/O task), it must update the task's LDT. Starting a new task may require modification of the GDT to add descriptors for the new task's LDT and TSS.

With the iAPX 286, however, it is not possible to read or write a system segment by loading its selector into DS or ES. This restriction prevents indiscriminate use of system segments within the operating system. Such use of a system segment requires that the operating system have a descriptor that identifies the system segment as a *data segment*.

The Builder allows for defining aliases for system segments. The Builder, by default, creates datasegment aliases for the GDT and the IDT at fixed locations in the GDT.

Note that aliases for descriptor tables should have PL 0 in order to maintain the integrity of the protection mechanism; otherwise, procedures outside the operating system could indiscriminately change the contents of descriptor tables.

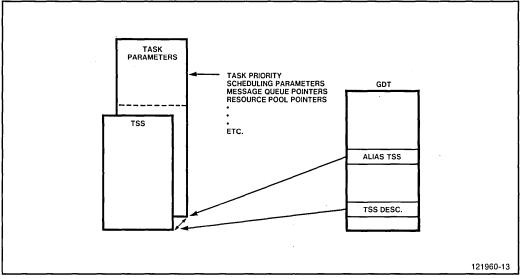

# Variation of Length

As illustrated in figure 2-13, aliases for a segment need not always have the same length. In the case shown, the processor's use of a descriptor to a TSS requires only that the segment contain 44 bytes. However, the operating system maintains another descriptor that includes additional information about the task.

Figure 2-12. Aliases for System Tables

2-18 121960-001

Figure 2-13. Aliases with Differing Limit

# **Sharing Segments among Tasks**

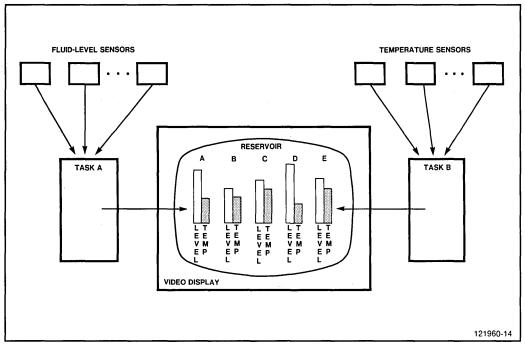

Yet another reason for using aliases is the need for sharing a segment among tasks. Consider an application in which a memory-mapped video display shows status information for a production process. In this application, there are two tasks, each monitoring different aspects of the process but interleaving data on the display (see figure 2-14). Figure 2-15 illustrates how both tasks can access the memory segment containing the display buffer.

You can find segment sharing needs of this sort in both static and dynamic systems. Note that there are other techniques for segment sharing that do not use aliases; for example, placing the segment's descriptor in the GDT, or permitting tasks to share a single LDT. The aliasing technique illustrated here has the advantages that

- No other tasks have access to the display buffer. (Putting its descriptor in the GDT makes it available to all other tasks.)

- Other segments in each of the tasks remain protected from the other task. (With a shared LDT, all segments of each task are accessible from the other.)

# Protection and Integrity with Aliasing

You must use aliases with care; improper use can compromise the protection and integrity of your system.

2-19 121960-001

Figure 2-14. Application of Segment Sharing

## CONTROL ACCESS TO ALIASES

When you use an alias to provide an alternate type for a system segment (to write to an LDT), any procedure that has access to that alias also has unlimited power to affect the entire system. Therefore, in constructing an operating system that uses such aliases, you must restrict them to the highest privilege levels of the operating system; that is, the DPL of such aliases should always be zero.

# PLAN FOR CHANGE

When you design a dynamic system that uses aliases for segment sharing, you must consider what will happen when there is any change in a segment to which aliases are pointing. For example, when a segment is relocated, all descriptors pointing to the relocated segment must be updated. When a segment is deleted, all aliases to it must be nullified. Chapter 5 presents a strategy for handling these changes.

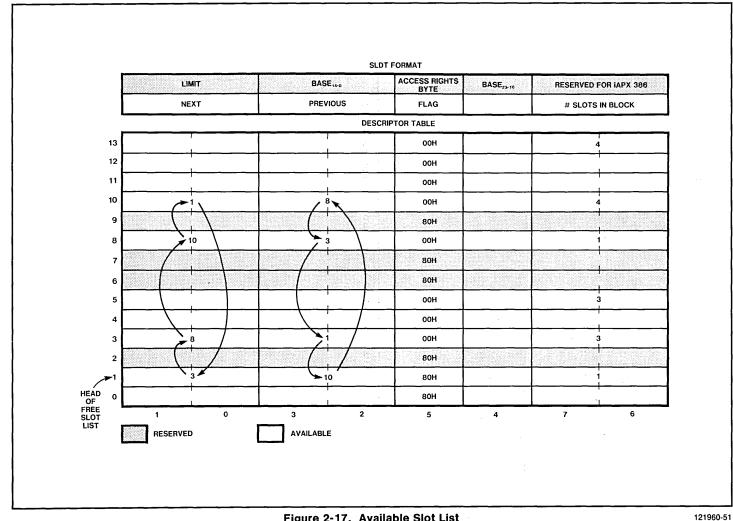

# **EXAMPLE OF DESCRIPTOR MANIPULATION**

As an example of how to manipulate descriptors and descriptor tables using an alias, consider the procedures POINT\_AT and NULLIFY in figure 2-16. POINT\_AT creates a descriptor at a given slot in the GDT. NULLIFY invalidates a descriptor in the GDT. It is intended for use in connection with POINT\_AT to prevent accidental use of descriptors that are no longer needed.

2-20 121960-001

Figure 2-15. Aliases for Segment Sharing

NULLIFY invalidates a descriptor by writing a value of 80H in the access rights byte. A value of 80H is invalid because it indicates a system segment of type zero, but no type zero is defined for system segments.

POINT\_AT purposely loads the access rights byte of the descriptor last, to ensure that an accidental use of the descriptor (as might occur if an external interrupt gives control to another procedure or task) does not find partially complete information in a descriptor that otherwise looks valid.

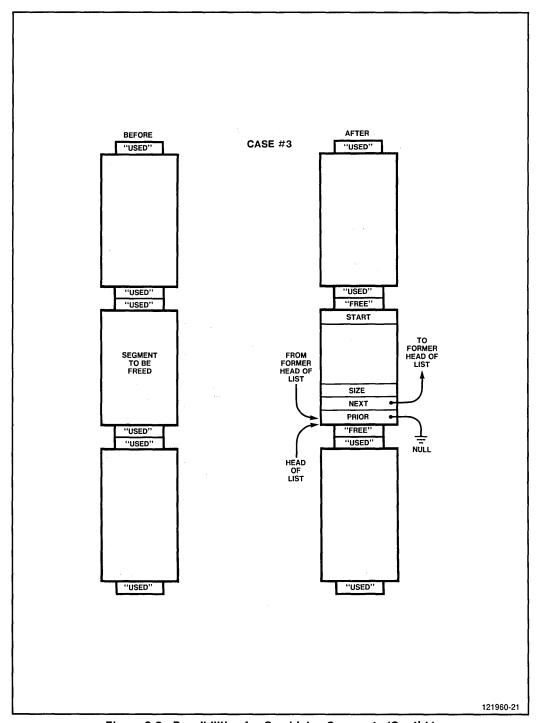

These procedures do no checking of the privilege level of the calling procedure, and they freely create descriptors of any type (except gate descriptors) and any DPL. Therefore, they are suitable for use only at PL 0. As long as no gates for these procedures are provided at another privilege level, they can be called only by other PL-0 procedures. For an example of how you might use such procedures, refer to the example of a memory manager in Chapter 3.