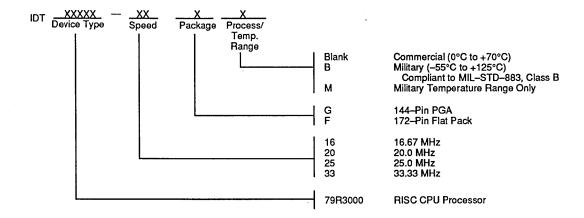

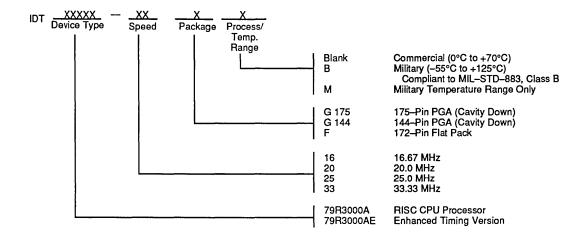

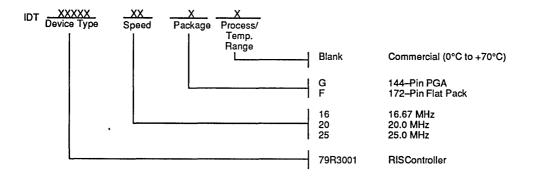

# 1991 IDT RISC R3000A, R3001, R3051<sup>™</sup> Family Product Information

Integrated Device Technology, Inc.

# 1991 IDT RISC R3000A, R3001, R3051<sup>™</sup> Family Product Information

Integrated Device Technology, Inc.

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- expected to result in a significant injury to the user.

A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

# 1991 IDT RISC R3000A, R3001, R3051 Family Product Information

# TABLE OF CONTENTS

| IDT79R3000                     | RISC CPU Processor                                | 1   |

|--------------------------------|---------------------------------------------------|-----|

| IDT79R3000A<br>IDT79R3000AE    | RISC CPU Processor                                | 25  |

| IDT79R3001                     | RISController™                                    | 53  |

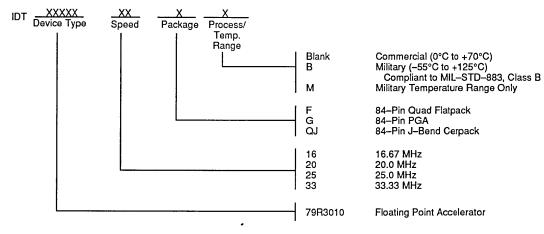

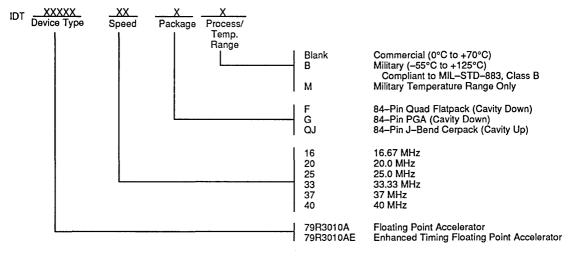

| IDT79R3010                     | RISC Floating-Point Accelerator (FPA)             | 83  |

| IDT79R3010A<br>IDT79R3010AE    | RISC Floating-Point Accelerator (FPA)             | 100 |

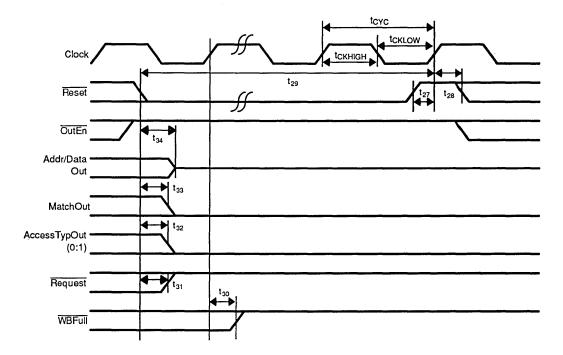

| IDT79R3020                     | RISC CPU Write Buffer 1                           | 123 |

| IDT79R3051™/E<br>IDT79R3052™/E | IDT79R3051 Family of Integrated RISControllers™ 1 | 41  |

| Package Informatio             | on 1                                              | 153 |

# **RISC CPU PROCESSOR**

Integrated Device Technology, Inc.

# FEATURES:

- Enhanced instruction set compatible version of the IDT79R2000 RISC CPU.

- Full 32-bit Operation—Thirty-two 32-bit registers and all instructions and addresses are 32-bit.

- Efficient Pipelining—The CPU's 5-stage pipeline design assists in obtaining an execution rate approaching one instruction per cycle. Pipeline stalls and exceptions are handled precisely and efficiently.

- On-Chip Cache Control—The IDT79R3000 provides a high bandwidth memory interface that handles separate external Instruction and Data Caches ranging in size from 4 to 256 Kbytes each. Both the caches are accessed during a single CPU cycle. All cache control is on-chip.

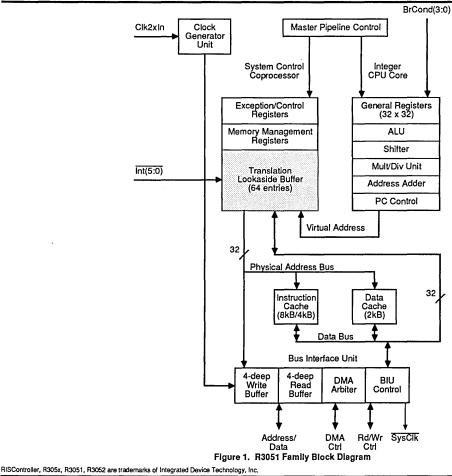

- On-Chip Memory Management Unit—A fully-associative, 64 entry Translation Lookaside Buffer (TLB) provides fast address translation for virtual-to-physical memory mapping of the 4 Gigabyte virtual address space.

- Coprocessor Interface—The IDT79R3000 generates all addresses and handles memory interface control for up to three additional tightly coupled external processors.

- Optimizing Compilers are available for C, Fortran, Pascal, COBOL, Ada, and PL/1.

- UNIX<sup>TM</sup> System V.3 and BSD 4.3 operating systems supported.

- High-speed CEMOS<sup>™</sup> technology.

- Instruction set compatible with the IDT79R2000 RISC CPU.

- 16.7MHz, 20MHz, 25MHz and 33MHz clock rates yield up to 28 MIPS sustained throughput.

- Supports independent multiword block refill of both the instruction and data caches with variable block sizes.

- Supports concurrent refill and execution of instructions.

- Partial word stores executed as read-modify-write operations.

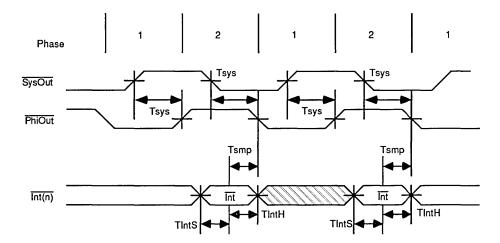

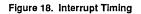

- 6 external interrupt inputs (up to 64 different sources), 2 software interrupts, with single cycle latency to exception handler routine.

- Flexible multiprocessing support on chip with no impact on uniprocessor designs.

- · Military product compliant to MIL-STD-883, Class B.

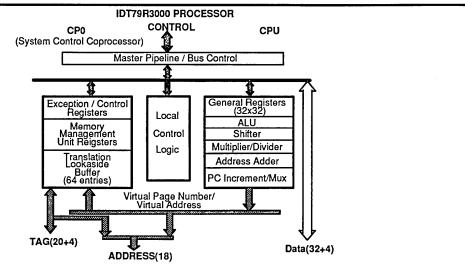

# **DESCRIPTION:**

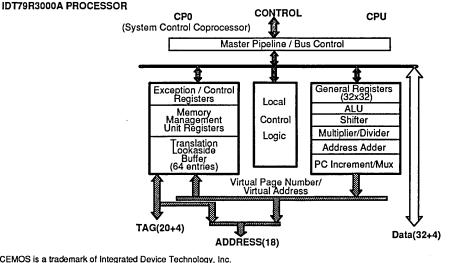

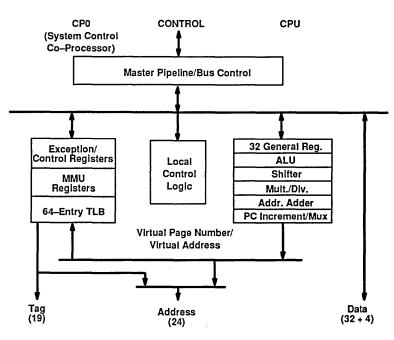

The IDT 79R3000 RISC Microprocessor consists of two tightlycoupled processors integrated on a single chip. The first processor is a full 32-bit CPU based on RISC (Reduced Instruction Set Computer) principles to achieve a new standard of microprocessor performance. The second processor is a system control coprocessor, called CP0, containing a fully-associative 64 entry TLB (Translation Lookaside Buffer), MMU (Memory Management Unit) and control registers, supporting a 4 Gigabyte virtual memory subsystem, and a Harvard Architecture Cache Controller achieving a bandwidth of over 260 Mbytes/second using industry standard static RAMs.

This data sheet provides an overview of the features and architecture of the 79R3000 CPU, Revision 2.0. A more detailed description of the operation of the device is incorporated in the "R3000 Family Hardware User Manual", and a more detailed architectural overview is provided in the "mips RISC Architecture" book, both available from IDT. Documentation providing details of the software and development environments supporting this processor are also available from IDT.

CEMOS is a trademark of Integrated Device Technology, Inc. UNIX is a registered trademark of AT&T.

## MILITARY AND COMMERCIAL TEMPERATURE RANGES

### IDT79R3000 CPU Registers

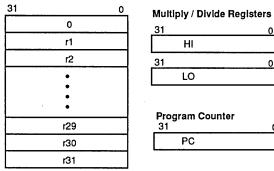

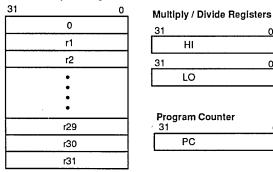

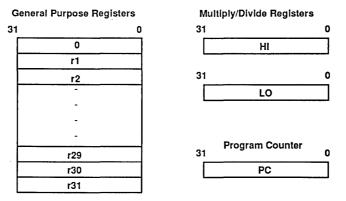

The IDT 79R3000 CPU provides 32 general purpose 32-bit registers, a 32-bit Program Counter, and two 32-bit registers that hold the results of integer multiply and divide operations. Only two of the 32 general registers have a special purpose: register r0 is hardwired to the value "0", which is a useful constant, and register r31 is used as the link register in jump-and-link instructions (return address for subroutine calls).

The CPU registers are shown in Figure 2. Note that there is no Program Status Word (PSW) register shown in this figure: the functions traditionally provided by a PSW register are instead provided in the *Status* and *Cause* registers incorporated within the System Control Coprocessor (CP0).

### General Purpose Registers

Figure 2. IDT79R3000 CPU Registers

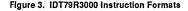

#### Instruction Set Overview

All IDT 79R3000 instructions are 32 bits long, and there are only three instruction formats. This approach simplifies instruction decoding thus minimizing instruction execution time. The 79R3000 processor initiates a new instruction on every run cycle, and is able to complete an instruction on almost every clock cycle. The only exceptions are the Load instructions and Branch instructions, which each have a single cycle of latency associated with their execution. Note, however, that in the majority of cases the compilers are able to fill these latency cycles with useful instructions which do not require the result of the previous instruction. This effectively eliminates these latency effects.

The actual instruction set of the CPU was determined after extensive simulations to determine which instructions should be implemented in hardware, and which operations are best synthesized in software from other basic instructions. This methodology resulted in the R3000 having the highest performance of any available microprocessor.

#### I-Type (Immediate)

|            | F - 4   | ···· ,   |       |        |         |       |

|------------|---------|----------|-------|--------|---------|-------|

| 31         | 26      | 25 21    | 20 16 | 15     |         | 0     |

|            | ор      | rs       | rt    | i      | mmediat | e     |

|            | ype (Ju | • •      |       |        |         |       |

| 3 <u>1</u> | 26      | 25       |       |        |         | 0     |

|            | ор      |          |       | target |         |       |

| R-T        | ype (Re | egister) |       |        |         |       |

| 31         | 26      | 25 21    | 20 16 | 15 11  | 10 6    | 50    |

|            | ор      | rs       | rt    | rd     | re      | funct |

The IDT79R3000 instruction set can be divided into the following groups:

Load/Store instructions move data between memory and general registers. They are all I-type instructions, since the only addressing mode supported is base register plus 16-bit, signed immediate offset.

The Load instruction has a single cycle of latency, which means that the data being loaded is not available to the instruction immediately after the load instruction. The compiler will fill this delay slot with either an instruction which is not dependent on the loaded data, or with a NOP instruction. There is no latency associated with the store instruction.

Loads and Stores can be performed on byte, half-word, word, or unaligned word data (32 bit data not aligned on a modulo-4 address). The CPU cache is constructed as a write-through cache.

Computational instructions perform arithmetic, logical and shift operations on values in registers. They occur in both R-type (both operands and the result are registers) and I-type (one operand is a 16-bit immediate) formats.

Note that computational instructions are three operand instructions; that is, the result of the operation can be stored into a different register than either of the two operands. This means that operands need not be overwritten by arithmetic operations. This results in a more efficient use of the large register set.

- Jump and Branch instructions change the control flow of a program. Jumps are always to a paged absolute address formed by combining a 26-bit target with four bits of the Program counter (J-type format, for subroutine calls), or 32-bit register byte addresses (R-type, for returns and dispatches). Branches have 16-bit offsets relative to the program counter (I-type). Jump and Link instructions save a return address in Register 31. The 79R3000 instruction set features a number of branch conditions. Included is the ability to compare a register to zero and branch, and also the ability to branch based on a comparison between two registers. Thus, net performance is increased since software does not have to perform arithmetic instructions prior to the branch to set up the branch conditions.

- Coprocessor instructions perform operations in the coprocessors. Coprocessor Loads and Stores are I-type. Coprocessor computational instructions have coprocessordependent formats (see coprocessor manuals).

- Coprocessor 0 instructions perform operations on the System Control Coprocessor (CP0) registers to manipulate the memory management and exception handling facilities of the processor.

- Special instructions perform a variety of tasks, including movement of data between special and general registers, system calls, and breakpoint. They are always R-type.

Table 1 lists the instruction set of the IDT79R3000 processor.

0

### IDT79R3000 RISC CPU PROCESSOR

| OP                             | DESCRIPTION                                                                                                                        | ОР                                    | DESCRIPTION                                                                                                                                         |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | Load/Store Instructions                                                                                                            |                                       | Multiply/Divide Instructions                                                                                                                        |

| LB<br>LBU<br>LH<br>LHU         | Load Byte<br>Load Byte Unsigned<br>Load Halfword<br>Load Halfword Unsigned                                                         | MULT<br>MULTU<br>DIV<br>DIVU          | Multiply<br>Multiply Unsigned<br>Divide<br>Divide Unsigned                                                                                          |

| LHO<br>LW<br>LWL<br>LWR        | Load Word<br>Load Word<br>Load Word Left<br>Load Word Right                                                                        | MFHI<br>MTHI<br>MFLO                  | Move From HI<br>Move To HI<br>Move To HI                                                                                                            |

| SB<br>SH<br>SW<br>SWL<br>SWR   | Store Byte<br>Store Halfword<br>Store Word<br>Store Word Left<br>Store Word Right                                                  | MTLO<br>J<br>JAL                      | Move To LO<br>Jump and Branch Instructions<br>Jump<br>Jump and Link                                                                                 |

|                                | Arithmetic Instructions                                                                                                            | JR<br>JALR<br>BEQ                     | Jump to Register<br>Jump and Link Register<br>Branch on Equal                                                                                       |

| ADDI<br>ADDIU<br>SLTI<br>SLTIU | (ALU Immediate)<br>Add Immediate<br>Add Immediate Unsigned<br>Set on Less Than Immediate<br>Set on Less Than Immediate<br>Unsigned | BNE<br>BLEZ<br>BGTZ<br>BLTZ<br>BGEZ   | Branch on Not Equal<br>Branch on Less than or Equal to Zero<br>Branch on Greater Than Zero<br>Branch on Less Than Zero<br>Branch on Greater than or |

| ANDI<br>ORI<br>XORI<br>LUI     | AND Immediate<br>OR Immediate<br>Exclusive OR Immediate<br>Load Upper Immediate                                                    | BLTZAL<br>BGEZAL                      | Equal to Zero<br>Branch on Less Than Zero and Link<br>Branch on Greater than or Equal to<br>Zero and Link                                           |

| ADD                            | Arithmetic Instructions<br>(3–operand, register–type)<br>Add                                                                       | SYSCALL<br>BREAK                      | Special Instructions<br>System Call<br>Break                                                                                                        |

| ADD                            | Add<br>Add Unsigned                                                                                                                |                                       | <b>Coprocessor Instructions</b>                                                                                                                     |

| SUB<br>SUBU                    | Subtract<br>Subtract Unsigned                                                                                                      | LWCz<br>SWCz                          | Load Word from Coprocessor<br>Store Word to Coprocessor<br>Move To Coprocessor                                                                      |

| SLT<br>SLTU                    | Set on Less Than<br>Set on Less Than Unsigned                                                                                      | MTCz<br>MFCz<br>CTCz                  | Move From Coprocessor<br>Move Control to Coprocessor<br>Move Control to Coprocessor                                                                 |

| AND<br>OR<br>XOR<br>NOR        | AND<br>OR<br>Exclusive OR<br>NOR                                                                                                   | CFCz<br>COPz<br>BCzT<br>BCzF          | Move Control From Coprocessor<br>Coprocessor Operation<br>Branch on Coprocessor z True<br>Branch on Coprocessor z False                             |

| SLL                            | Shift Instructions<br>Shift Left Logical                                                                                           |                                       | System Control Coprocessor<br>(CP0) Instructions                                                                                                    |

| SRL<br>SRA                     | Shift Right Logical<br>Shift Right Arithmetic                                                                                      | MTC0<br>MFC0                          | Move To CP0<br>Move From CP0                                                                                                                        |

| SLLV<br>SRLV<br>SRAV           | Shift Left Logical Variable<br>Shift Right Logical Variable<br>Shift Right Arithmetic Variable                                     | TLBR<br>TLBWI<br>TLBWR<br>TLBP<br>BFE | Read indexed TLB entry<br>Write Indexed TLB entry<br>Write Random TLB entry<br>Probe TLB for matching entry<br>Restore From Exception               |

Table 1. IDT79R3000 Instruction Summary

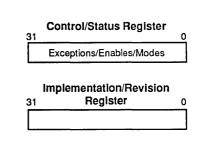

### IDT79R3000 System Control Coprocessor (CP0)

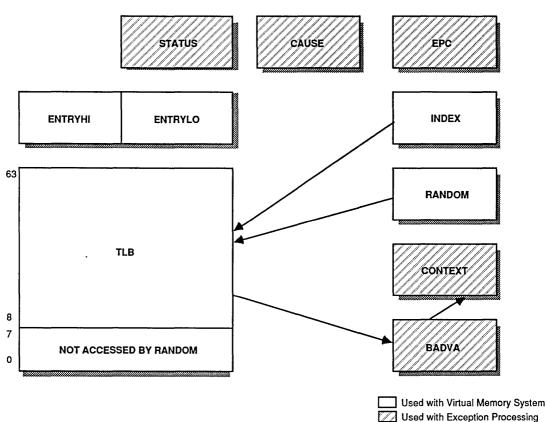

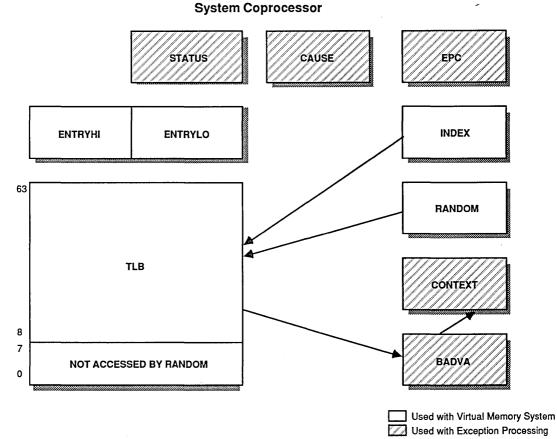

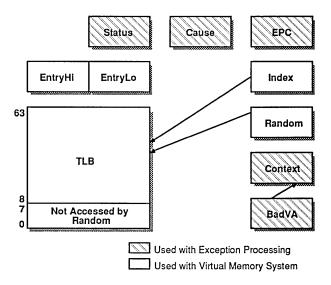

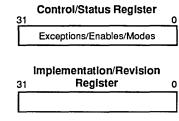

The IDT79R3000 can operate with up to four tightly-coupled coprocessors (designated CP0 through CP3). The System Control Coprocessor (or CP0), is incorporated on the IDT79R3000 chip and supports the virtual memory system and exception handling functions of the IDT79R3000. The virtual memory system is implemented using a Translation Lookaside Buffer and a group of programmable registers as shown in Figure 4.

# System Coprocessor

Figure 4. The System Coprocessor Registers

# System Control Coprocessor (CP0) Registers

The CP0 registers shown in Figure 4 are used to control the memory management and exception handling capabilities of the IDT79R3000. Table 2 provides a brief description of each register.

| REGISTER                                   | DESCRIPTION                                                                                                                                                                                                       |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EntryHi<br>EntryLo                         | High half of a TLB entry<br>Low half of a TLB entry                                                                                                                                                               |

| Index                                      | Programmable pointer into TLB array                                                                                                                                                                               |

| Random                                     | Pseudo-random pointer into TLB array                                                                                                                                                                              |

| Status<br>Cause<br>EPC<br>Context<br>BadVA | Mode, interrupt enables, and diagnostic status info<br>Indicates nature of last exception<br>Exception Program Counter<br>Pointer into kernel's virtual Page Table Entry array<br>Most recent bad virtual address |

| PRId                                       | Processor revision identification (Read only)                                                                                                                                                                     |

### Table 2. System Control Coprocessor (CP0) Registers

#### IDT79R3000 RISC CPU PROCESSOR

### Memory Management System

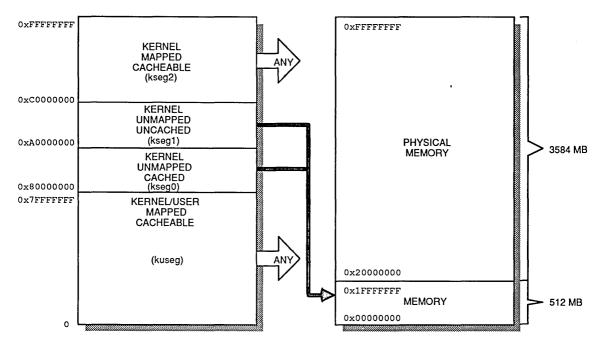

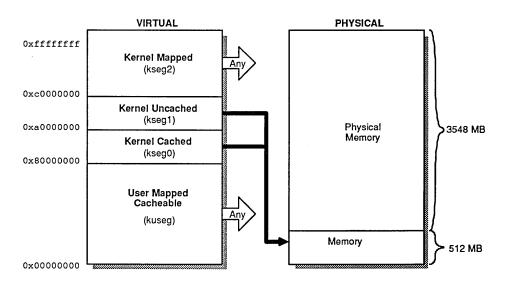

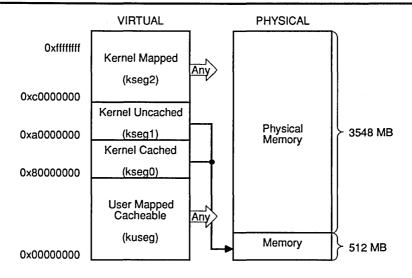

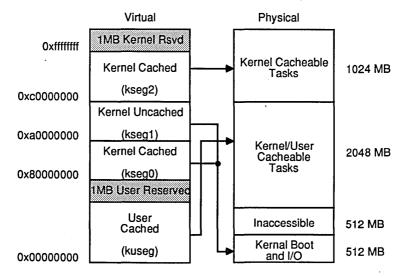

The IDT79R3000 has an addressing range of 4 Gbytes. However, since most IDT79R3000 systems implement a physical memory smaller than 4 Gbytes, the IDT79R3000 provides for the logical expansion of memory space by translating addresses composed in a large virtual address space into available physical memory address. The 4 GByte address space is divided into 2 GBytes which can be accessed by both the users and the kernel, and 2 GBytes for the kernel only.

### The TLB (Translation Lookaside Buffer)

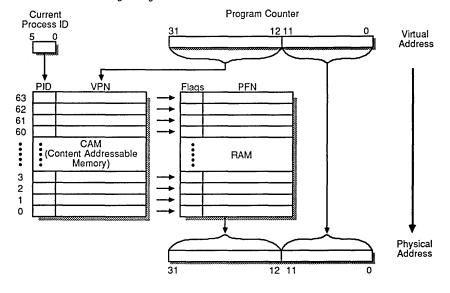

Virtual memory mapping is assisted by the Translation Lookaside Buffer (TLB). The on-chip TLB provides very fast virtual memory access and is well-matched to the requirements of multitasking operating systems. The fully-associative TLB contains 64 entries, each of which maps a 4-Kbyte page, with controls for read/write access, cacheability, and process identification. The TLB allows each user to access up to 2 Gbytes of virtual address space.

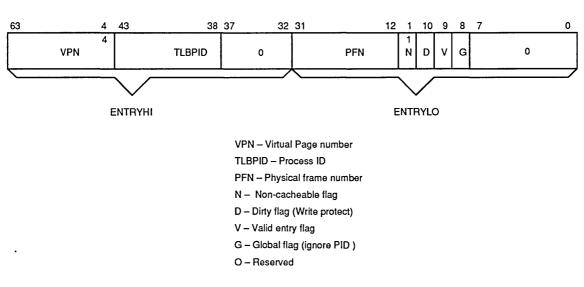

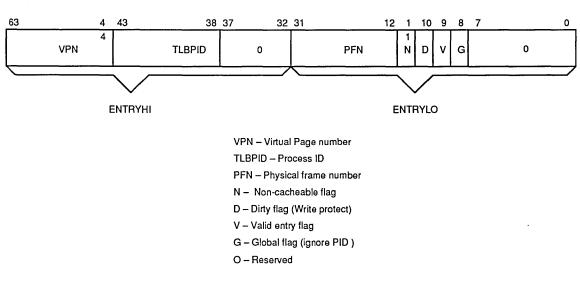

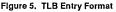

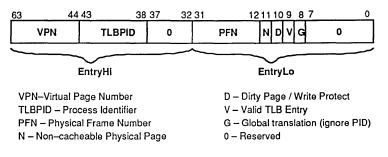

Figure 5 illustrates the format of each TLB entry. The Translation operation involves matching the current Process ID (PID) and upper 20 bits of the address against PID and VPN (Virtual Page Number) fields in the TLB. When both match (or the TLB entry is Global), the VPN is replaced with the PFN (Physical Frame Number) to form the physical address.

TLB misses are handled in software, with the entry to be replaced determined by a simple RANDOM function. The routine to process a TLB miss in the UNIX environment requires only 10–12 cycles, which compares favorably with many CPUs which perform the operation in hardware.

### IDT79R3000 Operating Modes

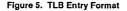

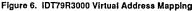

The IDT79R3000 has two operating modes: User mode and Kernelmode. The IDT79R3000 normally operates in the User mode until an exception is detected forcing it into the Kernel mode. It remains in the Kernel mode until a Restore From Exception (RFE) instruction is executed. The manner in which memory addresses are translated or *mapped* depends on the operating mode of the IDT79R3000. Figure 6 shows the MMU translation performed for each of the operating modes.

### TLB ENTRY FORMAT

MMU ADDRESS TRANSLATION VIRTUAL -> PHYSICAL

User Mode—in this mode, a single, uniform virtual address space (kuseg) of 2 Gbyte is available. Each virtual address is extended with a 6-bit process identifier field to form unique virtual addresses. All references to this segment are mapped through the TLB. Use of the cache for up to 64 processes is determined by bit settings for each page within the TLB entries.

Kernel Mode-four separate segments are defined in this mode:

- kuseg—when in the kernel mode, references to this segment are treated just like user mode references, thus streamlining kernel access to user data.

- kseg0—references to this 512 Mbyte segment use cache memory but are not mapped through the TLB. Instead, they always map to the first 0.5 GBytes of physical address space.

- kseg1—references to this 512 Mbyte segment are not mapped through the TLB and do not use the cache. Instead, they are hard-mapped into the same 0.5 GByte segment of physical address space as kseg0.

- kseg2—references to this 1 Gbyte segment are always mapped through the TLB and use of the cache is determined by bit settings within the TLB entries.

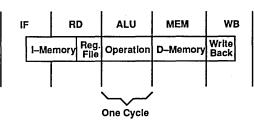

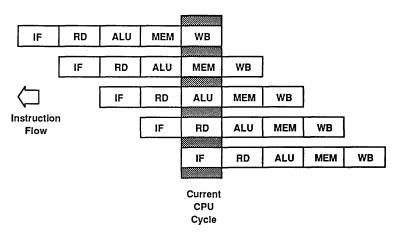

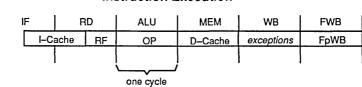

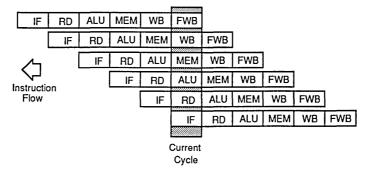

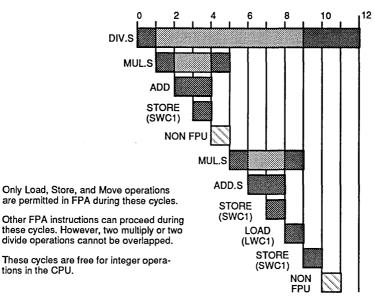

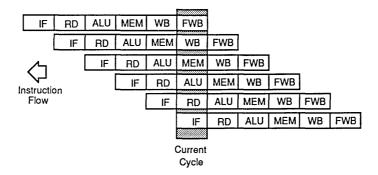

#### IDT79R3000 Pipeline Architecture

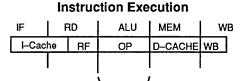

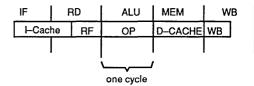

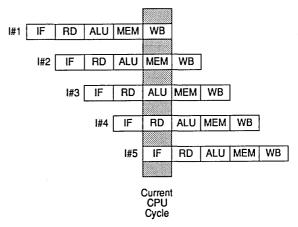

The execution of a single IDT79R3000 instruction consists of five primary steps:

- 1) IF Fetch the instruction (I-Cache).

- 2) RD Read any required operands from CPU registers while decoding the instruction.

- 3) ALU Perform the required operation on instruction operands.

- 4) MEM-Access memory (D-Cache).

- 5) WB --- Write back results to register file.

Each of these steps requires approximately one CPU cycle as shown in Figure 7 (parts of some operations overlap into another cycle while other operations require only 1/2 cycle).

one cycle

Figure 7. IDT79R3000 Instruction Pipeline

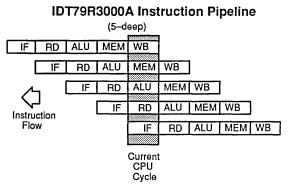

The IDT79R3000 uses a 5-stage pipeline to achieve an instruction execution rate approaching one instruction per CPU cycle. Thus, execution of five instructions at a time are overlapped as shown in Figure 8.

Figure 8. IDT79R3000 Execution Sequence

This pipeline operates efficiently because different CPU resources (address and data bus accesses, ALU operations, register accesses, and so on) are utilized on a non-interfering basis.

#### Memory System Hierarchy

The high performance capabilities of the IDT79R3000 processor demand system configurations incorporating techniques frequently employed in large, mainframe computers but seldom encountered in systems based on more traditional microprocessors.

A primary goal of systems employing RISC techniques is to minimize the average number of cycles each instruction requires for execution. In order to achieve this goal, RISC processors incorporate a number of RISC techniques including a compact and uniform instruction set, a deep instruction pipeline (as described above), and utilization of optimizing compilers. Many of the advantages obtained from these techniques can, however, be negated by an inefficient memory system.

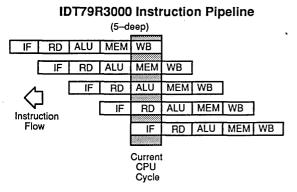

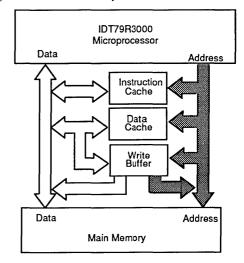

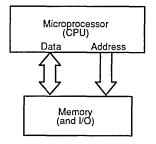

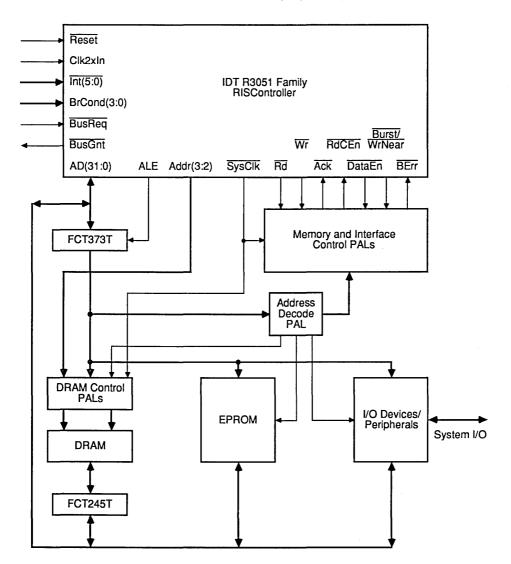

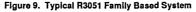

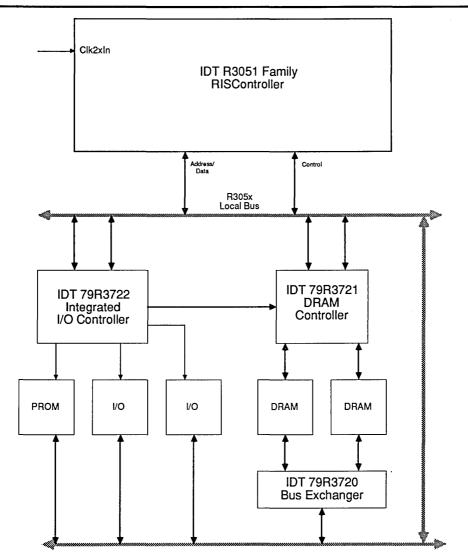

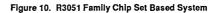

Figure 9 illustrates memory in a simple microprocessor system. In this system, the CPU outputs addresses to memory and reads instructions and data from memory or writes data to memory. The address space is completely undifferentiated: instructions, data, and I/O devices are all treated the same. In such a system, a primary limiting performance factor is memory bandwidth.

Figure 9. A Simple Microprocessor Memory System

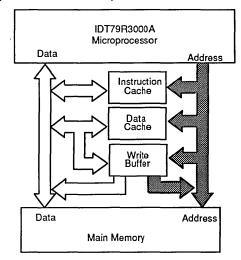

Figure 10 illustrates a memory system that supports the significantly greater memory bandwidth required to take full advantage of the IDT79R3000's performance capabilities. The key features of this system are:

- External Cache Memory—Local, high-speed memory (called cache memory) is used to hold instructions and data that is repetitively accessed by the CPU (for example, within a program loop) and thus reduces the number of references that must be made to the slower-speed main memory. Some microprocessors provide a limited amount of cache memory on the CPU chip itself. The external caches supported by the IDT79R3000 can be much larger; while a small cache can improve performance of some programs, significant improvements for a wide range of programs require large caches.

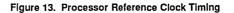

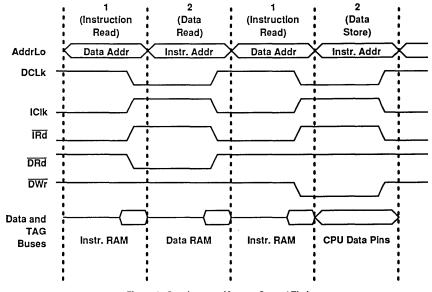

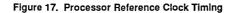

- Separate Caches for data and instructions—Even with high-speed caches, memory speed can still be a limiting factor because of the fast cycle time of a high-performance microprocessor. The IDT79R3000 supports separate caches for instructions and data and alternates accesses of the two caches during each CPU cycle. Thus, the processor can obtain data and instructions at the cycle rate of the CPU using caches constructed with commercially available IDT static RAM devices.

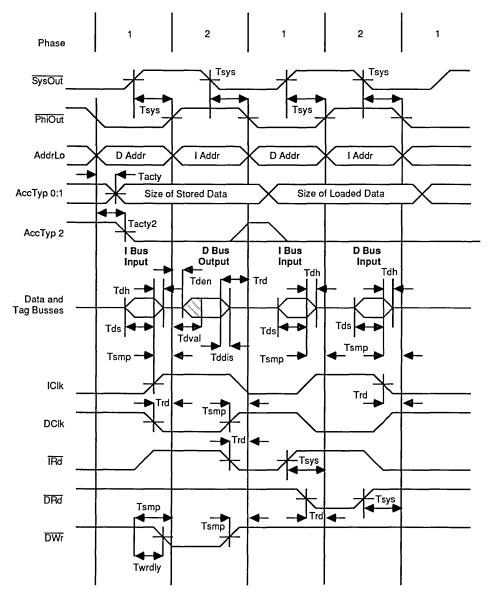

In order to maximize bandwidth in the cache while minimizing the requirement for SRAM access speed, the R3000 divides a single-processor clock cycle into two phases. During one phase, the address for the data cache access is presented while data previously addressed in the instruction cache is read; during the next phase, the data operation is completed while the instruction cache is being addressed. Thus, both caches are read in a single processor cycle using only one set of address and data pins.

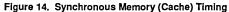

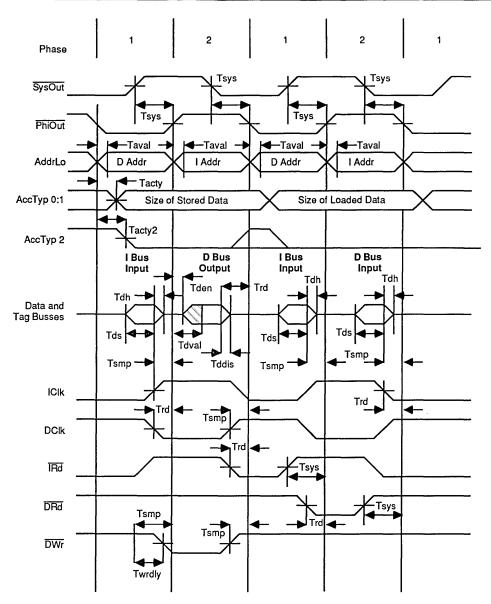

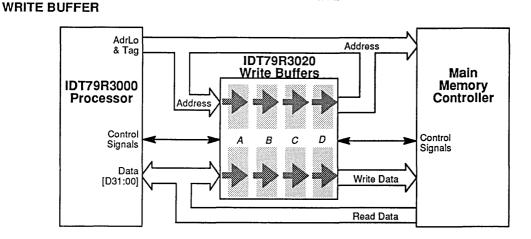

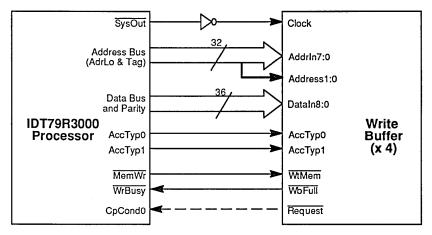

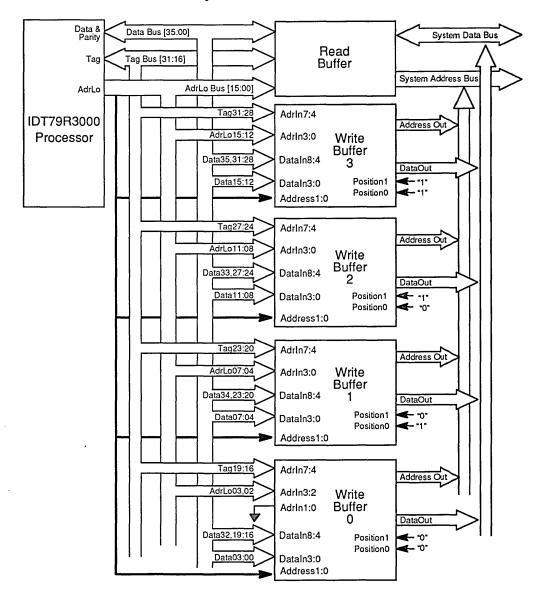

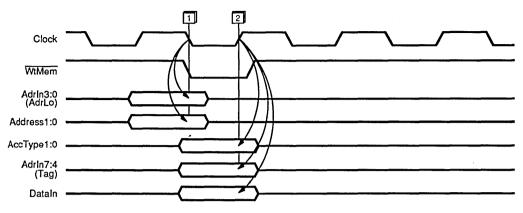

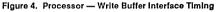

Write Buffer—In order to ensure data consistency, all data that is written to the data cache must also be written out to main memory. The cache write model used by the IDT79R3000 is that of a write-through cache; that is, all data written by the CPU is immediately written into the main memory. To relieve the CPU of this responsibility (and the inherent performance burden) the IDT79R3000 supports an interface to a write buffer. The IDT79R3020 Write Buffer captures data (and associated addresses) output by the CPU and ensures that the data is passed on to main memory.

Figure 10. An IDT79R3000 System with a High-Performance Memory System

#### IDT79R3000 Processor Subsystem Interfaces

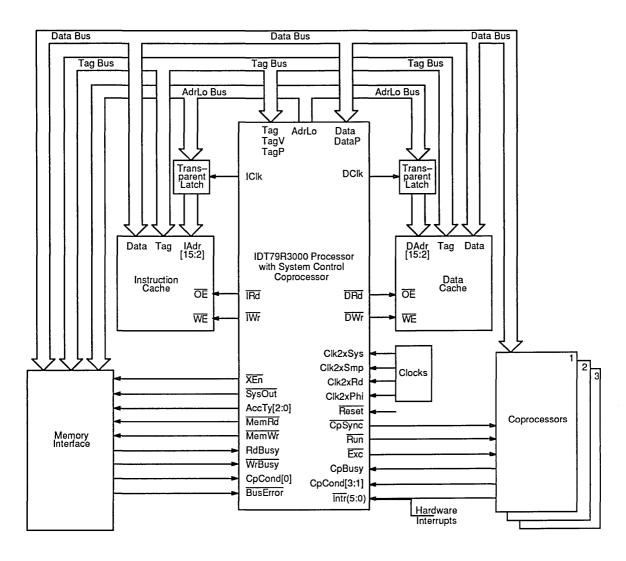

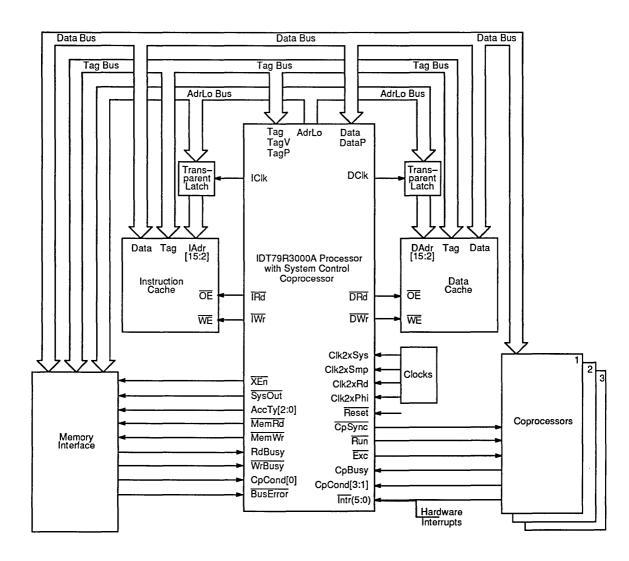

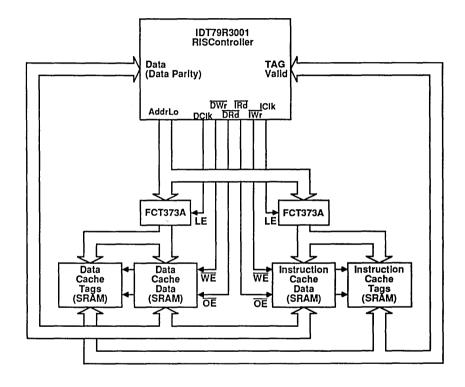

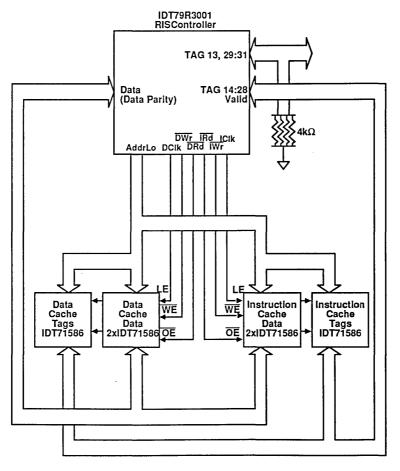

Figure 11 illustrates the three subsystem interfaces provided by the IDT79R3000 processor:

Cache control interface (on-chip) for separate data and instruction caches permits implementation of off-chip caches using standard IDT SRAM devices. The 79R3000 directly controls the cache memory with a minimum of external components. Both the instruction and data cache can vary from 0 to 256K Bytes (64 K entries). The 79R3000 also includes the TAG control logic which determines whether or not the entry read from the cache is the desired data.

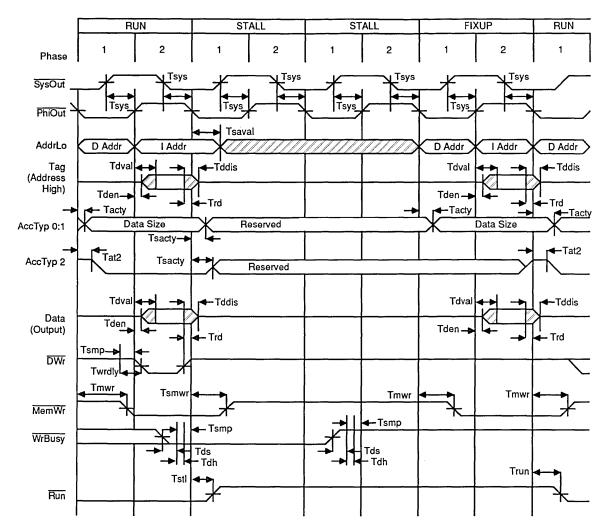

The 79R3000 cache controller implements a direct mapped cache for high net performance (bandwidth). It has the ability to refill multiple words when a cache miss occurs, thus reducing the effective miss rate to less than 2% for large caches. When a cache miss occurs, the 79R3000 can support refilling the cache in 1, 4, 8, 16, or 32 word blocks to minimize the effective penalty of having to access main memory. The 79R3000 also incorporates the ability to perform instruction streaming; while the cache is refilling, the processor can resume execution once the missed word is obtained from main memory. In this way, the processor can continue to execute concurrently with the cache block refill.

- Memory controller interface for system (main) memory. This

interface also includes the logic and signals to allow operation

with a write buffer to further improve memory bandwidth. In

addition to the standard full word access, the memory controller

supports the ability to write bytes and half-words by using partial

word operations. The memory controller also supports the

ability to retry memory accesses if, for example, the data

returned from memory is invalid and a bus error needs to be

signalled.

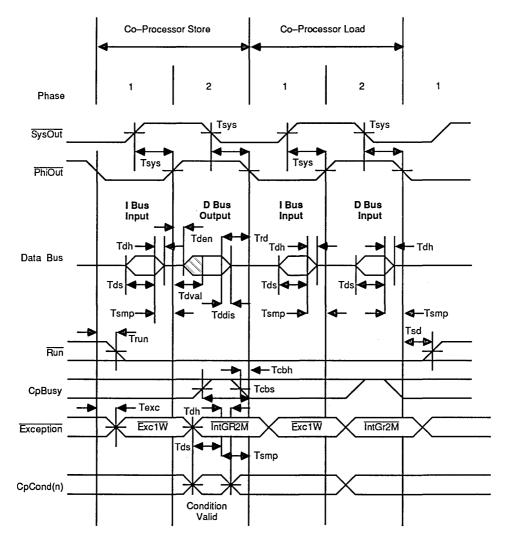

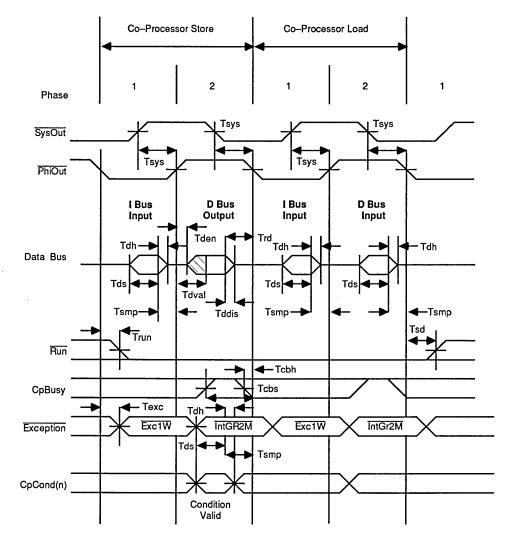

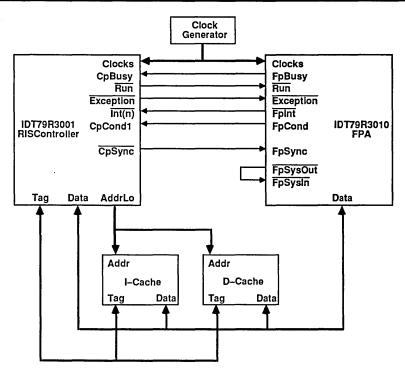

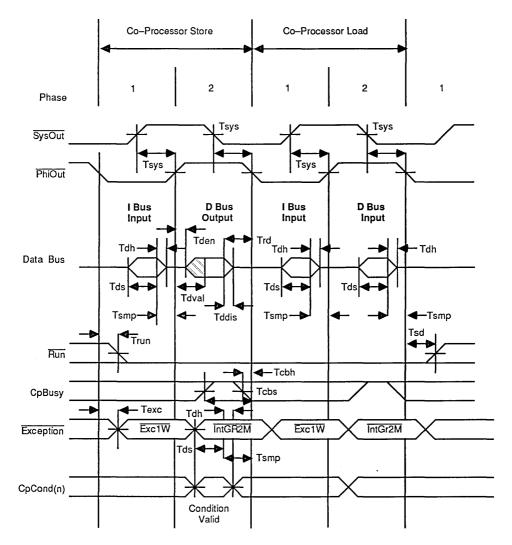

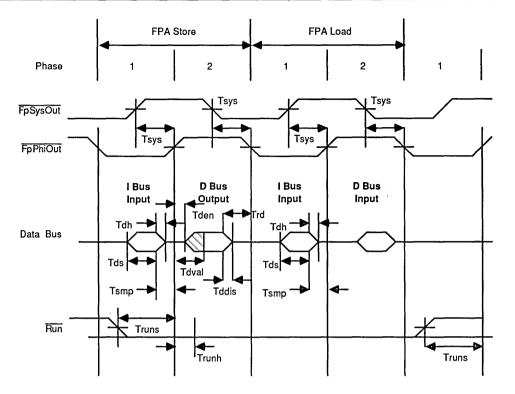

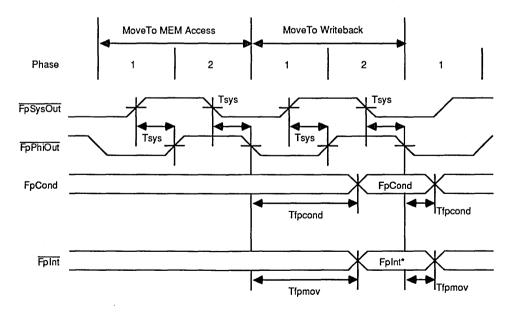

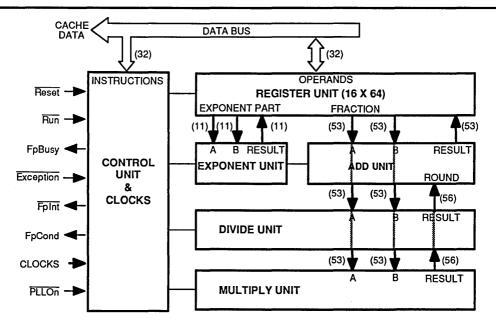

- Coprocessor Interface—The IDT79R3000 features a tightly coupled co-processor interface in which all co-processors maintain synchronization with the main processor; reside on the same data bus as the main processor; and participate in bus transactions in an identical manner to the main processor. The IDT79R3000 generates all required cache and memory control signals, including cache and memory addresses for attached coprocessors. As a result, only the data bus and a few control signals need to be connected to a coprocessor.

The interface supports three types of coprocessor instructions: loads/stores, coprocessor operations, and processorcoprocessor transfers. Note that coprocessor loads and stores occur directly between the coprocessor and memory, without requiring the data to go through the CPU.

Synchronization between the CPU and external coprocessors is achieved using a Phased-Lock Loop interface to the coprocessor. The coprocessor physical interface also includes coprocessor condition signals (CpCond(n)), which are used in coprocessor branch instructions, and a coprocessor busy signal (CpBusy) which is used to stall the CPU if the coprocessor needs to hold off subsequent operations.

Finally, a precise exception interface is defined between the CPU and coprocessors using the external interrupt inputs of the CPU. This allows a coprocessor exception, even if it was the result of a multi-cycle operation, to be traced to the precise coprocessor operation which caused it. This is an important feature for languages which can define specific error handlers for each task.

The interface supports up to four separate coprocessors. Coprocessor 0 is defined to be the system control coprocessor, and resides on the same chip as the CPU unit. Coprocessor 1 is the Floating Point Accelerator, IDT 79R3010. Coprocessors 2 and 3 are available to support an interface to application specific functions.

### MULTIPROCESSING SUPPORT

The IDT79R3000 supports multiprocessing applications in a simple but effective way. Multiprocessing applications require cache coherency across the multiple processors. The IDT79R3000 offers two signals to support cache coherency: the first, MPStall, stalls the processor within two cycles of being received and keeps it from accessing the cache. This allows an external agent to snoop into the processor data cache. The second signal, MPInvalidate, causes the processor to write data on the data cache bus which indicates the externally addressed cache entry is invalid. Thus, a subsequent access to that location would result in a cache miss, and the data would be obtained from main memory.

The two MP signals would be generated by a external logic which utilizes a secondary cache to perform bus snooping functions. The 79R3000 does not impose an architecture for this secondary cache, but rather is flexible enough to support a variety of application specific architectures and still maintain cache coherency. Further, there is no impact on designs which do not require this feature.

## **ADVANCED FEATURES**

The IDT79R3000 offers a number of additional features such as the ability to swap the instruction and data caches, facilitating diagnostics and cache flushing. Another feature isolates the caches, which forces cache hits to occur regardless of the contents of the tag fields.

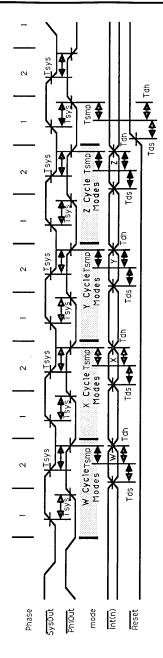

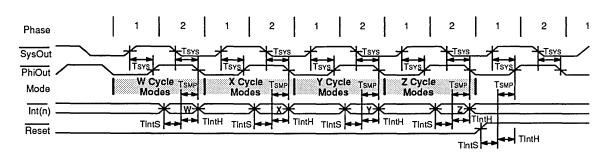

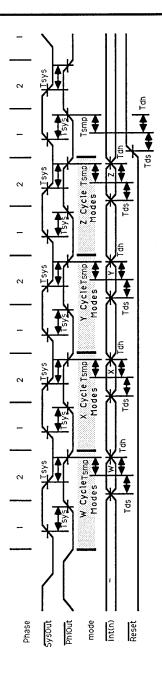

Further features of the IDT79R3000 are configured during the last four cycles prior to the negation of the RESET input. These functions include the ability to select cache sizes and cache refill block sizes; the ability to utilize the multiprocessor interface; whether or not instruction streaming is enabled; whether byte ordering follows "Big-Endian" or "Little-Endian" protocols, etc. Table 3 shows the configuration options selected at Reset. These are further discussed in the "Hardware User's Manual".

## **BACKWARD COMPATIBILITY WITH 79R2000**

The IDT79R3000 can be used in sockets designed for the 79R2000A. The pin-out of the 79R3000 has been selected to ensure this compatibility, with new functions mapped onto previously unused pins. The instruction set is compatible with that of the 79R2000 at the binary level. As a result, code written for the older processor can be executed. New features, such as block refill, instruction streaming, etc. can be selectively disabled.

In most 79R2000A applications, the 79R3000 can be placed in the socket with no modification to initialization settings. The initialization of the 79R3000 includes whether or not the device should operate as a 79R2000A. Systems using 79R2000A would normally have this input configured so that the device would default to this mode. Further application assistance on this topic is available from IDT.

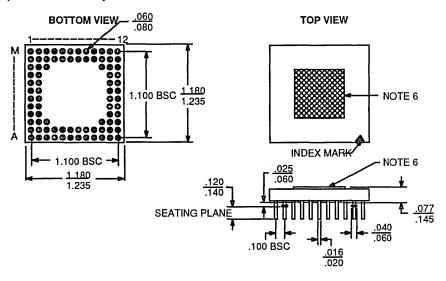

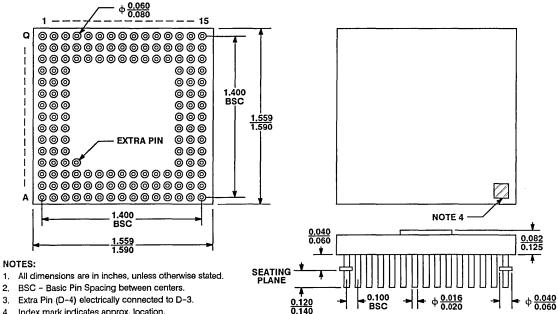

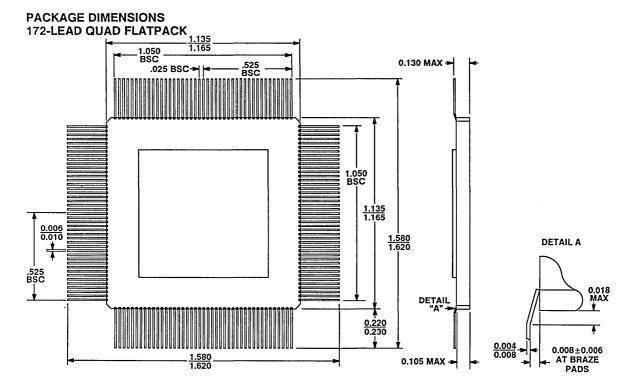

# A SPECIAL NOTE ON PACKAGING

Both the flat pack and the PGA packages for the 79R3000 incorporate separate power and ground planes to eliminate noise associated with high frequency operation. This, coupled with the numerous power and ground pins provided on the device, helps to ensure very reliable operation.

| INPUT | W CYCLE                     | X CYCLE                     | Y CYCLE                     | Z CYCLE                     |

|-------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| Int0  | DBlkSize0                   | DBlkSize1                   | Extend Cache                | BigEndian                   |

| Int1  | IBlkSize0                   | IBlkSize1                   | Reserved <sup>(1)</sup>     | TriState                    |

| Int2  | Reserved <sup>(1)</sup>     | IStream                     | Reserved <sup>(1)</sup>     | NoCache                     |

| Int3  | Reserved <sup>(1)</sup>     | StorePartial                | MultiProcessor              | BusDriveOn                  |

| Int4  | PhaseDelayOn <sup>(2)</sup> | PhaseDelayOn <sup>(2)</sup> | PhaseDelayOn <sup>(2)</sup> | PhaseDelayOn <sup>(2)</sup> |

| Int5  | R3000 Mode <sup>(2)</sup>   | R3000 Mode <sup>(2)</sup>   | R3000 Mode <sup>(2)</sup>   | R3000 Mode <sup>(2)</sup>   |

### NOTES:

1. Reserved entries must be driven high.

2. These values must be driven stable throughout the entire RESET period.

#### Table 3: IDT79R3000 Mode Selectable Features

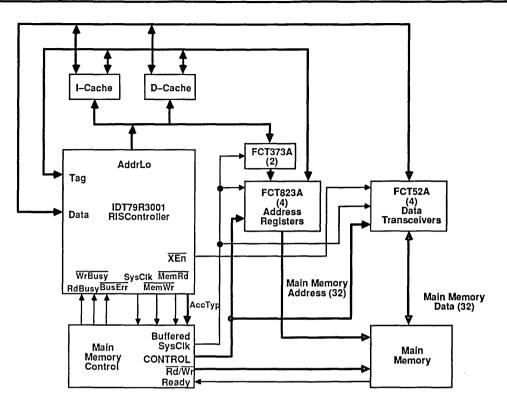

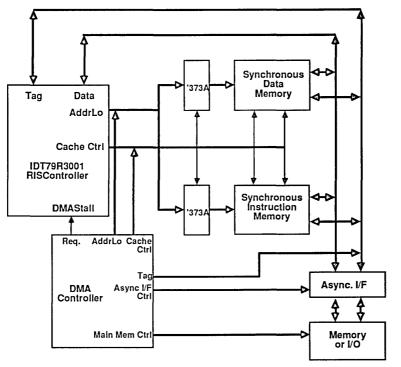

#### Figure 11. IDT79R3000 Subsystem Interfaces Example; 64 KB Caches

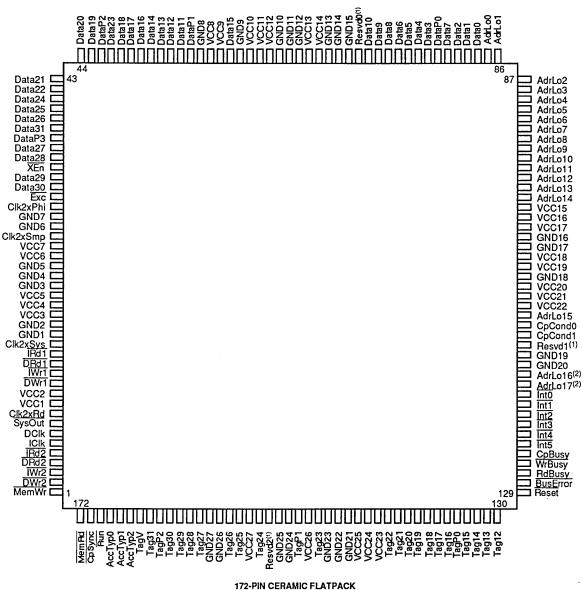

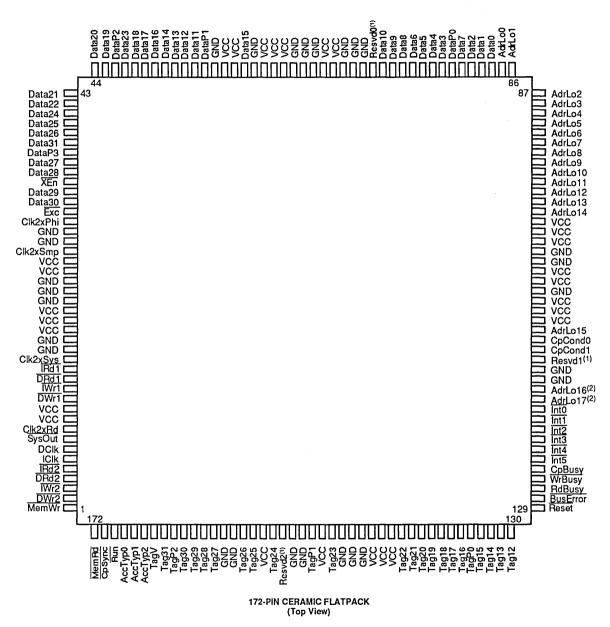

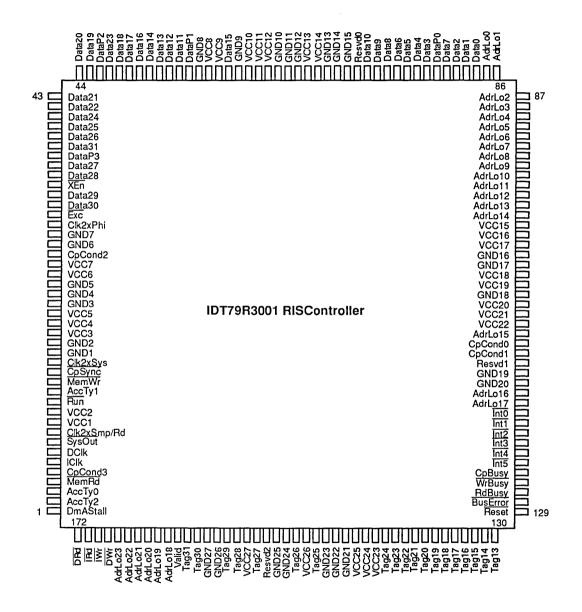

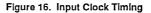

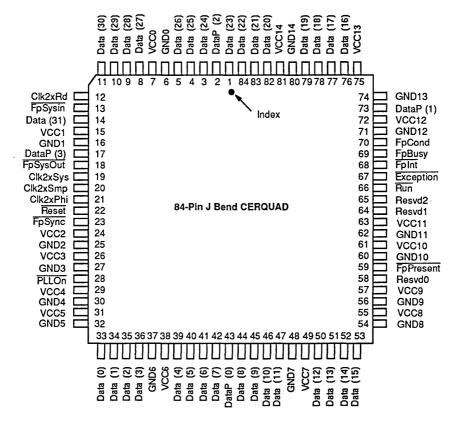

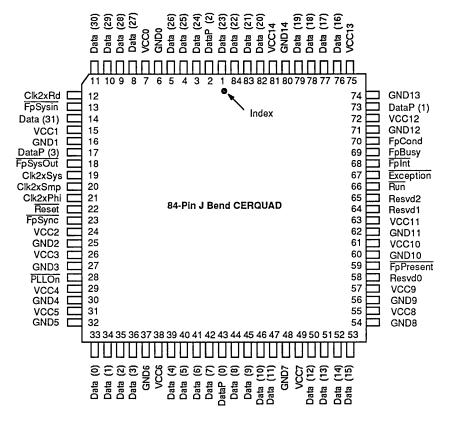

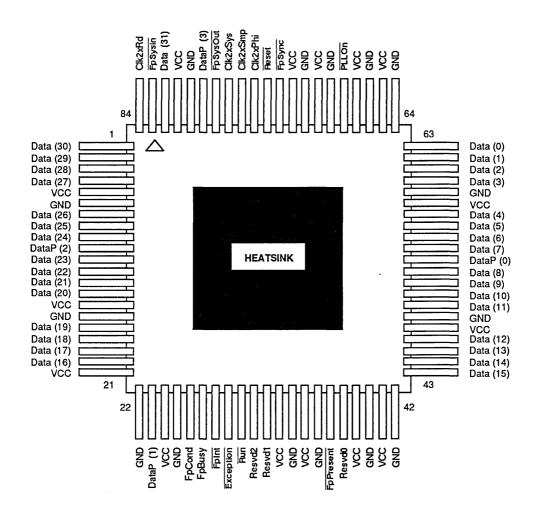

# **PIN CONFIGURATION**

(Cavity Side View)

10

### NOTES:

1. Reserved pins must not be connected.

AdrLo 16 & 17 are multi-function pins which are controlled by mode select programming on interrupt pins at reset time. AdrLo 16: MP Invalidate, CpCond (2). AdrLo 17: MP Stall, CpCond (3).

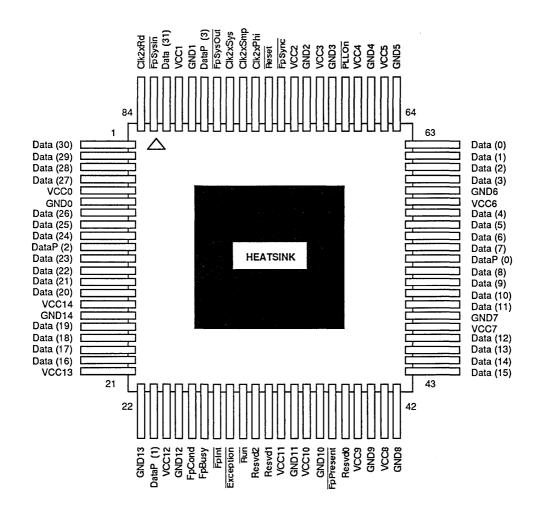

# **PIN CONFIGURATION**

|   | 1          | 2          | 3           | 4           | 5           | 6           | 7           | 8             | 9                          | 10                         | 11         | 12           | 13                | 14          | 15          |

|---|------------|------------|-------------|-------------|-------------|-------------|-------------|---------------|----------------------------|----------------------------|------------|--------------|-------------------|-------------|-------------|

| Α | VCC14      | AdrLo<br>6 | AdrLo<br>10 | AdrLo<br>11 | VCC12       | AdrLo<br>14 | AdrLo<br>15 | CpCond<br>0   | AdrLo <sup>(1)</sup><br>16 | AdrLo <sup>(1)</sup><br>17 | Intr2      | Intr5        | <u>₩r</u><br>Busy | Reset       | VCC10       |

| в | AdrLo<br>3 | DRd2       | AdrLo<br>7  | AdrLo<br>9  | AdrLo<br>12 | IRd2        | AdrLo<br>13 | CpCond<br>1   | Intr1                      | Intr3                      | Cp<br>Busy | Bus<br>Error | DR2               | Tag12       | Tag15       |

| с | AdrLo<br>0 | AdrLo<br>4 | VCC13       | AdrLo<br>5  | AdrLo<br>8  | GND13       | GND12       | VCC11         | IntrO                      | Intr4                      | Rd<br>Busy | GND11        | Tag13             | TagP0       | Tag18       |

| D | Data<br>1  | AdrLo<br>2 | GND0        |             |             |             |             |               |                            |                            |            |              | Tag14             | Tag17       | Tag19       |

| Е | DataP<br>0 | Data<br>0  | AdrLo<br>1  |             |             |             |             |               |                            |                            |            |              | Tag16             | Tag20       | VCC9        |

| F | VCC0       | Data<br>7  | Data<br>2   |             |             |             |             |               |                            |                            |            |              | GND10             | Tag21       | Tag23       |

| G | Data<br>4  | Data<br>3  | GND1        |             |             |             |             |               |                            |                            |            |              | GND9              | Tag22       | TagP1       |

| Н | Data<br>6  | Data<br>5  | Data<br>8   |             |             |             |             |               |                            |                            |            |              | VCC8              | Tag25       | Tag24       |

| J | Data<br>10 | DataP<br>1 | Data<br>9   |             |             |             |             |               |                            |                            |            |              | Tag28             | Tag29       | Tag26       |

| к | Data<br>15 | Data<br>11 | GND2        |             |             |             |             |               |                            |                            |            |              | GND8              | Tag<br>P2   | Tag27       |

| L | VCC1       | Data<br>12 | Data<br>17  |             |             |             |             |               |                            |                            |            |              | Acc<br>Typ2       | Tag31       | Tag30       |

| М | Data<br>13 | Data<br>16 | DataP<br>2  |             |             |             |             |               |                            |                            |            |              | GND7              | Acc<br>Typ1 | VCC7        |

| N | Data<br>14 | Data<br>18 | Data<br>19  | GND3        | Data<br>24  | Data<br>P3  | VCC3        | VCC4          | GND5                       | GND6                       | DRd1       | Mem<br>Wr    | Mem<br>Rd         | Run         | TagV        |

| Ρ | Data<br>23 | Data<br>20 | ĪWr2        | Data<br>22  | Data<br>26  | Data<br>27  | XEn         | Data<br>30    | Clk2x<br>Sys               | Cik2x<br>Rd                | DClk       | <b>IRd 1</b> | IWr1              | Cp<br>Sync  | Acc<br>Typ0 |

| ۵ | VCC2       | Data<br>21 | Data<br>25  | Data<br>31  | Data<br>28  | GND4        | Data<br>29  | Excep<br>tion | Clk2x<br>Phi               | Clk2x<br>Smp               | SysOut     | VCC5         | ICik              | DWr1        | VCC6        |

144-Pin PGA (Top View)

### NOTE:

AdrLo 16 & 17 are multi-function pins which are controlled by mode select programming on interrupt pins at reset time. AdrLo16: MP Invalidate, CpCond (2). AdrLo17: MP Stall, CpCond (3).

# **PIN DESCRIPTIONS**

| PIN NAME     | 1/O | DESCRIPTION                                                                                                                                                                                                                                            |

|--------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data (0–31)  | 1/0 | A 32-bit bus used for all instruction and data transmission among the processor, caches, memory interface, and coprocessors.                                                                                                                           |

| DataP (0-3)  | I/O | A 4-bit bus containing even parity over the data bus.                                                                                                                                                                                                  |

| Tag (12–31)  | I/O | A 20-bit bus used for transferring cache tags and high addresses between the processor, caches, and memory interface.                                                                                                                                  |

| TagV         | 1/0 | The tag validity indicator.                                                                                                                                                                                                                            |

| TagP (0-2)   | I/O | A 3-bit bus containing even parity over the concatenation of TagV and Tag.                                                                                                                                                                             |

| AdrLo (0-17) | 0   | An 18-bit bus containing byte addresses used for transferring low addresses from the processor to the caches and memory interface. (AdrLo 16: CpCond (2), AdrLo 17: CpCond (3) set by reset initialization).                                           |

| IRat         | 0   | Read enable for the instruction cache.                                                                                                                                                                                                                 |

| IWr1         | 0   | Write enable for the instruction cache.                                                                                                                                                                                                                |

| IRd2         | 0   | An identical copy of IRd 1 used to split the load.                                                                                                                                                                                                     |

| IWr2         | 0   | An identical copy of IWr1 used to split the load.                                                                                                                                                                                                      |

| ICIk         | 0   | The instruction cache address latch clock. This clock runs continuously.                                                                                                                                                                               |

| DRd1         | 0   | The read enable for the data cache.                                                                                                                                                                                                                    |

| DWr1         | 0   | The write enable for the data cache.                                                                                                                                                                                                                   |

| DRd2         | 0   | An identical copy of DRd1 used to split the load.                                                                                                                                                                                                      |

| DWr2         | 0   | An identical copy of DWr1 used to split the load.                                                                                                                                                                                                      |

| DClk         | 0   | The data cache address latch clock. This clock runs continuously.                                                                                                                                                                                      |

| XEn          | 0   | The read enable for the Read Buffer.                                                                                                                                                                                                                   |

| АссТур (0–2) | 0   | A 3-bit bus used to indicate the size of data being transferred on the data bus, whether or not a data transfer is<br>occurring, and the purpose of the transfer.                                                                                      |

| MemWr        | 0   | Signals the occurrence of a main memory write                                                                                                                                                                                                          |

| MemAd        | 0   | Signals the occurrence of a main memory read.                                                                                                                                                                                                          |

| BusError     | 1   | Signals the occurrence of a bus error during a main memory read or write.                                                                                                                                                                              |

| Run          | 0   | Indicates whether the processor is in the run or stall state.                                                                                                                                                                                          |

| Exception    | 0   | Indicates that the instruction about to commit state should be aborted and other exception related information.                                                                                                                                        |

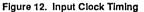

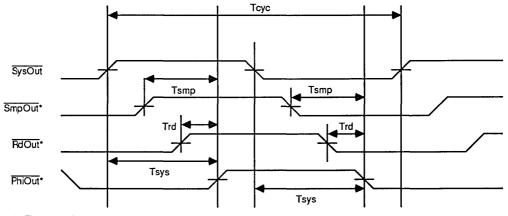

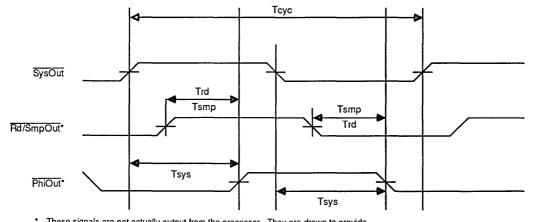

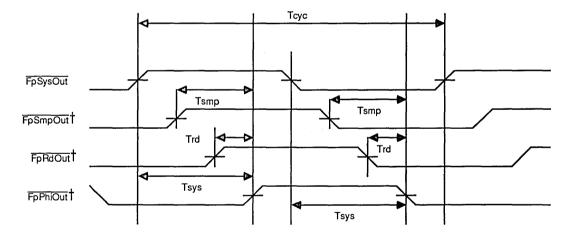

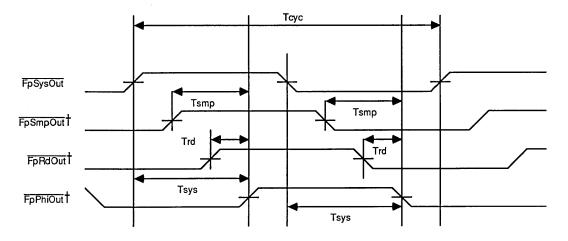

| SysOut       | 0   | A reflection of the internal processor clock used to generate the system clock.                                                                                                                                                                        |

| CpSync       | 0   | A clock which is identical to SysOut and used by coprocessors for timing synchronization with the CPU.                                                                                                                                                 |

| RdBusy       | 1   | The main memory read stall termination signal. In most system designs RdBusy is normally asserted and is deasserted only to<br>indicate the successful completion of a memory read. RdBusy is sampled by the processor only during memory read stalls. |

| WrBusy       | I   | The main memory write stall initiation/termination signal.                                                                                                                                                                                             |

| CpBusy       | I   | The coprocessor busy stall initiation/termination signal.                                                                                                                                                                                              |

| CpCond (0-1) | 1   | A 2-bit bus used to transfer conditional branch status from the coprocessors to the main processor.                                                                                                                                                    |

| CpCond (2–3) | !   | Conditional branch status from coprocessors to the processor. Function is provided on AdrLo 16/17 pins and is selected at reset time.                                                                                                                  |

| MPStall      | I   | Multiprocessing Stall. Signals to the processor that it should stall accesses to the caches in a multiprocessing environment. This is physically the same pin as CpCond3; its use is determined at RESET initialization.                               |

| MPInvalidate | I   | Multiprocessing Invalidate. Signals to the processor that it should issue invalidate data on the cache data bus. The address to be invalidated is externally provided. This is the same pin as CpCond2; its use is determined at RESET initialization. |

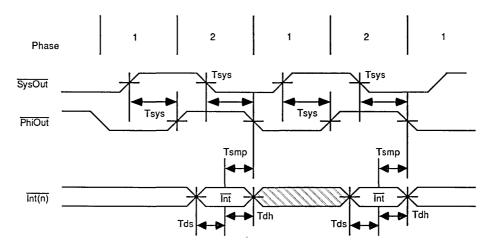

| Int (0–5)    | 1   | A 6-bit bus used by the memory interface and coprocessors to signal maskable interrupts to the processor. At reset time, mode select values are read in.                                                                                               |

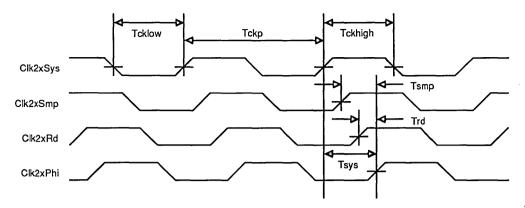

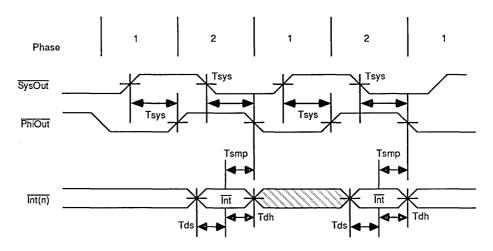

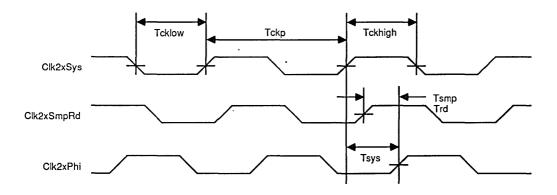

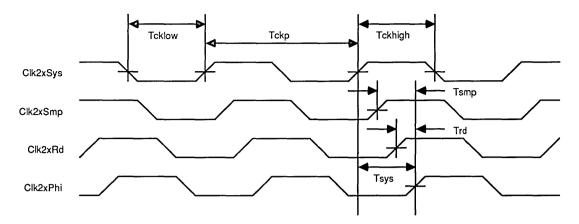

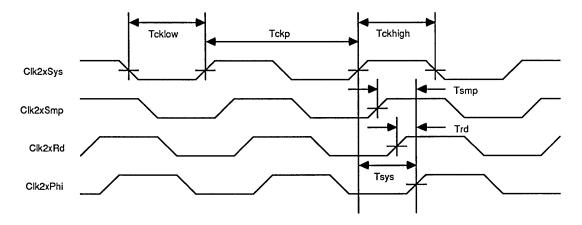

| Clk2xSys     | I   | The master double frequency input clock used for generating SysOut.                                                                                                                                                                                    |

| Clk2xSmp     | 1   | A double frequency clock input used to determine the sample point for data coming into the processor and coprocessors.                                                                                                                                 |

| Clk2xRd      | 1   | A double frequency clock input used to determine the enable time of the cache RAMs.                                                                                                                                                                    |

| Clk2xPhi     | 1   | A double frequency clock input used to determine the position of the internal phases, phase1 and phase2.                                                                                                                                               |

| Reset        | I   | Synchronous initialization input used to force execution starting from the reset memory address. Reset must be deasserted<br>synchronously but asserted asynchronously. The deassertion of reset must be synchronized by the leading edge of SysOut.   |

| SYMBOL           |                                            | COMMERCIAL   | MILITARY     | UNIT |

|------------------|--------------------------------------------|--------------|--------------|------|

| VTERM            | Terminal Voltage<br>with Respect to<br>GND | -0.5 to +7.0 | -0.5 to +7.0 | v    |

| T <sub>A</sub>   | Operating<br>Temperature                   | 0 to +70     | -55 to +125  | °C   |

| TBIAS            | Temperature<br>Under Bias                  | -55 to +125  | -65 to +135  | °C   |

| T <sub>STG</sub> | Storage<br>Temperature                     | -55 to +125  | -65 to +150  | °C   |

| VIN              | Input Voltage <sup>(2)</sup>               | -0.5 to +7.0 | -0.5 to +7.0 | V    |

# **ABSOLUTE MAXIMUM RATINGS**<sup>(1, 3)</sup>

### NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM PAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

VIN minimum = -3.0V for pulse width less than 15ns.

VIN should not exceed V<sub>CC</sub> +0.5 Volts.

DC ELECTRICAL CHARACTERISTICS

Not more than one output should be shorted at a time. Duration of the short should not exceed 30 seconds.

# RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| GRADE      | AMBIENT<br>TEMPERATURE | GND | Vcc       |

|------------|------------------------|-----|-----------|

| Military   | -55°C to +125°C        | ٥V  | 5.0 ± 10% |

| Commercial | 0°C to +70°C           | ٥V  | 5.0 ± 5%  |

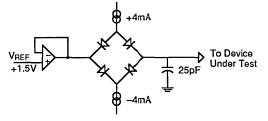

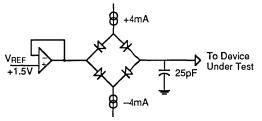

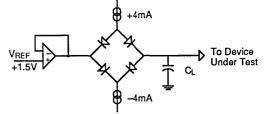

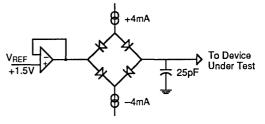

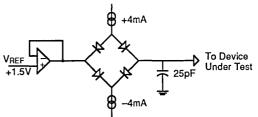

# **OUTPUT LOADING FOR AC TESTING**

| SYMBOL           | PARAMETER                          | TEST CONDITIONS                                | 16.6<br>MIN. | 7MHz<br>MAX. | 20.0<br>MIN. | MHz<br>MAX. | 25.0<br><u>MIN</u> . | MHz<br>MAX. | 33.33MHz<br>MIN. MAX. | UNIT |

|------------------|------------------------------------|------------------------------------------------|--------------|--------------|--------------|-------------|----------------------|-------------|-----------------------|------|

| VOH              | Output HIGH Voltage                | V <sub>CC</sub> = Min., I <sub>OH</sub> = -4mA | 3.5          | _            | 3.5          | -           | 3.5                  |             | 3.5 —                 | v    |

| VoL              | Output LOW Voltage                 | V <sub>CC</sub> = Min., I <sub>OL</sub> = 4mA  | -            | 0.4          | —            | 0.4         | _                    | 0.4         | — 0.4                 | V    |

| VOHC             | Output HIGH Voltage <sup>(7)</sup> | V <sub>CC</sub> = Min., I <sub>OH</sub> = -4mA | 4.0          | —            | 4.0          | -           | 4.0                  |             | 4.0                   | V    |

| V <sub>OHT</sub> | Output HIGH Voltage (4, 6)         | V <sub>CC</sub> = Min., I <sub>OH</sub> = -8mA | 2.4          | _            | 2.4          | _           | 2.4                  |             | 2.4 —                 | V    |

| VOLT             | Output LOW Voltage (4, 6)          | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8mA  | —            | 0.8          | —            | 0.8         | -                    | 0.8         | 0.8                   | v    |

| VIH              | Input HIGH Voltage (5)             |                                                | 2.0          |              | 2.0          | I           | 2.0                  | _           | 2.0                   | V    |

| VIL              | Input LOW Voltage (1)              |                                                | -            | 0.8          | _            | 0.8         |                      | 0.8         | - 0.8                 | V    |

| VIHS             | Input HIGH Voltage (2, 5)          |                                                | 3.0          |              | 3.0          | _           | 3.0                  | _           | 3.0 —                 | V    |

| VILS             | Input LOW Voltage (1, 2)           |                                                | _            | 0.4          |              | 0.4         | _                    | 0.4         | 0.4                   | V    |

| CiN              | Input Capacitance (6)              |                                                | _            | 10           | _            | 10          | _                    | 10          | 10                    | рF   |

| Солт             | Output Capacitance (6)             |                                                | —            | 10           | -            | 10          | _                    | 10          | - 10                  | pF   |

| lcc              | Operating Current                  | Vcc = Max.                                     | —            | 575          | _            | 650         | _                    | 750         | - 850                 | mA   |

| lн               | Input HIGH Leakage <sup>(3)</sup>  | VIH = VCC                                      |              | 10           | _            | 10          |                      | 10          | <b>10</b>             | μA   |

| կլ               | Input LOW Leakage (3)              | V <sub>IL</sub> = GND                          | -10          |              | -10          | _           | -10                  |             | -10                   | μA   |

| loz              | Output Tri-state Leakage           | V <sub>OH</sub> = 2.4V, V <sub>OL</sub> = 0.5V | -40          | 40           | -40          | . 40        | -40                  | 40          | -40 40                | μA   |

### NOTES:

1. VIL Min. = -3.0V for pulse width less than 15ns. VIL should not fall below -0.5 Volts for larger periods.

2. VIHs and VILs apply to Clk2xSys, Clk2xSmp, Clk2xRd, Clk2xPhi, CpBusy, and Reset.

3. These parameters do not apply to the clock inputs.

4. VOHT and VOLT apply to the bidirectional data and tag busses only. Note that VIH and VIL also apply to these signals. VOHT and VOLT are provided to give the designer further information about these specific signals.

5. VIH should not be held above Vcc + 0.5 volts.

6. Guaranteed by design.

7. VOHC applies to RUN and Exception.

# DC ELECTRICAL CHARACTERISTICS— MILITARY TEMPERATURE RANGE (T<sub>A</sub> = -55°C to +125°C, V<sub>CC</sub> = +5.0V ± 10%)

| SYMBOL | PARAMETER                          | TEST CONDITIONS                                | 16.6     | 7MHz       | 10.07 |

|--------|------------------------------------|------------------------------------------------|----------|------------|-------|

| STMBUL | PARAMETER                          | TEST CONDITIONS                                | MIN.     | MAX.       | UNIT  |

| Vон    | Output HIGH Voltage                | $V_{CC} = Min., I_{OH} = -4mA$                 | 3.5      | <i>d</i> t | v     |

| Vol    | Output LOW Voltage                 | Vcc = Min., IoL = 4mA                          | _        | 0.4        | v     |

| Vohc   | Output HIGH Voltage <sup>(7)</sup> | V <sub>CC</sub> = Min., I <sub>OH</sub> = -4mA | 4.0      |            | V     |

| VOHT   | Output HIGH Voltage (4, 6)         | V <sub>CC</sub> = Min., I <sub>OH</sub> = -8mA | 2.4      | —          | v     |

| VOLT   | Output LOW Voltage (4, 6)          | Vcc = Min., IoL = 8mA                          |          | 0.8        | v     |

| VIH    | Input HIGH Voltage (5)             |                                                | 2.0      |            | V     |

| VIL    | Input LOW Voltage (1)              |                                                |          | 0.8        | v     |

| VIHS   | Input HIGH Voltage (2, 5)          |                                                | 3.0      | _          | v     |

| VILS   | Input LOW Voltage (1, 2)           |                                                | <u> </u> | 0.4        | V     |

| CIN    | Input Capacitance (6)              |                                                |          | 10         | pF    |

| COUT   | Output Capacitance (6)             |                                                | <u> </u> | 10         | pF    |

| lcc    | Operating Current                  | V <sub>CC</sub> = Max.                         |          | 750        | mA    |

| Ін     | Input HIGH Leakage (3)             | VIH = Vcc                                      | _        | 10         | μA    |

| hε     | Input LOW Leakage (3)              | V <sub>IL</sub> = GND                          | -10      |            | μA    |

| loz    | Output Tri-state Leakage           | V <sub>OH</sub> = 2.4V, V <sub>OL</sub> = 0.5V | -40      | 40         | μΑ    |

NOTES:

1. VIL Min. = -3.0V for pulse width less than 15ns. VIL should not fall below -0.5 Volts for larger periods.

2. VIHs and VLs apply to Clk2xSys, Clk2xSmp, Clk2xRd, Clk2xPhi, CpBusy, and Reset.

3. These parameters do not apply to the clock inputs.

4. VOHT and VOLT apply to the bidirectional data and tag busses only. Note that VIH and VIL also apply to these signals. VOHT and VOLT are provided to give the designer further information about these specific signals.

5. VIH should not be held above Vcc + 0.5 volts.

6. Guaranteed by design.

7. VOHC applies to Run and Exception.

# AC ELECTRICAL CHARACTERISTICS<sup>(1, 2, 3)</sup> — COMMERCIAL TEMPERATURE RANGE (TA = $0^{\circ}C$ to +70°C, V<sub>CC</sub> = +5.0V ± 5%)

| SYMBOL              | PARAMETER                                                                                                                                             | TEST CONDITIONS  | 16.6<br>MIN. | 7MHz<br>MAX.                      | 20.0<br>MIN.      | MHz<br>MAX.                       | 25.0<br>MIN. | MHz<br>MAX.                       | 33.33MI<br>MIN. M/ |                            |                      |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|-----------------------------------|-------------------|-----------------------------------|--------------|-----------------------------------|--------------------|----------------------------|----------------------|

| Clock               |                                                                                                                                                       |                  |              |                                   |                   |                                   |              |                                   |                    |                            |                      |

| TCkHigh             | Input Clock High <sup>(2)</sup>                                                                                                                       | Transition < 5ns | 12.5         |                                   | 10                | _                                 | 8            | _                                 | 6 -                | -                          | ns                   |

| TCkLow              | Input Clock Low <sup>(2)</sup>                                                                                                                        | Transition < 5ns | 12.5         | _                                 | 10                | _                                 | 8            | _                                 | 6 -                | -                          | ns                   |

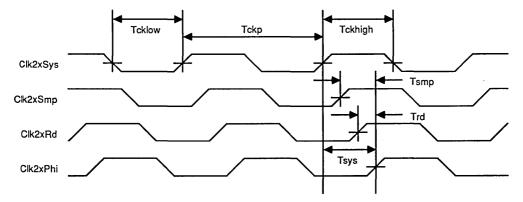

| T <sub>CkP</sub>    | Input Clock Period <sup>(2)</sup><br>Clk2xSys to Clk2xSmp <sup>(6)</sup><br>Clk2xSmp to Clk2xRd <sup>(6)</sup><br>Clk2xSmp to Clk2xPhi <sup>(6)</sup> |                  | 30<br>0<br>9 | 500<br>tcyc/4<br>tcyc/4<br>tcyc/4 | 25<br>0<br>0<br>7 | 500<br>tcyc/4<br>tcyc/4<br>tcyc/4 | 20<br>0<br>5 | 500<br>tcyc/4<br>tcyc/4<br>tcyc/4 | 0 tcy<br>0 tcy     | 00<br>/c/4<br>/c/4<br>/c/4 | ns<br>ns<br>ns<br>ns |

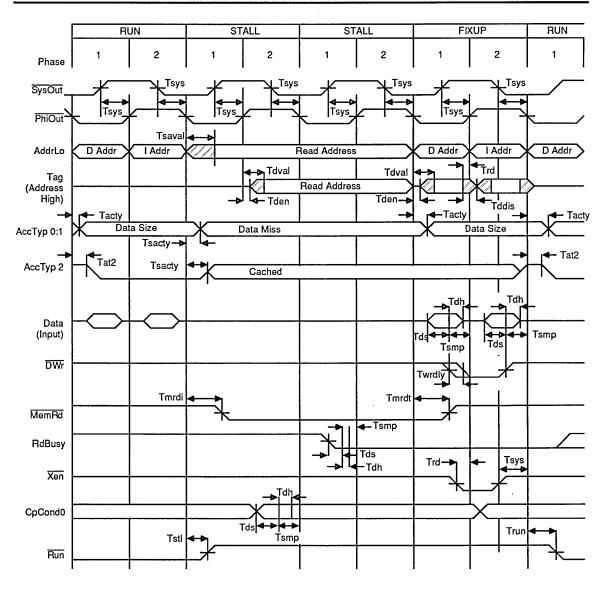

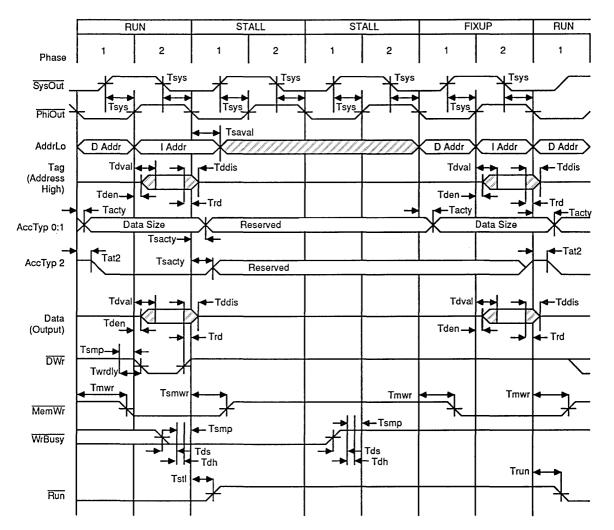

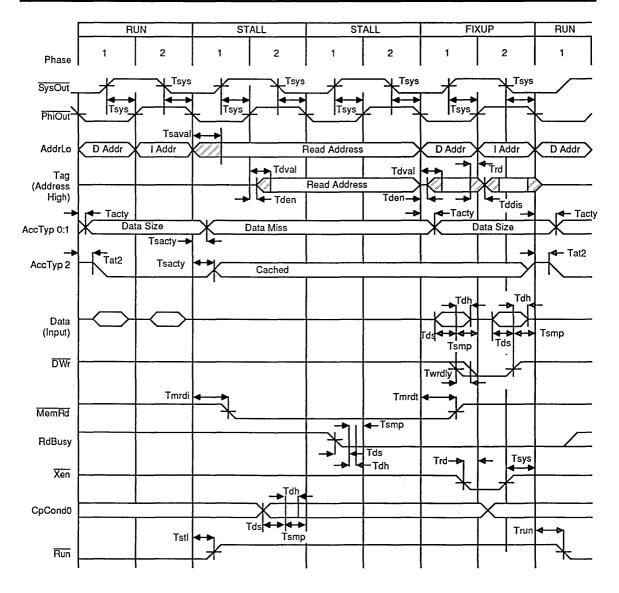

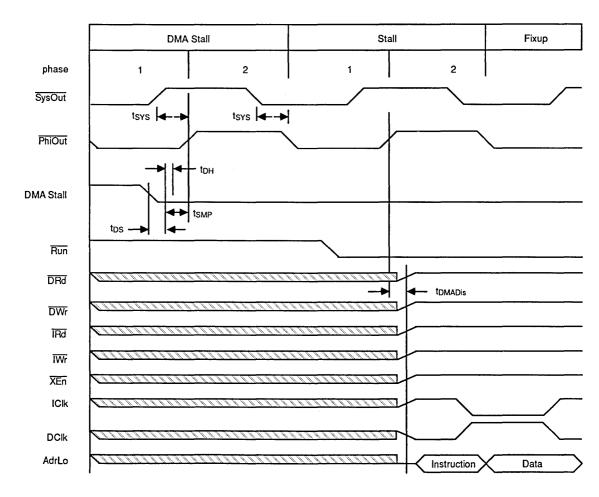

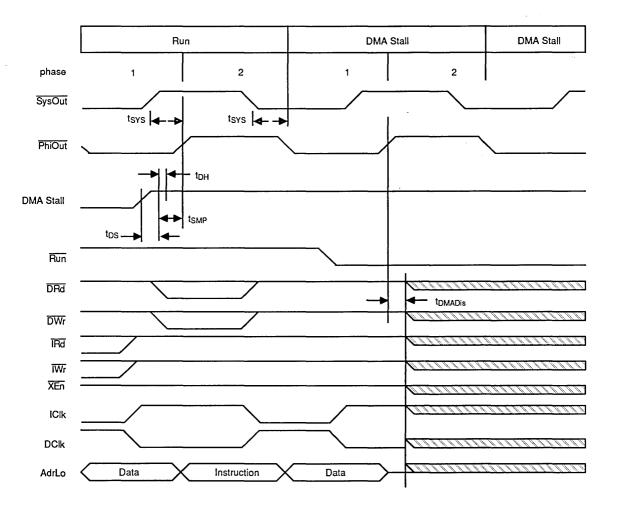

| Run Oper            | ration                                                                                                                                                |                  |              |                                   |                   |                                   |              |                                   |                    |                            |                      |

| TDEn                | Data Enable <sup>(3)</sup>                                                                                                                            |                  | -            | -2                                | —                 | -2                                | —            | -1.5                              |                    | 1                          | ns                   |

| T <sub>DDis</sub>   | Data Disable <sup>(3)</sup>                                                                                                                           |                  | -            | -1                                | —                 | -1                                | -            | -0.5                              |                    | 0.5                        | ns                   |

| T <sub>DVal</sub>   | Data Valid                                                                                                                                            | Load = 25pF      | -            | 3                                 |                   | 3                                 | 1            | 2                                 | - 2                | 2                          | ns                   |

| T <sub>WrDiy</sub>  | Write Delay                                                                                                                                           | Load = 25pF      | -            | 5                                 | -                 | 4                                 | -            | 3                                 | 2                  | 2                          | ns                   |

| T <sub>DS</sub>     | Data Set-up                                                                                                                                           |                  | 9            | -                                 | 8                 | —                                 | 6            |                                   | 4.5 -              | -                          | ns                   |

| T <sub>DH</sub>     | Data Hold                                                                                                                                             |                  | -2.5         |                                   | -2.5              | —                                 | -2.5         | —                                 | -1.5 +             | -                          | ns                   |

| T <sub>CBS</sub>    | CpBusy Set–up                                                                                                                                         |                  | 13           | _                                 | 11                |                                   | 9            | _                                 | 7 -                | -                          | ns                   |

| Тсвн                | CpBusy Hold                                                                                                                                           |                  | -2.5         | _                                 | -2.5              | _                                 | -2.5         | _                                 | -1.5 -             | -                          | ns                   |

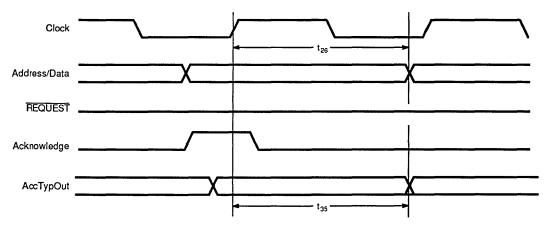

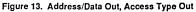

| Т <sub>АсТу</sub>   | Access Type (1:0)                                                                                                                                     | Load = 25pF      | _            | 7                                 | _                 | 6                                 |              | 5                                 | - 4                | 1                          | ns                   |

| T <sub>AT2</sub>    | Access Type (2)                                                                                                                                       | Load = 25pF      |              | 17                                |                   | 14                                | -            | 12                                | 8                  | .5                         | ns                   |

| T <sub>MWr</sub>    | Memory Write                                                                                                                                          | Load = 25pF      | 1            | 27                                | 1                 | 23                                | 1            | 18                                | 1 9                | .5                         | ns                   |

| TExc                | Exception                                                                                                                                             | Load = 25pF      | _            | 7                                 | —                 | 7                                 | -            | 5                                 | - 3                | .5                         | ns                   |

| Stall Ope           | ration                                                                                                                                                |                  |              |                                   |                   |                                   |              |                                   |                    |                            |                      |

| TSAVal              | Address Valid                                                                                                                                         | Load = 25pF      | _            | 30                                |                   | 23                                | -            | 20                                | — 1                | 5                          | ns                   |

| TSAcTy              | Address Type                                                                                                                                          | Load = 25pF      | _            | 27                                | _                 | 23                                | _            | 18                                | 1                  | 0                          | ns                   |

| T <sub>MRdi</sub>   | Memory Read Initiate                                                                                                                                  | Load = 25pF      | 1            | 27                                | 1                 | 23                                | 1            | 18                                | 1 1                | 0                          | ns                   |

| T <sub>MRdt</sub>   | Memory Read Terminate                                                                                                                                 | Load = 25pF      | -            | 7                                 | -                 | 7                                 |              | 5                                 | - 3                | .5                         | ns                   |

| T <sub>Stl</sub>    | Run Terminate                                                                                                                                         | Load = 25pF      | 2            | 17                                | 2                 | 15                                | 2            | 11                                | 2 8                | 3                          | ns                   |

| T <sub>Run</sub>    | Run Initiate                                                                                                                                          | Load = 25pF      | _            | 7                                 |                   | 6                                 |              | 4                                 |                    | 3                          | ns                   |

| T <sub>SMWr</sub>   | Memory Write                                                                                                                                          | Load = 25pF      | 1            | 27                                | 1                 | 23                                | 1            | 18                                | 1 9                | 5                          | ns                   |

| T <sub>SExc</sub>   | Exception Valid                                                                                                                                       | Load = 25pF      | 1            | 20                                | _                 | 18                                | _            | 15                                | _ 1                | 0                          | ns                   |

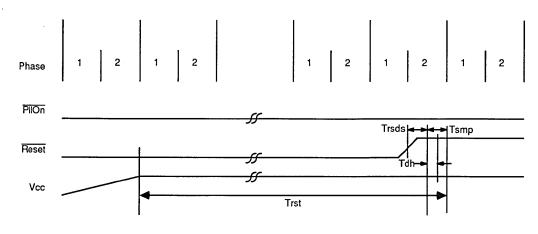

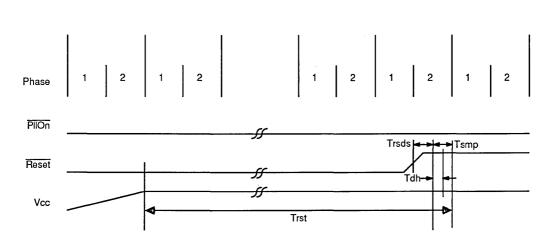

| Reset Init          | ialization                                                                                                                                            |                  |              |                                   |                   |                                   |              |                                   |                    |                            |                      |

| T <sub>RST</sub>    | Reset Pulse Width                                                                                                                                     |                  | 6            | _                                 | 6                 | _                                 | 6            |                                   | 6 +                | -   T                      | Тсус                 |

| T <sub>rstPLL</sub> | Reset timing, Phase-lock on <sup>(4, 5)</sup>                                                                                                         |                  | 3000         | _                                 | 3000              | _                                 | 3000         | _                                 | 3000 -             | - 7                        | Тсус                 |

| T <sub>rstcp</sub>  | Reset timing, Phase-lock off <sup>(4, 5)</sup>                                                                                                        |                  | 128          | _                                 | 128               | _                                 | 128          | _                                 | 128 –              | -   7                      | Тсус                 |

| Capacitiv           | e Load Deration                                                                                                                                       |                  |              |                                   |                   |                                   |              |                                   |                    |                            |                      |

| CLD                 | Load Derate <sup>(6)</sup>                                                                                                                            |                  | 0.5          | 1                                 | 0.5               | 1                                 | 0.5          | 1                                 | 0.5 1              | ns/                        | /25pF                |

NOTES:

1. All timings are referenced to 1.5V.

2. The clock parameters apply to all four 2xClocks: Clk2xSys, Clk2xSmp, Clk2xRd, and Clk2xPhi.

3. This parameter is guaranteed by design.

4. These parameters apply when the 79R3010 Floating Point Coprocessor is connected to the CPU. With phase lock on, Reset must be asserted for the longer of 3000 clock cycles or 200 microseconds.

5. Tcyc is one CPU clock cycle (two cycles of a 2x clock).

6. With the exception of the Run signal, no two signals on a given device will derate for a given load by a difference greater than 15%.

# AC ELECTRICAL CHARACTERISTICS<sup>(1, 2, 3)</sup> — MILITARY TEMPERATURE RANGE (T<sub>A</sub> = -55°C to +125°C, V<sub>CC</sub> = +5.0V ± 10%)

| SYMBOL              | PARAMETER                                                                                                                                             | TEST CONDITIONS  | 16.67MHz<br>MIN.                      | MAX.                              |                      |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------|-----------------------------------|----------------------|

| Clock               |                                                                                                                                                       | <u> </u>         | ·                                     |                                   | <b></b>              |

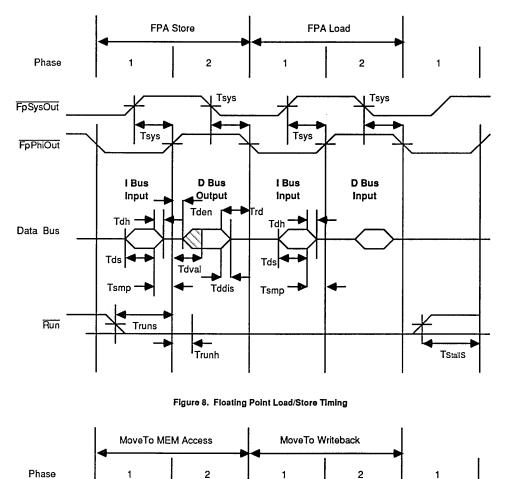

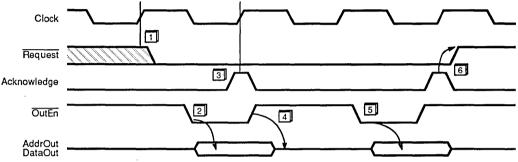

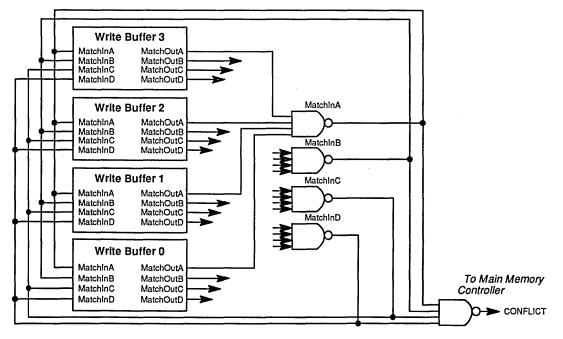

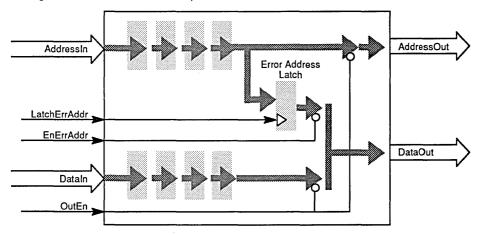

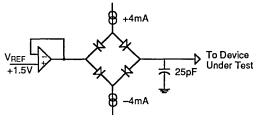

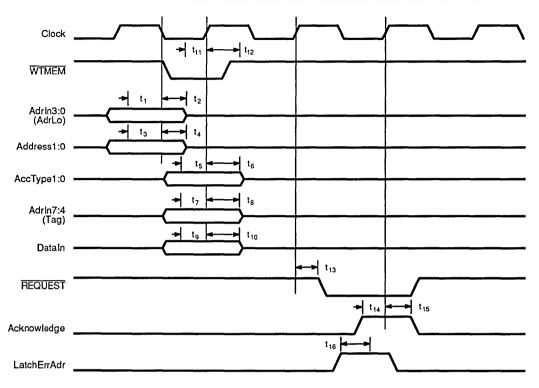

| TCkHigh             | Input Clock High <sup>(2)</sup>                                                                                                                       | Transition < 5ns | 12.5                                  |                                   | ns                   |