Integrated Device Technology, Inc.

# 1994 HIGH-PERFORMANCE SRAM DATA BOOK

2975 Stender Way, Santa Clara, California 95054-3090 Telephone: (800) 345-7015 • TWX: 910-338-2070 • FAX: (408) 492-8674

# ANNOUNCING

# IDT's New FAX-On-Demand Literature Request Service

Tired of waiting days or weeks for technical information you want *right now*?

Wait no longer—just access IDT's new FAX-On-Demand hotline to receive copies of current data sheets, application notes, and new product press releases within minutes of your phone call.

How does it work?

# Call (408) 492-8391

For an index of current information:

# Request document #1000

Individual document request numbers, product families, IDT product part numbers, descriptive titles, and page counts for each document are provided on the indices for your convenience. You may request up to 3 documents per phone call.

Integrated Device Technology, Inc.

VALUE THROUGH PERFORMANCE

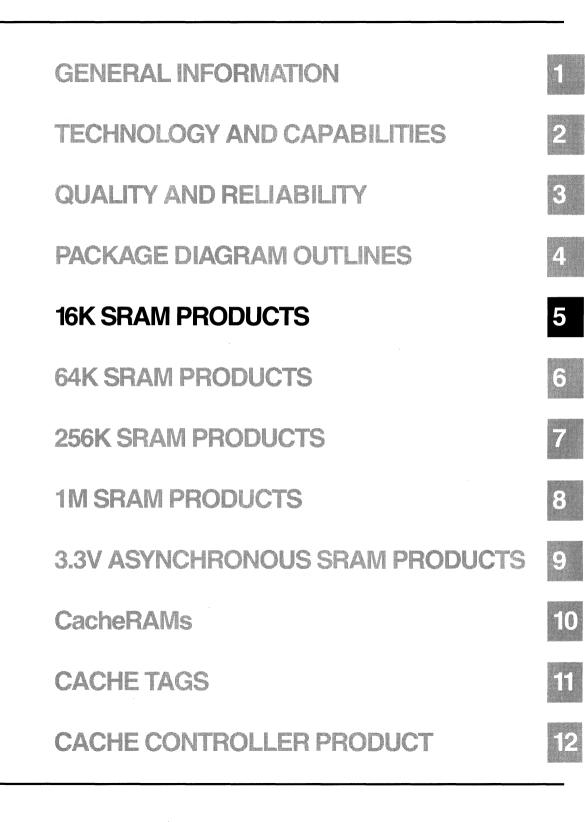

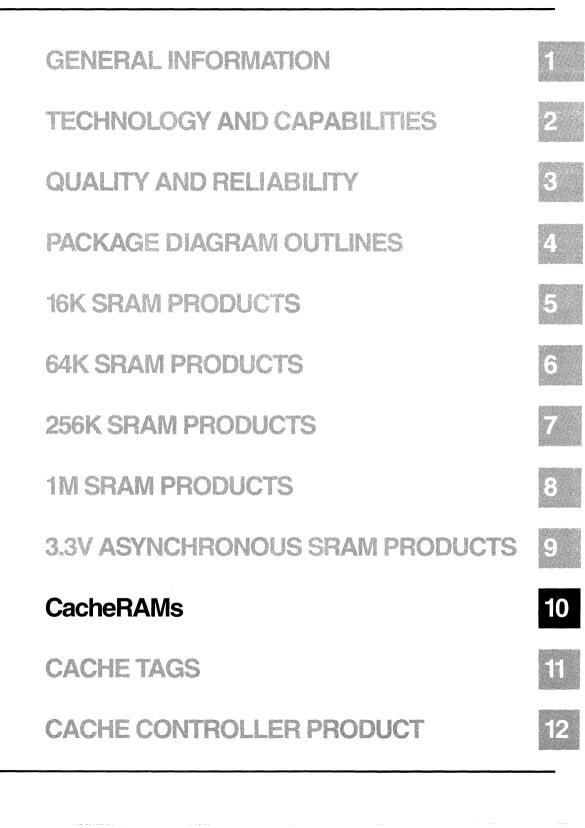

| GENERAL INFORMATION             | 1  |

|---------------------------------|----|

| TECHNOLOGY AND CAPABILITIES     | 2  |

| QUALITY AND RELIABILITY         | 3  |

| PACKAGE DIAGRAM OUTLINES        | 4  |

| 16K SRAM PRODUCTS               | 5  |

| 64K SRAM PRODUCTS               | 6  |

| 256K SRAM PRODUCTS              | 7  |

| 1M SRAM PRODUCTS                | 8  |

| 3.3V ASYNCHRONOUS SRAM PRODUCTS | 9  |

| CacheRAMs                       | 10 |

| CACHE TAGS                      | 11 |

| CACHE CONTROLLER PRODUCT        | 12 |

.

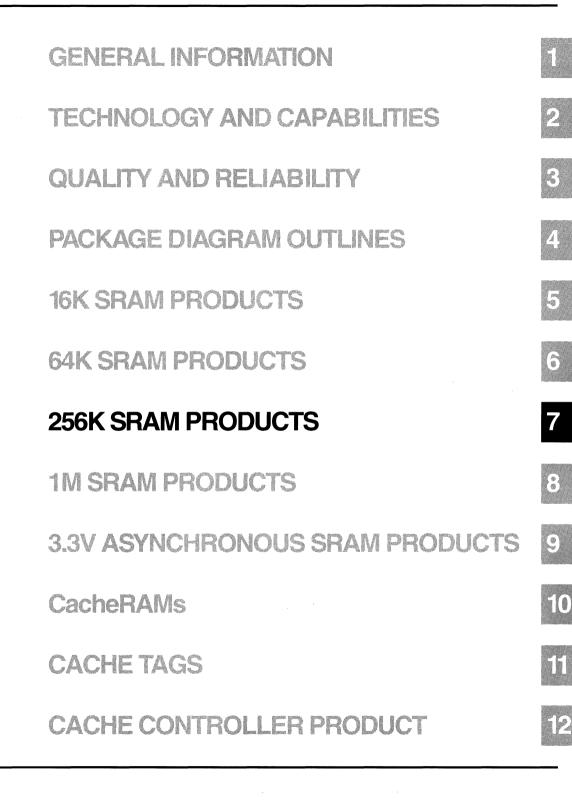

## **CONTENTS OVERVIEW**

For ease of use for our customers, Integrated Device Technology provides four separate data books: High-Performance Logic, Specialized Memories and Modules, RISC and RISC SubSystems, and High-Performance Static RAM.

IDT's 1994 High-Performance SRAM Data Book is comprised of both new product data sheets and revised data sheets on existing products. The new products include high-speed, high-density BiCMOS devices, specialty SRAM products, and true 3.3V high-performance SRAMs. The existing product data sheet revisions upgrade and correct the existing specification to more accurately reflect device improvements that have been made over time. Also included is a current packaging section for the products included in this book.

The SRAM Data Book's Table of Contents is a listing of the products contained in this data book only (in the past, we have also included products that appeared in other IDT data books). The number at the bottom center of the page denotes the section number and the sequence of the data sheet within that section, (i.e., 5.5 would be the fifth data sheet in the fifth section). The number in the lower right-hand corner is the page number for that particular data sheet.

The data sheets are organized in eight sections (16K, 64K, 256K, 1M, 3.3V, CacheRAMs, Cache Tags, and Cache Controller Product). Each section is then ordered by total number of bits (low to high), device word width (narrow to wide), and performance (slow to fast).

Integrated Device Technology, Inc. is a recognized leader in high-speed CMOS and BiCMOS technology and produces a broad line of products. This enables us to provide complete CMOS and BiCMOS solutions to designers of high-performance digital systems. Not only do our product lines include industry standard devices, they also feature products with faster speeds, lower power, and package and/ or architectural benefits that allow designers to significantly improve system performance.

**To find ordering information:** Ordering Information for all products in this book appears in Section 1, along with the Product Selector Matrix, Package Marking Description, and Functional Cross Reference. Reference data on our Technology Capabilities, Quality Commitments, and Package Diagram Outlines is included in Sections 2, 3, and 4 respectively.

To find product data: Begin with the Table of Contents (page 1.2), Product Selector Matrix (page 1.6), or with the Numeric Table of Contents (page 1.3). The Product Selector Matrix will help you identify the device you are interested in, while the Table of Contents indexes will direct you to the page on which the complete technical data sheet can be found. Data sheets may be of the following type:

**ADVANCE INFORMATION**—contain initial descriptions (subject to change) for products that are in development, including features, block diagrams, and target specifications.

**PRELIMINARY**—contain descriptions for products soon to be or recently, released to production, including features, pinouts, and block diagrams. Timing data are based on simulation or initial characterization and are subject to change upon full characterization.

FINAL—contain minimum and maximum limits specified over the complete voltage supply and temperature range for full production devices.

New products, product performance enhancements, additional package types, and new product families are being introduced frequently. Please contact your local IDT sales representative to determine the latest device specifications, package types, and product availability.

## LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an office of IDT.

- 1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Note: Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

The IDT logo is a registered trademark and BiCameral, BurstRAM, BUSMUX, CacheRAM, DECnet, Double-Density, FASTX, Four-Port, FLEXI-CACHE, Flexi-PAK, Flow-thruEDC, IDT/c, IDTenvY, IDT/sae, IDT/sim, IDT/ux, MacStation, MICROSLICE, Orion, PalatteDAC, REAL8, R3041, R3051, R3052, R3081, R3721, R4400, R4600, RISCompiler, RISController, RISCore, RISC Subsystem, RISC Windows, SARAM, SmartLogic, SyncFIFO, SyncBiFIFO, SPC, TargetSystem and WideBus are trademarks of Integrated Device Technology, Inc. MIPS is a registered trademark of MIPS Computer Systems, Inc

All others are trademarks of their respective companies.

1.1

# 1994 SRAM DATA BOOK TABLE OF CONTENTS

## PAGE

# **GENERAL INFORMATION**

| Contents Overview               | 1.1 |

|---------------------------------|-----|

| Table of Contents               | 1.2 |

| Numeric Table of Contents       | 1.3 |

| Ordering Information            | 1.4 |

| IDT Package Marking Description | 1.5 |

| SRAM Product Selector Matrix    |     |

| Functional Cross Reference      | 1.7 |

# **TECHNOLOGY AND CAPABILITIES**

| IDTLeading the CMOS Future                   | 2.1 |

|----------------------------------------------|-----|

| IDT Military and DESC-SMD Program            | 2.2 |

| Radiation Hardened Technology                | 2.3 |

| IDT Leading Edge CMOS Technology             |     |

| Surface Mount Technology                     | 2.5 |

| State-of-the-Art Facilities and Capabilities | 2.6 |

| Superior Quality and Reliability             |     |

# QUALITY AND RELIABILITY

| Quality, Service and Performance                                         | 3.1 |

|--------------------------------------------------------------------------|-----|

| IDT Quality Conformance Program                                          | 3.2 |

| Radiation Tolerant/Enhanced/Hardened Products for Radiation Environments | 3.3 |

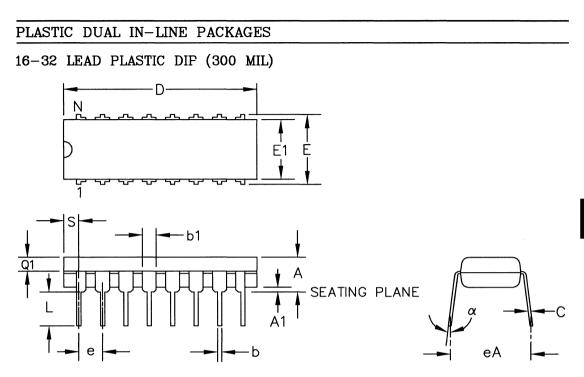

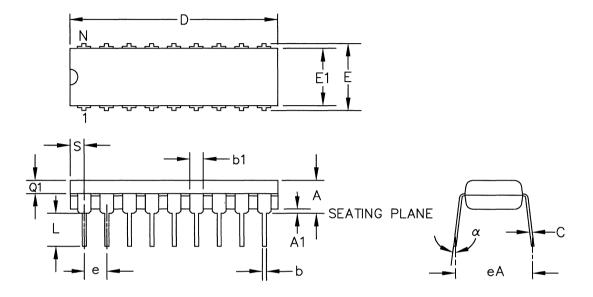

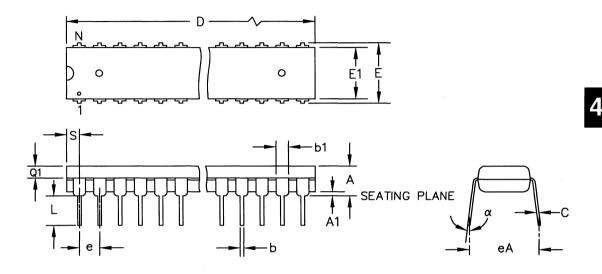

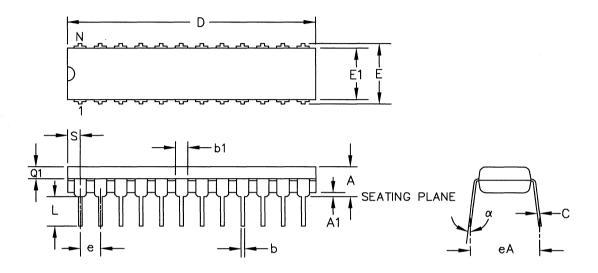

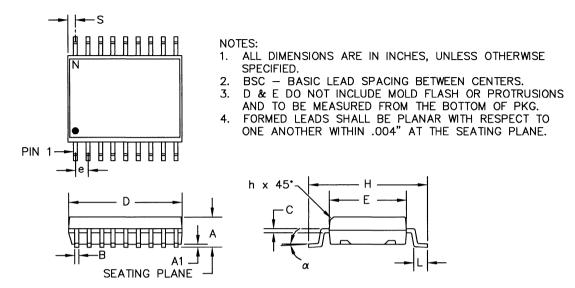

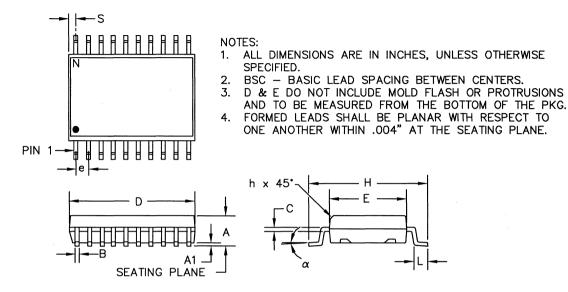

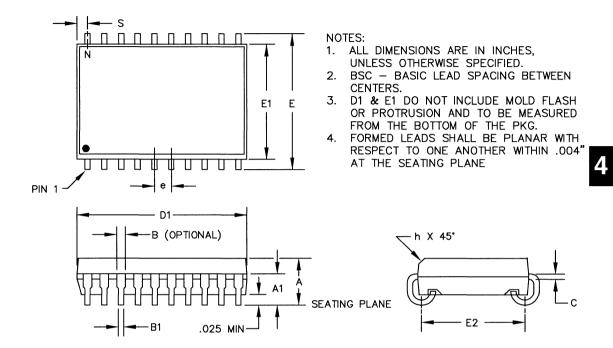

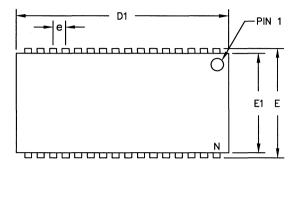

# PACKAGE DIAGRAM OUTLINES

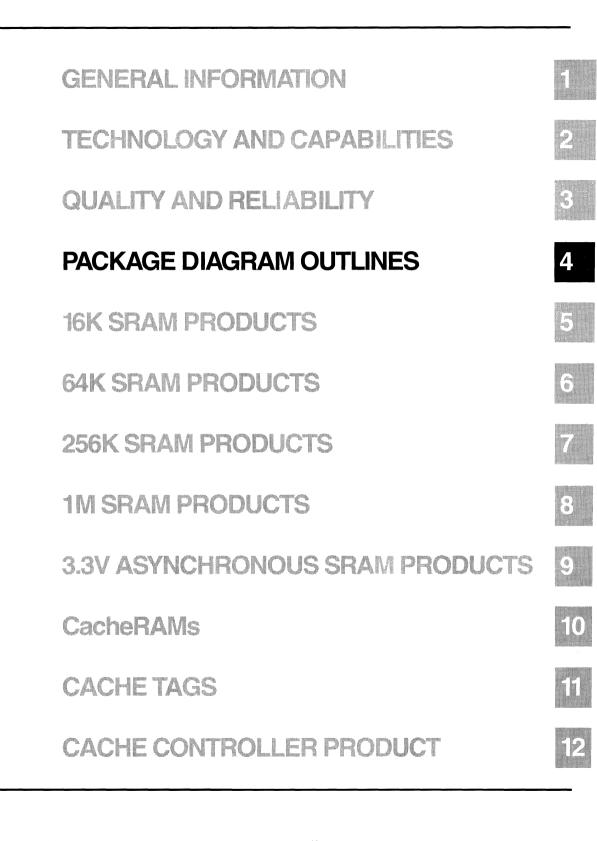

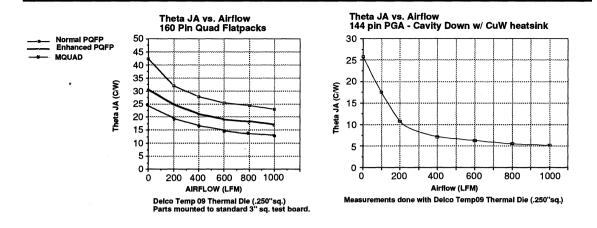

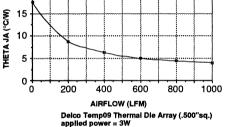

| Thermal Performance Calculations for IDT's Packages | 4.1 |

|-----------------------------------------------------|-----|

| Package Diagram Outline Index                       | 4.2 |

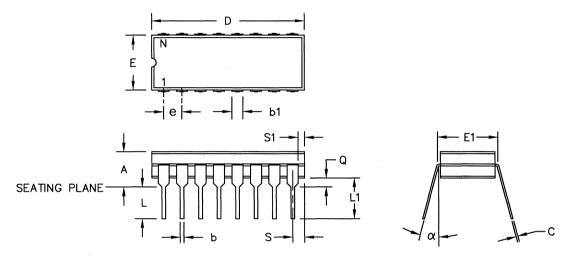

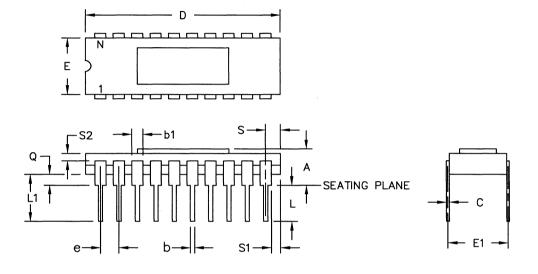

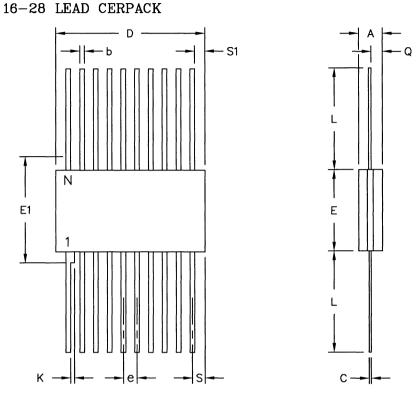

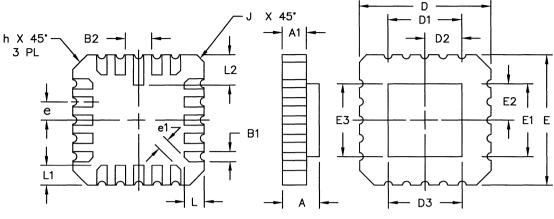

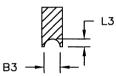

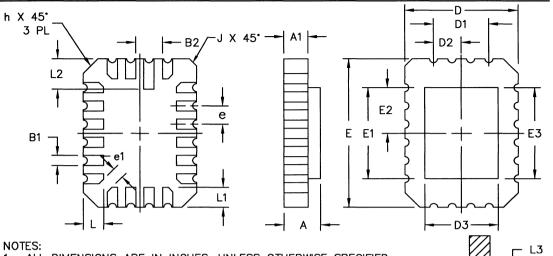

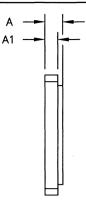

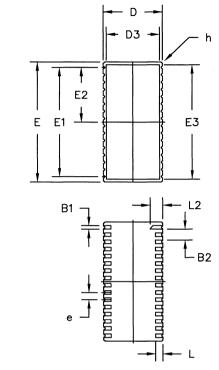

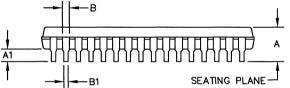

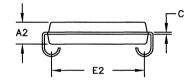

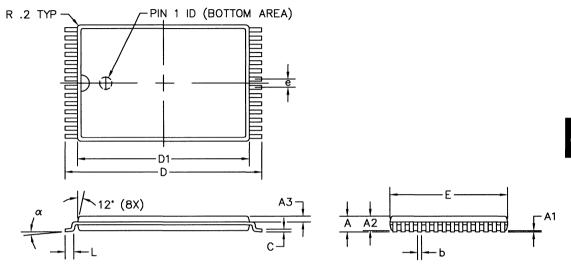

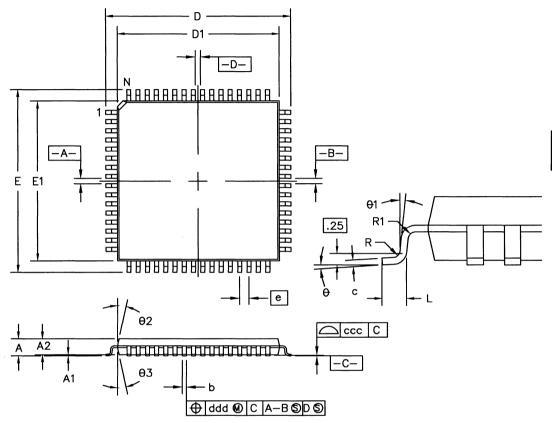

| Monolithic Package Diagram Outlines                 | 4.3 |

# **16K SRAM PRODUCTS**

| IDT6167  | 16K x 1 CMOS                           | 5.1 |

|----------|----------------------------------------|-----|

| IDT6168  | 4K x 4 CMOS                            | 5.2 |

| IDT71681 | 4K x 4 CMOS with Separate Input/Output | 5.3 |

| IDT71682 | 4K x 4 CMOS with Separate Input/Output | 5.3 |

| IDT6116  | 2K x 8 CMOS                            | 5.4 |

# 64K SRAM PRODUCTS

| IDT7187 | 64K x 1 CMOS                                         | 6.1 |

|---------|------------------------------------------------------|-----|

| IDT7188 | 16K x 4 CMOS                                         | 6.2 |

| IDT6198 | 16K x 4 CMOS with Output Enable                      | 6.3 |

| IDT7198 | 16K x 4 CMOS with Output Enable and $\overline{CS2}$ | 6.4 |

| IDT7164 | 8K x 8 CMOS                                          | 6.5 |

|         |                                                      |     |

# 256K SRAM PRODUCTS

| IDT61298SA | 64K x 4 CMOS | 7.1 |

|------------|--------------|-----|

| IDT71256   | 32K x 8 CMOS | 7.2 |

| IDT71256SA | 32K x 8 CMOS | 7.3 |

1.2

# 1994 SRAM DATA BOOK (Continued)

# **1M SRAM PRODUCTS**

| IDT71028 | 256K x 4 CMOS | 8.1 |  |

|----------|---------------|-----|--|

| IDT71024 | 128K x 8 CMOS | 8.2 |  |

|          |               |     |  |

## 3.3V ASYNCHRONOUS SRAM PRODUCTS

| IDT71V256SA | 32K x 8 CMOS 3.3V | 9.1 |

|-------------|-------------------|-----|

| IDT71V256SL | 32K x 8 CMOS 3.3V | 9.2 |

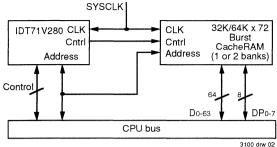

## CacheRAMs

| IDT71419  | 32K x 18 BiCMOS CacheRAM <sup>™</sup> for PowerPC <sup>™</sup> Processors | 10.1 |

|-----------|---------------------------------------------------------------------------|------|

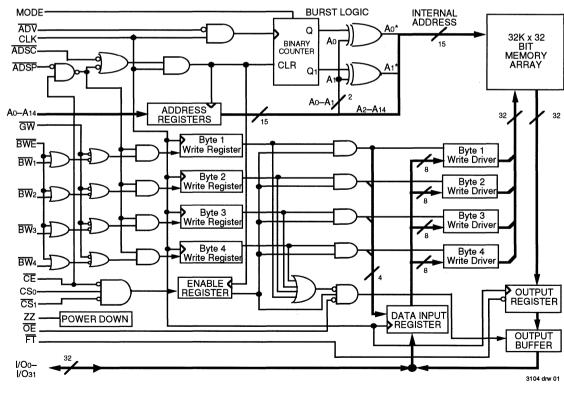

| IDT71420  | 32K x 18 BiCMOS CacheRAM for Pentium <sup>™</sup> Processors              | 10.2 |

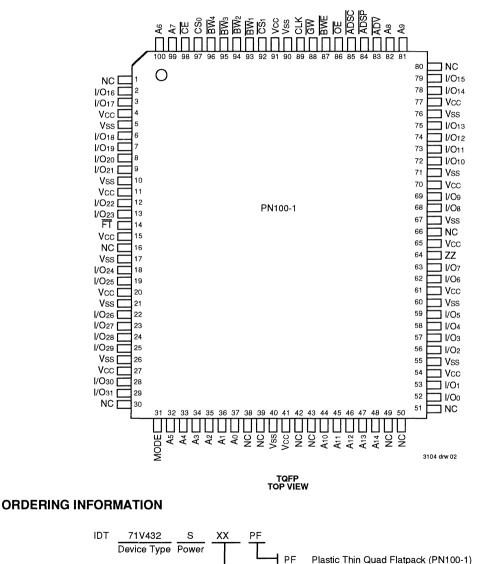

| IDT71V432 | 32K x 32 CMOS 3.3V Pipelined CacheRAM for Pentium Processors              | 10.3 |

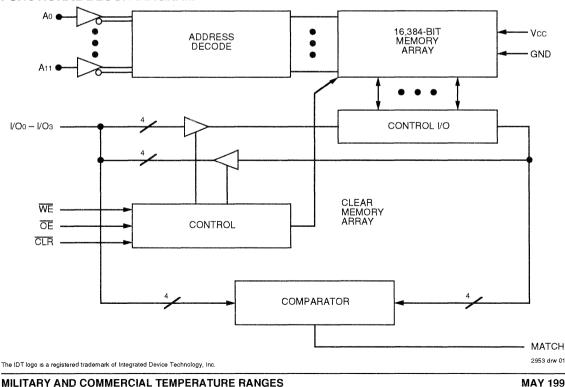

# Cache Tags

| IDT6178<br>IDT71B74 | 4K x 4 CMOS Cache Tag<br>8K x 8 BiCMOS Cache Tag          |      |

|---------------------|-----------------------------------------------------------|------|

| IDT71215            | 16K x 15 BiCMOS Cache Tag for Pentium Processors          |      |

| IDT71216            | 16K x 15 BiCMOS Cache Tag for PowerPC and RISC Processors | 11.4 |

## **Cache Controller PRODUCT**

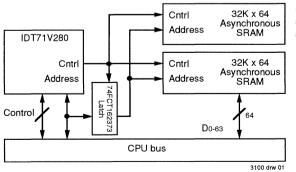

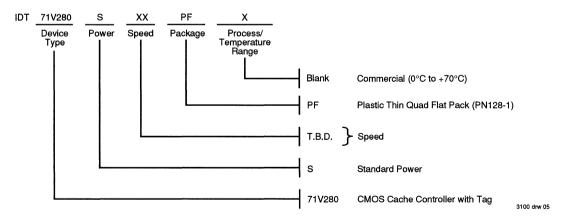

IDT71V280 16K x 10 CMOS 3.3V Cache Controller with Tag for Pentium Processors ...... 12.1

# IDT SALES OFFICE, REPRESENTATIVE AND DISTRIBUTOR LOCATIONS

# NUMERICAL TABLE OF CONTENTS

## PART NO.

| IDT6116     | 2K x 8 CMOS                                                         | 5.4  |

|-------------|---------------------------------------------------------------------|------|

| IDT6167     | 16K x 1 CMOS                                                        | 5.1  |

| IDT6168     | 4K x 4 CMOS                                                         | 5.2  |

| IDT6178     | 4K x 4 CMOS Cache Tag                                               | 11.1 |

| IDT6198     | 16K x 4 CMOS with Output Enable                                     | 6.3  |

| IDT61298SA  | 64K x 4 CMOS                                                        | 7.1  |

| IDT7164     | 8K x 8 CMOS                                                         | 6.5  |

| IDT7187     | 64K x 1 CMOS                                                        | 6.1  |

| IDT7188     | 16K x 4 CMOS                                                        | 6.2  |

| IDT7198     | 16K x 4 CMOS with Output Enable and CS2                             | 6.4  |

| IDT71024    | 128K x 8 CMOS                                                       | 8.2  |

| IDT71028    | 256K x 4 CMOS                                                       | 8.1  |

| IDT71215    | 16K x 15 BiCMOS Cache Tag for Pentium Processors                    | 11.3 |

| IDT71216    | 16K x 15 BiCMOS Cache Tag for PowerPC and RISC Processors           | 11.4 |

| IDT71256    | 32K x 8 CMOS                                                        | 7.2  |

| IDT71256SA  | 32K x 8 CMOS                                                        | 7.3  |

| IDT71419    | 32K x 18 BiCMOS CacheRAM for PowerPC Processors                     | 10.1 |

| IDT71420    | 32K x 18 BiCMOS CacheRAM for Pentium Processors                     | 10.2 |

| IDT71681    | 4K x 4 CMOS with Separate Input/Output                              | 5.3  |

| IDT71682    | 4K x 4 CMOS with Separate Input/Output                              | 5.3  |

| IDT71B74    | 8K x 8 BiCMOS Cache Tag                                             | 11.2 |

| IDT71V256SA | 32K x 8 CMOS 3.3V                                                   | 9.2  |

| IDT71V256SL | 32K x 8 CMOS 3.3V                                                   | 9.1  |

| IDT71V280   | 16K x 10 CMOS 3.3V Cache Controller with Tag for Pentium Processors | 12.1 |

| IDT71V432   | 32K x 32 CMOS 3.3V Pipelined CacheRAM for Pentium Processors        | 10.3 |

|             |                                                                     |      |

PAGE

## **ORDERING INFORMATION**

When ordering by TWX or Telex, the following format must be used:

- A. Complete Bill To.

- B. Complete Ship To.

- C. Purchase Order Number.

- D. Certificate of Conformance. Y or N.

- E. Customer Source Inspection. Y or N.

- F. Government Source Inspection. Y or N

- G. Government Contract Number and Rating.

- H. Requested Routing.

- IDT Part Number –

Each item ordered must use the complete part number exactly as listed in the price book.

- J. SCD Number Specification Control Document (Internal Traveller).

- K. Customer Part Number/Drawing Number/Revision Level -

Specify whether part number is for reference only, mark only, or if extended processing to customer specification is required.

- L. Customer General Specification Numbers/Other Referenced Drawing Numbers/Revision Levels.

- M. Request Date With Exact Quantity.

- N. Unit Price.

- O. Special Instructions, Including Q.A. Clauses, Special Processing.

Federal Supply Code Number/Cage Number - 61772

Dun & Bradstreet Number - 03-814-2600

Federal Tax I.D. - 94-2669985

TLX# — 887766

FAX# --- 408-727-3468

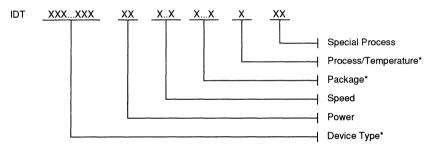

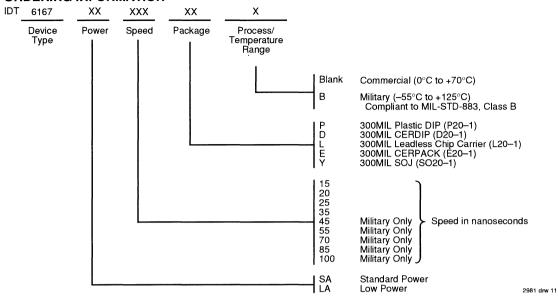

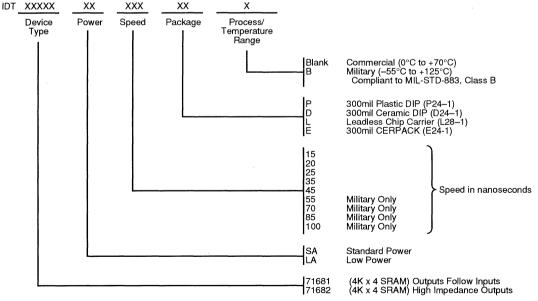

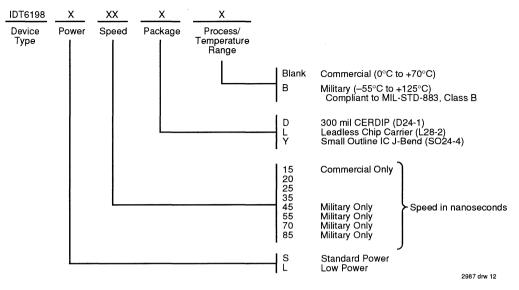

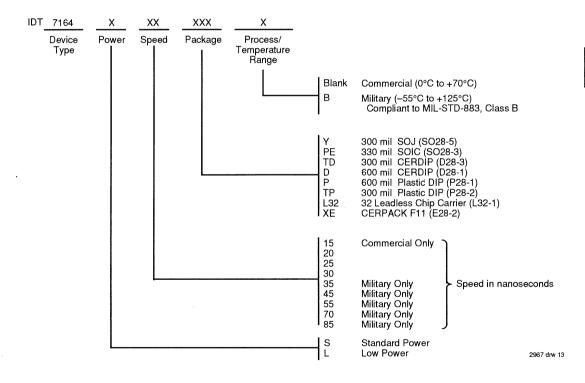

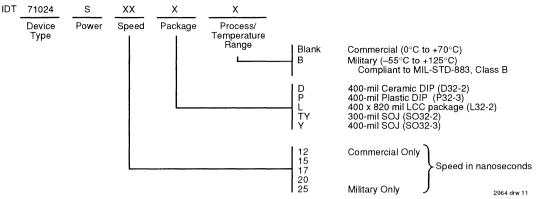

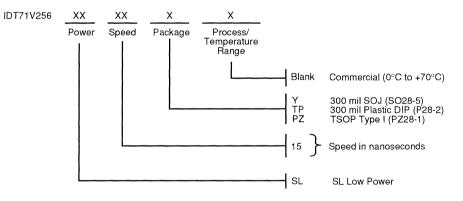

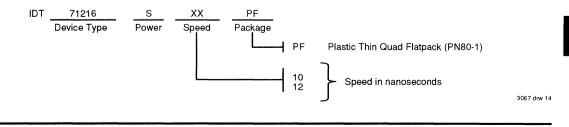

# PART NUMBER DESCRIPTION

A = Alpha Character N = Numeric Character

# **IDT PACKAGE MARKING DESCRIPTION**

## PART NUMBER DESCRIPTION

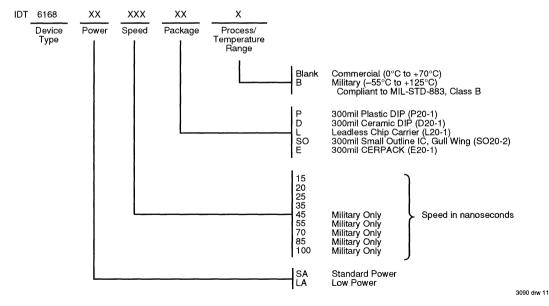

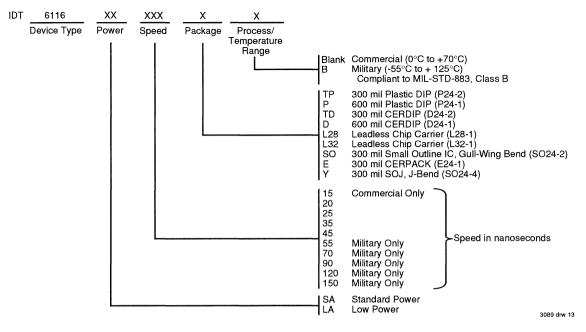

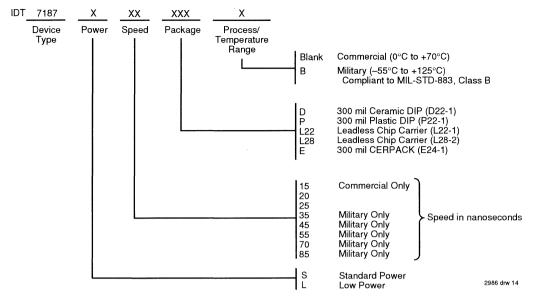

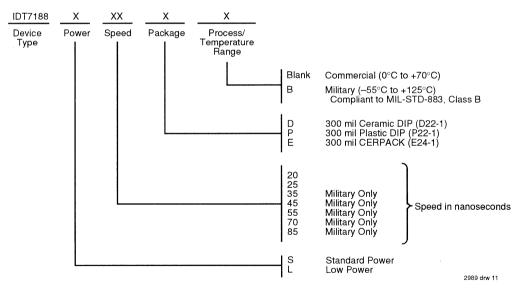

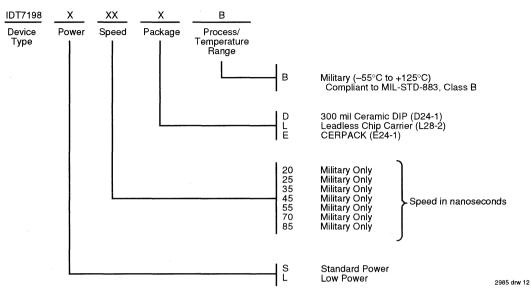

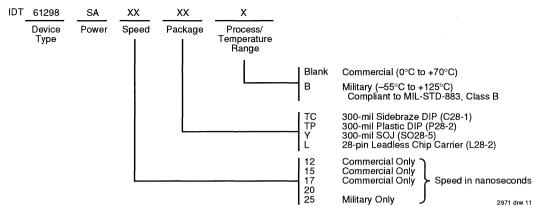

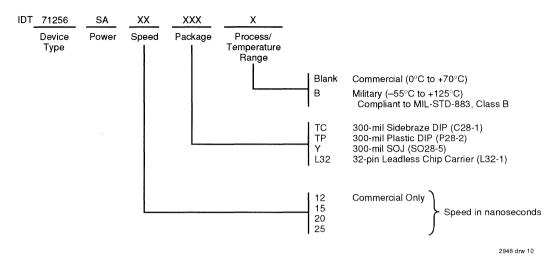

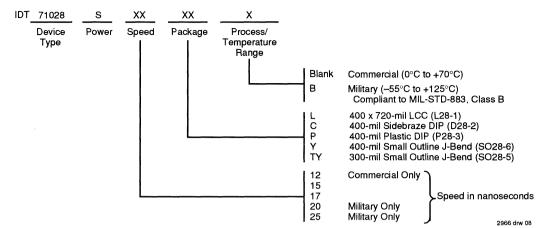

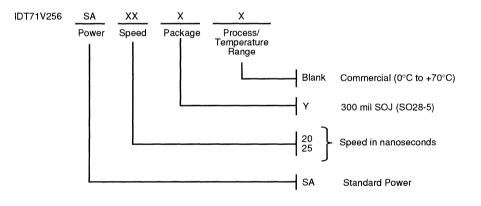

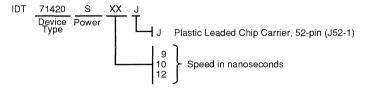

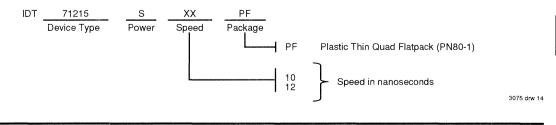

IDT's part number identifies the basic product, speed, power, package(s) available, operating temperature and processing grade. Each data sheet has a detailed description, using the part number, for ordering the proper product for the user's application. The part number is comprised of a series of alpha-numeric characters:

- 1. An "IDT" corporate identifier for Integrated Device Technology, Inc.

- 2. A basic device part number composed of alpha-numeric characters.

- A device power identifier, composed of one or two alpha characters, is used to identify the power options. In most cases, the following alpha characters are used: "S" or "SA" is used for the standard power product.

"L" or "LA" is used for lower power than the standard power product.

- A device speed identifier, when applicable, is either alpha characters, such as "A" or "B", or numbers, such as 20 or 45. The speed units, depending on the product, are in nanoseconds or megahertz.

- 5. A package identifier, composed of one or two characters. The data sheet should be consulted to determine the packages available and the package identifiers for that particular product.

- 6. A temperature/process identifier. The product is available in either the commercial or military temperature range, processed to a commercial specification, or the product is available in the military temperature range with full compliance to MIL-STD-883. Many of IDT's products have burn-in included as part of the standard commercial process flow.

- 7. A special process identifier, composed of alpha characters, is used for products which require radiation enhancement (RE) or radiation tolerance (RT).

Example for Monolithic Devices:

\* Field Identifier Applicable To All Products

## ASSEMBLY LOCATION DESIGNATOR

IDT uses various locations for assembly. These are identified by an alpha character in the last letter of the date code marked on the package. Presently, the assembly location alpha character is as follows:

- A = Anam, Korea

- I = USA

- P = Penang, Malaysia

## MIL-STD-883C COMPLIANT DESIGNATOR

IDT ships military products which are compliant to the latest revision of MIL-STD-883C. Such products are identified by a "C" designation on the package. The location of this designator is specified by internal documentation at IDT.

| Size/               |          |                                  |              | Part   |       | Speed          | Speeds (ns) Commercial                   |      |     | Speeds (ns) Commercial |      |      | Militar | y I  |      |       |      |

|---------------------|----------|----------------------------------|--------------|--------|-------|----------------|------------------------------------------|------|-----|------------------------|------|------|---------|------|------|-------|------|

| Function            | Org.     | Features                         | Process      | Number | Power | Commercial     | Military                                 | PDIP | SOJ | SOIC                   | TSOP | TQFP | PLCC    | SBRZ | CDIP | LCC   | CPAK |

| 16K                 | 16K x 1  |                                  | CMOS         | 6167   | SA/LA | 15,20,25,35    | 15,20,25,35,<br>45,55,70,85,100          | 20   | 20  | -                      | -    | —    | -       | -    | 20   | 20    | 20   |

|                     | 4K x 4   |                                  | CMOS         | 6168   | SA/LA | 15,20,25,35    | 15,20,25,35,<br>45,55,70,85,100          | 20   | -   | 20                     |      |      | —       |      | 20   | 20    | 20   |

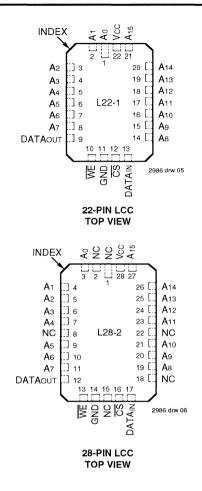

|                     | 4K x 4   | Sep I/O                          | CMOS         | 71681  | SA/LA | 15,20,25,35,45 | 15,20,25,35,<br>45,55,70,85,100          | 24   | _   | -                      |      |      | —       | -    | 24   | 28    | 24   |

|                     | 4K x 4   | Sep I/O                          | CMOS         | 71682  | SA/LA | 15,20,25,35,45 | 12,15,20,25,35,<br>45,55,70,85,100       | 24   | -   | _                      | _    | _    | -       | —    | 24   | 28    | 24   |

|                     | 2K x 8   |                                  | CMOS         | 6116   | SA/LA | 15,20,25,35,45 | 20,25,35,45,<br>55,70,90,120,150         | 24   | 24  | 24                     | _    |      | _       | _    | 24   | 28/32 | 24   |

| 64K                 | 64K x 1  |                                  | CMOS         | 7187   | S/L   | 15,20,25       | 20,25,35,<br>45,55,70,85                 | 22   | —   | —                      |      |      | _       |      | 22   | 22/28 | 24   |

|                     | 16K x 4  |                                  | CMOS         | 7188   | S/L   | 20,25          | 20,25,35,<br>45,55,70,85                 | 22   | —   | _                      |      |      | -       | —    | 22   | -     | 24   |

|                     | 16K x 4  | ŌĒ                               | CMOS         | 6198   | S/L   | 15,20,25,35    | 20,25,35,<br>45,55,70,85                 | -    | 24  |                        |      |      | -       | —    | 24   | 28    | —    |

|                     | 16K x 4  | OE, CS2                          | CMOS         | 7198   | S/L   | N/A            | 20,25,35,<br>45,55,70,85                 |      |     | _                      |      |      |         | -    | 24   | 28    | 24   |

|                     | 8K x 8   |                                  | CMOS         | 7164   | S/L   | 15,20,25,30    | 20,25,30,35,<br>45,55,70,85              | 28   | 28  | 28                     | -    | -    | -       | -    | 28   | 32    | 28   |

| 256K                | 64K x 4  |                                  | CMOS         | 61298  | SA    | 12,15,17,20    | 20,25                                    | 28   | 28  |                        | _    |      |         | 28   |      | 28    |      |

|                     | 32K x 8  |                                  | CMOS         | 71256  | S/L   | 20,25,35,45    | 25,30,35,45,<br>55,70,85,<br>100,120,150 | 28   | 28  | _                      | _    | -    |         | 28   | 28   | 28/32 | 28   |

|                     | 32K x 8  |                                  | CMOS         | 71256  | SA    | 12,15,20,25    | 15,20,25                                 | 28   | 28  |                        | _    |      |         | 28   |      | 32    | —    |

| 1M                  | 256K x 4 |                                  | CMOS         | 71028  | S/L   | 12,15,17       | 15,17,20,25                              | 28   | 28  | —                      | _    | -    |         | _    | 28   | 28    |      |

|                     | 128K x 8 |                                  | CMOS         | 71024  | S/L   | 12,15,17,20    | 15,17,20,25                              | 32   | 32  |                        | _    |      | -       | _    | 32   | 32    |      |

| 3.3V                | 32K x 8  | 3.3V                             | 3.3V CMOS    | 71V256 | SA    | 20,25          | N/A                                      |      | 28  | -                      |      |      |         | 1    | -    | -     | —    |

| SRAMs               | 32K x 8  | 3.3V                             | 3.3V CMOS    | 71V256 | SL    | 15             | N/A                                      | 28   | 28  |                        | 28   |      |         |      |      | -     | —    |

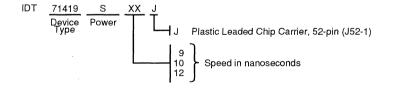

| Cache<br>SRAMs      | 32K x 18 | PowerPC<br>Burst                 | BiCMOS       | 71419  | S     | 9,10,12        | N/A                                      | _    |     | . —                    | _    |      | 52      | —    | -    | -     | —    |

|                     | 32K x 18 | Intel<br>Burst                   | BiCMOS       | 71420  | S     | 9,10,12        | N/A                                      | _    | -   | -                      | _    | _    | 52      |      |      | -     | -    |

|                     | 32K x 32 | 3.3V Intel<br>Pipelined<br>Burst | 3.3V<br>CMOS | 71V432 | S     | 9,10,12        | N/A                                      | _    | _   | _                      |      | 100  |         |      |      |       | _    |

| Cache               | 4K x 4   | Tag                              | CMOS         | 6178   | S     | 10,12,15,20,25 | N/A                                      | 22   | 24  |                        |      |      |         |      | 22   | -     | _    |

| Tags                | 8K x 8   | Tag                              | BICMOS       | 71B74  | S     | 8,10,12,15,20  | N/A                                      | 28   | 28  |                        |      | _    | -       |      |      | -     |      |

|                     | 16K x 15 | Intel Tag                        | BICMOS       | 71215  | S     | 10,12          | N/A                                      |      | —   |                        | _    | 80   | -       |      |      | -     | —    |

|                     | 16K x 15 | PwrPC Tag                        | BICMOS       | 71216  | S     | 10,12          | N/A                                      |      | _   | —                      |      | 80   | _       | —    | _    |       | —    |

| Cache<br>Controller | 16K x 10 | 3.3V<br>Controller<br>w/Tag      | 3.3V<br>CMOS | 71V280 | S     | 66MHz          | N/A                                      | —    | -   | _                      |      | 128  | _       |      |      | -     | -    |

1.6

----

# SRAM FUNCTIONAL CROSS REFERENCE GUIDE

**Note:** This cross reference guide reflects Functional Correlation ONLY. Please refer to the individual data sheet specifications to ensure that the IDT device meets your parametric and packaging requirements.

| ALLIANCE | IDT         | DESCRIPTION      |

|----------|-------------|------------------|

| AS7C256  | IDT71256SA  | 32K x 8 🖏        |

| AS7C3256 | IDT71V256SL | 32K x 8 - 3.3V   |

| AS7C3256 | IDT71V256SA | 32K x 8 — 3.3V   |

| AT&T     | IDT         | DESCRIPTION      |

| ATT7C167 | IDT6167     | 16K x 1          |

| ATT7C168 | IDT6168     | 4K x 4           |

| ATT7C171 | IDT71681    | 4K x 4 Sep I/O   |

| ATT7C172 | IDT71682    | 4K x 4 Sep I/O   |

| ATT7C116 | IDT6116     | 2K x 8           |

| ATT7C187 | IDT7187     | 64K x 1          |

| ATT7C164 | IDT7188     | 16K x 4          |

| ATT7C166 | IDT6198     | 16K x 4 OE       |

| ATT7C165 | IDT7198     | 16K x 4 OE/CS2   |

| ATT7C185 | IDT7164     | 8K x 8           |

| ATT7C195 | IDT61298SA  | 64K x 4 OE       |

| ATT7C199 | IDT71256    | 32K x 8          |

| ATT7C199 | IDT71256SA  | 32K x 8          |

| ATT7C106 | IDT71028    | 256K x 4 OE      |

| ATT7C109 | IDT71024    | 128K x 8         |

| ATT7C180 | IDT6178     | 4K x 4 Cache Tag |

| ATT7C174 | IDT71B74    | 8K x 8 Cache Tag |

| CYPRESS  | IDT         | DESCRIPTION      |

| CY7C167  | IDT6167     | 16K x 1          |

| CY7C167A | IDT6167     | 16K x 1          |

| CY7C168  | IDT6168     | 4K x 4           |

| CY7C168A | IDT6168     | 4K x 4           |

| CY7C169  | IDT6168     | 4K x 4           |

| CY7C169A | IDT6168     | 4K x 4           |

| CY7C171  | IDT71681    | 4K x 4 Sep I/O   |

| CY7C171A | IDT71681    | 4K x 4 Sep I/O   |

| CY7C172  | IDT71682    | 4K x 4 Sep I/O   |

| CY7C172A | IDT71682    | 4K x 4 Sep I/O   |

| CY7C128  | IDT6116     | 2K x 8           |

| CY7C128A | IDT6116     | 2K x 8           |

| CY7C187  | IDT7187     | 64K x 1          |

| CY7C187A | IDT7187     | 64K x 1          |

| CY7C164  | IDT7188     | 16K x 4          |

| CY7C164A | IDT7188     | 16K x 4          |

| CY7C166  | IDT6198     | 16K x 4 OE       |

| CYPRESS       | IDT         | DESCRIPTION           |

|---------------|-------------|-----------------------|

| CY7C166A      | IDT6198     | 16K x 4 OE            |

| CY7C185       | IDT7164     | 8K x 8                |

| CY7C185A      | IDT7164     | 8K x 8                |

| CY7C186       | IDT7164     | 8K x 8                |

| CY7C186A      | IDT7164     | 8K x 8                |

| CY7C195       | IDT61298SA  | 64K x 4 OE            |

| CY7B195       | IDT61298SA  | 64K x 4 OE            |

| CY7C198       | IDT71256    | 32K x 8               |

| CY7C198       | IDT71256SA  | 32K x 8               |

| CY7C199       | IDT71256    | 32K x 8               |

| CY7C199       | IDT71256SA  | 32K x 8               |

| CY7B198       | IDT71256SA  | 32K x 8               |

| CY7B199       | IDT71256SA  | 32K x 8               |

| CYC1399       | IDT71V256SL | 32K x 8 3.3V          |

| CYC1399       | IDT71V256SA | 32K x 8 — 3.3V        |

| CY7C106       | IDT71028    | 256K x 4 OE           |

| CY7C109       | IDT71024    | 128K x 8              |

| CY7C178       | IDT71420    | 32K x 18 — Burst Pent |

| EDI           | IDT         | DESCRIPTION           |

| EDI8164       | IDT7187     | 64K x 1               |

| EDI8416       | IDT7188     | 16K x 4               |

| ED18417       | IDT6198     | 16K x 4 OE            |

| ED18808CB     | IDT7164     | 8K x 8                |

| EDI8466CA     | IDT61298SA  | 64K x 4 OE            |

| EDI8466CB     | IDT61298SA  | 64K x 4 OE            |

| ED18833C      | IDT71256    | 32K x 8               |

| ED18833C      | IDT71256SA  | 32K x 8               |

| EDI8833LP     | IDT71256    | 32K x 8               |

| EDI8833LP     | IDT71256SA  | 32K x 8               |

| ED18833P      | IDT71256    | 32K x 8               |

| ED18833P      | IDT71256SA  | 32K x 8               |

| ED18834C      | IDT71256    | 32K x 8               |

| EDI8834C      | IDT71256SA  | 32K x 8               |

| EDI8834CA     | IDT71256    | 32K x 8               |

| EDI8834CA     | IDT71256SA  | 32K x 8               |

| ED184256CS    | IDT71028    | 256K x 4 OE           |

| EDI84256LPS   | IDT71028    | 256K x 4 OE           |

| ED184256PS    | IDT71028    | 256K x 4 OE           |

| EDI88130C     | IDT71024    | 128K x 8              |

| EDI88130LP    | IDT71024    | 128K x 8              |

| EDI88130P     | IDT71024    | 128K x 8              |

| EDI88130CS    | IDT71024    | 128K x 8              |

| EDI88130LPS   | IDT71024    | 128K x 8              |

| 25/00/10/21/0 |             | .2017.7.0             |

| EDI        | IDT        | DESCRIPTION           | INMOS      | IDT         | DESCRIPTION      |

|------------|------------|-----------------------|------------|-------------|------------------|

| EDI88130PS | IDT71024   | 128K x 8              | IMS1625    | IDT7188     | 16K x 4          |

| FUJITSU    | IDT        | DESCRIPTION           | IMS1624    | IDT6198     | 16K x 4 OE       |

| MB81C67    | IDT6167    | 16K x 1               | IMS1629    | IDT6198     | 16K x 4 OE       |

| MB81C68A   | IDT6168    | 4K x 4                | IMS1630    | IDT7164     | 8K x 8           |

| MB81C69A   | IDT6168    | 4K x 4                | IMS1635    | IDT7164     | 8K x 8           |

| MB81C71    | IDT7187    | 64K x 1               | LOGIC      | IDT         | DESCRIPTION      |

| MB81C71A   | IDT7187    | 64K x 1               | L7C167     | IDT6167     | 16K x 1          |

| MB81C74    | IDT7188    | 16K x 4               | L7C168     | IDT6168     | 4K x 4           |

| MB81C75    | IDT6198    | 16K x 4 OE            | L7C171     | IDT71681    | 4K x 4 Sep I/O   |

| MB81C78A   | IDT7164    | 8K x 8                | L7C172     | IDT71682    | 4K x 4 Sep I/O   |

| MB82B78    | IDT7164    | 8K x 8                | L6116      | IDT6116     | 2K x 8           |

| MB81C84A   | IDT61298SA | 64K x 4 OE            | L6116L     | IDT6116     | 2K x 8           |

| MB82B85    | IDT61298SA | 64K x 4 OE            | L7C187     | IDT7187     | 64K x 1          |

| MB8298     | IDT71256   | 32K x 8               | L7C164     | IDT7188     | 16K x 4          |

| MB8298     | IDT71256SA | 32K x 8               | L7C166     | IDT6198     | 16K x 4 OE       |

| MB82B88    | IDT71256SA | 32K x 8               | L7C165     | IDT7198     | 16K x 4 OE/CS2   |

| MB82B005   | IDT71028   | 256K x 4 OE           | L7C185     | IDT7164     | 8K x 8           |

| MB82B008   | IDT71024   | 128K x 8              | L7CL185    | IDT7164     | 8K x 8           |

| HITACHI    | IDT        | DESCRIPTION           | L7C195     | IDT61298SA  | 64K x 4 OE       |

| HM6267     | IDT6167    | 16K x 1               | L7C199     | IDT71256    | 32K x 8          |

| HM6268     | IDT6168    | 4K x 4                | L7CL199    | IDT71256    | 32K x 8          |

| HM6716     | IDT6116    | 2K x 8                | L7C199     | IDT71256SA  | 32K x 8          |

| HM6287     | IDT7187    | 64K x 1               | L7CL199    | IDT71256SA  | 32K x 8          |

| HM6287H    | IDT7187    | 64K x 1               | L7C180     | IDT6178     | 4K x 4 Cache Tag |

| HM6787     | IDT7187    | 64K x 1               | L7C174     | IDT71B74    | 8K x 8 Cache Tag |

| HM6787H    | IDT7187    | 64K x 1               | MICRON     | IDT         | DESCRIPTION      |

| HM6288     | IDT7188    | 16K x 4               | MT5C1601   | IDT6167     | 16K x 1          |

| HM6788     | IDT7188    | 16K x 4               | MT5C1604   | IDT6168     | 4K x 4           |

| HM6788H    | IDT7188    | 16K x 4               | MT5C1606   | IDT71681    | 4K x 4 Sep I/O   |

| HM6289     | IDT6198    | 16K x 4 OE            | MT5C1607   | IDT71682    | 4K x 4 Sep I/O   |

| HM6789     | IDT6198    | 16K x 4 OE            | MT5C1608   | IDT6116     | 2K x 8           |

| HM6789H    | IDT6198    | 16K x 4 OE            | MT5C6401   | IDT7187     | 64K x 1          |

| HM6709A    | IDT61298SA | 64K x 4 OE            | MT5C6404   | IDT7188     | 16K x 4          |

| HM62832H   | IDT71256   | 32K x 8               | MT5C6405   | IDT6198     | 16K x 4 OE       |

| HM62832H   | IDT71256SA | 32K x 8               | MT5C6408   | IDT7164     | 8K x 8           |

| HM62832UH  | IDT71256SA | 32K x 8               | MT5C2565   | IDT61298SA  | 64K x 4 OE       |

| HM62832UHL | IDT71256SA | 32K x 8               | MT5C2568   | IDT71256    | 32K x 8          |

| HM624256A  | IDT71028   | 256K x 4 OE           | MT5C2568   | IDT71256SA  | 32K x 8          |

| HM628127H  | IDT71024   | 128K x 8              | MT5LC2568  | IDT71V256SL | 32K x 8 — 3.3V   |

| IC WORKS   | IDT        | DESCRIPTION           | MT5LC2568  | IDT71V256SA | 32K x 8 — 3.3V   |

| ICW73B586A | IDT71420   | 32K x 18 — Burst Pent | MT5C1005   | IDT71028    | 256K x 4 OE      |

| ICW73B586B | IDT71420   | 32K x 18 — Burst Pent | MT5C1008   | IDT71024    | 128K x 8         |

| INMOS      | IDT        | DESCRIPTION           | MITSUBISHI | IDT         | DESCRIPTION      |

| IMS1403    | IDT6167    | 16K x 1               | M5M21C67   | IDT6167     | 16K x 1          |

| IMS1423    | IDT6168    | 4K x 4                | M5M21C68   | IDT6168     | 4K x 4           |

| IMS1600    | IDT7187    | 64K x 1               | M5M5187A   | IDT7187     | 64K x 1          |

| IMS1605    | IDT7187    | 64K x 1               | M5M5187B   | IDT7187     | 64K x 1          |

| IMS1620    | IDT7188    | 16K x 4               | M5M5188A   | IDT7188     | 16K x 4          |

| MITSUBISHI          | IDT         | DESCRIPTION            |

|---------------------|-------------|------------------------|

| M5M5188B            | IDT7188     | 16K x 4                |

| M5M5189A            | IDT6198     | 16K x 4 OE             |

| M5M5189B            | IDT6198     | 16K x 4 OE             |

| M5M5178             | IDT7164     | 8K x 8                 |

| M5M5178A            | IDT7164     | 8K x 8                 |

| M5M5178B            | IDT7164     | 8K x 8                 |

| M5M5259B            | IDT61298SA  | 64K x 4 OE             |

| M5M5278             | IDT71256    | 32K x 8                |

| M5M5278             | IDT71256SA  | 32K x 8                |

| M5M51004            | IDT71028    | 256K x 4 OE            |

| MOTOROLA            | IDT         | DESCRIPTION            |

| MCM6268             | IDT6168     | 4K x 4                 |

| MCM6287B            | IDT7187     | 64K x 1                |

| MCM6288             | IDT7188     | 16K x 4                |

| MCM6288B            | IDT7188     | 16K x 4                |

| MCM6288C            | IDT7188     | 16K x 4                |

| MCM6290             | IDT6198     | 16K x 4 OE             |

| MCM6290C            | IDT6198     | 16K x 4 OE             |

| MCM6264C            | IDT7164     | 8K x 8                 |

| MCM6209             | IDT61298SA  | 64K x 4 OE             |

| MCM6209C            | IDT61298SA  | 64K x 4 OE             |

| MCM6206             | IDT71256    | 32K x 8                |

| MCM6206C            | IDT71256    | 32K x 8                |

| MCM6206D            | IDT71256    | 32K x 8                |

| MCM6206             | IDT71256SA  | 32K x 8                |

| MCM6206C            | IDT71256SA  | 32K x 8                |

| MCM6206D            | IDT71256SA  | 32K x 8                |

| MCM62V06            | IDT71V256SL | 32K x 8 — 3.3V         |

| MCM62V06            | IDT71V256SA | 32K x 8 — 3.3V         |

| MCM6306D            | IDT71V256SL | 32K x 8 — 3.3V         |

| MCM6360D            | IDT71V256SA | 32K x 8 — 3.3V         |

| MCM6229             | IDT71028    | 256K x 4 OE            |

| MCM6229A            | IDT71028    | 256K x 4 OE            |

| MCM6229B            | IDT71028    | 256K x 4 OE            |

| MCM6226             | IDT71024    | 128K x 8               |

| MCM6226A            | IDT71024    | 128K x 8               |

| MCM67B518           | IDT71418    | 32K x 18 — Burst Pent  |

| MCM67M518           | IDT71419    | 32K x 18 — Burst PwrPC |

| MCM67H518           | IDT71420    | 32K x 18 — Burst Pent  |

| NEC                 | IDT         | DESCRIPTION            |

| uPD4311             | IDT6167     | 16K x 1                |

| uPD4314C            | IDT6168     | 4K x 4                 |

| uPD43140            | IDT7187     | 64K x 1                |

| uPD4361<br>uPD4361B | IDT7187     | 64K x 1                |

|                     |             |                        |

| uPD4362             | IDT7188     | 16K x 4                |

| uPD4362B            | IDT7188     | 16K x 4                |

| uPD4363             | IDT6198     | 16K x 4 OE             |

|             | l in z     |                       |

|-------------|------------|-----------------------|

| NEC         | IDT        | DESCRIPTION           |

| uPD4368     | IDT7164    | 8K x 8                |

| uPD43253    | IDT61298SA | 64K x 4 OE            |

| uPD43258    | IDT71256   | 32K x 8               |

| uPD43258A   | IDT71256   | 32K x 8               |

| uPD43258    | IDT71256SA | 32K x 8               |

| uPD43258A   | IDT71256SA | 32K x 8               |

| uPD431004   | IDT71028   | 256K x 4 OE           |

| uPD431008   | IDT71024   | 128K x 8              |

| PARADIGM    | IDT        | DESCRIPTION           |

| PDM41298    | IDT61298SA | 64K x 4 OE            |

| PDM41256    | IDT71256   | 32K x 8               |

| PDM41256    | IDT71256SA | 32K x 8               |

| PDM41028    | IDT71028   | 256K x 4 OE           |

| PDM41024    | IDT71024   | 128K x 8              |

| PDM44528    | IDT71420   | 32K x 18 — Burst Pent |

| PERFORMANCE | IDT        | DESCRIPTION           |

| P4C168      | IDT6168    | 4K x 4                |

| P4C1681     | IDT71681   | 4K x 4 Sep I/O        |

| P4C1682     | IDT71682   | 4K x 4 Sep I/O        |

| P4C116      | IDT6116    | 2K x 8                |

| P4C187      | IDT7187    | 64K x 1               |

| P4C188      | IDT7188    | 16K x 4               |

| P4C198      | IDT6198    | 16K x 4 OE            |

| P4C198A     | IDT7198    | 16K x 4 OE/CS2        |

| P4C164      | IDT7164    | 8K x 8                |

| P4C1298     | IDT61298SA | 64K x 4 OE            |

| P4C1256     | IDT71256   | 32K x 8               |

| P4C1256     | IDT71256SA | 32K x 8               |

| QUALITY     | IDT        | DESCRIPTION           |

| QS8768      | IDT6168    | 4K x 4                |

| QS8761      | IDT71681   | 4K x 4 Sep I/O        |

| QS8762      | IDT71682   | 4K x 4 Sep I/O        |

| QS8888      | IDT7188    | 16K x 4               |

| QS8888A     | IDT7188    | 16K x 4               |

| QS8886      | IDT6198    | 16K x 4 OE            |

| QS8885      | IDT7198    | 16K x 4 OE/CS2        |

| QS86446     | IDT61298SA | 64K x 4 OE            |

| QS83280     | IDT71256   | 32K x 8               |

| QS83280     | IDT71256SA | 32K x 8               |

| QS812880    | IDT71024   | 128K x 8              |

| QS8780      | IDT6178    | 4K x 4 Cache Tag      |

| QS83291     | IDT71589   | 32K x 9 Burst 486     |

| SAMSUNG     | TDT        | DESCRIPTION           |

| KM6165      | IDT7187    | 64K x 1               |

| KM6465      | IDT7188    | 16K x 4               |

| KM6465A     | IDT7188    | 16K x 4               |

| KM6465B     | IDT7188    | 16K x 4               |

|             |            |                       |

| SAMSUNG                                                                                                                                                                             | IDT                                                                                                                                                                             | DESCRIPTION                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KM6466                                                                                                                                                                              | IDT6198                                                                                                                                                                         | 16K x 4 OE                                                                                                                                                                                        |

| KM6466A                                                                                                                                                                             | IDT6198                                                                                                                                                                         | 16K x 4 OE                                                                                                                                                                                        |

| KM6466B                                                                                                                                                                             | IDT6198                                                                                                                                                                         | 16K x 4 OE                                                                                                                                                                                        |

| KM64B67                                                                                                                                                                             | IDT7198                                                                                                                                                                         | 16K x 4 OE/CS2                                                                                                                                                                                    |

| KM6865                                                                                                                                                                              | IDT7164                                                                                                                                                                         | 8K x 8                                                                                                                                                                                            |

| KM6865B                                                                                                                                                                             | IDT7164                                                                                                                                                                         | 8K x 8                                                                                                                                                                                            |

| KM64258                                                                                                                                                                             | IDT61298SA                                                                                                                                                                      | 64K x 4 OE                                                                                                                                                                                        |

| KM64258B                                                                                                                                                                            | IDT61298SA                                                                                                                                                                      | 64K x 4 OE                                                                                                                                                                                        |

| KM68257                                                                                                                                                                             | IDT71256                                                                                                                                                                        | 32K x 8                                                                                                                                                                                           |

| KM68257                                                                                                                                                                             | IDT71256SA                                                                                                                                                                      | 32K x 8                                                                                                                                                                                           |

| KM68257B                                                                                                                                                                            | IDT71256                                                                                                                                                                        | 32K x 8                                                                                                                                                                                           |

| KM68257B                                                                                                                                                                            | IDT71256SA                                                                                                                                                                      | 32K x 8                                                                                                                                                                                           |

| KM688V257                                                                                                                                                                           | IDT71V256SL                                                                                                                                                                     | 32K x 8 — 3.3V                                                                                                                                                                                    |

| KM688V257                                                                                                                                                                           | IDT71V256SA                                                                                                                                                                     | 32K x 8 — 3.3V                                                                                                                                                                                    |

| KM641001                                                                                                                                                                            | IDT71028                                                                                                                                                                        | 256K x 4 OE                                                                                                                                                                                       |

| KM681001                                                                                                                                                                            | IDT71024                                                                                                                                                                        | 128K x 8                                                                                                                                                                                          |

| SGS                                                                                                                                                                                 | IDT                                                                                                                                                                             | DESCRIPTION                                                                                                                                                                                       |

| MK41H67                                                                                                                                                                             | IDT6167                                                                                                                                                                         | 16K x 1                                                                                                                                                                                           |

| MK41H68                                                                                                                                                                             | IDT6168                                                                                                                                                                         | 4K x 4                                                                                                                                                                                            |

| MK41H87                                                                                                                                                                             | IDT7187                                                                                                                                                                         | 64K x 1                                                                                                                                                                                           |

| MK41H80                                                                                                                                                                             | IDT6178                                                                                                                                                                         | 4K x 4 Cache Tag                                                                                                                                                                                  |

| MK41S80                                                                                                                                                                             | IDT6178                                                                                                                                                                         | 4K x 4 Cache Tag                                                                                                                                                                                  |

| MK48S74                                                                                                                                                                             | IDT71B74                                                                                                                                                                        | 8K x 8 Cache Tag                                                                                                                                                                                  |

| SHARP                                                                                                                                                                               | IDT                                                                                                                                                                             | DESCRIPTION                                                                                                                                                                                       |

| LH5267A                                                                                                                                                                             | IDT6198                                                                                                                                                                         | 16K x 4 OE                                                                                                                                                                                        |

| LH52253                                                                                                                                                                             | IDT61298SA                                                                                                                                                                      | 64K x 4 OE                                                                                                                                                                                        |

| LH52258                                                                                                                                                                             | IDT71256                                                                                                                                                                        | 32K x 8                                                                                                                                                                                           |

| LH52258                                                                                                                                                                             | IDT71256SA                                                                                                                                                                      | 32K x 8                                                                                                                                                                                           |

| LH52258A                                                                                                                                                                            | IDT71256                                                                                                                                                                        | 32K x 8                                                                                                                                                                                           |

| LUEDOECA                                                                                                                                                                            | IDT71256SA                                                                                                                                                                      |                                                                                                                                                                                                   |

| LH52258A                                                                                                                                                                            | ID1712965A                                                                                                                                                                      | 32K x 8                                                                                                                                                                                           |

| LH52258A<br>LH52258B                                                                                                                                                                | IDT712565A                                                                                                                                                                      | 32K x 8<br>32K x 8                                                                                                                                                                                |

|                                                                                                                                                                                     |                                                                                                                                                                                 |                                                                                                                                                                                                   |

| LH52258B                                                                                                                                                                            | IDT71256                                                                                                                                                                        | 32K x 8                                                                                                                                                                                           |

| LH52258B<br>LH52258B                                                                                                                                                                | IDT71256<br>IDT71256SA                                                                                                                                                          | 32K x 8<br>32K x 8                                                                                                                                                                                |

| LH52258B<br>LH52258B<br>LH521002                                                                                                                                                    | IDT71256<br>IDT71256SA<br>IDT71028                                                                                                                                              | 32K x 8<br>32K x 8<br>256K x 4 OE                                                                                                                                                                 |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007                                                                                                                                        | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024                                                                                                                                  | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8                                                                                                                                                     |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br>SONY                                                                                                                                | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br>IDT                                                                                                                           | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br>DESCRIPTION                                                                                                                                      |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br>SONY<br>CXK5164                                                                                                                     | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br>IDT71024<br>IDT7187                                                                                                           | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br>DESCRIPTION<br>64K x 1                                                                                                                           |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br>SONY<br>CXK5164<br>CXK5464A                                                                                                         | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br><b>IDT</b><br>IDT7187<br>IDT7188                                                                                              | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br>DESCRIPTION<br>64K x 1<br>16K x 4                                                                                                                |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br>SONY<br>CXK5164<br>CXK5464A<br>CXK5466                                                                                              | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br><b>IDT</b><br>IDT7187<br>IDT7188<br>IDT7188                                                                                   | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br>DESCRIPTION<br>64K x 1<br>16K x 4<br>16K x 4                                                                                                     |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br><b>SONY</b><br>CXK5164<br>CXK5464A<br>CXK5466<br>CXK5465/7                                                                          | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br><b>IDT</b><br>IDT7187<br>IDT7188<br>IDT7188<br>IDT7188<br>IDT6198                                                             | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br>DESCRIPTION<br>64K x 1<br>16K x 4<br>16K x 4<br>16K x 4<br>16K x 4 OE                                                                            |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br>SONY<br>CXK5164<br>CXK5464A<br>CXK5466<br>CXK5465/7<br>CXK5863                                                                      | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br><b>IDT</b><br>IDT7187<br>IDT7188<br>IDT7188<br>IDT7188<br>IDT6198<br>IDT7164                                                  | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br>DESCRIPTION<br>64K x 1<br>16K x 4<br>16K x 4<br>16K x 4<br>16K x 4 OE<br>8K x 8                                                                  |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br><b>SONY</b><br>CXK5164<br>CXK5464A<br>CXK5466<br>CXK5465/7<br>CXK5863<br>CXK5863A                                                   | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br><b>IDT</b><br>IDT7187<br>IDT7188<br>IDT7188<br>IDT7188<br>IDT6198<br>IDT7164<br>IDT7164                                       | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br>DESCRIPTION<br>64K x 1<br>16K x 4<br>16K x 4<br>16K x 4<br>16K x 4<br>0E<br>8K x 8<br>8K x 8                                                     |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br><b>SONY</b><br>CXK5164<br>CXK5464A<br>CXK5466<br>CXK5465/7<br>CXK5863<br>CXK5863A<br>CXK58258                                       | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br>IDT71024<br>IDT7187<br>IDT7188<br>IDT7188<br>IDT7188<br>IDT6198<br>IDT7164<br>IDT7164<br>IDT71256                             | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br><b>DESCRIPTION</b><br>64K x 1<br>16K x 4<br>16K x 4<br>16K x 4<br>16K x 4<br>0E<br>8K x 8<br>8K x 8<br>32K x 8                                   |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br><b>SONY</b><br>CXK5164<br>CXK5464A<br>CXK5466<br>CXK5465/7<br>CXK5863<br>CXK5863A<br>CXK58258<br>CXK58258                           | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br>IDT71024<br>IDT7187<br>IDT7188<br>IDT7188<br>IDT7188<br>IDT6198<br>IDT7164<br>IDT7164<br>IDT71256<br>IDT71256SA               | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br><b>DESCRIPTION</b><br>64K x 1<br>16K x 4<br>16K x 4<br>16K x 4<br>16K x 4<br>8K x 8<br>8K x 8<br>32K x 8<br>32K x 8                              |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br><b>SONY</b><br>CXK5164<br>CXK5464A<br>CXK5466<br>CXK5465/7<br>CXK5863<br>CXK5863A<br>CXK58258<br>CXK58258<br>CXK58258B              | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br>IDT71024<br>IDT7187<br>IDT7188<br>IDT7188<br>IDT7188<br>IDT6198<br>IDT7164<br>IDT7164<br>IDT71256<br>IDT71256SA<br>IDT71256   | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br><b>DESCRIPTION</b><br>64K x 1<br>16K x 4<br>16K x 4<br>16K x 4<br>16K x 4<br>0E<br>8K x 8<br>8K x 8<br>32K x 8<br>32K x 8<br>32K x 8             |

| LH52258B<br>LH52258B<br>LH521002<br>LH521007<br><b>SONY</b><br>CXK5164<br>CXK5464A<br>CXK5466<br>CXK5465/7<br>CXK5863<br>CXK5863A<br>CXK58258<br>CXK58258<br>CXK58258B<br>CXK58258B | IDT71256<br>IDT71256SA<br>IDT71028<br>IDT71024<br>IDT71024<br>IDT7187<br>IDT7188<br>IDT7188<br>IDT7188<br>IDT6198<br>IDT7164<br>IDT7164<br>IDT71256<br>IDT71256SA<br>IDT71256SA | 32K x 8<br>32K x 8<br>256K x 4 OE<br>128K x 8<br><b>DESCRIPTION</b><br>64K x 1<br>16K x 4<br>16K x 4<br>16K x 4<br>16K x 4<br>0E<br>8K x 8<br>32K x 8<br>32K x 8<br>32K x 8<br>32K x 8<br>32K x 8 |

| TI        | IDT         | DESCRIPTION    |

|-----------|-------------|----------------|

| TM6716    | IDT6116     | 2K x 8         |

| TM6787    | IDT7187     | 64K x 1        |

| TM6788    | IDT7188     | 16K x 4        |

| TM6789    | IDT6198     | 16K x 4 OE     |

| TOSHIBA   | IDT         | DESCRIPTION    |

| TMM2018   | IDT6116     | 2K x 8         |

| TC5561    | IDT7187     | 64K x 1        |

| TC5562    | IDT7187     | 64K x 1        |

| TC55416   | IDT7188     | 16K x 4        |

| TC55416-H | IDT7188     | 16K x 4        |

| TC55417   | IDT6198     | 16K x 4 OE     |

| TC55417-H | IDT6198     | 16K x 4 OE     |

| TC5588    | IDT7164     | 8K x 8         |

| TC55465   | IDT61298SA  | 64K x 4 OE     |

| TC55328   | IDT71256    | 32K x 8        |

| TC55328   | IDT71256SA  | 32K x 8        |

| TC55B328  | IDT71256SA  | 32K x 8        |

| TC55V328  | IDT71V256SA | 32K x 8 — 3.3V |

.

| GENERAL INFORMATION             | 1  |

|---------------------------------|----|

| TECHNOLOGY AND CAPABILITIES     | 2  |

| QUALITY AND RELIABILITY         | 3  |

| PACKAGE DIAGRAM OUTLINES        | 4  |

| 16K SRAM PRODUCTS               | 5  |

| 64K SRAM PRODUCTS               | 6  |

| 256K SRAM PRODUCTS              | 7  |

| 1M SRAM PRODUCTS                | 8  |

| 3.3V ASYNCHRONOUS SRAM PRODUCTS | 9  |

| CacheRAMs                       | 10 |

| CACHE TAGS                      | 11 |

| CACHE CONTROLLER PRODUCT        | 12 |

# **IDT...LEADING THE CMOS FUTURE**

A major revolution is taking place in the semiconductor industry today. A new technology is rapidly displacing older NMOS and bipolar technologies as the workhorse of the '80s and beyond. That technology is high-speed CMOS. Integrated Device Technology, a company totally predicated on and dedicated to implementing high-performance CMOS products, is on the leading edge of this dramatic change.

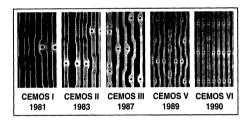

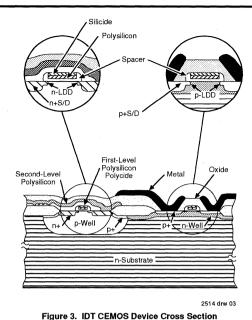

Beginning with the introduction of the industry's fastest CMOS 2K x 8 static RAM, IDT has grown into a company with multiple divisions producing a wide range of high-speed CMOS circuits that are, in almost every case, the fastest available. These advanced products are produced with IDT's proprietary CEMOS<sup>™</sup> technology, a twin-well, dry-etched, stepper-aligned process utilizing progressively smaller dimensions.

From inception, IDT's product strategy has been to apply the advantages of its extremely fast CEMOS technology to produce the integrated circuit elements required to implement high-performance digital systems. IDT's goal is to provide the circuits necessary to create systems which are far superior to previous generations in performance, reliability, cost, weight, and size. Many of the company's innovative product designs offer higher levels of integration, advanced architectures, higher density packaging and system enhancement features that are establishing tomorrow's industry standards. The company is committed to providing its customers with an everexpanding series of these high-speed, lower-power IC solutions to system design needs.

IDT's commitment, however, extends beyond state-of-theart technology and advanced products to providing the highest level of customer service and satisfaction in the industry. Manufacturing products to exacting quality standards that provide excellent, long-term reliability is given the same level of importance and priority as device performance. IDT is also dedicated to delivering these high-quality advanced products on time. The company would like to be known not only for its technological capabilities, but also for providing its customers with quick, responsive, and courteous service. IDT's product families are available in both commercial and military grades. As a bonus, commercial customers obtain the benefits of military processing disciplines, established to meet or exceed the stringent criteria of the applicable military specifications.

IDT is the leading U.S. supplier of high-speed CMOS circuits. The company's high-performance fast SRAM, FCT logic, high-density modules, FIFOs, multi-port memories, BiCMOS ECL I/O memories, RISC SubSystems, and the 32-and 64-bit RISC microprocessor families complement each other to provide high-speed CMOS solutions for a wide range of applications and systems.

In 1993, IDT introduced its newest RISC microprocessor based on the MIPS architecture for the desktop PC, and embedded control markets. The R4600 Orion microprocessor, is the first RISC processor offering Pentium performance at a cost lower than most of Intel's 486DX line.

The R4600 is a full 64-bit implementation of the MIPS III instruction set architecture found in the popular R4000PC and R4400PC, but uses a shorter pipeline resulting in fewer stalls and, therefore, higher performance.

When compared against other processors targeted at the Windows NT market, the R4600 possesses clear advantages. The R4600 has the best performance per dollar, the best performance per watt cfonsumed, and the most efficient use of silicon for the performance attained.

Dedicated to maintaining its leadership position as a stateof-the-art IC manufacturer, IDT will continue to focus on maintaining its technology edge as well as developing a broader range of innovative products. New products and speed enhancements are continuously being added to each of the existing product families, and additional product families are being introduced. Contact your IDT field representative or factory marketing engineer for information on the most current product offerings. If you'rebuilding state-of-the-art equipment, IDT wants to help you solve your design problems.

# IDT MILITARY AND DESC-SMD PROGRAM

IDT is a leading supplier of military, high-speed CMOS circuits. The company's high-performance Static RAMs, FCT Logic Family, Complex Logic (CLP), FIFOs, Specialty Memories (SMP), ECL I/O BiCMOS Memories, 32-bit RISC Microprocessor, RISC Subsystems and high-density Subsystems Modules product lines complement each other to provide high-speed CMOS solutions to a wide range of military applications and systems. Most of these product lines offer Class B products which are fully compliant to the latest revision of MIL-STD-883, Paragraph 1.2.1. In addition, IDT offers Radiation Tolerant (RT), as well as Radiation Enhanced (RE), products.

devices on Standard Military Drawings (SMD). The SMD program allows standardization of militarized products and reduction of the proliferation of non-standard source control drawings. This program will go far toward reducing the need for each defense contractor to make separate specification control drawings for purchased parts. IDT plans to have SMDs for many of its product offerings. Presently, IDT has 88 devices which are listed or pending listing. The devices are from IDT's SRAM, FCT Logic family, Complex Logic (CLP), FIFOs and Specialty Memories (SMP) product families. IDT expects to add another 20 devices to the SMD program in the near future. Users should contact either IDT or DESC for current status of products in the SMD program.

IDT has an active program with the Defense Electronic Supply Center (DESC) to list all of IDT's military compliant

|            | SMD            |            | SMD         |            | SMD                |

|------------|----------------|------------|-------------|------------|--------------------|

| SRAM       | IDT            | 5962-93177 | 7206L       | 5962-88654 | 54FCT640/A         |

|            |                |            | 72141L      | 5962-88655 | 54FCT534/A         |

| 84036      | 6116           | 5962-92101 | 72215LB     | 5962-89767 | 54FCT540/A         |

| 5962-88740 | 6116LA         | 5962-93138 | 72220L      | 5962-89766 | 54FCT541/A         |

| 84132      | 6167           | 5962-92057 | 72225LB     | 5962-89733 | 54FCT191/A         |

| 5962-86015 | 7187           | 5962-93189 | 72245LB     | 5962-89732 | 54FCT241/A         |

| 5962-86859 | 6198/7198/7188 | 5962-91757 | 72200L      | 5962-89652 | 54FCT399/A         |

| 5962-86705 | 6168           |            |             | 5962-89513 | 54FCT574/A         |

| 5962-85525 | 7164           | CLP        | IDT         | 5962-89731 | 54FCT833A/B        |

| 5962-88552 | 71256L         |            |             | 5962-89730 | 54FCT543/A         |

| 5962-88662 | 71256S         | 5962-87708 | 39C10B & C  | 5962-90901 | 29FCT52A/B/C       |

| 5962-88611 | 71682L         | 5962-88533 | 49C460A/B/C | 5962-92205 | 29FCT520AT/BT/CT   |

| 5962-89891 | 7198           | 5962-88613 | 39C60/A     | 5962-92157 | 49FCT805/A/806/A   |

| 5962-89892 | 6198           | 5962-88643 | 49C410      | 5962-92233 | 54FCT138T/AT/CT    |

| 5962-89690 | 6116           | 5962-86873 | 7216L       | 5962-92208 | 54FCT157T/AT/CT    |

| 5962-38294 | 7164           | 5962-87686 | 7217L       | 5962-92209 | 54FCT161T/AT/CT    |

| 5962-89692 | 7188           | 5962-88733 | 7210        | 5962-92210 | 54FCT163T/AT/CT    |