# HIGH PERFORMANCE CMOS DATA BOOK

| Technology/Capabilities         |

|---------------------------------|

| Static RAM                      |

| MICROSLICE <sup>™</sup>         |

| Digital Signal Processing (DSP) |

| Logic                           |

| Data Conversion                 |

| Subsystems Modules              |

| General Product Information     |

# HIGH-SPEED CMOS DATA BOOK

3236 Scott Boulevard, Santa Clara, California 95054

Telephone: (408) 727-6116 • TWX: 910-338-2070 • FAX: (408) 988-3029

Printed in U.S.A. 8/86

© 1986 Integrated Device Technology, Inc.

|  | \$ |  |

|--|----|--|

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

|  |    |  |

#### **CONTENTS OVERVIEW**

This book has been organized into sections by product families, with additional sections providing numerous aids to assist in a better understanding of our high-performance CMOS devices. These include descriptions of IDT's commitment to providing the highest levels of technology, quality and service in the industry; our CEMOS™ and surface mount technologies; facilities and capabilities; product selector guides; article reprints; application and technical notes; quality flows and testing; package-related data and ordering information. Two separate indexes have also been provided to ensure ease of use of this data book. One is organized by product line and function within the product line; the other is a numerical index. As a further aid, industry cross reference guides are provided by product family.

Three different types of data sheets are contained in this book:

**ADVANCE INFORMATION** — Contain initial descriptions for products that are in development, including features, pinouts and block diagrams.

**PRELIMINARY** — Contain minimum and maximum limits, based upon initial device characterization, which are subject to change upon full characterization over the specified supply and temperature range.

**FINAL** — Contain minimum and maximum limits specified over the complete supply and temperature range for full production devices.

New products, product performance enhancements, additional package types and new product families are being introduced frequently. Please contact your local IDT sales representative or call our factory at 1-800-IDT-CMOS to determine latest device specifications, package types and product availability.

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent, patent rights, or other rights, of Integrated Device Technology, Inc.

#### LIFE SUPPORT POLICY

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the manufacturer and an officer of IDT.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

CEMOS, MICROSLICE, SPC, and SYSTEM-SLICE are trademarks of Integrated Device Technology, Inc. SPC (Special Protocol Channel) has a patent pending.

FAST is a trademark of Fairchild Semiconductor Co.

### **TABLE OF CONTENTS**

| CONTENTS                   |                                         | PAGE  |

|----------------------------|-----------------------------------------|-------|

| Contents Overview          |                                         | i     |

| Disclaimer                 |                                         |       |

| Life Support Policy        |                                         |       |

| Table of Contents          |                                         |       |

| Alphanumeric Listing b     | by Product Line                         | ii    |

| Numerical Index            | ·                                       | vi    |

| Product Selector Guides    |                                         | x     |

| Cross Reference Guides     |                                         |       |

| Static RAM                 |                                         | xix   |

| MICROSLICE™                |                                         | xxii  |

|                            |                                         |       |

| Technology/Capabilitie     | s                                       |       |

| <b>0</b> , .               | S Future                                | 1-1   |

| •                          | OS Technology                           |       |

|                            | chnology                                |       |

|                            | logy                                    |       |

| State-of-the-Art Facilitie | es and Capabilities                     | 1-6   |

| Superior Quality and R     | eliability                              | 1-7   |

| Static RAMs                |                                         |       |

| IDT6116A                   | 16K (2Kx8) Static RAM                   | 2-1   |

| IDT6167A                   | 16K (16Kx1) Static RAM                  |       |

| IDT6168A                   | 16K (4Kx4) Static RAM                   | 2-15  |

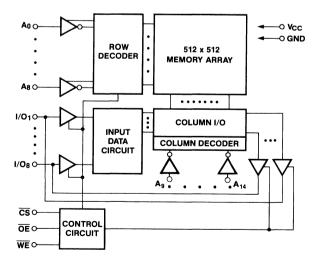

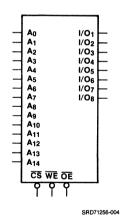

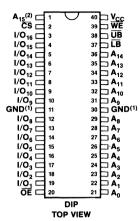

| IDT71256                   | 256K (32Kx8) Static RAM                 | 2-23  |

| IDT71257                   | 256K (256Kx1) Static RAM                |       |

| IDT71258                   | 256K (64Kx4) Static RAM                 | 2-27  |

| IDT7130/40                 | 8K (1Kx8) Dual-Port Static RAM          | 2-29  |

| IDT7132/42                 | 16K (2Kx8) Dual-Port Static RAM         | 2-41  |

| IDT71322                   | 16K (2Kx8) Dual-Port Static RAM         | 2-51  |

| IDT7133/43                 | 32K (2Kx16 & 4Kx8) Dual-Port Static RAM | 2-53  |

| IDT7134                    | 32K (4Kx8) Dual-Port Static RAM         | 2-55  |

| IDT71341                   | 32K (4Kx8) Dual-Port Static RAM         | 2-57  |

| IDT7164                    | 64K (8Kx8) Static RAM                   |       |

| IDT7165                    | 64K (8Kx8) Static RAM                   | 2-67  |

| IDT71681A/82A              | 16K (4Kx4) Static RAM                   |       |

| IDT7174                    | 64K (8Kx8) Static RAM                   |       |

| IDT7187                    | 64K (64Kx1) Static RAM                  |       |

| IDT7188                    | 64K (16Kx4) Static RAM                  |       |

| IDT7198                    | 64K (16Kx4) Static RAM                  |       |

| IDT71981/82                | 64K (16Kx4) Static RAM                  |       |

|                            |                                         | 2-115 |

| MICROSLICE™ (Bit-Sli       |                                         |       |

| IDT39C01C/D/E              | 4-Bit Microprocessor Slice              |       |

| IDT39C02A                  | Carry Lookahead Generator               |       |

| IDT39C03A/B                | 4-Bit Microprocessor Slice              |       |

| IDT39C09A/B                | 4-Bit Sequencer                         |       |

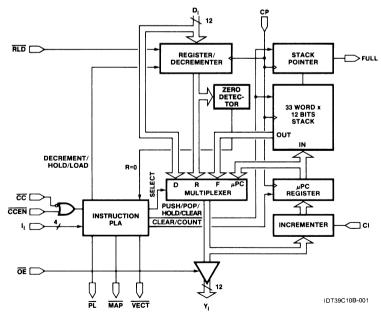

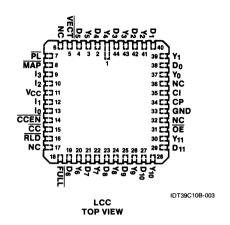

| IDT39C10B/C                | 12-Bit Sequencer                        |       |

| IDT39C11A/B                | 4-Bit Sequencer                         | 3-47  |

## TABLE OF CONTENTS (CONT'D)

| CONTENTS                | , ,                                   | PAGE  |

|-------------------------|---------------------------------------|-------|

| MICROSLICE™ (Cont'o     | 1.)                                   |       |

| IDT39C203/A             | 4-Bit Microprocessor Slice            | 3-71  |

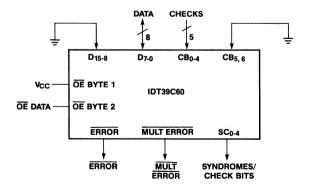

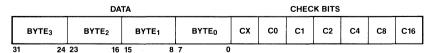

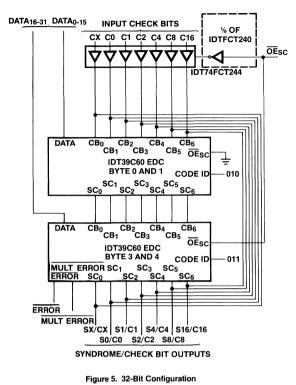

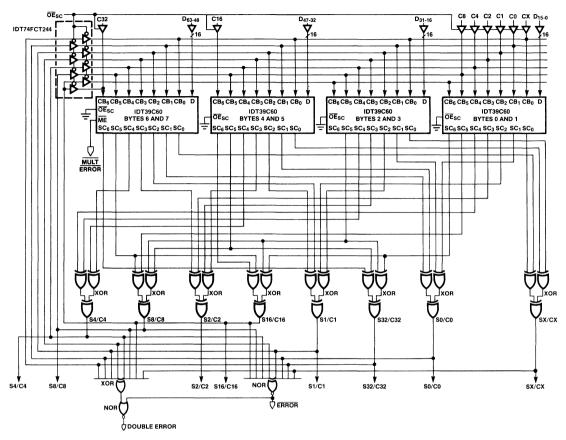

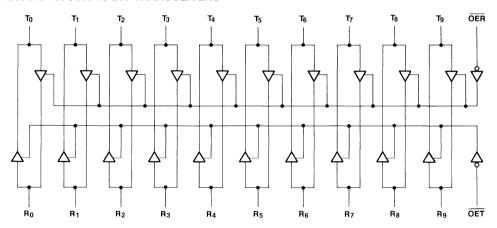

| IDT39C60                | 16-Bit Cascadeable E.D.C.             |       |

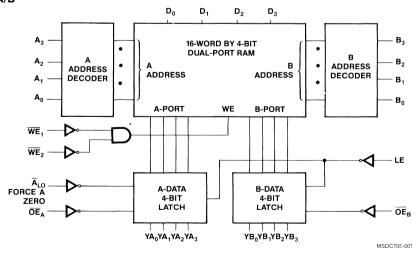

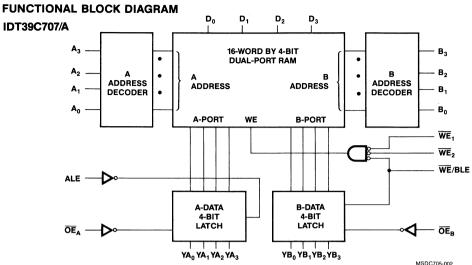

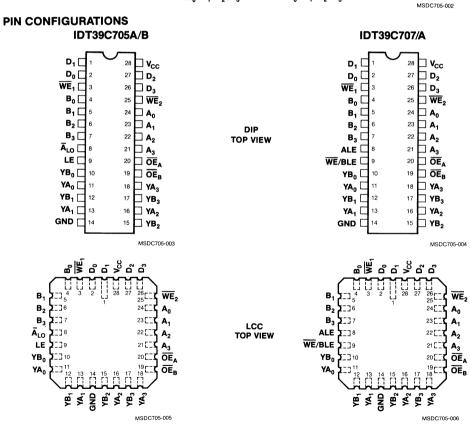

| IDT39C705A/B            | 16x4 Register File Extension          |       |

| IDT39C707/A             | 16x4 Register File Extension          |       |

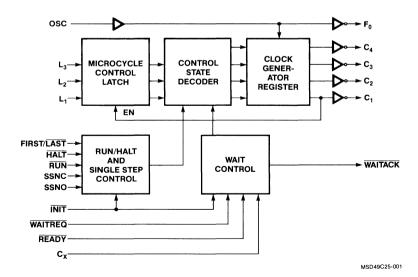

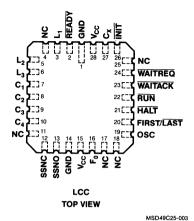

| IDT49C25                | Microcycle Length Controller          |       |

| IDT49C401/A             | 16-Bit Microprocessor Slice           |       |

| IDT49C402/A             | 16-Bit Microprocessor Slice           | 3-113 |

| IDT49C403/A             | 16-Bit Microprocessor Slice           | 3-124 |

| IDT49C404               | 32-Bit Microprocessor Slice           | 3-126 |

| IDT49C410/A             | 16-Bit Sequencer                      | 3-128 |

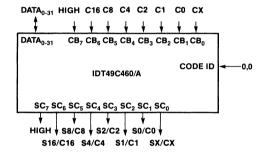

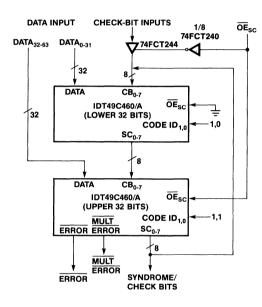

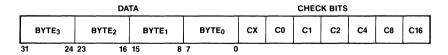

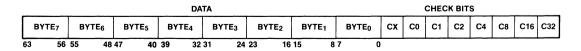

| IDT49C460/A             | 32-Bit Cascadeable E.D.C.             |       |

| Ordering Information    |                                       | 3-157 |

| Digital Signal Processi |                                       |       |

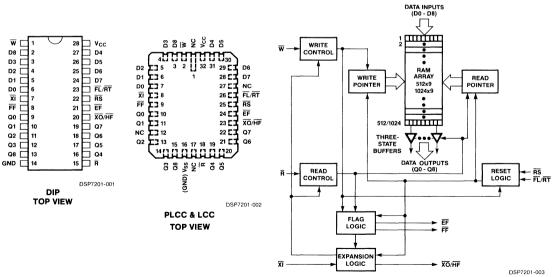

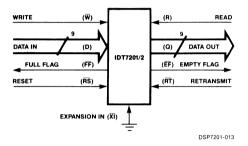

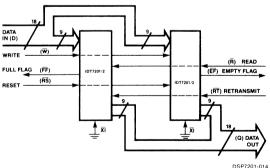

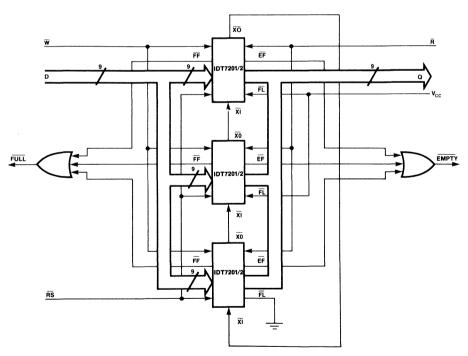

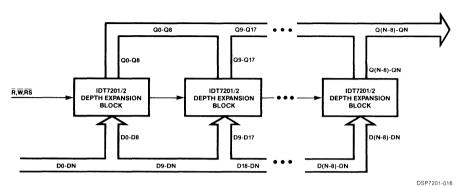

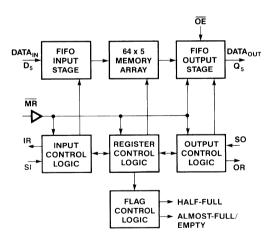

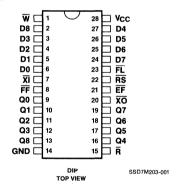

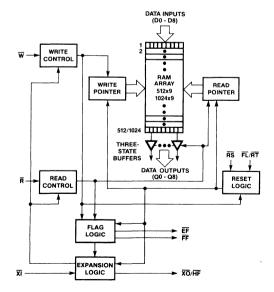

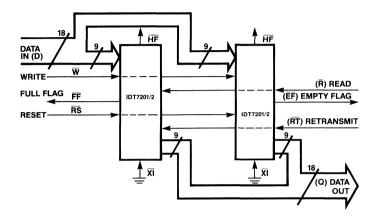

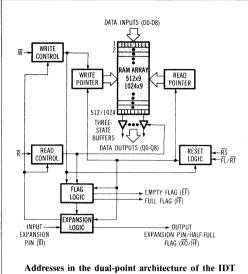

| IDT7201A/02A            | 512x9 & 1024x9 Half-Full Flag FIFO    | 4-1   |

| IDT7201/02              | 512x9 & 1024x9 Parallel In-Out FIFO   |       |

| IDT7203/04              | 2Kx9 & 4Kx9 Parallel In-Out FIFO      |       |

| IDT72064/65             | 64-Bit Floating Point                 |       |

| IDT7209                 | 12x12 Parallel Multiplier-Accumulator |       |

| IDT7210/43              | 16x16 Parallel Multiplier-Accumulator |       |

| IDT72103/04             | 2Kx9 & 4Kx9 Half-Full Flag FIFO       |       |

| IDT7212/13              | 12x12 Parallel Multiplier             |       |

| IDT7216/17              | 16x16 Parallel Multiplier             |       |

| IDT72264/65             | 64-Bit Floating Point                 |       |

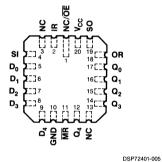

| IDT72401/02/03/04       | 64x4 & 64x5 Parallel In-Out FIFO      |       |

| IDT72413                | Parallel 64x5 FIFO                    |       |

| Ordering Information    |                                       | 4-78  |

| Logic                   |                                       |       |

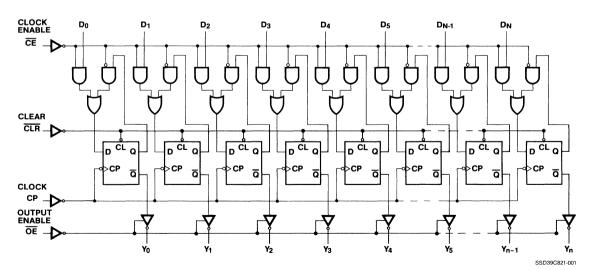

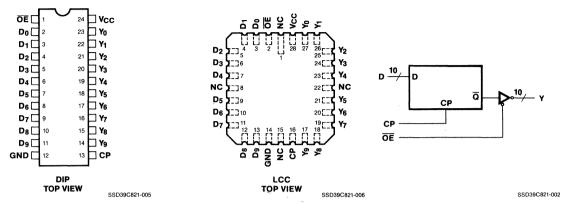

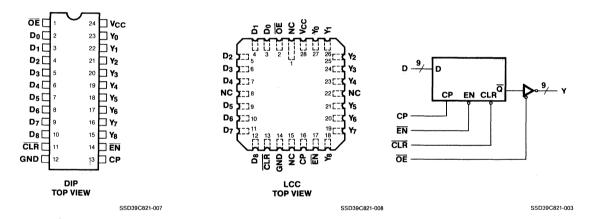

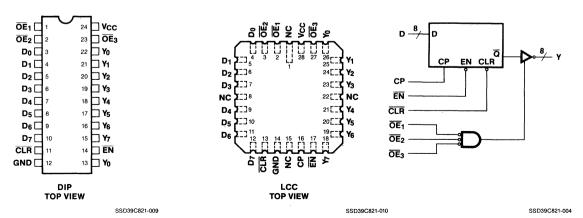

| IDT39C821               | 10-Bit Non-inverting Register         | 5-1   |

| IDT39C822               | 10-Bit Inverting Register             |       |

| IDT39C823               | 9-Bit Non-inverting Register          |       |

| IDT39C824               | 9-Bit Inverting Register              |       |

| IDT39C825               | 8-Bit Non-inverting Register          | 5-1   |

| IDT39C826               | 8-Bit Inverting Register              | 5-1   |

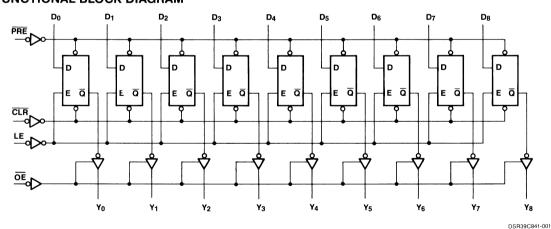

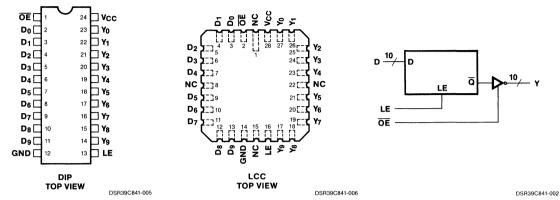

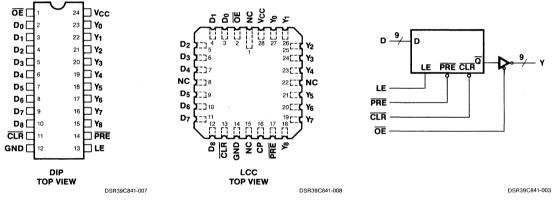

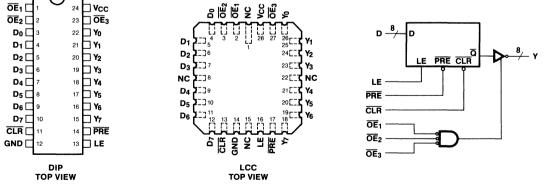

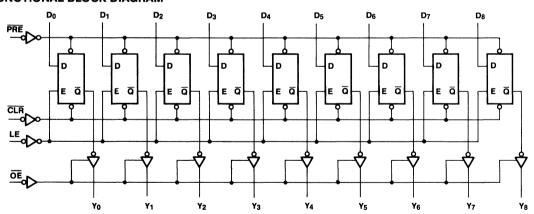

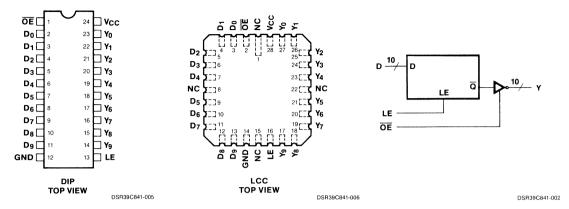

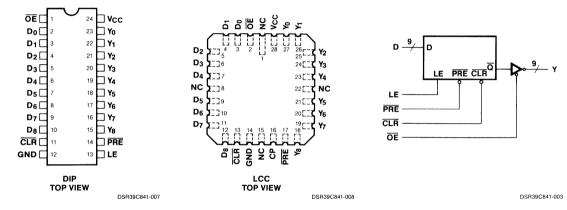

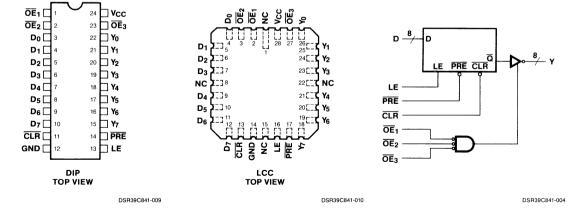

| IDT39C841               | 10-Bit Non-inverting Latch            | 5-7   |

| IDT39C842               | 10-Bit Inverting Latch                | 5-7   |

| IDT39C843               | 9-Bit Non-inverting Latch             | 5-7   |

| IDT39C844               | 9-Bit Inverting Latch                 | 5-7   |

| IDT39C845               | 8-Bit Non-inverting Latch             | 5-7   |

| IDT39C846               | 8-Bit Inverting Latch                 | 5-7   |

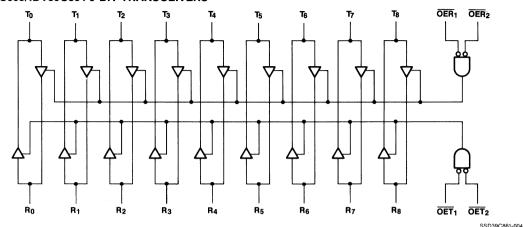

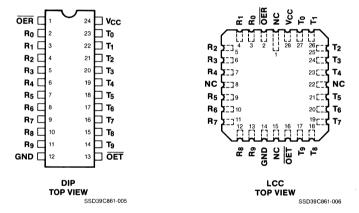

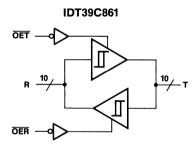

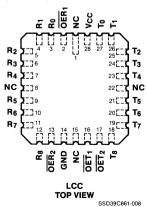

| IDT39C861               | 10-Bit Non-inverting Transceiver      | 5-13  |

| IDT39C862               | 10-Bit Inverting Transceiver          | 5-13  |

| IDT39C863               | 9-Bit Non-inverting Transceiver       | 5-13  |

| IDT39C864               | 9-Bit Inverting Transceiver           | 5-13  |

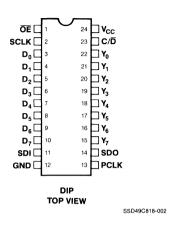

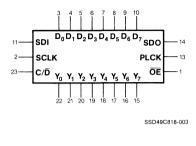

| IDT49C818               | Octal Register with SPC™              | 5-18  |

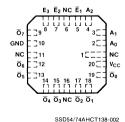

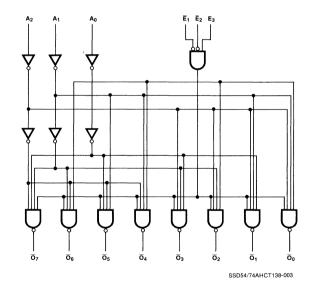

| IDT54/74AHCT138         | 1-of-8 Decoder                        | 5-20  |

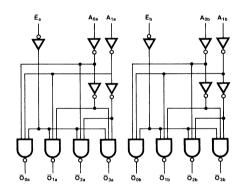

| IDT54/74AHCT139         | Dual 1-of-4 Decoder                   | 5-24  |

| IDT54/74AHCT161/163     | Synchronous Binary Counter            |       |

| IDT54/74AHCT182         | Carry Lookahead Generator             |       |

| IDT54/74AHCT191         | Up/Down Binary Counter                |       |

| IDT54/74AHCT193         | Up/Down Binary Counter                |       |

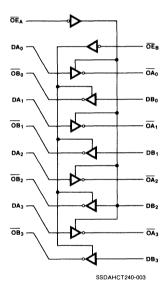

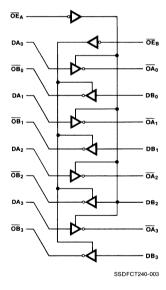

| IDT54/74AHCT240         | Octal Buffer                          |       |

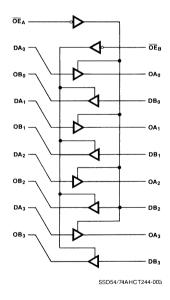

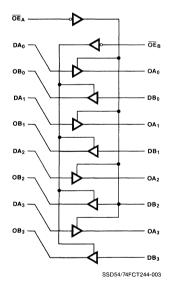

| IDT54/74AHCT244         | Octal Buffer                          | 5-47  |

# TABLE OF CONTENTS (CONT'D)

| CONTENTS             |                                  | PAGE  |

|----------------------|----------------------------------|-------|

| _ogic (CONT'D.)      |                                  |       |

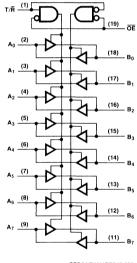

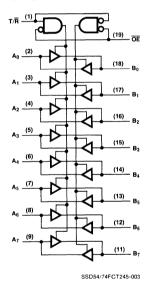

| IDT54/74AHCT245      | Octal Bidirectional Transceiver  | 5-50  |

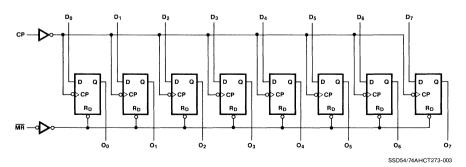

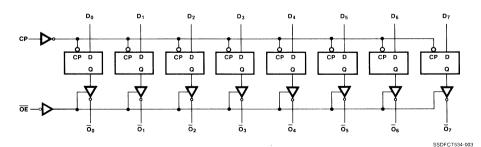

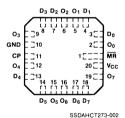

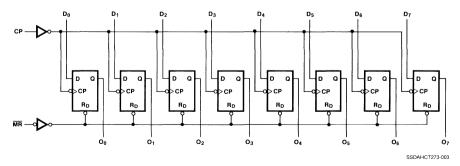

| IDT54/74AHCT273      | Octal D Flip-Flop                | 5-53  |

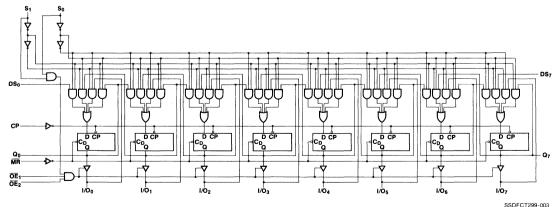

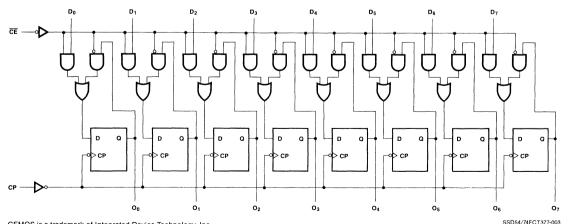

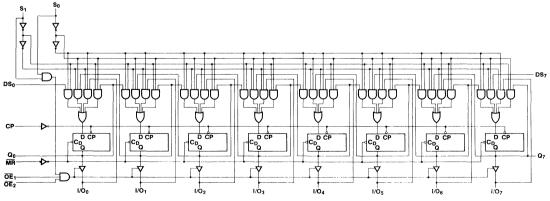

| IDT54/74AHCT299      | Universal Shift Register         | 5-57  |

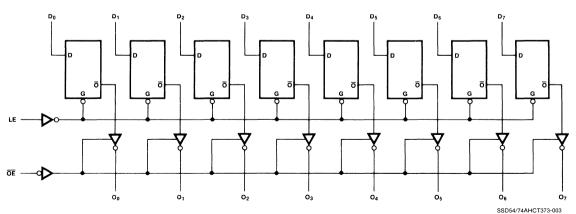

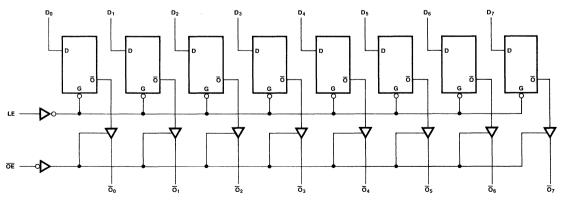

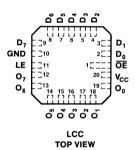

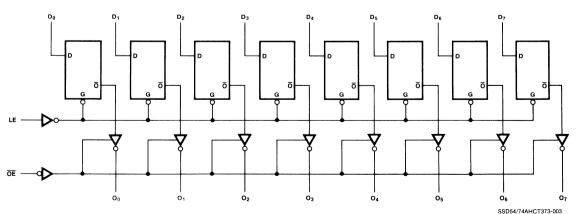

| IDT54/74AHCT373      | Octal Transparent Latch          | 5-61  |

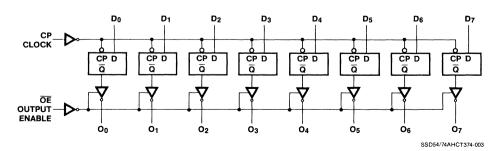

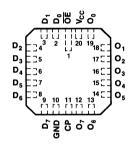

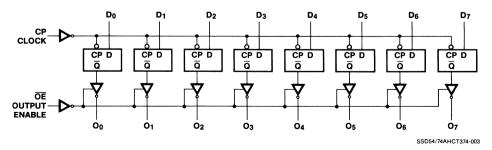

| IDT54/74AHCT374      | Octal D Flip-Flop                |       |

| IDT54/74AHCT377      | Octal D Flip-Flop                |       |

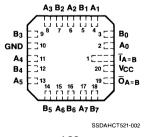

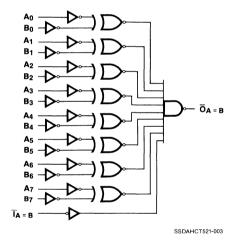

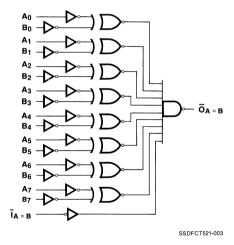

| IDT54/74AHCT521      | 8-Bit Comparator                 |       |

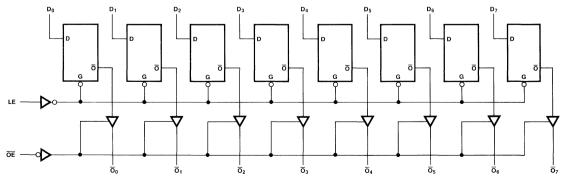

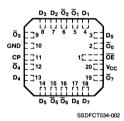

| IDT54/74AHCT533      | Octal Transparent Latch          | 5-76  |

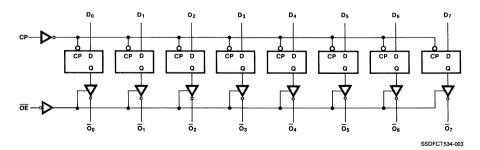

| IDT54/74AHCT534      | Octal D Flip-Flop                |       |

| IDT54/74AHCT573      | Octal Transparent Latch          |       |

| IDT54/74AHCT574      | Octal D Register                 |       |

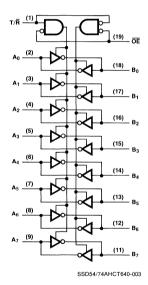

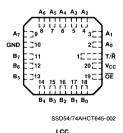

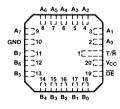

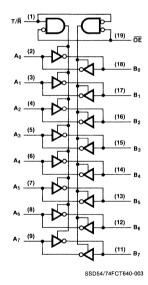

| IDT54/74AHCT640      | Octal Bidirectional Transceiver  |       |

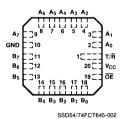

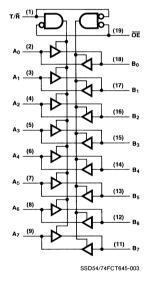

| IDT54/74AHCT645      | Octal Bidirectional Transceiver  |       |

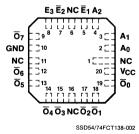

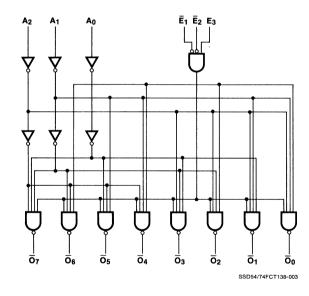

| IDT54/74FCT138/A     | 1-of-8 Decoder                   |       |

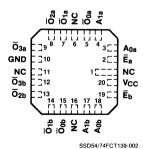

| IDT54/74FCT139/A     | Dual 1-of-4 Decoder              |       |

|                      | Synchronous Binary Counter       |       |

| IDT54/74FCT182/A     | Carry Lookahead Generator        |       |

| IDT54/74FCT191/A     | Up/Down Binary Counter           |       |

| IDT54/74FCT193/A     | Up/Down Binary Counter           |       |

| IDT54/74FCT240/A     | Octal Buffer                     |       |

| IDT54/74FCT244/A     | Octal Buffer                     |       |

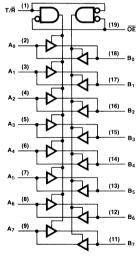

| IDT54/74FCT245/A     | Octal Bidirectional Transceiver  |       |

| IDT54/74FCT273/A     | Octal D Flip-Flop                |       |

| IDT54/74FCT299/A     | Octal Universal Shift Register   |       |

| IDT54/74FCT373/A     | Octal Transparent Latch          |       |

| IDT54/74FCT374/A     | Octal D Flip-Flop                |       |

| IDT54/74FCT377/A     | Octal D Flip-Flop                |       |

| IDT54/74FCT521/A     | 8-Bit Comparator                 |       |

| IDT54/74FCT533/A     | Octal Transparent Latch          |       |

| IDT54/74FCT534/A     | Octal D Flip-Flop                |       |

| IDT54/74FCT573/A     | Octal Transparent Latch          |       |

| IDT54/74FCT574/A     | Octal D Register                 |       |

| IDT54/74FCT640/A     | Octal Bidirectional Transceiver  |       |

| IDT54/74FCT645/A     | Octal Bidirectional Transceiver  |       |

| IDT54/74FCT821B      |                                  |       |

| IDT54/74FCT822B      | 10-Bit Non-inverting Register    |       |

| IDT54/74FCT823B      |                                  |       |

| IDT54/74FCT823B      | 9-Bit Non-inverting Register     |       |

| IDT54/74FCT825B      | 8-Bit Non-inverting Register     |       |

| IDT54/74FCT826B      |                                  |       |

| IDT54/74FCT820B      | 8-Bit Inverting Register         |       |

| IDT54/74FCT842B      | 10-Bit Non-inverting Latch       |       |

| IDT54/74FCT842B      | 10-Bit Inverting Latch           |       |

| IDT54/74FCT843B      | 9-Bit Non-inverting Latch        |       |

| IDT54/74FCT845B      | 9-Bit Inverting Latch            |       |

|                      | 8-Bit Non-inverting Latch        |       |

| IDT54/74FCT846B      | 8-Bit Inverting Latch            |       |

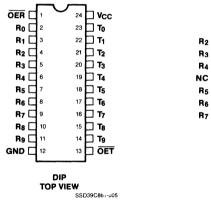

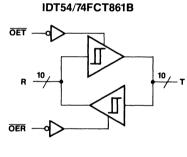

| IDT54/74FCT861B      | 10-Bit Non-inverting Transceiver |       |

| IDT54/74FCT862B      | 10-Bit Inverting Transceiver     |       |

| IDT54/74FCT863B      | 9-Bit Non-inverting Transceiver  |       |

| IDT54/74FCT864B      | 9-Bit Inverting Transceiver      |       |

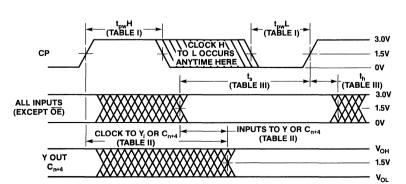

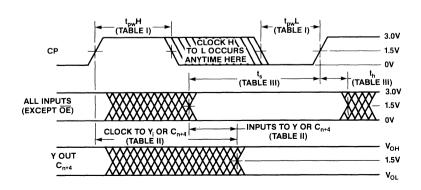

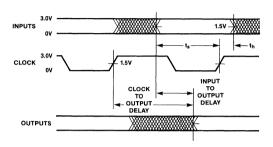

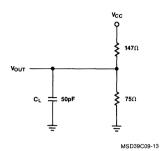

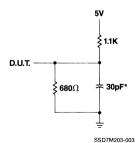

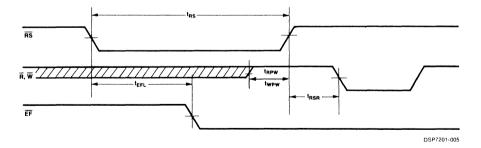

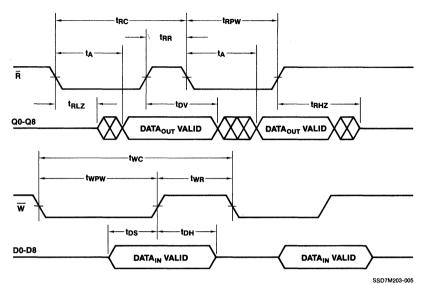

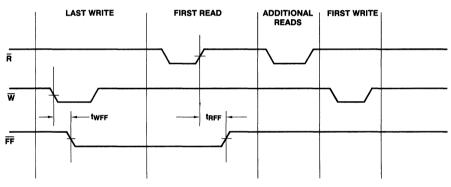

| DI54//4AHCI/FCI Fam  | ily Test Circuits and Waveforms  | 5-19/ |

| Ordering Information |                                  | J-198 |

| CONTENTS                |            |                                                                                | PAGE  |

|-------------------------|------------|--------------------------------------------------------------------------------|-------|

| <b>Data Convers</b>     | ion        |                                                                                |       |

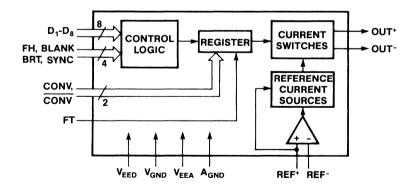

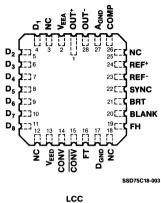

| IDT75C18/28             | 3          | 8-Bit 125MHz Video DAC                                                         | 6-1   |

| Ordering Infor          | mation     |                                                                                | 6-3   |

| Subsystems I            | Modules    |                                                                                |       |

| IDT7MP624               |            | 1 Megabit (64Kx16, 128Kx8 or 256Kx4) Plastic Static RAM Module                 | 7-1   |

| IDT7M134/13             | 35         | 64K (8Kx8) & 128K (16Kx8) Dual-Port RAM Module                                 |       |

| IDT7M136/13             |            | 128K (16Kx8) & 256K (32Kx8) Dual-Port RAM Module                               |       |

| IDT7M144/14             |            | 64K (8Kx8) & 128K (16Kx8) Slave Dual-Port RAM Module                           |       |

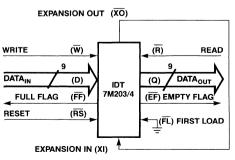

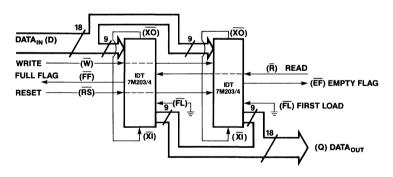

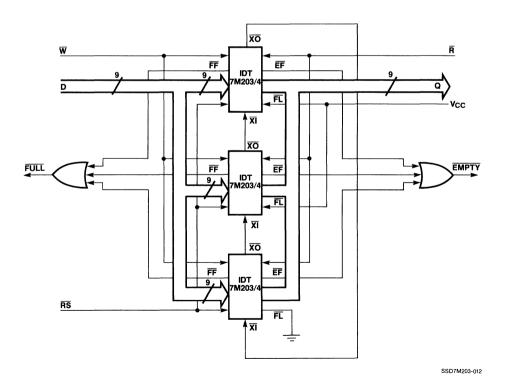

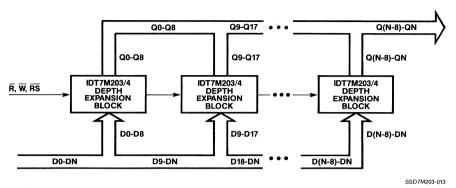

| IDT7M203/2              |            | 2Kx9 & 4Kx9 Parallel In-Out FIFO                                               |       |

| IDT7M205/2              | 06         | 8Kx9 & 16Kx9 Parallel In-Out FIFO                                              | 7-28  |

| IDT7M624                |            | 1 Megabit (64Kx16, 128Kx8 or 256Kx4) Static RAM Module                         | 7-29  |

| IDT7M656                |            | 256K (16Kx16, 32Kx8 or 64Kx4) Static RAM Module                                | 7-35  |

| IDT7M812/91             | 12         | 512K (64Kx8 or 64Kx9) Static RAM Module                                        |       |

| IDT7M824                |            | 1 Megabit (128Kx8) Static RAM Module                                           |       |

| IDT7M856                |            | 256K (32Kx8) Static RAM Module                                                 | 7-49  |

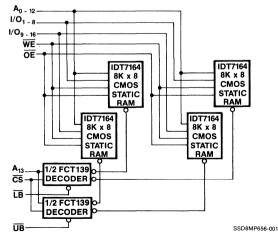

| IDT7M864/8              | M864       | 64K (8Kx8) Static RAM Module                                                   | 7-55  |

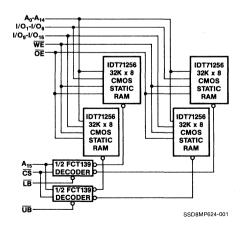

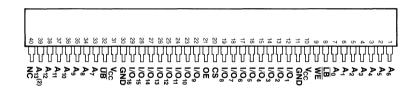

| IDT8MP624/              | 612        | 512K (32Kx16) Plastic Static RAM Module                                        | 7-60  |

| IDT8MP656/              | 628        | 256K (16Kx16) & 128K (8Kx16) Plastic Static RAM Module                         | 7-62  |

| IDT8MP824               |            | 1 Megabit (128Kx8) Plastic Static RAM Module                                   | 7-64  |

| IDT8M624/6              | 12         | 1 Megabit (64Kx16) & 512K (32Kx16) Static RAM Module                           | 7-66  |

| IDT8M656/6              | 28         | 256K (16Kx16) & 128K (8Kx16) Static RAM Module                                 | 7-68  |

| IDT8M824                |            | 1 Megabit (128Kx8) Static RAM Module                                           | 7-75  |

| IDT8M856                |            | 256K (32Kx8) Static RAM Module                                                 | 7-77  |

| Ordering Inform         | mation     |                                                                                | 7-83  |

| General Prod            | uct Infor  | mation                                                                         |       |

| Application No          |            |                                                                                |       |

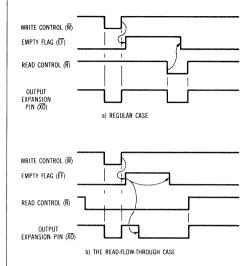

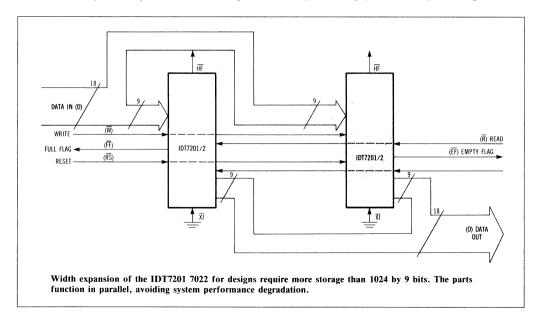

| Application No<br>AN-01 |            | tending the IDT7001/00 FIFO                                                    | 0.1   |

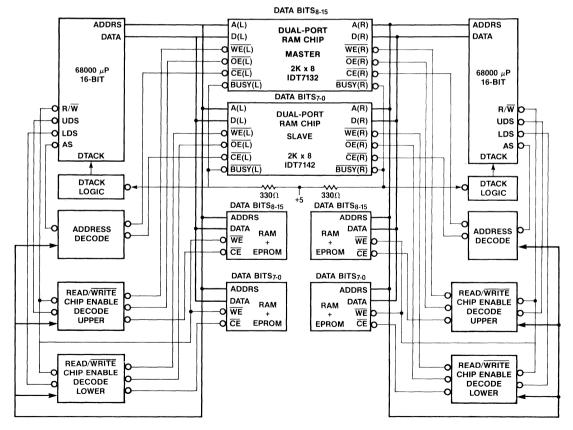

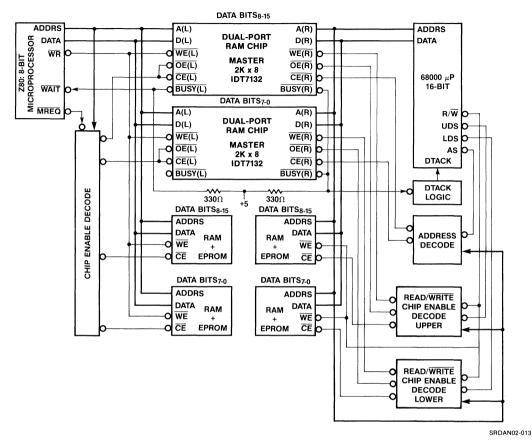

| AN-01<br>AN-02          |            | tanding the IDT7201/02 FIFOort RAMs Simplify Communication in Computer Systems |       |

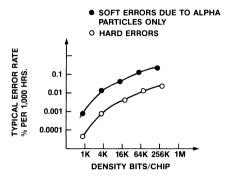

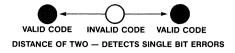

| AN-02<br>AN-03          |            | our Data with a High-Speed CMOS 16-, 32- or 64-Bit EDC                         |       |

| AN-03<br>AN-04          |            | peed CMOS TTL-Compatible Number-Crunching Elements for Fixed and               | 0-13  |

| AIN-04                  |            | ng Point Arithmetic                                                            | 8_27  |

| AN-05                   |            | e I/O RAMs Increase Speed and Reduce Part Count                                |       |

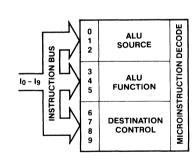

| AN-05<br>AN-06          |            | MOS Slices—New Building Blocks Maintain Microcode Compatibility                | 0-33  |

| AIN-00                  |            | crease Performance                                                             | 8-38  |

| AN-07                   |            | Tag RAM Chips Simplify Cache Memory Design                                     |       |

| Tech Note               |            | wo Chip Selects on the IDT7198                                                 |       |

|                         | _          | We only delects on the ID17130                                                 | 0 00  |

| Article Reprints        |            | olar-enhanced I/O Rivals Fast TTL Gates                                        | 0 55  |

|                         |            | Suit Military Applications                                                     |       |

|                         |            | ntend with Widely Differing Data Rates                                         |       |

|                         |            |                                                                                |       |

|                         |            | abricated in CMOS Rival the Speed of Bipolars                                  | 0-7 1 |

| Quality Confor          |            |                                                                                | 0.70  |

|                         |            | ty                                                                             |       |

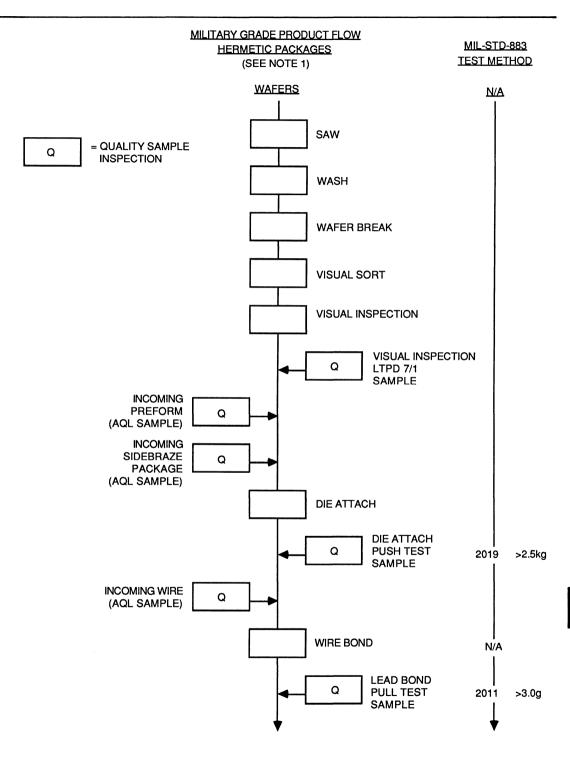

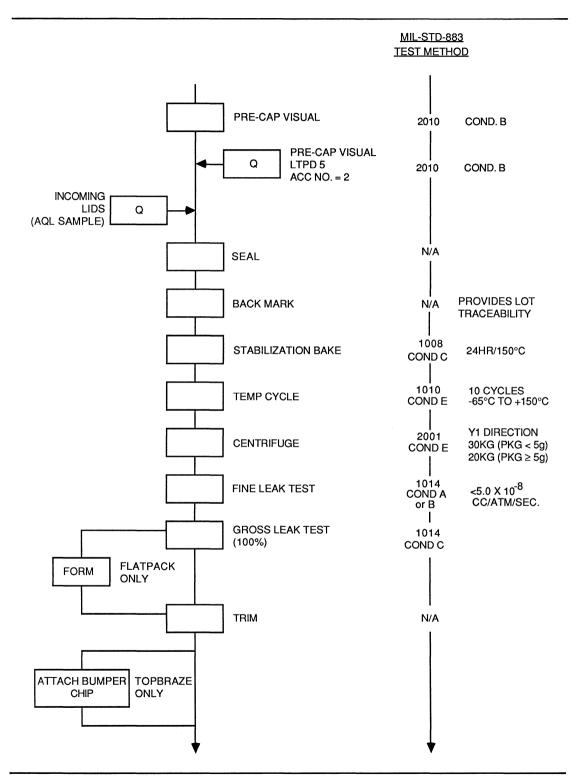

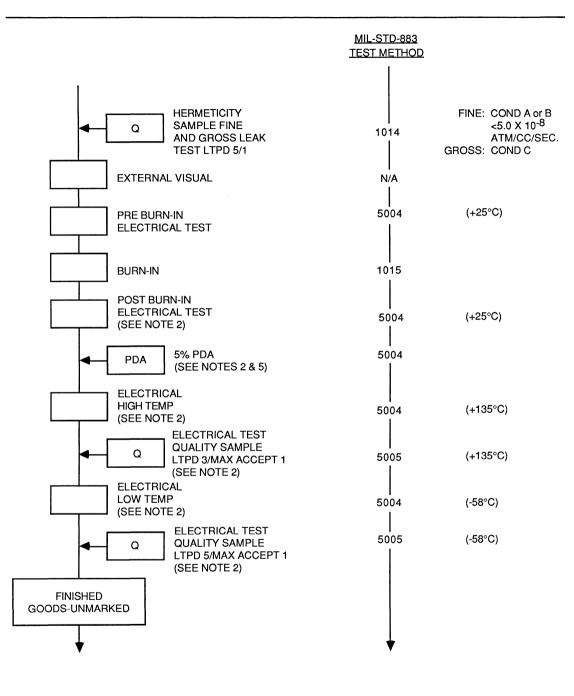

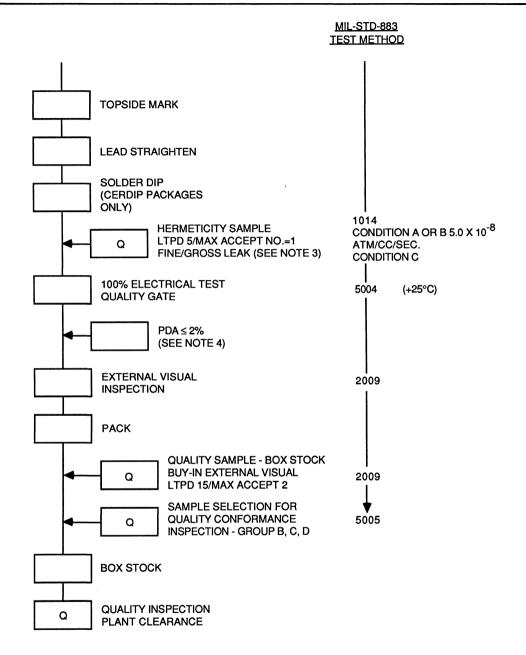

| •                       |            | ocessing Flow                                                                  |       |

| •                       |            | thic Hermetic Product Processing Flow                                          |       |

| •                       |            | f Integrated Device Technology Products for High-Radiation Environments        |       |

| •                       |            | s in the Testing of Fast CMOS Devices                                          |       |

|                         |            | les                                                                            |       |

|                         |            |                                                                                |       |

|                         | •          | nation                                                                         |       |

| Factory Direct          | Offices, D | Domestic and International Representatives, Authorized Distributors            | 8-114 |

### **NUMERIC TABLE OF CONTENTS**

| PART #       |                                  | PAGE |

|--------------|----------------------------------|------|

| 39C01C/D/E   | 4-Bit Microprocessor Slice       | 3-1  |

| 39C02A       | Carry Lookahead Generator        | 3-12 |

| 39C03A/B     | 4-Bit Microprocessor Slice       |      |

| 39C09A/B     | 4-Bit Sequencer                  | 3-47 |

| 39C10B/C     | 12-Bit Sequencer                 | 3-61 |

| 39C11A/B     | 4-Bit Sequencer                  | 3-47 |

| 39C203/A     | 4-Bit Microprocessor Slice       | 3-71 |

| 39C60        | 16-Bit Cascadeable E.D.C         | 3-73 |

| 39C705A/B    | 16x4 Register File Extension     | 3-99 |

| 39C707/A     | 16x4 Register File Extension     | 3-99 |

| 39C821       | 10-Bit Non-inverting Register    | 5-1  |

| 39C822       | 10-Bit Inverting Register        | 5-1  |

| 39C823       | 9-Bit Non-inverting Register     |      |

| 39C824       | 9-Bit Inverting Register         |      |

| 39C825       | 8-Bit Non-inverting Register     |      |

| 39C826       | 8-Bit Inverting Register         |      |

| 39C841       | 10-Bit Non-inverting Latch       |      |

| 39C842       | 10-Bit Inverting Latch           | 5-7  |

| 39C843       | 9-Bit Non-inverting Latch        | 5-7  |

| 39C844       | 9-Bit Inverting Latch            |      |

| 39C845       | 8-Bit Non-inverting Latch        | 5-7  |

| 39C846       | 8-Bit Inverting Latch            |      |

| 39C861       | 10-Bit Non-inverting Transceiver | 5-13 |

| 39C862       | 10-Bit Inverting Transceiver     |      |

| 39C863       | 9-Bit Non-inverting Transceiver  |      |

| 39C864       | 9-Bit Inverting Transceiver      | 5-13 |

| 49C25        | Microcycle Length Controller     |      |

| 49C401/A     | 16-Bit Microprocessor Slice      |      |

| 49C402/A     | 16-Bit Microprocessor Slice      |      |

| 49C403/A     | 16-Bit Microprocessor Slice      |      |

| 49C404       | 32-Bit Microprocessor Slice      |      |

| 49C410/A     | 16-Bit Sequencer                 |      |

| 49C460/A     | 32-Bit Cascadeable E.D.C.        |      |

| 49C818       | Octal Register with SPC™         |      |

| 54/74AHCT138 | 1-of-8 Decoder                   |      |

| 54/74AHCT139 | Dual 1-of-4 Decoder              |      |

| 54/74AHCT161 | Synchronous Binary Counter       |      |

| 54/74AHCT163 | Synchronous Binary Counter       |      |

| 54/74AHCT182 | Carry Lookahead Generator        |      |

| 54/74AHCT191 | Up/Down Binary Counter           |      |

| 54/74AHCT193 | Up/Down Binary Counter           |      |

| 54/74AHCT240 | Octal Buffer                     |      |

| 54/74AHCT244 | Octal Buffer                     |      |

| 54/74AHCT245 | Octal Bidirectional Transceiver  |      |

| 54/74AHCT273 | Octal D Flip-Flop                |      |

| 54/74AHCT299 | Universal Shift Register         |      |

| 54/74AHCT373 | Octal Transparent Latch          |      |

| 54/74AHCT374 | Octal D Flip-Flop                |      |

| 54/74AHCT377 | Octal D Flip-Flop                |      |

| 54/74AHCT521 | 8-Bit Comparator                 |      |

| 54/74AHCT533 | Octal Transparent Latch          |      |

| 54/74AHCT534 | Octal D Flip-Flop                |      |

| 54/74AHCT573 | Octal Transparent Latch          | 5-84 |

# NUMERIC TABLE OF CONTENTS (CONT'D)

| PART #        |                                       | PAGE  |

|---------------|---------------------------------------|-------|

| 54/74AHCT574  | Octal D Register                      | 5-88  |

| 54/74AHCT640  | Octal Bidirectional Transceiver       | 5-92  |

| 54/74AHCT645  | Octal Bidirectional Transceiver       | 5-95  |

| 54/74FCT138/A | 1-of-8 Decoder                        | 5-98  |

| 54/74FCT139/A | Dual 1-of-4 Decoder                   | 5-102 |

| 54/74FCT161/A | Synchronous Binary Counter            | 5-105 |

| 54/74FCT163/A | Synchronous Binary Counter            | 5-105 |

| 54/74FCT182/A | Carry Lookahead Generator             | 5-109 |

| 54/74FCT191/A | Up/Down Binary Counter                | 5-113 |

| 54/74FCT193/A | Up/Down Binary Counter                | 5-117 |

| 54/74FCT240/A | Octal Buffer                          | 5-121 |

| 54/74FCT244/A | Octal Buffer                          | 5-125 |

| 54/74FCT245/A | Octal Bidirectional Transceiver       | 5-129 |

| 54/74FCT273/A | Octal D Flip-Flop                     | 5-133 |

| 54/74FCT299/A | Octal Universal Shift Register        | 5-137 |

| 54/74FCT373/A | Octal Transparent Latch               | 5-141 |

| 54/74FCT374/A | Octal D Flip-Flop                     | 5-145 |

| 54/74FCT377/A | Octal D Flip-Flop                     |       |

| 54/74FCT521/A | 8-Bit Comparator                      | 5-153 |

| 54/74FCT533/A | Octal Transparent Latch               |       |

| 54/74FCT534/A | Octal D Flip-Flop                     | 5-160 |

| 54/74FCT573/A | Octal Transparent Latch               | 5-164 |

| 54/74FCT574/A | Octal D Register                      | 5-168 |

| 54/74FCT640/A | Octal Bidirectional Transceiver       | 5-172 |

| 54/74FCT645/A | Octal Bidirectional Transceiver       | 5-176 |

| 54/74FCT821B  | 10-Bit Non-inverting Register         | 5-180 |

| 54/74FCT822B  | 10-Bit Inverting Register             | 5-180 |

| 54/74FCT823B  | 9-Bit Non-inverting Register          |       |

| 54/74FCT824B  | 9-Bit Inverting Register              | 5-180 |

| 54/74FCT825B  | 8-Bit Non-inverting Register          | 5-180 |

| 54/74FCT826B  | 8-Bit Inverting Register              | 5-180 |

| 54/74FCT841B  | 10-Bit Non-inverting Latch            | 5-186 |

| 54/74FCT842B  | 10-Bit Inverting Latch                | 5-186 |

| 54/74FCT843B  | 9-Bit Non-inverting Latch             | 5-186 |

| 54/74FCT844B  | 9-Bit Inverting Latch                 | 5-186 |

| 54/74FCT845B  | 8-Bit Non-inverting Latch             | 5-186 |

| 54/74FCT846B  | 8-Bit Inverting Latch                 | 5-186 |

| 54/74FCT861B  | 10-Bit Non-inverting Transceiver      | 5-192 |

| 54/74FCT862B  | 10-Bit Inverting Transceiver          | 5-192 |

| 54/74FCT863B  | 9-Bit Non-inverting Transceiver       |       |

| 54/74FCT864B  | 9-Bit Inverting Transceiver           | 5-192 |

| 6116A         | 16K (2Kx8) Static RAM                 | 2-1   |

| 6167A         | 16K (16Kx1) Static RAM                | 2-8   |

| 6168A         | 16K (4Kx4) Static RAM                 |       |

| 7130          | 8K (1Kx8) Dual-Port Static RAM        |       |

| 7132          | 16K (2Kx8) Dual-Port Static RAM       |       |

| 7133          | 32K 2Kx16 Dual-Port Static RAM        |       |

| 7134          | 32K (4Kx8) Dual-Port Static RAM       |       |

| 7140          | 8K (1Kx8) Slave Dual-Port Static RAM  |       |

| 7142          | 16K (2Kx8) Slave Dual-Port Static RAM |       |

| 7143          | 32K 2Kx16 Slave Dual-Port Static RAM  |       |

| 7164          | 64K (8Kx8) Static RAM                 |       |

| 7165          | 64K (8Kx8) Static RAM                 | 2-67  |

# **NUMERIC TABLE OF CONTENTS (CONT'D)**

| PART # |                                                                | PAGE  |

|--------|----------------------------------------------------------------|-------|

| 7174   | 64K (8Kx8) Static RAM                                          | 2-82  |

| 7187   | 64K (64Kx1) Static RAM                                         | 2-89  |

| 7188   | 64K (16Kx4) Static RAM                                         | 2-95  |

| 7198   | 64K (16Kx4) Static RAM                                         | 2-101 |

| 7201   | 512x9 Parallel In-Out FIFO                                     | 4-11  |

| 7201A  | 512x9 Half-Full Flag FIFO                                      |       |

| 7202   | 1024x9 Parallel In-Out FIFO                                    | 4-11  |

| 7202A  | 1024x9 Half-Full Flag FIFO                                     | 4-1   |

| 7203   | 2048Kx9 Parallel In-Out FIFO                                   | 4-21  |

| 7204   | 4096Kx9 Parallel In-Out FIFO                                   | 4-21  |

| 7209   | 12x12 Parallel Multiplier-Accumulator                          | 4-35  |

| 7210   | 16x16 Parallel Multiplier-Accumulator                          | 4-42  |

| 7212   | 12x12 Parallel Multiplier                                      | 4-52  |

| 7213   | 12x12 Parallel Multiplier                                      | 4-52  |

| 7216   | 16x16 Parallel Multiplier                                      | 4-61  |

| 7217   | 16x16 Parallel Multiplier                                      | 4-61  |

| 7243   | 16x16 Parallel Multiplier-Accumulator                          | 4-42  |

| 71256  | 256K (32Kx8) Static RAM                                        | 2-23  |

| 71257  | 256K (256Kx1) Static RAM                                       | 2-25  |

| 71258  | 256K (64Kx4) Static RAM                                        | 2-27  |

| 71322  | 16K (2Kx8) Dual-Port Static RAM                                | 2-51  |

| 71341  | 32K (4Kx8) Dual-Port Static RAM                                | 2-57  |

| 71681A | 16K (4Kx4) Static RAM                                          | 2-73  |

| 71682A | 16K (4Kx4) Static RAM                                          |       |

| 71981  | 64K (16Kx4) Static RAM                                         |       |

| 71982  | 64K (16Kx4) Static RAM                                         |       |

| 72064  | 64-Bit Floating Point Multiplier                               | 4-31  |

| 72065  | 64-Bit Floating Point ALU                                      |       |

| 72103  | 2084Kx9 Half-Full Flag FIFO                                    | 4-50  |

| 72104  | 4096Kx9 Half-Full Flag FIFO                                    | 4-50  |

| 72264  | 64-Bit Floating Point Multiplier                               | 4-71  |

| 72265  | 64-Bit Floating Point ALU                                      | 4-71  |

| 72401  | 64x4 Parallel In-Out FIFO                                      |       |

| 72402  | 64x5 Parallel In-Out FIFO                                      | 4-75  |

| 72403  | 64x4 Parallel In-Out FIFO                                      | 4-75  |

| 72404  | 64x5 Parallel In-Out FIFO                                      |       |

| 72413  | Parallel 64x5 FIFO                                             |       |

| 75C18  | 8-Bit 125MHz Video DAC                                         |       |

| 75C28  | 8-Bit 125MHz Video DAC                                         |       |

| 7MP624 | 1 Megabit (64Kx16, 128Kx8 or 256Kx4) Plastic Static RAM Module |       |

| 7M134  | 64K (8Kx8) Dual-Port RAM Module                                |       |

| 7M135  | 128K (16Kx8) Dual-Port RAM Module                              |       |

| 7M136  | 128K (16Kx8) Dual-Port RAM Module                              |       |

| 7M137  | 256K (32Kx8) Dual-Port RAM Module                              |       |

| 7M144  | 64K (8Kx8) Slave Dual-Port RAM Module                          | 7-15  |

| 7M145  | 128K (16Kx8) Slave Dual-Port RAM Module                        |       |

| 7M203  | 2Kx9-Bit Parallel In-Out FIFO                                  |       |

| 7M204  | 4Kx9-Bit Parallel In-Out FIFO                                  |       |

| 7M205  | 8Kx9-Bit Parallel In-Out FIFO                                  |       |

| 7M206  | 16Kx9-Bit Parallel In-Out FIFO                                 |       |

| 7M624  | 1 Megabit (64Kx16, 128Kx8 or 256Kx4) Static RAM Module         |       |

| 7M656  | 256K (16Kx16, 32Kx8 or 64Kx4) Static RAM Module                |       |

| 7M812  | 512K 64Kx8 Static RAM Module                                   |       |

| 7M824  | 1 Megabit (128Kx8) Static RAM Module                           | /-46  |

# **NUMERIC TABLE OF CONTENTS (CONT'D)**

| PART # | ·                                            | PAGE |

|--------|----------------------------------------------|------|

| 7M856  | 256K (32Kx8) Static RAM Module               | 7-49 |

| 7M864  | 64K (8Kx8) Static RAM Module                 | 7-55 |

| 7M912  | 512K (64Kx8 or 64Kx9) Static RAM Module      |      |

| 8MP612 | 512K (32Kx16) Plastic Static RAM Module      |      |

| 8M612  | 512K (32K×16) Static RAM Module              | 7-66 |

| 8MP624 | 1 Megabit (64Kx16) Plastic Static RAM Module | 7-60 |

| 8M624  | 1 Megabit (64Kx16) Static RAM Module         | 7-66 |

| 8MP628 | 128K (8Kx16) Plastic Static RAM Module       |      |

| 8M628  | 128K (8Kx16) Static RAM Module               |      |

| 8MP656 | 256K (16Kx16) Plastic Static RAM Module      | 7-62 |

| 8M656  | 256K (16Kx16) Static RAM Module              | 7-68 |

| 8MP824 | 1 Megabit (128Kx8) Plastic Static RAM Module | 7-64 |

| 8M824  | 1 Megabit (128Kx8) Static RAM Module         | 7-75 |

| 8M856  | 256K (32Kx8) Static RAM Module               | 7-77 |

| 8M864  | 64K (8Kx8) Static RAM Module                 | 7-55 |

### High-Speed CMOS MICROSLICE™ Products

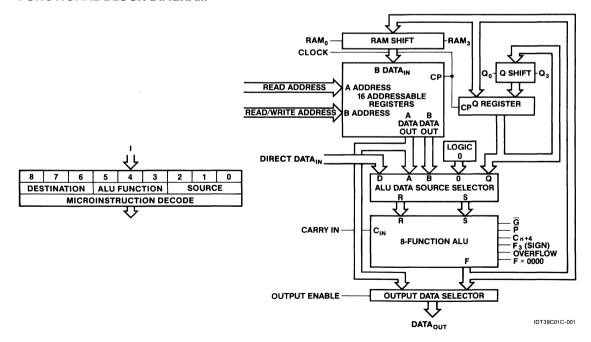

- CMOS microprogrammable bit-slice microprocessor family

- Meets or exceeds bipolar speeds and output drive at a small fraction of the power consumption

- Sequential letter suffix designates 20%-40% speed upgrade

- Instruction set/operation codes functionally identical to 2900 family

- IDT39C000 products are pin-compatible, performanceenhanced 2900 family replacements

- IDT49C000 products offer dramatically improved system performance through new innovative architectures

- · Available in military and commercial temperature ranges

- Produced with advanced CEMOS<sup>™</sup> high-performance technology

|   |                                     |                                                                                                                                                     |                                                             |               |      |              | Page  |

|---|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------|------|--------------|-------|

|   | Part Number                         | Description                                                                                                                                         | Replaces                                                    | (mV<br>Com'l. | Mil. | Availability | No.   |

|   | IDT39C01C<br>IDT39C01D<br>IDT39C01E | 4-Bit μP Slice                                                                                                                                      | Am2901B,C; Am29C01C;<br>IDM2901A,-2; SFC2901B,C;<br>CY7C901 | 105           | 165  | NOW          | 3-1   |

|   | IDT39C03A<br>IDT39C03B              | 4-Bit μP Slice                                                                                                                                      | Am2903, SFC2903                                             | 265           | 330  | NOW          | 3-15  |

|   | IDT39C203<br>IDT39C203A             | 4-Bit μP Slice                                                                                                                                      | Am29203                                                     | 265           | 330  | NOW          | 3-71  |

|   | IDT49C401<br>IDT49C401A             | 16-Bit μP Slice                                                                                                                                     | IMI4X2901B                                                  | 660           | 825  | NOW          | 3-103 |

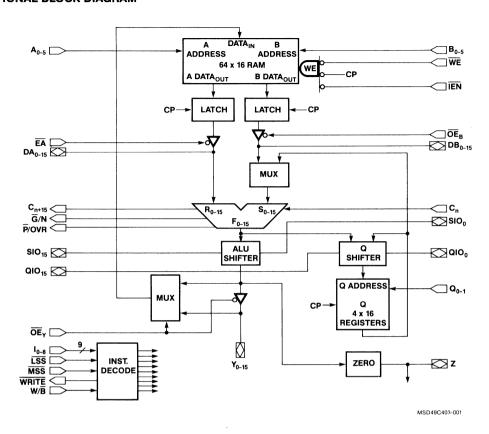

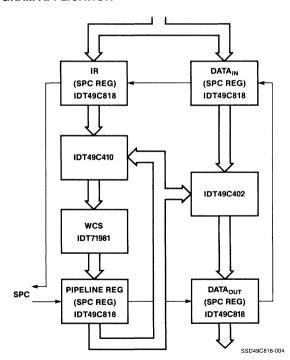

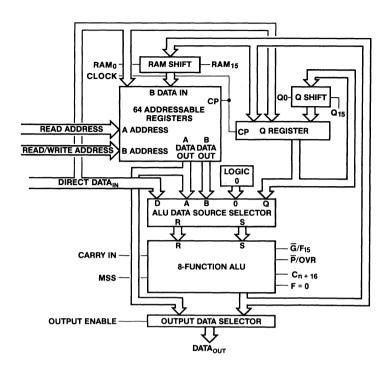

|   | IDT49C402<br>IDT49C402A             | 16-Bit µP Slice, Quad 2901 with 8 additional destination functions and a 64 × 16 dualport memory capacity                                           | UNIQUE                                                      | 660           | 825  | NOW          | 3-113 |

|   | IDT49C403<br>IDT49C403A             | 16-Bit µP Slice, Quad 2903/<br>29203 with 64 × 16 register<br>file, 4 Q-registers, word/BYTE<br>control, BYTE swap,<br>cascadeable                  | UNIQUE                                                      | 660           | 825  | NOW          | 3-124 |

|   | IDT49C404<br>IDT49C404A             | 32-Bit µP Slice, 3-port device with 32-Bit ALU, 64 × 32 register file, cascadeable funnel shifter, priority encoder, merge logic and mask generator | UNIQUE                                                      | 3500          | 4000 | Q4 '86       | 3-126 |

| 2 | IDT39C09A<br>IDT39C09B              | 4-Bit Sequencer                                                                                                                                     | Am2909A; CY7C909;<br>SFC2909; LM2909                        | 130           | 165  | NOW          | 3-47  |

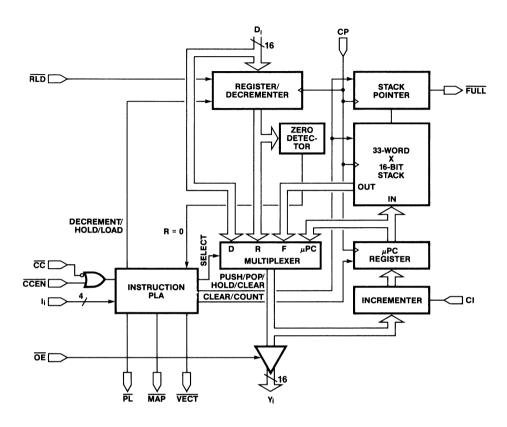

|   | IDT39C10B<br>IDT39C10C              | 12-Bit Sequencer with<br>33-Deep Stack                                                                                                              | Am2910A; CY7C910;<br>SFC2910; IDM2910                       | 395           | 495  | NOW          | 3-61  |

|   | IDT39C11A<br>IDT39C11B              | 4-Bit Sequencer                                                                                                                                     | Am2911A; CY7C911;<br>SFC2911A; IDM2911A                     | 130           | 165  | NOW          | 3-47  |

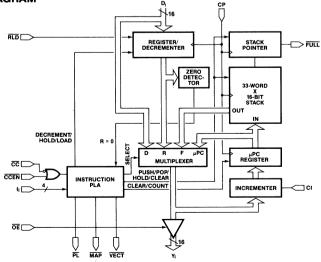

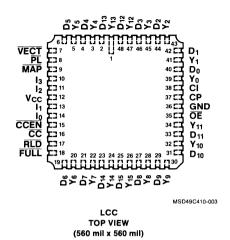

| ) | IDT49C410<br>IDT49C410A             | 16-Bit Sequencer with<br>33-Deep Stack                                                                                                              | UNIQUE                                                      | 395           | 495  | NOW          | 3-128 |

|   | IDT39C705A<br>IDT39C705B            | 16 × 4 Register File Extension                                                                                                                      | Am29705A                                                    | 105           | 165  | NOW          | 3-99  |

|   | IDT39C707<br>IDT39C707A             | 16 × 4 Register File Extension                                                                                                                      | Am29707                                                     | 105           | 165  | NOW          | 3-99  |

|   | IDT49C470<br>IDT49C470A             | 64 × 16 Register File                                                                                                                               | UNIQUE                                                      | _             |      | Q4 '86       | *     |

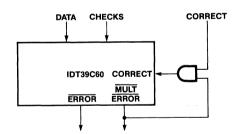

|   | IDT39C60<br>IDT39C60-1<br>IDT39C60A | 16-Bit Cascadeable Error<br>Detection Correction Unit                                                                                               | Am2960-1,A; N2960                                           | 450           | 550  | NOW          | 3-73  |

|   | IDT49C460<br>IDT49C460A             | 32-Bit Cascadeable Error<br>Detection Correction Unit                                                                                               | UNIQUE                                                      | 500           | 690  | NOW          | 3-138 |

|   | IDT39C02A                           | Carry Lookahead Generator                                                                                                                           | Am2902A                                                     | 30            | 30   | NOW          | 3-12  |

| : | IDT49C25                            | Clock Generator                                                                                                                                     | Am2925                                                      | 30            | 30   | NOW          | 3-101 |

\*Contact Factory

### **High-Speed CMOS Static RAMs**

- · Extremely fast access times

- · Low power consumption

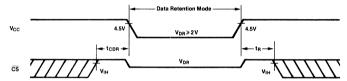

- 2V data retention battery backup on all low-power devices

- · Three-state outputs

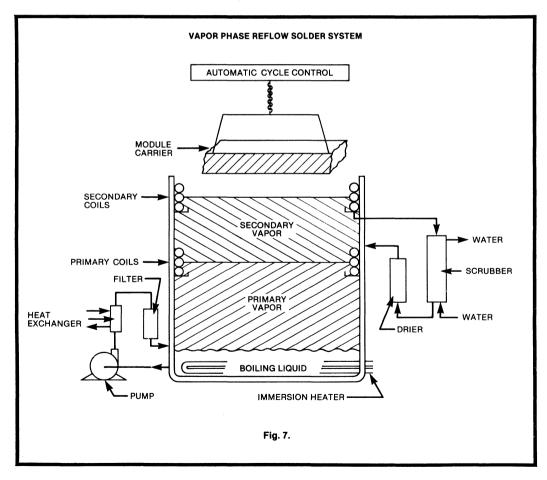

- 'M' type ceramic RAM modules are built with IDT monolithic RAMs in LCC packages surface mounted onto multi-layered, co-fired ceramic substrates using IDT's high-reliability vapor phase reflow soldering process

- 'MP' type commercial plastic modules are built using IDT monolithic RAMs in SMD plastic packages, surface mounted onto epoxy laminate (FR4) substrates

|             |                                                                                                                            |                |                      | Power         | (typical)       |              |             |

|-------------|----------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|---------------|-----------------|--------------|-------------|

| Part Number | Description                                                                                                                | Max. S<br>Mil. | Speed (ns)<br>Com'l. | Oper.<br>(mW) | Standby<br>(μW) | Availability | Page<br>No. |

| IDT6116A    | 16K (2K × 8)                                                                                                               | 35             | 30                   | 250           | 30              | NOW          | 2-1         |

| IDT6120     | 16K (2K × 8) with high-speed chip select (chip select access time)                                                         | 20             | 18                   | 200           | _               | Q4 '86       | *           |

| IDT6167A    | 16K (16K × 1)                                                                                                              | 20             | 15                   | 200           | 10              | NOW          | 2-8         |

| IDT6168A    | 16K (4K × 4)                                                                                                               | 25             | 20                   | 225           | 10              | NOW          | 2-15        |

| IDT6169     | 16K (4K × 4) with high-speed chip select (chip select access time)                                                         | 15             | 12                   | 225           | _               | Q4 '86       |             |

| IDT71681A   | 16K (4K × 4) with separate data inputs and outputs; outputs track inputs during write mode                                 | 25             | 20                   | 225           | 10              | NOW          | 2-73        |

| IDT71682A   | 16K (4K × 4) with separate data inputs and outputs; outputs in high impedance state during write mode                      | 25             | 20                   | 225           | 10              | NOW          | 2-73        |

| IDT7164     | 64K (8K × 8)                                                                                                               | 45             | 30                   | 300           | 30              | NOW          | 2-59        |

| IDT7165     | 64K (8K × 8) with asynchronous clear and high-speed chip select                                                            | 45             | 30                   | 300           | 30              | NOW          | 2-67        |

| IDT7174     | 64K (8K × 8) with cache address<br>comparator, asynchronous clear<br>and high-speed chip select                            | 45             | 35                   | 300           |                 | NOW          | 2-82        |

| IDT7187     | 64K (64K × 1)                                                                                                              | 30             | 25                   | 250           | 30              | NOW          | 2-89        |

| IDT7188     | 64K (16K × 4)                                                                                                              | 30             | 25                   | 300           | 30              | NOW          | 2-95        |

| IDT7198     | 64K (16K × 4) output enable (OE) and second chip select (CS <sub>2</sub> ) for added system flexibility and memory control | 30             | 25                   | 300           | 30              | NOW          | 2-101       |

| IDT71981    | 64K (16K × 4) with separate data inputs and outputs; outputs track inputs during write mode                                | 30             | 25                   | 300           | 30              | NOW          | 2-108       |

| IDT71982    | 64K (16K × 4) with separate data inputs and outputs; outputs in high impedance state during write mode                     | 30             | 25                   | 300           | 30              | NOW          | 2-108       |

| IDT71256    | 256K (32K × 8)                                                                                                             | 55             | 45                   | 350           | 100             | Q4 '86       | 2-23        |

| IDT71257    | 256K (256K × 1)                                                                                                            | 45             | 35                   | 350           | 100             | Q1 '87       | 2-25        |

| IDT71258    | 256K (64K × 4)                                                                                                             | 45             | 35                   | 350           | 100             | Q1 '87       | 2-27        |

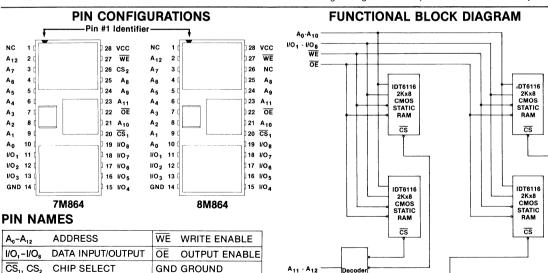

| IDT7M864    | 64K (8K × 8) RAM module with static RAM pinout                                                                             | 75             | 65                   | 325           | 80              | NOW          | 7-55        |

| IDT8M864    | 64K (8K $\times$ 8) RAM module with EPROM pinout                                                                           | 75             | 65                   | 325           | 80              | NOW          | 7-55        |

| IDT8M628    | 128K (8K $	imes$ 16) RAM module with monolithic pinout                                                                     | 60             | 50                   | 750           | 750             | Q4 '86       | 7-68        |

| IDT8MP628   | 128K (8K × 16) plastic SIP RAM module                                                                                      |                | 50                   | 750           | 750             | NOW          | 7-62        |

| IDT7M656    | 256K (16K × 16, 32K × 8, 64K × 4) RAM module – customer configurable organization                                          | 35             | 25                   | 2000          | 1500            | NOW          | 7-35        |

\*Contact Factory

## High-Speed CMOS Static RAMs (continued)

| Part Number | Description                                                                                            | Max.<br>Mil. | . Speed (ns)<br>Com'l. | Power<br>Oper.<br>(mW) | r (typical)<br>Standby<br>(μW) | Availability | Page<br>No. |

|-------------|--------------------------------------------------------------------------------------------------------|--------------|------------------------|------------------------|--------------------------------|--------------|-------------|

| IDT7M856    | 256K (32K × 8) RAM module with monolithic pinout                                                       | 55           | 50                     | 950                    | 1000                           | NOW          | 7-49        |

| IDT8M856    | 256K (32K × 8) RAM module with monolithic pinout (low-power)                                           | 55           | 50                     | 350                    | 500                            | NOW          | 7-77        |

| IDT8M656    | 256K (16K × 16) RAM module with monolithic pinout                                                      | 60           | 50                     | 1000                   | 1000                           | Q4 '86       | 7-68        |

| IDT8MP656   | 256K (16K × 16) plastic SIP RAM module                                                                 |              | 50                     | 1000                   | 1000                           | NOW          | 7-62        |

| IDT7M812    | 512K (64K × 8) RAM module offer-<br>ing maximum addressable memory<br>required by 8-bit MPs            | 55           | 45                     | 1800                   | 900                            | NOW          | 7-41        |

| IDT7M912    | 512K (64K x 9) RAM module offer-<br>ing maximum addressable memory<br>required by 8-bit MPs            | 55           | 45                     | 1800                   | 900                            | NOW          | 7-41        |

| IDT8M612    | 512K (32K × 16) RAM module with monolithic pinout                                                      | 75           | 60                     | 1000                   | 300                            | Q1 '87       | 7-66        |

| IDT8MP612   | 512K (32K × 16) plastic SIP RAM module                                                                 |              | 60                     | 1000                   | 300                            | Q4 '86       | 7-60        |

| IDT7M624    | 1 Megabit (64K × 16, 128K × 8,<br>256K × 4) RAM module – customer<br>configurable organization         | 40           | 30                     | 2000                   | 1600                           | NOW          | 7-29        |

| IDT7MP624   | 1 Megabit (64K × 16, 128K × 8,<br>256K × 4) plastic RAM module –<br>customer configurable organization |              | 30                     | 2000                   | 1600                           | Q4 '86       | 7-1         |

| IDT8M824    | 1 Megabit (128K × 8) RAM module with monolithic pinout                                                 | 75           | 60                     | 500                    | 150                            | Q1 '87       | 7-75        |

| IDT8MP824   | 1 Megabit (128K × 8) plastic SIP<br>RAM module                                                         |              | 60                     | 500                    | 150                            | Q4 '86       | 7-64        |

| IDT7M824    | Megabit (128K × 8) RAM module<br>with registered buffered/latched<br>addresses and I/Os                | 75           | 65                     | 950                    | 1600                           | NOW          | 7-46        |

| IDT8M624    | 1 Megabit (64K × 16) RAM module with monolithic pinout                                                 | 75           | 60                     | 1000                   | 300                            | Q1 '87       | 7-66        |

| IDT8MP624   | 1 Megabit (64K × 16) plastic SIP<br>RAM module                                                         | _            | 60                     | 1000                   | 300                            | Q4 '86       | 7-66        |

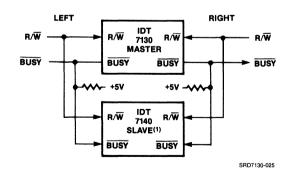

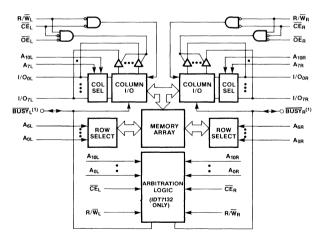

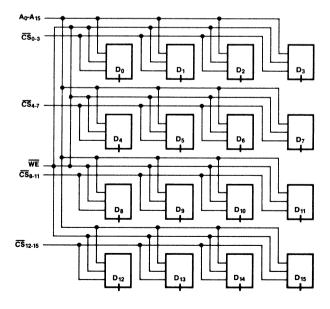

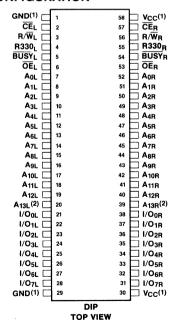

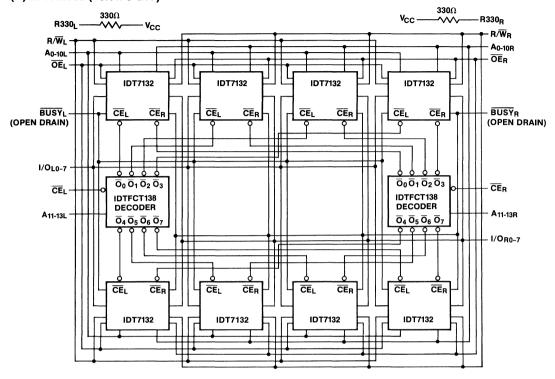

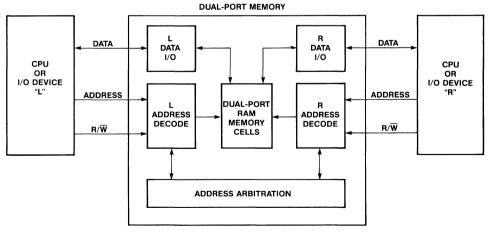

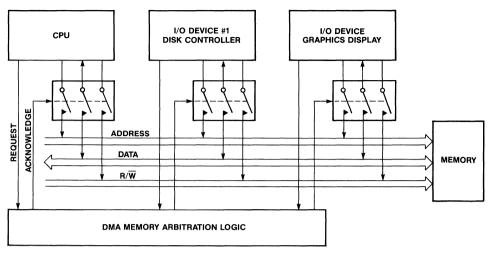

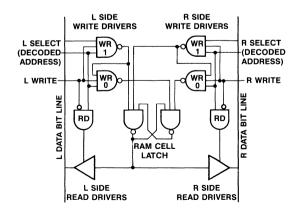

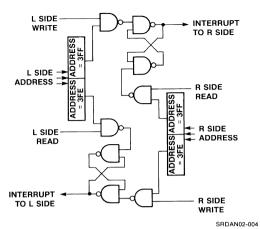

### **High-Speed CMOS Dual-Port RAMs**

- High-speed, low-power

- Independent read or write access to any memory location from either port

- Each port has separate controls, address and I/O

- · On-chip port arbitration logic

- Fully asynchronous operation from either port

- INT and BUSY flags (BUSY only in IDT7132/7142)

- Automatic power-down feature controlled by CE

- 2V data retention battery back-up on all low-power devices

- Dual-port RAM modules built with IDT monolithic dualport RAMs in LCC packages, surface mounted to multilayered, co-fired ceramic substrates using IDT's highreliability vapor phase reflow soldering process

|             |                                                                                                                         | Power (typical) |                      |               |                 |               |             |

|-------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|---------------|-----------------|---------------|-------------|

| Part Number | Description                                                                                                             | Max. S<br>Mil.  | Speed (ns)<br>Com'l. | Oper.<br>(mW) | Standby<br>(mW) | Availability  | Page<br>No. |

| IDT7130     | 8K (1K × 8) replaces Synertek<br>SY2130                                                                                 | 70<br>55        | 55<br>45             | 325           | 1               | NOW<br>Q4 '86 | 2-29        |

| IDT7132     | 16K (2K $\times$ 8) largest monolithic dualport static RAM available in the industry                                    | 70<br>55        | 55<br>45             | 325           | 1               | NOW<br>Q4 '86 | 2-41        |

| IDT7140     | 8K (1K × 8) functions as slave with IDT7130 to provide 16-bit words or wider; pin compatible with IDT7130               | 70<br>55        | 55<br>45             | 325           | 1               | NOW<br>Q4 '86 | 2-29        |

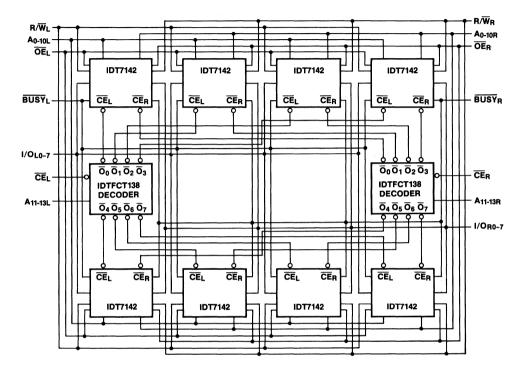

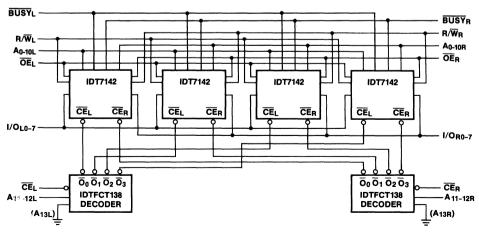

| IDT7142     | 16K (2K × 8) functions as slave with IDT7132 to provide 16-bit words or wider; pin compatible with IDT7132              | 70<br>55        | 55<br>45             | 325           | 1               | NOW<br>Q4 '86 | 2-41        |

| IDT71322    | 16K (2K × 8) with Semaphore                                                                                             | 55              | 45                   | 325           | 1               | Q1 '87        | 2-51        |

| IDT7133     | 32K (2K × 16)                                                                                                           | 90              | 70                   | 325           | 1               | Q4 '86        | 2-53        |

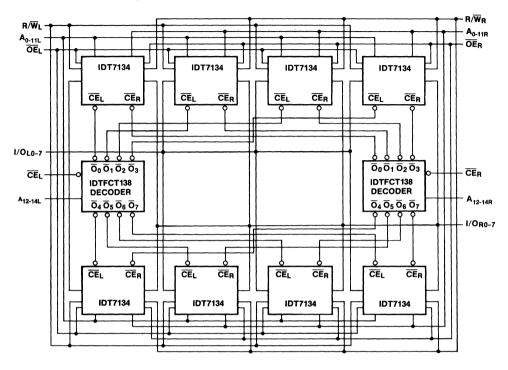

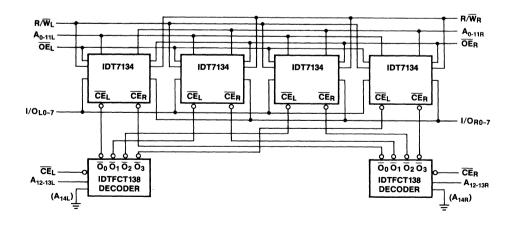

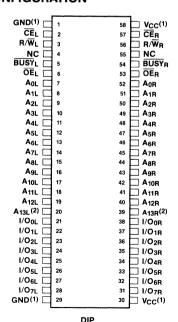

| IDT7134     | 32K (4K × 8) high-speed operation in system where on-chip arbitration is not needed                                     | 55              | 45                   | 325           | 1               | Q1 '87        | 2-55        |

| IDT71341    | 32K (4K × 8) with Semaphore                                                                                             | 55              | 45                   | 325           | 1               | Q1 '87        | 2-57        |

| IDT7143     | 32K (2K × 16) functions as slave<br>with IDT7133 to provide 32-bit<br>words or wider                                    | 90              | 70                   | 325           | 1               | Q4 '86        | 2-53        |

| IDT7M134    | 64K (8K × 8) dual-port RAM module                                                                                       | 90              | 70                   | 950           | 20              | NOW           | 7-3         |

| IDT7M135    | 128K (16K × 8) dual-port RAM<br>module                                                                                  | 90              | 70                   | 1600          | 50              | NOW           | 7-3         |

| IDT7M136    | 128K (16K × 8) functions in system where on-chip arbitration is not needed                                              | 80              | 60                   | 1000          | 30              | Q1'87         | 7-13        |

| IDT7M137    | 256K (32K × 8) dual-port RAM<br>module where on-chip arbitration is<br>not needed                                       | 80              | 60                   | 1800          | 60              | Q1'87         | 7-13        |

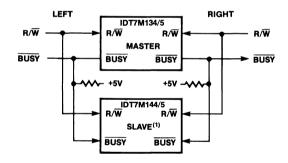

| IDT7M144    | 64K (8K × 8) functions as slave with IDT7M134 to provide 16-bit words or wider; pin compatible with IDT7M134            | 90              | 70                   | 950           | 20              | NOW           | 7-15        |

| IDT7M145    | 128K (16K × 8) functions as slave<br>with IDT7M135 to provide 16-bit<br>words or wider; pin compatible with<br>IDT7M135 | 90              | 70                   | 1600          | 50              | NOW           | 7-15        |

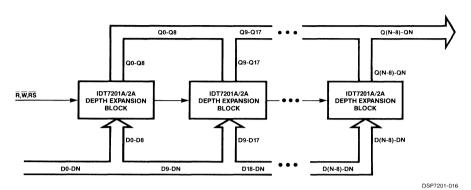

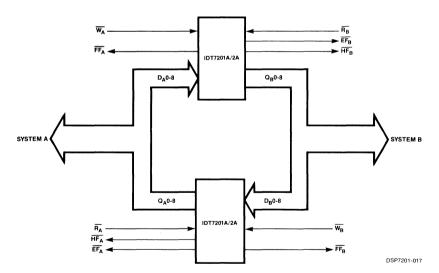

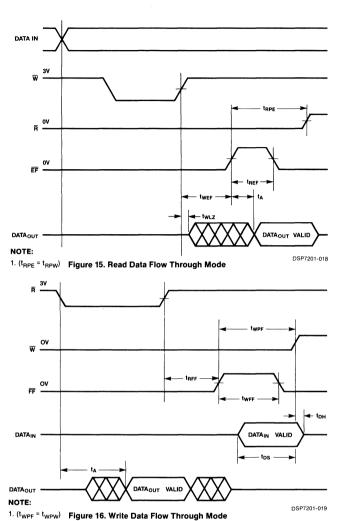

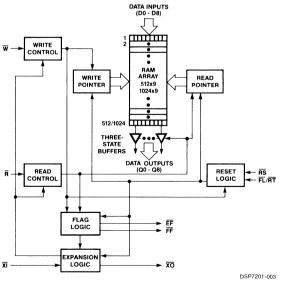

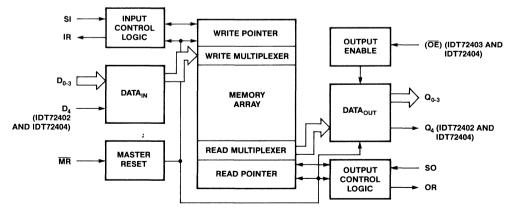

### **High-Speed CMOS FIFOs**

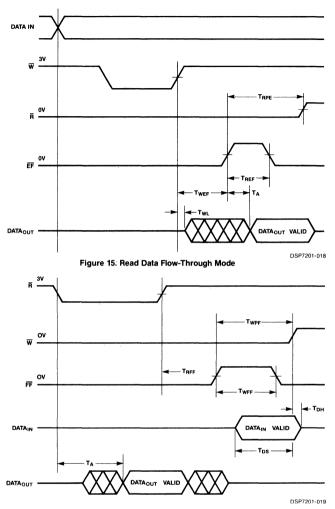

- · Extremely fast access and cycle times

- · Low-power consumption

- · Asynchronous and simultaneous read and write

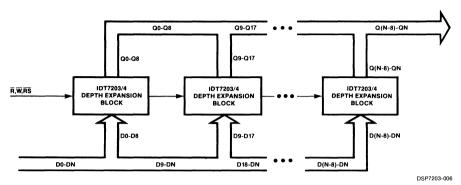

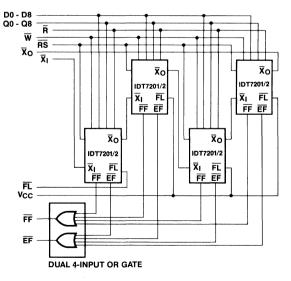

- Fully expandable by both word depth and/or bit width

- · Single read/write line operation

- · Empty, full and half-full flags indicate status

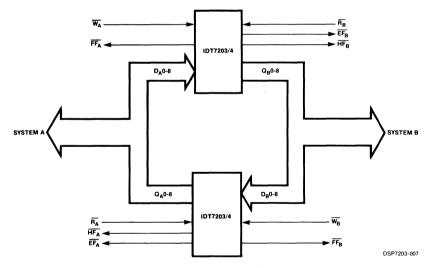

- · Master/slave multiprocessing applications

- · Bidirectional and rate buffer applications

- · Auto retransmit capability

- FIFO modules are built with IDT monolithic FIFOs in LCC packages, surface mounted to multi-layered, co-fired ceramic substrates using IDT's high-reliability vapor phase reflow soldering process

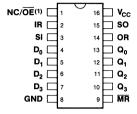

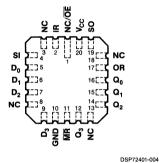

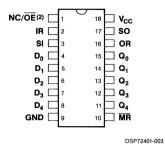

| Part Number | Description                                                     | Max. S<br>Mil. | Speed (ns)<br>Com'l. | Power<br>Oper.<br>(mW) | (typical)<br>Standby<br>(mW) | Availability | Page<br>No. |

|-------------|-----------------------------------------------------------------|----------------|----------------------|------------------------|------------------------------|--------------|-------------|

| IDT7201     | 512 × 9 replaces Mostek MK4501                                  | 40             | 35                   | 250                    | 25                           | NOW          | 4-11        |

| IDT7202     | 1024 × 9 largest monolithic FIFO available in the industry      | 40             | 35                   | 250                    | 25                           | NOW          | 4-11        |

| IDT7201A    | 512 × 9 half-full flag                                          | 40             | 35                   | 250                    | 25                           | NOW          | 4-1         |

| IDT7202A    | 1024 × 9 half-full flag                                         | 40             | 35                   | 250                    | 25                           | NOW          | 4-1         |

| IDT7203     | 2K × 9 half-full flag                                           | 50             | 50                   | 600                    | 100                          | Q4 '86       | 4-21        |

| IDT7204     | 4K × 9 half-full flag                                           | 50             | 50                   | 600                    | 100                          | Q4 '86       | 4-21        |

| IDT72103    | 2K × 9 serial input. Half-full, almostfull, almost-empty flags  | 50             | 50                   | 600                    | 100                          | Q4 '86       | 4-50        |

| IDT72104    | 4K × 9 serial input. Half-full, almost-full, almost-empty flags | 50             | 50                   | 600                    | 100                          | Q4 '86       | 4-50        |

| IDT72401    | 64 × 4 replace MMI 67401                                        | 60             | 50                   | 200                    | 20                           | Q1'87        | 4-75        |

| IDT72402    | 64 × 5 replace MMI 67402                                        | 60             | 50                   | 200                    | 20                           | Q1'87        | 4-75        |

| IDT72403    | 64 × 4 output enable                                            | 60             | 50                   | 200                    | 20                           | Q1'87        | 4-75        |

| IDT72404    | 64 × 5 output enable                                            | 60             | 50                   | 200                    | 20                           | Q1'87        | 4-75        |

| IDT72413    | 64 × 5 replace MMI 67413 output enable                          | 50             | 30                   | 200                    | 20                           | Q1'87        | 4-77        |

| IDT7M203    | 2K x 9 FIFO module using four IDT7201s                          | 50             | 40                   | 630                    | 100                          | NOW          | 7-18        |

| IDT7M204    | 4K × 9 FIFO module using four IDT7202s                          | 50             | 40                   | 630                    | 100                          | NOW          | 7-18        |

| IDT7M205    | 8K × 9 FIFO module using four IDT7203s                          | 65             | 60                   | 1400                   | 400                          | Q4'86        | 7-28        |

| IDT7M206    | 16K × 9 FIFO module using four IDT7204s                         | 65             | 60                   | 1400                   | 400                          | Q4'86        | 7-28        |

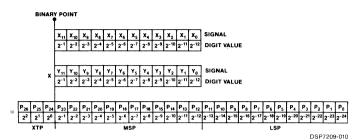

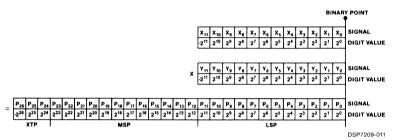

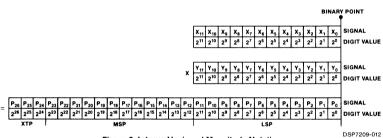

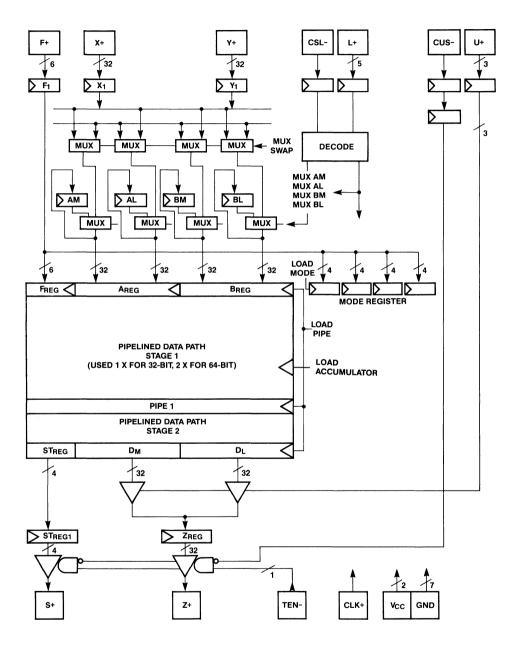

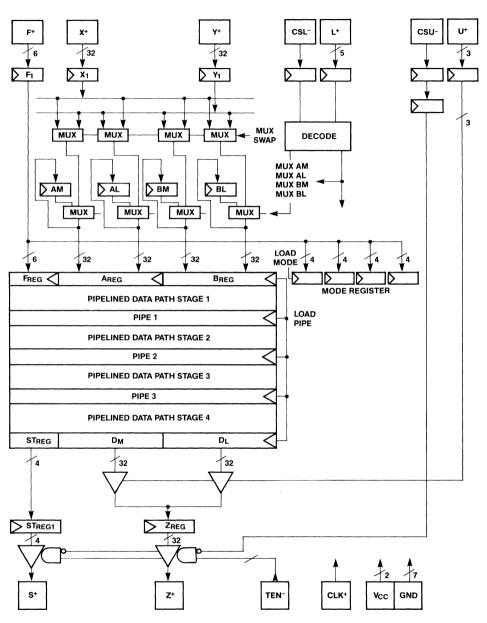

### **High-Speed CMOS Parallel Multiplier-Accumulators**

- · High-speed, low-power

- Parallel multiplier-accumulators with selectable accumulation, rounding and preloading

- Extended product output for multiple accumulations

- · Preload function allows output register to be preset

- All devices perform subtraction and double precision addition and multiplication

- Inputs and outputs directly TTL-compatible

|             |                                                                               | Power (typical) |                     |               |                  |              |             |

|-------------|-------------------------------------------------------------------------------|-----------------|---------------------|---------------|------------------|--------------|-------------|

| Part Number | Description                                                                   | Max. S<br>Mil.  | peed (ns)<br>Com'l. | Oper.<br>(mW) | Standby<br>(µmW) | Availability | Page<br>No. |

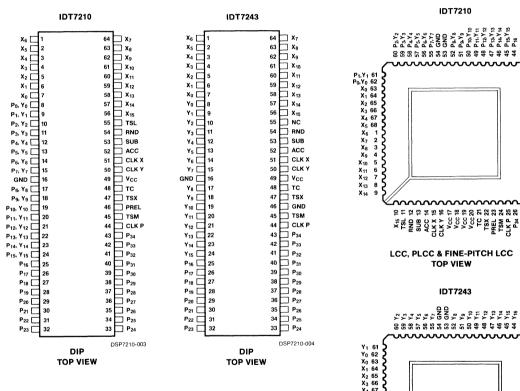

| IDT7209     | 12 × 12-pin and functionally compatible with TRW TDC1009J                     | 40              | 30                  | 200           | 500              | NOW          | 4-35        |

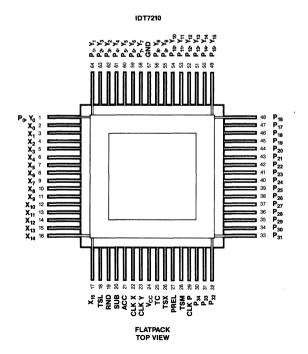

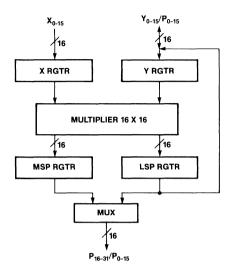

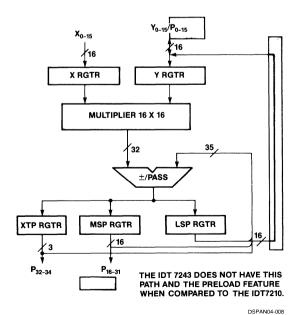

| IDT7210     | 16 x 16-with 35-bit output; pin and functionally compatible with TRW TDC1010J | 40              | 35                  | 200           | 500              | NOW          | 4-42        |

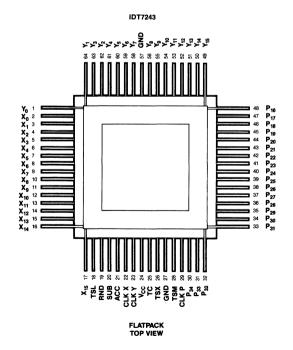

| IDT7243     | 16 x 16-with 19-bit output; pin and functionally compatible with TRW TDC1043  | 40              | 35                  | 200           | 500              | NOW          | 4-42        |

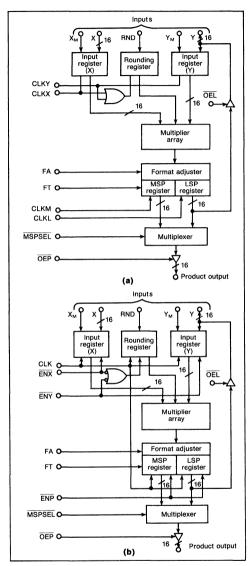

### **High-Speed CMOS Parallel Multipliers**

- · High-speed, low-power

- · Configured for easy array expansion

- User-controlled option for transparent output register mode

- · Round control for rounding the MSP

- Inputs and outputs directly TTL-compatible

- Three-state output controls and separate register enables

|             |                                                                                                | Power (typical) |                      |               |                 |              |             |

|-------------|------------------------------------------------------------------------------------------------|-----------------|----------------------|---------------|-----------------|--------------|-------------|

| Part Number | Description                                                                                    | Max. S<br>Mil.  | Speed (ns)<br>Com'l. | Oper.<br>(mW) | Standby<br>(μW) | Availability | Page<br>No. |

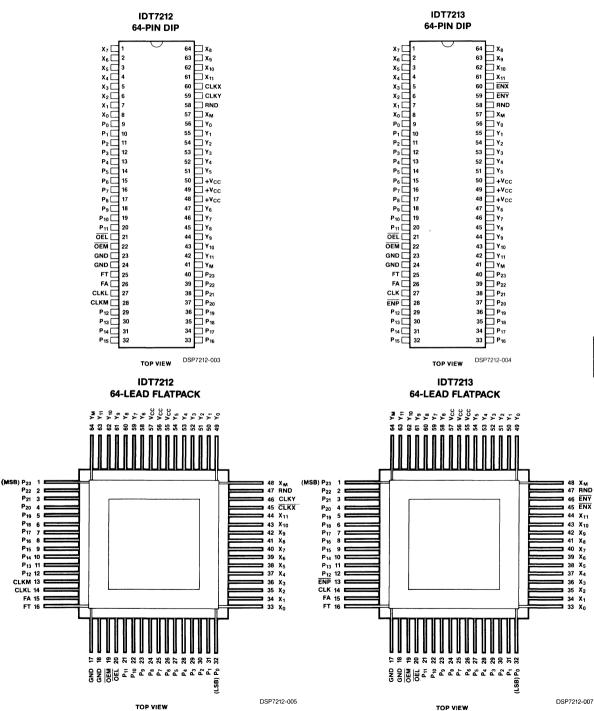

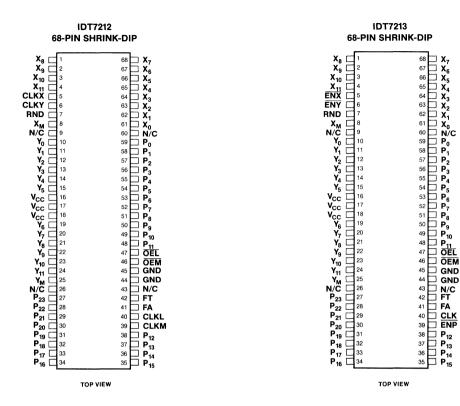

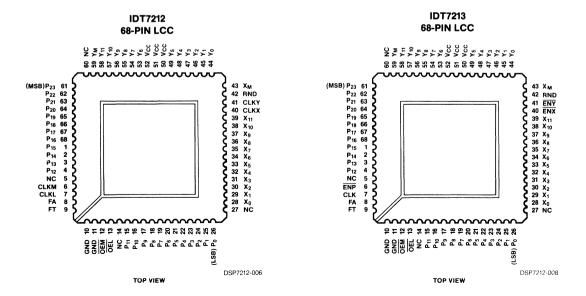

| IDT7212     | 12 × 12-pin and functionally compatible with TRW MPY012H                                       | 40              | 30                   | 150           | 500             | NOW          | 4-52        |

| IDT7213     | 12 × 12-with single clock architecture                                                         | 40              | 30                   | 150           | 500             | NOW          | 4-52        |

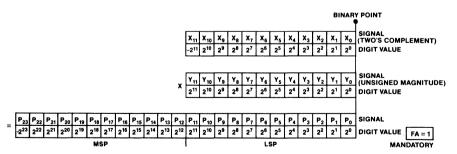

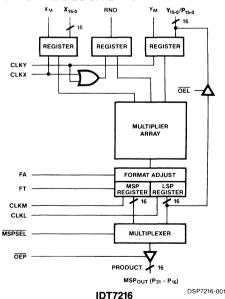

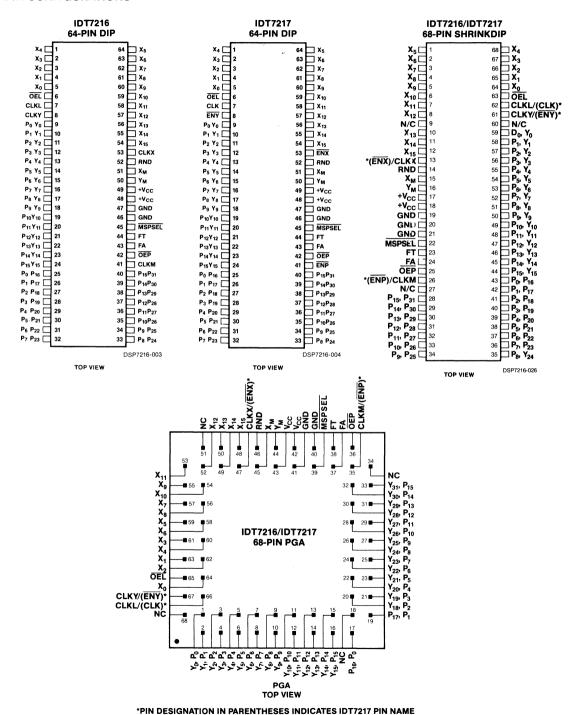

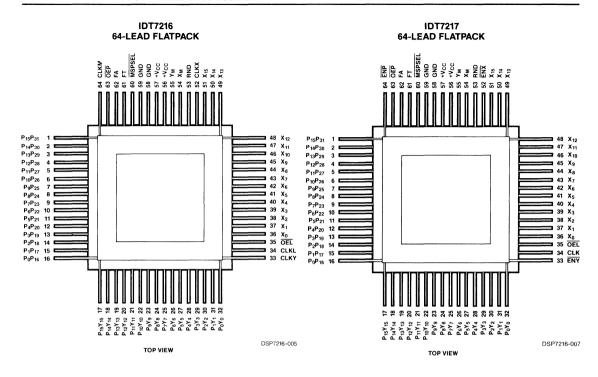

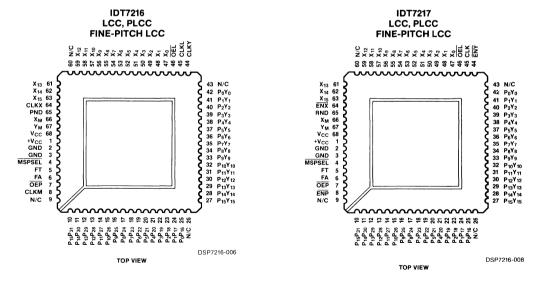

| IDT7216     | 16 x 16-pin and functionally<br>compatible with TRW MPY016H/K<br>and AMD Am29516               | 40              | 35                   | 150           | 500             | NOW          | 4-61        |

| IDT7217     | 16 x 16-with single clock<br>architecture; pin and functionally<br>compatible with AMD Am29517 | 40              | 35                   | 150           | 500             | NOW          | 4-61        |

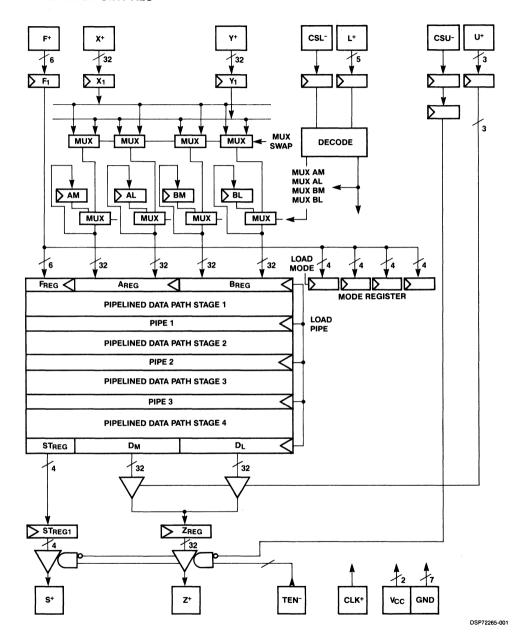

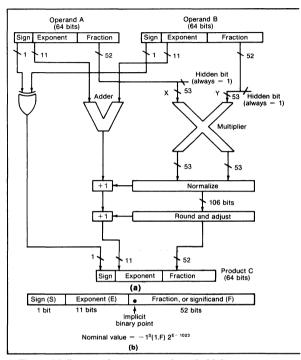

### **High-Speed CMOS Floating Point Products**

- Advanced CEMOS technology

- Full IEEE standard 754 conformance

- Single 5V supply

- Full 32-bit and 64-bit multiply and ALU operations

- 144-Pin Grid Array

- Low-power 750mW per device

| Part Number | Description                                                           | Max. Speed (ns)                                                            | Power (typical)<br>Oper. (mW) | Availability | Page<br>No. |

|-------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------|--------------|-------------|

| IDT72064    | 64-Bit Multiplier-pin and functionally compatible with Weitek WTL1064 | Single precision<br>5 MFLOPS (200)<br>Double precision<br>2.5 MFLOPS (400) | 750                           | Q4 '86       | 4-31        |

| IDT72065    | 64-Bit ALU-pin and functionally compatible with Weitek WTL1065        | Single precision<br>10 MFLOPS (100)<br>Double precision<br>10 MFLOPS (100) | 750                           | Q4 '86       | 4-31        |

| IDT72264    | 64-Bit Multiplier-pin and functionally compatible with Weitek WTL1264 | Single precision<br>10 MFLOPS (100)<br>Double precision<br>5 MFLOPS (200)  | 750                           | Q4 '86       | 4-71        |

| IDT72265    | 64-Bit ALU-pin and functionally compatible with Weitek WTL1265        | Single precision<br>10 MFLOPS (100)<br>Double precision<br>10 MFLOPS (100) | 750                           | Q4 '86       | 4-71        |

### **High-Speed CMOS Logic Products**

- FCTXXXA devices 35%-50% faster than FAST<sup>™</sup> with equivalent output drive but at dramatically lower CMOS power over full temperature and voltage supply extremes

- FCT devices same speed and output drive as FAST<sup>TM</sup>, but at dramatically lower CMOS power

- AHCT devices same speed and output drive as ALS, but at dramatically lower CMOS power

- 39C8XX devices same speed and output drive as 29800, but at dramatically lower CMOS power

- 54/74 FCT8XXB devices 32%-38% faster than 29800 with equivalent output drive, but at dramatically lower CMOS power

- Both CMOS and TTL output compatible (eliminates need for pull-up resistors when driving CMOS static RAMs)

- Substantially lower input current levels than FAST<sup>TM</sup> or ALS (5μA max.)

- JEDEC standard pinout for DIP and LCC

- · Pin-compatible with industry standard MSI logic

|                 |                                 | May S | peed (ns) | Power | (typical)<br>Standby |              | Page  |

|-----------------|---------------------------------|-------|-----------|-------|----------------------|--------------|-------|

| Part Number     | Description                     | Mil.  | Com'l.    | (mW)  | Standby<br>(μW)      | Availability | No.   |

| IDT54/74FCT138A | 1-of-8 Decoder                  | 7.8   | 5.8       | 10.0  | 5.0                  | NOW          | 5-98  |

| IDT54/74FCT139A | Dual 1-of-4 Decoder             | 7.8   | 5.9       | 10.0  | 5.0                  | NOW          | 5-102 |

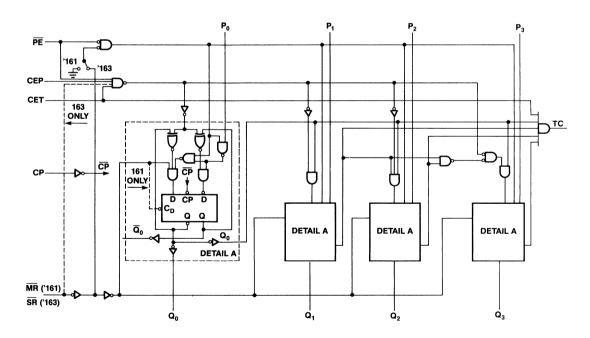

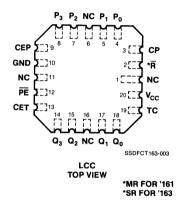

| IDT54/74FCT161A | Synchronous Binary Counter      | 7.5   | 7.2       | 10.0  | 5.0                  | Q4 '86       | 5-105 |

| IDT54/74FCT163A | Synchronous Binary Counter      | 7.5   | 7.2       | 10.0  | 5.0                  | Q4 '86       | 5-105 |

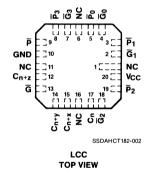

| IDT54/74FCT182A | Carry Lookahead Generator       |       |           | 10.0  | 5.0                  | Q4 '86       | 5-109 |

| IDT54/74FCT191A | Up/Down Binary Counter          | 10.5  | 7.8       | 10.0  | 5.0                  | Q4 '86       | 5-113 |

| IDT54/74FCT193A | Up/Down Binary Counter          | 6.9   | 6.5       | 10.0  | 5.0                  | Q4 '86       | 5-117 |

| IDT54/74FCT240A | Octal Buffer                    | 5.1   | 4.8       | 10.0  | 5.0                  | NOW          | 5-121 |

| IDT54/74FCT244A | Octal Buffer                    | 4.6   | 4.3       | 10.0  | 5.0                  | NOW          | 5-125 |

| IDT54/74FCT245A | Octal Bidirectional Transceiver | 4.9   | 4.6       | 10.0  | 5.0                  | NOW          | 5-129 |

| IDT54/74FCT273A | Octal D Flip-Flop               | 8.3   | 7.2       | 10.0  | 5.0                  | NOW          | 5-133 |

| IDT54/74FCT299A | Octal Universal Shift Register  | 9.5   | 7.2       | 10.0  | 5.0                  | NOW          | 5-137 |

| IDT54/74FCT373A | Octal Transparent Latch         | 5.6   | 5.2       | 10.0  | 5.0                  | NOW          | 5-141 |

| IDT54/74FCT374A | Octal D Flip-Flop               | 7.2   | 6.5       | 10.0  | 5.0                  | NOW          | 5-145 |

| IDT54/74FCT377A | Octal D Flip-Flop               | 8.3   | 7.2       | 10.0  | 5.0                  | NOW          | 5-149 |

| IDT54/74FCT521A | 8-Bit Comparator                | 9.5   | 7.2       | 10.0  | 5.0                  | NOW          | 5-153 |

| IDT54/74FCT533A | Octal Transparent Latch         | 5.6   | 5.2       | 10.0  | 5.0                  | NOW          | 5-156 |

| IDT54/74FCT534A | Octal D Flip-Flop               | 7.2   | 6.5       | 10.0  | 5.0                  | NOW          | 5-160 |

| IDT54/74FCT573A | Octal Transparent Latch         | 5.6   | 5.2       | 10.0  | 5.0                  | NOW          | 5-164 |

| IDT54/74FCT574A | Octal D Register                | 7.2   | 6.5       | 10.0  | 5.0                  | NOW          | 5-168 |

| IDT54/74FCT640A | Octal Bidirectional Transceiver | 5.3   | 5.0       | 10.0  | 5.0                  | NOW          | 5-172 |

| IDT54/74FCT645A | Octal Bidirectional Transceiver | 4.9   | 4.6       | 10.0  | 5.0                  | NOW          | 5-176 |

| IDT54/74FCT138  | 1-of-8 Decoder                  | 12.0  | 9.0       | 10.0  | 5.0                  | NOW          | 5-98  |

| IDT54/74FCT139  | Dual 1-of-4 Decoder             | 12.0  | 9.0       | 10.0  | 5.0                  | NOW          | 5-102 |

| IDT54/74FCT161  | Synchronous Binary Counter      | 11.5  | 11.0      | 10.0  | 5.0                  | Q4 '86       | 5-105 |

| IDT54/74FCT163  | Synchronous Binary Counter      | 11.5  | 11.0      | 10.0  | 5.0                  | Q4 '86       | 5-105 |

| IDT54/74FCT182  | Carry Lookahead Generator       | 11.5  | 9.0       | 10.0  | 5.0                  | NOW          | 5-109 |

| IDT54/74FCT191  | Up/Down Binary Counter          | 16.0  | 12.0      | 10.0  | 5.0                  | Q4 '86       | 5-113 |

| IDT54/74FCT193  | Up/Down Binary Counter          | 10.5  | 10.0      | 10.0  | 5.0                  | Q4 '86       | 5-117 |

| IDT54/74FCT240  | Octal Buffer                    | 9.0   | 8.0       | 10.0  | 5.0                  | NOW          | 5-121 |

| IDT54/74FCT244  | Octal Buffer                    | 7.0   | 6.5       | 10.0  | 5.0                  | NOW          | 5-125 |

| IDT54/74FCT245  | Octal Bidirectional Transceiver | 7.5   | 7.0       | 10.0  | 5.0                  | NOW          | 5-129 |

| IDT54/74FCT273  | Octal D Flip-Flop               | 15.0  | 13.0      | 10.0  | 5.0                  | NOW          | 5-133 |

| IDT54/74FCT299  | Octal Universal Shift Register  | 16.0  | 10.0      | 10.0  | 5.0                  | NOW          | 5-137 |

CONTINUED

# High-Speed CMOS Logic Products (continued)

|                 |                                 | Max S | peed (ns) | Power<br>Oper. | (typical)<br>Standby |              | Page  |

|-----------------|---------------------------------|-------|-----------|----------------|----------------------|--------------|-------|

| Part Number     | Description                     | Mil.  | Com'l.    | (mW)           | (μ <b>W</b> )        | Availability | No.   |

| IDT54/74FCT373  | Octal Transparent Latch         | 8.5   | 8.0       | 10.0           | 5.0                  | NOW          | 5-141 |

| IDT54/74FCT374  | Octal D Flip-Flop               | 11.0  | 10.0      | 10.0           | 5.0                  | NOW          | 5-145 |

| IDT54/74FCT377  | Octal D Flip-Flop               | 15.0  | 13.0      | 10.0           | 5.0                  | NOW          | 5-149 |

| IDT54/74FCT521  | 8-Bit Comparator                | 15.0  | 11.0      | 10.0           | 5.0                  | NOW          | 5-153 |