# The IBM27-82650 PowerPC to PCI Bridge User's Manual

PowerPC to PCI Bridge, Memory Controller, Arbiter, ROM Controller, and System Resource Manager

Introducing the 650 Bridge, with the 653 Buffer and 654 Controller, as a complete solution for interfacing PowerPC 60X microprocessors to the PCI local bus.

# The IBM27-82650 PowerPC to PCI Bridge User's Manual

PowerPC to PCI Bridge, Memory Controller, Arbiter, ROM Controller, and System Resource Manager

|  | , |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

© Copyright IBM Corporation, 1994. All rights reserved.

Note to US Government Users—Documentation related to restricted rights—Use, duplication, or disclosure is subject to restrictions set forth in GSA ADP Schedule Contract with IBM Corp.

IBM is a registered trademark, and IBM Microelectronics, PowerPC, PowerPC 601, PowerPC 603, PowerPC 604, PowerPC Architecture, and RiscWatch are trademarks of International Business Machines Corp. Intel is a registered trademark of Intel Corporation. Other company names and product identifiers are trademarks of the respective companies.

This document contains preliminary information about version 2.0 of the chip set and is subject to change by IBM without notice. IBM assumes no responsibility or liability for any use of the information contained herein. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. The products described in this document are not intended for use in implantation or other direct life support applications where malfunction may result in physical harm or injury to persons. NO WARRAN-TIES OF ANY KIND, INCLUDING BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, ARE OFFERED IN THIS DOCUMENT.

# The IBM27-82650 PowerPC to PCI Bridge User's Manual

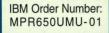

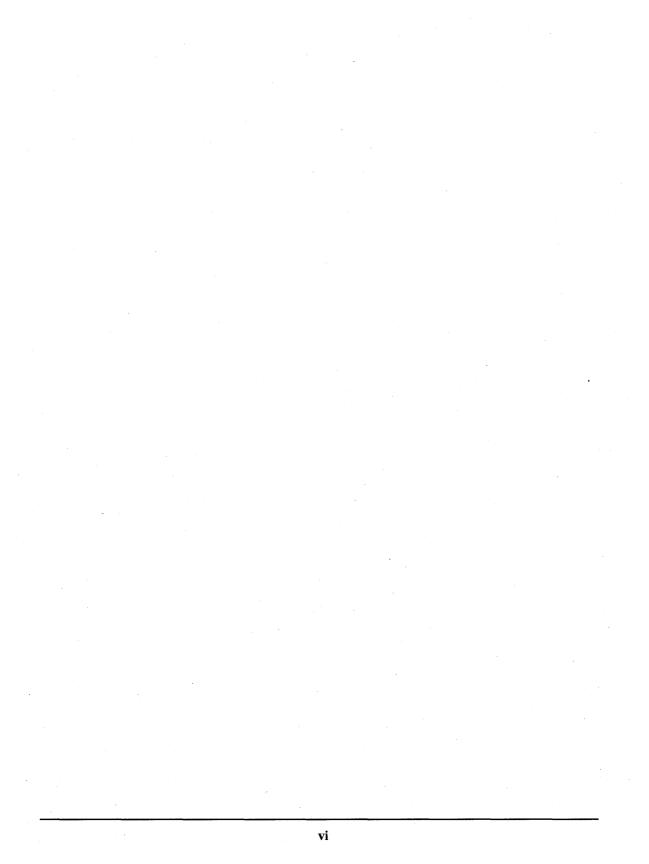

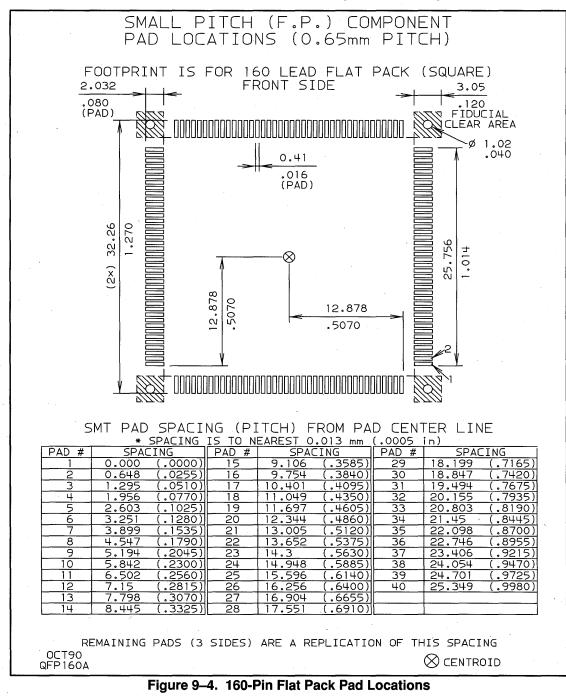

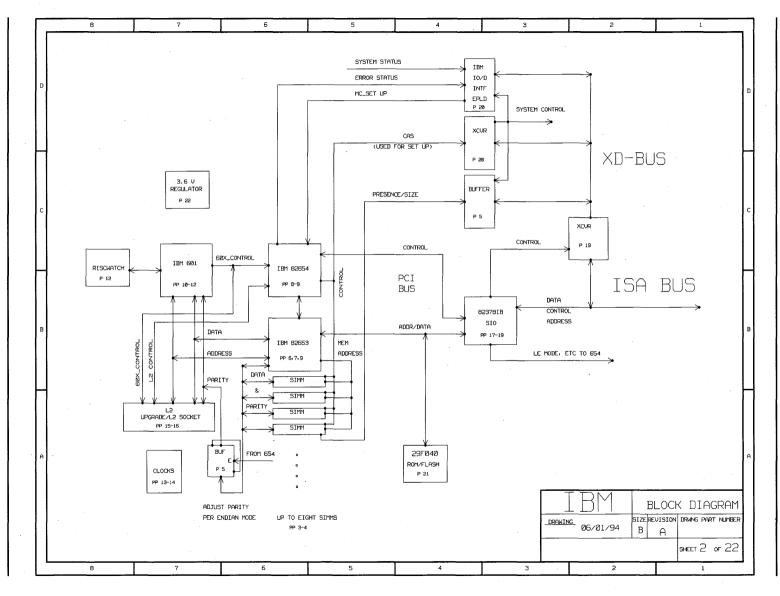

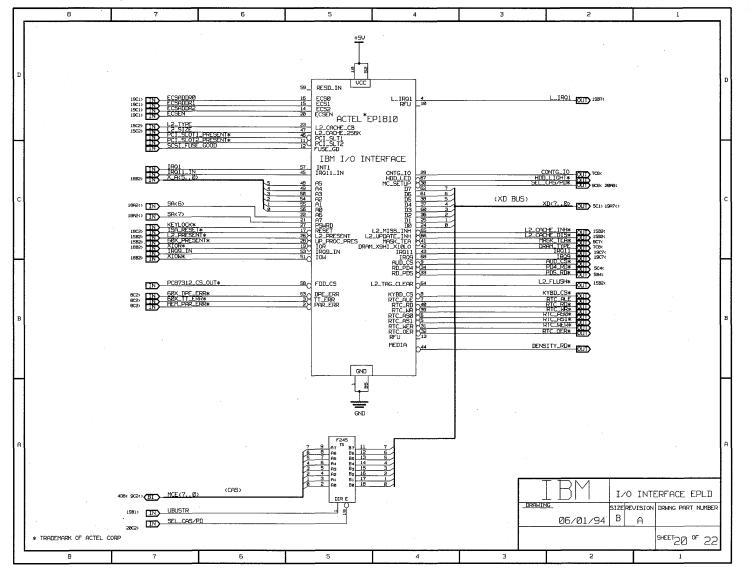

#### IBM 650 Bridge Chip Set in a Typical Configuration

iv

## The IBM27-82650 PCI Bridge Chip Set

#### PowerPC<sup>™</sup> to PCI Local Bus Bridge and Memory Controller

- Used in the PowerPC Reference

Platform Reference Implementation

- Supports the PowerPC 601, 603, and 604 (60X) Microprocessors

- Big- and Little-Endian Address Modes

- Up to 66MHz 60X CPU Bus Clock

- Interfaces the 60X CPU Host Bus to the PCI Local Bus (level 2.0)

- Up to 33MHz PCI Local Bus Clock Rate

- Enables Industry-Standard PCI Devices

- Integrated Arbiter, up to Six PCI Devices

- One Load on PCI Bus

- Support for Optional L2 Cache

- Write-Back and Write-Through Policy

- Snoops PCI to System Memory Addresses

- ISA Master to System Memory Support

- Direct Support for 8-Bit Flash/EPROM

- System Memory (DRAM) Controller

- 64-Bit Data Path for System Memory

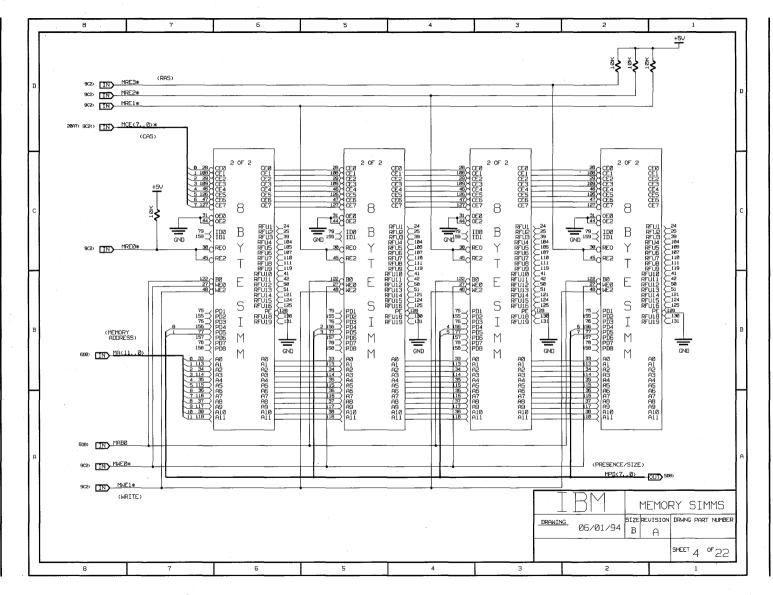

- Directly Supports 8M and 32M 8-Byte SIMMs

- Supports up to 256M of System Memory

- Memory Configuration Registers

- 70ns SIMMs Supported

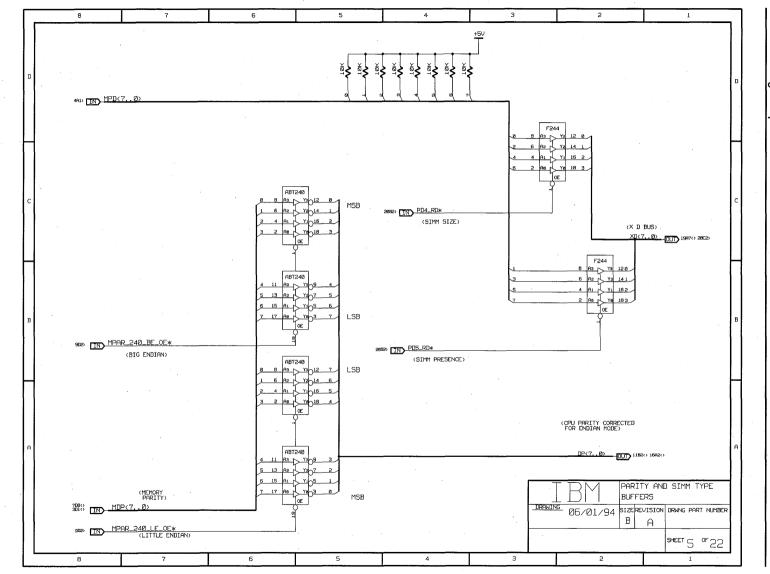

- System Memory Parity Generation and Checking

- Supports 60X CPU Burst Reads and Writes of System Memory

- PCI Burst Reads and Writes to System Memory

- Companion L2 Cache Controller Chip

- The IBM27-82681-66

- 44-Pin PLCC Package

- 256K or 512K Bytes

- 3.3V or 3.6V Power Supply

- 5V-Compatible I/O's

- 304-Pin and 160-Pin Quad Flatpacks

The IBM27-82650 PCI Bridge chip set (the 650 Bridge) provides an interface that can connect a PowerPC 60X CPU to high-performance, PCI (Peripheral Component Interconnect) devices like graphics, LAN, and SCSI controllers. The PCI bus standard defines an environment for high-speed, local bus operations. The 650 Bridge chip set provides the necessary control and communications logic to connect a PowerPC 60X CPU to PCI-compliant devices through the PCI bus.

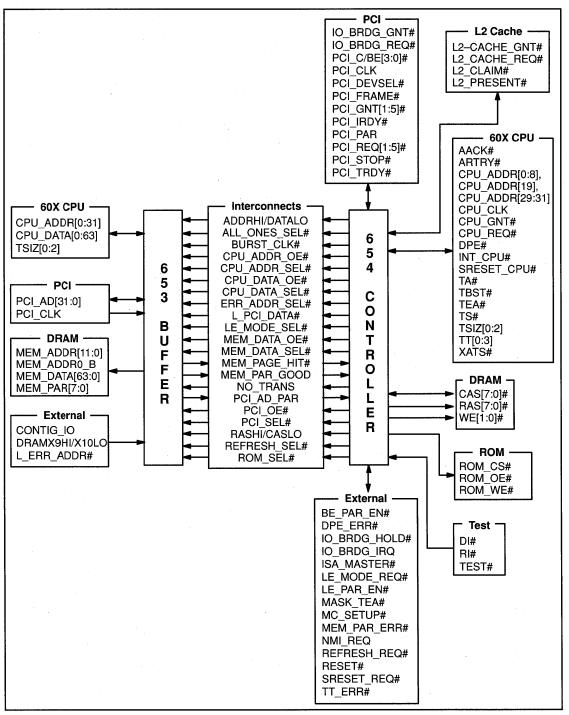

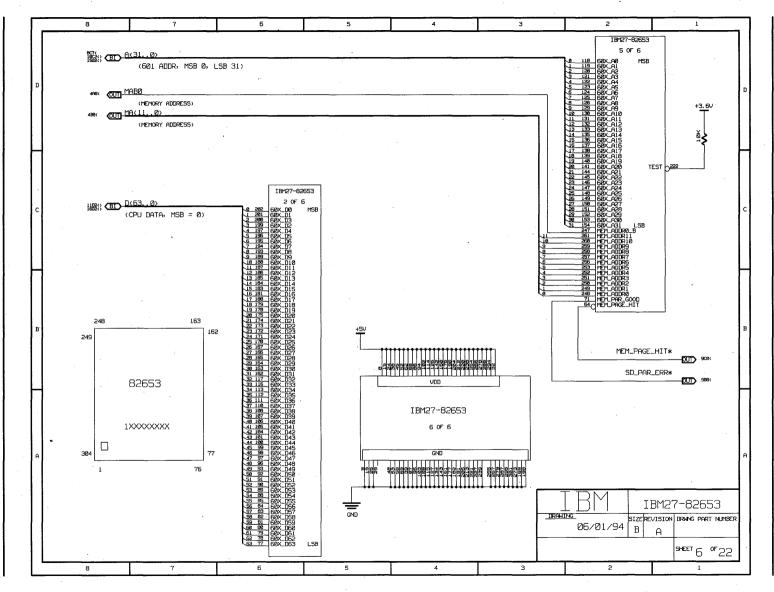

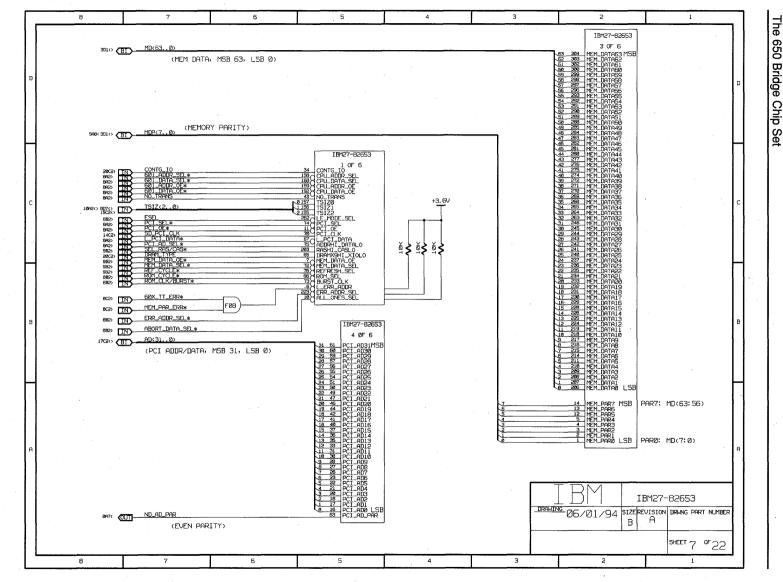

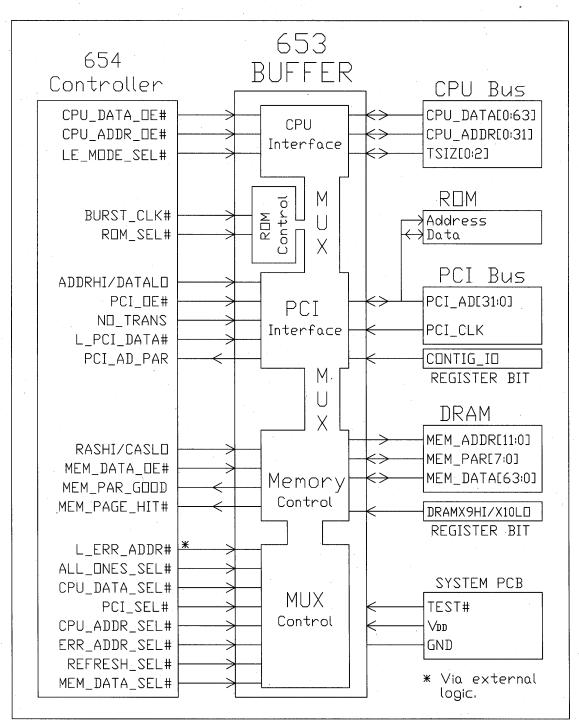

The 650 Bridge chip set is comprised of the IBM27-82653 Address/Data Buffer (the 653 Buffer) and the IBM27-82654 PCI/Memory controller (the 654 Controller). The 650 Bridge supports the PowerPC 601, 603, and 604 microprocessor chips. The 650 Bridge supports both the L1 memory cache of the 60X CPU and an optional L2 cache. Either cache can use write-through or write-back modes of operation.

The 650 Bridge performs the following distinct functions:

- PCI and 60X CPU Bus Arbitration Logic

- System Memory (DRAM) Controller—up to 256M

- Memory-Mapping of CPU Addresses to PCI Transactions

- 60X CPU to 32-bit PCI Local Bus Bridge

- Supports the PowerPC Memory Coherence Model

- System ROM Controller (Including Flash ROM Writes)

- Parity Error and System Error Detection and Reporting

# **Table of Contents**

| About T | his Book                                  |     |

|---------|-------------------------------------------|-----|

|         |                                           | xii |

|         | <b>9</b>                                  | xii |

|         |                                           | xii |

|         | Document Conventions xx                   |     |

|         | Acronyms and Abbreviations xx             | iii |

| Section | 1                                         |     |

|         | ge Architectural Overview                 | 1   |

| 1.1     | Summary of 650 Bridge Features            | 2   |

| 1.1.1   | 60X Microprocessor Support                | 2   |

| 1.1.2   | Central Arbiter                           | 2   |

| 1.1.3   | Memory Controller                         | 2   |

| 1.1.4   | PowerPC Local Bus                         | 3   |

| 1.1.5   | PCI Expansion Bus                         | 3   |

| 1.1.6   | Address Translation Logic                 | 4   |

| 1.1.7   | L2 Cache Support                          | 4   |

| 1.1.8   | System ROM Controller                     | 4   |

| 1.1.9   | Interrupt and Exception Logic             | 4   |

| Section | 2                                         |     |

| The PCI | Eus and 60X CPU Background Review         | 5   |

| 2.1     | The PCI Local Bus Review                  | 5   |

| 2.1.1   | PCI Local Bus References                  | 5   |

| 2.1.2   | PCI Local Bus Overview                    | 5   |

| 2.1.3   | PCI Signals                               | 6   |

| 2.1.4   | PCI Masters and Targets                   | 7   |

| 2.1.5   | PCI Arbitration                           | 7   |

| 2.1.6   | Basic Transfer Control                    | 7   |

| 2.1.7   | PCI Bus Commands                          | 8   |

| 2.1.8   | Termination of PCI Cycles                 | 8   |

| 2.2     | PowerPC 60X CPU Review                    | 8   |

| 2.2.1   | 601 CPU References                        | 9   |

| 2.2.2   | PowerPC 60X CPU Overview                  | 9   |

| 2.2.3   | CPU to 650 Bridge Signals                 | 9   |

| 2.2.4   | Cache (L1)                                | 11  |

| 2.2.5   |                                           | 11  |

| 2.2.6   | ······································    | 11  |

| 2.2.7   | 1 J F                                     | 2   |

| 2.2.8   |                                           | 2   |

| 2.2.9   | PIO or I/O Controller Operation (XATS#) 1 | 3   |

#### Section 3

| 650 Brid | dge Pin Descriptions                                          | 15 |

|----------|---------------------------------------------------------------|----|

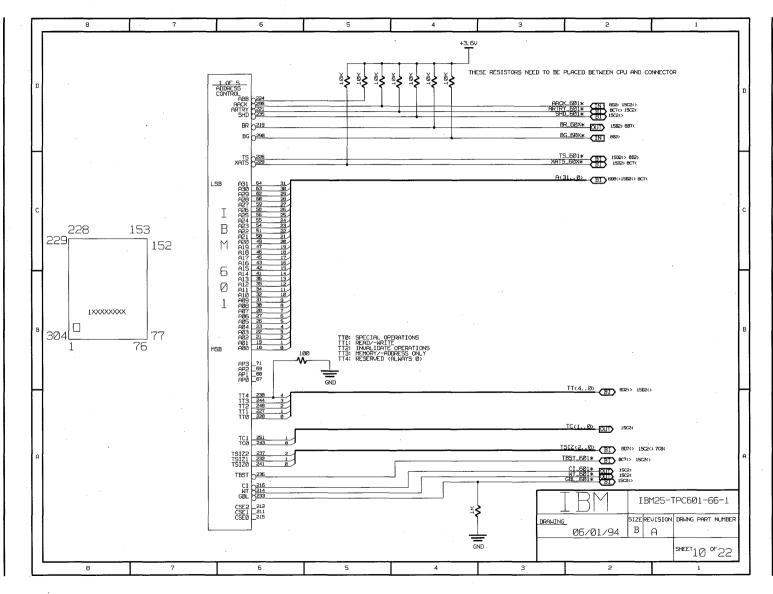

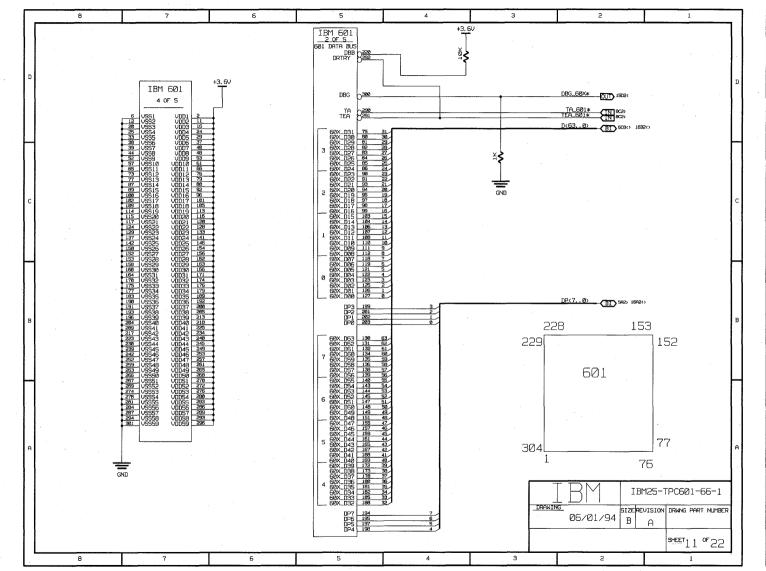

| 3.1      | 653 Buffer Pin Descriptions                                   | 15 |

| 3.1.1    | 653 Buffer to 60X CPU Bus Interface Signals                   | 17 |

| 3.1.2    | 653 Buffer to PCI Bus Interface Signals                       | 17 |

| 3.1.3    | 653 Buffer to System Memory Interface Signals                 | 17 |

| 3.1.4    | 653 Buffer to External Logic and System Interface Signals     | 18 |

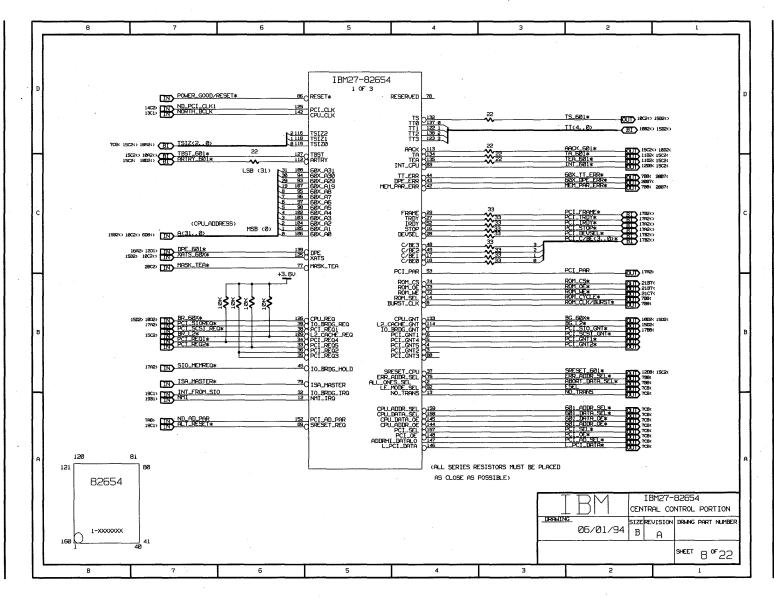

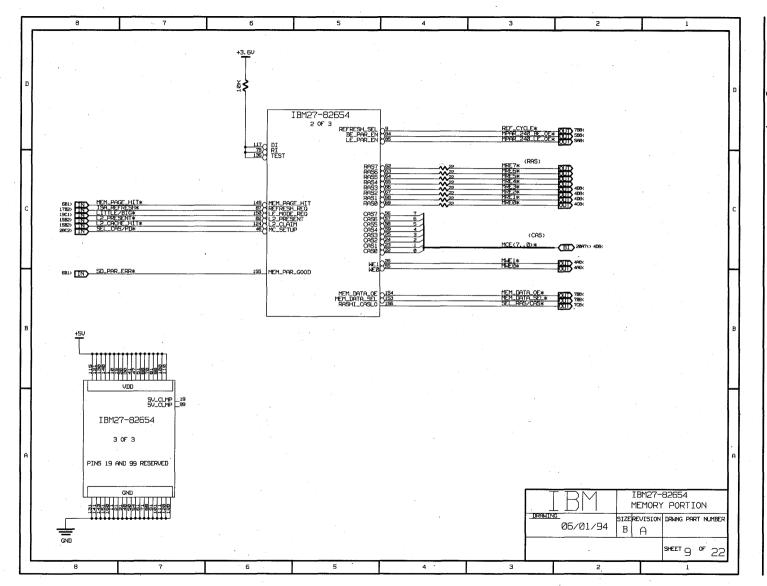

| 3.2      | 654 Controller Pin Descriptions                               | 18 |

| 3.2.1    | 654 Controller to 60X CPU Bus Interface Signals               | 19 |

| 3.2.2    | 654 Controller to PCI Bus Interface Signals                   | 21 |

| 3.2.3    | 654 Controller to System Memory (DRAM) Interface Signals      | 22 |

| 3.2.4    | 654 Controller to ROM (Flash or EPROM) Signals                | 22 |

| 3.2.5    | 654 Controller to L2 Cache Signals                            | 23 |

| 3.2.6    | 654 Controller to Test Signals                                | 23 |

| 3.2.7    | 654 Controller to External Logic and System Interface Signals | 23 |

| 3.3      | Signals Between the 653 Buffer and 654 Controller             | 25 |

|          |                                                               |    |

### Section 4

| 650 Bri | idge Theory of Operation                             | 29   |

|---------|------------------------------------------------------|------|

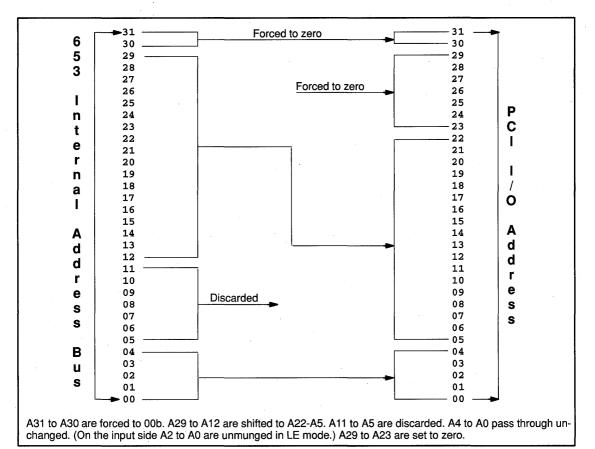

| 4.1     | 650 Bridge Mapping of 60X CPU Bus Addresses          | 29   |

| 4.1.1   | Address Mapping for Non-Contiguous I/O               | 29   |

| 4.1.2   | Address Mapping for Contiguous I/O                   | . 30 |

| 4.1.3   | PCI Final Address Formation                          | 31   |

| 4.2     | 650 Bridge Mapping of PCI Device Addresses           | 31   |

| 4.3     | 650 Bridge Bus Transactions                          | 32   |

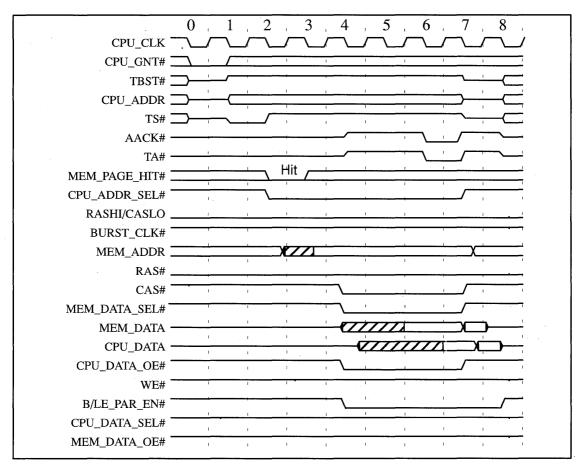

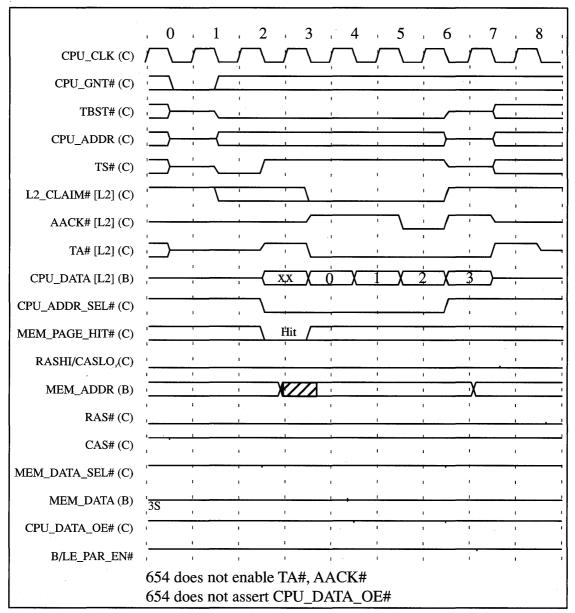

| 4.3.1   | CPU to Memory Read—Single-Beat, Page Hit, XCAS = 0   | 32   |

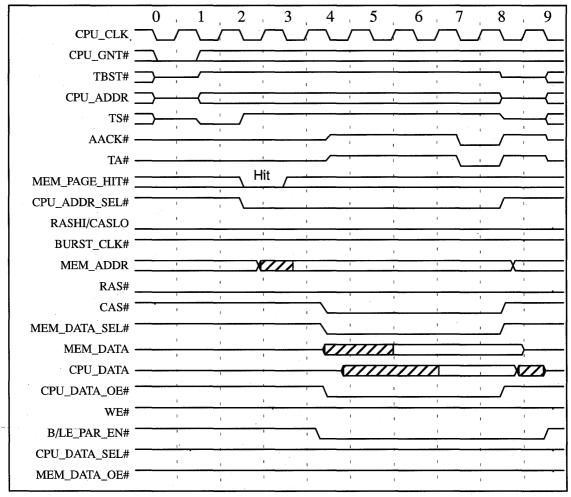

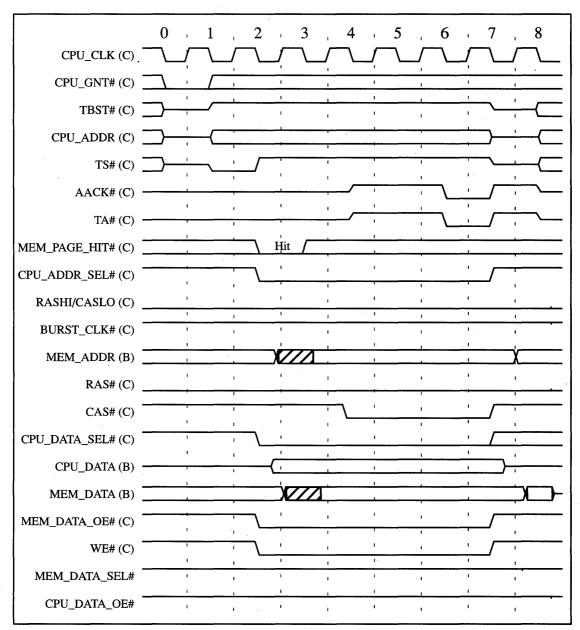

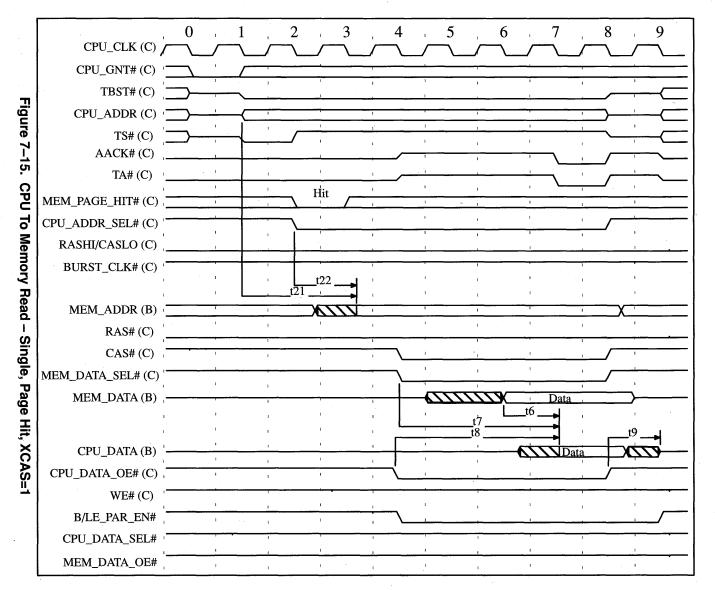

| 4.3.2   | CPU to Memory Read—Single-Beat, Page Hit, XCAS = 1   | 34   |

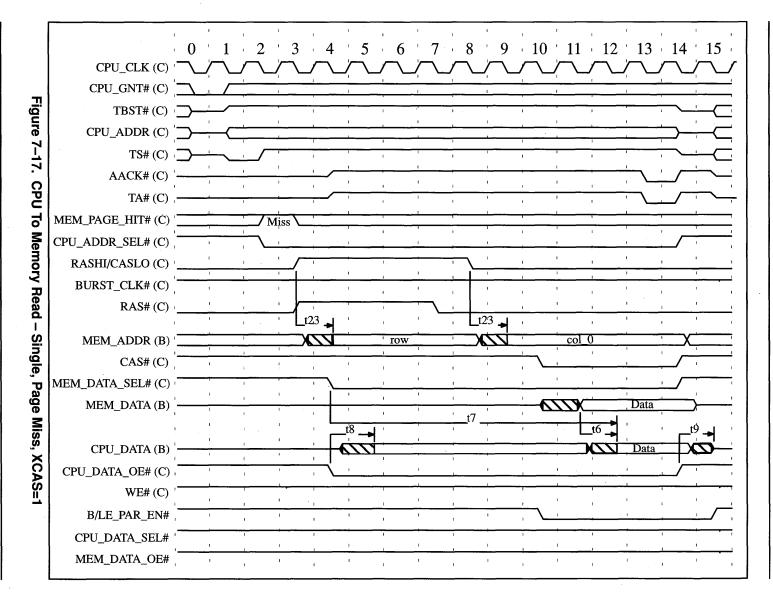

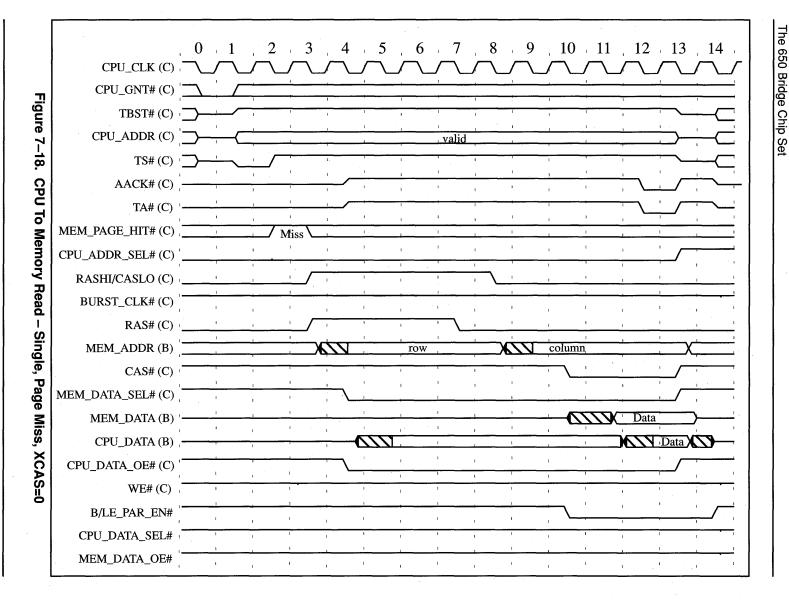

| 4.3.3   | CPU to Memory Read—Single-Beat, Page Miss, XCAS = 1  | 35   |

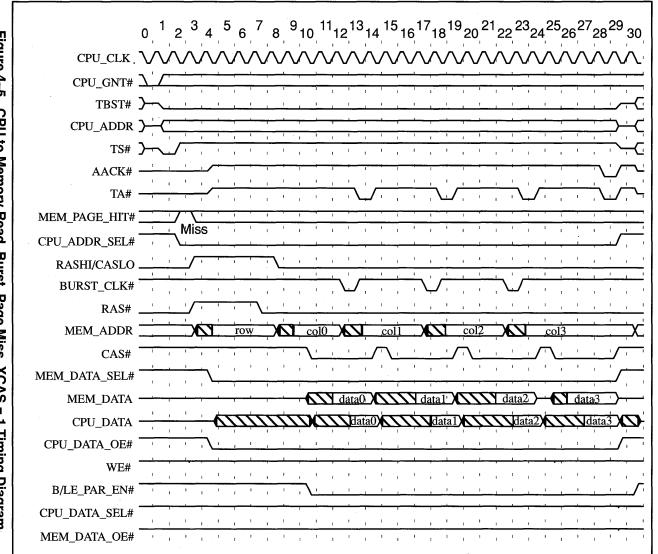

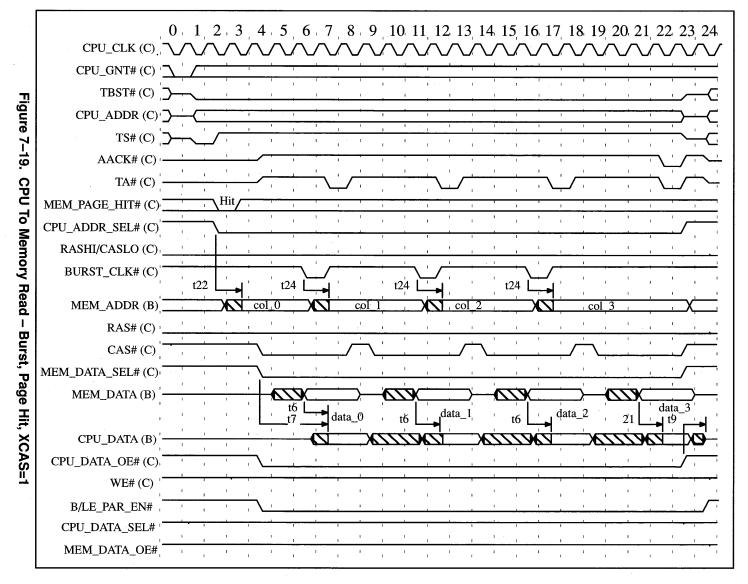

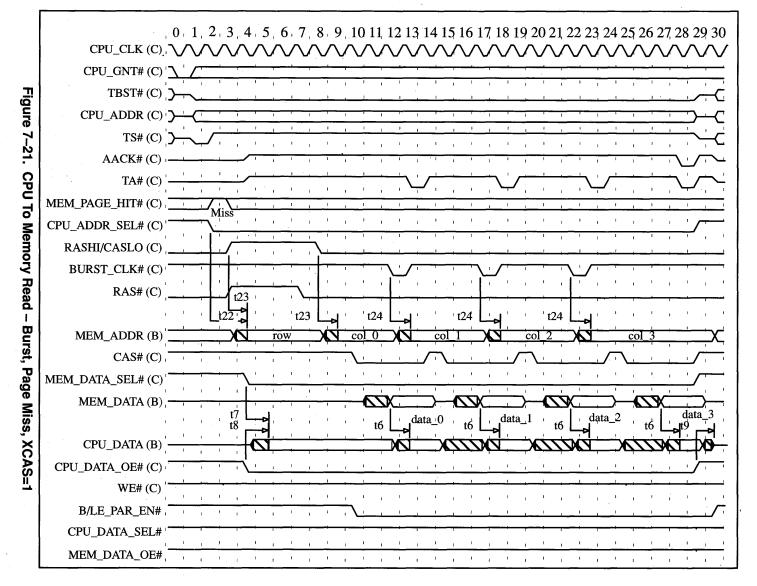

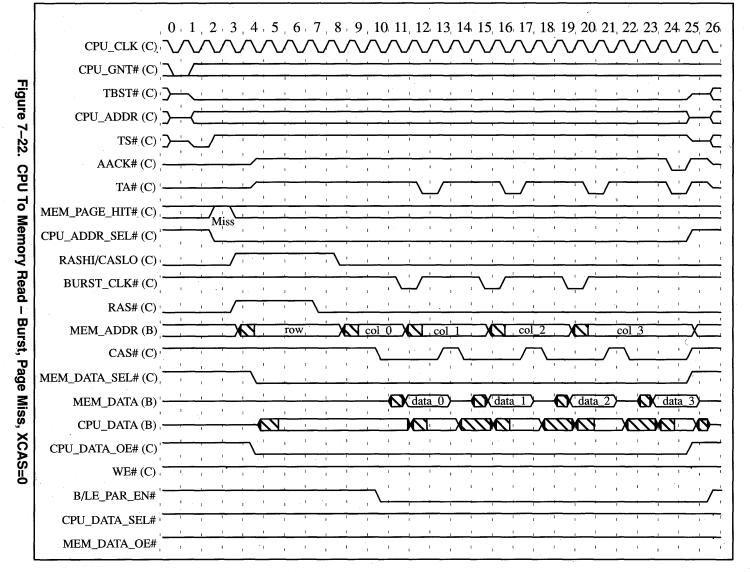

| 4.3.4   | CPU to Memory Read—Burst, Page Miss, XCAS = 1        | 36   |

| 4.3.5   | CPU to Memory Write—Single-Beat, Page Hit, XCAS = 0  | 38   |

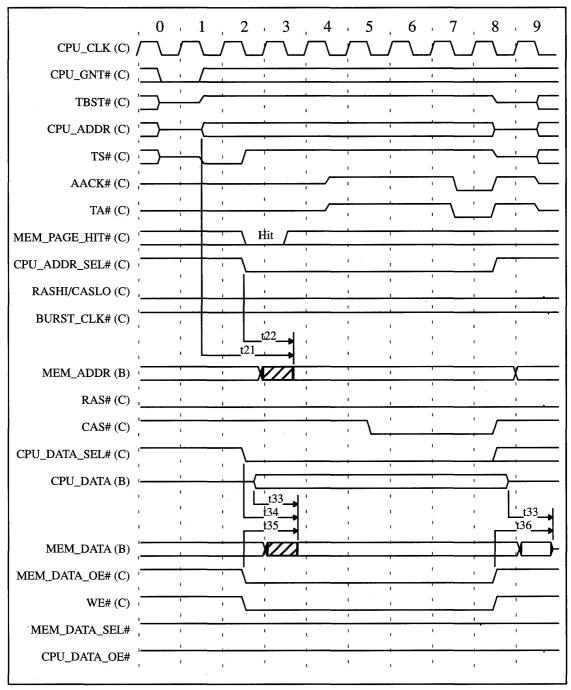

| 4.3.6   | CPU to Memory Write—Single-Beat, Page Hit, XCAS = 1  | 40   |

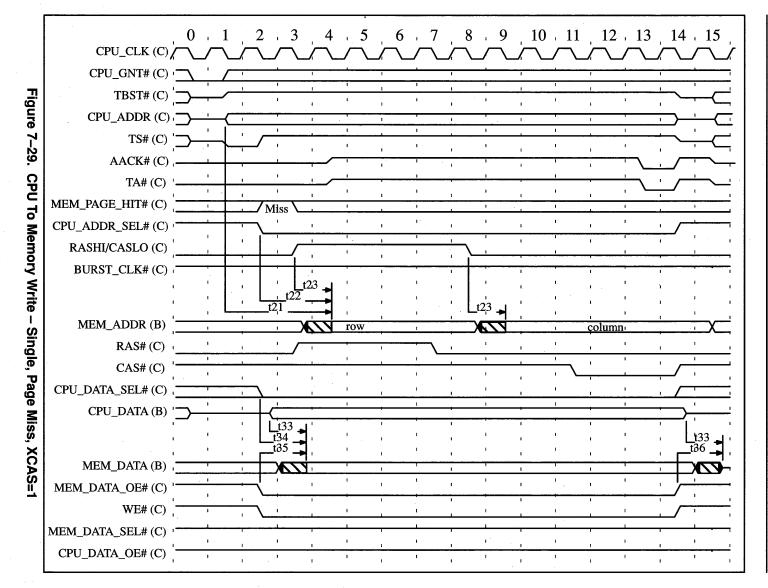

| 4.3.7   | CPU to Memory Write—Single-Beat, Page Miss, XCAS = 1 | 41   |

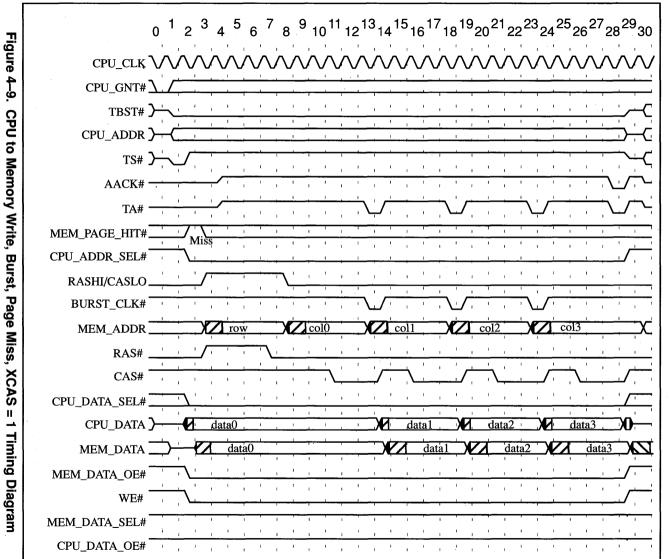

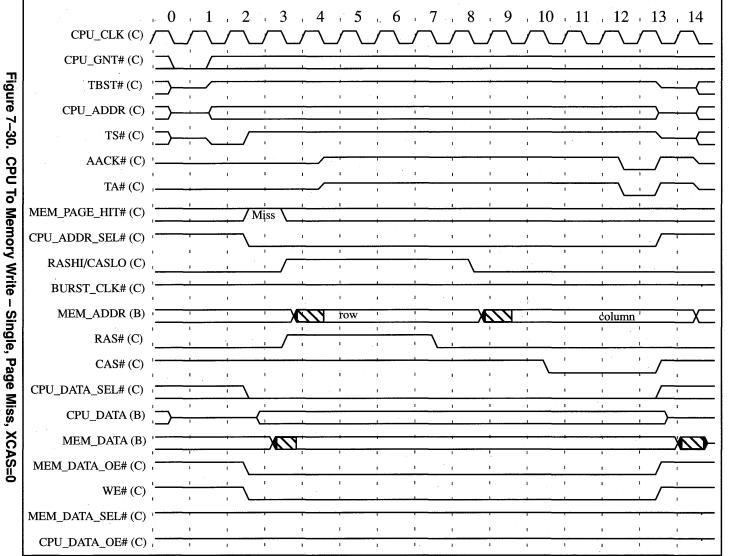

| 4.3.8   | CPU to Memory Write—Burst, Page Miss, XCAS = 1       | 42   |

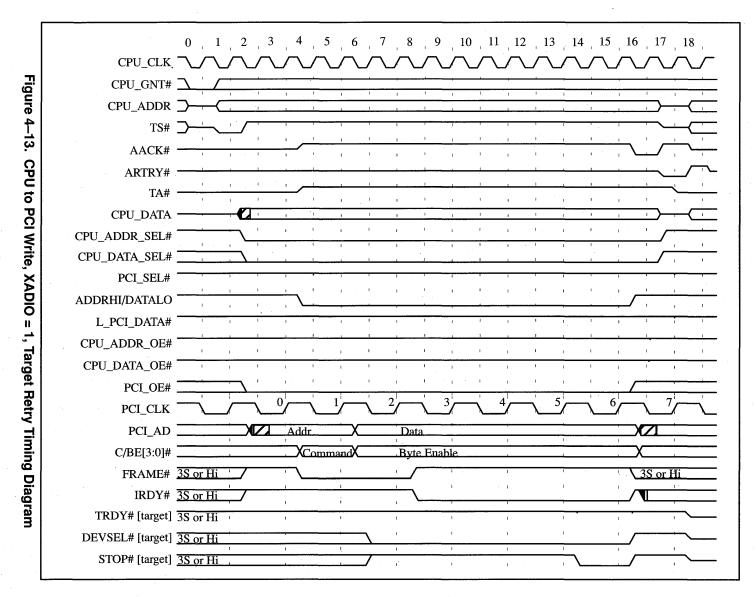

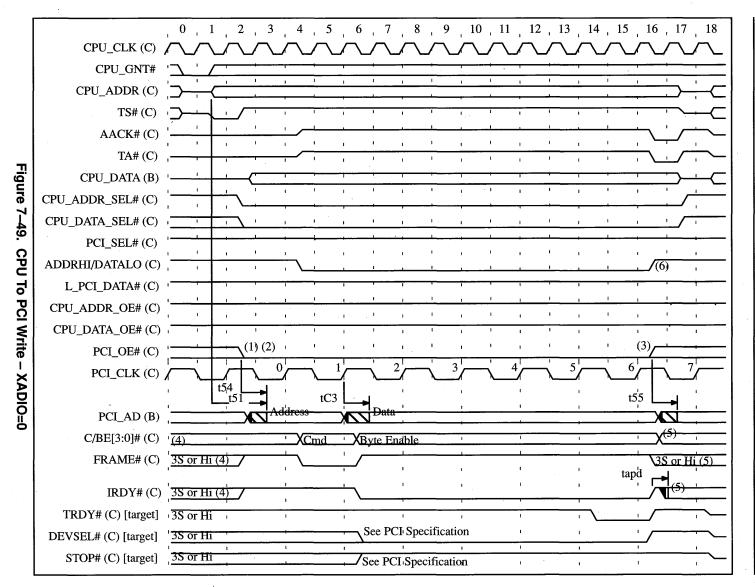

| 4.3.9   | CPU to PCI Write—XADIO = 1                           | 44   |

| 4.3.10  | CPU to PCI Write Additional Timing Examples          | 46   |

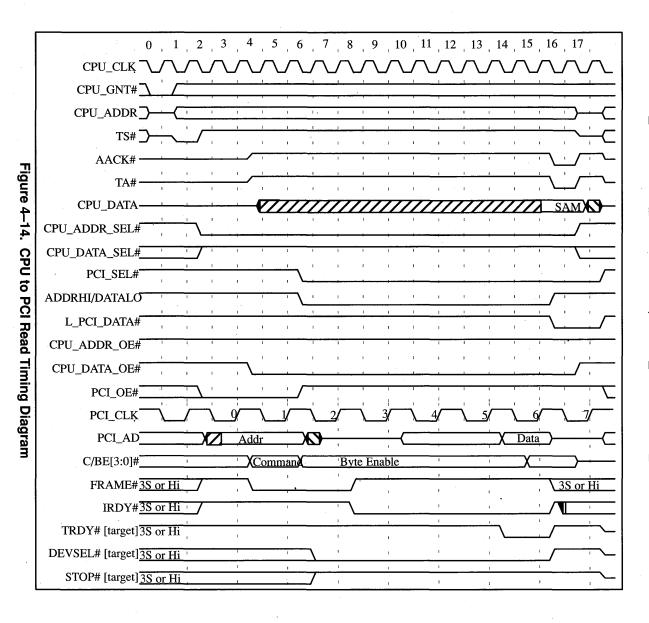

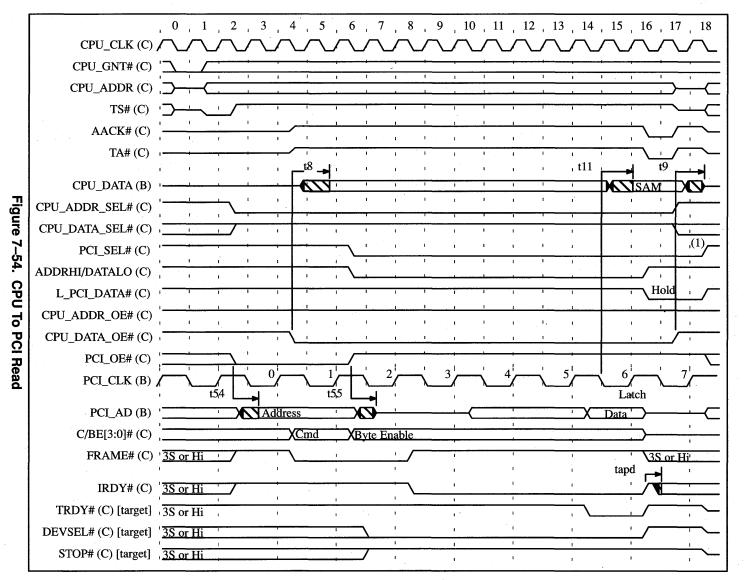

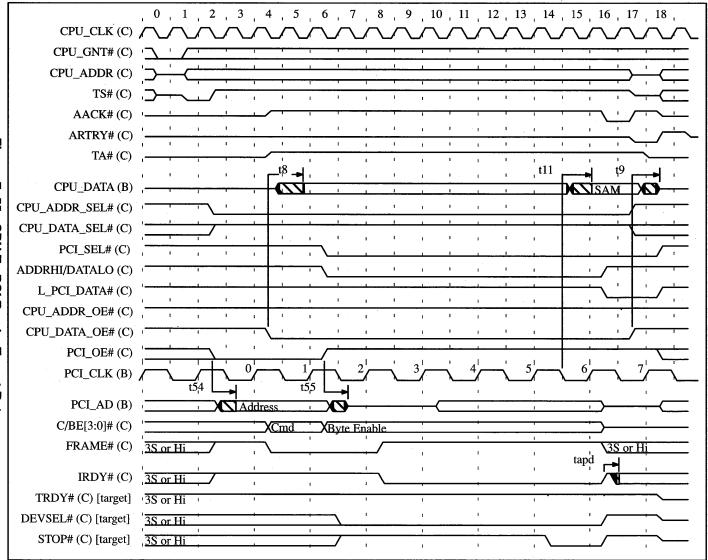

| 4.3.11  | CPU to PCI Read                                      | 49   |

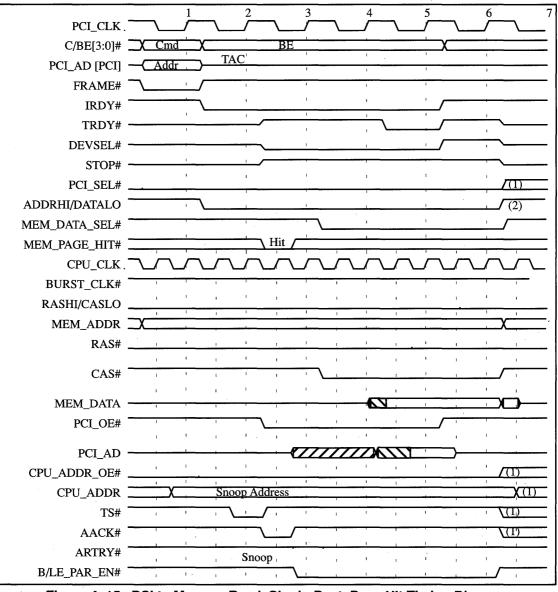

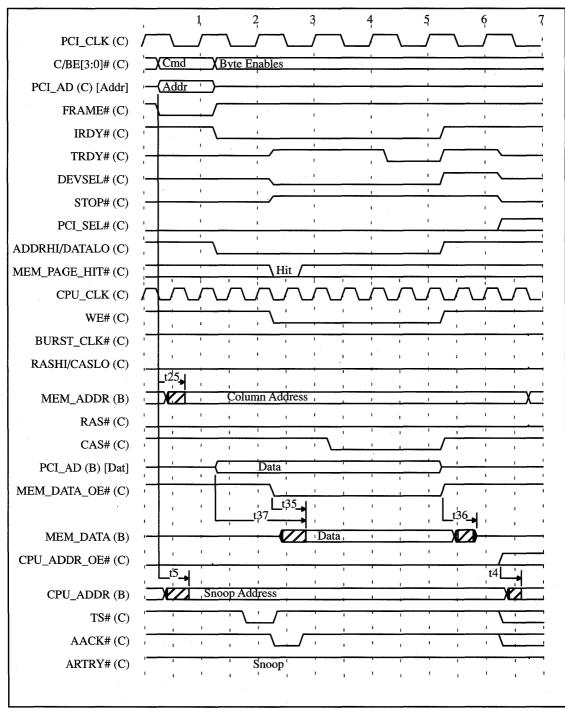

| 4.3.12  | PCI to Memory Read—Single-Beat, Page Hit             | 50   |

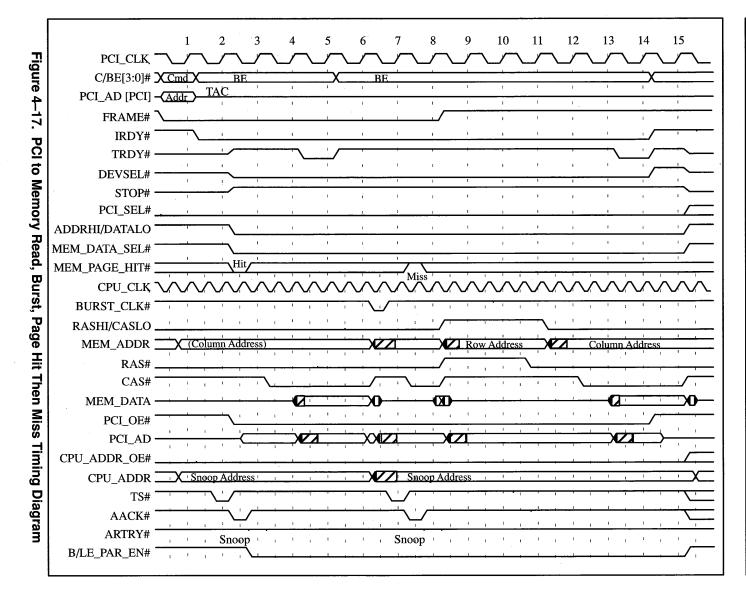

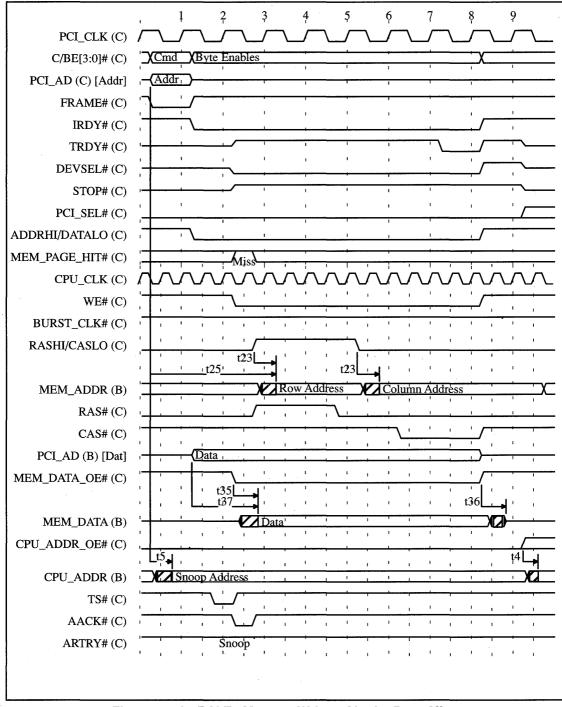

| 4.3.13  | PCI to Memory Read—Burst, Page Hit Then Miss         | 52   |

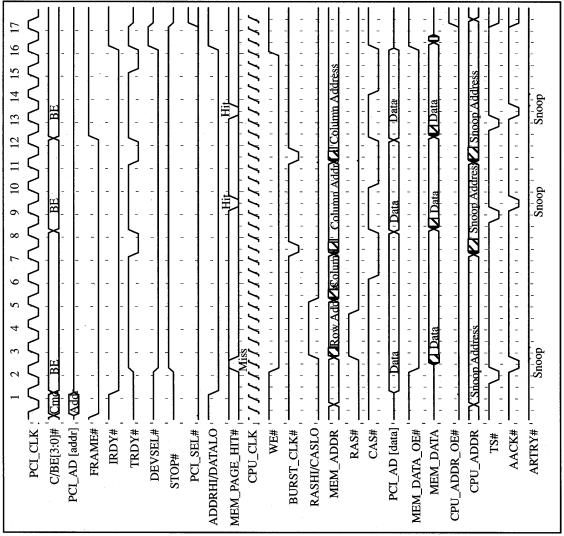

| 4.3.14  | PCI to Memory Write—Burst, Page Miss Then Hit        | 54   |

| Section<br>The 650 | 5 Bridge Functional Description                               | 55  |

|--------------------|---------------------------------------------------------------|-----|

| 5.1                | The 650 Bridge Arbiter                                        | 55  |

| 5.1.1              | Arbitration Description                                       | 56  |

| 5.1.2              | The Arbitration Fairness Mechanism                            | 56  |

| 5.1.3              | The Timeout Counter                                           | 56  |

| 5.1.4              | Support for System Memory (DRAM) Refresh                      | 56  |

| 5.1.5              | Support for Cache Snooping                                    | 56  |

| 5.1.6              | Bus Parking                                                   | 57  |

| 5.2                | 650 Bridge Programmability                                    | 57  |

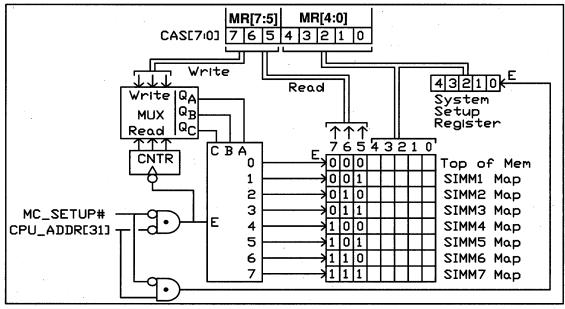

| 5.2.1              | Programming the 650 Bridge Memory Controller                  | 57  |

| 5.2.1.1            | Memory Controller Configuration                               | 57  |

| 5.2.1.2            | SIMM Mapping Registers                                        | 57  |

| 5.2.1.3            | SIMM Starting Address Registers                               | 58  |

| 5.2.1.4            | SIMM Starting Address Rules                                   | 59  |

| 5.2.1.5            | SIMM Top-of-Memory Logic                                      | 59  |

| 5.2.1.6            | SIMM Register Programming Rules                               | 59  |

| 5.2.1.7            | Reading the SIMM Registers                                    | 60  |

| 5.2.1.8            | SIMM Starting Address Example #1                              | 60  |

| 5.2.1.9            | SIMM Starting Address Example #2                              | 60  |

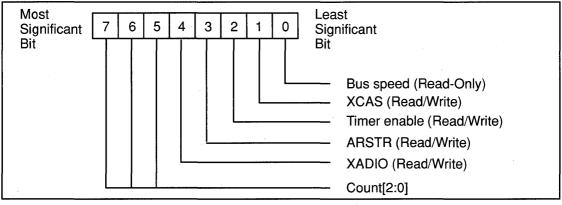

| 5.2.2              | Programming The System Setup Register                         | 61  |

| 5.2.2.1            | The Bus Speed Setting in the System Setup register            | 61  |

| 5.2.2.2            | The XCAS (Extended CAS#) Setting in the System Setup register | 61  |

| 5.2.2.3            | The Timer Enable Setting in the System Setup register         | 61  |

| 5.2.2.4            | The ARSTR Setting in the System Setup register                | 62  |

| 5.2.2.5            | The XADIO Setting in the System Setup register                | 62  |

| 5.2.2.6            | The Count[2:0] Counter in the System Setup register           | 62  |

| 5.2.2.7            | Bus Speed and XCAS Settings in the System Setup register      | 62  |

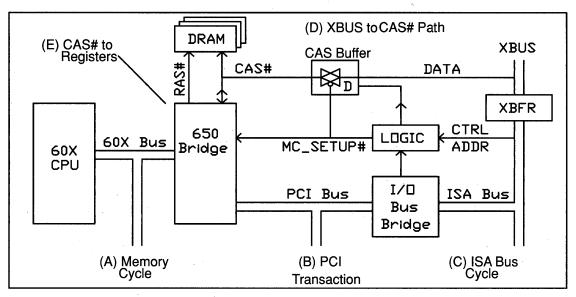

| 5.2.3              | Accessing the SIMM Registers and the System Setup Register    | 62  |

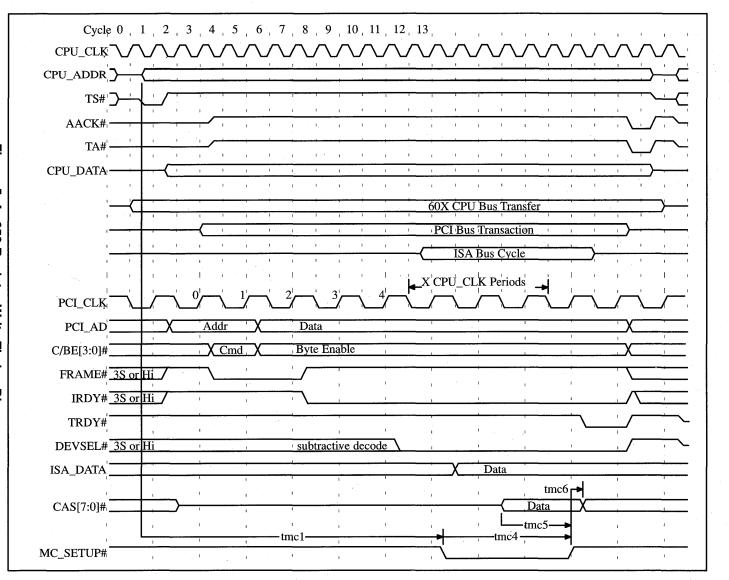

| 5.2.3.1            | SIMM Register and Setup Register Writes                       | 65  |

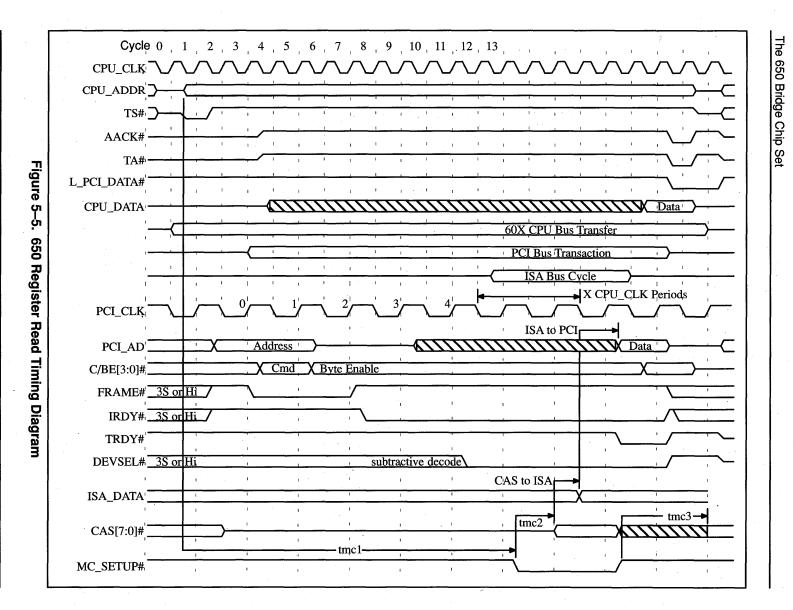

| 5.2.3.2            | SIMM Register and Setup Register Reads                        | 67  |

| 5.2.3.3            | Register Reads in the Example System                          | 68  |

| 5.2.3.4            | Register Writes in the Example System                         | 68  |

| 5.2.4              | Programming the Flash ROM Lock-Out Bit (W/O)                  | 68  |

| 5.3                | Little-Endian and Big-Endian Addressing Considerations        | 68  |

| 5.3.1              | 60X CPU Addressing in Big-Endian Mode                         | 68  |

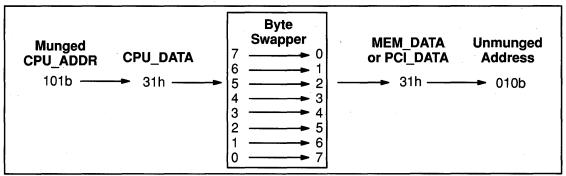

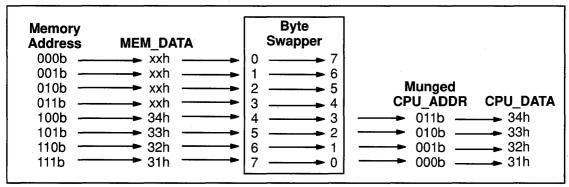

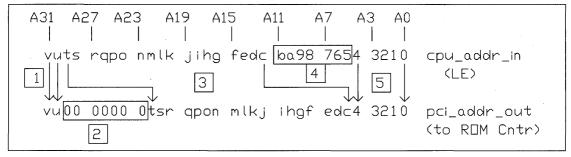

| 5.3.2              | 60X CPU Address Munging in Little-Endian Mode                 | 68  |

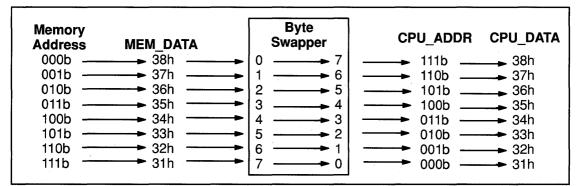

| 5.3.3              | 650 Bridge Address Unmunging in Little-Endian Mode            | 69  |

| 5.3.4              | Byte Swapping for Endian Compatibility                        | .70 |

| 5.3.5              | Unmunging and Byte Swapping for System Memory or PCI Writes   | 70  |

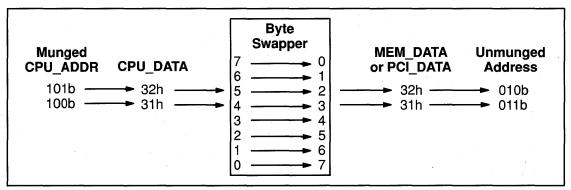

| 5.3.5.1            | An Example of a One-Byte Little-Endian Store Instruction      | 71  |

| 5.3.5.2            | An Example of a Two-Byte Little-Endian Store Instruction      | 71  |

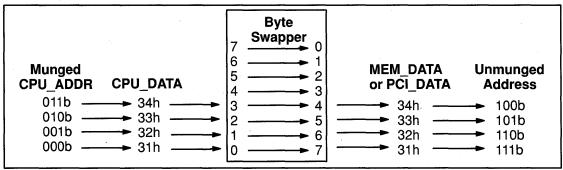

| 5.3.5.3            | An Example of a Four-Byte Little-Endian Store Instruction     | 72  |

|                    |                                                               |     |

.

| 5.3.5.4 | An Example of an Eight-Byte Little-Endian Store Instruction  | 73       |

|---------|--------------------------------------------------------------|----------|

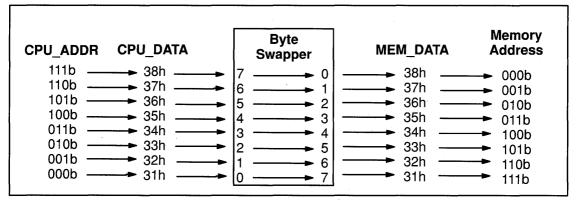

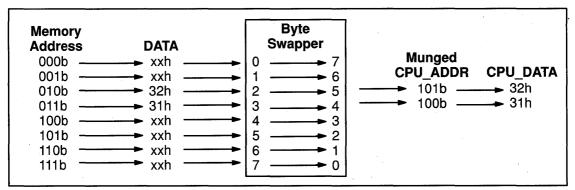

| 5.3.6   | Unmunging and Byte Swapping for System Memory and PCI Reads  | 73       |

| 5.3.6.1 | An Example of a Two-Byte Little-Endian Load Instruction      | 74       |

| 5.3.6.2 | An Example of a Four-Byte Little-Endian Load Instruction     | 74       |

| 5.3.6.3 | An Example of an Eight-Byte Little-Endian Load Instruction   | 75       |

| 5.3.7   | Instruction Fetches in Little-Endian Mode                    | 75       |

| 5.3.8   | LE_MODE_REQ# Assertion on the 654 Controller                 | 76       |

| 5.3.9   | Exceptions in Little-Endian Mode                             | 76       |

| 5.4     | Memory Controller Operation                                  | 76       |

| 5.4.1   | System Memory Timing                                         | 76       |

| 5.4.2   | 60X CPU to System Memory Burst-Mode Counting                 | 77       |

| 5.4.3   | PCI to System Memory Burst Mode Transfers                    | 77       |

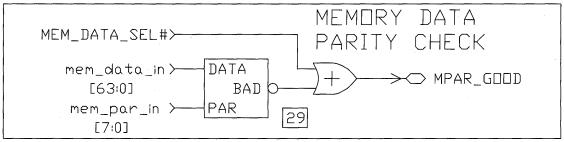

| 5.4.4   | System Memory Parity Generation and Checking                 | 78       |

| 5.4.5   | RAS# and CAS# Address Assignments                            | 78       |

| 5.4.6   | RAS[7:0]# Line Selection of SIMM Slots                       | 78       |

| 5.4.7   | RAS Timeout Counter                                          | 78       |

| 5.4.8   | 60X CPU to System Memory CAS[7:0]# Generation                | 79       |

| 5.4.9   | PCI to System Memory CAS[7:0]# Generation                    | 81       |

| 5.4.9.1 | PCI Read from System Memory                                  | 81       |

| 5.4.9.2 | PCI Write to System Memory                                   | 81       |

| 5.4.10  | System Memory Control Signals—BE_PAR_EN# and LE_PAR_EN#      | 82       |

| 5.5     | The 60X CPU Bus Cycles                                       | 82       |

| 5.5.1   | Data Transfers on the 60X CPU Bus                            | 82       |

| 5.5.1.1 | Transfer Start (TS#) and Transfer Acknowledge (TA# and TEA#) | 82       |

| 5.5.1.2 | 60X CPU Transfer Types—TT[0:3]                               | 83       |

| 5.5.1.3 | CPU Address-Only Access                                      | 84       |

| 5.5.1.4 | ECIWX and ECOWX                                              | 84       |

| 5.5.1.5 | CPU Address Alignments                                       | 84       |

| 5.5.2   |                                                              | 84       |

| 5.5.2.1 | 60X CPU to System Memory (DRAM) Cycles                       | 84<br>84 |

| 5.5.2.1 | 60X CPU to System Memory TSIZ[0:2] and TBST# Encoding        | 85       |

|         | Summary of CPU Read and Write System Memory Characteristics  | 85       |

| 5.5.3   | 60X CPU to PCI Cycles                                        |          |

| 5.5.3.1 | Valid 60X CPU to PCI Transactions                            | 86       |

| 5.5.3.2 | Termination Responses for 60X CPU to PCI Transactions        | 86       |

| 5.5.3.3 | PCI Target Retry                                             | 86       |

| 5.5.3.4 | PCI_C/BE[3:0]#—PCI Bus Command/Byte Enable Generation        | 86       |

| 5.5.3.5 | 60X CPU to PCI Bus Commands                                  | 86       |

| 5.5.3.6 | PCI Byte Enables                                             | 87       |

| 5.5.3.7 | Transfer Size Parameters for the PCI Bus                     | 88       |

| 5.5.4   | 60X CPU to PCI Interrupt Acknowledge Cycles                  | 88       |

| 5.5.5   | 60X CPU to Read Error Address Cycles                         | 88       |

| 5.5.6   | 60X CPU to System ROM Cycles                                 | 88       |

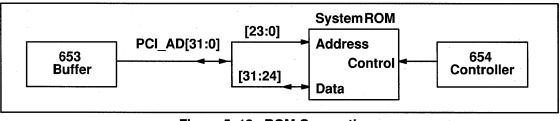

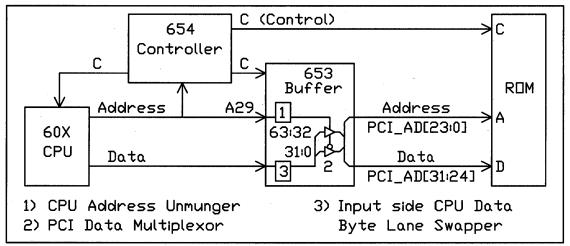

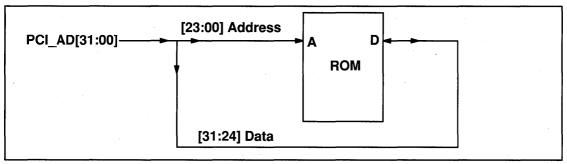

| 5.5.6.1 | ROM Addressing                                               | 89       |

112

113

| 5.5.6.2   | ROM Access Data Sizes and Alignments                        | 89  |

|-----------|-------------------------------------------------------------|-----|

| 5.5.6.3   | Single-Beat ROM Reads                                       | 89  |

| 5.5.6.4   | Burst ROM Reads                                             | 89  |

| 5.5.6.5   | Programming the ROM Boot For 601 Burst Reads                | 90  |

| 5.5.6.6   | 60X CPU to Flash ROM Write Cycles                           | 90  |

| 5.5.6.7   | Effect of Endian Mode on ROM Writes                         | 90  |

| 5.5.6.8   | Flash ROM Protection                                        | 90  |

| 5.5.7     | 60X CPU to System ROM Detailed Operation                    | 91  |

| 5.5.7.1   | ROM Write Detailed Operation                                | 91  |

| 5.5.7.2   | ROM Read Detailed Operation                                 | 95  |

| 5.6       | The PCI to 650 Bridge Transactions                          | 98  |

| 5.6.1     | PCI to System Memory Cycles                                 | 98  |

| 5.6.1.1   | I/O Bridge to System Memory                                 | 98  |

| 5.6.1.2   | ISA Master Memory Addressing                                | 98  |

| 5.6.1.3   | ISA Master Memory Addressing                                | 98  |

| 5.6.1.4   | PCI to System Memory (DRAM) PCI_C/BE[3:0]# Bus Commands     | 90  |

| 5.6.1.5   | Snoop Cycle Control Signals on the 60X CPU Host Bus         | 100 |

| 5.7       | L2 Secondary Cache Protocol                                 | 101 |

| 5.7.1     | L2 Caching for 60X CPU Accesses to System Memory            | 101 |

| 5.7.2     | Cache Snooping for PCI to System Memory Accesses            | 102 |

| 5.7.2.1   | Restoring ARTRY#                                            | 102 |

| 5.7.2.2   | Arbitration on Cache Hits                                   | 102 |

| 5.7.3     | Error Checking for the L2 Cache                             | 102 |

| 5.7.4     | Additional L2 Cache Information                             | 102 |

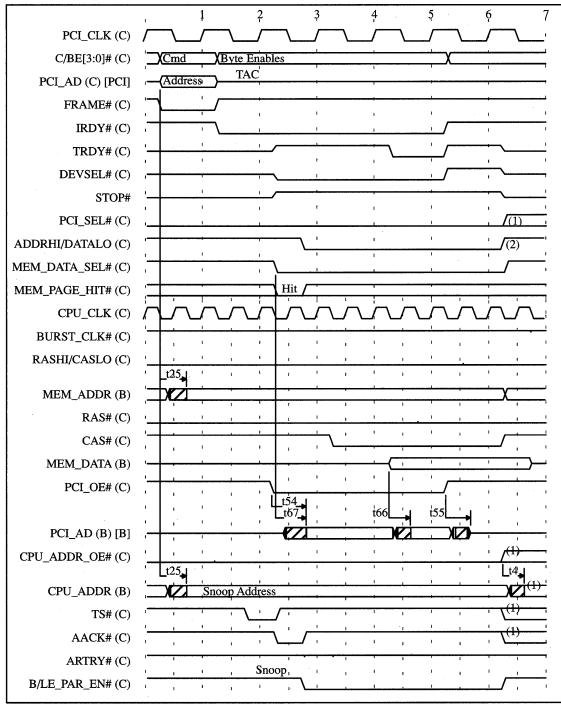

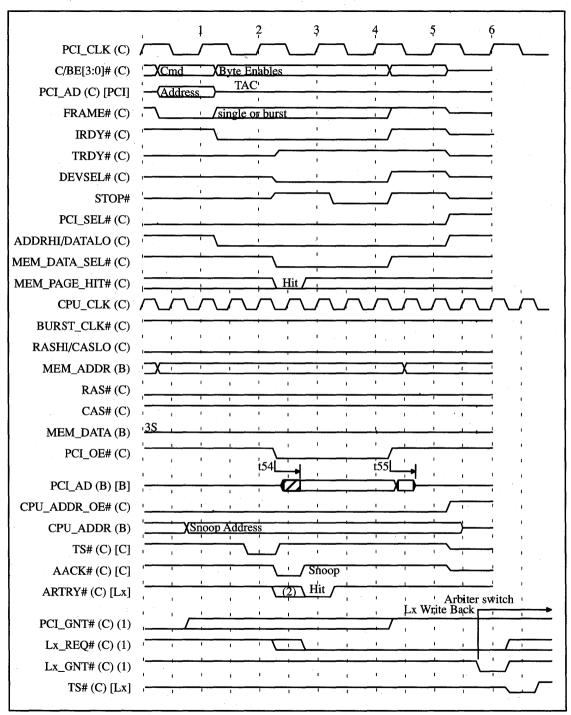

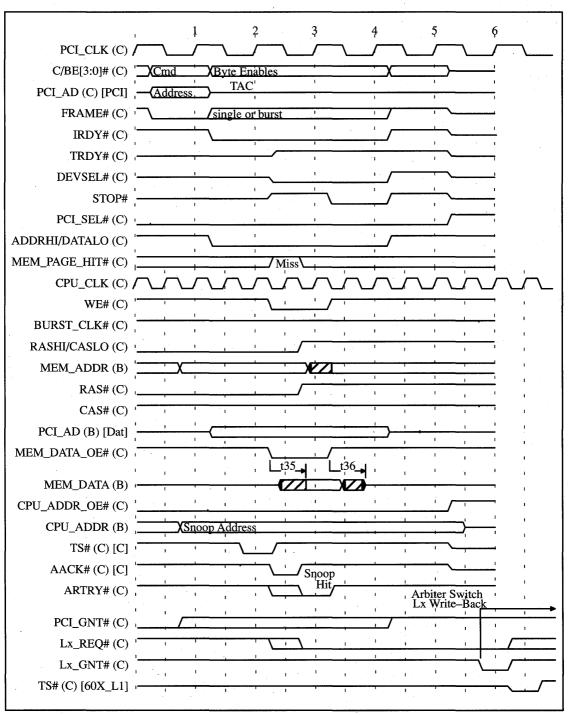

| 5.7.5     | Example of a PCI to Memory Read Transaction With Cache Hit  | 102 |

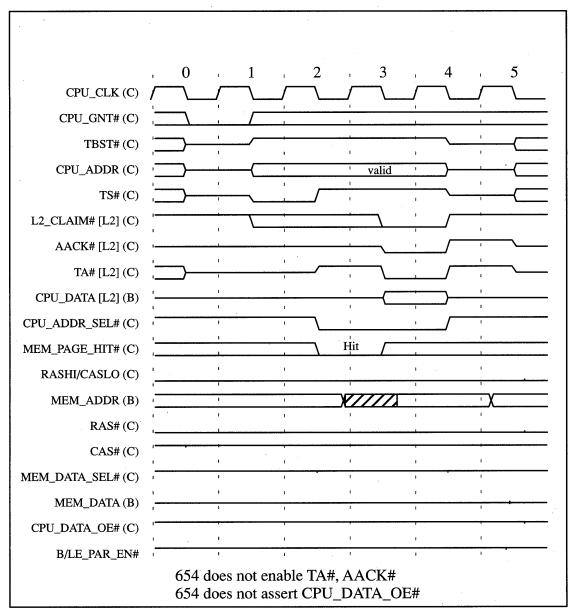

| 5.7.6     | Example of a CPU to Memory Read Transfer With Page Miss and | 100 |

| 0.7.0     | L2 Cache Hit                                                | 105 |

| 5.8       | The System Error Handler                                    | 106 |

| 5.8.1     | TEA# Error Reporting                                        | 106 |

| 5.8.2     | Interrupt Reporting                                         | 106 |

| 5.8.3     | Saving Memory Parity Error Addresses                        | 108 |

| 5.8.4     | Data Parity Error (DPE_ERR#)                                | 108 |

| 5.8.5     | Transfer Type Error                                         | 108 |

| 5.8.6     | Illegal PCI Operations                                      | 109 |

| 5.8.7     | Non-Maskable Interrupt (NMI_REQ)                            | 109 |

|           |                                                             |     |

| Section   | 6                                                           |     |

| Electrica | al Characteristics                                          | 111 |

| 6.1       | Absolute Maximum Ratings                                    | 111 |

| 6.2       | Recommended Operating Conditions                            | 112 |

| 6.2.1     | Signal And Temperature Ranges                               | 112 |

Power Dissipation

Thermal Characteristics .....

6.2.2

6.2.3

| 6.3      | Common Characteristics                                            | 114 |

|----------|-------------------------------------------------------------------|-----|

| 6.4      | Package/Pin Electrical Characteristics                            | 114 |

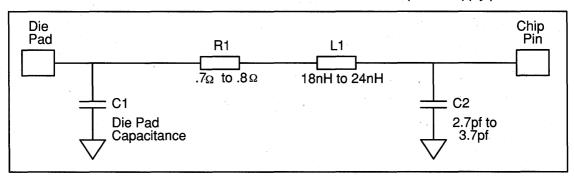

| 6.4.1    | 653 Buffer Model                                                  | 114 |

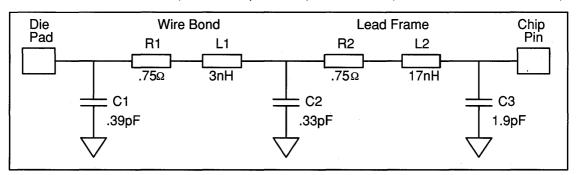

| 6.4.2    | 654 Controller Model                                              | 115 |

| 6.5      | 653 Buffer DC Characteristics By Signal                           | 116 |

| 6.6      | 654 Controller DC Characteristics By Signal                       | 118 |

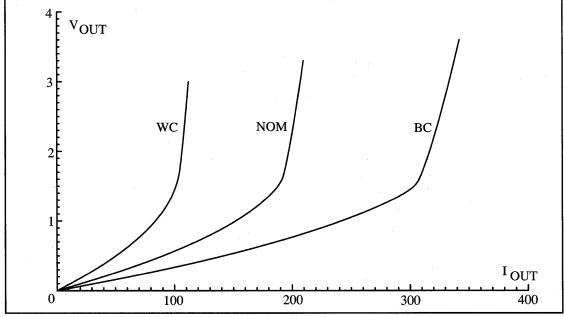

| 6.7      | Output V—I Curves                                                 | 122 |

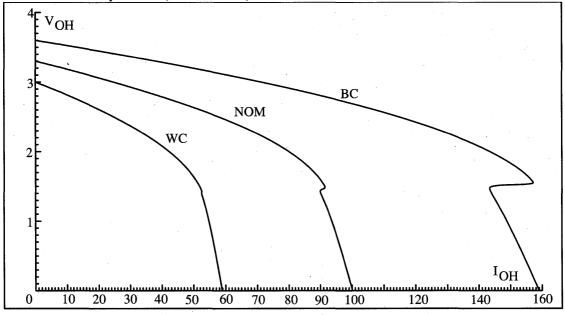

| 6.7.1    | PCI Local Bus Compatible Drivers                                  | 122 |

| 6.7.1.1  | Pull Up Curves, PCI Drivers, P/L = A                              | 122 |

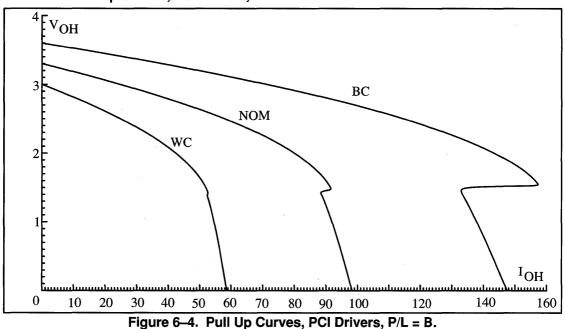

| 6.7.1.2  | Pull Up Curves, PCI Drivers, P/L = B                              | 123 |

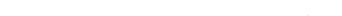

| 6.7.1.3  | Pull Up Curves, PCI Drivers, P/L = C                              | 123 |

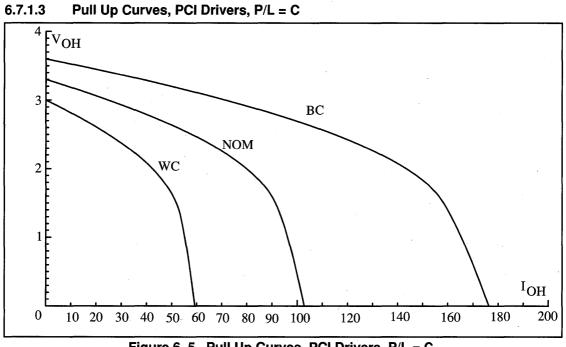

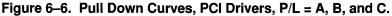

| 6.7.1.4  | Pull Down Curves, PCI Drivers, P/L = A, B, and C                  | 124 |

| 6.7.2    | TTL Driver Output Curves                                          | 124 |

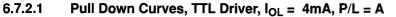

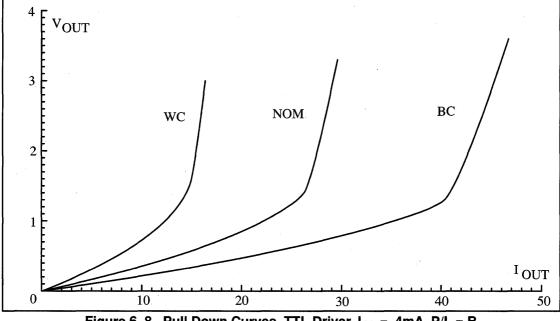

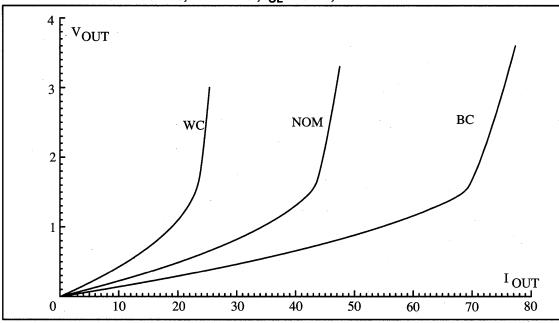

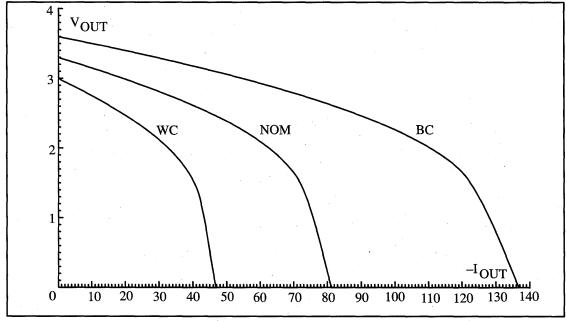

| 6.7.2.1  | Pull Down Curves, TTL Driver, IOL = 4mA, P/L = A                  | 125 |

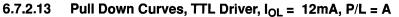

| 6.7.2.2  | Pull Down Curves, TTL Driver, IOL = 4mA, P/L = B                  | 125 |

| 6.7.2.3  | Pull Down Curves, TTL Driver, IOL = 4mA, P/L = C                  | 126 |

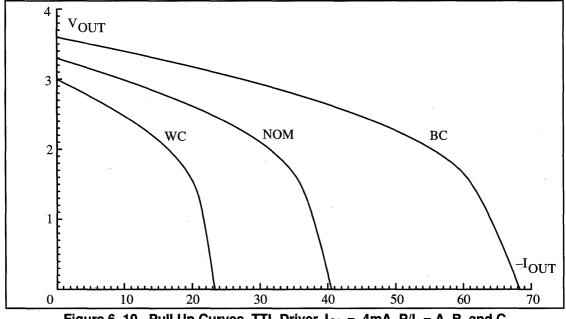

| 6.7.2.4  | Pull Up Curves, TTL Driver, IOL = 4mA, P/L = A, B, and C          | 126 |

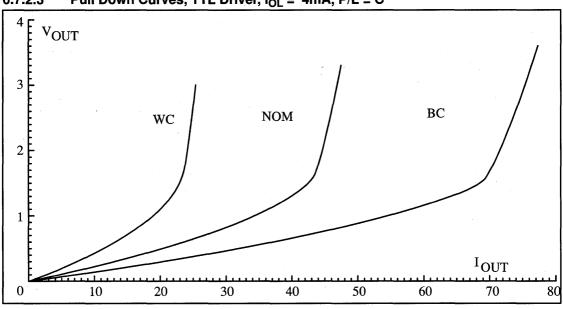

| 6.7.2.5  | Pull Down Curves, TTL Driver, IOL = 6mA, P/L = A                  | 127 |

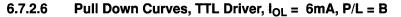

| 6.7.2.6  | Pull Down Curves, TTL Driver, IOL = 6mA, P/L = B                  | 127 |

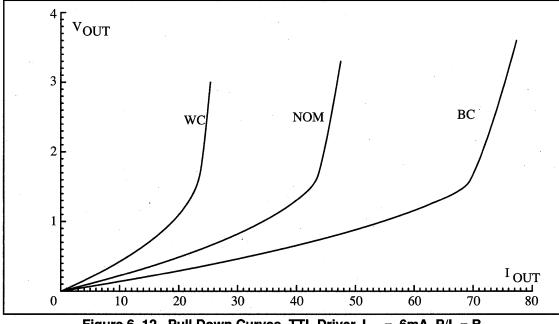

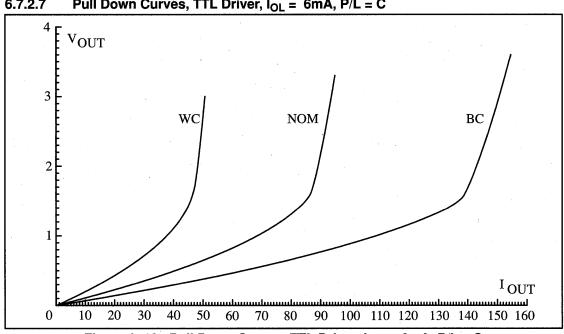

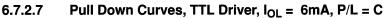

| 6.7.2.7  | Pull Down Curves, TTL Driver, IOL = 6mA, P/L = C                  | 128 |

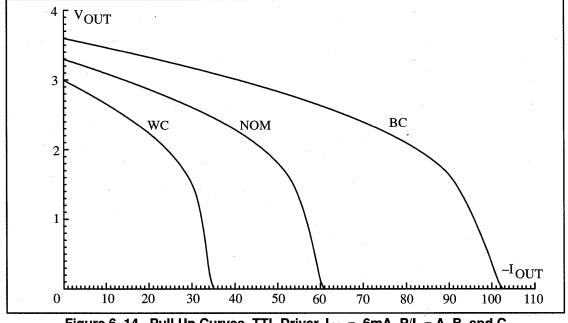

| 6.7.2.8  | Pull Up Curves, TTL Driver, IOL = 6mA, P/L = A, B, and C          | 128 |

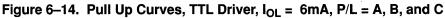

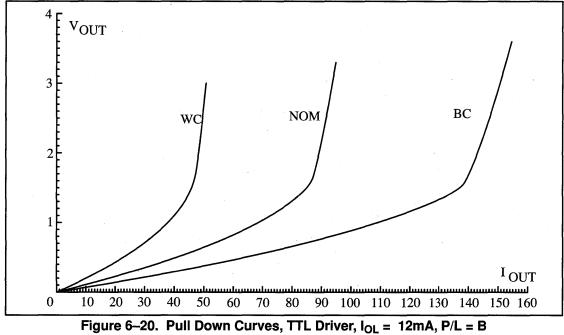

| 6.7.2.9  | Pull Down Curves, TTL Driver, IOL = 8mA, P/L = A                  | 129 |

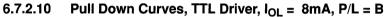

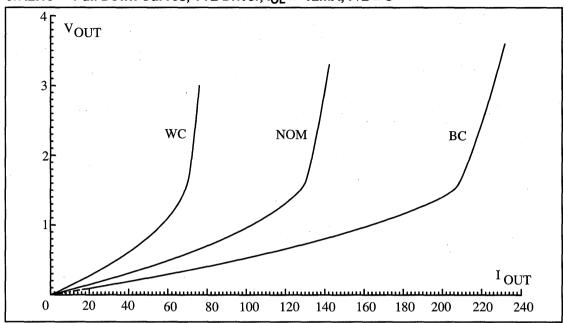

| 6.7.2.10 | Pull Down Curves, TTL Driver, IOL = 8mA, P/L = B                  | 129 |

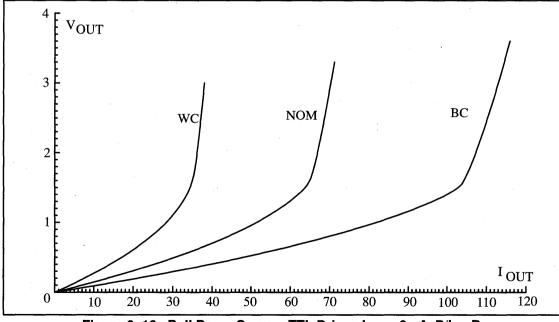

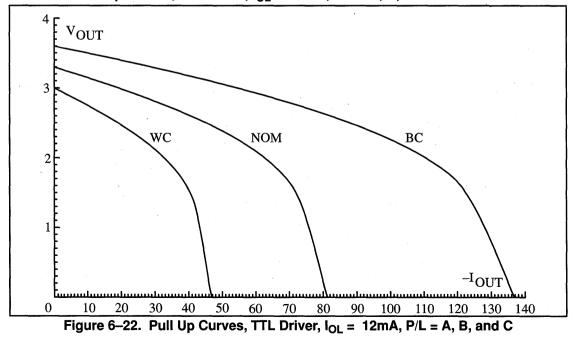

| 6.7.2.11 | Pull Down Curves, TTL Driver, IOL = 8mA, P/L = C                  | 130 |

| 6.7.2.12 | Pull Up Curves, TTL Driver, IOL = 8mA, P/L = A, B, and C          | 130 |

| 6.7.2.13 | Pull Down Curves, TTL Driver, IOL = 12mA, P/L = A                 | 131 |

| 6.7.2.14 | Pull Down Curves, TTL Driver, IOL = 12mA, P/L = B                 | 131 |

| 6.7.2.15 | Pull Down Curves, TTL Driver, IOL = 12mA, P/L = C                 | 132 |

| 6.7.2.16 | Pull Up Curves, TTL Driver, IOL = 12mA, P/L = A, B, and C         | 132 |

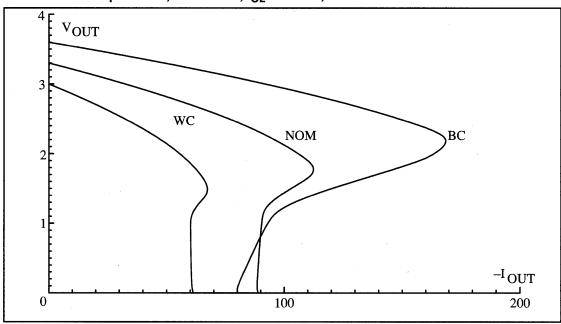

| 6.7.2.17 | Pull Up Curves, TTL Driver, IOL = 24mA, P/L = A                   | 133 |

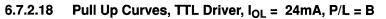

| 6.7.2.18 | Pull Up Curves, TTL Driver, IOL = 24mA, P/L = B                   | 133 |

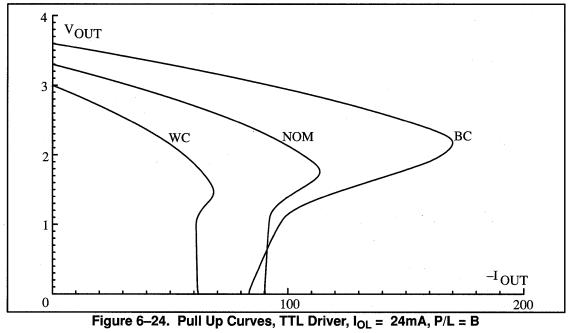

| 6.7.2.19 | Pull Up Curves, TTL Driver, IOL = 24mA, P/L = C                   | 134 |

| 6.7.2.20 | Pull Down Curves, TTL Driver, $IOL = 24mA$ , $P/L = A$ , B, and C | 134 |

### Section 7

| Timings | ·                                           | 135 |

|---------|---------------------------------------------|-----|

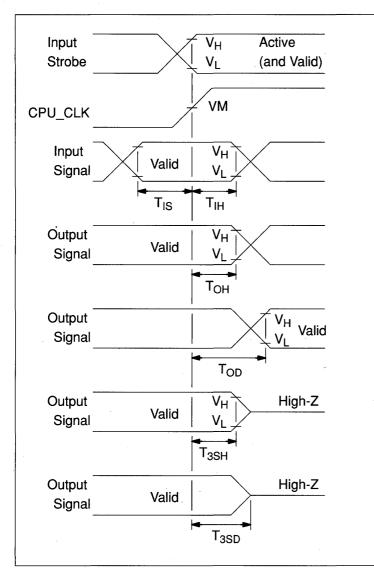

| 7.1     | Timing Conventions                          | 135 |

| 7.1.1   | Board Delays                                | 135 |

| 7.1.2   | Terms and Definitions                       | 135 |

| 7.1.2.1 | Signal Range Names                          | 135 |

| 7.1.2.2 | Signal Group Names                          | 135 |

| 7.1.2.3 | Timing Diagram and Timing Chart Definitions | 136 |

230

| 7 4 0              |                                                          | 100 |

|--------------------|----------------------------------------------------------|-----|

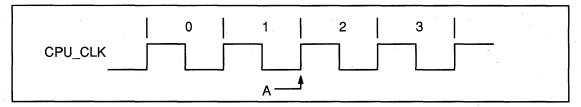

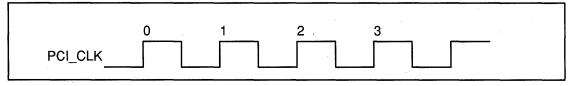

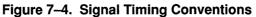

| 7.1.3              | Transaction Clock Cycle Nomenclature                     | 136 |

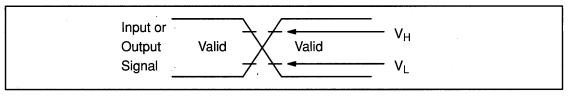

| 7.1.4              | Signal Switching Levels for Timing Analysis              | 136 |

| 7.1.5              | Input Setup Time                                         | 137 |

| 7.1.6              | Input Hold Time                                          | 137 |

| 7.1.7              | Output Hold Time                                         | 137 |

| 7.1.8              | Output Valid Delay Times                                 | 138 |

| 7.1.9              | Output Tri-State Hold Time                               | 138 |

| 7.1.10             | Output Tri-State Delay Time                              | 138 |

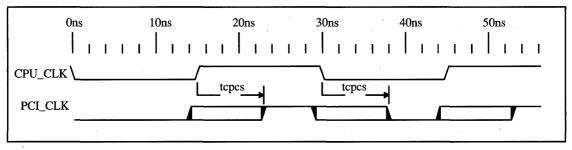

| 7.2                | Clock Considerations                                     | 140 |

| 7.2.1              | Clock Switching Levels                                   | 140 |

| 7.2.2              | The CPU_CLK                                              | 140 |

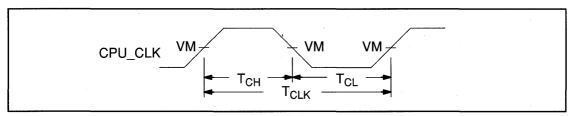

| 7.2.3              | The 654 Controller Clock and the 601 Clocks              | 140 |

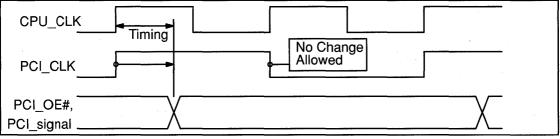

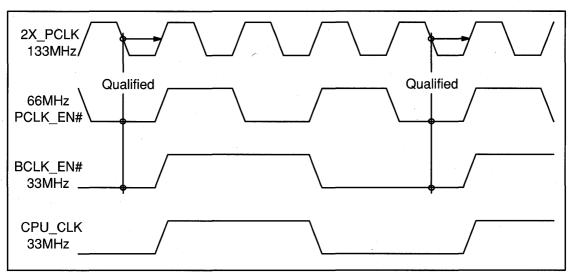

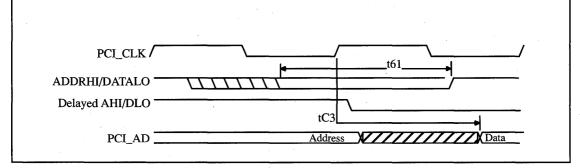

| 7.2.4              | CPU_CLK to PCI_CLK Skew                                  | 142 |

| 7.2.4.1            | Clocking In 2:1 Mode                                     | 142 |

| 7.2.4.2            | Clocking In 1:1 Mode                                     | 143 |

| 7.3                | Power-On Considerations                                  | 143 |

| 7.4                | 654 Controller Timing                                    | 144 |

| 7.4.1              | 654 Controller Synchronous Input Timing Characteristics  | 144 |

| 7.4.2              | 654 Controller Synchronous Output Timing Characteristics | 147 |

| 7.4.3              | Asynchronous Signals in the 654                          | 150 |

| 7.4.3.1            | AACK#                                                    | 150 |

| 7.4.3.1            | ALL ONES SEL#                                            | 150 |

| 7.4.3.2            | <b>—</b> — —                                             | 150 |

| 7.4.3.3            |                                                          |     |

|                    | CPU_ADDR_SEL#                                            | 150 |

| 7.4.3.5            | CPU_DATA_SEL#                                            | 150 |

| 7.4.3.6            | ERR_ADDR_SEL#                                            | 151 |

| 7.4.3.7            | MEM_DATA_OE#                                             | 151 |

| 7.4.3.8            | MEM_DATA_SEL#                                            | 151 |

| 7.4.3.9            | PCI_C/BE[3:0]#                                           | 151 |

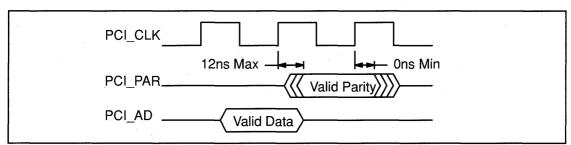

| 7.4.3.10           | PCI_PAR                                                  | 151 |

| 7.4.3.11           | TA#                                                      | 152 |

| 7.4.3.12           | WE[1:0]                                                  | 152 |

| 7.5                | 653 Buffer Timing Tables                                 | 153 |

| 7.6                | Detailed Timing Diagrams                                 | 160 |

|                    | •                                                        |     |

| Section<br>The 650 | 8<br>Bridge Pin Lists                                    | 203 |

| 8.1                | 653 Buffer Pin Lists                                     | 203 |

| 8.1.1              | 653 Buffer Numeric Pin List                              | 203 |

| 8.1.2              | 653 Buffer Alphabetic Pin Listing                        | 214 |

| 8.2                | 654 Controller Pin Lists                                 | 225 |

| 8.2.1              | 654 Controller Numeric Pin Lists                         | 225 |

| U.L.I              |                                                          | 220 |

654 Controller Alphabetic Pin List

8.2.2

| Section 9<br>650 Bridge Mechanical Drawings |                                                      | 235 |

|---------------------------------------------|------------------------------------------------------|-----|

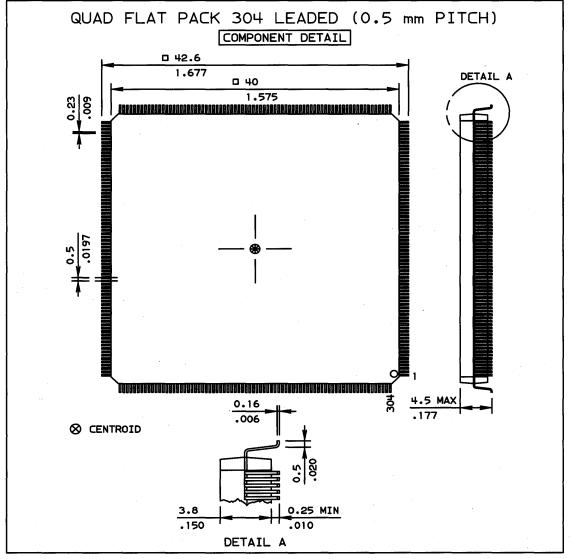

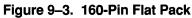

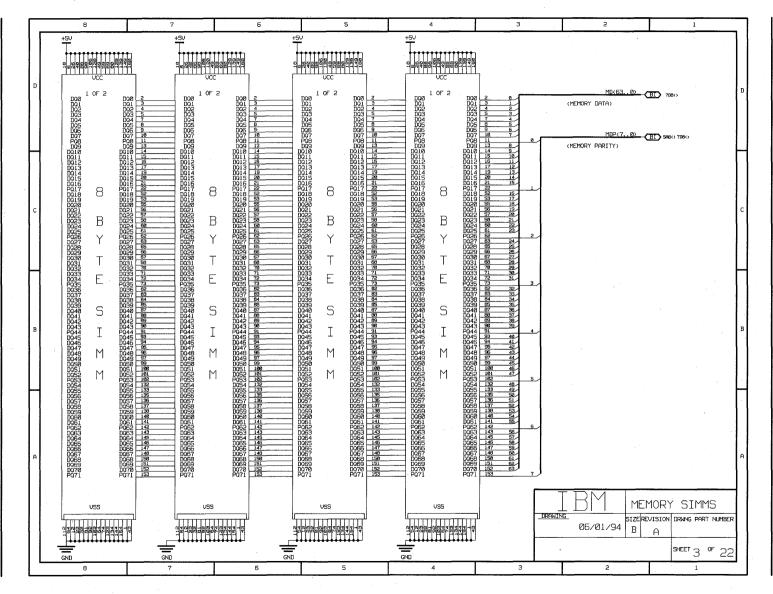

| 9.1                                         | 653 Buffer Quad Flat Pack Component Detail           | 235 |

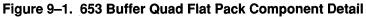

| 9.2                                         | 653 Buffer Quad Flat Pack Component Footprint        | 236 |

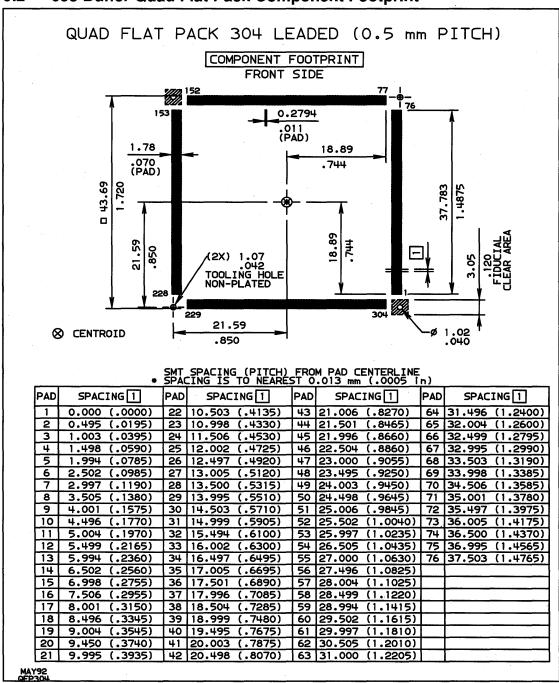

| 9.3                                         | 654 Controller 160-Pin Flat Pack Component Detail    | 237 |

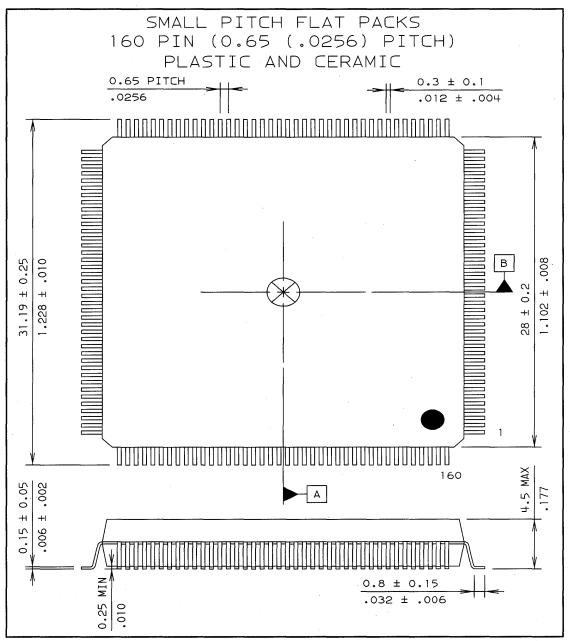

| 9.4                                         | 654 Controller 160-Pin Flat Pack Component Footprint | 238 |

## Appendixes:

#### Appendix A

| Initializ | ation and Setup Requirements                    | 239 |

|-----------|-------------------------------------------------|-----|

| A.1       |                                                 | 239 |

| A.1.1     | Cache Setup                                     | 239 |

| A.1.2     | PIO Setup                                       | 239 |

| A.1.3     | ARTRY# Precharge                                | 239 |

| A.1.4     | Checkstop Enable                                | 239 |

| A.1.5     | Bus Error Checks                                | 240 |

| A.2       | Initialization of the IBM 82650 Bridge Chip Set | 240 |

| A.3       | I/O Bridge Setup                                | 240 |

| A.4       | PCI Memory Address Assignment                   | 240 |

| A.5       | PCI Configuration Scan                          | 240 |

|           |                                                 |     |

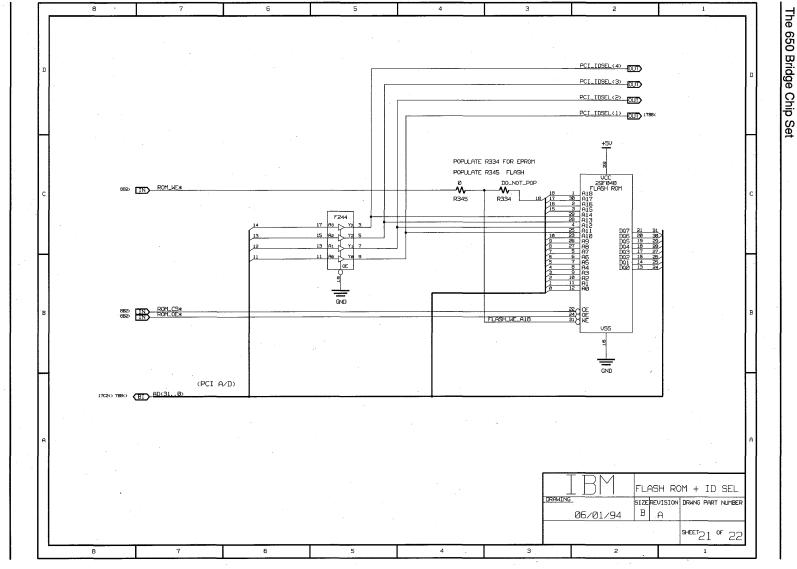

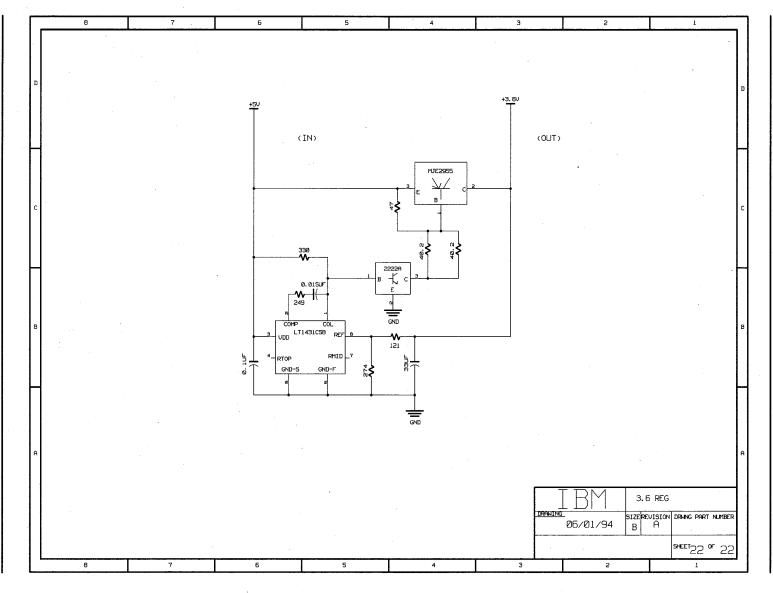

#### Appendix B

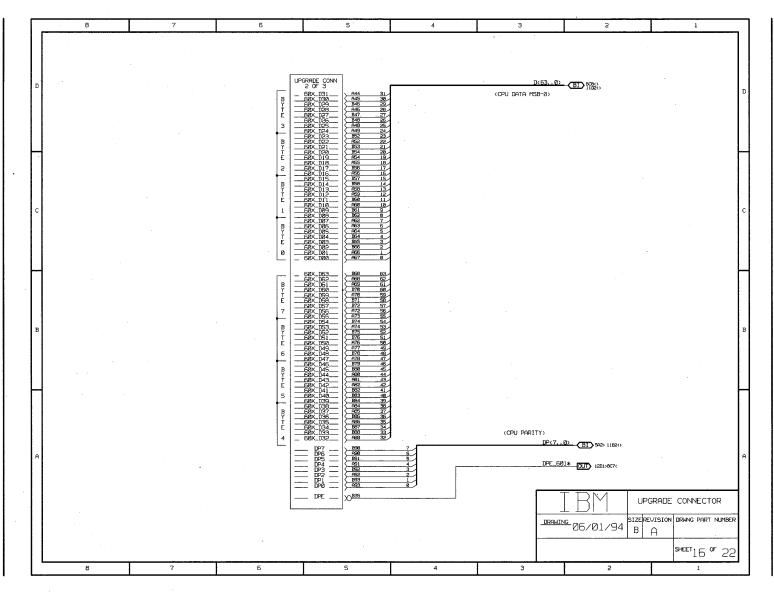

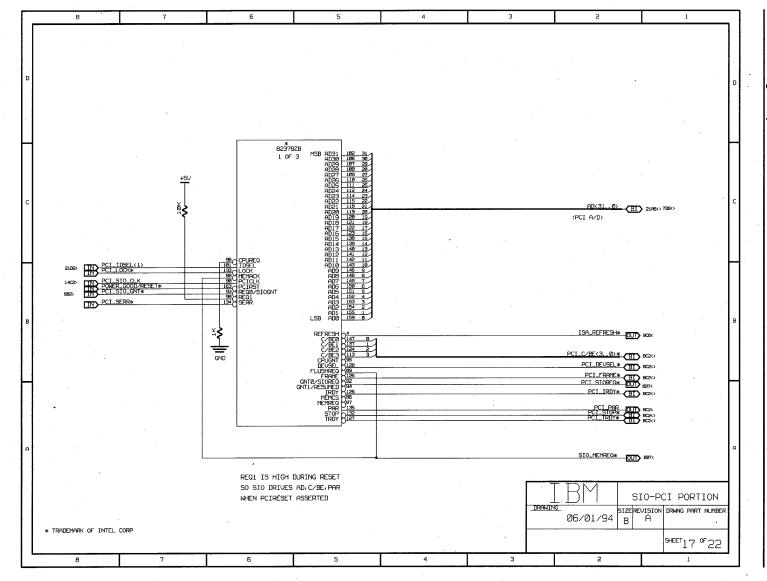

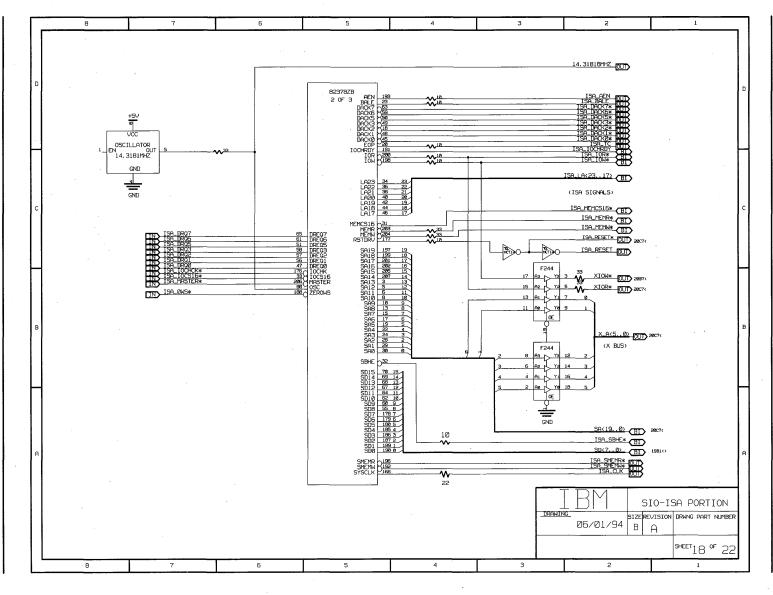

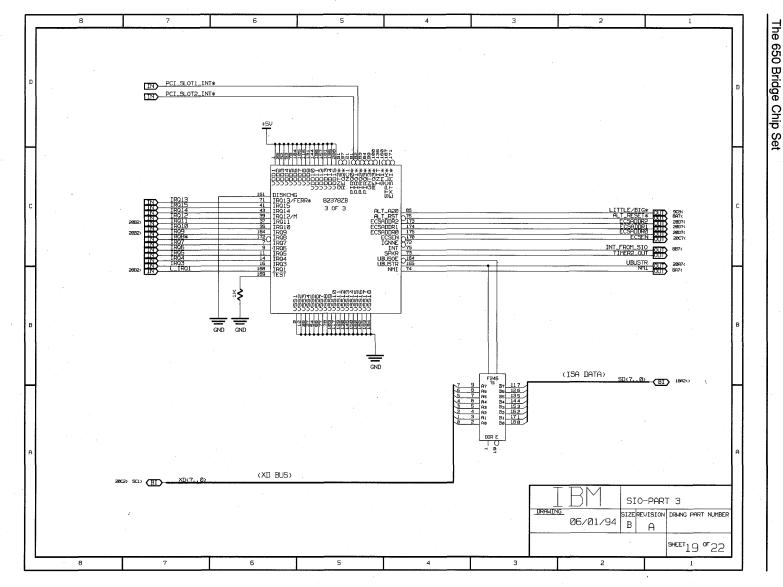

| Example Implementation |  | 241 |

|------------------------|--|-----|

|------------------------|--|-----|

#### Appendix C

| 653 Bu | ffer Details of Operation                            | 265 |

|--------|------------------------------------------------------|-----|

| C.1    | 653 Buffer Highlights                                | 265 |

| C.2    | 653 Buffer Pin Descriptions                          | 265 |

| C.2.1  | 60X CPU Bus Interface Signals                        | 267 |

| C.2.2  | System Memory Interface Signals                      | 267 |

| C.2.3  | PCI Bus Interface Signals                            | 268 |

| C.2.4  | 654 Controller Interface Signals                     | 268 |

| C.2.5  | External Logic and System Interface Signals          | 270 |

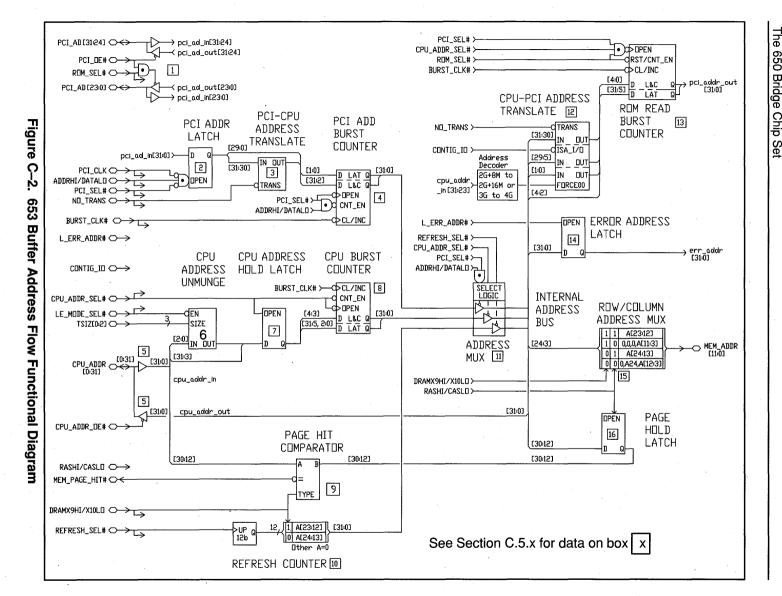

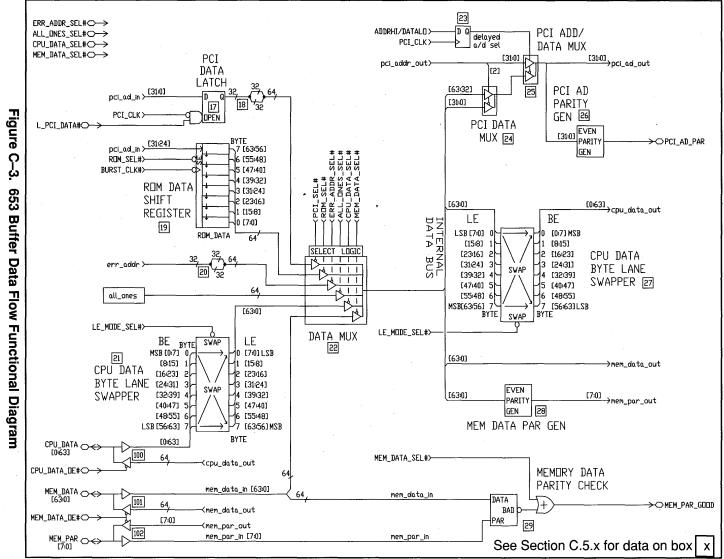

| C.3    | The 653 Buffer                                       | 271 |

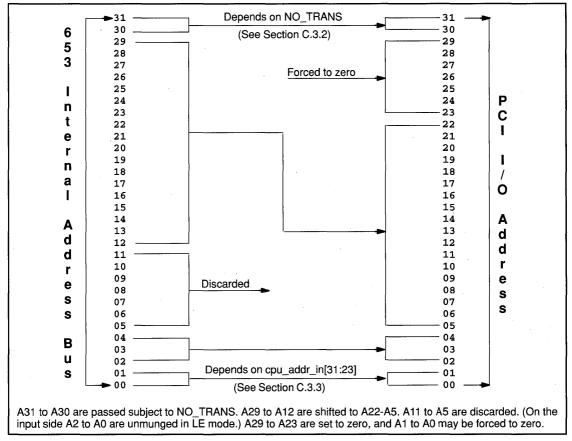

| C.3.1  | Architectural Overview Showing Address and Data Flow | 271 |

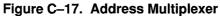

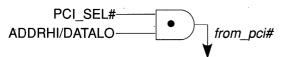

| C.3.2  | Two High-order PCI Address Bits—NO_TRANS Pin         | 274 |

| C.3.3  | Two Low-Order PCI Address Bits                       | 274 |

| C.3.4  | Contiguous I/O Pin                                   | 274 |

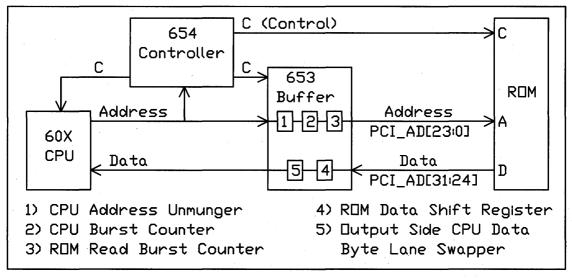

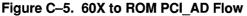

| C.3.5  | 60X to ROM Read Cycles                               | 275 |

| C.3.6  | 60X to ROM Write Cycles—Address and Data Flow        | 276 |

| C.3.7    | Error Address Latch                                    | 276 |  |  |  |

|----------|--------------------------------------------------------|-----|--|--|--|

| C.3.8    | Refresh Address Generation                             |     |  |  |  |

| C.3.9    | All_Ones Generator                                     | 276 |  |  |  |

| C.3.10   | Page Hit Generation                                    |     |  |  |  |

| C.3.11   | Special Considerations                                 | 277 |  |  |  |

| C.3.12   | Warm Reset                                             | 277 |  |  |  |

| C.4      | Detailed Analysis of Address and Data Flow             | 277 |  |  |  |

| C.4.1    | 60X to Memory Cycle Address Flow—Read or Write         | 277 |  |  |  |

| C.4.2    | 60X to Memory Cycle Data Flow—Write                    | 277 |  |  |  |

| C.4.3    | 60X to Memory Cycle Data Flow—Read                     | 278 |  |  |  |

| C.4.4    | 60X to PCI Cycle Address Flow—Read or Write            | 278 |  |  |  |

| C.4.5    | 60X to PCI Cycle Data FlowWrite                        | 278 |  |  |  |

| C.4.6    | 60X to PCI Cycle Data Flow—Read                        | 279 |  |  |  |

| C.4.7    | PCI Bus Master Cycles Address Flow—Read or Write       | 279 |  |  |  |

| C.4.8    | PCI to Memory Cycles Data Flow—Write                   | 280 |  |  |  |

| C.4.9    | PCI to Memory Cycles Data Flow—Read                    | 280 |  |  |  |

| C.5      | 653 Buffer Detailed Internal Descriptions              | 280 |  |  |  |

| C.5.1    | PCI_AD Transceivers                                    | 280 |  |  |  |

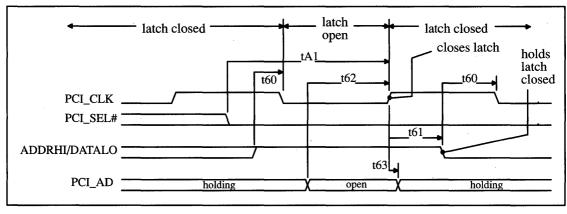

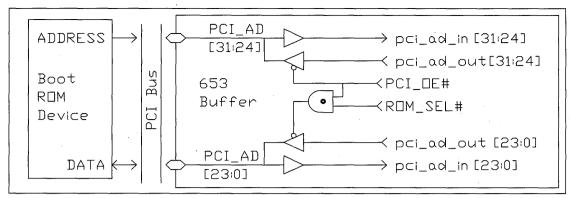

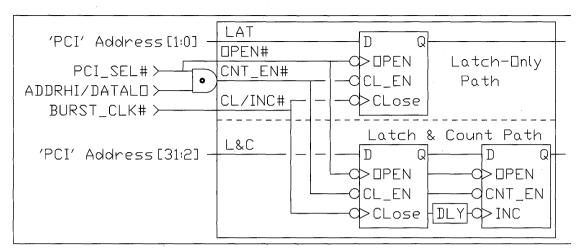

| C.5.2    | PCI Address Latch                                      | 281 |  |  |  |

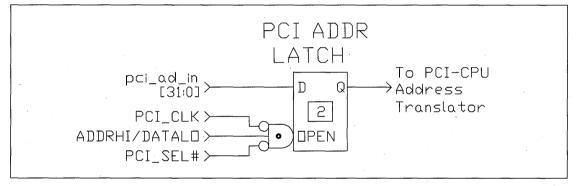

| C.5.3    | PCI to 60X CPU Address Translation                     | 281 |  |  |  |

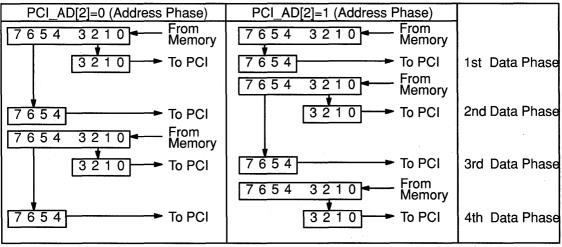

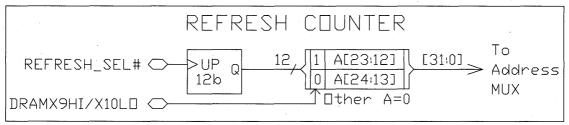

| C.5.4    | PCI Burst Counter                                      | 282 |  |  |  |

| C.5.5    | 60X CPU Address Bus Transceivers                       | 284 |  |  |  |

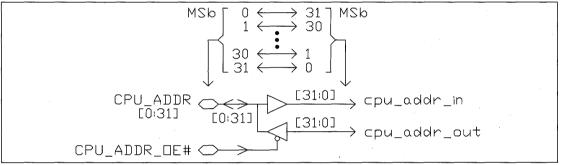

| C.5.6    | 60X CPU Address UnMunger                               | 284 |  |  |  |

| C.5.7    | 60X CPU Address Hold Latch                             | 285 |  |  |  |

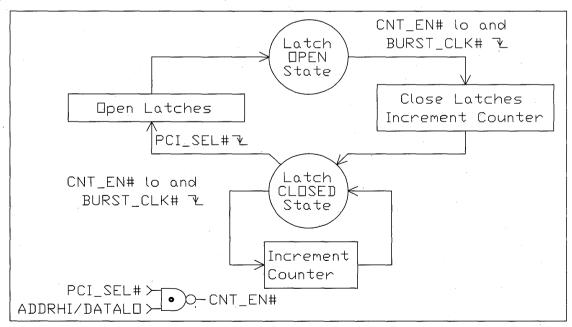

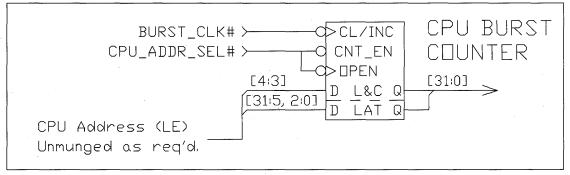

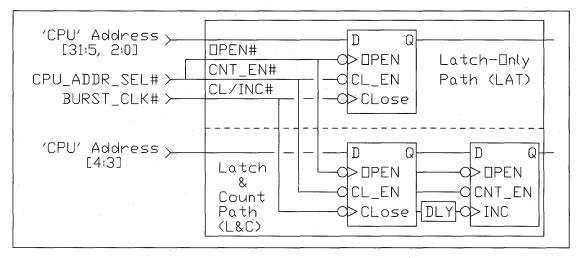

| C.5.8    | 60X CPU Burst Counter                                  | 285 |  |  |  |

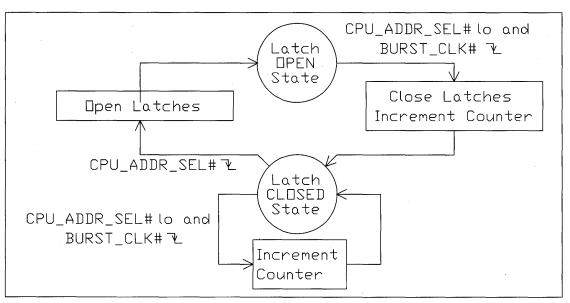

| C.5.9    | Page Hit Comparator                                    | 287 |  |  |  |

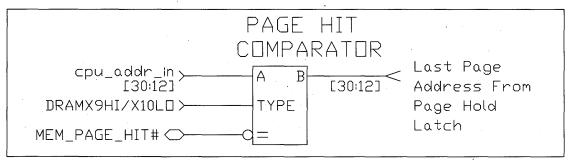

| C.5.10   | Refresh Counter                                        | 288 |  |  |  |

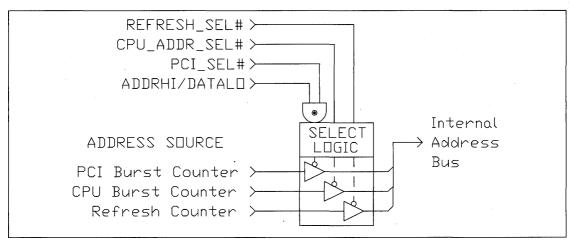

| C.5.11   | Address Multiplexer                                    | 288 |  |  |  |

| C.5.12   | 60X CPU to PCI Address Translation                     | 289 |  |  |  |

| C.5.12.1 | A[1:0] Translation—PCI Bus Special Requirements        | 290 |  |  |  |

| C.5.12.2 | A[4:2] Non-Translation                                 | 290 |  |  |  |

| C.5.12.3 | A[31:30] Translation—System Address Map Implementation | 290 |  |  |  |

| C.5.12.4 | A[29:5] Translation—PCI/ISA I/O Page Mapping           | 291 |  |  |  |

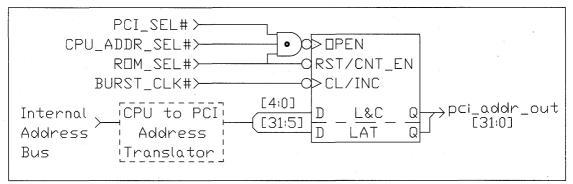

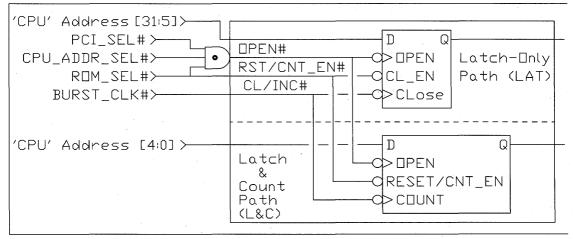

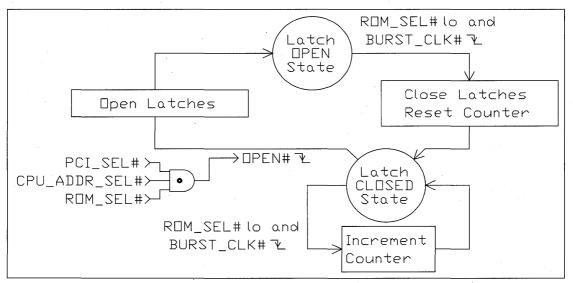

| C.5.13   | ROM Read Burst Counter                                 | 292 |  |  |  |

| C.5.14   | Error Address Latch                                    | 294 |  |  |  |

| C.5.15   | Row/Column Address Multiplexer                         | 294 |  |  |  |

| C.5.16   | Page Hold Latch                                        | 294 |  |  |  |

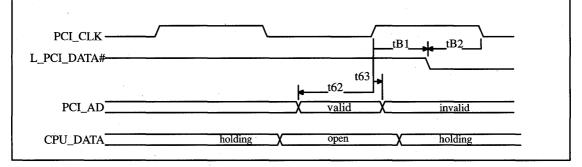

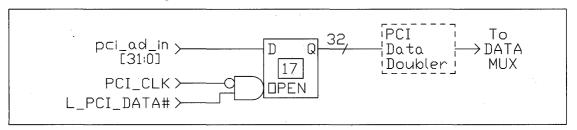

| C.5.17   | PCI Data Latch                                         | 294 |  |  |  |

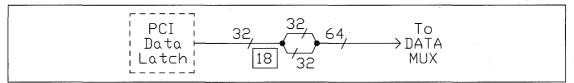

| C.5.18   | PCI Data Doubler                                       | 295 |  |  |  |

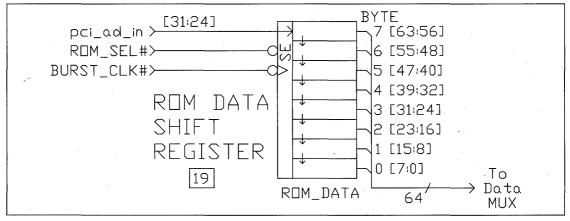

| C.5.19   | ROM Data Shift Register                                | 295 |  |  |  |

| C.5.20   | Error Address Doubler                                  | 296 |  |  |  |

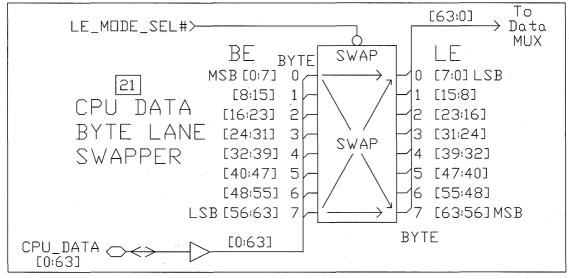

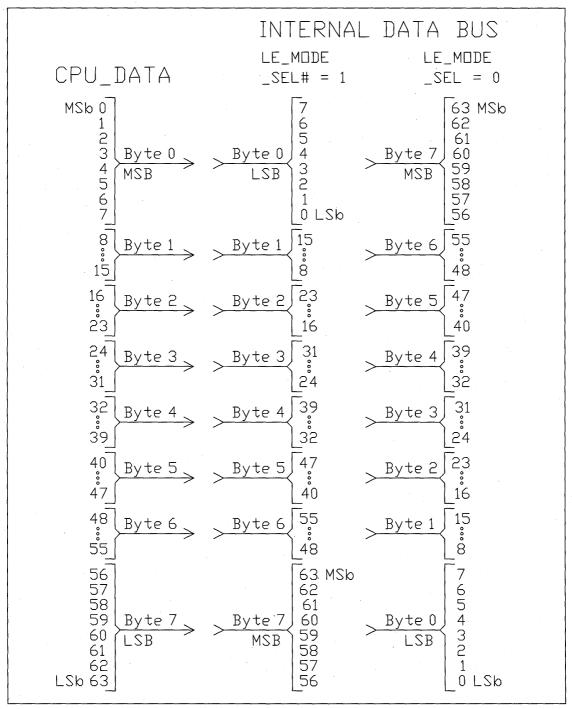

| C.5.21   | 60X CPU Byte Lane Swapper—Input Side                   | 296 |  |  |  |

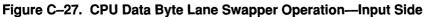

| C.5.22   | Data Multiplexer                                       | 299 |  |  |  |

|          |                                                        |     |  |  |  |

| 299 |

|-----|

| 300 |

| 300 |

| 301 |

| 301 |

| 303 |

| 303 |

|     |

#### Appendix D

| Addresse | es of Sales Offices |

|----------|---------------------|

| D.1      | USA                 |

| D.2      | Europe              |

| D.3      | Japan               |

## Tables:

| 2–1  | PCI Signals in the 650 Bridge                         | 6   |

|------|-------------------------------------------------------|-----|

| 2–2  | PCI Bus Commands                                      | 8   |

| 2–3  | 60X CPU Signals Connected to the 650 Bridge           | 9   |

| 2–4  | TT[0:3]—Transfer Type Codes                           | 11. |

| 2–5  | Big-Endian and Little-Endian Data Storage             | 12  |

| 3–1  | 653 Buffer to 60X CPU Bus Interface                   | 17  |

| 3–2  | 653 Buffer to PCI Bus Interface                       | 17  |

| 3–3  | 653 Buffer to System Memory Interface                 | 17  |

| 3–4  | 653 Buffer to External Logic and System Interface     | 18  |

| 3–5  | 654 Controller to 60X CPU Bus Interface               | 19  |

| 3–6  | 654 Controller to PCI Bus Interface                   | 21  |

| 3–7  | 654 Controller to System Memory (DRAM) Interface      | 22  |

| 3–8  | 654 Controller to ROM or Flash Signals                | 22  |

| 3–9  | 654 Controller to L2 Cache Signals                    | 23  |

| 3–10 | 654 Controller to Test Signals                        | 23  |

| 3–11 | 654 Controller to External Logic and System Interface | 23  |

| 3–12 | Signals Between the 653 Buffer and the 654 Controller | 25  |

| 4–1  | 650 Bridge Mapping of 60X CPU Bus Addresses           | 28  |

| 4–2  | 650 Bridge Mapping of PCI Device Addresses            | 31  |

| 5–1  | SIMM Mapping Register Selection                       | 58  |

| 5–2  | SIMM Mapping Register Starting Addresses              | 58  |

| 5–3  | Example #1 SIMM Mapping Register Setup                | 60  |

| 5—4  | Example #2 SIMM Mapping Register Setup                | 60  |

| 5–5  | System Setup Register Settings                        | 62  |

| 5-6  | SIMM Register Access Timing Chart                     | 65  |

| 5–7  | CPU_ADDR[29:31] Munging for Little-Endian Mode        | 69  |

|      |                                                       |     |

| 5–8  | Three Low-Order Address Bit Unmunge                     | 69  |

|------|---------------------------------------------------------|-----|

| 5–9  | Endian Formats from the Byte Swapper                    | 70  |

| 5–10 | DRAM Memory Timings                                     | 77  |

| 5–11 | RAS and CAS Address Assignments                         | 78  |

| 5–12 | CAS[7:0]# Assertion for 60X CPU Writes to System Memory | 80  |

| 5–13 | CAS[7:0]# Assertion for PCI Writes to System Memory     | 81  |

| 5–14 | TT[0:3]—Transfer Type Codes on the 60X CPU Host Bus     | 83  |

| 5–15 | 654 Controller Transfer Sizes From the 60X CPU          | 84  |

| 5–16 | 60X CPU to System Memory Size Alignment                 | 85  |

| 5–17 | 60X CPU to PCI Bus Commands                             | 87  |

| 5–18 | PCI Byte Enables for PCI_C/BE[3:0]#                     | 87  |

| 5–19 | ROM Write Data Flow in Big-Endian Mode                  | 93  |

| 5–20 | ROM Write Data Flow in Little-Endian Mode               | 93  |

| 5–21 | PCI Bus Commands from PCI Masters                       | 100 |

| 5–22 | Cache and 650 Bridge Action Table                       | 101 |

| 5–23 | System Error Reporting                                  | 107 |

| 8–1  | 653 Buffer Numeric Pin List                             | 203 |

| 8–2  | 653 Buffer Alphabetic Pin List                          | 214 |

| 8–3  | 654 Controller Numeric Pin List                         | 225 |

| 8–4  | 654 Controller Alphabetic Pin List                      | 230 |

| C–1  | 653 Buffer Signals—60X CPU Bus Interface                | 267 |

| C–2  | 653 Buffer Signals—System Memory Interface              | 267 |

| С–З  | 653 Buffer Signals—PCI Bus Interface                    | 268 |

| C–4  | 653 Buffer Signals—654 Controller Interface             | 268 |

| C–5  | 653 Buffer Signals—External Logic and System Interface  | 270 |

| C–6  | Low Order PCI Address Bit Settings                      | 274 |

| C–7  | PCI to 60X CPU and System Memory Address Translation    | 279 |

| C-8  | PCI to 60X CPU and System Memory Address Translation    | 282 |

| C–9  | Unmunging Address Bits in Little-Endian Mode            | 285 |

| C-10 | Address Multiplexer Source Selection Priority           | 289 |

| C–11 | 60X CPU To PCI Address Translation—High Order           | 290 |

| C–12 | Memory Row and Column Address Generation                | 294 |

| C–13 | Data Multiplexer Source Selection Priority.             | 299 |

|      |                                                         |     |

.

## Figures:

| 1–1                      | IBM 650 Bridge Chip Set in a Typical System Configuration              | ່ 1 |

|--------------------------|------------------------------------------------------------------------|-----|

| 3–1                      | 650 Bridge Pin Connections                                             | 16  |

| 4–1                      | Non-Contiguous PCI I/O Address Transformation                          | 30  |

| 4 <b></b> 2 <sup>°</sup> | CPU to Memory Read, Single-Beat, Page Hit, XCAS = 0 Timing Diagram     | 33  |

| 4–3                      | CPU to Memory Read, Single-Beat, Page Hit, XCAS = 1 Timing Diagram     | 34  |

| 44                       | CPU to Memory Read, Single-Beat, Page Miss, XCAS = 1 Timing Diagram .  | 35  |

| 45                       | CPU to Memory Read, Burst, Page Miss, XCAS = 1 Timing Diagram          | 37  |

| 4–6                      | CPU to Memory Write, Single-Beat, Page Hit, XCAS = 0 Timing Diagram    | 39  |

| 4–7                      | CPU to Memory Write, Single-Beat, Page Hit, XCAS = 1 Timing Diagram    | 40  |

| 4–8                      | CPU to Memory Write, Single-Beat, Page Miss, XCAS = 1 Timing Diagram . | 41  |

| 4–9                      | CPU to Memory Write, Burst, Page Miss, XCAS = 1 Timing Diagram         | 43  |

| 4–10                     | Timing of PCI_OE#                                                      | 44  |

| 4–11                     | CPU to PCI Write, XADIO = 1 Timing Diagram                             | 45  |

| 4–12                     | CPU to PCI Write, XADIO = 0, Offbeat TS# Timing Diagram                | 47  |

| 4–13                     | CPU to PCI Write, XADIO = 1, Target Retry Timing Diagram               | 48  |

| 4–14                     | CPU to PCI Read Timing Diagram                                         | 49  |

| 4–15                     | PCI to Memory Read, Single-Beat, Page Hit Timing Diagram               | 51  |

| 4–16                     | PCI To Memory Burst Read Transaction                                   | 52  |

| 4–17                     | PCI to Memory Read, Burst, Page Hit Then Miss Timing Diagram           | 53  |

| 4–18                     | PCI to Memory Write, Burst, Page Miss Then Hit Timing Diagram          | 54  |

| 5–1                      | The System Setup Register                                              | 61  |

| 5–2                      | 650 Register Access Pathway in the Example System                      | 63  |

| 5–3                      | 654 Setup Register Data Paths and Steering Logic                       | 63  |

| 5-4                      | 650 Register Write Timing Diagram                                      | 64  |

| 5–5                      | 650 Register Read Timing Diagram                                       | 66  |

| 5–6                      | Byte Swapper Operation for Example of a Store Byte Instruction         | 71  |

| 5–7                      | Byte Swapper Operation for Example of a Store Half-Word Instruction    | 72  |

| 5–8                      | Byte Swapper Operation for Example of a Store Word Instruction         | 72  |

| 5–9                      | Byte Swapper Operation for a Store Floating-Point Double Instruction   | 73  |

| 5–10                     | Byte Swapper Operation for Example of a Load Half-Word Instruction     | 74  |

| 5–11                     | Byte Swapper Operation for Example of a Load Word Instruction          | 75  |

| 5–12                     | Byte Swapper Operation for Example of Load Floating-Point Instruction  | 75  |

| 5–13                     | ROM Connections                                                        | -88 |

| 5–14                     | CPU to ROM Write Address and Data Flows                                | 91  |

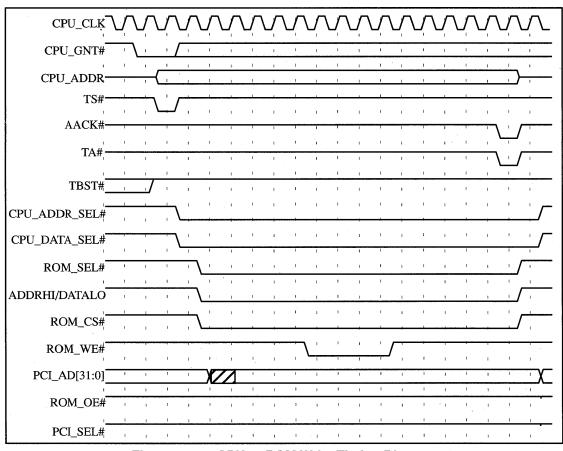

| 5–15                     | CPU to ROM Write Timing Diagram                                        | 92  |

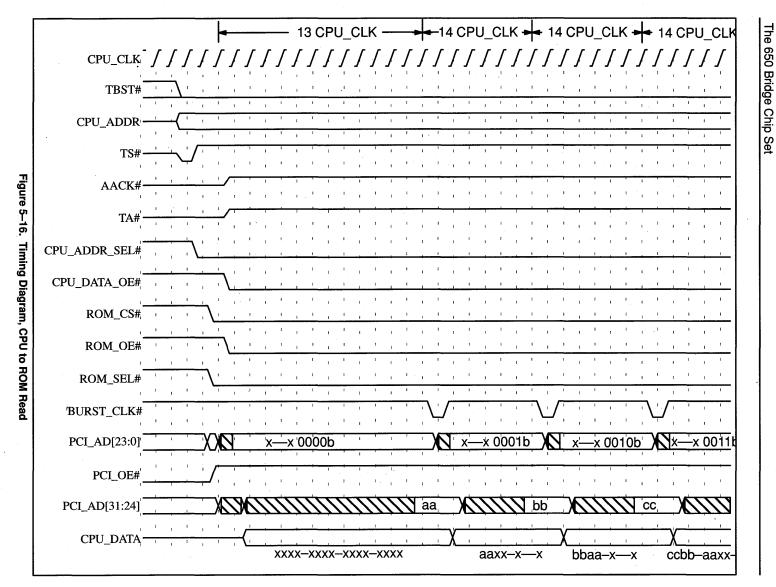

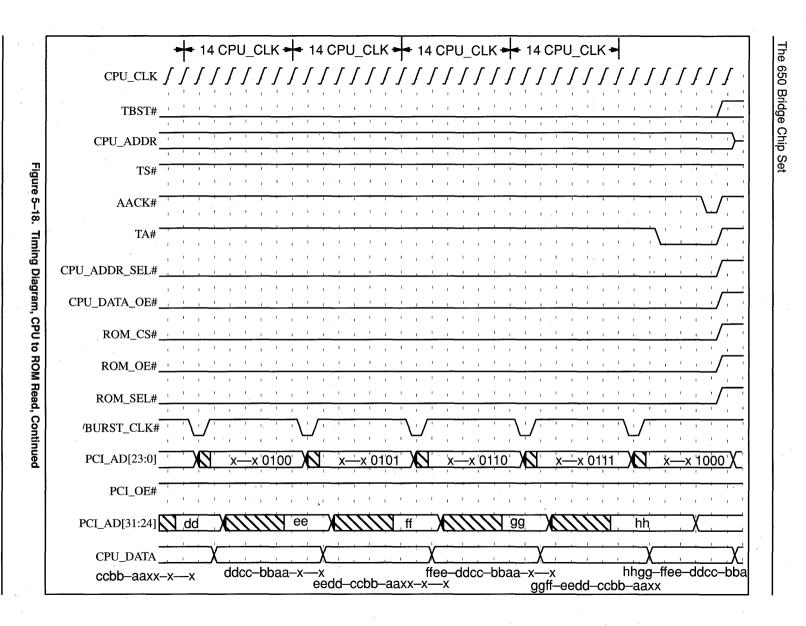

| 5–16                     | Timing Diagram, CPU to ROM Read                                        | 94  |

| 5–17                     | CPU to ROM Read Address and Data Flows                                 | 95  |

| 5–18                     | Timing Diagram, CPU to ROM Read, Continued                             | 96  |

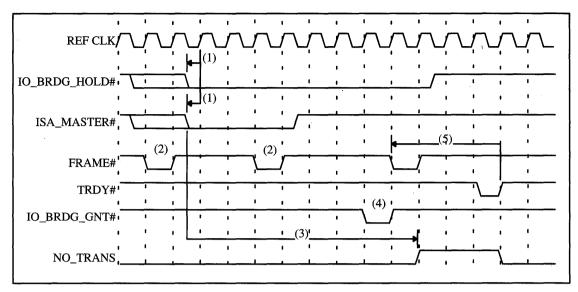

| 5–19                     | ISA Master Signal Timing                                               | 99  |

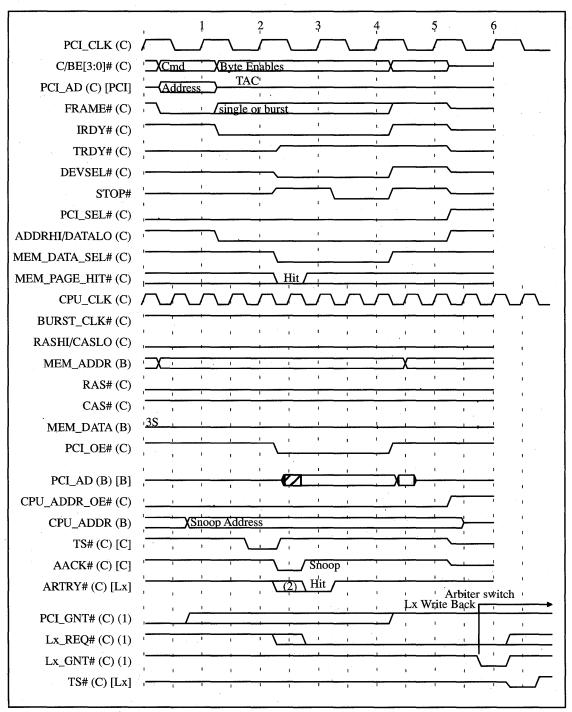

| 5–20                     | PCI to Memory Read – Cache Hit Timing Diagram                          | 104 |

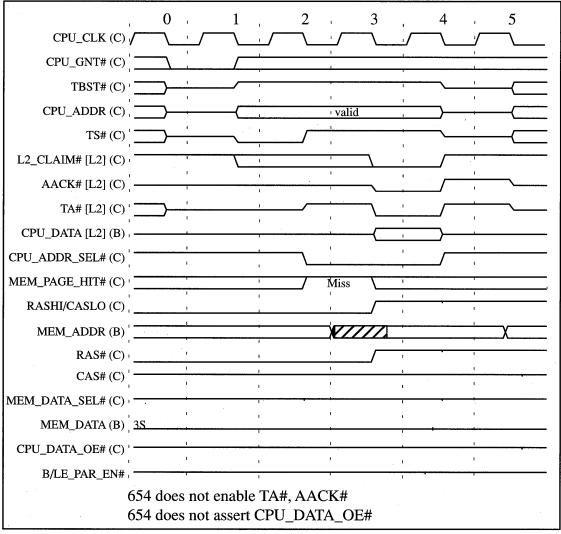

| 5–21                     | CPU to Memory Read – Page Miss, Cache Hit Timing Diagram               | 105 |

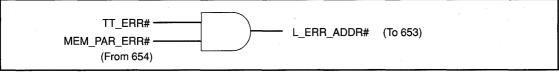

| 5–22 | Error Address External Support Gate                         | 108 |

|------|-------------------------------------------------------------|-----|

| 61   | 653 Package/Pin Electrical Model                            | 114 |

| 6–2  | 654 Package/Pin Electrical Model                            | 115 |

| 6–3  | Pull Up Curves, PCI Drivers, P/L = A.                       | 122 |

| 6-4  | Pull Up Curves, PCI Drivers, P/L = B.                       | 123 |

| 6–5  | Pull Up Curves, PCI Drivers, P/L = C.                       | 123 |

| 6–6  | Pull Down Curves, PCI Drivers, P/L = A, B, and C.           | 124 |

| 6–7  | Pull Down Curves, TTL Driver, IOL = 4mA, P/L = A            | 125 |

| 6–8  | Pull Down Curves, TTL Driver, IOL = 4mA, P/L = B            | 125 |

| 69   | Pull Down Curves, TTL Driver, IOL = 4mA, P/L = C            | 126 |

| 6–10 | Pull Up Curves, TTL Driver, IOL = 4mA, P/L = A, B, and C    | 126 |

| 6—11 | Pull Down Curves, TTL Driver, IOL = 6mA, P/L = A            | 127 |

| 6–12 | Pull Down Curves, TTL Driver, IOL = 6mA, P/L = B            | 127 |

| 6-13 | Pull Down Curves, TTL Driver, IOL = 6mA, P/L = C            | 128 |

| 6–14 | Pull Up Curves, TTL Driver, IOL = 6mA, P/L = A, B, and C    | 128 |

| 6–15 | Pull Down Curves, TTL Driver, IOL = 8mA, P/L = A            | 129 |

| 6–16 | Pull Down Curves, TTL Driver, IOL = 8mA, P/L = B            | 129 |

| 6–17 | Pull Down Curves, TTL Driver, IOL = 8mA, P/L = C            | 130 |

| 6–18 | Pull Up Curves, TTL Driver, IOL = 8mA, P/L = A, B, and C    | 130 |

| 6–19 | Pull Down Curves, TTL Driver, IOL = 12mA, P/L = A           | 131 |

| 6–20 | Pull Down Curves, TTL Driver, IOL = 12mA, P/L = B           | 131 |

| 6-21 | Pull Down Curves, TTL Driver, IOL = 12mA, P/L = C           | 132 |

| 6–22 | Pull Up Curves, TTL Driver, IOL = 12mA, P/L = A, B, and C   | 132 |

| 6–23 | Pull Up Curves, TTL Driver, IOL = 24mA, P/L = A             | 133 |

| 6–24 | Pull Up Curves, TTL Driver, IOL = 24mA, P/L = B             | 133 |

| 6–25 | Pull Up Curves, TTL Driver, IOL = 24mA, P/L = C             | 134 |

| 6–26 | Pull Down Curves, TTL Driver, IOL = 24mA, P/L = A, B, and C | 134 |

| 7–1  | CPU_CLK Cycle Nomenclature                                  | 136 |

| 7–2  | PCI_CLK Cycle Nomenclature                                  | 136 |

| 7–3  | Switching Levels                                            | 137 |

| 7–4  | Signal Timing Conventions                                   | 139 |

| 7–5  |                                                             | 140 |

| 7–6  |                                                             | 141 |

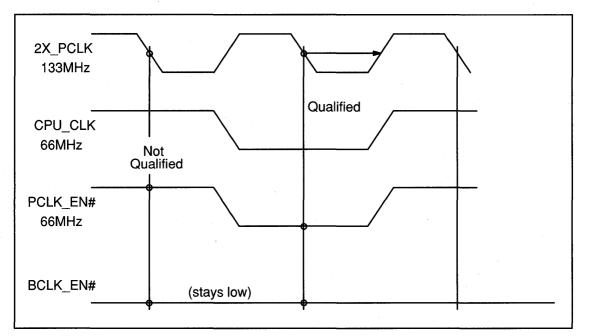

| 77   | CPU_CLK Phase Relationships at 66MHz                        | 141 |

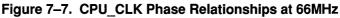

| 78   | CPU_CLK Phase Relationships at 33MHz                        | 142 |

| 7–9  | Timing Diagram, CPU_CLK to PCI_CLK Skew, 2:1 Mode           | 143 |

| 7–10 | Timing Diagram, CPU_CLK to PCI_CLK Skew, 1:1 Mode           | 143 |

| 7–11 | Timing of PCI_PAR                                           | 152 |

| 7–12 | PCI Bus Master Transaction—Address Latch Operation          | 159 |

| 7–13 | CPU to PCI Read—PCI Data Latch Operation                    | 159 |

| 7–14 | CPU to PCI Write—PCI Address/Data MUX                       | 159 |

| 7–15 | CPU To Memory Read – Single, Page Hit, XCAS=1               | 161 |

| 7–16 | CPU To Memory Read – Single, Page Hit, XCAS=0               | 162 |

| 7–17 | CPU To Memory Read – Single, Page Miss, XCAS=1       | 163 |

|------|------------------------------------------------------|-----|

| 7–18 | CPU To Memory Read – Single, Page Miss, XCAS=0       | 164 |

| 7–19 | CPU To Memory Read – Burst, Page Hit, XCAS=1         | 165 |

| 7–20 | CPU To Memory Read – Burst, Page Hit, XCAS=0         | 166 |

| 7–21 | CPU To Memory Read – Burst, Page Miss, XCAS=1        | 167 |

| 7–22 | CPU To Memory Read – Burst, Page Miss, XCAS=0        | 168 |

| 7–23 | CPU To Memory Read – Single, Page Hit, L2 Cache Hit  | 169 |

| 7–24 | CPU To Memory Read – Single, Page Miss, L2 Cache Hit | 170 |

| 7–25 | CPU To Memory Read – Burst, Page Hit, L2 Cache Hit   | 171 |

| 7–26 | CPU To Memory Read – Burst, Page Miss, L2 Cache Hit  | 172 |

| 7–27 | CPU To Memory Write – Single, Page Hit, XCAS=1       | 173 |

| 7–28 | CPU To Memory Write – Single, Page Hit, XCAS=0       | 174 |

| 7–29 | CPU To Memory Write – Single, Page Miss, XCAS=1      | 175 |

| 7–30 | CPU To Memory Write – Single, Page Miss, XCAS=0      | 176 |

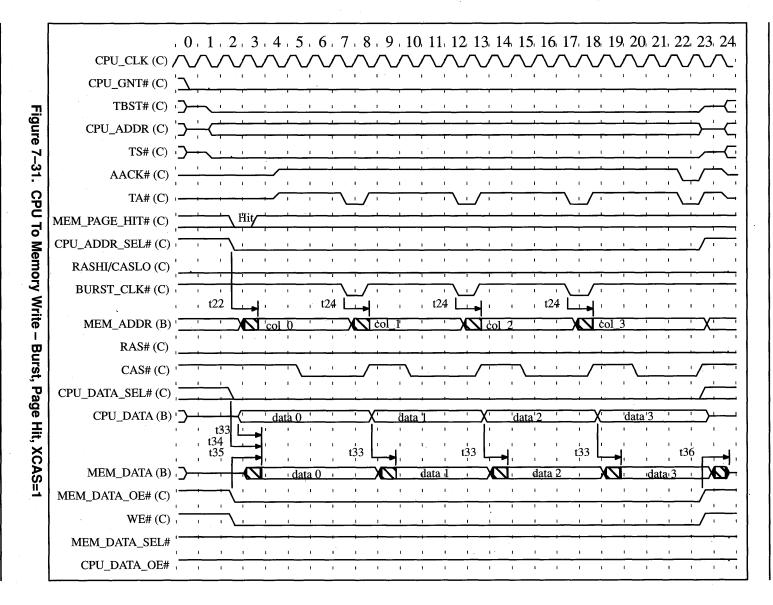

| 7–31 | CPU To Memory Write – Burst, Page Hit, XCAS=1        | 177 |

| 7–32 | CPU To Memory Write – Burst, Page Hit, XCAS=0        | 178 |

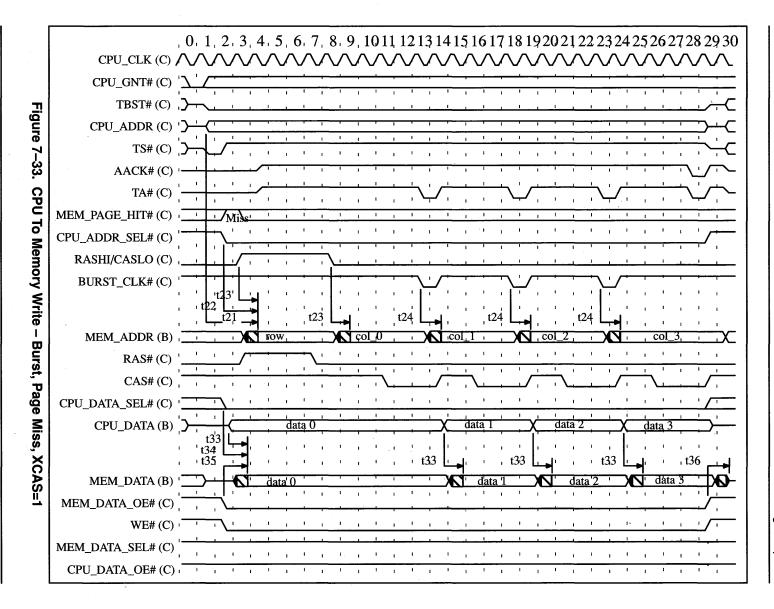

| 7–33 | CPU To Memory Write – Burst, Page Miss, XCAS=1       | 179 |

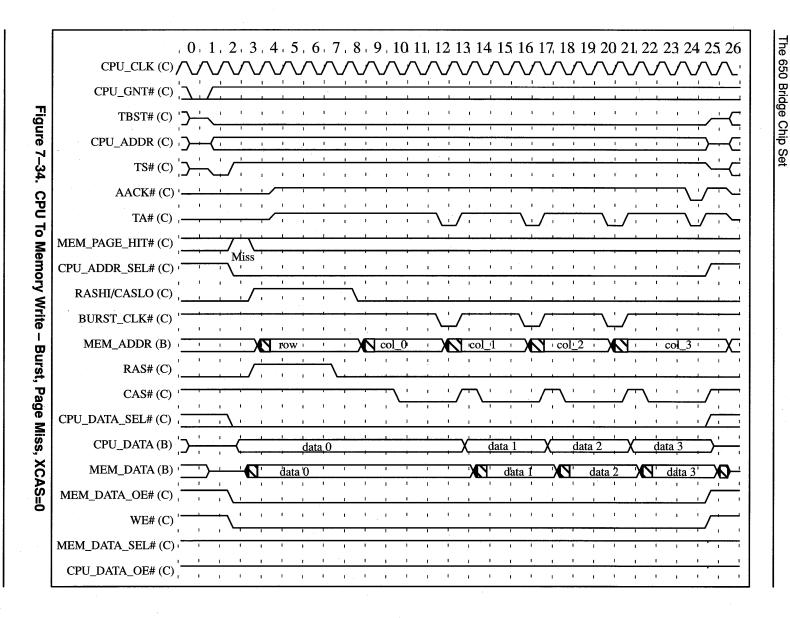

| 7–34 | CPU To Memory Write – Burst, Page Miss, XCAS=0       | 180 |

| 7–35 | PCI To Memory Read – Single, Page Hit                | 181 |

| 7–36 | PCI To Memory Read – Single, Page Miss               | 182 |

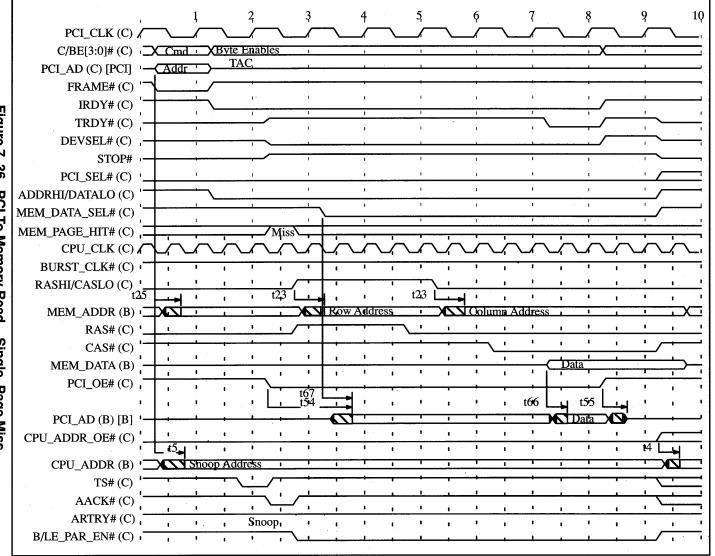

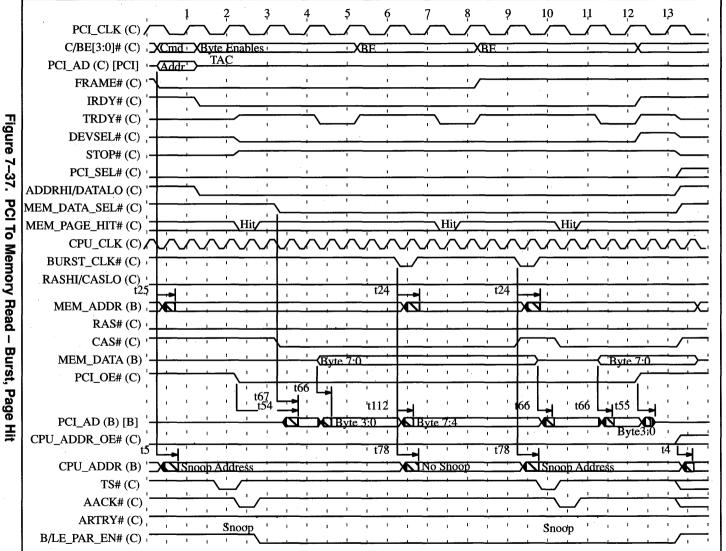

| 7–37 | PCI To Memory Read – Burst, Page Hit                 | 183 |

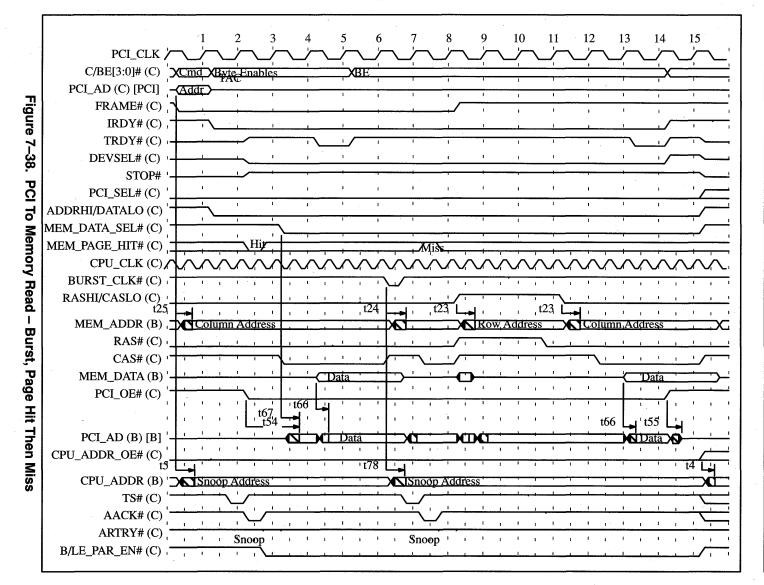

| 7–38 | PCI To Memory Read – Burst, Page Hit Then Miss       | 184 |

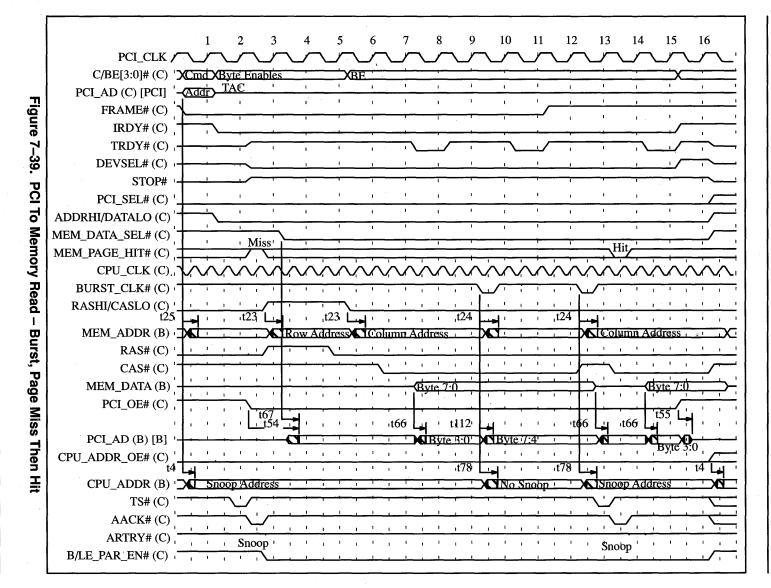

| 7–39 | PCI To Memory Read – Burst, Page Miss Then Hit       | 185 |

| 7–40 | PCI To Memory Read – Page Hit, Cache Hit             | 186 |

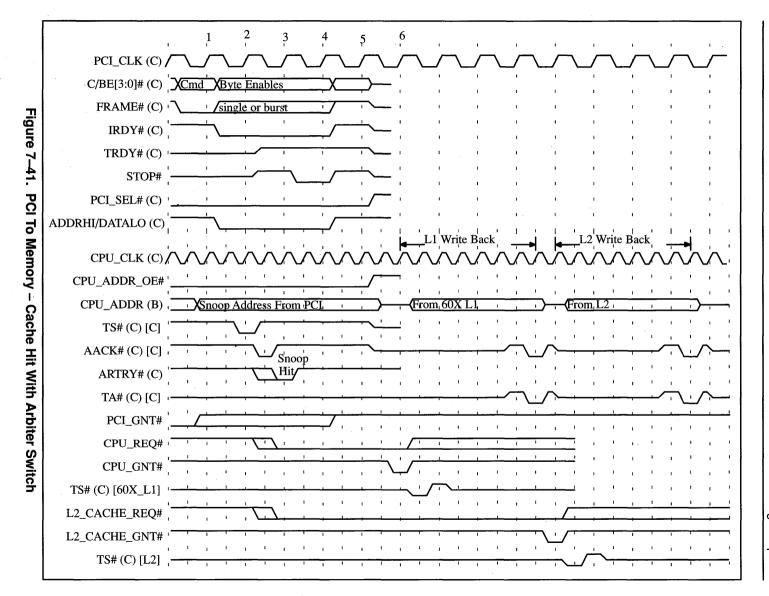

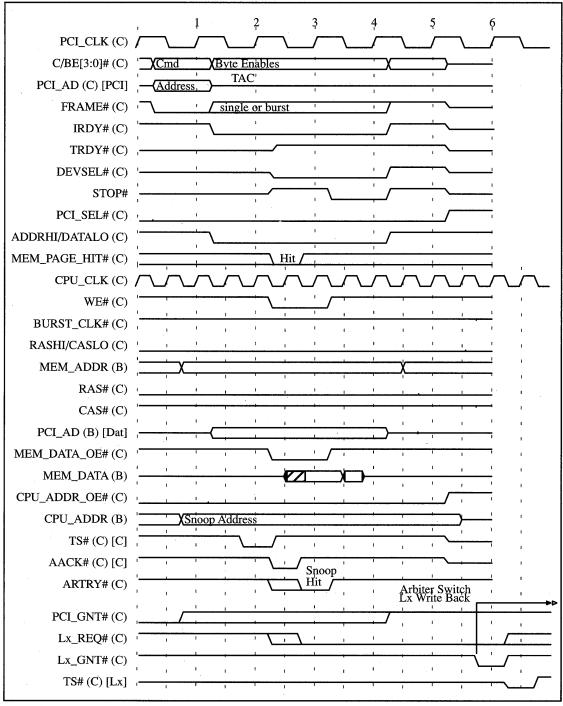

| 7–41 | PCI To Memory – Cache Hit With Arbiter Switch        | 187 |

| 7–42 | PCI To Memory Write – Single, Page Hit               | 188 |

| 7–43 | PCI To Memory Write – Single, Page Miss              | 189 |

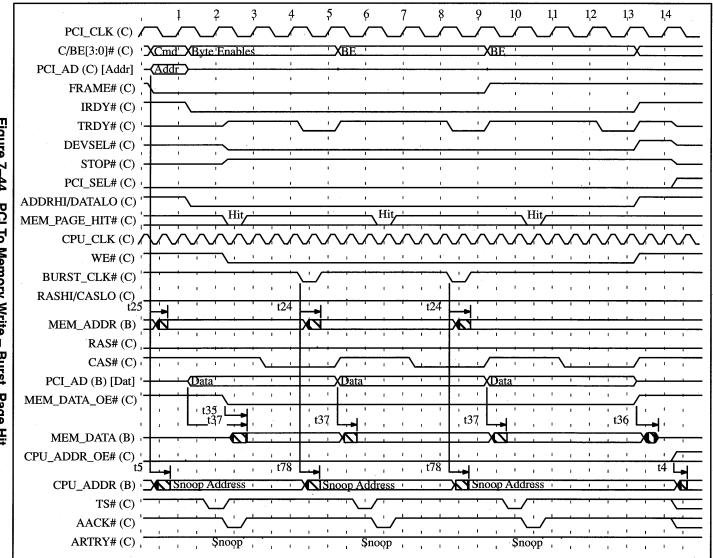

| 7–44 | PCI To Memory Write – Burst, Page Hit                | 190 |

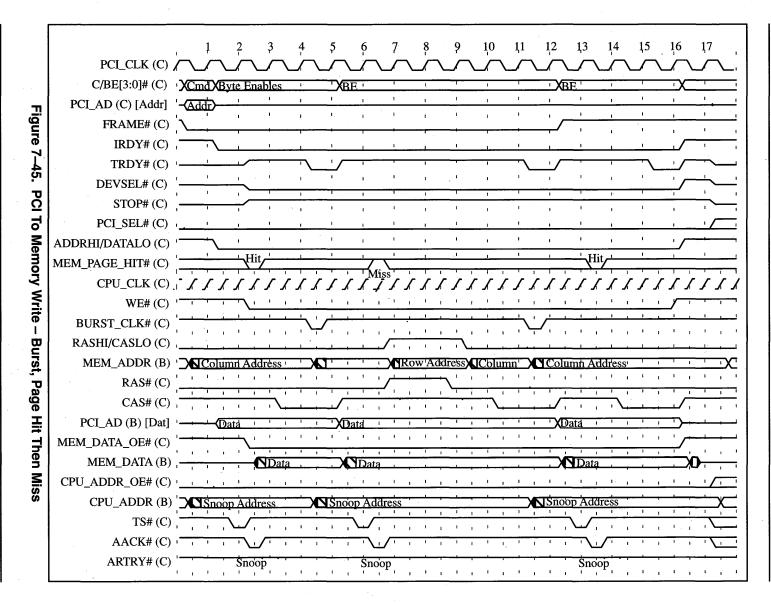

| 7–45 | PCI To Memory Write – Burst, Page Hit Then Miss      | 191 |

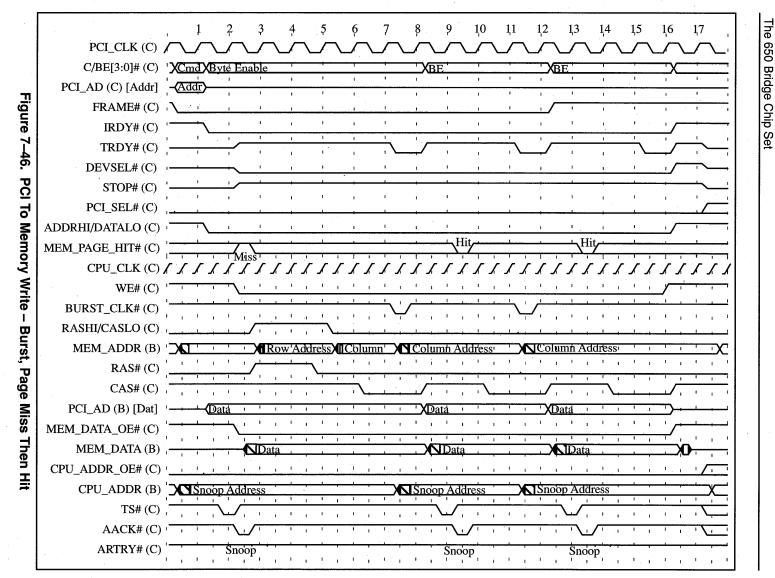

| 7–46 | PCI To Memory Write – Burst, Page Miss Then Hit      | 192 |

| 7–47 | PCI To Memory Write – Page Hit, Cache Hit            | 193 |

| 7–48 | PCI To Memory Write – Page Miss, Cache Hit           | 194 |

| 7–49 | CPU To PCI Write – XADIO=0                           | 195 |

| 7–50 | CPU To PCI Write – XADIO=0, Fast PCI Target Response | 196 |

| 7–51 | CPU To PCI Write – XADIO=0, Offbeat TS#              | 197 |

| 7–52 | CPU To PCI Write – XADIO=1                           | 198 |

| 7–53 | CPU To PCI Write – XADIO=1, Target Retry             | 199 |

| 7–54 | CPU To PCI Read                                      | 200 |

| 7–55 | CPU To PCI Read – Target Retry                       | 201 |

| 9—1  | 653 Buffer Quad Flat Pack Component Detail           | 235 |

| 9–2  | 653 Buffer Quad Flat Pack Component Footprint        | 236 |

| 9–3  | 160-Pin Flat Pack                                    | 237 |

| 9–4  | 160-Pin Flat Pack Pad Locations                      | 238 |

|      |                                                      |     |

| C–1  | 653 Buffer Pin Attachments                                     | 266 |

|------|----------------------------------------------------------------|-----|

| C–2  | 653 Buffer Address Flow Functional Diagram                     | 272 |

| С–3  | 653 Buffer Data Flow Functional Diagram                        | 273 |

| C–4  | Non-Contiguous PCI I/O Address Transformation                  | 275 |

| C–5  | 60X to ROM PCI_AD Flow                                         | 276 |

| C–6  | PCI_AD Transceivers                                            | 281 |

| C–7  | PCI Address Latch                                              | 281 |

| C–8  | PCI Burst Counter                                              | 282 |

| C9   | Combination Latch/Counter—PCI Burst Counter                    | 283 |

| C–10 | Latch/Counter Flow Diagram—PCI Burst Counter                   | 283 |

| C–11 | 60X CPU Address Bus Transceivers                               | 284 |

| C–12 | 60X CPU Burst Counter                                          | 285 |

| C–13 | Combination Latch/Counter—CPU Burst Counter                    | 286 |

| C-14 | Latch/Counter Flow Diagram—CPU Burst Counter                   | 287 |

| C–15 | Page Hit Comparator                                            | 287 |

| C–16 | Refresh Counter                                                | 288 |

| C17  | Address Multiplexer                                            | 289 |

| C–18 | 60X CPU To PCI Address Translator                              | 290 |

| C–19 | 60X CPU To PCI Address Translation—PCI/ISA IO                  | 291 |

| C–20 | ROM Read Burst Counter                                         | 292 |

| C–21 | Combination Latch/Counter—ROM Read Burst Counter               | 292 |

| C-22 | Latch/Counter Flow Diagram—ROM Read Burst Counter              | 293 |

| C–23 | PCI Data Latch                                                 | 295 |

| C24  | PCI Data Doubler                                               | 295 |

| C–25 | ROM Data Shift Register                                        | 295 |

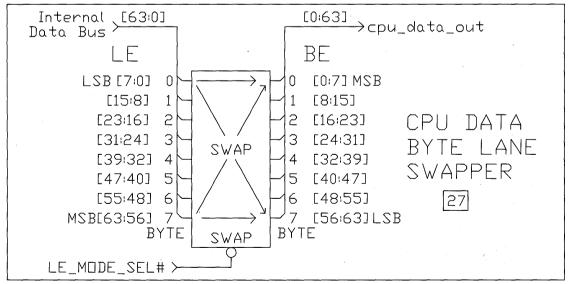

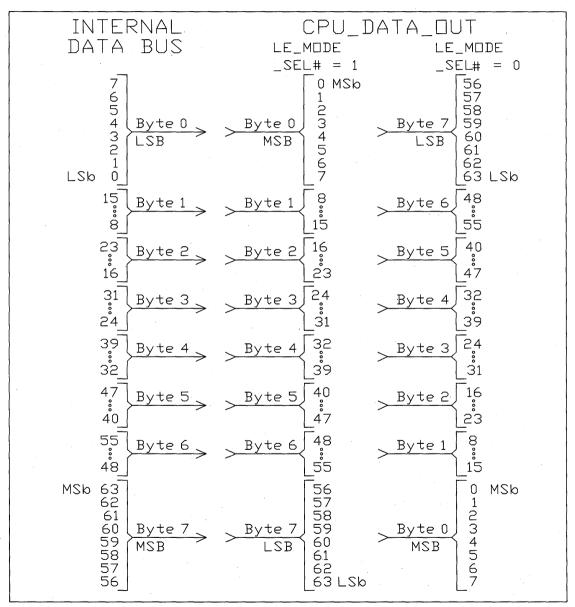

| C–26 | 60X CPU Data Byte Lane Swapper—Input Side                      | 296 |

| C–27 | CPU Data Byte Lane Swapper Operation—Input Side                | 298 |

| C–28 | Data Multiplexer                                               | 299 |

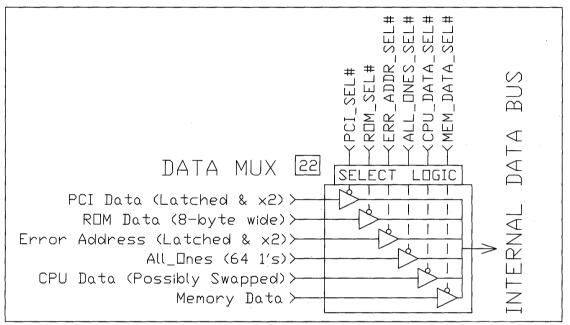

| C–29 | PCI Delay Flop, Data Multiplexer, and Address/Data multiplexer | 300 |

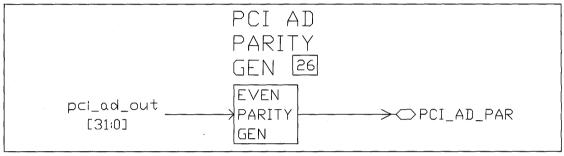

| C–30 | PCI Parity Generator                                           | 301 |

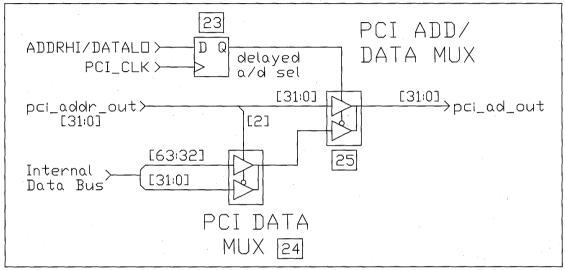

| C–31 | 60X CPU Data Byte Lane Swapper—Output Side                     | 301 |

| C–32 | 60X CPU Data Byte Lane Swapper Operation—Output Side           | 302 |

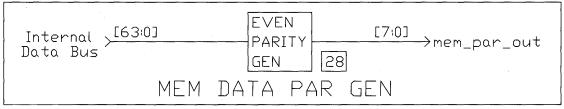

| C–33 | Memory Data Parity Generator                                   | 303 |

| C–34 | Memory Data Parity Checker                                     | 303 |

|      |                                                                |     |

## About This Book

#### Audience:

This book is designed for engineers and system designers who are interested in implementing PowerPC systems with a PCI bus. The material requires an understanding of computer systems at the hardware level.

#### **Document Organization:**

- Section 1 An architectural overview of the 650 Bridge with detailed lists of the features and functions of the 650 Bridge chip set.

- Section 2 A background review of the PCI Bus and 60X CPU.

- Section 3 653 Buffer and 654 Controller pin description tables arranged in functional groups with a separate table for all the interconnections between the two chips.

- Section 4 Theory of operations, including basic timing diagrams.

- Section 5 A functional description of the 650 Bridge.

- Section 6 Electrical characteristics of the chip set.

- Section 7 Detailed timing diagrams and tables.

- Section 8 Alphabetic and numeric pin lists for the 653 Buffer and 654 Controller.

- Section 9 Mechanical drawings.

- Appendix A Initialization and setup requirements.

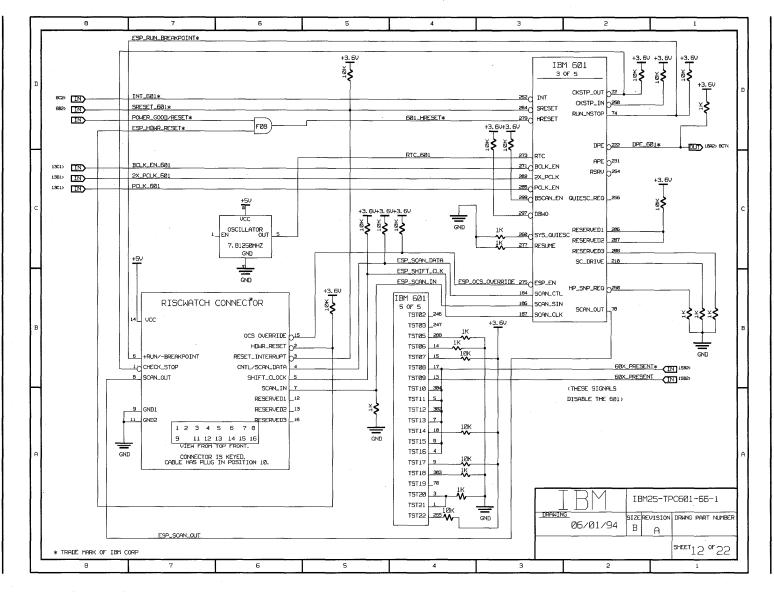

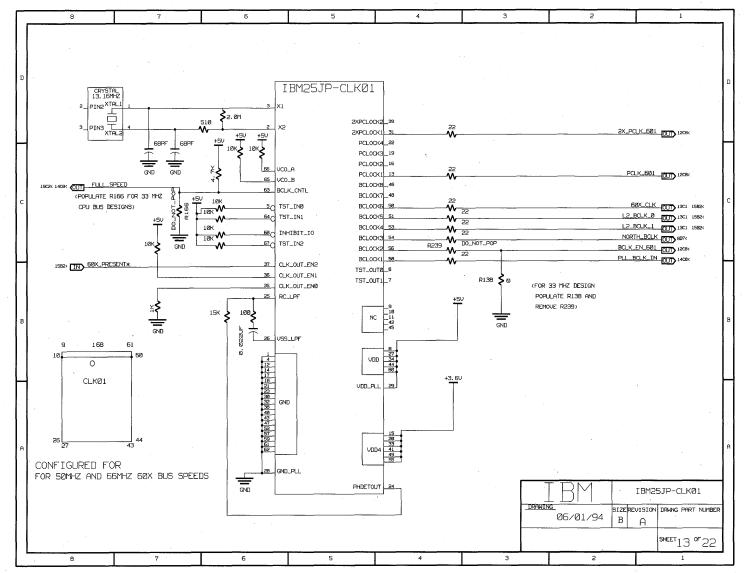

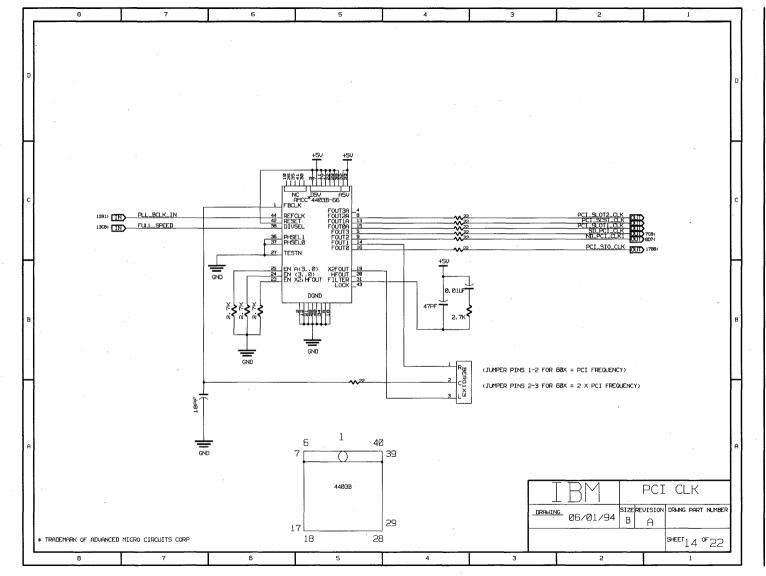

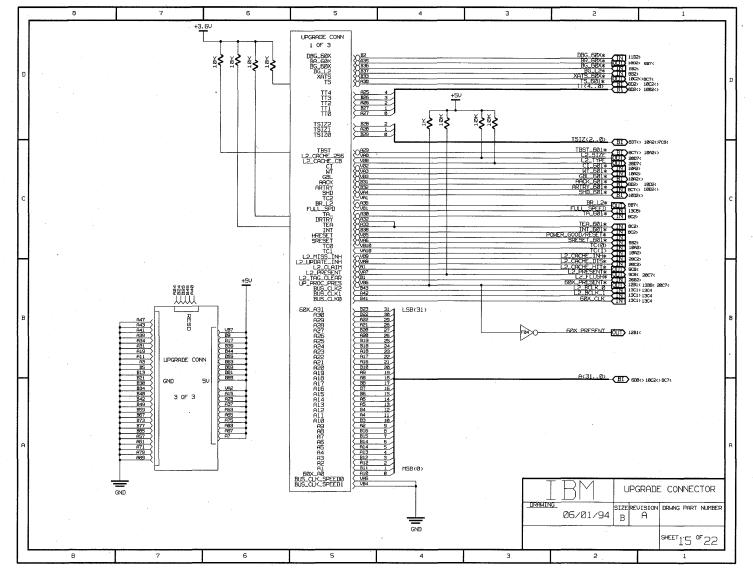

- Appendix B Example implementation schematics.

- Appendix C 653 Buffer details of operation.

Appendix D — Addresses of sales offices.

#### **Reference Material:**

- PowerPC 601 RISC Microprocessor User's Manual, IBM document number MPR601UMU-02

- PowerPC 601 RISC Microprocessor Hardware Specifications, IBM document number MPR601HSU-02

- PCI Local Bus Specification, Revision 2.0, April 30, 1993, available from the PCI SIG

- PCI System Design Guide, Revision 1.0, September 1993, available from the PCI SIG

- 32MB SIMM Engineering Specification, IBM document number MMDS08DSU-00

- 8MB SIMM Engineering Specification, IBM document number MMDS06DSU-00

- PowerPC Reference Platform Specification, Version 1.0, June 20, 1994

- The IBM27-82681-66 PowerPC L2 Cache Controller User's Guide, IBM document number MPRCL2UMU-01

#### **Document Conventions:**

Kilobytes, megabytes, and gigabytes are indicated by a single capital letter after the numeric value. For example, 4K means 4 kilobytes, 8M means 8 megabytes, and 4G means 4 gigabytes.

Fractional time values are identified with the terms ms, us, and ns, which represent milliseconds, microseconds, and nanoseconds respectively.

Hexadecimal values are identified with a lower-case letter h at the end of the value. For example, 001Fh means a 16-bit hexadecimal value of 1F. The letters A through F in the hexadecimal numbering system are always capitalized.

Binary values are identified with a lower-case letter b at the end of the value. For example, 0101b means a 4-bit binary value of 0101 (decimal five).

In identifying ranges of values *from* and *to* are used whenever possible. The range statement *from* 0 to 2M means from zero up to (but not including) two megabytes. The hexadecimal value for the range from 0 to 64K is: 0000h to FFFFh. This method is used in preference to constantly adding a - 1 term to the end of range statements.

The # symbol at the end of a signal name indicates that the active or asserted state of the signal occurs with a low voltage level. When the # symbol is not present after the signal name, the signal is asserted with a high voltage level.

The terms *asserted* and *negated* are used extensively. The term *asserted* indicates that a signal is active, regardless of whether that level is represented by a high or low voltage. The term *negated* means that a signal is inactive. The term *deasserted* is also used to indicate a signal that is negated.

The names of signals are in all upper-case letters. For example, TS#, AACK#, and PCI\_CLK are all signal names.

Signals with more than one pin are identified with square brackets and numbers after the pin names. For example, PCI\_AD[31:0] and TT[0:2] are signals with multiple pins. The # symbol that indicates that a signal is asserted low appears after the square brackets. For example, CAS[7:0]#.

Individual pins within a multi-pin signal group are identified with the pin number within the group in square brackets after the pin name. For example, PCI\_AD[5].

Multiple-pin signals that have the first number larger than the second number (PCI\_AD[31:0] for example) are little-endian signals. Multiple-pin signals that have the first number smaller than the second number (TT[0:2] for example) are big-endian signals.

#### Acronyms and Abbreviations:

In this document, the term 60X CPU refers to the PowerPC 601, 603, and 604 microprocessors.

The term I/O Bridge refers to a PCI master that serves to connect the PCI bus to a PC-standard bus like the ISA, EISA, or MicroChannel buses.

The term RAS refers to the row address select lines of the memory controller.

The term CAS refers to the column address select lines of the memory controller.

The term write-back means the same as copy-back in reference to a mode of cache operation.

The acronym PIO refers to I/O controller interface operations on the 60X CPU bus.

Figure 1–1. IBM 650 Bridge Chip Set in a Typical System Configuration

#### Section 1 650 Bridge Architectural Overview

The IBM27-82650 PCI Bridge chip set (the 650 Bridge) provides an interface that can connect a PowerPC 60X CPU to high-performance PCI (Peripheral Component Interconnect) devices like graphics, LAN, and SCSI controllers. The PCI bus standard defines an environment for highspeed local bus operations. The 650 Bridge chip set provides the necessary control and communications logic to connect a PowerPC 60X CPU to PCI-compliant devices through the PCI bus.

The 650 Bridge chip set is comprised of the IBM27-82653 Address and Data Buffer (the 653 Buffer) and the IBM27-82654 PCI and Memory Controller (the 654 Controller). The 650 Bridge supports the PowerPC 601<sup>™</sup>, PowerPC 603<sup>™</sup>, and PowerPC 604<sup>™</sup> microprocessor chips. Within this document, the three microprocessor chips (601, 603, and 604) are referred to generically as the 60X CPU. The 650 Bridge supports both the L1 memory cache of the 60X CPU and an optional L2 cache. Either cache can use write-through or write-back modes of operation.

Local bus standards like PCI and the VL-Bus have evolved to answer the need for higher performance I/O operations on microcomputer systems. The 650 Bridge provides an interface mechanism between PowerPC CPUs and the PCI bus. This interface allows system designers to take advantage of the standard PCI controllers that are available for many I/O applications. Figure 1–1 shows a typical PowerPC to PCI system. The address, data, and control signals from the 60X CPU host bus are connected to the 650 Bridge. An optional L2 (level 2) cache can also be connected to the host bus. (The L1 cache resides in the 60X microprocessor.) The 650 Bridge is connected to the PCI local bus (address/data and control signals) and also to the DRAM system memory and ROM devices. Communication between the 60X CPU and its I/O devices and system memory is managed by the 650 Bridge.

### 1.1 Summary of 650 Bridge Features

This section summarizes the features of the 650 Bridge—including the central arbiter, the memory controller, the PowerPC local bus, the PCI expansion bus, the address translation logic, the L2 cache, the ROM controller, and the interrupt and exception logic.

The 650 Bridge operates from 3.0V to 3.78V, allowing either 3.3V or 3.6V power sources.

#### 1.1.1 60X Microprocessor Support

The 650 Bridge supports the PowerPC 601, 603, and 604 microprocessors as follows:

- PowerPC 601

- Supports all 601 external clocking modes

- Supports CPU bus speed up to 66MHz

- PowerPC 603

- Supports all CPU clock multiplier modes except 1:1

- Supports CPU bus speed up to 66MHz (Without 1:1 mode, 66MHz:66MHz is not allowed, 66MHz:33MHz is allowed, 80MHz:40MHz is allowed.)

- Supports 64-bit mode of the 603 CPU

- PowerPC 604

- Supports all CPU clock multiplier modes

- Supports CPU bus speed up to 66MHz

#### 1.1.2 Central Arbiter

- DRAM refresh support

- Prioritized arbitration among the following devices:

- 1. DRAM refresh (highest priority)

- 2. 60X CPU

- 3. L2 write-back cache

- 4. I/O bridge

- 5. Five PCI masters (priority 5 to 9)

- Support for ISA bus masters when an ISA I/O bridge is installed on the PCI bus

- Operates CPU bus and PCI bus as a single-bus system

- · Implements a fairness algorithm

- Has a 63-count PCI bus latency timer to prevent lockup due to inoperative PCI devices

- During idle periods, the PCI bus grant is parked on the 60X CPU

#### 1.1.3 Memory Controller

- Supports memory operations for the PowerPC Architecture<sup>™</sup>

- Eight RAS outputs, eight CAS outputs, and two write-enable outputs

- The memory is eight-bytes wide (plus eight parity bits)

- Fast page-mode is supported

- Supports industry-standard 70ns SIMMs

- Directly supports 168-pin eight-byte 8M, 16M, and 32M SIMMs

- Supports 72-pin four-byte 4M, 8M, 16M, and 32M SIMMs

- Mixed use of 8M and 32M eight-byte SIMMs

- · Memory configurations available from 8M to 256M

- · Empty SIMM sockets are allowed at any position in the eight socket array

- Provides row-address and column-address multiplexing for SIMMs requiring:

- 10, 11, or 12 row by 9 column

- 10, 11, or 12 row by 10 column

- 11 row by 11 column

- Combined 12 row by 10 column and 11 row by 11 column

- Non-interleaved memory access operation

- Memory refresh address counter

- Auto-increment on every refresh cycle

- Auto-wrap at end of page

- Outputs multiplexed to memory address lines

- Burst-mode memory address generation logic

- 32-byte CPU bursts to and from memory

- Any length PCI burst to and from memory

- Generates even parity, one bit per byte

- · Checks parity eight-bytes wide on all memory reads

- Little-endian and big-endian addressing modes

- ISA master to DRAM access

- Optimized Timing is as follows:

- CPU to memory write hit or read hit at 66MHz—7-5-5-5 (CPU bus cycles)

- CPU to memory write hit or read hit at 50MHz, 40MHz, and 33MHz-6-4-4-4

- PCI to memory read hit at 33MHz—5-3-4-3 (PCI bus cycles)

- PCI to memory write hit at 33MHz-5-4-4-4

- See Table 5–10 for more details on memory timing

#### 1.1.4 PowerPC Local Bus

- 64-bit CPU data bus

- 32-bit CPU address bus

- · CPU can operate in big-endian or little-endian mode

- Logic to swap byte lanes and translate addresses for big-endian and little-endian modes

- Synchronous CPU bus speed support up to 66MHz

- PCI bus clock can be equal to or half the speed of CPU bus clock—up to 33MHz

#### 1.1.5 PCI Expansion Bus

- 650 Bridge chip set (653 Buffer and 654 Controller) presents one load to PCI bus

- PCI bus frequency 20 MHz to 33 MHz (maximum of PCI 2.0 specification)

- PCI bus frequency can be equal to or one-half the frequency of the CPU bus clock

- 32-bit multiplexed PCI address and data path

- Support for I/O Bus Bridge (ISA, EISA, MicroChannel)

- Support for ISA bus master access to system memory when an I/O bridge is installed

- PCI to DRAM access-with L1 and L2 cache snooping

- Supports all 60X to PCI transfers that do not cross a four-byte boundary

#### **Address Translation Logic** 1.1.6

- Support for memory mapping 60X address space into PCI spaces

- PCI I/O reads and writes

- PCI memory reads and writes

- · PCI configuration reads and writes

- PCI interrupt acknowledge reads

- Support for reverse translation of PCI addresses for snoops and PCI to memory access

- Support for contiguous ISA I/O and non-contiguous ISA I/O mappings (non-contiguous I/O allows operating systems to memory-protect 32-byte blocks of ISA I/O space)

- Forces the PCI AD bits[1:0] to 00b during the address phase of all PCI transactions except PCI I/O transactions

- Support for low-order address translation (unmunging) in little-endian mode

- Inputs for translation override

#### 1.1.7 L2 Cache Support

- L2 write-through or write-back cache support

- Handshakes with IBM27-82681-66 PowerPC L2 Cache Controller

- Snoop cycles to CPU generated for PCI reads and writes of system memory

- Parity checking on read cycles

- Allows timing of burst read hits up to 3-1-1-1

#### 1.1.8 System ROM Controller

- · Supports up to 8M of 8-bit ROM, flash, or EPROM connected to PCI\_AD lines

- Conversion buffers support 8-bit to 64-bit conversion

- · Logic for flash write

- Write lock-out support

- Single-beat (one-byte to eight-byte) read cycle

Single-beat (one-byte) write cycle

- Pseudo burst-mode (32-byte) read cycle

- Approximately 1.7us read cycle time at 66MHz

#### Interrupt and Exception Logic 1.1.9

- Interrupt pass-through to CPU

- Non-maskable interrupt (NMI) support

- The following types of errors are reported:

- CPU or PCI system memory read parity errors

- Illegal transfers:

The CPU attempts an illegal size, type, or alignment transfer

A PCI device target aborts to the CPU

A missing or unresponsive PCI device

- A PCI bus hangup condition

- L2 cache parity errors

- · Readable error address register

- Drives CPU data lines to all one-bits on out-of-range memory reads

- PCI configuration cycles return all one-bits when no device responds

Retimes the soft reset input to meet the 60X specifications

### Section 2 The PCI Bus and 60X CPU Background Review

The material in this section reviews the PCI local bus specifications and the 60X CPU features and functions. This material is intended for readers who are not familiar with the PCI specification or the operation of the 60X CPU.

## 2.1 The PCI Local Bus Review

This section provides a review of the operation of the PCI local bus. The PCI local bus standard defines a high-performance, 32-bit or 64-bit local bus with multiplexed address and data lines. The PCI local bus standard has been defined by the PCI SIG (Special Interest Group), a computer-industry standards group. The PCI local bus provides an interconnect mechanism between peripheral controllers, like graphics controllers and SCSI controllers, and host computer systems.

#### 2.1.1 PCI Local Bus References

The *PCI Local Bus Specification, Production Version, Revision 2.0*, dated April 30, 1993 contains the detailed information necessary for a full understanding of the PCI bus standard. The 650 Bridge provides the signals that are necessary to interact with devices that conform with the PCI standard as described in the specification. Implementing a PowerPC to PCI system with the 650 Bridge requires a full understanding of the PCI standard.

#### 2.1.2 PCI Local Bus Overview

The PCI bus can be either a 32-bit or a 64-bit multiplexed address/data bus implementation. The 650 Bridge is a 32-bit implementation. The 32-bit multiplexed address and data lines can encode addresses in the range of 0 to 4G (0000 0000h to FFFF FFFFh). During data phases, the 32-bit bus can transfer four bytes per phase. A PCI bus transaction consists of an address phase followed by one or more data phases.

The PCI bus can operate in single-beat or burst mode. The beginning address of a transfer can be followed by a variable number of consecutive 32-bit data words. Burst data transfer can occur at the rate of 32 bits per PCI bus clock cycle. The maximum PCI clock rate of 33MHz can support up to 132M bytes per second burst transfer rates.

#### 2.1.3 PCI Signals

Table 2–1 shows the standard PCI signals that are interfaced directly with the 650 Bridge chip set. The column labeled PCI Signal Name contains the signal name that is used in the PCI standard document. The column labeled 650 Bridge Signal Name contains the 650 Bridge signal name for the PCI signal. The *PCI Local Bus Specification* document describes all the possible PCI signals.

The # symbol at the end of a signal name indicates that the active or asserted state of the signal occurs with a low voltage level. When the # symbol is not present after the signal name, the signal is asserted with a high voltage level.

The terms *assert* and *negate* are used extensively. The term *assert* indicates that a signal is active, regardless of whether that level is represented by a high or low voltage. The term *negate* means that a signal is inactive. The term *deasserted* is also used to indicate a signal that is negated.

| Family            | PCI<br>Signal Name | 650 Bridge<br>Signal Name | Description                                                                                                                                                                                                                                 |

|-------------------|--------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address/Data      | AD[31:00]          | PCI_AD[31:00]             | Address and data bus, 32 bits multiplexed.                                                                                                                                                                                                  |

|                   | C/BE[3:0]#         | PCI_C/BE[3:0]#            | C (bus command) and BE (byte enable) multiplexed lines.<br>An address phase is a bus command, a data phase is BE.                                                                                                                           |

|                   | PAR                | PCI_PAR                   | Parity bit for PCI_AD and PCI_C/BE# combined, even par-<br>ity bit for the combination of 36 bits.                                                                                                                                          |

| Arbitration       | REQ#               | IO_BRDG_REQ#              | ISA or EISA PCI bus request, input to arbiter.                                                                                                                                                                                              |

|                   | GNT#               | IO_BRDG_GNT#              | ISA or EISA PCI bus grant, output from arbiter.                                                                                                                                                                                             |

|                   | REQ#               | PCI_REQ[1:5]#             | Five PCI bus request lines, input to arbiter.                                                                                                                                                                                               |

|                   | GNT#               | PCI_GNT[1:5]#             | Five PCI bus grant lines, output from arbiter.                                                                                                                                                                                              |

| Interface Control | FRAME#             | PCI_FRAME#                | PCI frame, asserted by the current master to indicate the beginning and duration of a bus access.                                                                                                                                           |

|                   | TRDY#              | PCI_TRDY#                 | PCI target ready, asserted by the target device to indicate its completion of the current data phase of a transaction.                                                                                                                      |

|                   | IRDY#              | PCI_IRDY#                 | PCI initiator ready, asserted by the master device to indi-<br>cate completion of the current data phase of a transaction.<br>When PCI_TRDY# and PCI_IRDY# are asserted on the<br>same bus clock cycle, the current data phase is complete. |

|                   | STOP#              | PCI_STOP#                 | PCI stop, asserted by a target to stop a transaction.                                                                                                                                                                                       |