USER'S MANUAL

# Hitachi Single-chip Microcomputer H8/300L Series Programming Manual

# Hitachi Single-chip Microcomputer H8/300L Series Programming Manual

ADE-602-040

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## Preface

The H8/300L Series of single-chip microcomputers is built around the high-speed H8/300L CPU, with an architecture featuring eight 16-bit (or sixteen 8-bit) general registers and a concise, optimized instruction set.

This manual gives detailed descriptions of the H8/300L instructions. The descriptions apply to all chips in the H8/300L Series. Assembly-language programmers should also read the separate H8/300 Series Cross Assembler User's Manual.

For hardware details, refer to the hardware manual of the specific chip.

# Contents

| Sec | ection 1. CPU 1 |                                                   |    |  |  |  |

|-----|-----------------|---------------------------------------------------|----|--|--|--|

| 1.1 | 1 Overview      |                                                   |    |  |  |  |

|     | 1.1.1 F         | eatures                                           | 1  |  |  |  |

|     | 1.1.2 D         | ata Structure                                     | 2  |  |  |  |

|     | 1.1.3 A         | ddress Space                                      | 4  |  |  |  |

|     | 1.1.4 R         | egister Configuration                             | 5  |  |  |  |

| 1.2 | Registers       | 3                                                 | 6  |  |  |  |

|     | 1.2.1 G         | eneral Registers                                  | 6  |  |  |  |

|     | 1.2.2 C         | ontrol Registers                                  | 6  |  |  |  |

|     | 1.2.3 Ir        | nitial Register Values                            | 7  |  |  |  |

| 1.3 | Instructio      | ons                                               | 8  |  |  |  |

|     | 1.3.1 T         | ypes of Instructions                              | 8  |  |  |  |

|     | 1.3.2 Ir        | nstruction Functions                              | 9  |  |  |  |

|     | 1.3.3 B         | asic Instruction Formats                          | 20 |  |  |  |

|     | 1.3.4 A         | ddressing Modes and Effective Address Calculation | 26 |  |  |  |

|     |                 |                                                   |    |  |  |  |

| Sec | tion 2. I       | nstruction Set                                    | 31 |  |  |  |

| 2.1 | Explanat        | ion Format                                        | 31 |  |  |  |

| 2.2 | Instructio      | ons                                               | 36 |  |  |  |

|     | 2.2.1 (1)       | ADD (add binary) (byte)                           | 36 |  |  |  |

|     | 2.2.1 (2)       | ADD (add binary) (word)                           | 37 |  |  |  |

|     | 2.2.2           | ADDS (add with sign extension)                    | 38 |  |  |  |

|     | 2.2.3           | ADDX (add with extend carry)                      | 39 |  |  |  |

|     | 2.2.4           | AND (AND logical)                                 | 40 |  |  |  |

|     | 2.2.5           | ANDC (AND control register)                       | 41 |  |  |  |

|     | 2.2.6           | BAND (bit AND)                                    | 42 |  |  |  |

|     | 2.2.7           | Bcc (branch conditionally)                        | 43 |  |  |  |

|     | 2.2.8           | BCLR (bit clear)                                  | 46 |  |  |  |

|     | 2.2.9           | BIAND (bit invert AND)                            | 48 |  |  |  |

|     | 2.2.10          | BILD (bit invert load)                            | 49 |  |  |  |

|     | 2.2.11          | BIOR (bit invert inclusive OR)                    | 50 |  |  |  |

|     | 2.2.12          | BIST (bit invert store)                           | 51 |  |  |  |

|     | 2.2.13          | BIXOR (bit invert exclusive OR)                   | 52 |  |  |  |

|     | 2.2.14          | BLD (bit load)                                    | 53 |  |  |  |

|     | 2.2.15          | BNOT (bit NOT)                                    | 54 |  |  |  |

| 2.2.16     | BOR (bit inclusive OR)                 |    |

|------------|----------------------------------------|----|

| 2.2.17     | BSET (bit set)                         |    |

| 2.2.18     | BSR (branch to subroutine)             |    |

| 2.2.19     | BST (bit store)                        | 60 |

| 2.2.20     | BTST (bit test)                        | 61 |

| 2.2.21     | BXOR (bit exclusive OR)                |    |

| 2.2.22 (1) | CMP (compare) (byte)                   |    |

| 2.2.22 (2) | CMP (compare) (word)                   |    |

| 2.2.23     | DAA (decimal adjust add)               |    |

| 2.2.24     | DAS (decimal adjust subtract)          | 68 |

| 2.2.25     | DEC (decrement)                        |    |

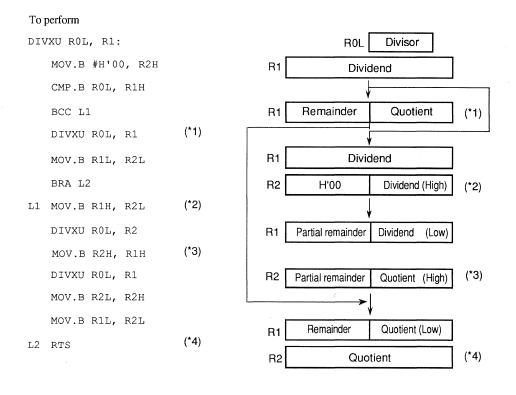

| 2.2.26     | DIVXU (divide extend as unsigned)      |    |

| 2.2.27     | EEPMOV (move data to EEPROM)           |    |

| 2.2.28     | INC (increment)                        |    |

| 2.2.29     | JMP (jump)                             |    |

| 2.2.30     | JSR (jump to subroutine)               |    |

| 2.2.31     | LDC (load to control register)         |    |

| 2.2.32 (1) | MOV (move data) (byte)                 |    |

| 2.2.32 (2) | MOV (move data) (word)                 |    |

| 2.2.32 (3) | MOV (move data) (byte)                 |    |

| 2.2.32 (4) | MOV (move data) (word)                 |    |

| 2.2.32 (5) | MOV (move data) (byte)                 |    |

| 2.2.32 (6) | MOV (move data) (word)                 |    |

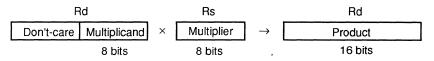

| 2.2.33     | MULXU (multiply extend as unsigned)    |    |

| 2.2.34     | NEG (negate)                           |    |

| 2.2.35     | NOP (no operation)                     |    |

| 2.2.36     | NOT (NOT = logical complement)         |    |

| 2.2.37     | OR (inclusive OR logical)              |    |

| 2.2.38     | ORC (inclusive OR control register)    |    |

| 2.2.39     | POP (pop data)                         |    |

| 2.2.40     | PUSH (push data)                       |    |

| 2.2.41     | ROTL (rotate left)                     |    |

| 2.2.42     | ROTR (rotate right)                    |    |

| 2.2.43     | ROTXL (rotate with extend carry left)  |    |

| 2.2.44     | ROTXR (rotate with extend carry right) |    |

| 2.2.45     | RTE (return from exception)            |    |

| 2.2.46     | RTS (return from subroutine)           |    |

|     | 2.2.47                                            | SHAL (shift arithmetic left)               | 98  |  |  |

|-----|---------------------------------------------------|--------------------------------------------|-----|--|--|

|     | 2.2.48                                            | SHAR (shift arithmetic right)              | 99  |  |  |

|     | 2.2.49                                            | SHLL (shift logical left)                  | 100 |  |  |

|     | 2.2.50                                            | SHLR (shift logical right)                 | 101 |  |  |

|     | 2.2.51                                            | SLEEP (sleep)                              | 102 |  |  |

|     | 2.2.52                                            | STC (store from control register)          | 103 |  |  |

|     | 2.2.53 (1)                                        | SUB (subtract binary) (byte)               | 104 |  |  |

|     | 2.2.53 (2)                                        | SUB (subtract binary) (word)               | 105 |  |  |

|     | 2.2.54                                            | SUBS (subtract with sign extension)        | 106 |  |  |

|     | 2.2.55                                            | SUBX (subtract with extend carry)          | 107 |  |  |

|     | 2.2.56                                            | XOR (exclusive OR logical)                 | 108 |  |  |

|     | 2.2.57                                            | XORC (exclusive OR control register)       | 109 |  |  |

| 2.3 | Operation                                         | Code Map                                   | 110 |  |  |

| 2.4 | List of Inst                                      | tructions                                  | 112 |  |  |

| 2.5 | Number of                                         | Execution States                           | 119 |  |  |

|     |                                                   |                                            |     |  |  |

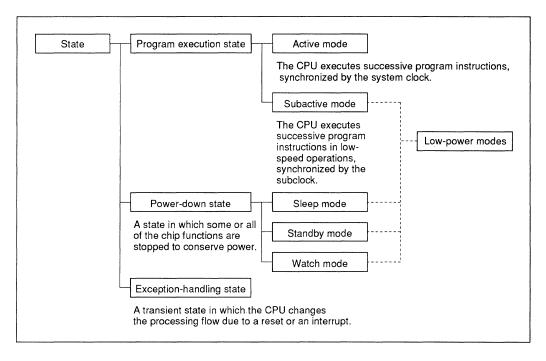

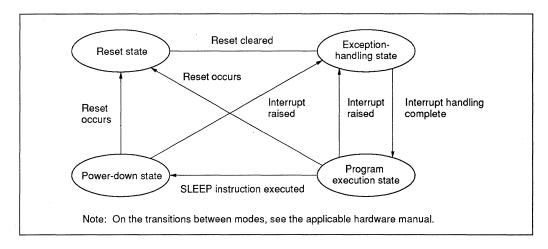

| Sec | tion 3. CI                                        | PU Operation States                        | 127 |  |  |

| 3.1 | Program E                                         | xecution State                             | 128 |  |  |

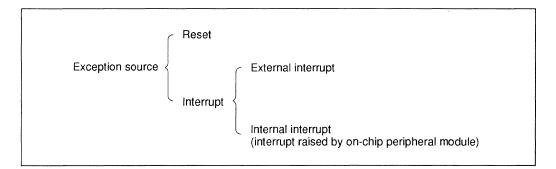

| 3.2 | Exception                                         | Handling States                            | 128 |  |  |

|     | 3.2.1                                             | Types and Priorities of Exception Handling | 128 |  |  |

|     | 3.2.2                                             | Exception Sources and Vector Table         | 129 |  |  |

|     | 3.2.3                                             | Outline of Exception Handling Operation    | 130 |  |  |

| 3.3 | Reset State                                       | 2                                          | 131 |  |  |

| 3.4 | 4 Power-Down State                                |                                            |     |  |  |

|     |                                                   |                                            |     |  |  |

| Sec | tion 4. Ba                                        | asic Operation Timing                      | 133 |  |  |

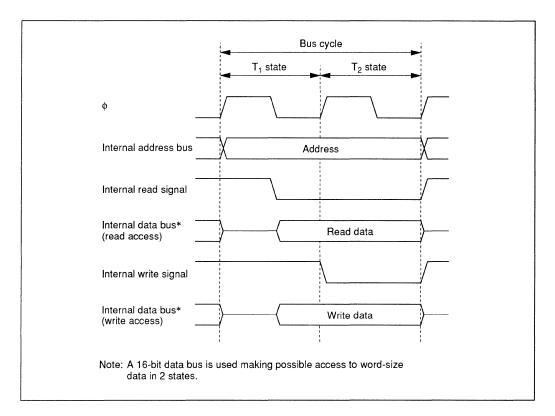

| 4.1 | 1 On-chip Memory (RAM, ROM)                       |                                            |     |  |  |

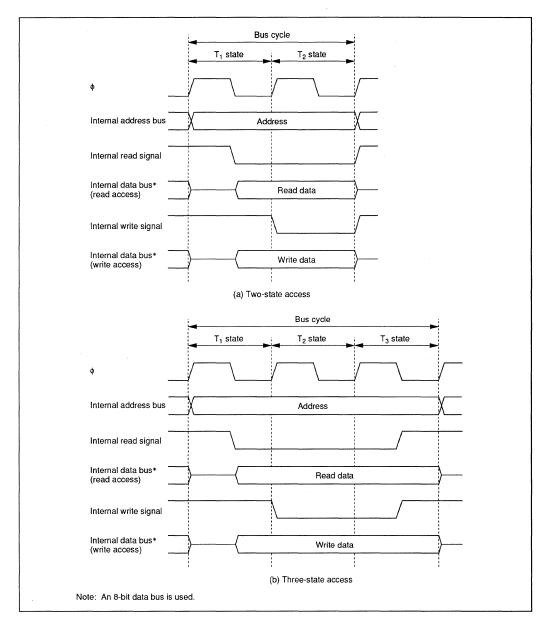

| 4.2 | 2 On-chip Peripheral Modules and External Devices |                                            |     |  |  |

|     |                                                   |                                            |     |  |  |

|     |                                                   |                                            |     |  |  |

## Section 1. CPU

## 1.1 Overview

The H8/300L CPU at the heart of the H8/300L Series features 16 general registers of 8 bits each (or 8 registers of 16-bits each), and a concise, optimized instruction set geared to high-speed operation.

## 1.1.1 Features

The H8/300L CPU has the following features.

General register configuration 16 8-bit registers (can be used as 8 16-bit registers)

55 basic instructions

- Multiply and divide instructions

- Powerful bit manipulation instructions

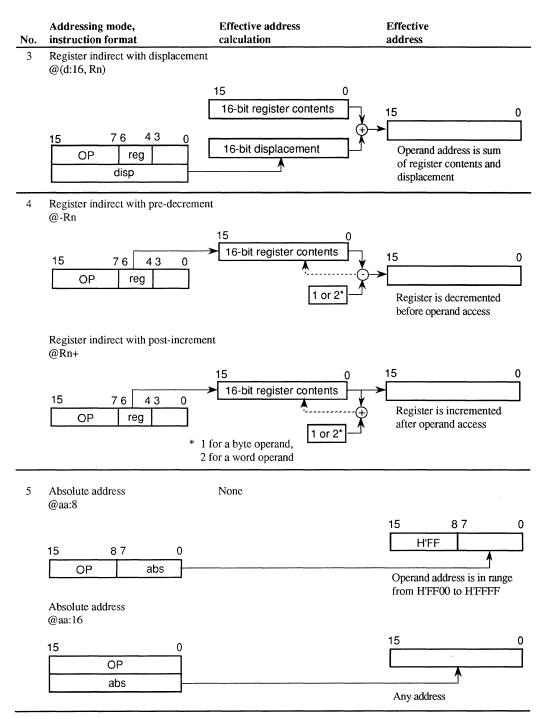

8 addressing modes

- Register direct (Rn)

- Register indirect (@Rn)

- Register indirect with displacement (@(d:16, Rn))

- Register indirect with post-increment/pre-decrement (@Rn+/@-Rn)

- Absolute address (@aa:8/@aa:16)

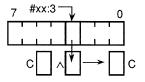

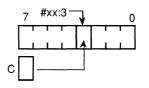

- Immediate (#xx:8/#xx:16)

- Program-counter relative (@(d:8, PC))

- Memory indirect (@@aa:8)

64-kbyte address space

High-speed operation

- All frequently used instructions are executed in 2 to 4 states

- High-speed operating frequency: 5 MHz Add/subtract between 8/16-bit registers: 0.4 μs 8 × 8-bit multiply: 2.8 μs 16 ÷ 8-bit divide: 2.8 μs

Low-power operation

• Transition to power-down state using SLEEP instruction

## 1.1.2 Data Structure

The H8/300L CPU can process 1-bit data, 4-bit (packed BCD) data, 8-bit (byte) data, and 16-bit (word) data.

- Bit manipulation instructions operate on 1-bit data specified as bit n (n = 0, 1, 2, ..., 7) in a byte operand.

- All operational instructions except ADDS and SUBS can operate on byte data.

- The MOV.W, ADD.W, SUB.W, CMP.W, ADDS, SUBS, MULXU (8 bits × 8 bits), and DIVXU (16 bits ÷ 8 bits) instructions operate on word data.

- The DAA and DAS instruction perform decimal arithmetic adjustments on byte data in packed BCD form. Each 4-bit of the byte is treated as a decimal digit.

**Data Structure in General Registers:** Data of all the sizes above can be stored in general registers as shown in figure 1-1.

| Data type                                                                                                                 | Register No. | Data format                      |

|---------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------|

| 1-Bit data                                                                                                                | RnH          | 7 0<br>76543210 Don't-care       |

| 1-Bit data                                                                                                                | RnL          | 7 0<br>Don't-care 76543210       |

| Byte data                                                                                                                 | RnH          | 7 0                              |

| Byte data                                                                                                                 | RnL          | 7 0<br>Don't-care                |

| Word data                                                                                                                 | Rn           |                                  |

| 4-Bit BCD data                                                                                                            | RnH          | 7 43 0<br>Upper Lower Don't-care |

| 4-Bit BCD data                                                                                                            | RnL          | 7 43 0<br>Don't-care Upper Lower |

| RnH:Upper 8 bits of General RegisterRnL:Lower 8 bits of General RegisterMSB:Most Significant BitLSB:Least Significant Bit |              |                                  |

Figure 1-1. Register Data Structure

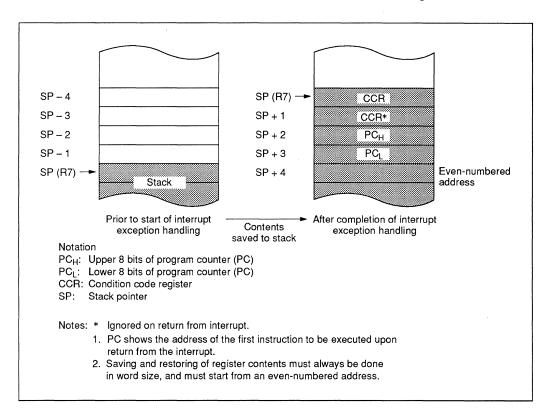

**Data Structure in Memory:** Figure 1-2 shows the structure of data in memory. The H8/300L CPU is able to access word data in memory (MOV.W instruction), but only if the word data starts from an even-numbered address. If an odd address is designated, no address error occurs, but the access is performed starting from the previous even address, with the least significant bit of the address regarded as 0.\* The same applies to instruction codes.

\* Note that the LSIs in the H8/300L Series also contain on-chip peripheral modules for which access in word size is not possible. Details are given in the applicable hardware manual.

| Data type                                                     | Address                     | Data format                   |

|---------------------------------------------------------------|-----------------------------|-------------------------------|

|                                                               |                             | 7 0                           |

| 1-Bit data                                                    | Address n                   | 76543210                      |

| Byte data                                                     | Address n                   |                               |

| Word data                                                     | Even address<br>Odd address | Upper 8 bits     Lower 8 bits |

| Byte data (CCR) on stack                                      | Even address<br>Odd address |                               |

| Word data on stack                                            | Even address<br>Odd address | Upper 8 bits                  |

|                                                               |                             |                               |

| CCR: Condition code register.                                 |                             |                               |

| Note: Word data must begin at an<br>*: Ignored when returned. | even address.               |                               |

Figure 1-2. Memory Data Formats

The stack is always accessed a word at a time. When the CCR is pushed on the stack, two identical copies of the CCR are pushed to make a complete word. When they are returned, the lower byte is ignored.

## 1.1.3 Address Space

The H8/300L CPU supports a 64-Kbyte address space (program code + data). The memory map differs depending on the particular chip in the H8/300L Series and its operating mode. See the applicable hardware manual for details.

## 1.1.4 Register Configuration

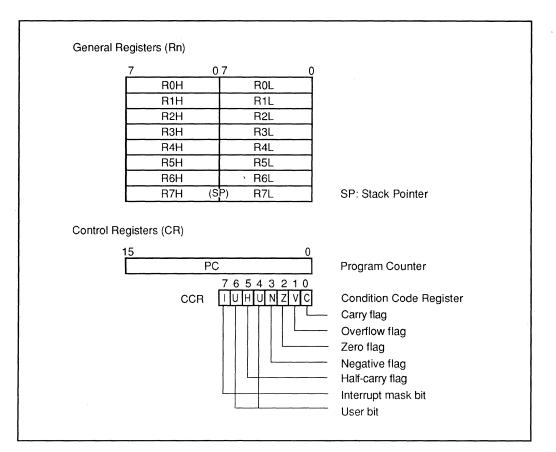

Figure 1-3 shows the register configuration of the H8/300L CPU. There are 16 8-bit general registers (R0H, R0L, ..., R7H, R7L), which can also be accessed as eight 16-bit registers (R0 to R7). There are two control registers: the 16-bit program counter (PC) and the 8-bit condition code register (CCR).

Figure 1-3. CPU Registers

## **1.2 Registers**

#### 1.2.1 General Registers

All the general registers can be used as both data registers and address registers. When used as address registers, the general registers are accessed as 16-bit registers (R0 to R7). When used as data registers, they can be accessed as 16-bit registers (R0 to R7), or the high (R0H to R7H) and low (R0L to R7L) bytes can be accessed separately as 8-bit registers. The register length is determined by the instruction.

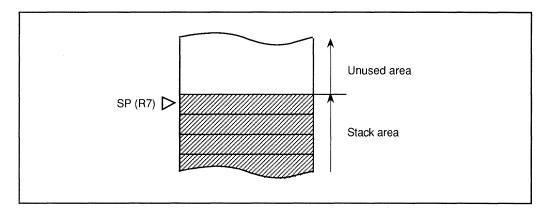

R7 also functions as the stack pointer, used implicitly by hardware in processing interrupts and subroutine calls. In assembly language, the letters SP can be coded as a synonym for R7. As indicated in figure 1-4, R7 (SP) points to the top of the stack.

Figure 1-4. Stack Pointer

#### **1.2.2 Control Registers**

The CPU has a 16-bit program counter (PC) and an 8-bit condition code register (CCR).

(1) **Program Counter (PC):** This 16-bit register indicates the address of the next instruction the CPU will execute. Instructions are fetched by 16-bit (word) access, so the least significant bit of the PC is ignored (always regarded as 0).

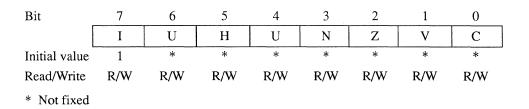

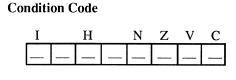

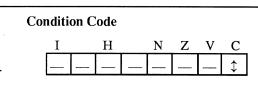

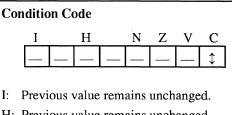

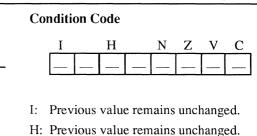

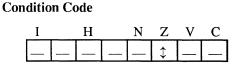

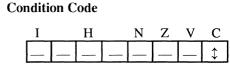

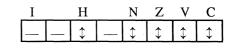

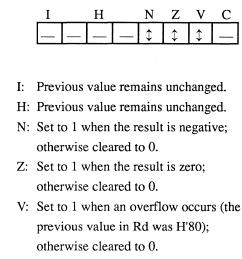

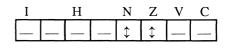

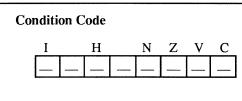

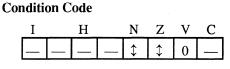

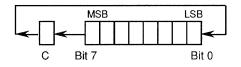

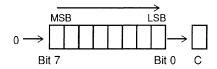

(2) Condition Code Register (CCR): This 8-bit register indicates the internal status of the CPU with an interrupt mask (I) bit and five flag bits: half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags. The two unused bits are available to the user. The bit configuration of the condition code register is shown below.

**Bit 7—Interrupt Mask Bit (I):** When this bit is set to 1, all interrupts except NMI are masked. This bit is set to 1 automatically at the start of interrupt handling.

**Bits 6 and 4—User Bits (U):** These bits can be written and read by software for its own purposes using LDC, STC, ANDC, ORC, and XORC instructions.

**Bit 5—Half-Carry (H):** This bit is used by add, subtract, and compare instructions to indicate a borrow or carry out of bit 3 or bit 11. It is referenced by the decimal adjust instructions.

Bit 3—Negative (N): This bit indicates the value of the most significant bit (sign bit) of the result of an instruction.

Bit 2—Zero (Z): This bit is set to 1 to indicate a zero result and cleared to 0 to indicate a nonzero result.

**Bit 1—Overflow** (V): This bit is set to 1 when an arithmetic overflow occurs, and cleared to 0 at other times.

Bit 0—Carry (C): This bit is used by:

- Add, subtract, and compare instructions, to indicate a carry or borrow at the most significant bit

- Shift and rotate instructions, to store the value shifted out of the most or least significant bit

- Bit manipulation instructions, as a bit accumulator

Note that some instructions involve no flag changes. The flag operations with each instruction are indicated in the individual instruction descriptions that follow in section 2, Instruction Set. CCR is used by LDC, STC, ANDC, ORC, and XORC instructions. The N, Z, V, and C flags are used by the conditional branch instruction (Bcc).

## 1.2.3 Initial Register Values

When the CPU is reset, the program counter (PC) is loaded from the vector table and the interrupt mask bit (I) in CCR is set to 1. The other CCR bits and the general registers are not initialized.

The initial value of the stack pointer (R7) is not fixed. To prevent program crashes the stack pointer should be initialized by software, by the first instruction executed after a reset.

## **1.3 Instructions**

Features:

- The H8/300L CPU has a concise set of 55 instructions.

- A general-register architecture is adopted.

- All instructions are 2 or 4 bytes long.

- Fast multiply/divide instructions and extensive bit manipulation instructions are supported.

- Eight addressing modes are supported.

#### 1.3.1 Types of Instructions

Table 1-1 classifies the H8/300L instructions by type. Section 2, Instruction Set, gives detailed descriptions.

| Function              | Instructions                                | Types |

|-----------------------|---------------------------------------------|-------|

| Data transfer         | MOV, POP*, PUSH*                            | 1     |

| Arithmetic operations | ADD, SUB, ADDX, SUBX, INC, DEC, ADDS, SUBS, | 14    |

|                       | DAA, DAS, MULXU, DIVXU, CMP, NEG            |       |

| Logic operations      | AND, OR, XOR, NOT                           | 4     |

| Shift                 | SHAL, SHAR, SHLL, SHLR, ROTL, ROTR, ROTXL,  | 8     |

|                       | ROTXR                                       |       |

| Bit manipulation      | BSET, BCLR, BNOT, BTST, BAND, BIAND, BOR    | 14    |

|                       | BIOR, BXOR, BIXOR, BLD, BILD, BST, BIST     |       |

| Branch                | Bcc**, JMP, BSR, JSR, RTS                   | 5     |

| System control        | RTE, SLEEP, LDC, STC, ANDC, ORC, XORC, NOP  | 8     |

| Block data transfer   | EEPMOV                                      | 1     |

|                       | Tota                                        | 1 55  |

#### Table 1-1. Instruction Classification

\* POP Rn is equivalent to MOV.W @SP+, Rn.

PUSH Rn is equivalent to MOV.W Rn, @-SP.

\*\* Bcc is a conditional branch instruction in which cc represents a condition.

## **1.3.2 Instruction Functions**

Tables 1-2 to 1-9 give brief descriptions of the instructions in each functional group. The following notation is used.

| Notation                                                                                                                                                                                                                                                                    |                                   |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--|--|--|

| Rd                                                                                                                                                                                                                                                                          | General register (destination)    |  |  |  |

| Rs                                                                                                                                                                                                                                                                          | General register (source)         |  |  |  |

| Rn                                                                                                                                                                                                                                                                          | General register                  |  |  |  |

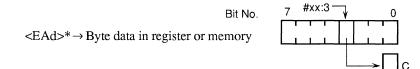

| (EAd)                                                                                                                                                                                                                                                                       | Destination operand               |  |  |  |

| (EAs)                                                                                                                                                                                                                                                                       | Source operand                    |  |  |  |

| CCR                                                                                                                                                                                                                                                                         | Condition code register           |  |  |  |

| N                                                                                                                                                                                                                                                                           | N (negative) bit of CCR           |  |  |  |

| Ζ                                                                                                                                                                                                                                                                           | Z (zero) bit of CCR               |  |  |  |

| Z<br>V                                                                                                                                                                                                                                                                      | V (overflow) bit of CCR           |  |  |  |

| С                                                                                                                                                                                                                                                                           | C (carry) bit of CCR              |  |  |  |

| PC                                                                                                                                                                                                                                                                          | Program counter                   |  |  |  |

| SP                                                                                                                                                                                                                                                                          | Stack pointer (R7)                |  |  |  |

| #Imm                                                                                                                                                                                                                                                                        | Immediate data                    |  |  |  |

| ор                                                                                                                                                                                                                                                                          | Operation field                   |  |  |  |

| disp                                                                                                                                                                                                                                                                        | Displacement                      |  |  |  |

| +                                                                                                                                                                                                                                                                           | Addition                          |  |  |  |

| _                                                                                                                                                                                                                                                                           | Subtraction                       |  |  |  |

| ×                                                                                                                                                                                                                                                                           | Multiplication                    |  |  |  |

| ÷                                                                                                                                                                                                                                                                           | Division                          |  |  |  |

| ^                                                                                                                                                                                                                                                                           | AND logical                       |  |  |  |

| V                                                                                                                                                                                                                                                                           | OR logical                        |  |  |  |

| $\oplus$                                                                                                                                                                                                                                                                    | Exclusive OR logical              |  |  |  |

| $\begin{array}{c} + \\ \hline - \\ \times \\ \hline + \\ \hline \\ + \\ \sim \\ \hline \\ \\ \hline \\ \hline \\ \hline \\ \\ \\ \hline \\ \\ \\ \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ | Move                              |  |  |  |

|                                                                                                                                                                                                                                                                             | Not                               |  |  |  |

| :3, :8,                                                                                                                                                                                                                                                                     | 16 3-bit, 8-bit, or 16-bit length |  |  |  |

## Table 1-2. Data Transfer Instructions

| MOV | B/W | $(E \wedge a) \rightarrow D d \rightarrow (E \wedge d)$             |

|-----|-----|---------------------------------------------------------------------|

|     | •   | $(EAs) \rightarrow Rd, Rs \rightarrow (EAd)$                        |

|     |     | Moves data between two general registers or between a general       |

|     |     | register and memory, or moves immediate data to a general register. |

|     |     | The Rn, @Rn, @(d:16, Rn), @aa:16, #xx:8 or #xx:16, @-Rn, and        |

|     |     | @Rn+ addressing modes are available for byte or word data. The      |

|     |     | @aa:8 addressing mode is available for byte data only.              |

|     |     | The $@-R7$ and $@R7+$ modes require word operands. Do not           |

|     |     | specify byte size for these two modes.                              |

| POP | W   | $(@SP+ \rightarrow Rn)$                                             |

|     |     | Pops a 16-bit general register from the stack.                      |

|     |     | Equivalent to MOV.W @SP+, Rn.                                       |

|     |     | $Rn \rightarrow @-SP$                                               |

|     |     | Pushes a 16-bit general register onto the stack.                    |

|     |     | Equivalent to MOV.W Rn, @-SP.                                       |

\* Size: Operand size

B: Byte

W: Word

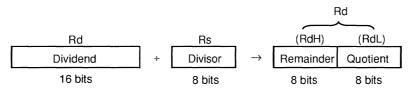

#### Instruction Size\* Function $Rd \pm Rs \rightarrow Rd, Rd + \#Imm \rightarrow Rd$ B/W ADD SUB Performs addition or subtraction on data in two general registers, or addition on immediate data and data in a general register. Immediate data cannot be subtracted from data in a general register. Word data can be added or subtracted only when both words are in general registers. В $Rd \pm Rs \pm C \rightarrow Rd, Rd \pm #Imm \pm C \rightarrow Rd$ ADDX SUBX Performs addition or subtraction with carry or borrow on byte data in two general registers, or addition or subtraction on immediate data and data in a general register. INC В $Rd \pm 1 \rightarrow Rd$ DEC Increments or decrements a general register. ADDS W $Rd \pm 1 \rightarrow Rd, Rd \pm 2 \rightarrow Rd$ SUBS Adds or subtracts immediate data to or from data in a general register. The immediate data must be 1 or 2. Rd decimal adjust $\rightarrow$ Rd В DAA DAS Decimal-adjusts (adjusts to packed BCD) an addition or subtraction result in a general register by referring to the condition code register. $Rd \times Rs \rightarrow Rd$ В MULXU Performs 8-bit $\times$ 8-bit unsigned multiplication on data in two general registers, providing a 16-bit result. DIVXU В $Rd \div Rs \rightarrow Rd$ Performs 16-bit ÷ 8-bit unsigned division on data in two general registers, providing an 8-bit quotient and 8-bit remainder. B/W Rd – #Imm CMP Rd - Rs, Compares data in a general register with data in another general register or with immediate data. Word data can be compared only between two general registers. $0 - Rd \rightarrow Rd$ В NEG Obtains the two's complement (arithmetic complement) of data in a general register.

## **Table 1-3.** Arithmetic Instructions

\* Size: Operand size

B: Byte

W: Word

| Table 1-4. | Logic | Operation | Instructions |

|------------|-------|-----------|--------------|

|------------|-------|-----------|--------------|

| Instruction | Size*                                           | Function                                                          |  |  |  |

|-------------|-------------------------------------------------|-------------------------------------------------------------------|--|--|--|

| AND         | В                                               | $Rd \wedge Rs \rightarrow Rd, Rd \wedge \#Imm \rightarrow Rd$     |  |  |  |

|             |                                                 | Performs a logical AND operation on a general register and        |  |  |  |

|             |                                                 | another general register or immediate data.                       |  |  |  |

| OR          | В                                               | $Rd \lor Rs \to Rd, Rd \lor \#Imm \to Rd$                         |  |  |  |

|             |                                                 | Performs a logical OR operation on a general register and another |  |  |  |

|             |                                                 | general register or immediate data.                               |  |  |  |

| XOR         | В                                               | $Rd \oplus Rs \to Rd,  Rd \oplus \#Imm \to Rd$                    |  |  |  |

|             |                                                 | Performs a logical exclusive OR operation on a general register   |  |  |  |

|             | and another general register or immediate data. |                                                                   |  |  |  |

| NOT         | В                                               | $\neg Rd \rightarrow Rd$                                          |  |  |  |

|             |                                                 | Obtains the one's complement (logical complement) of general      |  |  |  |

|             |                                                 | register contents.                                                |  |  |  |

|             |                                                 |                                                                   |  |  |  |

\* Size: Operand size

B: Byte

| Table | 1-5. | Shift | Instructions |

|-------|------|-------|--------------|

|-------|------|-------|--------------|

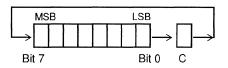

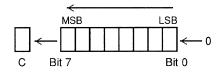

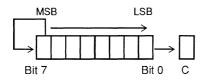

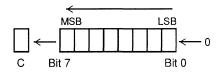

| Instruction | Size* | Function                                                             |  |

|-------------|-------|----------------------------------------------------------------------|--|

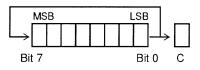

| SHAL        | В     | $Rd shift \rightarrow Rd$                                            |  |

| SHAR        |       | Performs an arithmetic shift operation on general register contents. |  |

| SHLL        | В     | $Rd shift \rightarrow Rd$                                            |  |

| SHLR        | -     | Performs a logical shift operation on general register contents.     |  |

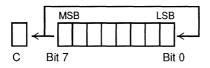

| ROTL        | В     | Rd rotate $\rightarrow$ Rd                                           |  |

| ROTR        |       | Rotates general register contents.                                   |  |

| ROTXL       | В     | Rd rotate through carry $\rightarrow$ Rd                             |  |

| ROTXR       |       | Rotates general register contents through the C (carry) bit.         |  |

\* Size: Operand size

B: Byte

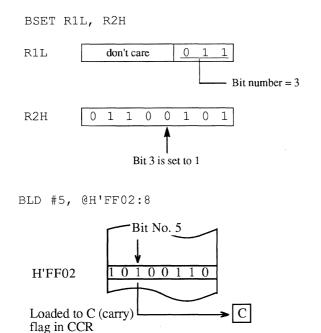

| Instruction | Size* | Function                                                                                                   |

|-------------|-------|------------------------------------------------------------------------------------------------------------|

| BSET        | В     | $1 \rightarrow ( of )$                                                                                     |

|             |       | Sets a specified bit in a general register or memory to 1. The bit is                                      |

|             |       | specified by a bit number, given in 3-bit immediate data or the lower                                      |

|             |       | three bits of a general register.                                                                          |

| BCLR        | В     | $0 \rightarrow (\langle \text{bit-No.} \rangle \text{ of } \langle \text{EAd} \rangle)$                    |

|             |       | Clears a specified bit in a general register or memory to 0. The bit                                       |

|             |       | is specified by a bit number, given in 3-bit immediate data or the lower                                   |

|             |       | three bits of a general register.                                                                          |

| BNOT        | В     | $\neg$ ( <bit-no.> of <ead>) <math>\rightarrow</math> (<bit-no.> of <ead>)</ead></bit-no.></ead></bit-no.> |

|             |       | Inverts a specified bit in a general register or memory. The bit is                                        |

|             |       | specified by a bit number, given in 3-bit immediate data or the lower                                      |

|             |       | three bits of a general register.                                                                          |

| BTST        | В     | $\neg$ ( <bit-no.> of <ead>) <math>\rightarrow</math> Z</ead></bit-no.>                                    |

|             |       | Tests a specified bit in a general register or memory and sets or                                          |

|             |       | clears the Z flag accordingly. The bit is specified by a bit number,                                       |

|             |       | given in 3-bit immediate data or the lower three bits of a general                                         |

|             |       | register.                                                                                                  |

| BAND        | В     | $C \land (\langle bit-No. \rangle of \langle EAd \rangle) \rightarrow C$                                   |

|             |       | ANDs the C flag with a specified bit in a general register or                                              |

|             |       | memory.                                                                                                    |

| BIAND       | В     | $C \land [\neg (\langle bit-No. \rangle of \langle EAd \rangle)] \rightarrow C$                            |

|             |       | ANDs the C flag with the inverse of a specified bit in a general                                           |

|             |       | register or memory.                                                                                        |

|             |       | The bit number is specified by 3-bit immediate data.                                                       |

| BOR         | В     | $C \lor (\langle bit-No. \rangle of \langle EAd \rangle) \rightarrow C$                                    |

|             |       | ORs the C flag with a specified bit in a general register or memory.                                       |

| BIOR        | В     | $C \vee [\neg (\langle bit-No. \rangle of \langle EAd \rangle)] \rightarrow C$                             |

|             |       | ORs the C flag with the inverse of a specified bit in a general                                            |

|             |       | register or memory.                                                                                        |

|             |       | The bit number is specified by 3-bit immediate data.                                                       |

## Table 1-6. Bit Manipulation Instructions

| Instruction | Size* | Function                                                                                |

|-------------|-------|-----------------------------------------------------------------------------------------|

| BXOR        | В     | $C \oplus (\langle bit-No. \rangle \text{ of } \langle EAd \rangle) \rightarrow C$      |

|             |       | Exclusive-ORs the C flag with a specified bit in a general register                     |

|             |       | or memory.                                                                              |

| BIXOR       | В     | $C \oplus [\neg(\langle bit-No. \rangle of \langle EAd \rangle)] \rightarrow C$         |

|             |       | Exclusive-ORs the C flag with the inverse of a specified bit in a                       |

|             |       | general register or memory.                                                             |

|             |       | The bit number is specified by 3-bit immediate data.                                    |

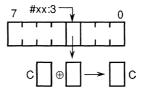

| BLD         | В     | $(\langle \text{bit-No.} \rangle \text{ of } \langle \text{EAd} \rangle) \rightarrow C$ |

|             |       | Copies a specified bit in a general register or memory to the C flag.                   |

| BILD        | В     | $\neg$ ( <bit-no.> of <ead>) <math>\rightarrow</math> C</ead></bit-no.>                 |

|             |       | Copies the inverse of a specified bit in a general register or                          |

|             |       | memory to the C flag.                                                                   |

|             |       | The bit number is specified by 3-bit immediate data.                                    |

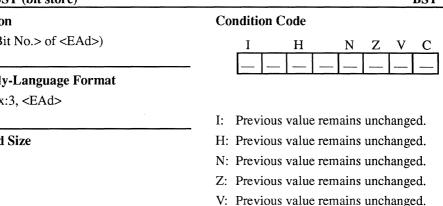

| BST         | В     | $C \rightarrow (\langle bit-No. \rangle of \langle EAd \rangle)$                        |

|             |       | Copies the C flag to a specified bit in a general register or memory.                   |

| BIST        | В     | $\neg C \rightarrow (\langle bit-No. \rangle of \langle EAd \rangle)$                   |

|             |       | Copies the inverse of the C flag to a specified bit in a general                        |

|             |       | register or memory.                                                                     |

|             |       | The bit number is specified by 3-bit immediate data.                                    |

## Table 1-6. Bit Manipulation Instructions (Cont.)

\* Size: Operand size

B: Byte

| Instruction | Size | Function         |                                                                            |                             |  |  |  |  |  |  |

|-------------|------|------------------|----------------------------------------------------------------------------|-----------------------------|--|--|--|--|--|--|

| Всс         |      | Branches if con  | Branches if condition cc is true. The branching conditions are as follows. |                             |  |  |  |  |  |  |

|             |      | follows.         |                                                                            |                             |  |  |  |  |  |  |

|             |      | Mnemonic         | Description                                                                | Condition                   |  |  |  |  |  |  |

|             |      | BRA (BT)         | Always (True)                                                              | Always                      |  |  |  |  |  |  |

|             |      | BRN (BF)         | Never (False)                                                              | Never                       |  |  |  |  |  |  |

|             |      | BHI              | High                                                                       | $C \lor Z = 0$              |  |  |  |  |  |  |

|             |      | BLS              | Low or Same                                                                | $C \lor Z = 1$              |  |  |  |  |  |  |

|             |      | BCC (BHS)        | Carry Clear                                                                | C = 0                       |  |  |  |  |  |  |

|             |      |                  | (High or Same)                                                             |                             |  |  |  |  |  |  |

|             |      | BCS (BLO)        | Carry Set (Low)                                                            | C = 1                       |  |  |  |  |  |  |

|             |      | BNE              | Not Equal                                                                  | $\mathbf{Z} = 0$            |  |  |  |  |  |  |

|             |      | BEQ              | Equal                                                                      | Z = 1                       |  |  |  |  |  |  |

|             |      | BVC              | Overflow Clear                                                             | V = 0                       |  |  |  |  |  |  |

|             |      | BVS              | Overflow Set                                                               | V = 1                       |  |  |  |  |  |  |

|             |      | BPL              | Plus                                                                       | N = 0                       |  |  |  |  |  |  |

|             |      | BMI              | Minus                                                                      | N = 1                       |  |  |  |  |  |  |

|             |      | BGE              | Greater or Equal                                                           | $N \oplus V = 0$            |  |  |  |  |  |  |

|             |      | BLT              | Less Than                                                                  | $N \oplus V = 1$            |  |  |  |  |  |  |

|             |      | BGT              | Greater Than                                                               | $Z \lor (N \oplus V) = 0$   |  |  |  |  |  |  |

|             |      | BLE              | Less or Equal                                                              | $Z \lor (N \oplus V) = 1$   |  |  |  |  |  |  |

|             |      |                  | 1                                                                          | 11                          |  |  |  |  |  |  |

| JMP         |      |                  | ditionally to a specified a                                                |                             |  |  |  |  |  |  |

| BSR         |      |                  | ibroutine at a specified di                                                | splacement from the current |  |  |  |  |  |  |

|             |      | address.         |                                                                            |                             |  |  |  |  |  |  |

| JSR         |      |                  | ibroutine at a specified ad                                                | ldress.                     |  |  |  |  |  |  |

| RTS         |      | Returns from a s | Returns from a subroutine.                                                 |                             |  |  |  |  |  |  |

## **Table 1-7. Branching Instructions**

| Instruction | Size* | Function                                                            |

|-------------|-------|---------------------------------------------------------------------|

| RTE         |       | Returns from an exception handling routine.                         |

| SLEEP       |       | Causes a transition to power-down state.                            |

| LDC         | В     | $Rs \rightarrow CCR, \#Imm \rightarrow CCR$                         |

|             |       | Moves immediate data or general register contents to the condition  |

|             |       | code register.                                                      |

| STC         | В     | $CCR \rightarrow Rd$                                                |

|             |       | Copies the condition code register to a specified general register. |

| ANDC        | В     | $CCR \land \#Imm \rightarrow CCR$                                   |

|             |       | Logically ANDs the condition code register with immediate data.     |

| ORC         | В     | $CCR \lor \#Imm \rightarrow CCR$                                    |

|             |       | Logically ORs the condition code register with immediate data.      |

| XORC        | В     | $CCR \oplus \#Imm \rightarrow CCR$                                  |

|             |       | Logically exclusive-ORs the condition code register with immediate  |

|             |       | data.                                                               |

| NOP         |       | $PC + 2 \rightarrow PC$                                             |

|             |       | Only increments the program counter.                                |

## Table 1-8. System Control Instructions

\* Size: Operand size

B: Byte

## Table 1-9. Block Data Transfer Instruction

| Instruction | Size | Function                                                                  |

|-------------|------|---------------------------------------------------------------------------|

| EEPMOV      |      | if $R4L \neq 0$ then                                                      |

|             |      | repeat $@R5+ \rightarrow @R6+$                                            |

|             |      | $R4L - 1 \rightarrow R4L$                                                 |

|             |      | until $R4L = 0$                                                           |

|             |      | else next;                                                                |

|             |      | Moves a data block according to parameters set in general registers       |

|             |      | R4L, R5, and R6.                                                          |

|             |      | R4L: size of block (bytes)                                                |

|             |      | R5: starting source address                                               |

|             |      | R6: starting destination address                                          |

|             |      | Execution of the next instruction starts as soon as the block transfer is |

|             |      | completed.                                                                |

|             |      | This instruction is for writing to the large-capacity EEPROM provided     |

|             |      | on chip with some models in the H8/300L Series. For details see the       |

|             |      | applicable hardware manual.                                               |

**Notes on Bit Manipulation Instructions:** BSET, BCLR, BNOT, BST, and BIST are readmodify-write instructions. They read a byte of data, modify one bit in the byte, then write the byte back. Care is required when these instructions are applied to registers with write-only bits and to the I/O port registers.

| Se                                                             | equence                                          | Operation                                                  |  |  |  |  |  |

|----------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|

| 1                                                              | Read Read one data byte at the specified address |                                                            |  |  |  |  |  |

| 2                                                              | Modify                                           | Modify one bit in the data byte                            |  |  |  |  |  |

| 3 Write Write the modified data byte back to the specified add |                                                  | Write the modified data byte back to the specified address |  |  |  |  |  |

**Example 1:** BCLR is executed to clear bit 0 in port control register 4 (PCR4) under the following conditions.

| P47:       | Input pin, Low   |

|------------|------------------|

| P46:       | Input pin, High  |

| P45 – P40: | Output pins, Low |

The intended purpose of this BCLR instruction is to switch P40 from output to input.

### **Before Execution of BCLR Instruction**

|              | P47   | P46   | P45    | <b>P4</b> 4 | P43    | P42    | P41    | P40    |

|--------------|-------|-------|--------|-------------|--------|--------|--------|--------|

| Input/output | Input | Input | Output | Output      | Output | Output | Output | Output |

| Pin state    | Low   | High  | Low    | Low         | Low    | Low    | Low    | Low    |

| PCR4         | 0     | 0     | 1      | 1           | 1      | 1      | 1      | 1      |

| PDR4         | 1     | 0     | 0      | 0           | 0      | 0      | 0      | 0      |

## **Execution of BCLR Instruction**

BCLR #0 @PCR4 ; clear bit 0 in PCR4

## After Execution of BCLR Instruction

|              | P47    | P46    | P45    | P44    | P43    | P42    | P41    | P40   |

|--------------|--------|--------|--------|--------|--------|--------|--------|-------|

| Input/output | Output | Input |

| Pin state    | Low    | High   | Low    | Low    | Low    | Low    | Low    | High  |

| PCR4         | 1      | 1      | 1      | 1      | 1      | 1      | 1      | 0     |

| PDR4         | 1      | 0      | 0      | 0      | 0      | 0      | 0      | 0     |

**Explanation:** To execute the BCLR instruction, the CPU begins by reading PCR4. Since PCR4 is a write-only register, it is read as H'FF, even though its true value is H'3F.

Next the CPU clears bit 0 of the read data, changing the value to H'FE.

Finally, the CPU writes this value (H'FE) back to PCR4 to complete the BCLR instruction.

As a result, bit 0 in PCR4 is cleared to 0, making P40 an input pin. In addition, bits 7 and 6 in PCR4 are set to 1, making P47 and P46 output pins.

**Example 2:** BSET is executed to set bit 0 in the port 4 port data register (PDR4) under the following conditions.

P47: Input pin, Low

P46: Input pin, High

P45 – P40: Output pins, Low

The intended purpose of this BSET instruction is to switch the output level at P40 from Low to High.

#### **Before Execution of BSET Instruction**

|              | P47   | P46   | P45    | P44    | P43    | P42    | P41    | P40    |

|--------------|-------|-------|--------|--------|--------|--------|--------|--------|

| Input/output | Input | Input | Output | Output | Output | Output | Output | Output |

| Pin state    | Low   | High  | Low    | Low    | Low    | Low    | Low    | Low    |

| PCR4         | 0     | 0     | 1      | 1      | 1      | 1      | 1      | 1      |

| PDR4         | 1     | 0     | 0      | 0      | 0      | 0      | 0      | 0      |

## **Execution of BSET Instruction**

BSET #0 @PDR4 ; set bit 0 in port 4 port data register

#### After Execution of BSET Instruction

|              | P47   | P46   | P45    | P44    | P43    | P42    | P41    | P40    |

|--------------|-------|-------|--------|--------|--------|--------|--------|--------|

| Input/output | Input | Input | Output | Output | Output | Output | Output | Output |

| Pin state    | Low   | High  | Low    | Low    | Low    | Low    | Low    | High   |

| PCR4         | 0     | 0     | 1      | 1      | 1      | 1      | 1      | 1      |

| PDR4         | 0     | 1     | 0      | 0      | 0      | 0      | 0      | 1      |

**Explanation:** To execute the BSET instruction, the CPU begins by reading port 4. Since P47 and P46 are input pins, the CPU reads the level of these pins directly, not the value in the port data register. It reads P47 as Low (0) and P46 as High (1).

Since P45 to P40 are output pins, for these pins the CPU reads the value in PDR4. The CPU therefore reads the value of port 4 as H'40, although the actual value in PDR4 is H'80.

Next the CPU sets bit 0 of the read data to 1, changing the value to H'41.

Finally, the CPU writes this value (H'41) back to PDR4 to complete the BSET instruction.

As a result, bit 0 in PDR4 is set to 0, switching pin P40 to High output. However, bits 7 and 6 in PDR4 change their values.

## **1.3.3 Basic Instruction Formats**

(1) Format of Data Transfer Instructions

Figure 1-5 shows the format used for data transfer instructions.

| 15 8 7 0                                         | MOV                                               |

|--------------------------------------------------|---------------------------------------------------|

| op r <sub>m</sub> r <sub>n</sub>                 | $Rm \rightarrow Rn$                               |

| 15 8 7 0                                         |                                                   |

| op r <sub>m</sub> r <sub>n</sub>                 | $Rn \rightarrow @Rm$ , or $@Rm \rightarrow Rn$    |

| 15 8 7 0                                         |                                                   |

| op r <sub>m</sub> r <sub>n</sub>                 | @(d:16, Rm) $\rightarrow$ Rn, or                  |

| disp.                                            | $Rn \rightarrow @(d:16, Rm)$                      |

| 15 8 7 0                                         |                                                   |

| op r <sub>m</sub> r <sub>n</sub>                 | @Rm+ $\rightarrow$ Rn, or Rn $\rightarrow$ @-Rm   |

| 15 8 7 0                                         |                                                   |

| op r <sub>n</sub> abs.                           | @aa:8 $\rightarrow$ Rn, or Rn $\rightarrow$ @aa:8 |

| 15 8 7 0                                         |                                                   |

| op r <sub>n</sub>                                | @aa:16 $\rightarrow$ Rn, or                       |

| abs.                                             | $Rn \rightarrow @aa:16$                           |

| 15 8 7 0                                         |                                                   |

| op r <sub>n</sub> IMM                            | #xx:8 → Rn                                        |

|                                                  |                                                   |

| 15 8 7 0                                         |                                                   |

| op r <sub>n</sub>                                | #xx:16 → Rn                                       |

| IMM                                              |                                                   |

| 15 8 7 0                                         |                                                   |

| op r <sub>n</sub>                                | POP, PUSH                                         |

|                                                  |                                                   |

| Notation                                         |                                                   |

| op: Operation field                              |                                                   |

| r <sub>m</sub> , r <sub>n</sub> : Register field |                                                   |

| disp: Displacement                               |                                                   |

| abs.: Absolute address                           |                                                   |

| IMM: Immediate data                              |                                                   |

Figure 1-5. Instruction Format of Data Transfer Instructions

(2) Format of Arithmetic, Logic Operation, and Shift Instructions

Figure 1-6 shows the format used for arithmetic, logic operation, and shift instructions.

| 15                                        |                  | 8 | 7   |    | 0 |                            |

|-------------------------------------------|------------------|---|-----|----|---|----------------------------|

|                                           | ор               |   | ۲m  | rn |   | ADD, SUB, CMP (Rm)         |

|                                           |                  |   |     |    |   | ADDX, SUBX (Rm)            |

| 15                                        |                  | 8 | 7   |    | 0 |                            |

|                                           | ор               |   |     | ٢n |   | ADDS, SUBS, INC, DEC, DAA, |

|                                           |                  |   |     |    |   | DAS, NEG, NOT              |

| 15                                        |                  | 8 | 7   |    | 0 |                            |

|                                           | ор               |   |     | rn |   | MULXU, DIVXU               |

|                                           |                  |   |     |    |   |                            |

| 15                                        |                  | 8 | 7   |    | 0 |                            |

| ор                                        | rn               |   | IMN | Λ  |   | ADD, ADDX, SUBX, CMP       |

|                                           |                  |   |     |    |   | (#xx:8)                    |

| 15                                        |                  | 8 | 7   |    | 0 |                            |

|                                           | ор               |   | rm  | rn |   | AND, OR, XOR (Rm)          |

| 15                                        |                  | 8 | 7   |    | 0 |                            |

| ор                                        | r <sub>n</sub>   | Ť | IMN | Λ  | Ť | AND, OR, XOR (#xx:8)       |

| L                                         |                  |   |     |    | J |                            |

| 15                                        |                  | 8 | 7   |    | 0 |                            |

|                                           | ор               |   |     | rn |   | SHAL, SHAR, SHLL, SHLR,    |

|                                           |                  |   |     |    |   | ROTL, ROTR, ROTXL, ROTXR   |

|                                           |                  |   |     |    |   |                            |

| Notation                                  | On another first |   |     |    |   |                            |

| op:                                       | Operation field  |   |     |    |   |                            |

| r <sub>m</sub> , r <sub>n</sub> :<br>IMM: | Register field   |   |     |    |   |                            |

|                                           | initieulate uato | а |     |    |   |                            |

|                                           |                  |   |     |    |   |                            |

Figure 1-6. Instruction Format of Arithmetic, Logic, and Shift Instructions

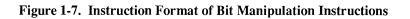

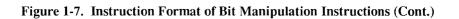

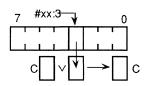

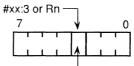

## (3) Format of Bit Manipulation Instructions

Figure 1-7 shows the format used for bit manipulation instructions.

| 15            | 8                                  | 7   |                       | 0              | BSET, BCLR, BNOT, BTST          |

|---------------|------------------------------------|-----|-----------------------|----------------|---------------------------------|

| r             | <br>op                             |     | IMM                   |                |                                 |

|               | OP                                 |     | IIVIIVI               | r <sub>n</sub> | Operand: register direct (Rn)   |

|               |                                    |     |                       |                | Bit No.: immediate (#xx:3)      |

| 15            | 8                                  | 7   |                       | 0              |                                 |

|               | ор                                 |     | r <sub>m</sub>        | r <sub>n</sub> | Operand: register direct (Rn)   |

|               |                                    |     |                       |                | Bit No .: register direct (Rm)  |

| 15            | 8                                  | 7   |                       | 0              |                                 |

|               | ор                                 | Т   | r <sub>n</sub>        | 0000           | Operand: register indirect (@Rn |

|               | ор                                 | -   | IMM                   | 0000           | Bit No.: immediate (#xx:3)      |

|               |                                    |     |                       |                |                                 |

| 15            | 8                                  | 7   |                       | 0              |                                 |

|               | ор                                 | T   | rn                    | 0000           | Operand: register indirect (@Rn |

|               | ор                                 |     | r <sub>m</sub>        | 0000           | Bit No.: register direct (Rm)   |

|               |                                    |     |                       |                |                                 |

| 15            | 8                                  | 7   |                       | 0              |                                 |

|               | ор                                 |     |                       | abs.           | Operand: absolute (@aa:8)       |

| ,             | ор                                 |     | IMM                   | 0000           | Bit No.: immediate (#xx:3)      |

|               | _                                  |     |                       | _              |                                 |

| 15            |                                    | 7   |                       | 0              |                                 |

|               | op                                 |     |                       | abs.           | Operand: absolute (@aa:8)       |

|               | ор                                 |     | r <sub>m</sub>        | 0000           | Bit No.: register direct (Rm)   |

|               |                                    |     |                       |                |                                 |

| 15            | 8                                  | 7   |                       | 0              | BAND, BOR, BXOR, BLD, BST       |

|               | ор                                 |     | IMM                   | r <sub>n</sub> | Operand: register direct (Rn)   |

|               |                                    |     |                       |                | Bit No.: immediate (#xx:3)      |

| 15            | 8                                  | 7   |                       | 0              |                                 |

|               |                                    | T T | r                     |                | Operand: register indirect (@Rn |

|               | op<br>op                           |     | r <sub>n</sub><br>IMM | 0000           |                                 |

|               |                                    |     |                       | 0000           | Bit No.: immediate (#xx:3)      |

| 15            | 8                                  | 7   |                       | 0              |                                 |

|               | ор                                 | Τ   | at                    | DS.            | Operand: absolute (@aa:8)       |

|               | ор                                 |     | IMM                   | 0000           | Bit No .: immediate (#xx:3)     |

| Matellar      |                                    |     |                       |                | 、 <i>、 、</i>                    |

| Notation      |                                    |     |                       |                |                                 |

| op:           | Operation field                    |     |                       |                |                                 |

| rm, rn:       | Register field                     |     |                       |                |                                 |

|               | بممتداء امم مقررا ممما ٨           | ~   |                       |                |                                 |

| abs.:<br>IMM: | Absolute address<br>Immediate data | 5   |                       |                |                                 |

| 15                           | 8                | 7              | 0    | BIAND, BIOR, BIXOR, BILD, BIS   |

|------------------------------|------------------|----------------|------|---------------------------------|

|                              |                  | IMM            | rn   | Operand: register direct (Rn)   |

| ·····                        |                  |                |      | Bit No.: immediate (#xx:3)      |

| 15                           | 8                | 7              | 0    |                                 |

|                              | ор               | r <sub>n</sub> | 0000 | Operand: register indirect (@Ri |

|                              | ор               | IMM            | 0000 | Bit No.: immediate (#xx:3)      |

| 15                           | 8                | 7              | 0    |                                 |

|                              | ор               | а              | bs.  | Operand: absolute (@aa:8)       |

|                              | ор               | IMM            | 0000 | Bit No.: immediate (#xx:3)      |

|                              |                  |                |      |                                 |

| lotation                     | า                |                |      |                                 |

| p:                           | Operation field  |                |      |                                 |

|                              | Register field   |                |      |                                 |

| m, rn:                       |                  |                |      |                                 |

| m, r <sub>n</sub> :<br>abs.: | Absolute address |                |      |                                 |

(4) Format of Branching Instructions

Figure 1-8 shows the format used for branching instructions.

| 15             |                 | 8   | 7   |                |    |     | 0 |              |

|----------------|-----------------|-----|-----|----------------|----|-----|---|--------------|

| ор             | , CC            |     |     | disp           | ). |     |   | Bcc          |

| 15             |                 | 8   | 7   |                |    |     | 0 |              |

|                | ор              |     |     | r <sub>m</sub> | 0  | 00  | 0 | JMP (@Rm)    |

| 15             |                 | 8   | 7   |                |    |     | 0 |              |

|                |                 | 0   |     |                |    |     |   | JMP (@aa:16) |

|                |                 | ab  | S.  |                |    |     |   |              |

| 15             |                 | 8   | 7   |                |    |     | 0 |              |

|                | ор              |     |     | abs            | 5. |     |   | JMP (@@aa:8) |

| 15             |                 | 8   | 7   |                |    |     | 0 |              |

|                | ор              |     |     | dis            | p. |     |   | BSR          |

| 15             |                 | 8   | 7   |                |    |     | 0 |              |

|                | ор              | -   |     | r <sub>m</sub> | 0  | 0 0 | 0 | JSR (@Rm)    |

| 15             |                 | 8   | 7   |                |    |     | 0 |              |

|                |                 | op  |     |                |    |     |   | JSR (@aa:16) |

|                |                 | ab  |     |                |    |     |   | , ,          |

| 15             |                 | 8   | 7   |                |    |     | 0 |              |

| -              | ор              |     |     | abs            |    |     |   | JSR (@@aa:8) |

| 15             |                 | 8   | 7 · |                |    |     | 0 |              |

|                |                 |     | p   |                |    |     |   | RTS          |

|                |                 |     |     |                |    |     |   |              |

| lotatior       | n               |     |     |                |    |     |   |              |

| p:             | Operation field |     |     |                |    |     |   |              |

| c:             | Condition field |     |     |                |    |     |   |              |

| m <sup>:</sup> | Register field  |     |     |                |    |     |   |              |

| isp.:          | Displacement    |     |     |                |    |     |   |              |

| bs.:           | Absolute addre  | ess |     |                |    |     |   |              |

**Figure 1-8. Instruction Format of Branching Instructions**

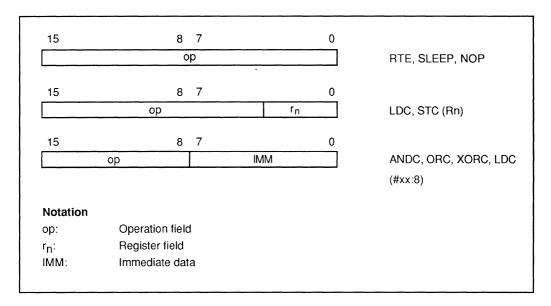

### (5) Format of System Control Instructions

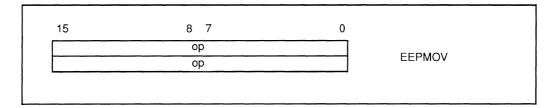

Figure 1-9 shows the format used for system control instructions.

## Figure 1-9. Instruction Format of System Control Instructions

(6) Format of Block Data Transfer Instruction

Figure 1-10 shows the format used for the block data transfer instruction.

## Figure 1-10. Instruction Format of Block Data Transfer Instruction

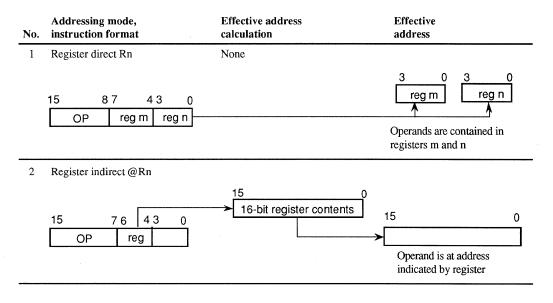

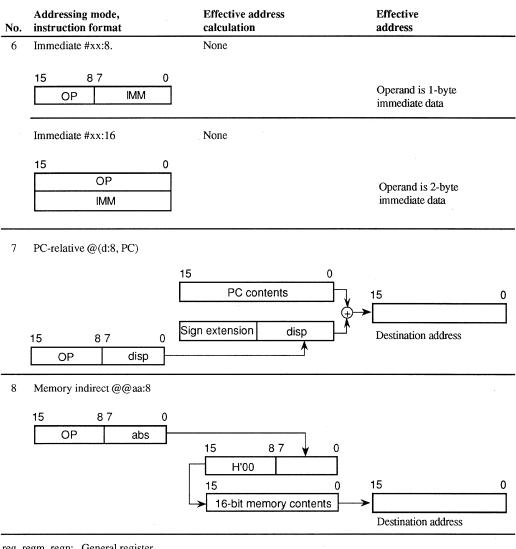

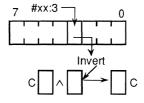

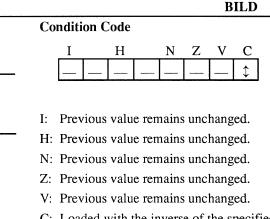

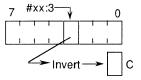

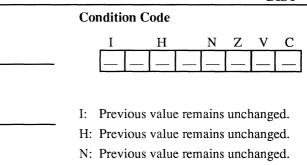

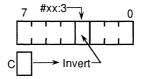

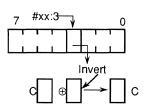

## 1.3.4 Addressing Modes and Effective Address Calculation