# H8/300H Series Programming Manual

HITACHI

# Major Revisions and Additions in this Version

| Page | Item                    |                                                               | Description                        |

|------|-------------------------|---------------------------------------------------------------|------------------------------------|

| P27  | Figure 1-12 Instruction | n Formats                                                     | Figure (4) amended                 |

| P33  | Table 1-6 Effective Ad  | dress Calculation (8)                                         | Table amended                      |

| P51  | 2.2.6 BAND              |                                                               | Notes added                        |

| P58  | 2.2.11 BIOR             | Operand Format and Number of<br>States Required for Execution | Register direct 1st byte amended   |

| P67  | 2.2.18 BSR              |                                                               | Notes description added            |

| P74  | 2.2.22 (3) CMP (L)      | Operand Format and Number of<br>States Required for Execution | Operands amended                   |

| P86  | 2.2.26 (3) DIVXS        |                                                               | Description amended                |

| P87  | DIVXS Example 2         |                                                               | Example 2 added                    |

| P106 | 2.2.33 JSR Cautions     |                                                               | Description added                  |

| P108 | 2.2.34 (1) LDC (B)      |                                                               | Description amended<br>/added      |

| P110 | 2.2.34 (2) LDC (W)      | Operand Format and Number of<br>States Required for Execution | Mnemonic amended                   |

| P114 | 2.2.35 (4) MOV (B)      | Description                                                   | Description amended                |

| P117 | 2.2.35 (5) MOV (W)      | Operand Format and Number of<br>States Required for Execution | Table contents amended             |

| P119 | 2.2.35 (6) MOV (L)      | Operand Format and Number of<br>States Required for Execution | Table contents amended             |

| P123 | 2.2.35 (8) MOV (W)      | Operand Format and Number of<br>States Required for Execution | Table contents amended             |

| P125 | 2.2.35 (9) MOV (L)      | Operand Format and Number of<br>States Required for Execution | Table contents amended             |

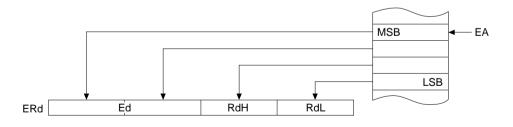

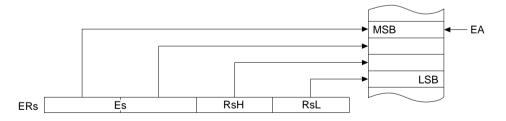

| P129 | 2.2.38 (2) MULXS (W)    |                                                               | Figure amended                     |

| P144 | 2.2.45 (2) POP (L)      |                                                               | Number of execution states amended |

| P146 | 2.2.46 (2) PUSH (L)     |                                                               | Number of execution states amended |

| P160 | 2.2.52 RTS              |                                                               | Figure amended                     |

| P174 | 2.2.58 (1) STC (B)      | Assembly-Language Format                                      | Assembler format amended           |

|      | 2.2.58 (1) STC (B)      | Operand Format and Number of<br>States Required for Execution | Mnemonic amended                   |

| Page          | Item                     |                                                               | Description                                      |

|---------------|--------------------------|---------------------------------------------------------------|--------------------------------------------------|

| P175          | 2.2.58 (2) STC (W)       |                                                               | Instruction amended                              |

|               | 2.2.58 (2) STC (W)       | Assembler Format                                              | Assembler format amended                         |

| P176          | 2.2.58 (2) STC (W)       | Operand Format and Number of<br>States Required for Execution | Mnemonic amended                                 |

| P180          | 2.2.60 SUBS              | Operation                                                     | Operation amended                                |

| P189          | (1) Data Transfer Instru | uctions MOV.W @ERs+,Rd                                        | Operation amended                                |

|               | (1) Data Transfer Instru | uctions MOV.W Rs,@ERd                                         | Operation amended                                |

|               | (1) Data Transfer Instru | uctions MOV.W Rs,@(d:24,ERd)                                  | Number of execution states amended               |

|               | (1) Data Transfer Instru | uctions MOV.L #xx:32,ERd                                      | Operation and number of execution states amended |

| P190          | (1) Data Transfer Instru | uctions MOV.L @ERs+,ERd                                       | Operation amended                                |

|               | (1) Data Transfer Instru | uctions POP.L ERn                                             | Number of execution states amended               |

|               | (1) Data Transfer Instru | uctions PUSH.L ERn                                            | Number of execution states amended               |

| P191          | (2) Arithmetic Operatio  | n Instructions DAA Rd                                         | Condition code amended                           |

| P192          | (2) Arithmetic Operatio  | n Instructions CMP.L #xx:32,ERd                               | Number of execution states amended               |

| P196          | (5) Bit Manipulation Ins | structions                                                    | Table amended                                    |

| P197,<br>P198 | (6) Branch Instructions  |                                                               | Added                                            |

| P198          | (7) System Control Inst  | tructions LDC @ERs,CCR                                        | Operation amended                                |

|               | (7) System Control Inst  | tructions LDC @(d:16,ERs),CCR                                 | Operation amended                                |

|               | (7) System Control Inst  | tructions LDC @(d:24,ERs),CCR                                 | Operation amended                                |

|               | (7) System Control Inst  | tructions LDC @ERs+,CCR                                       | Operation amended                                |

| P204          | Table 2-3 Instruction C  | Codes (4) MOV.B@aa:16,Rd                                      | Instruction format amended                       |

| P231          | Table 2-8 Bus States     | BSR d:16                                                      | Execution order nos.2 to 5 amended               |

| P234,<br>P235 | Table 2-8 Bus States     | POP.W Rn to PUSH.L ERn                                        | Instruction added                                |

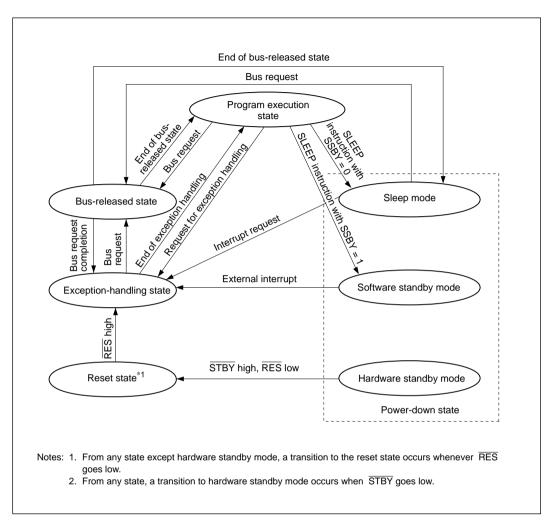

| P240          | Figure 3-2 State Trans   | litions                                                       | Figure amended                                   |

|               |                          |                                                               |                                                  |

# Contents

| Section | on 1 C     | PU                                                | 1  |

|---------|------------|---------------------------------------------------|----|

| 1.1     | Overview   | 7                                                 | 1  |

|         | 1.1.1 Fe   | eatures                                           | 1  |

|         | 1.1.2 D    | ifferences from H8/300 CPU                        | 2  |

| 1.2     | CPU Ope    | erating Modes                                     | 3  |

| 1.3     | Address S  | Space                                             | 7  |

| 1.4     | Register   | Configuration                                     | 8  |

|         | 1.4.1 O    | verview                                           | 8  |

|         | 1.4.2 G    | eneral Registers                                  | 9  |

|         | 1.4.3 C    | ontrol Registers                                  | 10 |

|         | 1.4.4 In   | itial Register Values                             | 11 |

| 1.5     | Data For   | mats                                              | 12 |

|         | 1.5.1 G    | eneral Register Data Formats                      | 12 |

|         | 1.5.2 M    | lemory Data Formats                               | 13 |

| 1.6     | Instructio | n Set                                             | 15 |

|         | 1.6.1 O    | verview                                           | 15 |

|         | 1.6.2 In   | structions and Addressing Modes                   | 16 |

|         | 1.6.3 Ta   | ables of Instructions Classified by Function      | 18 |

|         | 1.6.4 B    | asic Instruction Formats                          | 27 |

|         | 1.6.5 A    | ddressing Modes and Effective Address Calculation | 28 |

|         |            |                                                   |    |

| Section | on 2 Ir    | nstruction Descriptions                           | 35 |

| 2.1     | Tables an  | d Symbols                                         | 35 |

|         | 2.1.1 A    | ssembler Format                                   | 36 |

|         | 2.1.2 O    | peration                                          | 37 |

|         | 2.1.3 C    | ondition Code                                     | 38 |

|         | 2.1.4 In   | struction Format                                  | 38 |

|         | 2.1.5 R    | egister Specification                             | 39 |

|         | 2.1.6 B    | it Data Access in Bit Manipulation Instructions   | 40 |

| 2.2     | Instructio | n Descriptions                                    | 41 |

|         | 2.2.1 (1)  | ADD (B)                                           | 42 |

|         | 2.2.1 (2)  | ADD (W)                                           | 43 |

|         | 2.2.1 (3)  | ADD (L)                                           | 44 |

|         | 2.2.2      | ADDS                                              | 45 |

|         | 2.2.3      | ADDX                                              | 46 |

|         | 2.2.4 (1)  | AND (B)                                           | 47 |

|         | 2.2.4 (2)  | AND (W)                                           | 48 |

|         | 2.2.4 (3)  | AND (L)                                           | 49 |

|         | 2.2.5      | ANDC                                              | 50 |

| 2.2.6      | BAND       | 51  |

|------------|------------|-----|

| 2.2.7      | Bcc        | 52  |

| 2.2.8      | BCLR       | 54  |

| 2.2.9      | BIAND      | 56  |

| 2.2.10     | BILD       | 57  |

| 2.2.11     | BIOR       | 58  |

| 2.2.12     | BIST       | 59  |

| 2.2.13     | BIXOR      | 60  |

| 2.2.14     | BLD        | 61  |

| 2.2.15     | BNOT       | 62  |

| 2.2.16     | BOR        | 64  |

| 2.2.17     | BSET       | 65  |

| 2.2.18     | BSR        | 67  |

| 2.2.19     | BST        | 68  |

| 2.2.20     | BTST       | 69  |

| 2.2.21     | BXOR       | 71  |

| 2.2.22 (1) | CMP (B)    | 72  |

| 2.2.22 (2) | CMP (W)    | 73  |

|            | CMP (L)    | 74  |

| 2.2.23     | DAA        | 75  |

| 2.2.24     | DAS        | 77  |

| 2.2.25 (1) | DEC (B)    | 79  |

| 2.2.25 (2) | DEC (W)    | 80  |

| 2.2.25 (3) | DEC (L)    | 81  |

| 2.2.26(1)  | DIVXS (B)  | 82  |

| 2.2.26 (2) | DIVXS (W)  | 84  |

| 2.2.26 (3) | DIVXS      | 86  |

| 2.2.27 (1) | DIVXU (B)  | 90  |

| 2.2.27 (2) | DIVXU (W)  | 91  |

| 2.2.28(1)  | EEPMOV (B) | 95  |

| 2.2.28 (2) | EEPMOV (W) | 96  |

| 2.2.29 (1) | EXTS (W)   | 98  |

| 2.2.29 (2) | EXTS (L)   | 99  |

| 2.2.30(1)  | EXTU (W)   | 100 |

| 2.2.30 (2) | EXTU (L)   | 101 |

|            | INC (B)    | 102 |

|            | INC (W)    |     |

|            | INC (L)    |     |

| 2.2.32     | JMP        |     |

| 2.2.33     | JSR        | 106 |

| 2.2.34 (1) | LDC (B)    | 108 |

|            |            |     |

| 2.2.34 (2) | LDC (W)   | 109 |

|------------|-----------|-----|

| 2.2.35 (1) | MOV (B)   | 111 |

| 2.2.35 (2) | MOV (W)   | 112 |

| 2.2.35 (3) | MOV (L)   | 113 |

| 2.2.35 (4) | MOV (B)   | 114 |

| 2.2.35 (5) | MOV (W)   | 116 |

| 2.2.35 (6) | MOV (L)   | 118 |

| 2.2.35 (7) | MOV (B)   | 120 |

| 2.2.35 (8) | MOV (W)   | 122 |

| 2.2.35 (9) | MOV (L)   | 124 |

| 2.2.36     | MOVFPE    | 126 |

| 2.2.37     | MOVTPE    | 127 |

| 2.2.38 (1) | MULXS (B) | 128 |

| 2.2.38 (2) | MULXS (W) | 129 |

| 2.2.39 (1) | MULXU (B) | 130 |

| 2.2.39 (2) | MULXU (W) | 131 |

| 2.2.40(1)  | NEG (B)   | 132 |

| 2.2.40 (2) | NEG (W)   | 133 |

| 2.2.40 (3) | NEG (L)   | 134 |

| 2.2.41     | NOP       | 135 |

| 2.2.42 (1) | NOT (B)   | 136 |

| 2.2.42 (2) | NOT (W)   | 137 |

| 2.2.42 (3) | NOT (L)   | 138 |

| 2.2.43 (1) | OR (B)    | 139 |

| 2.2.43 (2) | OR (W)    | 140 |

| 2.2.43 (3) | OR (L)    | 141 |

| 2.2.44     | ORC       | 142 |

| 2.2.45 (1) | POP (W)   | 143 |

| 2.2.45 (2) | POP (L)   | 144 |

| 2.2.46(1)  | PUSH (W)  | 145 |

| 2.2.46(2)  | PUSH (L)  | 146 |

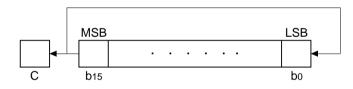

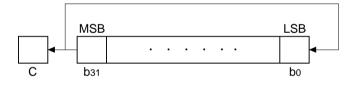

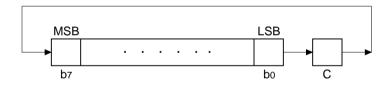

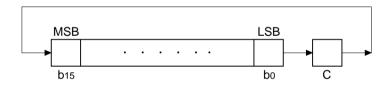

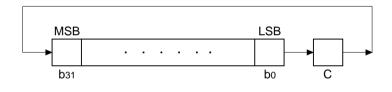

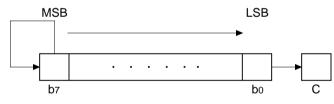

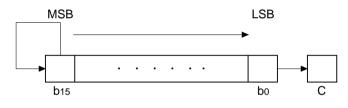

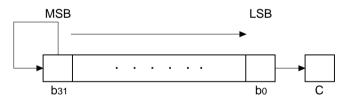

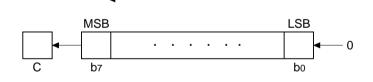

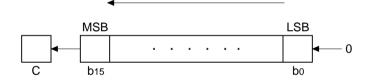

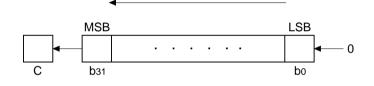

| 2.2.47 (1) | ROTL (B)  | 147 |

| 2.2.47 (2) | ROTL (W)  | 148 |

| • •        | ROTL (L)  |     |

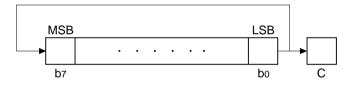

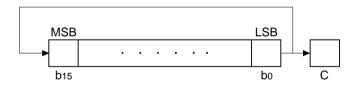

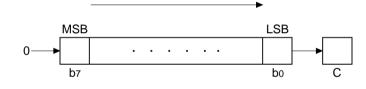

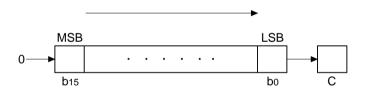

| 2.2.48 (1) | ROTR (B)  | 150 |

| 2.2.48 (2) | ROTR (W)  | 151 |

| • •        | ROTR (L)  |     |

|            | ROTXL (B) |     |

|            | ROTXL (W) |     |

|            | ROTXL (L) |     |

| 2.2.50(1)  | ROTXR (B) | 156 |

|        | 2.2.50 (2)  | ROTXR (W)                                    | 157 |

|--------|-------------|----------------------------------------------|-----|

|        | 2.2.50 (3)  | ROTXR (L)                                    | 158 |

|        | 2.2.51      | RTE                                          | 159 |

|        | 2.2.52      | RTS                                          | 160 |

|        | 2.2.53 (1)  | SHAL (B)                                     | 161 |

|        | 2.2.53 (2)  | SHAL (W)                                     | 162 |

|        | 2.2.53 (3)  | SHAL (L)                                     | 163 |

|        | 2.2.54 (1)  | SHAR (B)                                     | 164 |

|        | 2.2.54 (2)  | SHAR (W)                                     | 165 |

|        | 2.2.54 (3)  | SHAR (L)                                     | 166 |

|        | 2.2.55 (1)  | SHLL (B)                                     | 167 |

|        |             | SHLL (W)                                     |     |

|        | 2.2.55 (3)  | SHLL (L)                                     | 169 |

|        | 2.2.56(1)   | SHLR (B)                                     | 170 |

|        | 2.2.56 (2)  | SHLR (W)                                     | 171 |

|        | 2.2.56 (3)  | SHLR (L)                                     | 172 |

|        | 2.2.57      | SLEEP                                        | 173 |

|        | 2.2.58 (1)  | STC (B)                                      | 174 |

|        | 2.2.58 (2)  | STC (W)                                      | 175 |

|        | 2.2.59(1)   | SUB (B)                                      | 177 |

|        | 2.2.59 (2)  | SUB (W)                                      | 178 |

|        | 2.2.59 (3)  | SUB (L)                                      | 179 |

|        | 2.2.60      | SUBS                                         | 180 |

|        | 2.2.61      | SUBX                                         | 181 |

|        | 2.2.62      | TRAPA                                        | 182 |

|        | 2.2.63 (1)  | XOR (B)                                      | 183 |

|        |             | XOR (W)                                      |     |

|        | 2.2.63 (3)  | XOR (L)                                      | 185 |

|        | 2.2.64      | XORC                                         | 186 |

| 2.3    | Instruction | n Set Summary                                | 187 |

| 2.4    | Instruction | n Codes                                      | 200 |

| 2.5    |             | Code Map                                     |     |

| 2.6    | -           | f States Required for Instruction Execution  |     |

| 2.7    | Condition   | Code Modification                            | 221 |

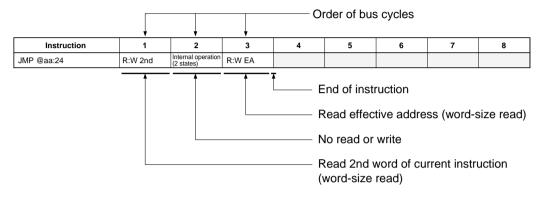

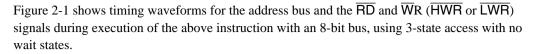

| 2.8    | Bus cycles  | s During Instruction Execution               | 226 |

|        | 2           |                                              |     |

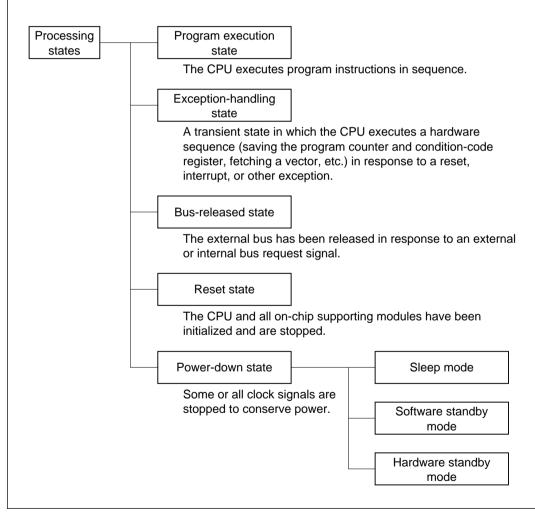

| Sectio | on 3 Pr     | ocessing States                              | 239 |

| 3.1    |             |                                              |     |

| 3.2    |             | Execution State                              |     |

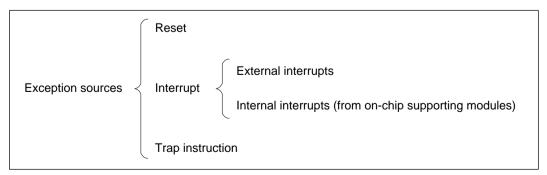

| 3.3    | -           | -Handling State                              |     |

|        | -           | pes of Exception Handling and Their Priority |     |

|        |             |                                              |     |

|      | 3.3.2 Exception-Handling Sequences |  |

|------|------------------------------------|--|

| 3.4  | Bus-Released State                 |  |

| 3.5  | Reset State                        |  |

| 3.6  | Power-Down State                   |  |

|      | 3.6.1 Sleep Mode                   |  |

|      | 3.6.2 Software Standby Mode        |  |

|      | 3.6.3 Hardware Standby Mode        |  |

| Sect | tion 4 Basic Timing                |  |

| 4.1  | Overview                           |  |

| 4.2  | On-Chip Memory (RAM, ROM)          |  |

| 4.3  | On-Chip Supporting Modules         |  |

| 4.4  | External Data Bus                  |  |

# Section 1 CPU

## 1.1 Overview

The H8/300H CPU is a high-speed central processing unit with an internal 32-bit architecture that is upward-compatible with the H8/300 CPU. The H8/300H CPU has sixteen 16-bit general registers, can address a 16-Mbyte linear address space, and is ideal for realtime control.

#### 1.1.1 Features

The H8/300H CPU has the following features.

- Upward-compatible with H8/300 CPU

- Can execute H8/300 object programs

- General-register architecture

- Sixteen 16-bit general registers (also usable as sixteen 8-bit registers or eight 32-bit registers)

- Sixty-two basic instructions

- 8/16/32-bit arithmetic and logic instructions

- Multiply and divide instructions

- Powerful bit-manipulation instructions

- Eight addressing modes

- Register direct [Rn]

- Register indirect [@ERn]

- Register indirect with displacement [@(d:16,ERn) or @(d:24,ERn)]

- Register indirect with post-increment or pre-decrement [@ERn+ or @-ERn]

- Absolute address [@aa:8, @aa:16, or @aa:24]

- Immediate [#xx:8, #xx:16, or #xx:32]

- Program-counter relative [@(d:8,PC) or @(d:16,PC)]

- Memory indirect [@@aa:8]

- 16-Mbyte address space

- High-speed operation

- All frequently-used instructions execute in two to four states

- Maximum clock frequency: 16 MHz

- 8/16/32-bit register-register add/subtract: 125 ns

- 8 × 8-bit register-register multiply: 875 ns

- 16 ÷ 8-bit register-register divide: 875 ns

- 16  $\times$  16-bit register-register multiply: 1375 ns

- $32 \div 16$ -bit register-register divide: 1375 ns

- Two CPU operating modes

- Normal mode

- Advanced mode

- Low-power mode

- Transition to power-down state by SLEEP instruction

#### 1.1.2 Differences from H8/300 CPU

In comparison to the H8/300 CPU, the H8/300H CPU has the following enhancements.

• More general registers

Eight 16-bit registers have been added.

• Expanded address space

Normal mode supports the same 64-kbyte address space as the H8/300 CPU.

Advanced mode supports a maximum 16-Mbyte address space.

• Enhanced addressing

The addressing modes have been enhanced to make effective use of the 16-Mbyte address space.

• Enhanced instructions

Signed multiply/divide instructions and other instructions have been added.

# **1.2 CPU Operating Modes**

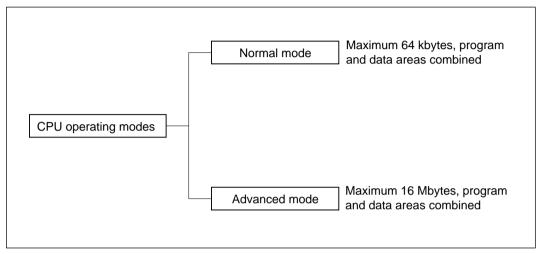

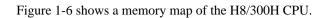

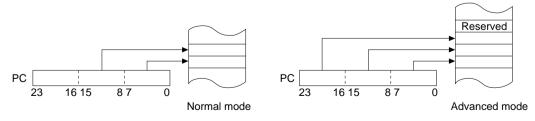

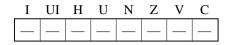

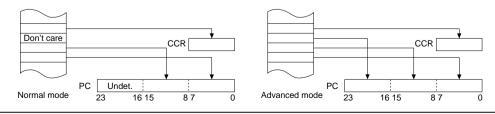

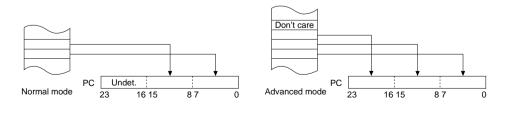

The H8/300H CPU has two operating modes: normal and advanced. Normal mode supports a maximum 64-kbyte address space. Advanced mode supports up to 16 Mbytes. The mode is selected at the mode pins of the microcontroller. For further information, refer to the relevant hardware manual.

Figure 1-1 CPU Operating Modes

(1) **Normal Mode:** The exception vector table and stack have the same structure as in the H8/300 CPU.

Address Space: A maximum address space of 64 kbytes can be accessed, as in the H8/300 CPU.

**Extended Registers (En):** The extended registers (E0 to E7) can be used as 16-bit data registers, or they can be combined with the general registers (R0 to R7) for use as 32-bit data registers. When En is used as a 16-bit register it can contain any value, even when the corresponding general register (R0 to R7) is used as an address register. If the general register is referenced in the register indirect addressing mode with pre-decrement (@–Rn) or post-increment (@Rn+) and a carry or borrow occurs, however, the value in the corresponding extended register will be affected.

**Instruction Set:** All additional instructions and addressing modes of the H8/300 CPU can be used. If a 24-bit effective address (EA) is specified, only the lower 16 bits are used.

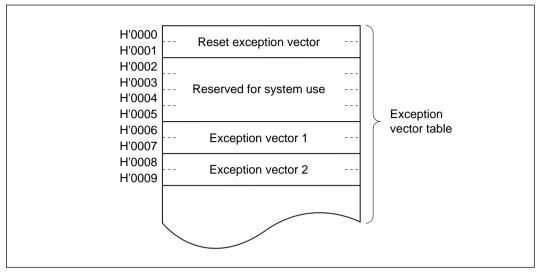

**Exception Vector Table and Memory Indirect Branch Addresses:** In normal mode the top area starting at H'0000 is allocated to the exception vector table. One branch address is stored per 16 bits (figure 1-2). The exception vector table differs depending on the microcontroller, so see the microcontroller hardware manual for further information.

Figure 1-2 Exception Vector Table (normal mode)

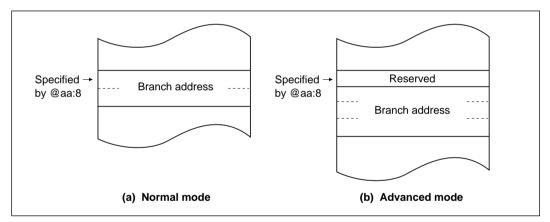

The memory indirect addressing mode (@@aa:8) employed in the JMP and JSR instructions uses an 8-bit absolute address to specify a memory operand that contains a branch address. In normal mode the operand is a 16-bit word operand, providing a 16-bit branch address. Branch addresses can be stored in the top area from H'0000 to H'00FF. Note that this area is also used for the exception vector table.

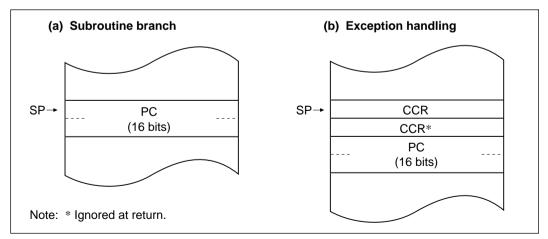

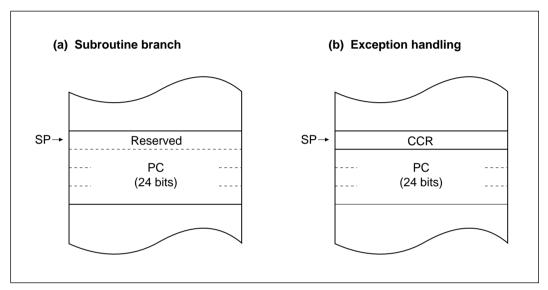

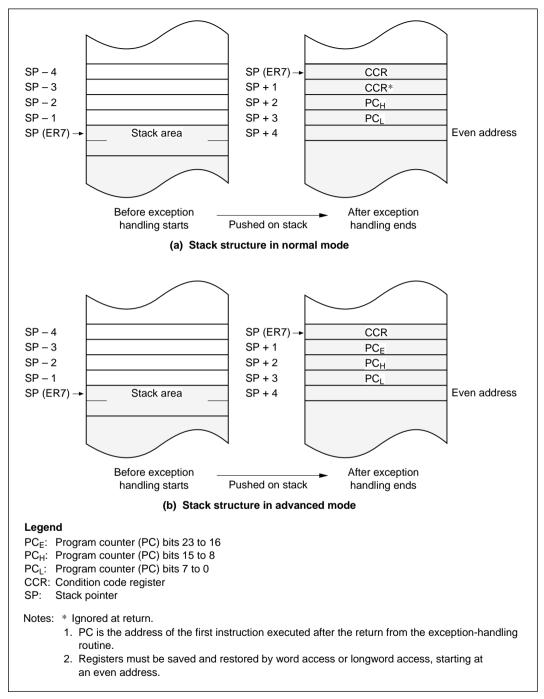

**Stack Structure:** When the program counter (PC) is pushed on the stack in a subroutine call, and the PC and condition-code register (CCR) are pushed on the stack in exception handling, they are stored in the same way as in the H8/300 CPU. See figure 1-3.

Figure 1-3 Stack Structure (normal mode)

(2) Advanced Mode: In advanced mode the exception vector table and stack structure differ from the H8/300 CPU.

Address Space: Up to 16 Mbytes can be accessed linearly.

**Extended Registers (En):** The extended registers (E0 to E7) can be used as 16-bit data registers, or they can be combined with the general registers (R0 to R7) for use as 32-bit data registers. When a 32-bit register is used as an address register, the upper 8 bits are ignored.

Instruction Set: All additional instructions and addressing modes of the H8/300H can be used.

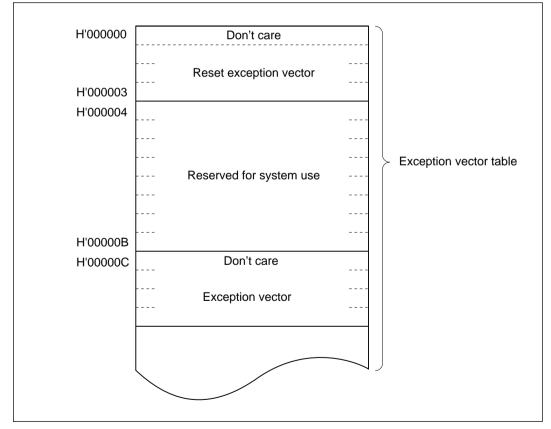

**Exception Vector Table and Memory Indirect Branch Addresses:** In advanced mode the top area starting at H'000000 is allocated to the exception vector table in units of 32 bits. In each 32 bits, the upper 8 bits are ignored and a branch address is stored in the lower 24 bits (figure 1-4). The exception vector table differs depending on the microcontroller, so see the relevant hardware manual for further information.

Figure 1-4 Exception Vector Table (advanced mode)

The memory indirect addressing mode (@@aa:8) employed in the JMP and JSR instructions uses an 8-bit absolute address to specify a memory operand that contains a branch address. In advanced mode the operand is a 32-bit longword operand, of which the lower 24 bits are the branch address. Branch addresses can be stored in the top area from H'000000 to H'0000FF. Note that this area is also used for the exception vector table.

**Stack Structure:**When the program counter (PC) is pushed on the stack in a subroutine call, and the PC and condition-code register (CCR) are pushed on the stack in exception handling, they are stored as shown in figure 1-5.

Figure 1-5 Stack Structure (advanced mode)

# 1.3 Address Space

Figure 1-6 Memory Map

# **1.4 Register Configuration**

#### 1.4.1 Overview

The H8/300H CPU has the internal registers shown in figure 1-7. There are two types of registers: general and extended registers, and control registers.

| 15     |                           | 07  | 07                                 |

|--------|---------------------------|-----|------------------------------------|

|        | E0                        | R0H | R0L                                |

|        | E1                        | R1H | R1L                                |

|        | E2                        | R2H | R2L                                |

|        | E3                        | R3H | R3L                                |

|        | E4                        | R4H | R4L                                |

|        | E5                        | R5H | R5L                                |

|        | E6                        | R6H | R6L                                |

| SP     | E7                        | R7H | R7L                                |

|        |                           |     | 7654004                            |

|        |                           |     |                                    |

| Legenc | <b>I</b><br>Stack pointer |     | 7 6 5 4 3 2 1<br>CCR I U H U N Z V |

#### Figure 1-7 CPU Registers

#### 1.4.2 General Registers

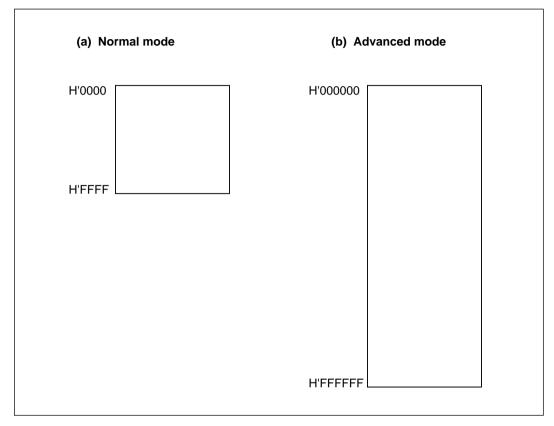

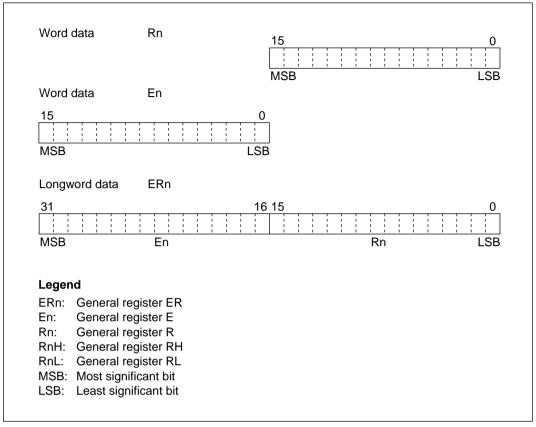

The H8/300H CPU has eight 32-bit general registers. These general registers are all functionally alike and can be used without distinction between data registers and address registers. When a general register is used as a data register, it can be accessed as a 32-bit, 16-bit, or 8-bit register. When the general registers are used as 32-bit registers or as address registers, they are designated by the letters ER (ER0 to ER7).

The ER registers divide into 16-bit general registers designated by the letters E (E0 to E7) and R (R0 to R7). These registers are functionally equivalent, providing a maximum sixteen 16-bit registers. The E registers (E0 to E7) are also referred to as extended registers.

The R registers divide into 8-bit general registers designated by the letters RH (R0H to R7H) and RL (R0L to R7L). These registers are functionally equivalent, providing a maximum sixteen 8-bit registers.

Figure 1-8 illustrates the usage of the general registers. The usage of each register can be selected independently.

Figure 1-8 Usage of General Registers

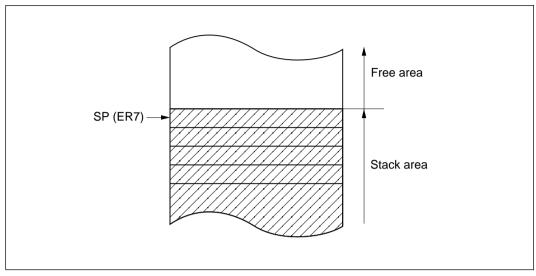

General register ER7 has the function of stack pointer (SP) in addition to its general-register function, and is used implicitly in exception handling and subroutine calls. Figure 1-9 shows the stack.

Figure 1-9 Stack

#### 1.4.3 Control Registers

The control registers are the 24-bit program counter (PC) and the 8-bit condition-code register (CCR).

(1) **Program Counter (PC):** This 24-bit counter indicates the address of the next instruction the CPU will execute. The length of all CPU instructions is 16 bits (one word) or a multiple of 16 bits, so the least significant PC bit is ignored. When an instruction is fetched, the least significant PC bit is regarded as 0.

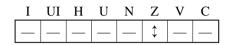

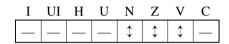

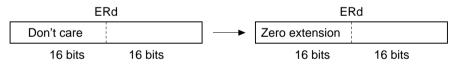

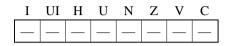

(2) Condition Code Register (CCR): This 8-bit register contains internal CPU status information, including the interrupt mask bit (I) and half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags.

**Bit 7—Interrupt Mask Bit (I):** Masks interrupts other than NMI when set to 1. (NMI is accepted regardless of the I bit setting.) The I bit is set to 1 by hardware at the start of an exception-handling sequence.

**Bit 6—User Bit (U):** Can be written and read by software using the LDC, STC, ANDC, ORC, and XORC instructions. This bit can also be used as an interrupt mask bit. For details see the relevant microcontroller hardware manual.

**Bit 5—Half-Carry Flag (H):** When the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B, or NEG.B instruction is executed, this flag is set to 1 if there is a carry or borrow at bit 3, and cleared to 0 otherwise. When the ADD.W, SUB.W, CMP.W, or NEG.W instruction is executed, the H flag is set to 1 if there is a carry or borrow at bit 11, and cleared to 0 otherwise. When the ADD.L, SUB.L, CMP.L, or NEG.L instruction is executed, the H flag is set to 1 if there is a carry or borrow at bit 27, and cleared to 0 otherwise.

**Bit 4—User Bit (U):** Can be written and read by software using the LDC, STC, ANDC, ORC, and XORC instructions.

**Bit 3—Negative Flag (N):** Indicates the most significant bit (sign bit) of the result of an instruction.

**Bit 2—Zero Flag (Z):** Set to 1 to indicate a zero result, and cleared to 0 to indicate a non-zero result.

**Bit 1—Overflow Flag (V):** Set to 1 when an arithmetic overflow occurs, and cleared to 0 at other times.

Bit 0—Carry Flag (C): Set to 1 when a carry occurs, and cleared to 0 otherwise. Used by:

- Add instructions, to indicate a carry

- Subtract instructions, to indicate a borrow

- Shift and rotate instructions, to store the value shifted out of the end bit

The carry flag is also used as a bit accumulator by bit manipulation instructions. Some instructions leave some or all of the flag bits unchanged. For the action of each instruction on the flag bits, refer to the detailed descriptions of the instructions starting in section 2.2.1.

Operations can be performed on the CCR bits by the LDC, STC, ANDC, ORC, and XORC instructions. The N, Z, V, and C flags are used as branching conditions for conditional branch (Bcc) instructions.

#### 1.4.4 Initial Register Values

When the CPU is reset, the program counter (PC) is loaded from the vector table and the I bit in the condition-code register (CCR) is set to 1. The other CCR bits and the general registers and extended registers are not initialized. In particular, the stack pointer (extended register E7 and general register R7) is not initialized. The stack pointer must therefore be initialized by an MOV.L instruction executed immediately after a reset.

# **1.5 Data Formats**

The H8/300H CPU can process 1-bit, 4-bit, 8-bit (byte), 16-bit (word), and 32-bit (longword) data. Bit-manipulation instructions operate on 1-bit data by accessing bit n (n = 0, 1, 2, ..., 7) of byte operand data. The DAA and DAS decimal-adjust instructions treat byte data as two digits of 4-bit BCD data.

#### 1.5.1 General Register Data Formats

Figure 1-10 shows the data formats in general registers.

| Data type      | Register number | Data format                                                                                                      |

|----------------|-----------------|------------------------------------------------------------------------------------------------------------------|

| 1-bit data     | RnH             | 7 0<br>7 6 5 4 3 2 1 0 Don't care                                                                                |

| 1-bit data     | RnL             | 7         0           Don't care         7         6         5         4         3         2         1         0 |

| 4-bit BCD data | RnH             | 7     4     3     0       Upper     Lower     Don't care                                                         |

| 4-bit BCD data | RnL             | 7430Don't careUpperLower                                                                                         |

| Byte data      | RnH             | 7 0<br>Don't care<br>MSB LSB                                                                                     |

| Byte data      | RnL             | 7     0       Don't care                                                                                         |

Figure 1-10 General Register Data Formats

Figure 1-10 General Register Data Formats (cont)

#### 1.5.2 Memory Data Formats

Figure 1-11 shows the data formats on memory. The H8/300H CPU can access word data and longword data on memory, but word or longword data must begin at an even address. If an attempt is made to access word or longword data at an odd address, no address error occurs but the least significant bit of the address is regarded as 0, so the access starts at the preceding address. This also applies to instruction fetches.

| Data type     |                |            | D           | ata   | form     | nat   |       |            |

|---------------|----------------|------------|-------------|-------|----------|-------|-------|------------|

|               | Address        |            |             |       | <u> </u> | _     |       |            |

| 1-bit data    | Address L      | 7<br>7   0 | 6   9       | 5   4 | 4   :    | 3   2 | 2   - | 0<br>1   0 |

| Byte data     | Address L      | MSB;       | 1<br>1<br>1 | 1     | 1        | 1     | 1     | LSB        |

| Word data     | Address 2M     | MSB;       | 1           | 1     | 1        | 1     | 1     | 1          |

|               | Address 2M + 1 | :          | 1           | 1     | 1        |       | 1     | LSB        |

| Longword data | Address 2N     | MSB:       | 1           | 1     | 1        |       | 1     |            |

|               | Address 2N + 1 | 1          |             | 1     | 1        |       | 1     |            |

|               | Address 2N + 2 | ł          | 1           | 1     | 1        | 1     | 1     |            |

|               | Address 2N + 3 |            | 1           | 1     | 1        |       | 1     | LSB        |

|               |                |            |             |       |          |       |       |            |

Figure 1-11 Memory Data Formats

When ER7 is used as an address register to access the stack, the operand size should be word size or longword size.

# 1.6 Instruction Set

#### 1.6.1 Overview

The H8/300H CPU has 62 types of instructions, which are classified by function in table 1-1. For a detailed description of each instruction see section 2.2, Instruction Descriptions.

| Table 1-1 | Instruction | Classification |

|-----------|-------------|----------------|

|-----------|-------------|----------------|

| Function                 | Instructions                                                                                                 | Number |

|--------------------------|--------------------------------------------------------------------------------------------------------------|--------|

| Data transfer            | MOV, PUSH*1, POP*2, MOVTPE, MOVFPE                                                                           | 3      |

| Arithmetic<br>operations | ADD, SUB, ADDX, SUBX, INC, DEC, ADDS, SUBS, DAA,<br>DAS, MULXU, MULXS, DIVXU, DIVXS, CMP, NEG, EXTS,<br>EXTU | 18     |

| Logic operations         | AND, OR, XOR, NOT                                                                                            | 4      |

| Shift                    | SHAL, SHAR, SHLL, SHLR, ROTL, ROTR, ROTXL, ROTXR                                                             | 8      |

| Bit manipulation         | BSET, BCLR, BNOT, BTST, BAND, BIAND, BOR, BIOR, BXOR, BIXOR, BLD, BILD, BST, BIST                            | 14     |

| Branch                   | Bcc*2, JMP, BSR, JSR, RTS                                                                                    | 5      |

| System control           | TRAPA, RTE, SLEEP, LDC, STC, ANDC, ORC, XORC, NOP                                                            | 9      |

| Block data transfer      | EEPMOV                                                                                                       | 1      |

|                          |                                                                                                              |        |

Total 62 types

Notes: The shaded instructions are not present in the H8/300 instruction set.

- POP.W Rn and PUSH.W Rn are identical to MOV.W @SP+, Rn and MOV.W Rn, @-SP. POP.L ERn and PUSH.L ERn are identical to MOV.L @SP+, ERn and MOV.L ERn, @-SP.

- 2. Bcc is the generic designation of a conditional branch instruction.

## 1.6.2 Instructions and Addressing Modes

Table 1-2 indicates the instructions available in the H8/300H CPU.

#### Table 1-2 Instruction Set Overview

|                       |             |     |                 |      |             |             | Addressing Mode | s     |        |          |           |            |          |

|-----------------------|-------------|-----|-----------------|------|-------------|-------------|-----------------|-------|--------|----------|-----------|------------|----------|

| Function              | Instruction | #xx | Rn              | @ERn | @(d:16,ERn) | @(d:24,ERn) | @ERn+/@-ERn     | @aa:8 | @aa:16 | 6 @aa:24 | @(d:8,PC) | @(d:16,PC) | @@aa:8 — |

| Data                  | MOV         | BWL | BWL             | BWL  | BWL         | BWL         | BWL             | В     | BWL    | BWL      |           |            |          |

| transfer              | POP, PUSH   | _   | _               | _    | _           | _           | _               | _     | _      | _        |           |            | – WL     |

|                       | MOVFPE,     | _   | _               | _    | _           | _           | _               | _     | В      | _        |           |            |          |

|                       | MOVTPE      |     |                 |      |             |             |                 |       |        |          |           |            |          |

|                       | ADD, CMP    | BWL | BWL             | _    | _           | _           | _               | _     | _      | _        |           |            |          |

| operations            | SUB         | WL  | BWL             | _    | _           | _           | _               | _     | _      | _        |           |            |          |

|                       | ADDX,       | В   | В               | _    | _           | _           | _               | _     | _      | _        |           |            |          |

|                       | SUBX        |     |                 |      |             |             |                 |       |        |          |           |            |          |

|                       | ADDS,       | _   | L <sup>*1</sup> | _    | _           | _           | _               | _     | _      | _        |           |            |          |

|                       | SUBS        |     |                 |      |             |             |                 |       |        |          |           |            |          |

|                       | INC, DEC    | _   | BWL             | _    | _           | _           | _               | _     | _      | _        |           |            |          |

|                       | DAA, DAS    | _   | В               | _    | _           | _           | _               | _     | _      | _        |           |            |          |

|                       | MULXU,      | _   | BW              | _    | _           | _           | _               | _     | _      | _        |           |            |          |

|                       | DIVXU       | _   |                 |      |             |             |                 |       |        |          |           |            |          |

|                       | MULXS,      |     | BW              | _    | _           | _           | _               | _     | _      | _        |           |            |          |

|                       | DIVXS       | _   |                 |      |             |             |                 |       |        |          |           |            |          |

|                       | NEG         |     | BWL             | _    | _           | _           | _               | _     |        | _        |           |            |          |

|                       | EXTU, EXTS  | —   | WL              | _    | _           | _           | _               | _     | _      | _        |           |            |          |

|                       | AND, OR,    | BWL | BWL             | _    | _           | _           | _               | _     |        | _        |           |            |          |

| operations            | XOR         |     |                 |      |             |             |                 |       |        |          |           |            |          |

|                       | NOT         | _   | BWL             | _    | _           | _           | _               | _     | _      | _        | _ ·       |            |          |

| Shift                 |             | _   | BWL             | _    | _           | _           | _               | _     | _      | _        |           |            |          |

| Bit manipu-<br>lation |             | _   | В               | В    | _           | _           | _               | В     | _      | _        |           |            |          |

#### Table 1-2 Instruction Set Overview (cont)

|          |             |     |    |      |             |             | Addressing Mode | 5    |         |         |             |              |        |       |

|----------|-------------|-----|----|------|-------------|-------------|-----------------|------|---------|---------|-------------|--------------|--------|-------|

| Function | Instruction | #xx | Rn | @ERn | @(d:16,ERn) | @(d:24,ERn) | @ERn+/@-ERn     | @aa: | B @aa:1 | 6 @aa:2 | 24 @(d:8,PC | ;) @(d:16,PC | ;) @@a | a:8 — |

| Branch   | Bcc, BSR    | _   | _  | _    | _           | _           | _               | _    | _       | _       | 0           | 0            | _      | _     |

|          | JMP, JSR    | _   | _  | 0    | _           | —           | _               | _    | _       | O *2    | _           | _            | 0      | _     |

|          | RTS         | _   | _  | _    | _           | —           | _               | _    | _       | _       | _           | _            | _      | 0     |

| System   | TRAPA       | _   | _  | _    | _           | —           | _               | _    | _       | _       | _           | _            | _      | 0     |

| control  | RTE         | _   | _  | _    | _           | _           | _               | _    | _       | _       | _           | _            | _      | 0     |

|          | SLEEP       | _   | _  | _    | _           | _           | _               | _    | _       | _       | _           | _            | _      | 0     |

|          | LDC         | В   | В  | W    | W           | W           | W               | _    | W       | W       | _           | _            | _      | _     |

|          | STC         | _   | В  | W    | W           | W           | W               | _    | W       | W       | _           | _            | _      | _     |

|          | ANDC,       | В   | _  | _    | _           | _           | _               | _    | _       | _       | _           | _            | _      | _     |

|          | ORC,        |     |    |      |             |             |                 |      |         |         |             |              |        |       |

|          | XORC        |     |    |      |             |             |                 |      |         |         |             |              |        |       |

|          | NOP         | _   | _  | _    | _           | _           | _               | _    | _       | _       | _           | _            | _      | 0     |

|          | EEPMOV.B    | _   | _  | _    | _           | _           | _               | _    | _       | _       | _           | _            | _      | 0     |

| transfer | EEPMOV.W    | _   | _  | _    | _           | _           | _               | _    | _       | _       | _           | _            | _      | 0     |

#### Addressing Modes

#### Legend

B: Byte

W: Word

L: Longword

: Newly added instruction in H8/300H CPU

- Notes: 1. The operand size of the ADDS and SUBS instructions of the H8/300H CPU has been changed to longword size. (In the H8/300 CPU it was word size.)

- 2. Because of its larger address space, the H8/300H CPU uses a 24-bit absolute address for the JMP and JSR instructions. (The H8/300 CPU used 16 bits.)

#### 1.6.3 Tables of Instructions Classified by Function

Table 1-3 summarizes the instructions in each functional category. The notation used in table 1-3 is defined next.

#### **Operation Notation**

| Rd            | General register (destination)*    |

|---------------|------------------------------------|

| Rs            | General register (source)*         |

| Rn            | General register*                  |

| ERn           | General register (32-bit register) |

| (EAd)         | Destination operand                |

| (EAs)         | Source operand                     |

| CCR           | Condition code register            |

| N             | N (negative) bit of CCR            |

| Z             | Z (zero) bit of CCR                |

| V             | V (overflow) bit of CCR            |

| С             | C (carry) bit of CCR               |

| PC            | Program counter                    |

| SP            | Stack pointer                      |

| #IMM          | Immediate data                     |

| disp          | Displacement                       |

| +             | Addition                           |

|               | Subtraction                        |

| ×             | Multiplication                     |

| ÷             | Division                           |

| ^             | AND logical                        |

| V             | OR logical                         |

| Ð             | Exclusive OR logical               |

| $\rightarrow$ | Move                               |

|               | Not                                |

| :3/:8/:16/:24 | 3-, 8-, 16-, or 24-bit length      |

|               |                                    |

Note: \* General registers include 8-bit registers (R0H/R0L to R7H/R7L), 16-bit registers (R0 to R7, E0 to E7), and 32-bit registers (ER0 to ER7).

| Туре          | Instruction | Size* | Function                                                                                                                                                                                   |  |  |

|---------------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Data transfer | MOV         | B/W/L | $(EAs) \rightarrow Rd$ , $Rs \rightarrow (EAd)$<br>Moves data between two general registers or between<br>a general register and memory, or moves immediate<br>data to a general register. |  |  |

|               | MOVFPE      | В     | $(EAs) \rightarrow Rd$<br>Moves external memory contents (addressed by<br>@aa:16) to a general register in synchronization with<br>an E clock.                                             |  |  |

|               | MOVTPE      | В     | $Rs \rightarrow (EAd)$<br>Moves general register contents to an external memory<br>location (addressed by @aa:16) in synchronization with<br>an E clock.                                   |  |  |

|               | POP         | W/L   | @SP+ → Rn<br>Pops a register from the stack. POP.W Rn is identical t<br>MOV.W @SP+, Rn. POP.L ERn is identical to MOV.L<br>@SP+, ERn.                                                      |  |  |

|               | PUSH        | W/L   | Rn → @–SP<br>Pushes a register onto the stack. PUSH.W Rn is<br>identical to MOV.W Rn, @–SP. PUSH.L ERn is<br>identical to MOV.L ERn, @–SP.                                                 |  |  |

B: Byte W: Word

| Туре                     | Instruction  | Size* | Function                                                                                                                                                                                                                                                                                                       |

|--------------------------|--------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic<br>operations | ADD<br>SUB   | B/W/L | $Rd \pm Rs \rightarrow Rd$ , $Rd \pm \#IMM \rightarrow Rd$<br>Performs addition or subtraction on data in two general<br>registers, or on immediate data and data in a general<br>register. (Immediate byte data cannot be subtracted<br>from data in a general register. Use the SUBX or ADD<br>instruction.) |

|                          | ADDX<br>SUBX | В     | $Rd \pm Rs \pm C \rightarrow Rd$ , $Rd \pm \#IMM \pm C \rightarrow Rd$<br>Performs addition or subtraction with carry or borrow<br>on byte data in two general registers, or on immediate<br>data and data in a general register.                                                                              |

|                          | INC<br>DEC   | B/W/L | $Rd \pm 1 \rightarrow Rd$ , $Rd \pm 2 \rightarrow Rd$<br>Increments or decrements a general register by 1 or 2.<br>(Byte operands can be incremented or decremented by<br>1 only.)                                                                                                                             |

|                          | ADDS<br>SUBS | L     | $\begin{array}{ll} Rd\pm 1 \to Rd, & Rd\pm 2 \to Rd, & Rd\pm 4 \to Rd \\ Adds \text{ or subtracts the value 1, 2, or 4 to or from data in} \\ a \ 32-bit \ register. \end{array}$                                                                                                                              |

|                          | DAA<br>DAS   | В     | Rd decimal adjust $\rightarrow$ Rd<br>Decimal-adjusts an addition or subtraction result in a<br>general register by referring to the CCR to produce<br>4-bit BCD data.                                                                                                                                         |

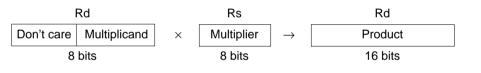

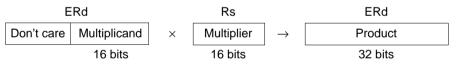

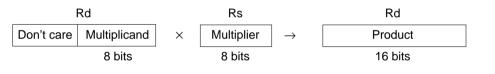

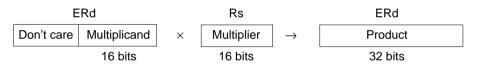

|                          | MULXS        | B/W   | $Rd \times Rs \rightarrow Rd$<br>Performs signed multiplication on data in two general<br>registers: either 8 bits $\times$ 8 bits $\rightarrow$ 16 bits or 16 bits $\times$ 16<br>bits $\rightarrow$ 32 bits.                                                                                                 |

|                          | MULXU        | B/W   | $\begin{array}{l} Rd\timesRs\toRd\\ Performs \text{ unsigned multiplication on data in two general}\\ registers: either 8 bits\times8 \text{ bits}\to16 \text{ bits or 16 bits}\times16\\ bits\to32 \text{ bits.} \end{array}$                                                                                 |

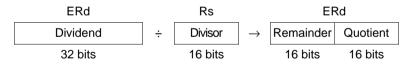

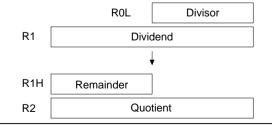

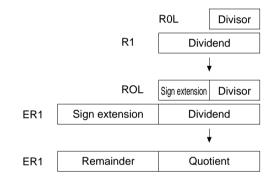

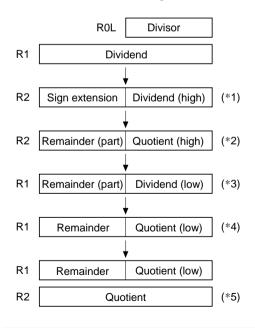

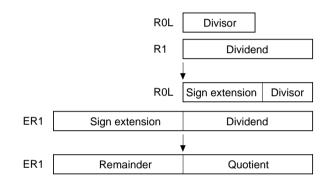

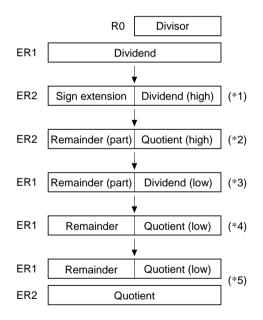

|                          | DIVXS        | B/W   | Rd ÷ Rs → Rd<br>Performs signed division on data in two general<br>registers: either 16 bits ÷ 8 bits → 8-bit quotient and<br>8-bit remainder or 32 bits ÷ 16 bits → 16-bit quotient<br>and 16-bit remainder.                                                                                                  |

| Table 1-3 | Instructions | Classified by | Function | (cont) |

|-----------|--------------|---------------|----------|--------|

|-----------|--------------|---------------|----------|--------|

Note: \* Size refers to the operand size.

B: Byte

W: Word

| Туре                     | Instruction | Size* | Function                                                                                                                                                                                                                              |  |  |  |

|--------------------------|-------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

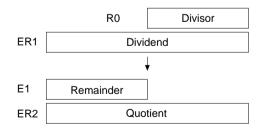

| Arithmetic<br>operations | DIVXU       | B/W   | Rd ÷ Rs → Rd<br>Performs unsigned division on data in two general<br>registers: either 16 bits ÷ 8 bits → 8-bit quotient and 8-<br>bit remainder or 32 bits ÷ 16 bits → 16-bit quotient and<br>16-bit remainder.                      |  |  |  |

|                          | CMP         | B/W/L | Rd – Rs, Rd – #IMM<br>Compares data in a general register with data in<br>another general register or with immediate data, and<br>sets the CCR according to the result.                                                               |  |  |  |

|                          | NEG         | B/W/L | $0 - Rd \rightarrow Rd$<br>Takes the two's complement (arithmetic complement) of data in a general register.                                                                                                                          |  |  |  |

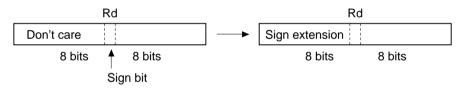

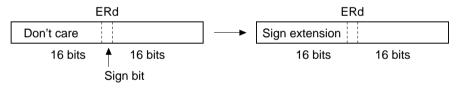

|                          | EXTS        | W/L   | Rd (sign extension) $\rightarrow$ Rd<br>Extends byte data in the lower 8 bits of a 16-bit register<br>to word data, or extends word data in the lower 16 bits<br>of a 32-bit register to longword data, by extending the<br>sign bit. |  |  |  |

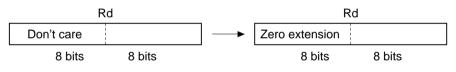

|                          | EXTU        | W/L   | Rd (zero extension) $\rightarrow$ Rd<br>Extends byte data in the lower 8 bits of a 16-bit register<br>to word data, or extends word data in the lower 16 bits<br>of a 32-bit register to longword data, by padding with<br>zeros.     |  |  |  |

| Logic operations         | AND         | B/W/L | $Rd \wedge Rs \rightarrow Rd$ , $Rd \wedge \#IMM \rightarrow Rd$<br>Performs a logical AND operation on a general register<br>and another general register or immediate data.                                                         |  |  |  |

|                          | OR          | B/W/L | $Rd \lor Rs \to Rd$ , $Rd \lor \#IMM \to Rd$<br>Performs a logical OR operation on a general register<br>and another general register or immediate data.                                                                              |  |  |  |

|                          | XOR         | B/W/L | $Rd \oplus Rs \rightarrow Rd$ , $Rd \oplus \#IMM \rightarrow Rd$<br>Performs a logical exclusive OR operation on a general<br>register and another general register or immediate<br>data.                                             |  |  |  |

|                          | NOT         | B/W/L | $\neg$ (Rd) $\rightarrow$ (Rd)<br>Takes the one's complement of general register<br>contents.                                                                                                                                         |  |  |  |

Note: \* Size refers to the operand size.

B: Byte

W: Word

| Туре                          | Instruction    | Size* | Function                                                                                                                                                                                                                                                                |

|-------------------------------|----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shift operations              | SHAL<br>SHAR   | B/W/L | Rd (shift) $\rightarrow$ Rd<br>Performs an arithmetic shift on general register<br>contents.                                                                                                                                                                            |

|                               | SHLL<br>SHLR   | B/W/L | Rd (shift) $\rightarrow$ Rd Performs a logical shift on general register contents.                                                                                                                                                                                      |

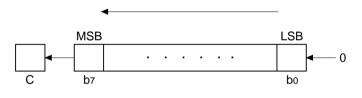

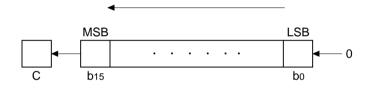

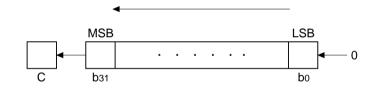

|                               | ROTL<br>ROTR   | B/W/L | Rd (rotate) $\rightarrow$ Rd<br>Rotates general register contents.                                                                                                                                                                                                      |

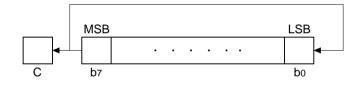

|                               | ROTXL<br>ROTXR | B/W/L | Rd (rotate) $\rightarrow$ Rd Rotates general register contents through the carry bit.                                                                                                                                                                                   |

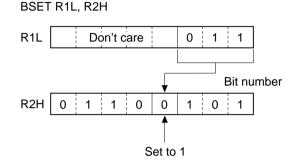

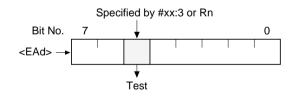

| Bit-manipulation instructions | BSET           | В     | $1 \rightarrow$ ( <bit-no.> of <ead>)<br/>Sets a specified bit in a general register or memory<br/>operand to 1. The bit number is specified by 3-bit<br/>immediate data or the lower three bits of a general<br/>register.</ead></bit-no.>                             |

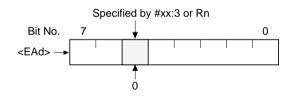

|                               | BCLR           | В     | $0 \rightarrow$ ( <bit-no.> of <ead>)<br/>Clears a specified bit in a general register or memory<br/>operand to 0. The bit number is specified by 3-bit<br/>immediate data or the lower three bits of a general<br/>register.</ead></bit-no.>                           |

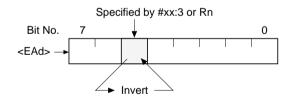

|                               | BNOT           | В     | ¬ ( <bit-no.> of <ead>) → (<bit-no.> of <ead>)<br/>Inverts a specified bit in a general register or memory<br/>operand. The bit number is specified by 3-bit<br/>immediate data or the lower three bits of a general<br/>register.</ead></bit-no.></ead></bit-no.>      |

|                               | BTST           | В     | ¬ ( <bit-no.> of <ead>) → Z<br/>Tests a specified bit in a general register or memory<br/>operand and sets or clears the Z flag accordingly. The<br/>bit number is specified by 3-bit immediate data or the<br/>lower three bits of a general register.</ead></bit-no.> |

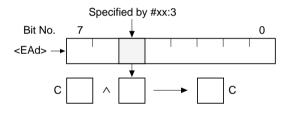

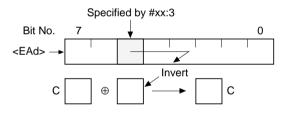

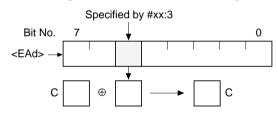

|                               | BAND           | В     | $C \land ( of ) \rightarrow C$<br>ANDs the carry flag with a specified bit in a general register or memory operand and stores the result in the carry flag.                                                                                                             |

|                               | BIAND          | В     | $C \land \neg$ ( <bit-no.> of <ead>) <math>\rightarrow C</math><br/>ANDs the carry flag with the inverse of a specified bit in<br/>a general register or memory operand and stores the<br/>result in the carry flag.</ead></bit-no.>                                    |

|                               |                |       | The bit number is specified by 3-bit immediate data.                                                                                                                                                                                                                    |

Note: \* Size refers to the operand size.

B: Byte

W: Word

| Туре                          | Instruction | Size* | Function                                                                                                                                                                                                           |

|-------------------------------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

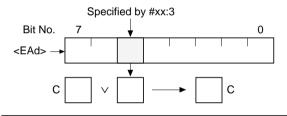

| Bit-manipulation instructions | BOR         | В     | $C \lor (\text{-bit-No.> of } \text{-}EAd\text{-}) \rightarrow C$<br>ORs the carry flag with a specified bit in a general<br>register or memory operand and stores the result in the<br>carry flag.                |

|                               | BIOR        | В     | $C \lor [\neg (\text{sbit-No.> of } (\text{EAd>})] \rightarrow C$<br>ORs the carry flag with the inverse of a specified bit in a<br>general register or memory operand and stores the<br>result in the carry flag. |

|                               |             |       | The bit number is specified by 3-bit immediate data.                                                                                                                                                               |

|                               | BXOR        | В     | $C \oplus ( of ) \rightarrow C$<br>Exclusive-ORs the carry flag with a specified bit in a general register or memory operand and stores the result in the carry flag.                                              |

|                               | BIXOR B     |       | $C \oplus [\neg ( of )] \rightarrow C$<br>Exclusive-ORs the carry flag with the inverse of a specified bit in a general register or memory operand and stores the result in the carry flag.                        |

|                               |             |       | The bit number is specified by 3-bit immediate data.                                                                                                                                                               |

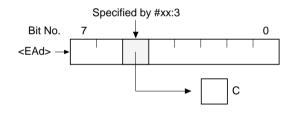

|                               | BLD         | В     | ( <bit-no.> of <ead>) <math>\rightarrow</math> C<br/>Transfers a specified bit in a general register or<br/>memory operand to the carry flag.</ead></bit-no.>                                                      |

|                               | BILD        | В     | ¬ ( <bit-no.> of <ead>) → C<br/>Transfers the inverse of a specified bit in a general<br/>register or memory operand to the carry flag.</ead></bit-no.>                                                            |

|                               |             |       | The bit number is specified by 3-bit immediate data.                                                                                                                                                               |

|                               | BST B       |       | $C \rightarrow$ ( <bit-no.> of <ead>)<br/>Transfers the carry flag value to a specified bit in a<br/>general register or memory operand.</ead></bit-no.>                                                           |

|                               | BIST        | В     | $\neg$ C $\rightarrow$ ( <bit-no.> of <ead>)<br/>Transfers the inverse of the carry flag value to a<br/>specified bit in a general register or memory operand.</ead></bit-no.>                                     |

|                               |             |       | The bit number is specified by 3-bit immediate data.                                                                                                                                                               |

Note: \* Size refers to the operand size. B: Byte

| Туре                      | Instruction | Size* | Function                                                                                                     |                               |                           |  |  |  |

|---------------------------|-------------|-------|--------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------|--|--|--|

| Branching<br>instructions | Всс         | _     | Branches to a specified address if a specified condition is true. The branching conditions are listed below. |                               |                           |  |  |  |

|                           |             |       | Mnemonic                                                                                                     | Mnemonic Description          |                           |  |  |  |

|                           |             |       | BRA(BT)                                                                                                      | Always (true)                 | Always                    |  |  |  |

|                           |             |       | BRN(BF)                                                                                                      | Never (false)                 | Never                     |  |  |  |

|                           |             |       | BHI                                                                                                          | High                          | $C \lor Z = 0$            |  |  |  |

|                           |             |       | BLS                                                                                                          | Low or same                   | C ∨ Z = 1                 |  |  |  |

|                           |             |       | Bcc(BHS)                                                                                                     | Carry clear<br>(high or same) | C = 0                     |  |  |  |

|                           |             |       | BCS(BLO)                                                                                                     | Carry set (low)               | C = 1                     |  |  |  |

|                           |             |       | BNE                                                                                                          | Not equal                     | Z = 0                     |  |  |  |

|                           |             |       | BEQ                                                                                                          | Equal                         | Z = 1                     |  |  |  |

|                           |             |       | BVC                                                                                                          | Overflow clear                | V = 0                     |  |  |  |

|                           |             |       | BVS                                                                                                          | Overflow set                  | V = 1                     |  |  |  |

|                           |             |       | BPL                                                                                                          | Plus                          | N = 0                     |  |  |  |

|                           |             |       | BMI                                                                                                          | Minus                         | N = 1                     |  |  |  |

|                           |             |       | BGE                                                                                                          | Greater or equal              | $N \oplus V = 0$          |  |  |  |

|                           |             |       | BLT                                                                                                          | Less than                     | N ⊕ V = 1                 |  |  |  |

|                           |             |       | BGT                                                                                                          | Greater than                  | $Z \lor (N \oplus V) = 0$ |  |  |  |

|                           |             |       | BLE                                                                                                          | Less or equal                 | $Z \lor (N \oplus V) = 1$ |  |  |  |

|                           | JMP         | _     | Branches unc                                                                                                 | onditionally to a specif      | ied address.              |  |  |  |

|                           | BSR         | _     | Branches to a                                                                                                | subroutine at a specif        | ied address.              |  |  |  |

|                           | JSR         | _     | Branches to a subroutine at a specified address.                                                             |                               |                           |  |  |  |

|                           | RTS         | _     | Returns from                                                                                                 | a subroutine.                 |                           |  |  |  |

Table 1-3 Instructions Classified by Function (cont)

Note: \* Size refers to the operand size.

| Туре           | Instruction | Size* | Function                                                                                                                                                                                                       |

|----------------|-------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| System control | TRAPA       | _     | Starts trap-instruction exception handling.                                                                                                                                                                    |

| instructions   | RTE         | _     | Returns from an exception-handling routine.                                                                                                                                                                    |

|                | SLEEP       | _     | Causes a transition to the power-down state.                                                                                                                                                                   |

|                | LDC         | B/W   | $(EAs) \rightarrow CCR$<br>Moves the source operand contents to the condition<br>code register. Byte transfer is performed in the #xx:8,<br>Rs addressing mode and word transfer in other<br>addressing modes. |

|                | STC         | B/W   | $CCR \rightarrow$ (EAd)<br>Transfers the CCR contents to a destination location.<br>Byte transfer is performed in the Rd addressing mode<br>and word transfer in other addressing modes.                       |

|                | ANDC        | В     | $CCR \land \#IMM \rightarrow CCR$<br>Logically ANDs the condition code register with immediate data.                                                                                                           |

|                | ORC         | В     | $CCR \lor \#IMM \rightarrow CCR$<br>Logically ORs the condition code register with immediate data.                                                                                                             |

|                | XORC        | В     | $CCR \oplus \#IMM \rightarrow CCR$<br>Logically exclusive-ORs the condition code register<br>with immediate data.                                                                                              |

|                | NOP         | —     | $PC + 2 \rightarrow PC$<br>Only increments the program counter.                                                                                                                                                |

Table 1-3 Instructions Classified by Function (cont)

Note: \* Size refers to the operand size.

B: Byte W: Word

| Туре                                  | Instruction | Size* | Function                                                                                             |

|---------------------------------------|-------------|-------|------------------------------------------------------------------------------------------------------|

| Block data<br>transfer<br>instruction | EEPMOV.B    |       | if R4L ≠ 0 then<br>Repeat @ER5 +→ @ER6 +<br>R4L – 1→R4L<br>Until R4L = 0<br>else next;               |

|                                       | EEPMOV.W    | _     | if R4 ≠ 0 then<br>Repeat @ER5 +→ @ER6 +<br>R4 – 1→R4L<br>Until R4 = 0<br>else next;                  |

|                                       |             |       | Transfers a data block according to parameters set in general registers R4L or R4, ER5, and R6.      |

|                                       |             |       | R4L or R4: size of block (bytes)<br>ER5: starting source address<br>R6: starting destination address |

|                                       |             |       | Execution of the next instruction begins as soon as the transfer is completed.                       |

Note: \* Size refers to the operand size.

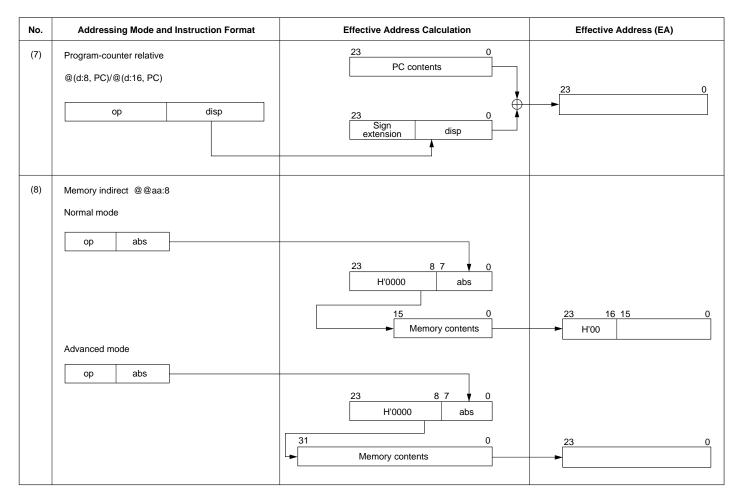

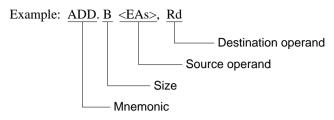

#### **1.6.4 Basic Instruction Formats**

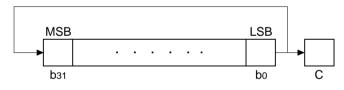

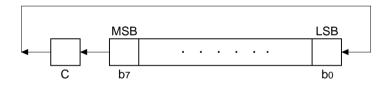

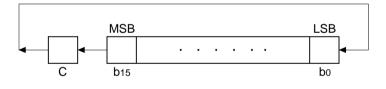

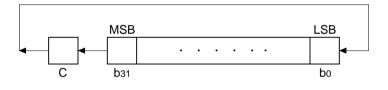

The H8/300H instructions consist of 2-byte (1-word) units. An instruction consists of an operation field (OP field), a register field (r field), an effective address extension (EA field), and a condition field (cc).

**Operation Field:** Indicates the function of the instruction, the effective address, and the operation to be carried out on the operand. The operation field always includes the first four bits of the instruction. Some instructions have two operation fields.

**Register Field:** Specifies a general register. Address registers are specified by 3 bits, data registers by 3 bits or 4 bits. Some instructions have two register fields. Some have no register field.

**Effective Address Extension:** Eight, 16, or 32 bits specifying immediate data, an absolute address, or a displacement. A 24-bit address or a displacement is treated as 32-bit data in which the first 8 bits are 0.

Condition Field: Specifies the branching condition of Bcc instructions.

Figure 1-12 shows examples of instruction formats.

|            | ор            |                       |                 |              | NOP, RTS, etc.                      |

|------------|---------------|-----------------------|-----------------|--------------|-------------------------------------|

| (2) Operat | tion field ar | nd register fi        | elds            |              |                                     |

|            | ор            |                       | rn              | rm           |                                     |

|            |               |                       |                 |              | ADD. Rn, Rm, etc.                   |

| (3) Operat |               | <b>egister fields</b> | s, and effectiv | e address ex |                                     |

| (3) Operat |               | •                     | rn              |              |                                     |

|            | (             | ор<br>EA (d           | rn              | rm           | tension<br>]<br>MOV @(d:16, Rn), Rm |

Figure 1-12 Instruction Formats

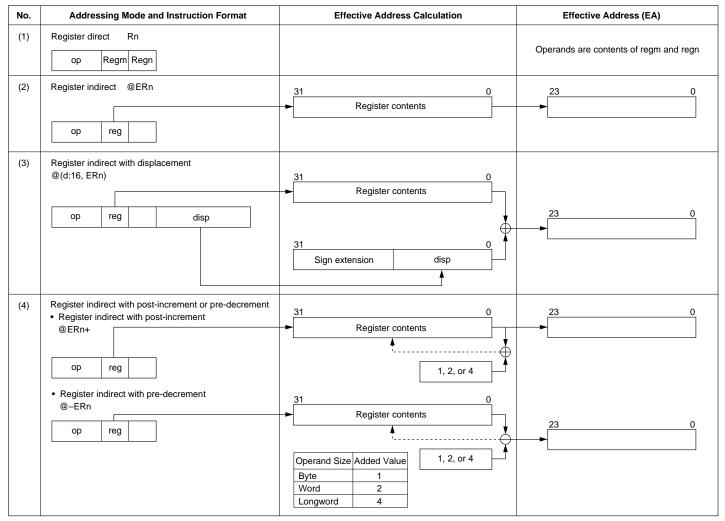

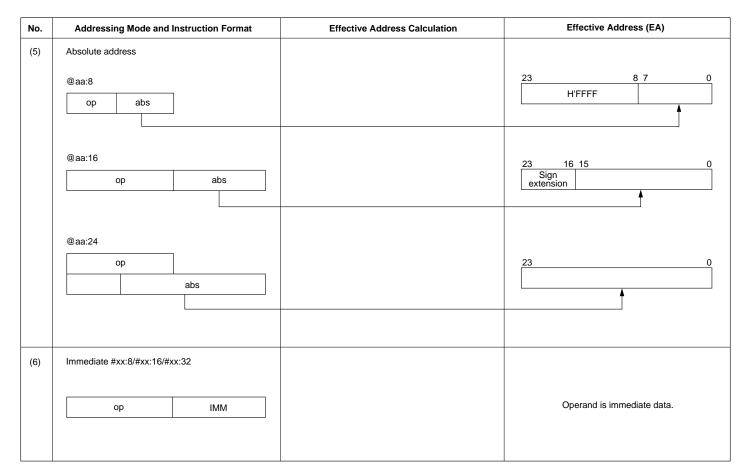

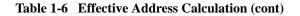

#### 1.6.5 Addressing Modes and Effective Address Calculation

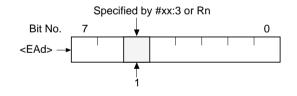

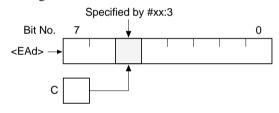

(1) Addressing Modes: The H8/300H CPU supports the eight addressing modes listed in table 1-4. Each instruction uses a subset of these addressing modes. Arithmetic and logic instructions can use the register direct and immediate modes. Data transfer instructions can use all addressing modes except program-counter relative and memory indirect. Bit manipulation instructions use register direct, register indirect, or absolute (8-bit) addressing mode to specify an operand, and register direct (BSET, BCLR, BNOT, and BTST instructions) or immediate (3-bit) addressing mode to specify a bit number in the operand.

| No. | Addressing Mode                                                               | Symbol                  |

|-----|-------------------------------------------------------------------------------|-------------------------|

| 1   | Register direct                                                               | Rn                      |

| 2   | Register indirect                                                             | @ERn                    |

| 3   | Register indirect with displacement                                           | @(d:16,ERn)/@(d:24,ERn) |

| 4   | Register indirect with post-increment<br>Register indirect with pre-decrement | @ERn+<br>@-ERn          |

| 5   | Absolute address                                                              | @aa:8/@aa:16/@aa:24     |

| 6   | Immediate                                                                     | #xx:8/#xx:16/#xx:32     |

| 7   | Program-counter relative                                                      | @(d:8,PC)/@(d:16,PC)    |

| 8   | Memory indirect                                                               | @@aa:8                  |