HD641016 USER'S MANUAL

#U15

# HD641016 USER'S MANUAL

When using this document, keep the following in mind:

- This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# Section 1. Contents

| Section      | on 1. Contents                                     | 1        |  |  |

|--------------|----------------------------------------------------|----------|--|--|

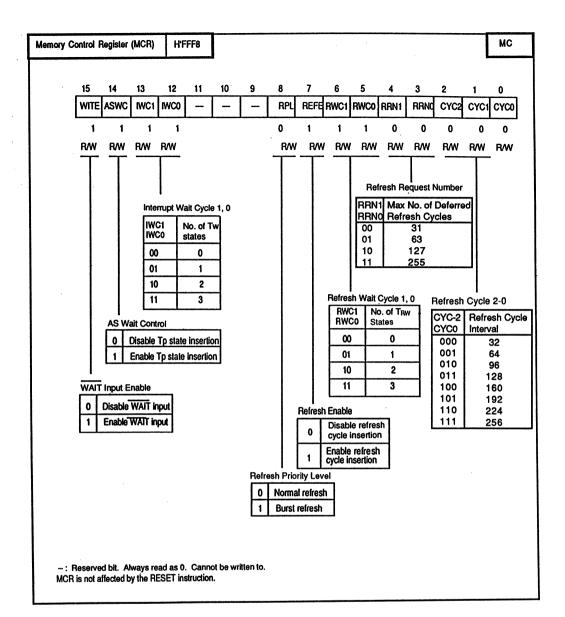

| Section      | on 2. Overview                                     | 9        |  |  |

| 2.1          | Description                                        | 9        |  |  |

| 2.2 Features |                                                    |          |  |  |

| 2.2          |                                                    | 9        |  |  |

|              | 2.2.1 CPU Features 2.2.2 On-Chip Hardware Features |          |  |  |

|              | 2.2.2 On-Chip riardware readures                   | 10<br>10 |  |  |

|              | 2.2.3 Other Features                               | 11       |  |  |

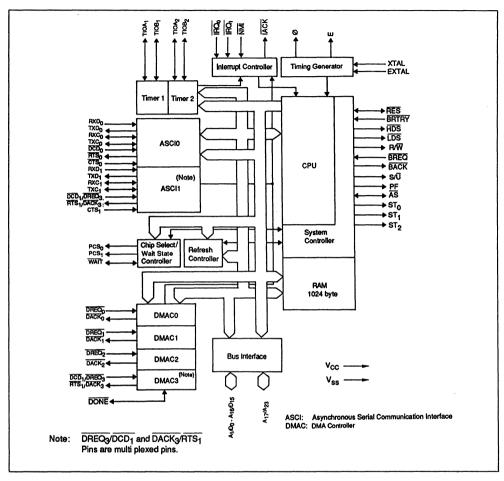

| 2.3          | Block Diagram                                      | 12       |  |  |

| 2.5          | Block Diagram                                      | 12       |  |  |

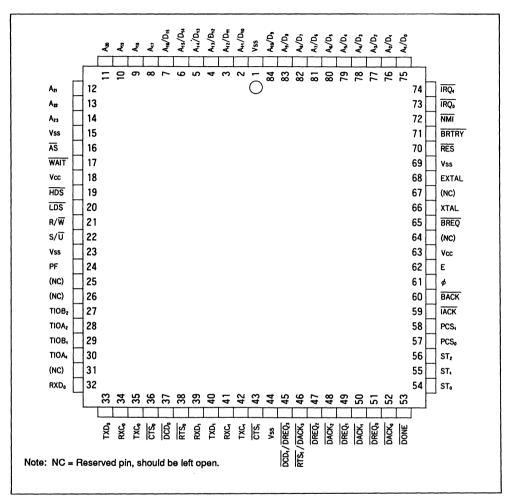

| Section      | on 3. Pin Description                              | 13       |  |  |

| 3.1          | Multiplexed Pins                                   | 17       |  |  |

| 3.2          | Pin Function                                       | 17       |  |  |

| 3.2          |                                                    | 17       |  |  |

|              | 3.2.1 Power Supply                                 | 17       |  |  |

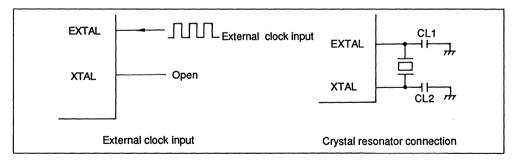

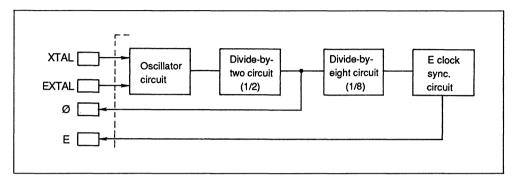

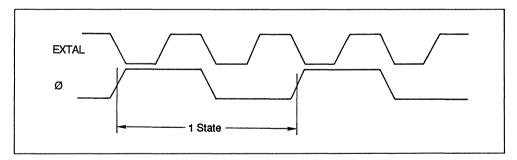

|              | 3.2.2 Clock Signals                                | 18       |  |  |

|              | 3.2.3 System Control                               | 18       |  |  |

|              | 3.2.5 Memory Interface                             | 19       |  |  |

|              | 3.2.6 Status                                       | 19       |  |  |

|              | 3.2.7 Address and Data Bus                         | 20       |  |  |

|              | 3.2.8 DMAC                                         | 20       |  |  |

|              | 3.2.10 Asynchronous Serial I/O (ASCI)              | 21       |  |  |

|              | 3.2.10 Asynchronous Serial I/O (ASCI)              | 21       |  |  |

|              | 3.2.11 Chip Select                                 | 21       |  |  |

| Section      | on 4. CPU                                          | 22       |  |  |

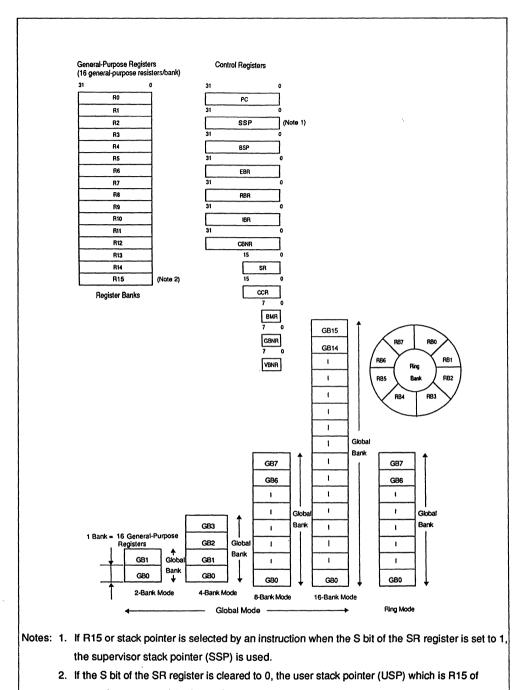

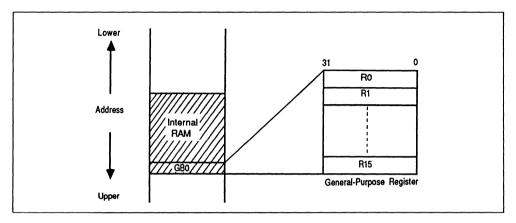

| 4.1          | Programming Model                                  | 22       |  |  |

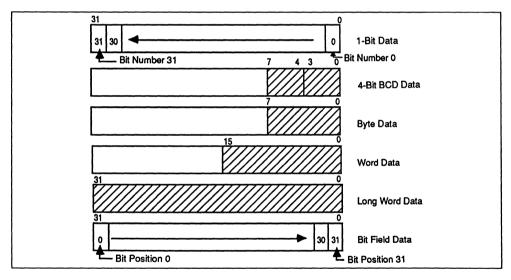

| 4.2          | Data Types                                         | 24       |  |  |

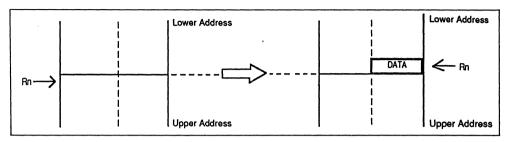

|              | 4.2.1 General-Purpose Register Data Organization   | 24       |  |  |

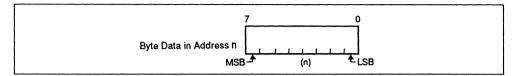

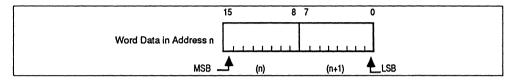

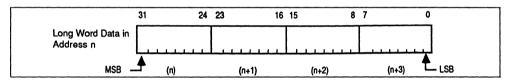

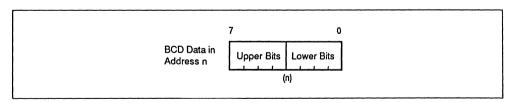

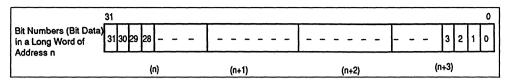

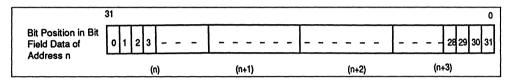

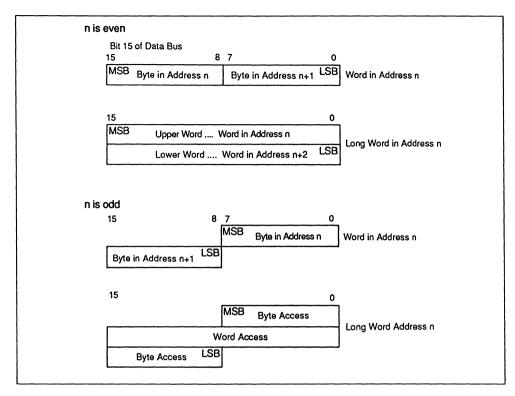

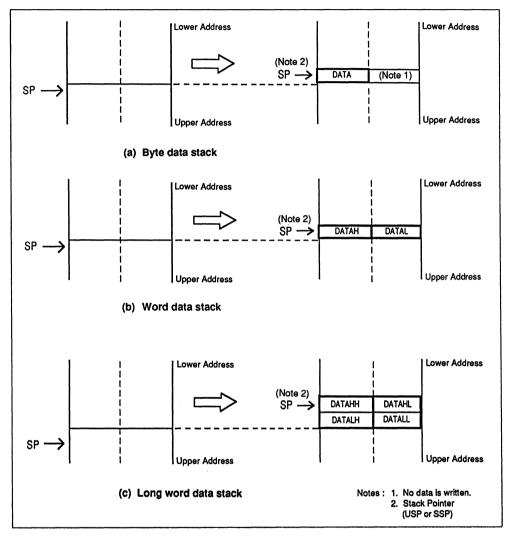

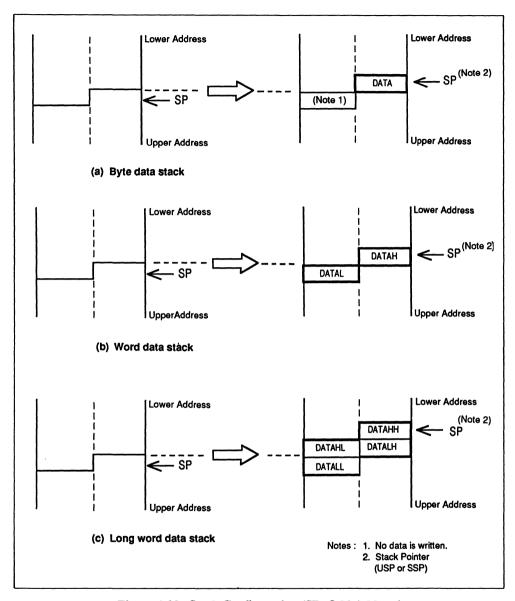

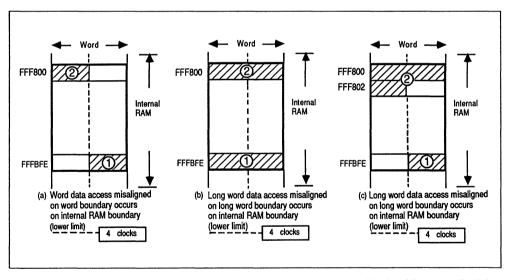

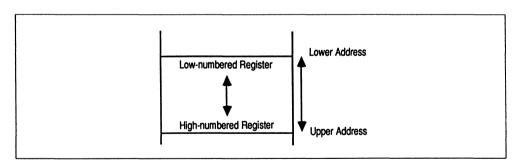

|              | 4.2.2 Memory Data Organization                     | 25       |  |  |

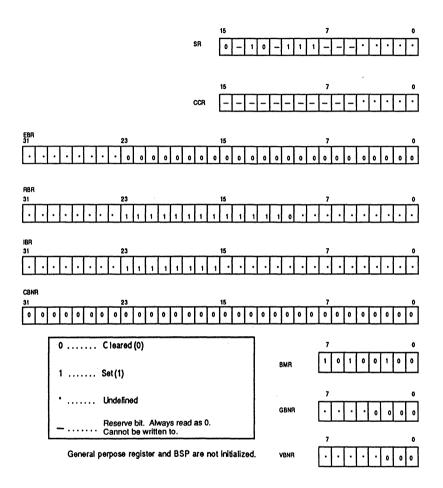

| 4.3          | Registers                                          | 28       |  |  |

| 1.5          | 4.3.1 Program Counter (PC)                         | 28       |  |  |

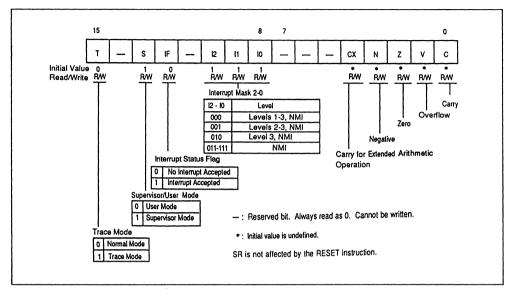

|              | 4.3.2 Status Register (SR)                         | 29       |  |  |

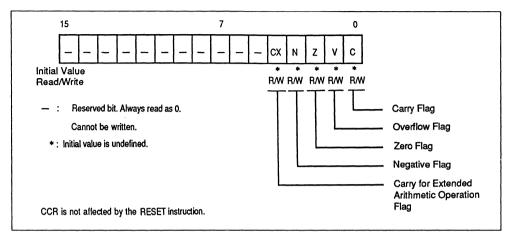

|              | 4.3.3 Condition Code Register (CCR)                | 31       |  |  |

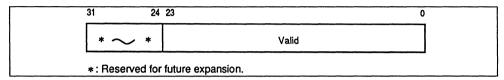

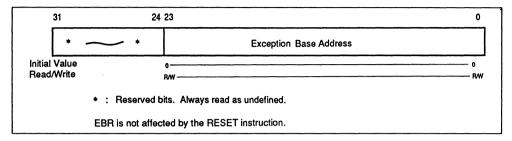

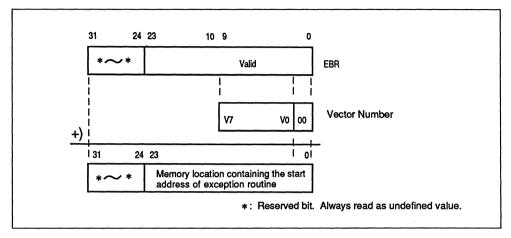

|              | 4.3.4 Exception Vector Base Register (EBR)         | 32       |  |  |

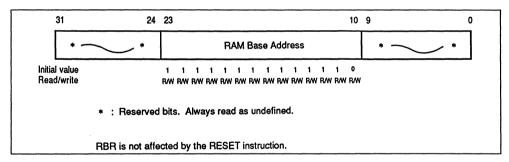

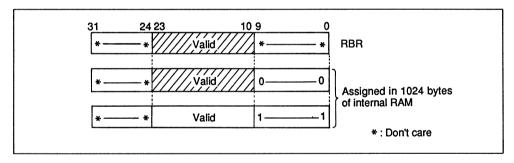

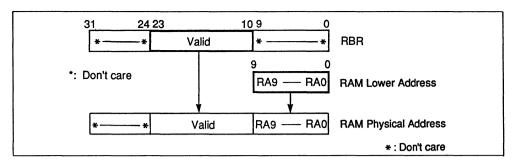

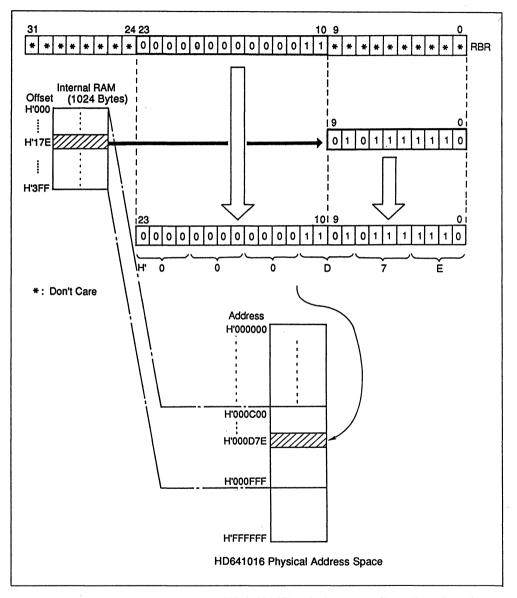

|              | 4.3.5 RAM Base Register (RBR)                      | 32       |  |  |

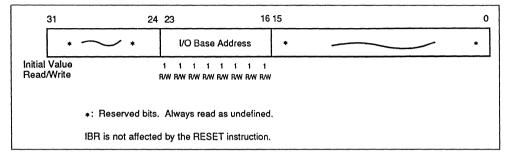

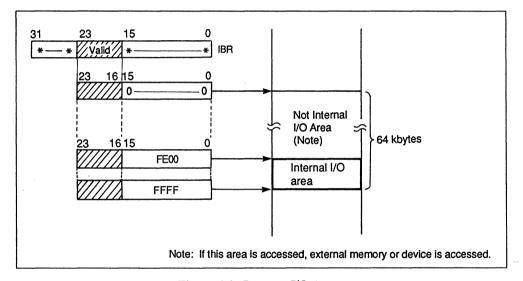

|              | 4.3.6 I/O Base Register (IBR)                      | 33       |  |  |

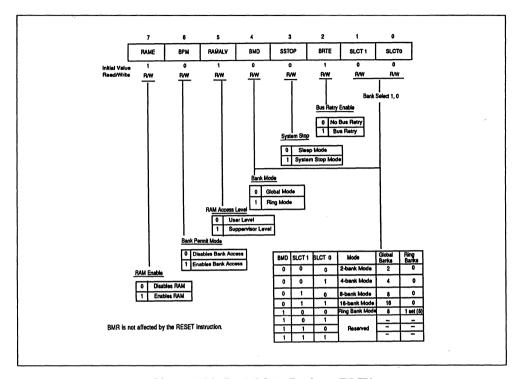

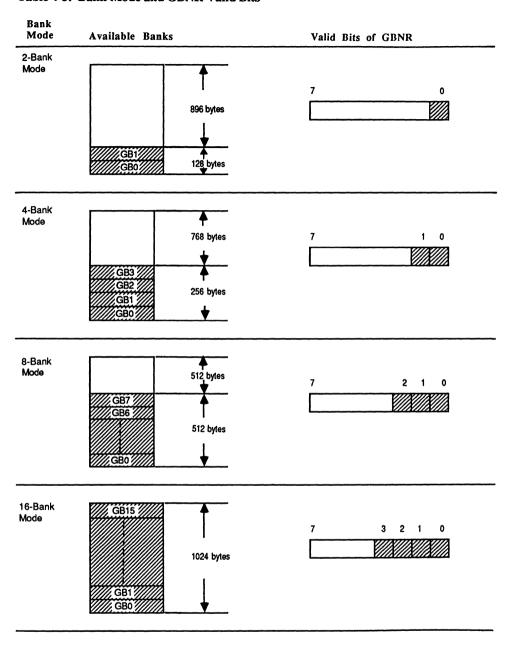

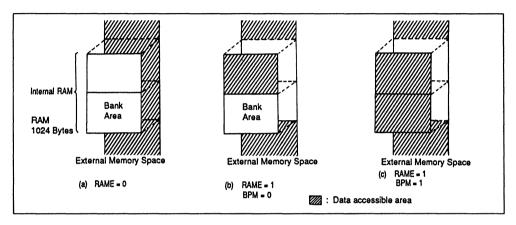

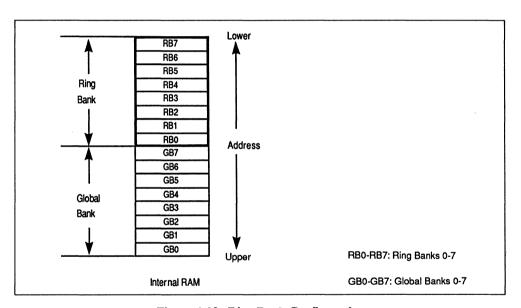

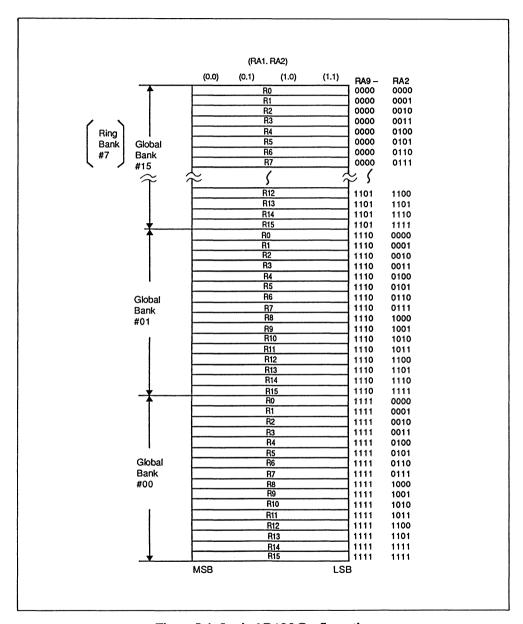

|              | 4.3.7 Bank Mode Register (BMR)                     | 34       |  |  |

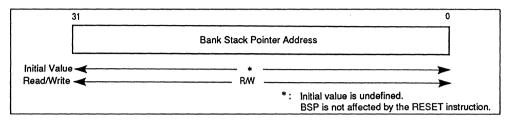

|              | 4.3.8 Bank Stack Pointer (BSP)                     | 36       |  |  |

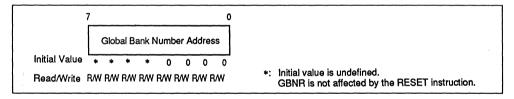

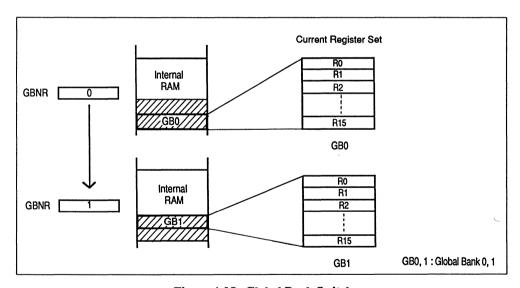

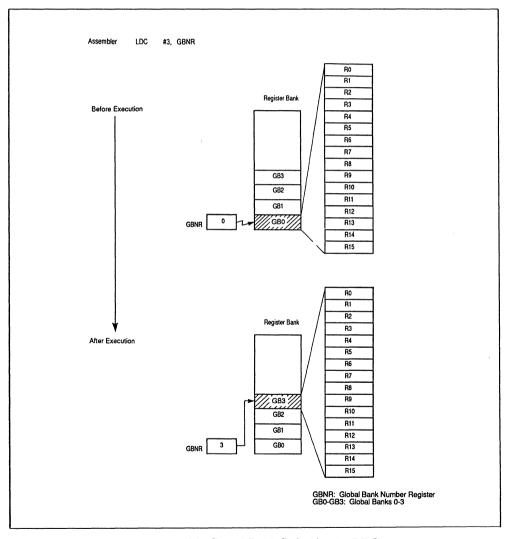

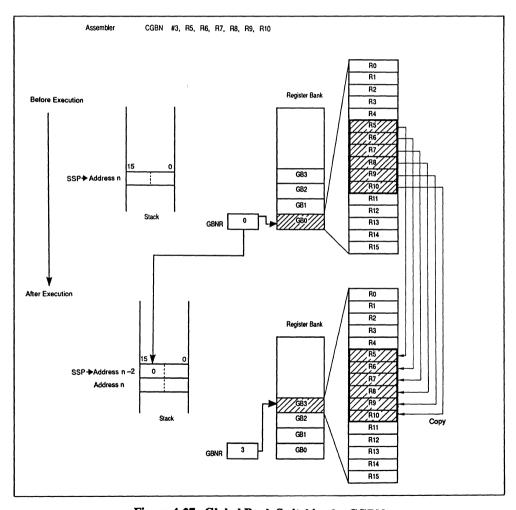

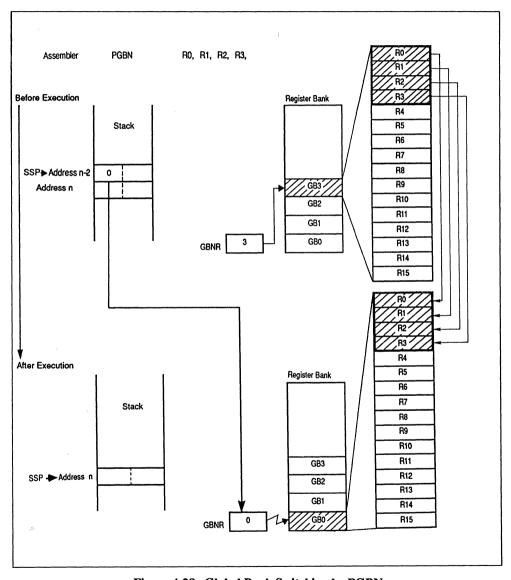

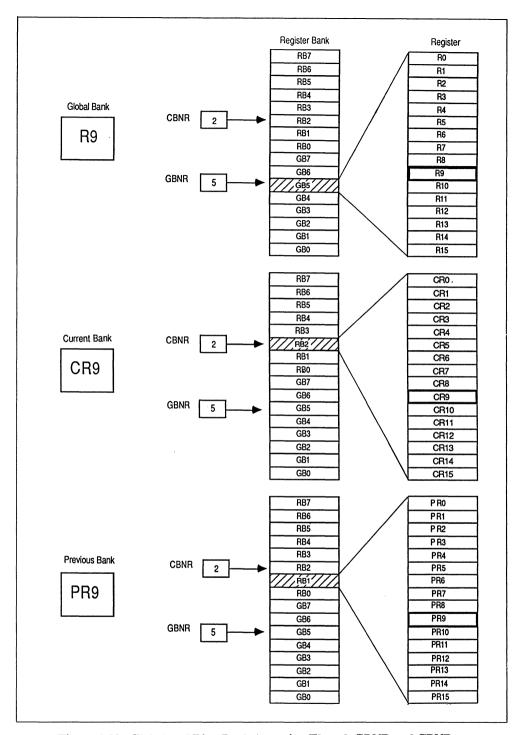

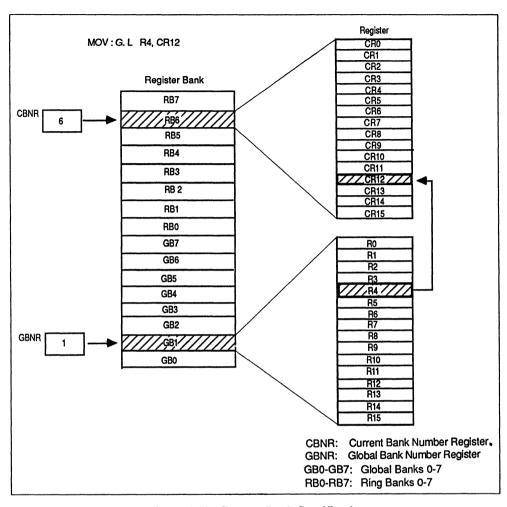

|              | 4.3.9 Global Bank Number Register (GBNR)           | 36       |  |  |

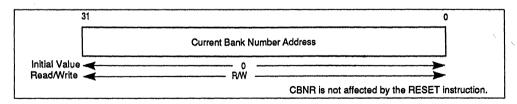

|              | 4.3.10 Current Bank Number Register (CBNR)         | 36       |  |  |

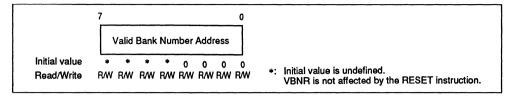

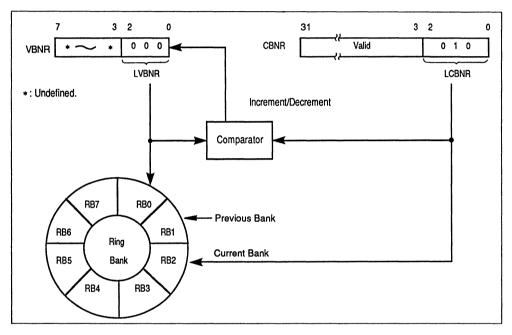

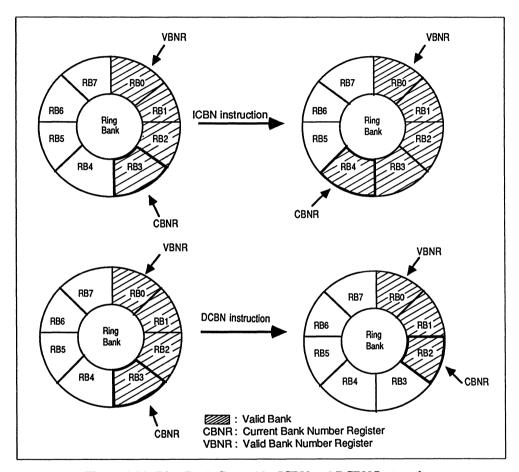

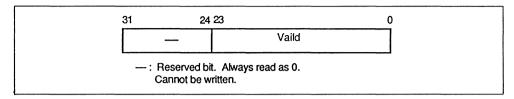

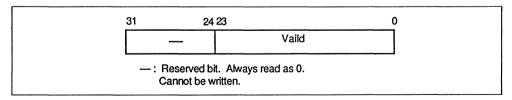

|              | 4.3.11 Valid Bank Number Register (VBNR)           | 37       |  |  |

|              |                                                    | 37<br>37 |  |  |

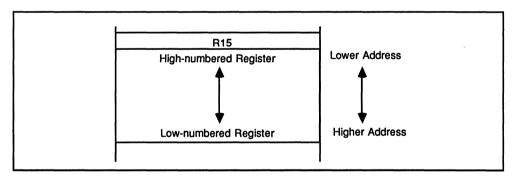

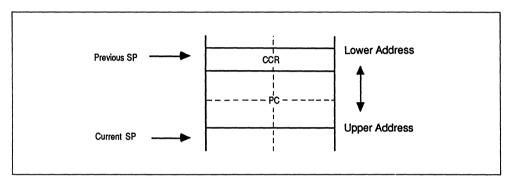

|              | 4.3.13 R15 and the Stack Pointer                   |          |  |  |

|              | T.J.IT DINGE CUILIEUIUUUI                          |          |  |  |

| 2      |

|--------|

| 8      |

|        |

| 8      |

| 8      |

| 9      |

| 8      |

| 2      |

| 2      |

| 2      |

| 3      |

| 5      |

| 9      |

| 0      |

| 4<br>8 |

| 9      |

| 0      |

| 3      |

| 1      |

| 3      |

| 6      |

| 6      |

| 7      |

| 9      |

| 9      |

| ó      |

| 5      |

| 6      |

| 7      |

| 8      |

| 9      |

| 2      |

|        |

| 4      |

| 4      |

| 7      |

| 8      |

| 8      |

| _      |

| 2      |

| 2      |

| 3      |

| 1      |

|        |

| 1      |

| 2      |

| 2      |

| 2      |

|        |

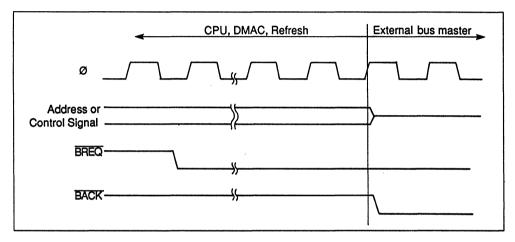

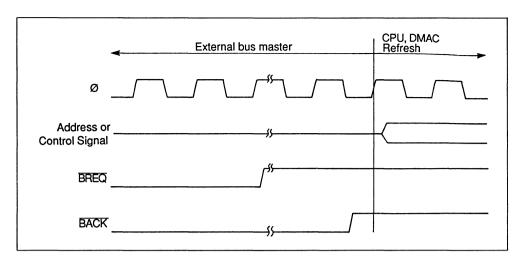

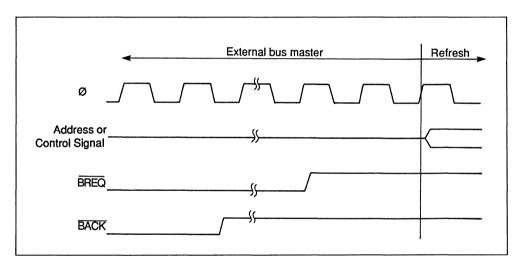

|                                         | 7.3.2 DMAC Is Current Bus Master                                   | 173<br>174<br>174 |

|-----------------------------------------|--------------------------------------------------------------------|-------------------|

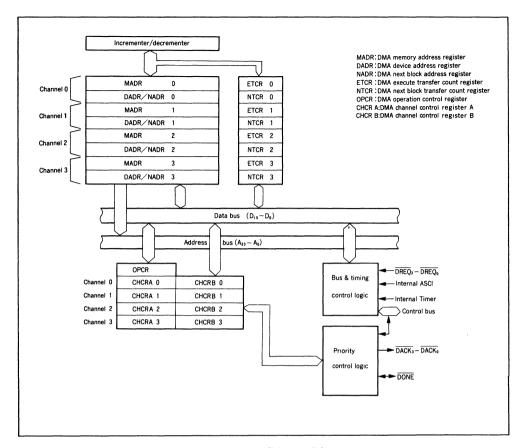

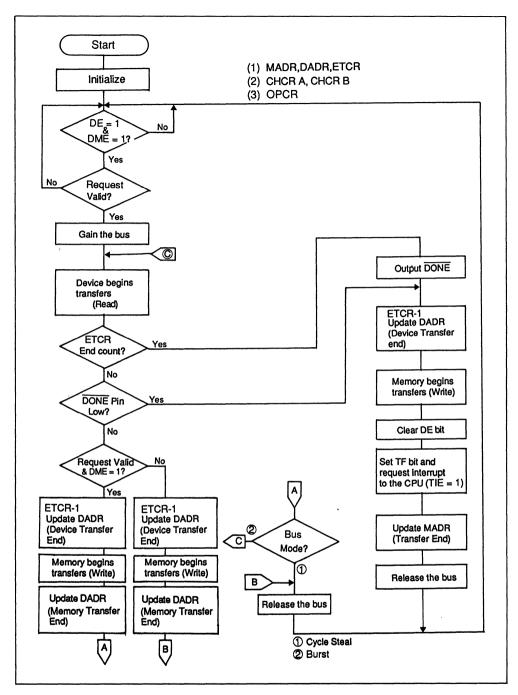

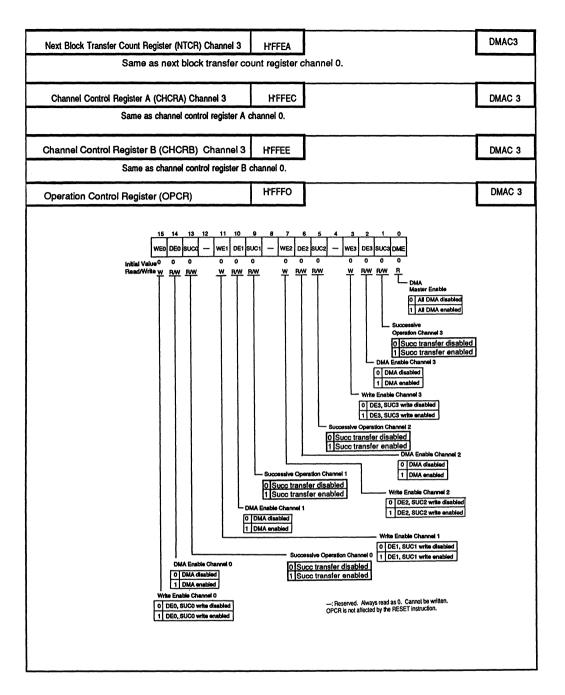

| Sectio                                  | n 8. DMA Controller (DMAC)                                         | 175               |

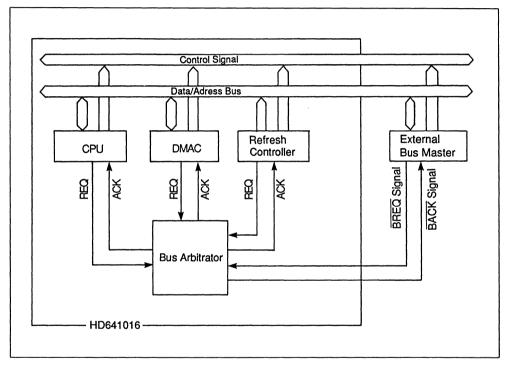

| 8.1                                     | Overview                                                           | 175               |

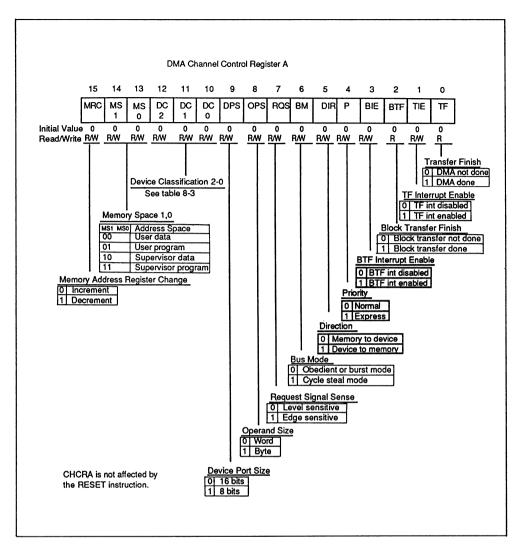

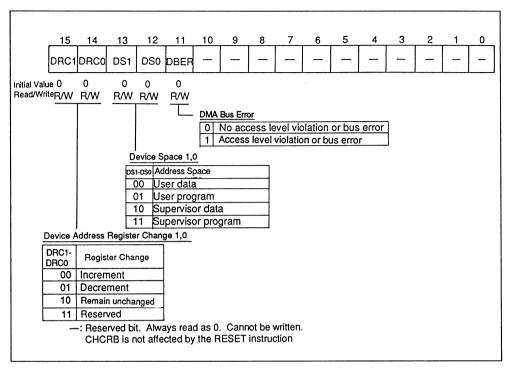

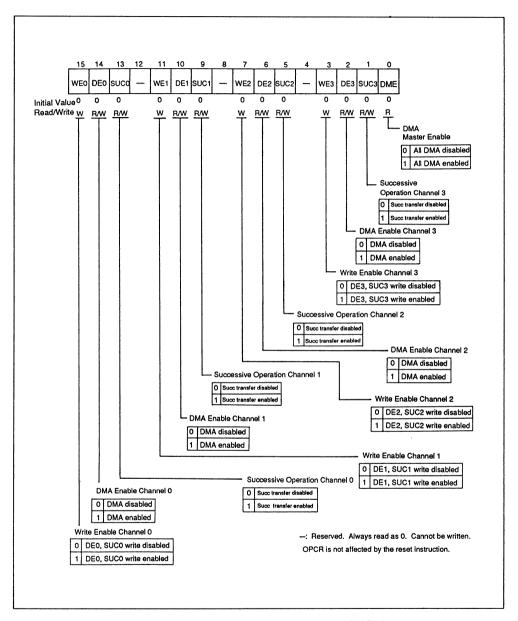

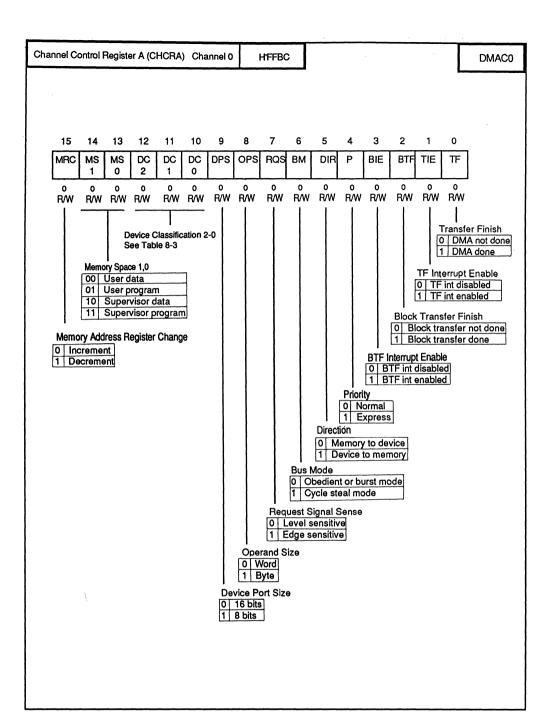

| 8.2                                     | DMAC Registers                                                     | 177               |

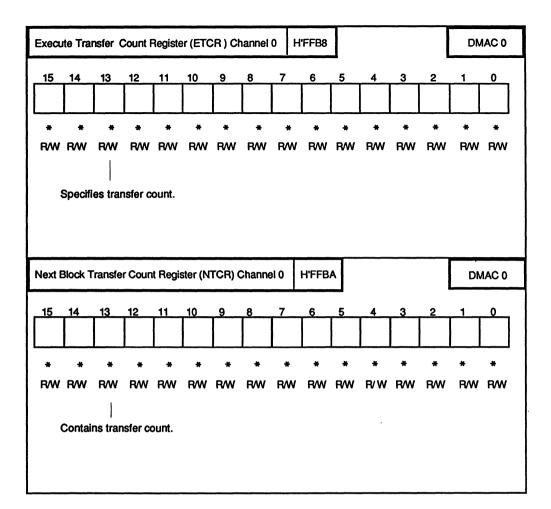

|                                         | 8.2.1 Memory Address Register Channels 3-0 (MADR3-MADR0)           | 178               |

|                                         | 8.2.2 Device Address Register/Next Block Address Register Channels |                   |

|                                         | 3-0 (DADR0/NADR3-DADR0/NADR0)                                      | 179               |

|                                         | 8.2.4 Next Block Transfer Count Register Channels 3-0              | 180<br>180        |

|                                         | (NTCR3-NTCR0)                                                      | 180               |

|                                         | 8.2.6 Channel Control Register B Channels 3-0 (CHCRB3-CHCRB0)      | 185               |

| 0.2                                     | 8.2.7 Operation Control Register (OPCR)                            | 187               |

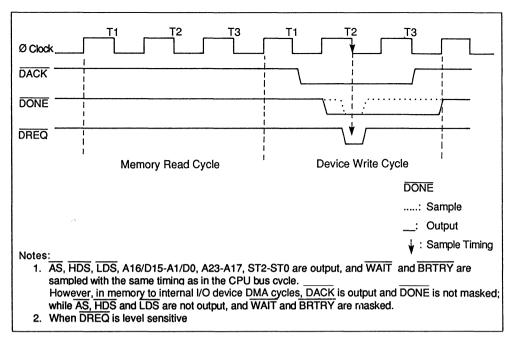

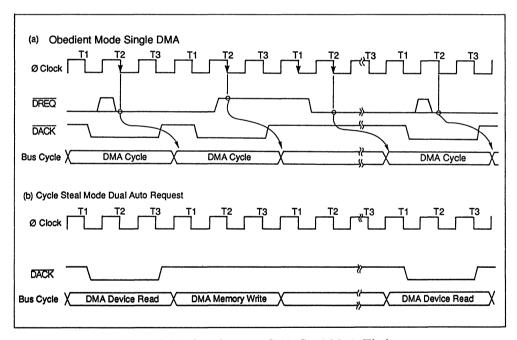

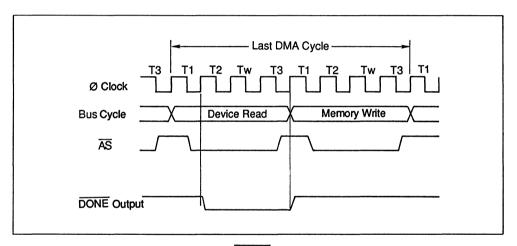

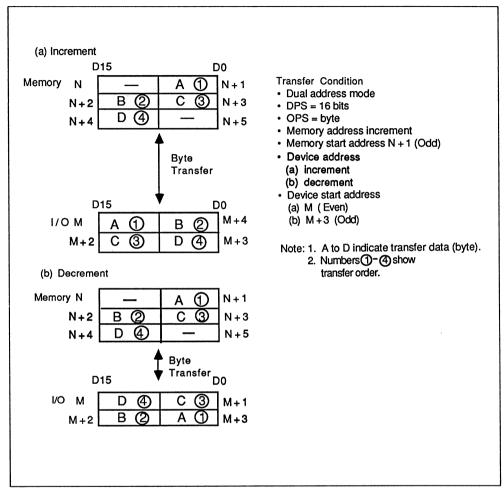

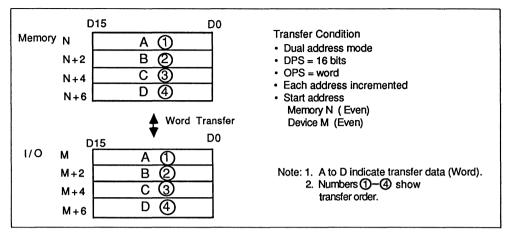

| 8.3                                     | DMA Operation and Procedures                                       | 188               |

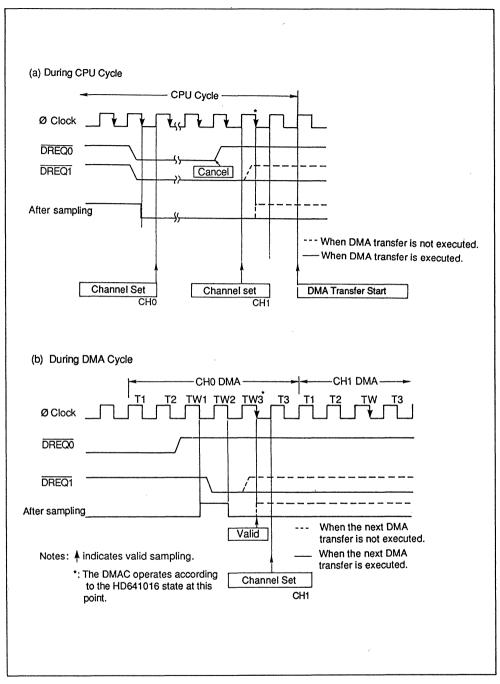

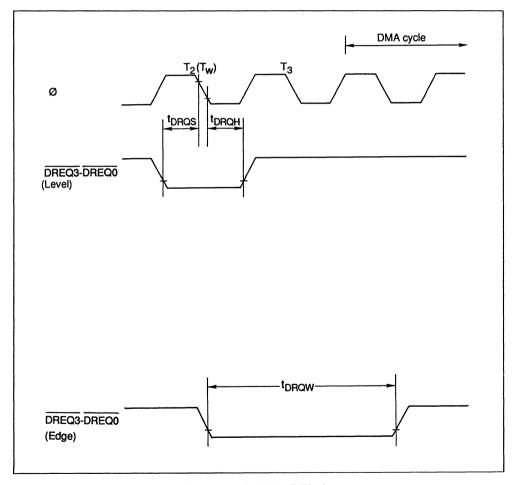

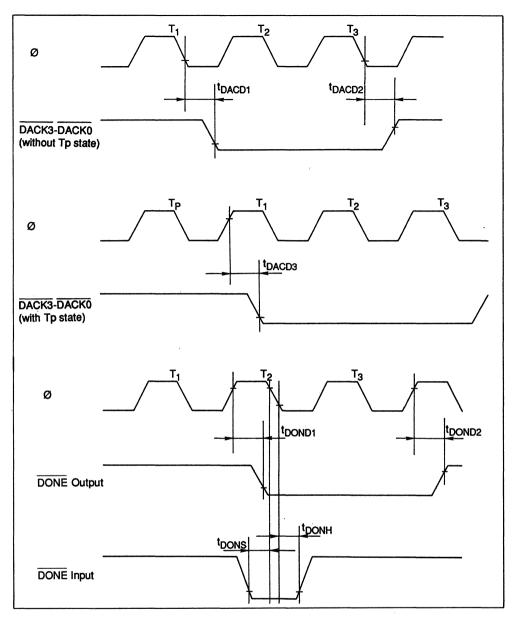

|                                         | 8.3.1 Transfer Requests 8.3.2 Applicable Devices                   | 188<br>191        |

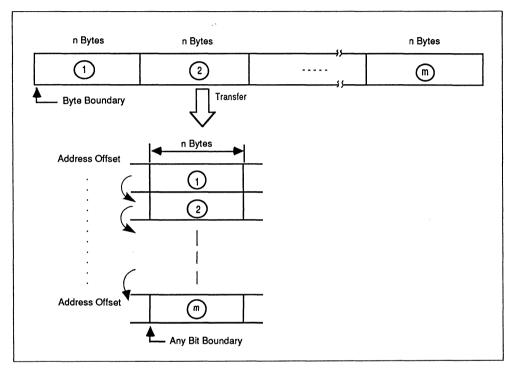

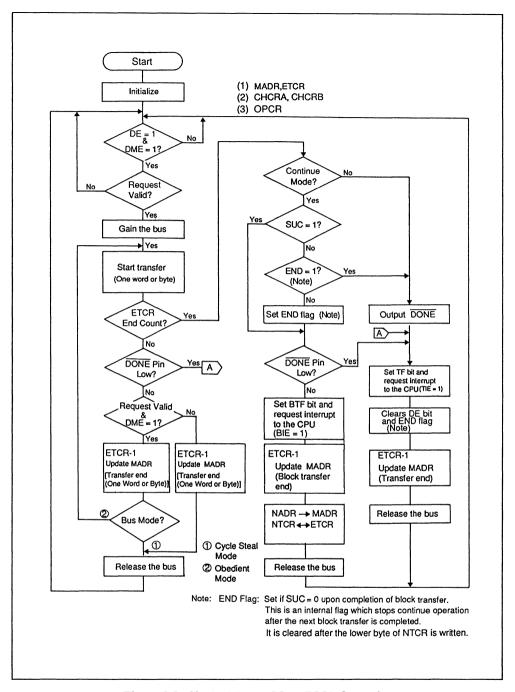

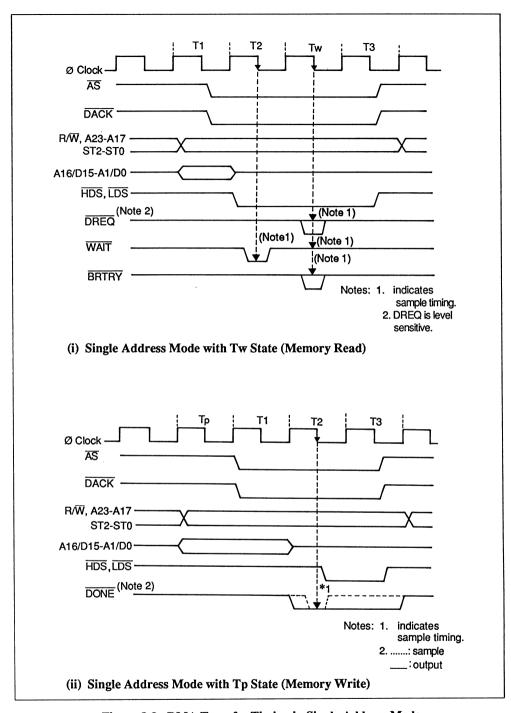

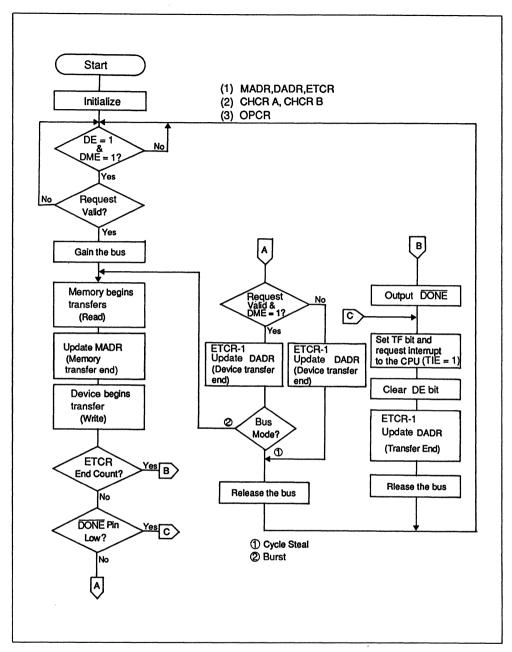

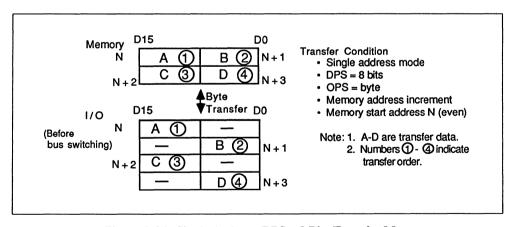

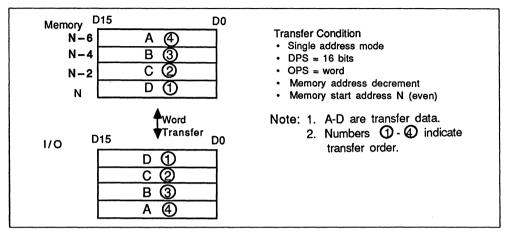

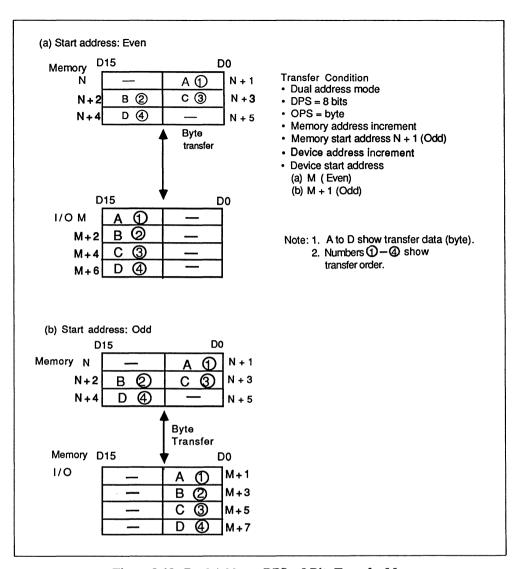

|                                         | 8.3.3 Data Transfer                                                | 191               |

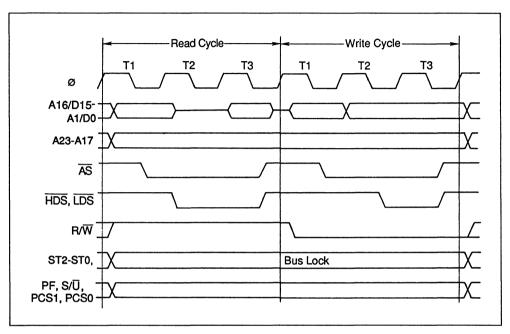

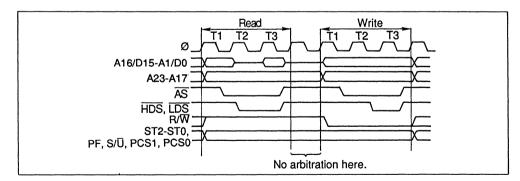

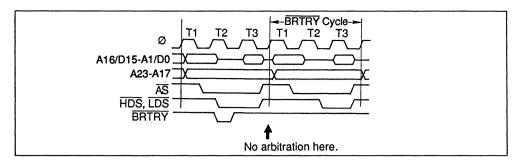

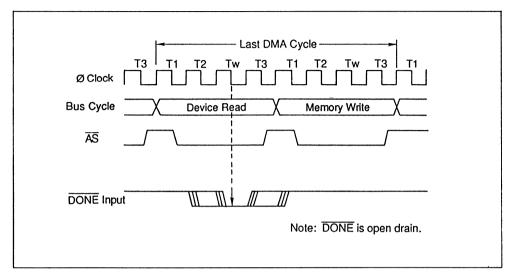

|                                         | 8.3.4 Bus Mode                                                     | 198               |

|                                         | 8.3.5 Continue Operation                                           | 200               |

|                                         | 8.3.6 End Operation                                                | 200               |

|                                         | 8.3.7 Address Update and Transfer Map 8.3.8 DMA Priority           | 202<br>207        |

| 8.4                                     | Internal DMA                                                       | 208               |

| • • • • • • • • • • • • • • • • • • • • | 8.4.1 Internal ASCI and DMAC                                       | 208               |

|                                         | 8.4.2 Internal Timer and DMAC                                      | 209               |

| 8.5                                     | DMA Transfer Stop by NMI and Bus Error                             | 209               |

| 8.6                                     | DMAC and Reset                                                     | 210               |

| 8.7                                     | DMAC Notes                                                         | 210               |

|                                         |                                                                    |                   |

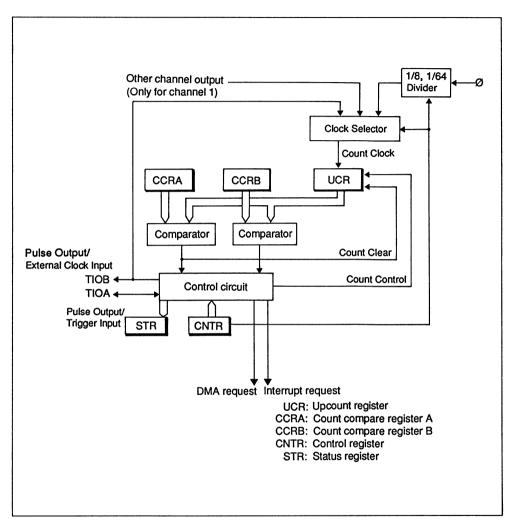

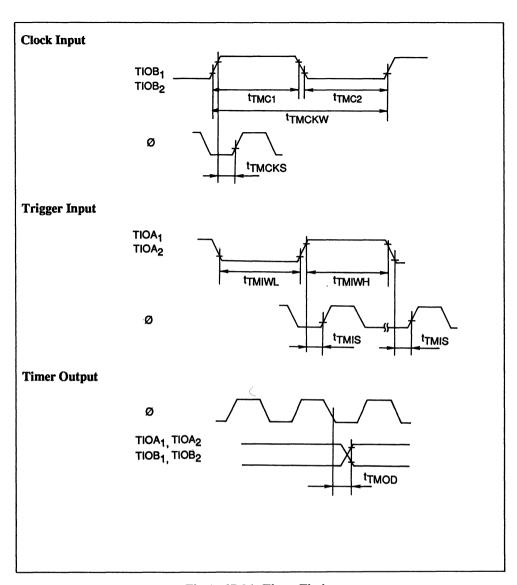

| Sectio                                  | n 9. Timers                                                        | 212               |

| 9.1                                     | Features                                                           | 212               |

| )                                       | 9.1.1 Multifunction Timers                                         | 212               |

|                                         | 9.1.2 Block Diagram                                                | 213               |

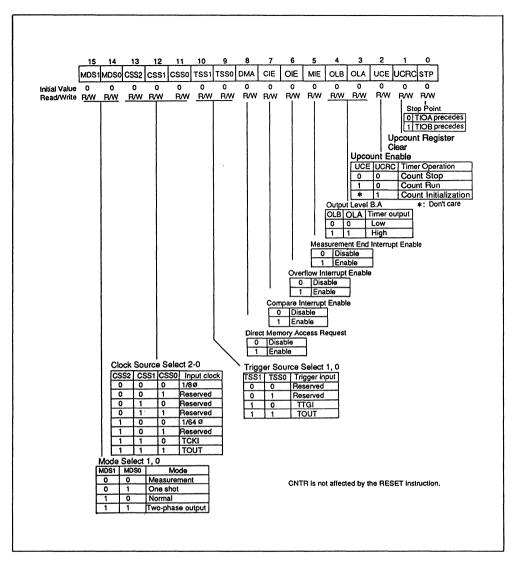

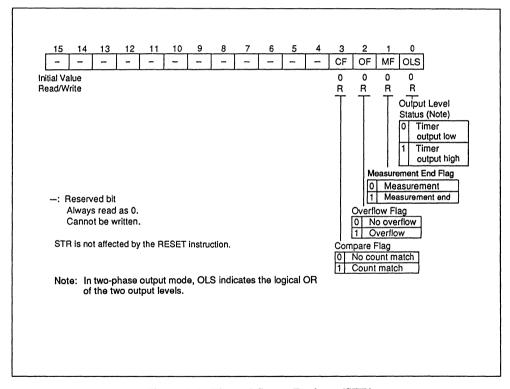

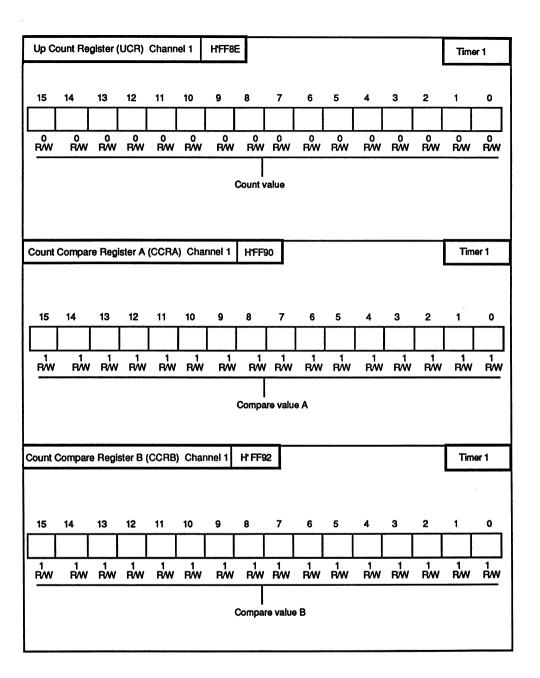

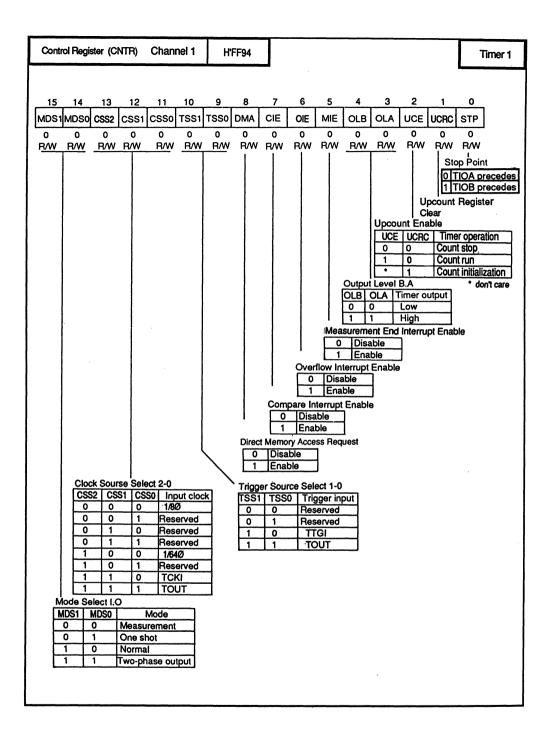

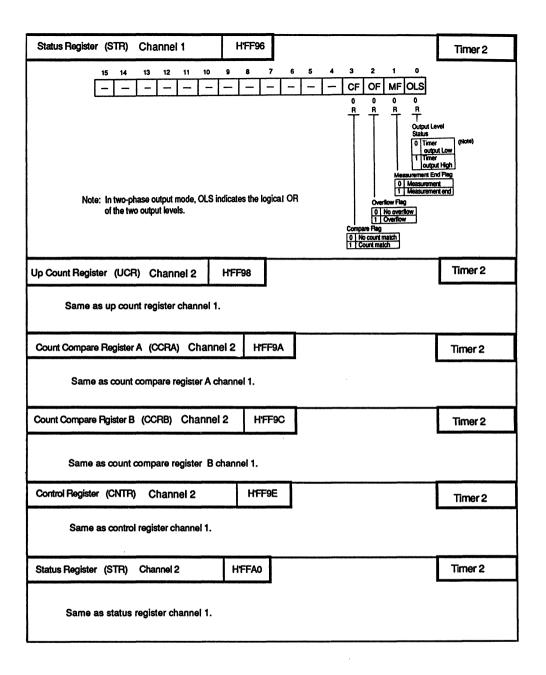

| 9.2                                     | Timer Registers                                                    | 214               |

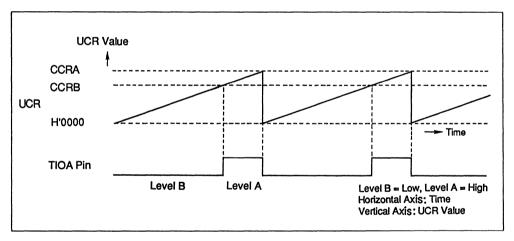

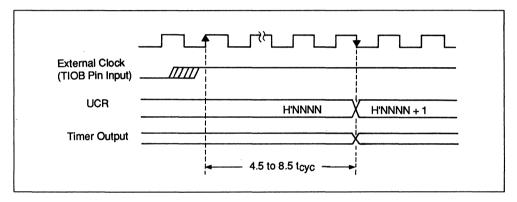

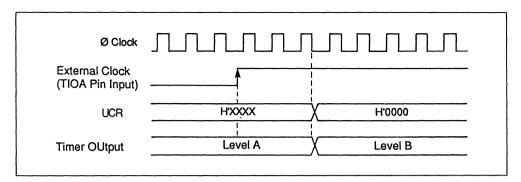

|                                         | 9.2.1 Upcount Registers (UCR)                                      | 214.              |

|                                         | 9.2.2 Count Compare Registers A,B (CCRA, CCRB)                     | 214               |

|                                         | 9.2.3 Control Registers (CNTR)                                     | 214               |

| 9.3                                     |                                                                    |                   |

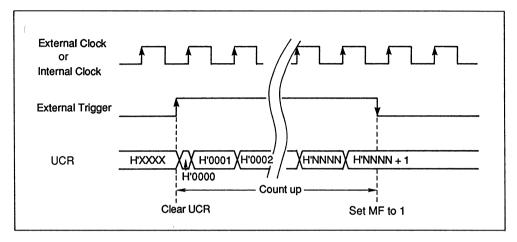

| 9.5                                     | Timer Operation 9.3.1 Normal Mode                                  | 221               |

|                                         | 9.3.2 Measurement Mode                                             | 221               |

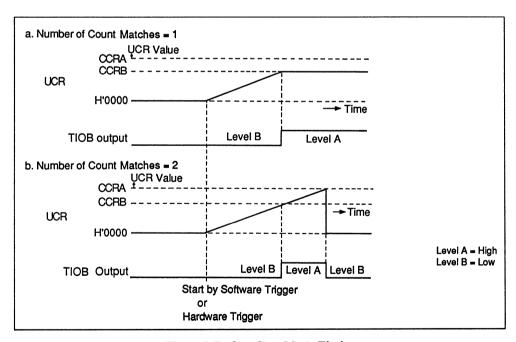

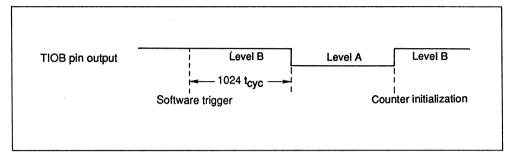

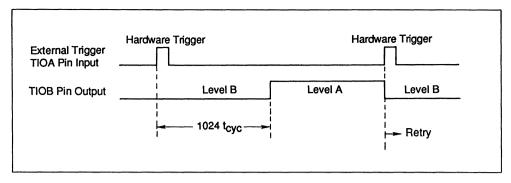

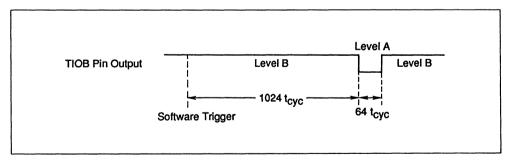

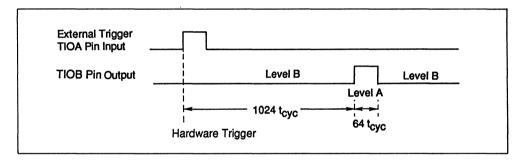

|                                         | 9.3.3 One-Shot Mode                                                | 222               |

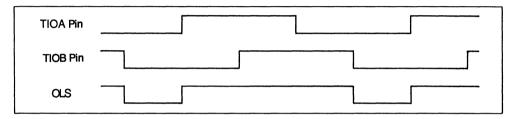

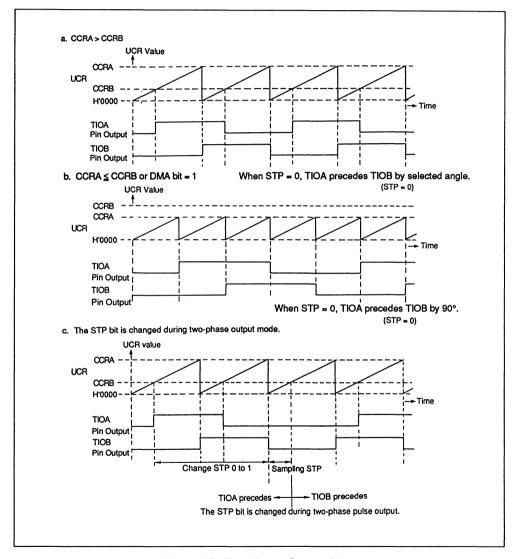

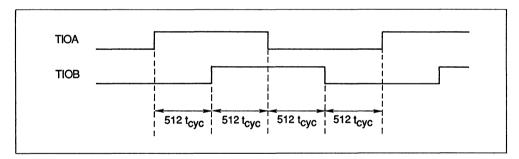

| 0.4                                     | 9.3.4 Two-Phase Output Mode                                        | 224               |

| 9.4                                     | Timer Application                                                  | 225               |

|                                         | 9.4.1 Interval Timer                                               | 225<br>226        |

|                                         | 9.4.2 Event Counter                                                | 226<br>226        |

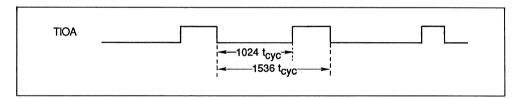

|                                         | 9.4.4 Two-Phase Pulse Generator                                    | 226               |

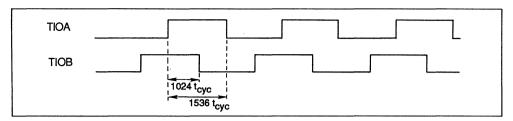

|                                         | 9.4.5 ±90° Two-Phase Pulse Generator                               | 227               |

|                                         | 0.4.6 Pulse Width Measurement                                      | 228               |

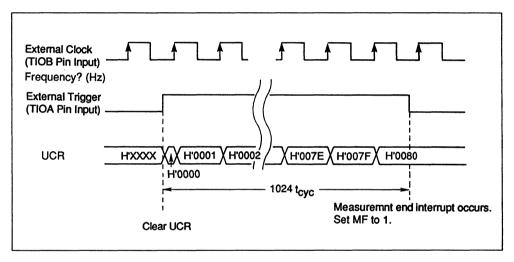

|         | 9.4.7 Frequency Measurement                                   | 230        |

|---------|---------------------------------------------------------------|------------|

| 9.5     | 9.4.11 Hardware-Triggered One-Shot (2) Timer and On-Chip DMAC | 232        |

|         |                                                               |            |

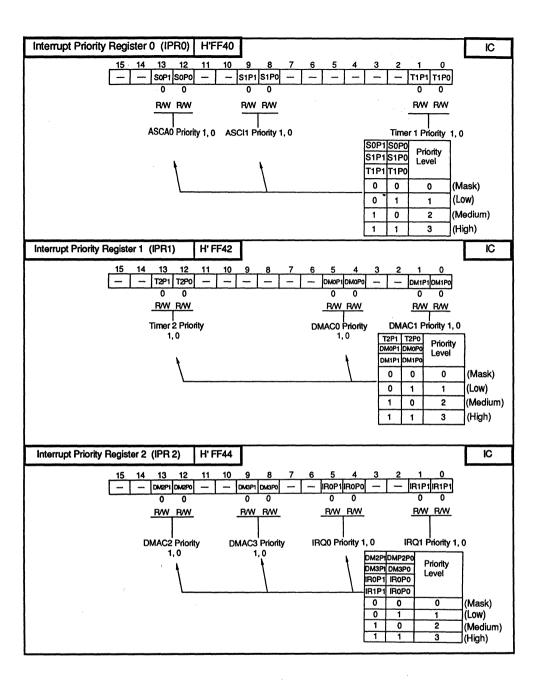

| 9.6     | Timer Interrupt Priority                                      | 233        |

| 9.7     | Timer and Reset                                               |            |

| 9.8     | Timer Notes                                                   | 234        |

|         |                                                               |            |

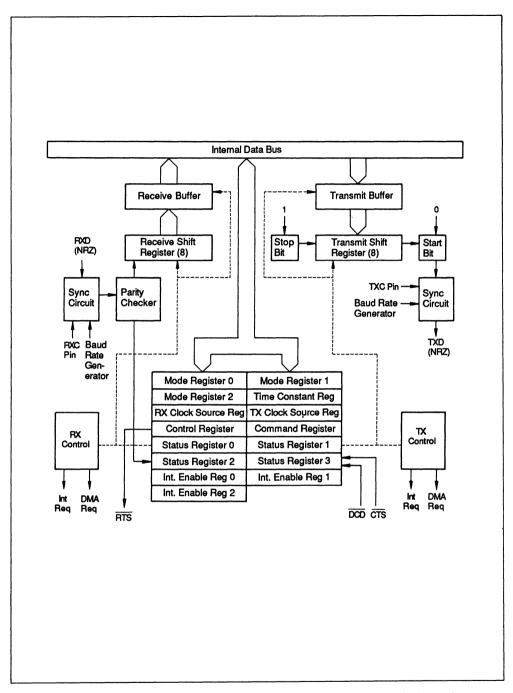

| Section | n 10. Asynchronous Serial Communication                       |            |

|         | Interface                                                     | 236        |

| 10.1    |                                                               |            |

|         | Overview                                                      | 236        |

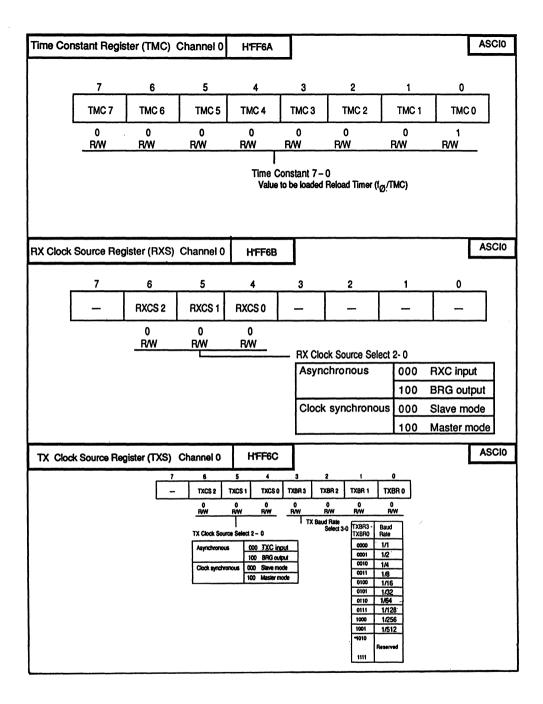

| 10.2    | ASCI Registers                                                | 238        |

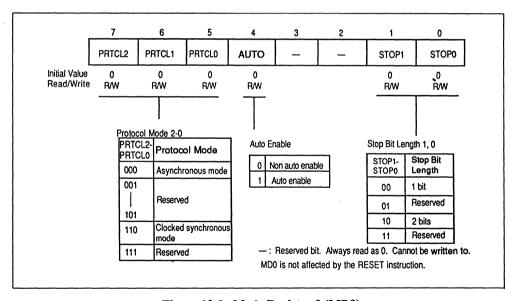

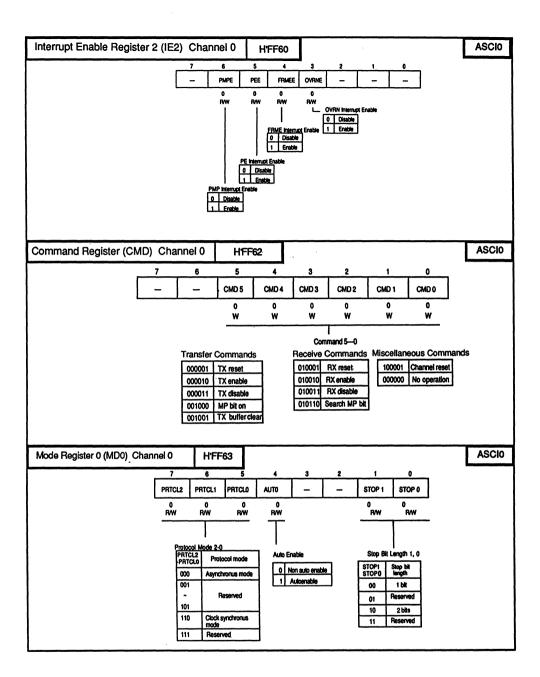

|         | 10.2.1 Mode Register 0 (MD0)                                  | 240        |

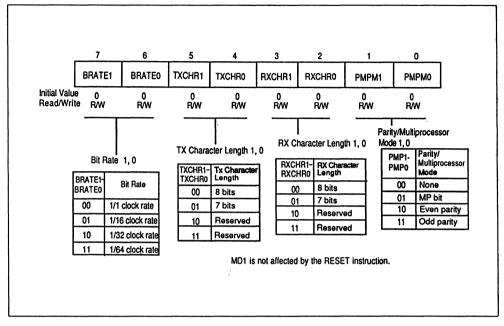

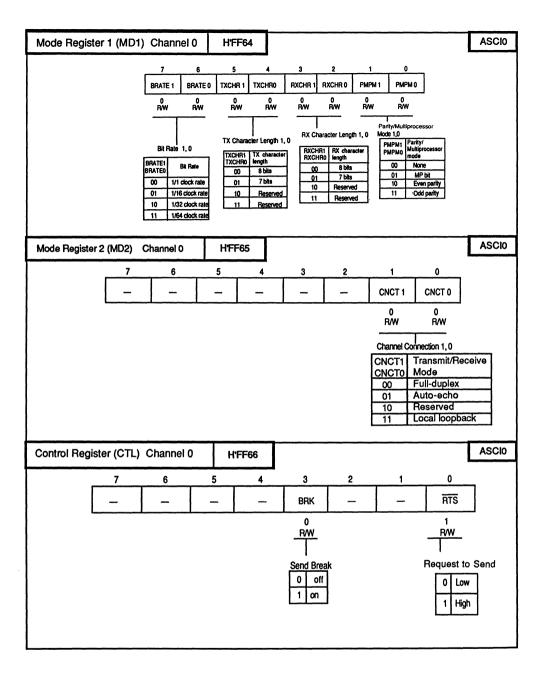

|         | 10.2.2 Mode Register 1 (MD1)                                  | 243        |

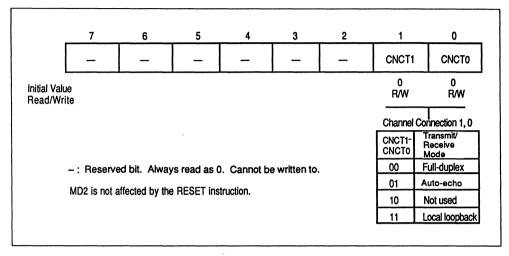

|         | 10.2.3 Mode Register 2 (MD2)                                  | 246        |

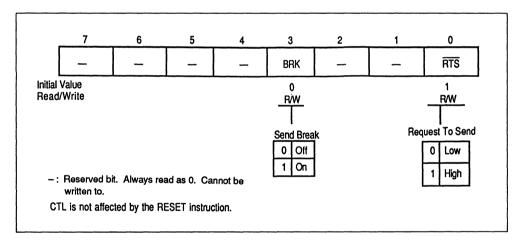

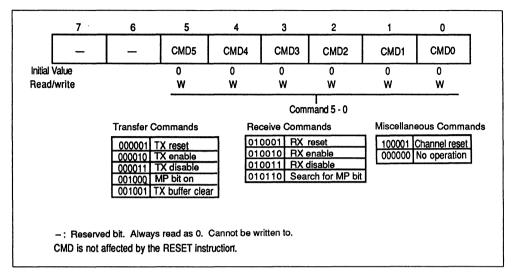

|         | 10.2.4 Control Register (CTL)                                 | 247        |

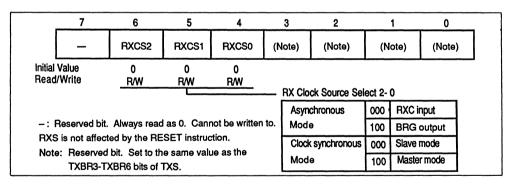

|         | 10.2.5 RX Clock Source Register (RXS)                         | 248        |

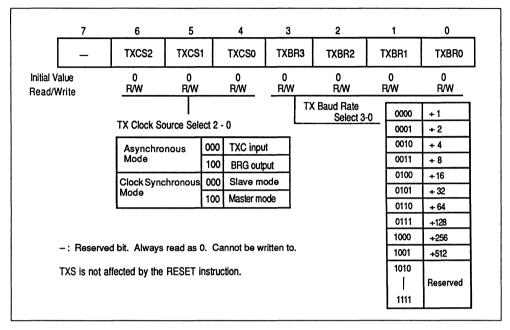

|         | 10.2.6 TX Clock Source Register (TXS)                         | 251<br>254 |

|         | 10.2.8 Command Register (CMD)                                 | 255        |

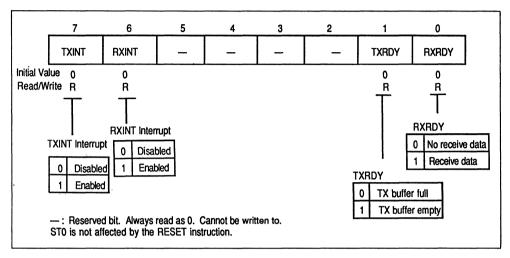

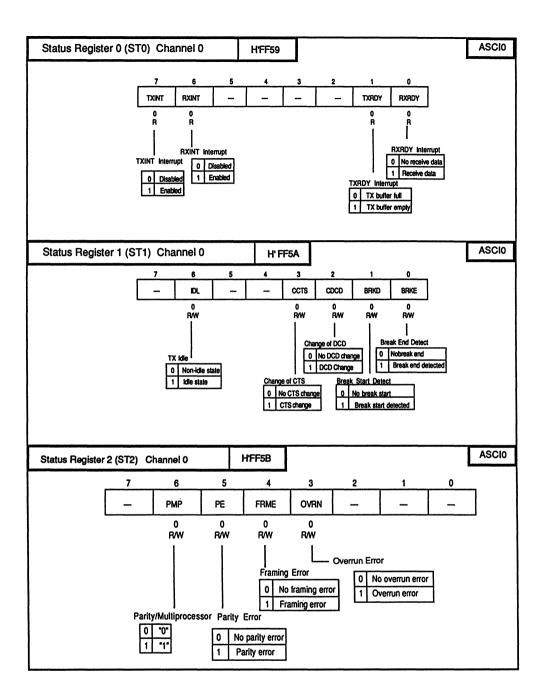

|         | 10.2.9 Status Register 0 (ST0)                                | 257        |

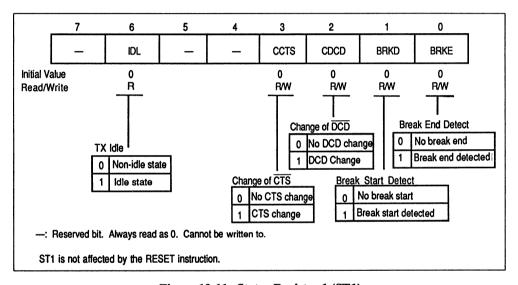

|         | 10.2.10 Status Register 1 (ST1)                               | 259        |

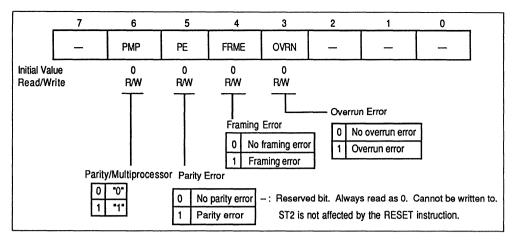

|         | 10.2.11 Status Register 2 (ST2)                               | 260        |

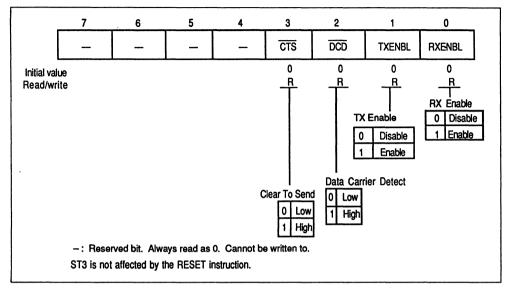

|         | 10.2.12 Status Register 3 (ST3)                               | 263        |

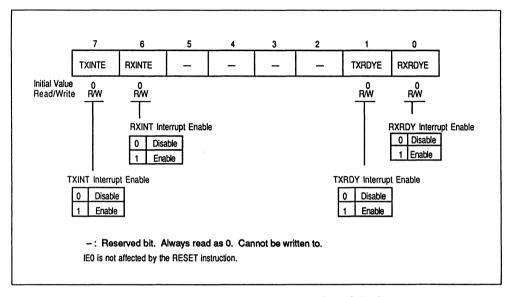

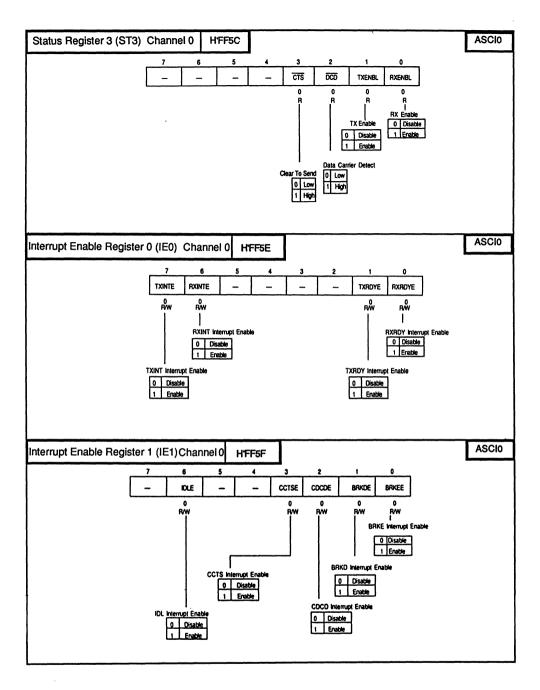

|         | 10.2.13 Interrupt Enable Register 0 (IEO)                     | 264        |

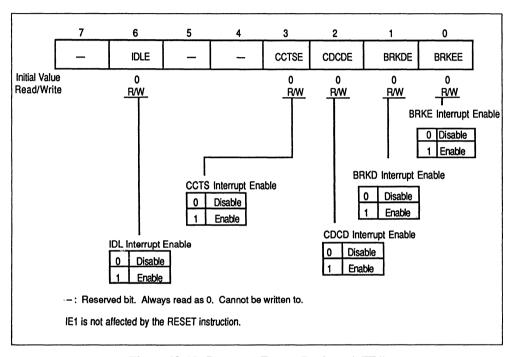

|         | 10.2.14 Interrupt Enable Register 1 (IE1)                     | 265        |

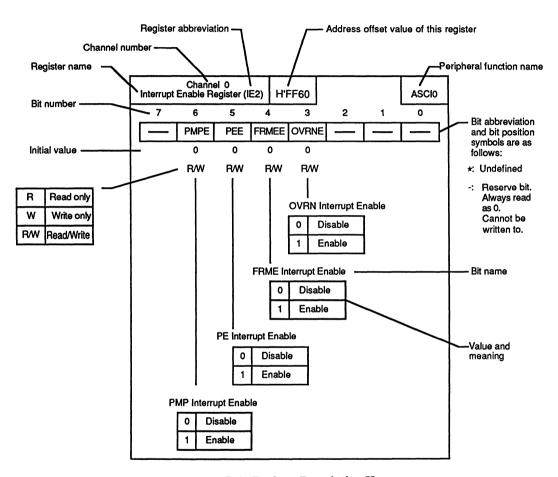

|         | 10.2.15 Interrupt Enable Register 2 (IE2)                     | 267        |

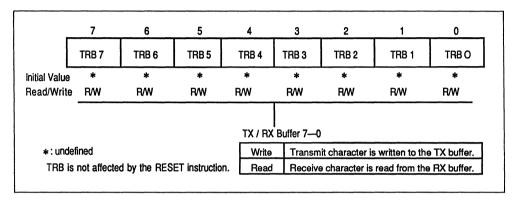

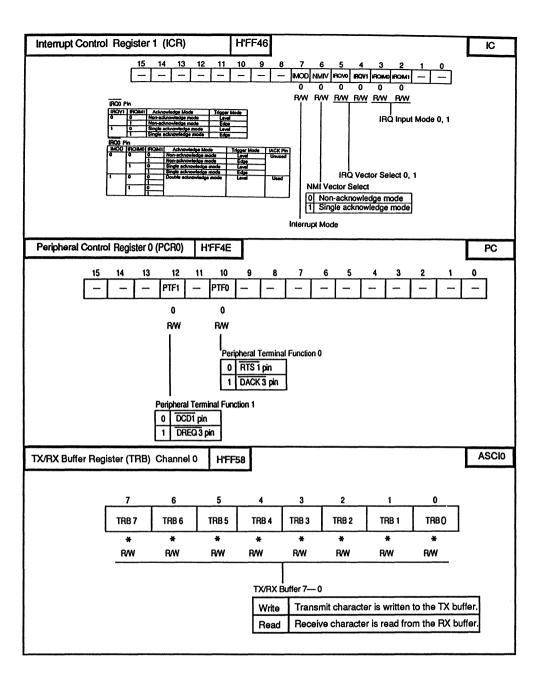

| 10.2    | 10.2.16 TX/RX Buffer Register (TRB)                           | 268        |

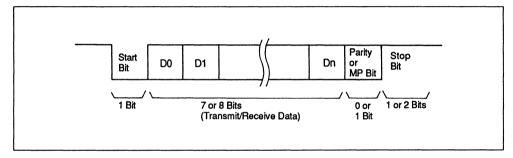

| 10.5    | ASCI Asynchronous Mode Operation                              | 269<br>269 |

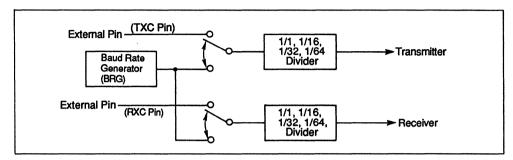

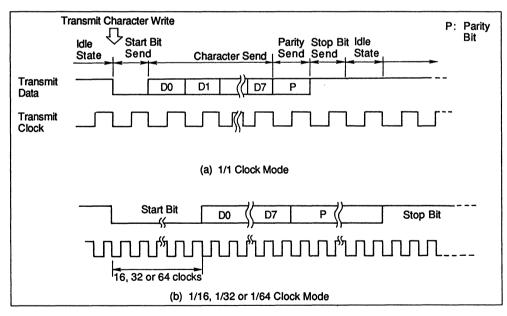

|         | 10.3.2 Baud Rate                                              |            |

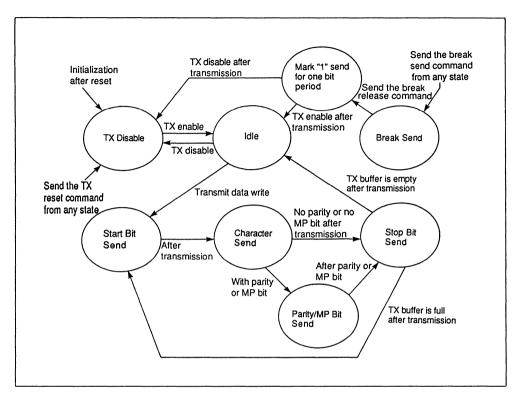

|         | 10.3.3 Transmission State                                     |            |

|         | 10.3.4 Transmit Operation                                     |            |

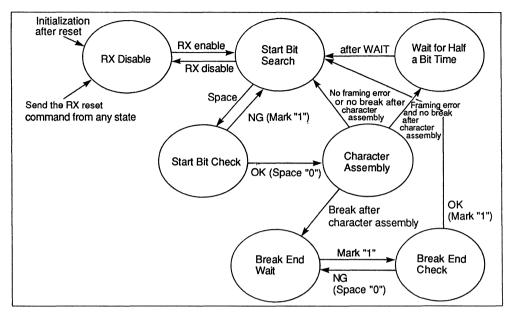

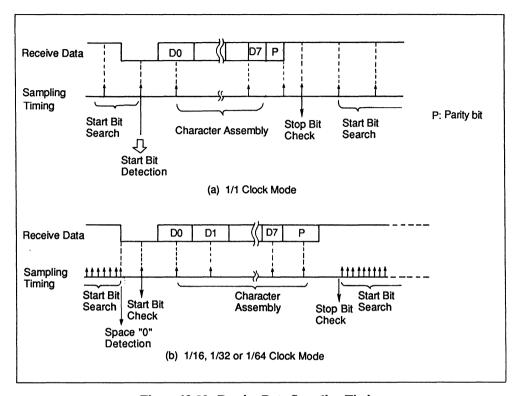

|         | 10.3.5 Receive State                                          |            |

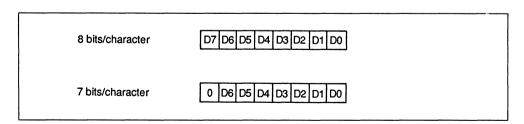

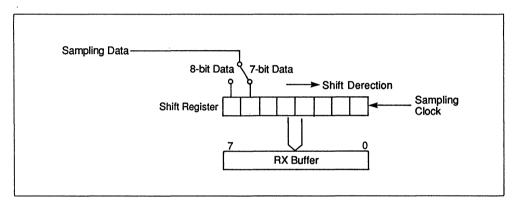

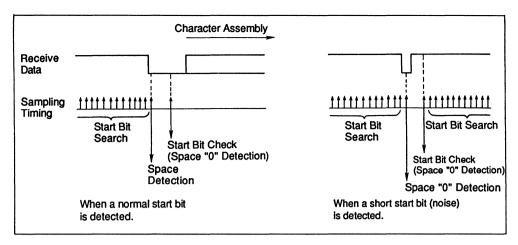

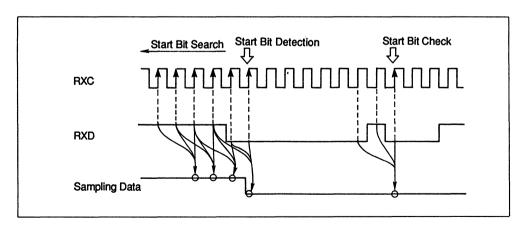

|         | 10.3.6 Receive Operation                                      | 275        |

|         | 10.3.7 Parity/MP Bit                                          | 278        |

|         | 10.3.8 Error Check                                            | 278        |

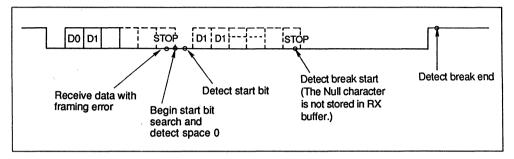

|         | 10.3.9 Break Send/Detection                                   | 279        |

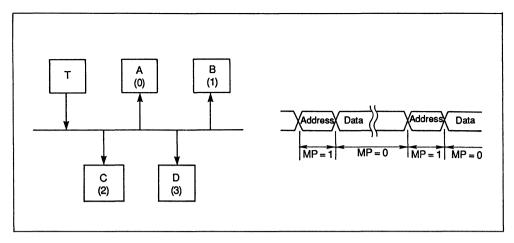

| 10.4    | 10.3.10 Multiprocessor Support                                | 280        |

| 10.4    | ASCI Clock Synchronous Mode Operation                         |            |

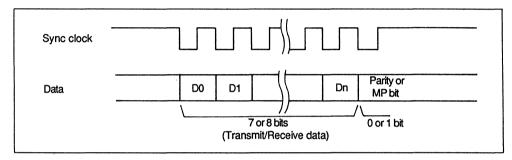

|         | 10.4.1 Character Format                                       | 282        |

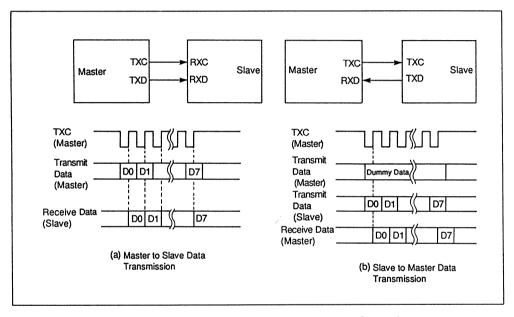

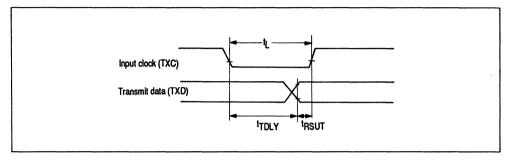

|         | 10.4.2 ASCI Clock Synchronous Mode Operation                  | 283        |

| 10.5    | Serial Data Transfer by CPU and DMAC                          | 285        |

|         | 10.5.1 Polling                                                | 285        |

|         | 10.5.2 Interrupt                                              | 285        |

| 40.0    | 10.5.3 DMA Transfer                                           | 285        |

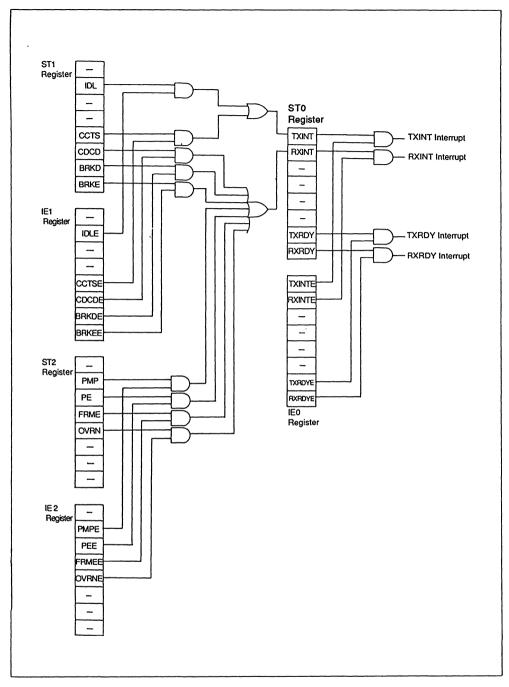

|         | ASCI Interrupts                                               | 286        |

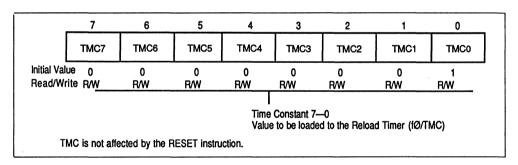

| 10.7    | Baud Rate Generator (BRG)                                     | 290        |

|         | 10.7.1 BRG Features                                           | 290        |

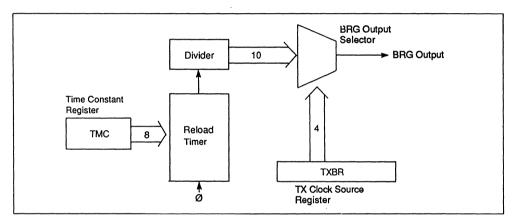

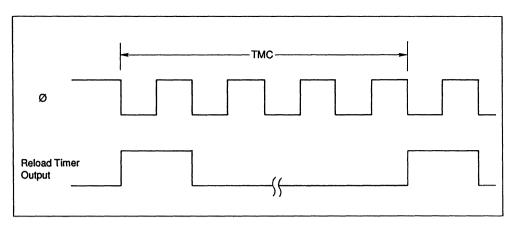

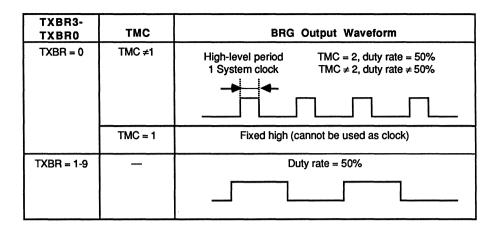

|         | 10.7.2 BRG Operation                                          | 290        |

|         | 10.7.3 BRG Output Frequency                                   | 292        |

|         | 10.7.4 Register Values and Bit Rates                          | 292        |

| 10.8    | Future ASCI Compatibility                                       | 299        |

|---------|-----------------------------------------------------------------|------------|

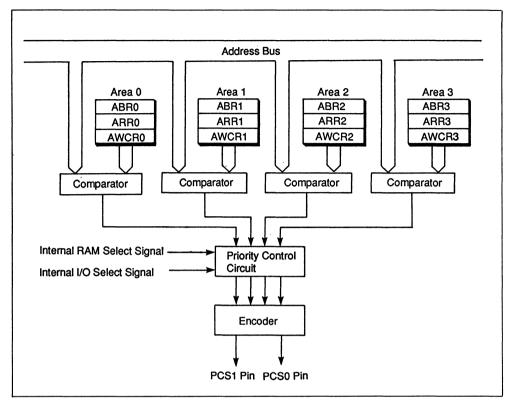

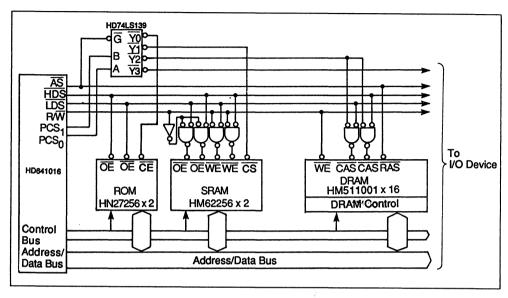

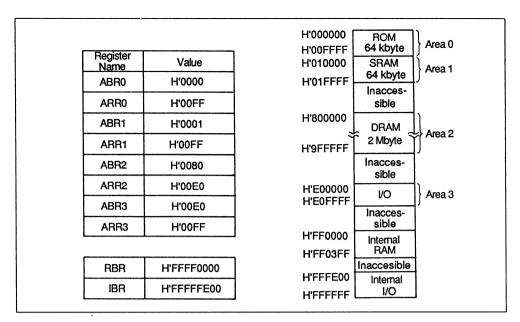

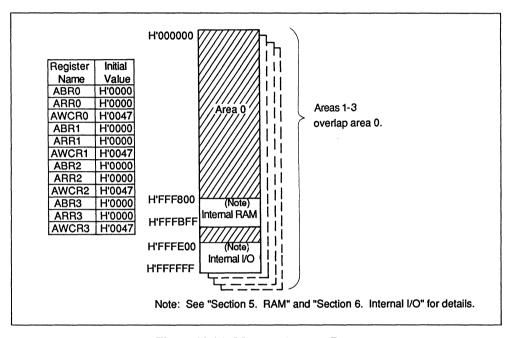

| Section | n 11. Chip Select Controller                                    | 301        |

| 11.1    | Overview                                                        | 301        |

| 11.2    | Chip Select Controller Registers                                | 303        |

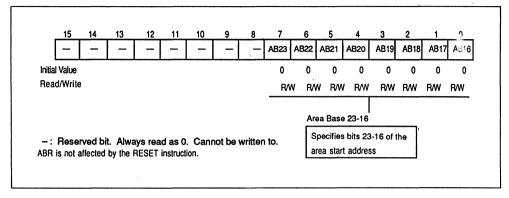

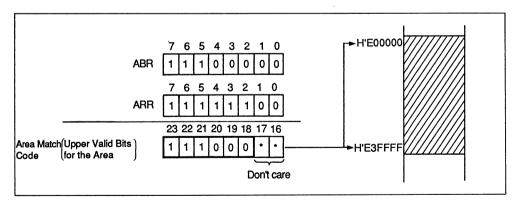

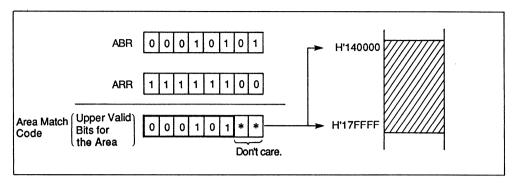

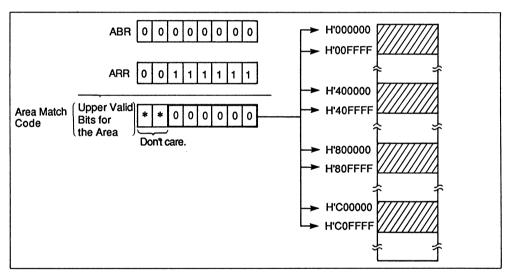

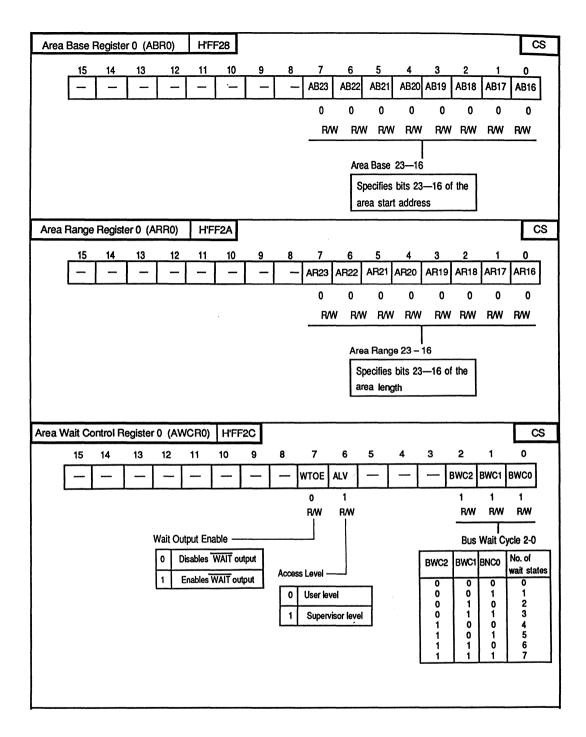

|         | 11.2.1 Area Base Registers 3-0 (ABR3-ABR0)                      | 304        |

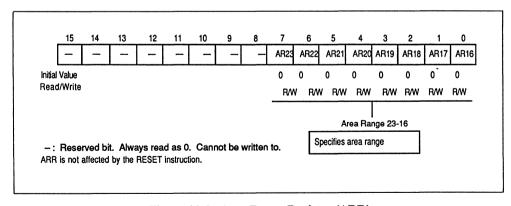

|         | 11.2.2 Area Range Registers 3-0 (ARR3-ARR0)                     | 304        |

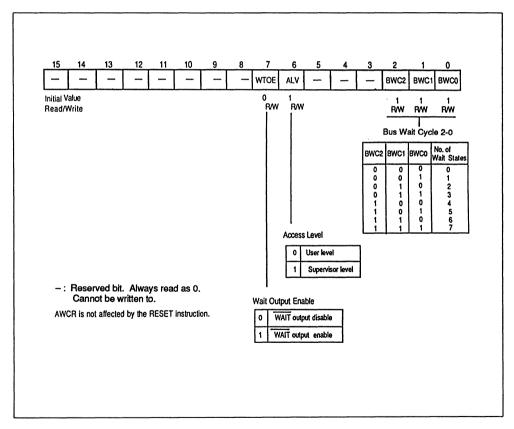

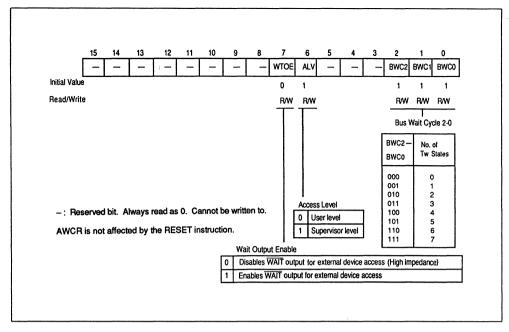

|         | 11.2.3 Area Wait Control Registers 3-0 (AWCR3-AWCR0)            | 305        |

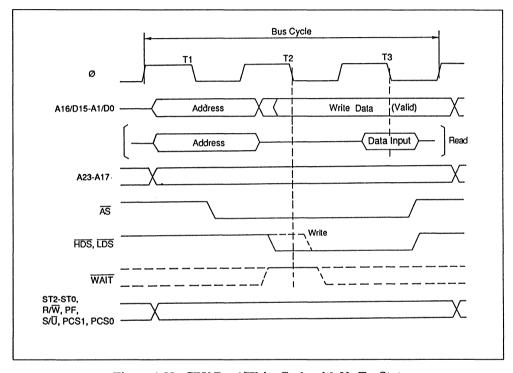

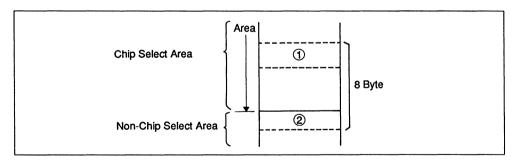

| 11.3    | Chip Select Controller Operation                                | 306        |

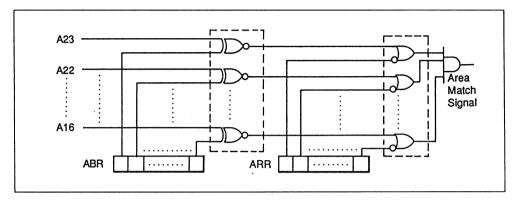

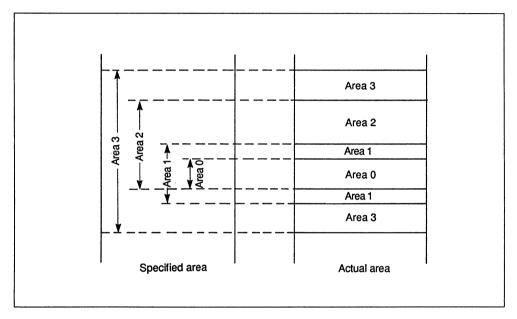

|         | 11.3.1 Area Determination                                       | 306        |

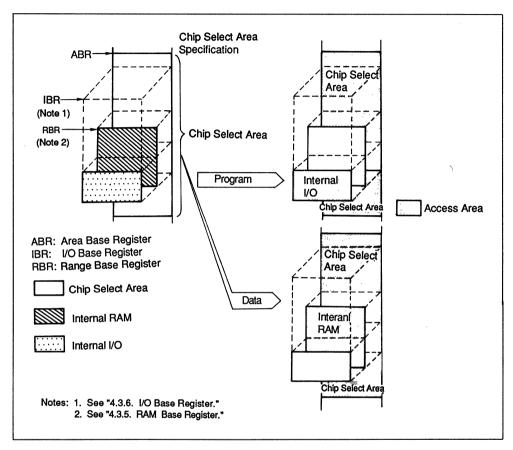

|         | 11.3.2 Chip Select Area, Internal RAM, and Internal I/O Overlap | 309        |

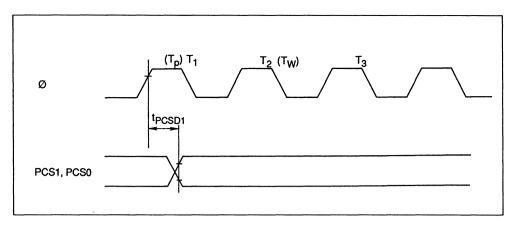

|         | 11.3.3 PCS Output                                               | 311        |

|         | 11.3.4 Access Level                                             | 311        |

| 11 /    | 11.3.5 Access Disable Area                                      | 311        |

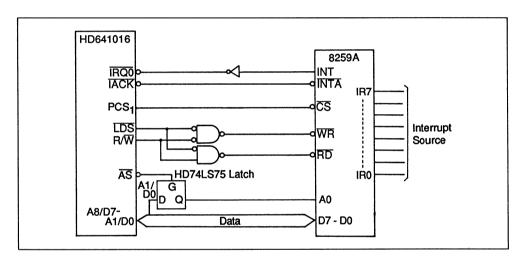

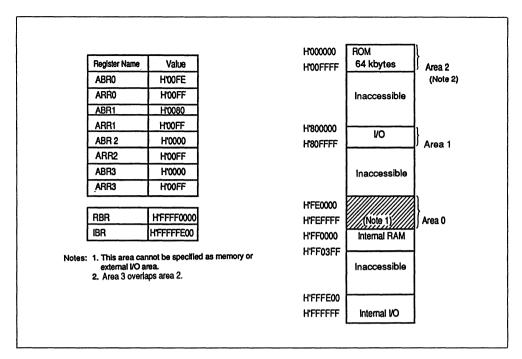

| 11.4    | Chip Select Controller Applications                             | 312        |

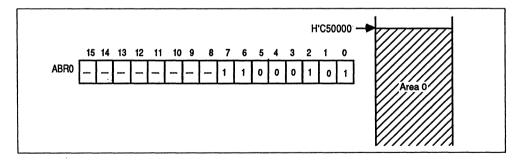

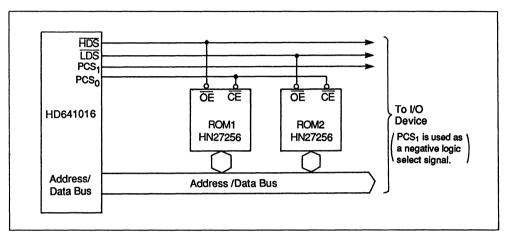

|         | 11.4.1 Small Application System with ROM and I/O                | 312<br>314 |

| 11.5    | Chip Select Controller and Reset                                | 216        |

| 11.5    | Chip Select Controller Operation Notes                          | 317        |

| 11.0    | Crip Select Controller Operation Profes                         | 317        |

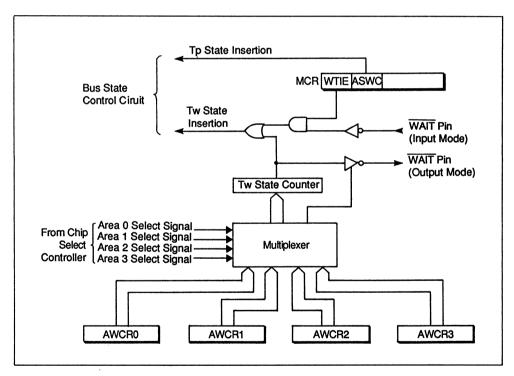

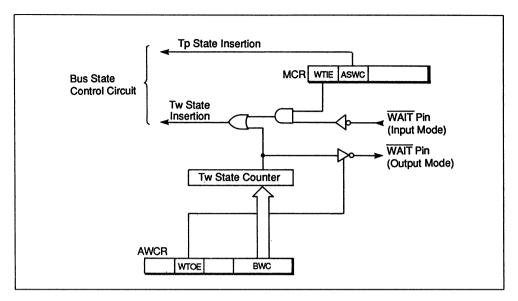

| Section | n 12. Wait State Controller                                     | 318        |

|         |                                                                 |            |

| 12.1    | Overview                                                        |            |

| 12.2    | Wait State Controller Registers                                 | 319        |

|         | 12.2.1 Area Wait Control Registers 3-0 (AWCR3-AWCR0)            | 319        |

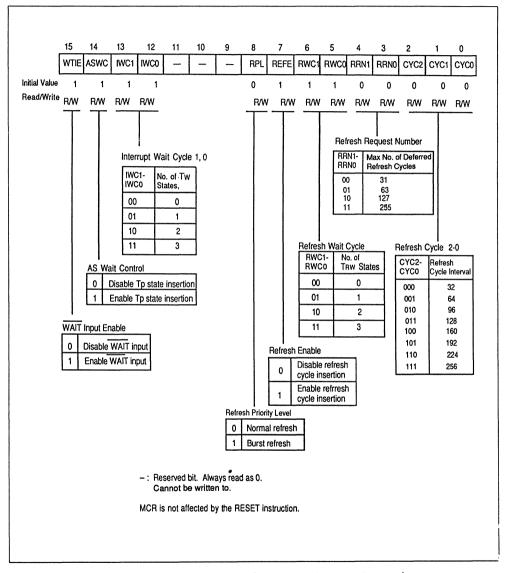

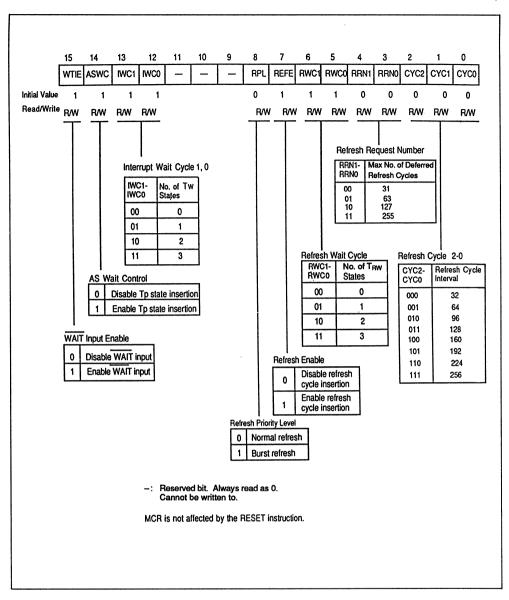

|         | 12.2.2 Memory Control Register (MCR)                            | 322        |

| 12.3    | Wait State Controller Operation                                 |            |

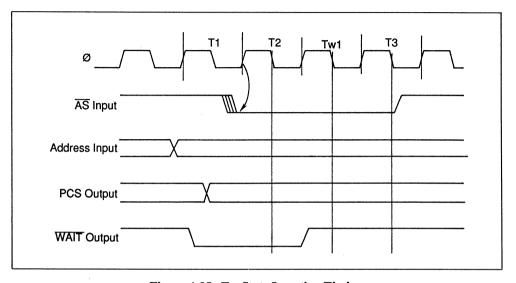

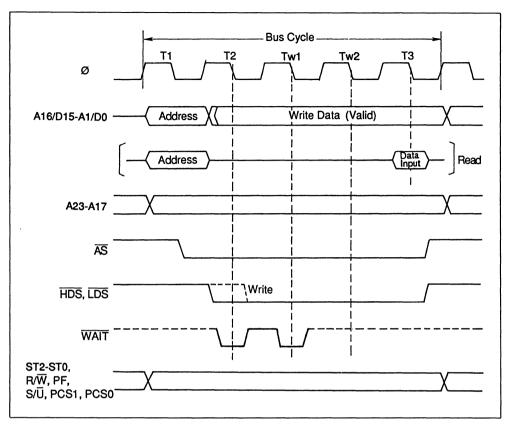

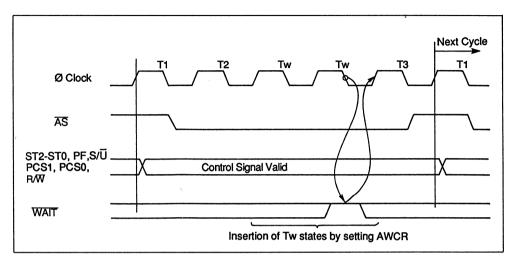

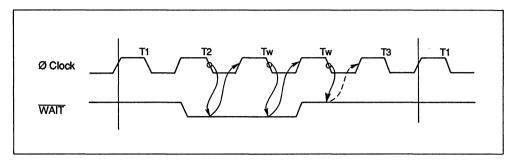

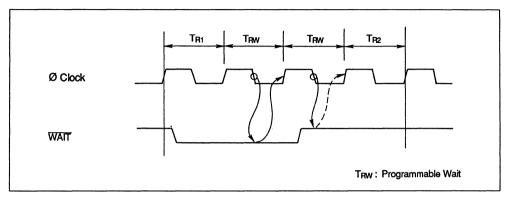

|         | 12.3.1 Programmable Tw State Insertion                          | 326        |

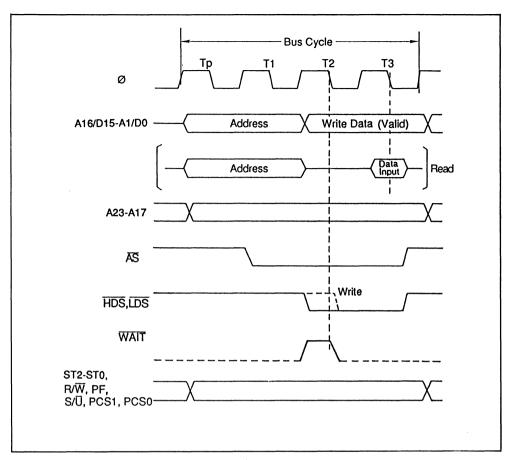

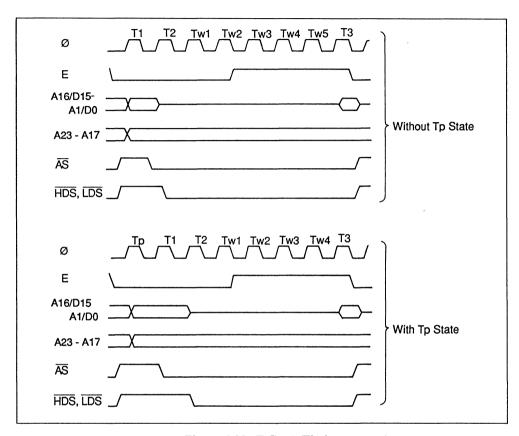

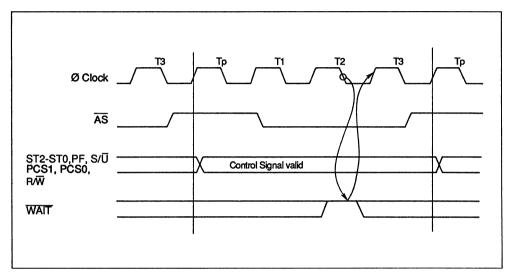

|         | 12.3.2 Tp State Insertion                                       | 327        |

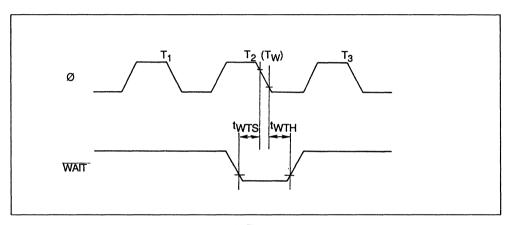

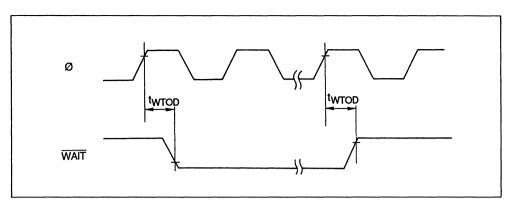

|         | WAIT Input)                                                     | 328        |

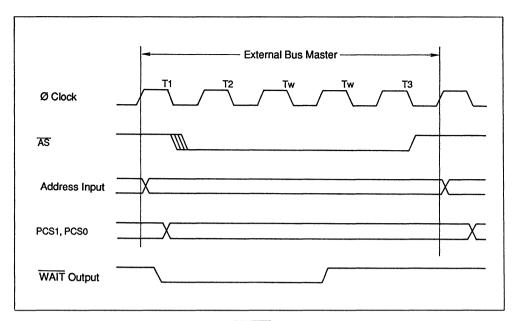

|         | WAIT Input )                                                    | 328        |

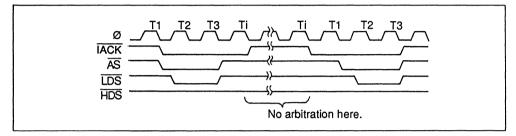

|         | 12.3.5 Tw State Insertion during an Interrupt Acknowledge Cycle | 329        |

| 12.4    | Wait State Controller Notes                                     | 329        |

|         |                                                                 |            |

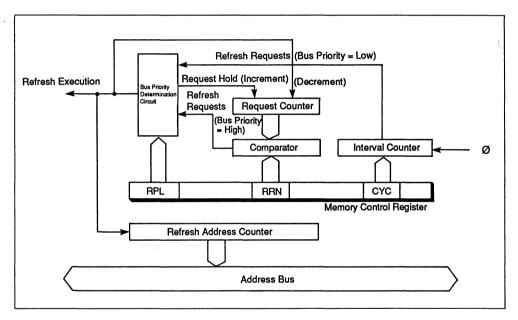

| Section | n 13. Dynamic RAM Refresh Controller                            | 330        |

| 13.1    | Overview                                                        |            |

|         | DRAM Refresh Controller Register                                |            |

| 13.2    |                                                                 |            |

| 12.2    | 13.2.1 Memory Control Register (MCR)                            |            |

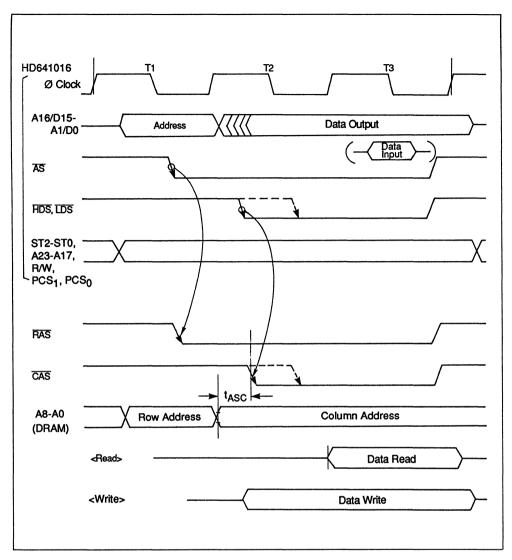

| 13.3    | DRAM Refresh Controller Operation and Procedure                 |            |

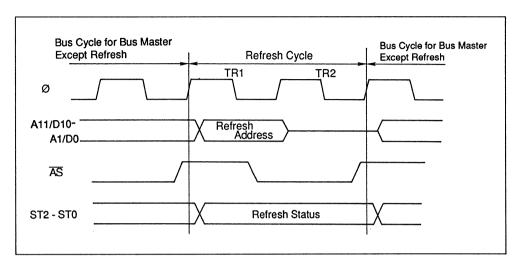

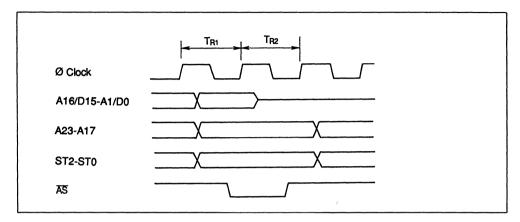

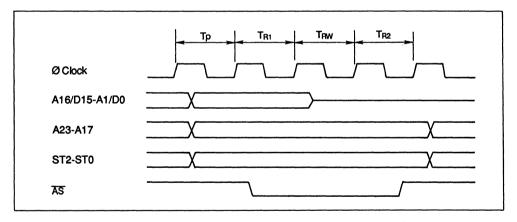

|         | 13.3.1 Basic Operation                                          | 335        |

| 10.4    | 13.3.2 TRW State Insertion by WAIT                              | 337        |

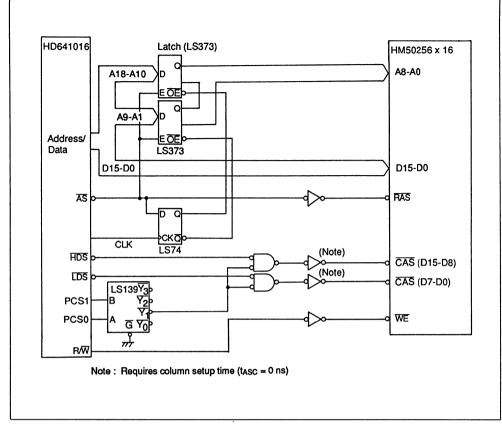

| 13.4    | Application Example                                             | 337        |

|         | 13.4.1 Refresh Insertion Interval                               | 337        |

|         | 13.4.2 DRAM Interface Circuit                                   | 338        |

| 13.5    | DRAM Refresh Controller and Reset                               | 341        |

|         | 13.5.1 DRAM Refresh Controller Operation at Power-On Reset      | 341<br>341 |

|         | 13.5.2 DRAM Refresh Controller Operation at Manual Reset        |            |

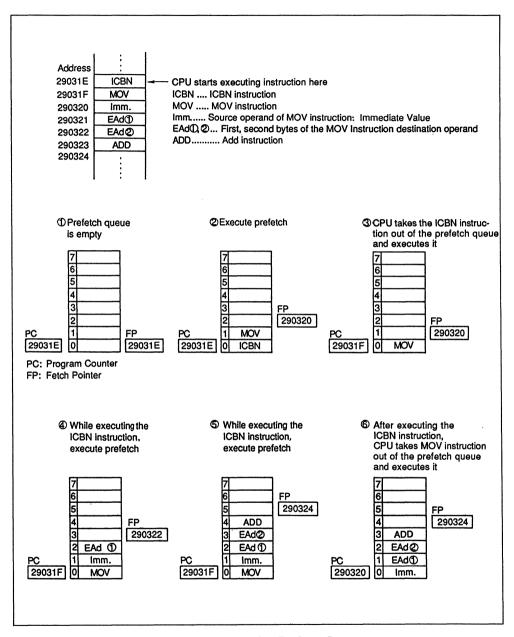

| 10.0    | Instruction Execution                                           | 341        |

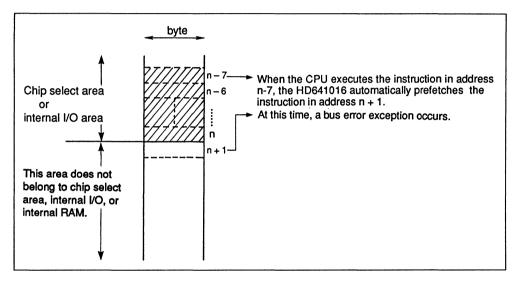

| 13.6    | DRAM Refresh Controller Notes                                   | 341        |

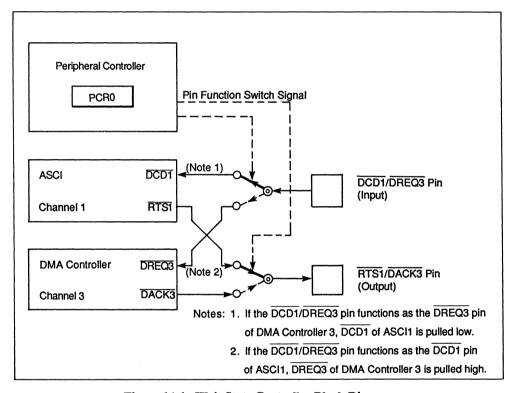

| Section 14. Peripheral Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 342        |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| 14.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |  |  |  |  |

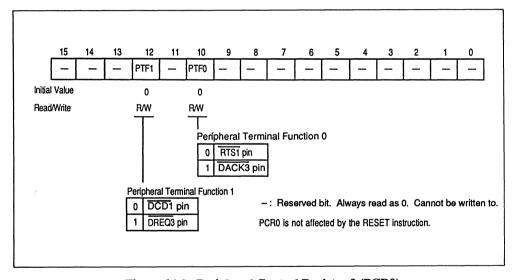

| 14.2 Peripheral Controller Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |  |  |  |  |

| 14.2.1 Peripheral Control Register 0 (PCR0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |  |  |  |  |

| 14.3 Peripheral Controller Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3/1/       |  |  |  |  |

| 14.4 Peripheral Controller Operation Notes 34.4 Peripheral Controlle |            |  |  |  |  |

| 14.4 Tempheral Controller Operation (votes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 344        |  |  |  |  |

| 0 ' 15 T D C ' 15 T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |  |  |  |  |

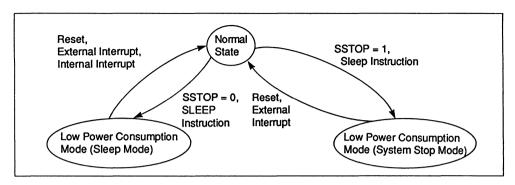

| Section 15. Low Power Consumption Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |  |  |  |  |

| 15.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 345        |  |  |  |  |

| 15.2 Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |  |  |  |  |

| 15.3 System Stop Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 346        |  |  |  |  |

| 15.4 Low Power Consumption Mode Transition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |  |  |  |  |

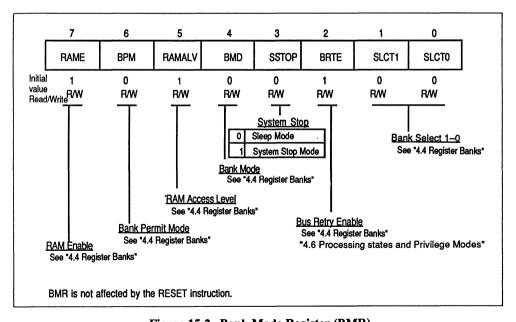

| 15.5 Bank Mode Register (BMR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |  |  |  |  |

| 15.6 Comparison between Sleep and System Stop Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 240        |  |  |  |  |

| 13.5 Comparison between sleep and system stop windes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 343        |  |  |  |  |

| 0 ' 16 T ' ' 0 '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |  |  |  |  |

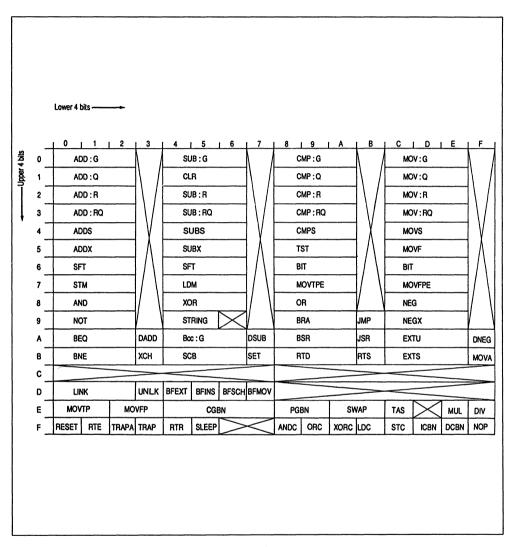

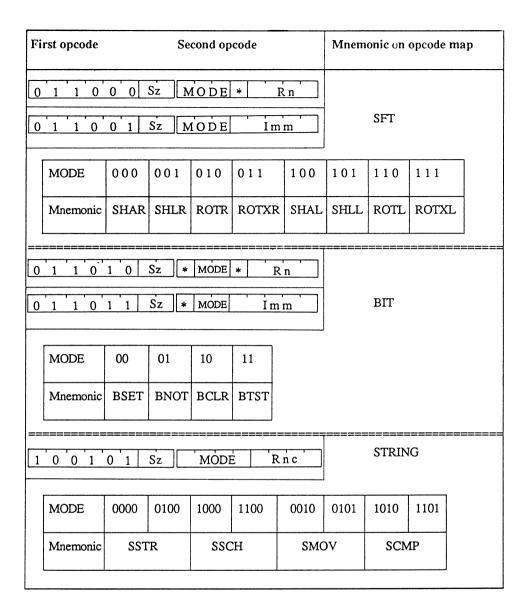

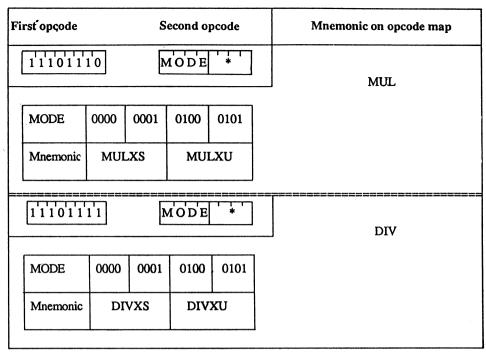

| Section 16. Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |  |  |  |  |

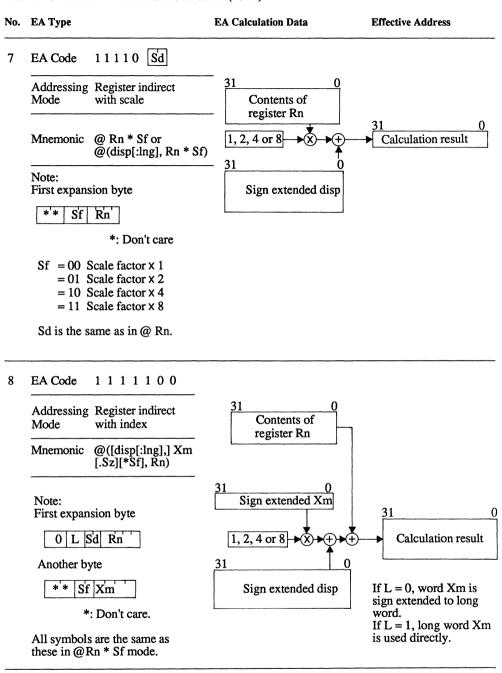

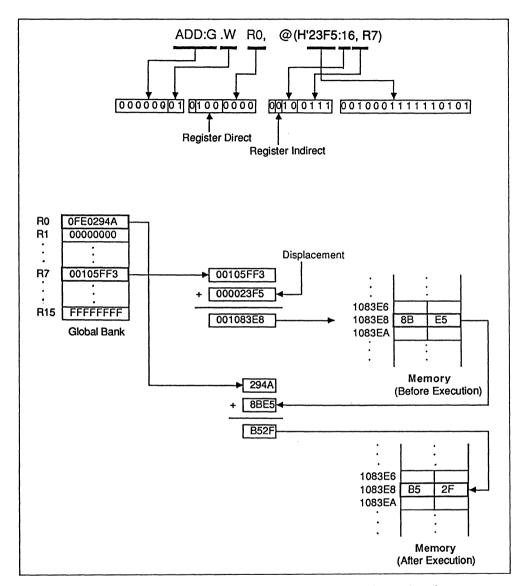

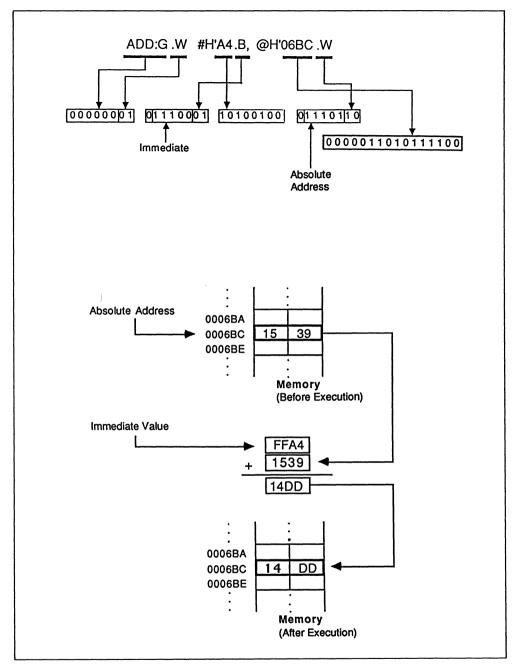

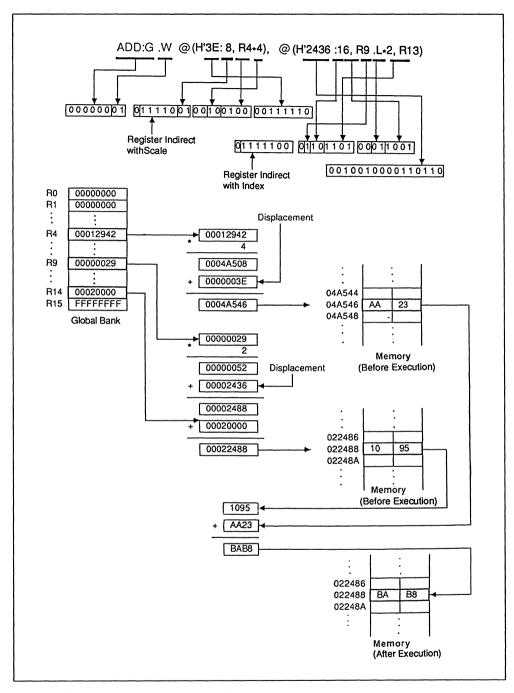

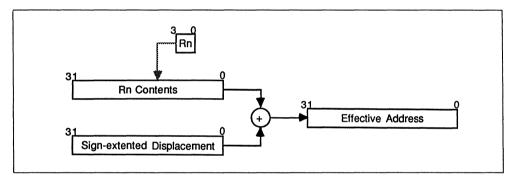

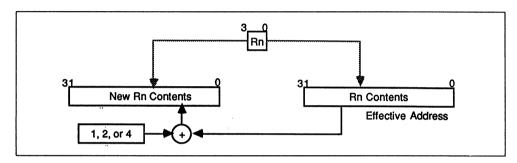

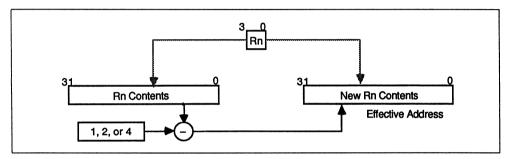

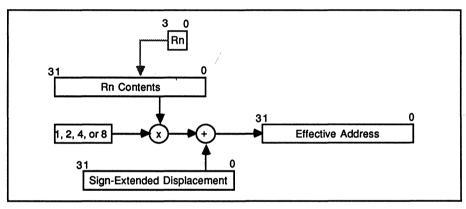

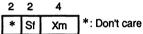

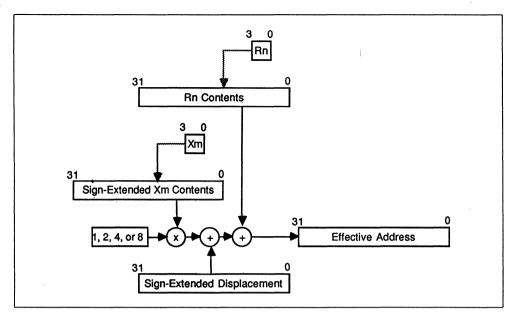

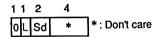

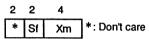

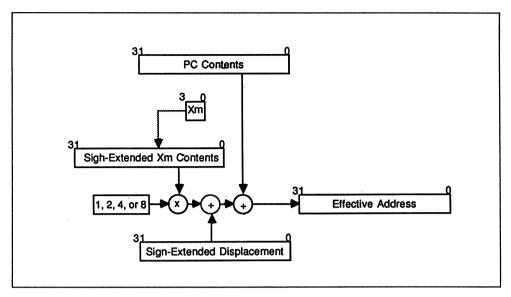

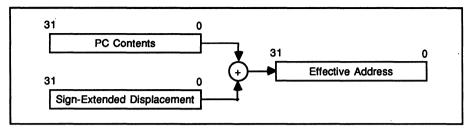

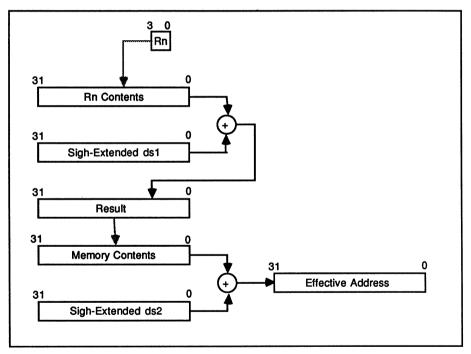

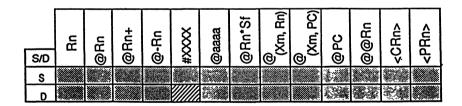

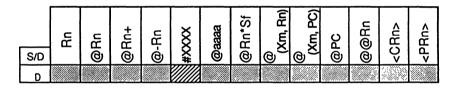

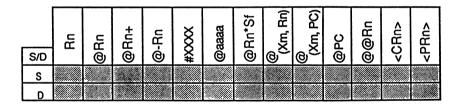

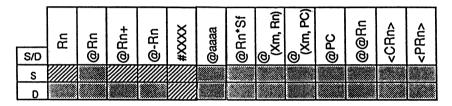

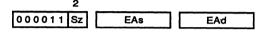

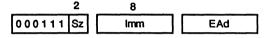

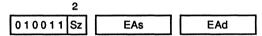

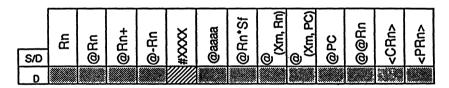

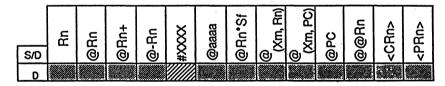

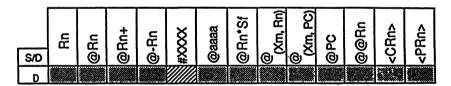

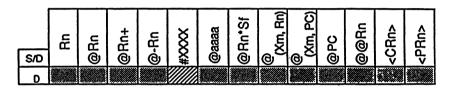

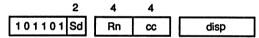

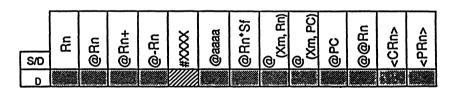

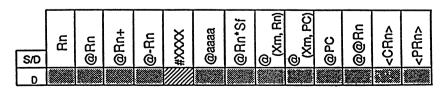

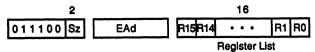

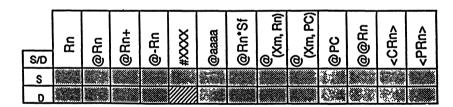

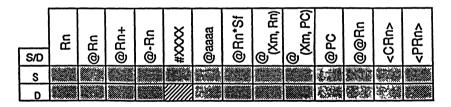

| 16.1 Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 350        |  |  |  |  |

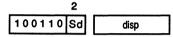

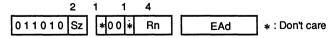

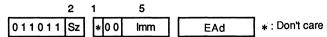

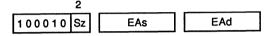

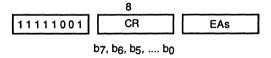

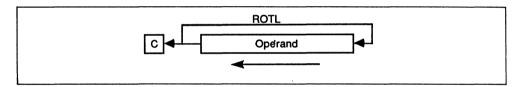

| 16.2 Instruction Set Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 364        |  |  |  |  |

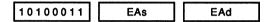

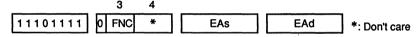

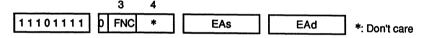

| 16.3 Instruction Set Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |  |  |  |  |

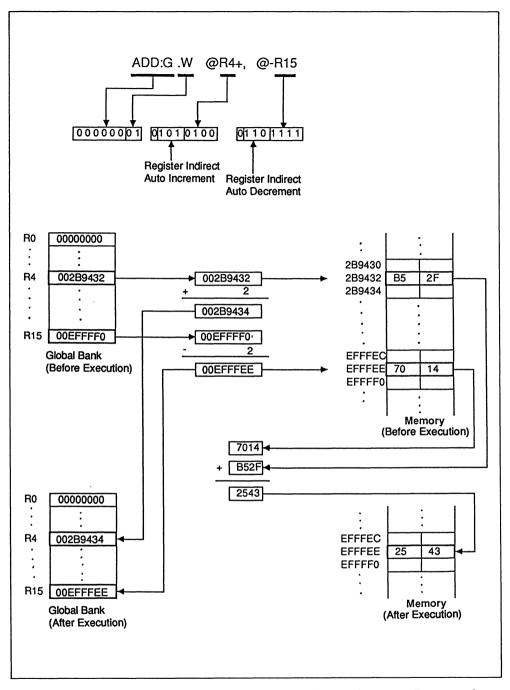

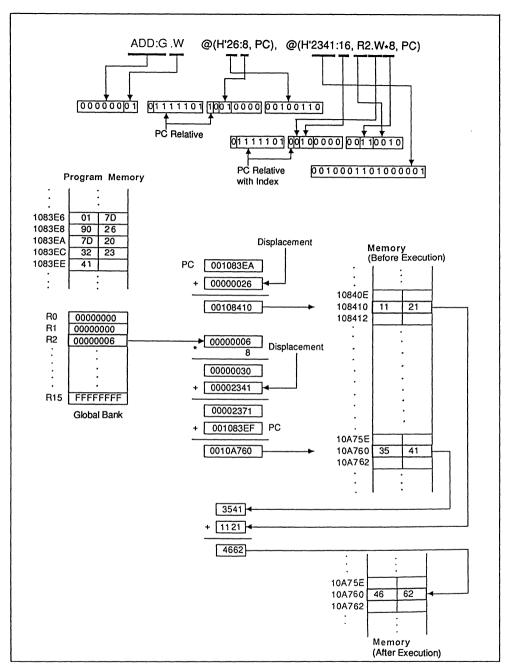

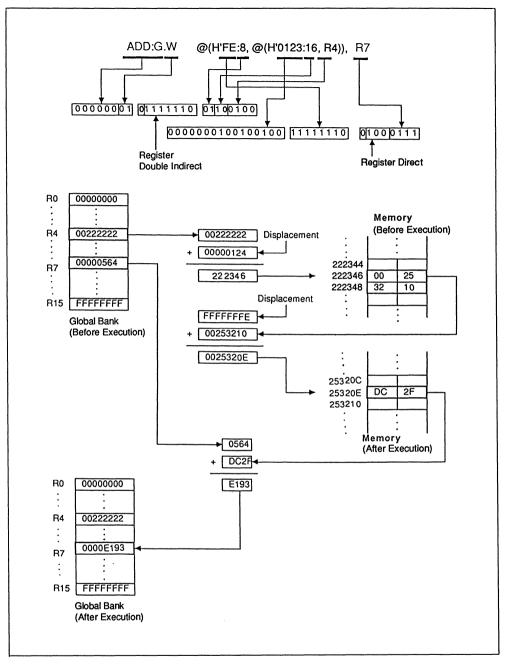

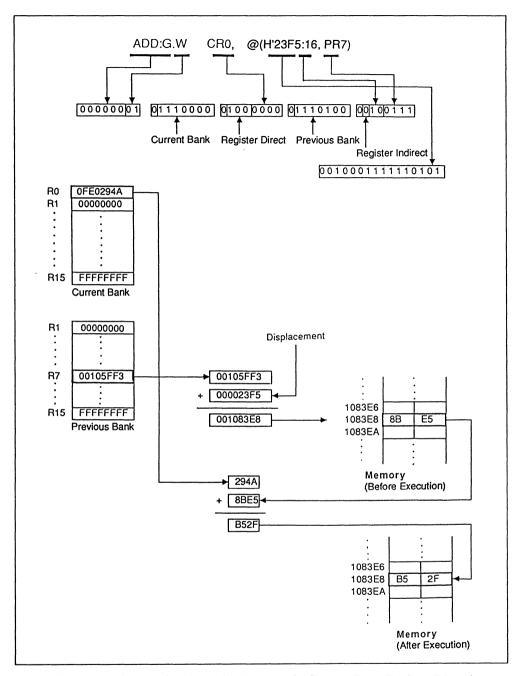

| 16.3.1 ADD:G (Add Binary)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 381        |  |  |  |  |

| 16.3.2 ADD:Q (Add Quick)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 382        |  |  |  |  |

| 16.3.3 ADD:R (Add Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 383        |  |  |  |  |

| 16.3.4 ADD:RO (Add Register Quick)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 384        |  |  |  |  |

| 16.3.5 ADDS (Add with Sign Extension)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 385        |  |  |  |  |

| 16.3.6 ADDX (Add with CX Flag)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 386        |  |  |  |  |