## 8-BIT SINGLE-CHIP MICROCOMPUTER DATA BOOK

# 8-BIT SINGLE-CHIP MICROCOMPUTER DATABOOK

When using this manual, the reader should keep the following in mind:

- 1. This manual may, wholly or partially, be subject to change without notice.

- 2. All rights reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this manual without Hitachi's permission.

- 3. Hitachi will not be responsible for any damage to the user that may result from accidents or any other reasons during operation of his unit according to this manual.

- 4. This manual neither ensures the enforcement of any industrial properties or other rights, nor sanctions the enforcement right thereof.

### **INDEX**

| • | GENERAL INFO                         |                                                            |     |

|---|--------------------------------------|------------------------------------------------------------|-----|

|   |                                      | ee Guide                                                   |     |

|   | <ul> <li>Introduction of</li> </ul>  | f Packages                                                 | 17  |

|   | <ul> <li>Quality Assurar</li> </ul>  | 100                                                        | 25  |

|   | <ul> <li>Reliability Test</li> </ul> | Data                                                       | 31  |

|   | Design Procedu                       | ure and Support Tools for 8-bit Single-chip Microcomputers | 36  |

|   |                                      |                                                            |     |

| • | DATA SHEETS                          |                                                            |     |

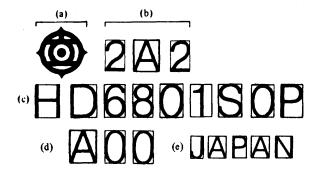

|   | HD6801S0                             | Microcomputer Unit (NMOS)                                  | 41  |

|   | HD6801S5                             | Microcomputer Unit (NMOS)                                  | 41  |

|   | HD6801V0                             | Microcomputer Unit (NMOS)                                  | 75  |

|   | HD6801V5                             | Microcomputer Unit (NMOS)                                  | 75  |

|   | HD6803                               | Micro Processing Unit (NMOS)                               | 109 |

|   | HD6803-1                             | Micro Processing Unit (NMOS)                               | 109 |

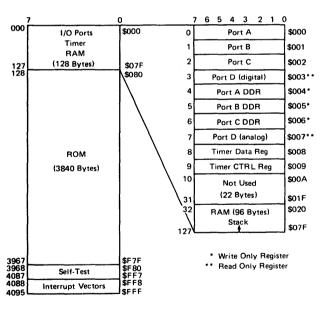

|   | HD6805S1                             | Microcomputer Unit (NMOS)                                  | 136 |

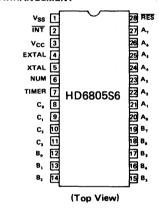

|   | HD6805S6                             | Microcomputer Unit (NMOS)                                  | 156 |

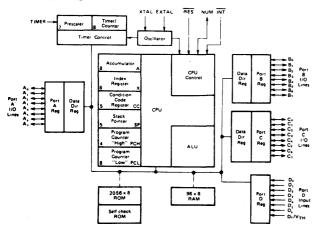

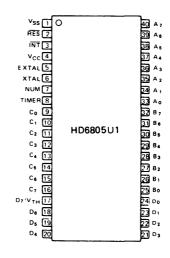

|   | HD6805U1                             | Microcomputer Unit (NMOS)                                  | 176 |

|   | HD6805V1                             | Microcomputer Unit (NMOS)                                  | 197 |

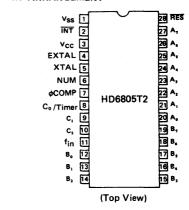

|   | HD6805T2                             | Microcomputer Unit (NMOS)                                  | 218 |

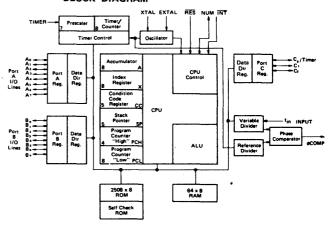

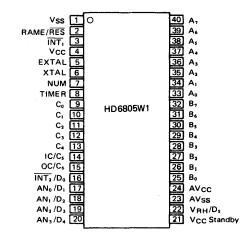

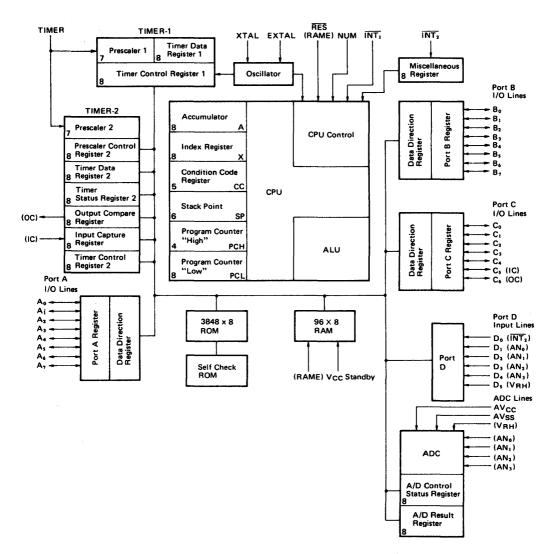

|   | HD6805W1                             | Microcomputer Unit (NMOS)                                  |     |

|   | HD6301V1                             | Microcomputer Unit (CMOS)                                  | 247 |

|   | HD63A01V1                            | Microcomputer Unit (CMOS)                                  |     |

|   | HD63B01V1                            | Microcomputer Unit (CMOS)                                  | 247 |

|   | HD6301X0                             | Microcomputer Unit (CMOS)                                  |     |

|   | HD63A01X0                            | Microcomputer Unit (CMOS)                                  |     |

|   | HD63B01X0                            | Microcomputer Unit (CMOS)                                  |     |

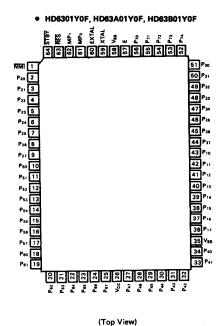

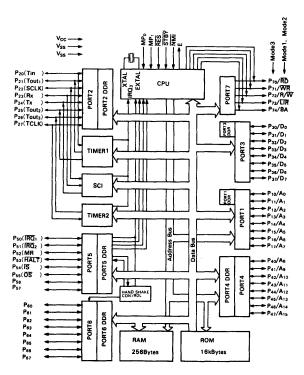

|   | HD6301Y0                             | Microcomputer Unit (CMOS)                                  |     |

|   | HD63A01Y0                            | Microcomputer Unit (CMOS)                                  |     |

|   | HD63B01Y0                            | Microcomputer Unit (CMOS)                                  |     |

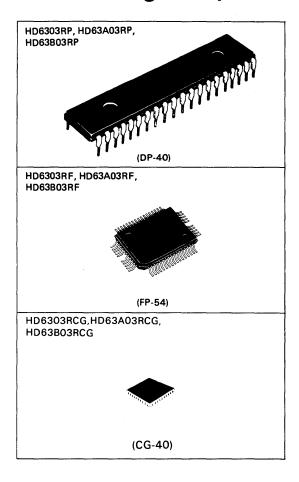

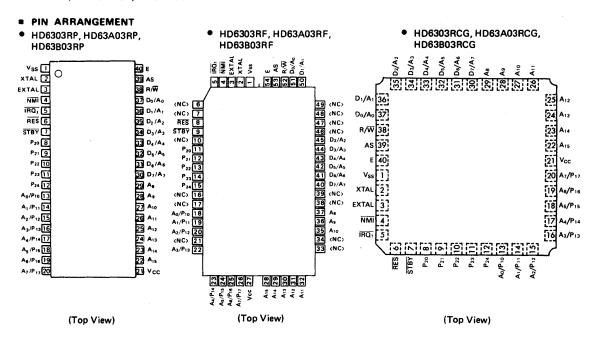

|   | HD6303R                              | Micro Processing Unit (CMOS)                               |     |

|   | HD63A03R                             | Micro Processing Unit (CMOS)                               |     |

|   | HD63B03R                             | Micro Processing Unit (CMOS)                               |     |

|   | HD6303X                              | Micro Processing Unit (CMOS)                               |     |

|   | HD63A03X                             | Micro Processing Unit (CMOS)                               | 252 |

|   | HD63B03X                             | Micro Processing Unit (CMOS)                               |     |

|   | HD6303Y                              | Micro Processing Unit (CMOS)                               | 200 |

|   | HD63A03Y                             | Micro Processing Unit (CMOS)                               | 300 |

|   | HD63B03Y                             | Micro Processing Unit (CMOS)                               | 300 |

|   | HD6305U0                             | Microcomputer Unit (CMOS)                                  | 300 |

|   | HD63A05U0                            | Microcomputer Unit (CMOS)                                  | 391 |

|   | HD63B05U0                            | Microcomputer Unit (CMOS)                                  | 391 |

|   | HD6305V0                             | Microcomputer Unit (CMOS)                                  | 391 |

|   | HD63A05V0                            | Microcomputer Unit (CMOS)                                  | 393 |

|   | HD63B05V0                            | Microcomputer Unit (CMOS)                                  | 393 |

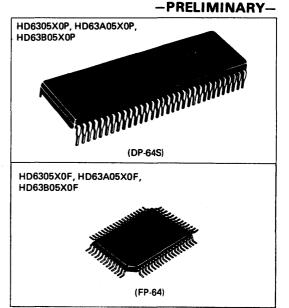

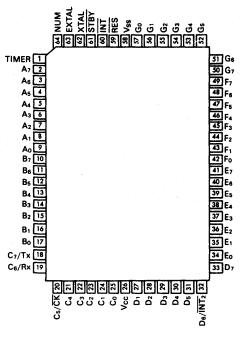

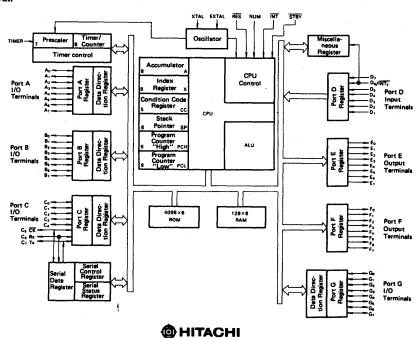

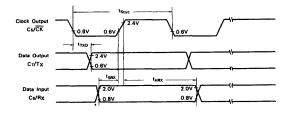

|   | HD6305X0                             | Microcomputer Unit (CMOS)                                  | 393 |

|   |                                      | Microcomputer Unit (CMOS)                                  | 395 |

|   | HD63A05X0                            | Microcomputer Unit (CMOS)                                  | 395 |

|   | HD63B05X0                            | Microcomputer Unit (CMOS)                                  | 395 |

|   | HD6305X1                             | Microcomputer Unit (CMOS)                                  |     |

|   | HD63A05X1                            | Microcomputer Unit (CMOS)                                  |     |

|   | HD63B05X1                            | Microcomputer Unit (CMOS)                                  |     |

|   | HD6305X2                             | Microcomputer Unit (CMOS)                                  |     |

|   | HD63A05X2                            | Microcomputer Unit (CMOS)                                  |     |

|   |                                      | BEIGROCOMMUTAR LIMIT II BEI N. I                           | 477 |

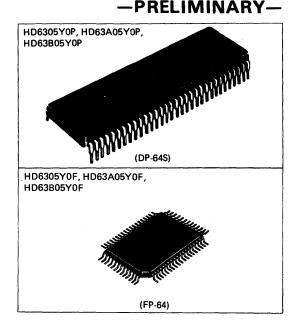

| HD6305Y0                            | Microcomputer Unit (CMOS)                                       | 45  |

|-------------------------------------|-----------------------------------------------------------------|-----|

| HD63A05Y0                           | Microcomputer Unit (CMOS)                                       | 45  |

| HD63B05Y0                           | Microcomputer Unit (CMOS)                                       | 45  |

| HD6305Y1                            | Microcomputer Unit (CMOS)                                       | 470 |

| HD63A05Y1                           | Microcomputer Unit (CMOS)                                       | 470 |

| HD63B05Y1                           | Microcomputer Unit (CMOS)                                       | 47  |

| HD6305Y2                            | Microcomputer Unit (CMOS)                                       | 479 |

| HD63A05Y2                           | Microcomputer Unit (CMOS)                                       | 47  |

| HD63B05Y2                           | Microcomputer Unit (CMOS)                                       | 47  |

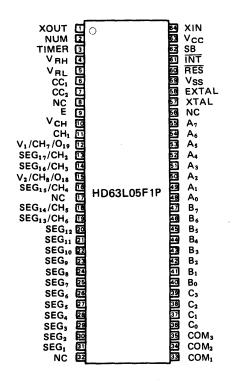

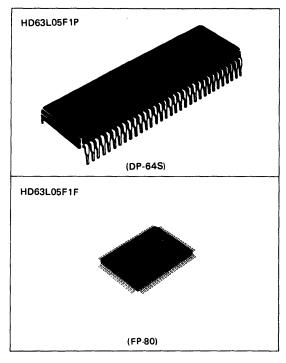

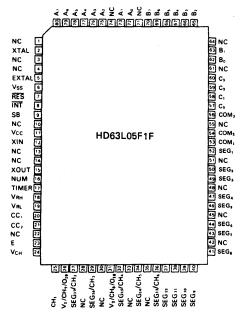

| HD63L05F1                           | Microcomputer Unit (CMOS)                                       | 50  |

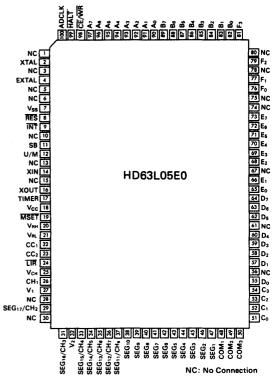

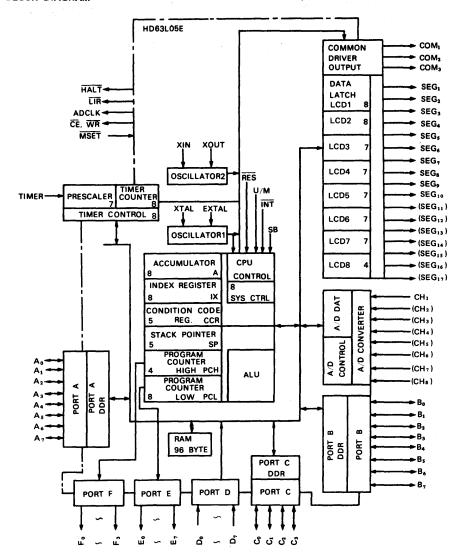

| HD63L05E0                           | Evaluation Chip for HD63L05F1 (CMOS)                            | 52  |

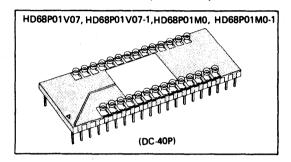

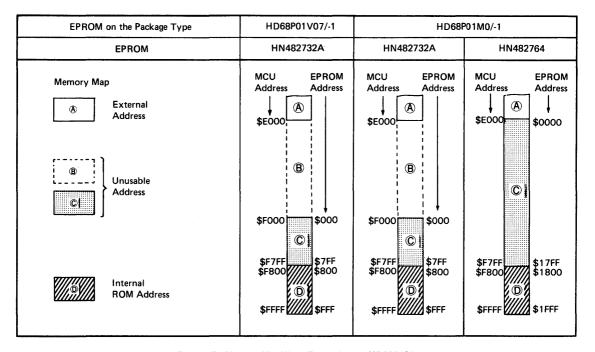

| HD68P01V07                          | Microcomputer Unit (NMOS)                                       | 546 |

| HD68P01V07-1                        | Microcomputer Unit (NMOS)                                       | 541 |

| HD68P01M0                           | Microcomputer Unit (NMOS)                                       | 540 |

| HD68P01M0-1                         | Microcomputer Unit (NMOS)                                       | EAG |

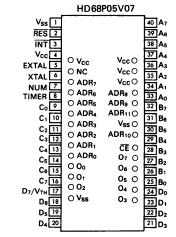

| HD68P05V07                          | Microcomputer Unit (NMOS)                                       | -   |

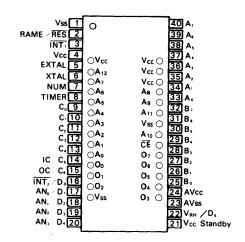

| HD68P05W0                           | Microcomputer Unit (NMOS)                                       | -   |

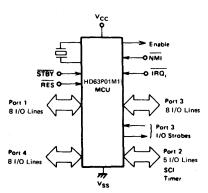

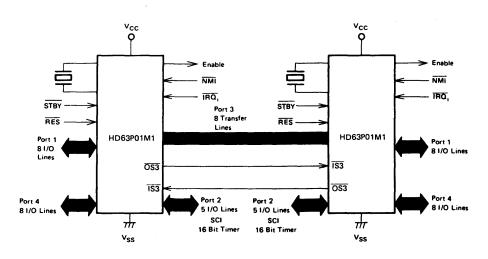

| HD63P01M1                           | Microcomputer Unit (CMOS)                                       | (2) |

| HD63PA01M1                          | Microcomputer Unit (CMOS)                                       | 636 |

| HD63PB01M1                          | Microcomputer Unit (CMOS)                                       | 631 |

| HD63P05Y0                           | Microcomputer Unit (CMOS)                                       | 669 |

| HD63PA05Y0                          | Microcomputer Unit (CMOS)                                       | 661 |

| HD63PB05Y0                          | Microcomputer Unit (CMOS)                                       | 669 |

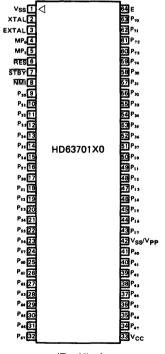

| HD63701X0                           | Microcomputer Unit (CMOS) · · · · · · · · · · · · · · · · · · · | 670 |

|                                     | ,                                                               | 0,0 |

| <ul> <li>INTRODUCTION</li> </ul>    | OF RELATED DEVICES                                              |     |

| <ul> <li>8/16-bit Mult</li> </ul>   | -chip Microcomputers -                                          | 675 |

| <ul> <li>4-bit Single-ch</li> </ul> | ip Microcomputer HMCS400 Series                                 | 677 |

| <ul> <li>4-bit Single-ch</li> </ul> | p Microcomputer HMCS40 Series                                   | 678 |

|                                     | ries                                                            |     |

| <ul> <li>IC Memories</li> </ul>     |                                                                 | 682 |

| <ul> <li>Gate Array .</li> </ul>    |                                                                 | 685 |

|                                     | Synthesizer System                                              |     |

|                                     | Combo LSI                                                       |     |

| •                                   |                                                                 |     |

|                                     |                                                                 |     |

| ■ HITACHI SA                        | ALES OFFICE LOCATIONS69                                         | 12  |

## GENERAL INFORMATION

- Quick Reference Guide

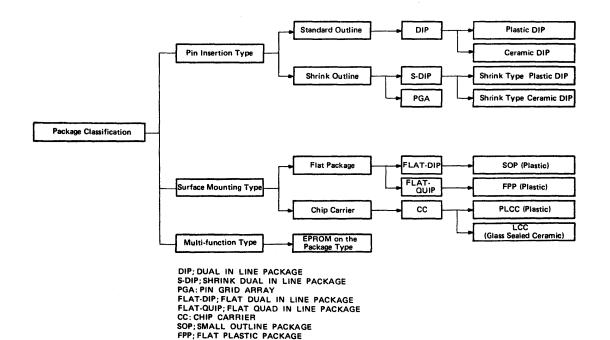

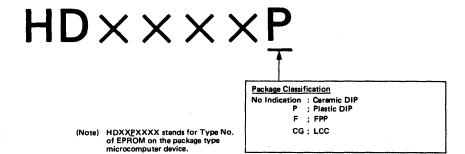

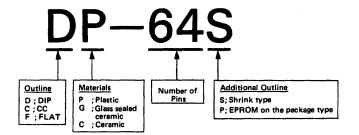

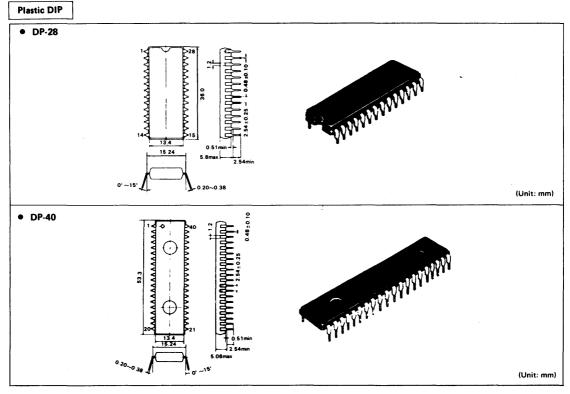

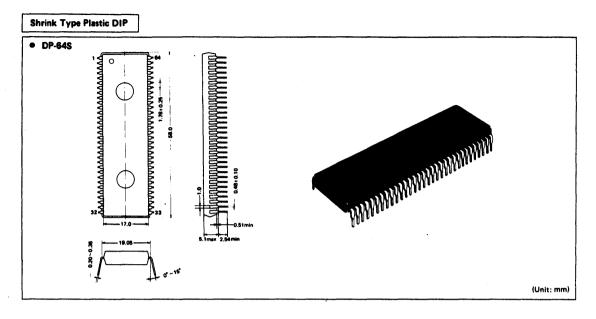

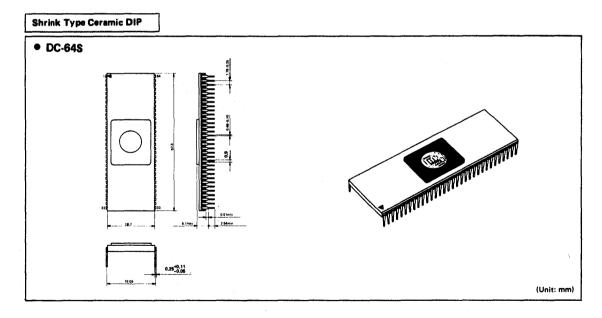

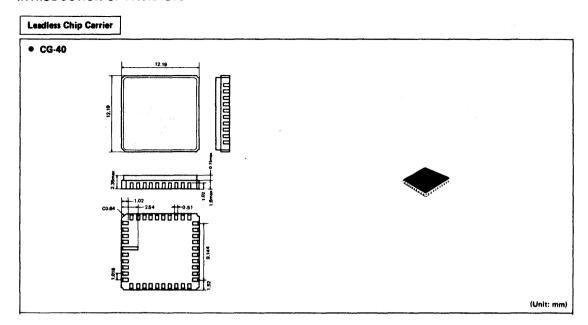

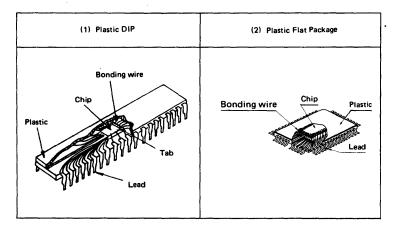

- Introduction of Packages

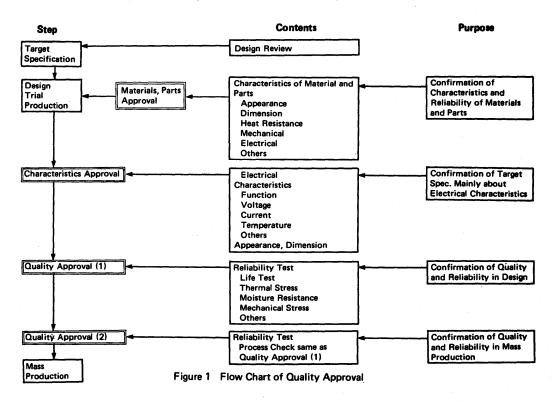

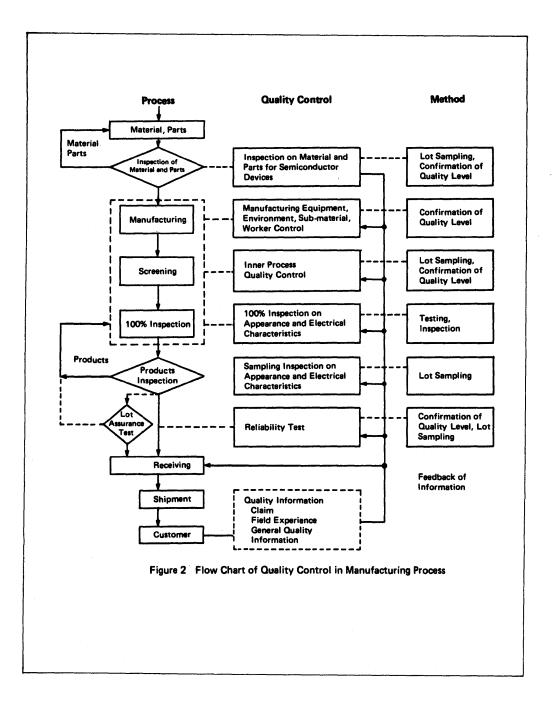

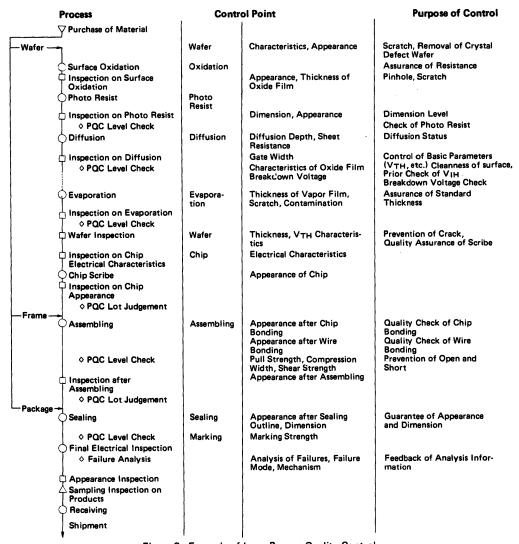

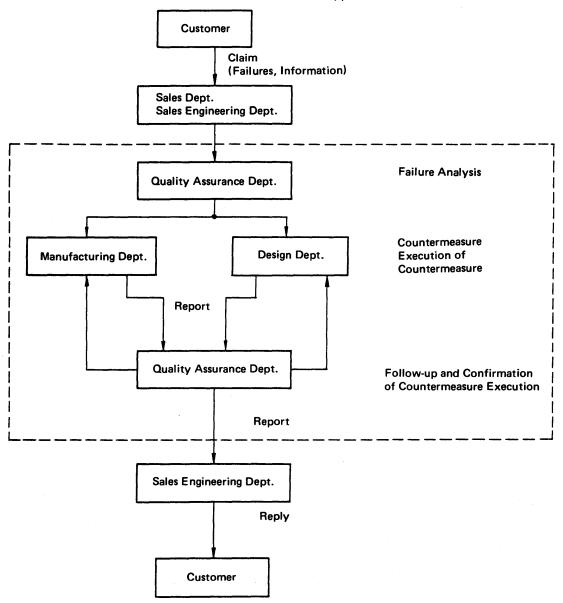

- Quality Assurance

- Reliability Test Data

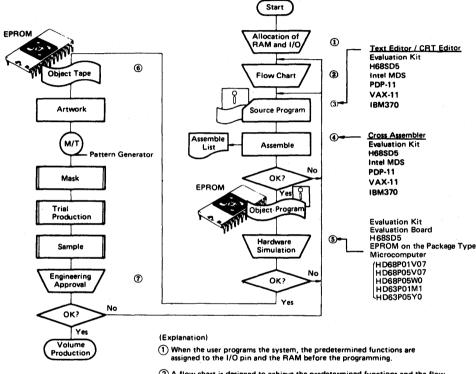

- Design Procedure and Support Tools for 8-bit Single-chip Microcomputers

#### QUICK REFERENCE GUIDE

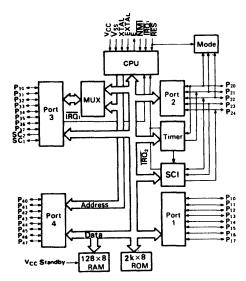

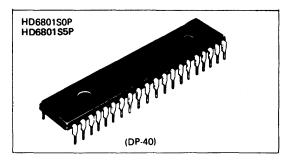

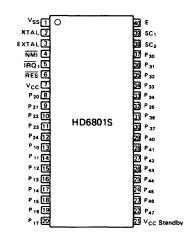

#### ■ NMOS 8-BIT SINGLE-CHIP MICROCOMPUTER HD6801 SERIES

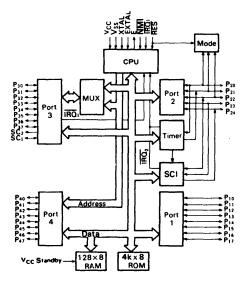

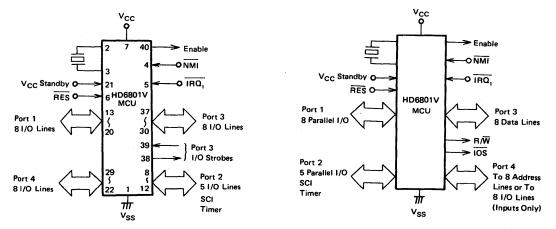

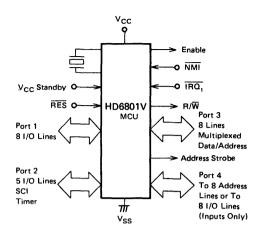

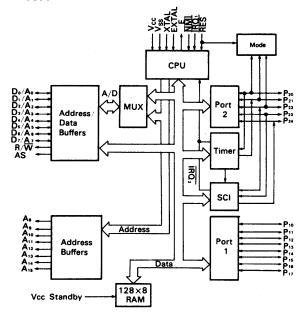

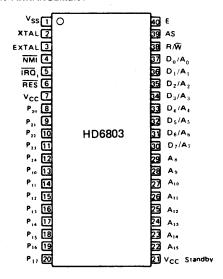

|                 | Type No.       |                  | HD6801S0<br>HD6801S5                                                                                                                       | HD6801V0<br>HD6801V5                         | HD6803<br>HD6803-1 |  |  |

|-----------------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------|--|--|

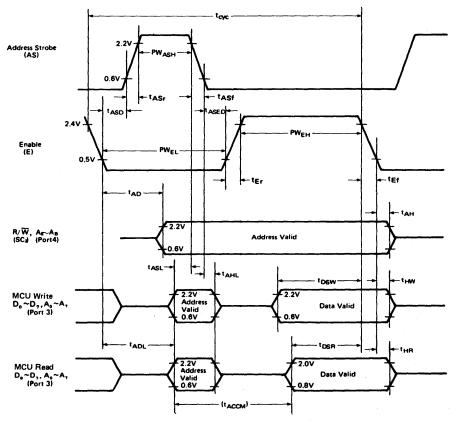

|                 | Bus Timing (N  | lHz)             | 1.0/1.25                                                                                                                                   | 1.0/1.25                                     | 1.0/1.25           |  |  |

| LSI             | Supply Voltag  | e (V)            | 5.0                                                                                                                                        | 5.0                                          | 5.0                |  |  |

| Characteristics | Operating Ten  | nperature * (°C) | 0~+70                                                                                                                                      | 0 ~ +70                                      | 0~+70              |  |  |

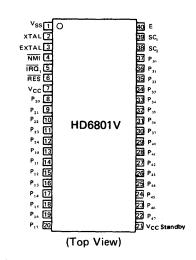

|                 | Package †      |                  | DP-40                                                                                                                                      | DP-40                                        | DP-40              |  |  |

|                 | Memory         | ROM (k byte)     | 2                                                                                                                                          | 4                                            | _                  |  |  |

|                 | Memory         | RAM (byte)       | 128                                                                                                                                        | 128                                          | 128                |  |  |

|                 | I/O Port       |                  | 29                                                                                                                                         | 29                                           | 13                 |  |  |

|                 |                | External         | 2                                                                                                                                          | 2                                            | 2                  |  |  |

|                 | Interrupt      | Soft             | 1                                                                                                                                          | 1                                            | 1                  |  |  |

| Functions       | menupi         | Timer            | 3                                                                                                                                          | 3                                            | 3                  |  |  |

|                 |                | Serial           | 1                                                                                                                                          | 1                                            | 1                  |  |  |

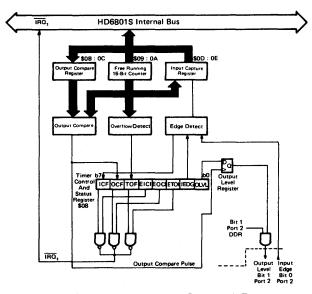

|                 | Timer          |                  | <ul> <li>Free running counter 16-bit x 1</li> <li>Output compare register 16-bit x 1</li> <li>Input capture register 16-bit x 1</li> </ul> |                                              |                    |  |  |

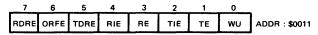

|                 | SCI            |                  | Full double step-stop type                                                                                                                 |                                              |                    |  |  |

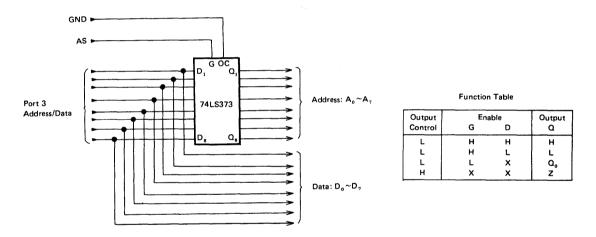

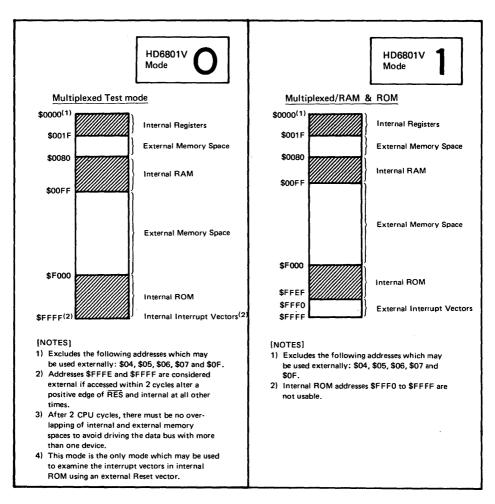

|                 | External Mem   | ory Expansion    | Address/data non-<br>(256 bytes)     Address/data mul-<br>(65k bytes)                                                                      | Address/data<br>multiple mode<br>(65k bytes) |                    |  |  |

|                 | Clock Pulse Go | enerator         | Bui                                                                                                                                        | t-in (External clock use                     | eable)             |  |  |

|                 | Built-in RAM   | Holding          |                                                                                                                                            | Yes (64 bytes)                               |                    |  |  |

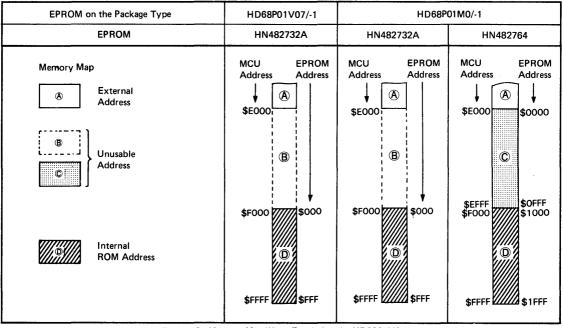

| EPROM on the Pa | ckage Type**   |                  | HD68P01V07<br>HD68P01V07-1                                                                                                                 | HD68P01V07<br>HD68P01V07-1                   | _                  |  |  |

| Compatibility   |                |                  | MC6801<br>MC6801-1                                                                                                                         | _                                            | MC6803<br>MC6803-1 |  |  |

<sup>\*</sup> Wide Temperature Range (-40  $\sim$  +85 $^{\circ}$ C) version is available.

<sup>\*\*</sup> HD68P01M0 useable.

<sup>†</sup> DP; Plastic DIP

#### • NMOS 8-BIT SINGLE-CHIP MICROCOMPUTER HD6805 SERIES

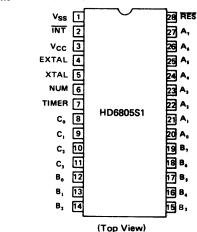

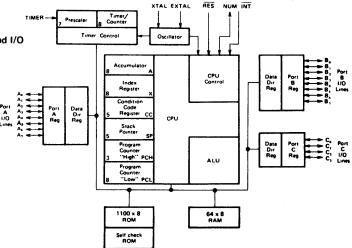

|                            | Type No.                                                                 |                                         | HD68  | B05S1        | HD68                 | 0556"                              | HD68           | USUI        |

|----------------------------|--------------------------------------------------------------------------|-----------------------------------------|-------|--------------|----------------------|------------------------------------|----------------|-------------|

|                            | Clock Frequer                                                            | ncy (MHz)                               | 1     | .0           | 1.                   | 0                                  | 1.             | 0           |

| LSI                        | Supply Voltag                                                            |                                         | 5.    | 25           | 5.:                  | 25                                 | 5.3            | 25          |

| Characteristics            | Operating Ten                                                            | nperature *** ( °C)                     | 0~+70 |              | 0~+70                |                                    | 0~+70          |             |

|                            | Package †                                                                |                                         | DP-28 |              | DP                   | -28                                | DP-40          |             |

|                            | Memory                                                                   | ROM (k byte)                            | 1.1   |              | 1.8                  |                                    | - 2            | 2           |

|                            | Wellioty                                                                 | RAM (byte)                              | 64    |              | 6                    | 4                                  | 96             |             |

|                            | 1                                                                        | I/O Port                                |       | 20           |                      | 20                                 |                | 24          |

|                            | I/O.Port                                                                 | Input Port                              | 20    | _            | 20                   | _                                  | 32             | 8           |

|                            |                                                                          | Output Port                             |       | _            | 1                    | -                                  |                | -           |

|                            |                                                                          | Nesting                                 | (     | 6            | (                    | 3                                  |                | 3           |

|                            |                                                                          | External                                | 1     |              |                      |                                    |                | )           |

|                            | Interrupt                                                                | Soft                                    | 1     |              | 1                    |                                    | 1              |             |

|                            |                                                                          | Timer                                   | 1     |              | 1                    |                                    | 1              |             |

|                            |                                                                          | Serial                                  |       | _            | -                    | _                                  | _              |             |

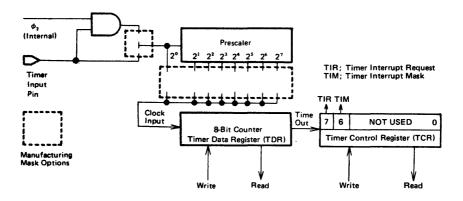

| Functions                  | Timer                                                                    |                                         |       |              |                      | 8-bit timer<br>Event coun          |                | prescaler   |

| Functions                  | Timer                                                                    |                                         |       |              |                      |                                    |                | prescaler   |

| Functions                  | Timer                                                                    |                                         |       |              |                      | Event coun                         | ter            | prescaler   |

| Functions                  |                                                                          | enerator                                | -     | <del></del>  | -                    | Event coun                         | ter            |             |

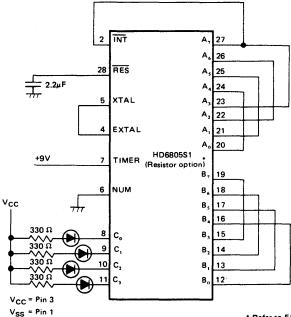

| Functions                  | SCI<br>Clock Pulse G                                                     | enerator<br>Automatic Reset (LVI)       |       |              | -                    | Resistor<br>Crystal                | ter            | -           |

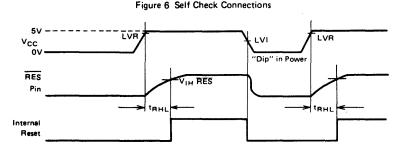

| Functions                  | SCI<br>Clock Pulse G                                                     | Automatic Reset (LVI)                   | Y     |              | •                    | Resistor<br>Crystal                | eter -         | -           |

| Functions                  | SCI Clock Pulse G Low-voltage A Self-check Mo                            | Automatic Reset (LVI)                   | Y     | es           | • • • • • • • • Avai | Resistor<br>Crystal                | -<br>Y<br>Avai | es          |

| Functions                  | SCI Clock Pulse G Low-voltage A Self-check Mo                            | Automatic Reset (LVI) ode ory Expansion | Y     | es<br>ilable | • • • • • • • • Avai | Resistor<br>Crystal<br>es          | -<br>Y<br>Avai | es<br>lable |

| Functions  EPROM on the Pa | SCI Clock Pulse G Low-voltage A Self-check Mo External Mem Other Feature | Automatic Reset (LVI) ode ory Expansion | Y     | es<br>ilable | • • • • • • • • Avai | Resistor<br>Crystal<br>es<br>lable | -<br>Y<br>Avai | es<br>lable |

<sup>\*</sup> Preliminary \*\* Under development

<sup>\*\*\*</sup> Wide Temperature Range (-40  $\sim$  +85°C) version is available. † DP; Plastic DIP

| HD68  | HD6805V1 |                                | 05T2** | HD6805W1*                                       |                         |  |

|-------|----------|--------------------------------|--------|-------------------------------------------------|-------------------------|--|

| 1.    | 0        | 1                              | .0     | 1.                                              | 0                       |  |

| 5.2   | 25       | 5.                             | 25     | 5.2                                             | 25                      |  |

| 0~    | +70      | 0~                             | +70    | 0 ~ +70                                         |                         |  |

| DP-   | 40       | DP-28                          |        | DP-                                             | 40                      |  |

| 1     | 1        | 2.5                            |        | 4                                               | 1                       |  |

| 9     | 96       |                                | i4     | 9                                               | 6                       |  |

|       | 24       |                                | 19     |                                                 | 23                      |  |

| 32    | 8        | 19                             | _      | 29                                              | 6                       |  |

|       |          | j                              |        | 1                                               | _                       |  |

| 6     | <br>i    |                                | 6      | 1:                                              | 2                       |  |

| 1     |          |                                | 1      | 2                                               | ?                       |  |

| 1     | }        |                                | 1      | 1                                               |                         |  |

| 1     |          |                                | 1      | 4                                               | )                       |  |

| _     | -        | -                              | -      |                                                 |                         |  |

|       |          |                                |        | 8-bit t with 7 presca     Event     8-bit compa | '-bit<br>ler<br>counter |  |

| -     | -        | _                              |        | _                                               |                         |  |

|       |          | • Cry                          | stal   |                                                 |                         |  |

| Y     | es       | Y                              | es     | Y                                               | es                      |  |

| Avail | able     | Avai                           | lable  | Avail                                           | able                    |  |

|       | -        |                                | _      | -                                               | -                       |  |

|       |          | PLL logi<br>for RF<br>synthesi |        | 8 byte                                          | nel<br>al<br>onverter   |  |

| HD68P | 05∨07    |                                | -      | HD68F                                           | 05W0*                   |  |

| T -   | -        | MC68                           | 05T2   | -                                               | -                       |  |

#### ■ CMOS 8-BIT SINGLE-CHIP MICROCOMPUTER HD6301 SERIES

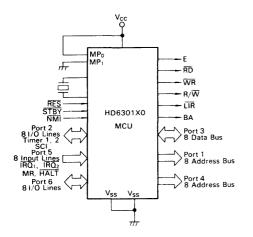

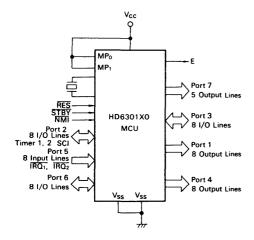

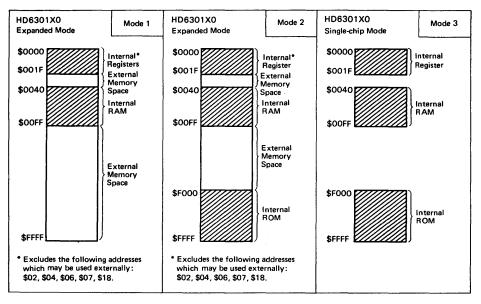

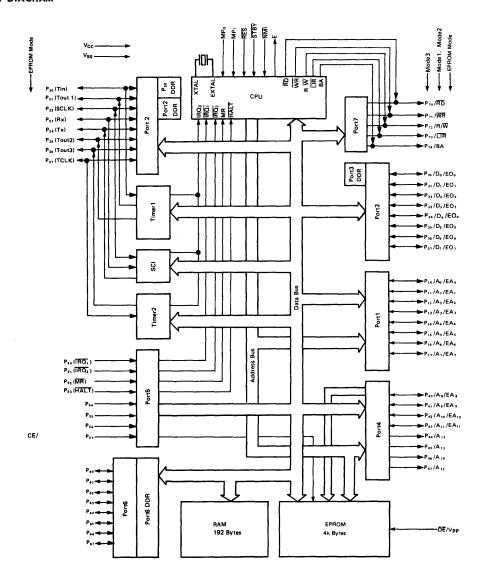

|                        | Type No.       |                    | HD6301<br>HD63A0<br>HD63B0 | 01V1                                                                | HD6301X0<br>HD63A01X0<br>HD63B01X0                                                                                                                         |                                                                                                        |  |

|------------------------|----------------|--------------------|----------------------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

|                        | Bus Timing (M  | MHz)               | 1.5 (HD                    | 1.0 (HD6301V1)<br>1.5 (HD63A01V1)<br>2.0 (HD63B01V1)                |                                                                                                                                                            | 1.0 (HD6301X0)<br>1.5 (HD63A01X0)<br>2.0 (HD63B01X0)                                                   |  |

| LSI<br>Characteristics | Supply Volta   | ge (V)             |                            | 5.0                                                                 | . 5                                                                                                                                                        | .0                                                                                                     |  |

|                        | Operating Ter  | mperature *** (°C) | 0~-                        | +70                                                                 | 0~+                                                                                                                                                        | -70                                                                                                    |  |

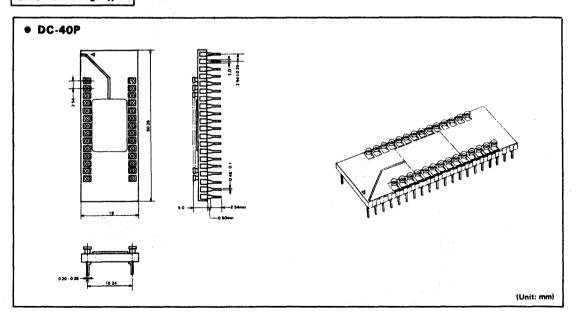

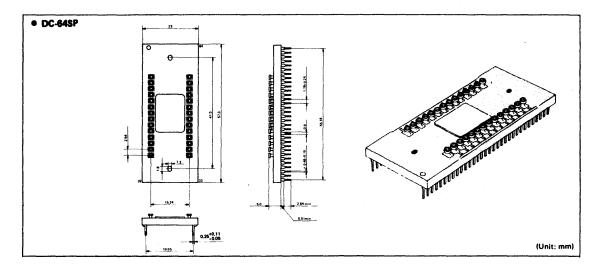

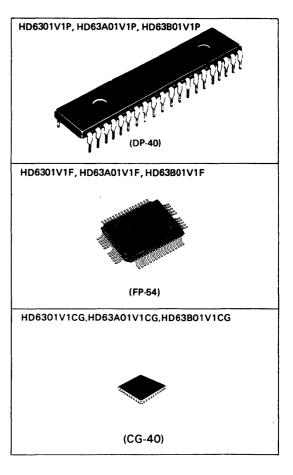

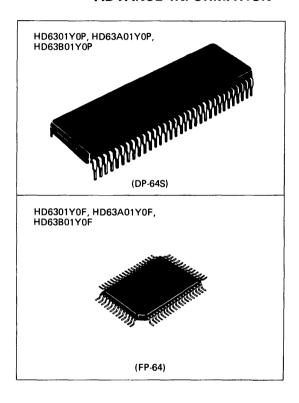

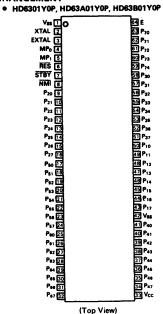

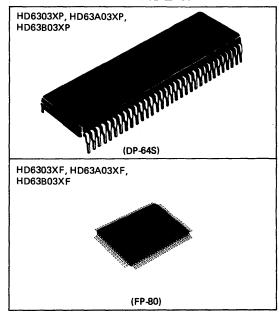

|                        | Package †      |                    | DP-40, I                   | FP-54, CG-40                                                        | DP-64S,                                                                                                                                                    | FP-80                                                                                                  |  |

|                        | Memory         | ROM (k byte)       | 4                          |                                                                     | 4                                                                                                                                                          |                                                                                                        |  |

|                        | Wiemory        | RAM (byte)         | 12                         | 8                                                                   | 19:                                                                                                                                                        | 2                                                                                                      |  |

|                        |                | I/O Port           |                            | 29                                                                  |                                                                                                                                                            | 24                                                                                                     |  |

|                        | I/O Port       | Input Port         | 29                         | _                                                                   | 53                                                                                                                                                         | 8                                                                                                      |  |

|                        |                | Output Port        |                            | -                                                                   | lΓ                                                                                                                                                         | 21                                                                                                     |  |

|                        |                | External           | 2                          |                                                                     | 3                                                                                                                                                          |                                                                                                        |  |

|                        | Interrupt      | Soft               | 2 3                        |                                                                     | 2                                                                                                                                                          |                                                                                                        |  |

|                        |                | Timer              |                            |                                                                     | 4                                                                                                                                                          |                                                                                                        |  |

| Functions              |                | Serial             | 1                          |                                                                     | 1                                                                                                                                                          |                                                                                                        |  |

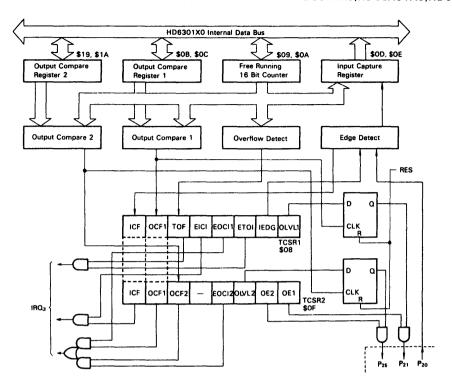

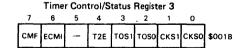

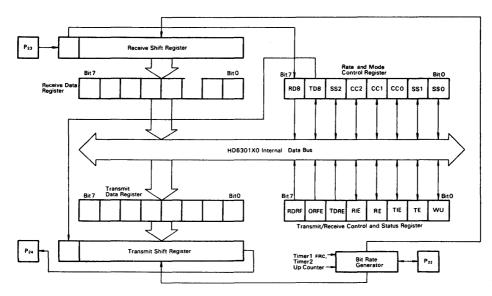

|                        | Timer          | Timer              |                            | t x 1 counter x 1 are register x 1 register x1                      | 16-bit x 1  Free running counter x 1  Output compare register x2  Input capture register x 1  8-bit x 1  (8-bit up counter x 1  Time constant register x 1 |                                                                                                        |  |

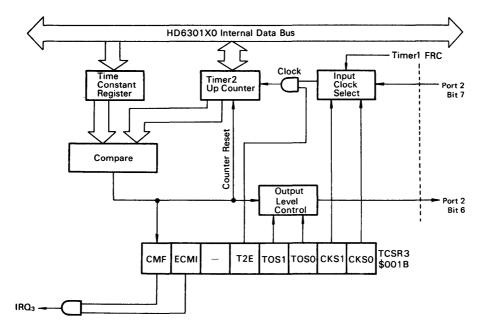

|                        | SCI            |                    | Asynch                     | ronous                                                              | Asynchronous/Synchronous                                                                                                                                   |                                                                                                        |  |

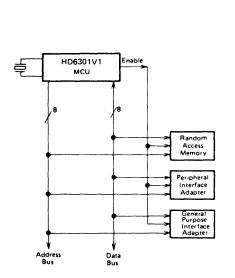

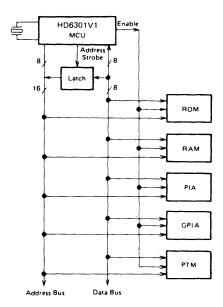

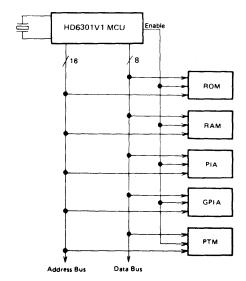

|                        | External Men   | nory Expansion     | 65k t                      | oytes                                                               | 65k b                                                                                                                                                      | ytes                                                                                                   |  |

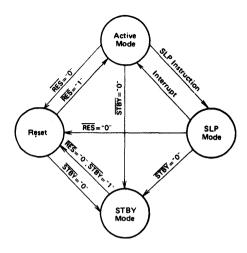

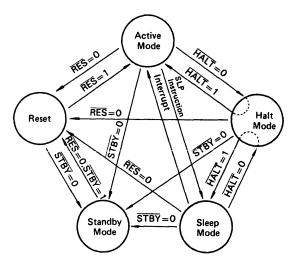

|                        | Other Features |                    | ●Low power of              | Error detection     Low power consumption modes (sleep and standby) |                                                                                                                                                            | Error detection     Low power consumption modes (sleep and standby)     Slow memory interface     Halt |  |

| EPROM on the P         | ackage Type    |                    | HD63P0<br>HD63P0<br>HD63P0 | A01M1*                                                              | HD6370<br>(EPROM                                                                                                                                           | )1X0**<br>I on-chip)                                                                                   |  |

<sup>\*</sup> Preliminary \*\* Under development \*\*\* Wide Temperature Range (-40 ~ +85°C) version is available.

<sup>†</sup> DP; Plastic DIP, FP; Plastic Flat Package, CG; Glass-sealed Ceramic Leadless Chip Carrier

| •<br>•<br>•<br>(0)<br>Y0)<br>Y0) | 1.5 (HD<br>2.0 (HD<br>5.<br>0 ~<br>DP-40, FP                                                  | 03R<br>03R<br>06303R)<br>06303R)<br>063B03R)<br>0<br>+70<br>-54, CG-40<br> | 1.5 (H<br>2.0 (H<br>E<br>0 ~<br>DP-64                                                                                                                                                | A03X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | HD638<br>1.0 (H<br>1.5 (H<br>2.0 (H<br>5<br>0 ~<br>DP-648                                                                                                                                                                                                                    | 039*** 8039*** B039*** D6303Y) D63A03Y) D63B03Y) 6.0 -+70 6., FP-64 - 56 24 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Y0)<br>Y0)                       | 1.5 (HD<br>2.0 (HD<br>5.<br>0 ~<br>DP-40, FP                                                  | 063A03R)<br>063B03R)<br>0<br>+70<br>-54, CG-40<br>-<br>-<br>28<br>13<br>-  | 1.5 (H<br>2.0 (H<br>0 ~<br>DP-64:                                                                                                                                                    | D63A03X) D63B03X) 5.0+70 S, FP-80 192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.5 (H<br>2.0 (H<br>5<br>0 ~<br>DP-648                                                                                                                                                                                                                                       | D63A03Y)<br>D63B03Y)<br>5.0<br>+70<br>5, FP-64<br>-<br>56<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                  | 0 ~<br>DP-40, FP<br>-<br>12                                                                   | +70<br>-54, CG-40<br>-<br>28<br>13<br>-                                    | 0 ~<br>DP-645                                                                                                                                                                        | - +70<br>S, FP-80<br>-<br>92<br>16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0 ~<br>DP-645                                                                                                                                                                                                                                                                | +70<br>5, FP-64<br>-<br>56<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                  | DP-40, FP                                                                                     | -54, CG-40<br>28<br>13<br>                                                 | DP-645                                                                                                                                                                               | S, FP-80<br>-<br>92<br>16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DP-645                                                                                                                                                                                                                                                                       | 5, FP-64<br>-<br>56<br>24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                  | 13                                                                                            | 28<br>13<br>—                                                              | 1                                                                                                                                                                                    | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                            | 56 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                  | 13                                                                                            | 13<br>_<br>_                                                               |                                                                                                                                                                                      | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                  | 13                                                                                            | 13<br>_<br>_                                                               |                                                                                                                                                                                      | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                              | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                  |                                                                                               | _                                                                          | 24                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                  |                                                                                               | -                                                                          | 24                                                                                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 24                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                  |                                                                                               | _                                                                          | ]                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |