# **OHITACHI** ISIS-II 6301 CROSS ASSEMBLER USER'S MANUAL

# ISIS-II 6301 CROSS ASSEMBLER USER'S MANUAL

When using this manual, the reader should keep the following in mind:

- 1. This manual may, wholly or partially, be subject to change without notice.

- 2. All rights reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this manual without Hitachi's permission.

- 3. Hitachi will not be responsible for any damage to the user that may result from accidents or any other reasons during operation of his unit according to this manual.

- 4. This manual neither ensures the enforcement of any industrial properties or other rights, nor sanctions the enforcement right thereof.

# INTRODUCTION

The S31MDS1-F is a cross assembler which runs on Intel\* development systems under the ISIS-II operating system, and processes assembly language programs for the HD6800 micro-processor and HD6801 and HD6301 single-chip microcomputers. The assembler accepts ISIS-II files containing 6800/6801/6301 source statements, and produces assembly listings and object files.

\*"Intel" is a registered trademark of Intel Corporation, Santa Clara, CA.

The cross assembler is provided in the form of a single sided, double density floppy disk.

# TABLE OF CONTENTS

· • · ·

|   |           |                                      | PAGE |

|---|-----------|--------------------------------------|------|

| 1 | DESCRIPTI | ON OF ASSEMBLER                      | 1    |

| 2 | FORMAT OF | STATEMENTS                           | 3    |

|   | 2.1 Gener | al Concepts                          | 5    |

|   | 2.1.1     | Constants                            | 5    |

|   | 2.1.2     | Location Counter                     | 7    |

|   | 2.1.3     | Symbols                              | 7    |

|   | 2.1.4     | Expressions                          | 9    |

|   | 2.1.5     | Fields                               | 10   |

|   | 2.2 Instr | cuctions                             | 13   |

|   | 2.2.1     | Inherent Addrssing Mode              | 13   |

|   | 2.2.2     | Immediate Addressing Mode            | 14   |

|   | 2.2.3     | Direct and Extended Addressing Modes | 15   |

|   | 2.2.4     | Indexed Addressing Mode              | 16   |

|   | 2.2.5     | Relative Addressing Mode             | 16   |

|   | 2.2.6     | Immediate-Direct Addressing Mode     | 17   |

|   | 2.2.7     | Immediate-Indexed Addressing Mode    | 17   |

|   | 2.2.8     | Bit-Direct Addressing Mode           | 18   |

|   | 2.2.9     | Bit-Indexed Addressing Mode          | 18   |

| PA                                          | AGE |

|---------------------------------------------|-----|

| 2.3 Directives 1                            | 18  |

| -                                           | L 9 |

| 2.3.2 ENDC2                                 | 20  |

| 2.3.3 EQU 2                                 | 21  |

| 2.3.4 FCB 2                                 | 23  |

| 2.3.5 FCC 2                                 | 24  |

| 2.3.6 FDB 2                                 | 25  |

| 2.3.7 IFxx 2                                | 26  |

| 2.3.8 ORG2                                  | 28  |

| 2.3.9 RMB 2                                 | 29  |

| 2.3.10 SET 3                                | 30  |

| 2.3.11 SPC 3                                | 31  |

| 3 USING THE ASSEMBLER                       | 32  |

| 3.1 Primary vs General Controls 3           | 33  |

| 3.2 Primary Controls 3                      | 33  |

| 3.3 General Controls3                       | 35  |

| 3.4 Initial Settings of Controls 3          | 6   |

| 4 DESCRIPTION OF FILES PRODUCED 3           | 7   |

| 4.1 Listing File 3                          | 7   |

| 4.1.1 Source Listing Format3                | 7   |

| 4.1.2 Error Messages 3                      | 9   |

| 4.1.3 Symbol Table Format                   | 0   |

| 4.1.4 Cross Reference Format4               | 1   |

| 4.2 Object File 4                           | 2   |

| 4.3 Console Output 4                        | 2   |

| APPENDIX A INSTRUCTION TABLE 4              | 3   |

| APPENDIX B EXAMPLE OF PROGRAMMING4          | -   |

| APPENDIX C EXAMPLE OF PROGRAM DEVELOPMENT 5 |     |

# **1 DESCRIPTION OF ASSEMBLER**

- - -

The ISIS-II 6301 Cross Assembler runs on Intel development systems under the ISIS-II operating system, and processes assembly language programs for the HD6800 microprocessor and HD6801 and HD6301 single-chip microcomputers. The assembler accepts ISIS-II files containing HD6800/6801/6301 source statements, and produces assembly listings and object files.

This manual assumes familiarity with the Intel development system, the ISIS-II operating system, and the HD6800 microprocessor and/or the HD6801 and/or HD6301 micro-computers. The purpose of the manual is to assist a user already familiar with the HD6800/6801/6301 instruction set and architecture in using the assembler. For further information on the development system and ISIS-II, consult the Intel publications: ISIS-II SYSTEM USER'S GUIDE, 9800306 and the publication describing your version of the MDS (development system). For information on the architecture and instruction set of the HD6800, HD6801, and/or HD6301, consult the appropriate Programming Reference Manual from the processor's manufacturer.

To use the assembler, you will require an Intel disk-based Microcomputer Development System with 32K or more of RAM memory and two or more disk drives, ISIS-II operating system software, and a diskette containing the program ASM31.\*

\*Program name is ASM31. HITACHI's Part No. is S31MDS1-F. Please note the difference.

Section 2 of this manual will describe the required assembly language statement format. Section 3 will describe the command lines used to invoke the assembler. Section 4 covers the files produced, including the source listing (with a list of possible error messages) and the object file. ----

The assembler normally assumes the opcodes to be for the HD6800 microprocessor. Use of the MOD01 or MOD31 control (see section 3.2) is necessary to enable use of the full HD6801 opcode set (of which the HD6800 opcodes are a subset). Use of the MOD31 control is necessary to enable use of the full HD6301 opcode set (of which the HD6800 and HD6801 opcodes are a subset).

2 FORMAT OF STATEMENTS

. . . . . . . . .

An assembly language program consists of a series of source lines, which fall into four categories:

- 1: Blank lines contain no printing characters.

- 2: Comment lines begin with an asterisk ("\*").

- 3: Control lines begin with a dollar sign ("S").

- 4: Assembly language statements, including instructions and directives.

Blank lines, which contain no characters other than spaces or tabs, and comment lines, which are identified by an asterisk as the first character, are ignored by the assembler except for purposes of listing, and can be included at any point before the END statement. Controls will be described in section 3, assembly language instructions in section 2.2, and assembler directives in section 2.3.

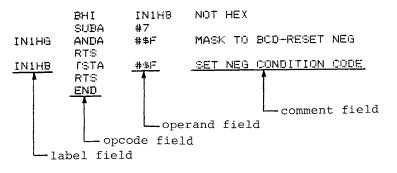

Each line consists of a series of ASCII characters ending with a carriage return and line feed. Tabs are converted to one or more spaces, as required to advance the listing to the next tab position on the line. (Tab positions occur at every eight columns starting at the first character of the line.) \$TITLE(' FIG. 2-1 INCHNP EQU \$06A0 NEGDAT EQU 205 -----assembly language statement ----blank line ORG. \$06A5 \* INPUT ONE HEXADECIMAL CHAR CONVERT TO BCD ----comment line \* NEG CONDITION CODE, RESENTEDOD HEX, SETENOT 8SR INCHNP IN1H < CONVERT BOD TO HEX > CBCDHK ChiPA #\$30 NOT HEX -----assembly language statement BMI IN1HB CMPA #\$39 IN1HG GOOD HEX BLS #\$41 CMP/A BMI IN1H8 NOT HEX #\$46 CHIPA IN1HB NOT HEX BHI SUBA #7 ANDA 排争F MASK TO BOD-RESET NEG IN1HG RTS **IN1HB** TSTA #\$F SET NEG CONDITION CODE RTS END

\*\*\*

Fig. 2-1 Sample of source program

#### 2.1 General Concepts

. . . .

Before describing the formats of individual instruction and directive statements, this manual will explain the general form of assembly language statements.

# 2.1.1 Constants

Constants can be specified as numbers (in binary, octal, decimal, or hexadecimal notation) or characters.

Number constants consists of one or more digits valid in the particular base in which they are expressed, preceded (except in the case of decimal numbers) by a special character to indicate the base. The base-designation prefixes and valid characters are given for each base in the table below:

| Base             | <u>Prefix Char</u> | Valid Digits |

|------------------|--------------------|--------------|

| 2 (binary)       | ક                  | 0,1          |

| 8 (octal)        | e                  | 07           |

| 10 (decimal)     | (none)             | 09           |

| 16 (hexadecimal) | \$                 | 09, AF       |

For example, the number 19 decimal could be expressed as "19", "\$13", "@23", or "%10011".

The allowable range of values for constants is 0..65535 decimal (\$0..\$FFFF hexadecimal). If a larger constant is specified, the constant is converted to a value within the allowed range.

Character strings are identified by their first character, which is a single-quote character ("'"). The single-quote is followed by one or more ASCII characters and a closing single-quote. To represent the single-quote character itself as one of the characters in the string, the single-quote must occur twice in a row between the opening and closing single-quote marks. ----

For example, a space would be coded as "' '", the capital letter Z as "'Z'", and the word "CAN'T" as "'CAN''T'".

Note that non-printing ASCII characters cannot be coded in this fashion. They must be coded by their numerical equivalents; for instance, a carriage return can be coded as "\$0D".

The interpreted value of the string is dependent on how the string is used. Each string is encoded as a series of bytes, one per character. The first byte corresponds to the first character of the string, and so on. If a one-character string is used in an expression, the value returned is the numeric equivalent of the ASCII character in that string, in the range \$0020..\$007F. If a two-character string is used, the value returned has the first character in the left-hand (more significant) byte and the second character in the right-hand (less significant) byte of a two-byte value. Each byte is again in the range \$20..\$7F.

For example, "'A'" returns \$41, while "'AB'" returns \$4142.

Strings of more than two characters are not meaningful in expressions; their use is limited to the FCC directive (see section 2.3.5) and the TITLE control (see section 3.3).

# 2.1.2 Location Counter

The location counter is an internal value maintained by the assembler. It indicates the address where the next instruction or data byte will be placed. The assembler assumes a starting location counter value of \$0000. The location counter can be changed at any time using the ORG directive (see section 2.3.8).

Whenever a byte of code is stored (resulting from a 6800/6801/ 6301 instruction or a data definition directive), the location counter is incremented by one (1). For example, if the location counter value is \$013A, and the instruction "LDAA #1" is encountered, the two-byte code for the instruction will be stored at locations \$013A and \$013B, and the location counter value will be changed to \$013C.

The value of the location counter can be used in expressions via the asterisk ("\*") in an expression-operand position. (In an expression-operator position, the asterisk denotes multiplication.) The location counter value is in the range \$0000..\$FFFF.

# 2.1.3 Symbols

Symbols are specified as a sequence of one to six alphanumeric characters, the first of which must be alphabetic. They can take on any values in the range \$0000...\$FFFF.

Some examples of valid symbol names are: "A", "LOCTN1", and "FFFF". Note that the latter is a symbol name and not a hexadecimal constant because it begins with a letter, not "\$". Symbols are defined when used as labels of instructions or directives. A symbol first defined as the label of a SET directive can be redefined later in the program via another SET directive. Prior to the first definition of that label, its value will be the <u>last</u> value to which it is SET in your program. After the first definition (including in the symbol table listing), the symbol always has the most recent value assigned to it by a SET directive. For example:

. . . reference 1 to symbol SYMB1 . . . SYMB1 SET 4 . . . reference 2 to symbol SYMB1 . . . SYMB1 SET 15 . . . reference 3 to symbol SYMB1 . . . END

In the above program, references 1 and 3 to symbol SYMB1 would return the value 15, while reference 2 would return the value 4. The symbol table would show the value 15 (\$000F).

Any symbol first defined as a label of some statement other than SET may not be redefined later in the program. Attempting to redefine such a symbol will result in an error (see section 4.1.2). Attempting to redefine, by means other than SET, a symbol first defined via SET will result in a similar error.

# 2.1.4 Expressions

Expressions are combinations of symbols, constants, location counter references, and/or operators which produce a value. They are used in the operand field of a statement (see section 2.1.5 for more on statement fields). The minimum expression consists of a single symbol or constant or location counter reference. Using arithmetic and logical operators and additional symbols and/or constants, more complex expressions can be constructed.

The allowed operators (all single characters) are:

- \* multiplication

- / division

- + addition

- subtraction (or negation if used as unary operator)

In addition, left and right parentheses ("(", ")") are available for grouping and for overriding operator priorities, which are as follows (all operators on the same line have the same priority; operators on higher lines are executed first):

unary -\* / + -

As mentioned above, any subexpression in parentheses is executed first, using the above priorities.

As an example of priorities of expression evaluation, the expression "5+(3+4)\*2" would produce the value 19.

# 2.1.5 Fields

Each assembly statement (instruction or directive) is divided into up to four fields as follows:

Fig. 2-2 Fields

#### (1) Field Usage

Only the opcode field is required in all assembly statements. (These fields do not apply to blank lines, comment lines, or control lines.) The opcode field contains the name of the instruction or directive. The requirements of the other fields are dependent on which instruction or directive is in the opcode field.

The label field is used for symbol definition in instructions, data definition directives, and EQU and SET directives, as described previously (see section 2.1.3).

If the instruction or directive in the opcode field uses an operand, the operand field is required. If no operand is used for that particular instruction or directive, the operand field is omitted. The contents of the operand field vary with the type of instruction or directive.

The comment field is ignored by the assembler except for purposes of listing. It allows the programmer to insert remarks into the text of the assembly language program.

# 10 HITACHI

Next come up to four pairs of hexadecimal digits, in one to four columns. For one-byte instructions, there is one column with two digits, representing the byte of code generated. For two-byte instructions, there are two columns with two digits each. For three-byte instructions, there are two columns -the first with two characters, the second with four characters (representing two bytes). Data definition directives list up to four bytes per line, each as two hexadecimal characters.

After these columns is the line number and the source line.

#### (2) Field Formatting

The label field may optionally end with a colon (":") immediately following the symbol name. The label field must begin with the first character on the line (ie, it may not have any spaces or tabs preceding it), whether it is used with or without a colon.

If the label field is present, it is followed by one or more spaces and/or tabs followed by the opcode field. If the label field is omitted, the line must begin with one or more spaces and/or tabs followed by the opcode field.

If the opcode field contains a four-letter instruction name which references a register (A, B, D, or X) with the fourth letter (for example, LDAA), the fourth letter may optionally be separated from the first three with a space or tab. For example, LDAA can be written as "LDAA" or "LDA A".

The operand field, if present, is separated from the opcode field by one or more spaces and/or tabs.

The comment field, if present, is separated from the field preceding it (the opcode field if there is no operand, the operand field if an operand is present) by one or more spaces and/or tabs.

# 2.2 Instructions

Instructions are statements which generate actual code to be executed by an HD6800/HD6801/HD6301. They are classified here according to the addressing modes they use. The addressing mode, in turn, determines the use of the operand field of an instruction.

2.2.1 Inherent Addressing Mode

Instructions with inherent addressing have no operands; the operand field is thus omitted with these instructions.

The following instructions use inherent addressing (exclusively):

| ABA      | ASLA      | ASLB      | ASRA | ASRB  | CBA  | CLC   | CLI  |

|----------|-----------|-----------|------|-------|------|-------|------|

| CLRA     | CLRB      | CLV       | COMA | COMB  | DAA  | DECA  | DECB |

| DES      | DEX       | INCA      | INCB | INS   | INX  | LSRA  | LSRB |

| NEGA     | NEGB      | NOP       | PSHA | PSHB  | PULA | PULB  | ROLA |

| ROLB     | RORA      | RORB      | RTI  | RTS   | SBA  | SEC   | SEI  |

| SEV      | SWI       | TAB       | TAP  | TBA   | TPA  | TSTA  | TSTB |

| TSX      | TXA       | WAI       |      |       |      |       |      |

| (for HD6 | 5801/HD63 | 301 only: | ABX  | ASLD  | LSLA | LSLB  | LSLD |

|          |           |           | LSRD | MUL   | PSHX | PULX) |      |

| (for HD6 | 5301 only | :         | SLP  | XGDX) |      |       |      |

. .

These instructions generate one byte of code each.

# 2.2.2 Immediate Addressing Mode

Instructions with immediate addressing require an operand field consisting of the character "#" followed by an expression (for example, "LDAA #VALUE1-1".

All instructions which can use immediate addressing can also use direct, extended, and indexed addressing (discussed in sections 2.2.3 and 2.2.4 below).

The following instructions can use immediate addressing. The expression in the operand field should produce a value in the range 0..255 (\$0..\$FF) for the two-byte instructions and 0..65535 (\$0..\$FFFF) for the three-byte instructions. The two-byte immediate instructions are:

A DCA ADCB ADDA ADDB ANDA ANDB BITA BITB CMPA CMPB EORA EORB LDAA LDAB ORAA ORAB SBCA SBCB SUBA SUBB

The three-byte immediate instructions are:

CPX LDS LDX (for HD6801/HD6301 only: ADDD LDD SUBD)

# 2.2.3 Direct and Extended Addressing Modes

Instructions with direct and extended addressing require an operand field consisting of an expression (which the HD6800/6801/6301 interprets as an address). If the instruction can use direct addressing, and the expression contains no forward references (see section 2.3.3 for an explanation of forward references) and evaluates to a value in the range 0..255 (\$0..\$FF), direct addressing will be automatically selected, and the instruction will produce two bytes of code. In all other cases, extended addressing will be used, and the instruction will produce three bytes of code.

The following instructions can use either direct or extended addressing:

| ADCA    | ADCB     | ADDA      | ADDB | ANDA | ANDB | BITA  | BITB |

|---------|----------|-----------|------|------|------|-------|------|

| CMPA    | CMPB     | CPX       | EORA | EORB | LDAA | LDAB  | LDS  |

| LDX     | ORAA     | ORAB      | SBCA | SBCB | SUBA | SUBB  |      |

| (for HD | 6801/HD6 | 301 only: | ADDD | LDD  | STD  | SUBD) |      |

The following can use extended but not direct addressing:

| ASL     | ASR       | CLR       | COM  | DEC | INC | JMP | JSR |

|---------|-----------|-----------|------|-----|-----|-----|-----|

| LSR     | NEG       | ROL       | ROR  | TST |     |     |     |

| (for HD | 6801/HD63 | 301 only: | LSL) |     |     |     |     |

For HD6801/HD6301 only: JSR can use direct as well as extended addressing.

#### 2.2.4 Indexed Addressing Mode

Instructions with indexed addressing require an operand field consisting of an expression (interpreted by the 6800/6801/6301 as an address) followed immediately by the two-character suffix ",X". For example: "LDAA OFFSET,X". They generate three bytes of code.

The following instructions can use indexed addressing. Note that they are the same instructions as those which can use extended addressing:

| ADCA     | ADCB     | ADDA     | ADDB | ANDA | ANDB | ASL  | ASR   |

|----------|----------|----------|------|------|------|------|-------|

| BITA     | BITB     | CLR      | CMPA | CMPB | COM  | CPX  | DEC   |

| EORA     | EORB     | INC      | JMP  | JSR  | LDAA | LDAB | LDS   |

| LDX      | LSR      | NEG      | ORAA | ORAB | ROL  | ROR  | SBCA  |

| SBCB     | SUBA     | SUBB     | TST  |      |      |      |       |

| (for HD6 | 801/HD63 | 01 only: | ADDD | LDD  | LSL  | STD  | SUBD) |

# 2.2.5 Relative Addressing Mode

Instructions with relative addressing require an operand field consisting of an expression producing as a value an address which is in the range \*-126 to \*+129 where "\*" is the location counter value prior to processing the instruction (ie, "\*" is the address at which the first byte of the instruction will be placed).

The following instructions use relative addressing (exclusively):

| BCC  | BCS       | BEQ      | BGE   | BGT | BHI  | BLE | BLS |

|------|-----------|----------|-------|-----|------|-----|-----|

| BLT  | BMI       | BNE      | BPL   | BRA | BSR  | BVC | BVS |

| (for | HD6801/HD | 6301 onl | y:BHS | BLO | BRN) |     |     |

2.2.6 Immediate-Direct Addressing Mode (HD6301 only)

Instructions with immediate-direct addressing require two operands: the character "#" followed by an expression (in the range 0..255, or \$0..\$FF), and a direct address value (in the range 0..255, or \$0..\$FF), separated by commas. For example: "AIM #\$7F,\$D5".

The following HD6301 instructions use immediate-direct addressing (plus immediate-indexed addressing):

AIM EIM OIM TIM

2.2.7 Immediate-Indexed Addressing Mode (HD6301 only)

Instructions with immediate-indexed addressing require two operands: the character "#" followed by an expression (in the range 0..255, or \$0..\$FF), and an expression (with a value in the range 0..255, or \$0..\$FF) followed immediately by the two-character suffix ",X", separated by commas. For example: "OIM #\$18,2,X".

See section 2.2.6 above for the HD6301 instructions which use immediate-indexed (and immediate-direct) addressing.

#### 2.2.8 Bit-Direct Addressing Mode (HD6301 only)

Instructions with bit-direct addressing require two operands: the bit number (in the range 0..7) and a direct address value (in the range 0..255, or \$0..\$FF), separated by commas. For example: "BSET 4,\$3B".

The following HD6301 instructions use bit-direct (and bit-indexed) addressing:

BCLR BSET BTGL BTST

2.2.9 Bit-Indexed Addressing Mode (HD6301 only)

These instructions (the same ones as listed in section 2.2.8 above) require two operands: the bit number (in the range 0..7), and an expression (with a value in the range 0..255, or \$0..\$FF) followed immediately by the two-character suffix ",X", separated by commas. For example: "BTGL 3,OFST,X".

#### 2.3 Directives

Directives differ from instructions in that they do not produce code for instructions which can be executed by the 6800/6801/ 6301. Some place data constants into the code; others generate no code at all, but are used by the assembler for other purposes, such as changing the location counter or signifying the end of your program. The valid assembler directives are:

| END  | ENDC | EQU  | FCB  | FCC  | FDB  | IFC | IFEQ |

|------|------|------|------|------|------|-----|------|

| IFGE | IFGT | IFLE | IFLT | IFNC | IFNE | ORG | RMB  |

| SET  | SPC  |      |      |      |      |     |      |

# 2.3.1 END

. . . .

The END directive is used to indicate the end of your program. It cannot be omitted, and must be the last line of the program. Any lines following the first END statement occurring in the file will be ignored (they will not even be listed). The END statement does not use the operand field.

ISIS-II 6301 CROSS ASSEMBLER, V1.0, HITACHI LTD.

1 \$20031 2 \* 3 \* END DIRECTIVE 4 \* 1000 ORIG \$1000 6 7 START LDD 1000 CC 0000 **#**O 1003 FD 1006 8 STD VAL. 10 VAL RMB 2 1006 1008 ENL 11

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 2-3 END directive

PAGE

2.3.2 ENDC

The ENDC directive is used to indicate the end of a conditional assembly section initiated by a corresponding IFC directive (see section 2.3.7). The maximum nesting depth allowed for conditional assembly directives (IFxx..ENDC blocks) is eight.

PAGE 1

|                                                    | 1 *<br>2 * CONE<br>3 * | DITIONAL ASSEMBLY                |

|----------------------------------------------------|------------------------|----------------------------------|

| 0001<br>0002                                       | 5 FLAG1<br>6 FLAG2     | SEN 1<br>SET 2                   |

|                                                    | 8<br>9<br>10           | IFEQ FLAG1<br>FCC 'SKIP'<br>ENDC |

| 0000 20 41 53 53<br>0004 45 4D 42 40<br>0008 45 20 | 12<br>13<br>14<br>15   | IFNE FLAG2<br>FCC 'ASSEMBLE'     |

|                                                    | 16                     | ENIC                             |

| 000A 20 41 53 53<br>000E 45 4D 42 40<br>0012 45 20 | 18<br>19<br>20         | IFEQ FLAG1-1<br>FCC 'ASSEMBLE'   |

| 0012 45 20                                         | 21<br>22               | ENDO                             |

| 0014                                               | 24                     | END                              |

ISIS-II 6301 CROSS ASSEMBLER, V1.0, HITACHI LTD.

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 2-4 ENDC directive

2.3.3 EQU

The EQU (equate) directive is used to assign a value to a symbol. While a symbol may be defined by placing the symbol name in the label field of an instruction statement or a data constant directive, that definition can only give the symbol the value of the location counter at that point in the program. Symbol definition with the EQU directive allows the symbol to take on any value, which is stated as an expression in the [required] operand field. For example:

| VAL  | EQU  | 5+(3+4)*2 |

|------|------|-----------|

| LOCA | EQU  | *         |

| LOCB | LDAA | #VAL      |

would assign the value 19 to VAL and use that value as the immediate operand of the LDAA instruction. LOCA and LOCB would both be assigned the same value, that of the location counter before the LDAA instruction is processed.

ISIS-II 6301 CROSS ASSEMBLER, V1.0, HITACHI LTD. PAGE 1

1 \* 2 \* EQU DIRECTIVE 3 \*

| 0000                         | 6 LAB1                                   | RMB               | 100                                          |

|------------------------------|------------------------------------------|-------------------|----------------------------------------------|

| 0003                         | 8 LAB2                                   | EQU               | LAB1+5                                       |

| 0005                         | 10 LAB3                                  | EQU               | LAEC                                         |

| 0180<br>0180<br>9600<br>0180 | 12 LAB4<br>13 LAB5<br>14 LAB6<br>15 LAB7 | EQU<br>EQU<br>EQU | 75*512/100<br>\$180<br>512*73<br>19200*2/100 |

| 0064                         | 17                                       | END               |                                              |

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 2-5 EQU directive

One symbol may be used in defining another symbol. If the symbol used in an operand field expression is defined later in your program than its use in that expression, then it is said that the expression contains a "forward reference" to the symbol. Two-level forward referencing is when the definition of a forward-referenced symbol itself contains a forward reference. Such two-level forward referencing cannot be handled by the assembler, which will not be able to define the first symbol in the chain. Consider this section of a program:

| VALl | EQU | 1    |

|------|-----|------|

| VAL2 | EQU | VAL4 |

| VAL3 | EQU | VAL1 |

| VAL4 | EQU | VAL6 |

| VAL5 | EQU | VAL4 |

| VAL6 | EQU | 6    |

| VAL7 | EQU | VAL3 |

In the above example, VAL1 is set to 1 and VAL6 is set to 6. VAL3 is also set to 1, then VAL7 is set to 1. Now consider VAL4; it contains a forward reference to VAL6 but the definition of VAL6 itself contains no forward references, so VAL4 will be correctly set to 6. VAL5 uses VAL4 after VAL4 has been defined, so again there is no problem. But VAL2 has a forward reference to VAL4, which in turn has a forward reference to VAL6. This is two levels of forward referencing, and cannot be processed correctly. VAL2 will be flagged as undefined.

# 2.3.4 FCB

The FCB (form constant byte) directive requires one or more operands separated by commas (","). The value of each of the operands should be in the range 0..255 (\$0..\$FF -- 8 bits). Each operand value will be stored as one byte in the generated code, in the order that the operands occur, left to right.

ISIS-II 6301 CROSS ASSEMBLER, V1.0, HITACHI LTD.

1 🛪 2 \* FCB DIRECTIVE 3 × 0000 FF 5 FCB **≸**FF 0001 01 01 FC8 \*, %01 6 0003 OA 7 LAB FCB 5\*2 0004 03 09 08 8 FCB LA8,9,8 9 END 0007

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 2-6 FCB directive

PAGE

2.3.5 FCC

The FCC (form constant character string) directive requires in the operand field either: (1) a character string enclosed in single quotes; or (2) a number, followed by a comma, followed by a string in single quotes. Each character in the string will be stored as one byte in the generated code, in the order that the characters occur, left to right. If the second form of the operand is used, the number given will determine the number of bytes to be generated. If the number is greater than the count of characters in the string, space characters (" ", or \$20) will be appended to the string until the specified number of bytes has been generated. Examples:

FORM1 FCC 'STRING OF TEXT' FORM2 FCC 80,'STRING TO WHICH SPACES ARE APPENDED'

JSIS-II 6301 CROSS ASSEMBLER, V1.0, HITACHI LTD. PAGE 1

1 \* 2 \* FCC DIRECTIVE 3 \* 0000 54 45 58 54 5 MS61 FCC 'TEXI' 0004 54 45 58 54 6 MSG2 FCC '9,'TEXT' 0008 20 20 20 20 7 0000 20 8 000D 9 END

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 2-7 FCC directive

# 2.3.6 FDB

. .....

The FDB (form double-byte constant) directive requires one or more operands separated by commas. The value of each operand can be anywhere in the range 0..65535 (\$0..\$FFFF -- 16 bits). Each operand value will be stored as two consecutive bytes (more significant byte first) in the generated code.

ISIS-II 6301 CROSS ASSEMBLER, V1.0, HITACHI LTD.

1 \* 2 \* FDB DIRECTIVE 3 \*

| 0000 00 02<br>0002 00 0F 00 FF<br>0006 0F FF FF FF | 5<br>6 LAB<br>7 | FDB<br>FDB  | 2<br>\$F,\$FF,\$FFF,\$FFF |

|----------------------------------------------------|-----------------|-------------|---------------------------|

| 000A 00 04<br>000C                                 | 8<br>9          | FDB<br>ENLI | LA8+2                     |

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 2-8 FDB directive

PAGE

2.3.7 IFxx

These directives allow the assembler to conditionally assemble the section of your program between the IFxx directive and the corresponding ENDC directive. Two forms are available:

> IFtypel stringl, string2 IFtype2 expression

With the first form, the two strings are compared. If they compare and the IFC directive is used, or if they do not compare and the IFNC directive is used, the conditional program section will be assembled; otherwise it will skipped.

With the second form, the expression is evaluated and compared to zero. The result of that comparison, along with the specific directive used, determines whether or not the conditional code will be assembled. The list of directives used with this form, along with the comparison results which will cause assembly of the conditional code to take place, is as follows:

IFEQexpression = 0IFGEexpression >= 0IFGTexpression > 0IFLEexpression <= 0</td>IFLTexpression < 0</td>IFNEexpression  $\neq 0$

The maximum nesting depth allowed for IFxx..ENDC blocks is eight.

|                                                               | 1 *<br>2 * COND1<br>3 *    | TIONAL A            | ASSEMELY                |

|---------------------------------------------------------------|----------------------------|---------------------|-------------------------|

| 0001<br>0002                                                  | 5 FLAG1<br>6 FLAG2         | SET<br>SET          | 1<br>2                  |

| 1                                                             | 8<br>19<br>10              | IFEQ<br>FCC<br>ENDC | FLAG1<br>' SKIP '       |

| 0000 20 41 53 53 1<br>0004 45 48 42 40 1<br>0008 45 20 1      | 12<br>13<br>14             | IFNE<br>FCC<br>ENDC | FLAG2<br>' ASSEMBLE '   |

| 1<br>000A 20 41 53 53 1<br>000E 45 40 42 40 2<br>0012 45 20 2 | .8<br>.9<br>20<br>21<br>22 | IFEQ<br>FCC<br>ENDC | FLAG1-1<br>' ASSEMRLE ' |

| 0014 2                                                        | 24                         | END                 |                         |

ASSEMBLY COMPLETE. NO ERRORS.

----

Fig. 2-9 IFxx directive

# 2.3.8 ORG

The ORG (origin) directive is used to change the value of the location counter to the value of the expression in the [required] operand field. The expression may not contain any forward references.

PAGE 1

| ISIS-II | 6301 | CROSS | ASSEMBL     | ER,    | V1. | 0, HIT | ACHI LTD. |

|---------|------|-------|-------------|--------|-----|--------|-----------|

|         |      |       | 1<br>2<br>3 | *<br>* | ORG | DIRECT | IVE       |

| 0000    |      |       | 4           |        |     | RMB    | 10        |

| 0020    |      |       | 6           |        |     | ORG    | \$20      |

| 0020    |      |       | 7           |        |     | RHB    | 5         |

| 0100    |      |       | 9           |        |     | ORG    | \$100     |

| 0100    |      |       | 11          |        |     | END    |           |

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 2-10 ORG directive

# 2.3.9 RMB

. . . . . . . .

The RMB (reserve memory bytes) directive adds the value of the [required] operand field expression to the location counter, in order to reserve a block of memory, which is not set to any value. The expression may not contain any forward references.

ISIS-II 6301 CROSS ASSEMBLER, V1.0, HITACHI LTD.

FAGE 1

|                      | 1<br>234    | **         | RMB | DIRECTIVE         | <u>.</u> |

|----------------------|-------------|------------|-----|-------------------|----------|

| 0000<br>0001<br>000B | 6<br>7<br>8 | CLA<br>CLA |     | RMB<br>RMB<br>ENU | 1<br>10  |

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 2-11 RMB directive

# 2.3.10 SET

The SET directive functions like the EQU directive (see section 2.3.3) except that it allows redefinition of the symbol in the label field. An operand is required. For a clarification of the difference between EQU and SET, see the explanation on the definition of symbols (section 2.1.3).

ISIS-II 6301 CROSS ASSEMBLER, V1.0, HIJACHI LTD. PAGE 1

| 1 | * |     |           |

|---|---|-----|-----------|

| 2 | * | SET | DIRECTIVE |

| 3 | * |     |           |

| 0000 | Ċ  | SLAB1 | SEN | :40     |

|------|----|-------|-----|---------|

| 0000 | 8  | SLAB2 | SET | SLAB1   |

| 0005 | 10 | SLAB2 | SEI | 5       |

| 0004 | 12 | SLAB2 | SET | SLA82-1 |

| 0000 | 14 |       | END |         |

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 2-12 SET directive

## 2.3.11 SPC

The SPC (space) directive is used to skip a number of blank lines on the listing. The line with the SPC directive is not printed, but in its place are inserted blank lines. The [required] operand value is the number of blank lines to be inserted (limited to the number of lines remaining on the listing page). "SPC 1" produces the same effect as a blank source line. "SPC 255" produces the same effect as a page eject control with normal length pages.

## 3 USING THE ASSEMBLER

An assembly is initiated by one of the following commands to the ISIS-II operating system:

ASM31 sourcefile controls :F1:ASM31 sourcefile controls :Fn:ASM31 sourcefile controls

The first form is used if the assembler program, ASM31, is on the diskette inserted into drive 0 (typically your system diskette). The second form is used if the assembler is on the diskette inserted into drive 1. The third command is a general form of the second, where the drive number where the diskette with the assembler is located is substituted for the letter "n" in ":Fn:ASM31".

"sourcefile" is the name of a file containing the program to be assembled. A typical name might be ":Fl:TEST2.M31" (if the file is on the diskette in drive 1).

"controls" is an optional list of assembly controls, in any order, as discussed below.

## 3.1 Primary vs General Controls

Controls are classified according to where they can be used. A primary control may appear in the console command, or as an embedded control line before the first assembly language statement, blank line, or comment line in the source file. A general control may appear in the console command, or as an embedded control line at any location in the source file prior to the END statement.

An embedded control line in the source file begins with a dollar sign ("\$") as the first character and may contain one or more controls.

Some controls require a file name or a number enclosed in parentheses following the control name. There may optionally be one or more spaces between the control name and the open parenthesis character ("(").

3.2 Primary Controls

PRINT (name) Causes an assembly listing to be written to the specified file or device. Examples: PRINT (:LP:) -- list to the line printer PRINT (:Fl:TMPFIL.LST) -- list to file PRINT (:CO:) -- list to the console

NOPRINT Suppresses the assembly listing.

OBJECT (name) Causes an object module in Intel\* hexadecimal paper tape format to be written to the specified file or device. Examples: OBJECT (:Fl:OBJFIL.HEX) -- to disk file OBJECT (:HP:) -- output to tape punch

NOOBJECT Suppresses the object module.

- MOD01 Allows use of HD6801 opcodes (see section 1).

- MOD31 Allows use of HD6301 opcodes (see section 1).

- SYMBOLS Causes a sorted listing of all user-defined symbols to be written on the list device at the end of the assembly.

- NOSYMBOLS Suppresses the symbol table listing.

- XREF Causes a sorted cross reference listing of all symbols, giving the line numbers where the symbol was used and defined, to be written on the list device at the end of the assembly.

- NOXREF Suppresses the cross reference listing.

- PAGING Causes the assembly listing to be segmented into pages, with a page number and header at the top of each page.

- NOPAGING Suppresses the paging option.

- \* "Intel" is a registered trademark of Intel Corporation.

FORMS Causes the assembler to issue a form feed character for moving the listing to the top of a new page.

NOFORMS Suppresses the forms option; causes the assembler to issue several line feed characters instead of the form feed character.

PAGEWIDTH (nn) Causes the assembler listing pages to be "nn" columns wide. Examples: PAGEWIDTH (132) PAGEWIDTH (80)

PAGELENGTH (nn) Causes the assembler listing pages to be "nn" lines long. Examples: PAGELENGTH (84) -- legal size paper PAGELENGTH (66) -- letter size paper

3.3 General Controls

- LIST Enables the listing of source statements until the next NOLIST control is encountered.

- NOLIST Disables the listing of statements until the next LIST control is encountered.

- TITLE ('text') Causes the specified text line (maximum 72 characters) to be printed as a title at the top of each page of the listing.

- EJECT Causes the next line of the listing to begin at the top of a new page.

INCLUDE (name) Following this control line, the assembler will input source lines from the file specified by "name"; at the end of the "name"d file, input of source lines will resume from the original source file, immediately following the INCLUDE control line. INCLUDEs can be nested to a depth of five.

### 3.4 Initial Settings of Controls

If not, or until, explicitly set in the command line or in embedded control line statements, the default settings of the controls are as follows:

```

PRINT (sourcefilename.LST)

OBJECT (sourcefilename.HEX)

SYMBOLS

NOXREF

PAGING

FORMS

PAGEWIDTH (120)

PAGELENGTH (66)

```

In explanation of the default PRINT and OBJECT controls: if not explicitly specified and not suppressed by the NOPRINT or NOOBJECT controls, the default listing and object files have the same name and disk drive number as the source file, and the extensions .LST for the listing file and .HEX for the object module file.

The MODOl and MOD3l options are <u>not</u> assumed unless explicitly requested; without them ASM3l recognizes only HD6800 opcodes.

#### 4 DESCRIPTION OF FILES PRODUCED

#### 4.1 Listing File

. . . . . .

The listing file (normally produced unless suppressed by the NOPRINT control) contains a listing of your source program with generated object code and any error messages, a symbol table (unless suppressed by the NOSYMBOLS control), and (if selected by the XREF control) a cross reference table. These sections of the listing are described in further detail in the following sections. (This description assumes that you are using the PAGING option.)

### 4.1.1 Source Listing Format

The first line on each page identifies the version of the assembler and gives the page number of the listing. The second line contains the title specified by the TITLE directive, if any.

The rest of the page consists of source file lines, one per listing line. There are several items on each listing line to the left of the source line. The first is the error character, normally blank unless the assembler detected an error in processing the source line. Next is a four-hexadecimal-digit value: on EQU and SET statements, it is the value assigned to the symbol in the label field. On ORG statements, it is the new location counter value. On instruction and data definition directive statements, it is the location at which the first byte is placed. 1 \$MOD31

-

| 0100                                                                                                                                                                                                                                                                                                                                                      | 5 * (A,B)                                                                                                                                                                                    | RT BINAR<br>BINARY<br>CINTER T                            | VALUE<br>O STURE                                                                       | IMAL & STORE 5 CHAR<br>DACIMAL CHARS                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0100<br>0101<br>0103                                                                                                                                                                                                                                                                                                                                      | 10 SAVEA<br>11 SAVEX<br>12 SAVEX1                                                                                                                                                            |                                                           | 1<br>2<br>2                                                                            | ACCUMULATOR A<br>STORE DATA POINTER<br>POINTER TO CONSTANTS                                                                         |

| 0200<br>0200 FF 0101<br>0203 CE 022F<br>0206 7F 0100<br>0209 A3 00<br>0208 25 05<br>020D 7C 0100<br>0210 20 F7<br>0212 E3 00<br>0214 36<br>0215 FF 0103<br>0218 FE 0101<br>0218 8B 30<br>0211 A7 00<br>0210 A7 00<br>0211 A7 00<br>0211 FF 0101<br>0221 FF 0101<br>0224 FE 0103<br>0227 08<br>0227 08<br>0228 08<br>0229 8C 0239<br>0220 26 D8<br>0222 3E | 14<br>15<br>17<br>17<br>17<br>18<br>17<br>20<br>21<br>22<br>19<br>20<br>21<br>22<br>22<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36 | SUBD<br>BCS<br>INC<br>BRA                                 | SAVEA<br>0,X<br>CVDECS<br>SAVEA<br>CVDEC2<br>0,X<br>SAVEX1<br>SAVEX1<br>SAVEX<br>SAVEX | INC CHAR BEING BUILT<br>RESTORE PARTICAL RESULT<br>X - STORE CHAR POINTER<br>MAKE ASCII CHAR<br>RESTORE A<br>X=POINTER TO CONSTANTS |

| 022F 27 10<br>0231 03 E8<br>0233 00 64<br>0235 00 0A<br>0237 00 01<br>0239                                                                                                                                                                                                                                                                                | 38 * CONST<br>39 K10K<br>40<br>41<br>42<br>43<br>43                                                                                                                                          | ANTS FOR<br>FDB<br>FDB<br>FDB<br>FDB<br>FDB<br>FDB<br>END | CONVERS<br>10000<br>1000<br>100<br>10<br>1                                             | NCI                                                                                                                                 |

ASSEMBLY COMPLETE. NO ERRORS.

Fig. 4-1 Source listing

#### 4.1.2 Error Messages

- - ---

The first error detected by the assembler on any source line processed is reported by a single letter placed in the first column of the listing line. The possible error codes are:

- A Invalid addressing mode.

- B Relative branch range error.

- C Command line error. An embedded control line in error, or a primary control occurring after an assembly statement.

- D Depth error. Complex expression overflows internal stack.

- I Invalid character in source.

- L Invalid label in label field.

- M Multiple symbol definition.

- N Nesting error. Parentheses or quotes do not match.

- 0 Opcode error. Unrecognizable opcode.

- P Phase error. Due to illegal forward references elsewhere.

- Q Questionable syntax.

- R Invalid or missing register specification.

- S Syntax error. Missing or extra operands.

- U Undefined symbol reference.

- V Value error. Operand exceeds allowed range.

1SIS-II 6301 CROSS ASSEMBLER, V1.0, HITACHI LTD.

PAGE 1

| 1000                                                      | 1<br>2 *                                         | ORB                          | \$1000 START AT 1000 HEX            |

|-----------------------------------------------------------|--------------------------------------------------|------------------------------|-------------------------------------|

| 004E<br>1FF0<br>006F<br>003C                              | 3 IMMED<br>4 LÜNGI<br>5 DIRECT<br>6 INDEX<br>7 * | EQU<br>EQU<br>EQU<br>EQU     | %01001110<br>\$1FF0<br>\$4F<br>\$3C |

| S 1000 30 008B<br>1003 43<br>B 1004 20 7D<br>1006 BD 006F | 8<br>9<br>10<br>11<br>12 *                       | ADD A<br>ASL A<br>BRA<br>JSR | \$2883<br>DIRECT                    |

| 1009<br>ASSEMBLY COMPLETE.<br>(error code)                | 13<br>2 ERRORS.                                  | END                          |                                     |

Fig. 4-2 Error Message

At the end of the source listing (after the END statement), a line is printed which says:

ASSEMBLY COMPLETE. n ERRORS.

where "n" is the number of lines in which errors were detected.

In addition to the error messages on the listing, some error messages may appear on the console. Discussion of these is deferred to the description of the console output (section 4.3).

4.1.3 Symbol Table Format

The symbol table starts on a new page. Each entry (there are several per line) consists of a symbol's name and its value (as a four-hexadecimal-digit number).

ISIS-II 6301 CROSS ASSEMBLER, V1.0, HITACHI LTD. PAGE 2

CVBTD 0200 CVDEC1 0206 CVDEC2 0209 CVDEC5 0212 K10K 022F SAVEA 0100 SAVEX 0101 SAVEX1 0103 SYMBOL LISTING COMPLETE.

Fig. 4-3 Symbol table

40 HITACHI

## 4.1.4 Cross Reference Format

. . . . . .

The cross reference table starts on a new page. Each line gives the symbol name followed by a list of lines where it is referenced. Any line where the symbol is defined has the character "#" following the line number.

ISIS-II 6301 CROSS ASSEMBLER, VI.O, HITACHI LTD.

PAGE 3

| CVBID  | 15# |     |     |     |

|--------|-----|-----|-----|-----|

| CVDEC1 | 17# | 35  |     |     |

| CVDEC2 | 18# | 21  |     |     |

| CVDECS | 19  | 22# |     |     |

| K10K   | 16  | 34  | 39# |     |

| SAVEA  | 10# | 17  | 20  |     |

| SAVEX  | 11# | 15  | 25  | -30 |

| SAVEX1 | 12# | 24  | 31  |     |

|        |     |     |     |     |

CROSS REFERENCE COMPLETE.

# Fig. 4-4 Cross reference table

## 4.2 Object File

The object file contains a series of records in the Intel\* hexadecimal paper tape format. To convert the file to an ISIS-II compatible absolute object file, use the ISIS-II command HEXOBJ:

HEXOBJ filename.HEX to filename.OBJ

Remember to prefix the "filename" with the appropriate disk drive number in each case.

4.3 Console Output

Unless PRINT or OBJECT output is directed to the console (in which case see sections 4.1 and 4.2 for a description of that output), the console output is limited to the following:

- 1 A banner giving the version number of the assembler

- 2 "ASSEMBLY COMPLETE. n ERRORS." (as in listing file)

- 3 "COMMAND ERROR." if there is a problem with the controls in the command line invoking the ASM68 assembler.

- 4 "SYMBOL TABLE OVERFLOW." if the program being assembled has more labels than can be contained in available memory. Note: specifying the XREF option reduces the number of labels that can be handled.

- 5 "ERROR n USER PC xxxx": ISIS-II error messages which can occur at any time, due to disk errors, etc. A common cause of ERROR 35 (end of file): no END line.

\* "Intel" is a registered trademark of Intel Corporation, Santa Clara CA.

# APPENDIX A INSTRUCTION TABLE

· · · · · ·

OP : operation code ∿ : cycle count # : byte count

|                                                              |        |           |   |          |        |    |                            |                       |             |                            |                       | A      | ddre           | essi                  | .ng         | Mod                        | le                    |                       | _                                            |                                                               |                                                                         |    |              |   |    |              |   |          |            |        |           |            |    |

|--------------------------------------------------------------|--------|-----------|---|----------|--------|----|----------------------------|-----------------------|-------------|----------------------------|-----------------------|--------|----------------|-----------------------|-------------|----------------------------|-----------------------|-----------------------|----------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------|----|--------------|---|----|--------------|---|----------|------------|--------|-----------|------------|----|

| Mnemonic<br>Code                                             | 1 only | 6801/6301 |   | Inh      | ere    | nt | Imm                        | edi                   | ate         | Di                         | rec                   | t      | Ext            | ene                   | đ           | Ind                        | lexe                  | d                     | Rel                                          | ati                                                           | ve                                                                      |    | nedi<br>Lrec |   |    | neđi<br>ndex |   |          | it<br>irec | t      | Bi<br>-In | .t<br>ndex | ed |

|                                                              | 630    | 680       |   | OP       | r      | #  | OP                         | N                     | #           | OP                         | $\sim$                | #      | OP             | ~                     | #           | OP                         | N                     | #                     | OP                                           | N                                                             | #                                                                       | OP | $\sim$       | # | OP | ~<br>∼       | # | OP       | $\sim$     | #      | OP        | N          | #  |

| ABA<br>ABX<br>ADCA<br>ADCB<br>ADDA<br>ADDB<br>ADDD           |        | •         |   | 1B<br>3A | 2<br>3 | 1  | 89<br>C9<br>8B<br>CB<br>C3 | 2<br>2<br>2<br>2<br>4 | 2<br>2<br>2 | 99<br>D9<br>98<br>D8<br>D3 | 3<br>3<br>3<br>3<br>5 | 2<br>2 | F9<br>BB       | 4<br>4<br>4<br>4<br>6 | 3<br>3<br>3 | A9<br>E9<br>AB<br>EB<br>E3 | 4<br>4<br>4<br>4<br>6 | 2<br>2<br>2<br>2<br>2 |                                              |                                                               |                                                                         |    |              |   |    |              |   |          |            |        |           |            |    |

| AIM<br>ANDA<br>ANDB<br>ASL<br>ASLA                           | •      |           |   | 48       | 2      | 1  | 84<br>C4                   | 2<br>2                |             | 94<br>D4                   | 3                     | 2<br>2 | B4<br>F4<br>78 | 4<br>4<br>6           | 3           | A4<br>E4<br>68             | 4<br>4<br>6           | 2<br>2<br>2           |                                              |                                                               |                                                                         | 71 | 6            | 3 | 61 | 7            | 3 |          |            |        |           |            |    |

| ASLB<br>ASLD<br>ASR                                          |        | •         | 0 | 58<br>05 | 2      | 1  |                            |                       |             |                            |                       |        | 77             | 6                     | 3           | 67                         | 6                     | 2                     |                                              |                                                               |                                                                         |    |              |   |    |              |   |          |            |        |           |            |    |

| ASRA<br>ASRB<br>BCC<br>BCLR                                  |        |           |   | 47<br>57 | 2<br>2 | 1  |                            |                       |             |                            |                       |        |                |                       |             |                            |                       |                       | 24                                           | 3                                                             | 2                                                                       |    |              | ļ |    |              |   | 71       | 6          | 3      | 61        | 7          | 3  |

| BCLIA<br>BCS<br>BEQ<br>BGE<br>BGT<br>BHI<br>BHS<br>BITA      |        | •         |   |          |        |    | 85                         | 2                     | 2           | 95                         | 3                     | 2      | в5             | 4                     | 3           | А5                         | 4                     | 2                     | 25<br>27<br>2C<br>2E<br>22<br>24             | 3<br>3<br>3<br>3<br>3<br>3<br>3                               | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2                                    |    |              |   |    |              |   |          | 6          | 5      | 61        |            |    |

| BITB<br>BLE<br>BLO<br>BLS<br>BLT<br>BMI<br>BNE<br>BPL<br>BRA |        |           |   | ~        |        |    | C5                         | 2                     |             | D5                         | 3                     | 2      | F5             | 4                     | 3           |                            | 4                     | 2                     | 2F<br>25<br>23<br>2D<br>2B<br>26<br>2A<br>20 | 3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3 | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 |    |              |   |    |              |   |          |            |        |           |            |    |

| BRN<br>BSET<br>BSR                                           | •      | •         |   |          |        |    |                            | i                     |             |                            |                       |        |                |                       |             |                            |                       |                       | 21<br>8D                                     | 3                                                             | 2                                                                       |    |              |   |    |              |   | 72       | 6          | 3      | 62        | 7          | 3  |

| BTGL<br>BTST                                                 | •      |           |   |          |        |    |                            |                       |             |                            |                       |        |                |                       |             |                            |                       |                       |                                              |                                                               |                                                                         |    |              |   |    |              |   | 75<br>7B | 6          | 3<br>3 | 65<br>6B  | 7<br>7     | 3  |

|                                            | 2      |                   |                      |                  |                  |                      |                  |             | -                    |                  | 1                | Addr           | ess                   | inc              | g Mo           | de          |                            |          |        |        |            |        |   |            |        |        |   |    |          |   |           |            |    |

|--------------------------------------------|--------|-------------------|----------------------|------------------|------------------|----------------------|------------------|-------------|----------------------|------------------|------------------|----------------|-----------------------|------------------|----------------|-------------|----------------------------|----------|--------|--------|------------|--------|---|------------|--------|--------|---|----|----------|---|-----------|------------|----|

| Mnemonic<br>Code                           | 01 onl | 6801/6301<br>only | Inh                  | ere              | nt               | Imm                  | edi              | ate         | Di                   | rec              | t                | Ext            | end                   | ed               | Ind            | exe         | đ                          | Rel      | ati    | ve     | Imm<br>-Di |        |   | Imm<br>-In |        |        |   |    | t<br>rec | t | Bi<br>-In | .t<br>Idex | ed |

|                                            | 63     | 68<br>0n          | OP                   | Ś                | #                | OP                   | Ş                | #           | OP                   | 2                | #                | OP             | $\sim$                | #                | OP             | $\sim$      | #                          | OP       | ~ ∼    | #      | OP         | $\sim$ | # | ОР         | $\sim$ | $\sim$ | # | OP | $\sim$   | # | OP        | N          | #  |

| BVC<br>BVS<br>CBA<br>CLC<br>CLI            |        |                   | 11<br>0C<br>0E       | 2<br>2<br>2      | 1<br>1<br>1      |                      |                  |             | I                    |                  |                  |                |                       |                  |                |             |                            | 28<br>29 | з<br>3 | 2<br>2 |            |        |   |            |        |        |   |    |          |   |           |            |    |

| CLR<br>CLRA<br>CLRB<br>CLV                 |        |                   | 4F<br>5F<br>0A       | 2 2 2 2          | 1 1 1 1          |                      |                  |             |                      |                  |                  | 7F             | 6                     | 3                | 6F             | 6           | 2                          |          |        |        |            |        |   |            |        |        |   |    |          |   |           |            |    |

| CMPA<br>CMPB<br>COM<br>COMA                |        |                   | 43                   | 2                | 1                | 81<br>C1             | 2<br>2           |             | 91<br>D1             | 33               | 2<br>2           | B1<br>F1<br>73 | 4<br>4<br>6           | 3                | A1<br>E1<br>63 | 4<br>4<br>6 | 2<br>2<br>2                |          |        |        |            |        |   |            |        | -      |   |    |          |   |           |            |    |

| COMB<br>CPX<br>DAA<br>DEC                  |        |                   | 53<br>19             | 2<br>2           | 1                | 8C                   | 4                | 3           | 9C                   | 5                | 2                | BC<br>7A       | 6                     | 3                | AC<br>6A       | 6           | 2<br>2                     |          |        |        |            | i i    |   |            |        |        |   |    |          | 1 | ļ         |            |    |

| DECA<br>DECB<br>DES<br>DEX<br>EIM          |        |                   | 4A<br>5A<br>34<br>09 | 2<br>2<br>3<br>3 | 1<br>1<br>1<br>1 |                      |                  |             |                      |                  |                  |                |                       |                  |                |             |                            |          |        |        | 75         |        |   | C.F.       |        |        | 2 |    |          |   |           |            |    |

| EIM<br>EORA<br>EORB<br>INC<br>INCA<br>INCB |        |                   | 4C<br>5C             | 2<br>2           | 1                | 88<br>C8             | 2<br>2           | 2<br>2      | 98<br>D8             | 3<br>3           | 2<br>2           | В8<br>F8<br>7С | 4<br>4<br>6           |                  | A8<br>E8<br>6C | 4<br>4<br>6 | 2<br>2<br>2                |          |        |        | /5         | 6      | 3 | 65         | 7      |        | З |    |          |   |           |            |    |

| INS<br>INX<br>JMP<br>JSR<br>IDAA           |        |                   | 31<br>08             | 3                | 1                | 86                   | 2                | 2           | 9D<br>96             | 5                | 22               | 7E<br>BD<br>B6 | 364                   | 3                | 6E<br>AD<br>A6 | 3<br>6<br>4 | 2<br>2<br>2                |          |        |        |            |        |   |            | }      |        |   |    |          |   |           |            |    |

| LDAB<br>LDD<br>LDS<br>LDX<br>LSL           |        | •                 |                      |                  |                  | C6<br>CC<br>8E<br>CE | 2<br>3<br>3<br>3 | 2<br>3<br>3 | D6<br>DC<br>9E<br>DE | 3<br>4<br>4<br>4 | 2<br>2<br>2<br>2 | F6             | 4<br>5<br>5<br>5<br>6 | 3<br>3<br>3<br>3 | E6<br>EC<br>AE | 45556       | 2<br>2<br>2<br>2<br>2<br>2 |          |        |        |            |        |   |            |        |        |   |    |          |   |           |            |    |

| LSL<br>LSLA<br>LSLB<br>LSLD<br>LSR         |        | •••               | 48<br>58<br>05       | 2<br>2<br>3      | 1<br>1<br>1      |                      |                  |             |                      |                  |                  | 78             | 6                     | Ī                | 64             | 6           | 2                          |          |        |        |            |        |   |            | }      |        |   |    |          |   |           |            |    |

| LSRA<br>LSRB                               |        |                   | 44<br>54             | 2<br>2           | 1<br>1           |                      |                  |             |                      |                  |                  | /4             |                       |                  |                |             | 2                          |          |        |        |            |        |   |            |        |        |   |    |          |   |           |            |    |

|                                                           | 5      |                  | Τ                                |                             |                       |                |             |     |                                              |                                 |                                      | Addı                                         | ess                        | ing                                                                                         | g Mc                                   | de                              |               |     |     |     |    |              |   |    |              |   |    |           |     |           |   |     |

|-----------------------------------------------------------|--------|------------------|----------------------------------|-----------------------------|-----------------------|----------------|-------------|-----|----------------------------------------------|---------------------------------|--------------------------------------|----------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------|---------------|-----|-----|-----|----|--------------|---|----|--------------|---|----|-----------|-----|-----------|---|-----|

| Mnemonic<br>Code                                          | luo lu | 6801/630<br>only | In                               | nere                        | ent                   | Imn            | edi         | ate | Di                                           | .rec                            | t                                    | Ext                                          | ene                        | d                                                                                           | Ind                                    | exe                             | d             | Rel | ati | .ve |    | nedi<br>.rec |   |    | nedi<br>ndex |   |    | t<br>Dire | ect | Bi<br>-Ir |   | ed. |

|                                                           | 63(    | 68<br>0 n        | OP                               | $^{\sim}$                   | #                     | OP             | r           | #   | OP                                           | $\sim$                          | #                                    | OP                                           | $\sim$                     | #                                                                                           | OP                                     | $\sim$                          | #             | OP  | N   | #   | OP | $\sim$       | # | ОР | v            | # | OP | n         | #   | OP        | v | #   |

| LSRD<br>MUL<br>NEG<br>NEGA                                |        | •                | 04<br>3D<br>40                   | 3<br>10<br>2                | 1<br>11<br>1          |                |             |     | 70                                           | 6                               | 3                                    | 60                                           | 6                          | 2                                                                                           |                                        |                                 |               |     |     |     |    |              |   |    |              |   |    |           |     |           |   |     |

| NEGB<br>NOP<br>OIM<br>ORAA                                | •      |                  | 50<br>01                         | 2<br>2                      | 1<br>1                | 8A             | 2           | 2   | 9A                                           | 2                               | 0                                    | BA                                           |                            | -<br>-                                                                                      |                                        |                                 | 2             |     |     |     | 72 | 6            | 3 | 62 | 7            | 3 |    |           |     |           |   |     |

| ORAB<br>PSHA<br>PSHB<br>PSHX<br>PULA<br>PULB              |        | •                | 36<br>37<br>3C<br>32<br>33       | 3<br>3<br>4<br>4<br>4       | 1<br>1<br>1<br>1      | CA             | 2           |     | DA                                           | 3                               |                                      | FA                                           | 4                          |                                                                                             | AA<br>EA                               | 4                               | 2             |     |     |     | -  |              |   |    |              |   |    |           |     |           |   |     |

| PULX<br>ROL<br>ROLA<br>ROLB<br>RTI<br>RTS<br>SBA          |        |                  | 38<br>49<br>59<br>3B<br>39<br>10 | 5<br>2<br>2<br>10<br>5<br>2 | 1<br>1<br>1<br>1<br>1 |                |             |     |                                              |                                 |                                      | 79                                           | 6                          | 3                                                                                           | 69                                     | 6                               | 2             |     |     |     |    |              |   |    |              |   |    |           |     |           |   |     |

| SBCA<br>SBCB<br>SEC<br>SEI<br>SEV<br>SLP                  |        |                  | OD<br>OF<br>OB<br>1A             | 2 2 2 4                     | 1 1 1 1 1             | 82<br>C2       | 2<br>2      | 2   | 92<br>D2                                     | 3                               | 2<br>2                               | B2<br>F2                                     | 4<br>4                     |                                                                                             | A2<br>E2                               | 4                               | 2<br>2        |     |     |     |    |              |   |    |              |   |    |           |     |           |   |     |

| STAA<br>STAB<br>STD<br>STS<br>STX<br>SUBA<br>SUBB<br>SUBD |        | •                |                                  |                             |                       | 80<br>C0<br>83 | 2<br>2<br>4 | 22  | 97<br>D7<br>D7<br>9F<br>9F<br>90<br>D7<br>90 | 3<br>3<br>4<br>4<br>4<br>3<br>5 | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2 | 87<br>F7<br>FD<br>BF<br>FF<br>80<br>F0<br>83 | 4<br>5<br>5<br>4<br>4<br>6 | 3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3 | A7<br>E7<br>AF<br>EF<br>A0<br>E0<br>A3 | 4<br>4<br>5<br>5<br>4<br>4<br>6 | N N N N N N N |     |     |     |    |              |   |    |              |   |    |           |     |           |   |     |

| SWI<br>TAB<br>TAP<br>TBA<br>TIM                           |        |                  | 3F<br>16<br>06<br>17             | 12<br>2<br>2<br>2           | 1<br>1<br>1           |                |             |     |                                              |                                 |                                      |                                              |                            |                                                                                             |                                        |                                 |               |     |     |     | 7в | 6            | 2 | 6в | 7            | 3 |    |           |     |           |   |     |

| TPA<br>TST                                                |        |                  | 07                               | 2                           | 1                     |                |             |     |                                              |                                 |                                      | 7D                                           | 6                          | 3                                                                                           | 6D                                     | 6                               | 2             |     |     |     | 10 | 0            |   |    | ,            |   |    |           |     |           |   |     |

| TSTA<br>TSTB<br>TSX<br>TXS<br>WAI<br>XGDX                 | •      |                  | 4D<br>5D<br>30<br>35<br>3E<br>18 | 2<br>2<br>3<br>9<br>2       | 1<br>1<br>1<br>1<br>1 |                |             |     |                                              |                                 |                                      |                                              |                            |                                                                                             |                                        |                                 |               |     |     |     |    |              |   |    |              |   |    |           |     |           |   |     |

·- · - ·

B.1 CVBTD Binary-to-Decimal Conversion Subroutine

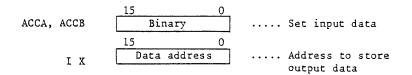

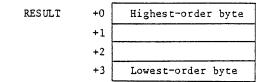

CVBTD is a subroutine to convert a 16-bit binary number to 5-character decimal data.

Linkage: As shown below, sets the high-order 8 bis of input data in accumulator A and the low-order 8 bits in accumulator B. Then, sets the address to store output data in the index register.

|        | 7      | 0                        |

|--------|--------|--------------------------|

| DATA+0 | 10000s |                          |

| 1      | 1000s  |                          |

| 2      | 100s   | Output data (ASCII code) |

| 3      | 10s    |                          |

| 4      | 15     |                          |