# Microcomputer Data Book

A World Leader in Technology

# DIPLOMAT ELECTRONICS

1293-A Mountain View/Alviso Road Sunnyvale, California 94086 (408) 734-1900

# **MICROCOMPUTER DATA BOOK**

# **INDEX**

|   | GENERAL INF                         | ORMATION                                                  | 5   |

|---|-------------------------------------|-----------------------------------------------------------|-----|

| • |                                     | cage Information                                          |     |

| • | <ul> <li>Reliability and</li> </ul> | Quality Assurance                                         | 12  |

| • | <ul> <li>Design Procedu</li> </ul>  | ure and Support Tools for 8-bit Single-chip Microcomputer | 20  |

| • | <ul><li>HMCS6800 Fa</li></ul>       | amily Instruction Set                                     | 23  |

| • | <ul><li>8-bit Microcom</li></ul>    | nputers for Industrial Application                        | 29  |

|   |                                     |                                                           |     |

|   |                                     | )                                                         |     |

| • |                                     | nputer HMCS6800 Single-chip Series                        |     |

|   | HD6801S0                            | Microcomputer Unit                                        |     |

|   | HD6801S5                            | Microcomputer Unit                                        |     |

|   | HD6801V0                            | Microcomputer Unit                                        |     |

|   | HD6801V5                            | Microcomputer Unit                                        |     |

|   | HD6803                              | Micro Processing Unit                                     |     |

|   | HD6803-1                            | Micro Processing Unit                                     |     |

|   | HD6805S1                            | Microcomputer Unit                                        |     |

|   | HD6805U1                            | Microcomputer Unit                                        |     |

|   | HD6805V1                            | Microcomputer Unit                                        |     |

|   | HD6805W0                            | Microcomputer Unit                                        |     |

|   | HD6805X0                            | Microcomputer Unit                                        |     |

|   | HD6301V0 (CI                        |                                                           |     |

|   | HD63A01V0 (0                        |                                                           |     |

|   | HD63B01V0 (C                        |                                                           |     |

|   | HD6303 (CMC                         |                                                           |     |

|   | HD63A03 (CM                         |                                                           |     |

|   | HD63B03 (CM                         |                                                           |     |

|   | HD63L05 (CM                         |                                                           |     |

|   | HD68P01S0                           | Microcomputer Unit                                        |     |

|   | HD68P01V05                          | Microcomputer Unit                                        |     |

|   | HD68P01V07                          | Microcomputer Unit                                        |     |

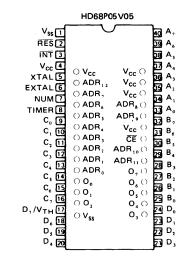

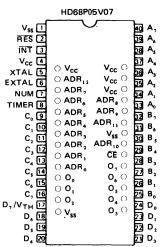

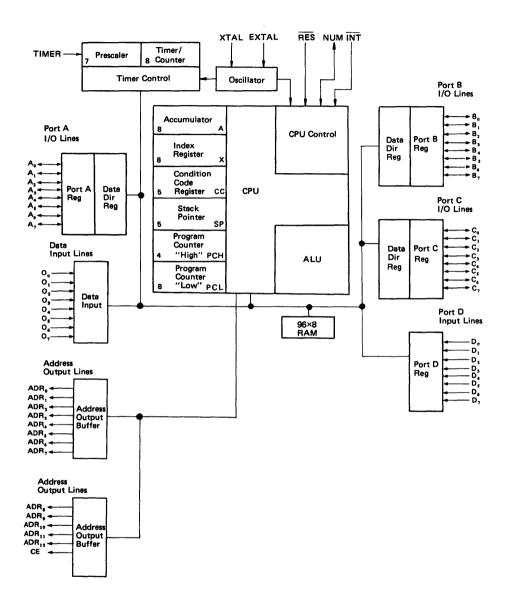

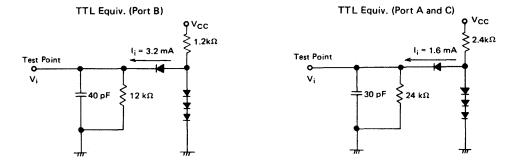

|   | HD68P05V05                          | Microcomputer Unit                                        |     |

| _ | HD68P05V07                          | Microcomputer Unit                                        |     |

| • |                                     | nputer HMCS6800 Multi-chip Series                         |     |

|   | HD6800<br>HD68A00                   | Micro Processing Unit                                     |     |

|   |                                     | Micro Processing Unit                                     |     |

|   | HD68B00                             | Micro Processing Unit                                     |     |

|   | HD6802                              | Microprocessor with Clock and RAM                         |     |

|   | HD6802W                             | Microprocessor with Clock and RAM                         |     |

|   | HD6809<br>HD68A09                   | Micro Processing Unit                                     |     |

|   | HD68B09                             | Micro Processing Unit                                     |     |

|   | HD6809E                             | Micro Processing Unit                                     |     |

|   | HD68A09E                            | Micro Processing Unit                                     | 423 |

|   | HD68B09E                            | Micro Processing Unit                                     |     |

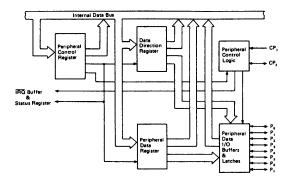

|   | HD6821                              | Peripheral Interface Adapter                              |     |

|   | HD68A21                             | Peripheral Interface Adapter                              |     |

|   | HD68B21                             | Peripheral Interface Adapter                              |     |

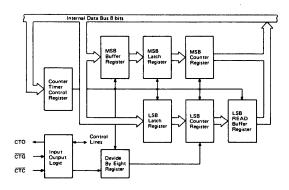

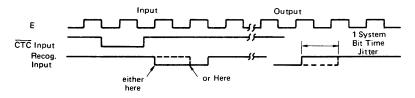

|   | HD6840                              | Programmable Timer Module                                 |     |

|   | HD68A40                             | Programmable Timer Module                                 |     |

|   | HD68B40                             | Programmable Timer Module                                 |     |

|   | HD6843                              | Floppy Disk Controller                                    |     |

|   | HD68A43                             | Floppy Disk Controller                                    |     |

|   |                                     |                                                           | 100 |

| HD6844                             | Direct Memory Access Controller                 | 513   |

|------------------------------------|-------------------------------------------------|-------|

| HD68A44                            | Direct Memory Access Controller                 | 513   |

| HD68B44                            | Direct Memory Access Controller                 | 513   |

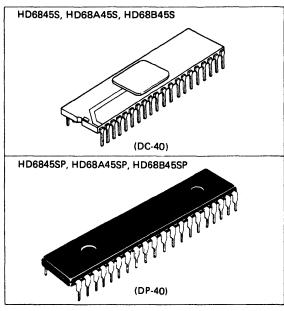

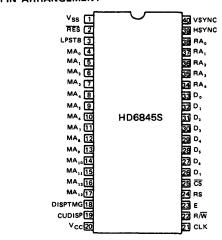

| HD6845S                            | CRT Controller                                  | 546   |

| HD68A45S                           | CRT Controller                                  | 546   |

| HD68B45S                           | CRT Controller                                  |       |

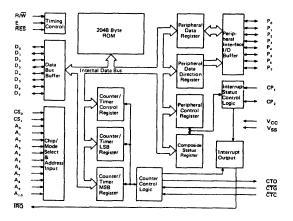

| HD6846                             | Combination ROM I/O Timer                       |       |

| HD6850                             | Asynchronous Communication Interface Adapter    | 606   |

| HD68A50                            | Asynchronous Communication Interface Adapter    | 606   |

| HD6852                             | Synchronous Serial Data Adapter                 |       |

| HD68A52                            | Synchronous Serial Data Adapter                 |       |

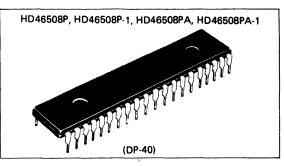

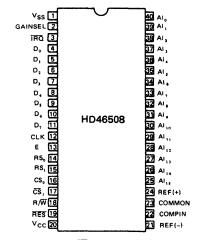

| HD46508                            | Analog Data Acquisition Unit                    |       |

| HD46508-1                          | Analog Data Acquisition Unit                    |       |

| HD46508A                           | Analog Data Acquisition Unit                    |       |

| HD46508A-1                         | Analog Data Acquisition Unit                    |       |

| HD146818 (C                        |                                                 |       |

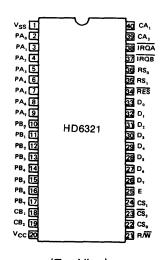

| HD6321 (CM                         | OS) Peripheral Interface Adapter                | 665   |

| HD63A21 (CN                        |                                                 |       |

| HD63B21 (CN                        |                                                 |       |

| HD6340 (CM                         |                                                 |       |

| HD63A40 (CI                        | MOS) Programmable Timer Module                  | 666   |

| HD63B40 (CN                        |                                                 |       |

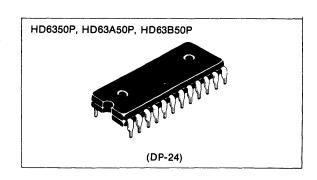

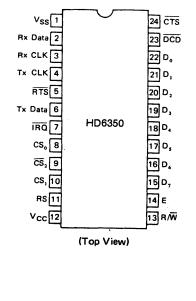

| HD6350 (CM                         | OS) Asynchronous Communication Interface Adapte |       |

| HD63A50 (CI                        |                                                 | r 667 |

| HD63B50 (CN                        |                                                 |       |

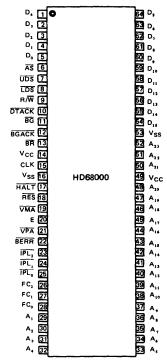

| <ul> <li>16-bit Microco</li> </ul> | omputer HMCS68000 Multi-chip Series             |       |

| HD68000-4                          | Micro Processing Unit                           |       |

| HD68000-6                          | Micro Processing Unit                           |       |

| HD68000-8                          | Micro Processing Unit                           |       |

| HD68000-10                         | Micro Processing Unit                           |       |

| HD68450                            | Direct Memory Access Controller                 | 752   |

| INTRODUCTION                       | ON OF THE RELATED DEVICES                       | 753   |

| <ul> <li>MOS Memori</li> </ul>     | es                                              | 754   |

|                                    | ID74S/HD74LS Series                             |       |

| Advanced Lov                       | w Power Schottky TTL HD74ALS Series             | 761   |

|                                    | HD14000B/UB Series                              |       |

|                                    |                                                 |       |

|                                    | uits                                            |       |

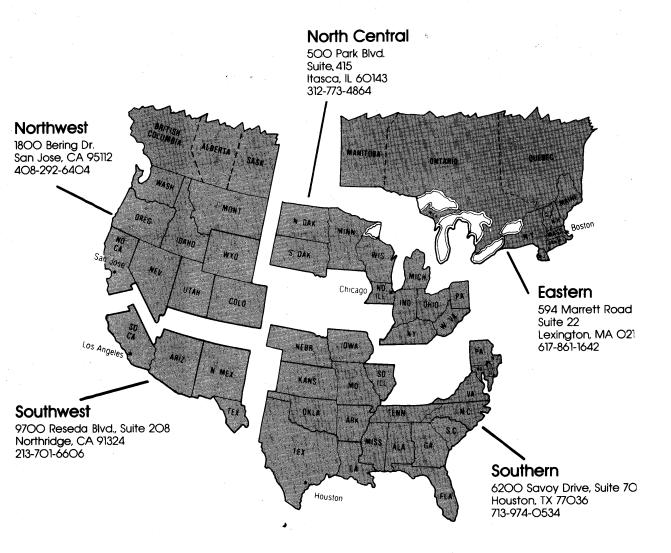

|                                    | DENCE                                           | 7/7   |

| E CRUGO REFE                       | RENCE                                           | /0/   |

### NOTICE

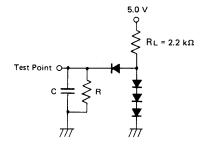

The example of an applied circuit or combination with other equipment shown herein indicates characteristics and performance of a semiconductor-applied products. The Company shall assume no responsibility for any problem involving a patent caused when applying the descriptions in the example.

# GENERAL INFORMATION

- Type and Package Information

- Reliability and Ouality Assurance

- Design Procedure and Support Tools for 8-bit Single-chip Microcomputer

- HMCS6800 Family Instruction Set

- 8-bit Microcomputers for Industrial Application

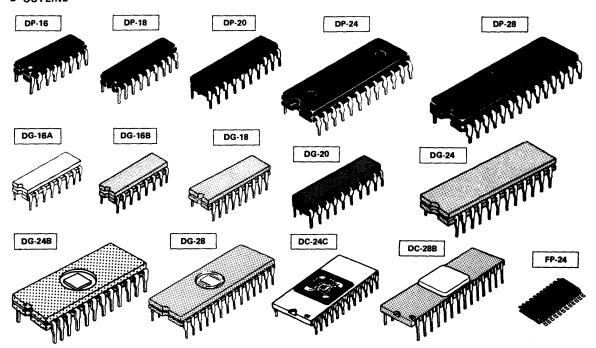

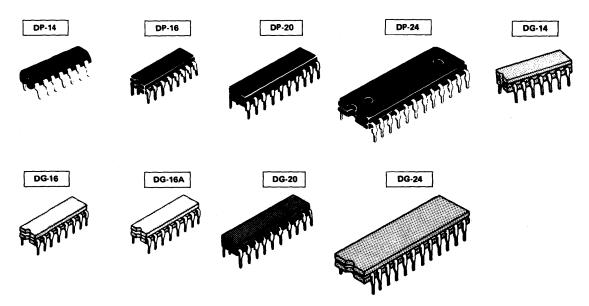

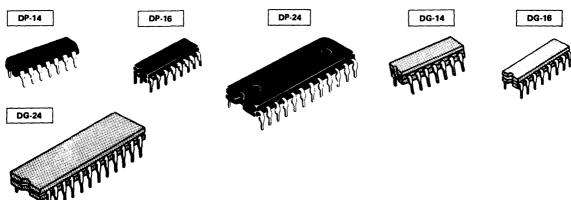

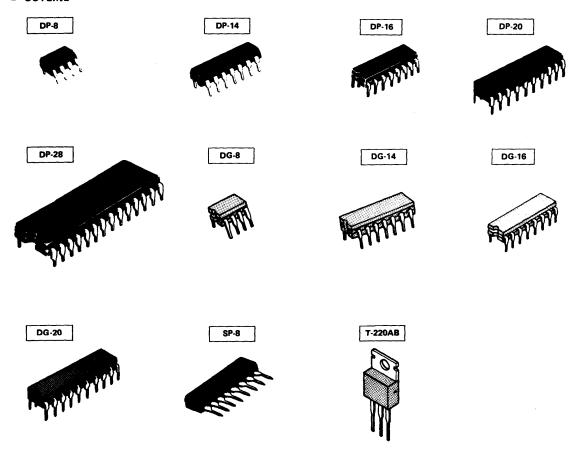

# TYPE AND PACKAGE INFORMATION

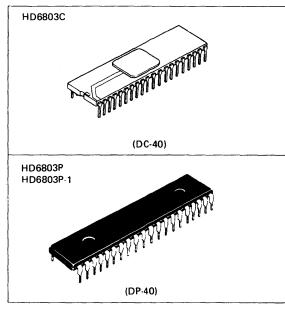

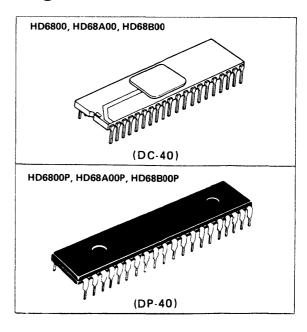

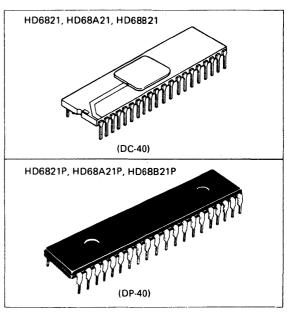

The Hitachi Microcomputer LSI are classified into 3 types; plastic mold type, side-brazed ceramic type and flat package, according to the type of material and outline used for the package. Therefore, after taking into consideration the operating environment and other conditions, please select the optimum package. In regard to the types which have two package materials, please define clearly when ordering the package material code (C or P) (See the following table). As List of 8/16-bit Microcomputer LSI Package shows, old type numbers are changed from HD468XX to HD68XX (standard number). But as for original products of Hitachi, the type numbers are not changed.

#### Division of Package Material

Types which have side-brazed ceramic and plastic mold package.

| Side-brazed C   | Plastic Mold           |                 |

|-----------------|------------------------|-----------------|

| Single-chip LSI | HD68XXC                |                 |

| Multi-chip LSI  | HD68XX € No indication | HD68XX <u>P</u> |

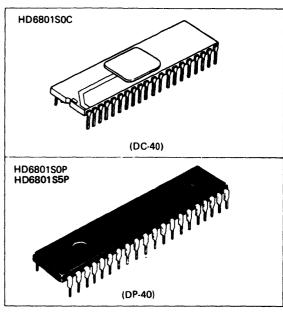

#### ■ List of 8/16-bit Microcomputer LSI Package

| Chin Division      | Type No.   |                 | Function               |         | Packa | ge* |          |

|--------------------|------------|-----------------|------------------------|---------|-------|-----|----------|

| Chip Division      | Type No.   | o. Old type No. | Function               | Pin No. | С     | P   | F        |

|                    | HD6801S0   | _               |                        | 40      | •     | •   | П        |

|                    | HD6801S5   | _               |                        | 40      |       | •   | Τ        |

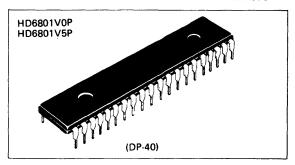

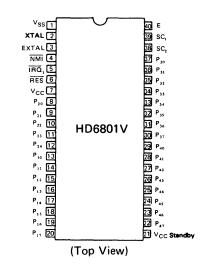

|                    | HD6801V0   | -               | Microcomputer Unit     | 40      |       | •   | Т        |

|                    | HD6801V5   | _               |                        | 40      |       | •   | Π        |

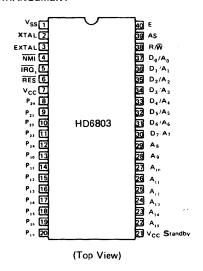

|                    | HD6803     | _               | Micro Processing Unit  | 40      | •     | •   | Т        |

|                    | HD6803-1   | _               | wildro Processing Onit | 40      |       | •   | Π        |

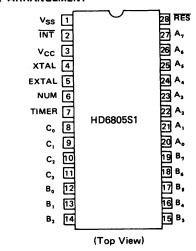

|                    | HD6805S1   | _               |                        | 28      |       | •   |          |

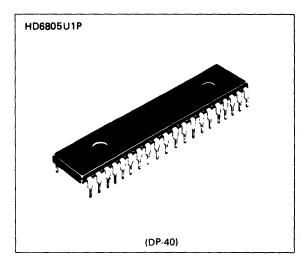

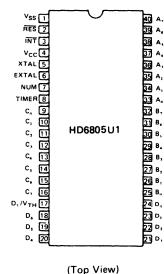

|                    | HD6805U1   | _               |                        | 40      |       | •   | Π        |

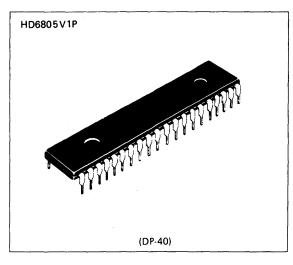

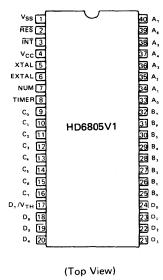

|                    | HD6805V1   | _               | Microcomputer Unit     | 40      |       | •   | $\Box$   |

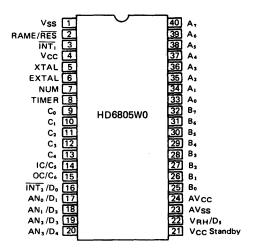

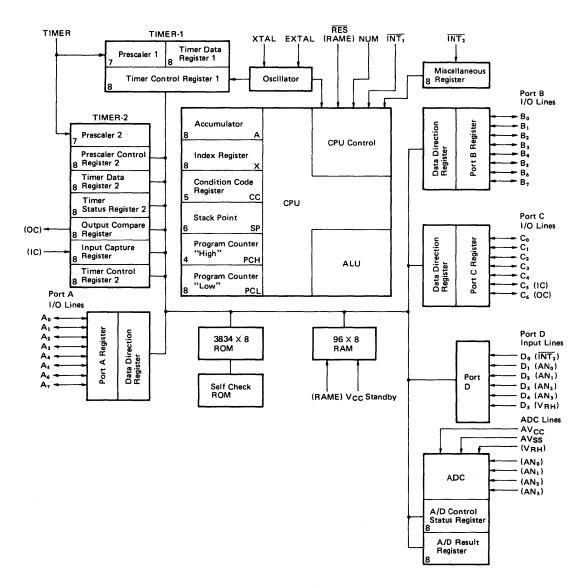

|                    | HD6805W0   | _               |                        | 40      |       | •   | T        |

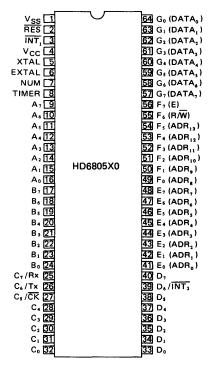

| O bis Circula abia | HD6805X0   | _               |                        | 64      |       | •   |          |

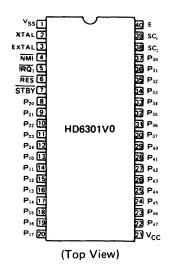

| 8-bit Single-chip  | HD6301V0   | -               |                        | 40      |       | •   | T        |

|                    | HD63A01V0  | -               |                        | 40      |       | •   |          |

|                    | HD63B01V0  | _               |                        | 40      |       | •   | $\vdash$ |

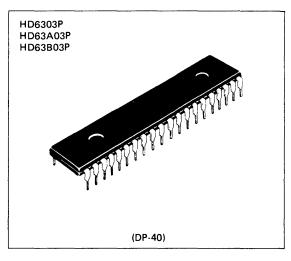

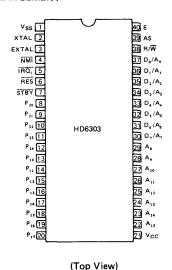

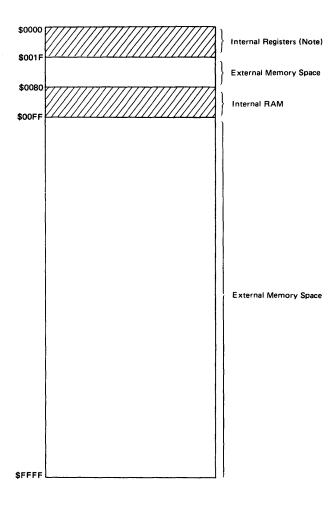

|                    | HD6303     | -               | Micro Processing Unit  | 40      |       | •   | Г        |

|                    | HD63A03    | _               |                        | 40      |       | •   | Γ        |

|                    | HD63B03    | -               |                        | 40      |       | •   | Г        |

|                    | HD6333     | -               |                        | 40      |       | •   |          |

|                    | HD63A33    | _               |                        | 40      |       | •   |          |

|                    | HD63B33    | _               |                        | 40      |       | •   |          |

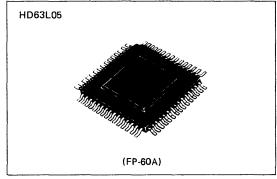

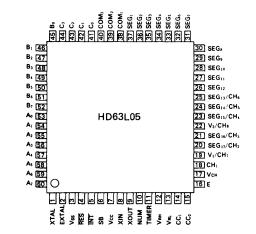

|                    | HD63L05    | -               |                        | 60      |       |     | Ŀ        |

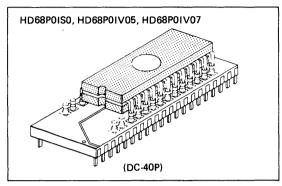

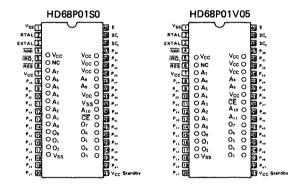

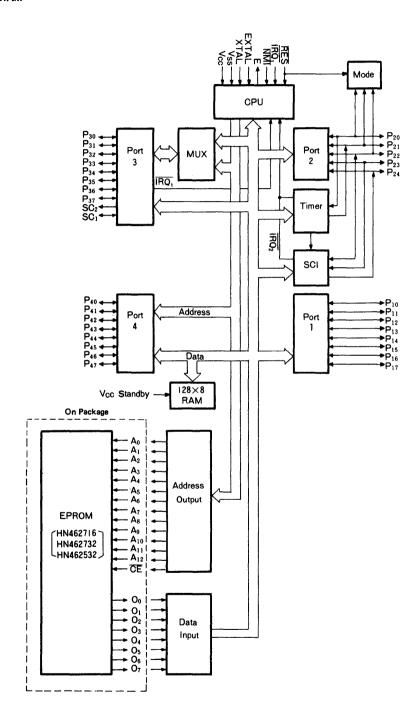

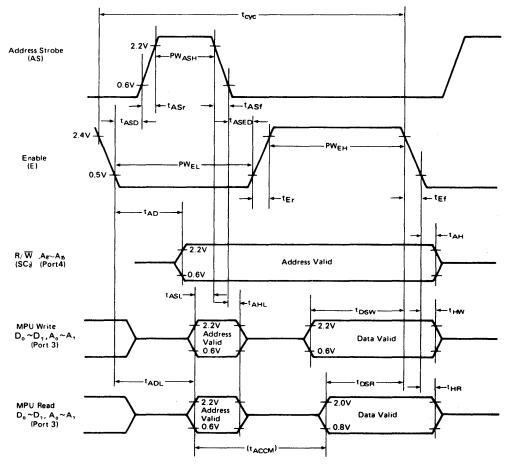

|                    | HD68P01S0  |                 |                        | 40**    | •     |     |          |

|                    | HD68P01V05 | _               |                        | 40**    | •     |     |          |

|                    | HD68P01V07 | _               | Microcomputer Unit     | 40**    | •     |     |          |

|                    | HD68P05V05 | _               |                        | 40**    | •     |     |          |

|                    | HD68P05V07 | _               |                        | 40**    | •     |     |          |

<sup>\*</sup> The package codes of C, P, and F are applied to the package materials as follows.

C: Side-brazed Ceramic DIP, P: Plastic DIP, F: Flat Package.

<sup>\*\*</sup> EPROM on the package,

## TYPE AND PACKAGE INFORMATION-

| Chip Division    | Type No.   | Old turns No                                     | Function                        | Package* |               |   |         |

|------------------|------------|--------------------------------------------------|---------------------------------|----------|---------------|---|---------|

| Omp Bivision     | Турс 140.  | Old type No.                                     | e No.                           |          | С             | Р |         |

|                  | HD6800     | HD46800D                                         |                                 | 40       | •             | • |         |

|                  | HD68A00    | HD468A00                                         | Micro Processing Unit           | 40       | •             | • |         |

|                  | HD68B00    | HD468B00                                         |                                 | 40       | •             | • |         |

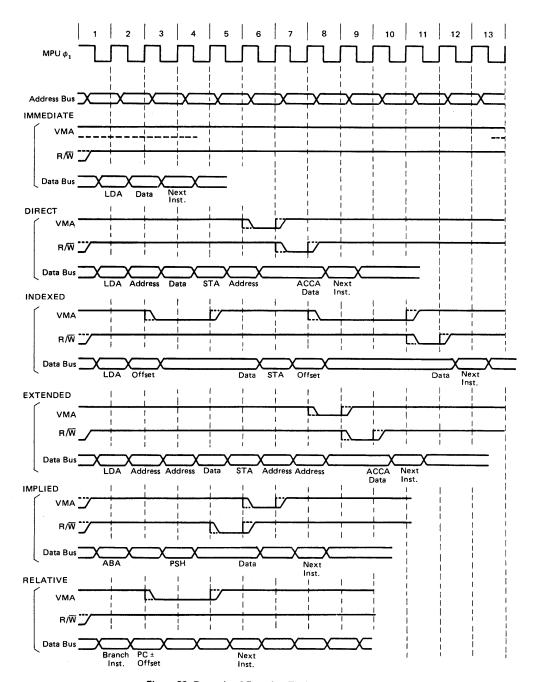

|                  | HD6802     | HD46802                                          | Microprocessor with Clock       | 40       | •             | • | Ţ       |

|                  | HD6802W    | _                                                | and RAM                         | 40       |               | • |         |

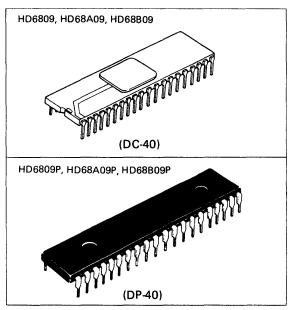

|                  | HD6809     |                                                  |                                 | 40       | •             | • |         |

|                  | HD68A09    |                                                  |                                 | 40       | •             | • | T       |

|                  | HD68B09    |                                                  | Minus Burnasius Hair            | 40       | •             | • | T       |

|                  | HD6809E    | _                                                | Micro Processing Unit           | 40       | •             | • | T       |

|                  | HD68A09E   | _                                                |                                 | 40       | •             | • | T       |

|                  | HD68B09E   | _                                                | 1                               | 40       | •             | • | 1       |

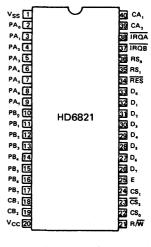

|                  | HD6821     | HD46821                                          |                                 | 40       | •             |   | 1       |

|                  | HD68A21    | HD468A21                                         | Peripheral Interface Adapter    | 40       | •             | • | T       |

|                  | HD68B21    | HD468B21                                         | ·                               | 40       | •             | • | 1       |

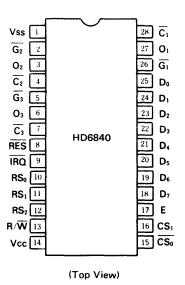

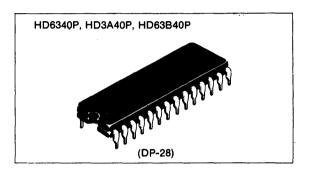

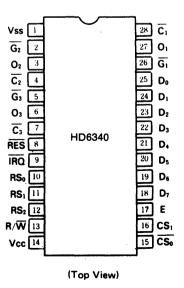

|                  | HD6840     | <del> </del>                                     |                                 | 28       | •             | • | †       |

|                  | HD68A40    |                                                  | Programmable Timer Module       | 28       | •             | • | $t^{-}$ |

|                  | HD68B40    | _                                                |                                 | 28       | •             | • | T       |

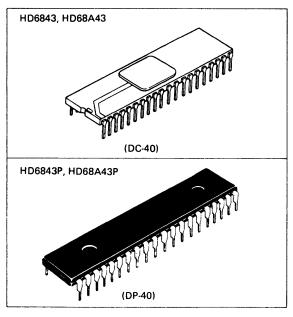

| 3-bit Multi-chip | HD6843     | HD46503S                                         | Floppy Disk Controller          | 40       | •             | • | +-      |

|                  | HD68A43    | HD46503S-1                                       |                                 | 40       | •             | • | +       |

|                  | HD6844     | HD46504                                          |                                 | 40       | •             | • | 1       |

|                  | HD68A44    | HD46504-1                                        | Direct Memory Access Controller | 40       | •             | • | 1       |

|                  | HD68B44    | HD46504-2                                        | Controller                      | 40       | •             | • | +       |

|                  | HD6845S    | HD46505S                                         |                                 | 40       | •             | • | +       |

|                  | HD68A45S   | HD46505S-1                                       | CRT Controller                  | 40       | •             | • | †       |

|                  | HD68B45S   | HD46505S-2                                       |                                 | 40       | •             | • | T       |

|                  | HD6846     | HD46846                                          | Combination ROM I/O Timer       | 40       | •             | • | +-      |

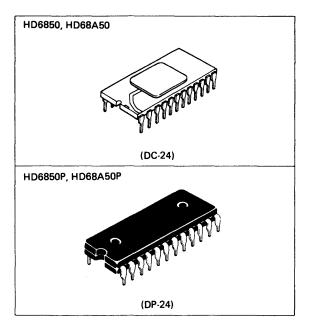

|                  | HD6850     | HD46850                                          | Asynchronous Communications     | 24       | •             | • | +       |

|                  | HD68A50    | HD468A50                                         | Interface Adapter               | 24       | •             | • | +-      |

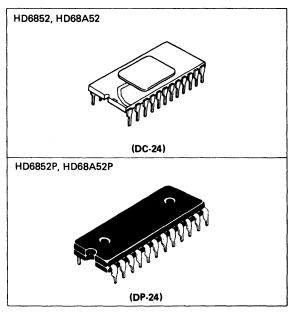

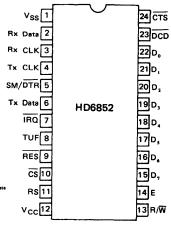

|                  | HD6852     | HD46852                                          | Synchronous Serial Data         | 24       | •             | • | +       |

|                  | HD68A52    | HD468A52                                         | Adapter                         | 24       | •             | • | ╁╴      |

|                  | HD46508    |                                                  |                                 | 40       | <del></del> - | • | ╁╴      |

|                  | HD46508-1  |                                                  |                                 | 40       |               | • | ╁       |

|                  | HD46508A   |                                                  | Analog Data Acquisition Unit    | 40       |               | • | +       |

|                  | HD46508A-1 | _                                                |                                 | 40       |               | • | +       |

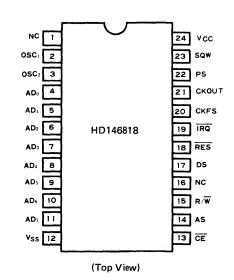

|                  | HD146818   |                                                  | Real Time Clock Plus RAM        | 24       |               | • | +       |

| <del></del>      | HD68000-4  | _                                                |                                 | 64       | •             |   | +       |

|                  | HD68000-6  | <del>                                     </del> |                                 | 64       | •             |   | ╁       |

| 6-bit Multi-chip | HD68000-8  | <del> </del>                                     | Micro Processing Unit           | 64       | •             |   | +       |

|                  | HD68000-10 | <del> </del>                                     |                                 | 64       | -             |   | +-      |

|                  | HD68450    | <del>                                     </del> | Direct Memory Access Controller | 64       | -             |   | +-      |

<sup>\*</sup> The package codes of C, P, and F are applied to the package materials as follows. C: Side-brazed Ceramic DIP, P: Plastic DIP, F: Flat Package.

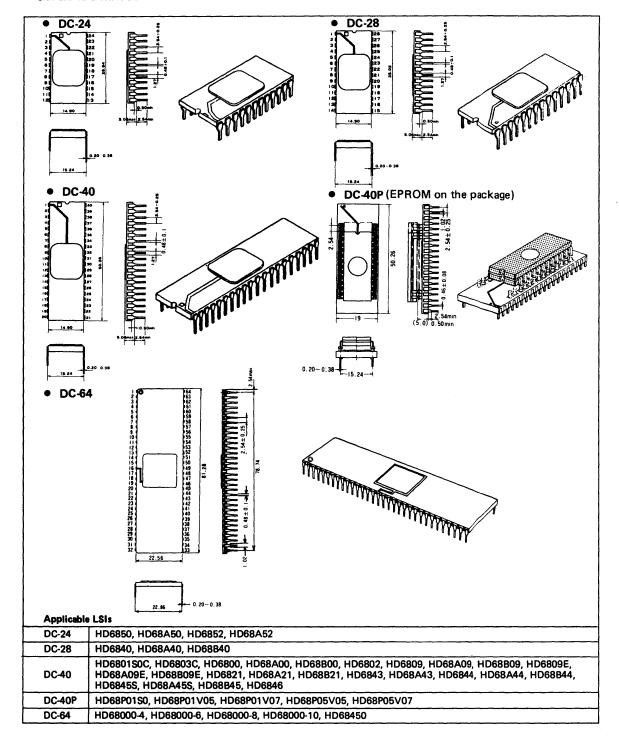

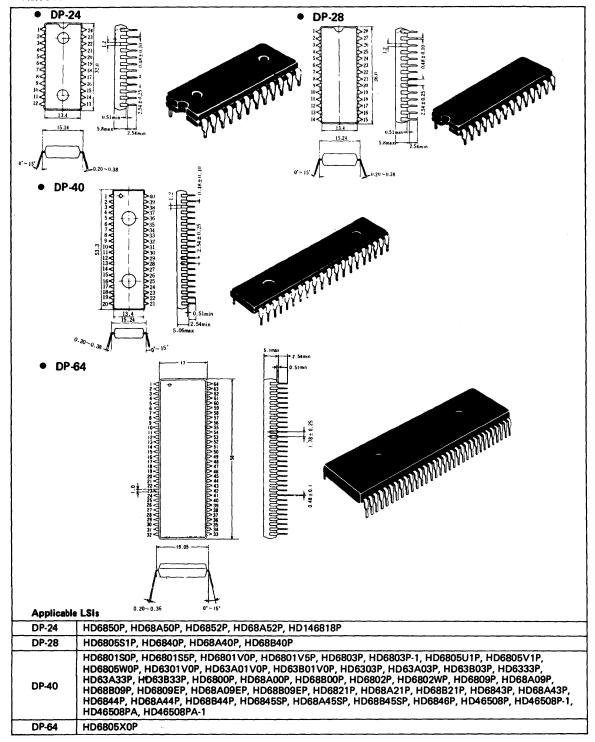

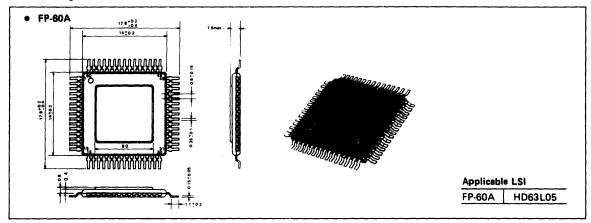

- Package Information (Dimensions in mm)

- Side-brazed Ceramic DIP

#### Plastic DIP

#### Flat Package

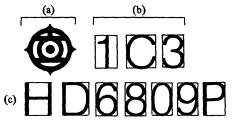

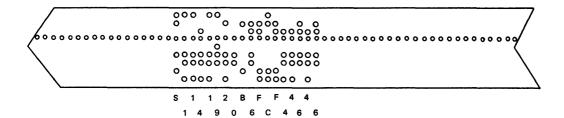

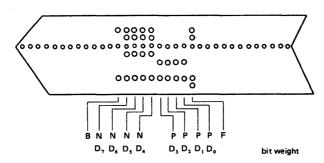

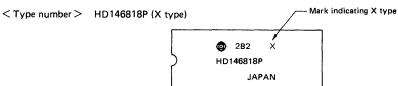

#### Marking

There are two kinds of marking. One has a new ordering No. (Case I) and the other has both new and old ordering No. (Case II). They are listed on the List of 8/16-bit Microcomputer LSI Package. Case I is applied to the LSI which has

only new ordering No. listed in the List of 8/16-bit Microcomputer LSI Package and Case II is applied to the LSI which has both Ordering No.

Case I (Indicated an ordering No.)

© 2A2 HD68011S0P

Case III (Example of marking on Single-chip)

Case II (Indicated a New & Old ordering No.)

#### Meaning of each mark

| 14160 | ining of each mark |

|-------|--------------------|

| (a)   | Hitachi mark       |

| (b)   | Lot Code           |

| (c)   | New type No.       |

| (d)   | Japan mark         |

| (e)   | Old type No.       |

| (f)   | ROM Code           |

# RELIABILITY AND QUALITY ASSURANCE

#### 1. INTRODUCTION

Microcomputer is required to provide higher reliability and quality with increasing function, enlarging scale and widening application. To meet this demand, Hitachi is improving the quality by evaluating reliability, building up quality in process, strengthening inspection and analyzing field data etc..

This chapter describes reliability and quality assurance data for Hitachi 8-bit and 16-bit microcomputer based test and failure analysis results. More detail data and new information will be reported in another reliability data sheet.

#### 2. PACKAGE AND CHIP STRUCTURE

#### 2.1 Package

Packages are generally classified into 2 types; one is the hermetic sealed type using metal or glass and the other is the plastic molded type. Hitachi 8-bit microcomputer are produced in plastic package or side-braze package.

Selection of package type should be done considering the application, environment, reliability, cost and other factors of the system.

The reliability of plastic molded type has been greatly im-

proved, recently their applications have been expanded to automobiles measuring and control systems, and computer terminal equipment operated under relatively severe conditions.

Actually, field application data has revealed that their failure rates in a commercial environment are equivalent to those of the hermetic sealed type.

However, in a view of reliability guarantee, the hermetic sealed type passes a leak test 100%. Due to poor screening technology, the plastic type may exhibit moisture absorption or permeation inherent to their plastic materials.

Therefore, Hitachi recommends users employ the hermetic sealed type for certain systems which require high durability against severe conditions, long service life and high reliability.

On the other hand, production output and application of plastic molded type continue to increase.

To meet such requirements, Hitachi has considerably improved moisture resistance, operation stability, and chip and plastic manufacturing process.

Plastic and side-braze package type structure are shown in Figure 1 and Table 1.

Figure 1 Package Structure

Table 1 Package Material and Properties

| Item      | Side-braze                  | Plastic                 |

|-----------|-----------------------------|-------------------------|

| Package   | Alumina                     | ероху                   |

| Lead      | Tin plating Brazed Alloy 42 | Solder dipping Alloy 42 |

| Seal      | Au-Sn Alloy                 | N.A                     |

| Die bond  | Au-Si                       | Au-Si                   |

| Wire bond | Ultrasonic                  | Thermo compression      |

| Wire      | Al                          | Au                      |

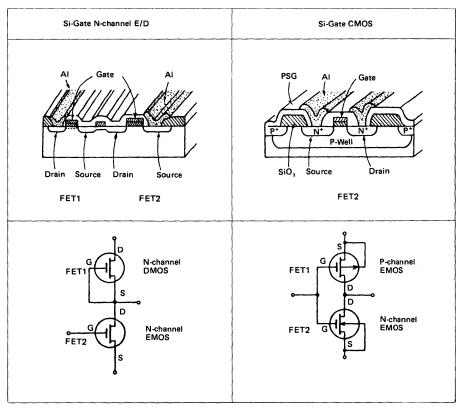

#### 2.2 Chip Structure

HMCS6800 family are produced in NMOS E/D technology or low power CMOS technology. Si-gate process is used in both

types because of high reliability and high density.

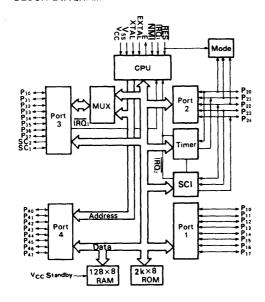

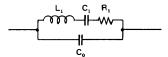

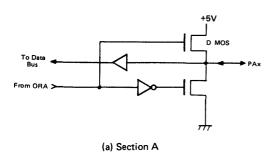

Chip structure and basic circuit are shown in Figure 2.

Figure 2 Chip Structure and Basic Circuit

#### 3. QUALITY QUALIFICATION AND EVALUATION

### 3.1 Reliability Test Methods

Reliability test methods shown in Table 2 are used to qualify

and evaluate the new products and new process.

Table 2 Reliability Test Methods

| Test Items                                                                                       | Test Condition                                                                   | MIL-STD-883B Method No. |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------|

| Operating Life Test                                                                              | 125°C, 1000hr                                                                    | 1005,2                  |

| High Temp, Storage<br>Low Temp, Storage<br>Steady State Humidity<br>Steady State Humidity Biased | Tstg max, 1000hr<br>Tstg min, 1000hr<br>65°C 95%RH, 1000hr<br>85°C 85%RH, 1000hr | 1008,1                  |

| Temperature Cycling Temperature Cycling                                                          | -55°C ∼ 150°C, 10 cycles<br>-20°C ∼ 125°C, 200 cycles                            | 1010,4                  |

| Thermal Shock<br>Soldering Heat                                                                  | 0°C ~ 100°C, 100 cycles<br>260°C, 10 sec                                         | 1011,3                  |

| Mechanical Shock                                                                                 | 1500G 0.5 sec, 3 times/X, Y, Z                                                   | 2002,2                  |

| Vibration Fatigue                                                                                | 60Hz 20G, 32hrs/X, Y, Z                                                          | 2005,1                  |

| Valiable Frequency                                                                               | 20~2000Hz 20G, 4 min/X, Y, Z                                                     | 2007,1                  |

| Constant Acceleration                                                                            | 20000G, 1 min/X, Y, Z                                                            | 2001,2                  |

| Lead Integrity                                                                                   | 225gr, 90° 3 times                                                               | 2004.3                  |

### RELIABILITY AND QUALITY ASSURANCE-

#### 3.2 Reliability Test Results

#### 3.2.1 Dynamic Life Test

The reliability for chip design is evaluated by dynamic life test. The test results of HMCS6800 microcomputer family are

shown in Table 3. Depend on these test results, the 70°C failure rate is determined 0.007%/1000hrs (confidence level 60%, activation energy 0.7eV)

Table 3 Dynamic Life Test Result

| Device           | Sample Size | Component Hour | Failure |

|------------------|-------------|----------------|---------|

| HD6800           | 248         | 248000         | 0       |

| HD6802           | 452         | 153712         | 1       |

| HD6809           | 85          | 85000          | 0       |

| HD6801           | 146         | 146000         | 0       |

| HD6803           | 45          | 45000          | 0       |

| HD6805           | 114         | 114000         | 0       |

| MPU Total        | 1090        | 791712         | 1       |

| HD6821           | 399         | 266368         | 1       |

| HD6850           | 158         | 158000         | 0       |

| HD6852           | 170         | 125816         | 0       |

| HD6846           | 69          | 69000          | 0       |

| HD6843           | 66          | 55000          | 0       |

| HD6844           | 80          | 69000          | 0       |

| HD6845S          | 88          | 55000          | 0       |

| HD6840           | 64          | 64000          | 0       |

| HD46508          | 140         | 140000         | 0       |

| Peripheral Total | 1234        | 1002184        | 1       |

| Total            | 2324        | 1793896        | 2       |

#### 3.2.2 Temperature-Humidity Bias Test

The moisture resistance of plastic package is evaluated by

temperature-humidity bias test, 85°C/85% RH biased condition. The result of this test is shown in Table 4.

Table 4 85°C/85%RH Bias Test Result

| Device            | Sample Size | Component Hore   | Failure |

|-------------------|-------------|------------------|---------|

| MPU<br>Peripheral | 132<br>226  | 132000<br>204000 | 0 0     |

| Total             | 358         | 336000           | 0       |

#### 3.2.3 Storage Life Test

These tests evaluate the effect of storage at high temperature, low temperature or high humidity without bias.

(1) Plastic Package

Table 5 Storage Life Test on Plastic Package

| Test Items               | Condition                     | Sample Size | Failure |

|--------------------------|-------------------------------|-------------|---------|

| High Temp, High Humidity | 65°C/95%RH, 1000hrs           | 288         | 0       |

| High Temp, High Humidity | 80°C/90%RH, 1000hrs           | 88          | 0       |

| Presser Cooker           | 2atm 121°C, 100hrs            | 266         | 0       |

| High Temp, Storage       | $Ta = 150^{\circ}C$ , 1000hrs | 85          | 0       |

| Low Temp, Storage        | $Ta = -55^{\circ}C$ , 1000hrs | 34          | 0       |

#### (2) Side-braze

Table 6 Storage Life Test on Side-braze Package

| Test Items               | Condition                     | Sample Size | Failure |

|--------------------------|-------------------------------|-------------|---------|

| High Temp, High Humidity | 65°C/95%RH, 1000hrs           | 90          | 0       |

| High Temp, Storage       | $Ta = 150^{\circ}C, 1000hrs$  | 313         | 0       |

| Low Temp, Storage        | $Ta = -55^{\circ}C$ , 1000hrs | 86          | 0       |

#### 3.2.4 Mechanical & Environmental Test

Table 7 Mechanical & Environmental Test Results

| Test Item                | Condition                        | Plast       | tic     | Side-b      | raze    |

|--------------------------|----------------------------------|-------------|---------|-------------|---------|

| - rest item              | Condition                        | Sample Size | Failure | Sample Size | Failure |

| Temperature Cycling      | -55°C ~ 150°C 10 cycles          | 4159        | 0       | 4920        | 1       |

|                          | -55°C ~ 150°C 200 cycles         | 826         | 1       | 359         | 0       |

| Thermal Shock            | 0°C ~ 100°C 10 cycles            | 110         | 0       | 175         | 0       |

| Soldering Heat           | 260°C, 10sec                     | 180         | 0       | 177         | 0       |

| Mechanical Shock         | 1500G 0.5 ms<br>3 times/X, Y, Z  | 110         | 0       | 189         | 0       |

| Vibration Fatigue        | 60Hz, 20G<br>32hrs/X, Y, Z       | 110         | 0       | 167         | 0       |

| Vibration Variable Freq. | 20 ~ 2000Hz 20G<br>4 min/X, Y, Z | 110         | 0       | 167         | 0       |

| Lead Integrity           | Bending Tention Fatigue          | 65 pins     | o       | 102 pins    | 0       |

### 3.3 Reliability Test Results on 16-bit MPU

Table 8 Reliability Test Results on 16-bit MPU HD68000 (Side-braze)

| Test Items               | Condition                                     | Sample Size | Failures |

|--------------------------|-----------------------------------------------|-------------|----------|

| Operation Life Test (1)  | Ta = 125°C, V <sub>CC</sub> = 5.5V 1000hrs    | 30          | 0        |

| Operation Life Test (2)  | $Ta = 150^{\circ}C$ , $V_{CC} = 5.5V$ 1000hrs | 20          | 0        |

| High Temperature Storage | Ta = 295°C, 1000hrs                           | 20          | 0        |

| Temperature Cycling (1)  | -55°C ∼ 150°C, 10 cycles                      | 105         | 0        |

| Temperature Cycling (2)  | -20°C ∼ 125°C. 500 cvcles                     | 45          | 0        |

| Thermal Shock            | -55°C ~ 125°C, 15 cycles                      | 22          | 0        |

| Soldering Heat           | 260°C, 10 sec                                 | 22          | 0        |

| Mechanical Shock         | 1500G, 5 msec 3 times/X, Y, Z                 | 22          | 0        |

| Vibration Variable Freq. | 20G, 100~2000Hz 3 times/X, Y, Z               | 22          | 0        |

| Constant Acceleration    | 20000G, 1 min/X, Y, Z                         | 22          | 0        |

| Solderability            | 230°C, 5 sec                                  | 22          | 0        |

#### 4. QUALITY CONTROL IN PROCESS

Process quality control plays an extremely important role in

quality assurance for semiconductor devices. Examples of control items are shown in Figure 3 and Figure 4.

| Flow             | Process             | Inspection & QC Item                                                         |

|------------------|---------------------|------------------------------------------------------------------------------|

| Q                | Wafer process       |                                                                              |

| 4                | Probe test          | 100% Electrical test                                                         |

|                  | Dicing/Break        |                                                                              |

| <b>├</b>         | Chip visual         | 100% visual inspection                                                       |

|                  | Die bonding         | Patroll inspection once/day/machine visual                                   |

|                  | Wire bonding        | once/day/machine visual<br>once/week/machine bond dimension<br>bond strength |

|                  | Internal visual     | 100% visual inspection                                                       |

| 🗘                | Molding             |                                                                              |

| 4                | Temperature cycling | 100%, Cond55°C ~ 150°C, 10 cycles                                            |

|                  | Lead trim & form    |                                                                              |

|                  | Solder dipping      |                                                                              |

| │ <del>│</del> → | External visual     | 100% visual inspection                                                       |

|                  | Mark                |                                                                              |

|                  | Burn-in             | 100% Burn-in, 125°C static                                                   |

| 🛉                | Electrical test     | 100% DC, AC & Functional test                                                |

| 🕁                | External visual     | 100% visual inspection                                                       |

| \$               | Lot acceptance      |                                                                              |

|                  | Warehouse           |                                                                              |

Figure 3 Quality Plan in Plastic Package Process

| Flow       | Process             | Inspection & QC Item                                                                     |

|------------|---------------------|------------------------------------------------------------------------------------------|

| Q          | Wafer process       |                                                                                          |

|            | Probe test          | 100% Electrical test                                                                     |

|            | Dicing/Break        |                                                                                          |

|            | Chip visual         | 100% visual inspection                                                                   |

|            | Die bonding         | Patrol inspection once/day/machine Visual                                                |

|            | Wire bonding        | Patrol inspection once/day/machine visual once/week/machine bond dimention bond strength |

| -          | Internal visual     | 100% visual inspection                                                                   |

|            | Seal                |                                                                                          |

| 4          | Temperature cycling | 100%, Cond55°C ~ 150°C, 10 cycles                                                        |

| 🕆          | Leak test           | 100% Fine leak (He)<br>100% Gross leak (Bubble)                                          |

|            | Plating             |                                                                                          |

|            | Lead cutting        | ,                                                                                        |

| >          | External visual     | 100% visual inspection                                                                   |

|            | Mark                |                                                                                          |

|            | Burn-in             | 100% Burn-in, 125°C static                                                               |

| 中          | Electrical test     | 100% DC, AC & Functional test                                                            |

|            | External visual     | 100% visual inspection                                                                   |

| \$         | Lot acceptance      |                                                                                          |

| $\bigcirc$ | Warehouse           |                                                                                          |

Test/Inspection process

Production process

QC and QA operation

Figure 4 Quality Plan in Side-braze Package Process

#### 5. QUALITY DATA FROM FIELD USE

Field failure rate is estimated in advance through production process evaluation and reliability tests. Past field data on similar devices provides the basis for this estimation. Quality information from the users are indispensable to the improvement of products quality. Therefore, field data on products delivered to the users are followed up carefully. On the basis of information furnished by the user, failure analysis is conducted and the results are quickly fed back to the design and production divisions.

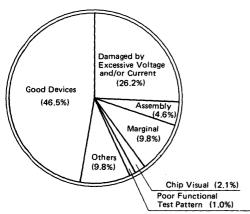

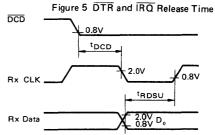

Failure analysis result on 8-bit microcomputer returned to Hitachi from April '80 to March '81 is shown in Figure 5.

Figure 5 Failure Analysis Result

#### 6. PRECAUTION

#### 6.1 Storage

It is preferable to store semiconductor devices in the following ways to prevent detrioration in their electrical characteristics, solderability, and appearance, or breakage.

- (1) Store in an ambient temperature of 5 to 30°C, and in a relative humidity of 40 to 60%.

- (2) Store in a clean air environment, free from dust and active

- (3) Store in a container which does not induce static electricity.

- (4) Store without any physical load.

- (5) If semiconductor devices are stored for a long time, store them in the unfabricated form. If their lead wires are formed beforehand, bent parts may corrode during storage.

- (6) If the chips are unsealed, store them in a cool, dry, dark, and dustless place. Assemble them within 5 days after unpacking. Storage in nitrogen gas is desirable. They can be stored for 20 days or less in dry nitrogen gas with a dew point at -30°C or lower. Unpacked devices must not be stored for over 3 months.

- (7) Take care not to allow condensation during storage due to rapid temperature changes.

#### 6.2 Transportation

As with storage methods, general precautions for other electronic component parts are applicable to the transportation of semiconductors, semiconductor-incorporating units and other similar systems. In addition, the following considerations must be given, too:

- Use containers or jigs which will not induce static electricity as the result of vibration during transportation. It is desirable to use an electrically conductive container or aluminium foil,

- (2) In order to prevent device breakage from clothes-induced static electricity, workers should be properly grounded with a resistor while handling devices. The resistor of about 1 M ohm must be provided near the worker to protect from electric shock.

- (3) When transporting the printed circuit boards on which semiconductor devices are mounted, suitable preventive measures against static electricity induction must be taken; for example, voltage built-up is prevented by shorting terminal circuit. When a belt conveyor is used, prevent the conveyor belt from being electrically charged by applying some surface treatment.

- (4) When transporting semiconductor devices or printed circuit boards, minimize mechanical vibration and shock.

#### 6.3 Handling for Measurement

Avoid static electricity, noise and surge-voltage when semiconductor devices are measured. It is possible to prevent breakage by shorting their terminal circuits to equalize electrical potential during transportation. However, when the devices are to be measured or mounted, their terminals are left open to provide the possibility that they may be accidentally touched by a worker, measuring instrument, work bench, soldering iron, belt conveyor, etc. The device will fail if it touches something which leaks current or has a static charge. Take care not to allow curve tracers, synchroscopes, pulse generators, D.C. stabilizing power supply units etc. to leak current through their terminals or housings.

Especially, while the devices are being tested, take care not to apply surge voltage from the tester, to attach a clamping circuit to the tester, or not to apply any abnornal voltage through a bad contact from a current source.

During measurement, avoid miswiring and short-circuiting. When inspecting a printed circuit board, make sure that no soldering bridge or foreign matter exists before turning on the power switch.

Since these precautions depend upon the types of semiconductor devices, contact Hitachi for further details.

#### 6.4 Soldering

Semiconductor devices should not be left at high temperatures for a long time. Regardless of the soldering method, soldering must be done in a short time and at the lowest possible temperature. Soldering work must meet soldering heat test conditions, namely, 260°C for 10 seconds and 350°C for 3 seconds at a point 1 to 1.5 mm away from the end of the device package.

Use of a strong alkali or acid flux may corrode the leads, deteriorating device characteristics. The recommended soldering iron is the type that is operated with a secondary voltage supplied by a transformer and grounded to protect from lead current. Solder the leads at the farthest point from the device package.

#### 6.5 Removing Residual Flux

To insure the reliability of electronic systems, residual flux must be removed from circuit boards. Detergent or ultrasonic cleaning is usually applied. If chloric detergent is used for the plastic molded devices, package corrosion may occur. Since cleaning over extended periods or at high temperatures will

### RELIABILITY AND QUALITY ASSURANCE

cause swollen chip coating due to solvent permeation, select the type of detergent and cleaning condition carefully. Lotus Solvent and Dyfron Solvent are recommended as a detergent. Do not use any trichloroethylene solvent. For ultrasonic cleaning, the following conditions are advisable:

- Frequency: 28 to 29 kHz (to avoid device resonation)

- Ultrasonic output: 15W/2

- Keep the devices out of direct contact with the power generator.

- Cleaning time: Less than 30 seconds

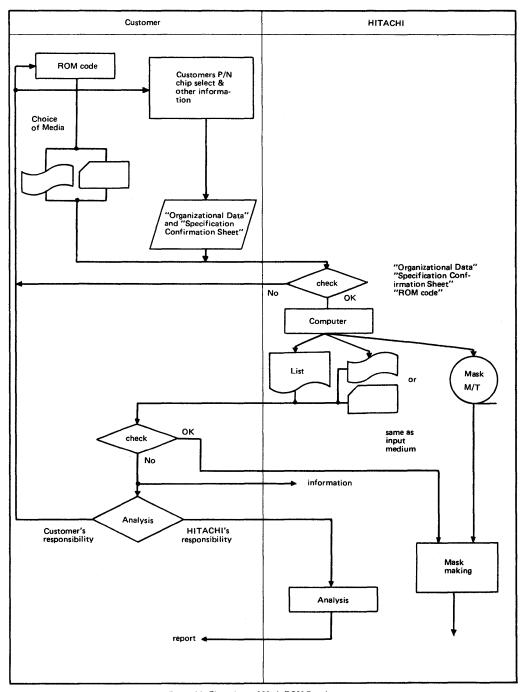

# DESIGN PROCEDURE AND SUPPORT TOOLS FOR 8-BIT SINGLE-CHIP MICROCOMPUTER

The cross assembler and the hardware simulator using various types of computer are prepared by the company as supporting systems to develop user's programs.

User's programs are mask programed into the ROM and

delivered as the LSI by the company.

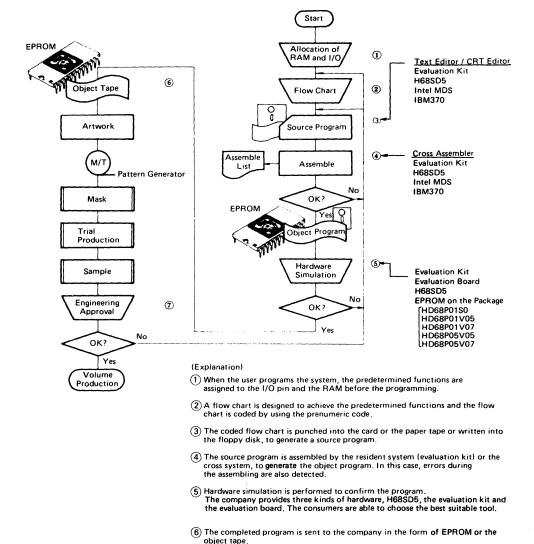

Fig. 1 shows the typical program design procedure and Table 1 shows the system development support tools for the HD6801 and HD6805 Family which are used in these processes.

Figure 1 Program Design Procedure

started.

Options such as ROM is masked by the company, LSI is testatively produced and the sample is handed in to the user. After the user has evaluated the sample and confirmed that the program is correct, mass production is

# DESIGN PROCEDURE AND SUPPORT TOOLS FOR 8-BIT SINGLE-CHIP MICROCOMPUTER

Table 1 System Development Support Tools

|                                    |                                                   | Residen             | t System                 |                                                | Cross             | System              |

|------------------------------------|---------------------------------------------------|---------------------|--------------------------|------------------------------------------------|-------------------|---------------------|

| Type No.                           | Evaluation Kit                                    | Evaluation<br>Board | EPROM on the Package     | H68SD5 + Emulator Set<br>(Hardware + Software) | HITAC M<br>IBM370 | Intel<br>MDS220/230 |

| HD6801S0<br>HD6801S5               | H61EVT2* (Hardware)<br>+<br>S31MIX-R (Software)   | H61EV00*            | HD68P01S0                | H68SD5 + H61MIX1*                              | 0                 | 0                   |

| HD6801V0<br>HD6801V5               | H61EVT2* (Hardware)<br>+<br>S31MIX1-R (Software)  | H61EV01*            | HD68P01V05<br>HD68P01V07 | H68SD5 + H61MIX1*                              | 0                 | 0                   |

| HD6805S1                           | H65EVT2 (Hardware)<br>+<br>S65MIX1-R (Software)   | H65EV00*            | HD68P05V05<br>HD68P05V07 | H68SD5 + H65MIX1                               |                   | 0                   |

| HD6805U1<br>HD6805V1               | H65EVT2 (Hardware)<br>+<br>S65MIX1-R (Software)   | H65EV01*            | HD68P05V05<br>HD68P05V07 | H68SD5 + H65MIX1                               |                   | 0                   |

| HD6805W0                           | H65EVT3* (Hardware)<br>+<br>S65MIX1-R (Software)  | H65EV02*            | _                        | H68SD5 + H65MIX2                               |                   | 0                   |

| HD6301V0<br>HD63A01V0<br>HD63B01V0 | H31EVT1* (Hardware)<br>+<br>S31MIX1-R (Software)  | H31EV00*            | -                        | H68SD5 + H31MIX1*                              | 0                 | 0                   |

| HD63L05                            | H3L5EVT1* (Hardware)<br>+<br>S65MIX1-R (Software) | H3L5EV00*           | _                        | H68SD5 + H3L5MIX1*                             |                   | 0                   |

<sup>\*</sup> Under development

#### DESIGN PROCEDURE AND SUPPORT TOOLS FOR 8-BIT SINGLE-CHIP MICROCOMPUTER

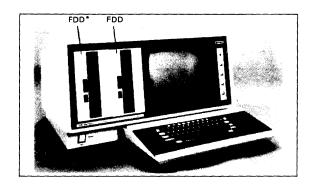

■ Single-Chip Microcomputer Development System

The H68SD5 is a development system for Hitachi 4-bit and 8-bit single-chip microcomputers.

It is an all-in-one type compact HD6800 based CRT/Key board microcomputer terminal with one Floppy disk driver and has standard interface for the TTY (RS-232C or TTL level) and printer (Centronics parallel interface). The EPROM Writer and the second Floppy disk driver are optionally available.

#### **Features**

Supports the system development for 8-bit and 4-bit single chip microcomputers - HD6801/6805 family and HMCS40

series.

- Disk based low cost system

- Provides the CRT Editor, Assembler, Emulator and EPROM Writer controlled by FDOS-III

- 56k-byte RAMs

- Allows linking between the H68SD5 and the I/O devices (TTY and Printer)

- Easy to debug user's prototype system using the Emulator Module

H68SD5

**EPROM Writer\***

HD6801/6805 family) **Emulator Module\* HMCS40** series

\* Option

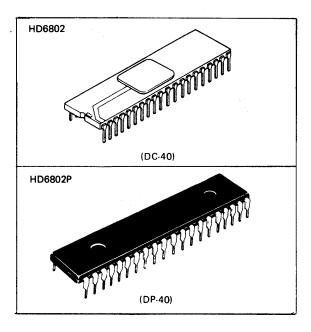

# **HMCS6800 FAMILY INSTRUCTION SET**

# Accumulator and Memory Operations

|                         |               | d Memory Op                         |          | HE     | 26<br>26<br>26 | 80<br>80      | 17       |           | H         | D6<br>D6 | 80<br>80<br>80<br>80 | 5U<br>5V |          |            | н      | )6:           | 30       | 1∨       |          | _       | HD6         | 3L    | 05       |              | ŀ            | HC      | )68<br>)68 | 302           |      |          |               |           |               | 80                |                       |      |          |

|-------------------------|---------------|-------------------------------------|----------|--------|----------------|---------------|----------|-----------|-----------|----------|----------------------|----------|----------|------------|--------|---------------|----------|----------|----------|---------|-------------|-------|----------|--------------|--------------|---------|------------|---------------|------|----------|---------------|-----------|---------------|-------------------|-----------------------|------|----------|

| Operations              | Mne-<br>monic | Boolean/<br>Arithmetic<br>Operation | IMMED    | DIRECT | INDEX          | EXTND         | IMPL     | MANEN     | DIRECT    | INDEX    | EXTND                | IMPL     | RELATIVE | IMMED      | DIRECT | INDEX         | EXTND    | IMPL     | RELATIVE | IMMED   | DIRECT      | EXTND | IMPL     | RELATIVE     | IMMED        | DIRECT  | INDEX      | EXTND         | IMPL | RELATIVE | IMMED         | DIRECT    | INDEX         | EXTND             | EXT INDIRECT          | IMPL | RELATIVE |

| Add                     | ADDA          | A+M→A                               | 0        |        | 0              | 0             |          |           | ) c       | 0        | 0                    |          |          | Ō          | 0      | 0             |          |          |          | 0       | 00          | 0     | I        |              | 0            |         |            | 0             |      |          |               |           |               | 0                 |                       | I    | _        |

|                         | ADDB          | B+M→B                               | $\circ$  | 0      | 0              | 0             |          | 1         | _         |          | _                    | L        | L        | 0          | 0      | 0             | 0        |          | $\perp$  | _       |             |       |          | L            | 0            | 0       | Q          | 0             |      |          | Q             | 0         | 0             | 0                 | 이                     |      |          |

| Add<br>Double           | ADDD          | A:B+M:M+1<br>→A:B                   | 0        | 0      | 0              | 0             |          |           |           |          |                      |          |          | 0          | 0      | 0             | 0        |          |          |         |             |       |          |              |              |         |            |               |      |          | 0             | 0         | 0             | 0                 |                       |      |          |

| Add<br>Accumulators     | ABA           | A + B→A                             |          |        |                |               | 0        |           |           |          |                      |          |          |            |        |               |          | 0        |          |         |             |       |          |              |              |         |            |               |      |          |               |           |               |                   |                       |      |          |

| Add with                | ADCA          | A+M+C→A                             | 0        | O      | 0              | Ō             |          | (         | 0         | 10       | 0                    |          |          | 0          | 0      | 0             | 0        |          |          |         | 20          | 0     | 1        | Г            | 0            | 0       | Ô          | 0             |      | 1        | 0             | o         | 0             | 0                 | 히                     | 7    | _        |

| Carry                   | ADCB          | B+M+C→B                             |          | 0      |                |               |          | Ι         |           | Ι        |                      | Τ        | I        | Ō          |        | 0             |          |          |          |         |             |       |          |              |              |         | 0          | Ó             |      |          | Ô             | 0         | 0             | 0                 | 0                     | I    |          |

| Subtract                | SUBA          | AM→A                                |          | 0      |                |               |          |           | )         |          | 0                    | L        |          |            |        | 0             | 0        |          |          |         | $\supset C$ | 0     |          |              | 0            | 0       | 0          | 0             |      |          | 0             | 0         | 0             | 0                 | $\overline{\bigcirc}$ |      |          |

|                         | SUBB          | B−M→B                               | 0        | 0      | 0              | 0             |          | 1         | 1         | L        | 1                    | L        | <u> </u> | 0          | 0      | 0             | 0        |          |          | _       | 1           | 1     | L        | _            | 0            | 0       | 0          | 0             |      | _        | 이             | 의         | 의             | 9                 | 의                     | _    |          |

| Subtract<br>Double      | SUBD          | A:B-M:M+1<br>→A:B                   | 0        | 0      | 0              | 0             |          |           |           |          |                      |          | }        | 0          | 0      | 0             | 0        |          |          |         |             |       |          |              |              |         |            |               |      |          | 0             |           | 0             |                   |                       |      |          |

| Subtract<br>Accumulator | SBA           | A-B→A                               |          |        |                |               | 0        |           |           |          |                      |          |          |            |        |               |          | 0        |          |         |             |       |          |              |              |         |            |               | 0    |          |               |           |               |                   |                       |      | -        |

| Subtract with           | SBCA          | A-M-C→A                             | 0        | 0      | 0              | Ō             | $\Box$   | 1         | 50        | 10       | olo                  | T        |          | 0          | 0      | 0             | 0        |          |          | 5       | olc         | 0     | 1        |              | 0            | 0       | Ö          | 0             |      | 7        | 0             | 0         | 0             | 0                 | ot                    | 7    | -        |

| Carry                   | SBCB          | B-M-C→B                             | 0        | 0      | Ó              | 0             |          | I         |           |          |                      |          |          | Ō          | 0      | Ö             | 0        |          |          | 1       | T           | T     |          |              | 0            | 0       | 0          | Õ             |      |          | 0             | 0         | 0             | 0                 | ol                    | T    |          |

| Multiply                | MUL           | A×B→A:B                             |          |        |                |               | 0        | I         | I         |          | I                    | L        |          |            |        |               |          | 0        |          |         |             | Γ     |          |              |              |         |            |               |      |          |               | $\exists$ |               | $\Box$            |                       | 0    |          |

| Decimal<br>Adjust A     | DAA           | Decimal Adjust<br>Accumulator       |          |        |                |               | 0        |           |           |          |                      |          |          |            |        |               |          | 0        |          |         |             |       |          |              |              |         |            |               | 0    |          |               |           |               |                   |                       |      |          |

| Increment               | INC           | M + 1 → M                           |          |        | 0              | O             | $\sqcap$ | T         | 10        | 10       |                      | T        |          | T          | 1      | 0             | 0        |          | $\neg$   |         | olc         | 1     |          | 1            | _            |         | 0          | 0             |      | 1        |               | ol        | 0             | ol                | ō†                    | 7    |          |

|                         | INCA          | A+1→A                               |          |        |                |               | 0        | 1         | 1         | 1        | T                    | 0        |          | 1          |        |               |          | 0        | $\top$   | 7       | $\top$      |       | 0        | 1            |              |         |            |               | 0    |          |               |           |               |                   | 1                     | ol   | -        |

|                         | INCB          | B+1→B                               |          |        |                |               | 0        | T         |           |          |                      | Ī        | T        |            |        |               |          | O        |          | 1       | T           | T     |          |              |              |         |            |               | 0    |          |               |           |               |                   | (                     | 0    |          |

| Decrement               | DEC           | M – 1 → M                           |          |        | 0              | 0             |          | I         | C         |          |                      |          |          |            |        | 0             | 0        |          |          |         | ) C         |       |          |              |              |         | 0          | 0             |      |          |               | 0         | 0             | 0                 | 0                     |      | _        |

|                         | DECA          | A-1→A                               | L        |        | L              | L.            | 0        | 1         | $\perp$   | 1        | L                    | 0        |          | L          |        |               |          | 0        |          |         |             |       | 0        |              |              |         |            |               | 0    |          |               |           |               |                   |                       | 0    |          |

|                         | DECB          | B-1→B                               | L        |        | _              | L             | 0        | 1         | 1         | 1        | 1_                   | L        | 1_       | L          | 1_     |               |          | 0        | 4        | 1       |             | 1_    | 1_       | <u> </u>     |              |         |            |               | 0    | _        | _             | _         | _             | _                 |                       | 의    |          |

| Clear                   | CLR           | 0→M                                 | L        |        | 0              | 0             |          | 1         | 10        |          | 4                    | L        | 1        | <u> </u>   | 1_     | 0             | 0        |          | 4        | 4       | <u> </u>    | 4     | 1        | _            |              | _       | 0          | 0             | 1    | _        | -             | 의         | 익             | 익                 |                       | _    |          |

|                         | CLRA          | 0→A                                 | <u> </u> | -      | ļ              | _             | 9        | +         | +         | +-       | ┿-                   | 0        | 1-       | ┞          | -      |               |          | Ö        | +        | 4       | +           | ╄-    | 0        | ļ            | _            | L       |            |               |      | 4        |               | -+        | -             |                   |                       | 의    |          |

| Compose                 | CLRB          | 0→B<br>A – M                        |          |        |                |               | 0        | 1         | 1         | 1        | L                    | ╄-       | -        | <u></u>    |        | $\overline{}$ |          | 0        | -        | =       |             | 1     | -        | -            |              |         |            |               | 0    | -        | $\rightarrow$ | ᅱ         | 긁             | $=$ $\frac{1}{2}$ |                       | 익    |          |

| Compare                 | CMPB          | B-M                                 |          | 0      |                |               | $\vdash$ | -         |           |          | 10                   | -        | ┼        | 읮          | 00     | 으             | 0        | -        |          | 4       | $\supset C$ | 14    | -        | <del> </del> |              | 00      |            |               | -    |          |               | 의         |               | 읫                 | 의.                    | +    |          |

| Compare<br>Double       | CMPD          | A:B-M:M+1                           |          |        |                |               |          | $\dagger$ | $\dagger$ | -        | -                    |          | T        |            |        | $\cup$        | $\cup$   |          | 1        | 1       | +           | -     | $\vdash$ | -            | 9            |         | 0          | $\mathcal{L}$ |      | 1        |               |           |               | 0                 |                       | +    |          |

| Compare<br>Accumulators | СВА           | A-B                                 |          |        | -              | -             | 0        | †         | 1         | 1-       |                      |          |          | $\vdash$   |        |               |          | 0        | +        | 7       |             | t     |          | -            | -            |         |            |               | 0    | 1        | 1             | 7         | $\dagger$     | +                 | +                     | 1    |          |

| Test Zero or            | TST           | M-00                                | +-       | -      | 0              |               | +        | +         | to        | to       | +                    | +        | +-       | +          | -      | 0             | 0        | -        | +        | -1,     | əlc         | +-    | +-       | -            | <del> </del> |         | 0          | 0             | +-+  | +        | -             | 러         | $\rightarrow$ | 0                 | ət                    | +    |          |

| Minus                   | TSTA          | A-00                                |          |        | ř              | ۲             | o        | $\dagger$ | +         | 1        | +                    | 6        | +        | †          | 1      | $\preceq$     | $\vdash$ | 0        | +        | -+      | 4           | +     | 0        | -            | <del> </del> | -       | $\preceq$  | ۲             | 0    | -1       | +             | 4         | 4             | 7                 |                       | ət   |          |

|                         | TSTB          | B-00                                | T        |        |                | _             | Ö        | +         | $\top$    | +        | †                    | Ť        | 1        | 1          |        |               |          | ŏ        | +        | 7       | +           | T     | ľ        |              |              |         |            | _             | ŏ    | 1        | +             | +         | +             | +                 |                       | ŏt   |          |

| And                     | ANDA          | A·M→A                               |          | 0      |                |               |          | 10        | O         | 10       | 0                    | T        | Ι        |            | 0      |               |          |          |          | 5       |             | 0     |          |              | 0            | O       | O          | 0             |      |          |               |           |               | 0                 |                       | 7    | _        |

|                         | ANDB          | B·M→B                               | 0        | 0      | 0              | Ō             |          | I         | Ι         | Ι        | Γ                    |          | I        | 0          | 0      | 0             | 0        |          |          |         |             |       |          |              |              |         | 0          | 0             |      |          |               |           |               | 0                 |                       |      |          |

| Or                      | ORAA<br>ORA   | A+M→A                               | 0        | 0      | 0              | 0             |          |           | C         | 0        | 0                    |          |          | 1          | 0      | 0             | 0        |          |          | 2       | 00          | 0     |          |              | 0            | 0       | 0          | 0             |      |          | 0             | 0         |               | 0                 |                       | 1    |          |

|                         | ORAB<br>ORB   | B+M→B                               | 0        | 0      | 0              | 0             |          | T         |           |          |                      |          |          | 0          | 0      | 0             | 0        |          |          |         |             |       |          |              | 0            | 0       | 0          | 0             |      | 1        | 0             |           | 0             |                   |                       | 1    | _        |

| Exclusive Or            | EORA          | A⊕M→A                               | 0        | 0      | 0              | 0             | $\vdash$ | 1         | oto       | 10       | to                   | 1        | T        | 0          | 0      | 0             | 0        |          |          | ٥tc     | olo         | to    | 1        |              | 0            | 0       | Ō          | 0             | 1    | +        | ol            | ot        | ol            | 0                 | σt                    | +    | _        |

|                         | EORB          | B⊕M→B                               | 0        | 0      | 0              | Ō             |          | Ť         | Ť         |          | Τ                    | 1        | $\vdash$ | Ŏ          | 00     | Ó             | Ó        |          | 1        | +       | 1           | Ť     | 1        | Γ            | Ó            | 0       | 0          | Ō             |      | 1        | 0             | Ol:       | 010           | Ok                | Ol.                   | 7    | -        |

|                         |               | М→м                                 |          |        | 0              |               |          |           | C         | 0        |                      |          | Ι        |            |        | 0             | 0        |          |          | -       | O C         | Ī     | I        | Γ            |              |         | 0          | 0             |      | 1        | -             | o         | 0             | 0                 | ŌŢ                    | 1    |          |

| 1's                     | COMA          | A→A                                 |          |        |                |               | 0        | $\prod$   |           | L        |                      | 0        |          | L          |        |               |          | 0        | $\Box$   | I       | $\perp$     |       | 0        |              |              |         |            |               | 0    | $\Box$   |               | J         | $\Box$        | J                 |                       | 9    | _        |

|                         | СОМВ          |                                     | L        |        |                |               | 0        | 1         | $\perp$   |          |                      | L        | L        | L          |        |               |          | 0        | 1        | $\perp$ | L           | L     | L        |              |              |         |            |               | 0    | _[       | J             | $\Box$    | $\Box$        | $\bot$            |                       | 0    |          |

| Complement 2's (Negate) | NEG           | 00 – M→M                            | _        |        | 0              | 0             |          | 1         | 10        | 10       | -                    | Ļ        | Ļ.       | <u> </u>   |        | 0             |          |          | 1        | 1       | 2 0         | -     | 1        | _            |              | _       | 0          | 0             |      | _]       | _             | 의         | 0             | 0                 |                       | _    | _        |

| Z 3 (Negate)            |               | 00 – A→A                            | _        |        |                | _             | 0        | +         | +         | 1        | 1                    | 0        | 1_       | <b> </b> _ |        | _             |          | Ö        | 4        | 1       |             | 1     | 10       | ļ_           | $\sqcup$     | _       |            |               | 의    | 4        | 4             | _         | _             | 4                 |                       | 의    |          |

| Dia Tosa                |               | 00 – B→B                            |          |        |                |               | 0        | 1         | 1         | 1        | 1                    | 1        | +-       | F          |        | =             |          | 0        | 4        | 4       | 1           | 1     | 1        | _            |              | _       |            | _             | 0    | 4        | $\downarrow$  | $\exists$ | 4             | $\downarrow$      |                       | 익    |          |

| Bit Test                | BITA          | A · M                               | 일        | 0      | 9              | 9             | $\vdash$ | 1         |           | 40       | 40                   | +        | -        | 12         | 0      | 읮             | 9        | $\vdash$ | -49      | 4       | <u> </u>    | 10    |          |              | 의            | 의       | 0          | 10            | 1    | 4        | 의             | 炓         | 읮             | 9(                | 升                     | 4    |          |

|                         | BITB          | B · M                               | $\cup$   | 0      | $\cup$         | $\mathcal{O}$ | LL       | L         |           | 1        | 1                    | [        | 1        | S          | 0      | $\circ$       | 9        | L I      | L        | _       |             | 1_    | L        | _            | $\cup$       | $\circ$ | 0          | $\odot$       |      |          | $\cup$        | $\cup$    | O             | 0                 | $\cup$ L              |      | _        |

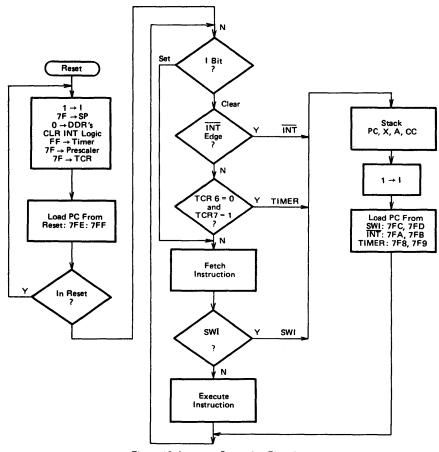

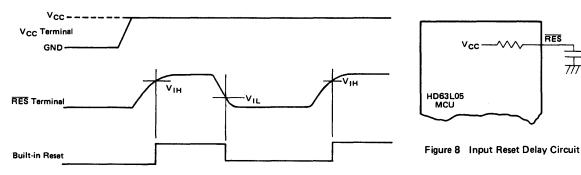

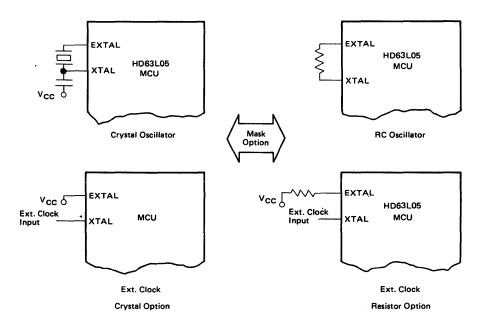

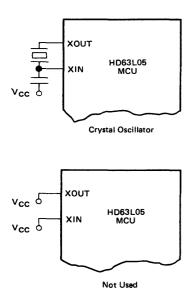

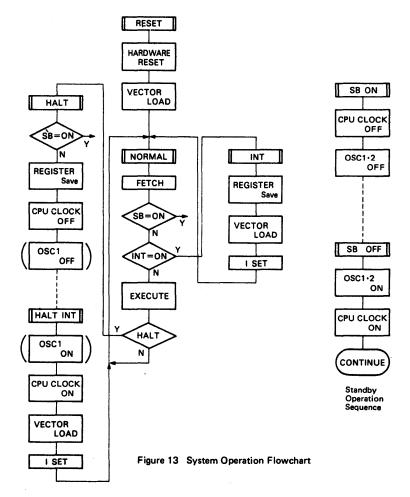

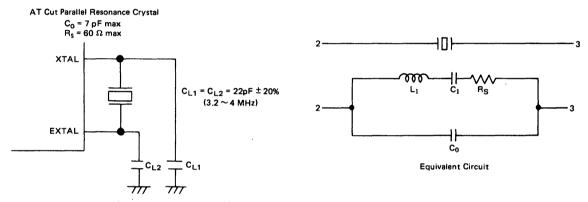

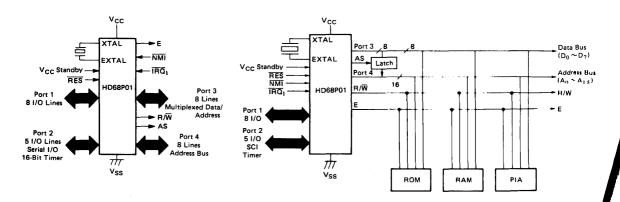

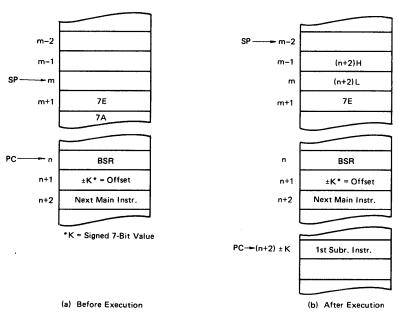

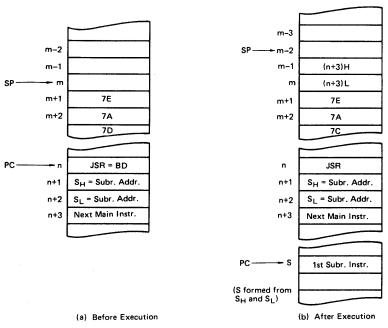

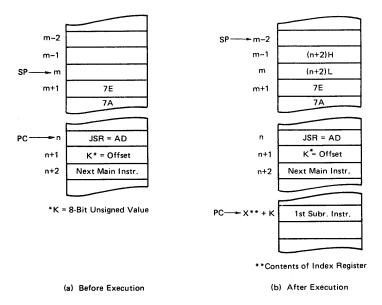

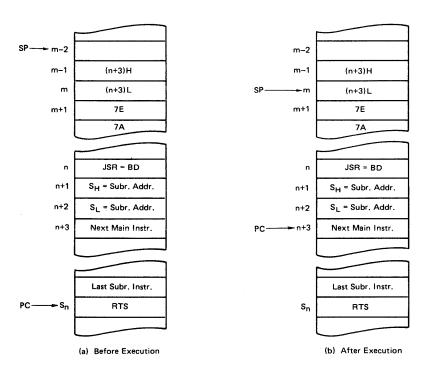

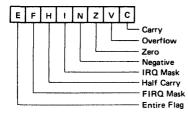

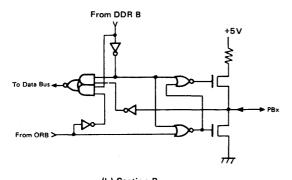

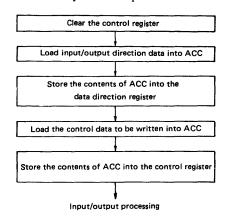

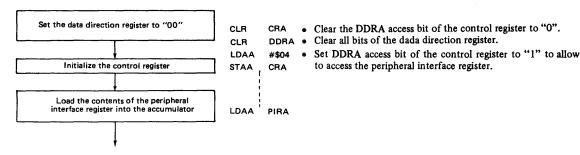

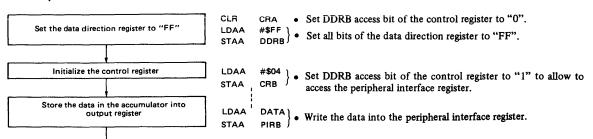

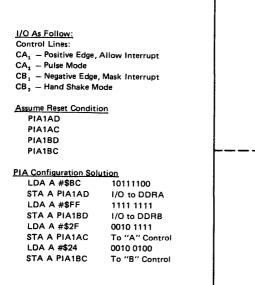

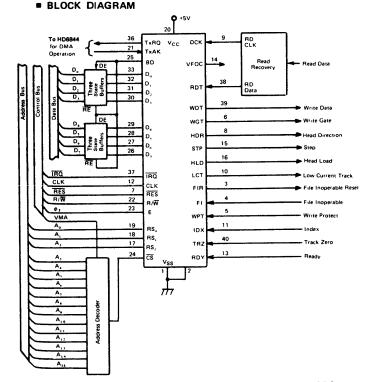

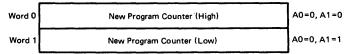

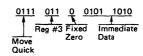

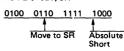

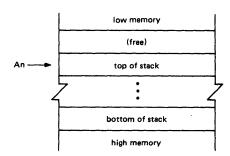

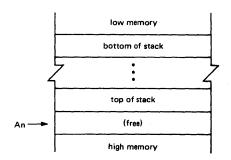

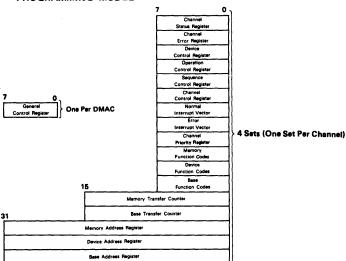

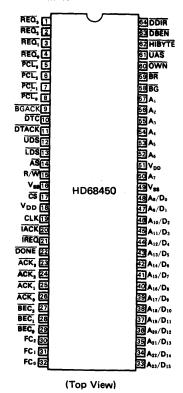

# HMCS6800 FAMILY INSTRUCTION SET