- HD6301/HD6303 SERIES HANDBOOK

USER'S MANUALS

SOFTWARE APPLICATION NOTES

HARDWARE APPLICATION NOTES

WIDE TEMPERATURE SPECIFICATIONS

## HD6301/HD6303 SERIES HANDBOOK

- **USER'S MANUALS:**

- HD6301V1/HD6303R

- HD63701V

- HD6301X0/HD6303X/HD63701X0

- SOFTWARE APPLICATION NOTES

- **MARDWARE APPLICATION NOTES**

- **C LANGUAGE PROGRAMMING TECHNIQUES**

#### **M** APPENDIX:

- HD6301V/HD6303R Q and A

- HD6301X0/HD6303X OSCILLATOR CIRCUIT

- WIDE TEMPERATURE RANGE SPECIFICATIONS

-40°C to +85°C (J VERSION)

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

### **INDEX**

Ouick Reference Guide

Addressing Modes, CPU Architecture, and Instruction Set

HD6301V1/HD6303R User's Manual

HD63701V User's Manual

HD6301X0/HD6303X/HD63701X0 User's Manual

HD6301Y0/HD6303Y/HD63701Y0 User's Manual

Software Application Notes

Hardware Application Notes

C Language Programming Techniques

APPENDIX:

HD6301V1/HD6303R Q and A—HD6301X0/HD6303X Oscillation Circuit Wide Temperature Range Specifications, -40°C to +85°C, (J Version) Hitachi Sales Offices Section 10, Page 1318

#### **TABLE OF CONTENTS**

| Section Quick   | on 1<br>x Reference Guide                                | Page |

|-----------------|----------------------------------------------------------|------|

| QUICK           | REFERENCE GUIDE                                          | 1    |

| PACK            | AGE REFERENCE GUIDE                                      | 4    |

| Section Address | on 2 essing Modes, CPU Architecture, and Instruction Set | Page |

| 1. AS           | SSEMBLY LANGUAGE                                         | 17   |

| 1.1             | Addressing Modes                                         | 17   |

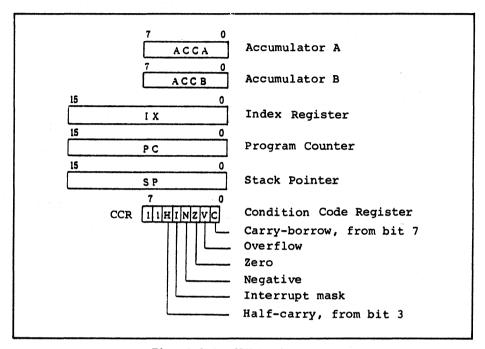

| 1.2             | CPU Registers                                            | 26   |

| 1.3             | Instruction Set Details                                  | 28   |

| Section HD63    | on 3<br>01V1/HD6303R User's Manual                       | Page |

| Notice          | on HD6301V1 and HD6303R                                  | 126  |

|                 | /ERVIEW                                                  | 128  |

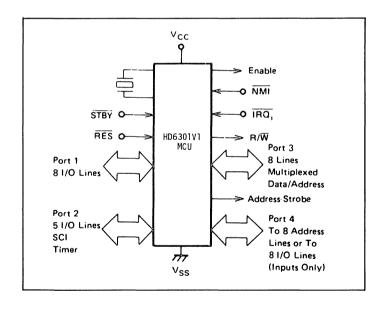

| 1.1             | Features of HD6301V1                                     | 128  |

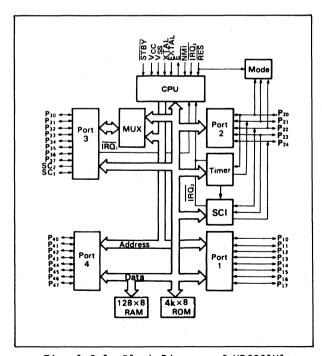

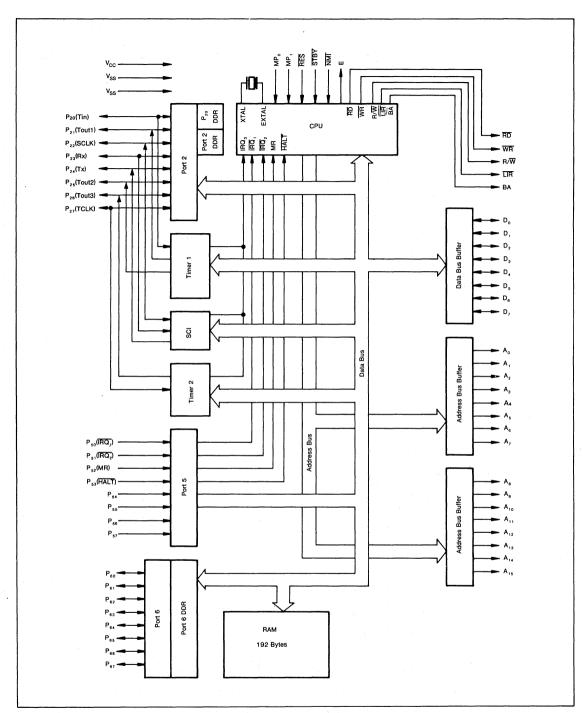

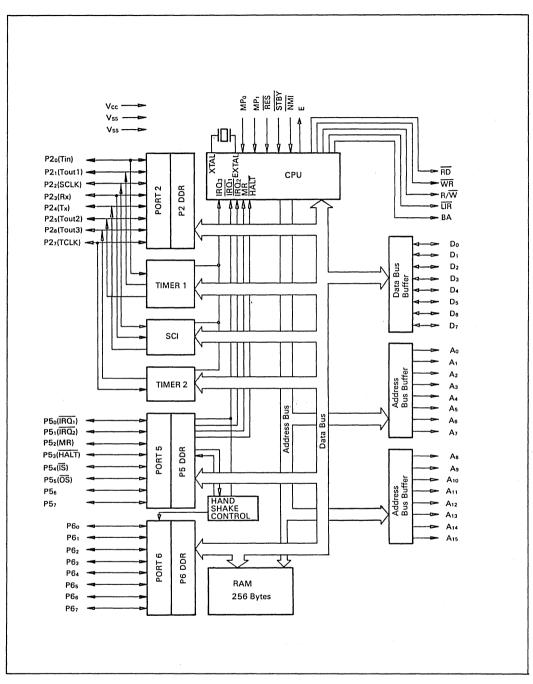

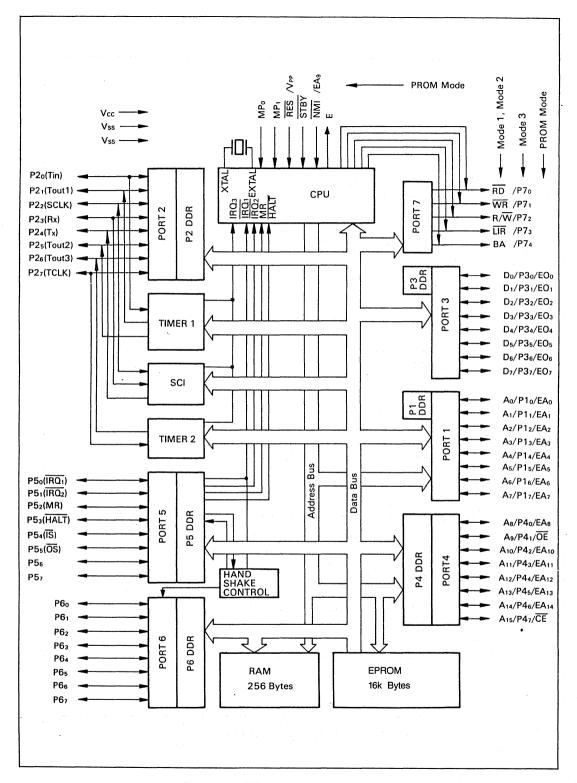

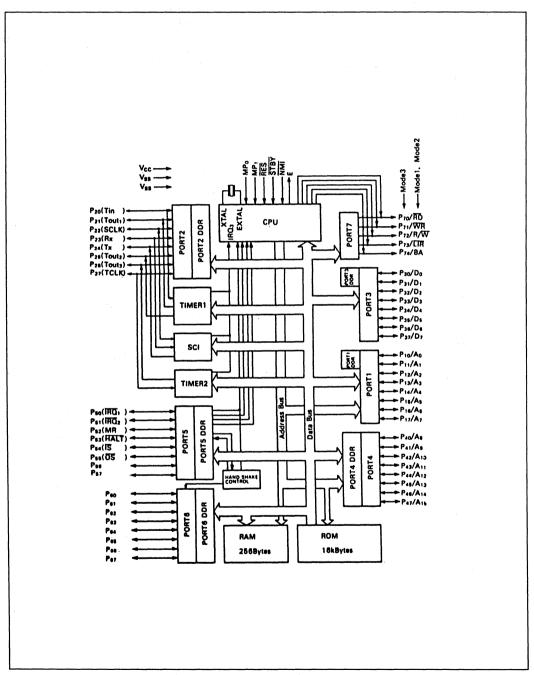

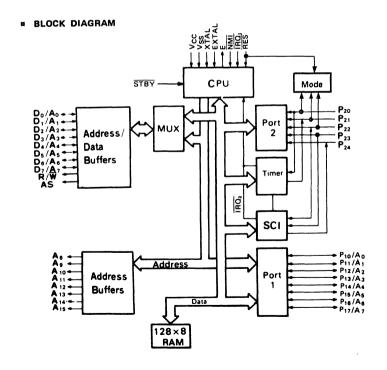

| 1.2             | Block Diagram                                            | 128  |

| 1.3             | Functional Pin Description                               | 129  |

| 2. IN           | TERNAL ARCHITECTURE AND OPERATIONS                       | 130  |

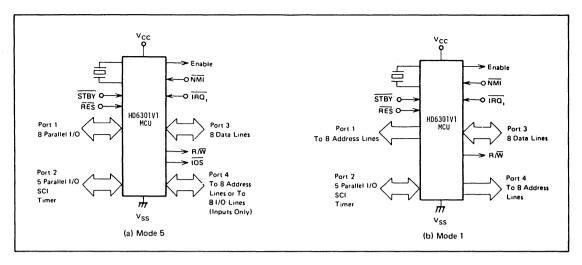

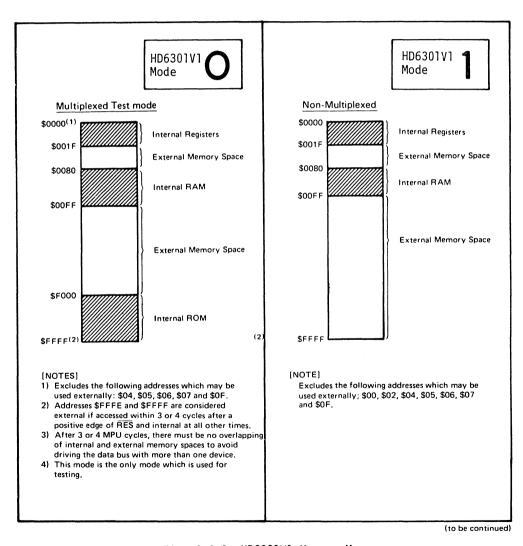

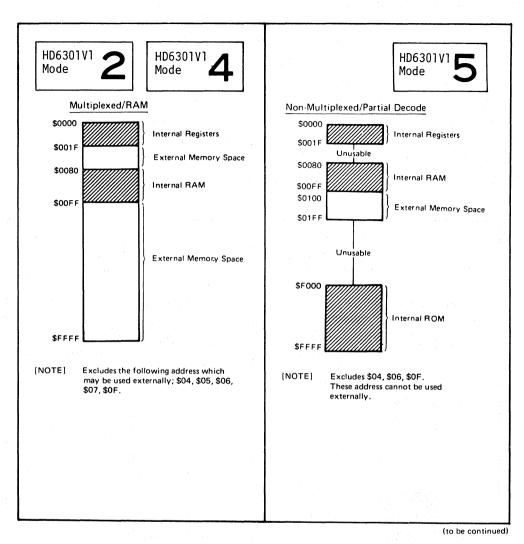

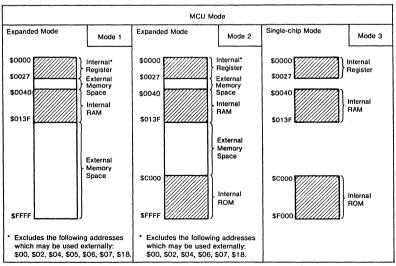

| 2.1             | Mode Selection                                           | 130  |

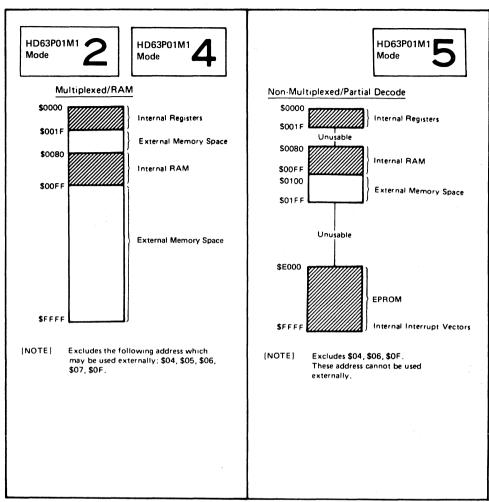

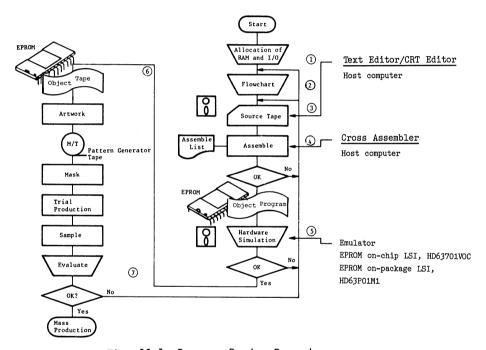

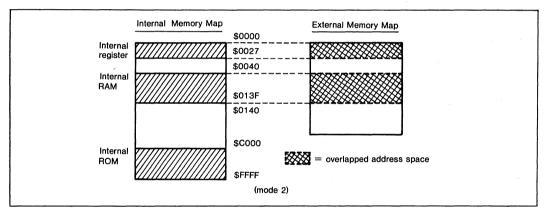

| 2.2             | Memory Map                                               | 135  |

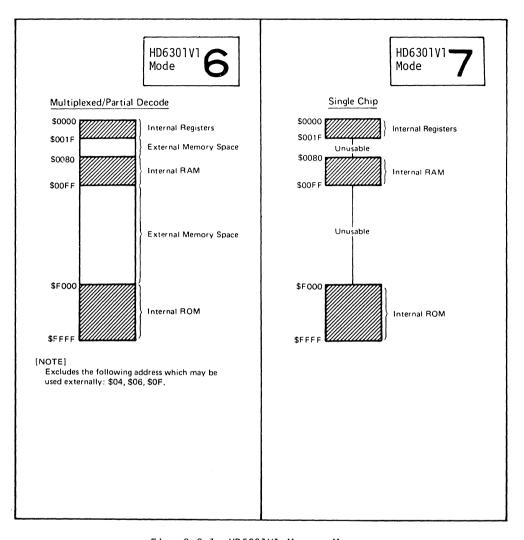

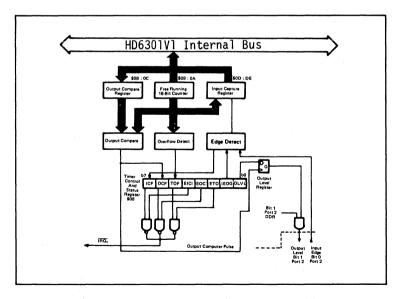

| 2.3             | Registers                                                | 140  |

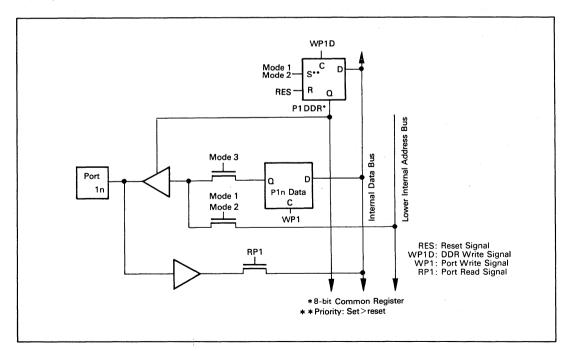

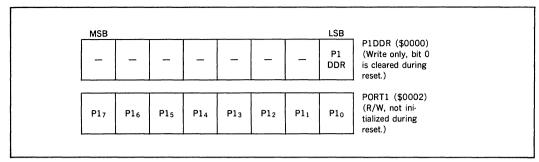

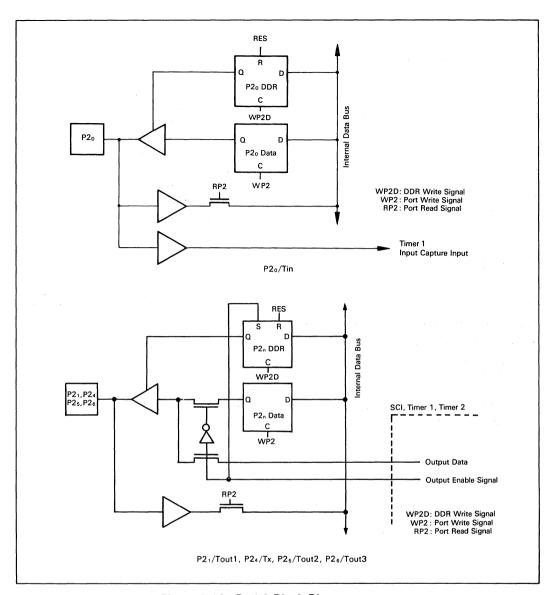

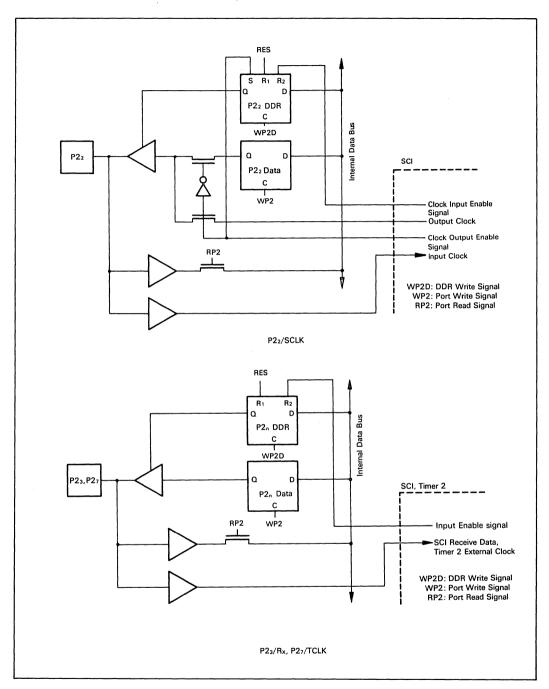

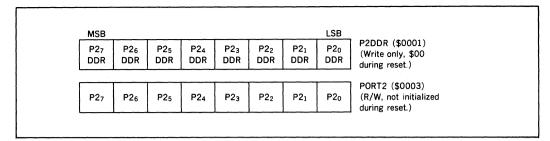

| 2.4             | I/O Ports                                                | 142  |

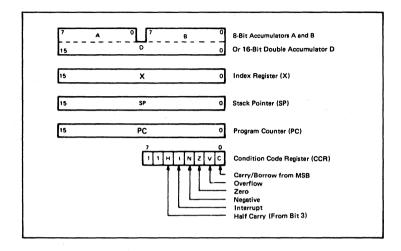

| 2.5             | Programmable Timer                                       | 146  |

| 2.6             | Serial Communication Interface                           | 150  |

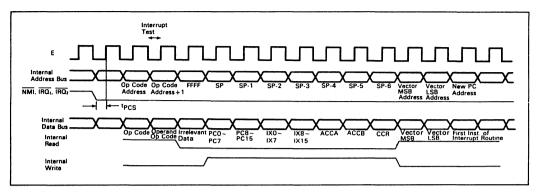

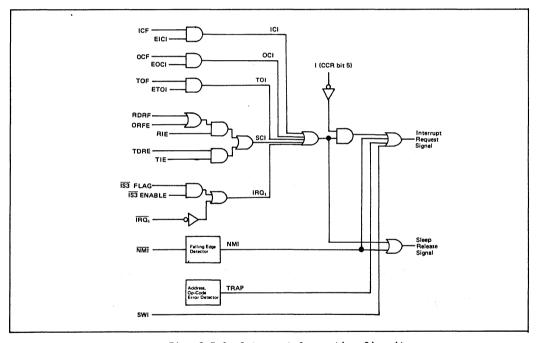

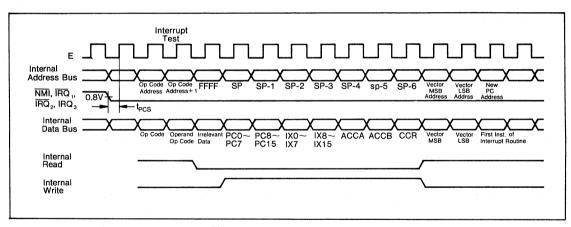

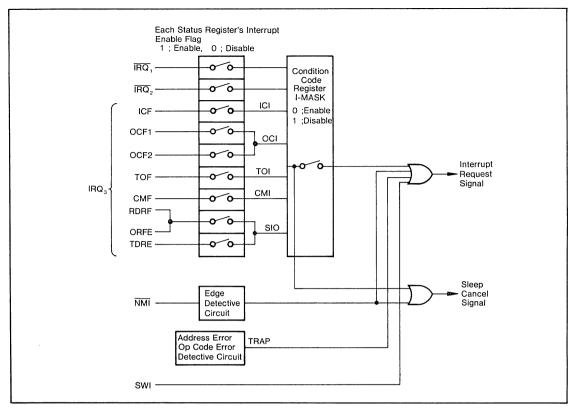

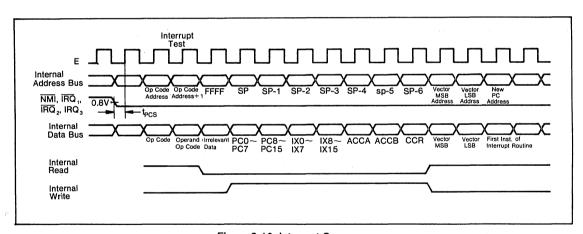

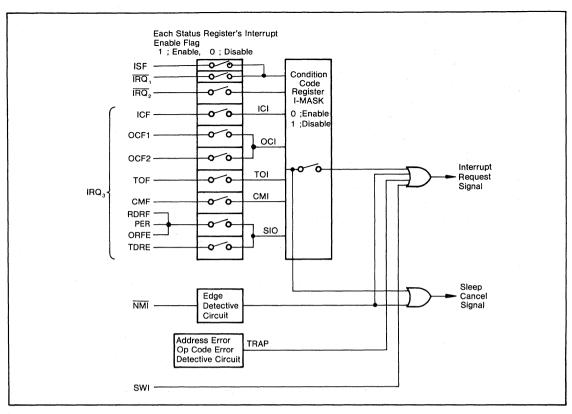

| 2.7             | Interrupts                                               | 157  |

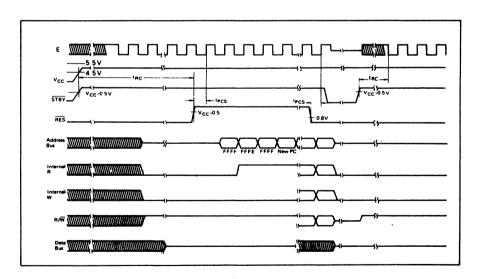

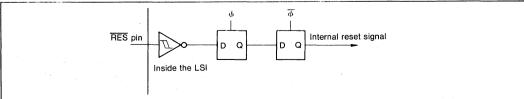

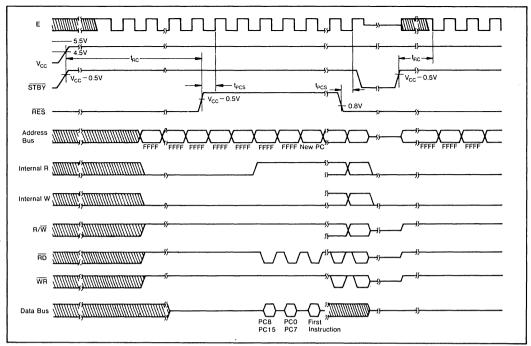

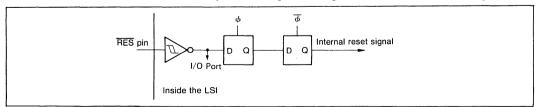

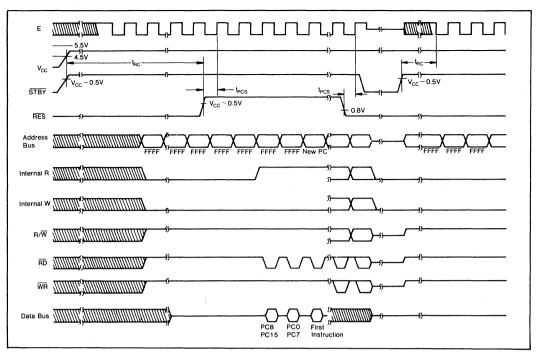

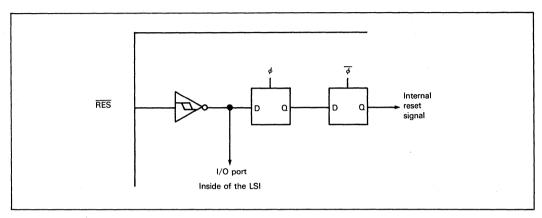

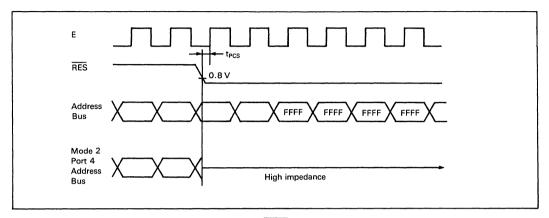

| 2.8             | Reset                                                    | 159  |

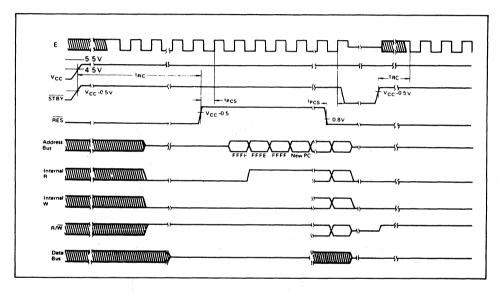

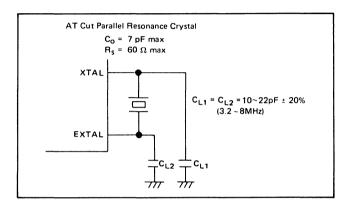

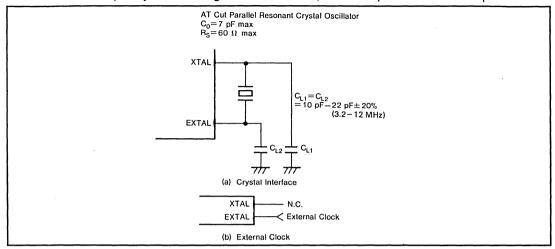

| 2.9             | Oscillator                                               | 161  |

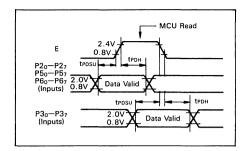

| 2.10            | Strobe Signals                                           | 161  |

| 2.11            | RAM Control Register                                     | 162  |

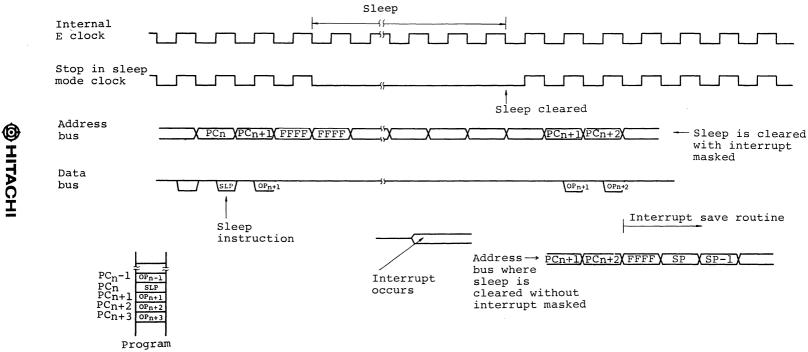

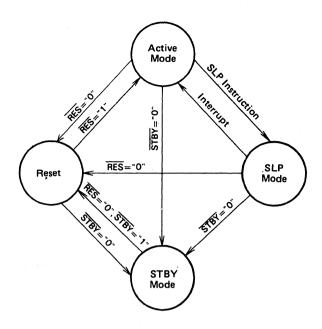

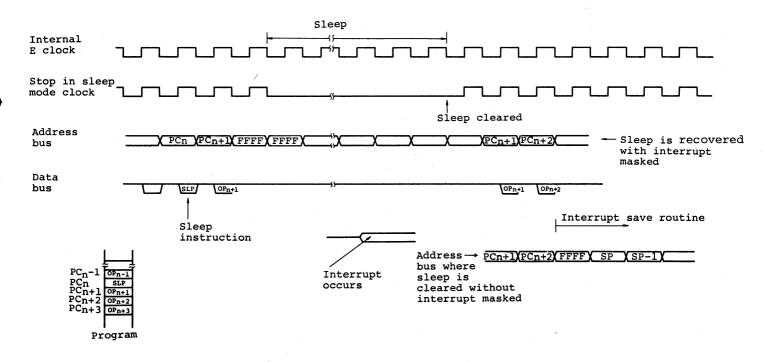

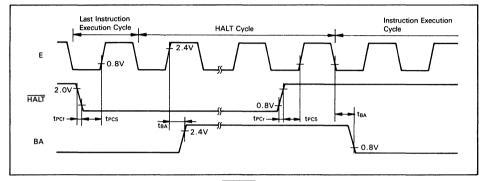

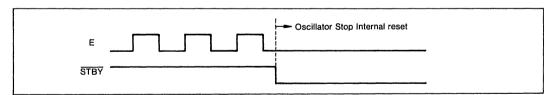

| 2.12            | Low Power Consumption Mode                               | 163  |

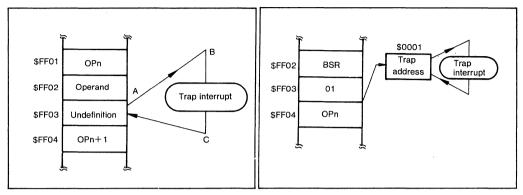

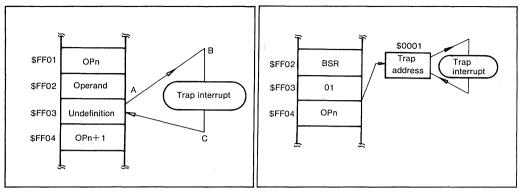

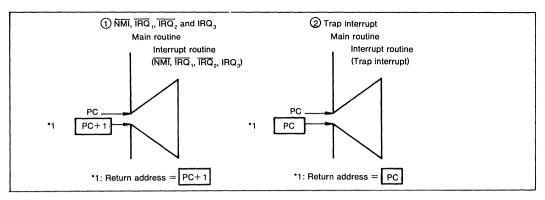

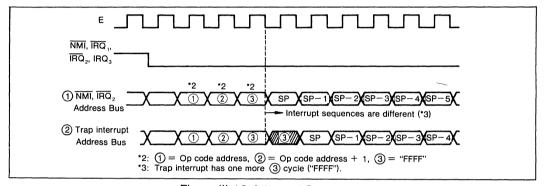

| 2 12            | TRAP Function                                            | 167  |

| 3. INSTRUCTIONS                                                      | 168  |

|----------------------------------------------------------------------|------|

| 3.1 Addressing Modes                                                 | 168  |

| 3.2 Instruction Set                                                  | 170  |

| 3.3 Instruction Execution Cycles                                     | 175  |

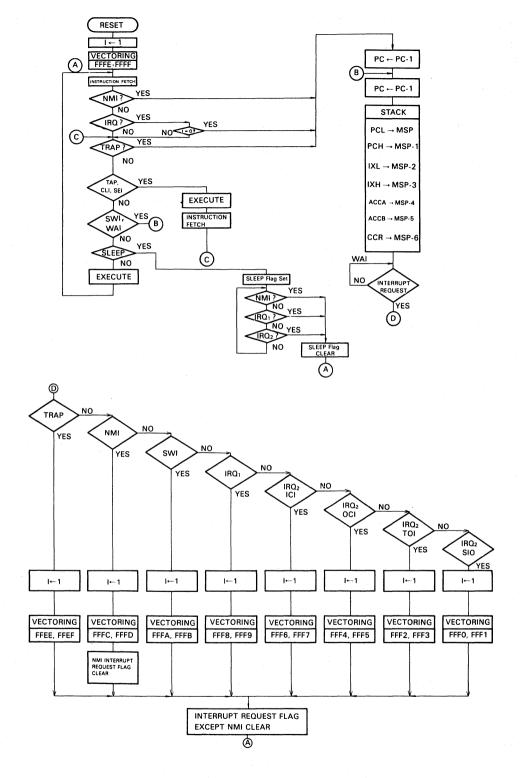

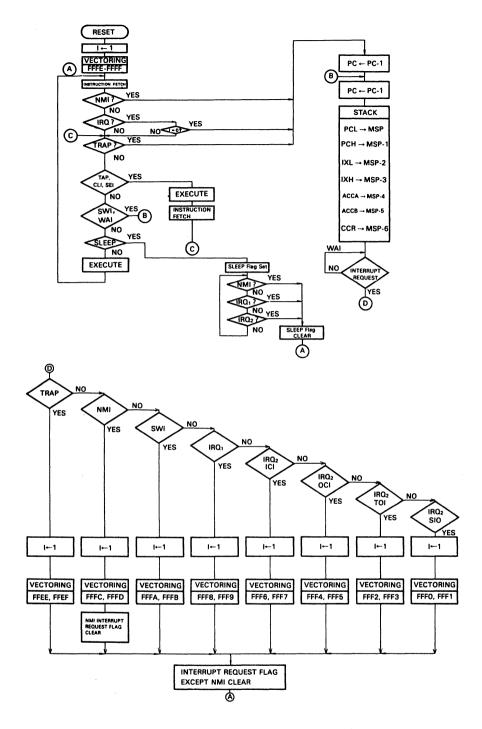

| 3.4 System Flowchart                                                 | 181  |

|                                                                      |      |

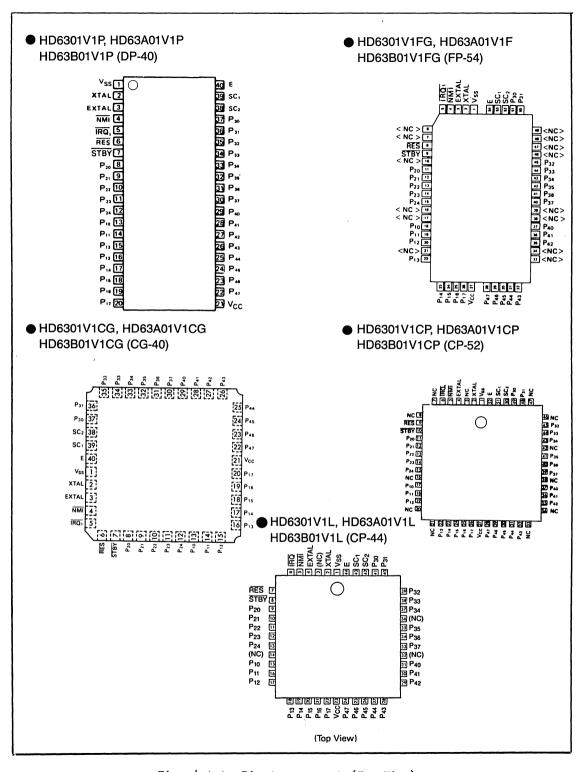

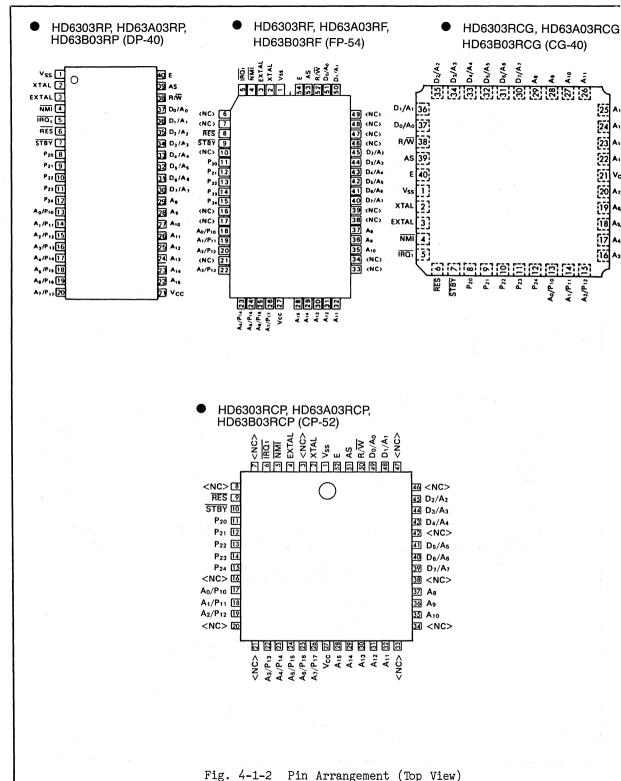

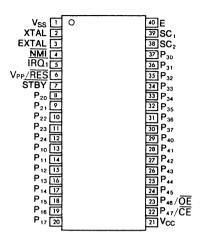

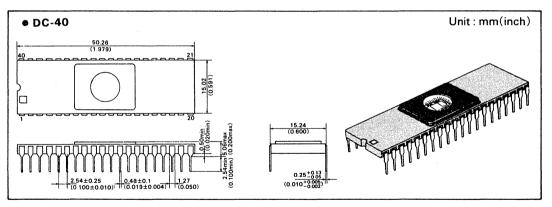

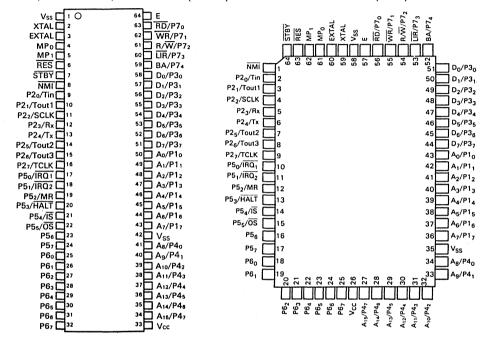

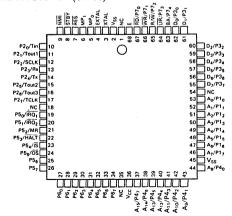

| 4. PIN ARRANGEMENT AND PACKAGE INFORMATION                           | 183  |

| 5. ELECTRICAL CHARACTERISTICS                                        | 186  |

| 6. APPLICATIONS                                                      | 191  |

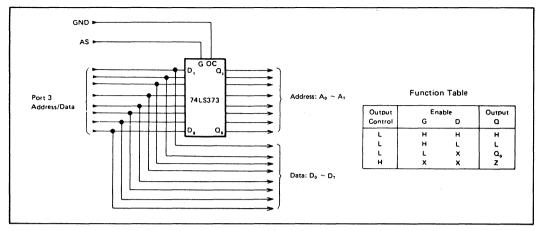

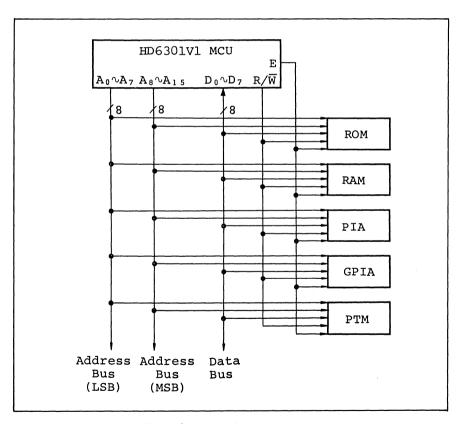

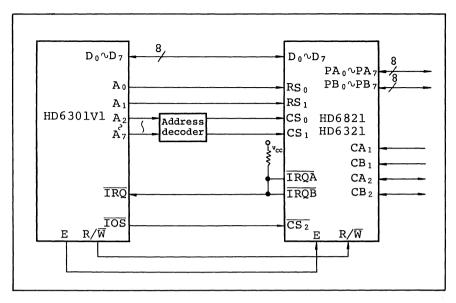

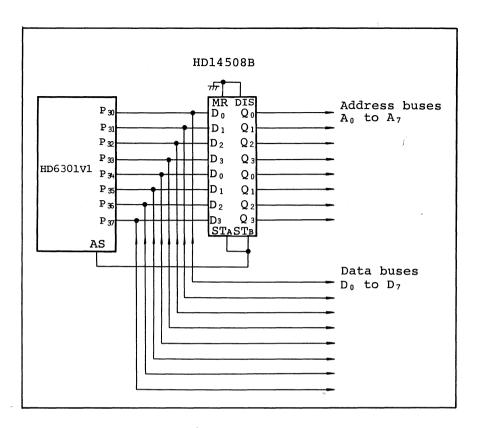

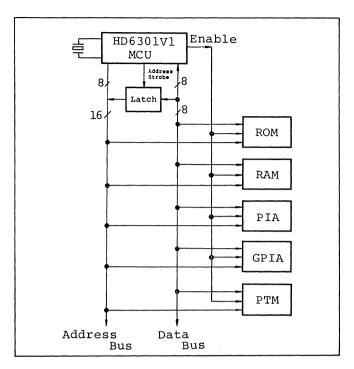

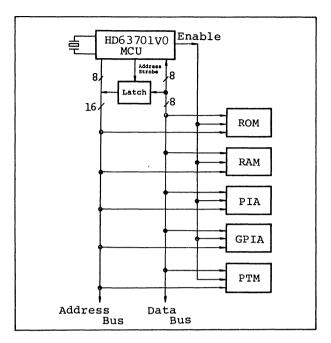

| 6.1 Use of External Expanded Mode                                    | 191  |

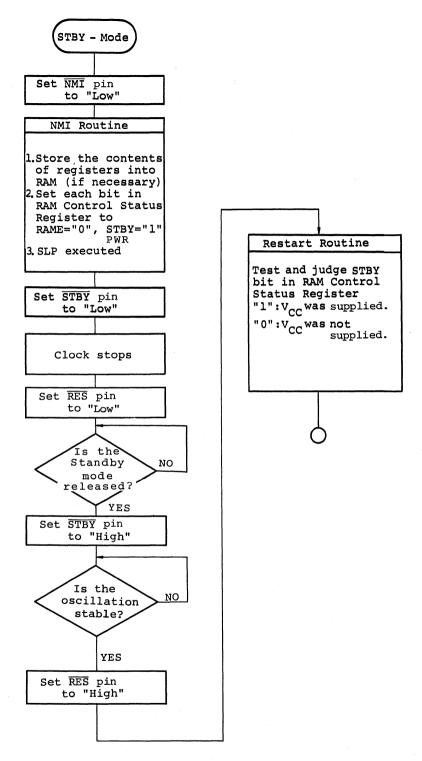

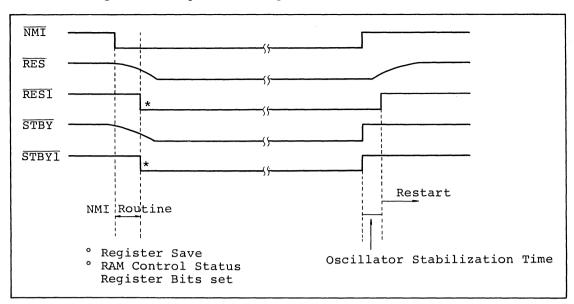

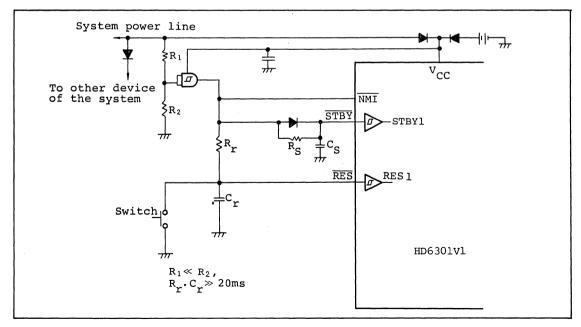

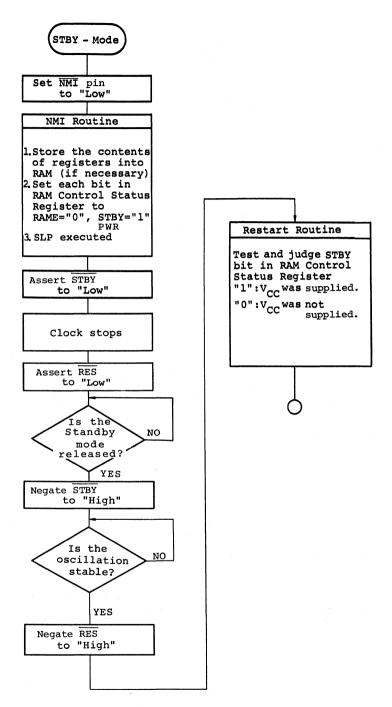

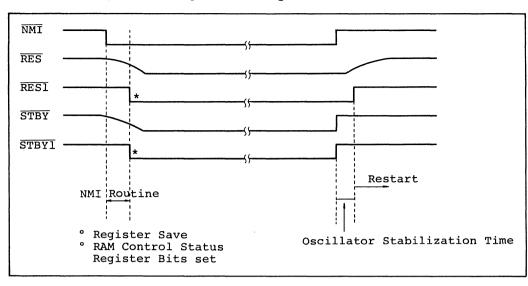

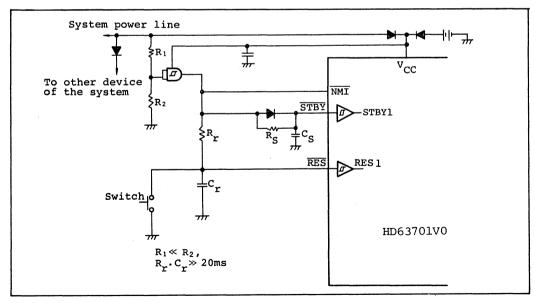

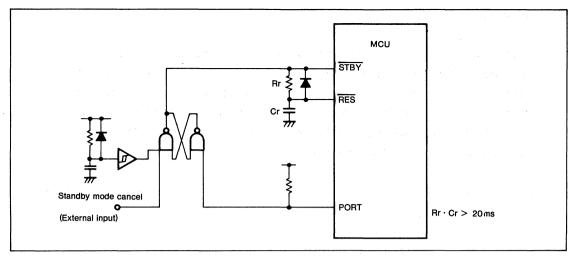

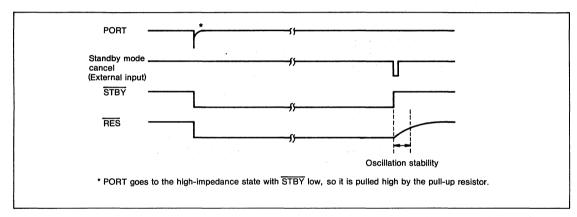

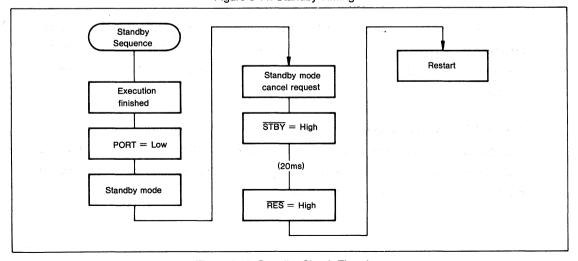

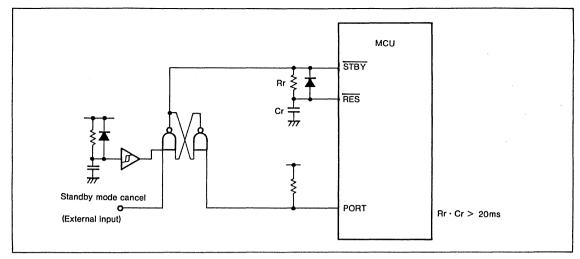

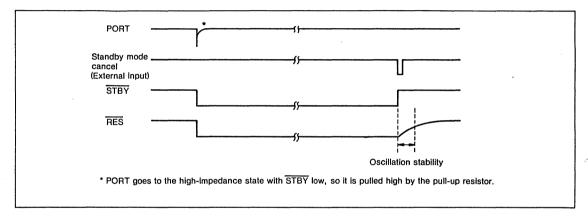

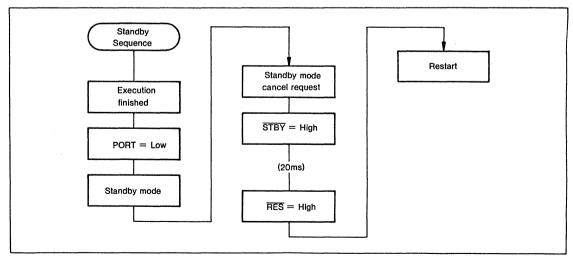

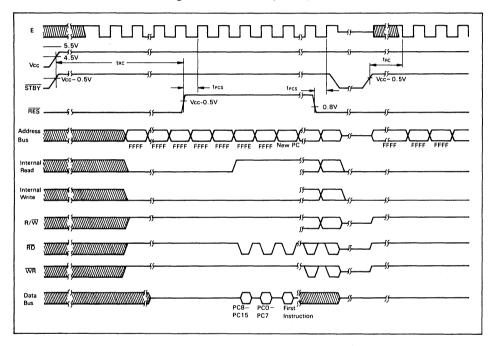

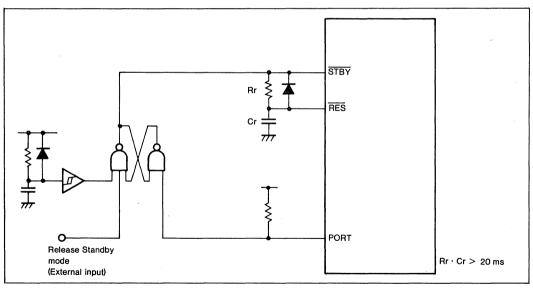

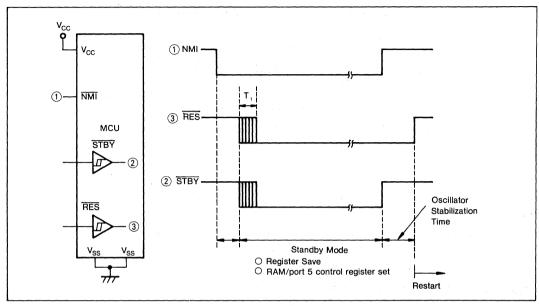

| 6.2 Standby Mode                                                     | 195  |

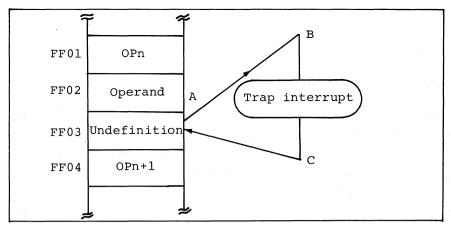

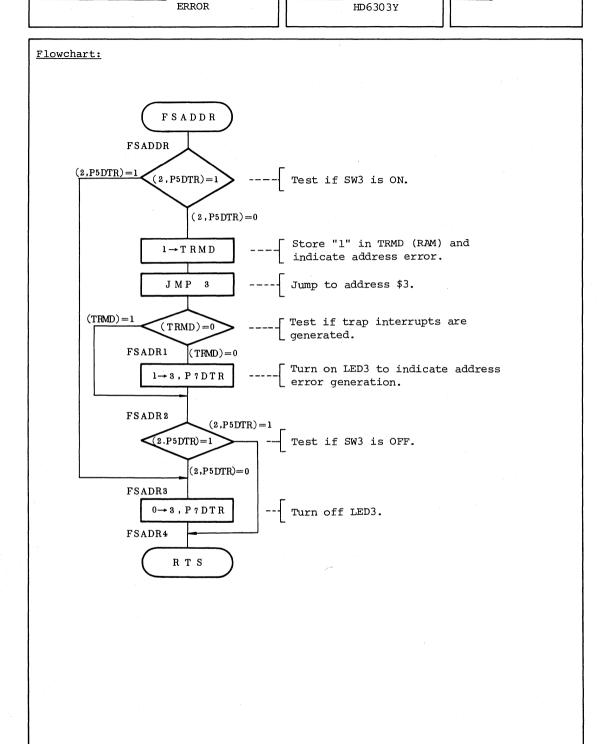

| 6.3 Address Trap, OP-Code Trap Application                           | 198  |

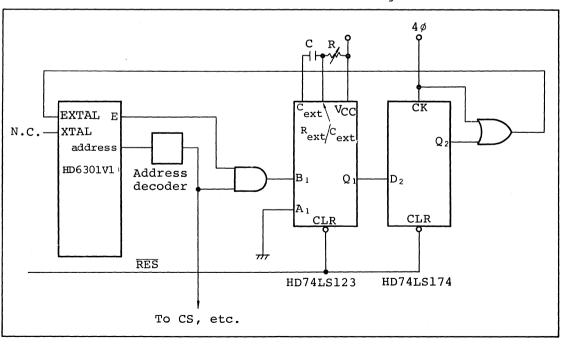

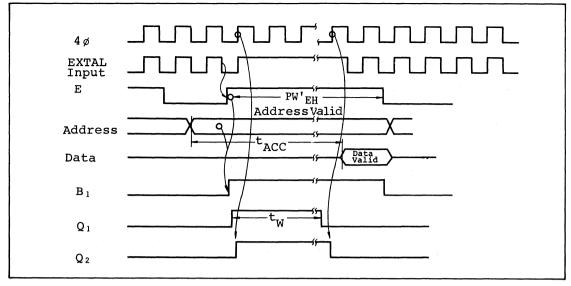

| 6.4 Slow Memory Interface                                            | 199  |

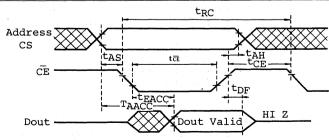

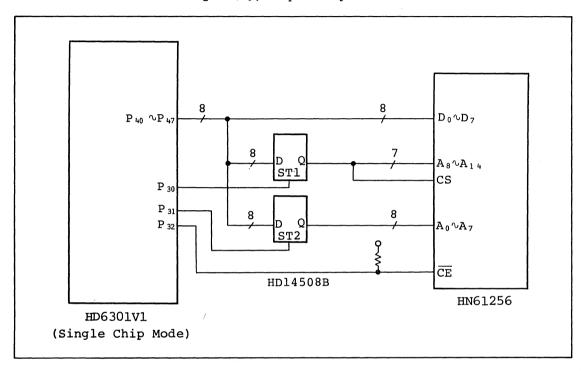

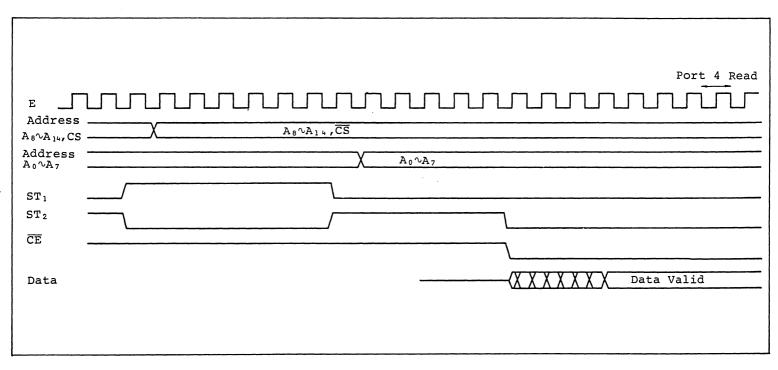

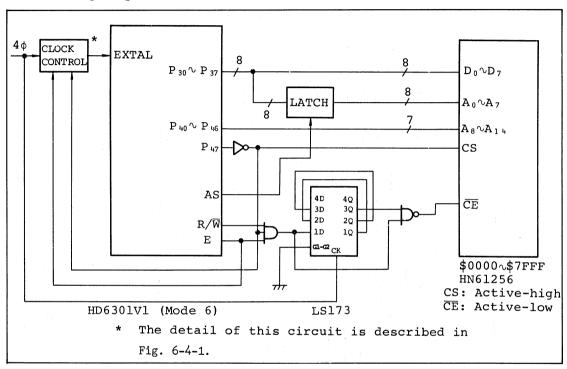

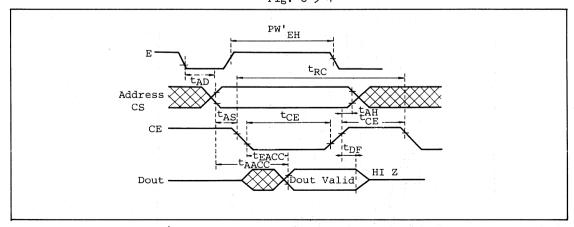

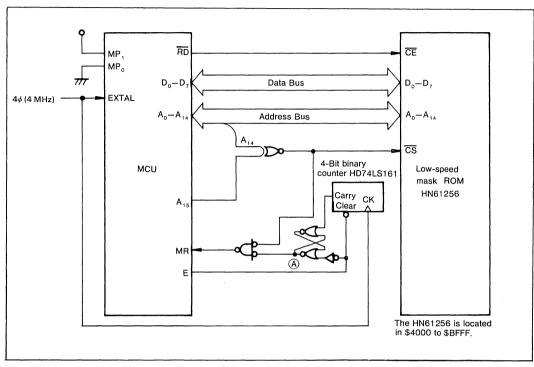

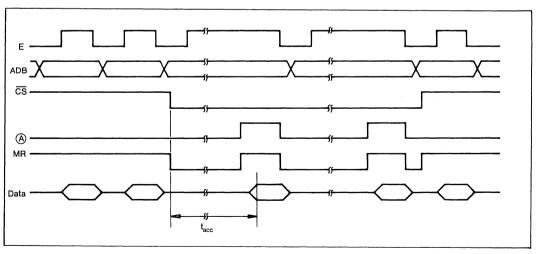

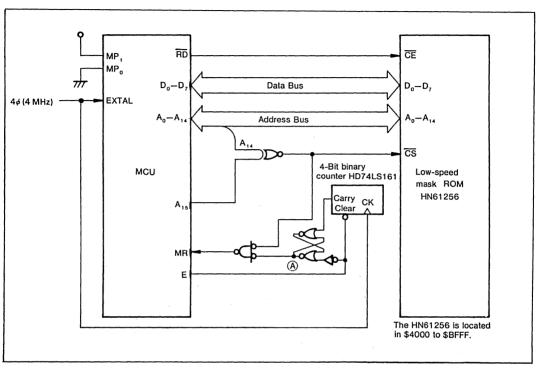

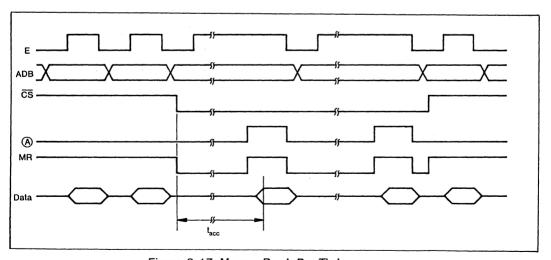

| 6.5 Interface to HN61256                                             | 200  |

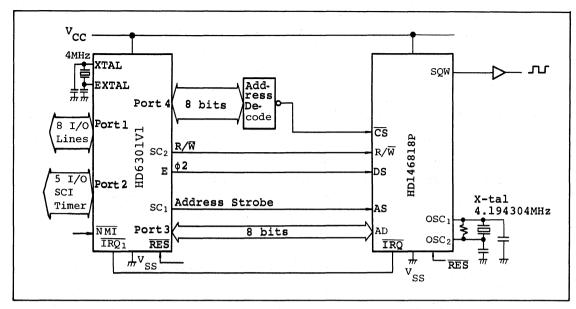

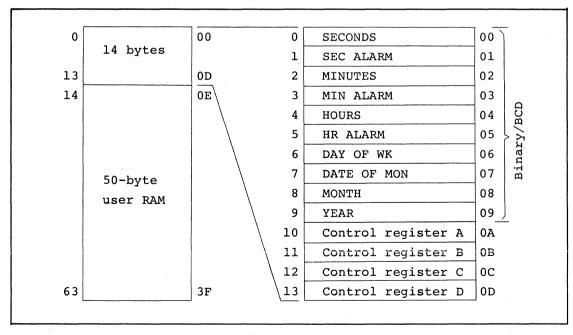

| 6.6 Interface to the Realtime Clock (HD146818)                       | 205  |

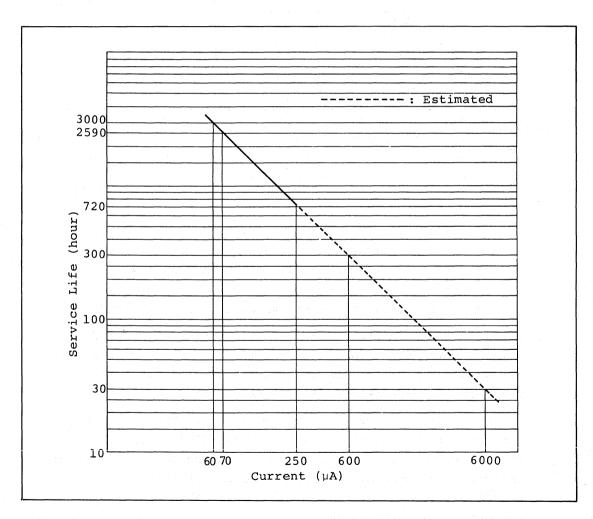

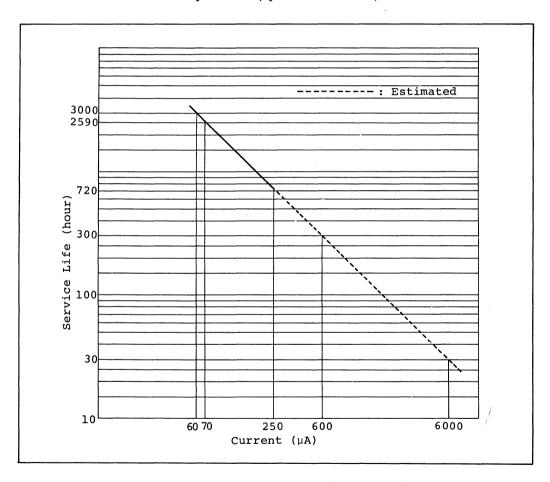

| 6.7 Reference Data of Battery Service Life                           | 208  |

|                                                                      |      |

| 7. PRECAUTIONS                                                       | 209  |

| 7.1 Write-Only Register                                              | 209  |

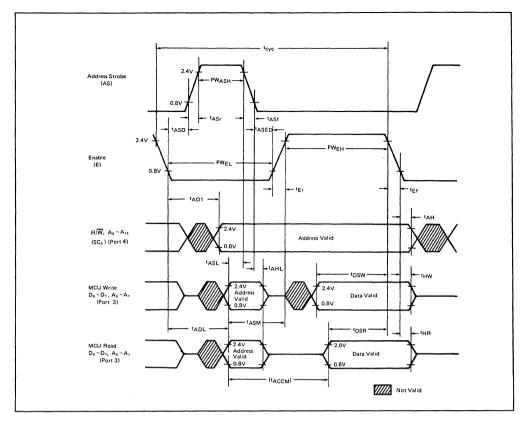

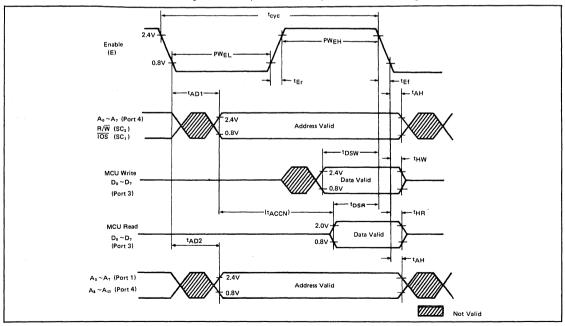

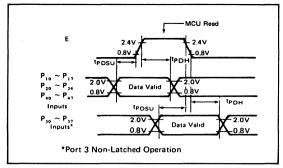

| 7.2 Address Strobe (AS)                                              | 209  |

| 7.3 Mode 0                                                           | 209  |

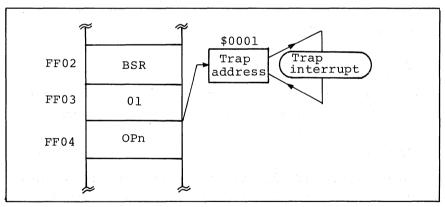

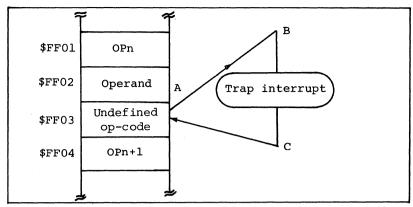

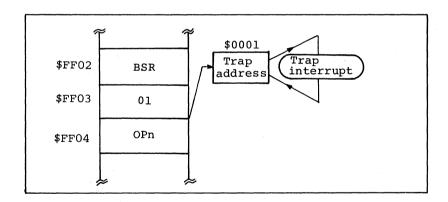

| 7.4 Trap Interrupt                                                   | 209  |

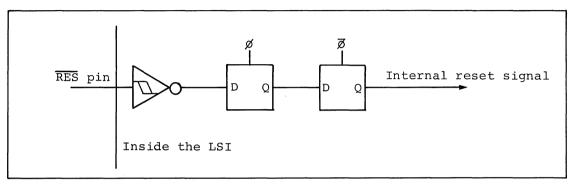

| 7.5 Power-on Reset                                                   | 211  |

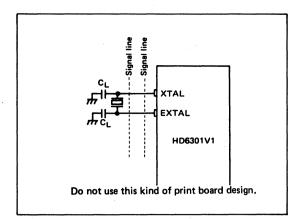

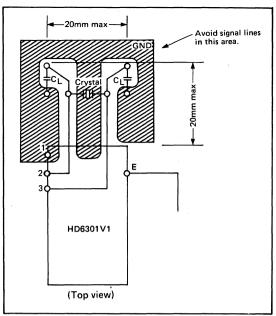

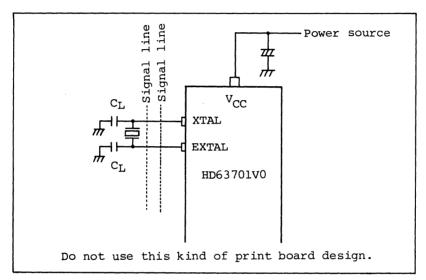

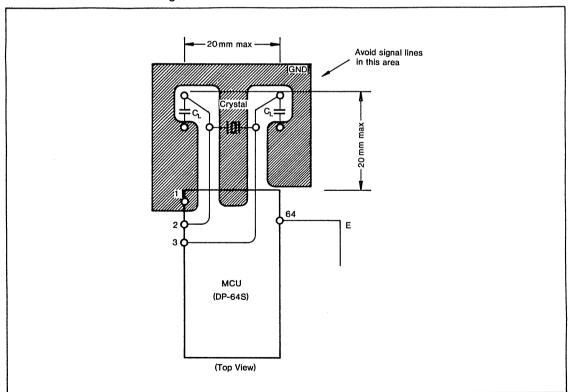

| 7.6 Precaution to the Board Design of Oscillation Circuit            | 211  |

| 7.7 Application Note for High Speed System Design Using the HD6301V1 | 212  |

| APPENDIX                                                             |      |

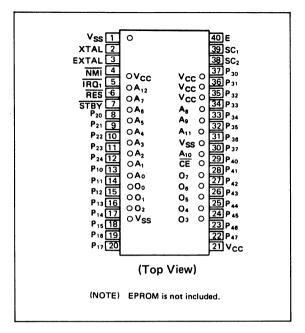

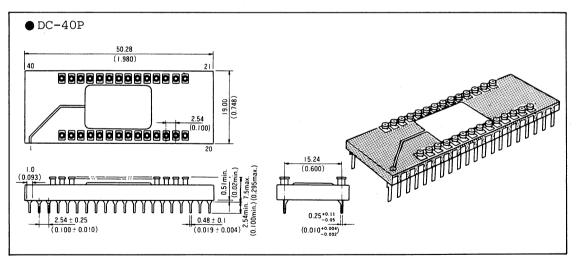

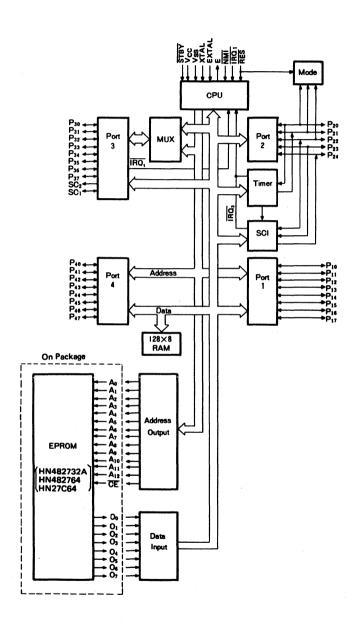

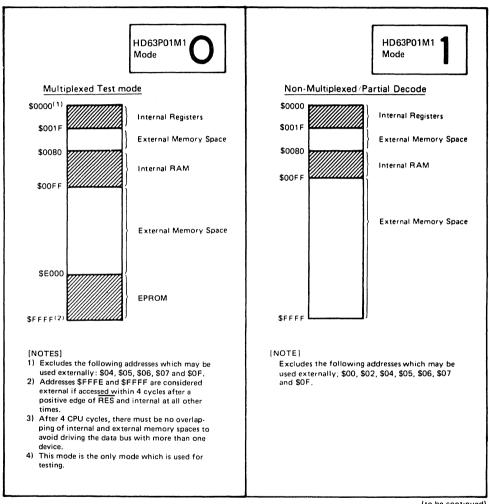

| I. EPROM on Package HD63P01M1                                        | 218  |

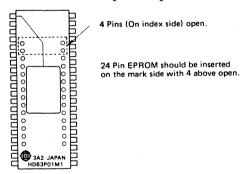

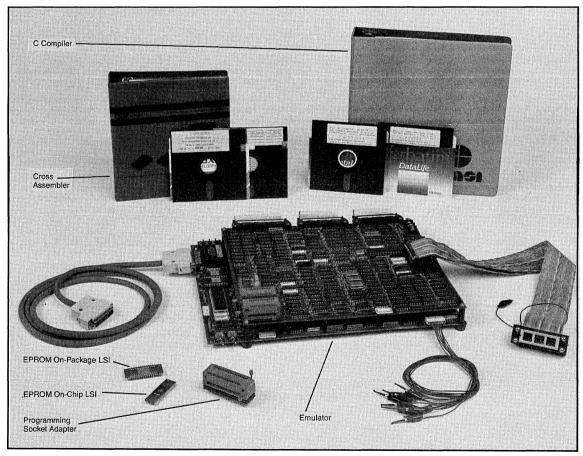

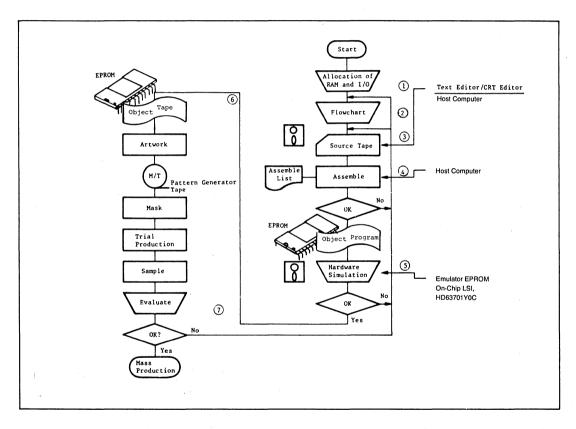

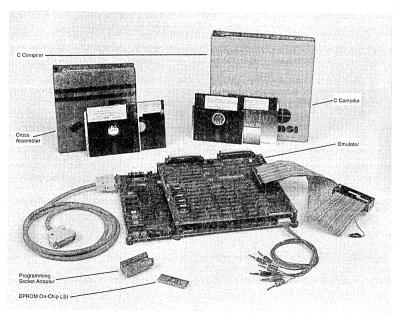

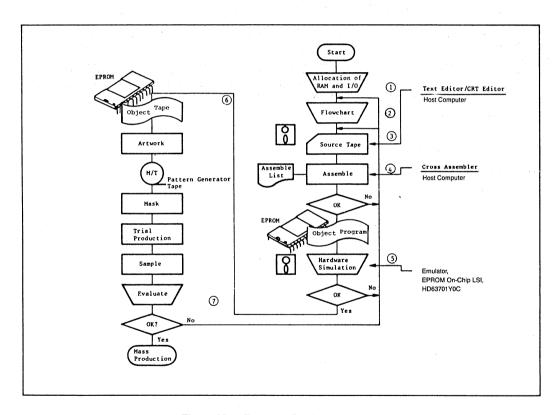

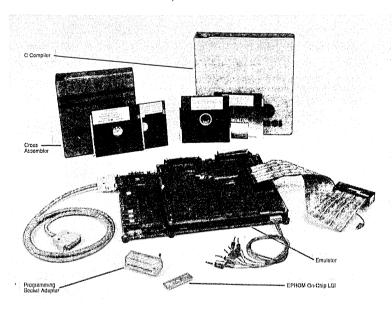

| II. Program Development Procedure and Support System                 | 226  |

| III. Q&A                                                             | 233  |

|                                                                      |      |

| Section 4                                                            |      |

| HD63701V User's Manual                                               | Page |

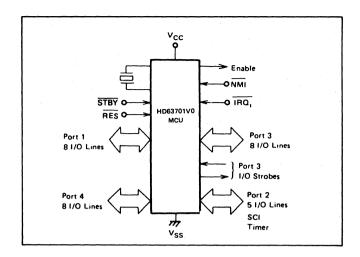

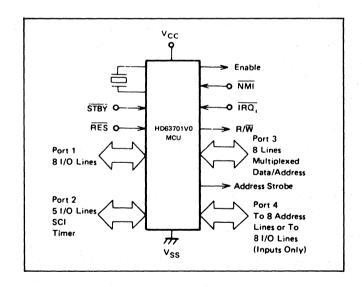

| 1. OVERVIEW                                                          | 251  |

| 1.1 Features of HD63701V0                                            | 251  |

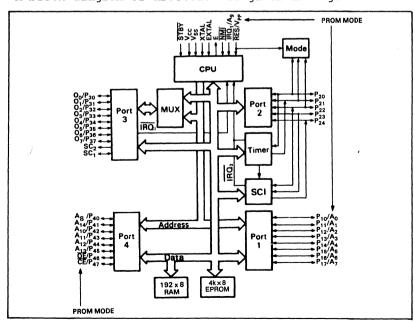

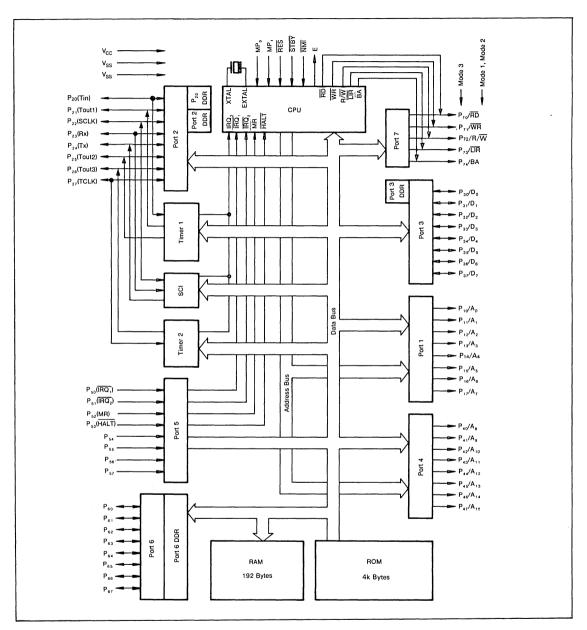

| 1.2 Block Diagram                                                    | 251  |

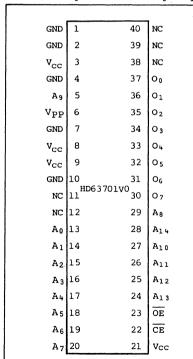

| 1.3 Functional Pin Description                                       | 252  |

| 2. IN | TERNAL ARCHITECTURE                                  | 253  |

|-------|------------------------------------------------------|------|

| 2.1   | Mode Selection                                       | 253  |

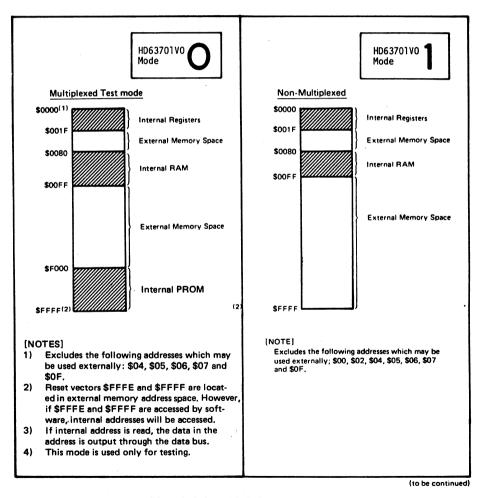

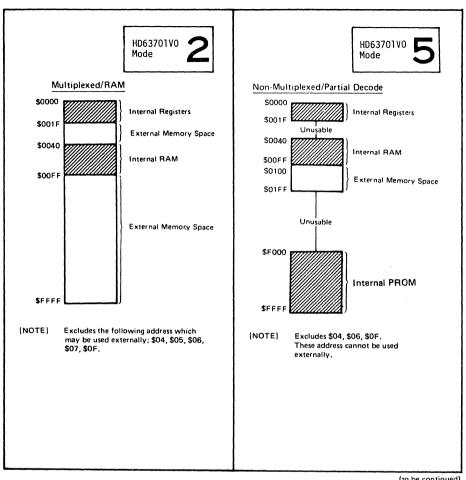

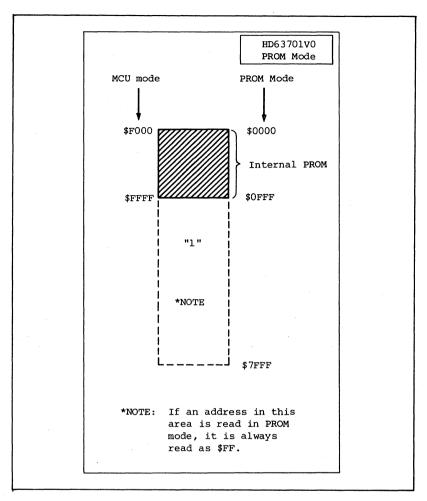

| 2.2   | Memory Map                                           | 258  |

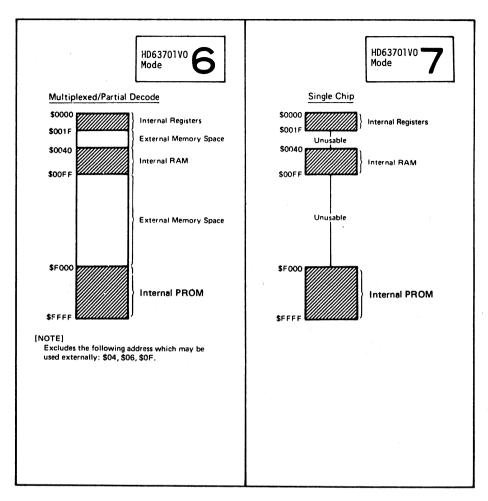

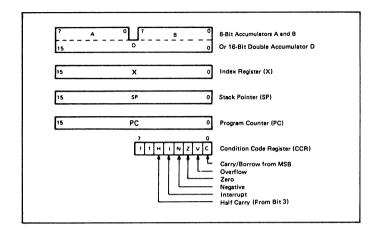

| 2.3   | CPU Registers                                        | .263 |

| 2.4   | Ports                                                | 265  |

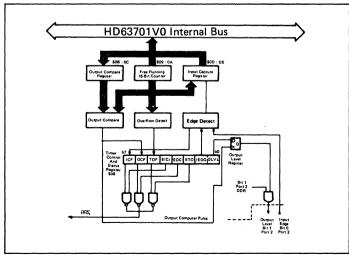

| 2.5   | Timer                                                | 269  |

| 2.6   | Serial Communication Interface                       | 273  |

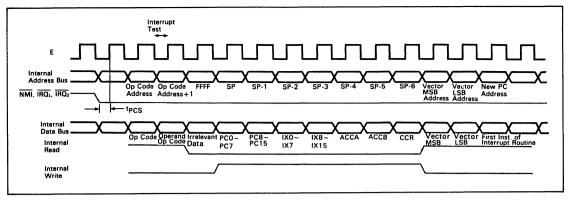

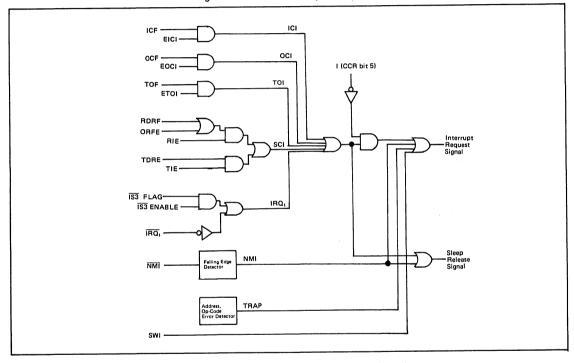

| 2.7   | Interrupts                                           | 281  |

| 2.8   | Reset                                                | 283  |

| 2.9   | Oscillator                                           | 285  |

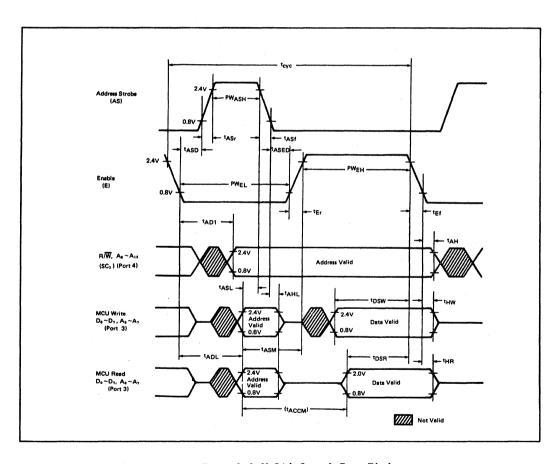

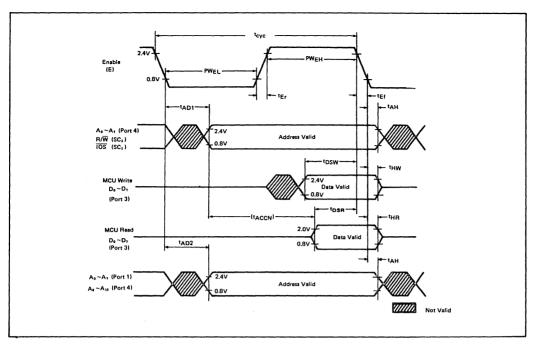

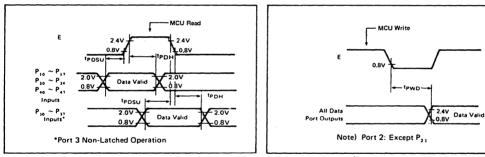

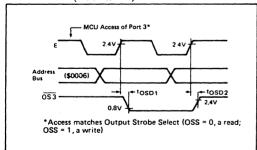

| 2.10  | Strobe Signals                                       | 286  |

| 2.11  | RAM Control Register                                 | 287  |

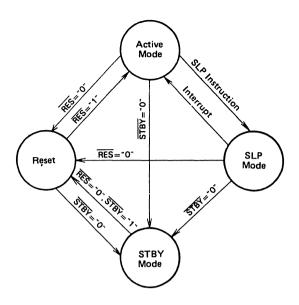

| 2.12  | Low Power Consumption Mode                           | 287  |

| 2.13  | TRAP Function                                        | 292  |

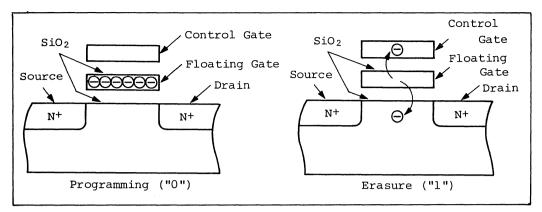

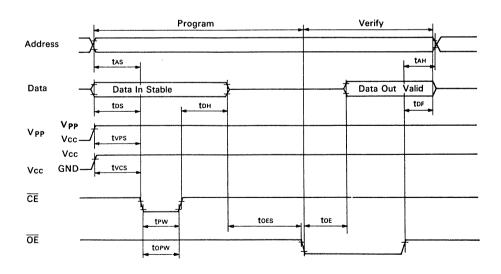

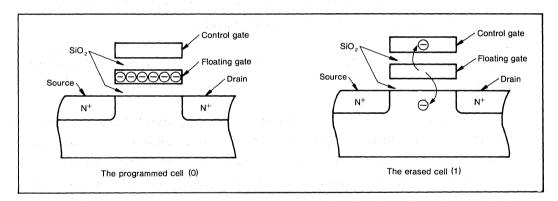

| 3. EF | PROM (PROM) PROGRAMMING AND TECHNICAL SPECIFICATIONS | 293  |

| 3.1   | PROM Mode                                            | 293  |

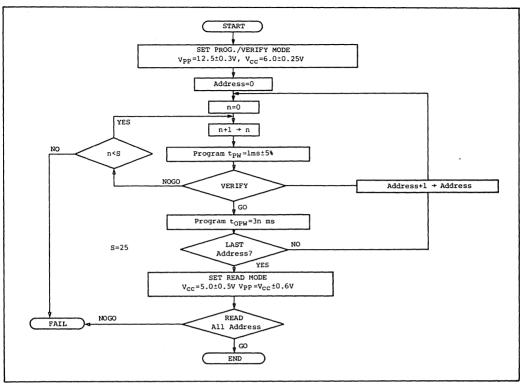

| 3.2   | Programming/Verification                             | 294  |

| 3.3   | Erasure                                              | 295  |

| 3.4   | On-Chip PROM Characteristics and Application         | 296  |

| 3.5   | Instruction Set Overview                             | 300  |

| 3.6   | Addressing Modes                                     | 300  |

| 3.7   | Instruction Set                                      | 302  |

| 3.8   | Instruction Execution Cycles                         | 307  |

| 3.9   | System Flowchart                                     | 313  |

| 3.10  | Pin Arrangement and Package Information              | 315  |

| 3.11  | Electrical Characteristics                           | 316  |

|       |                                                      | 0.0  |

|       | PPLICATIONS                                          | 322  |

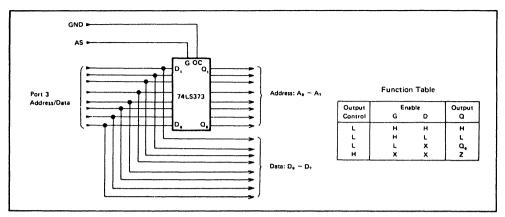

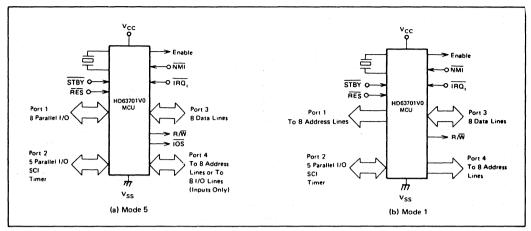

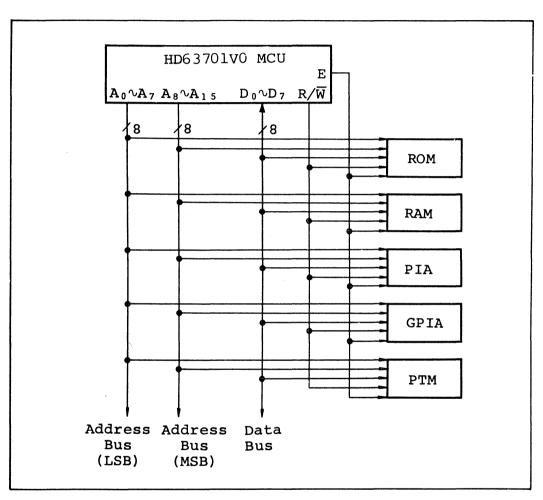

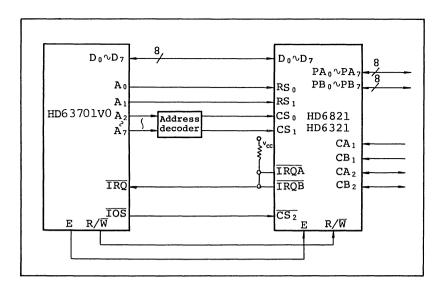

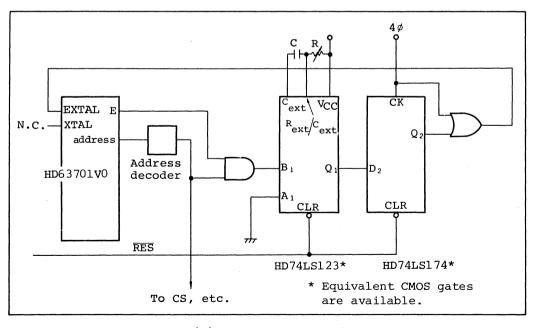

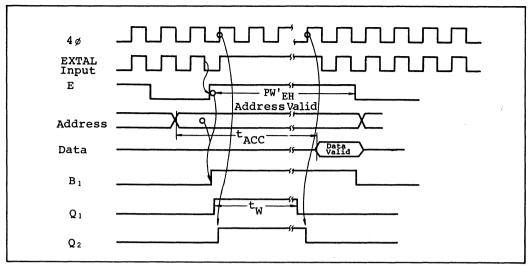

| 4.1   | Use of External Expanded Mode                        | 322  |

| 4.2   | Standby Mode                                         | 327  |

| 4.3   | Address Trap, OP-Code Trap Application               | 330  |

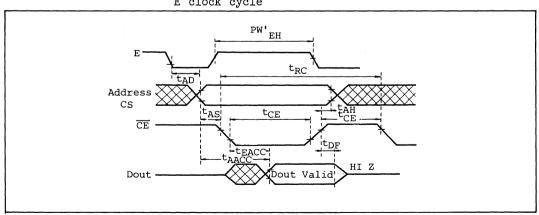

| 4.4   | Slow Memory Interface                                | 331  |

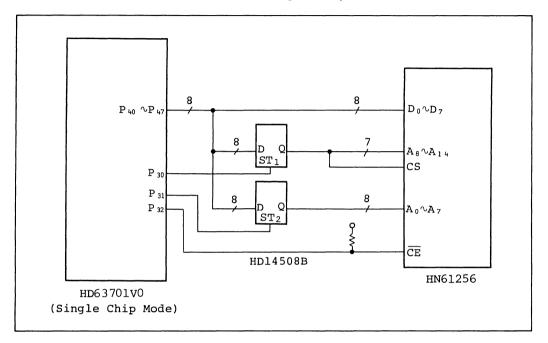

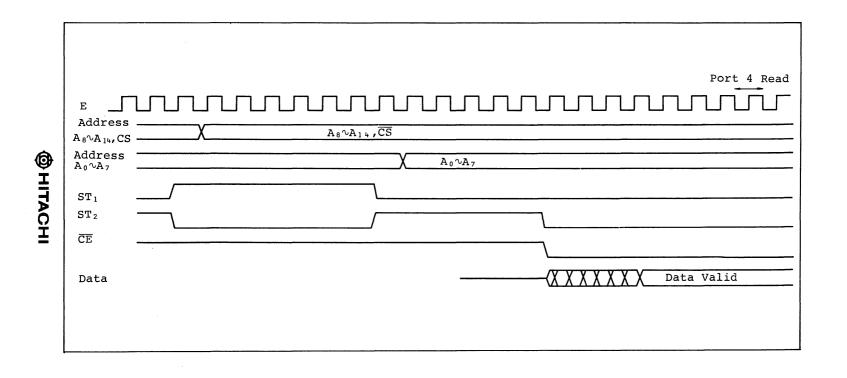

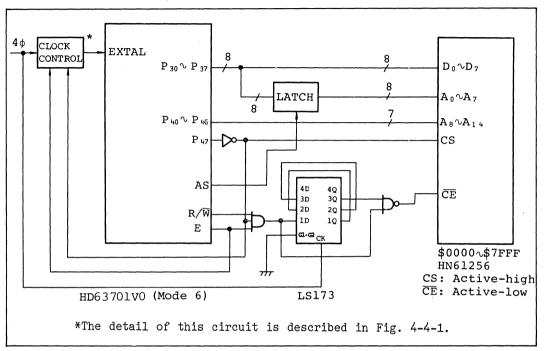

| 4.5   | Interface to HN61256                                 | 332  |

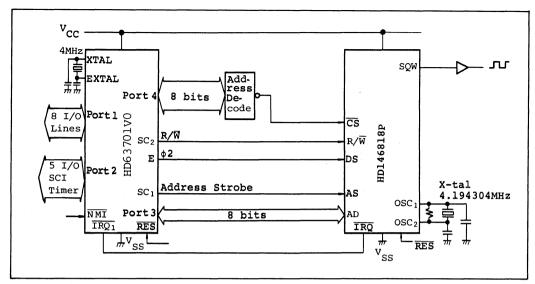

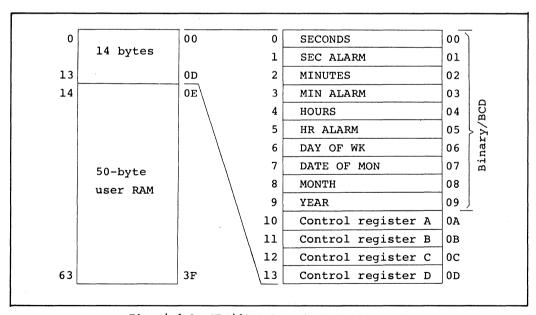

| 4.6   | Interface to the Realtime Clock (HD146818)           | 337  |

| 4.7   | Reference Data of Battery Service Life               | 340  |

| 5. PF | RECAUTIONS                                           | 341  |

| 5.1   | Write Only Register                                  | 341  |

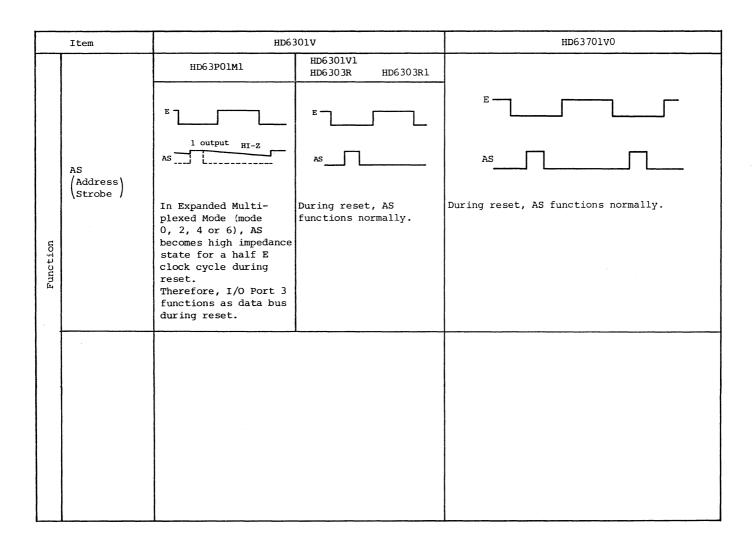

| 5.2   | Address Strobe (AS)                                  | 341  |

| 5.3   | Mode 0                                               | 341  |

| 5.4   | Trap Interrupt                                       | 341  |

| 5.5    | Precaution to the Board Design of Oscillation Circuit               | 343  |

|--------|---------------------------------------------------------------------|------|

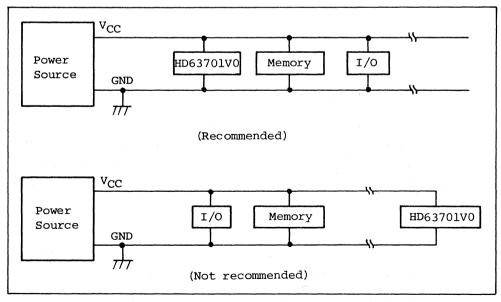

| 5.6    | Application Note for High Speed System Design Using the HD63701V0 . | 343  |

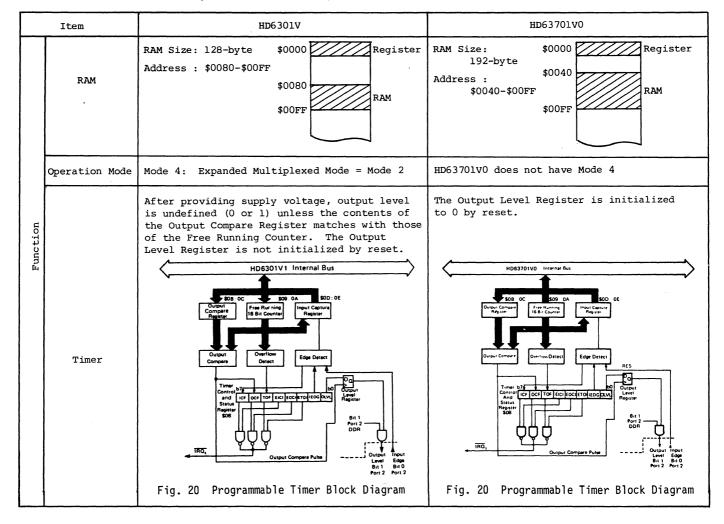

| 5.7    | Differences between HD6301V and HD63701V                            | 347  |

| APPEN  | INIX                                                                |      |

| 7.1    | Support Tools                                                       | 353  |

| II.    | Q & A                                                               | 355  |

|        |                                                                     |      |

| Sectio |                                                                     |      |

|        | 11 3<br>11 X0/HD6303 X/HD63701 X0 User's Manual                     | Page |

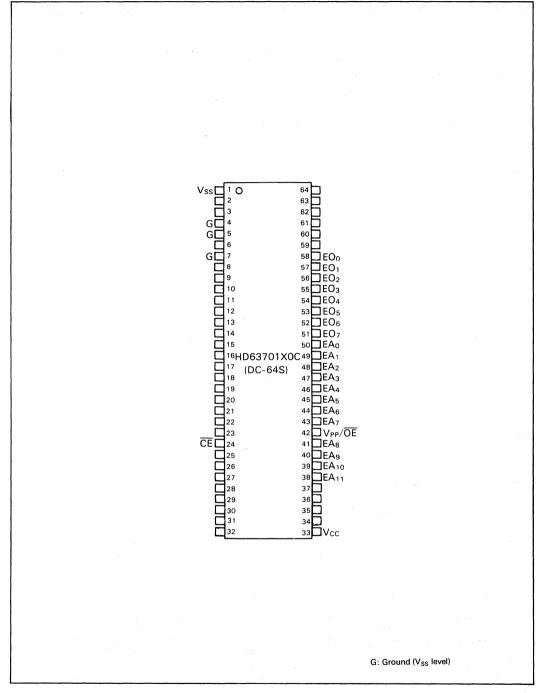

| 1 OV   | ERVIEW                                                              | 375  |

| 1.1    | Features                                                            | 375  |

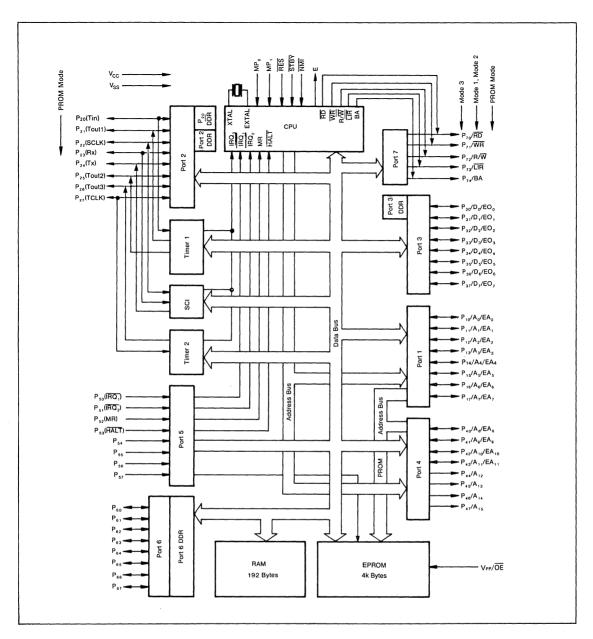

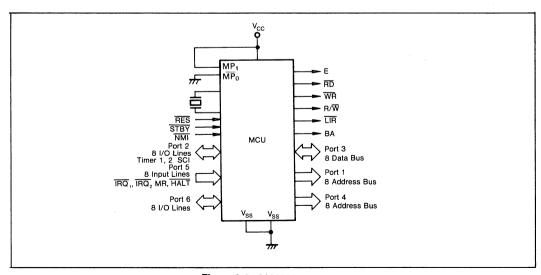

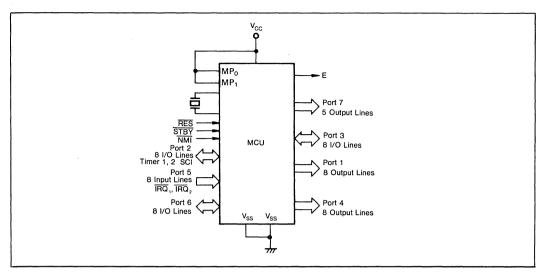

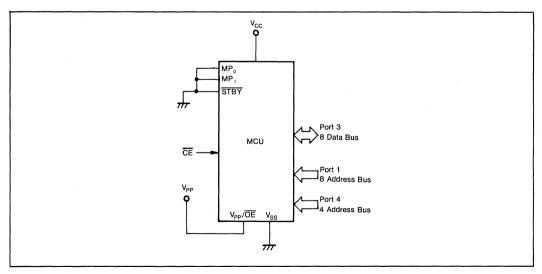

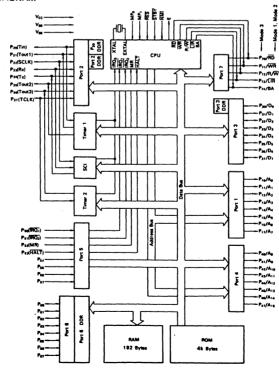

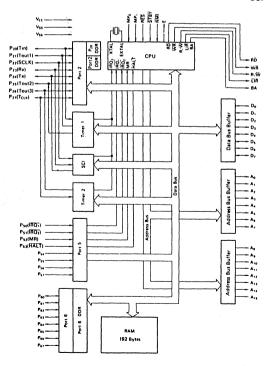

| 1.2    | Block Diagrams                                                      | 377  |

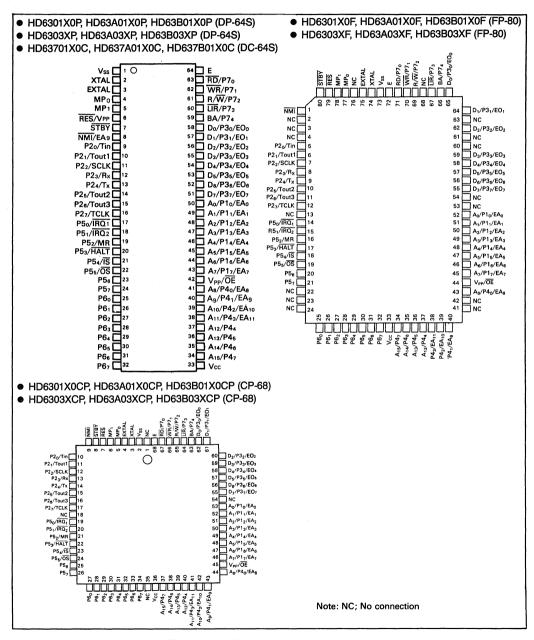

| 1.3    | Pin Description                                                     | 380  |

|        |                                                                     | 000  |

| 2. INT | TERNAL ARCHITECTURE AND OPERATION                                   | 383  |

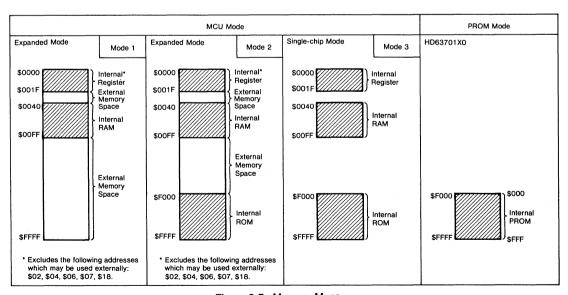

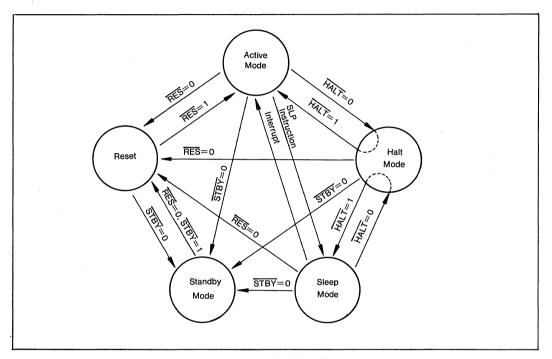

| 2.1    | Operation Modes                                                     | 383  |

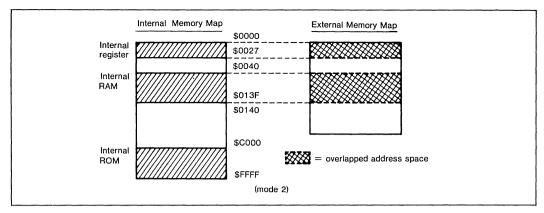

| 2.2    | Memory Map                                                          | 386  |

| 2.3    | Function Pin Description                                            | 388  |

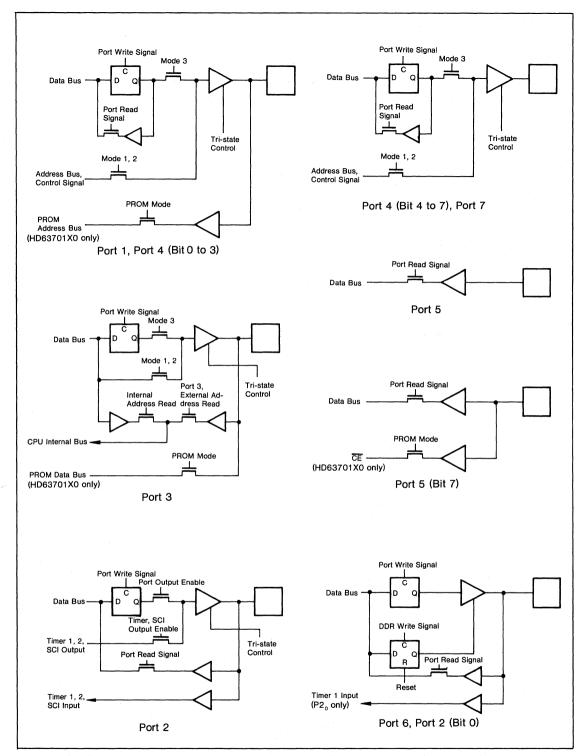

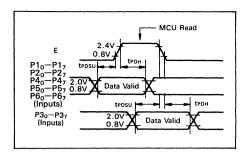

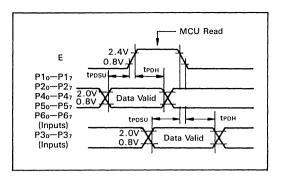

| 2.4    | Ports                                                               | 393  |

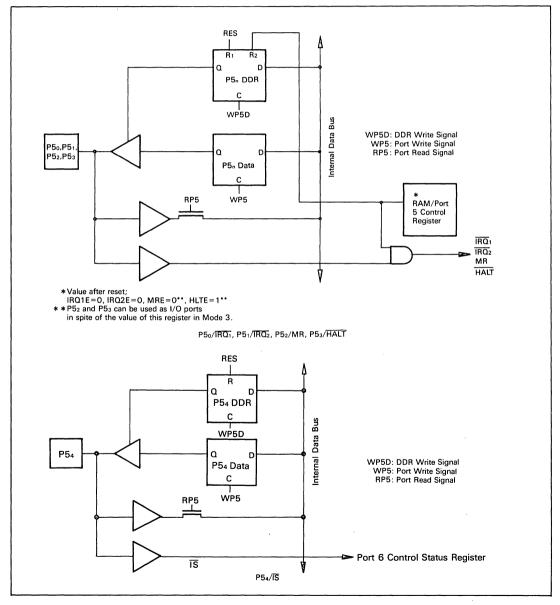

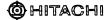

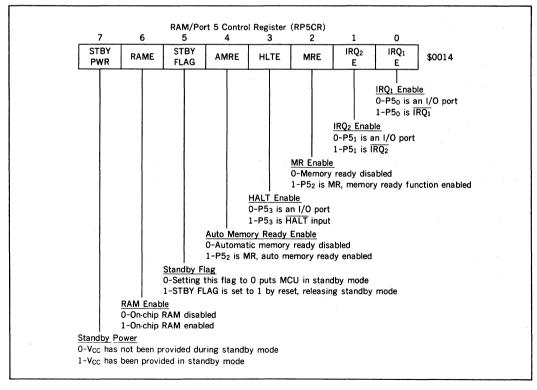

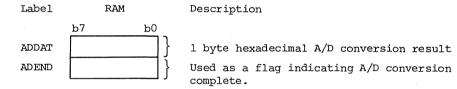

| 2.5    | RAM/Port 5 Control Register                                         | 397  |

| 3. CP  | U FUNCTION                                                          | 399  |

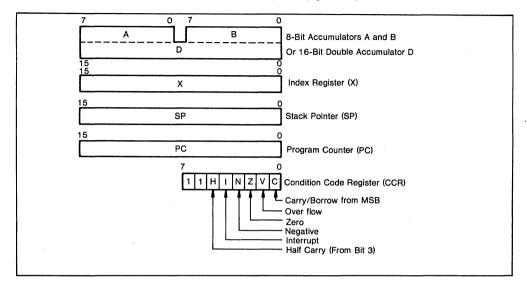

| 3.1    | CPU Registers                                                       | 399  |

| 3.2    | Addressing Modes                                                    | 400  |

| 3.3    | Instruction Set                                                     | 402  |

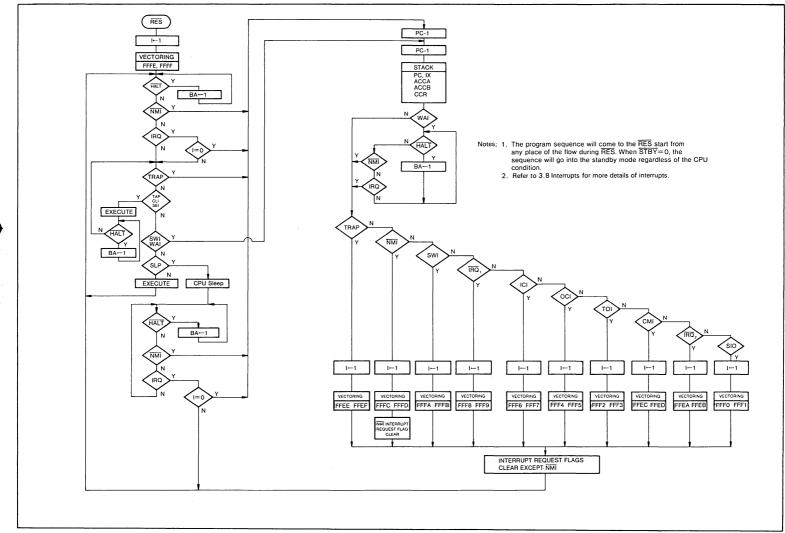

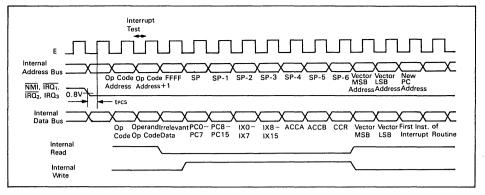

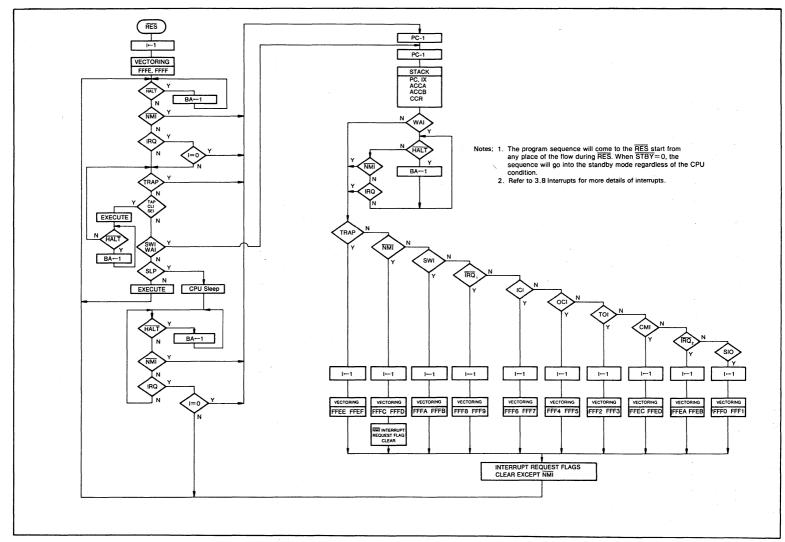

| 3.4    | CPU Instruction Flow.                                               | 408  |

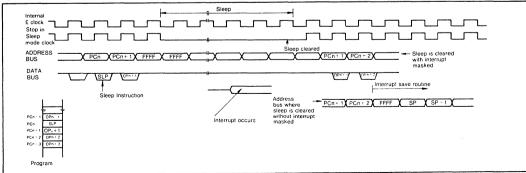

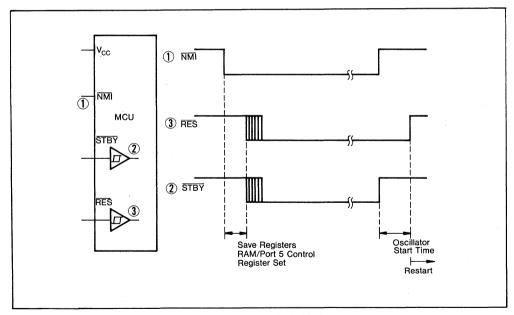

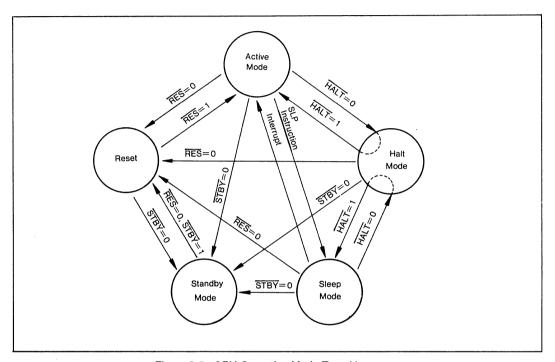

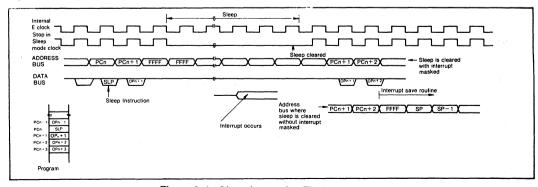

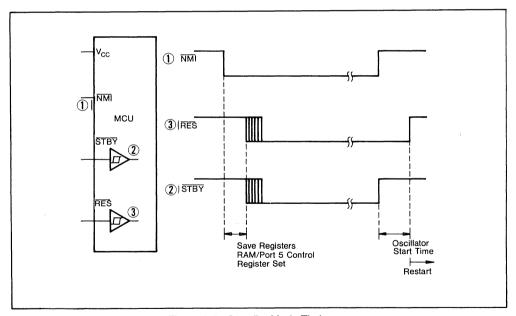

| 3.5    | Low Power Dissipation Modes                                         | 410  |

| 3.6    | Trap Function                                                       | 413  |

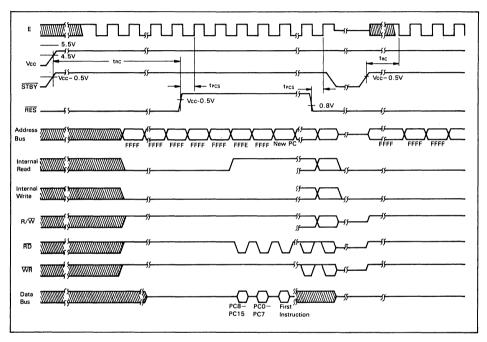

| 3.7    | Reset                                                               | 414  |

| 3.8    | Interrupts                                                          | 415  |

|        |                                                                     |      |

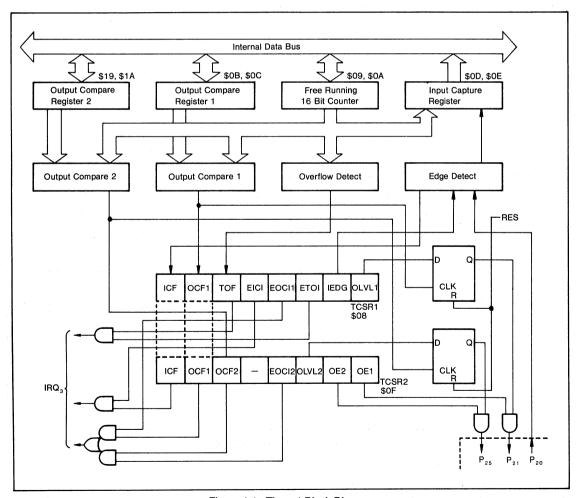

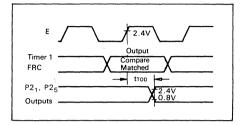

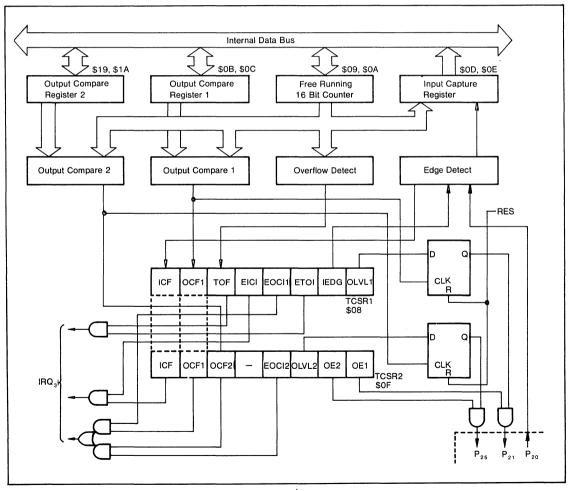

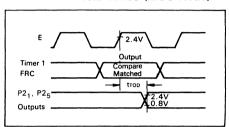

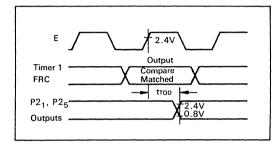

| 4. TIN | MER 1                                                               | 418  |

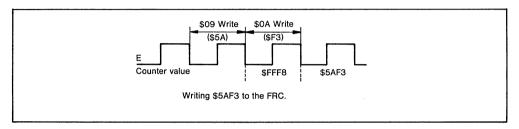

| 4.1    | Free-Running Counter (FRC)                                          | 419  |

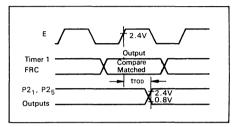

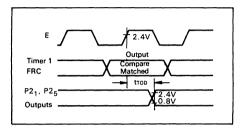

| 4.2    | Output Compare Registers (OCR)                                      | 419  |

| 4.3    | Input Compare Register (ICR)                                        | 420  |

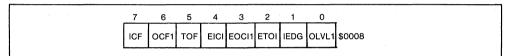

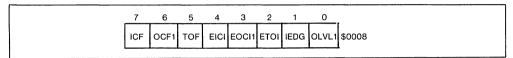

| 4.4    | Timer Control/Status Register 1 (TCSR1)                             | 420  |

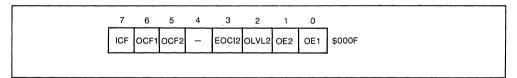

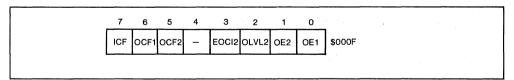

| 4.5    | Timer Control/Status Register 2 (TCSR2)                             | 421  |

| 4.6    | Timer Status Flags                                                  | 423  |

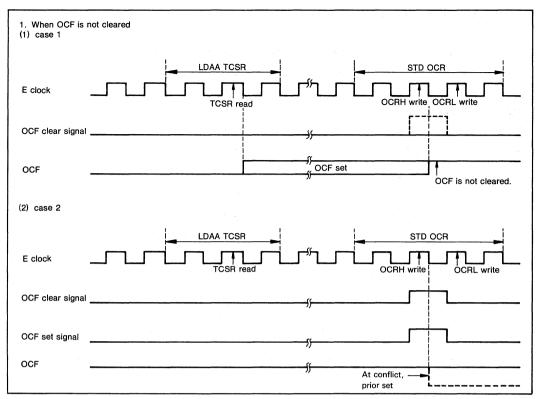

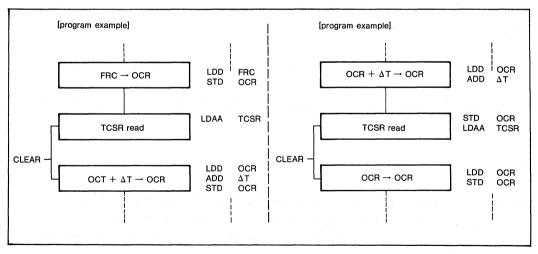

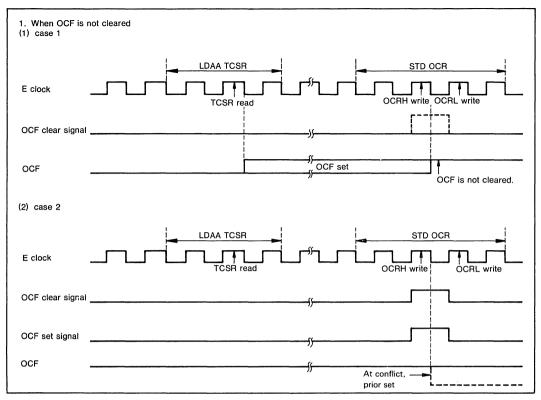

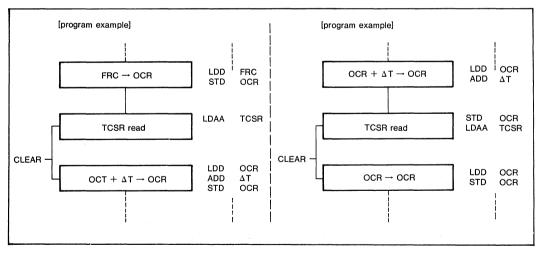

| 4.7    | Precautions on Cleaning the OCF                                     | 423  |

|        |                                                                     |      |

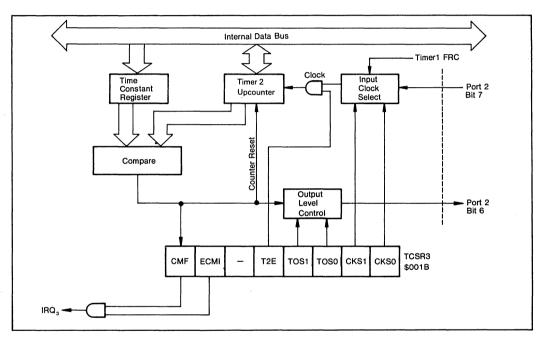

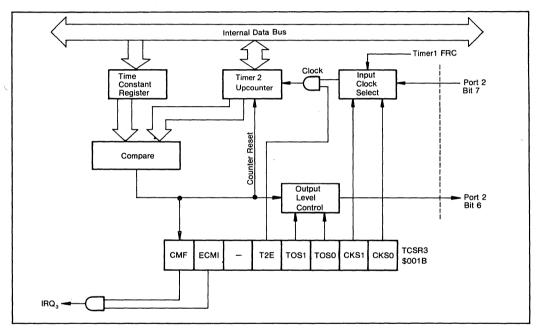

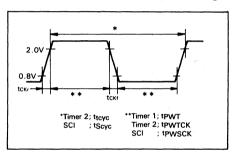

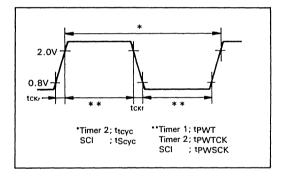

| 5. TIN | MER 2                                                           | 425 |

|--------|-----------------------------------------------------------------|-----|

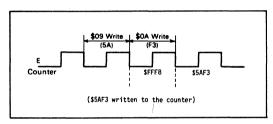

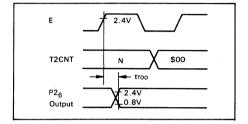

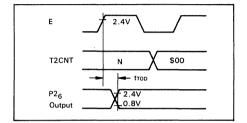

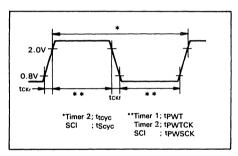

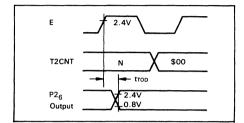

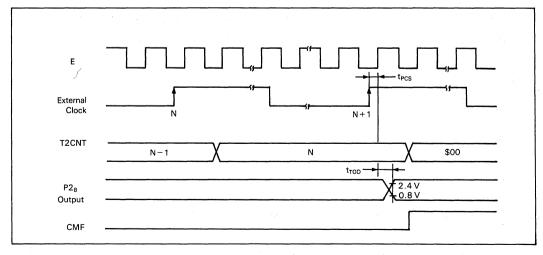

| 5.1    | Timer 2 Upcounter (T2CNT)                                       | 425 |

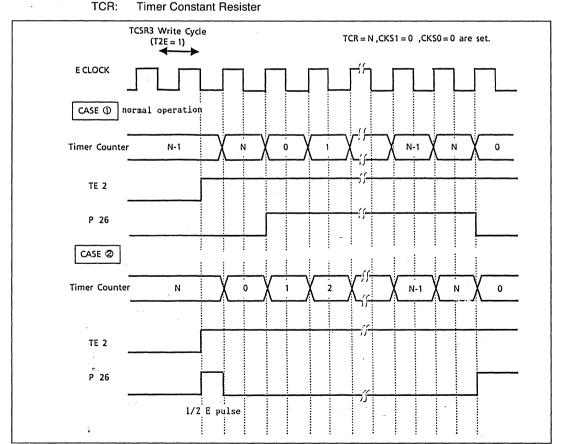

| 5.2    | Timer Constant Register (TCONR)                                 | 426 |

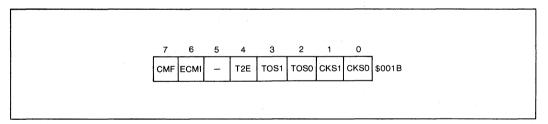

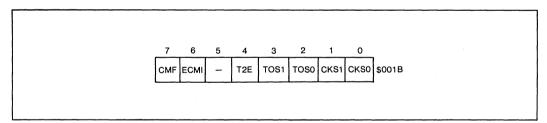

| 5.3    | Timer Control/Status Register 3 (TCSR3)                         | 426 |

| 5.4    | Timer Status Flags                                              | 428 |

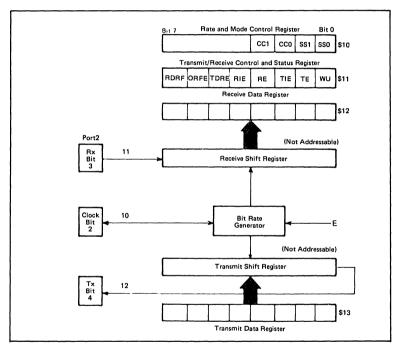

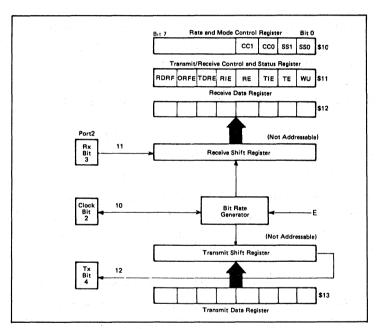

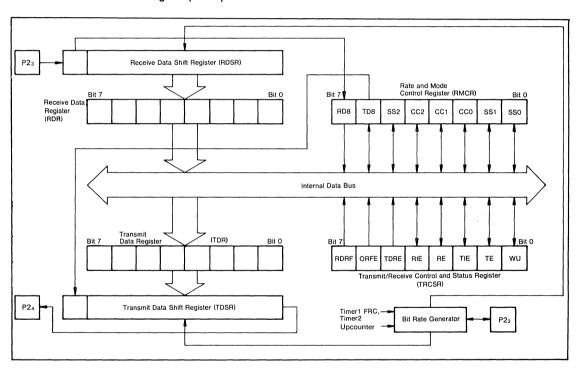

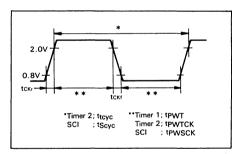

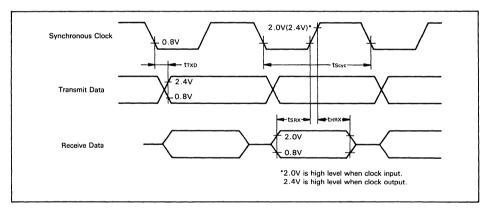

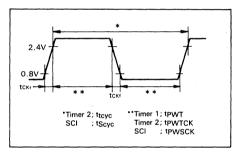

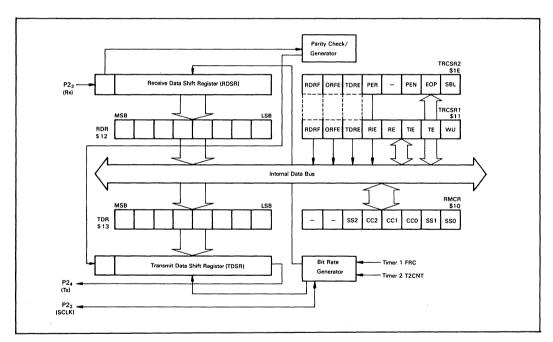

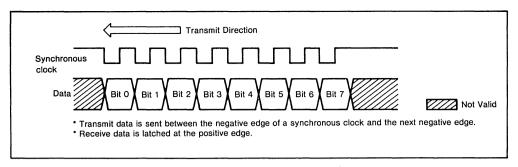

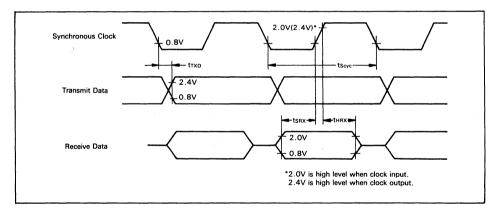

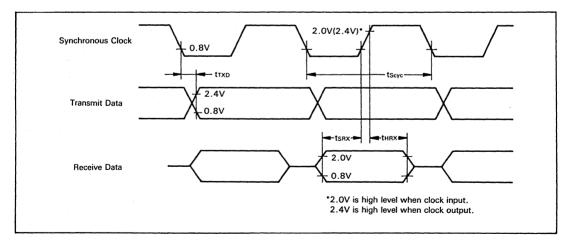

| 6. SE  | RIAL COMMUNICATIONS INTERFACE                                   | 429 |

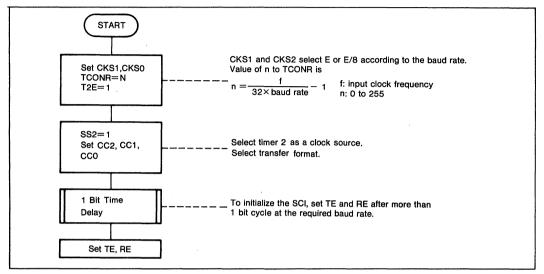

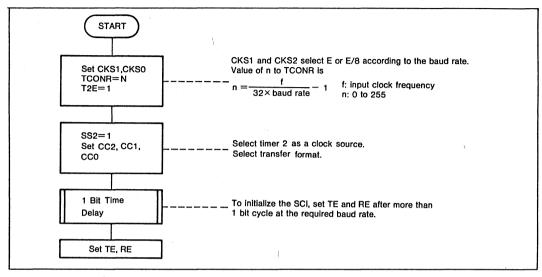

| 6.1    | Initialization                                                  | 429 |

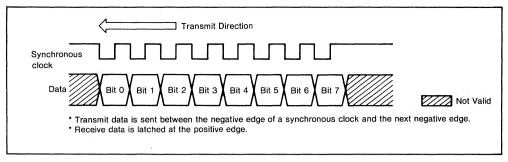

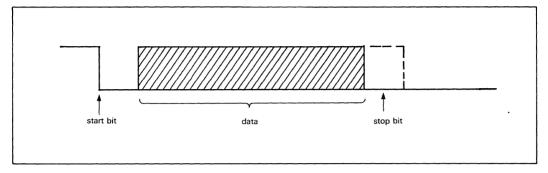

| 6.2    | Asynchronous Mode                                               | 430 |

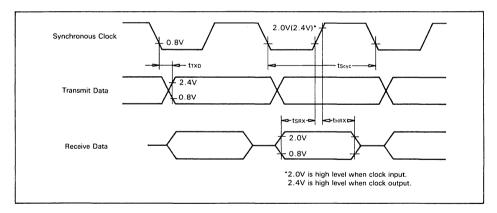

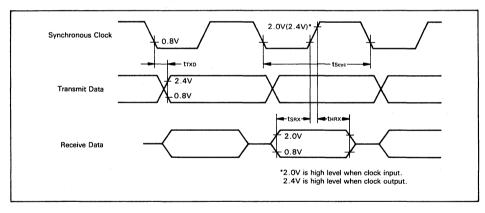

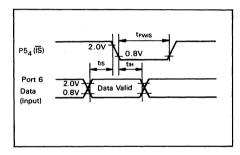

| 6.3    | Clock Synchronous Mode                                          | 431 |

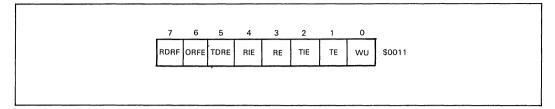

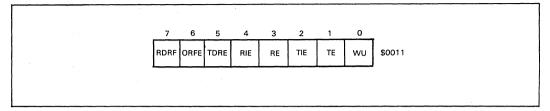

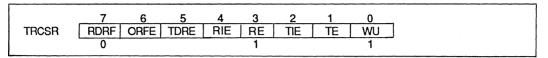

| 6.4    | Transmit/Receive Control Status Register (TRCSR)                | 433 |

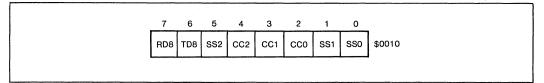

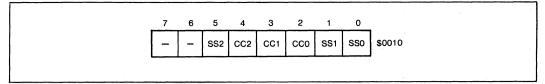

| 6.5    | Transmit Rate/Mode Control Register (RMCR)                      | 434 |

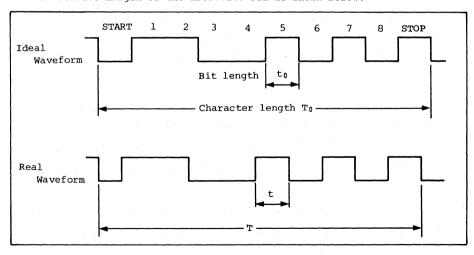

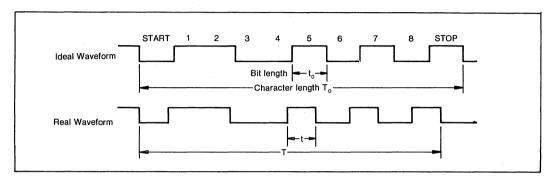

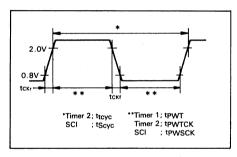

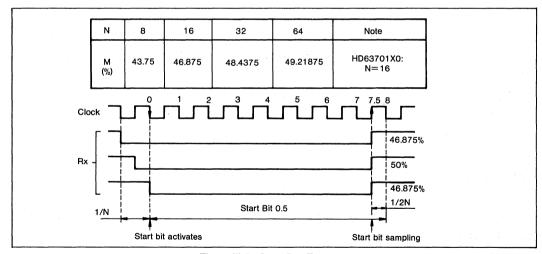

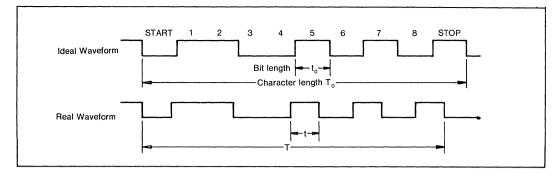

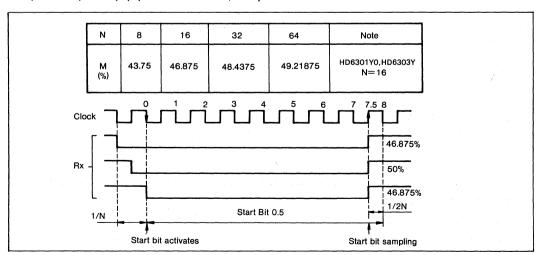

| 6.6    | SCI Receiving Margin                                            | 438 |

| 6.7    | Timer, SCI Status Flags                                         | 438 |

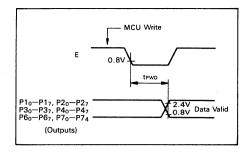

| 6.8    | Precaution for Clock-Synchronous Serial Communication Interface | 439 |

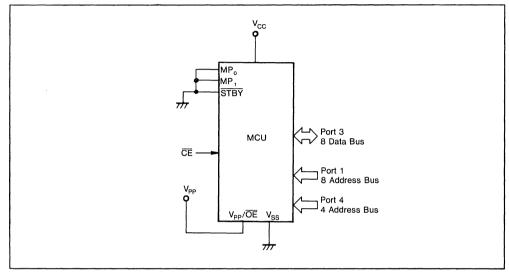

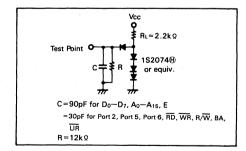

| 7. HC  | 063701X0 PROGRAMMABLE ROM (EPROM)                               | 441 |

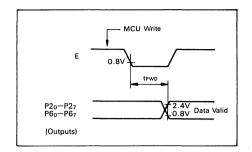

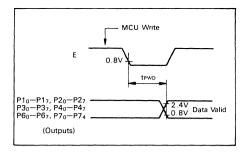

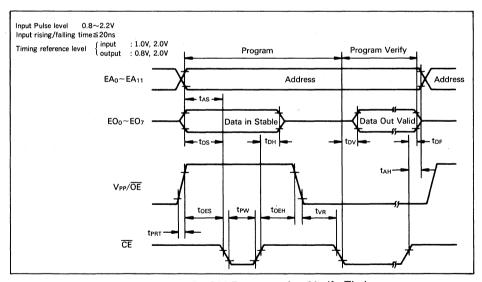

| 7.1    | Programming and Verification                                    | 443 |

| 7.2    | Erasing (Window Package)                                        | 444 |

| 7.3    | Characteristics and Applications                                | 444 |

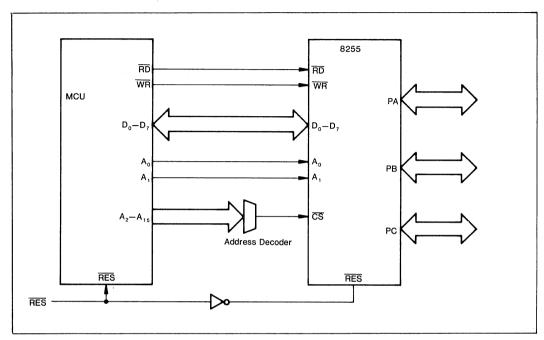

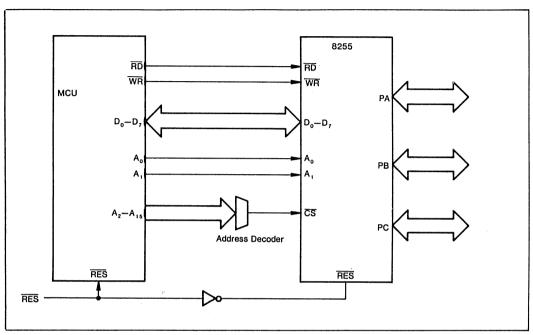

| 8. AP  | PLICATIONS                                                      | 447 |

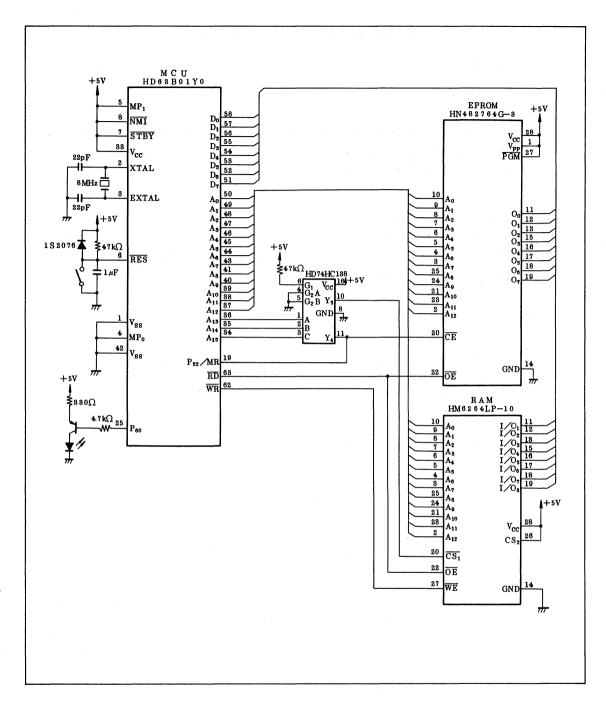

| 8.1    | HD6301X0 or HD63701X0 in Expanded Mode                          | 447 |

| 8.2    | HD6301X0 or HD63701X0 in Single-Chip Mode                       | 448 |

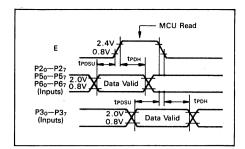

| 8.3    | Timer Applications                                              | 448 |

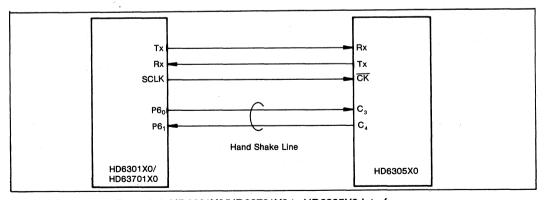

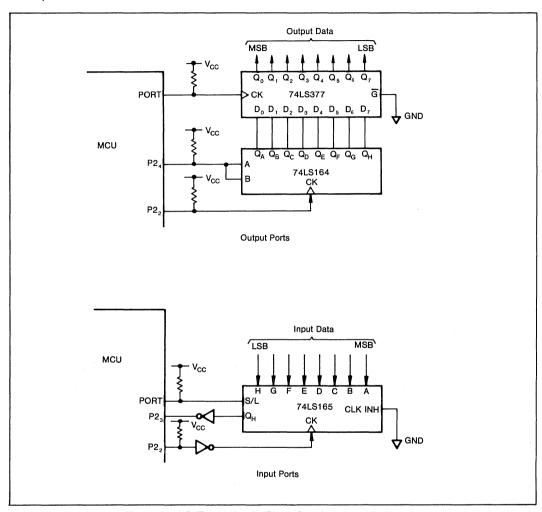

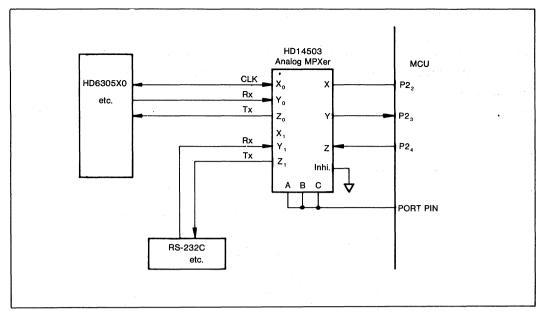

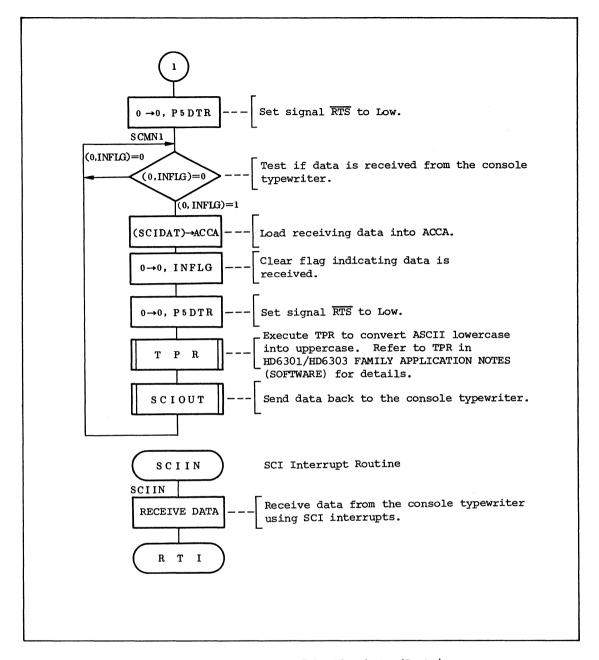

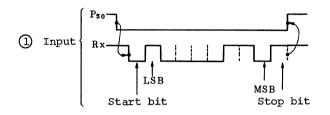

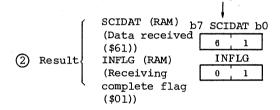

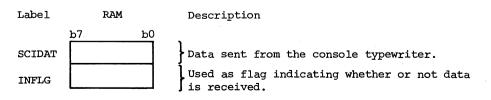

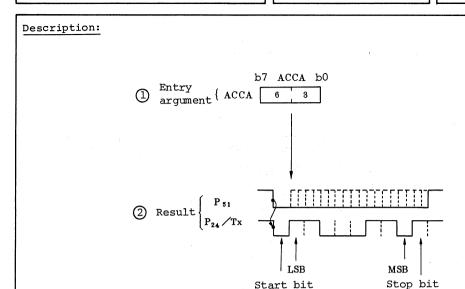

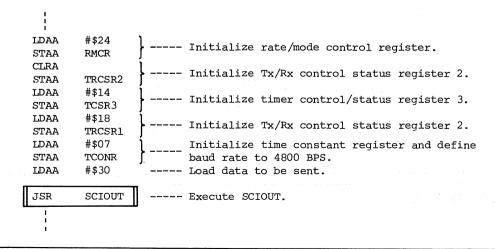

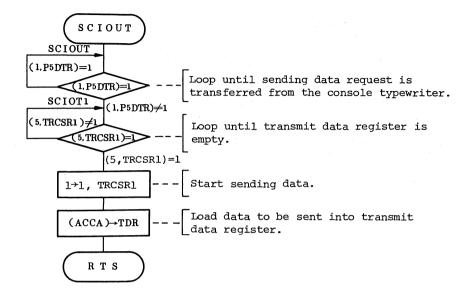

| 8.4    | SCI Applications                                                | 452 |

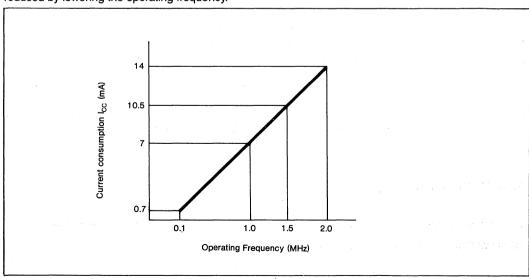

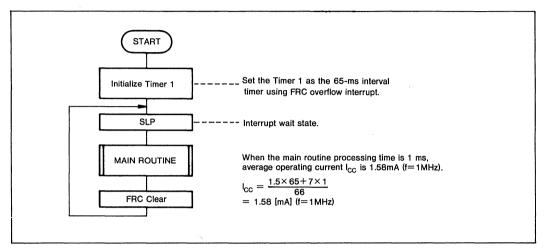

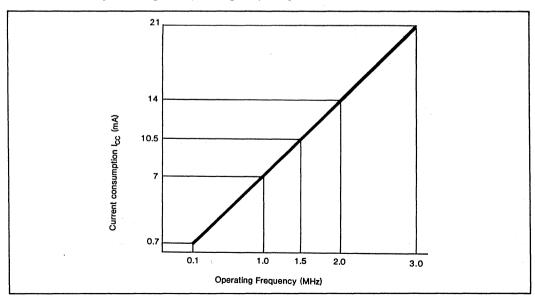

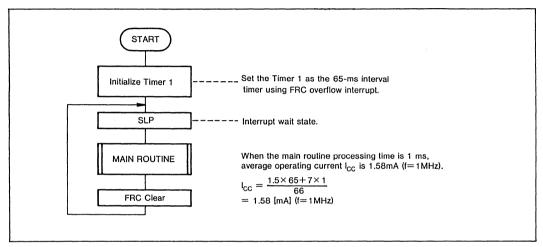

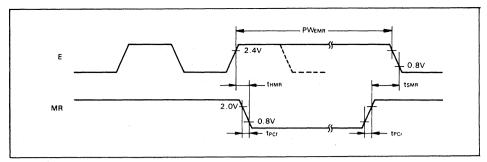

| 8.5    | Lowering Operating Current                                      | 454 |

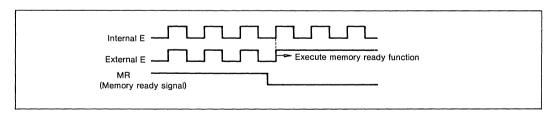

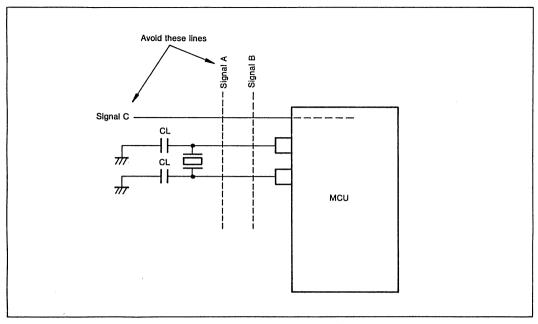

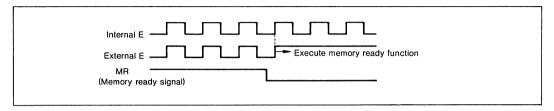

| 8.6    | Memory Ready Application                                        | 457 |

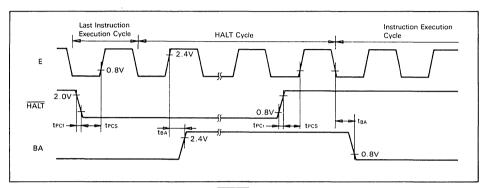

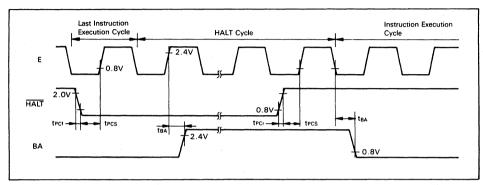

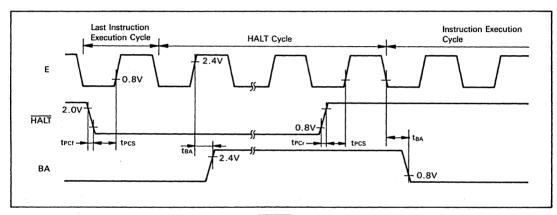

| 8.7    | Halt Application                                                | 458 |

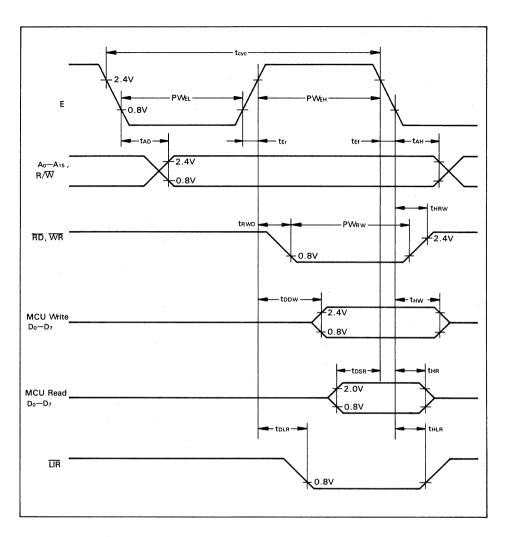

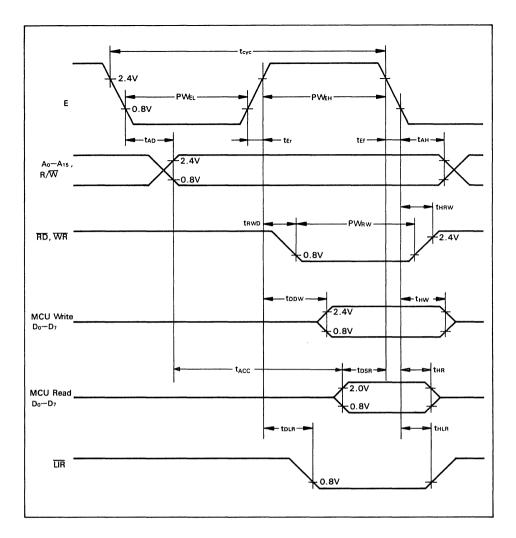

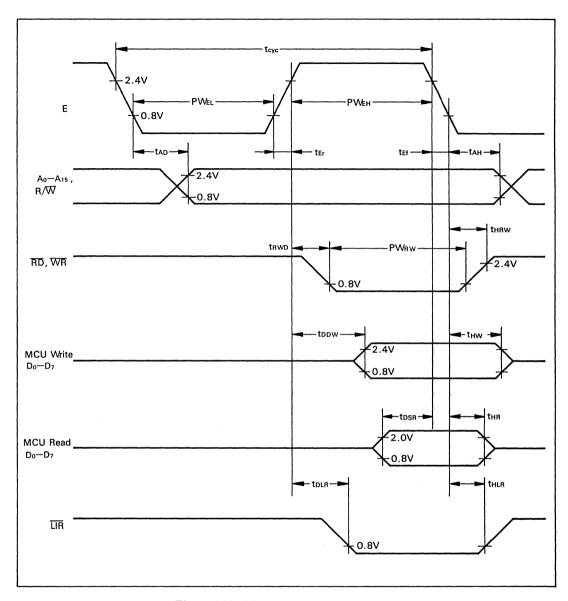

| 8.8    | RD, WR Application                                              | 459 |

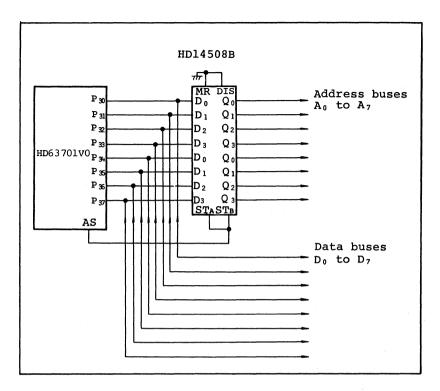

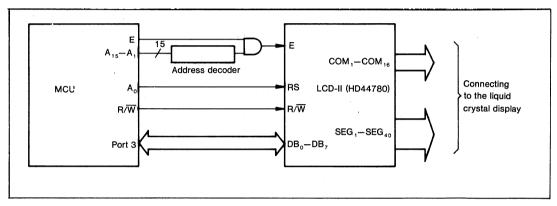

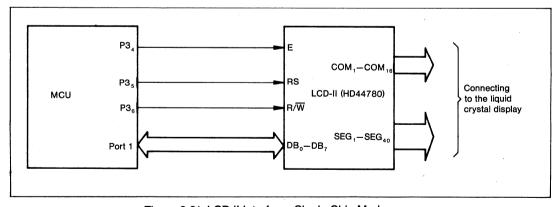

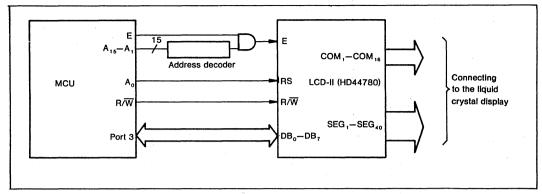

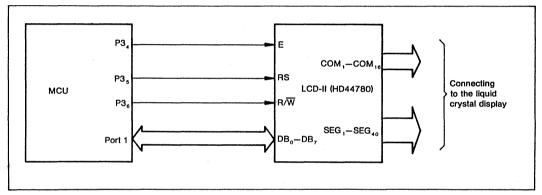

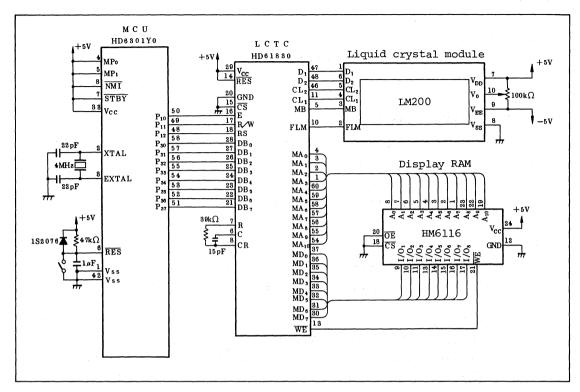

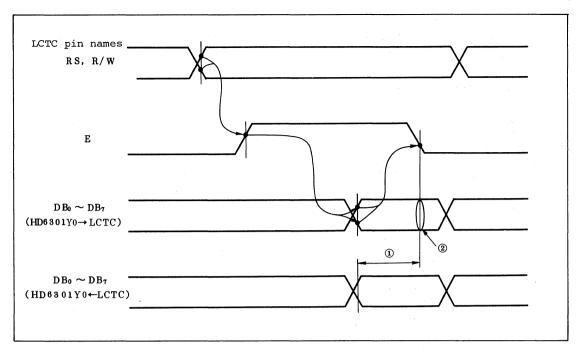

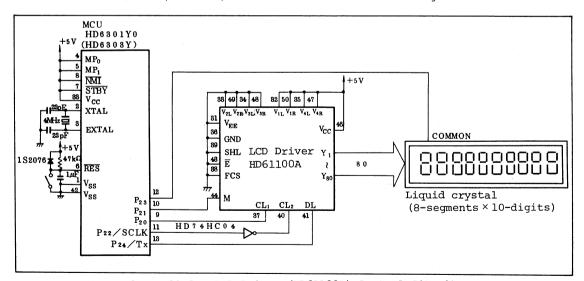

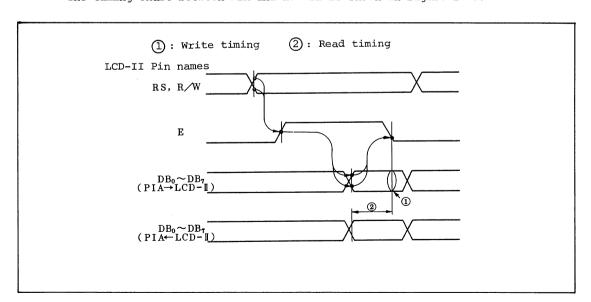

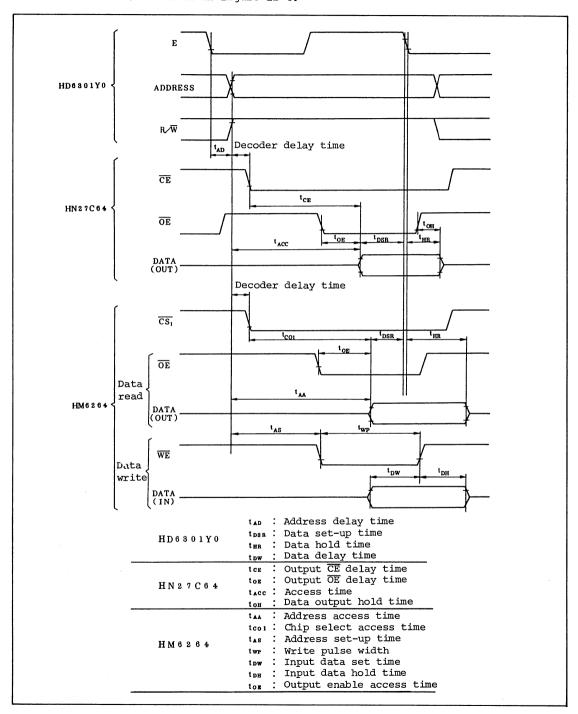

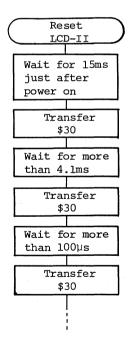

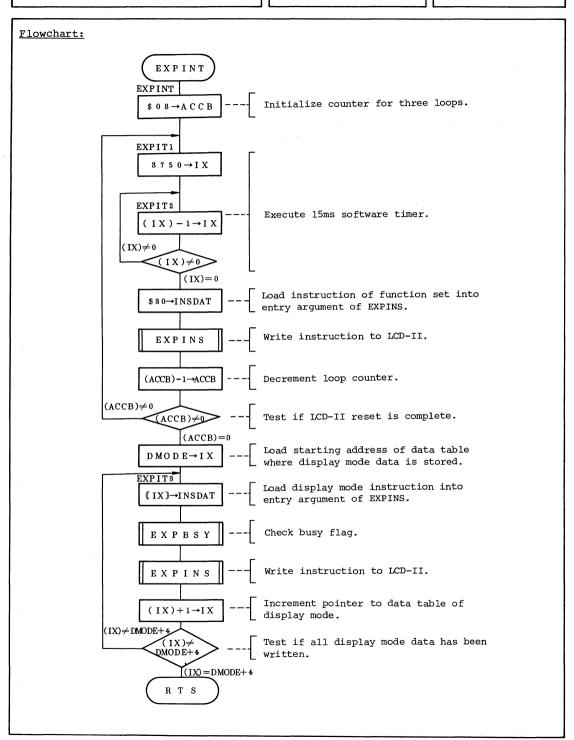

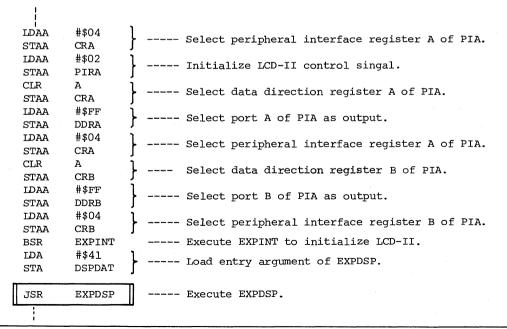

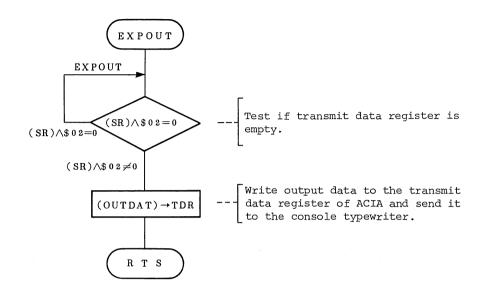

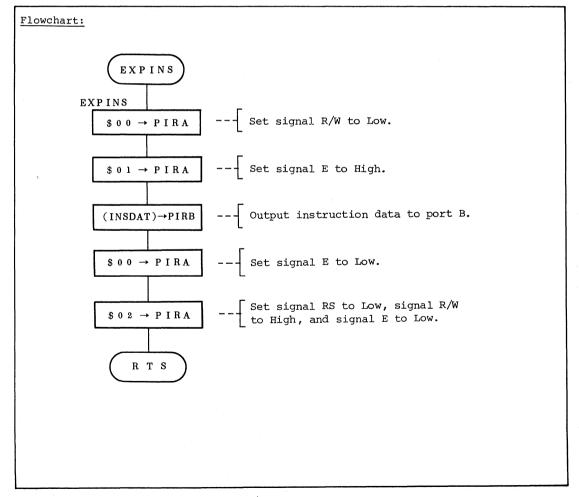

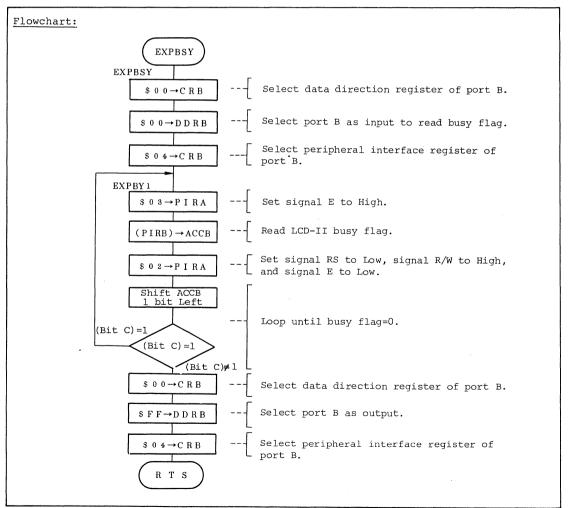

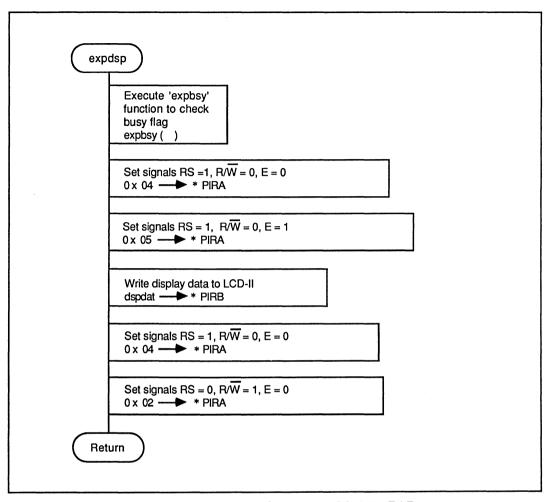

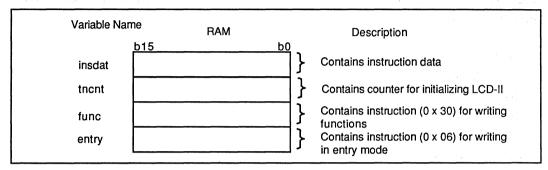

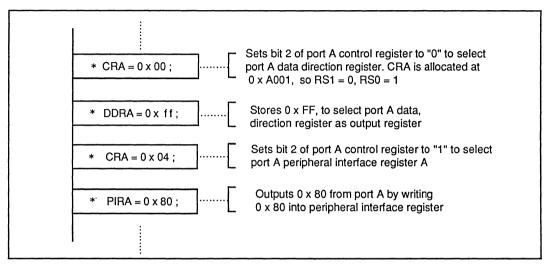

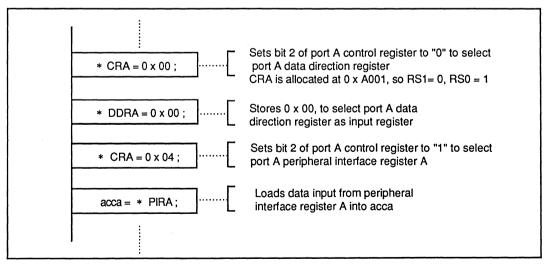

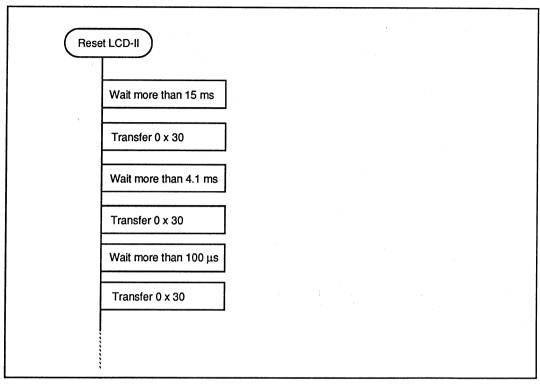

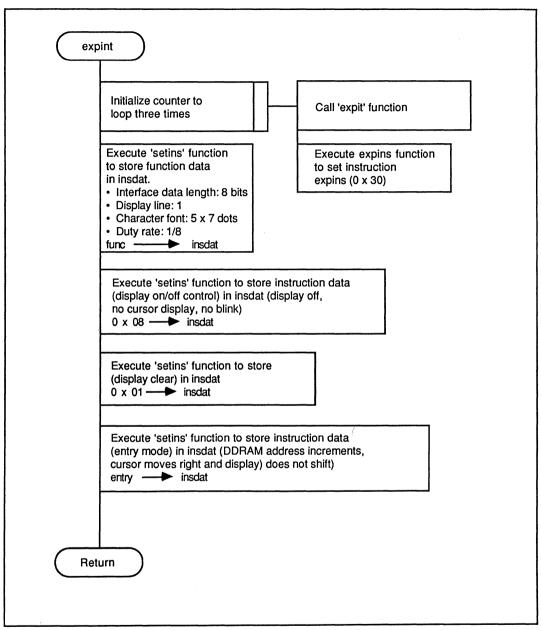

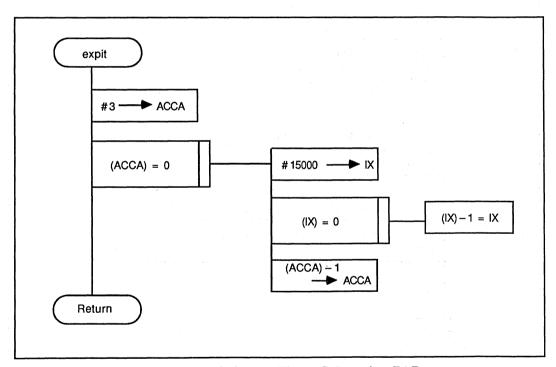

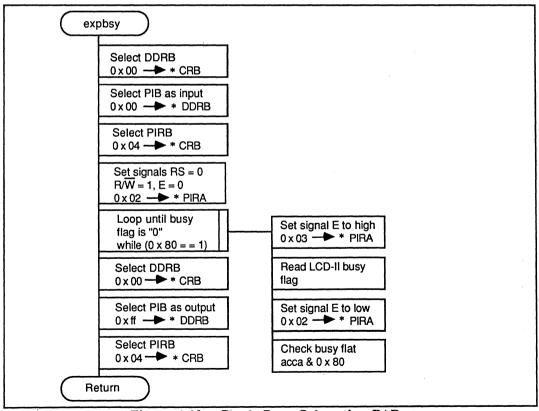

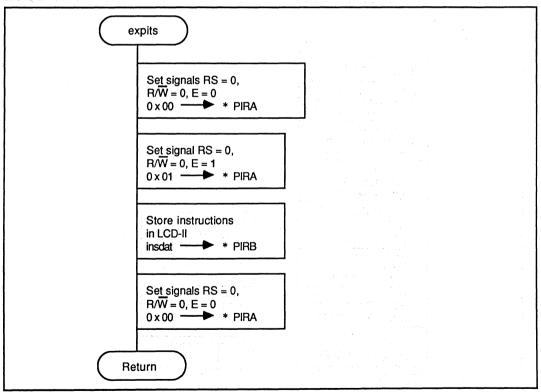

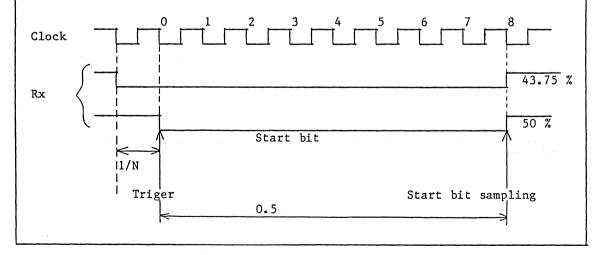

| 8.9    | LCD-II Interface Application                                    | 460 |

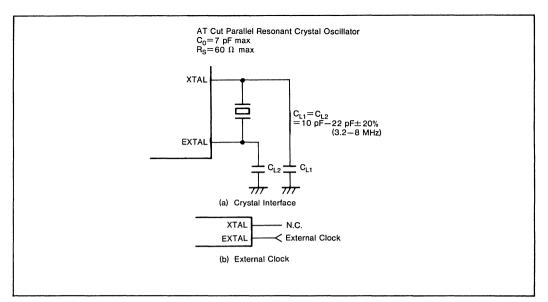

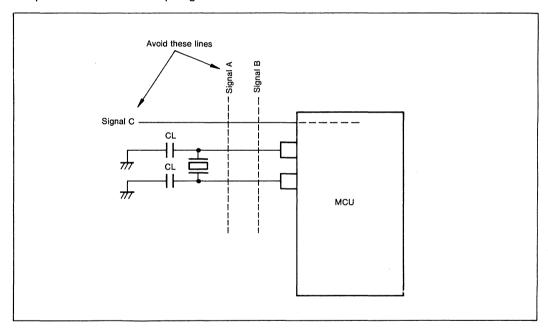

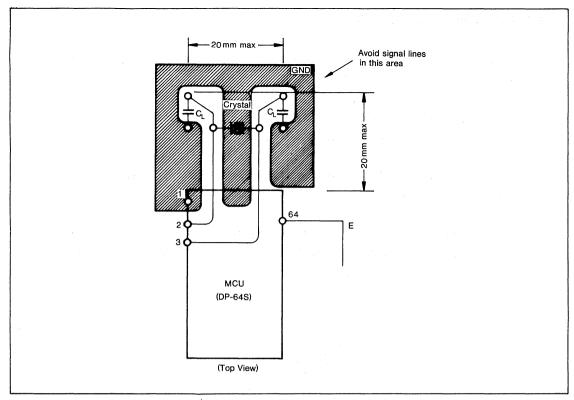

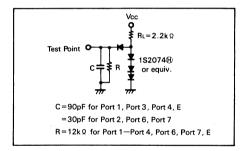

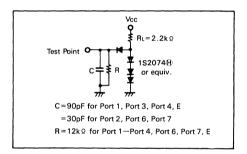

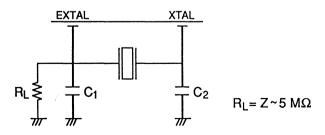

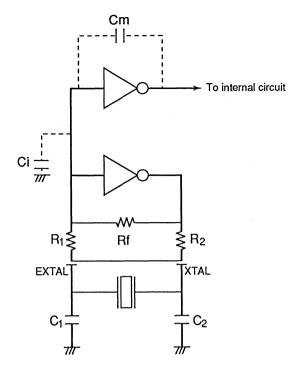

| 8.10   | Oscillation Board Design                                        | 461 |

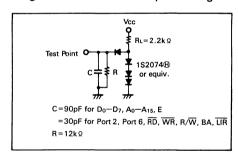

| APPEN  | NDIX I. ELECTRICAL CHARACTERISTICS                              | 463 |

| APPEN  | NDIX II. INSTRUCTION EXECUTION CYCLES                           | 485 |

| APPEN  | NDIX III. QUESTIONS AND ANSWERS                                 | 491 |

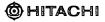

| III.1  | Parallel Ports                                                  | 491 |

| III.2  | Serial Ports                                                    | 492 |

| III.3  | Timer/Counter                                                   | 495 |

| III.4   | Bus Interface                                                              | 497  |

|---------|----------------------------------------------------------------------------|------|

| III.5   | Interrupt Control                                                          | 500  |

| III.6   | Oscillation Circuit                                                        | 502  |

| III.7   | Reset                                                                      | 502  |

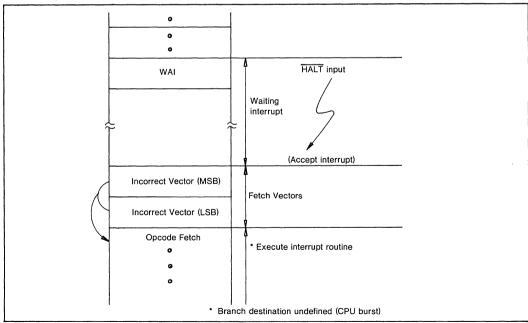

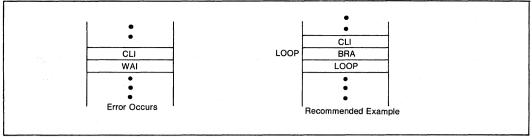

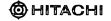

| III.8   | Low Power Dissipation Mode                                                 | 505  |

| III.9   | Software                                                                   | 507  |

| III.10  | Others                                                                     | 508  |

| APPEN   | DIX IV. THE DIFFERENCES BETWEEN HD63701X0 and HD6301X0                     | 509  |

| APPEN   | DIX V. PROGRAM DEVELOPMENT PROCEDURE  AND SUPPORT SYSTEM                   | 510  |

| Section |                                                                            |      |

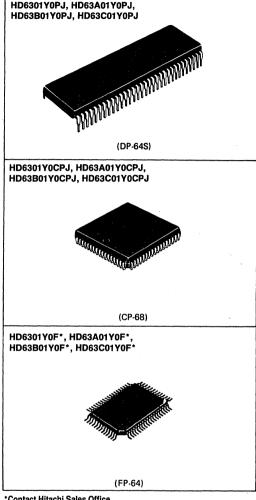

| HD630   | 1Y0/HD6303Y/HD63701Y0 User's Manual                                        | Page |

| 1. OVI  | ERVIEW                                                                     | 519  |

| 1.1     | Features                                                                   | 519  |

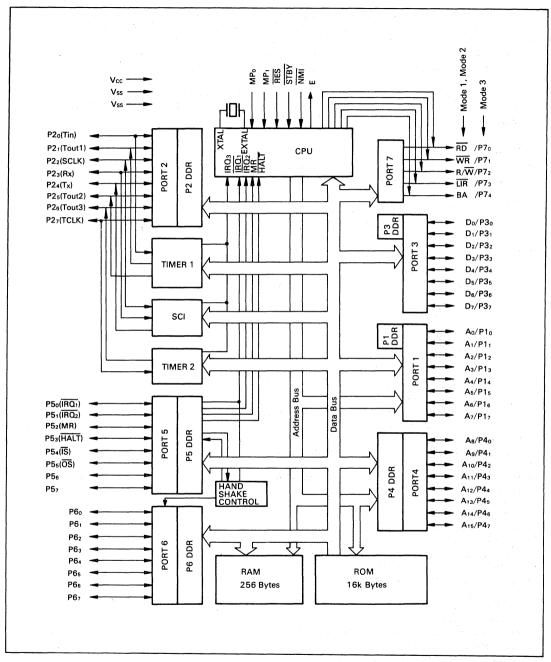

| 1.2     | Block Diagrams                                                             | 520  |

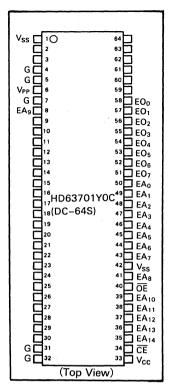

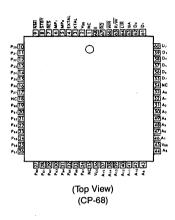

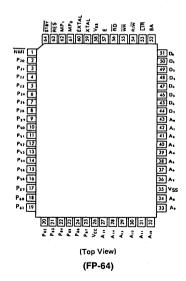

| 1.4     | Pin Description                                                            | 523  |

| 2. INT  | ERNAL ARCHITECTURE AND OPERATION                                           | 526  |

| 2.1     | Operation Modes                                                            | 526  |

| 2.2     | Memory Map                                                                 | 527  |

| 2.3     | Function Pin Description                                                   | 528  |

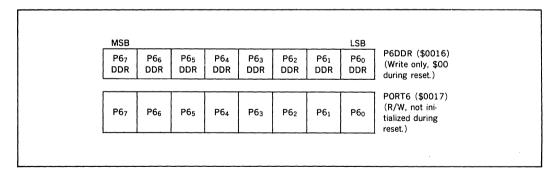

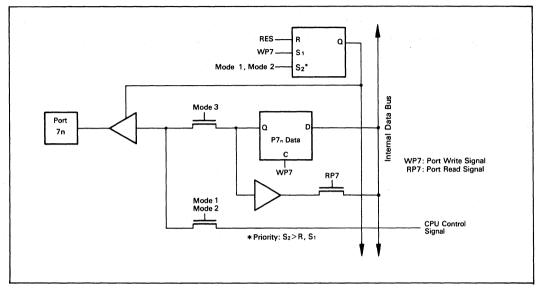

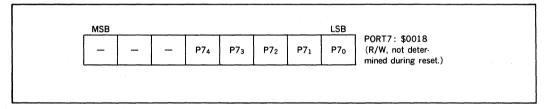

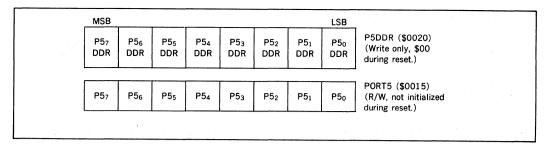

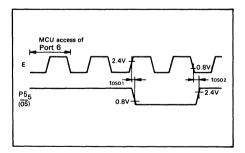

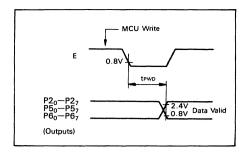

| 2.4     | Ports.                                                                     | 531  |

| 2.5     | RAM/Port 5 Control Register                                                | 543  |

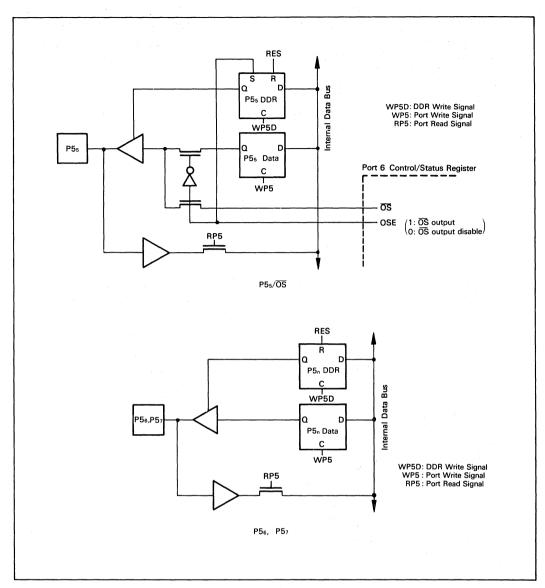

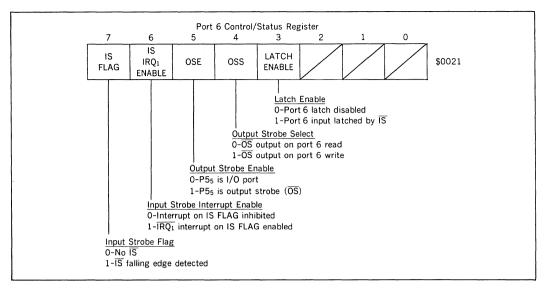

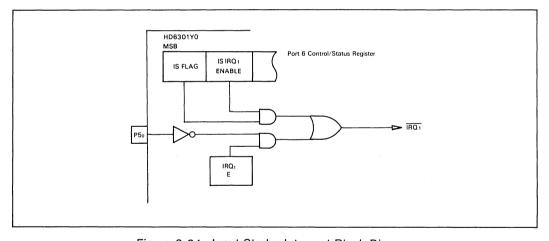

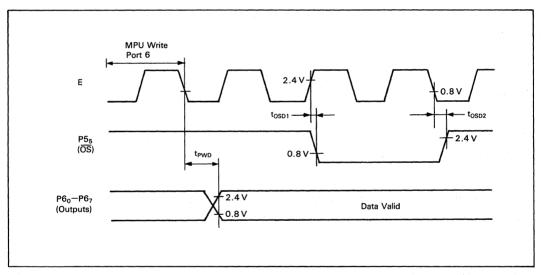

| 2.6     | Port 6 Control/Status Register                                             | 546  |

| 3. CPI  | J FUNCTION                                                                 | 548  |

| 3.1     | CPU Registers                                                              | 548  |

| 3.2     | Addressing Modes                                                           | 549  |

| 3.3     | Instruction Set                                                            | 551  |

| 3.4     | CPU Instruction Flow                                                       | 557  |

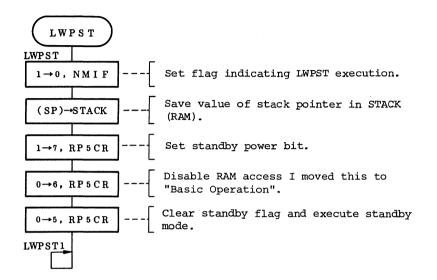

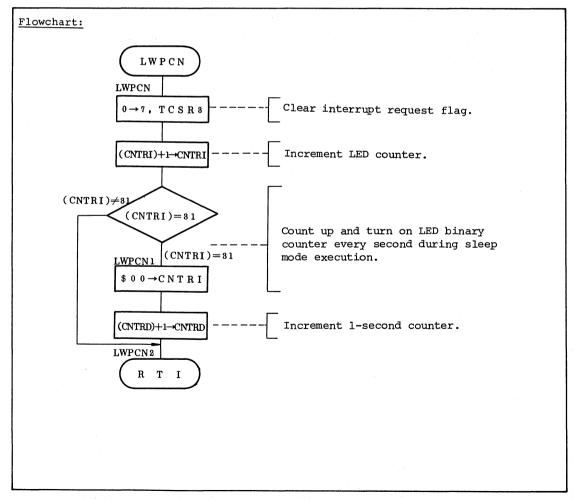

| 3.5     | Low Power Dissipation Modes                                                | 559  |

| 3.6     | Trap Function                                                              | 562  |

| 3.7     | Reset                                                                      | 563  |

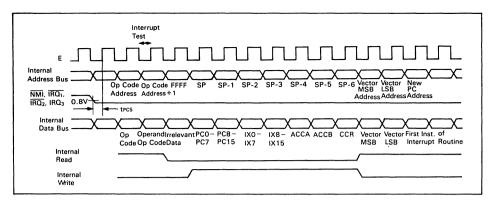

| 3.8     | Interrupts                                                                 | 564  |

| 4. TIM  |                                                                            | 567  |

| 4.1     | Free-Running Counter (FRC)                                                 | 568  |

| 4.2     | Output Compare Registers (OCR)                                             | 568  |

|         | 그는 물문을 보고 가는 회에 가는 그는 후 그렇게 된 것들은 회사를 가는 모든 그를 가는 그는 그를 모든 것을 받았습니다. 모든 그리 |      |

| 4.3    | Input Compare Register (ICR)                                    | 569 |

|--------|-----------------------------------------------------------------|-----|

| 4.4    | Timer Control/Status Register 1 (TCSR1)                         | 569 |

| 4.5    | Timer Control/Status Register 2 (TCSR2)                         | 570 |

| 4.6    | Timer Status Flags                                              | 572 |

| 4.7    | Precautions on Cleaning the OCF                                 | 572 |

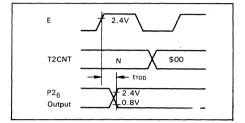

| 5. TII | MER 2                                                           | 574 |

| 5.1    | Timer 2 Upcounter (T2CNT)                                       | 574 |

| 5.2    | Timer Constant Register (TCONR)                                 | 575 |

| 5.3    | Timer Control/Status Register 3 (TCSR3)                         | 575 |

| 5.4    | Timer Status Flags                                              | 576 |

| 5.5    | Precaution for Toggle Pulse Function of HD6301Y0/HD6303Y/       |     |

|        | HD63701Y0 Timer 2                                               | 577 |

| 6. SE  | ERIAL COMMUNICATIONS INTERFACE                                  | 578 |

| 6.1    | Initialization                                                  | 578 |

| 6.2    | Asynchronous Mode                                               | 579 |

| 6.3    | Clock Synchronous Mode                                          | 580 |

| 6.4    | Transmit/Receive Control Status Register (TRCSR)                | 582 |

| 6.5    | Transmit Rate/Mode Control Register (RMCR)                      | 583 |

| 6.6    | SCI Receiving Margin                                            | 586 |

| 6.7    | SCI Status Flags                                                | 587 |

| 6.8    | Precaution for Clock-Synchronous Serial Communication Interface | 588 |

| 7. HC  | 063701Y0 Programming ROM (EPROM)                                | 589 |

| 7.1    | Programming and Verification                                    | 590 |

| 7.2    | Erasing (Window Package)                                        | 591 |

| 7.3    | Characteristics and Applications                                | 591 |

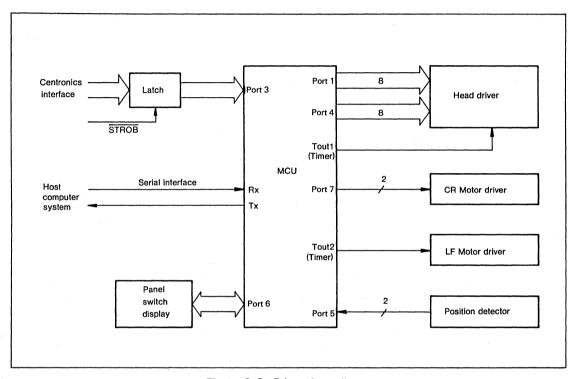

| 8. AF  | PPLICATIONS                                                     | 593 |

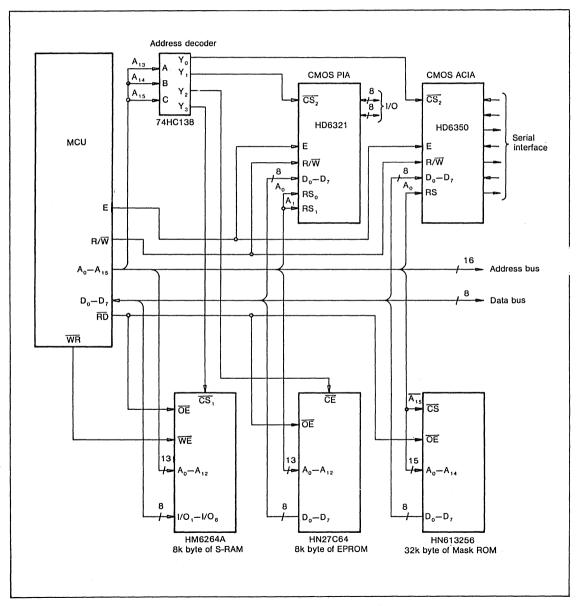

| 8.1    | HD6301Y0 in Expanded Mode                                       | 593 |

| 8.2    | HD6301Y0 in Single-Chip Mode                                    | 594 |

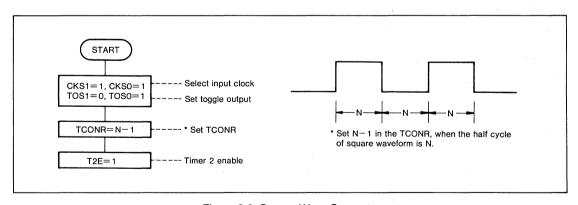

| 8.3    | Timer Applications                                              | 594 |

| 8.4    | SCI Applications                                                | 598 |

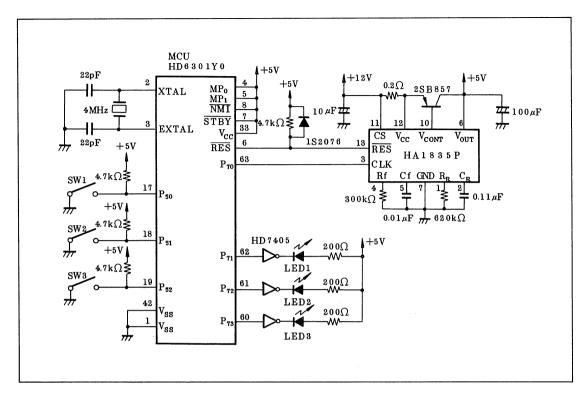

| 8.5    | Lowering Operating Current                                      | 600 |

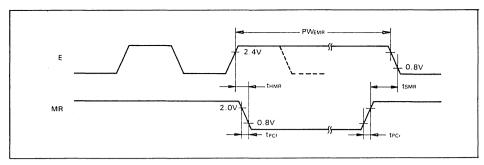

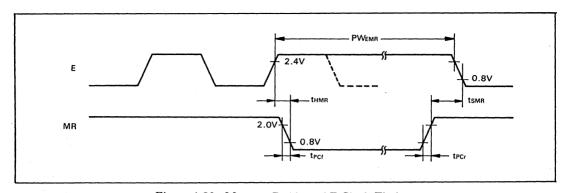

| 8.6    | Memory Ready Application                                        | 603 |

| 8.7    | Halt Application                                                | 604 |

| 8.8    | RD, WR Application                                              | 605 |

| 8.9    | LCD-II Interface Application                                    | 605 |

| 8.10   | Oscillation Circuit Board Design                                | 606 |

|        |                                                                 |     |

| APPENDIX I. ELECTRICAL CHARACTERISTICS                      | 608  |

|-------------------------------------------------------------|------|

| APPENDIX II. INSTRUCTION EXECUTION CYCLES                   | 630  |

| APPENDIX III. QUESTIONS AND ANSWERS                         | 636  |

| III.1 Parallel Ports                                        | 636  |

| III.2 Serial Ports                                          | 639  |

| III.3 Timer/Counter                                         | 644  |

| III.4 Bus Interface                                         | 647  |

| III.5 Interrupt Control                                     | 650  |

| III.6 Oscillation Circuit                                   | 653  |

| III.7 Reset                                                 | 653  |

| III.8 Low Power Dissipation Mode                            | 657  |

| III.9 Software                                              | 660  |

| III.10 Others                                               | 661  |

| APPENDIX IV. THE DIFFERENCES BETWEEN HD63701Y0 and HD6301Y0 | 663  |

| APPENDIX V. PROGRAM DEVELOPMENT PROCEDURE AND SUPPORT       |      |

| SYSTEM                                                      | 664  |

| V.1 Overview                                                | 664  |

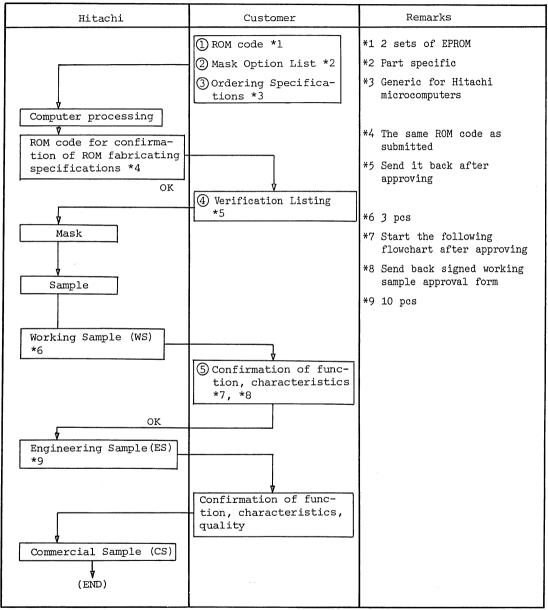

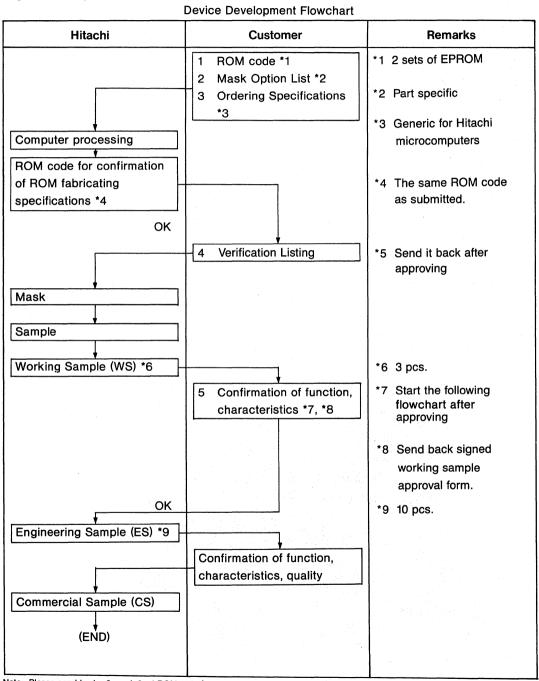

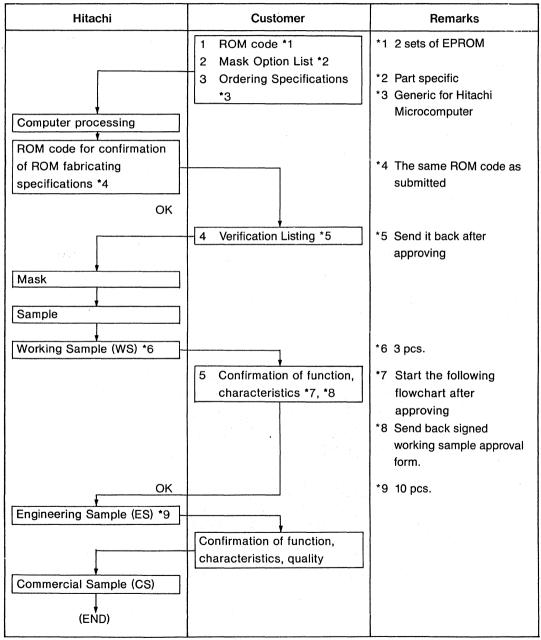

| V.2 Single Chip Microcomputer ROM Ordering Procedure        | 666  |

|                                                             |      |

| Section 7 Software Application Notes                        | Page |

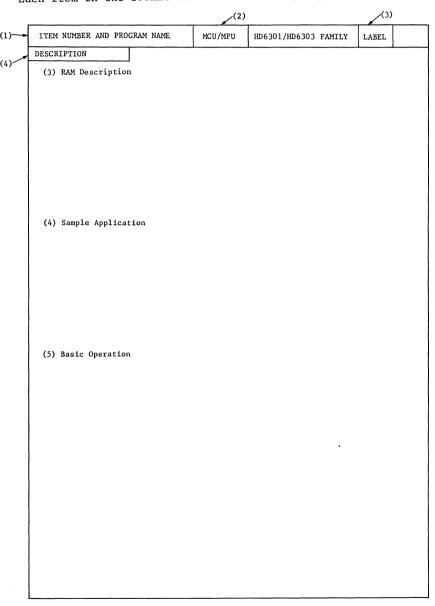

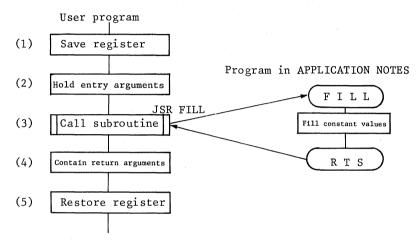

| 1. HOW TO USE APPLICATION NOTES                             | 675  |

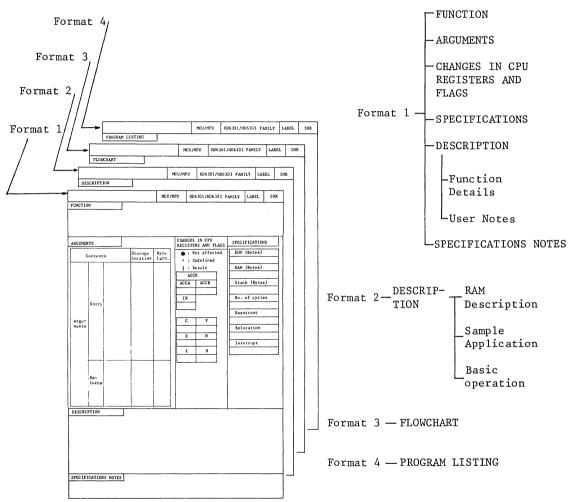

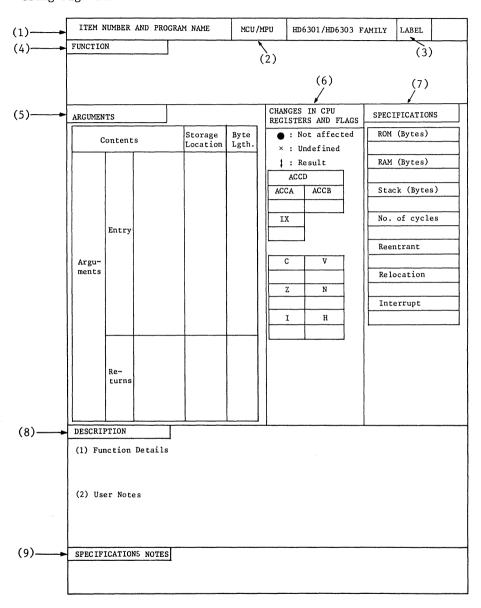

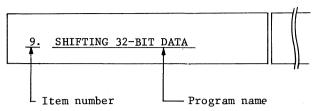

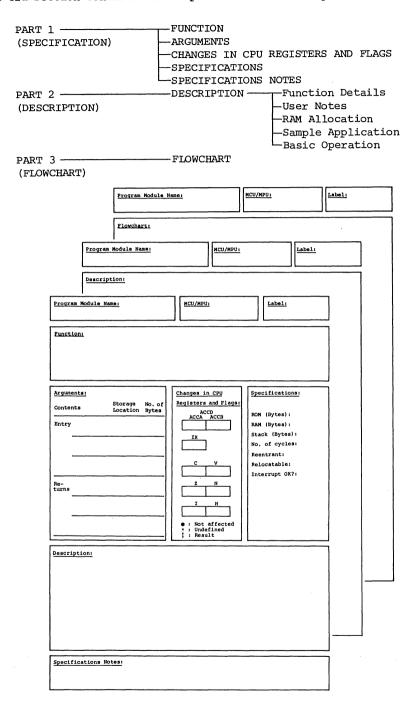

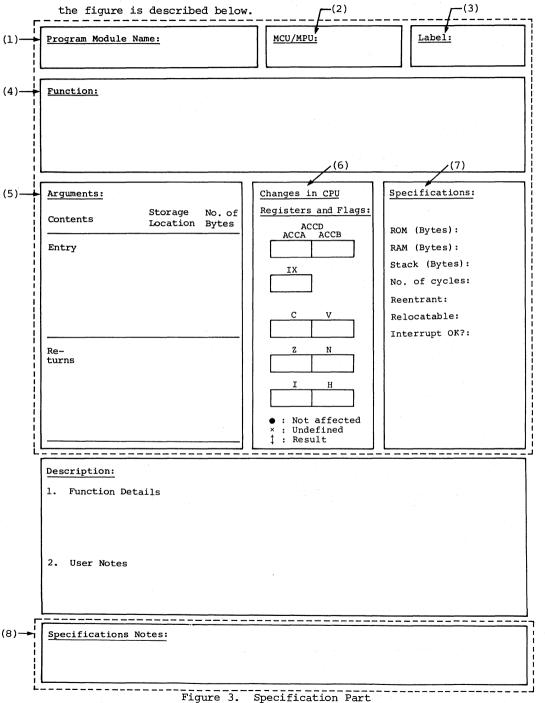

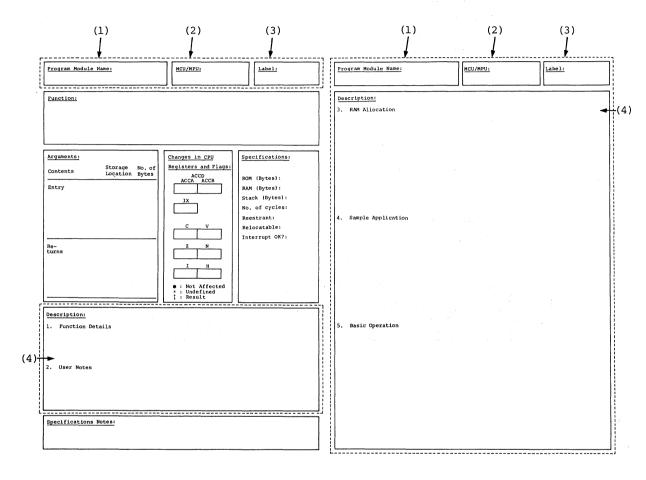

| 1.1 Formats                                                 | 675  |

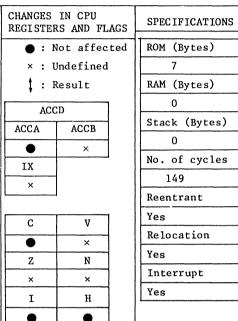

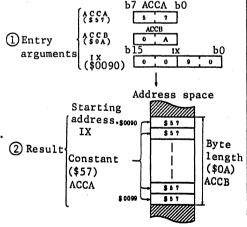

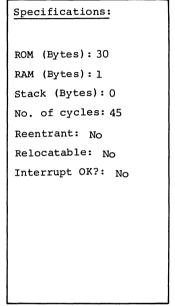

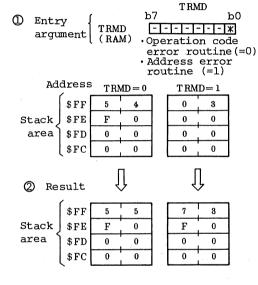

| 1.1.1 Specification Format (Format 1)                       | 677  |

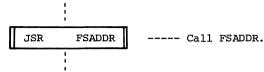

| 1.1.2 Description Format (Format 2)                         | 683  |

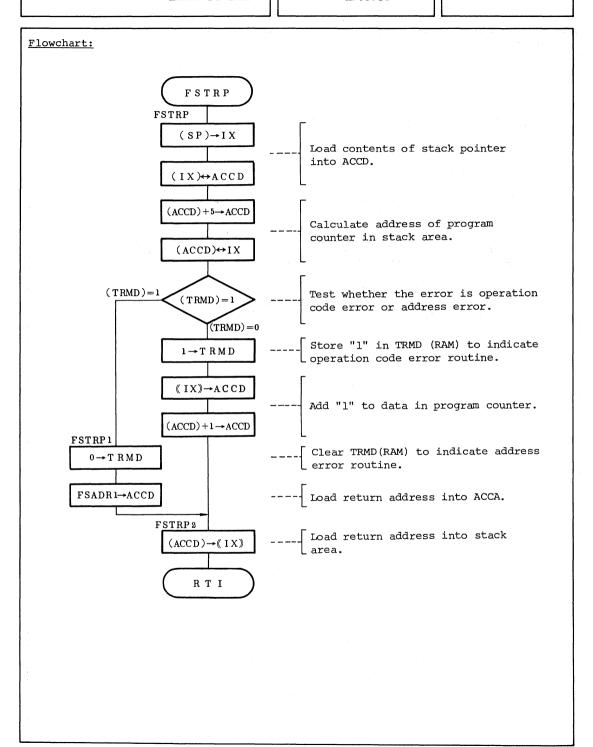

| 1.1.3 Flowchart Format (Format 3)                           | 686  |

| 1.1.4 Program Listing Format (Format 4)                     | 688  |

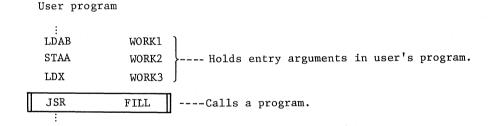

| 1.2 How to Execute Programs                                 | 690  |

| 1.3 Symbols                                                 | 692  |

| PROGRAM APPLICATION EXAMPLES                                |      |

| Program Application Table                                   | 693  |

| MOVING DATA                                                 |      |

|                                                             |      |

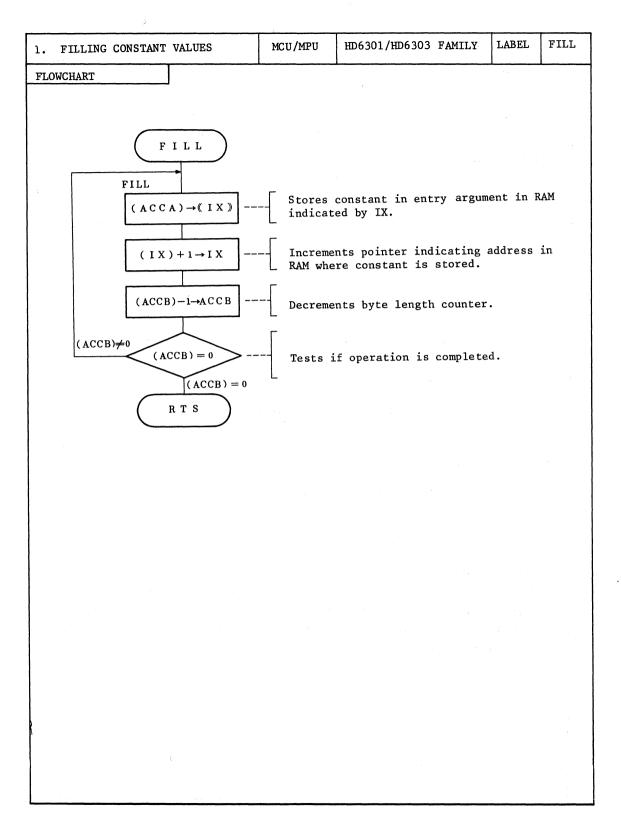

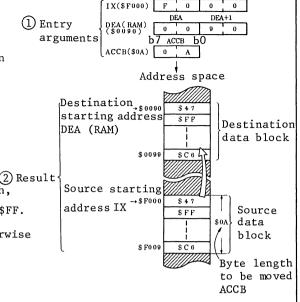

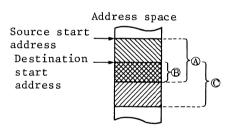

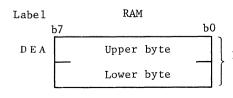

| Filling Constant Values (Fill)                              | 694  |

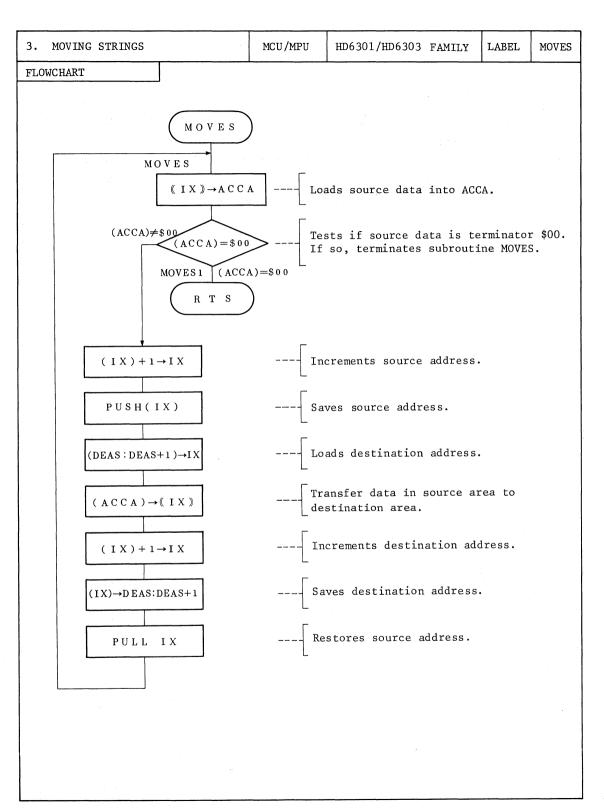

| 3.         | Moving Strings (Moves)                                   | 703        |

|------------|----------------------------------------------------------|------------|

|            | ANCHING FROM TABLE                                       | 700        |

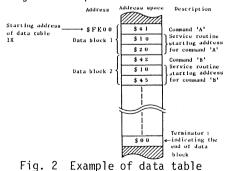

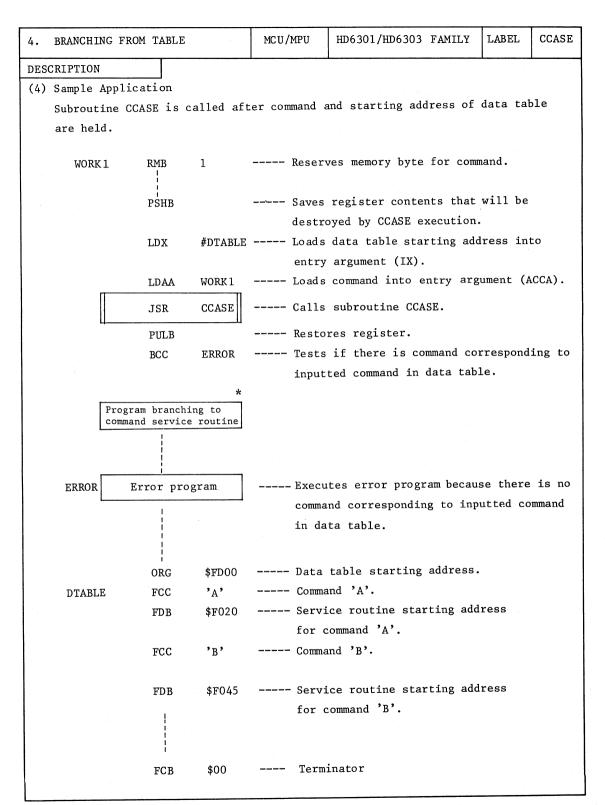

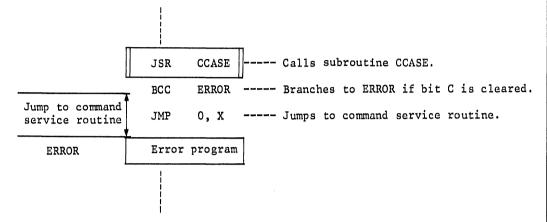

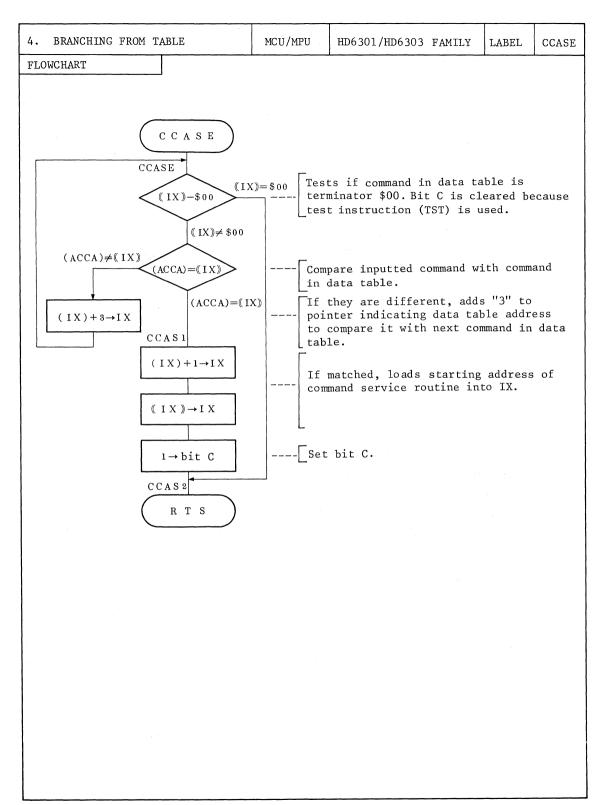

| 4.         | Branching From Table (CCASE)                             | 708        |

| HAI        | NDLING ASCII                                             |            |

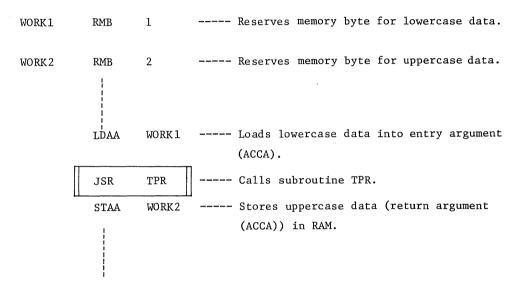

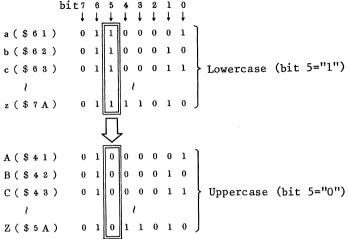

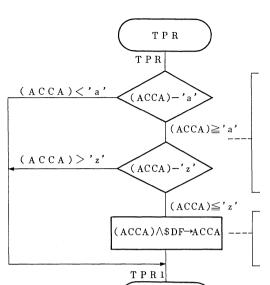

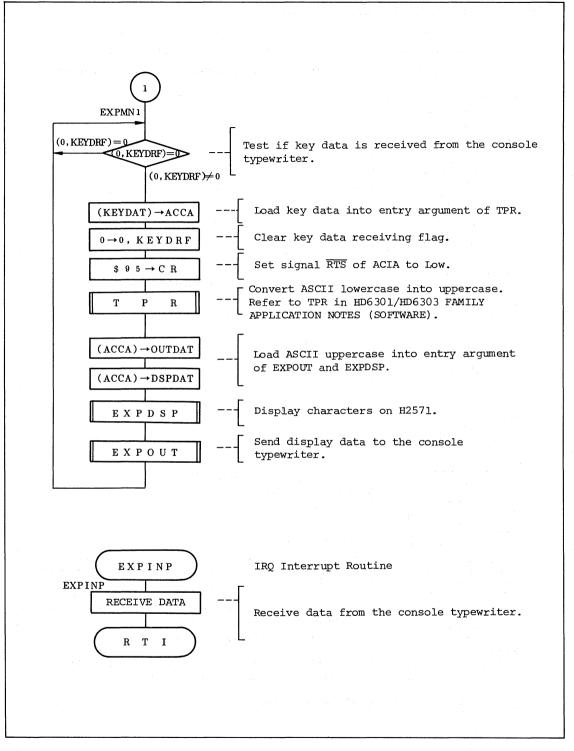

| 5.         | Converting ASCII Lowercase Into Uppercase (TPR)          | 714        |

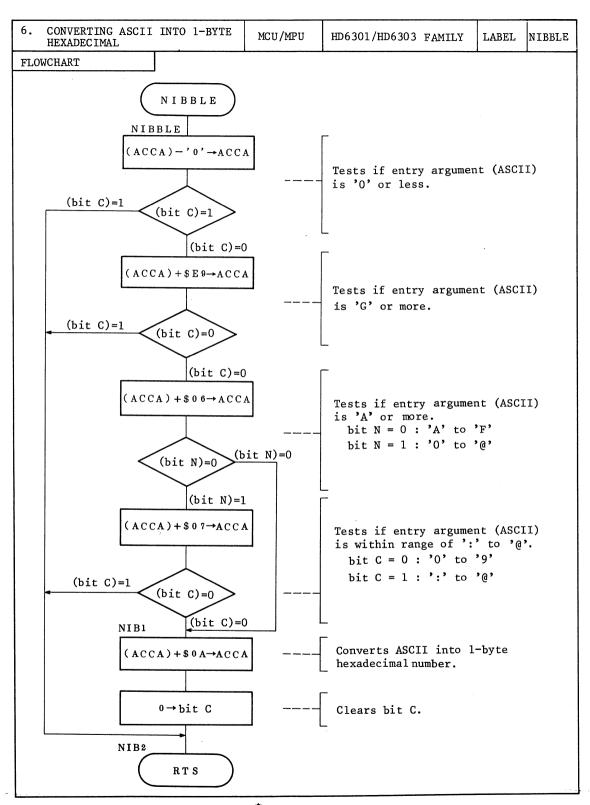

| 6.<br>–    | Converting ASCII Into 1-Byte Hexadecimal (Nibble)        | 719        |

| 7.         | Converting 8-Bit Binary Data Into ASCII (COBYTE)         | 724        |

| віт        | MANIPULATION                                             |            |

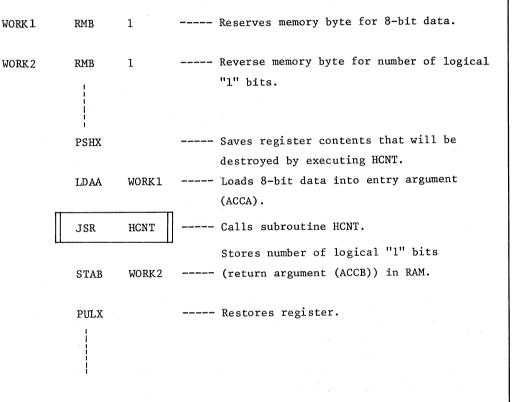

| 8.         | Counting Number of Logical "1" Bits In 8-Bit Data (HCNT) | 729        |

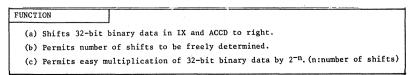

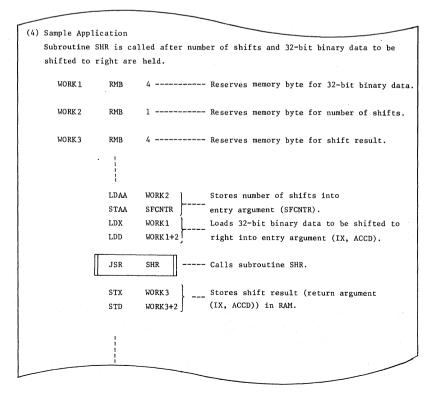

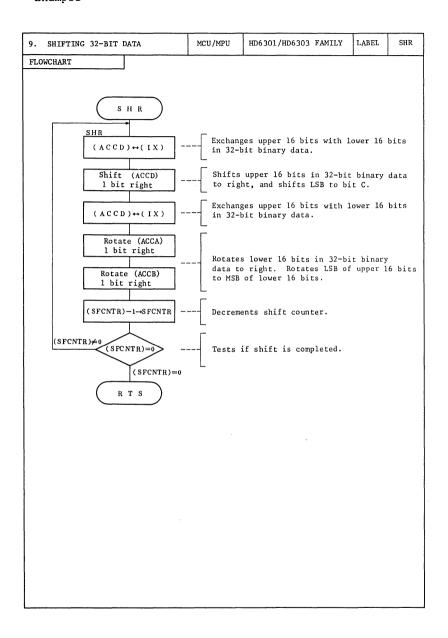

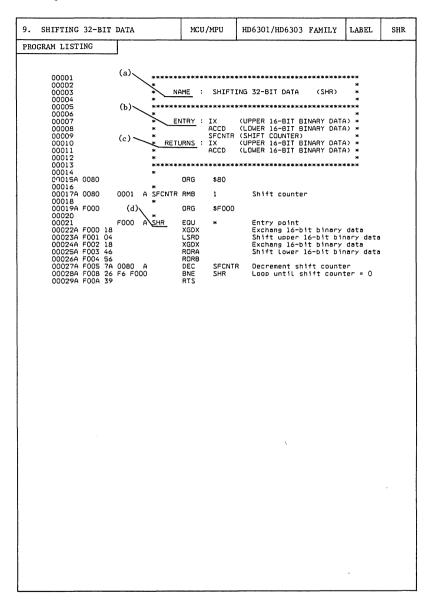

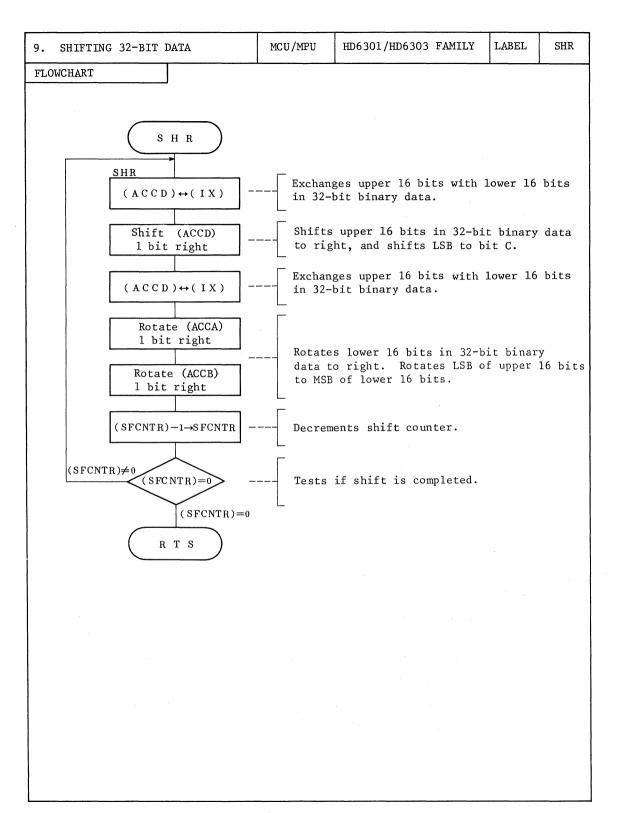

| 9.         | Shifting 32-Bit Data (SHR)                               | 733        |

| СО         | UNTER                                                    |            |

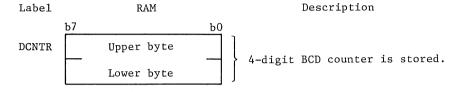

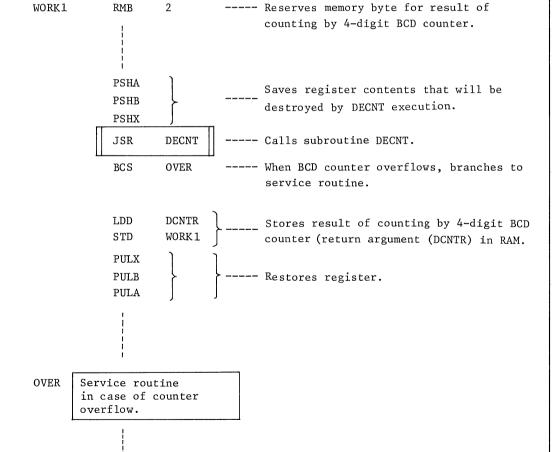

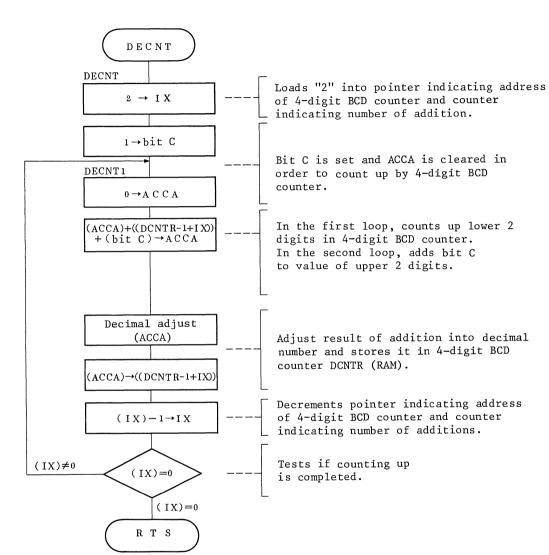

| 10.        | 4-Digit BCD Counter (DECNT)                              | 738        |

| CO         | MPARISON                                                 |            |

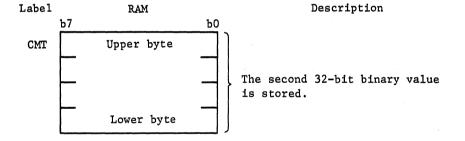

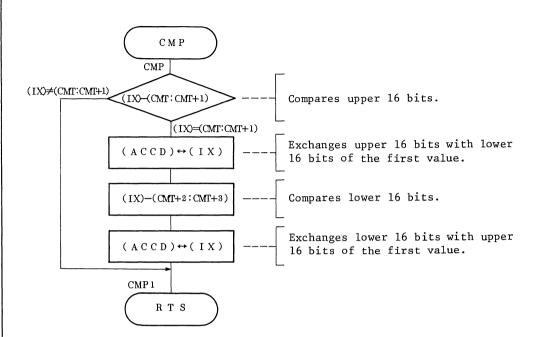

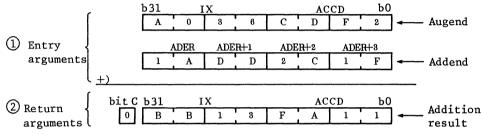

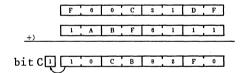

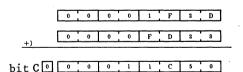

| 11.        | Comparing 32-Bit Binary Data (CMP)                       | 743        |

|            |                                                          |            |

|            | THMETIC OPERATION                                        | 740        |

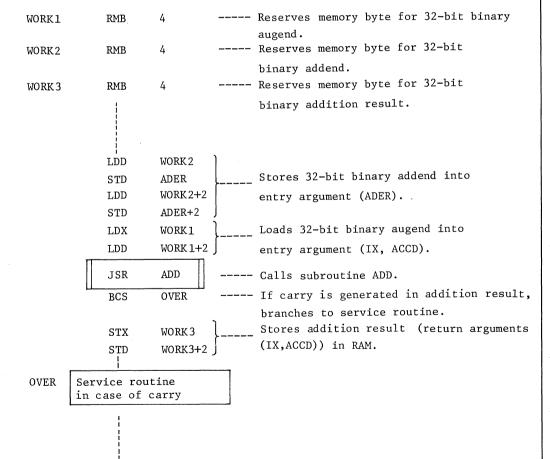

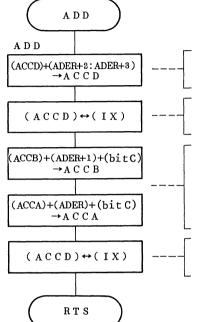

| 12.        | Adding 32-Bit Binary Data (ADD)                          | 749<br>755 |

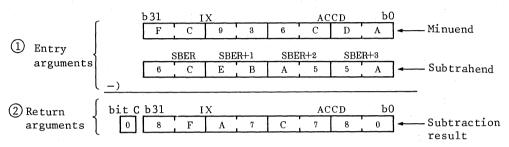

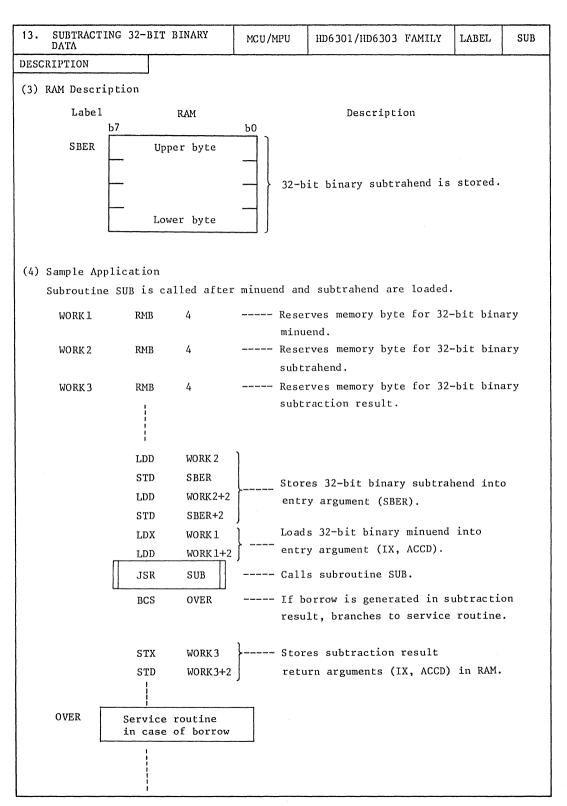

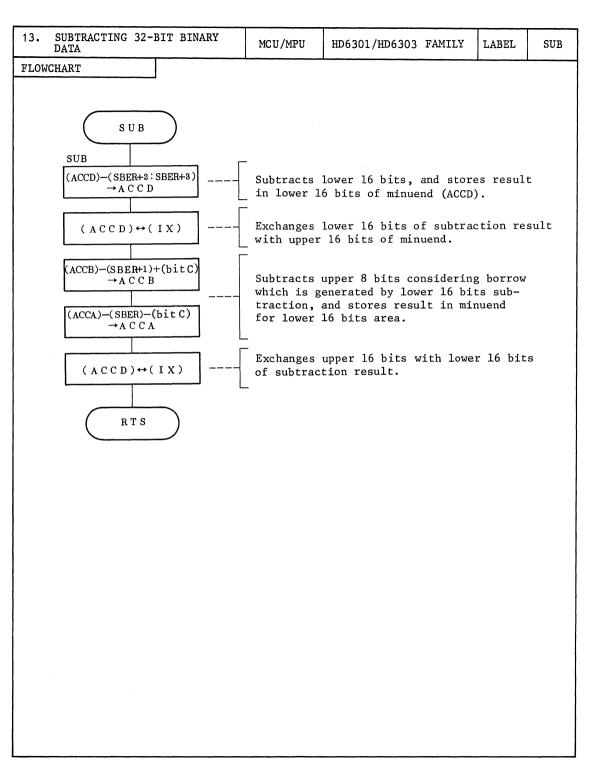

| 13.<br>14. | Subtracting 32-Bit Binary Data (SUB)                     | 755<br>761 |

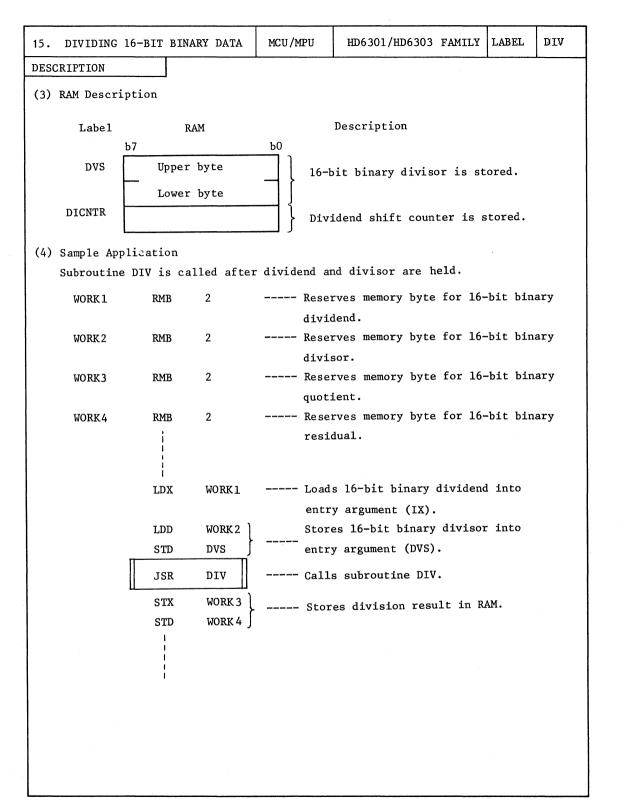

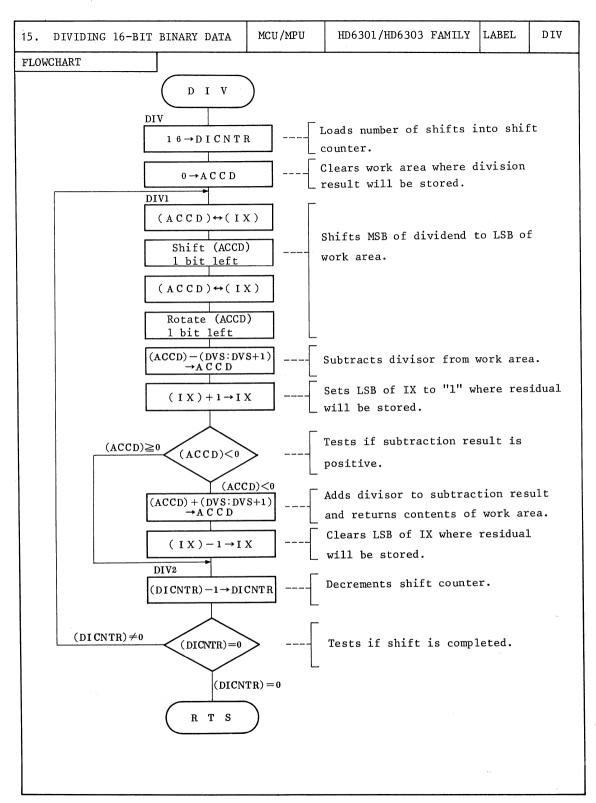

| 15.        | Dividing 16-Bit Binary Data (DIV)                        | 768        |

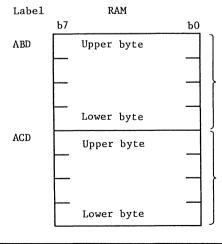

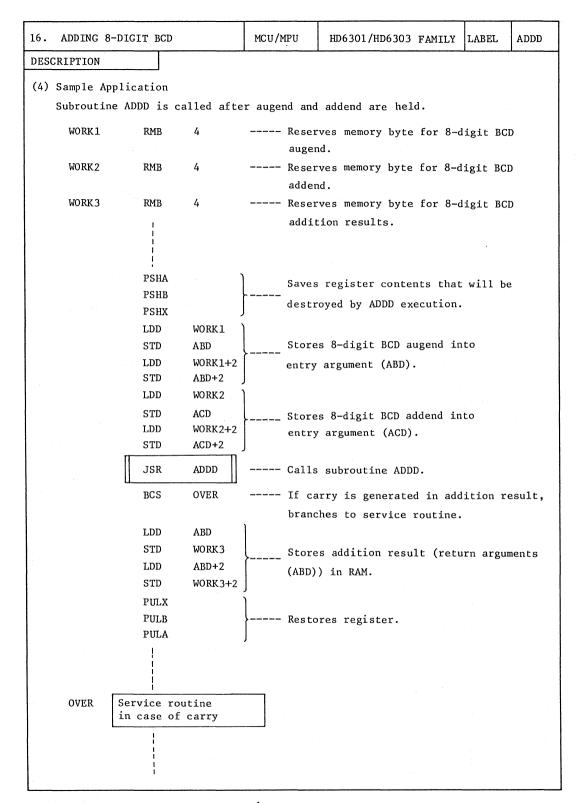

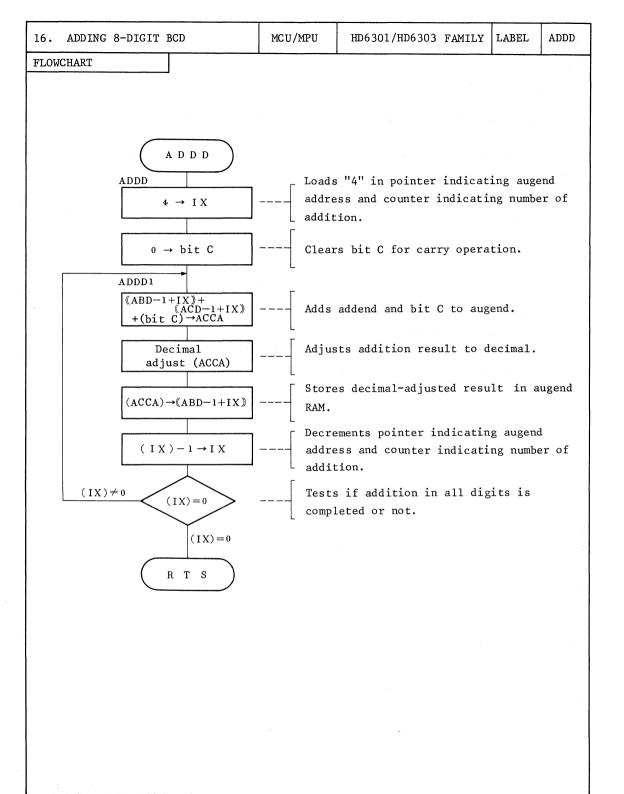

| 16.        | Adding 8-Digit BCD (ADDD)                                | 774        |

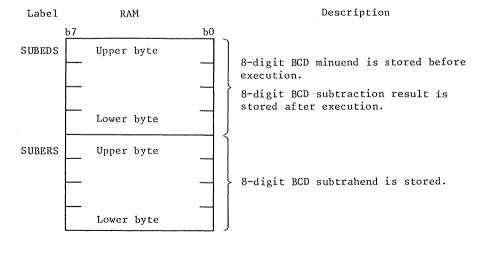

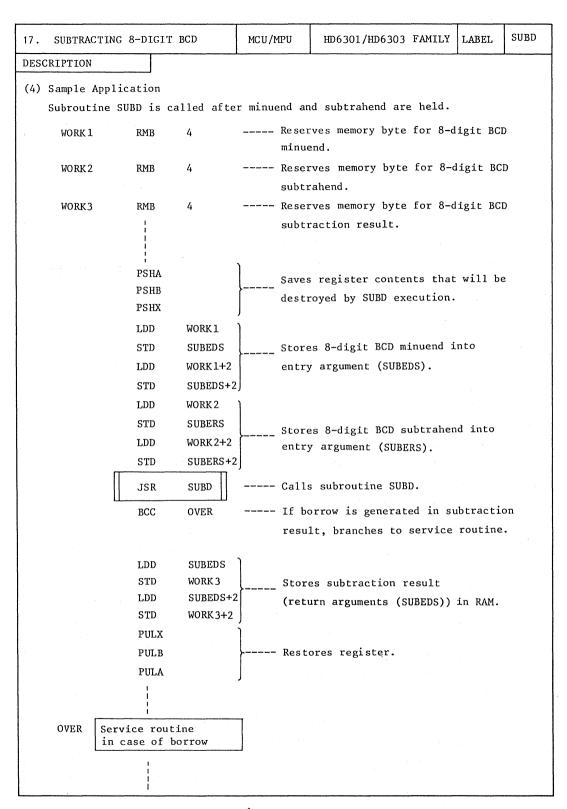

| 17.        | Subtracting 8-Digit BCD (SUBD)                           | 780        |

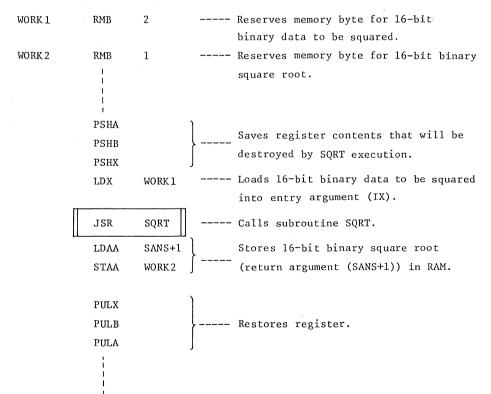

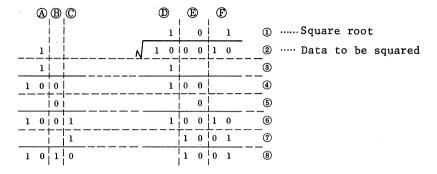

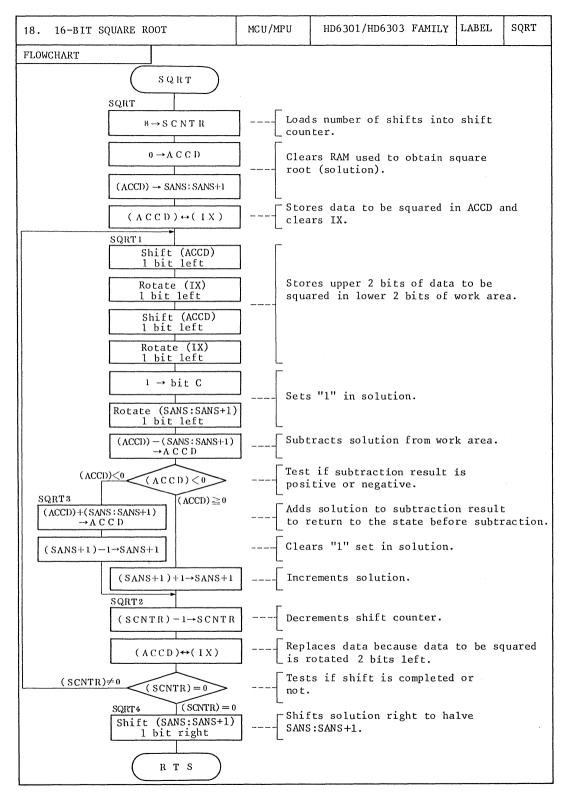

| 18.        | 16-Bit Square Root (SQRT)                                | 786        |

| CO         | NVERTING BCD INTO HEXADECIMALS                           |            |

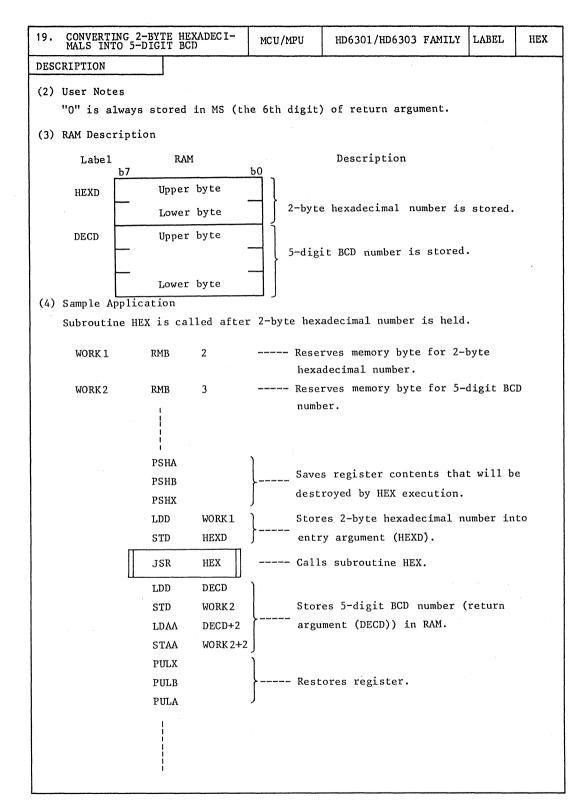

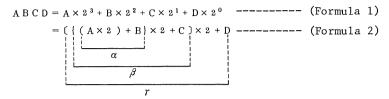

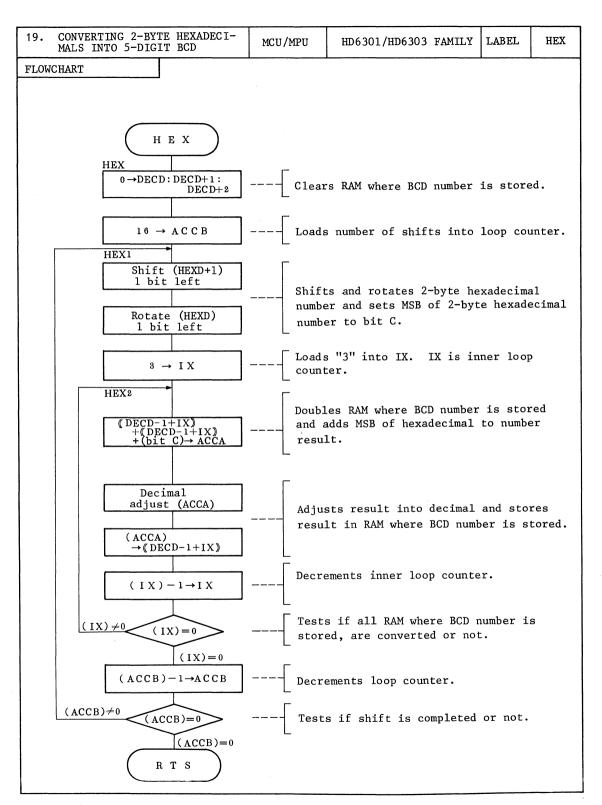

| 19.        | Converting 2-Byte Hexadecimals Into 5-Digit BCD (HEX)    | 791        |

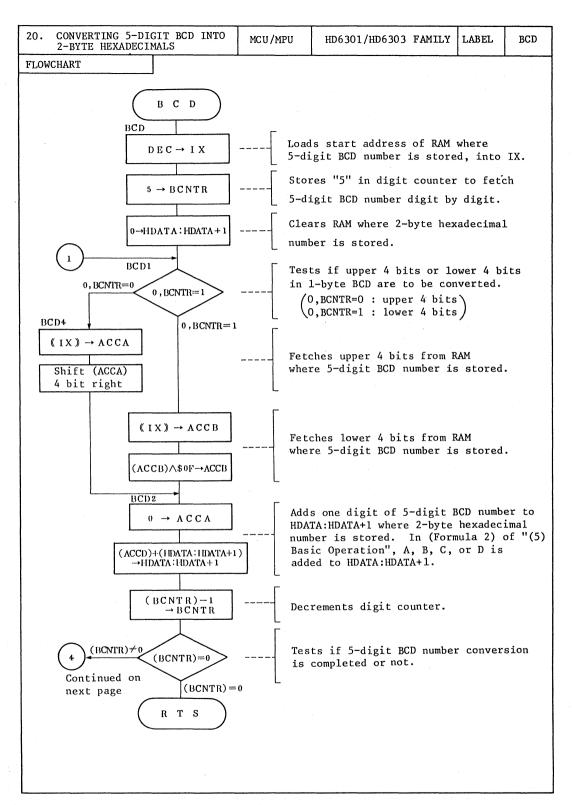

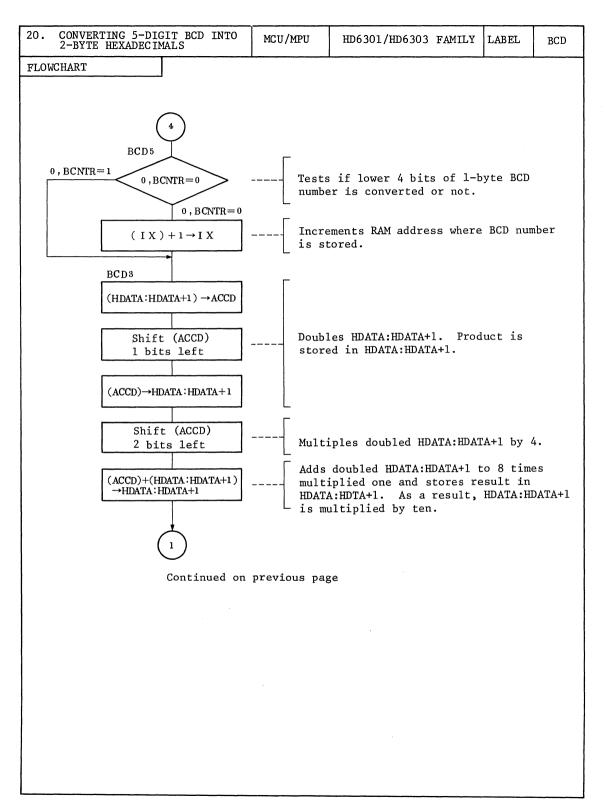

| 20.        | Converting 5-Digit BCD Into 2-Byte Hexadecimals (BCD)    | 796        |

| 00         | DTIMO                                                    |            |

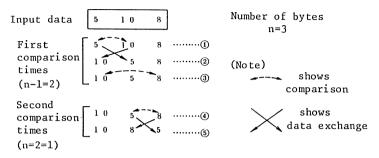

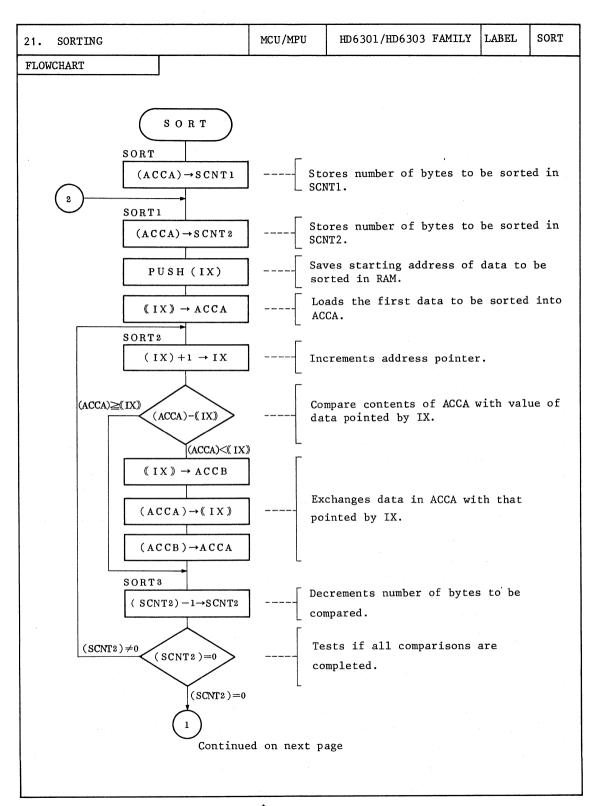

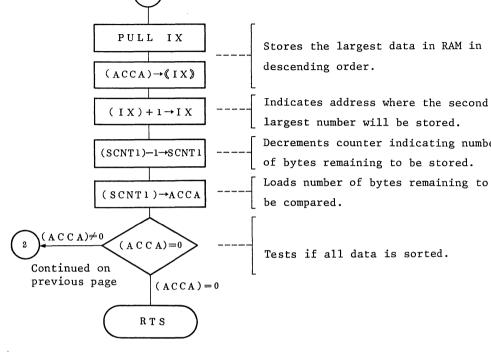

| 21.        | RTING Sorting (SORT)                                     | 803        |

| ۷۱.        |                                                          | 000        |

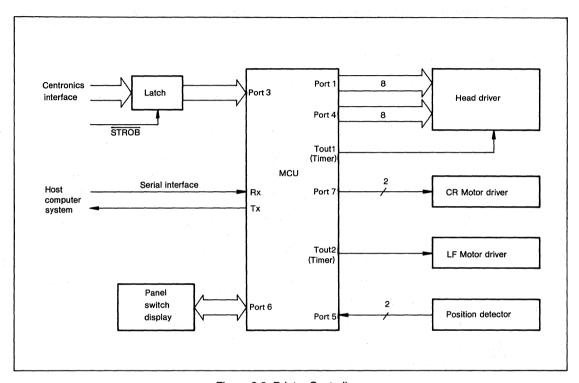

| Sec        | ction 8 Hardware Application Notes                       | Page       |

|            | PLICATION NOTES GUIDE                                    | 815        |

| 1.         | Symbols                                                  | 815        |

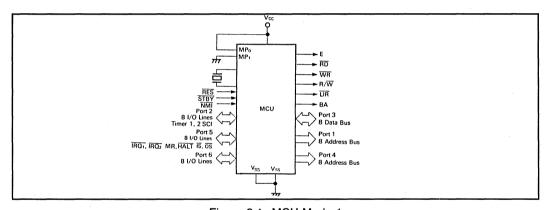

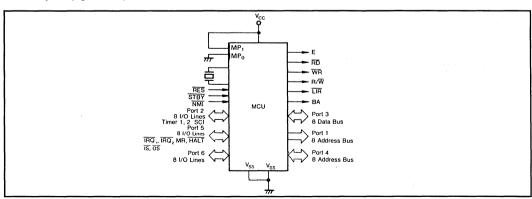

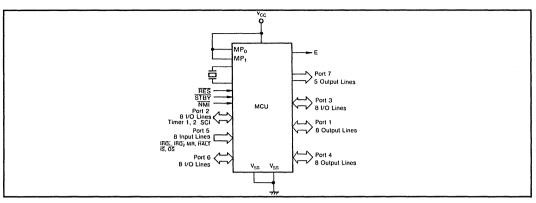

| 2.         | Application Example Configuration                        | 817        |

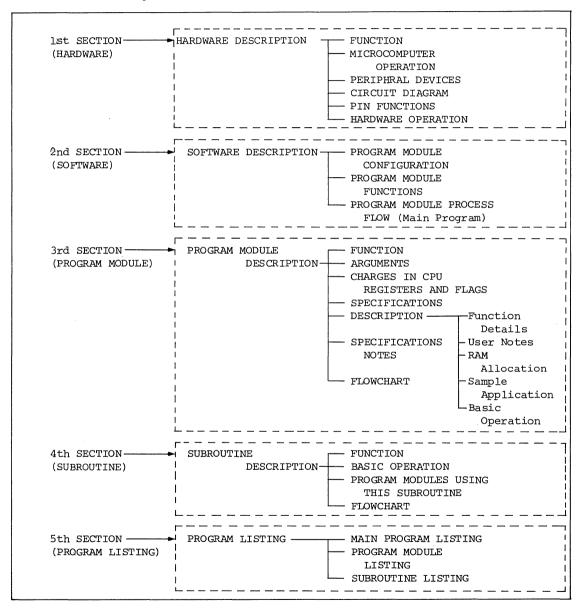

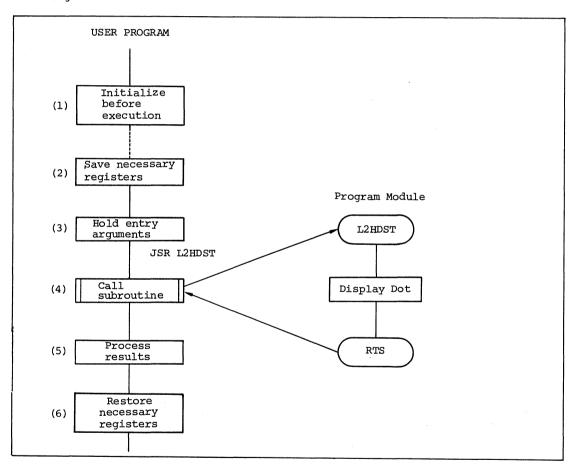

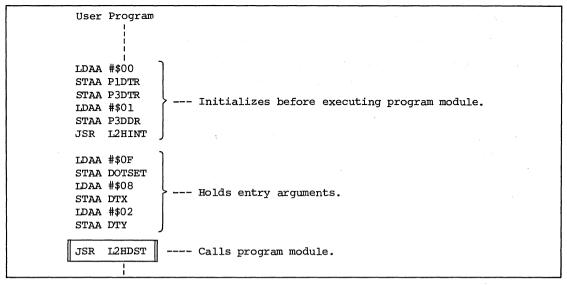

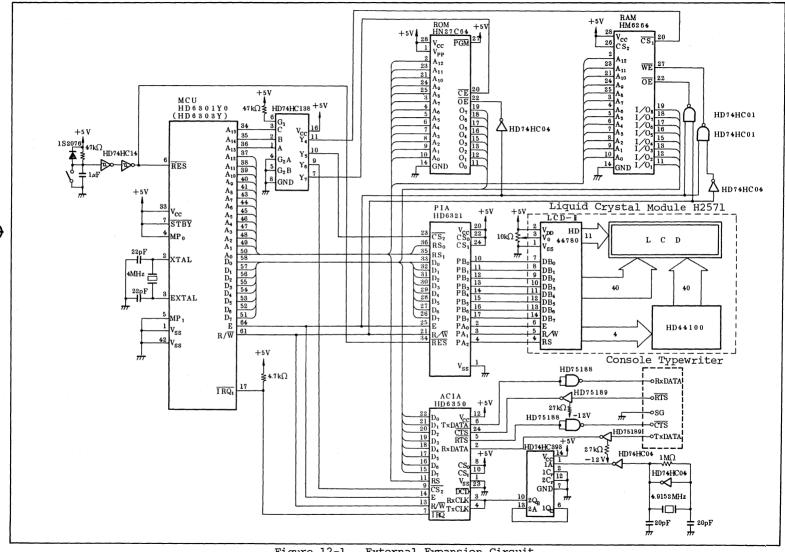

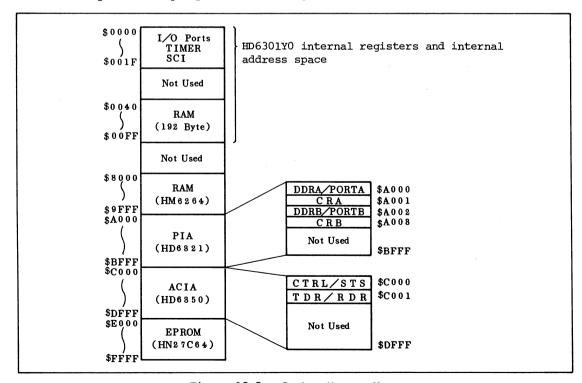

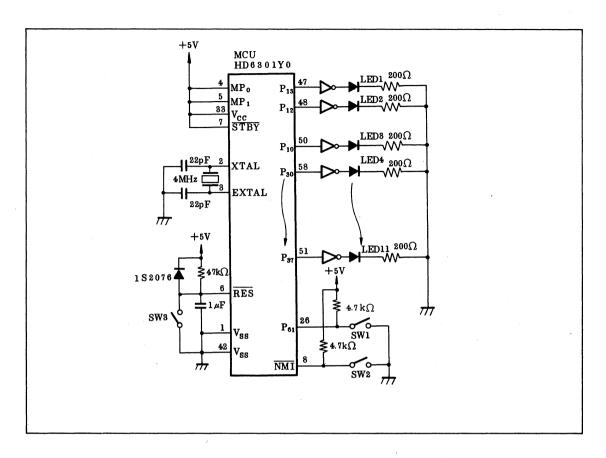

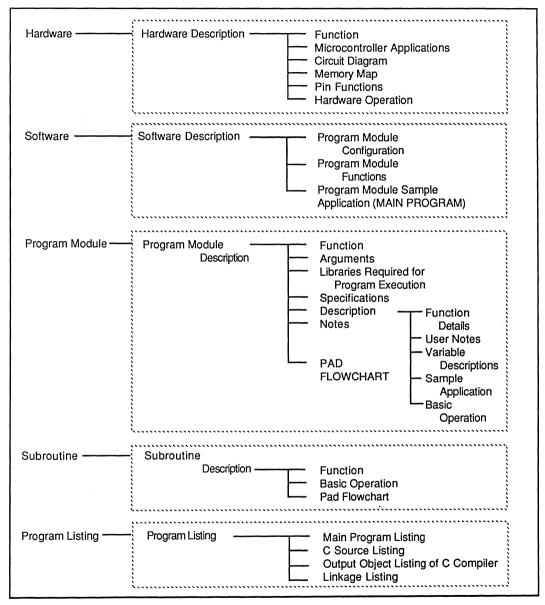

| 3.       | 1st Section (Hardware)                            | 819  |

|----------|---------------------------------------------------|------|

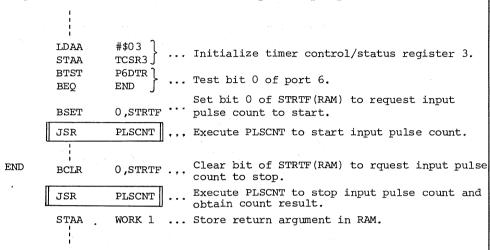

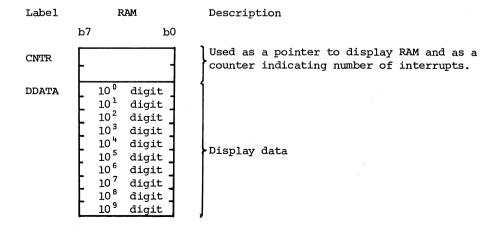

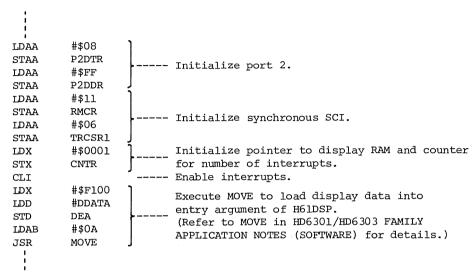

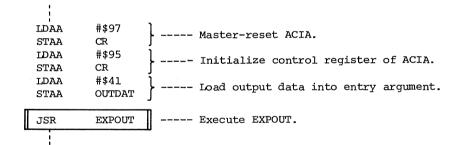

| 4.       | 2nd Section (Software)                            | 823  |

| 5.       | 3rd Section (Program Module)                      | 825  |

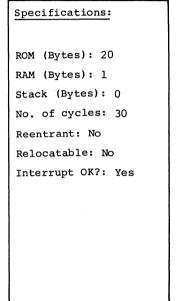

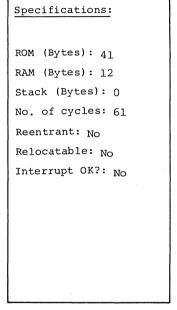

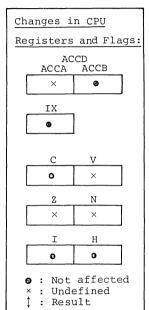

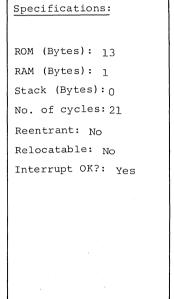

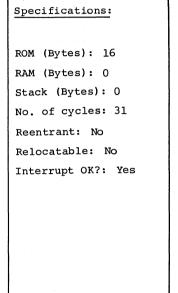

| 5.       | 1 Specification                                   | 826  |

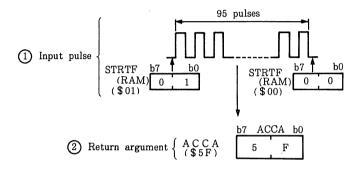

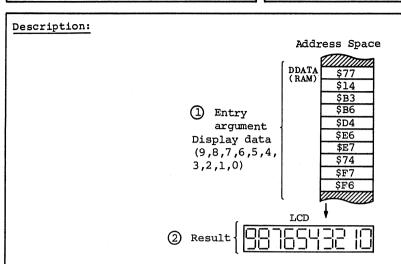

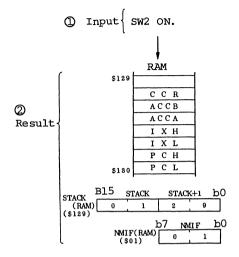

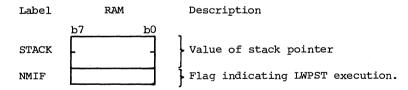

| 5.       | 2 Description                                     | 832  |

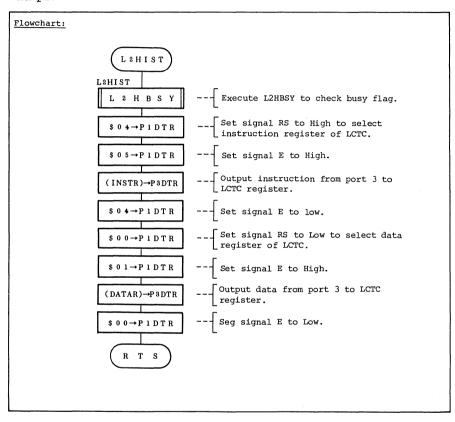

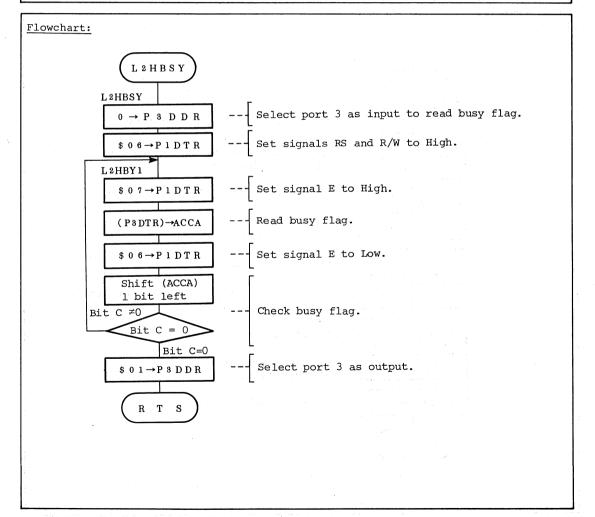

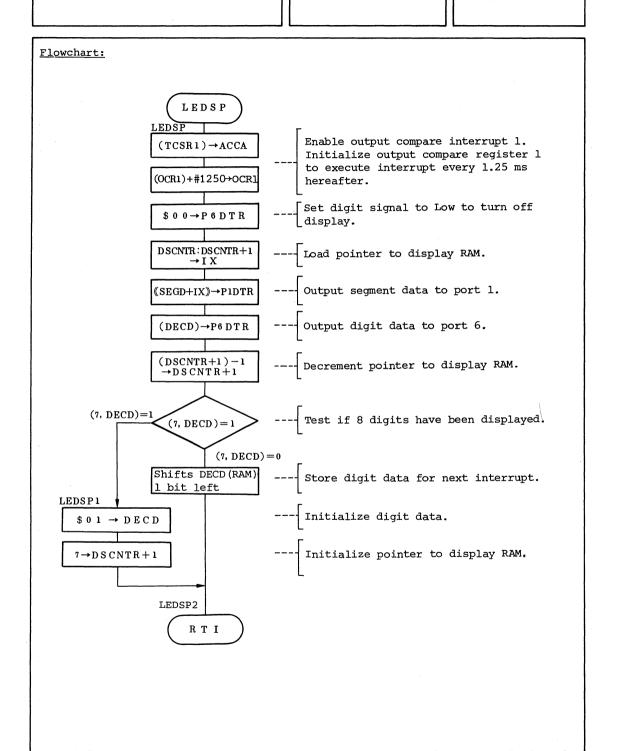

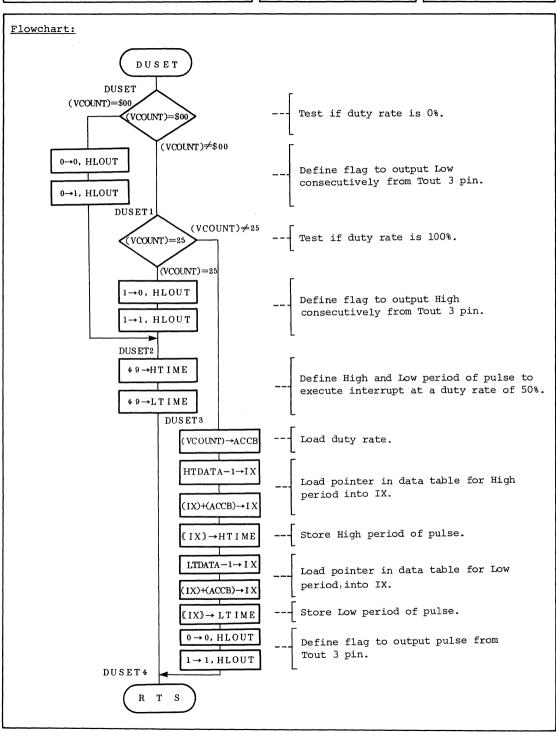

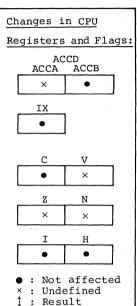

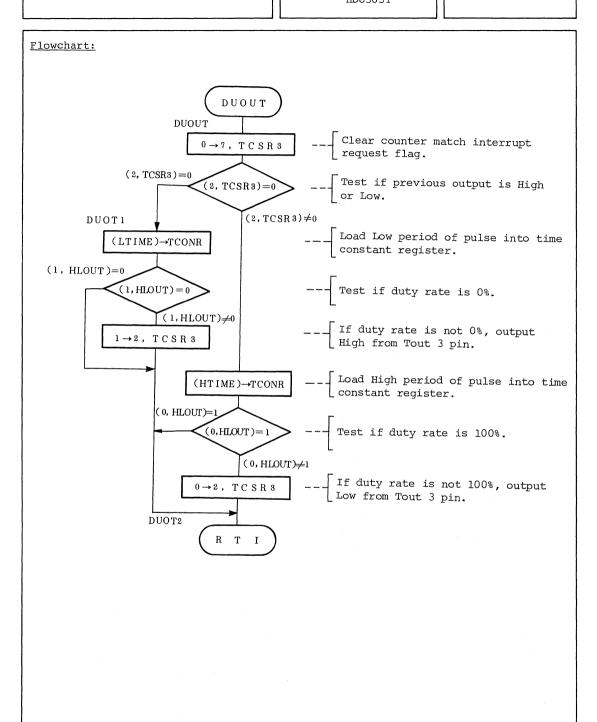

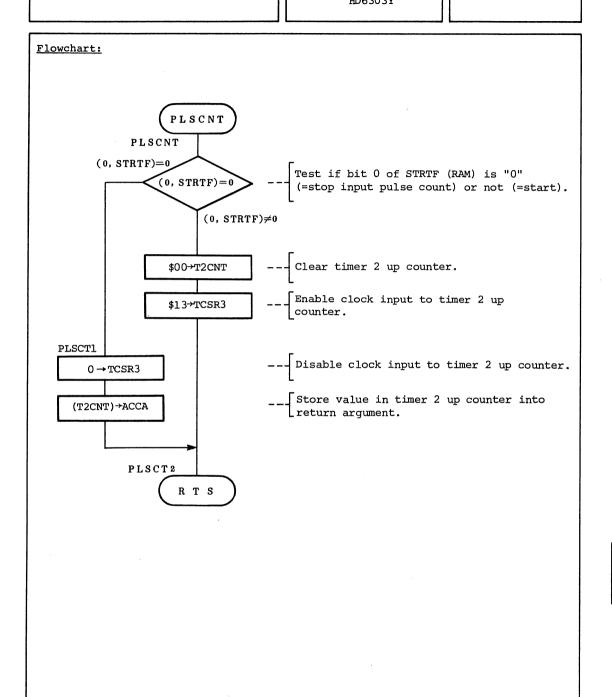

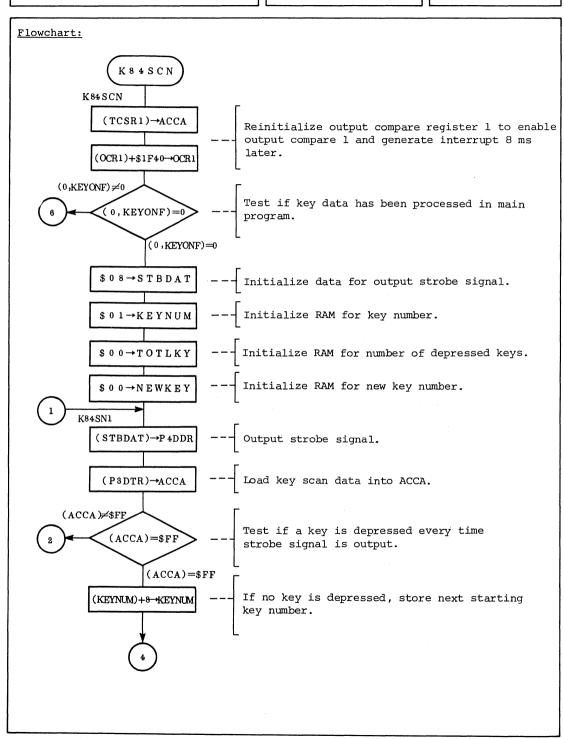

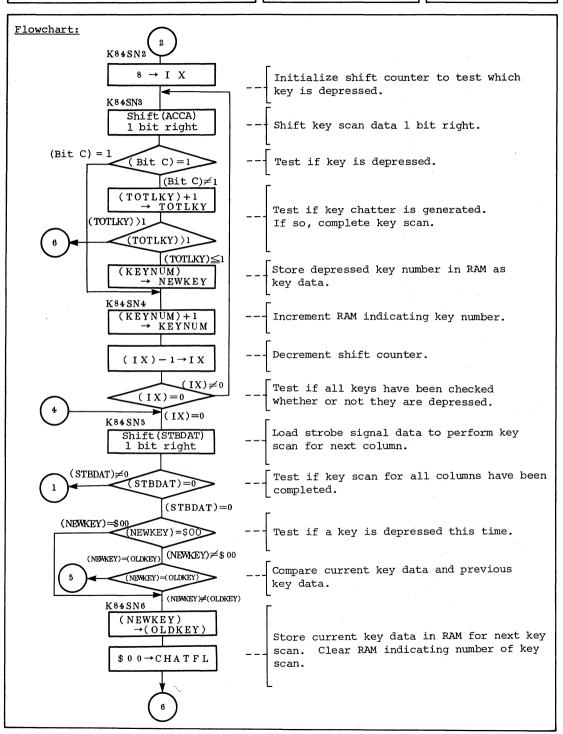

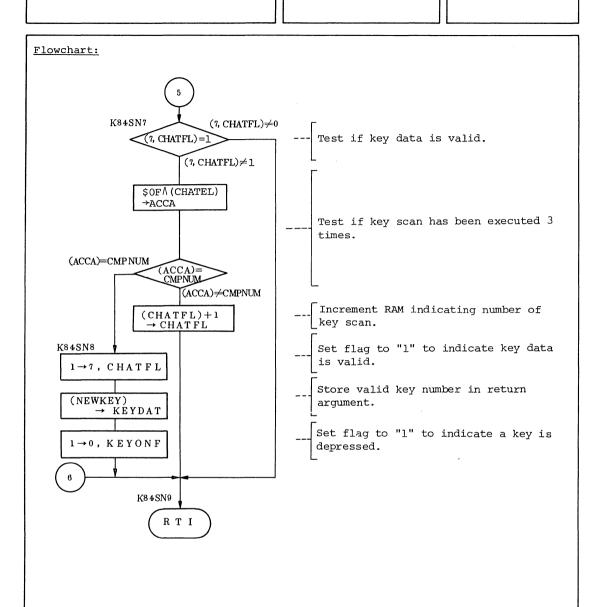

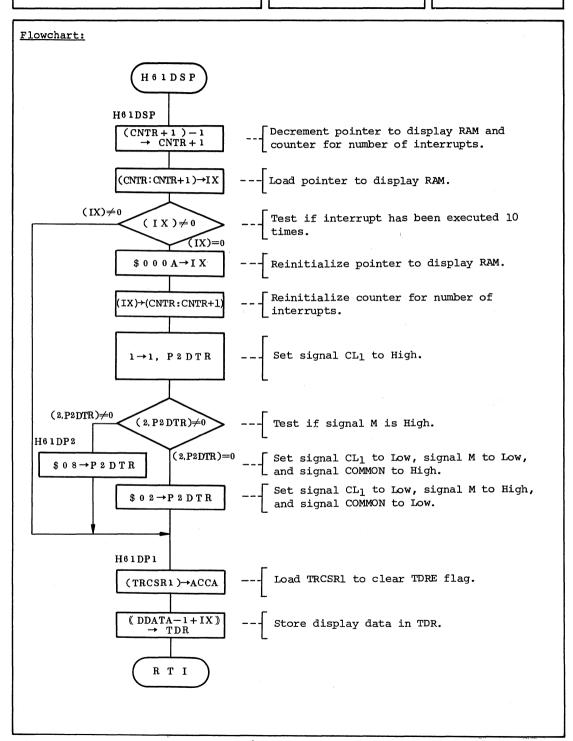

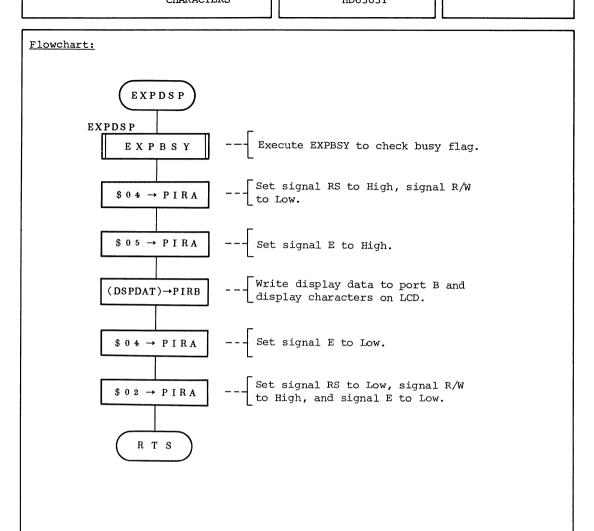

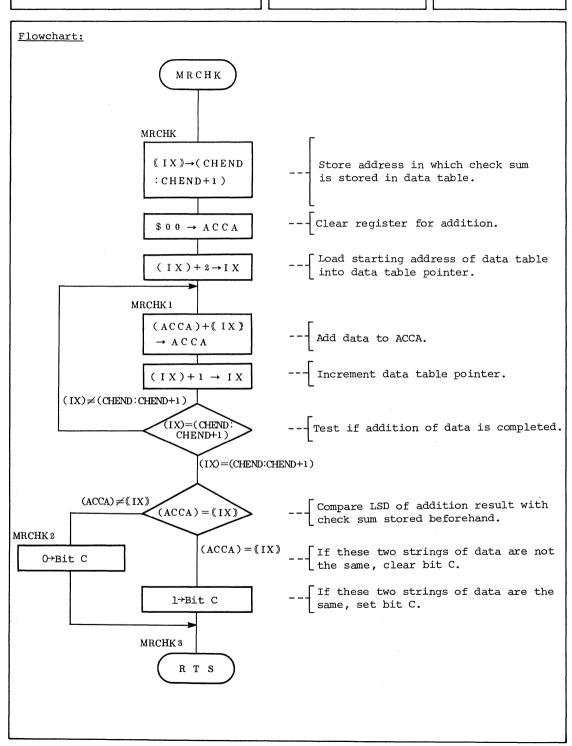

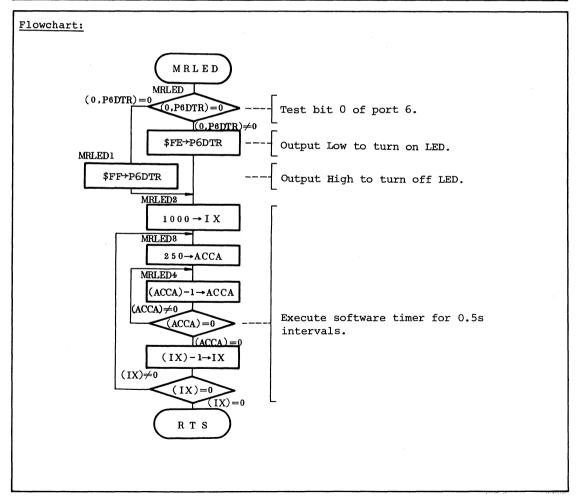

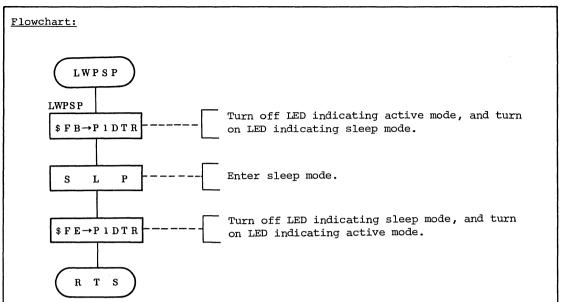

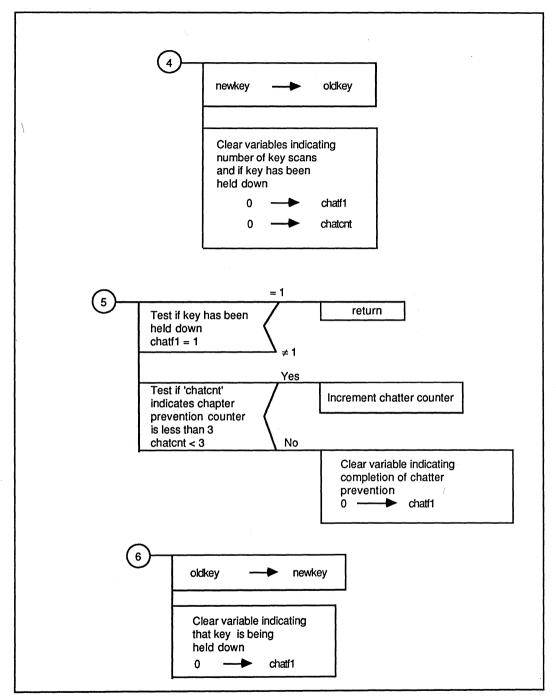

| 5.       | 3 Flowchart                                       | 836  |

| 6.       | 4th Section (Subroutine)                          | 837  |

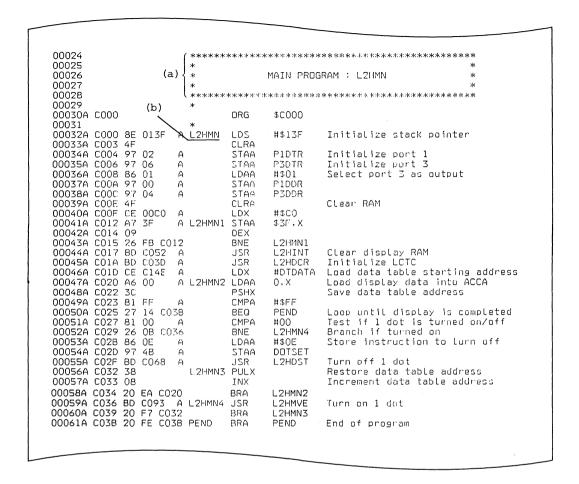

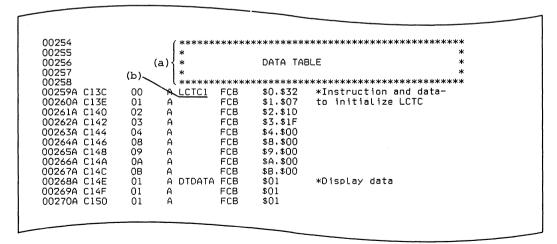

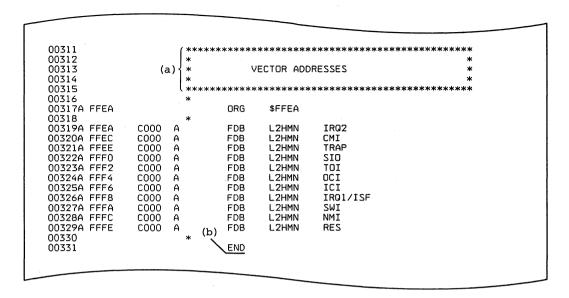

| 7.       | 5th Section (Program Listing)                     | 840  |

| 8.       | Program Module Execution                          | 845  |

| SYS      | STEM APPLICATION EXAMPLES                         | 848  |

| Sys      | tem Application Examples                          | 848  |

| \∩       | PORT APPLICATIONS                                 | 849  |

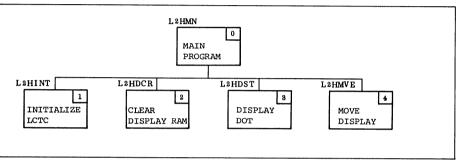

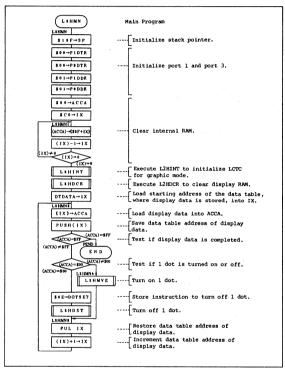

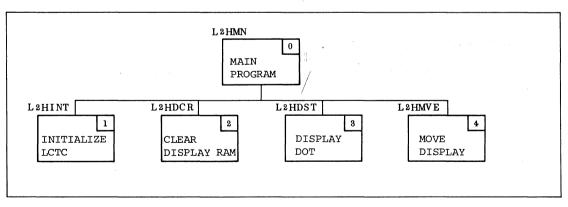

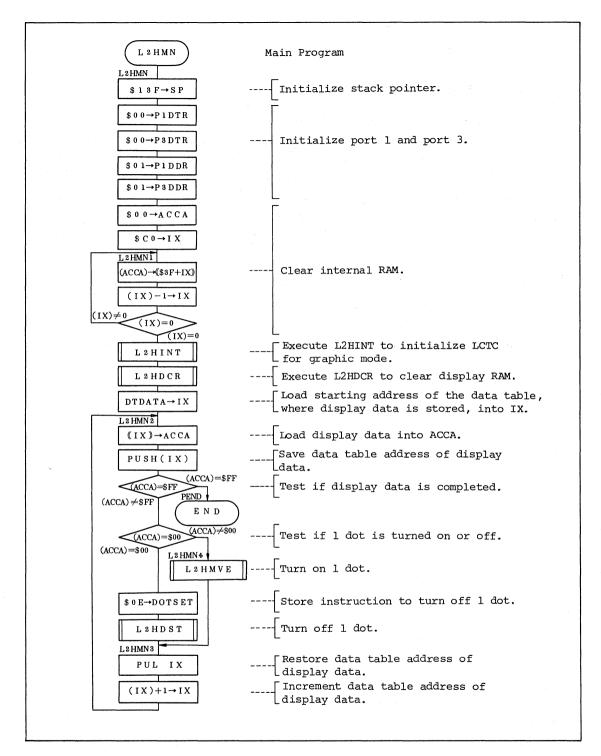

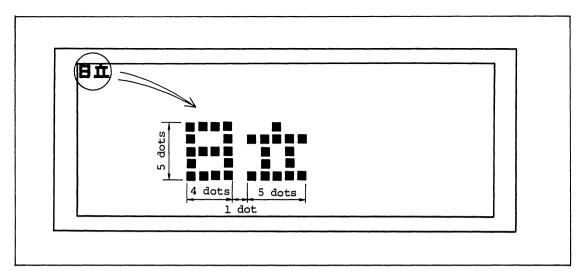

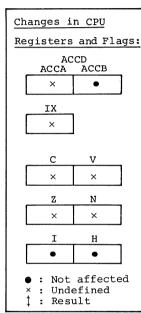

| 1.       | HD61830 (LM200) Graphic Mode                      | 849  |

| 1.<br>2. | Darlington Transistor Drive (LED Dynamic Display) | 883  |

|          |                                                   | 000  |

| TIM      | ER APPLICATIONS                                   | 896  |

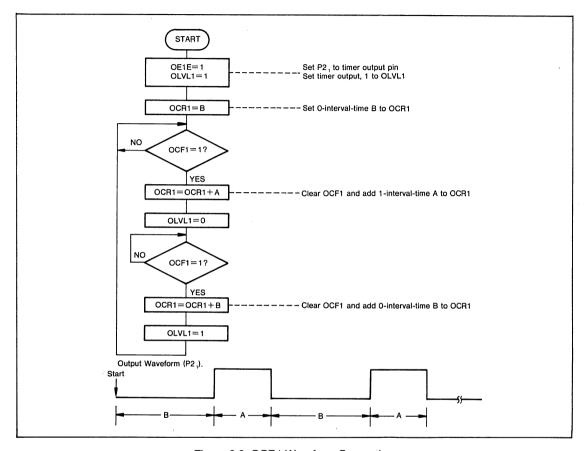

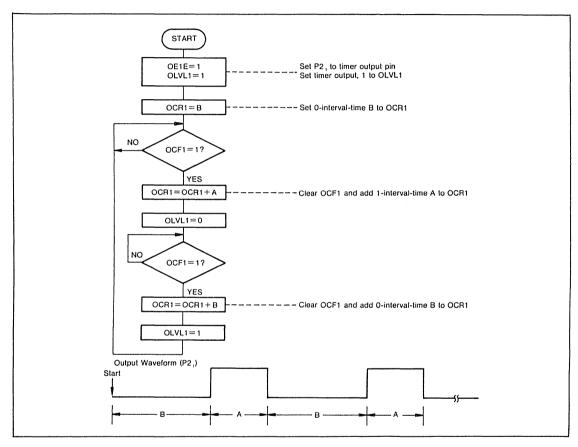

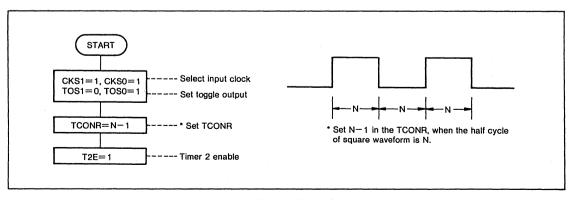

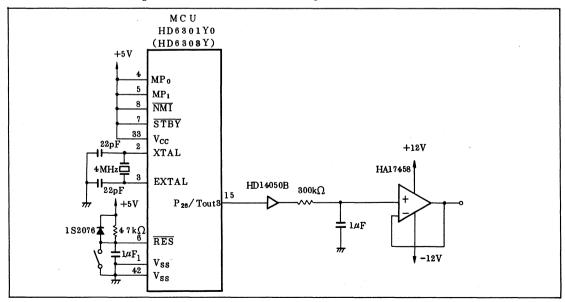

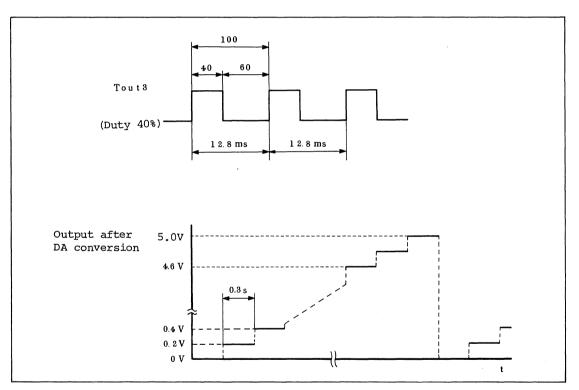

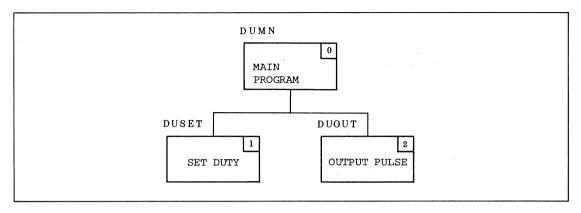

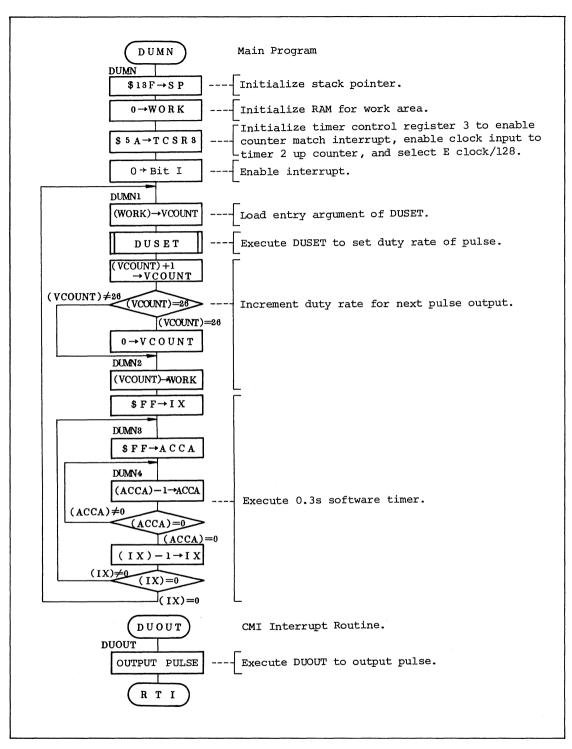

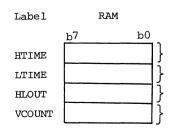

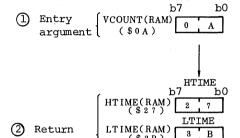

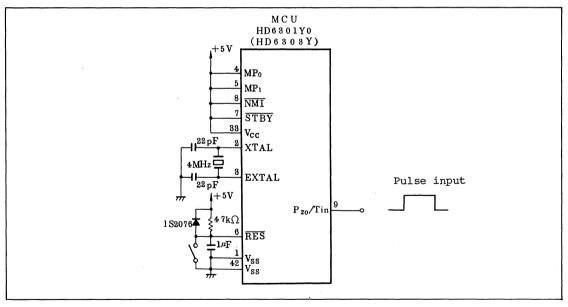

| 3.       | Duty Control of Pulse Output and DA Conversion    | 896  |

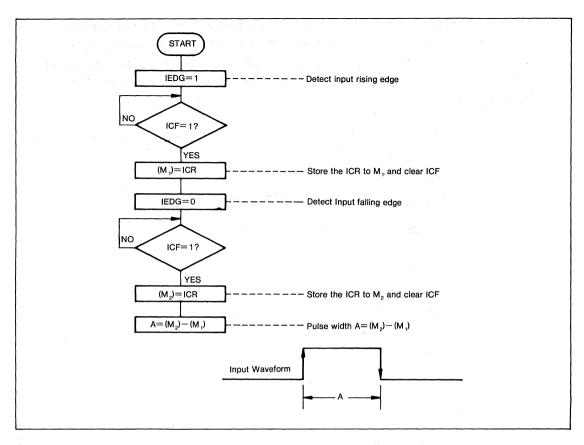

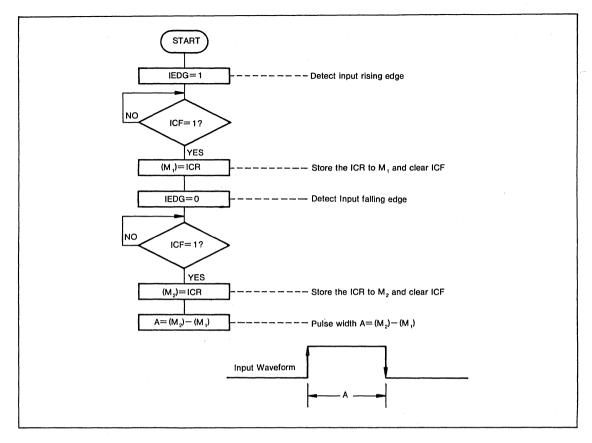

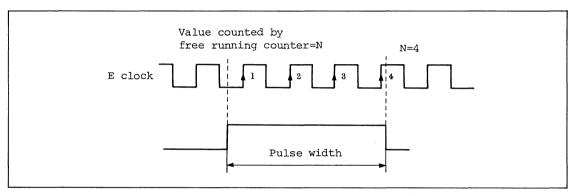

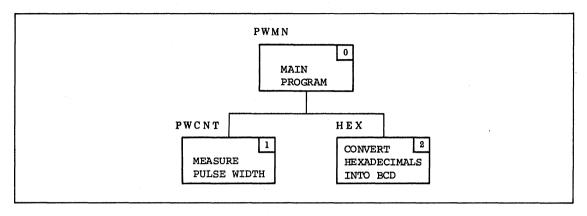

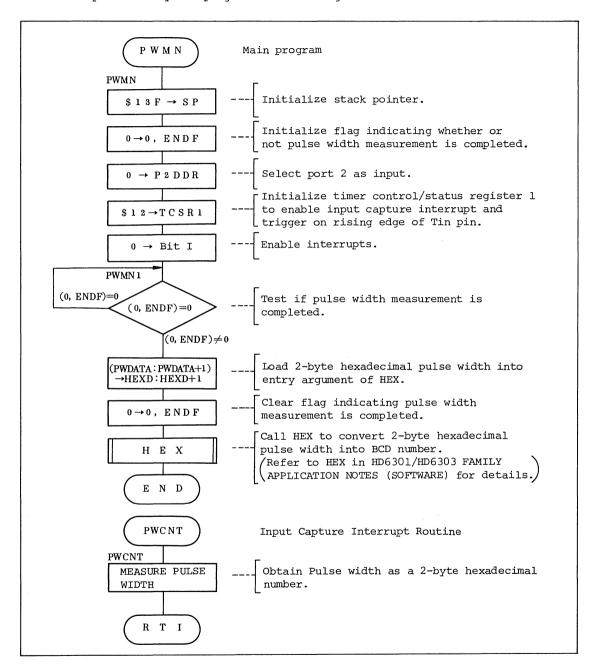

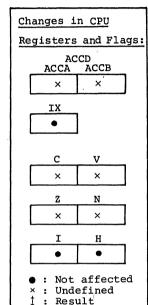

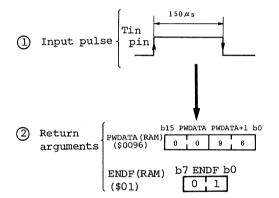

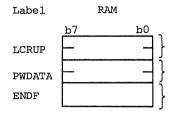

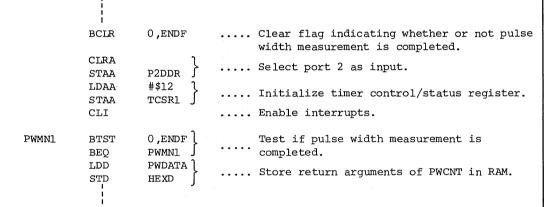

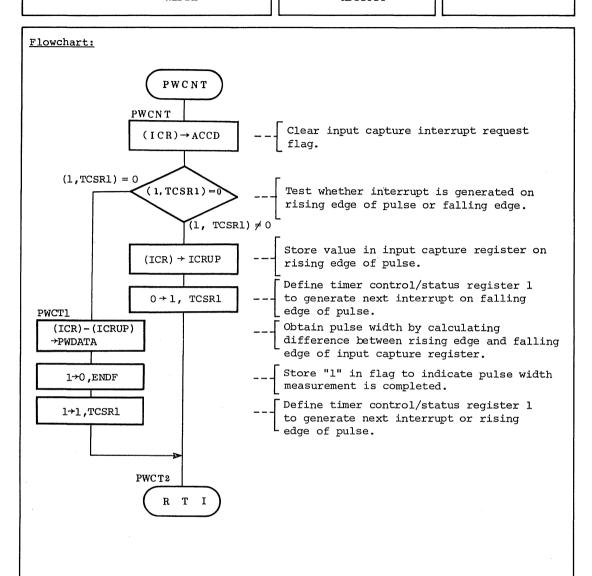

| 4.       | Pulse Width Measurement                           | 912  |

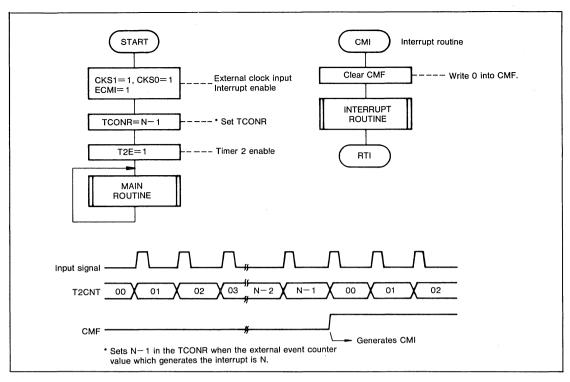

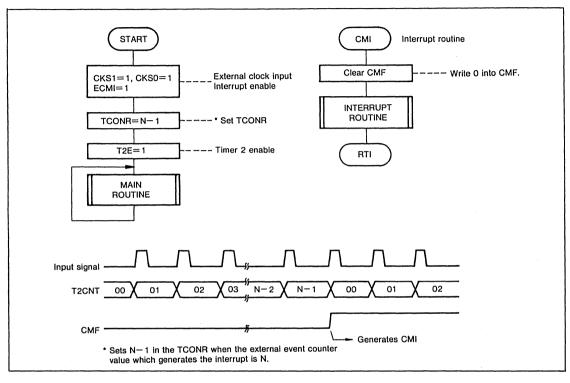

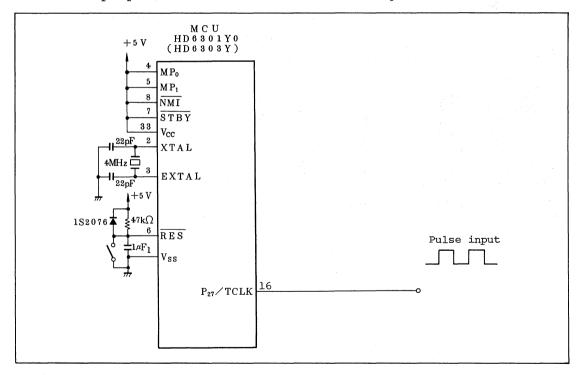

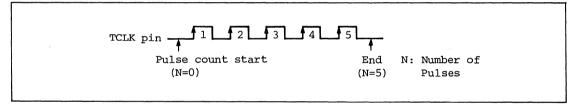

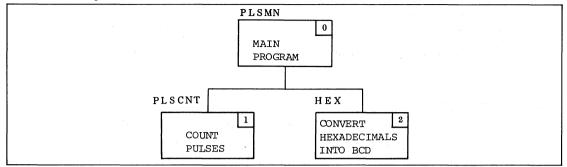

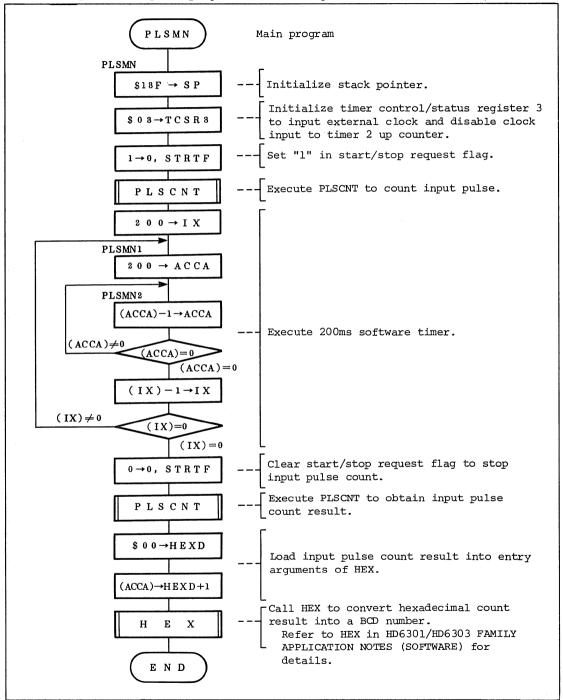

| 5.       | Input Pulse Count                                 | 922  |

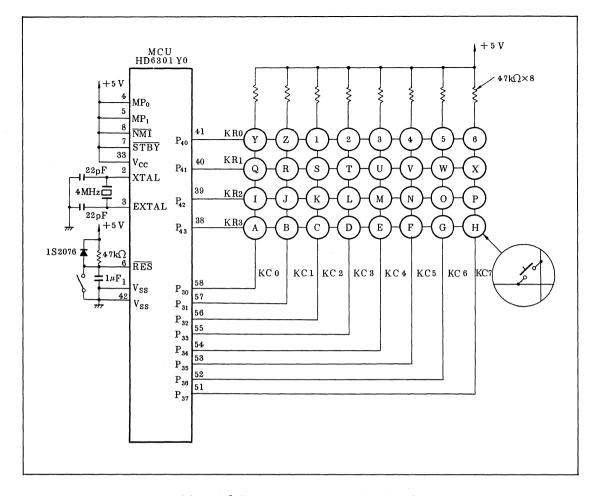

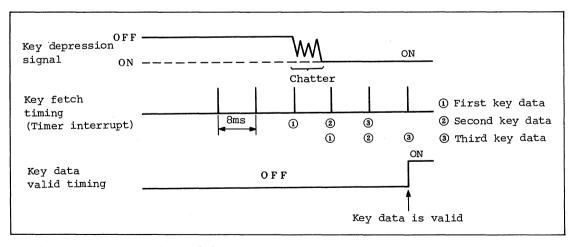

| 6.       | 8 × 4 Key Matrix                                  | 932  |

| INT      | ERRUPT APPLICATION                                | 947  |

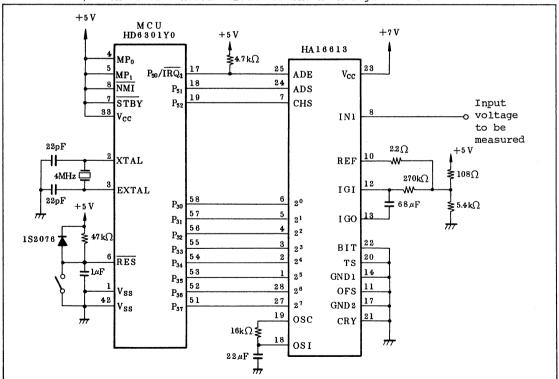

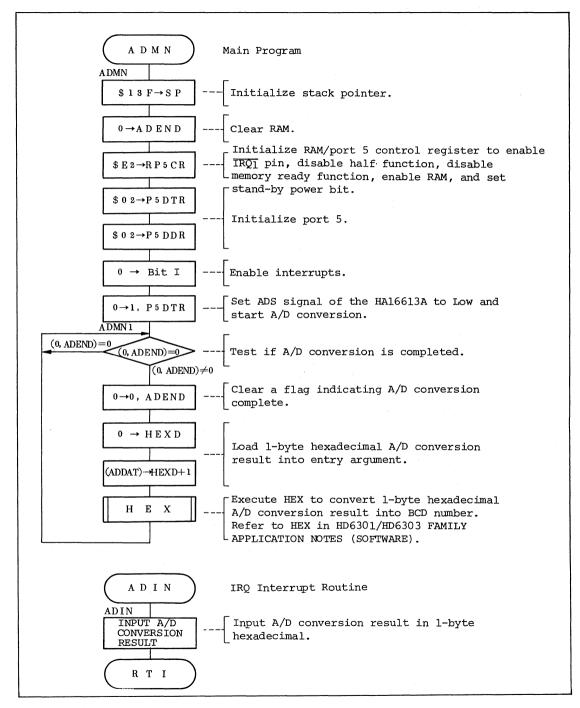

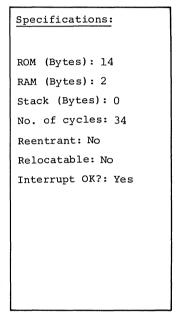

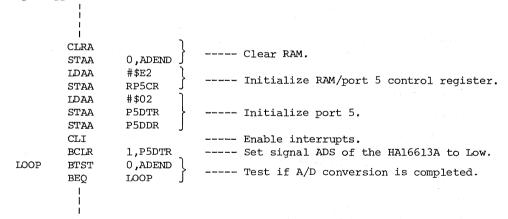

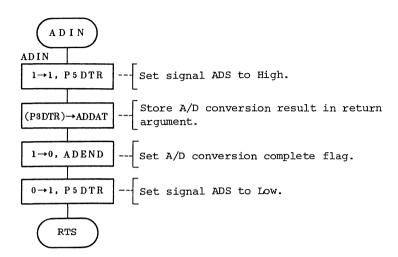

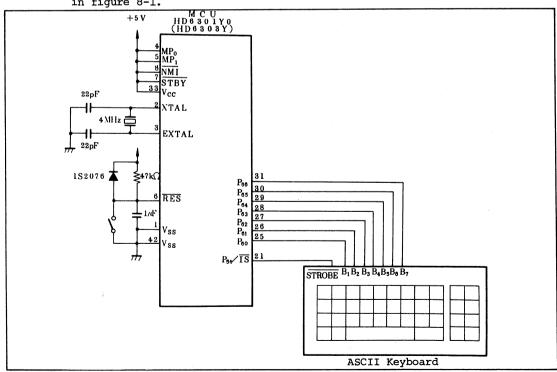

| 7.       | A/D Converter (HA16613A) Control                  | 947  |

|          |                                                   | 0 17 |

| PAF      | RALLEL HANDSHAKE APPLICATIONS                     | 956  |

| 8.       | Standard Keyboard Interface                       | 956  |

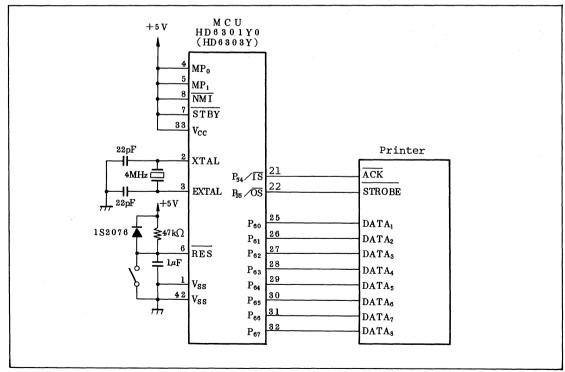

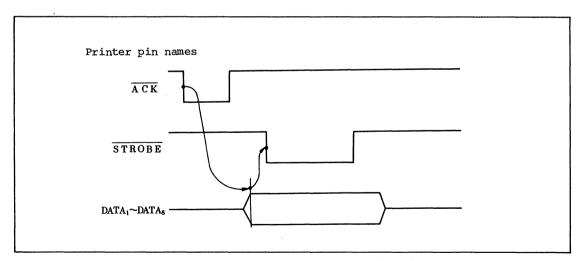

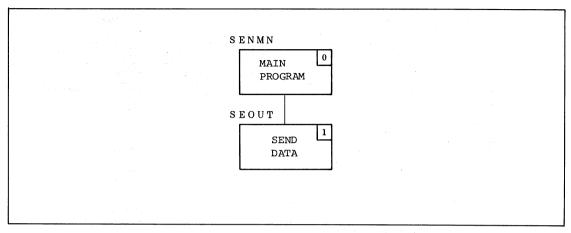

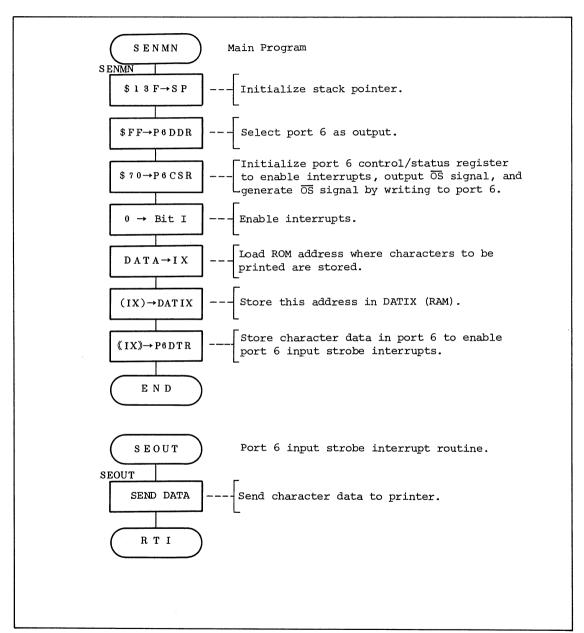

| 9.       | Centronics Interface                              | 970  |

| SCI      | APPLICATIONS                                      | 982  |

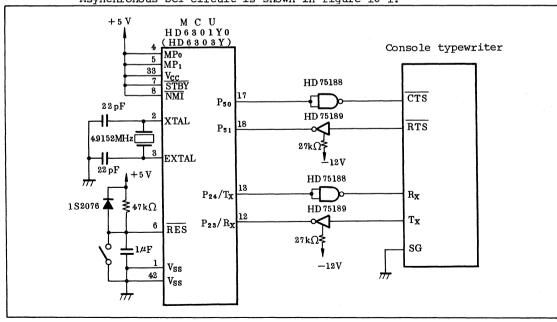

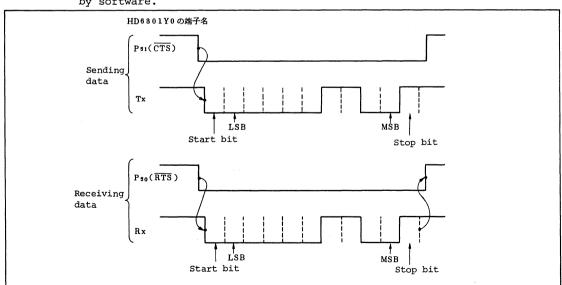

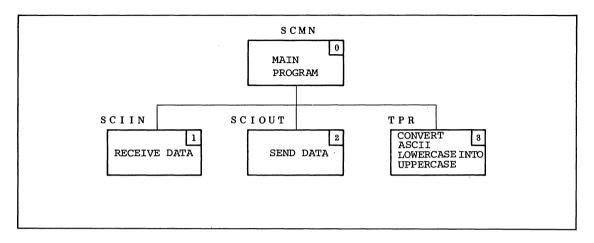

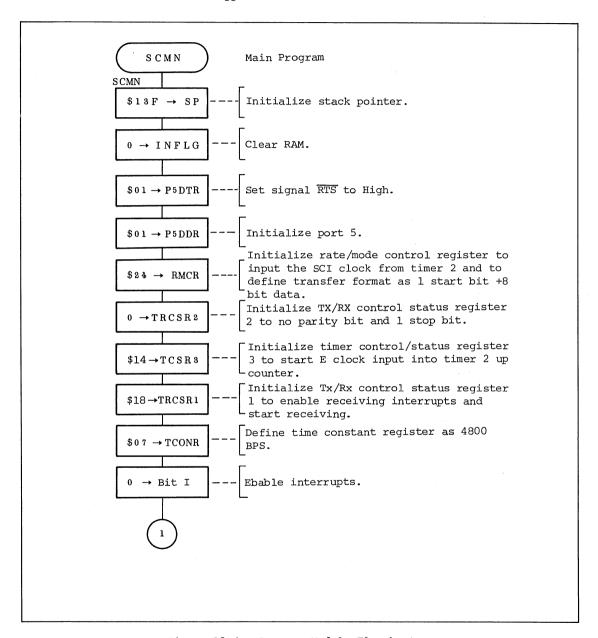

| 10.      | Data Transfer With Asynchronous SCI               | 982  |

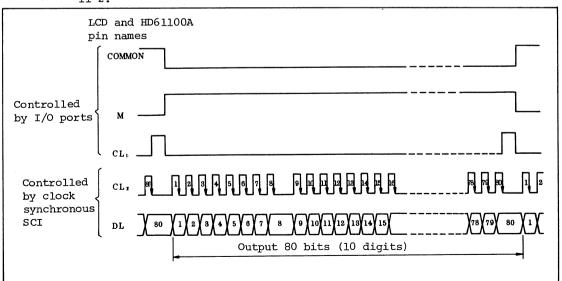

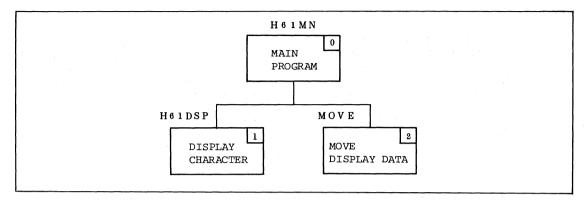

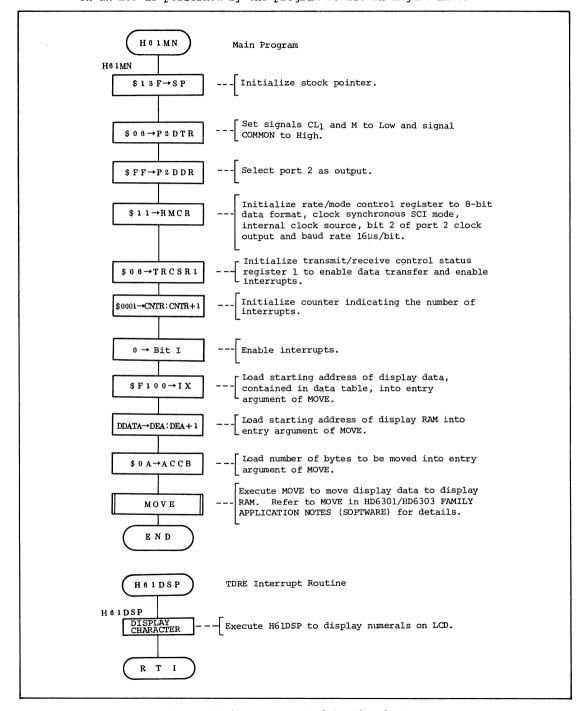

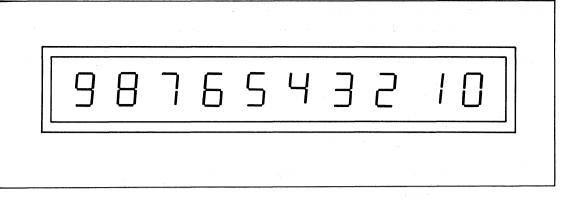

| 11.      | Liquid Crystal Drived (HD61100A) Control          | 998  |

|          |                                                   |      |

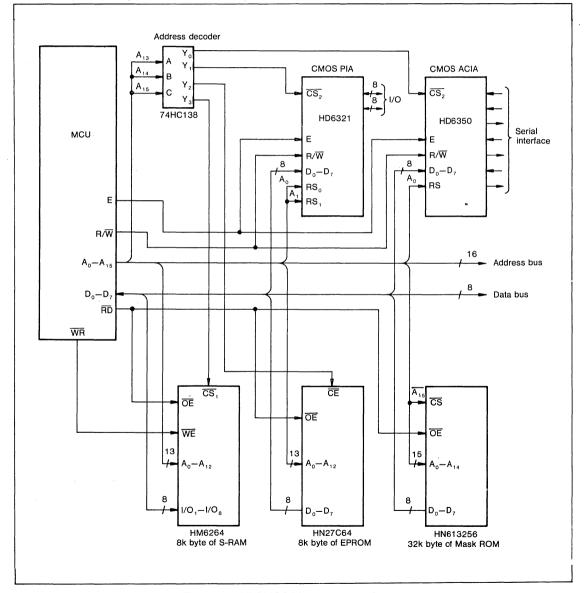

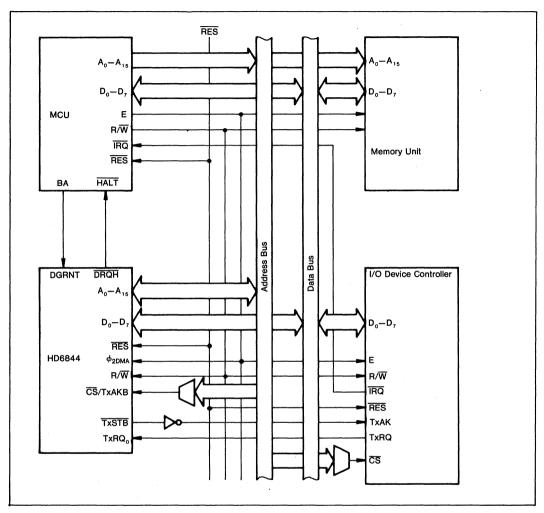

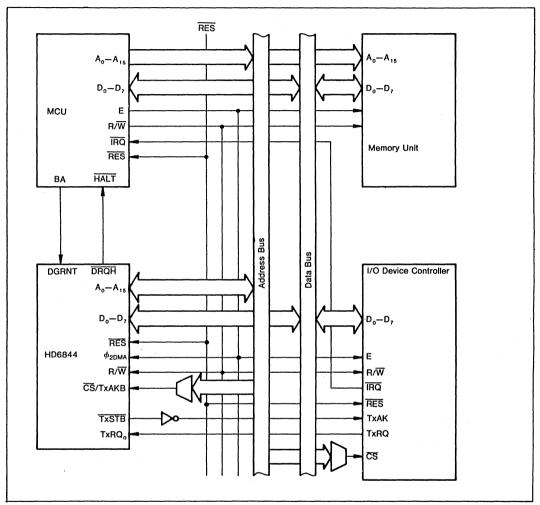

|          | TERNAL EXPANSION APPLICATIONS                     | 1010 |

| 12.      | External Expansion                                | 1010 |

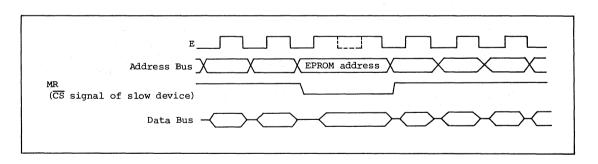

| 13.      | Slow Device Interface                             | 1043 |

| LO       | W POWER DISSIPATION/FAIL-SAFE APPLICATIONS        | 1057 |

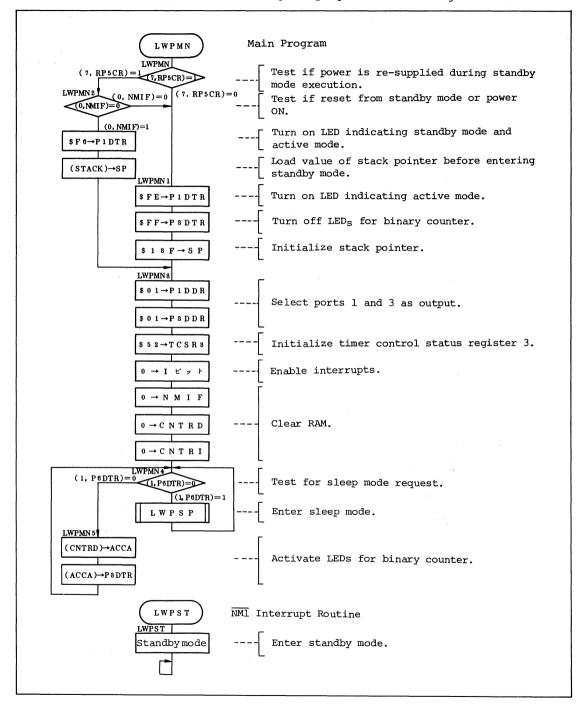

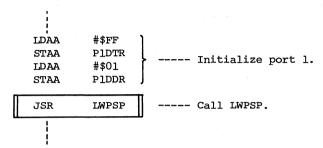

| 14.      | Low Power Dissipation Mode                        | 1057 |

| 15.      | HA1835P Control and Error Detection               | 1074 |

#### Section 9

| C Lan | guage Programming Techniques                     | Page |

|-------|--------------------------------------------------|------|

| 1. HO | W TO USE APPLICATION NOTES                       | 1105 |

| 1.1 H | ardware Section                                  | 1107 |

| 1.1.1 | Function                                         | 1107 |

| 1.1.2 | Microcontroller Applications                     | 1107 |

| 1.1.3 | Circuit Diagram                                  | 1108 |

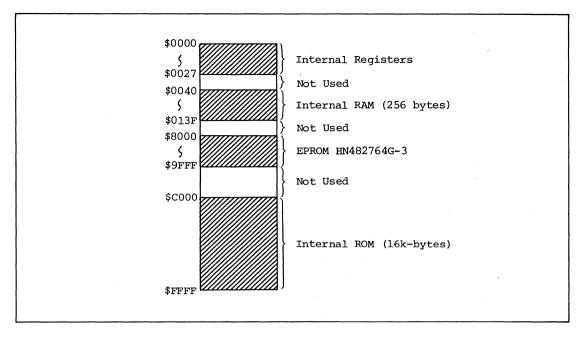

| 1.1.4 | Memory Map                                       | 1109 |

| 1.1.5 | Pin Functions                                    | 1110 |

| 1.1.6 | Hardware Operation                               | 1111 |

| 1.2 S | oftware Section                                  | 1112 |

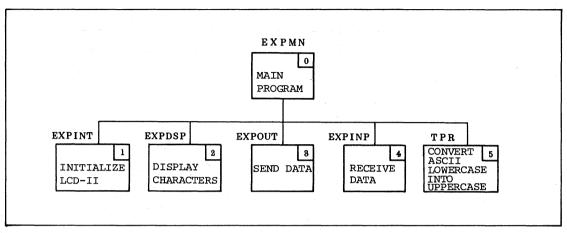

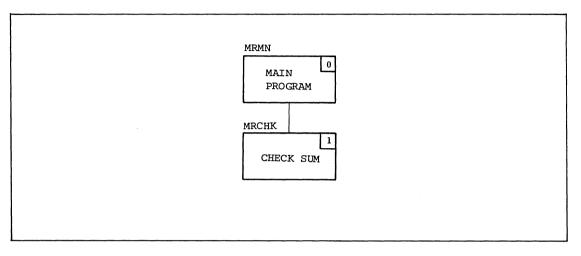

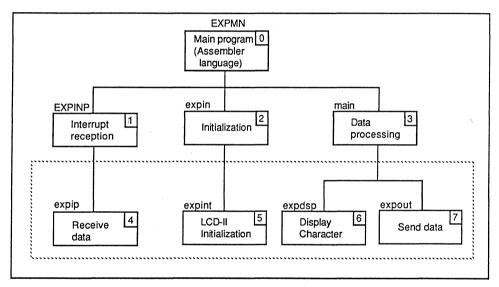

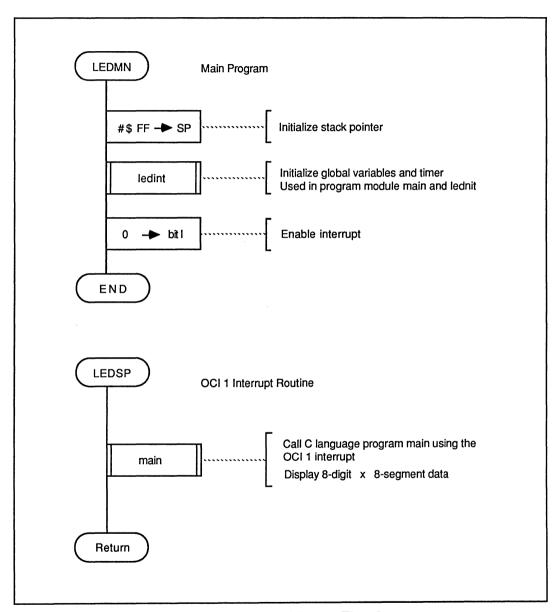

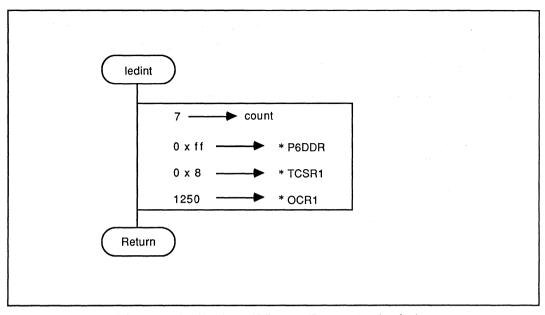

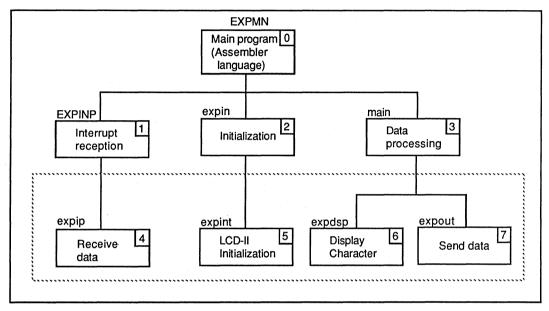

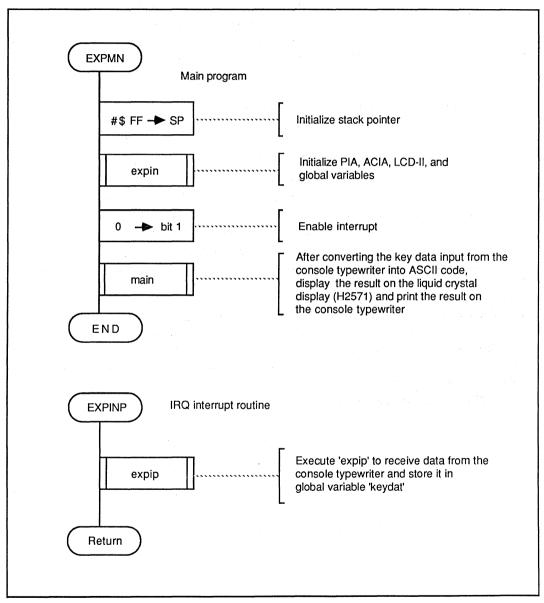

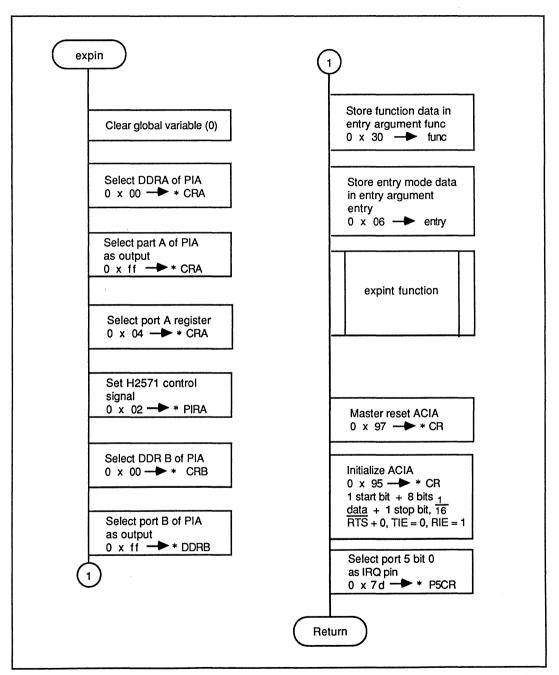

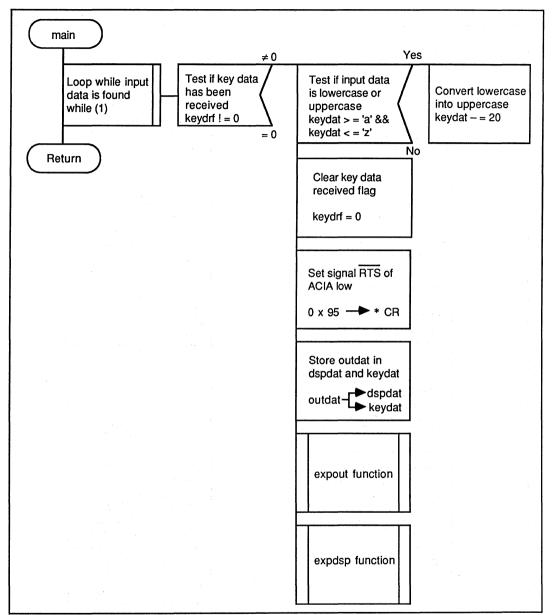

| 1.2.1 | Program Module Configuration                     | 1112 |

| 1.2.2 | Program Module Functions                         | 1113 |

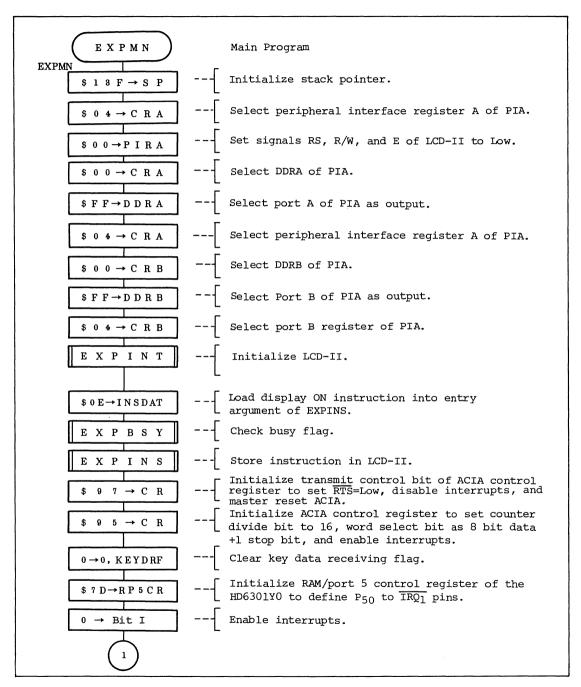

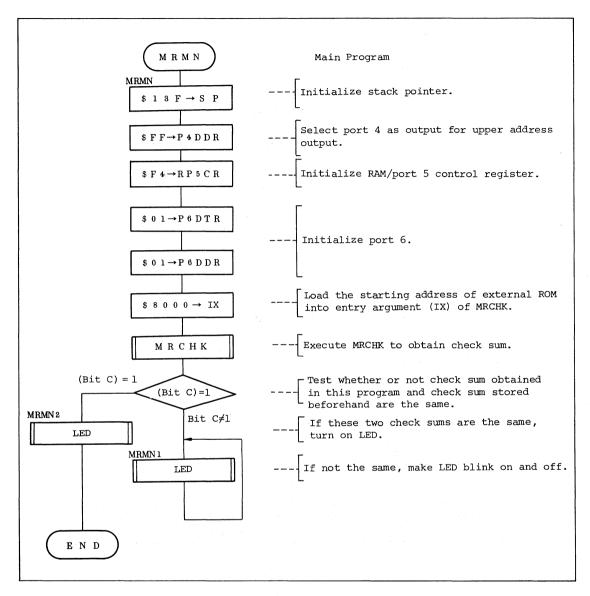

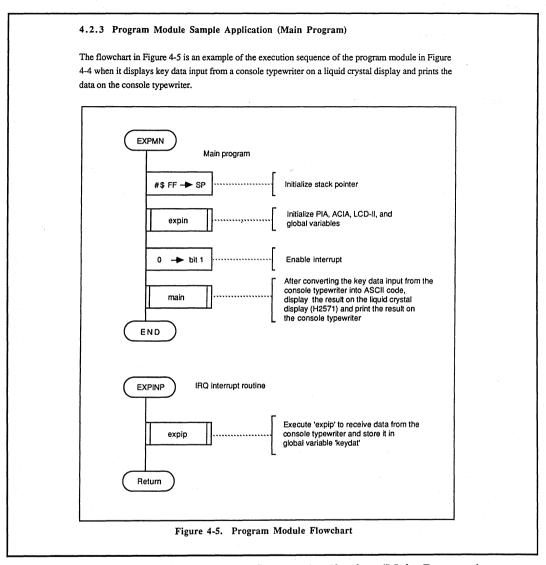

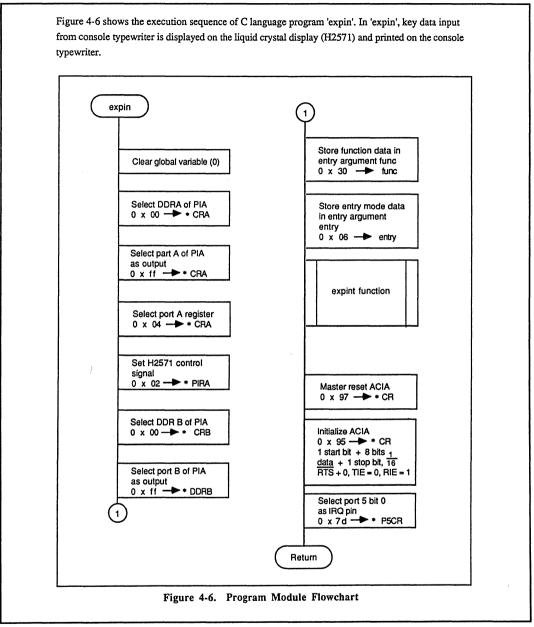

| 1.2.3 | Program Module Sample Application (Main Program) | 1114 |

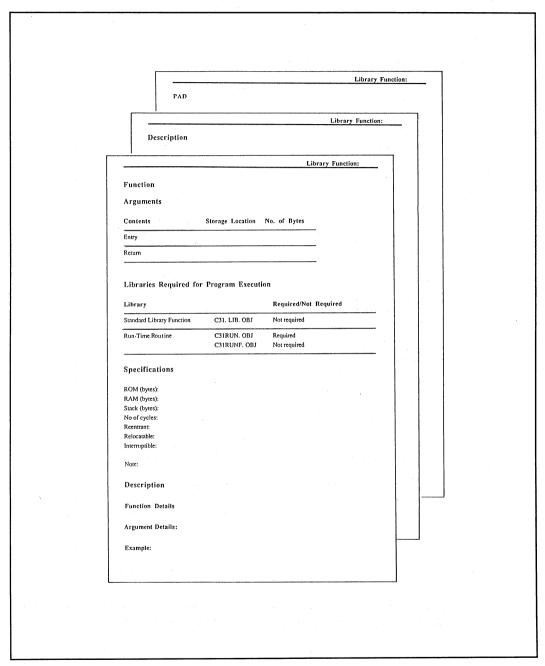

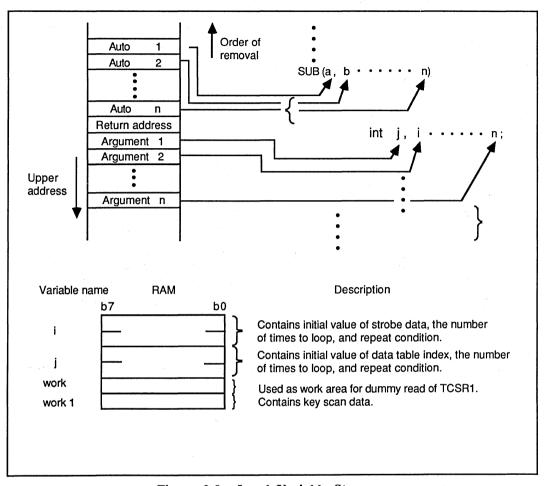

| 1.3 P | rogram Module Section                            | 1116 |

| 1.3.1 | Page Heading                                     | 1117 |

| 1.3.2 | Function                                         | 1117 |

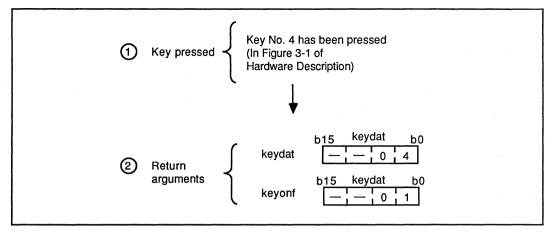

| 1.3.3 | Arguments                                        | 1117 |

| 1.3.4 | Libraries Required for Program Execution         | 1118 |

| 1.3.5 | Specifications                                   | 1119 |

| 1.3.6 | Description                                      | 1120 |

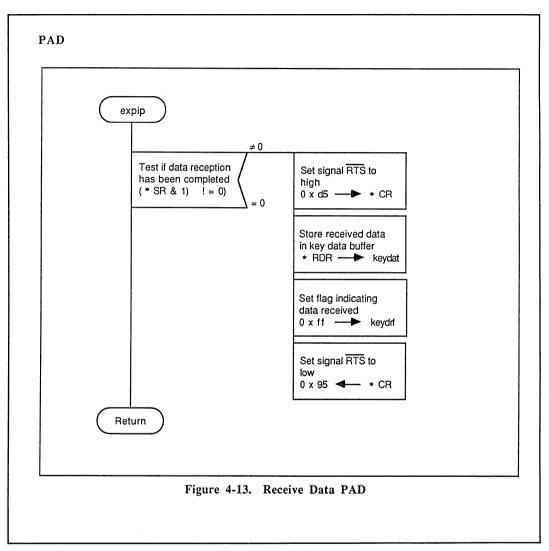

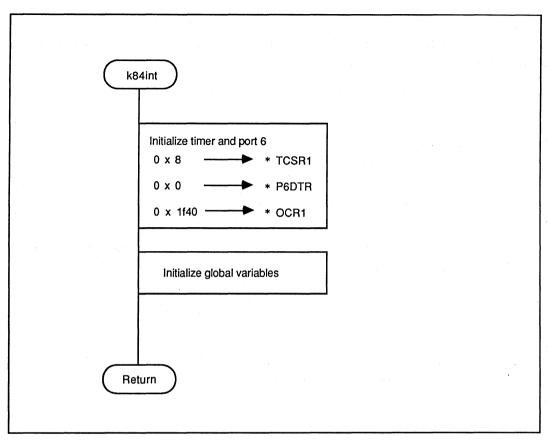

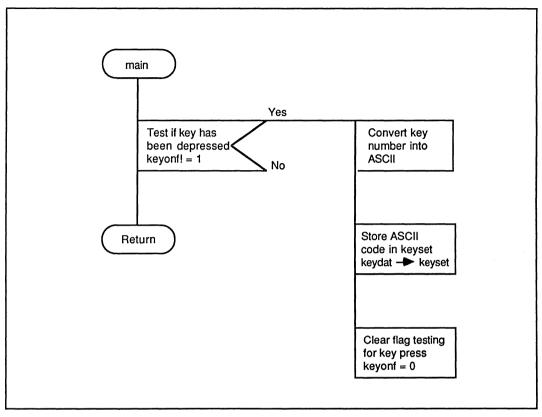

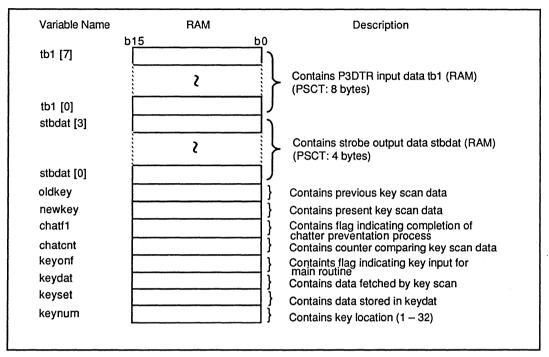

| 1.3.7 | PAD                                              | 1123 |

| 1.4 S | ubroutine Section                                | 1124 |

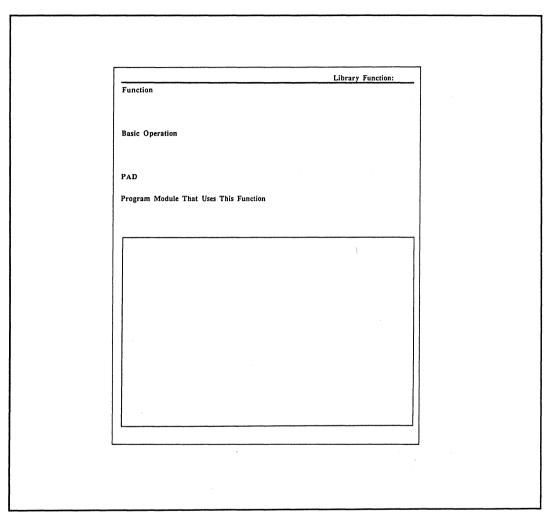

| 1.4.1 | Page Heading                                     | 1125 |

| 1.4.2 | Function                                         | 1125 |

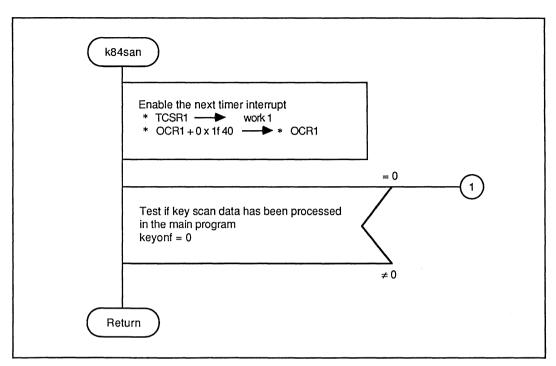

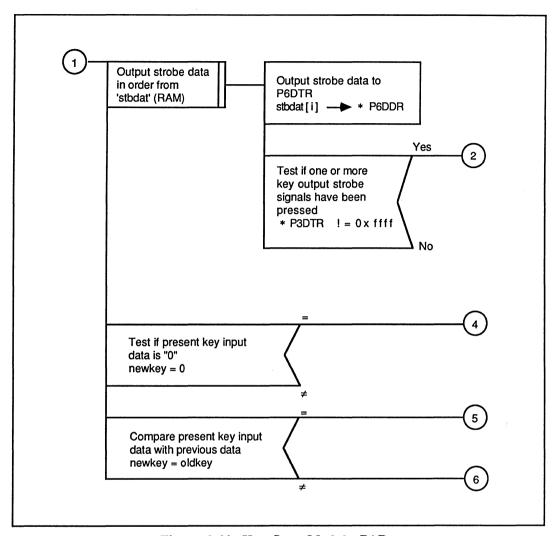

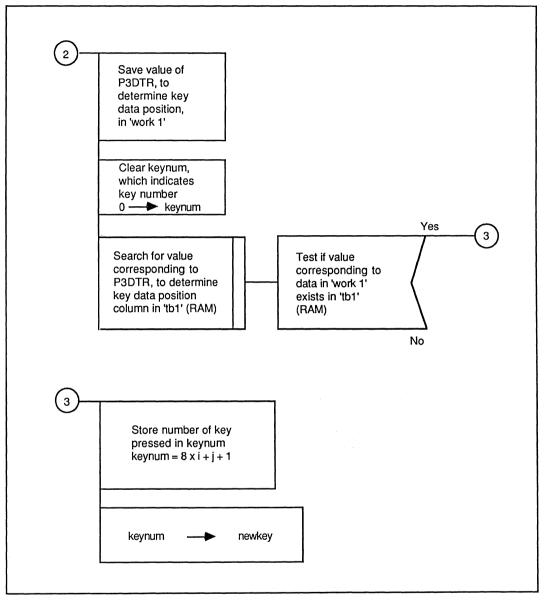

| 1.4.3 | Basic Operation                                  | 1125 |

| 1.4.4 | Program Modules That Use This Function           | 1126 |

| 1.4.5 | PAD                                              | 1126 |

| 1.5 P | rogram Listing Section                           | 1127 |

| 1.5.1 | Page Heading                                     | 1127 |

| 1.5.2 | Function                                         | 1128 |

| 1.5.3 | Output Object Listing of C Compliler             | 1131 |

| 1.5.4 | Linkage Listing                                  | 1132 |

| 1.6 P | rogram Module Use                                | 1135 |

| 1.7 Pad Symbols Description                            | 1137 |

|--------------------------------------------------------|------|

| 1.8 Symbols                                            | 1138 |

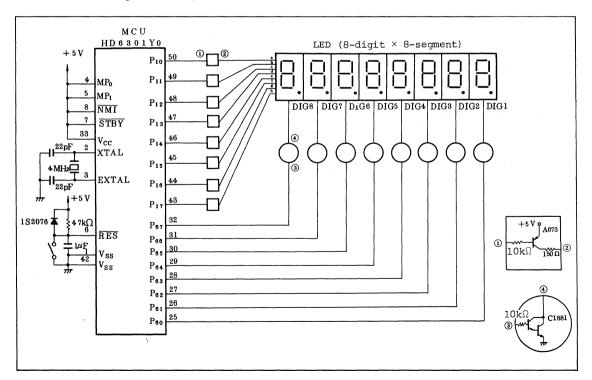

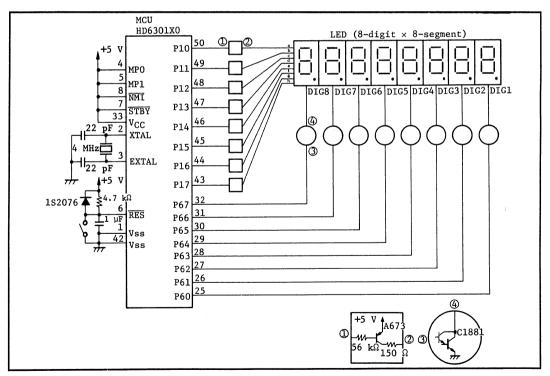

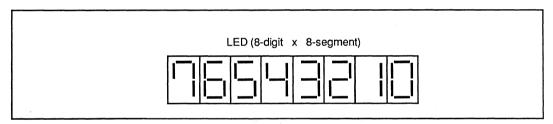

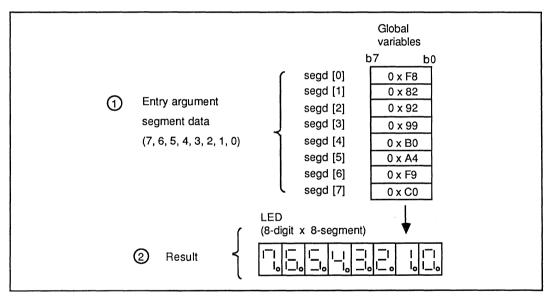

| 2. DARLINGTON TRANSISTOR DRIVE (LED DYNAMIC DISPLAY)   | 1139 |

| 2.1 Hardware Description                               | 1139 |

| 2.1.1 Function                                         | 1139 |

| 2.1.2 Microcontroller Applications                     | 1139 |

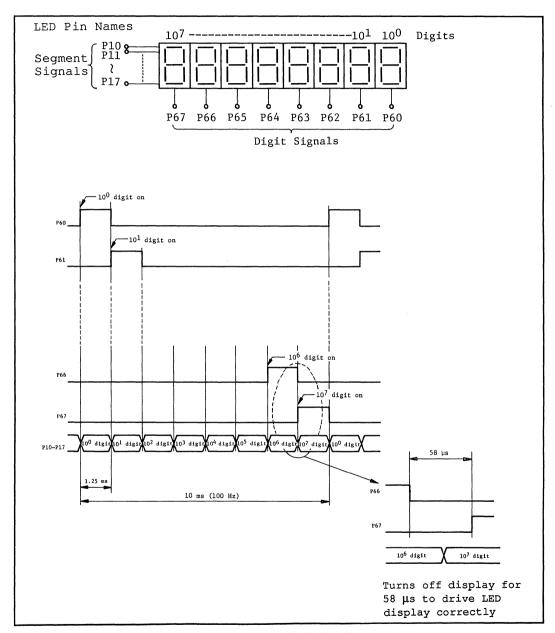

| 2.1.3 Circuit Diagram                                  | 1139 |

| 2.1.4 Pin Functions                                    | 1140 |

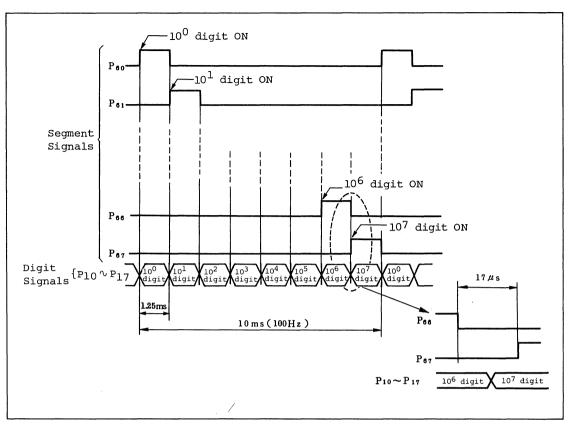

| 2.1.5 Hardware Operation                               | 1141 |

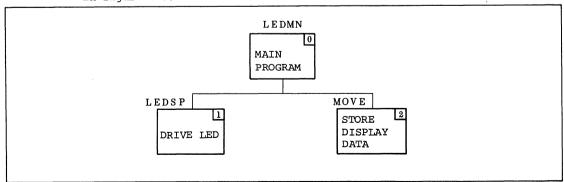

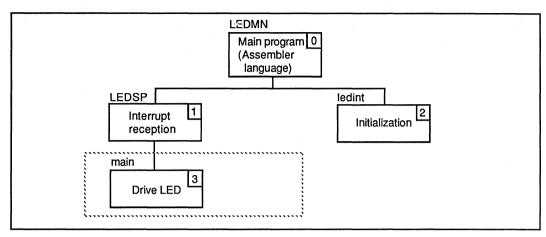

| 2.2 Software Description                               | 1142 |

| 2.2.1 Program Module Configuration                     | 1142 |

| 2.2.2 Program Module Functions                         | 1142 |

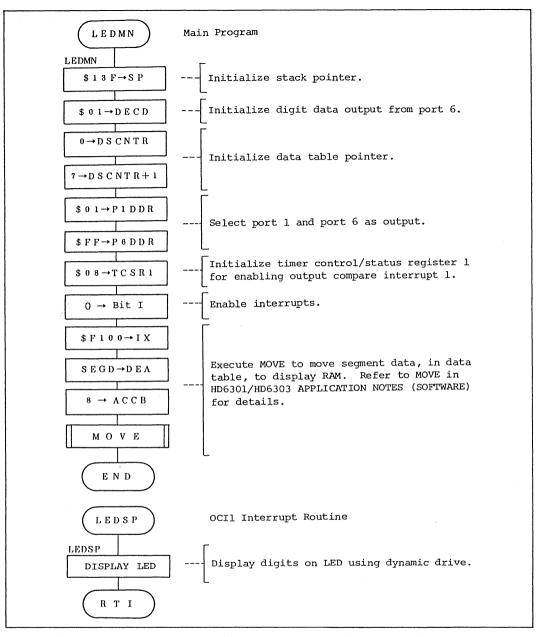

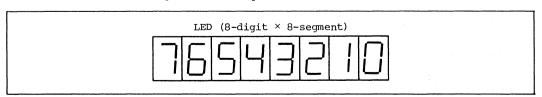

| 2.2.3 Program Module Sample Application (Main Program) | 1143 |

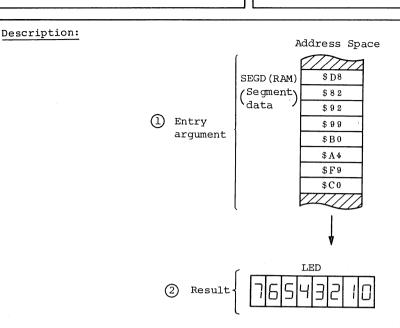

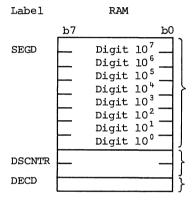

| 2.3 Program Module Description                         | 1144 |

| 2.4 Program Listing                                    | 1152 |

| 2.4.1 Main Program Listing                             | 1152 |

| 2.4.2 C Source Listing                                 | 1153 |

| 2.4.3 Output Object Listing of C Complier              | 1154 |

| 2.4.4 Linkage Listing                                  | 1157 |

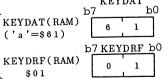

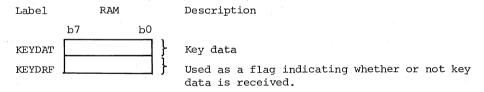

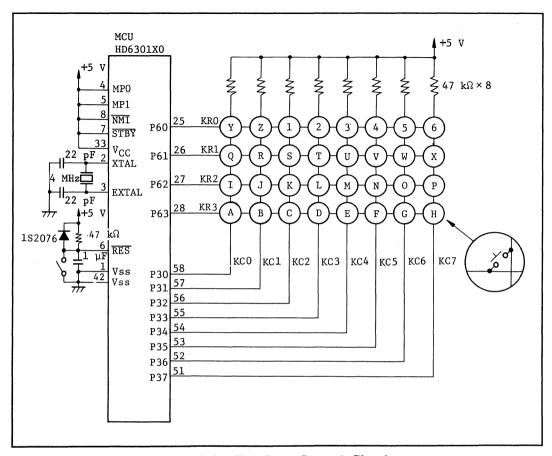

| 3. 8×4 KEY MATRIX                                      | 1159 |

| 3.1 Hardware Description                               | 1159 |

| 3.1.1 Function                                         | 1159 |

| 3.1.2 Microcontroller Applications                     | 1159 |

| 3.1.3 Circuit Diagram                                  | 1160 |

| 3.1.4 Pin Functions                                    | 1161 |

| 3.1.5 Hardware Operation                               | 1161 |

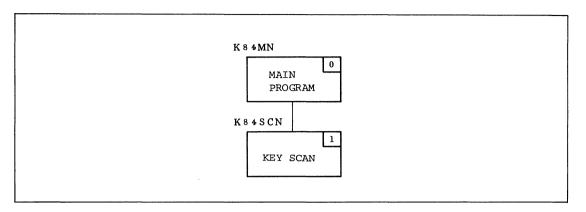

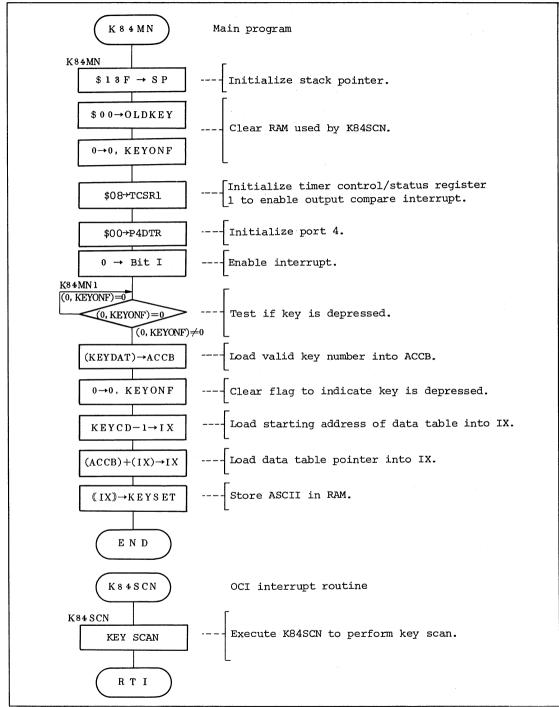

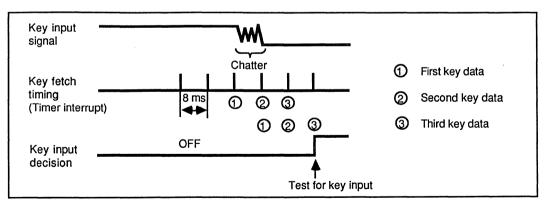

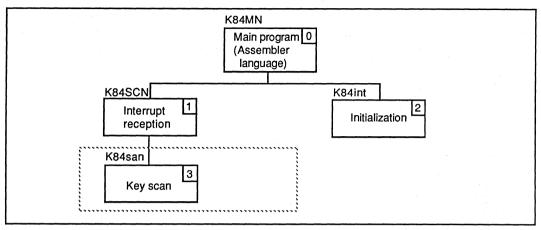

| 3.2 Software Description                               | 1162 |

| 3.2.1 Program Module Configuration                     | 1162 |

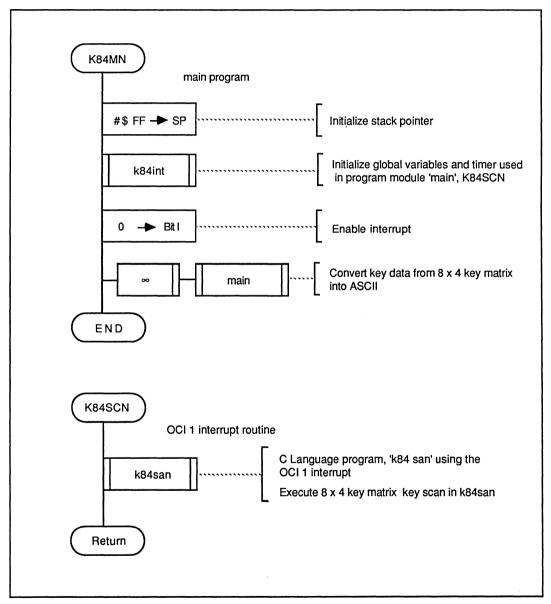

| 3.2.2 Program Module Functions                         | 1162 |

| 3.2.3 Program Module Sample Application (Main Program) | 1163 |

| 3.3 Program Module Description                         | 1165 |

| 3.4 Program Listing                                    | 1177 |

| 3.4.1 Main Program Listing                             | 1177 |

|                                                        |      |

| 3.4.1                  | Main Program Listing                                                                                                     | 1177 |

|------------------------|--------------------------------------------------------------------------------------------------------------------------|------|

| 3.4.2                  | C Source Listing                                                                                                         | 1178 |

| 3.4.3                  | Output Object Listing of C Compiler                                                                                      | 1180 |

| 3.4.4                  | Linkage Listing                                                                                                          | 1185 |

| 4 · EV                 | TERNAL EXPANSION                                                                                                         | 1187 |

| 4. LA                  | TENNAL EXPANSION                                                                                                         | 1107 |

| 4.1 H                  | ardware Description                                                                                                      | 1187 |

| 4.1.1                  | Function                                                                                                                 | 1187 |

| 4.1.2                  | Microcontroller Applications                                                                                             | 1187 |

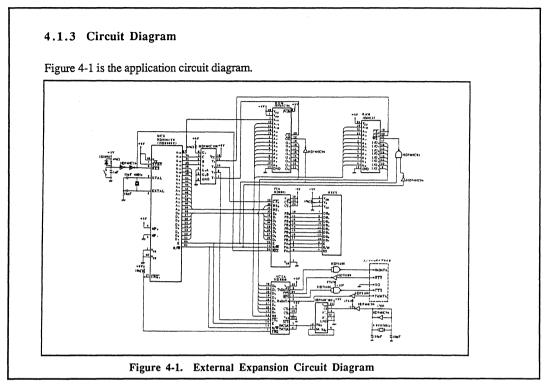

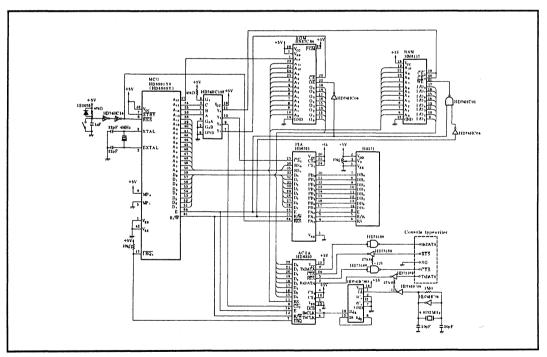

| 4.1.3                  | Circuit Diagram                                                                                                          | 1187 |

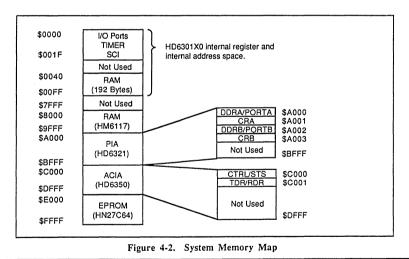

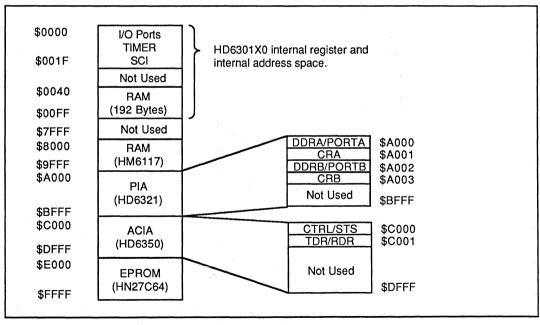

| 4.1.4                  | Memory Map                                                                                                               | 1188 |

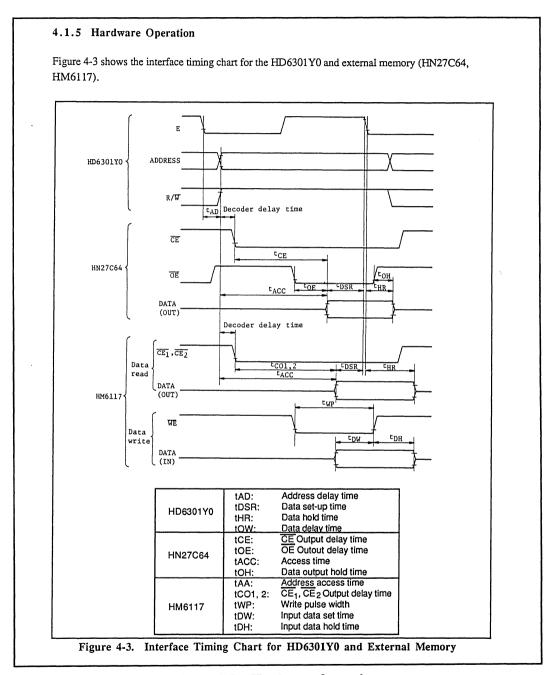

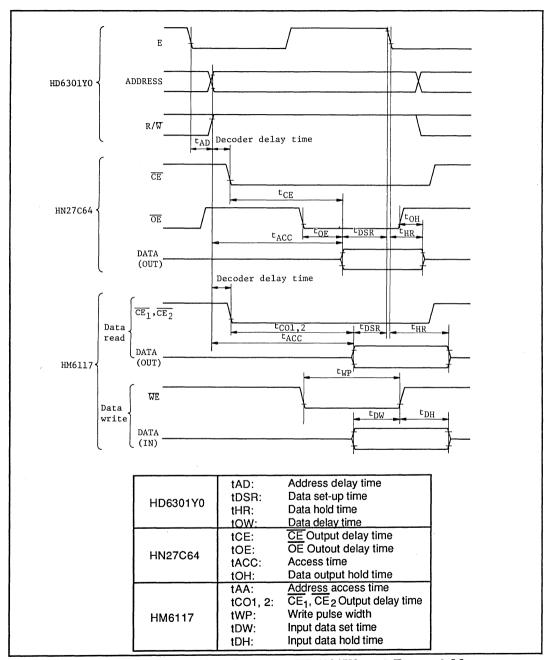

| 4.1.5                  | Hardware Operation                                                                                                       | 1189 |

| 4.2 S                  | oftware Description                                                                                                      | 1190 |

| 4.2.1                  | Program Module Configuration                                                                                             | 1190 |

| 4.2.2                  | Program Module Functions                                                                                                 | 1190 |

| 4.2.3                  | Program Module Sample Application (Main Program)                                                                         | 1192 |

|                        | rogram Module Description                                                                                                | 1194 |

| 4.4 P                  | rogram Listing                                                                                                           | 1220 |

| 4.4.1                  | Main Program Listing                                                                                                     | 1220 |

| 4.4.2                  | C Source Listing                                                                                                         | 1222 |

|                        | Output Object Listing of C Compiler                                                                                      | 1226 |

|                        | Linkage Listing.                                                                                                         | 1232 |

| APPEN                  |                                                                                                                          |      |

|                        |                                                                                                                          | 1005 |

| C Prog                 | ram and Assembly Program Comparison                                                                                      | 1235 |

|                        | on 10—Appendix                                                                                                           |      |

|                        | 01V1/HD6303R Q & A—HD6301X0/HD6303X Oscillation Circuit<br>Temperature Range Specifications, -40°C to +85°C, (J Version) | Page |

|                        | 06301V1/HD6303R Q & A                                                                                                    | 1239 |

| (a)                    | Parallel Port                                                                                                            |      |

| (1)                    | Process to Use a Port as an Output                                                                                       | 1241 |

| (b)                    | Serial Port                                                                                                              |      |

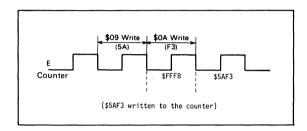

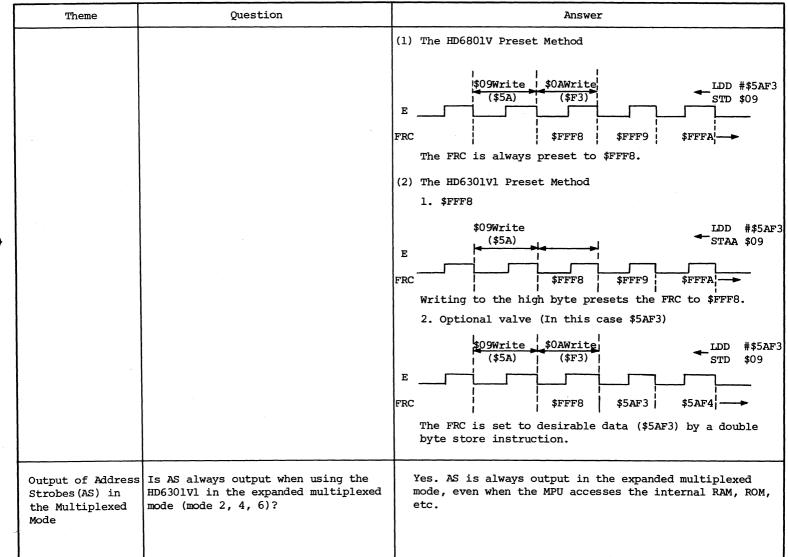

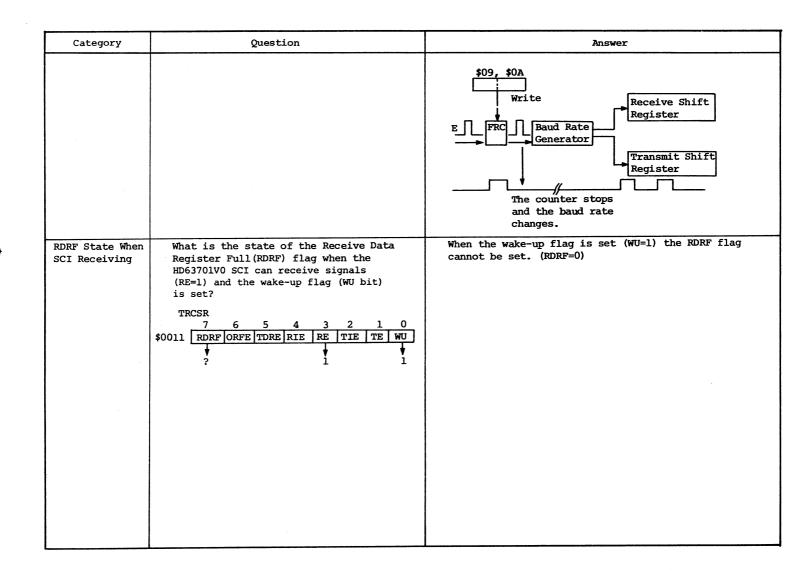

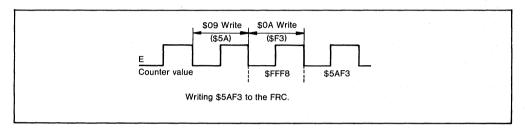

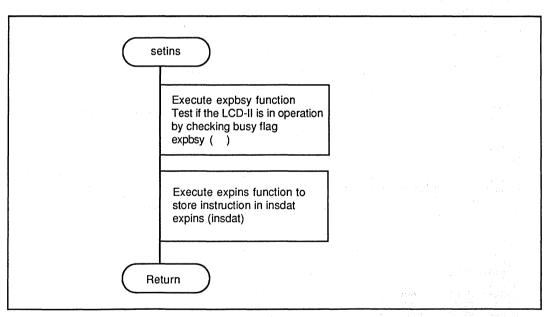

| (1)                    | Relation between Writing into the FRC and SCI Operation                                                                  | 1242 |

| (2)                    | Writing into the FRC during Serial Receive/Transmit                                                                      | 1243 |

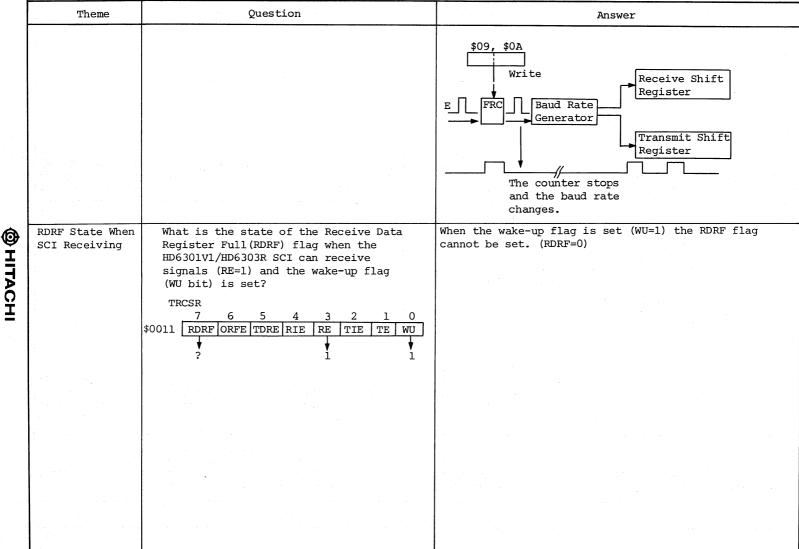

| (3)                    | RDRF State When SCI Receiving                                                                                            | 1244 |

| (4)                    | Serial I/O Operation                                                                                                     | 1245 |

| ( <del>-)</del><br>(5) | Serial I/O Register Read                                                                                                 | 1246 |

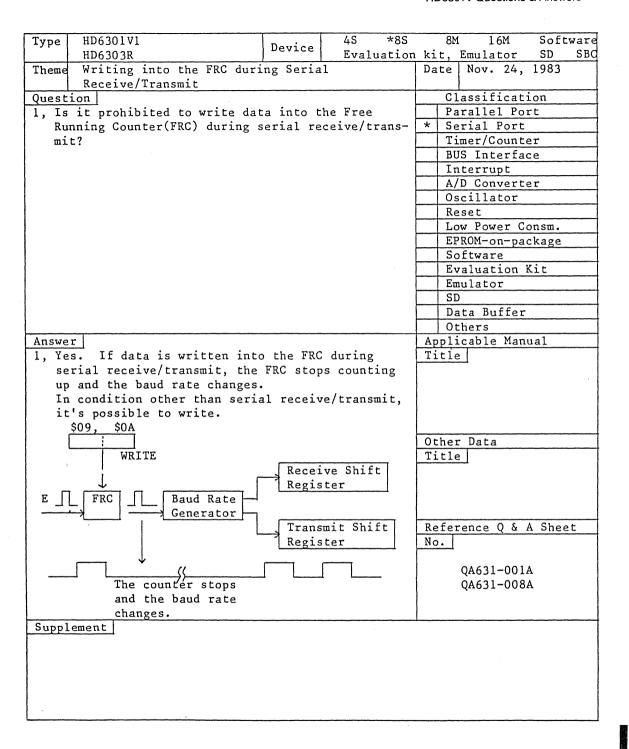

| (6)                    | Detection of the HD6301V1 Serial Start Bit                                                                               | 1247 |

| (0)                    | © HITACHI                                                                                                                | 144/ |

|                        |                                                                                                                          |      |

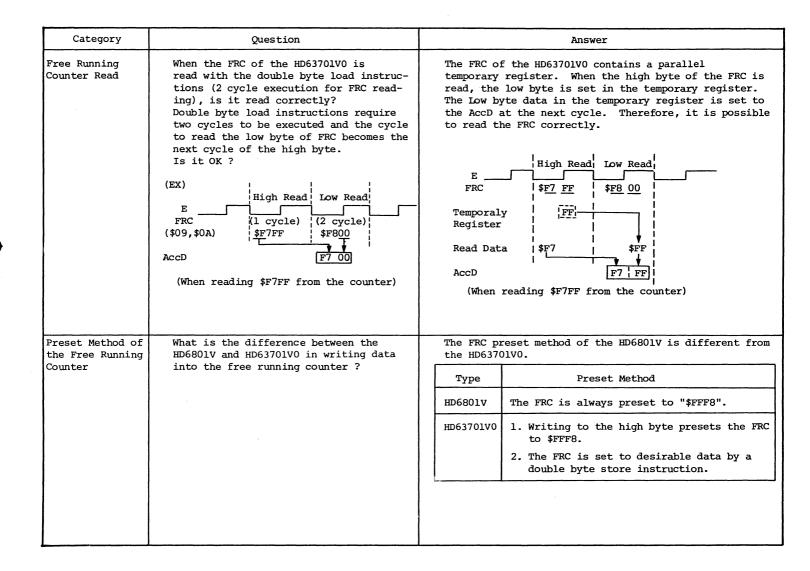

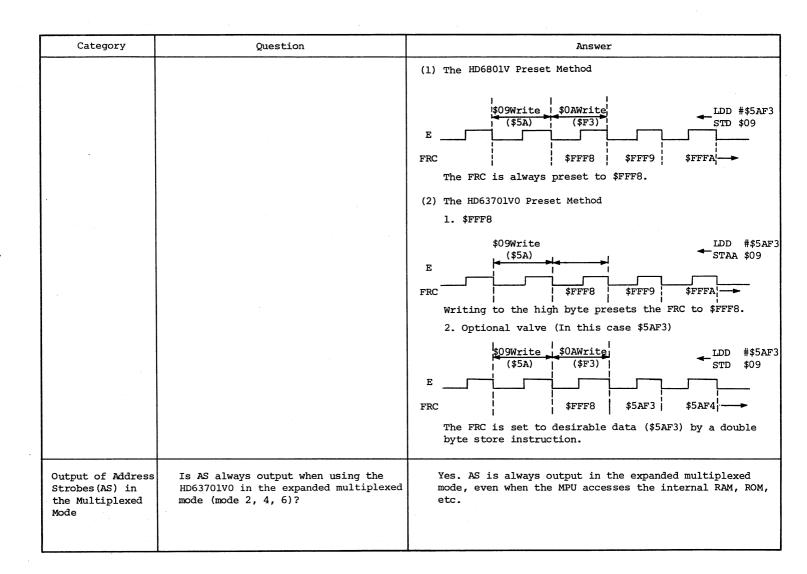

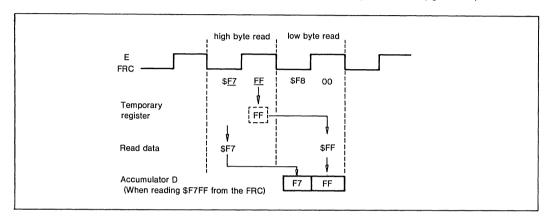

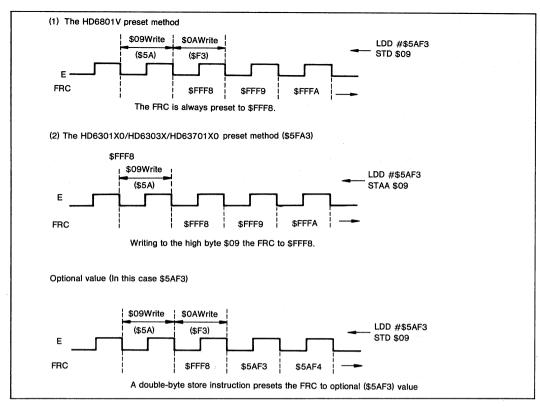

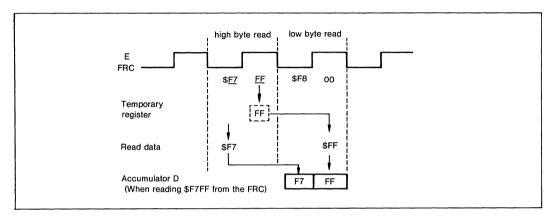

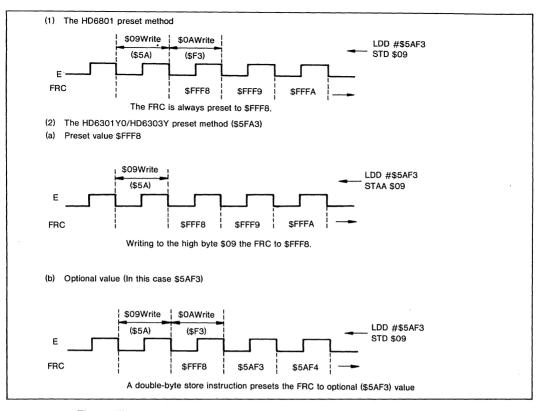

| (c)<br>(1)<br>(2)                         | Timer/Counter Free Running Counter Read                                                                                                                                      |                                      |  |  |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|--|

| (d)<br>(1)                                | BUS Interface Output of Address Strobe (AS) in the Multiplexed Mode                                                                                                          | 1252                                 |  |  |

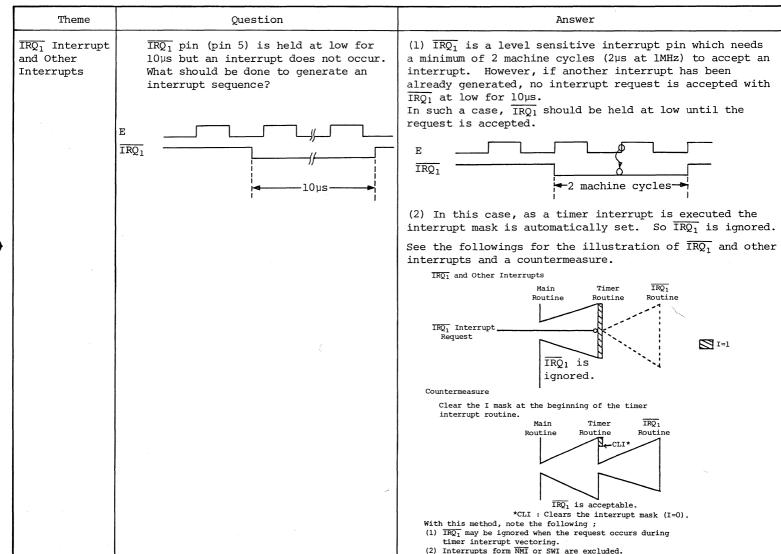

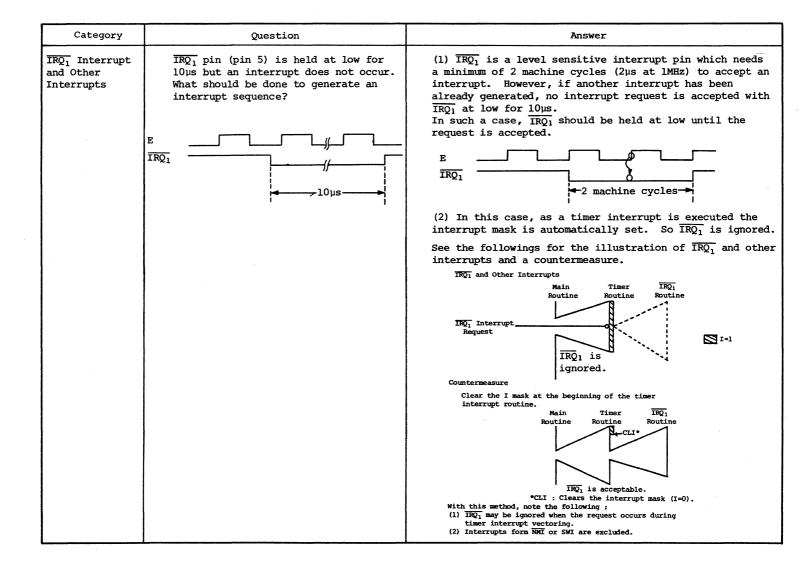

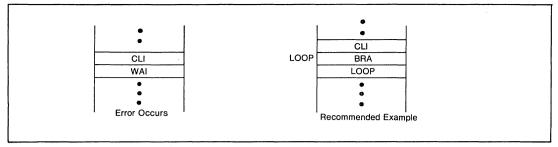

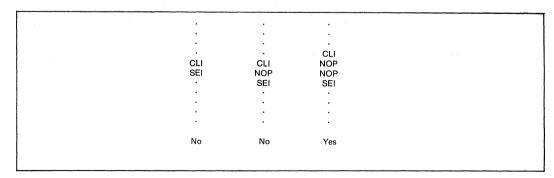

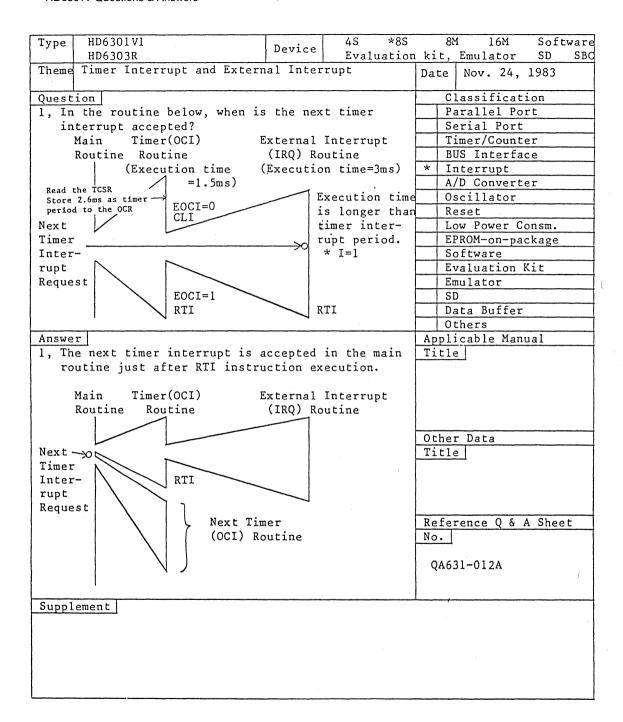

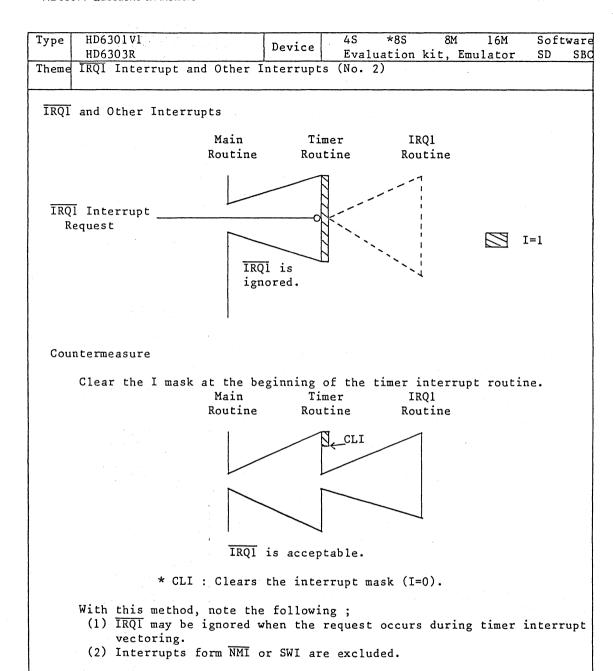

| (e)<br>(1)<br>(2)<br>(3)<br>(4)           | Interrupt IRQ1 Acceptance. Timer Interrupt and External Interrupt IRQ1 Interrupt and Other Interrupts. CLI Instruction and Interrupt Operation                               | 1253<br>1254<br>1255<br>1257         |  |  |

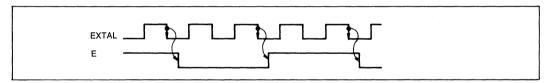

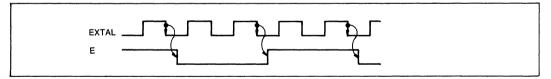

| (f)<br>(1)                                | Oscillator Relation between the External Clock (EXTAL Clock) and Enable Clock (E Clock)                                                                                      | 1258                                 |  |  |

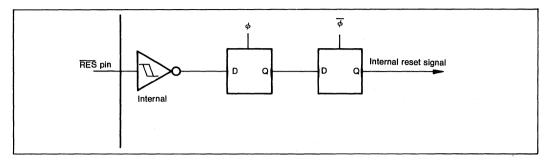

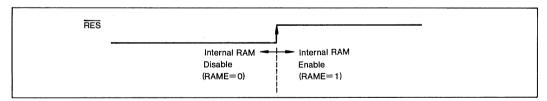

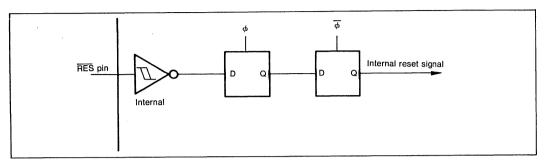

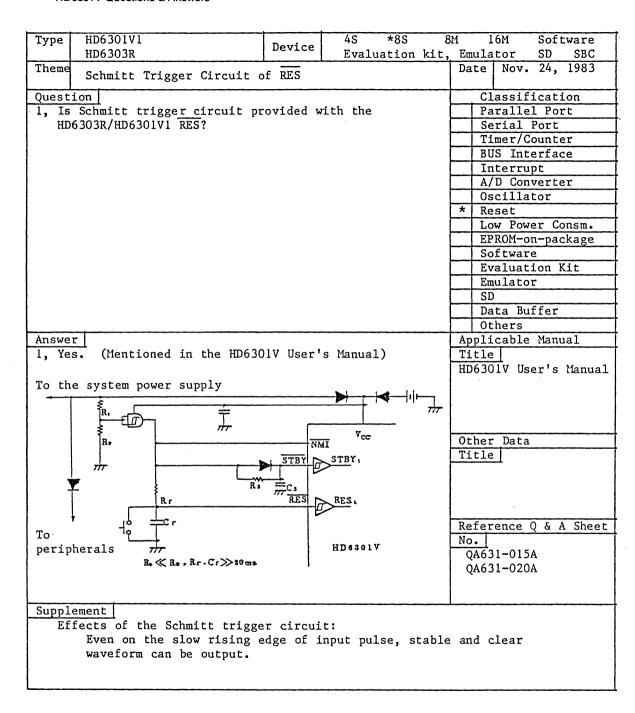

| (g)<br>(1)<br>(2)<br>(3)<br>(4)<br>(5)    | Reset Constants of the Reset Circuit Schmitt Trigger Circuit of RES I/O Port State on Resetting SCI (Pin 39) State on Resetting Port Output after Resetting                  | 1259<br>1260<br>1261<br>1262<br>1263 |  |  |

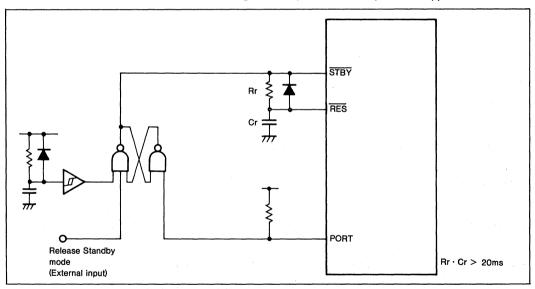

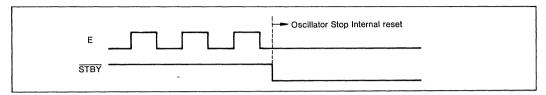

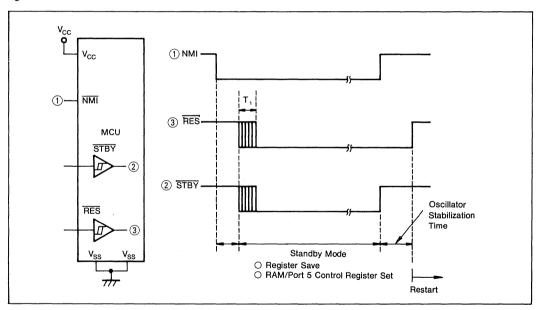

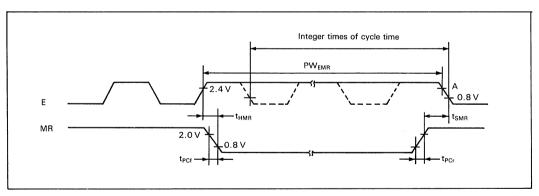

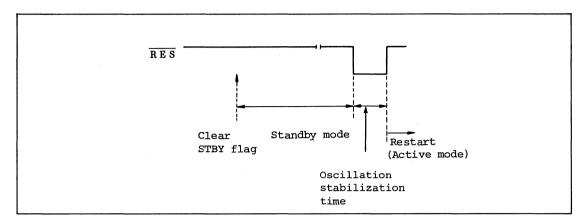

| (h)<br>(1)<br>(2)<br>(3)<br>(4)<br>(5)    | Low Power Consumption Schmitt Trigger Circuit of STBY  I/O Port State During Standby.  Return from Standby Mode.  Going into the Standby Mode.  Timing for the Standby Mode. | 1264<br>1265<br>1266<br>1267<br>1268 |  |  |

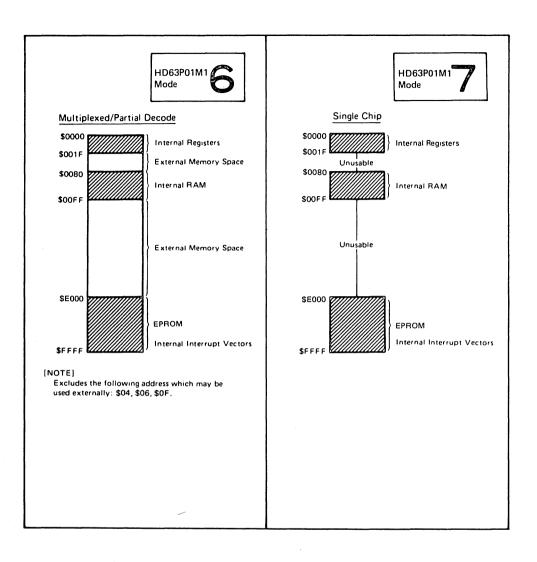

| (i)<br>(1)<br>(2)<br>(3)                  | EPROM-on-Package Usage of EPROM Socket Pins for the HD63P01M (No. 1) Usage of EPROM Socket Pins for the HD63P01M (No. 2) Usage of EPROM Socket Pins for the HD63P01M (No. 3) | 1269<br>1270<br>1271                 |  |  |

| (j)<br>(1)<br>(2)                         | Software Usage of Bit Manipulation Instructions                                                                                                                              |                                      |  |  |

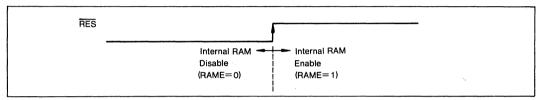

| (k)<br>(1)                                | Others RAM Access Disable during Program Execution                                                                                                                           | 1275                                 |  |  |

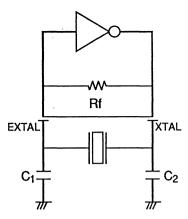

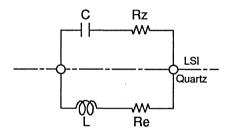

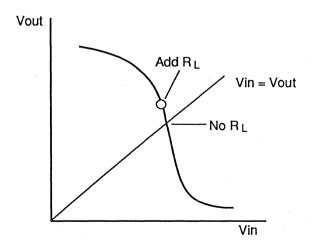

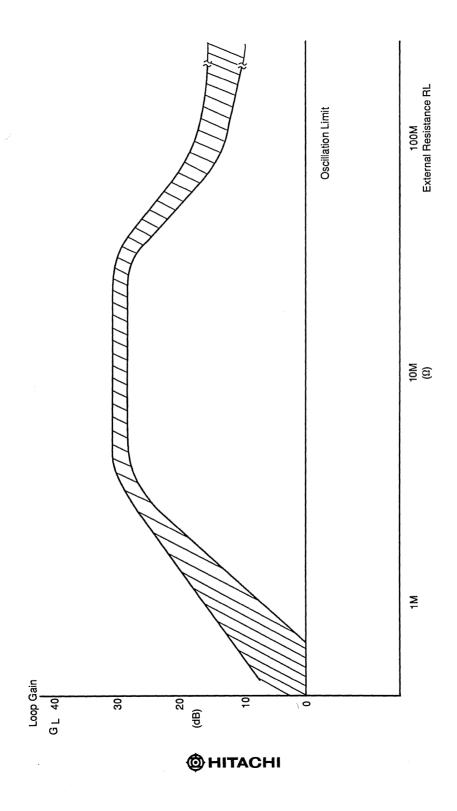

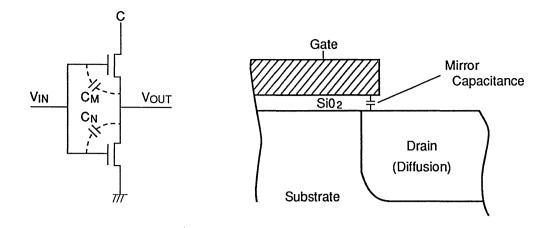

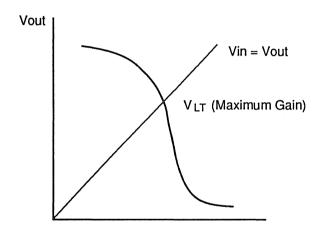

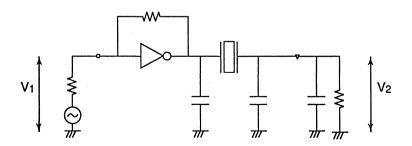

| 2. HD                                     | 6301X0/HD6303X OSCILLATOR CIRCUIT                                                                                                                                            | . 1276                               |  |  |

|                                           | de Temperature Range Specifications –40°C to +85°C (J Version)                                                                                                               |                                      |  |  |

|                                           | 1V1, HD63A01V1, HD63B01V1                                                                                                                                                    |                                      |  |  |

| HD6301X0, HD63A01X0, HD63B01X0            |                                                                                                                                                                              |                                      |  |  |

| HD6301Y0, HD63A01Y0, HD63B01Y0, HD63C01Y0 |                                                                                                                                                                              |                                      |  |  |

| HD6303R, HD63A03R, HD63B03R               |                                                                                                                                                                              |                                      |  |  |

| HD6303X, HD63A03X, HD63B03X               |                                                                                                                                                                              |                                      |  |  |

| HD630                                     | 3Y, HD63A03Y, HD63B03Y, HD63C03Y                                                                                                                                             | . 1310                               |  |  |

|                                           | HITACHI SALES OFFICES PAGE 1318                                                                                                                                              |                                      |  |  |

## HD6301/HD6303 SERIES HANDBOOK

## Section One

- Quick Reference Guide and

- Package Reference

Guide

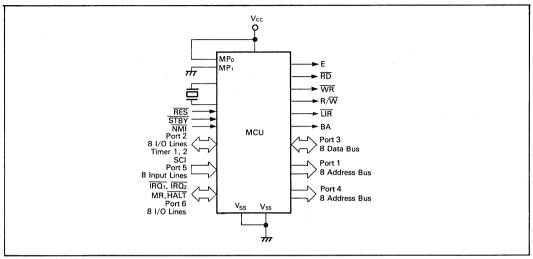

#### **8-BIT SINGLE-CHIP MICROCOMPUTER**

#### ■ CMOS 8-BIT SINGLE-CHIP MICROCOMPUTER HD6301 SERIES

| Type No                   |                           | HD6301V1           |                                                                                              | HD6301X0<br>HD63A01X0                    |                                                                                                                                                              |    |

|---------------------------|---------------------------|--------------------|----------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| туре ио.                  |                           |                    |                                                                                              |                                          | HD63B01X0                                                                                                                                                    |    |

| 1.0                       | Bus Timing (MHz)          |                    | 1.0 (HD6301V1)<br>1.5 (HD63A01V1)<br>2.0 (HD63B01V1)                                         |                                          | 1.0 (HD6301X0)<br>1.5 (HD63A01X0)<br>2.0 (HD63B01X0)                                                                                                         |    |

| LSI<br>Characteristics    | Supply Voltage (V)        |                    | 5.0                                                                                          |                                          | 5.0                                                                                                                                                          |    |

|                           | Operating Te              | mperature (°C)     | 0 ~ +70*3,*4                                                                                 |                                          | 0 ~ +70*3                                                                                                                                                    |    |

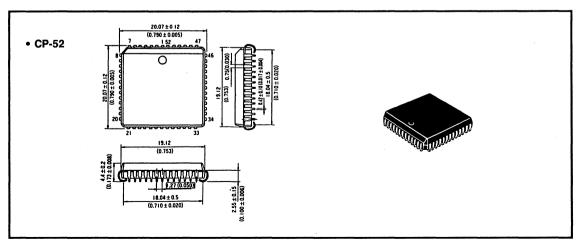

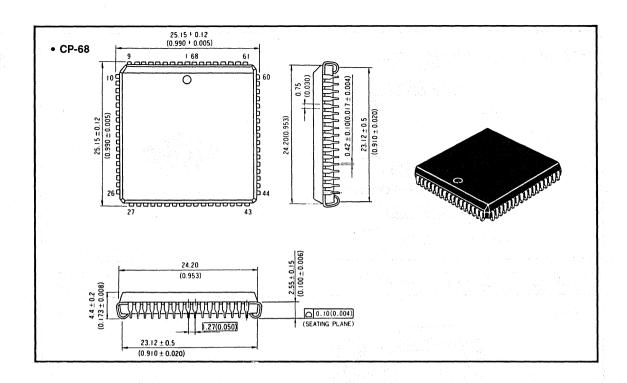

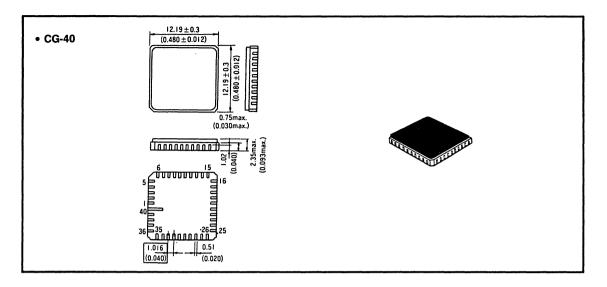

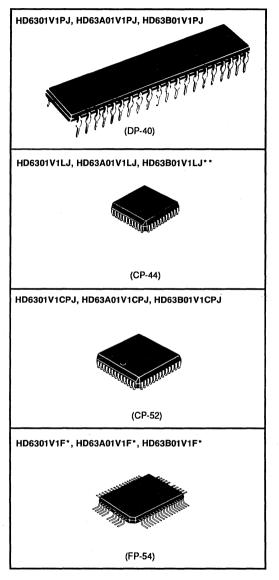

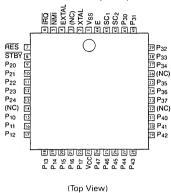

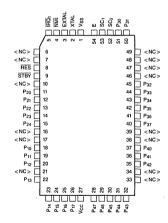

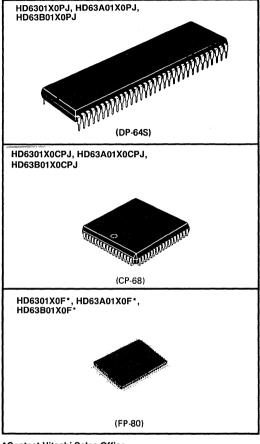

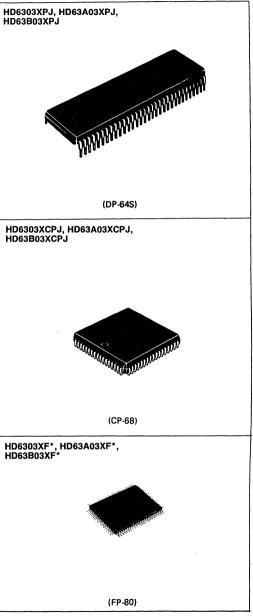

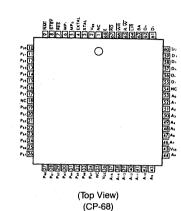

|                           | Type No.                  | 6-40, CP-44, CP-52 | DP-64S, FP-80, CP-68                                                                         |                                          |                                                                                                                                                              |    |

|                           | Memoty                    | ROM (k byte)       | . 4                                                                                          | 1                                        | 4                                                                                                                                                            |    |

|                           | Inclinery                 | RAM (byte)         | 128                                                                                          |                                          | 192                                                                                                                                                          |    |

|                           | I/O Port                  | I/O Port           | 29                                                                                           |                                          |                                                                                                                                                              | 24 |

|                           |                           | Input Port         | 29                                                                                           |                                          | 53                                                                                                                                                           | 8  |

|                           |                           | Output Port        |                                                                                              | _                                        |                                                                                                                                                              | 21 |

|                           |                           | External           | 2                                                                                            |                                          | 3                                                                                                                                                            |    |

|                           | Interrunt                 | Soft               | 2                                                                                            |                                          | 2                                                                                                                                                            |    |

|                           | interrupt                 | Timer              | 3                                                                                            |                                          | 4                                                                                                                                                            |    |

| Functions                 |                           | Serial             | 1                                                                                            |                                          | 1                                                                                                                                                            |    |

|                           | Timer                     |                    | 16-bit x 1  Free running counter x 1  Output compare register x 1  Input capture register x1 |                                          | 16-bit x 1  / Free running counter x 1  Output compare register x2  Input capture register x1  8-bit x 1  / 8-bit up counter x 1  Time constant register x 1 |    |

|                           | SCI                       |                    | Asynch                                                                                       | ronous                                   | Asynchronous/Synchronous                                                                                                                                     |    |

|                           | External Memory Expansion |                    | 65k bytes                                                                                    |                                          | 65k bytes                                                                                                                                                    |    |

|                           | Other Features            |                    |                                                                                              |                                          | Error detection     Low power dissipation modes (sleep and standby)     Slow memory interface     Halt                                                       |    |

| EPROM on Chip Type        |                           | HD637A01V0C        |                                                                                              | HD63701X0C<br>HD637A01X0C<br>HD637B01X0C |                                                                                                                                                              |    |

| EPROM on the Package Type |                           |                    | HD63P01M1                                                                                    |                                          | <u> </u>                                                                                                                                                     |    |

<sup>\*1</sup> Preliminary \*2 Under development \*3 Wide temperature range (-40 ~ +85°C) version is available.

$<sup>^{\</sup>rm e4}$  Wide temperature range (-40  $\sim$  +125°C) version is available.

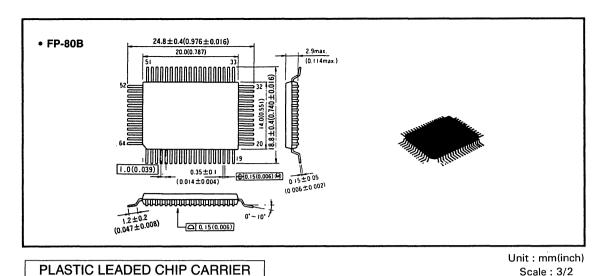

<sup>†</sup> DP; Plastic DIP, FP; Plastic Flat Package, CG; Glass-sealed Ceramic Leadless Chip Carrier, CP; Plastic Leaded Chip Carrier (J-bend leads)

| +                                                                                                                                                             |               | <del></del>                                                                                   |    |                                                                                                                                                              |               |                                                                                                                                                              |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------------------------------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| HD6301Y0<br>HD63A01Y0<br>HD63B01Y0<br>HD63C01Y0                                                                                                               |               | HD6303R<br>HD63A03R<br>HD63B03R                                                               |    | HD6303X<br>HD63A03X<br>HD63B03X                                                                                                                              |               | HD6303Y<br>HD63A03Y<br>HD63B03Y<br>HD63C03Y                                                                                                                  |    |

| 1.0 (HD6301Y0)<br>1.5 (HD63A01Y0)<br>2.0 (HD63B01Y0<br>3.0 (HD63C01Y0)                                                                                        |               | 1.0 (HD6303R)<br>1.5 (HD63A03R)<br>2.0 (HD63B03R)                                             |    | 1.0 (HD6303X)<br>1.5 (HD63A03X)<br>2.0 (HD63B03X)                                                                                                            |               | 1.0 (HD6303Y)<br>1.5 (HD63A03Y)<br>2.0 (HD63B03Y)<br>3.0 (HD63C03Y)                                                                                          |    |

|                                                                                                                                                               | 5.0           | 5.0                                                                                           |    | 5.0                                                                                                                                                          |               | 5.0                                                                                                                                                          |    |

| 0~                                                                                                                                                            | +70*3         | 0~+70*3,*4                                                                                    |    | 0~+70*3                                                                                                                                                      |               | 0~+70*3                                                                                                                                                      |    |

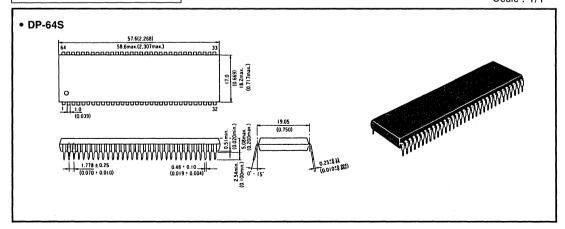

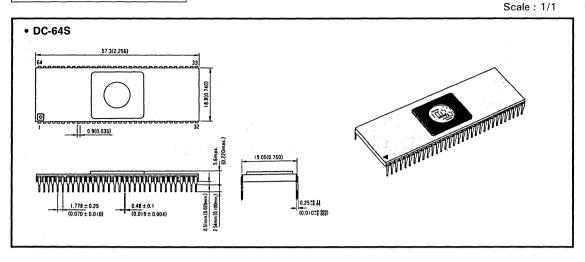

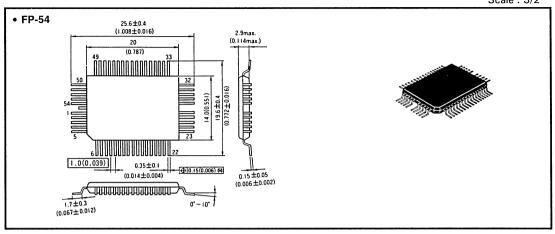

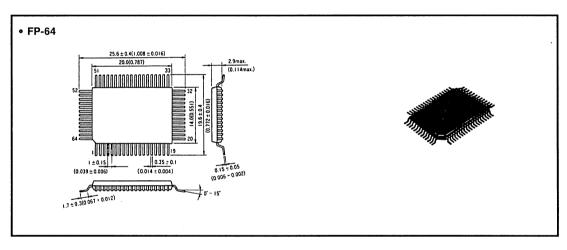

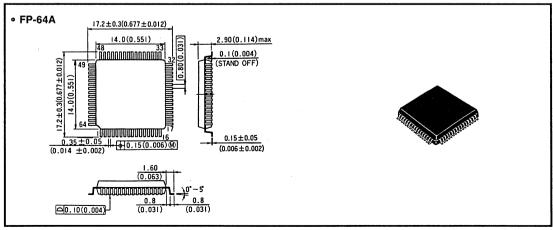

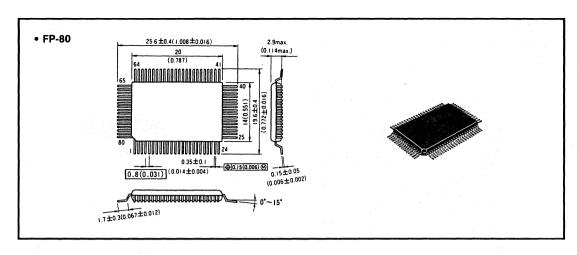

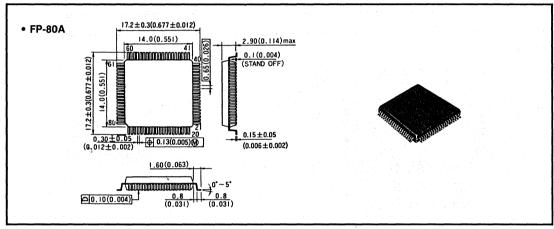

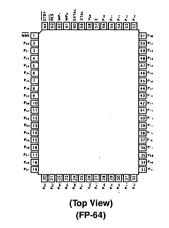

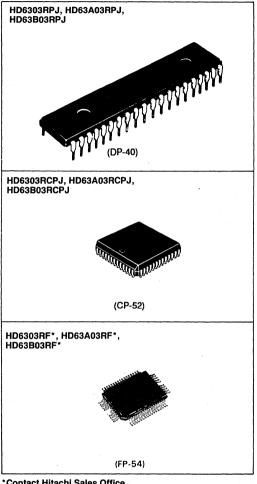

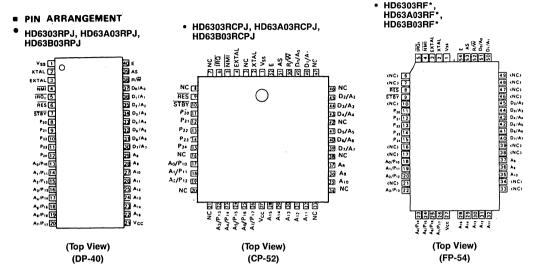

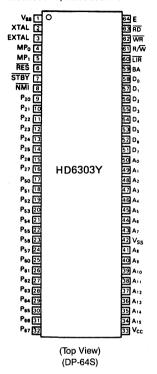

| DP-64S, FP-64,                                                                                                                                                | FP-64A, CP-68 | DP-40, FP-54, CG-40, CP-52                                                                    |    | DP-64S, FP-80, CP-68                                                                                                                                         |               | DP-64S, FP-64, FP-64A, CP-68                                                                                                                                 |    |

| 1                                                                                                                                                             | 6             | _                                                                                             |    | -                                                                                                                                                            |               |                                                                                                                                                              | _  |

| 25                                                                                                                                                            | 56            | 128                                                                                           |    | 192                                                                                                                                                          |               | 256                                                                                                                                                          |    |

|                                                                                                                                                               | 48            |                                                                                               | 13 |                                                                                                                                                              | 16            |                                                                                                                                                              | 24 |

| 53                                                                                                                                                            | _             | 13                                                                                            | _  | 24                                                                                                                                                           | 8             | 24                                                                                                                                                           | _  |

|                                                                                                                                                               | 5             |                                                                                               | _  |                                                                                                                                                              | _             |                                                                                                                                                              | _  |

| 3                                                                                                                                                             | 3             | 2                                                                                             |    | 3                                                                                                                                                            |               | 3                                                                                                                                                            |    |

| 2                                                                                                                                                             |               | 2                                                                                             |    | 2                                                                                                                                                            |               | 2                                                                                                                                                            |    |

| 4                                                                                                                                                             |               | 3                                                                                             |    | 4                                                                                                                                                            |               | 4                                                                                                                                                            |    |

| 1                                                                                                                                                             |               | 1                                                                                             |    | 1                                                                                                                                                            |               | 1                                                                                                                                                            |    |

| 16-bit x 1  (Free running counter x 1  Output compare register x 2  Input capture register x 1  8-bit x 1  (8-bit up counter x 1  Time constant register x 1) |               | 16-bit x 1  Free running counter x 1  Output compare register x 1  Input capture register x 1 |    | 16-bit x 1  (Free running counter x 1  Output compare register x 2  Input capture register x 1  8-bit x 1  (8-bit up counter x 1  Time constant register x 1 |               | 16-bit x 1  (Free running counter x 1  Output compare register x 2  Input capture register x 1  8-bit x 1  (8-bit up counter x 1  Time constant register x 1 |    |

| Asynchronous                                                                                                                                                  | /Synchronous  |                                                                                               |    |                                                                                                                                                              | s/Synchronous |                                                                                                                                                              |    |

| 65k bytes                                                                                                                                                     |               | 65k bytes                                                                                     |    | 65k bytes                                                                                                                                                    |               | 65k bytes                                                                                                                                                    |    |

| Error detection     Low power dissipation modes (sleep and standby)     Slow memory interface     Halt                                                        |               | Error detection     Low power dissipation modes (sleep and standby)                           |    | Error detection     Low power dissipation     modes (sleep and standby)     Slow memory interface     Halt                                                   |               | Error detection     Low power dissipation     modes (sleep and standby)     Slow memory interface     Halt                                                   |    |

| HD6370IY0C<br>HD637A01Y0C<br>HD637B01Y0C                                                                                                                      |               | -                                                                                             |    | -                                                                                                                                                            |               | -                                                                                                                                                            |    |

| _                                                                                                                                                             |               | -                                                                                             |    | _                                                                                                                                                            |               | -                                                                                                                                                            |    |

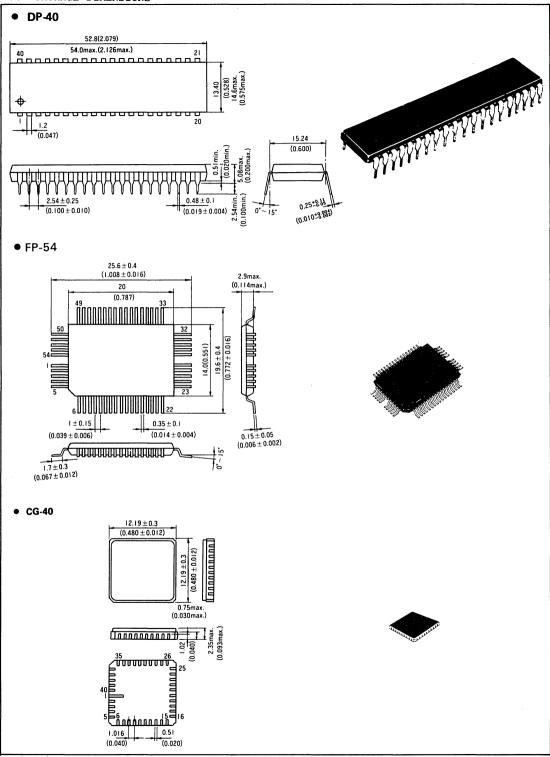

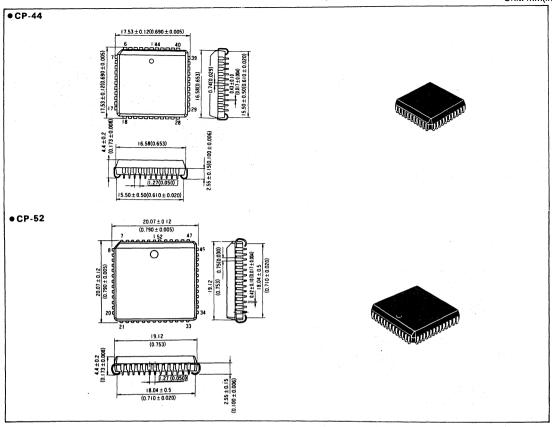

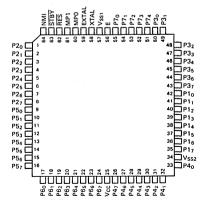

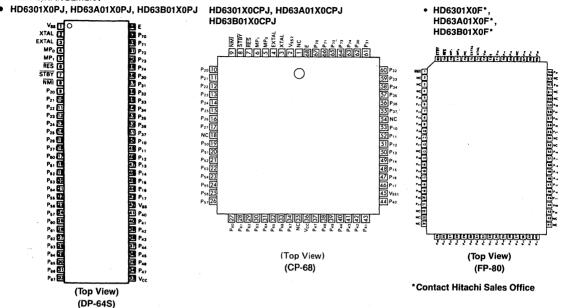

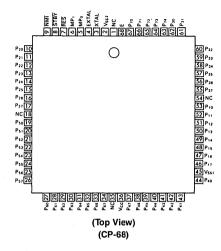

#### PACKAGE REFERENCE GUIDE

Hitachi microcomputer devices include various types of package which meet a lot of requirements such as ever smaller, thinner and more versatile electric appliances. When selecting a package suitable for the customers' use, please refer to the following for Hitachi microcomputer packages.

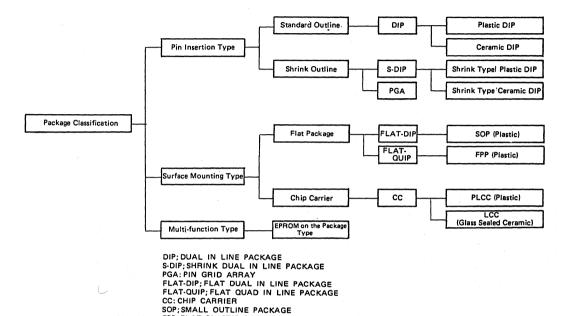

#### 1. Package Classification

There are pin insertion types, surface mounting types and

multi-function types, applicable to each kind of mounting method. Also, plastic and ceramic materials are offered according to use.

Fig. 1 shows the package classification according to the mounting types on the Printed Circuit Board (PCB) and the materials.

Fig. 1 Package Classification according to the Mounting Type on the Printed Circuit Board and the Materials.

FPP; FLAT PLASTIC PACKAGE PLCC; PLASTIC LEADED CHIP CARRIER LCC; LEADLESS CHIP CARRIER

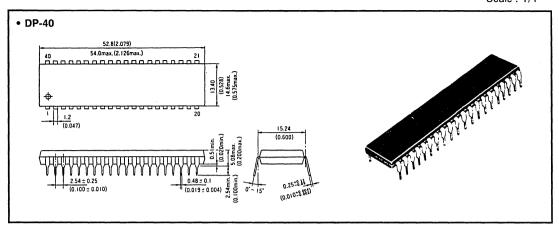

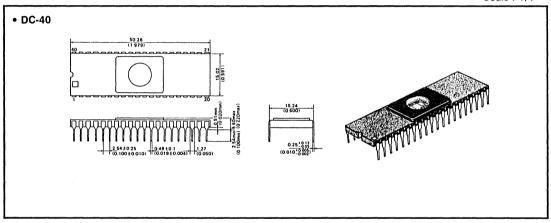

Unit: mm(inch) Scale: 1/1

#### **CERAMIC DIP**

Unit : mm(linch) Scale : 1/1

#### SHRINK TYPE PLASTIC

Unit : mm(inch) Scale : 1/1

#### **CERAMIC SHRINK TYPE**

Unit : mm(inch)

#### FLAT PACKAGE

Unit: mm(inch) Scale: 3/2

Scale: 3/2

# • CP-44 17.53 ± 0.12(0.690 ± 0.005) 17.53 ± 0.12(0.690 ± 0.005) 16.58(0.653) 2.55±0.15(0.100±0.006) 16.58(0.653)

15.50±0.50(0.610±0.020)

#### LEADLESS CHIP CARRIER

Unit : mm(inch) Scale : 3/2

# HD6301/HD6303 SERIES HANDBOOK

Section Two

Addressing Modes, CPU Architecture, and Instruction Set

# Section 2 Addressing Modes, CPU Architecture, and Instruction Set Table of Contents

|       |                         | Page |

|-------|-------------------------|------|

| 1. AS | SSEMBLY LANGUAGE        | 17   |

| 1.1   | Addressing Modes        | 17   |

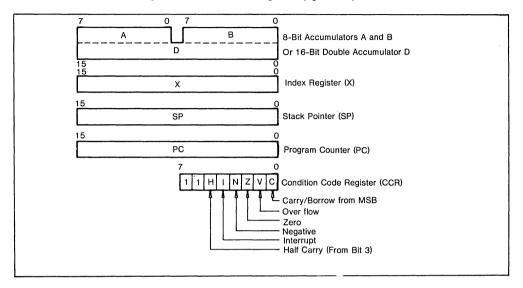

| 1.2   | CPU Registers           | 26   |

| 1.3   | Instruction Set Details | 28   |

#### 1. ASSEMBLY LANGUAGE

#### 1.1 Addressing Modes

The assembler determines the addressing mode by referencing the operator and operand fields. There are seven different addressing modes available.

- (1) Accumulator addressing

- (2) Implied addressing

- (3) Immediate addressing

- (4) Direct addressing

- (5) Extended addressing

- (6) Indexed addressing

- (7) Relative addressing

Before going into details about individual addressing modes, we explain the dual operand mode in which an instruction has two operands.

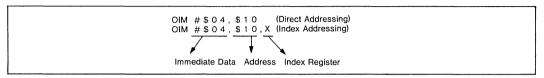

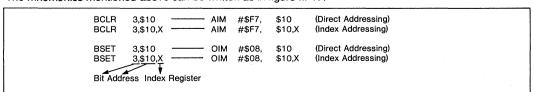

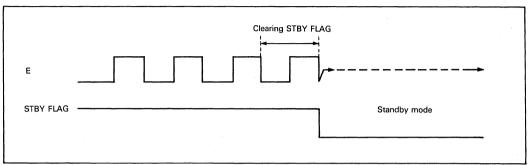

For eight instructions AIM, OIM, EIM, TIM, BCLR, BSET, BTGL and BTST, the operand field requires two operands (the first and second operands). The first operand includes the immediate data (constant) for AIM, OIM and TIM; and the bit number for bit operation for BCLR, BSET, BTGL and BTST. The second operand specifies a memory address in either indexed or direct addressing mode

## (1) Accumulator Addressing

Thirteen instructions allow Accumulator A or B as an operand. They are: ASL, ASR, CLR, COM, DEC, INC, LSR, NEG, PSH, PUL, ROL, ROR and TST. In this case, an SP or HT between the operator and the operand may be omitted. Each accumulator addressing instructions is converted into a one-byte machine code by the assembler.

#### Example:

| Instruction code | Machine code (Hexadecimal) |

|------------------|----------------------------|

| ASL A or ASLA    | 48                         |

| ASR B or ASRB    | 57                         |

#### (2) Implied Addressing

In the implied addressing mode, the instruction contained in the operator field permits the address for operation to be clear-cut. The operand is therefore unnecessary.

This implied addressing includes 31 instructions: ABA, ABX, ASLD, CBA, CLC, CLI, CLV, DAA, DES, DEX, INS, INX, LSRL, MUL, NOP, PSHX, PULX, RTI, RTS, SBA, SEC, SEI, SEV, SWI, TAB, TAP, TBA, TPA, TSX, TXS and WAI. Each instruction is converted into a one-byte machine code by the assembler.

## (3) Immediate Addressing

There are 16 instructions that allow immediate addressing. They are: ADC, ADD, AND, BIT, CMP, CPX, EOR, LDA, LDS, LDX, ORA, SBC, SUB, LDD, ADDD and SUBD.

The operand field starts with #, followed by numerical data in decimal, hexadecimal, octal or binary, symbols (labels) that will take specific values during assembling, expressions and ASCII constants.

In any case, the assembler converts the immediate data (operand) into an unsigned 8-bit binary, or 16-bit binary for CPX, LDS, LDX, LDD, ADD and SUBD. The resulting immediate data range from 0 to 255, or 0 to 65535 for 16-bit operand instructions.

#### Example:

| Statement         | Machine code (Hexadecimal)<br>Label = 100 |    |    |  |  |

|-------------------|-------------------------------------------|----|----|--|--|

|                   | Byte 1 Byte 2 Byte 3                      |    |    |  |  |

| LDA A #25         | 86                                        | 19 | -  |  |  |

| LDA A #LABEL      | 86                                        | 64 | -  |  |  |

| LDA A #LABEL + 25 | 86                                        | 7D | -  |  |  |

| LDA A #'A         | 86                                        | 41 | -  |  |  |

| CPX #256          | 8C                                        | 01 | 00 |  |  |

In this case, the characters following "'" are converted into 7-bit ASCII data. The #'conversion is not generally used with CPX, LDS and LDX instructions. If it is used, however, the converted ASCII data is stored into byte 3. The assembler enables each immediate addressing instruction to be converted into 2 bytes in machine code (3 bytes in the case of CPX, LDS, LDX, LDD, ADDD and SUBD).

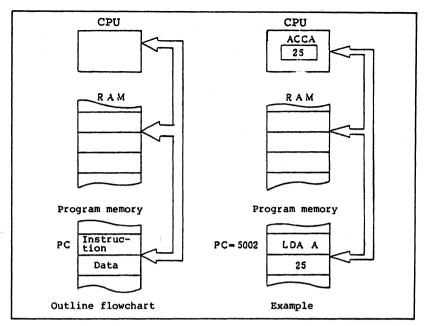

Figure 1-1-1 shows how data flows in immediate addressing mode.

Fig. 1-1-1 Data Activity in Immediate Addressing Mode

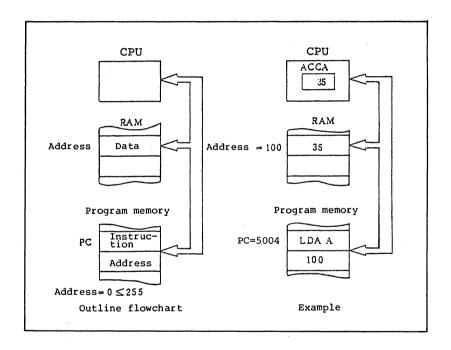

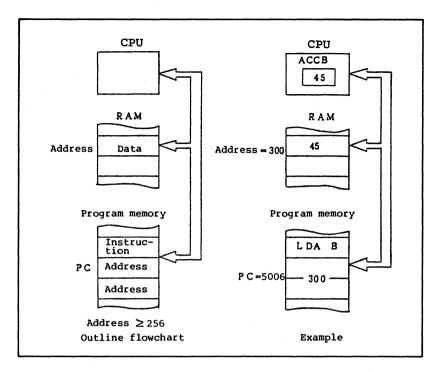

## (4) Direct Addressing and Extended Addressing

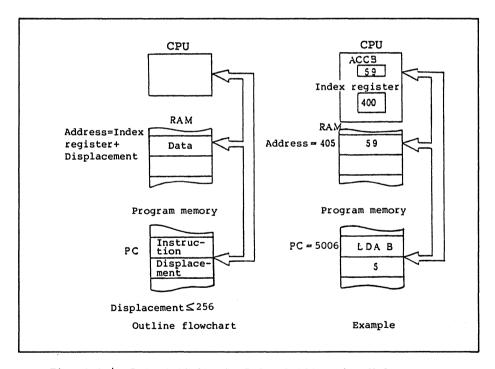

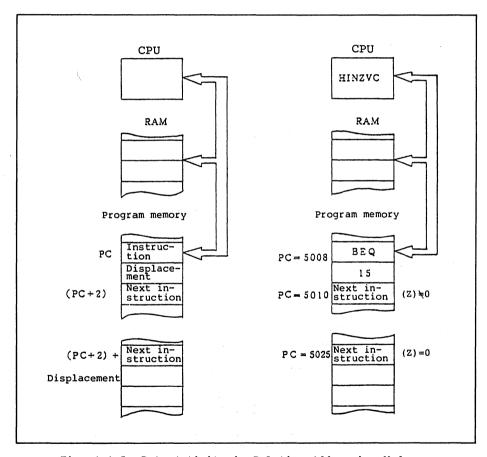

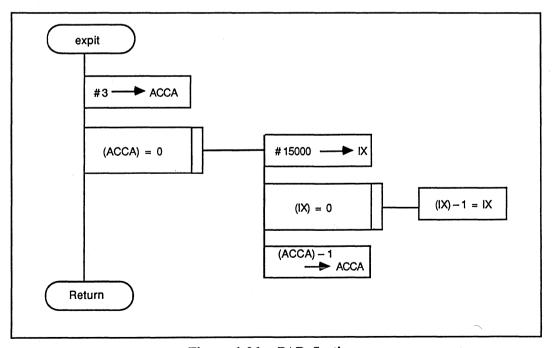

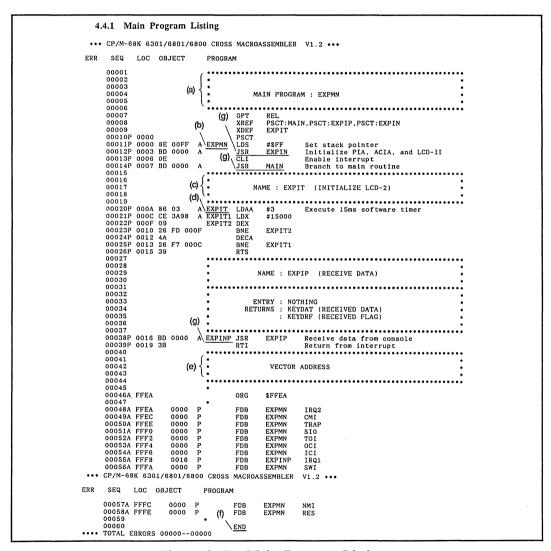

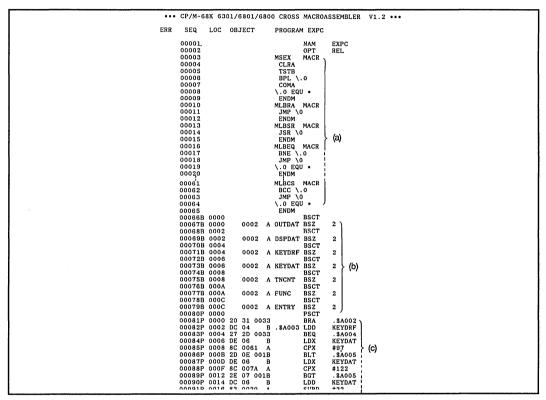

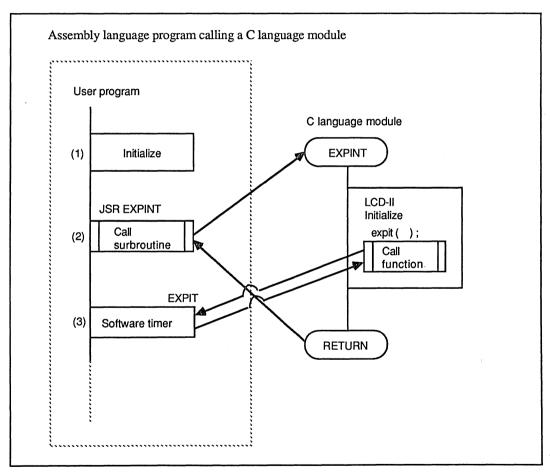

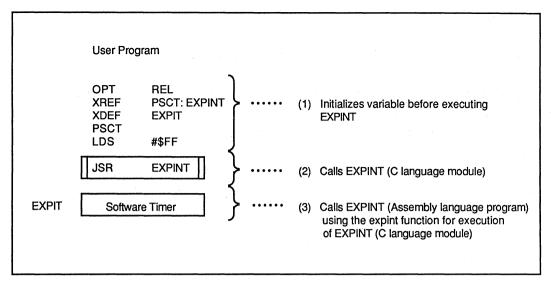

In direct addressing mode, the assembler converts the instruction into 2 bytes of machine code. The second byte, after conversion, includes an unsigned 8-bit binary address.