4-BIT SINGLE-CHIP MICROCOMPUTER DATA BOOK

# 4-BIT SINGLE-CHIP MICROCOMPUTER DATABOOK

This advance data has been preliminarily prepared based on manuscript translated in Japan. Use this information with caution, therefore, as the accuracy of the copy cannot be guaranteed. A revised, U.S. edition of this technical data is currently in preparation, and may be ordered by returning the Business Reply Card at the back of this publication.

When using this manual, the reader should keep the following in mind:

- 1. This manual may, wholly or partially, be subject to change without notice.

- 2. All rights reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this manual without Hitachi's permission.

- 3. Hitachi will not be responsible for any damage to the user that may result from accidents or any other reasons during operation of his unit according to this manual.

- 4. This manual neither ensures the enforcement of any industrial properties or other rights, nor sanctions the enforcement right thereof.

# INDEX

| ■ GENERAL INFORMATION                                                   |

|-------------------------------------------------------------------------|

| Quick Reference Guide                                                   |

| Introduction of Packages                                                |

| • Quality Assurance                                                     |

| Reliability Test Data                                                   |

| Design Procedure and Support Tools for 4-bit Single-chip Microcomputers |

| ■ DATA SHEETS                                                           |

| 4-bit Single-chip Microcomputer HMCS40 Series                           |

| HMCS44C (HD44801), HMCS44CL (HD44808)                                   |

| HMCS45C (HD44820), HMCS45CL (HD44828)                                   |

| HMCS46C (HD44840), HMCS46CL (HD44848)                                   |

| HMCS47C (HD44860), HMCS47CL (HD44868)                                   |

| 4-bit Single-chip Microcomputer HMCS40 Series                           |

| Liquid Crystal Display Driving Type                                     |

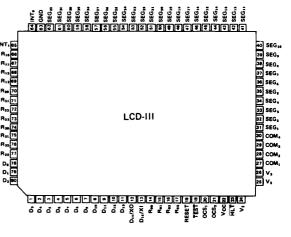

| LCD-III (HD44790, HD44795)                                              |

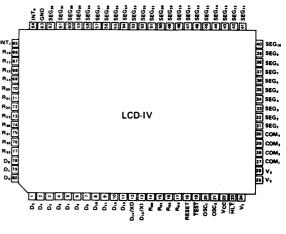

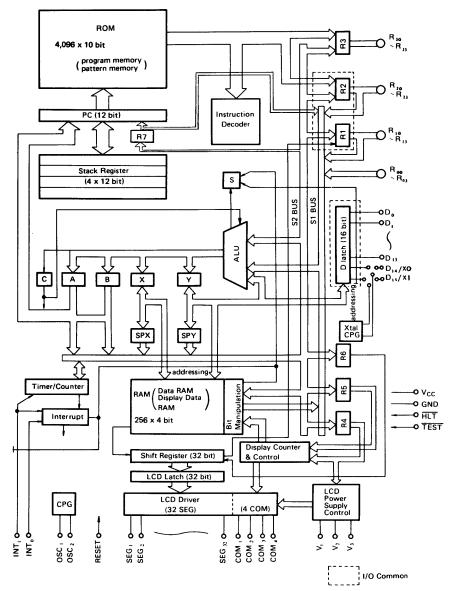

| LCD-IV (HD613901)                                                       |

|                                                                         |

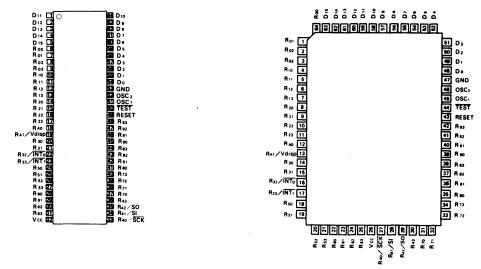

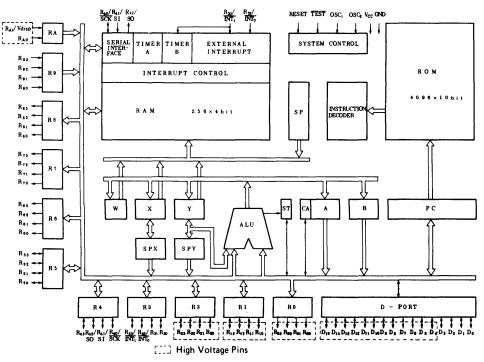

| 4-bit Single-chip Microcomputer HMCS400 Series                          |

| HMCS404C (HD614042)                                                     |

| HD614P080S                                                              |

| Evaluation Chip for 4-bit Single-chip Microcomputers                    |

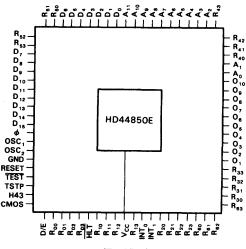

| HD44850E                                                                |

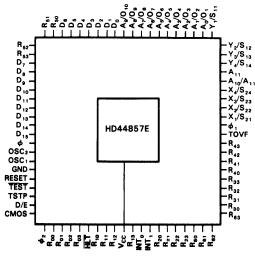

| HD44857E                                                                |

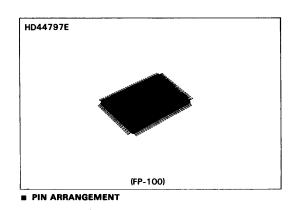

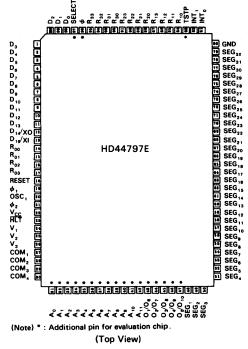

| HD44797E                                                                |

|                                                                         |

|                                                                         |

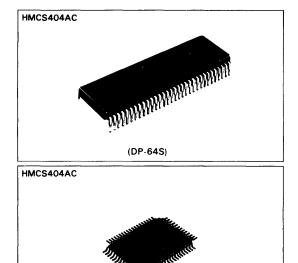

| HMC\$404AC (HD614048)                                                   |

| HMCS404CL (HD614045)                                                    |

# NOTE: No new designs for HMCS 42/43/44A/45A/47A/42C/42CL/43C/43CL accepted after April 1984.

# GENERAL INFORMATION

- Quick Reference Guide

- Introduction of Packages

- Quality Assurance

- Reliability Test Data

- Design Procedure and Support Tools for 8-bit Single-chip Microcomputers

-

# QUICK REFERENCE GUIDE

# ■ CMOS 4-BIT SINGLE-CHIP MICROCOMPUTER HMCS40 SERIES

|                                   |                   | Family Name<br>(Type Name) |                    | (H<br>HN | 1CS44CL<br>D44808)<br>1CS44C<br>D44801) | (HI<br>HM | ICS45CL<br>D44828)<br>ICS45C<br>D44820) |  |

|-----------------------------------|-------------------|----------------------------|--------------------|----------|-----------------------------------------|-----------|-----------------------------------------|--|

| 8                                 | Supply Voltage    |                            | (V)                | 3/5      | 3/5                                     |           | ;                                       |  |

| Characteristics                   | Power Dissipatio  | on (typ.)                  | (mW)               | 0.4      | /0.9                                    | 0.4       | /0.9                                    |  |

| i i i i i                         | Max. I/O Termin   | al Voltage                 | (V)                | Vc       | c+0.3                                   | Vc        | c+0.3                                   |  |

| har                               | Operating Temp    | erature Range *1           | (°C)               | - 2      | 0 to+75                                 | -20       | ) to +75                                |  |

| ပ                                 | Package           | ·······                    |                    | DP       | -42, DP-42S                             | FP        | -54, DP-64S                             |  |

|                                   | Memory ROM        |                            | (bits)             |          | 148 x 10<br>8x10* <sup>2</sup>          |           | 48 x 10<br>3x10* <sup>2</sup>           |  |

|                                   |                   | RAM                        | (bits)             | 16       | 160 x 4                                 |           | 0 x 4                                   |  |

|                                   | Registers         |                            |                    | 8        |                                         | 6         |                                         |  |

|                                   | Stack Registers   |                            |                    | 4        |                                         | 4         |                                         |  |

| ŝ                                 | I/O Ports         | 4-Bit Data Input           |                    |          | -                                       |           | -                                       |  |

| Functions                         |                   | 4-Bit Data Outpu           | t                  | 1        | -                                       |           | 4 x 1                                   |  |

| Ē                                 |                   | Discrete Output            |                    | 32       | _                                       | 44        | -                                       |  |

|                                   |                   | 4-Bit Data Input/          | Output             |          | 4 x 4                                   |           | 4 x 6                                   |  |

|                                   |                   | Discrete Input/O           | utput              |          | 1 x 16                                  |           | 1 x 16                                  |  |

|                                   |                   | External                   |                    | 2        |                                         | 2         | 2                                       |  |

|                                   | Interrupts        | Timer/Counter              |                    | 1<br>71  |                                         | 1         |                                         |  |

|                                   | Instructions      | Number of Instru           | ctions             |          |                                         | 71        |                                         |  |

|                                   | Cycle Time (µs)   |                            | 20/10              |          | 20/                                     | /10       |                                         |  |

|                                   | Built-in Clock Pu | Ise Generator              |                    |          |                                         |           |                                         |  |

| Power on Reset<br>Battery Back-up |                   | No                         | /Yes               | No       | /Yes                                    |           |                                         |  |

|                                   |                   | Halt                       |                    | Ha       | lt                                      |           |                                         |  |

| Evaluation Chip                   |                   |                            | 044850E<br>044857E |          | 044850E<br>044857E                      |           |                                         |  |

| F                                 | Reference Page    |                            |                    |          | 174                                     |           | 196                                     |  |

\*1 Wide Temperature Range (-40 to +85°C) version is available, except LCD-IV \*2 Pattern Memory \*3 LCD DRIVE FUNCTION

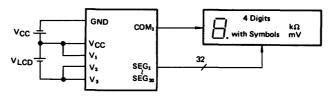

|         | Common     | 4                      |

|---------|------------|------------------------|

| LCD     | Segment    | 32                     |

| Drive   | Duty       | Static, 1/2, 1/3, 1/4  |

|         | Bias       | 1/2, 1/3               |

| Display | Capability | 4x32 Matrix (1/4 Duty) |

Expandable using the LCD Driver HD44100H.

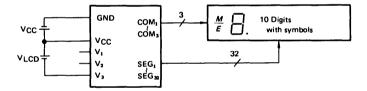

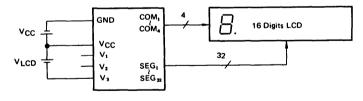

| HMCS46CL<br>(HD44848)<br>HMCS46C<br>(HD44840) |             | (HC<br>HM    | ICS47CL<br>044868)<br>ICS47C<br>044860) | (H)          | D-Ⅲ* <sup>3</sup><br>D44795,<br>044790) |              | D-IV* <sup>3</sup><br>D613901) |   |

|-----------------------------------------------|-------------|--------------|-----------------------------------------|--------------|-----------------------------------------|--------------|--------------------------------|---|

| 3/5                                           |             | 3/5          |                                         | 3/5          | 5                                       | 3/5          | ;                              |   |

| 0.4                                           | l/9         | 0.4          | /9                                      | 0.4          | I/6                                     | 0.8          | 3/13.5                         |   |

| ٧c                                            | c+0.3       | Vc           | c+0.3                                   | Vc           | c+0.3                                   | Vc           | c+0.3                          |   |

| -2                                            | 0 to +75    | -20          | ) to +75                                | -2           | ) to +75                                | - 20         | ) to +75                       |   |

| DP                                            | -42, DP-42S | FP-          | 54, DP-64S                              | FP           | -80                                     | FP           | -80                            |   |

| 4,0                                           | 96 x 10     | 4,096 x 10   |                                         |              | 2,048 x 10<br>128 x 10* <sup>2</sup>    |              | 96 x 10                        |   |

| 256 x 4<br>8                                  |             | 256 x 4<br>6 |                                         | 160 x 4<br>6 |                                         | 256 x 4<br>6 |                                |   |

|                                               |             |              |                                         |              |                                         |              |                                | 4 |

|                                               | -           |              |                                         |              | 4 x 1                                   |              | 4 x 1                          |   |

|                                               | -           | -            | 4 x 1                                   | 32           | 4 x 1                                   | 32           | 4 x 1                          |   |

| 32                                            | -           | 44           | -                                       |              | -                                       |              | _                              |   |

|                                               | 4 x 4       | 7            | 4 x 6                                   | 7            | 4 x 2                                   |              | 4 x 2                          |   |

|                                               | 1 x 16      | 7            | 1 x 16                                  |              | 1 x 16                                  | 7            | 1 x 16                         |   |

| 2                                             | •           | 2            |                                         | 2            | 2                                       |              |                                |   |

| 1.                                            |             | 1            |                                         | 1            |                                         | 1            |                                |   |

| 71<br>20/5                                    |             | 71           |                                         | 71           | 71                                      |              |                                |   |

|                                               |             | 20/5         |                                         | 20,          | 20/10                                   |              | /5                             |   |

|                                               |             | <b></b>      | Yes                                     |              |                                         | <u>_</u>     |                                |   |

| No/Yes                                        |             | No           | /Yes                                    | Ye           | S                                       | No           |                                |   |

| Ha                                            | lt          | Hal          | t                                       | Ha           | lt                                      | Ha           | lt                             |   |

| Hait<br>HD44857E                              |             | HD44857E     |                                         |              | HD44797E                                |              | HD44797E                       |   |

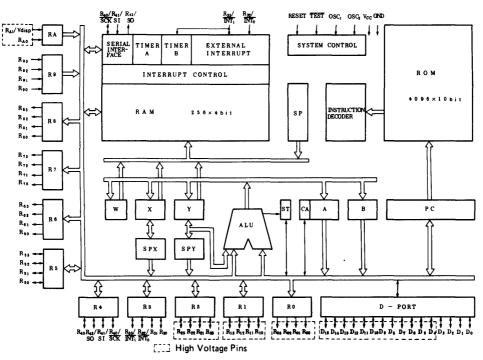

# QUICK REFERENCE GUIDE

# CMOS 4-BIT SINGLE-CHIP MICROCOMPUTER HMCS400 SERIES

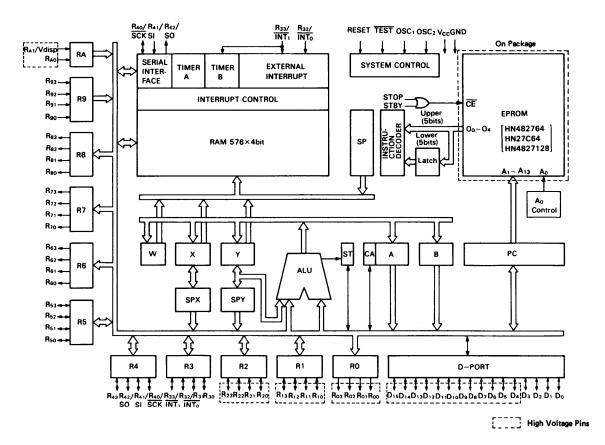

|           | Family                                             | y Name (Type  | Name)        |        | HMCS404C<br>HD614042) | н        | NCS404         | AC*       | н          | MÇS404CL*           | HC                           | 0614P080St                                                                        |

|-----------|----------------------------------------------------|---------------|--------------|--------|-----------------------|----------|----------------|-----------|------------|---------------------|------------------------------|-----------------------------------------------------------------------------------|

| 8         | Supply Voltage (V)<br>Power Dissipation (typ) (mW) |               |              | 4 to 6 |                       | 4.5 to 6 | .0             | 1         | 2,7 to 6.0 |                     | 4.5 to 5.5                   |                                                                                   |

| risti     |                                                    |               |              | 9.0    |                       | 13.5     |                |           | 4.5        |                     | 9.0                          |                                                                                   |

| 2 8       | Max. I/O Tern                                      | ninal Voltage | (V)          |        | Vcc-40                |          | Vcc-4          | 0         | T          | V <sub>CC</sub> -40 |                              | V <sub>CC</sub> -40                                                               |

| ara       | Operating Ten                                      | nperature Rar | ige (°C)     |        | -20 to +75            |          | -20 to +       | 75        | 1          | -20 to +75          |                              | -20 to +75                                                                        |

| ర్        | Package                                            |               |              | FI     | P-64, DP-64S          | FI       | -64, DP        | -64S      | FP         | -64, DP-64S         |                              | DC-64SP                                                                           |

|           | Memory                                             | ROM           | (bits)       |        | 4096 x 10             |          | 4096 × 1       | 10        |            | 4096 x 10           | with<br>EPR<br>•8,19<br>with | 6-word x 10-bit<br>standard<br>OM 2764<br>2-word x 10-bit<br>standard<br>OM 27128 |

|           |                                                    | RAM           | (bits)       |        |                       | 256 × 4  |                | 256 x 4   |            | 576 x 4             |                              |                                                                                   |

|           | Registers                                          | Registers     |              | 7      |                       | 7        |                | 7 16      |            |                     | 7 16                         |                                                                                   |

|           | Stack Registers                                    |               | 16           |        |                       | 16       |                |           |            |                     |                              |                                                                                   |

| Functions |                                                    | 4-Bit Input   | :            |        | 4 x 1<br>2 x 1        |          | 4 x 1<br>2 x 1 |           |            | 4 x 1<br>2 x 1      |                              | 4 x 1<br>2 x 1                                                                    |

| ŝ.        | I/O Ports                                          | 4-Bit Outp    | ut           | 58     | 4 x 4                 | 58       | 4 x 4          |           | 58         | 4 x 4               | 58                           | 4 x 4                                                                             |

|           | .,                                                 | 4-Bit Input   | t/Output     | 7      | 4 × 5                 | 7 **     | 4 x 5          |           | 7          | 4 x 5               |                              | 4 x 5                                                                             |

|           |                                                    | 1-Bit Input   | t/Output     |        | 1 x 16                |          | 1 x 16         | 6         | 1          | 1 x 16              |                              | 1 x 16                                                                            |

|           |                                                    | External      |              |        | 2                     | <u> </u> | 2              |           |            | 2                   |                              | 2                                                                                 |

|           | Interrupts                                         | Timer/Cou     | nter         | 1      | 2                     |          | 2              |           |            | 2                   |                              | 2                                                                                 |

|           | 1                                                  | Serial Inter  | face         |        | 1                     | T        | 1              |           | 1          | 1                   |                              | 1                                                                                 |

|           | Instructions                                       | Number of     | Instructions | 1      | 99                    |          | 99             |           | 1          | 99                  |                              | 99                                                                                |

|           | Instructions                                       | Cycle Time    | e (μs)       | 1      | 2                     |          | 1.33           |           |            | 4                   |                              | 1,33                                                                              |

|           | Built-in Clock                                     | Pulse Genera  | tor          |        |                       |          | Yes (E         | xternal o | lrive is p | oossible)           | -                            |                                                                                   |

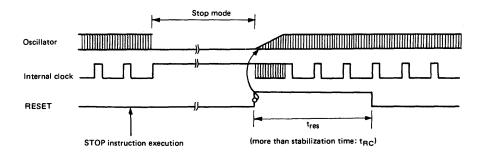

|           | Others                                             |               |              |        | Low                   | Power D  | issipatio      | n Mode    | (Stop n    | node, Stand-by      | mode)                        |                                                                                   |

| 1e        | ference Page                                       |               |              | 1      | 357                   |          | 394            |           | 1          | 396                 |                              | 398                                                                               |

\* Under Development † EPROM on the Package Type

.

.

.

.

~~

# **INTRODUCTION OF PACKAGES**

Hitachi microcomputer devices are offered in a variety of packages, to meet various user requirements.

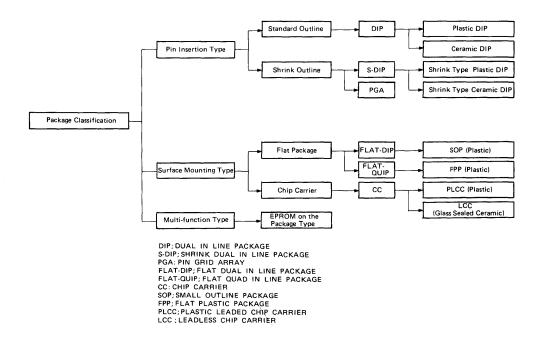

#### 1. Package Classification

When selecting suitable packaging, please refer to the Package Classifications given in Fig. 1 for pin insertion, surface mount, and multi-function types, in plastic and ceramic.

Fig. 1 Package Classification according to Material and Printed Circuit Board Mounting Type

## INTRODUCTION OF PACKAGES

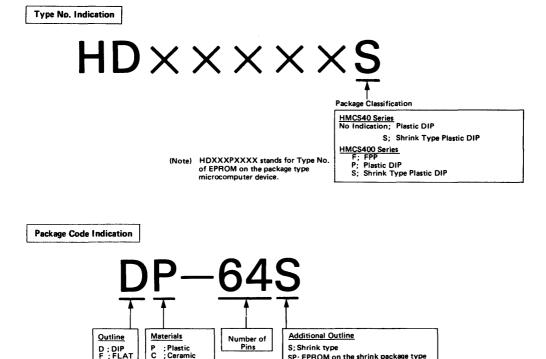

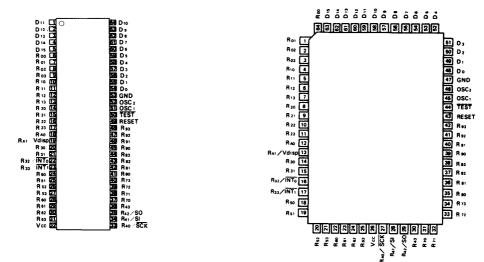

#### 2. Type No. and Package Code Indication

The Hitachi type No. for 4-bit single-chip microcomputer devices is followed by package material and outline specifications, as shown below. The package type used for each device is identified by code as follows, illustrated in the data sheet of each device.

When ordering, please write the package code next to the type number.

SP; EPROM on the shrink package type

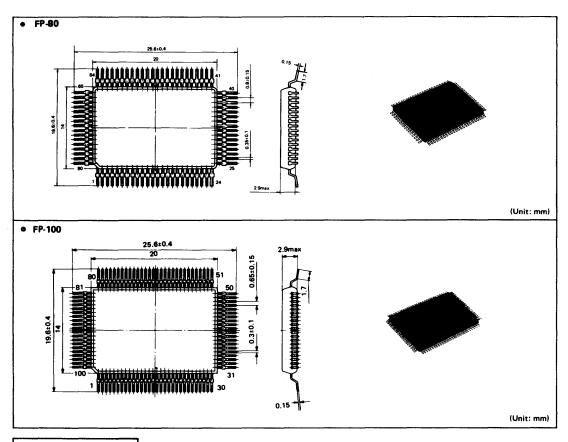

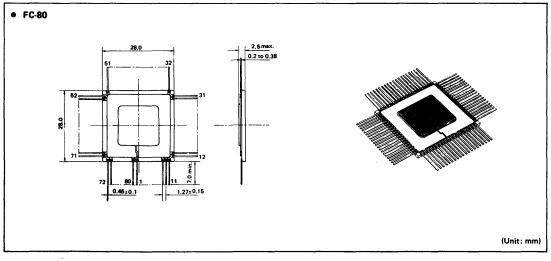

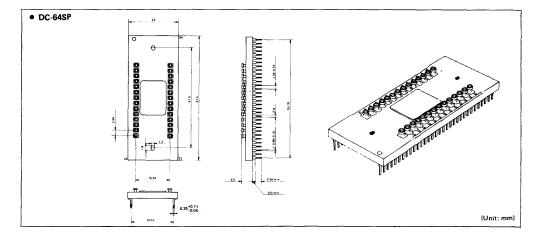

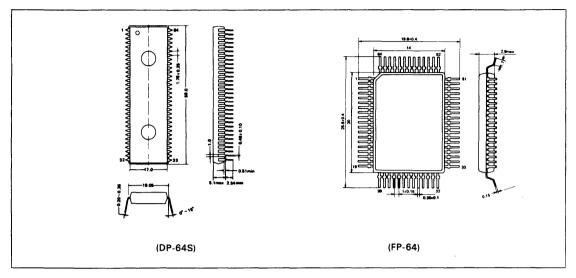

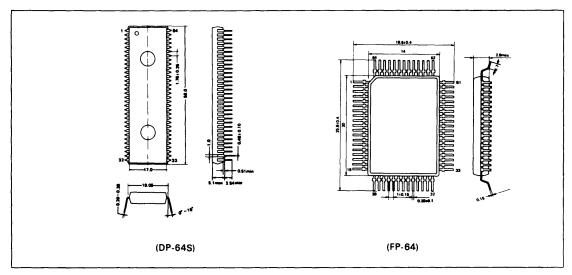

# 3. Package Dimensional Outline

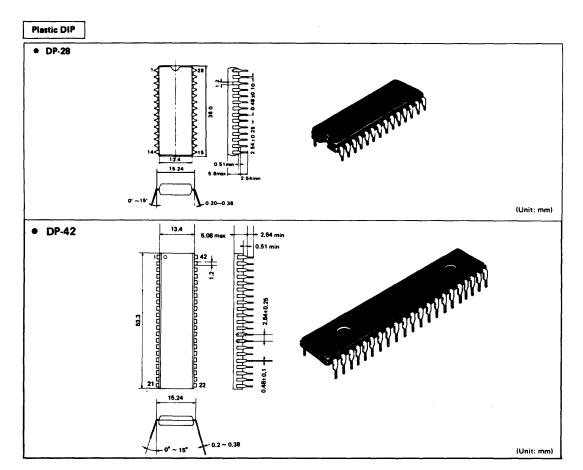

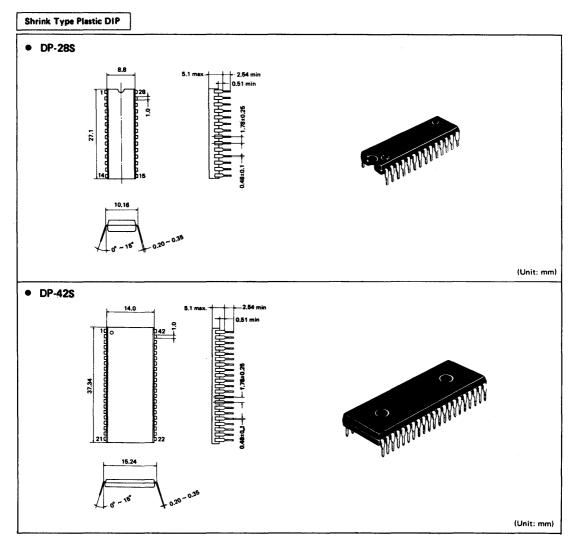

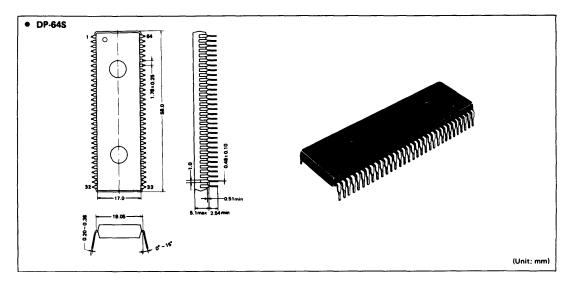

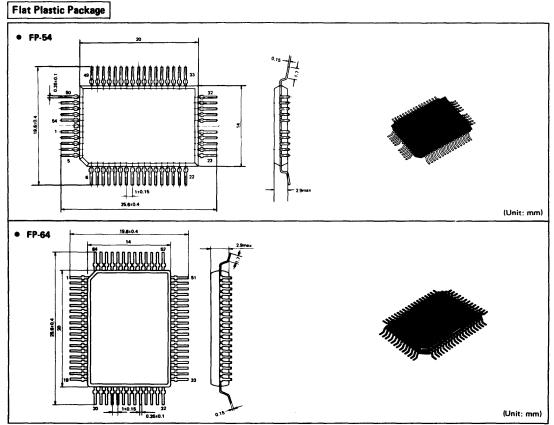

Hitachi 4-bit single-chip microcomputer devices employ the packages shown in Table 1 according to PCB mounting method.

| Mounting method       | Package classification                        |              | Package material | Package code                      |

|-----------------------|-----------------------------------------------|--------------|------------------|-----------------------------------|

|                       | Standard outline (DIP) Shrink outline (S-DIP) |              | Plastic          | DP-28<br>DP-42                    |

| Pin insertion type    |                                               |              | Plastic          | DP-28S<br>DP-42S<br>DP-64S        |

| Surface mounting type | Flat package                                  | FPP          | Plastic          | FP-54<br>FP-64<br>FP-80<br>FP-100 |

|                       | FPC                                           |              | Ceramic          | FC-80                             |

| Multi-function type   | EPROM on the                                  | backage type | Ceramic          | DC-64SP                           |

Table 1 Package List

# **INTRODUCTION OF PACKAGES-**

# INTRODUCTION OF PACKAGES

15

# INTRODUCTION OF PACKAGES-

# Flat Package of Ceramic

j<sup>1</sup>

#### 4. Mounting Method

Package lead pins are surface treated with solder coating or plating to facilitate PCB mounting. The lead pins are connected to the package by eutectic solder. Common connecting method of leads and precautions are explained as follows:

#### 4.1 Mounting Methods of Pin Insertion Type Package Insert lead pins into the PCB through-holes (usually about

$\phi$ 0.8mm). Soak leads in a wave solder tub.

Lead pins held by the through-holes enable handling of the package through the soldering process, and facilitate automated soldering. When soldering leads in the wave solder tub, do not get solder on the package.

#### 4.2 Mounting Method of Surface Mount Type Package

Apply the specified quantity of solder paste to the pattern on any printed board by the screen printing method, to temporarily fix the package to the board. The solder paste melts when heated in a reflowing furnace, and package leads and the pattern of the printed board are fixed by the surface tension of the melted solder and self alignment.

The size of the pattern where leads are attached should be 1.1 to 1.3 times the leads' width, depending on paste material or furnace adjustment.

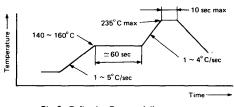

The temperature of the reflowing furnace is dependent on packaging material and type. Fig. 2 lists the adjustment of the reflowing furnace for FPP. Pre-heat the furnace to  $150^{\circ}$  C. Surface temperature of the resin should be kept at  $235^{\circ}$  C maximum for 10 minutes or less.

- (1) The temperature of the leads should be kept at 260° for 10 minutes or less.

- (2) The temperature of the resin should be kept at 235° for 10 minutes or less.

- (3) Below is shown the temperature profile when soldering a package by the reflowing method.

#### Fig. 2 Reflowing Furnace Adjustment for FPP

Employ adequate heating or temperature control equipment to prevent damage to the plastic package epoxy-resin material. When using an infrared heater, avoid long exposure at temperatures higher than the glass transition point of epoxy-resin (about 150° C), which may cause package damage and loss of reliability characteristics. Equalize the temperature inside and outside of packages by reducing the heat of the upper surface of the packages.

FPP leads may easily bend in shipment or during handling, and impact soldering onto the printed board. Heat the bent leads again with a soldering iron to reshape them.

Use a rosin flux when soldering. Do not use chloric flux because the chlorine in the flux has a tendency to remain on the leads and reduce reliability. Use alcohol, chlorothene or freon to wash away rosin flux from packages. These solvents should not remain on the packages for an excessive length of time, because the package markings may disappear.

# QUALITY ASSURANCE

#### 1. VIEWS ON QUALITY AND RELIABILITY

Basic views on quality at Hitachi are to meet the individual uers' required quality level and maintain a general quality level equal to or above that of the general market. The quality required by the user may be specified by contract, or may be indefinite. In either case, efforts are made to assure reliable performance in actual operating circumstances. Quality control during the manufacturing process, and quality awareness from design through production lead to product quality and customer satisfaction. Our quality assurance technique consists basically of the following steps:

- (1) Build in reliability at the design stage of new product development.

- (2) Build in quality at all steps in the manufacturing process.

- (3) Execute stringent inspection and reliability confirmation of final products.

- (4) Enhance quality levels through field data feed back.

- (5) Cooperate with research laboratories for higher quality and reliability.

With the views and methods mentioned above, utmost efforts are made to meet users' requirements.

# 2. RELIABILITY DESIGN OF SEMICONDUCTOR DEVICES

#### 2.1 Reliability Targets

The reliability target is an important factor in sales, manufacturing, performance, and price. It is not adequate to set a reliability target based on a single set of common test conditions. The reliability target is set based on many factors:

- (1) End use of semiconductor device.

- (2) End use of equipment in which device is used.

- (3) Device manufacturing process.

- (4) End user manufacturing techniques.

- (5) Quality control and screening test methods.

- (6) Reliability target of system.

#### 2.2 Reliability Design

The following steps are taken to meet the reliability targets:

- (1) Design Standardization

- As for design rules, critical items pertaining to quality and reliability are always studied at circuit

design, device design, layout design, etc. Therefore, as long as standardized processing and materials are used the reliability risk is extremely small even in the case of new development devices, with the exception of special requirements imposed by functional needs.

(2) Device Design

It is important for the device design to consider total balance of process, structure, circuit, and layout design, especially in the case where new processes and/or new materials are employed. Rigorous technical studies are conducted prior to device development.

(3) Reliability Evaluation by Functional Test Functional Testing is a useful method for design and process reliability evaluation of IC's and LSI devices which have complicated functions.

The objectives of Functional Test are:

- Determining the fundamental failure mode.

- Analysis of relation between failure mode and manufacturing process.

- Analysis of failure mechanism.

- Establishment of QC points in manufacturing process.

#### 2.3 Design Review

Design Review is an organized method to confirm that a design satisfies the performance required and meets design specifications. In addition, design review helps to insure quality and reliability of the finished products. At Hitachi, design review is performed from the planning stage to production for new products, and also for design changes on existing products. Items discussed and considered at design review are: (1) Description of the products based on design

- documents.

- (2) From the standpoint of each participant, design documents are studied, and for points needing clarification, further investigation will be carried out.

- (3) Specify quality control and test methods based on design documents and drawings.

- (4) Check process and ability of manufacturing line to achieve design goal.

- (5) Preparation for production.

- (6) Planning and execution of sub-programs for design changes proposed by individual specialists,

for test, experiments, and calculations to confirm the design changes.

(7) Analysis of past failures with similar devices, discussion of methods to prevent them, and planning and execution of test programs to confirm success.

# 3. QUALITY ASSURANCE SYSTEM

#### 3.1 Activity of Quality Assurance

General views of overall quality assurance in Hitachi are as follows:

- (1) Problems in each individual process should be solved in the process. Therefore, at the finished product stage the potential failure factors have been removed.

- (2) Feedback of information is used to insure a satisfactory level of ability process.

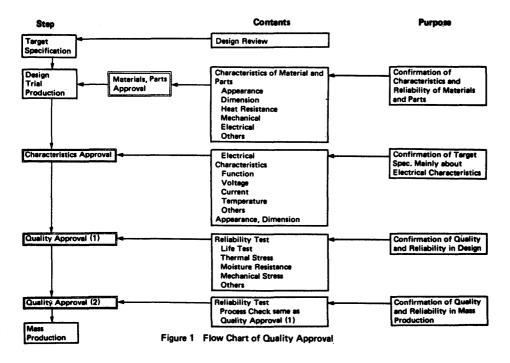

#### 3.2 Quality Approval

To insure quality and reliability, quality approval is carried out at the preproduction stage of device design, as described in section 2. Our views on quality approval are:

- (1) A third party executes approval objectively from the standpoint of the customer.

- (2) Full consideration is given to past failures and information from the field.

- (3) No design change or process change without QA approval.

- (4) Parts, materials, and processes are closely monitored.

- (5) Control points are established in mass production after studying the process abilities and variables.

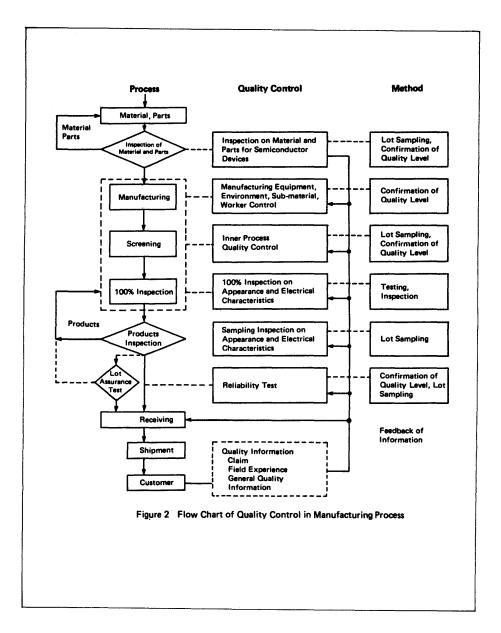

#### 3.3 Quality and Reliability Control at Mass Production

Quality control is accomplished through division of functions in manufacturing, quality assurance, and other related departments. The total function flow is shown in Fig. 2. The main points are described below.

### 3.3.1 Quality Control of Parts and Materials

As semiconductor devices tend towards higher performance and higher reliability, the importance of quality control of parts and materials becomes paramount. Items such as crystals, lead frames, fine wire for wire bonding, packages, and materials needed in manufacturing processes such as masks and chemicals, are all subject to rigorous inspection and control. Incoming inspection is performed based on the purchase specification and drawing. The sampling is executed based mainly on MIL-STD-105D.

The other activities of quality assurance are as follows:

- (1) Outside vendor technical information meeting.

- (2) Approval and guidance of outside vendors.

- (3) Chemical analysis and test.

The typical check points of parts and materials are shown in Table 1.

| Material,<br>Parts | Importent<br>Control Items    | Point for Check                               |

|--------------------|-------------------------------|-----------------------------------------------|

|                    | Appearance                    | Demage and Contamina-<br>tion on Surface      |

| Nafer              | Dimension<br>Sheet Resistance | Flatness<br>Resistance                        |

|                    | Defect Density                | Defect Numbers                                |

|                    | Crystel Axis                  |                                               |

|                    | Appearance                    | Defect Numbers, Scratch                       |

| Mask               | Dimension                     | Dimension Level                               |

|                    | Gradation                     | Uniformity of Gradation                       |

| ine                | Appearance                    | Contamination, Scratch,                       |

| Vire for           | Dimension                     | Bend, Twist                                   |

| Vire               | Purity                        | Purity Level                                  |

| Bonding            | Elongation Ratio              | Mechanical Strength                           |

|                    | Appearance                    | Contamination, Scratch<br>Dimension Level     |

| rame               | Dimension<br>Processing       | Dimension Level                               |

|                    | Accuracy                      |                                               |

|                    | Plating<br>Mounting           | Bondability, Solderability<br>Heat Resistance |

|                    | Characteristics               | near nusicance                                |

|                    | Appearance                    | Contamination, Scratch                        |

|                    | Dimension<br>Leak Resistance  | Dimension Level                               |

|                    | Plating                       | Bondability, Solderability                    |

| eramic             | Mounting                      | Heat Resistance                               |

| Package            | Characteristics<br>Electrical |                                               |

|                    | Characteristics               |                                               |

|                    | Mechanical<br>Strength        | Mechanical Strength                           |

|                    | Composition                   | Characteristics of                            |

|                    |                               | Plastic Material                              |

|                    | Electrical<br>Characteristics |                                               |

| lastic             | Thermal                       |                                               |

| 103110             | Characteristics               | Martin Davidson                               |

|                    | Molding<br>Performance        | Molding Performance                           |

|                    | Mounting                      | Mounting Characteristics                      |

|                    | Characteristics               | 1                                             |

#

#### 3.3.2 Inner Process Quality Control

Inner Process Quality Control performs very important functions in quality assurance of semiconductor devices. The manufacturing Inner Process Quality Control is shown in Fig. 3.

(1) Quality Control of Semi-final Products and Final Products

Potential failure factors of semiconductor devices are removed in the manufacturing process. To achieve this, check points are set-up in each process and products which have potential failure factors are not moved to the next process step. Manufacturing lines are rigidly selected and tight inner process quality controls are executed—rigid checks in each process and each lot, 100% inspection to remove failure factors caused by manufacturing variables and high temperature aging and temperature cycling. Elements of inner process quality control are as follows:

- Condition control of equipment and workers environment and random sampling of semifinal products.

- Suggestion system for improvement of work.

- Education of workers.

- Maintenance and improvement of yield.

- Determining quality problems, and implementing countermeasures.

- Transfer of quality information.

- (2) Quality Control of Manufacturing Facilities and Measuring Equipment

Manufacturing equipment is improving as higher performance devices are needed. At Hitachi, the automation of manufacturing equipment is encouraged. Maintenance Systems maintain operation of high performance equipment. There are daily inspections which are performed based on related specifications. Inspection points are listed in the specifications and are checked one by one to prevent any omission. As for adjustment and maintenance of measuring equipment, specifications are checked one by one to maintain and improve quality.

(3) Quality Control of Manufacturing Circumstances and Sub-Materials

The quality and reliability of semiconductor devices are highly affected by the manufacturing process. Therefore, controls of manufacturing circumstances such as temperature, humidity and dust, and the control of submaterials, like gas, and pure water used in a manufacturing process, are intensively executed.

Dust control is essential to realize higher integration and higher reliability of devices. At Hitachi, maintenance and improvement of cleanliness at manufacturing sites is accomplished through attention to buildings, facilities, air conditioning systems, delivered materials, clothes, work environment, and periodic inspection of floating dust concentration.

### 3.3.3 Final Product Inspection and Reliability Assurance

(1) Final Product Inspection

Lot inspection is done by the quality assurance

|      | Process                                           | Contr            | ol Point                                                             | Purpose of Control                                                            |

|------|---------------------------------------------------|------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------|

|      | $\nabla$ Purchase of Material                     |                  |                                                                      |                                                                               |

| er — |                                                   | Wafer            | Characteristics, Appearance                                          | Scratch, Removal of Crystal<br>Defect Wafer                                   |

|      | C Surface Oxidation                               | Oxidation        |                                                                      | Assurance of Resistance                                                       |

|      | Inspection on Surface Oxidation                   |                  | Appearance, Thickness of<br>Oxide Film                               | Pinhole, Scratch                                                              |

|      | OPhoto Resist                                     | Photo            |                                                                      |                                                                               |

|      |                                                   | Resist           | Dimension, Appearance                                                | Dimension Level                                                               |

|      | ↓ Inspection on Photo Resist<br>♦ PQC Level Check | ļ                | Dimension, Appearance                                                | Check of Photo Resist                                                         |

|      |                                                   | Diffusion        | Diffusion Depth, Sheet<br>Resistance                                 | Diffusion Status                                                              |

|      | Inspection on Diffusion                           |                  | Gate Width                                                           | Control of Basic Parameters                                                   |

|      | ♦ PQC Level Check                                 |                  | Characteristics of Oxide Film<br>Breakdown Voltage                   | (VTH, etc.) Cleanness of sur<br>Prior Check of VIH<br>Breakdown Voltage Check |

|      | C Evaporation                                     | Evapora-<br>tion | Thickness of Vapor Film,<br>Scratch, Contamination                   | Assurance of Standard<br>Thickness                                            |

|      | Inspection on Evaporation                         |                  |                                                                      |                                                                               |

|      | Wafer Inspection                                  | Wafer            | Thickness, VTH Characteris-<br>tics                                  | Prevention of Crack,<br>Quality Assurance of Scribe                           |

|      | Inspection on Chip<br>Electrical Characteristics  | Chip             | Electrical Characteristics                                           |                                                                               |

|      | 🗘 Chip Scribe                                     |                  | Appearance of Chip                                                   |                                                                               |

|      | Inspection on Chip<br>Appearance                  |                  |                                                                      |                                                                               |

|      | PQC Lot Judgement                                 |                  |                                                                      |                                                                               |

|      |                                                   | Assembling       | Appearance after Chip<br>Bonding<br>Appearance after Wire<br>Bonding | Quality Check of Chip<br>Bonding<br>Quality Check of Wire<br>Bonding          |

|      | ♦ PQC Level Check                                 |                  | Pull Strength, Compression<br>Width, Shear Strength                  | Prevention of Open and<br>Short                                               |

|      | L Inspection after                                |                  | Appearance after Assembling                                          |                                                                               |

|      | PQC Lot Judgement                                 |                  | 1                                                                    |                                                                               |

| age  | Sealing                                           | Sealing          | Appearance after Sealing<br>Outline, Dimension                       | Guarantee of Appearance<br>and Dimension                                      |

|      | ♦ PQC Level Check                                 | Marking          | Marking Strength                                                     |                                                                               |

|      | O Final Electrical Inspection                     |                  |                                                                      | 1                                                                             |

|      | ♦ Failure Analysis                                |                  | Analysis of Failures, Failure<br>Mode, Mechanism                     | Feedback of Analysis Infor-<br>mation                                         |

|      | Appearance Inspection                             |                  |                                                                      |                                                                               |

|      | Sampling Inspection on Products                   |                  |                                                                      |                                                                               |

|      | 🗘 Receiving                                       |                  |                                                                      | 1                                                                             |

|      | Shipment                                          |                  | 1                                                                    |                                                                               |

Figure 3 Example of Inner Process Quality Control

department for products which were judged good in 100% test . . . the final process in manufacturing. Though 100% yield is expected, sampling inspection is executed to prevent mixture of bad product by mistake. The inspection is executed not only to confirm that the products have met the users' requirements but also to consider potential

quality factors. Lot inspection is executed based on MIL-STD-105D.

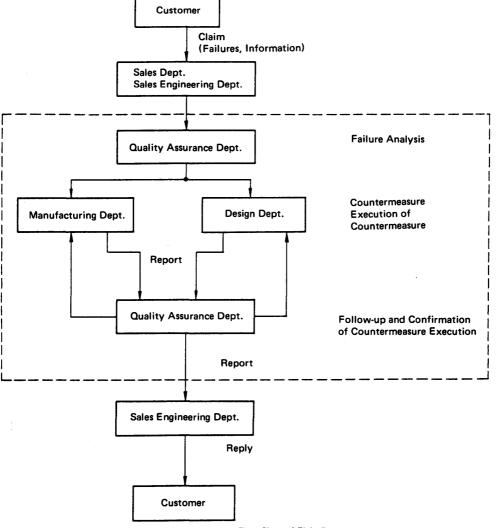

(2) Reliability Assurance Tests To assure the reliability of semiconductor devices, reliability tests and tests on individual manufacturing lots that are required by the user, are periodically performed.

Figure 4 Process Flow Chart of Field Failure

#### 1. INTRODUCTION

Microcomputers provide high reliability and quality to meet the demands of increased functions, enlarging scale, and widening application. Hitachi has improved the quality level of microcomputer products by evaluating reliability, building quality into the manufacturing process, strengthening inspection techniques, and analyzing field data.

The following reliability and quality assurance data for Hitachi 8-bit single-chip microcomputers indicates results from test and failure analysis.

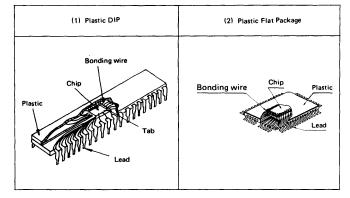

#### 2. PACKAGE AND CHIP STRUCTURE 2.1 Packaging

#### Production output and application of plastic packaging continues to increase, expanding to automobile measuring and control systems, and computer terminal equipment operating under severe conditions. To meet this demand, Hitachi has significantly improved moisture resistance and operational stability in the plastic manufacturing process.

Plastic and side-brazed ceramic package structures are shown in Figure 1 and Table 1.

Figure 1 Package Structure

#### Table 1 Package Material and Properties

| Item      | Plastic DIP             | Plastic Flat Package    |

|-----------|-------------------------|-------------------------|

| Package   | Ероху                   | Ероху                   |

| Lead      | Solder dipping Alloy 42 | Solder plating Alloy 42 |

| Die bond  | Au-Si or Ag paste       | Au-Si or Ag paste       |

| Wire bond | Thermo compression      | Thermo compression      |

| Wire      | Au                      | Au                      |

# RELIABILITY TEST DATA OF MICROCOMPUTER-

# 2.2 Chip Structure

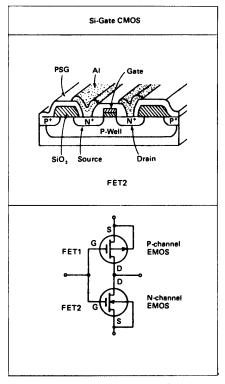

The HMCS40 family is produced in low power CMOS technology. The Si-gate process is used because of high reliability and high density.

Chip structure and basic circuitry are shown in Figure 2.

Figure 2 Chip Structure and Basic Circuit

# 3. QUALITY QUALIFICATION AND EVALUATION

# 3.1 Reliability Test Methods

Reliability test methods shown in Table 2 are used to qualify and evaluate the new products and new process.

| Table 2 | Reliability | y Test Methods |

|---------|-------------|----------------|

|---------|-------------|----------------|

| Test Items                                                                                       | Test Condition                                                                   | MIL-STD-883B Method No. |

|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------|

| Operating Life Test                                                                              | 125°C, 1000hr                                                                    | 1005,2                  |

| High Temp, Storage<br>Low Temp, Storage<br>Steady State Humidity<br>Steady State Humidity Biased | Tstg max, 1000hr<br>Tstg min, 1000hr<br>65°C 95%RH, 1000hr<br>85°C 85%RH, 1000hr | 1008,1                  |

| Temperature Cycling<br>Temperature Cycling                                                       | -55°C ~ 150°C, 10 cycles<br>-20°C ~ 125°C, 200 cycles                            | 1010,4                  |

| Thermal Shock<br>Soldering Heat                                                                  | 0°C ~ 100°C, 100 cycles<br>260°C, 10 sec                                         | 1011,3                  |

| Mechanical Shock                                                                                 | 1500G 0.5 msec, 3 times/X, Y, Z                                                  | 2002,2                  |

| Vibration Fatigue                                                                                | 60Hz 20G, 32hrs/X, Y, Z                                                          | 2005,1                  |

| Variable Frequency                                                                               | 20~2000Hz 20G, 4 min/X, Y, Z                                                     | 2007,1                  |

| Constant Acceleration                                                                            | 20000G, 1 min/X, Y, Z                                                            | 2001,2                  |

| Lead Integrity (DIP)                                                                             | 225gr, 90° 3 times                                                               | 2004,3                  |

| Lead Integrity (FPP)                                                                             | 225gr, 90° 1 time                                                                | 2004                    |

# 3.2 Reliability Test Results

Reliability Test Results of 4-bit single-chip microcomputer devices is shown in Table 3 to Table 7.

## Table 3 Dynamic Life Test

| Device  | Package | Sample Size | Component Hours | Failure |

|---------|---------|-------------|-----------------|---------|

| HMCS47C | DP-64S  | 90          | 90000           | 0       |

|         | FP-54   | 90          | 90000           | 0       |

| HMCS46C | DP-42   | 90          | 90000           | 0       |

|         | DP-42S  | 45          | 45000           | 0       |

| HMCS45C | DP-64S  | 45          | 45000           | 0       |

|         | FP-54   | 120         | 120000          | 1 *     |

| HMCS44C | DP-42   | 162         | 162000          | 1 **    |

|         | DP-42S  | 45          | 45000           | 0       |

| LCD-III | FP-80   | 90          | 90000           | 0       |

\* Surface contamination \*\* Aluminum metallization open

# Table 4 High Temperature, High Humidity Test (Moisture Resistance Test)

# (1) 85°C 85%RH Bias Test

| Package  | 168 hrs | 500 hrs | 1000 hrs |                     |

|----------|---------|---------|----------|---------------------|

| DIP-type | 0/205   | 0/205   | 1*/205   |                     |

| FP-type  | 0/185   | 0/185   | 1*/185   | *Aluminum corrosion |

Condition; C MOS: V<sub>CC</sub> = 5.5V

## (2) High Temperature High Humidity Storage Life Test

## a) 65°C/95%RH

| Package  | 168 hrs | 500 hrs | 1000 hrs |                     |

|----------|---------|---------|----------|---------------------|

| DIP-type | 0/870   | 0/870   | 1*/870   |                     |

| FP-type  | 0/545   | 0/545   | 1*/545   | *Aluminum corrosion |

# RELIABILITY TEST DATA OF MICROCOMPUTER-

| b) | 85°C/95%RH |

|----|------------|

| -  | 0.1        |

| Package  | 168 hrs | 500 hrs | 1000 hrs |

|----------|---------|---------|----------|

| DIP-type | 0/220   | 0/220   | 1*/220   |

| FP-type  | 0/165   | 0/165   | 1*/165   |

\*Aluminum corrosion

## (3) Pressure Cooker Test

(121°C, 2 atm)

| Package  | 40 hrs | 60 hrs | 100 hrs | 200 hrs |

|----------|--------|--------|---------|---------|

| DIP-type | 0/55   | 0/55   | 0/55    | 0/55    |

| FP-type  | 0/55   | 0/55   | 0/55    | 1*/55   |

\*Current leakage

# (4) MIL-STD-883B Moisture Resistance Test

(-65°C ~ - 10°C, 90%RH or more)

| Package  | 10 cycles | 20 cycles | 40 cycles |

|----------|-----------|-----------|-----------|

| DIP-type | 0/50      | 0/50      | 0/50      |

| FP-type  | 0/22      | 0/22      | 0/22      |

## Table 5 Temperature Cycling Test

(-55°C ~ 150°C)

| Package  | 10 cycles | 100 cycles | 200 cycles |

|----------|-----------|------------|------------|

| DIP-type | 0/1637    | 0/1637     | 0/1637     |

| FP-type  | 0/1514    | 0/1514     | 0/1514     |

Table 6 High Temperature, Low Temperature Storage Life Test

| Package  | Temperature | 168 hrs | 500 hrs | 1000 hrs |

|----------|-------------|---------|---------|----------|

| D10 +    | 150°C       | 0/43    | 0/43    | 0/43     |

| DIP-type | -55°C       | 0/50    | 0/50    | 0/50     |

|          | 150°C       | 0/53    | 0/53    | 0/53     |

| FP-type  | -55°C       | 0/40    | 0/40    | 0/40     |

| Test Item                | Condition                            | Plastic     | DIP     | Flat Plastic P | ackage  |

|--------------------------|--------------------------------------|-------------|---------|----------------|---------|

| iest item                | Condition                            | Sample Size | Failure | Sample Size    | Failure |

| Thermal Shock            | 0°C ~ 100°C<br>10 cycles             | 150         | 0       | 100            | 0       |

| Soldering Heat           | 260°C, 10 sec.                       | 140         | 0       | 160            | 0       |

| Salt Water Spray         | 35°C, NaCl 5%<br>24 hrs              | 40          | 0       | 40             | 0       |

| Solderability            | 230°C, 5 sec.<br>Rosin flux          | 34          | 0       | 34             | 0       |

| Drop Test                | 75cm, maple board<br>3 times         | 38          | 0       | 38             | 0       |

| Mechanical Shock         | 1500G, 0.5ms<br>3 times/X, Y, Z      | 45          | 0       | 45             | 0       |

| Vibration Fatigue        | 60 Hz, 20G<br>32hrs/X, Y, Z          | 120         | 0       | 45             | 0       |

| Vibration Variable Freq. | 100 ~ 2000Hz<br>20G, 4 times/X, Y, Z | 45          | 0       | 45             | 0       |

| Lead Integrity           | 225g, 90°<br>Bonding 3 times         | 45          | 0       | -              | -       |

|                          | 225g, 90°<br>Bonding 1 time          | -           | _       | 45             | 0       |

# Table 7 Mechanical and Environmental Test

### RELIABILITY TEST DATA

#### 4. PRECAUTIONS

#### 4.1 Storage

To prevent deterioration of electrical characteristics, solderability, appearance or structure, Hitachi recommends semiconductor devices be stored as follows:

- (1) Store in ambient temperatures of 5 to 30° C, with a relative humidity of 40 to 60%.

- (2) Store in a clean, dust- and active gas-free environment.

- (3) Store in conductive containers to prevent static electricity.

- (4) Store without any physical load.

- (5) When storing devices for an extended period, store in an unfabricated form, to minimize corrosion of pre-formed lead wires.

- (6) Unsealed chips should be stored in a cool, dry, dark and dust-free environment. Assembly should be performed within 5 days of unpacking. Devices can be stored for up to 20 days in dry nitrogen gas with a dew point at -30° C or less.

- (7) Prevent condensation during storage due to rapid temperature changes.

#### 4.2 Transportation

General precautions for electronic components are applicable in transporting semiconductors, units incorporating semiconductors, and other similar systems. In addition, Hitachi recommends the following:

- (1) When transporting semiconductor devices or printed circuit boards, minimize mechanical vibration and shock. Use containers or jigs which will not induce static electricity as a result of vibration. Use of an electrically conductive container or aluminum foil is recommended.

- (2) To prevent device deterioration from clothing-induced static electricity, workers should be properly grounded while handling devices. Use of a 1 M ohm resistor is recommended to prevent electric shock.

- (3) When transporting printed curcuit boards containing semiconductor devices, suitable preventive measures against static electricity must be taken. Voltage build-up can be avoided by shorting the card-edge terminals. When a belt conveyor is used, apply some surface treatment to prevent build-up of electrical charge.

- (4) Minimize mechanical vibration and shock when transporting semiconductor devices or printed circuit boards.

#### 4.3 Handling for Measurement

Avoid static electricity, noise and voltage surge when measuring or mounting devices. Precaution should be taken against current leakage through terminals and housings of curve tracers, synchroscopes, pulse generators, and DC power sources.

When testing devices, prevent voltage surges from the tester, attached clamping circuit, and any excessive voltage possible through accidental contact.

In inspecting a printed circuit board, power should not be applied if any solder bridges or foreign matter is present.

#### 4.4 Soldering

Semiconductor devices should not be exposed to high temperatures for excessive periods. Soldering must be performed consistent with temperature conditions of  $260^\circ$  C for 10 seconds,  $350^\circ$  C for 3 seconds, and at a distance of 1 to 1.5mm from the end of the device package.

A soldering iron with secondary voltage supplied through a grounded transformer is recommended to protect against leakage current. Use of alkali or acid flux, which may corrode the leads, is not recommended.

#### 4.5 Removing Residual Flux

Detergent or ultrasonic removal of residual flux from circuit boards is necessary to ensure system reliability. Selection of detergent type and cleaning conditions are important factors.

When chloric detergent is used for plastic packaged devices, care must be taken against package corrosion. Extended cleaning periods and excessive temperature conditions can cause the chip coating to swell due to solvent permeation. Hitachi recommends use of Lotus and Dyfron solvents. Trichloroethvlene solvent is not suitable.

The following conditions are advisable for ultrasonic cleaning:

- Frequency: 28 to 29 k Hz (to avoid device resonation)

- Ultrasonic output: 15W/l

- Keep devices from making direct contact with power generator

- Cleaning time: Less than 30 seconds.

# DESIGN PROCEDURE AND SUPPORT TOOLS FOR 4-BIT SINGLE-CHIP MICROCOMPUTER

The cross assembler and the hardware simulator using various types of computer are prepared by Hitachi as supporting systems to develop user's programs.

ered as the LSI by the company.

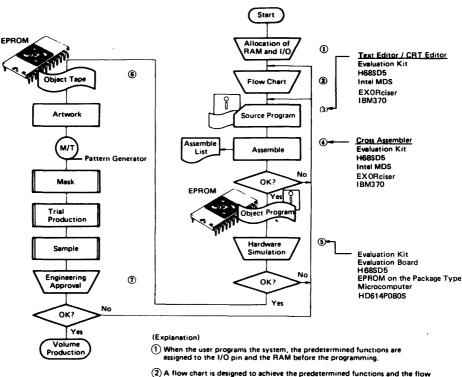

Fig. 1 shows the typical program design procedure and Table 1 shows the system development support tools for 4-bit single-chip microcomputer family used in these processes.

User's programs are mask programmed into the ROM and deliv-

- (2) A flow chart is designed to achieve the predetermined functions and the flow chart is coded by using the mnemonic code.

- (3) The coded flow chart is punched into the card or the paper tape or written into the floppy disk, to generate a source program.

- The source program is assembled by the evaluation kit or the H68SD5, to generate the object program. In this case, errors during the assembling are also detected.

- (5) Hardware simulation is performed to confirm the program. The company provides four kinds of hardware, the H68SD5, the evaluation kit, the evaluation board and the EPROM on the package type microcomputer. The consumers are able to choose the best suitable tool.

- (6) The completed program is sent to the company in the form of EPROM or the object tape.

- ⑦ Options such as ROM is masked by the company, LSI is testatively produced and the sample is handed in to the user. After the user has evaluated the sample and confirmed that the program is correct, mass production is started.

Figure 1 Program Design Procedure

## DESIGN PROCEDURE AND SUPPORT TOOLS FOR 4-BIT SINGLE-CHIP MICROCOMPUTERS

| Family No.                 |                              | Resident System           |             |                                       |           | Cross System     |            |              |  |

|----------------------------|------------------------------|---------------------------|-------------|---------------------------------------|-----------|------------------|------------|--------------|--|

|                            | *2                           | Evaluation                | EPROM on    | H68SD5 +                              |           | Intel MDS220/230 |            |              |  |

|                            | Evaluation Kit <sup>*2</sup> | Board                     | the Package | Emulator set*3<br>(Hardware+Software) | 1BM370    | ISIS-II          | CP/M       | EXORciser-11 |  |

| HMCS44C<br>HMCS45C         | H40EVKIT2                    | H45CEV00<br>H47CEV00      | _           | H68SD5+H40MIX1                        | S40XAM1-T | S40MDS1-F        | -          | S40EXR1-F    |  |

| HMCS46C<br>HMCS47C         | H40EVKIT2                    | H47CEV00                  | -           | H68SD5+H40MIX1                        | -         | S40MDS1-F        | -          | S40EXR1-F    |  |

| LCD-111                    | H40EVKIT4*1                  | H40LCEV00<br>H40LCEV04 *1 | -           | H68SD5+H40MIX2<br>H68SD5+H40MIX4*1    | S40XAM1-T | S40MDS1-F        | -          | S40EXR1-F    |  |

| LCD-IV                     | H40EVKIT4*1                  | H40LCEV04*1               | -           | H68SD5+H40M1X4*1                      | -         | S40MDS1-F        | -          | S40EXR1-F    |  |

| HMCS404C                   | -                            | -                         | HD614P080S  | H68SD5+H400CMIX1                      | -         | S400MDS1F        | S400MDS2F  | -            |  |

| HMCS404CL*1<br>HMCS404AC*1 | -                            | -                         | *1          | *1                                    | -         | S400MDS1 F       | S400MDS2 F | -            |  |

## Table 1 System Development Support Tools

\*1 : Under Davelopment

\*2 : Cross Assembler is Supplied with Evaluation Kit.

\*3 : Cross Assembler is Supplied with Emulator.

\*4 : MDS is a registered trade mark of Mohorwk Data Science Corp. ISIS-II is a registered trade mark of Intel Corp. CP/M is a registered trade mark of Digital Research Inc. EXORciser is a registered trade mark of Motorola Inc.

# DESIGN PROCEDURE AND SUPPORT TOOLS FOR 4-BIT SINGLE-CHIP MICROCOMPUTERS

# ■ SINGLE-CHIP MICROCOMPUTER DEVELOPMENT SYSTEM

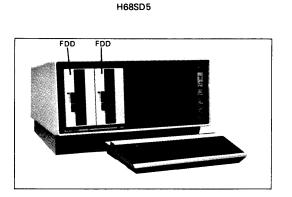

The H68SD5 is a development system for Hitachi 4-bit and 8-bit single-chip microcomputers.

It is compact HD6800—based CRT/Key board microcomputer terminal, with two Floppy disk drivers, and has standard interface for the TTY (RS-232C or TTL level) and printer (Centronics parallel interface). An optional EPROM Writer is available.

#### Features

Supports system development for 8-bit and 4-bit single chip microcomputers

#### System Configuration

- Disk based low cost system

- Provides the CRT Editor, Assembler, Emulator and EPROM Writer controlled by FDOS-III

- 56k-byte RAM

- Allows linking between the H68SD5 and the I/O devices (TTY and Printer)

- Easy to debug user's prototype system using the Emulator Module

#### **EPROM Writer**

Emulator Module

8-bit single-chip microcomputer family HMCS40 series HMCS400 series ----

# DATA SHEETS

----

Preliminary data sheets herein contain information on new products. Specifications and information are subject to change without notice.

Advance Information data sheets herein contain information on a product under development. Hitachi reserves the right to change or discontinue these products without notice.

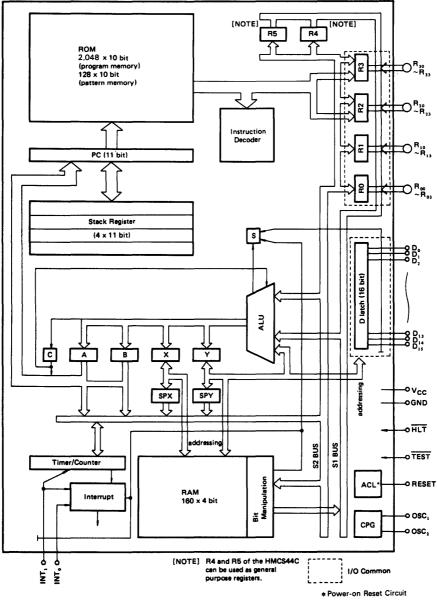

# HMCS44C(HD44801) HMCS44CL(HD44808)

The HMCS44C is the CMOS 4-bit single chip microcomputer which contains ROM, RAM, I/O and Timer/Event Counter on single chip. The HMCS44C is designed to perform efficient controller function as well as arithmetic function for both binary and BCD data. The CMOS technology of the HMCS44C provides the flexibility of microcomputers for battery powered and battery back-up applications.

### FEATURES

- 4-bit Architecture

- 2,048 Words of Program ROM (10 bits/Word) . 128 Words of Pattern ROM (10 bits/Word)

- 160 Digits of Data RAM (4 bits/Digit)

- 32 I/O Lines and 2 External Interrupt Lines

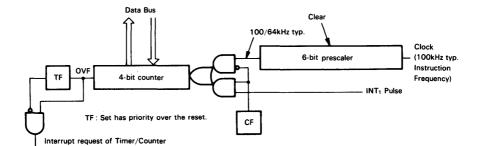

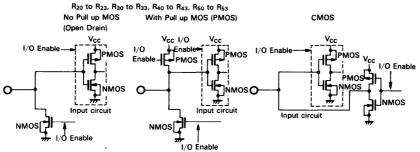

- Timer/Event Counter

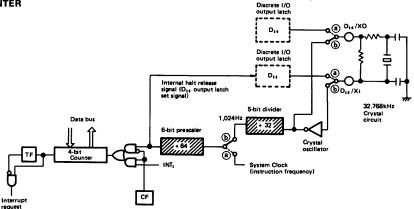

- Instruction Cycle Time: HMCS44C; 10 μs

- HMCS44CL; 20 µs

- All Instructions except One Instruction; Single Word and Single Cycle

- **BCD** Arithmetic Instructions

- Pattern Generation Instruction •

- Table Look Up Capability -

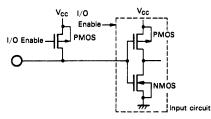

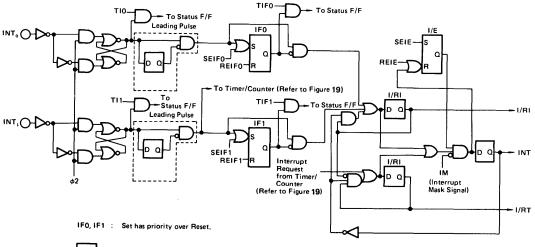

- Powerful Interrupt Function

- 3 Interrupt Sources

- 2 External Interrupt Lines Timer/Event Counter

- **Multiple Interrupt Capability**

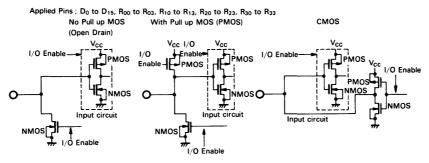

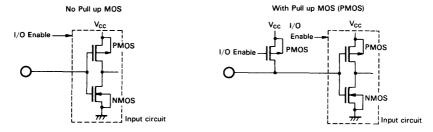

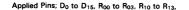

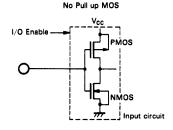

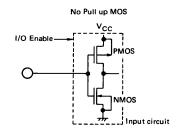

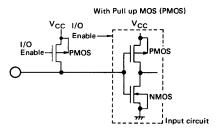

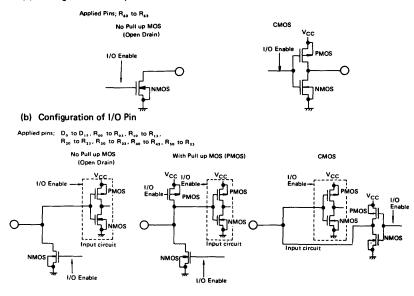

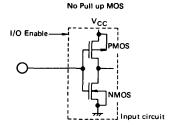

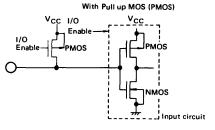

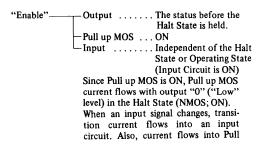

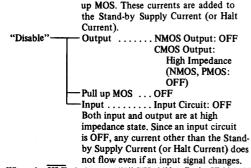

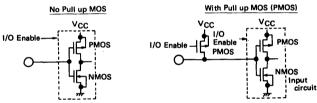

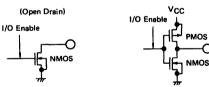

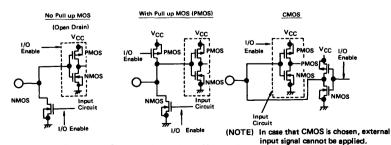

- Bit Manipulation Instructions for Both RAM and I/O Option of I/O Configuration Selectable on Each Pin; Pull Up

- MOS or CMOS or Open Drain

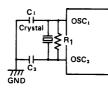

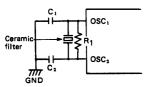

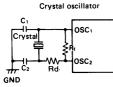

- Built-in Oscillator

- Built-in Power-on Reset Circuit (HMCS44C only)

- Low Operating Power Dissipation; 2mW typ.

- Stand-by Mode (Halt Mode); 50 μW max.

- CMOS Technology

- Single Power Supply: HMCS44C; 5V±10% HMCS44CL; 2.5V to 5.5V

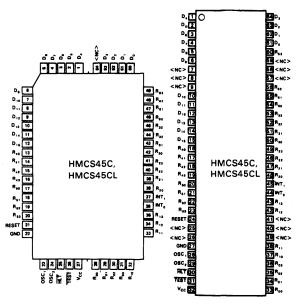

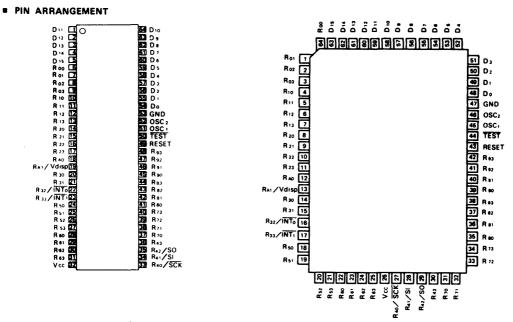

(DP-42) HMCS44C, HMCS44CL

PIN ARRANGEMENT

HMCS44C.HMCS44CL

|                                           | -                    |                                                                             |

|-------------------------------------------|----------------------|-----------------------------------------------------------------------------|

| o<br>DDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDDD | HMCS44C,<br>HMCS44CL | 2 - 0 33 23 1 30 23 22 21 20 T O<br>DDDRREREE E E E E E E E E E E E E E E E |

|                                           | TT March             |                                                                             |

(Top View)

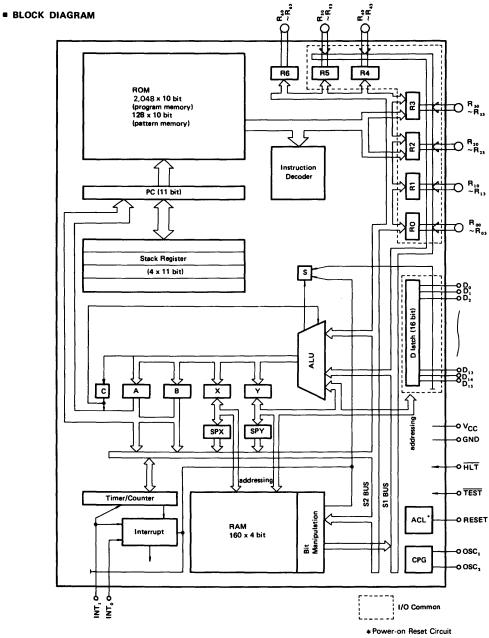

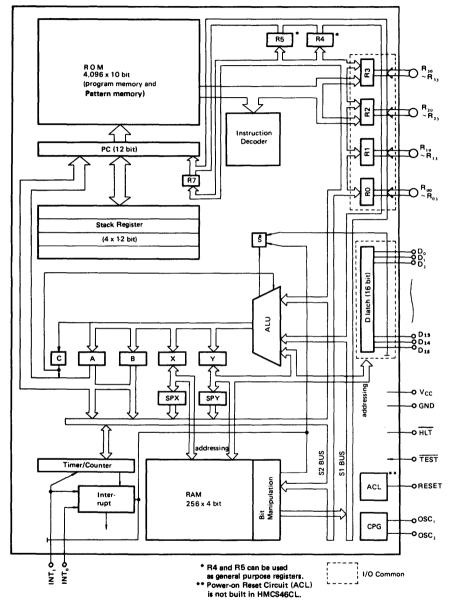

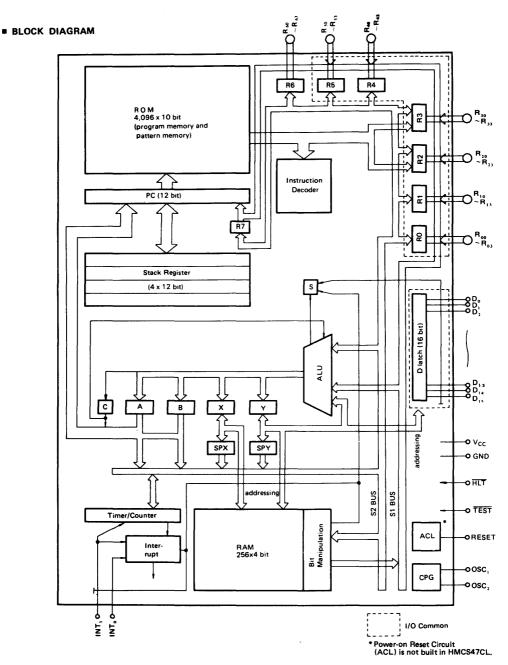

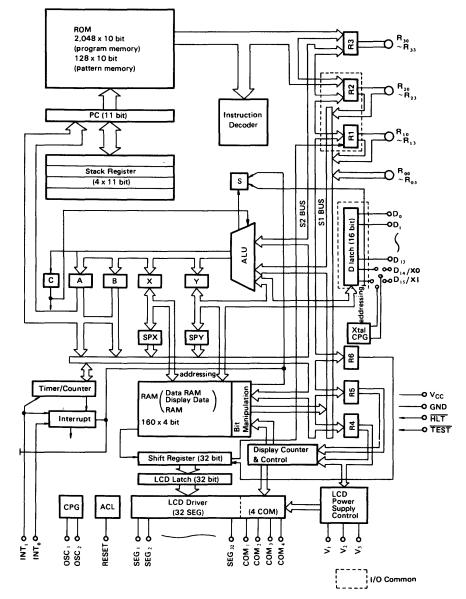

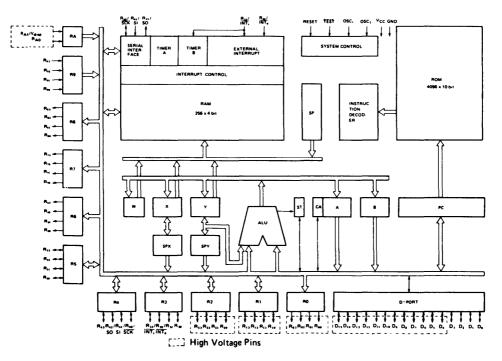

### BLOCK DIAGRAM

(ACL) is not built in HMCS44CL.

### HMCS44C, HMCS44CL -

### ■ HMCS44C ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>=5V + 10%) ● ABSOLUTE MAXIMUM RATINGS

| Item                             | Symbol         | Value                        | Unit | Remarks                                                                |

|----------------------------------|----------------|------------------------------|------|------------------------------------------------------------------------|

| Supply Voltage                   | Vcc            | -0.3 to +7.0                 | v    |                                                                        |

| Terminal Voltage (1)             | VT1            | -0.3 to V <sub>cc</sub> +0.3 | v    | Except for terminals specified by V <sub>T2</sub>                      |

| Terminal Voltage (2)             | VT2            | -0.3 to +10.0                | V    | Applied to only open drain output pins,<br>open drain I/O common pins, |

| Maximum Total Output Current (1) | -Σ <b>Ι</b> 01 | 45                           | mA   | [NOTE 3]                                                               |

| Maximum Total Output Current (2) | Σlo2           | 45                           | mA   | [NOTE 3]                                                               |

| Operating Temperature            | Topr           | -20 to +75                   | Ĵ    |                                                                        |

| Storage Temperature              | Tstg           | -55 to +125                  | r    |                                                                        |

[NOTE 1] Permanent LSI damage may occur if maximum ratings are exceeded. Normal operation should be under the conditions of "ELECTRICAL CHARACTERISTICS-1, -2." If these conditions are exceeded, it could affect reliability of LSI.

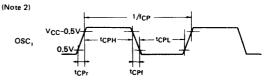

NOTE 2 All voltages are with respect to GND.

[NOTE 3] Maximum Total Output Current is total sum of output currents which can flow out (or flow in) simultaneously.

ų.

| Item                                 | Symbol          | Tect                                                                | Conditions                                                                                    |                      | Value |      | Unit | Note |

|--------------------------------------|-----------------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------|-------|------|------|------|

| item                                 | Symbol          | Test                                                                | Jonations                                                                                     | min.                 | typ.  | max. | Omt  | NOLE |

| Input "Low" Voltage                  | VIL             |                                                                     |                                                                                               | -                    | _     | 1.0  | v    |      |

| Input "High" Voltage (1)             | ViH1            |                                                                     |                                                                                               | $V_{cc} - 1.0$       |       | Vcc  | V    | 2    |

| Input "High" Voltage (2)             | VIH2            |                                                                     |                                                                                               | $V_{cc} - 1.0$       |       | 10   | v    | 3    |

| Output "Low" Voltage                 | Vol             | IoL = 1.6mA                                                         | $I_{OL} = 1.6 mA$                                                                             |                      |       | 0.8  | v    |      |

| Output "High" Voltage (1)            | VoH1            | —I <sub>он</sub> =1.0r                                              | nA                                                                                            | 2.4                  |       | -    | v    | 4    |

| Output "High" Voltage (2)            | Voh2            | -Іон=0.01                                                           | ImA                                                                                           | V <sub>cc</sub> -0.3 |       |      | v    | 5    |

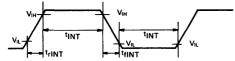

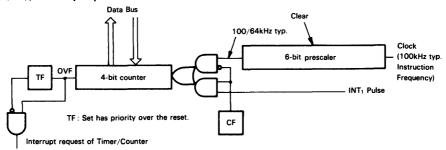

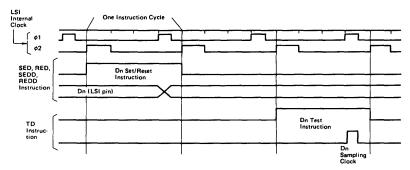

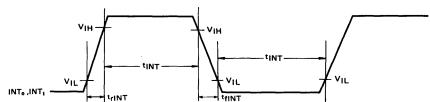

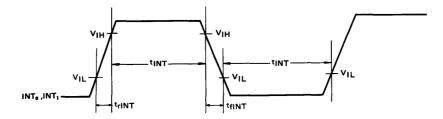

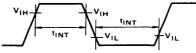

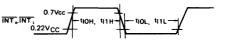

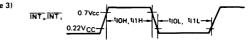

| Interrupt Input Hold Time            | tINT            |                                                                     |                                                                                               | 2 · Tinst            |       |      | μS   |      |

| Interrupt Input Fall Time            | tfINT           |                                                                     |                                                                                               | - 1                  | -     | 50   | μS   |      |

| Interrupt Input Rise Time            | trINT           | 1                                                                   |                                                                                               | -                    |       | 50   | μS   |      |

| Output "High" Current                | Іон             | V <sub>0H</sub> =10V                                                |                                                                                               | -                    | -     | 3    | μA   | 6    |

|                                      |                 | V <sub>in</sub> =0 to V                                             | $V_{in}=0$ to $V_{CC}$                                                                        |                      | ••    | 1.0  |      | 2    |

| Input Leakage Current                | lu.             | V <sub>in</sub> =0 to 1                                             | V <sub>in</sub> =0 to 10V                                                                     |                      |       | 3    | μA   | 3    |

| Pull up MOS Current                  | — Ip            | V <sub>cc</sub> =5V                                                 |                                                                                               | 60                   | -     | 250  | μA   |      |

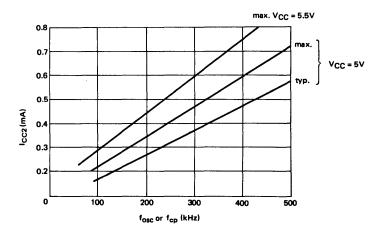

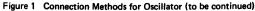

| Supply Current (1)                   | Icc1            | V <sub>in</sub> =V <sub>CC</sub> ,<br>Ceramic Filter<br>Oscillation |                                                                                               |                      |       | 2    | mA   | 7    |

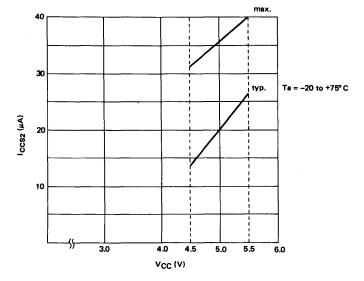

| Supply Current (2)                   | Icc2            | 1                                                                   | V <sub>in</sub> =V <sub>CC</sub> ,<br>R <sub>f</sub> Oscillation,<br>External Clock Operation |                      | -     | 1.0  | mA   | 7    |

| Standburk (Oldenburge Current        |                 | $\overline{HLT} = 1.0V$                                             | $V_{in}=0$ to $V_{CC}$                                                                        |                      | -     | 1    | μA   | 2, 8 |

| Standby I/O Leakage Current          | ILS             | HLI = 1.0V                                                          | $V_{in}=0$ to $10V$                                                                           | -                    |       | 3    | μA   | 3, 8 |

| Standby Supply Current               | lccs            | Vin=Vcc, Ĥ                                                          | LT=0.2V                                                                                       |                      |       | 10   | μA   | 9    |

| External Clock Operation             |                 |                                                                     |                                                                                               |                      |       |      | J    |      |

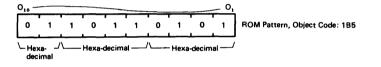

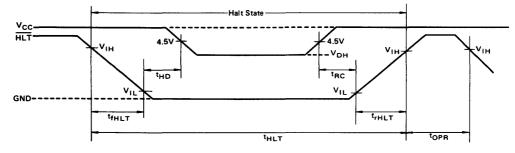

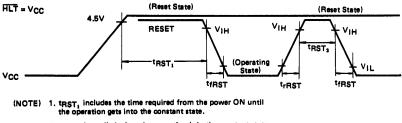

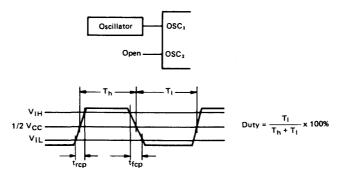

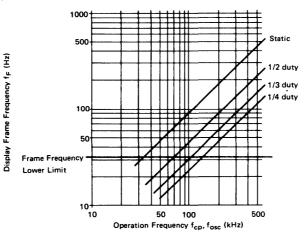

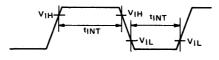

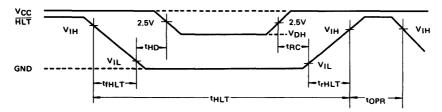

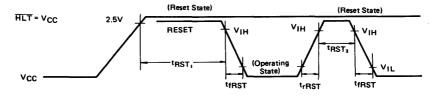

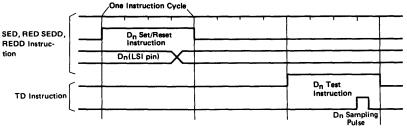

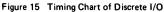

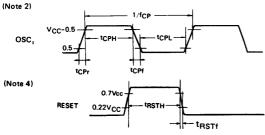

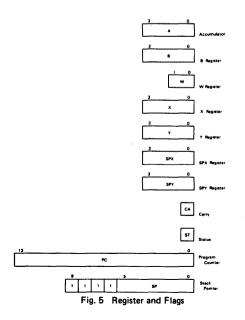

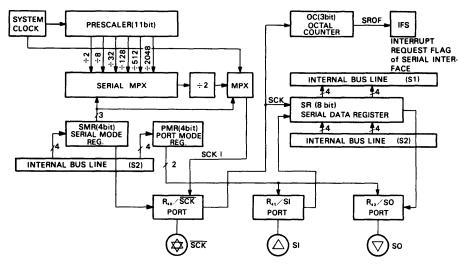

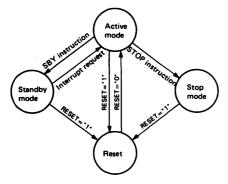

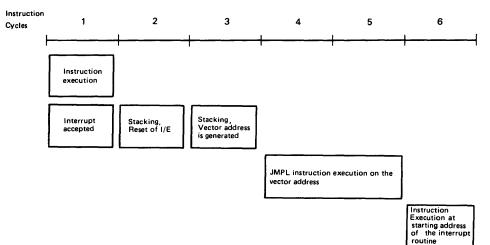

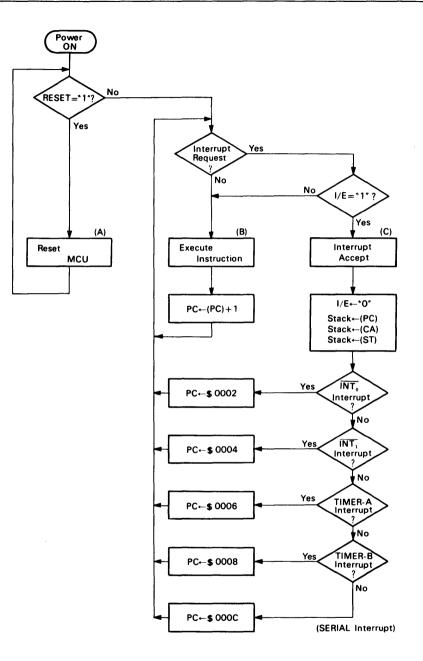

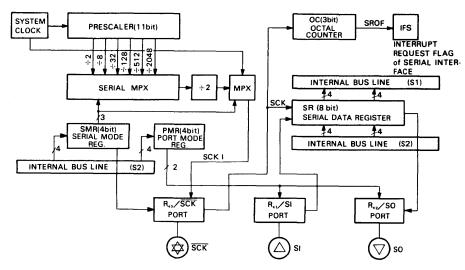

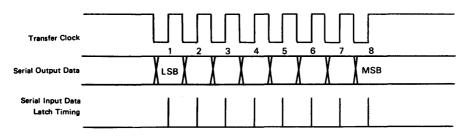

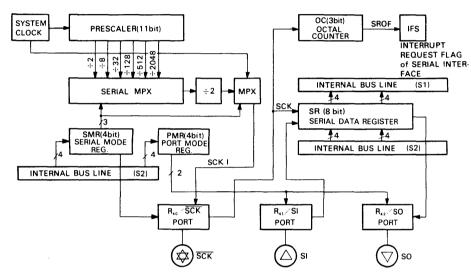

| External Clock Frequency             | fcp             |                                                                     |                                                                                               | 200                  | 400   | 440  | kHz  |      |