# <u>SPARClite</u> <u>MB86860 Series</u> <u>User Manual</u>

Edition 1.1 - Jul. 29, 1999

Fujitsu Ltd.

The User Manual consists of Hardware Manual Edition 1.1 - Jul. 29, 1999 and Programming Manual Edition 1.0 - Jun. 22, 1999

<u>SPARClite</u> <u>MB86860 Series</u> <u>Hardware Manual</u>

Edition 1.1 - Jul. 29, 1999

Fujitsu Ltd.

Rev.1.1 Jul.29/ 99

Fig 8-3 of Page 8-10 and Fig.8-4 of Page 8-11 DQ32, 33, 33, 34, , 62 => DQ32, 33, 34, 35, , 63

Page 8-12 Note is added.

### Contents

| 1. Summary                                                                                                                                                                                                                                                                                                                               | 1-1                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| <ul> <li>1.1. Introduction</li></ul>                                                                                                                                                                                                                                                                                                     | 1-1<br>1-1<br>1-1<br>1-1<br>1-1<br>1-1<br>1-2<br>1-2<br>1-2            |

| 2. Pins                                                                                                                                                                                                                                                                                                                                  | 2-1                                                                    |

| 2.1. Package Pin Assignments2.2. Pin Overview2.2.1. MB86860 Pin Overview2.2.2 MB86861 Pin Overview2.3. Outer Package Dimension Drawing2.4. Explanation of Pin Functions2.4.1. SPARClite Bus Signals2.4.2. SDRAM-IF Signals2.4.3. Interrupt Signals2.4.4. DMAC, DSU and Sleep Mode related Signals2.4.5. Other Signals2.4.6. Test Signals | 2-2<br>2-4<br>2-6<br>2-7<br>2-7<br>2-7<br>2-11<br>2-13<br>2-13<br>2-13 |

| 3. Registers                                                                                                                                                                                                                                                                                                                             | 3-1                                                                    |

| <ul><li>3.1. IU Status/Control Registers</li></ul>                                                                                                                                                                                                                                                                                       |                                                                        |

| 4. Processor Core                                                                                                                                                                                                                                                                                                                        | 4-1                                                                    |

| <ul><li>4.1. Summary</li></ul>                                                                                                                                                                                                                                                                                                           |                                                                        |

# FUĴÎTSU

| 4.2.2. Register Overview                                                                                                                                                                               | 4-2                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 4.2.3. Register Details                                                                                                                                                                                |                                                                                                                             |

| 4.2.3. Caches                                                                                                                                                                                          |                                                                                                                             |

| 4.3.1. Summary                                                                                                                                                                                         |                                                                                                                             |

| 4.3.2. Cache Memory Assignments                                                                                                                                                                        |                                                                                                                             |

| 4.3.3. Tag/Data Format                                                                                                                                                                                 |                                                                                                                             |

| 4.3.4. Operating Functions                                                                                                                                                                             |                                                                                                                             |

| 4.4. DSU (Debug Support Unit)                                                                                                                                                                          |                                                                                                                             |

| 4.4.1. Summary                                                                                                                                                                                         |                                                                                                                             |

| 4.4.2. Related Pin Overview                                                                                                                                                                            |                                                                                                                             |

| 4.4.3. Register Overview                                                                                                                                                                               |                                                                                                                             |

| 4.4.4. Register Details                                                                                                                                                                                |                                                                                                                             |

| 4.4.5. Explanation of Functions                                                                                                                                                                        |                                                                                                                             |

| 4.5. Low Power Consumption Mode                                                                                                                                                                        |                                                                                                                             |

| 4.5.1. Summary                                                                                                                                                                                         |                                                                                                                             |

| 4.5.2. Related Pin Overview                                                                                                                                                                            |                                                                                                                             |

| 4.5.3. Register Overview                                                                                                                                                                               | 4-18                                                                                                                        |

| 4.5.4. Register Details                                                                                                                                                                                |                                                                                                                             |

| 4.5.5. Explanation of Functions                                                                                                                                                                        | 4-19                                                                                                                        |

| 4.5.6. Items Requiring Attention in Sleep Mode                                                                                                                                                         |                                                                                                                             |

| 5. TLB                                                                                                                                                                                                 | 5-1                                                                                                                         |

|                                                                                                                                                                                                        |                                                                                                                             |

| 5.1. Summary                                                                                                                                                                                           | 5-1                                                                                                                         |

| 5.6. Register Overview                                                                                                                                                                                 |                                                                                                                             |

| 5.7. Register Details                                                                                                                                                                                  | 5-3                                                                                                                         |

|                                                                                                                                                                                                        |                                                                                                                             |

| 5.7.1. TLB Control Register (TCR)                                                                                                                                                                      | 5-3                                                                                                                         |

| 5.7.2. Virtual Word Address Entry Register (VWE0-15)                                                                                                                                                   | 5-3                                                                                                                         |

| 5.7.2. Virtual Word Address Entry Register (VWE0-15)                                                                                                                                                   | 5-3                                                                                                                         |

|                                                                                                                                                                                                        | 5-3<br>5-3                                                                                                                  |

| <ul><li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li><li>5.7.3. Physical Word Address Entry Register (PWE0-15)</li></ul>                                                                   | 5-3<br>5-3<br>5-4                                                                                                           |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li> <li>5.7.3. Physical Word Address Entry Register (PWE0-15)</li> <li>5.8. Operating Functions</li> <li>6. Data Buffer Unit</li> </ul> | 5-3<br>5-3<br>5-4<br><b> 6-1</b>                                                                                            |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-3<br>5-4<br><b> 6-1</b><br>6-1                                                                                     |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-3<br>5-4<br><b> 6-1</b><br>6-1<br>6-2                                                                              |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-3<br>5-4<br><b> 6-1</b><br>6-1<br>6-2<br>6-2                                                                       |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-3<br>5-4<br><b> 6-1</b><br>6-1<br>6-2<br>6-2<br>6-2                                                                |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-3<br>5-4<br><b> 6-1</b><br>6-1<br>6-2<br>6-2<br>6-3                                                                |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-3<br>5-4<br><b> 6-1</b><br>6-1<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3                                                  |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-3<br>5-4<br><b> 6-1</b><br>6-1<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3                                           |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-4<br><b> 6-1</b><br>6-1<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-3                                           |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-4<br>5-4<br>6-1<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-4                                                   |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-4<br><b></b> 6-1<br>6-1<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-3<br>6-4<br>6-5                             |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-4<br><b></b> 6-1<br>6-1<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-3<br>6-4<br>6-5                             |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-4<br>5-4<br>6-1<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-3<br>6-4<br>6-5<br>7-1                              |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-4<br>5-4<br>6-1<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-3<br>6-4<br>6-5<br><b> 7-1</b><br>7-1               |

| <ul> <li>5.7.2. Virtual Word Address Entry Register (VWE0-15)</li></ul>                                                                                                                                | 5-3<br>5-4<br>5-4<br>6-1<br>6-2<br>6-2<br>6-2<br>6-2<br>6-3<br>6-3<br>6-3<br>6-3<br>6-4<br>6-5<br><b> 7-1</b><br>7-1<br>7-1 |

| 7.3.1. Address Range Specifier Registers (ARSR0-5)                |      |

|-------------------------------------------------------------------|------|

| 7.3.2. Address Mask Registers (AMR0-5)                            |      |

| 7.3.3. Wait State Specifier Registers (WSSR0-5)                   |      |

| 7.3.4. MEXC Parity Error Control Registers (MXPEF)                |      |

| 7.3.5. MEXC Parity Error Control Registers                        | 7-4  |

|                                                                   |      |

|                                                                   |      |

| 7.3.6. Idle Cycle Control Register                                |      |

| 7.4. Operating Functions                                          |      |

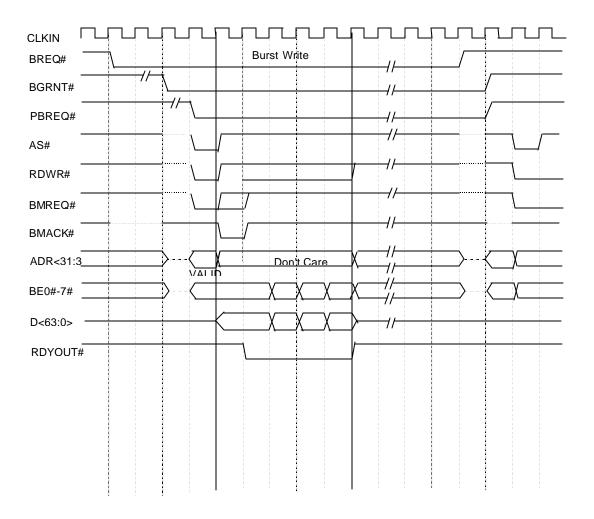

| 7.4.1. Operations when CPU has the Bus Right                      |      |

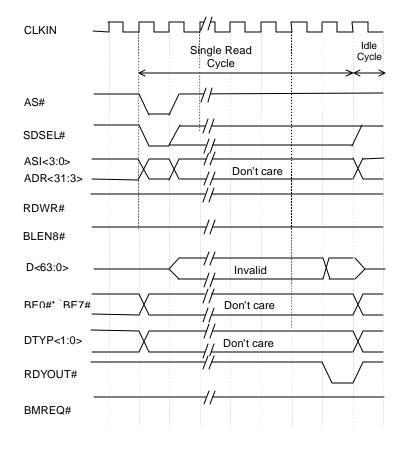

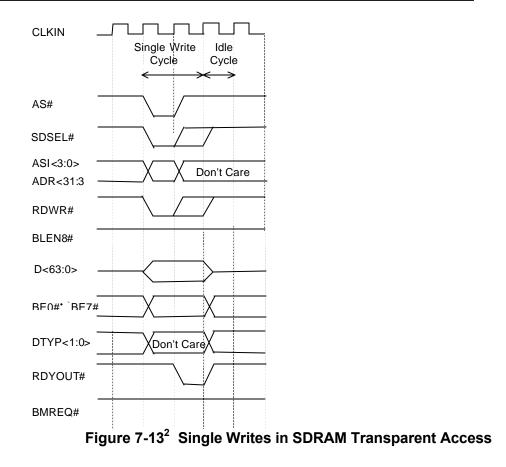

| 7.4.2. Access Transparent Mode to SDRAM (MB86861 only)            | ′-15 |

| 8. SDRAM-IF                                                       | 8-1  |

|                                                                   |      |

| 8.1. Summary                                                      | 8-1  |

| 8.2. Pin Overview                                                 | 8-1  |

| 8.3. Register Overview                                            | 8-2  |

| 8.4. Register Details                                             | 8-3  |

| 8.4.1. SDRAM Address Range Specifier Registers (SDARSR0-5)        | 8-3  |

| 8.4.2. SDRAM Address Mask Registers (SDAMR0-1)                    |      |

| 8.4.3. SDRAM Configuration Register (SDCFG)                       |      |

| 8.4.4. Auto Refresh Register (ART)                                |      |

| 8.4.5. SDRAM Status Register (SSR)                                |      |

| 8.4.6. SDRAM CS Characteristic Registers (CSCR0-3) (MB86861 only) |      |

| 8.4.7. SDRAM Start Address Registers (SSAR0-3) (MB86861 only)     |      |

| 8.4.8. SDRAM Address Mask Registers SAMR0-3) (MB86861 only)       |      |

| 8.5. Operating Functions                                          |      |

| 8.5.1. Parity Generation & Check Functions                        |      |

|                                                                   |      |

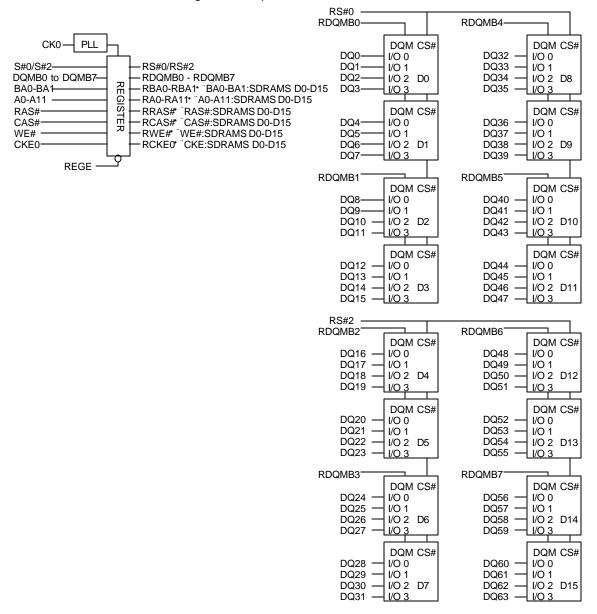

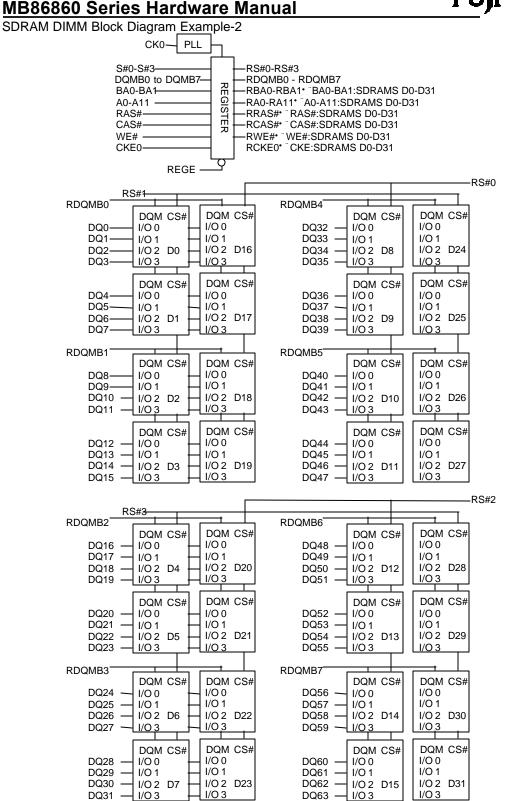

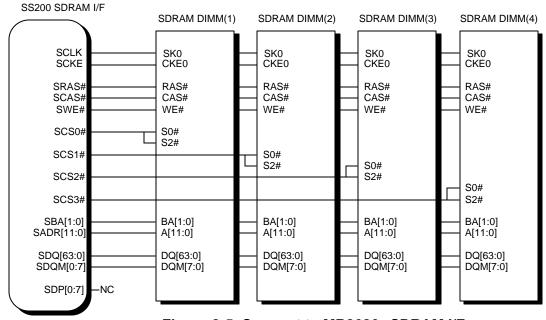

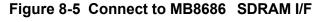

| 8.5.2. SDRAM Connections with SDRAM Buses                         |      |

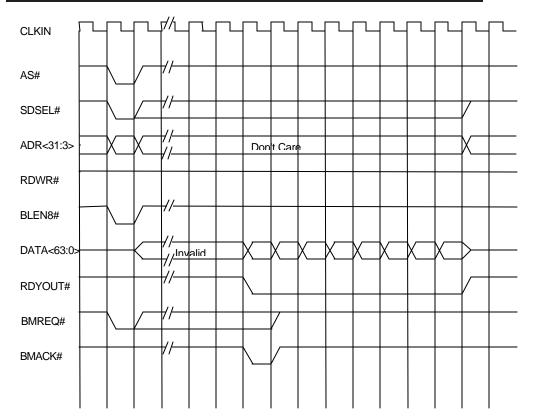

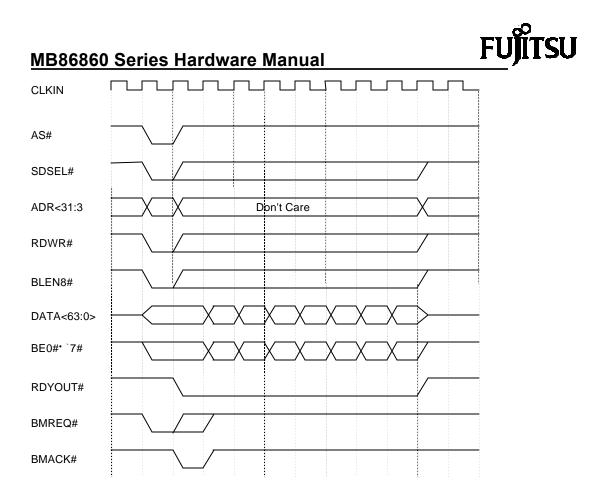

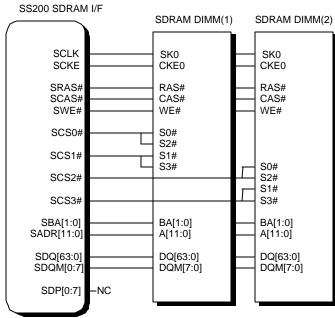

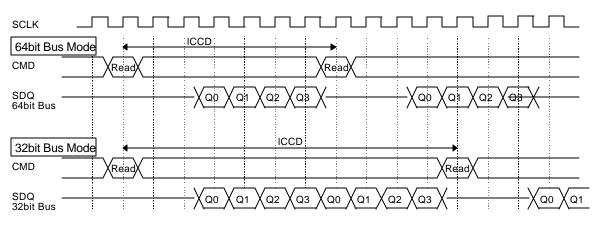

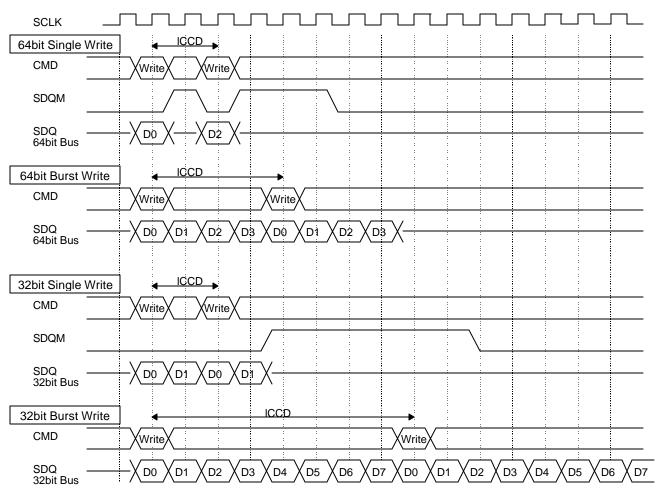

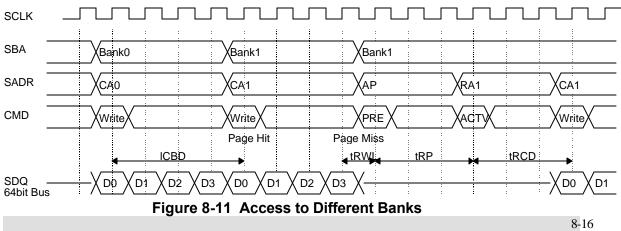

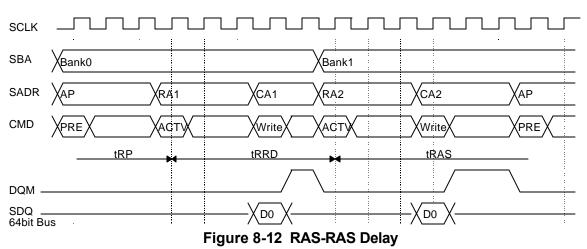

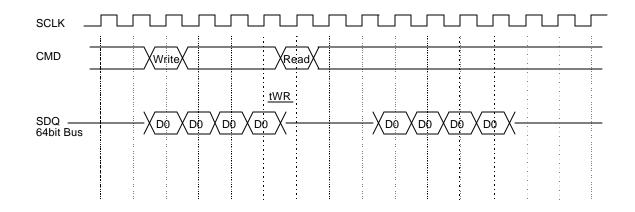

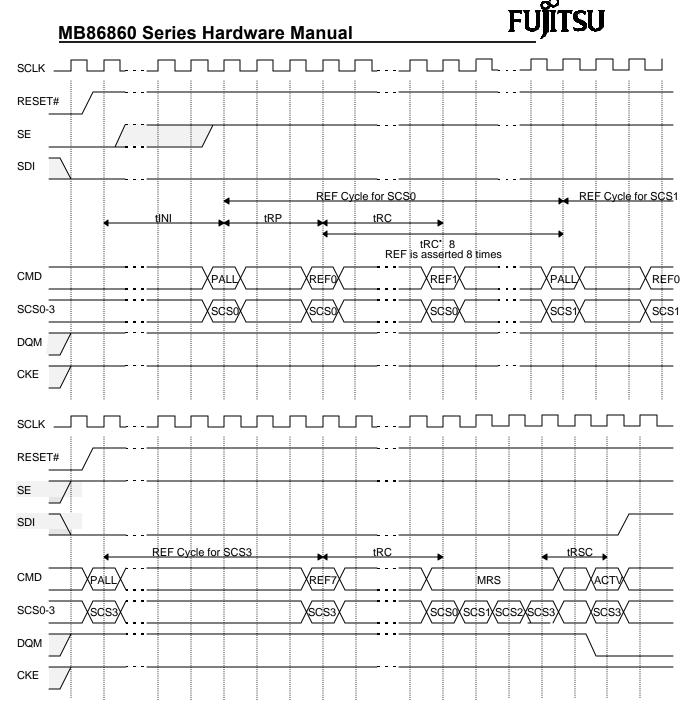

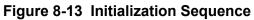

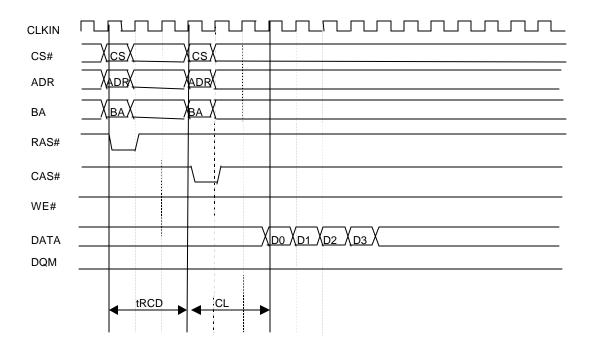

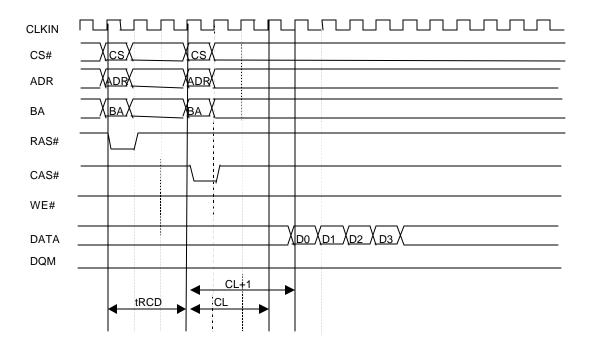

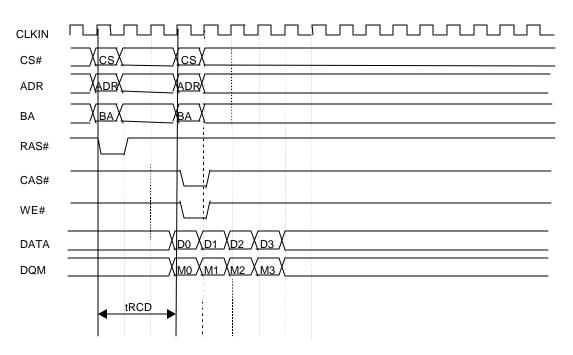

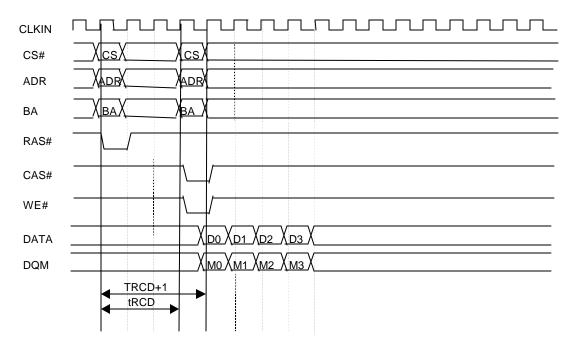

| 8.5.3. Timing Diagram                                             | 5-13 |

| 9. DMAC                                                           | 9-1  |

| 9.1. Summary                                                      | 0.1  |

| 9.1. Summary<br>9.2. Related Pin Overview                         |      |

|                                                                   |      |

| 9.3. Register Overview                                            |      |

| 9.4. Register Details.                                            | 9-1  |

| 9.4.1. DMA Control Registers (DCR0-1)                             |      |

| 9.4.2. DMA Source Address Register                                |      |

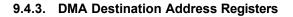

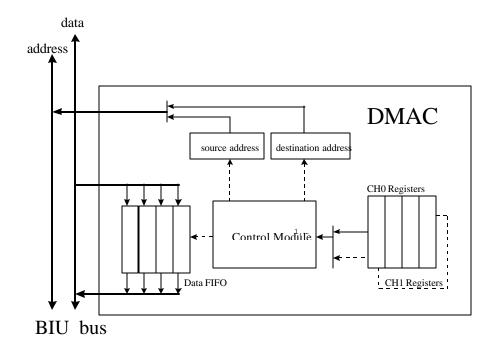

| 9.4.3. DMA Destination Address Register                           |      |

| 9.4.4. DMA Word Length Register                                   |      |

| 9.5. Operating Functions                                          |      |

| 9.5.1. Internal Bus Priority Order                                |      |

| 9.5.2. Transfer System                                            | 9-4  |

| 9.5.3. Register Summary                                           |      |

| 9.5.4. Activation/Termination                                     | 9-4  |

| 9.5.5. Exception Processing                                       | 9-5  |

FUĴÎTSU

# 1. Summary

#### 1.1. Introduction

The MB8686 Series processors are high-end processors which conform to SPARC Architecture Manual Version 8. This Manual explains MB86860 Series Processor (MB86860/86861) specifications.

When developing software for use by these processors reference should also be made to the following manuals:

- SPARClite Instruction Set Manual

- MB86860 series Programming Manual

#### 1.2. Features

#### 1.2.1. Core Part

- Conforms to SPARC V8

- Maximum 200mhz Internal operating frequency

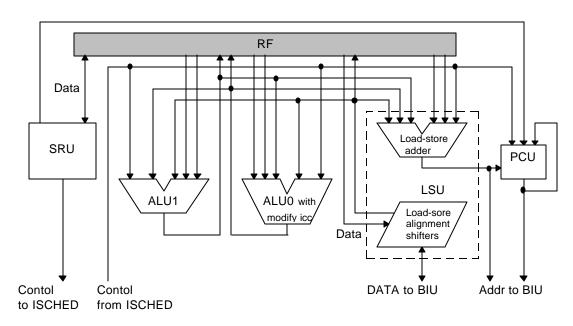

- Uses 2-issue superscalar architecture

- 16KB 4-way instruction cache

- 16KB 4-way data cache (write through)

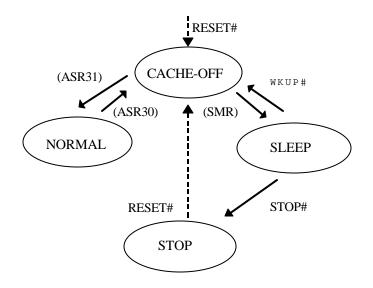

- Power Down Mode

- Bi-endian support

#### 1.2.2. Debug Support Function

- All types of break function (Instruction Address/external pin/software/single step)

- Equipped with 16-column address trace buffer

- Single step operation

#### 1.2.3. Data Buffer Module

- 4-column instruction buffer

- 4-column x 2 read buffer

- 16-column write buffer

#### 1.2.4. Address Conversion (TLB) Function (MB86861/MB86862)

- Number of TLB entries = 16

- Supports 4KB, 1MB, 4MB, 16MB and 64MB page sizes

- Different page sizes can be set for each entry

- When there are misses in address conversions, address from the CPU are output as they are as physical addresses without cativating traps

#### 1.2.5. SDRAM Interface

- 64 and 32-bit data bus widths can be selected

- Maximum 100MHz operation

- Auto and self-refresh supported

- Parity functions supported

#### 1.2.6. SPARClite Interface

- 64-bit, 32-bit-16-bit and 8-bit data buses

- Programmable Chip Select Generator Function (5-chip select)

- Wait State Control Function which generates waits for each chip select

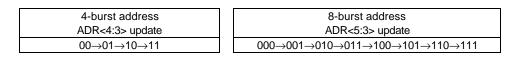

- Burst Mode Support

- Parity Function Support

- Transparent access to SDRAM function (MB86861 only)

#### 1.2.7. Bus-bridge DMA

• Equipped with 2 DMA channels. 1 chanel simultaneous operation.

#### 1.2.8. Power Supply

- Internal: 2.5V

- I/O pins: 3.3V

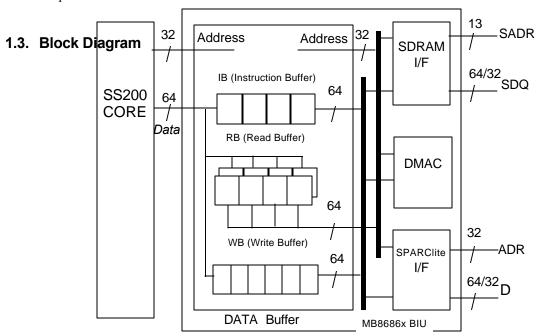

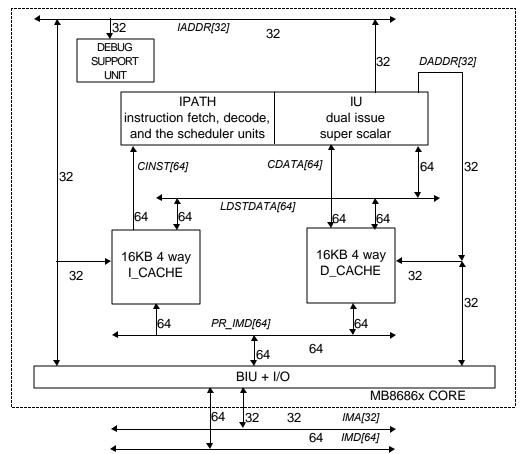

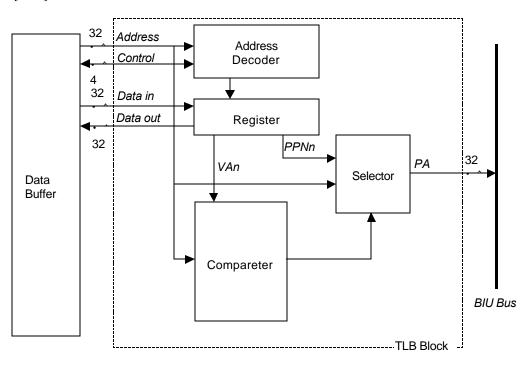

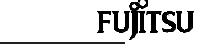

Figure 1.1 MB8686x Processor Block Diagram

2. Pins

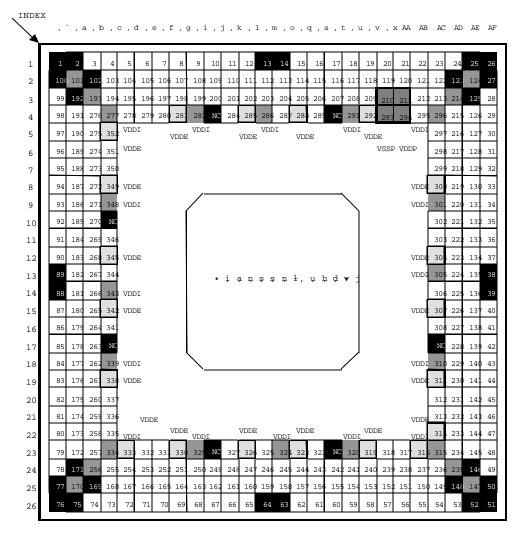

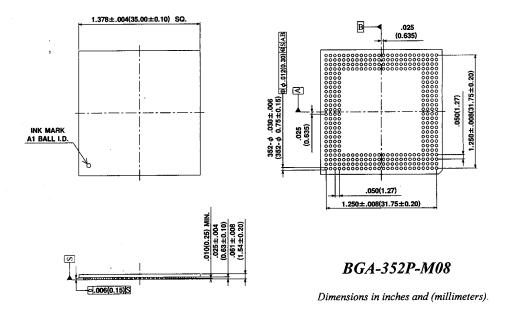

2.1. Package Pin Assignments

: Signals (269pins)

|   | : VDDI(24pins)     | 101, 124  | , 147, | 170, | 193, | 214, |          |         |

|---|--------------------|-----------|--------|------|------|------|----------|---------|

|   |                    | 235, 256  | , 277, | 282, | 286, | 291, |          |         |

|   |                    | 296, 301  | , 305, | 310, | 315, | 320, |          |         |

|   |                    | 324, 329  | , 334, | 339, | 343, | 348  |          |         |

|   | · VDDE( 20pins)    | 281, 285  | , 288, | 292, | 300, | 304, | Addition | al      |

|   |                    | 307, 311  | , 319, | 323, | 326, | 330, |          | 314,316 |

|   |                    | 338, 342, | 345,   | 349  |      |      |          | 333,352 |

|   | · VSS (28pins)     | 1, 2      | , 13,  | 14,  | 25,  | 26,  | NC       | 283,290 |

|   |                    | 27, 38    | , 39,  | 50,  | 51,  | 52,  | 7pins    | 309,321 |

|   |                    | 63, 64    | , 75,  | 76,  | 77,  | 88,  |          | 328,340 |

|   |                    | 89, 100   | , 102, | 123, | 125, | 146, |          | 347     |

| _ |                    | 148, 169  | , 171, | 192  |      |      |          | -       |

|   | VDDP1 (for CPU Cor | e PLL)211 |        |      |      |      |          |         |

|   | VDDP2(for BIU part | PLL) 294  |        |      |      |      |          |         |

|   | VSSP1 (for CPU Cor | e PLL)210 |        |      |      |      |          |         |

|   | VSSP2(for BIU part | PLL) 293  |        |      |      |      |          |         |

3-1

# 2.2. Pin Overview

| Att. | 1     | - Input                                                          |

|------|-------|------------------------------------------------------------------|

|      | 0     | - Output                                                         |

| -    | NC    | - Non-connected                                                  |

|      | VDD   | - Internal Logic 2.5V Power Supply Pin                           |

|      | VDDE  | - 3.3V Power Supply Pin for I/O                                  |

|      | VSS   | <ul> <li>Internal Logic and common grant pins for I/O</li> </ul> |

|      | VDDP1 | - Power Supply Pin for PLL inside CP Core                        |

|      | VSSP1 | - Grant pin for PLL inside CPU Core                              |

|      | VDDP2 | - Power Supply Pin for BIU PLL.                                  |

|      | VSSP2 | - Power Supply Pin for BIU PLL                                   |

|      |       |                                                                  |

This part shows pin properties in the MB86860 and MB86861 and the parts with differing functions.

#### 2.2.1. MB86860 Pin Overview Table 2-1 MB86860 Pin Overview

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table 2-1 MB86860 Pin Overview |     |      |          |      |      |       |      |          |      |      |        |     |            |              |             |        |        |                |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-----|------|----------|------|------|-------|------|----------|------|------|--------|-----|------------|--------------|-------------|--------|--------|----------------|---------|

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ю                              | ).  |      | Left sid | de   | PKC  | 3 Pin | No.  | Bottom   | side | PKG  | Pin No | ).  | Right sid  | le           | PKG Pin No. |        |        | Top side       |         |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | E                              | EC) | Pin  | name     | Att. | (Fj) | (JE   | DEC) | Pin name | Att. | (Fj) | (JEDI  | EC) | Pin name   | att.         | (Fj)        | (JEI   | DEC)   | Pin name       | Att.    |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                | 1   | VSS  |          | VSS  | 76   | А     | 26   | vss      | VSS  | 51   | AF     | 26  | VSS        | VSS          | 26          | AF     | 1      | VSSP           | vss     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | VDDI         | 296         | AC     | 4      | VDDI           | VDDI    |

| 352D5VDDEVDDE333E23VDDEVDDE314AC22VDDE99A3D<24>I/O74C26SDQ<16>I/O49AF24SDQ<4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | I/O          | 213         |        | 3      | TRST#          | I       |

| 99A3D<24>I/O74C26SDQ<16>I/O49AF24SDQ<4191B4D<25>I/O168D<25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |     |      |          |      |      |       |      | · ·      |      |      |        |     |            | VDDE         | 295         | AB     | 4      | TDI            | T       |

| 191B4D<25>VO168D<25SDQ<17>IO145AE23SDQ<4235D6DP4VO332F23SDP5IO233AD22SDQ<4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | I/O          | 24          | AD     | 1      | TMS            | T       |

| 275C5D<26>I/O254E24SDQ<18>I/O233AD22SDQ<4351D6DP4I/O332F23SDP5I/O313AC21SDP1101B2VDDIVDDII/O73D26SDQ<19>I/O144AF23SDQ<4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |     |      |          |      |      |       |      | ~        |      |      |        |     | •          | I/O          | 122         | AC     | 2      | TDO            | 0       |

| 351D6DP4VO332F23SDP5IO313AC21SDP1101B2VDDIVDDIIT0B25VDDIVDDI147AE25VDDI98A4D<27>VO73D26SDQ<19>IO144AE22SDQ<2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |     |      |          |      |      |       |      | -        |      |      |        |     | · ·        | I/O          | 212         | AB     | 3      | TCLK           | ĩ       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |     |      |          |      |      |       |      | · ·      |      |      |        |     |            | I/O          | 294         | AA     | 4      | VDDP           | VDDP    |

| 98A4D<27>I/O73DD26SDQ<19>I/O48AF23SDQ<4190B5D<28>I/O167E25SDQ<20>I/O144AE22SDQ<2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | VDDI         | 124         | AE     | 2      | VDDI           | VDDI    |

| 190B5 $D<28>$ $IO$ $167$ E $25$ $SDQ<20>$ $IO$ $144$ AE $22$ $SDQ<22$ 274C6 $D-29>$ $IO$ $253$ F $24$ $SDQ<21>$ $IO$ $312$ AC $20$ $SDP4$ 350D7DP3 $IO$ $331$ G $23$ $SDP4$ $IO$ $312$ AC $20$ $SDP0192B3VSSVSSIO72E26SDQ<22>IO47AF22SDQ<$                                                                                                                                                                                                                                                                                                                                                                                                                     |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | I/O          | 23          | AC     | 1      | TEST1          | I       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |     |      |          |      |      |       |      | · ·      |      | -    |        |     | •          | I/O          | 121         | AB     | 2      | TEST2          | T       |

| 350D7DP3I/O331G2.3SDP4I/O312A.C. 20SDP0192B3VSSVSS169C25VSSVSS146AE24VSS97A5D<30>I/O72E26SDQ<22>I/O47AF22SDQ<2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                |     |      |          |      |      |       |      | ~        |      |      |        |     | •          | I/O          | 211         | AA     | 3      | VDDP           | VDDP    |

| 192B3VSSVSS169C25VSSVSS146AE24VSS97A5D<30>I/O72E26SDQ<22>I/O47AF22SDQ<5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |     |      |          |      |      |       |      | ~        |      |      |        |     | •          | I/O<br>I/O   | 293         | Y      | 4      | VSSP           | VSSP    |

| 97A5D<30>I/O72E26SDQ<22>I/O47AF22SDQ<25348D9VDDIVDDI329J23VDDIVDDI310AC18VDDI189B6D<31>I/O166F25SDQ<23>I/O143AE21SDQ<52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | VSS          | 123         | AD     | 2      | VSSP           | VSS     |

| 348D9VDDIVDDI329J23VDDIVDDI310AC18VDDI189B6D<31>I/O166F25SDQ<23>I/O143AE21SDQ<5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |     |      | _        |      |      |       |      |          |      |      |        |     |            | I/O          | 22          | AB     | 1      | CLKSEL1        | T       |

| 189B6 $0 < 31 >$ $IO$ 166F25 $SDQ < 23 >$ $IO$ 143AE21 $SDQ < 23 >$ 349D8VDDEVDDE330H23VDDEVDDE311AC19VDDE96A6 $D < 33 >$ I/O71F26 $SDQ < 25 >$ I/O46AF21 $SDQ < 25 >$ 188B7 $D < 34 >$ I/O165G25 $SDQ < 25 >$ I/O46AF21 $SDQ < 25 >$ 100A2VSSVSS75B26VSSVSS50AF25VSS272C8 $D < 35 >$ I/O251H24 $SDQ < 27 >$ I/O230AD19 $SDQ < 25 >$ 95A7 $D < 36 >$ I/O164H25 $SDQ < 28 >$ I/O45AF20 $SDQ < 25 >$ 271C9 $D < 38 >$ I/O250J24 $SDQ < 30 >$ I/O229AD18 $SDQ < 26 >$ 347D10NCNC328K23NCNC309AC17NC94A8 $D < 39 >$ I/O69H26 $SDQ < 31 >$ I/O44AF19 $SDQ < 30 >$ 346D11DP2I/O163J25SDQM00140AE18 $SDQ < 30 >$ 346<                                                 |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | VDDI         | 291         | V      | 4      | VDDI           | VDDI    |

| 273C7D<32>I/O252G24SDQ<24>I/O231AD20SDQ<25349D8VDDEVDDE330H23VDDEVDDE311AC19VDDE96A6D<33>I/O71F26SDQ<25>I/O46AF21SDQ<5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | VDDI<br>I/O  | 120         | ĂĂ     | 2      | CLKIN          | T       |

| 349D8VDDEVDDE330H23VDDEVDDE311AC19VDDE96A6D<33>I/O71F26SDQ<25>I/O46AF21SDQ<5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |     |      |          |      |      |       |      | ~        |      | -    |        |     |            | I/O<br>I/O   | 210         | Y      | 3      | VSSP           | VSSP    |

| 96A6 $D < 33 >$ $I/O$ 71F26 $SDQ < 25 >$ $I/O$ 46AF21 $SDQ < 25 >$ 188B7 $D < 34 >$ $I/O$ 165G25 $SDQ < 25 >$ $I/O$ 142AE20 $SDQ < 25 >$ 100A2VSSVSS75B26VSSVSS50AF25VSS272C8 $D < 35 >$ $I/O$ 251H24 $SDQ < 27 >$ $I/O$ 230AD19 $SDQ < 25 >$ 95A7 $D < 36 >$ $I/O$ 70G26 $SDQ < 22 >$ $I/O$ 45AF20 $SDQ < 25 >$ 187B8 $D < 37 >$ $I/O$ 164H25 $SDQ < 29 >$ $I/O$ 141AE19 $SDQ < 25 >$ 271C9 $D < 38 >$ $I/O$ 250J24 $SDQ < 30 >$ $I/O$ 229AD18 $SDQ < 25 >$ 347D10NCNC328K23NCNC309AC17NC94A8 $D < 39 >$ $I/O$ 163J25 $SDQM0$ 0140AE18 $SDQ < 40 >$ 186B9 $D < 41 >$ $I/O$ 249K24 $SDQM1$ 0228AD17 $SDQ < 40 >$ 346D11 $D < 44 >$ $I/O$ 249K24 $SDQM1$ 0228AD |                                |     |      |          |      | -    |       |      | · ·      |      | -    |        |     | •          | VDDE         | 292         | W      | 4      | VDDE           | VDDE    |

| 188B7D<34>I/O165G25SDQ<26>I/O142AE20SDQ<25100A2VSSVSS75B26VSSVSS50AF25VSS272C8D<35>I/O251H24SDQ<27>I/O230AD19SDQ<25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                |     |      |          |      |      |       |      |          |      | -    |        |     |            | VDDE<br>I/O  | 292         | AA     | 4      | CLKSEL0        | T       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |     |      |          |      |      |       |      | ~        |      | -    |        |     | •          | I/O<br>I/O   | 119         | Y      | 2      | RESET#         | T       |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | VSS          | 25          | AE     | 1      | VSSP           | VSS     |

| 95A7D<36>I/O70G26SDQ<28>I/O45AF20SDQ<25187B8D<37>I/O164H25SDQ<29>I/O141AE19SDQ<25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                |     |      | _        |      |      |       |      |          |      |      |        |     |            | V 3 3<br>I/O | 209         | W      | 3      | BCLK           | 1       |

| 187B8 $D < 37 >$ I/O164H25 $SDQ < 29 >$ I/O141AE19 $SDQ < 29 <$ 271C9 $D < 38 >$ I/O250J24 $SDQ < 30 >$ I/O229AD18 $SDQ < 40 <$ 347D10NCNC328K23NCNC309AC17NC94A8 $D < 39 >$ I/O69H26 $SDQ < 31 >$ I/O44AF19 $SDQ < 40 <$ 186B9 $D < 40 >$ I/O163J25 $SDQM0$ O140AE18 $SDQ < 40 <$ 270C10 $D < 41 >$ I/O163J25 $SDQM1$ O228AD17 $SDQ < 40 <$ 343D $D < 41 >$ I/O249K24 $SDQM2$ O43AF18 $ADR < 40 <$ 346D11DP2I/O327L23FLOAT#I308AC16 $ADR < 40 <$ 345B10 $D < 43 >$ I/O162K25 $SDQM3$ O139AE17 $ADR < 40 <$ 269C11 $D < 44 >$ I/O248L24 $SDQM4$ O227AD16 $ADR < 40 <$ 343D14VDDIVDDI324P23VDDIVDDI305AC13VDDI343D<                                             |                                |     |      |          |      |      |       |      | ~        |      |      |        |     | •          | I/O<br>I/O   | 209         | Y      | 1      | PLLCEN         | T       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |     |      |          |      |      |       |      | ~        |      |      |        |     | •          | I/O<br>I/O   | 118         | W      | 2      | STOP#          | T       |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |     |      |          |      |      |       |      | ~        |      |      |        |     | •          | I/O<br>I/O   | 208         | v      | 3      | BEN#           | T       |

| 94A8 $D < 39 >$ I/O69H26 $SDQ < 31 >$ I/O44AF19 $SDQ < 31 >$ 186B9 $D < 40 >$ I/O163J25 $SDQM0$ O140AE18 $SDQ < 32 >$ 270C10 $D < 41 >$ I/O249K24 $SDQM1$ O228AD17 $SDQ < 32 >$ 93A9 $D < 42 >$ I/O68J26 $SDQM2$ O43AF18 $ADR < 32 >$ 346D11DP2I/O327L23FLOAT#I308AC16 $ADR < 32 >$ 269C11 $D < 43 >$ I/O162K25 $SDQM3$ O139AE17 $ADR < 32 >$ 269C11 $D < 44 >$ I/O248L24 $SDQM4$ O227AD16 $ADR < 32 >$ 343D14VDDIVDI324P23VDDIVDI305AC13VDII184B11 $D < 45 >$ I/O161L25 $DQM6$ O138AE16 $ADR < 32 >$ 345D12VDDEVDDE326M23VDDE307AC15VDDE343D14VDDIVDDE326M23VDDE307AC15VDDE345D12VDDEVDE<                                                                     |                                |     |      |          |      |      |       |      | ~        |      |      |        |     | · ·        | NC           | 208         | U V    | 4      | DEIN#<br>NC    | I<br>NC |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | I/O          | 19          | w      | 4      | IRL<0>         | INC.    |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | I/O<br>I/O   | 117         | v      | 2      | IRL<0>         | I<br>T  |

| 93       A       9       D<42>       I/O       68       J       26       SDQM2       O       43       AF       18       ADR         346       D       11       DP2       I/O       327       L       23       FLOAT#       I       308       AC       16       ADR         185       B       10       D<43>       I/O       162       K       25       SDQM3       O       139       AE       17       ADR         269       C       11       D<44>       I/O       248       L       24       SDQM4       O       227       AD       16       ADR<                                                                                                            |                                |     |      |          |      |      |       |      | ~        |      | -    |        |     |            | I/O<br>I/O   | 207         | U V    | 3      | IRL<2>         | I<br>T  |

| 346       D       11       DP2       I/O       327       L       23       FLOAT#       I       308       AC       16       ADR<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |     |      |          |      | -    |       |      | ~        |      | -    |        |     | · ·        | 0            | 18          | v      | 1      | IRL<2>         | I<br>T  |

| 185       B       10       D<43>       I/O       162       K       25       SDQM3       O       139       AE       17       ADR<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |     |      |          |      |      |       |      | ~        |      | -    |        |     |            | 0            | 289         | v<br>T | 4      | DBREAK#        | I<br>T  |

| 269       C       11       D<44>       I/O       248       L       24       SDQM4       O       227       AD       16       ADR<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                |     |      |          |      |      |       |      |          | -    |      |        |     |            | 0            | 116         | U      | 2      | BRKEN#         | I<br>T  |

| 92       A       10       D<45>       I/O       67       K       26       SDQM5       O       42       AF       17       ADR<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                |     |      |          |      |      |       |      | ~        |      |      |        |     |            | 0            | 206         | Т      | 3      | BRKGO          | 0       |

| 343       D       14       VDDI       VDDI       324       P       23       VDDI       VDDI       305       AC       13       VDDI         184       B       11       D<46>       I/O       161       L       25       DQM6       O       138       AE       16       ADR<                                                                                                                                                                                                                                                                                                                                                                                     |                                |     |      |          |      |      |       |      | ~        |      |      |        |     |            | 0            | 200         | U      | 5<br>1 |                | U<br>I  |

| 184       B       11       D<46>       I/O       161       L       25       DQM6       O       138       AE       16       ADR         345       D       12       VDDE       VDDE       326       M       23       VDDE       VDDE       307       AC       15       VDDE         91       A       11       D<47>       I/O       66       L       26       DQM7       O       41       AF       16       ADR<                                                                                                                                                                                                                                                 |                                |     |      |          |      |      |       |      |          | -    |      |        |     |            | VDDI         |             | N      | 4      | BREQ#<br>VDDI  | VDDI    |

| 345       D       12       VDDE       VDDE       326       M       23       VDDE       VDDE       307       AC       15       VDDE         91       A       11       D<47>       I/O       66       L       26       DQM7       O       41       AF       16       ADR<                                                                                                                                                                                                                                                                                                                                                                                        |                                |     |      |          |      |      |       |      |          |      |      |        |     |            |              | 286         | T      | 2      | BGRNT#         | 0       |

| 91       A       11       D<47>       I/O       66       L       26       DQM7       O       41       AF       16       ADR<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |     |      |          |      | -    |       |      | · ·      | -    |      |        |     |            | O<br>VDDE    | 115<br>288  | R      | 4      | VDDE           | VDDE    |

| 268         C         12         D<48>         I/O         247         M         24         SADR<0>         O         226         AD         15         ADR<           183         B         12         D<49>         I/O         160         M         25         SADR<1>         O         137         AE         15         ADR<                                                                                                                                                                                                                                                                                                                            |                                |     |      |          |      |      |       |      |          |      |      |        |     |            |              |             | Т      | 4      |                |         |

| 183         B         12         D<49>         I/O         160         M         25         SADR<1>         O         137         AE         15         ADR<           89         A         13         VSS         VSS         64         N         26         VSS         VSS         39         AF         14         VSS                                                                                                                                                                                                                                                                                                                                    |                                |     |      |          |      |      |       |      | -        |      |      |        |     |            | 0<br>0       | 16          | R      | 3      | PBREQ#<br>BE0# | 0<br>0  |

| 89 A 13 VSS VSS 64 N 26 VSS VSS 39 AF 14 VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                |     |      |          |      |      |       |      |          | -    |      |        |     |            | 0            | 205         | R<br>R | 3<br>2 | BE0#<br>BE1#   | 0       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |     |      | >        |      |      |       |      |          |      |      |        |     |            | VSS          | 114         | к<br>Р |        |                | VSS     |

| ן אָטן א 12 (D<3U> (I/U) (I) ססן או 20 (SADK<2> (U) (I) 40 (AF IS (ADK<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                |     |      |          |      |      |       |      |          |      |      |        |     |            |              | 14          |        | 1      | VSS<br>DE2#    |         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |     |      |          |      |      |       |      |          |      |      |        |     |            | 0            | 15          | R      | 1      | BE2#<br>BE2#   | 0       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                |     |      |          |      |      |       |      |          |      |      |        |     | ADR < 12 > | 0            | 287         | P      | 4      | BE3#<br>BE4#   | 0       |

| 267 C 13 D<51> I/O 246 N 24 SADR<4> O 225 AD 14 ADR<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                              | 13  | D<31 | >        | 1/0  | 246  | IN    | 24   | SADK<4>  | U    | 223  | AD     | 14  | ADR<13>    | 0            | 204         | Р      | 3      | BE4#           | 0       |

(Table 2-2 MB86860 Pins continued)

| PKO       | 3 Pin 1 | No.      | Left sid          | le           | PKC        | G Pin N  | Jo.          | Bottom s           | ide          | PKG        | Pin No   |        | Right si         | le        | PKC      | G Pin No | ).     | Top si               | de           |

|-----------|---------|----------|-------------------|--------------|------------|----------|--------------|--------------------|--------------|------------|----------|--------|------------------|-----------|----------|----------|--------|----------------------|--------------|

| (Fj)      | (JEI    | DEC)     | Pin name          | Att.         | (Fj)       | (JEI     | DEC)         | Pin name           | Att.         | (Fj)       | (JEDI    | EC)    | Pin name         | att.      | (Fj)     | (JEDI    | EC)    | Pin name             | Att.         |

| 182       | В       | 13       | D<52>             | I/O          | 159        | N        | 25           | SADR<5>            | 0            | 136        | AE       | 14     | ADR<14>          | 0         | 113      | Р        | 2      | BE5#                 | 0            |

| 181       | B       | 14       | D<52>             | I/O<br>I/O   | 158        | P        | 25           | SADR<5>            | 0<br>0       | 135        | AE       |        | ADR<15>          | 0<br>0    | 112      | N        | 2      | BE6#                 | 0<br>0       |

| 266       |         | 14       | D<54>             | I/O          | 245        | P        | 24           | SADR<7>            | 0<br>0       | 224        | AD       |        | ADR<16>          | õ         | 203      | N        | 3      | BE7#                 | õ            |

| 87        | Ă       | 15       | D<55>             | I/O          | 62         | R        | 26           | SADR<8>            | õ            | 37         | AF       |        | ADR<17>          | õ         | 12       | M        | 1      | WKUP#                | I            |

| 88        |         | 14       | VSS               | VSS          | 63         | Р        | 26           | VSS                | VSS          | 38         | AF       | 13     |                  | VSS       | 13       | N        | 1      | VSS                  | VSS          |

| 180       |         | 15       | D<56>             | I/O          | 157        | R        | 25           | SADR<9>            | 0            | 134        | AE       |        | ADR<18>          | 0         | 111      | Μ        | 2      | PDWN#                | 0            |

| 265       | С       | 15       | D<57>             | I/O          | 244        | R        | 24           |                    | 0            | 223        | AD       |        | ADR<19>          | 0         | 202      | М        | 3      | AS#                  | 0            |

| 86        |         | 16       | D<58>             | I/O          | 61         | Т        | 26           | SADR<11>           | 0            | 36         | AF       | 11     | ADR<20>          | 0         | 11       | L        | 1      | RD#                  | 0            |

| 342       | D       | 15       | VDDE              | VDDE         | 323        | R        | 23           | VDDE               | VDDE         | 304        | AC       | 12     | VDDE             | VDDE      | 285      | М        | 4      | VDDE                 | VDDE         |

| 179       | В       | 16       | D<59>             | I/O          | 156        | Т        | 25           | SADR<12>           | 0            | 133        | AE       | 11     | ADR<21>          | 0         | 110      | L        | 2      | RDWR#                | 0            |

| 85        | А       | 17       | D<60>             | I/O          | 60         | U        | 26           | SRAS#              | 0            | 35         | AF       | 10     | ADR<22>          | 0         | 10       | Κ        | 1      | LOCK#                | 0            |

| 264       | С       | 16       | D<61>             | I/O          | 243        | Т        | 24           | SCKE#              | 0            | 222        | AD       | 11     | ADR<23>          | 0         | 201      | L        | 3      | D<0>                 | I/O          |

| 178       | В       | 17       | D<62>             | I/O          | 155        | U        | 25           | SCAS#              | 0            | 132        | AE       | 10     | ADR<24>          | 0         | 109      | Κ        | 2      | D<1>                 | I/O          |

| 341       | D       | 16       | DP0               | I/O          | 322        | Т        | 23           | SCLK               | 0            | 303        | AC       | 11     | ADR<25>          | 0         | 284      | L        | 4      | D<2>                 | I/O          |

| 84        | А       | 18       | D<63>             | I/O          | 59         | V        | 26           | SWE#               | 0            | 34         | AF       | 9      | ADR<26>          | 0         | 9        | J        | 1      | D<3>                 | I/O          |

| 263       | С       | 17       | MEXC#             | Ι            | 242        | U        | 24           | SCS0#              | 0            | 221        | AD       | 10     | ADR<27>          | 0         | 200      | Κ        | 3      | D<4>                 | I/O          |

| 339       | D       | 18       | VDDI              | VDDI         | 320        | V        | 23           | VDDI               | VDDI         | 301        | AC       | 9      | VDDI             | VDDI      | 282      | J        | 4      | VDDI                 | VDDI         |

| 177       | В       | 18       | READY#            | Ι            | 154        | V        | 25           | SCS1#              | 0            | 131        | AE       | 9      | ADR<28>          | 0         | 108      | J        | 2      | D<5>                 | I/O          |

| 83        | А       | 19       | RDYOUT#           | 0            | 58         | W        | 26           | SCS2#              | 0            | 33         | AF       | 8      | ADR<29>          | 0         | 8        | Η        | 1      | D<6>                 | I/O          |

| 340       |         | 17       | NC                | NC           | 321        | U        | 23           | NC                 | NC           | 302        | AC       | 10     | NC               | NC        | 283      | Κ        | 4      | NC                   | NC           |

| 262       | С       | 18       | BMODE32#          |              | 241        | V        | 24           | SCS3#              | 0            | 220        | AD       | 9      | ADR<30>          | 0         | 199      | J        | 3      | D<7>                 | I/O          |

| 176       |         | 19       | BMODE16#          |              | 153        | W        | 25           | SBA<0>             | 0            | 130        | AE       | 8      | ADR<31>          | 0         | 107      | Н        | 2      | D<8>                 | I/O          |

| 82        | А       | 20       | SDQ<0>            | I/O          | 57         | Y        | 26           | SBA<1>             | 0            | 32         | AF       | 7      | DTYP<1>          | 0         | 7        | G        | 1      | D<9>                 | I/O          |

| 261       | С       | 19       | SDQ<1>            | I/O          | 240        | W        | 24           | SDQ<32>            | I/O          | 219        | AD       | 8      | DTYP<0>          | 0         | 198      | Н        | 3      | D<10>                | I/O          |