# **SPARClite**

# **MB86860 Series Data Sheet**

Rev.1.2 July 27, 1999

### Fujitsu

This material is preliminary and is subject to change without notice.

SPARClite is a registered trademark of SPARC International, Inc. in the United States. Fujitsu Microelectronics, Inc. has been

granted exclusive use of this trademark.

# 860 Series 32-bit RISC Embedded Processor

### 1. Features

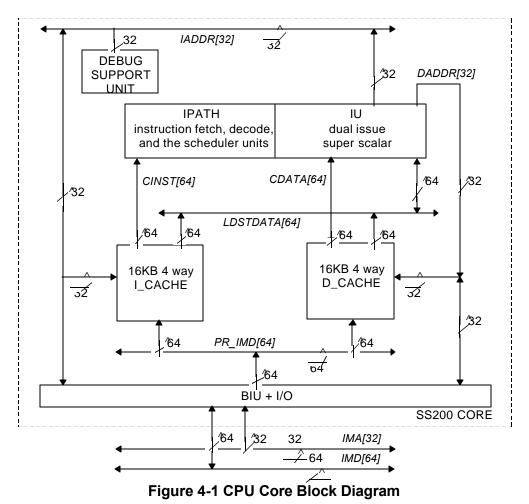

#### 1.1. CPU Core Part

- Conforms to SPARC V8

- Internal operating frequency maximum 200MHz

- 2-issue super-scalar architecture

- 16KB 4-way instruction cache

- 16KB 4-way data cache

- Power Down Mode

- Bi-endian support

#### 1.2. Debug Support Functions

- Break Function (Instruction Address / External pins / Software / Single Step)

- 16-depth Address Trace Buffer

- Single Step Operation

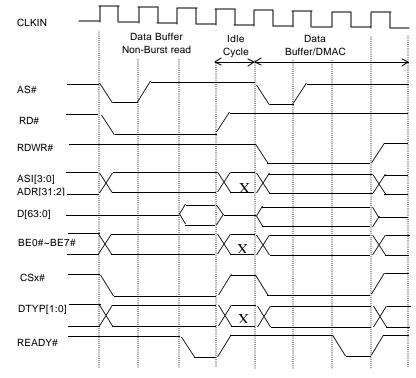

#### 1.3. Data Buffer Module

- 4 Column Instruction Buffer

- 4 Column X 2 Read Buffer

- 16 Column Write Buffer

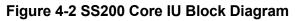

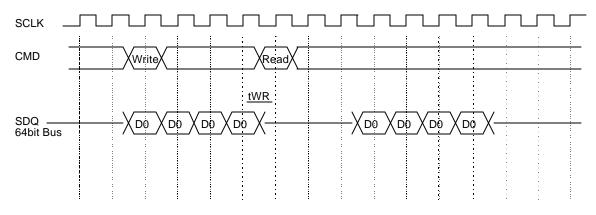

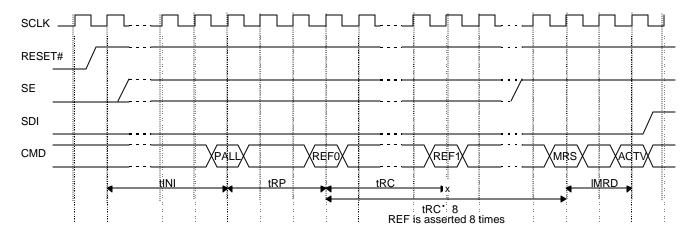

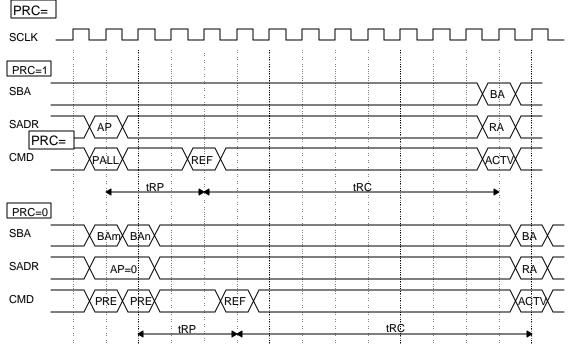

#### 1.4. SDRAM Interface

- 64 bit Data Bus Widths

- Maximum 100MHz Operation

- Auto / Self-Refresh Support

- Parity Function Support

#### 1.5. SPARClite Bus Interface

- 8 / 16 / 32 / 64-bit Data Bus

- Burst Mode Support

- Parity Function Support

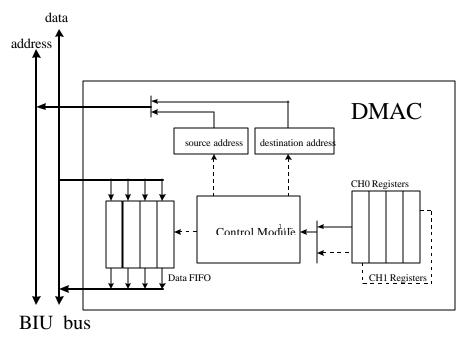

#### 1.6. Bus-bridge DMA

• DMA 2 channels. Simultaneous operation 1 channel

#### 1.7. Power Supply

- Internal: 2.5V

- I/O Pins: 3.3V

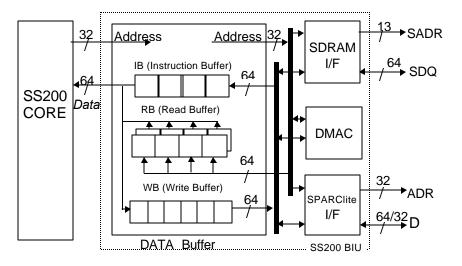

### 1.8. MB86860 Block Diagram

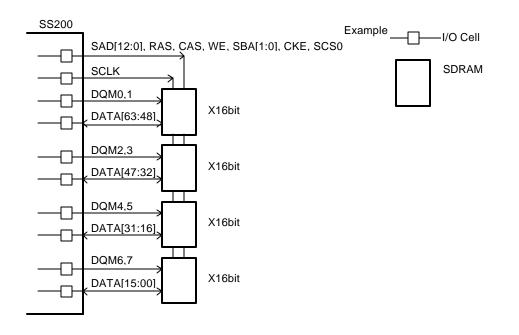

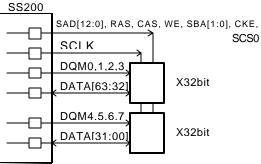

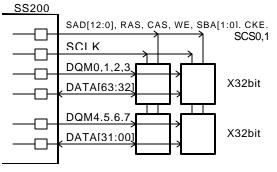

Figure 1.1 SS200 BIU Block Diagram

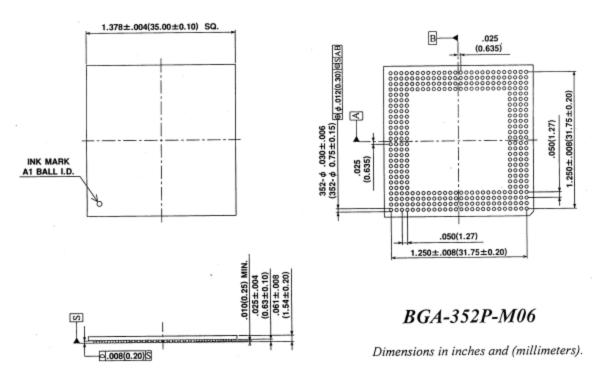

1.9 MB86860 Pin Overview

1.9.1 Package

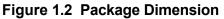

### 1.9.2 MB86860 signal list

Table 1.1 Pin Assignment

| PKG  | Pin I | No.  | Lei    | ft   | PKG  | Pin N | lo. | Botto   | m    | PKG  | 6 Pin | No.  | Rigl    | ht   | PKG  | i Pin | No.  | Тор     | D    |

|------|-------|------|--------|------|------|-------|-----|---------|------|------|-------|------|---------|------|------|-------|------|---------|------|

| (FJ) | (JEI  | DEC) | Signal | Att. | (FJ) | (JED  | EC) | Signal  | Att. | (FJ) | (JE   | DEC) | Signal  | Att. | (FJ) | (JEI  | DEC) | Signal  | Att. |

| 1    | Α     | 1    | VSS    | VSS  | 76   | A 2   | 26  | VSS     | VSS  | 51   | AF    | 26   | VSS     | VSS  | 26   | AF    | 1    | VSSP    | VSS  |

| 277  | D     | 4    | VDDI   | VDDI | 334  | D     | 23  | VDDI    | VDDI | 315  | AC    | 23   | VDDI    | VDDI | 296  | AC    | 4    | VDDI    | VDDI |

| 276  | С     | 4    | D<23>  | I/O  | 255  | D     | 24  | SDQ<15> | I/O  | 234  | AD    | 23   | SDQ<45> | I/O  | 213  | AC    | 3    | TRST#   | I    |

| 352  | D     | 5    | VDDE   | VDDE | 333  | Е 2   | 23  | VDDE    | VDDE | 314  | AC    | 22   | VDDE    | VDDE | 295  | AB    | 4    | TD1     | I    |

| 99   | А     | 3    | D<24>  | I/O  | 74   | С     | 26  | SDQ<16> | I/O  | 49   | AF    | 24   | SDQ<46> | I/O  | 24   | AD    | 1    | TMS     | I    |

| 191  | В     | 4    | D<25>  | I/O  | 168  | D     | 25  | SDQ<17> | I/O  | 145  | AE    | 23   | SDQ<47> | I/O  | 122  | AC    | 2    | TD0     | 0    |

| 275  | С     | 5    | D<26>  | I/O  | 254  | E 2   | 24  | SDQ<18> | I/O  | 233  | AD    | 22   | SDQ<48> | I/O  | 212  | AB    | 3    | TCLK    | 1    |

| 351  | D     | 8    | DP4    | I/O  | 332  | F 2   | 23  | ADP5    | I/O  | 313  | AC    | 21   | SDP1    | I/O  | 294  | AA    | 4    | VDDP    | VDDP |

| 101  | В     | 2    | VDDI   | VDDI | 170  | в 2   | 25  | VDDI    | VDDI | 147  | AE    | 25   | VDDI    | VDDI | 124  | AE    | 2    | VDDI    | VDDI |

| 98   | А     | 4    | D<27>  | I/O  | 73   | D     | 26  | SDQ<19> | I/O  | 48   | AF    | 23   | SDQ<49> | I/O  | 23   | AC    | 1    | TEST1   | I    |

| 190  | В     | 5    | D<28>  | I/O  | 167  | Е 2   | 25  | SDQ<20> | I/O  | 144  | AE    | 22   | SDQ<50> | I/O  | 121  | AB    | 2    | TEST2   | I    |

| 274  | С     | 6    | D<29>  | I/O  | 253  | F 2   | 24  | SDQ<21> | I/O  | 232  | AD    | 21   | SDQ<51> | I/O  | 211  | AA    | 3    | VDDP    | VDDP |

| 350  | D     | 7    | DP3    | I/O  | 331  | G 2   | 23  | SDP4    | I/O  | 312  | AC    | 20   | SDP0    | I/O  | 293  | Υ     | 4    | VSSP    | VSSP |

| 192  | В     | 3    | VSS    | VSS  | 169  | C 2   | 25  | VSS     | VSS  | 146  | AE    | 24   | VSS     | VSS  | 123  | AD    | 2    | VSSP    | VSS  |

| 97   | А     | 5    | D<30>  | I/O  | 72   | Е 2   | 26  | SDQ<22> | I/O  | 47   | AF    | 22   | SDQ<52> | I/O  | 22   | AB    | 1    | CLKSEL1 | I    |

| 348  | D     | 9    | VDDI   | VDDI | 329  | -     | 23  | VDDI    | VDDI | 310  | AC    | 18   | VDDI    | VDDI | 291  | V     | 4    | VDDI    | VDDI |

| 189  | В     | 6    | D<31>  | I/O  | 166  | F 2   | 25  | SDQ<23> | I/O  | 143  | AE    | 21   | SDQ<53> | I/O  | 120  | AA    | 2    | CLKIN   | I    |

| 273  | С     | 7    | D<32>  | I/O  | 252  | G 2   | 24  | SDQ<24> | I/O  | 231  | AD    | 20   | SDQ<54> | I/O  | 210  | Υ     | 3    | VSSP    | VSSP |

| 349  | D     | 8    | VDDE   | VDDE | 330  | Н :   | 23  | VDDE    | VDDE | 311  | AC    | 19   | VDDE    | VDDE | 292  | W     | 4    | VDDE    | VDDE |

| 96   | А     | 6    | D<33>  | I/O  | 71   | F 2   | 26  | SDQ<25> | I/O  | 46   | AF    | 21   | SDQ<55> | I/O  | 21   | AA    | 1    | CLKSEL0 | I    |

| 188  | В     | 7    | D<34>  | I/O  | 165  | G 2   | 25  | SDQ<26> | I/O  | 142  | AE    | 20   | SDQ<56> | I/O  | 119  | Υ     | 2    | RESET#  | I    |

| 100  | А     | 2    | VSS    | VSS  | 75   | в     | 26  | VSS     | VSS  | 50   | AF    | 25   | VSS     | VSS  | 25   | AE    | 1    | VSSP    | VSS  |

| 272  | С     | 8    | D<35>  | I/O  | 251  | Н :   | 24  | SDQ<27> | I/O  | 230  | AD    | 19   | SDQ<57> | I/O  | 209  | W     | 3    | BCLK    | I    |

| 95   | А     | 7    | D<36>  | I/O  | 70   | G     | 26  | SDQ<28> | I/O  | 45   | AF    | 20   | SDQ<58> | I/O  | 20   | Υ     | 1    | PLLCEN  | 1    |

| 187  | В     | 8    | D<37>  | I/O  | 164  | н :   | 25  | SDQ<29> | I/O  | 141  | AE    | 19   | SDQ<59> | I/O  | 118  | W     | 2    | STOP#   | 1    |

| 271  | С     | 9    | D<38>  | I/O  | 250  | J     | 24  | SDQ<30> | I/O  | 229  | AD    | 18   | SDQ<60> | I/O  | 208  | V     | 3    | BEN#    | I    |

| 347  | D     | 10   | NC     | NC   | 328  | K 2   | 23  | NC *1   | NC   | 309  | AC    | 17   | NC      | NC   | 290  | U     | 4    | NC      | NC   |

| 94   | А     | 8    | D<39>  | I/O  | 69   | н :   | 26  | SDQ<31> | I/O  | 44   | AF    | 19   | I/O     | I/O  | 19   | W     | 1    | ILR<0>  | 1    |

| 186  | В     | 9    | D<40>  | I/O  | 163  | J     | 25  | SDQM0   | 0    | 140  | AE    | 18   | I/O     | I/O  | 117  | V     | 2    | IRL<1>  | I    |

| 270  | С     | 10   | D<41>  | I/O  | 249  | K 2   | 24  | SDQM1   | 0    | 228  | AD    | 17   | I/O     | I/O  | 207  | U     | 3    | IRL<2>  | I    |

| 93   | А     | 9    | D<42>  | I/O  | 68   | J     | 26  | SDQM2   | 0    | 43   | AF    | 18   | 0       | 0    | 18   | V     | 1    | IRL<3>  | 1    |

| 346  | D     | 11   | DP2    | I/O  | 327  | L     | 23  | FLOAT#  | 1    | 308  | AC    | 16   | 0       | 0    | 289  | Т     | 4    | DBREAK# | I    |

| 185  | В     | 10   | D<43>  | I/O  | 162  | K :   | 25  | SDQM3   | 0    | 139  | AE    | 17   | 0       | 0    | 116  | U     | 2    | BRKEN#  | I    |

| 269  | С     | 11   | D<44>  | I/O  | 248  | L     | 24  | SDQM4   | 0    | 227  | AD    | 16   | 0       | 0    | 206  | Т     | 3    | BRKG0   | 0    |

| 92   | А     | 10   | D<45>  | I/O  | 67   | K 2   | 26  | SDQM5   | 0    | 42   | AF    | 17   | 0       | 0    | 17   | U     | 1    | BREQ#   | I    |

| 343  | D     | 14   | VDDI   | VDDI | 324  | Р 2   | 23  | VDDI    | VDDI | 305  | AC    | 13   | VDDI    | VDDI | 286  | Ν     | 4    | VDDI    | VDDI |

| 184  | В     | 11   | D<46>  | I/O  | 161  | L     | 25  | SDQM6   | 0    | 138  | AE    | 16   | ADR<7>  | 0    | 115  | Т     | 2    | BGRNT#  | 0    |

| 345  | D     | 12   | VDDE   | VDDE | 326  | М     | 23  | VDDE    | VDDE | 307  | AC    | 15   | VDDE    | VDDE | 288  | R     | 4    | VDDE    | VDDE |

| 91   | А     | 11   | D<47>  | I/O  | 66   | L     | 26  | SDQM7   | 0    | 41   | AF    | 16   | ADR<8>  | 0    | 16   | Т     | 1    | PBREQ#  | 0    |

| 268  | С     | 12   | D<48>  | I/O  | 247  | М     | 24  | SADR<0> | 0    | 226  | AD    | 15   | ADR<9>  | 0    | 205  | R     | 3    | BE0#    | 0    |

| 183  | В     | 12   | D<49>  | I/O  | 160  | М     | 25  | SADR<1> | 0    | 137  | AE    | 15   | ADR<10> | 0    | 114  | R     | 2    | BE1#    | 0    |

| 89   | А     | 13   | VSS    | VSS  | 64   | Ν     | 26  | VSS     | VSS  | 39   | AF    | 14   | VSS     | VSS  | 14   | Р     | 1    | VSS     | VSS  |

| 90   | А     | 12   | D<50>  | I/O  | 65   | М     | 26  | SADR<2> | 0    | 40   | AF    | 15   | ADR<11> | 0    | 15   | R     | 1    | BE2#    | 0    |

| 344  | D     | 13   | DP1    | I/O  | 325  | N 2   | 23  | SADR<3> | 0    | 306  | AC    | 14   | ADR<12> | 0    | 287  | Р     | 4    | BE3#    | 0    |

VDDI: VDD for Internal Logic --- 2.5V VDDE: VDD for I/O Pad ------ 3.3V VDDP: VDD for built-in PLL ---- 2.5V

Table 1.2 Pin Assignment (continued)

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DKC |   |    | DIE 1.2 I III ASSI |      | <u> </u> |   |    | Bottor   | <b>n</b> | DKC | Din | Jo | Righ    | t I  | PKG Pin No. Top |    |   | n      |            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|----|--------------------|------|----------|---|----|----------|----------|-----|-----|----|---------|------|-----------------|----|---|--------|------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |   |    |                    | Δ#   |          |   |    |          |          |     |     |    | 8       |      |                 |    |   |        | р<br>Att.  |

| 182         B         13         D-52>         1/0         159         N         25         SADR-5>         0         136         AE         14         ADR-14>         0         113         P         2         BE5#           181         B         14         D-55>         1/0         158         P         24         SADR-5>         0         135         AE         13         ADR-15>         0         112         N         2         BE6#           266         C         14         D-55>         1/0         62         P         24         SADR-3>         0         224         ADR-15>         0         12         M         1         WKUP#           88         A         15         D-55>         1/0         157         R<25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . / |   | /  | 2                  |      |          | ì |    | - U      |          |     | ``` |    |         |      |                 | `` |   | U      | Ац.<br>О   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |   |    |                    |      | -        |   |    |          | _        |     |     |    |         |      | -               |    |   |        | 0          |

| 266         C         14         De55+         I/O         245         P         24         SADR-7-         O         224         AD         13         ADR-16>         O         121         M         1         WKUP#           87         A         14         VSS                                                                                                                                                                                                                               |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | 0          |

| 87       A       15       Dc55>       I/O       62       P       26       VSS       VSS       37       AF       12       ADR-17>       O       12       M       I       WKUP#         88       A       14       VSS       VSS       ISS       VSS                                                                                                                                                                                                                                                                                                                               |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | 0          |

| 88         A         14         VSS         VSS         63         P         26         VSS         VSS         13         VSS         13         N         1         VSS           180         B         15         D<56>         100         157         R         25         SADR49>         O         134         AE         12         ADR:18>         O         111         M         2         PDWN#           286         A         16         D<55>         1/O         61         T         26         SADR<11>         O         36         AF         11         ADR:21>         O         110         K         1         RDWR#           342         D         15         VDDE         VDDE         SSAR:42>         O         133         AE         11         ADR:22>         O         110         K         1         LOCK#           264         C         16         D<60>         1/O         63         SCK#         O         32         AE         10         ADR:23>         O         201         L         3         D         1         D         2         D         10         ADR:24>         O         10                                                                                                                                                                                                                                                                      |     |   |    | -                  |      | -        |   |    | -        | -        |     |     |    | _       | -    |                 |    | - |        | I          |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |   |    |                    |      |          |   |    |          | -        | -   |     |    |         | -    |                 |    |   | -      | VSS        |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      | -               |    |   |        | 0          |

| 342         D         15         VDDE         VDDE         VDE                                                                                                                                                                                                              |     | С |    |                    | I/O  |          |   | 24 |          | 0        | 223 | AE  | 11 |         |      | 202             |    | 3 | AS#    | 0          |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 86  | А | 16 | D<58>              | I/O  | 61       | Т | 26 | SADR<11> | 0        | 36  | AF  | 11 |         | 0    | 11              | L  | 1 | RD#    | 0          |

| 85A17D<60>I/O60U26SRAS#O35AF10ADR<22>O10K1LOCK#264C166D<61>I/O124T24SCKE#O222AD11ADR<23>O201L3DDD341D16DPOI/O322T23SCLKO303AC11ADR<23>O284L4D<25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 342 | D | 15 | VDDE               | VDDE | 323      | R | 23 | VDDE     | VDDE     | 304 | AC  | 12 | VDDE    | VDDE | 285             | М  | 4 | VDDE   | VDDE       |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 179 | В | 16 | D<59>              | I/O  | 156      | Т | 25 | SADR<12> | 0        | 133 | AE  | 11 | ADR<21> | 0    | 110             | L  | 2 | RDWR#  | 0          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 85  | А | 17 | D<60>              | I/O  | 60       | U | 26 | SRAS#    | 0        | 35  | AF  | 10 | ADR<22> | 0    | 10              | К  | 1 | LOCK#  | 0          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 264 | С | 16 | D<61>              | I/O  | 243      | Т | 24 | SCKE#    | 0        | 222 | AD  | 11 | ADR<23> | 0    | 201             | L  | 3 | D<0>   | I/O        |

| 84A18D<63>I/O59V26SWE#O34AF9ADR<26>O9J1D<3>263C17MEXC#I242U24SCS0#O221AD10ADR<27>O200K3DD339D18VDDIVDDI320V23VDDIVDI301AC9VDIVDDI282J4VDDI177B18READY#I154V25SC51#O131AE9SDR<28>O18H1D<65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 178 | В | 17 | D<62>              | I/O  | 155      | U | 25 | SCAS#    | 0        | 132 | AE  | 10 | ADR<24> | 0    | 109             | К  | 2 | D<1>   | I/O        |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 341 | D | 16 | DP0                | I/O  | 322      | Т | 23 | SCLK     | 0        | 303 |     | 11 | ADR>25> | 0    | 284             | L  | 4 | D<2>   | I/O        |

| 339       D       18       VDDI       VDDI       320       V       23       VDDI       VDDI       301       AC       9       VDDI       VDDI       282       J       4       VDDI         177       B       18       READY#       I       154       V       25       SCS1#       O       131       AE       9       SDR<28>       O       108       J       2       D<5>         83       A       19       RDYOUT#       O       58       W       26       SCS2#       O       33       AF       8       ADR<29>       O       8       H       1       D<6>         262       C       19       BMODE32#       I       231       V       23       NC       NC       302       AC       10       NC<*2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 84  |   | 18 | D<63>              | I/O  | 59       | V | 26 | SWE#     | 0        | 34  | AF  | 9  | ADR<26> | 0    | 9               | J  | 1 | D<3>   | I/O        |

| 177       B       18       READY#       I       154       V       25       SCS1#       O       131       AE       9       SDR<28>       O       108       J       2       D<5>         83       A       19       RDYOUT#       O       58       W       26       SCS2#       O       33       AF       8       ADR<29>       O       88       H       1       D<6>         340       D       17       NC       NC       321       U       23       NC       NC       302       AC       10       NC *2       NC       283       K       4       NC         262       C       19       BMODE16#       I       153       W       25       SBA<0>       O       130       AE       8       ADR<31>       O       177       G       1       D<9>         261       C       19       SDQ<1>       I/O       240       W 24       SDQ<32>       I/O       219       AD       8       DTYP<0>       O       188       H       3       D<10>       175       B       20       SDQ<2>       I/O       152       Y 25       SDQ<33>       I/O       129 <td< td=""><td>263</td><td>С</td><td>17</td><td></td><td></td><td>242</td><td></td><td>24</td><td></td><td>_</td><td>221</td><td>AD</td><td>10</td><td></td><td>0</td><td>200</td><td>К</td><td>3</td><td></td><td>I/O</td></td<>                                                                                                                                 | 263 | С | 17 |                    |      | 242      |   | 24 |          | _        | 221 | AD  | 10 |         | 0    | 200             | К  | 3 |        | I/O        |

| 83         A         19         RDYOUT#         0         58         W         26         SCS2#         0         33         AF         8         ADR<29>         0         8         H         1         D<6>           340         D         17         NC         NC         321         U         23         NC         NC         302         AC         10         NC *2         NC         283         K         4         NC           262         C         19         BMODE32#         I         241         V         24         SCS3#         O         220         AD         9         ADR<3D>         O         199         J         3         D<7>           176         B         19         BMODE16#         I         153         W 25         SBA <d>         O         130         AE         8         ADR&lt;3D&gt;         O         107         H         2         D&lt;8&gt;           261         C         19         SDQ&lt;1&gt;//O         57         Y 26         SBA<d>         0         219         AF         2         VSS         VSS         2         B         1         VSS           171         B         <td< td=""><td>339</td><td></td><td>18</td><td>VDDI</td><td>VDDI</td><td>320</td><td></td><td>23</td><td></td><td>VDDI</td><td></td><td></td><td></td><td>VDDI</td><td>VDDI</td><td>282</td><td>J</td><td></td><td>VDDI</td><td>VDDI</td></td<></d></d> | 339 |   | 18 | VDDI               | VDDI | 320      |   | 23 |          | VDDI     |     |     |    | VDDI    | VDDI | 282             | J  |   | VDDI   | VDDI       |

| 340         D         17         NC         NC         321         U         23         NC         NC         302         AC         10         NC         283         K         4         NC           262         C         19         BMODE32#         I         241         V         24         SCS3#         O         220         AD         9         ADR<30>         O         199         J         3         D         D           176         B         19         BMODE16#         I         153         W         25         SBA<0>         O         130         AE         8         ADR<31>         O         107         H         2         D         D         P         G         1         D         P         D         P         AD         P         D         P         D         T         G         1         D         P         D         Z         D         S         S         S         S         S         S         Z         D         S         D         S         D         S         D         S         D         S         D         S         D         S         D         S                                                                                                                                                                                                                                                                                       | 177 |   |    |                    |      |          |   |    |          |          |     |     |    | SDR<28> |      | 108             |    |   | D<5>   | I/O        |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | I/O        |

| 176       B       19       BMODE16#       I       153       W 25       SBA<0>       O       130       AE       8       ADR<31>       O       107       H       2       D<8>         82       A       20       SDQ<0>       I/O       57       Y       26       SBA<1>       O       32       AF       7       DTYP<1>       O       7       G       1       D<9>         261       C       19       SDQ<1>       I/O       240       W 24       SDQ<32>       I/O       219       AD       8       DTYP<0>       O       198       H       3       D<10>         171       B       24       VSS       VSS       148       AD 25       VSS       VSS       27       AF       2       VSS       VSS       2       B       1       VSS         175       B       20       SDQ<2>       I/O       152       Y       25       SDQ<33>       I/O       31       AF       6       BMREQ#       O       6       F       1       D<12>       D       33       D       281       H       4       VDE         338       D       19       VDE       VDE                                                                                                                                                                                                                                                                                                                                                                     |     |   |    | -                  | -    |          | - | -  | -        | -        |     | -   |    | -       | -    |                 |    |   | -      | NC         |

| 82       A       20       SDQ<0>       I/O       57       Y       26       SBA<1>       O       32       AF       7       DTYP<1>       O       7       G       1       D<9>         261       C       19       SDQ<1>       I/O       240       W       24       SDQ<32>       I/O       219       AD       8       DTYP<0>       O       198       H       3       D<10>         171       B       24       VSS       VSS       148       AD<25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -   |   | -  |                    |      |          | - |    |          | -        |     |     |    |         | -    |                 |    | - |        | I/O        |

| 261       C       19       SDQ<1>       I/O       240       W 24       SDQ<32>       I/O       219       AD       8       DTYP<0>       O       198       H       3       D<10>         171       B       24       VSS       VSS       148       AD<25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |   |    |                    |      |          |   |    |          | _        |     |     |    |         | -    | -               |    |   |        | I/O        |

| 171       B       24       VSS       VSS       148       AD 25       VSS       VSS       27       AF 2       VSS       VSS       2       B       1       VSS         175       B       20       SDQ<2>       I/O       152       Y       25       SDQ<33>       I/O       129       AE       7       BMACK#       I       106       G       2       D<11>         81       A       21       SDQ<3>       I/O       56       AA 26       SDQ<34>       I/O       31       AF 6       BMREQ#       O       6       F       1       D<12>         338       D       19       VDDE       VDDE       319       W       23       VDDE       VDDE       300       AC       8       VDDE       VDE       281       H       4       VDDE         260       C       20       SDQ<4>       I/O       239       Y       24       SDQ<35>       I/O       218       AD       7       ERROR#       O       197       G       3       D<13>         174       B       21       ADQ<5>       I/O       151       AA 25       SDQ<36>       I/O       128       AE 6                                                                                                                                                                                                                                                                                                                                                             |     |   |    |                    |      |          |   |    |          | _        |     |     |    |         |      |                 |    |   | -      | I/O        |

| 175       B       20       SDQ<2>       I/O       152       Y       25       SDQ<33>       I/O       129       AE       7       BMACK#       I       106       G       2       D<11>         81       A       21       SDQ<3>       I/O       56       AA       26       SDQ<34>       I/O       31       AF       6       BMREQ#       O       6       F       1       D<12>         338       D       19       VDDE       VDDE       319       W       23       VDDE       VDDE       300       AC       8       VDDE       VDDE       281       H       4       VDDE         260       C       20       SDQ<4>       I/O       239       Y       24       SDQ<35>       I/O       218       AD       7       ERROR#       O       197       G       3       D<13>         174       B       21       ADQ<5>       I/O       151       AA       25       SDQ<36>       I/O       128       AE       6       EOP#       O       105       F       2       D<14>         80       A       22       SDQ<6>       I/O       55       AB       26                                                                                                                                                                                                                                                                                                                                                                  |     |   |    |                    |      | -        |   |    |          |          |     |     |    |         | _    |                 |    |   |        | I/O        |

| 81       A       21       SDQ<3>       I/O       56       AA 26       SDQ<34>       I/O       31       AF 6       BMREQ#       O       6       F       1       D<12>         338       D       19       VDDE       VDDE       319       W 23       VDDE       VDDE       300       AC 8       VDDE       VDDE       281       H       4       VDDE         260       C       20       SDQ<4>       I/O       239       Y 24       SDQ<35>       I/O       218       AD 7       ERROR#       O       105       F       2       D<13>         174       B       21       ADQ<5>       I/O       151       AA 25       SDQ<36>       I/O       128       AE 6       EOP#       O       105       F       2       D<14>         80       A       22       SDQ<6>       I/O       55       AB 26       SDQ<37>       I/O       30       AF 5       CS0#       O       5       E       1       D<15>         337       D       20       SDQ<7>       I/O       318       Y 23       SDQ<38>       I/O       217       AD 6       CS2#       O       196       F<3                                                                                                                                                                                                                                                                                                                                                     |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | VSS        |

| 338       D       19       VDDE       VDDE       319       W 23       VDDE       VDDE       300       AC 8       VDDE       VDDE       281       H 4       VDDE         260       C       20       SDQ<4>       I/O       239       Y 24       SDQ<35>       I/O       218       AD 7       ERROR#       O       197       G 3       D<13>         174       B       21       ADQ<5>       I/O       151       AA 25       SDQ<36>       I/O       128       AE 6       EOP#       O       105       F 2       D<14>         80       A       22       SDQ<6>       I/O       55       AB 26       SDQ<37>       I/O       30       AF 5       CS0#       O       5       E 1       D<15>         337       D       20       SDQ<7>       I/O       318       Y 23       SDP3       I/O       299       AC 7       CS1#       O       280       G 4       DP7         259       C       21       SDQ<8>       I/O       238       AA 24       SDQ<38>       I/O       217       AD 6       CS2#       O       196       F 3       D<16>         173       B       22 <td></td> <td>I/O</td>                                                                                                                                 |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | I/O        |

| 260       C       20       SDQ<4>       I/O       239       Y       24       SDQ<35>       I/O       218       AD       7       ERROR#       O       197       G       3       D<13>         174       B       21       ADQ<5>       I/O       151       AA 25       SDQ<36>       I/O       128       AE       6       EOP#       O       105       F       2       D<14>         80       A       22       SDQ<6>       I/O       55       AB 26       SDQ<37>       I/O       30       AF       5       CS0#       O       5       E       1       D<15>         337       D       20       SDQ<7>       I/O       318       Y       23       SDP3       I/O       299       AC       7       CS1#       O       280       G       4       DP7         259       C       21       SDQ<8>       I/O       238       AA 24       SDQ<38>       I/O       217       AD       6       CS2#       O       196       F       3       D<16>         173       B       22       SDQ<9>       I/O       150       AB 25       SDQ<39>       I/O       127                                                                                                                                                                                                                                                                                                                                                             |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | 1/0        |

| 174       B       21       ADQ<5>       I/O       151       AA 25       SDQ<36>       I/O       128       AE 6       EOP#       O       105       F       2       D<14>         80       A       22       SDQ<6>       I/O       55       AB 26       SDQ<37>       I/O       30       AF 5       CS0#       O       55       E       1       D<15>         337       D       20       SDQ<7>       I/O       318       Y       23       SDP3       I/O       299       AC 7       CS1#       O       280       G       4       DP7         259       C       21       SDQ<8>       I/O       238       AA 24       SDQ<38>       I/O       217       AD 6       CS2#       O       196       F       3       D<16>         173       B       22       SDQ<9>       I/O       150       AB 25       SDQ<39>       I/O       127       AE 5       CS3#       O       104       E       2       D<17>         79       A       23       SDQ<10>       I/O       54       AC 26       SDQ<40>       I/O       29       AF 4       CS4#       O       4       D<1                                                                                                                                                                                                                                                                                                                                                   |     |   | -  |                    |      |          |   | -  |          |          |     |     |    |         |      | -               |    |   |        | VDDE       |

| 80       A       22       SDQ<6>       I/O       55       AB 26       SDQ<37>       I/O       30       AF 5       CS0#       O       5       E       1       D<15>         337       D       20       SDQ<7>       I/O       318       Y       23       SDP3       I/O       299       AC 7       CS1#       O       280       G       4       DP7         259       C       21       SDQ<8>       I/O       238       AA 24       SDQ<38>       I/O       217       AD 6       CS2#       O       196       F       3       D<16>         173       B       22       SDQ<9>       I/O       150       AB 25       SDQ<39>       I/O       127       AE 5       CS3#       O       104       E       2       D<17>         79       A       23       SDQ<10>       I/O       54       AC 26       SDQ<40>       I/O       29       AF 4       CS4#       O       4       D<1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |   | -  |                    |      |          |   |    |          |          |     |     |    | _       | -    | -               |    | - | -      | 1/O        |

| 337       D       20       SDQ<7>       I/O       318       Y       23       SDP3       I/O       299       AC       7       CS1#       O       280       G       4       DP7         259       C       21       SDQ<8>       I/O       238       AA       24       SDQ<38>       I/O       217       AD       6       CS2#       O       196       F       3       D<16>         173       B       22       SDQ<9>       I/O       150       AB       25       SDQ<39>       I/O       127       AE       5       CS3#       O       104       E       2       D<17>         79       A       23       SDQ<10>       I/O       54       AC 26       SDQ<40>       I/O       29       AF       4       CS4#       O       4       D       1       D<18>         256       C       24       VDDI       VDDI       235       AD 24       VDDI       VDI       214       AD 3       VDDI       VDI       193       C       3       VDI         336       D       21       SDP7       I/O       317       AA 23       SDP2       I/O       298       AC<                                                                                                                                                                                                                                                                                                                                                            |     |   |    |                    |      |          |   | -  |          |          |     |     |    |         |      |                 |    |   |        | I/O<br>I/O |

| 259       C       21       SDQ<8>       I/O       238       AA 24       SDQ<38>       I/O       217       AD 6       CS2#       O       196       F 3       D<16>         173       B       22       SDQ<9>       I/O       150       AB 25       SDQ<39>       I/O       127       AE 5       CS3#       O       104       E 2       D<17>         79       A       23       SDQ<10>       I/O       54       AC 26       SDQ<40>       I/O       29       AF 4       CS4#       O       4       D 1       D<18>         256       C       24       VDDI       VDDI       235       AD 24       VDDI       VDI       214       AD 3       VDDI       VDI       193       C 3       VDDI         336       D       21       SDP7       I/O       317       AA 23       SDP2       I/O       298       AC 6       CS5#       O       279       F 4       DP6         77       A       25       VSS       VSS <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>-</td><td></td><td></td><td></td><td>1/O<br/>1/O</td></t<>                                                                                                                               |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      | -               |    |   |        | 1/O<br>1/O |

| 173       B       22       SDQ<9>       I/O       150       AB 25       SDQ<39>       I/O       127       AE 5       CS3#       O       104       E 2       D<17>         79       A       23       SDQ<10>       I/O       54       AC 26       SDQ<40>       I/O       29       AF 4       CS4#       O       4       D       1       D<18>         256       C       24       VDDI       VDDI       235       AD 24       VDDI       VDI       214       AD 3       VDDI       VDI       193       C 3       VDDI         336       D       21       SDP7       I/O       317       AA 23       SDP2       I/O       298       AC 6       CS5#       O       279       F 4       DP6         77       A       25       VSS       VS       52       AE 26       VSS       VS       125       AE 3       VSS       VSS       102       C 2       VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |   |    |                    |      |          |   |    |          |          |     |     |    |         | -    |                 |    |   |        | 1/O<br>1/O |

| 79       A       23       SDQ<10>       I/O       54       AC 26       SDQ<40>       I/O       29       AF 4       CS4#       O       4       D 1       D<18>         256       C       24       VDDI       VDDI       235       AD 24       VDDI       VDDI       214       AD 3       VDDI       VDDI       193       C 3       VDDI         336       D       21       SDP7       I/O       317       AA 23       SDP2       I/O       298       AC 6       CS5#       O       279       F 4       DP6         77       A       25       VSS       VSS       52       AE 26       VSS       VSS       125       AE 3       VSS       VSS       102       C 2       VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | 1/O<br>1/O |

| 256         C         24         VDDI         VDDI         235         AD         24         VDDI         214         AD         3         VDDI         193         C         3         VDDI           336         D         21         SDP7         I/O         317         AA         23         SDP2         I/O         298         AC         6         CS5#         O         279         F         4         DP6           77         A         25         VSS         VSS         52         AE         26         VSS         VSS         125         AE         3         VSS         102         C         2         VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | 1/O        |

| 336         D         21         SDP7         I/O         317         AA         23         SDP2         I/O         298         AC         6         CS5#         O         279         F         4         DP6           77         A         25         VSS         VSS         52         AE         26         VSS         125         AE         3         VSS         102         C         2         VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |   |    |                    |      | -        |   |    |          |          |     |     |    |         |      |                 |    |   |        | VDDI       |

| 77 A 25 VSS VSS 52 AE 26 VSS VSS 125 AE 3 VSS VSS 102 C 2 VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | I/O        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |   |    |                    |      | -        |   |    |          |          |     |     |    |         | _    | -               |    |   | -      | VSS        |

| 258 C 22 SDQ<11> I/O 237 AB 24 SDQ<41> I/O 216 AD 5 ASI<0> O 195 E 3 D<19>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 258 | c | 22 | SDQ<11>            | 1/0  | 237      |   |    | SDQ<41>  | 1/0      | 216 | AD  | 5  | ASI<0>  | 0    | 195             | Ē  | 3 | D<19>\ | 1/0        |

| 172 B 23 SDQ<12> I/O 149 AC 25 SDQ<42> I/O 126 AE 4 ASI<1> O 103 D 2 D<20>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | I/O        |

| 78         A         24         SDQ<13>         I/O         53         AD         26         SDQ<43>         I/O         28         AF         3         ASI<2>         O         3         C         1         D<21>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |   |    |                    |      | -        |   |    |          |          |     |     |    |         |      |                 |    |   |        | I/O        |

| 335 D 22 SDP6 I/O 316 AB 23 VDDE VDDE 297 AC 5 ASI<3> O 278 E 4 DP5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |   |    |                    |      |          |   |    |          |          |     |     |    |         |      |                 |    |   |        | IO         |

| 257 C 23 SDQ<14> I/O 236 AC 24 SDQ<44> I/O 215 AD 4 NCTEST# I 194 D 3 D<22>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |   |    |                    |      |          |   |    |          |          |     |     |    |         | I    |                 |    |   |        | I/O        |

VDDI: VDD for Internal Logic ---- 2.5V VDDE: VDD for I/O Pad ------ 3.3V VDDP: VDD for built-in PLL ----- 2.5V

Note \*1) Pin 328 (NC) is reserved OUTPUT(SDC) MB86862.

Note \*2) Pin 302 (NC) is reserved INPUT (BLEN8#) for MB86861 and MB86862.

Note \*3) Pin 215 (NCTEST#) is changed to SDSEL# (input) for MB868661 and MB86862.

#### 1.9.3 Package Pin Assignment (Power, GND)

Figure 1.3 Package Pin Assignments

# 2. Programmers Model

### 2.1. ASI Assignments

MB86860 ASI assignments are as shown below.

|         | Table 2.1                                |

|---------|------------------------------------------|

| ASI     | Function                                 |

| 0h      | reserved                                 |

| 1h      | special regs.                            |

| 2h      | reserved                                 |

| 3h      | reserved for TLB probe                   |

| 4h      | internal regs. / user I/O *1             |

| 5h-6h   | reserved                                 |

| 7h      | user I/O regs.                           |

| 8h      | user inst.                               |

| 9h      | supervisor inst.                         |

| ah      | user data                                |

| bh      | supervisor data                          |

| ch      | I-Cache TAG diagnostic                   |

| dh      | I-Cache Set Diagnostic                   |

| eh-fh   | reserved                                 |

| 10h-14h | reserved (I-Cache/D-Cache line flush) *2 |

| 15h-17h | reserved                                 |

| 18h-1bh | I-Cache line flush                       |

| 1ch     | D-Cache TAG diagnostic                   |

| 1dh     | D-Cache Set diagnostic                   |

| 1eh-30h | reserve                                  |

| 31h     | Flush entire I-Cache/D-cache             |

| 32h-ffh | reserved                                 |

Note \*1) 0x0000000~0x7FFFFFF of ASI=4 is a USER area, and since 0x8000000~0xFFFFFFF is a reserved area it cannot be used. Note \*2) I-cache/D-cache line flush function is not implemented.

### 2.2. Register Overview

The following is an overview of the registers located in the SS200 memory spaces.

| ASI   | Address    | Register                                         |

|-------|------------|--------------------------------------------------|

| 0x01  | 0x00002004 | Sleep mode register                              |

| 0x01  | 0x0000FF00 | Instruction Address Descriptor Register1 (ADR1)  |

| 0x01  | 0x0000FF04 | Instruction Address Descriptor Register2 (ADR2)  |

| 0x01  | 0x0000FF18 | Debug Control Register (DCR)                     |

| 0x01  | 0x0000FF1C | Debug Status Register (DSR)                      |