#### ASSP CMOS

## **FUJITSU**

# SPARClite Series 32-Bit RISC Embedded Processor

#### **MB86833**

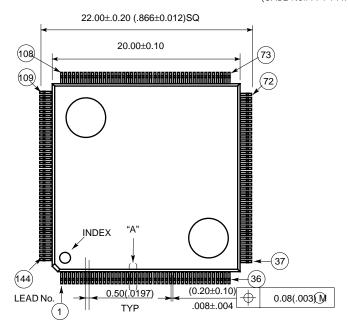

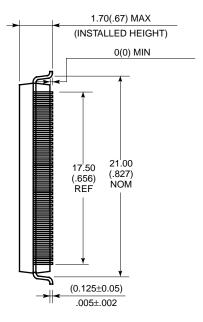

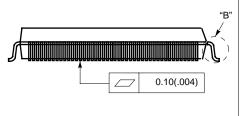

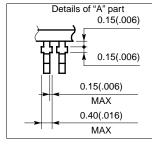

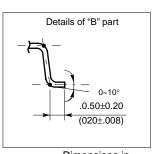

#### **Package**

- 144-pin, Plastic LQFP

- FPT-144-M08

#### Features

- 66 MHz CPU with on-chip clock multiplier

- SPARC high performance RISC architecture

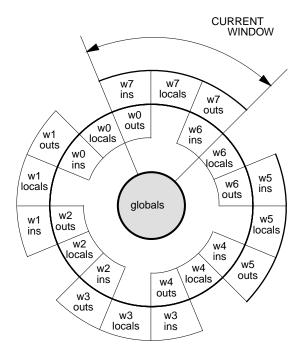

- 8 window, 136 word register file

- 16 address spaces, 256 Mbyte each

- Harvard-style separate on-chip instruction and data buses

- 1 Kbyte direct-mapped instruction cache

- 1 Kbyte direct-mapped data cache

- Flexible locking mechanism for data and instruction cache entries

- Option to force non-cached operation for memory areas selected by programmable chip selects; also qualification on a cycle-by-cycle basis using Non-Cache Pin

- Four-level buffered writes and one-level instruction prefetching

- CPU and core logic at up to 5 times the frequency of bus interface unit using on-chip clock multiplier (33 MHz maximum BIU frequency)

- Bus interface support for 8-, 16-, or 32-bit wide memory

- Support for burst mode cache fills

- DRAM controller with fast page or burst-mode EDO DRAM support

- Interrupt controller with fast response time and programmable priority

- Burst mode ROM support

- · Power-saving sleep mode with clock gear function

- Programmable address decoder and wait-state generator

- Single vector trapping

- 0.35 micron gate, 2-level metal CMOS technology, 3.3V internal with 3.3 or 5V I/O

#### **Table of Contents**

| General Discussion                            | 5  |

|-----------------------------------------------|----|

| Pin Configuration                             | 5  |

| Block Diagram of MB86833                      |    |

| Ordering Code                                 | £  |

| Pin Assignment – 144-pin LQFP                 |    |

| Signal Descriptions                           | 8  |

| Pin Status Description                        |    |

| Access Type                                   |    |

| Overview                                      | 13 |

| Key Features                                  | 13 |

| Sleep Mode                                    |    |

| MB86833 Instruction Set                       |    |

| CPU                                           |    |

| Address Space                                 |    |

| Registers                                     |    |

| Instruction Sets                              | 16 |

| Interrupt                                     | 16 |

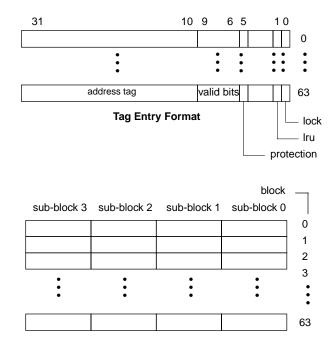

| Cache                                         |    |

| Bus Interface                                 | 18 |

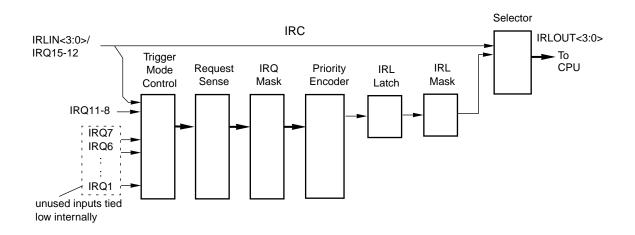

| Interrupt Controller                          | 18 |

| Interrupt Trigger Modes                       | 18 |

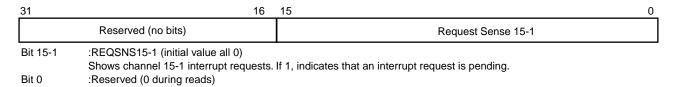

| Request Sense Register (Read only)            | 19 |

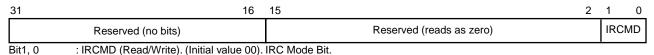

| IRC Mode Register                             | 19 |

| Interrupt Controller Modes                    | 19 |

| Interrupt Controller Operation                |    |

| Clock Generator                               | 20 |

| Clock Multiplication Factor                   | 20 |

| Clock Gear                                    | 21 |

| Internal Clock Control/Status (ICCS) Register | 21 |

| Changing the Clock Multiplication Factor      |    |

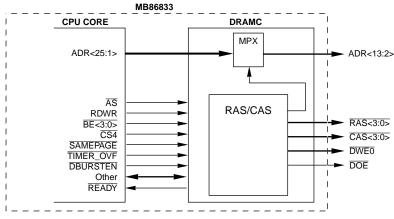

| DRAM Controller                               |    |

| Programmable Chip Select                      |    |

| Use of Chip Select                            |    |

| <u>CS0</u>                                    |    |

| CS1 and CS2                                   |    |

| <del>CS3</del>                                |    |

| <u>CS4</u>                                    |    |

| <u>CS5</u>                                    |    |

| Idle Cycle Insertion Function                      | 22  |

|----------------------------------------------------|-----|

| IDLEEN Pin Tied Low                                | 22  |

| IDLEEN Pin Tied High                               | 22  |

| Idle Cycle Insertion Function                      |     |

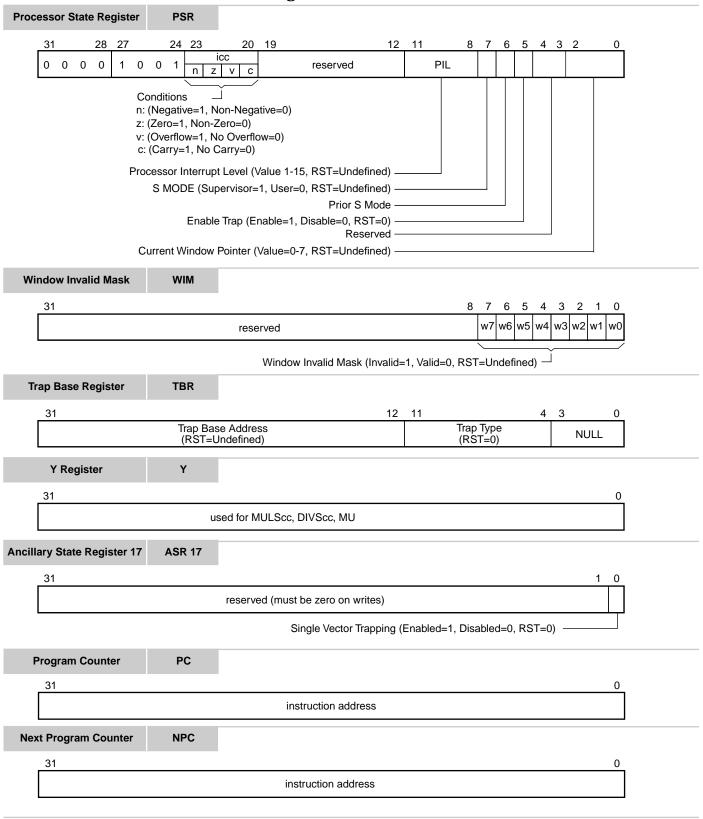

| MB86833 Control and Status Registers—Read/Write    | 24  |

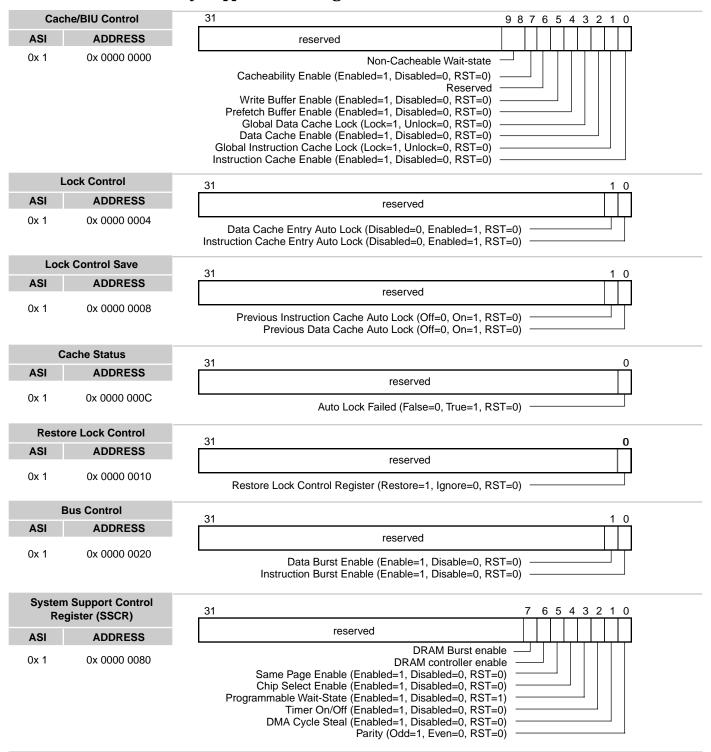

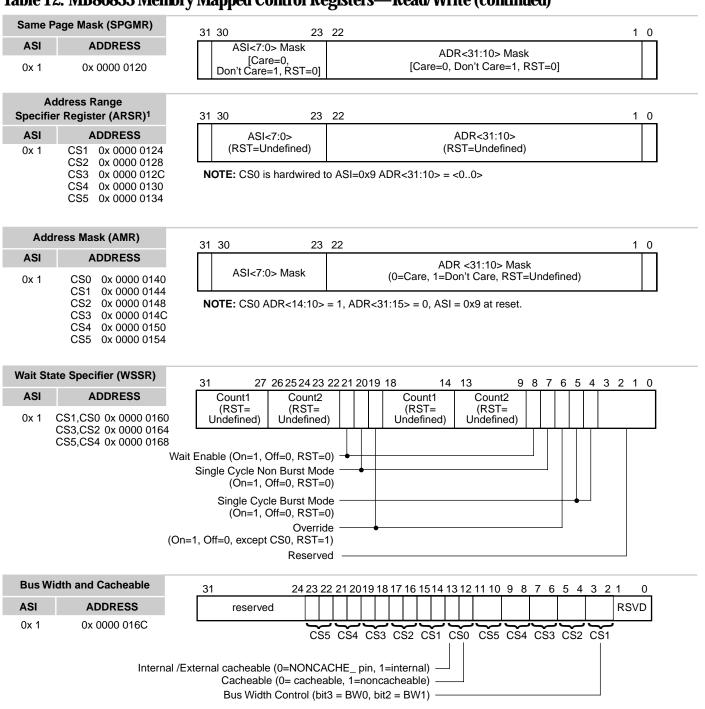

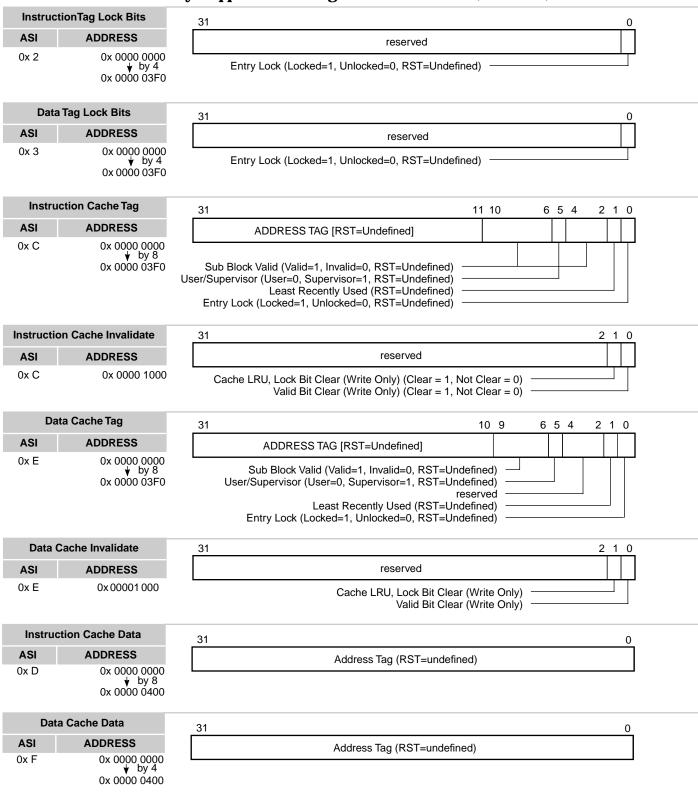

| MB86833 Memory Mapped Control Registers—Read/Write | 25  |

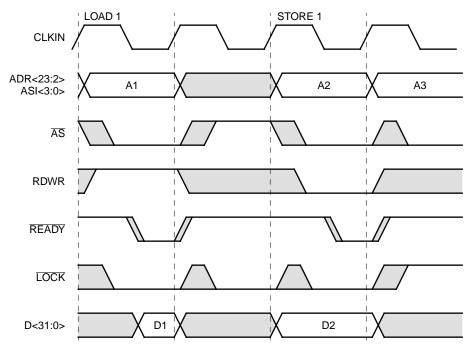

| Bus Operation                                      | 31  |

| Operation of the BIU                               | 31  |

| Exception Handling                                 | 31  |

| Bus Cycles                                         | 31  |

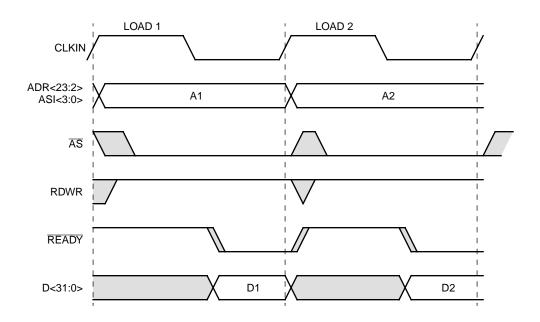

| Load                                               | 31  |

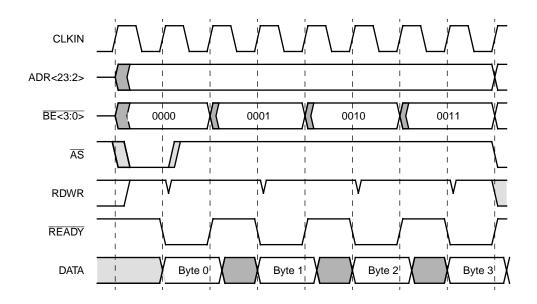

| Load (32-bit bus width)                            | 31  |

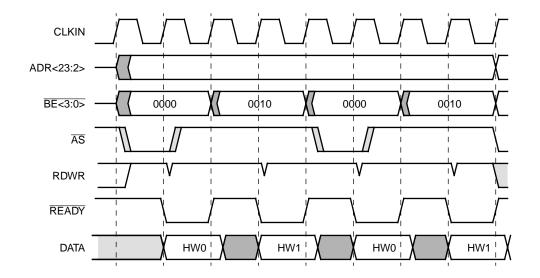

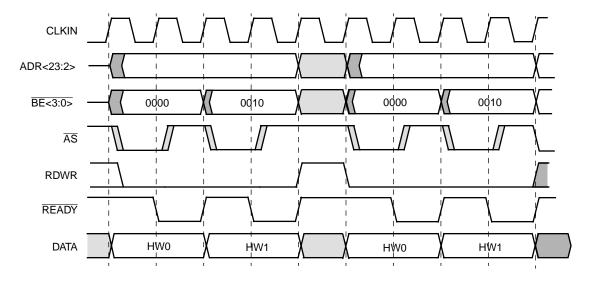

| Load (16-bit bus width)                            | 32  |

| Load (8-bit wide bus)                              | 32  |

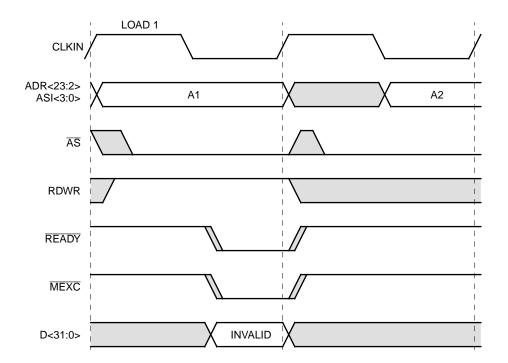

| Load with Exception                                | 32  |

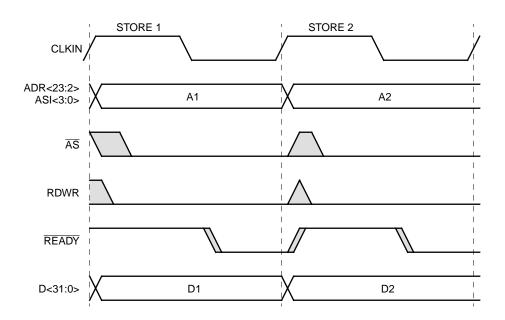

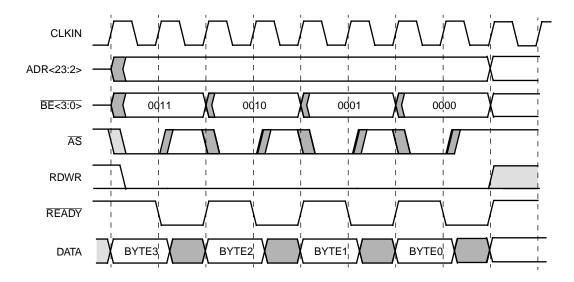

| Store                                              | 32  |

| Store (32-bit bus width)                           | 32  |

| Store (16-bit wide bus)                            | 32  |

| Store (8-bit wide bus)                             | 32  |

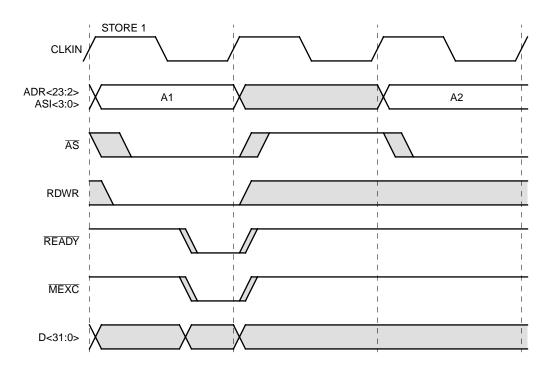

| Store with Exception                               | 32  |

| Atomic Load Store                                  | 32  |

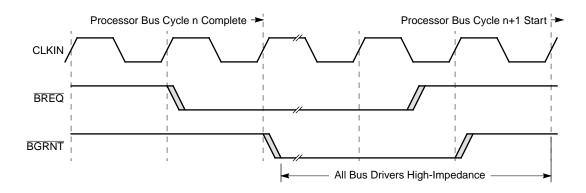

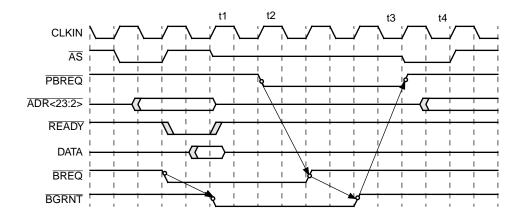

| External Bus Request and Grant                     | 32  |

| 8- and 16-Bit Bus Modes                            |     |

| Bus Width Control of CSO                           | 33  |

| Bus Width Control Bits of CS1 to CS5               |     |

| Burst Mode Transactions                            | 33  |

| ADR<3:2> Sequence in Burst Mode                    | 33  |

| Selection of Hyperpage Mode (EDO Mode)             | 33  |

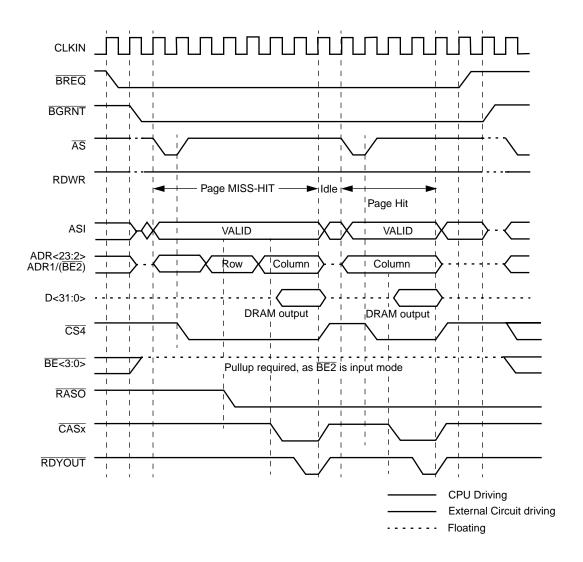

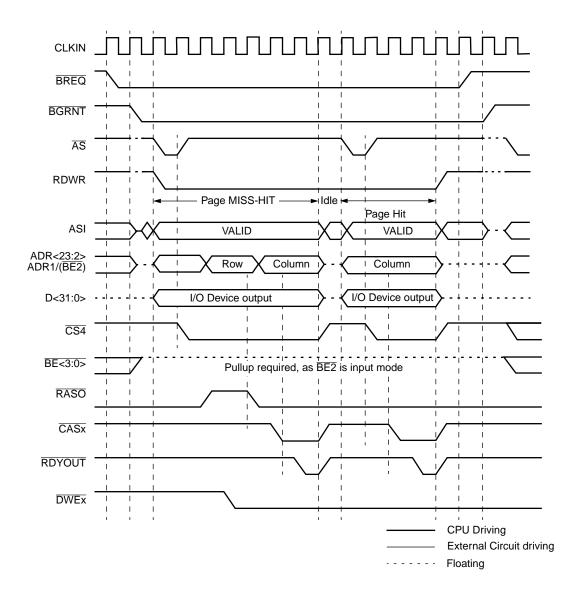

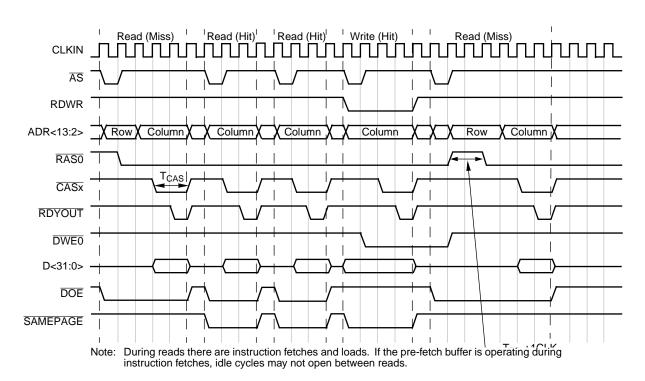

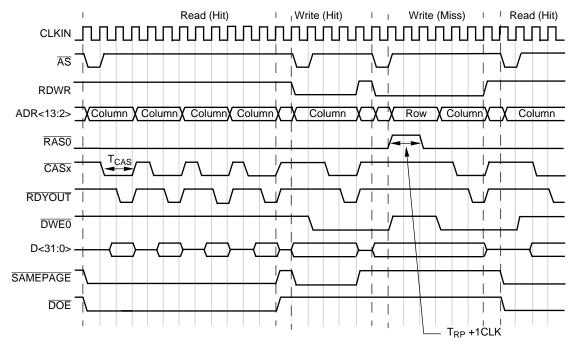

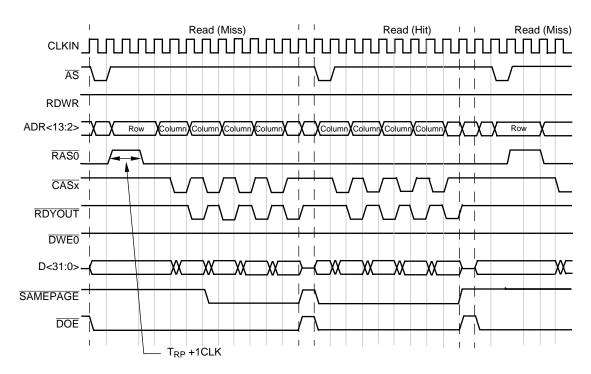

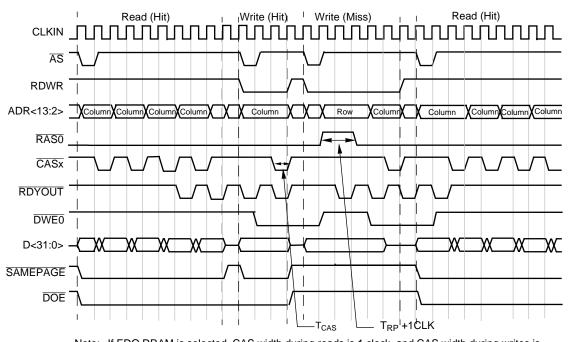

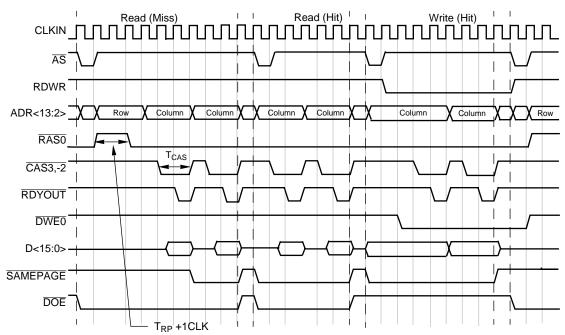

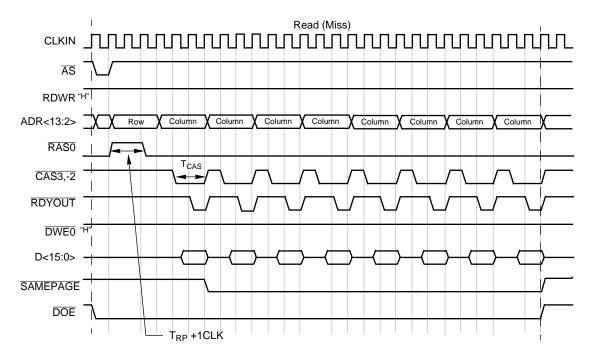

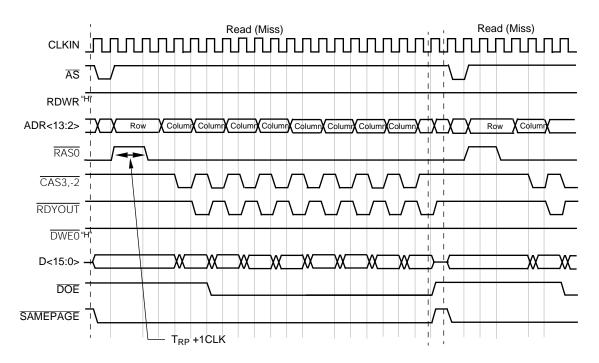

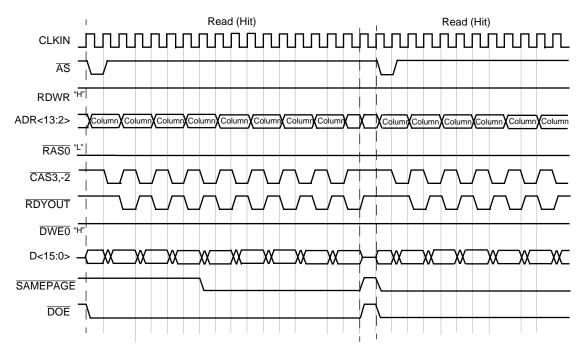

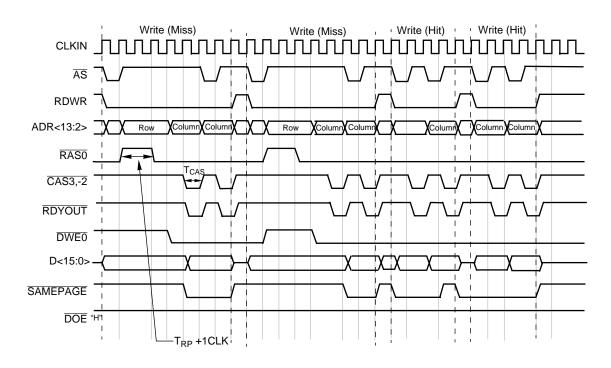

| Basic DRAM Access Timing                           | 34  |

| DRAM Access Timing:                                | 34  |

| Electrical Characteristics                         | 47  |

| Absolute Maximum Ratings                           | 47  |

| Recommended Operating Conditions                   | 47  |

| DC Characteristics                                 | 48  |

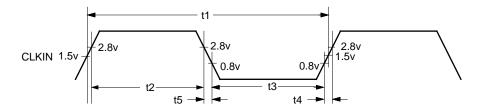

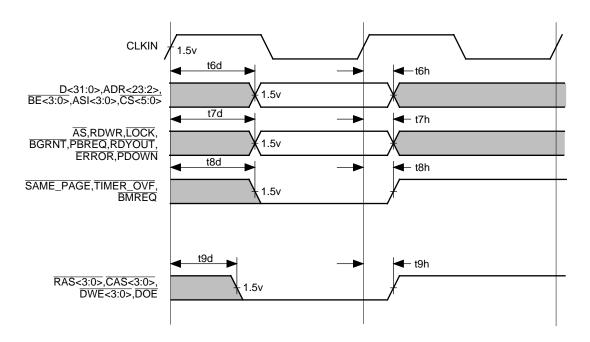

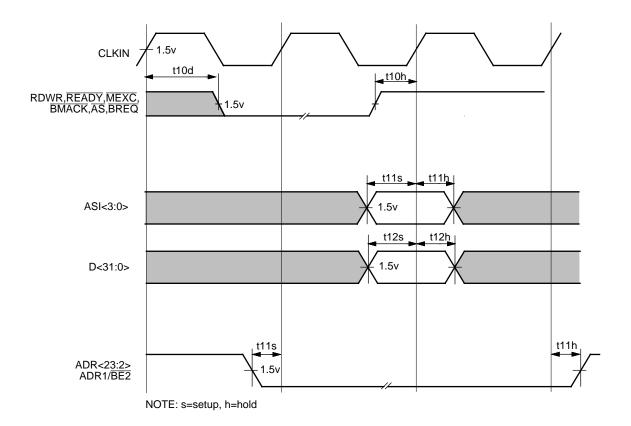

| AC Characteristics                                 | 49  |

| Exterior Dackage Drawing                           | 5.1 |

#### **General Discussion**

The MB86833 is a member of the MB8683X series of RISC processors which offers high performance and high integration for a wide range of embedded applications. The processor is based on the SPARC architecture and is upward code-compatible with previous implementations. At 66 MHz, the processor runs at up to 66 MIPS.

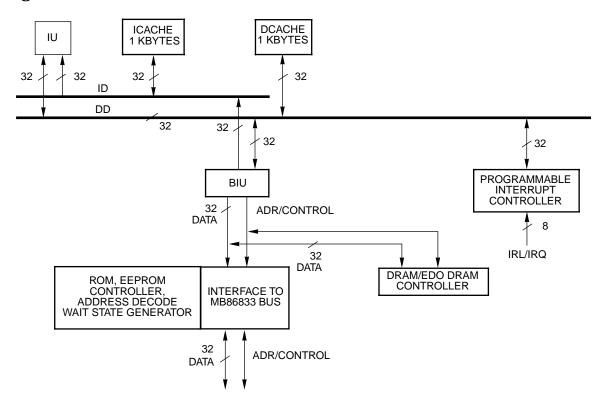

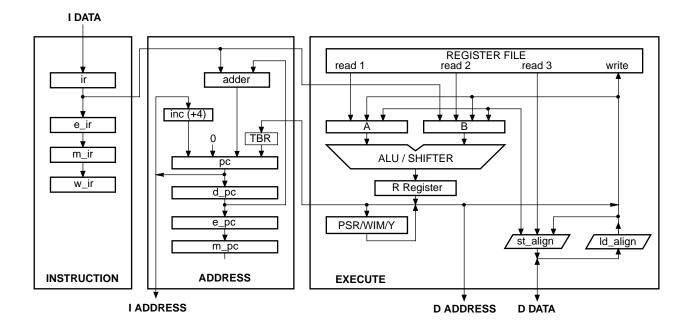

The MB86833 is housed in a low-profile 144-pin plastic package. The on-chip data and instruction caches help decouple the processor from external memory latency. Separate on-chip instruction and data paths provide a high-bandwidth interface between the integer unit (IU) and caches.

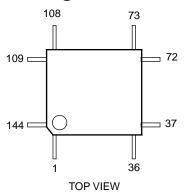

#### **Pin Configuration**

For maximum performance with a minimum of glue logic, the MB86833 includes: programmable chip select outputs and wait state generation, built-in support for page-mode DRAM, EDO DRAM, and page-mode EEPROM, and support for 8 and 16 and 32-bit memory. These features combine to give the MB86833 high integration and high performance, with the flexibility and efficiency to make it the ideal choice for a wide variety of low cost, embedded systems.

#### **Block Diagram of MB86833**

**Table 1. Ordering Code**

| Clock Frequency (MHz) | Ordering Code | Package Type     |

|-----------------------|---------------|------------------|

| 66                    | MB86833PFV-G  | Plastic LQFP 144 |

Note: The ordering code for production level product. Early shipments of this device may be marked with "ES" to indicate that the part is not yet at full production status.

Table 2. Pin Assignment – 144-pin LQFP

| Pin<br>No. | I/O | Pin Name | Pin<br>No. | I/O | Pin Name  | Pin<br>No. | I/O | Pin Name   | Pin<br>No. | 1/0 | Pin Name     |

|------------|-----|----------|------------|-----|-----------|------------|-----|------------|------------|-----|--------------|

| 1          |     | VDD      | 37         |     | VDD       | 73         |     | VDD        | 109        |     | VDD          |

| 2          | ı   | BMODE16  | 38         | 1/0 | D2        | 74         | 0   | BE3 / ADRO | 110        | I   | MEXC         |

| 3          | I/O | D28      | 39         | I/O | D1        | 75         | I/O | BE2 / ADR1 | 111        | I/O | ADR23        |

| 4          | I/O | D27      | 40         | 1/0 | D0        | 76         | 0   | BE1        | 112        | I/O | ASI3 / ADR24 |

| 5          | I/O | D26      | 41         | 0   | DWE0      | 77         | 0   | BE0        | 113        | I/O | ASI2 / ADR25 |

| 6          | I/O | D25      | 42         | 0   | RAS0      | 78         | N/A | N.C.       | 114        | I/O | ASI1 / ADR26 |

| 7          | I/O | D24      | 43         | 0   | CAS0      | 79         | N/A | N.C.       | 115        | I/O | ASIO / ADR27 |

| 8          | I/O | D23      | 44         | 0   | CAS1      | 80         | I   | NONCACHE   | 116        | I   | IRL3 / IRQ15 |

| 9          |     | VSS      | 45         |     | VSS       | 81         |     | VSS        | 117        |     | VSS          |

| 10         | I/O | D22      | 46         | 0   | CAS2      | 82         | 1/0 | ADR2       | 118        | I   | IRL2 / IRQ14 |

| 11         | I/O | D21      | 47         | 0   | CAS3      | 83         | 1/0 | ADR3       | 119        | I   | IRL1 / IRQ13 |

| 12         | I/O | D20      | 48         | 0   | DOE       | 84         | 1/0 | ADR4       | 120        | I   | IRL0 / IRQ12 |

| 13         | I/O | D19      | 49         | 0   | ERROR     | 85         | 1/0 | ADR5       | 121        | I   | FLOAT        |

| 14         | I/O | D18      | 50         | 0   | LOCK      | 86         | 1/0 | ADR6       | 122        | 0   | PDOWN        |

| 15         | 1/0 | D17      | 51         | I   | CTEST     | 87         | 1/0 | ADR7       | 123        | I   | WKUP         |

| 16         | 1/0 | D16      | 52         | I   | BREQ      | 88         | 1/0 | ADR8       | 124        | I   | RESET        |

| 17         | I   | BTEST    | 53         | 0   | PBREQ     | 89         | I/O | ADR9       | 125        | I   | IDLEEN       |

| 18         |     | IO_VDD   | 54         |     | IO_VDD    | 90         |     | IO_VDD     | 126        |     | IO_VDD       |

| 19         |     | VSS      | 55         |     | VSS       | 91         |     | VSS        | 127        |     | VSS          |

| 20         | 1/0 | D15      | 56         | 0   | BGRNT     | 92         | I/O | ADR10      | 128        | I   | CLKSEL2      |

| 21         | I/O | D14      | 57         | I   | BMACK     | 93         | I/O | ADR11      | 129        | I   | CLKSEL1      |

| 22         | I/O | D13      | 58         | 0   | BMREQ     | 94         | I/O | ADR12      | 130        | I   | CLKSEL0      |

| 23         | I/O | D12      | 59         | 0   | TIMER_OVF | 95         | I/O | ADR13      | 131        | I   | CLKEXT       |

| 24         | I/O | D11      | 60         | 0   | SAMEPAGE  | 96         | I/O | ADR14      | 132        | I   | CLKIN        |

| 25         | 1/0 | D10      | 61         | I/O | ĀS        | 97         | 1/0 | ADR15      | 133        | I   | IRQ11        |

| 26         | 1/0 | D9       | 62         | I/O | RDWR      | 98         | I/O | ADR16      | 134        | I   | IRQ10        |

| 27         | I/O | D8       | 63         | 0   | RDYOUT    | 99         | I/O | ADR17      | 135        | I   | IRQ9         |

| 28         | I   | BMODE8   | 64         | 0   | CS5       | 100        | I   | READY      | 136        | I   | IRQ8         |

| 29         |     | VDD      | 65         |     | VDD       | 101        |     | VDD        | 137        |     | VDD          |

| 30         |     | VSS      | 66         |     | VSS       | 102        |     | VSS        | 138        |     | VSS          |

| 31         | I/O | D7       | 67         | 0   | CS4       | 103        | 1/0 | ADR18      | 139        | N/A | N.C.         |

| 32         | I/O | D6       | 68         | 0   | CS3       | 104        | I/O | ADR19      | 140        | I   | ASISEL       |

| 33         | I/O | D5       | 69         | 0   | CS2       | 105        | I/O | ADR20      | 141        | 1/0 | D31          |

| 34         | I/O | D4       | 70         | 0   | CS1       | 106        | I/O | ADR21      | 142        | 1/0 | D30          |

| 35         | I/O | D3       | 71         | 0   | CS0       | 107        | I/O | ADR22      | 143        | 1/0 | D29          |

| 36         |     | IO_VDD   | 72         |     | IO_VDD    | 108        |     | IO_VDD     | 144        |     | IO_VDD       |

<sup>\*</sup> These inputs have a 50K  $\Omega$  internal pullup resistor.

#### **Table 3. Signal Descriptions**

| Symbol                                 | Туре |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | Des                 | scription             |                        |                            |

|----------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|-----------------------|------------------------|----------------------------|

| CLKIN                                  | ı    | <b>CLOCK:</b> The clock input pin. The clock is the timebase for the operation of the bus interface unit (BIU). An on-chip clock multiplier allows the CPU and core logic to run at integer multiples of the clock frequency $(\times 1, \times 2, \times 3, \times 4, \text{ or } \times 5)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |                     |                       |                        |                            |

| CLKEXT                                 | I    | <b>EXTERNAL CLOCK BYPASS:</b> The external clock selection pin. If tied low, the clock is generated by the internal PLL/clock multiplier. If tied high, the external clock (i.e., the signal on CLKIN) is used without modification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                     |                       |                        |                            |

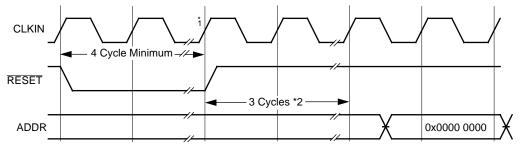

| RESET                                  | I    | <b>SYSTEM RESET:</b> The reset input. The CPU and core logic are initialized by pulsing this input low. The clock must be stable for 100 ms before the reset pulse is de-asserted. The reset pulse must be a minimum of four CLKIN cycles in length. The CPU begins execution at location 0 three CLKIN cycles after the reset pulse is de-asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |                     |                       |                        |                            |

|                                        |      | INTERNAL CLOCK SELECT: Th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ese pins select t | the clock frequenc  | y multiplier, as des  | cribed in the table be | elow.                      |

|                                        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CLKSEL2           | CLKSEL1             | CLKSEL0               | Internal Clock         |                            |

|                                        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                 | L                   | L                     | x1                     |                            |

| LKSEL0                                 | ,    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                 | L                   | Н                     | x2                     |                            |

| LKSEL1<br>LKSEL2                       | 1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                 | Н                   | L                     | х3                     |                            |

| ENGLEZ                                 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                 | Н                   | Н                     | x4                     |                            |

|                                        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L                 | Н                   | Н                     | x5                     |                            |

|                                        |      | Note: CLKSEL0 and CLKSEL1 and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | d CLKSEL2 do n    | ot have internal pu | ıllup resistors, so t | hey must be tied high  | n or low.                  |

| TEST                                   | I    | CTEST BTEST: Test pins. Must be tied high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |                     |                       |                        |                            |

| .DR<23:2><br>.SI<3:0>/<br>.DR<24:27>   | 1/0  | ADDRESS BUS: The 26-bit address bus ADR<23:2> references a 32-bit word. ADR1 and ADR0 are generated for 8- and 16-bit bus width transactions and are driven on the byte enables BE2 and BE3. The address is not valid during idle cycles. During bus grant mode, the address bus becomes an input, and it is used by the CS generator circuit and on-chip core logic. When ADR<23:2> is driven in this mode, ADR<31:28> are treated as 0 internally. If the DRAM controller is enabled, it multiplexes row and column addresses and drives them on ADR<13:2>.  ADDRESS SPACE IDENTIFIER: The address space identifier (ASI) selects one of 16 separate address spaces referenced by the address bus. These spaces distinguish between user and supervisor space, instruction and data space, memory and peripheral control registers, and other addressable areas. When ASISEL is high these pins are ASI<3:0>, while when ASISEL is low these pins are ADR<24:27>. The timing is identical to ADR<23:2>. The ASI signals become inputs during bus grant mode when ASISEL is taken low. This is used for CS generation and internal address |                   |                     |                       |                        |                            |

|                                        |      | decoding. In this mode, ASI<7:4> ASI SELECT SIGNAL: In bus gra This pin has a pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |                     |                       | 112 through 115 driv   | ve ASI<3:0> or ADR<24:27>. |

| ASISEL                                 | ,    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ASISE             | L AS                | I<3:0> / ADR <2       | 4:27>                  |                            |

| SISEE                                  | '    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | L                 |                     | ADR <28:31>           |                        |                            |

|                                        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Н                 |                     | ASI <3:0>             |                        |                            |

| <u>45</u>                              | 1/0  | ADDRESS STROBE: A one-cycle low pulse is driven on $\overline{AS}$ during the first clock of the bus cycle. The bus cycle starts with assertion of $\overline{AS}$ and ends with assertion of $\overline{READY}$ or $\overline{RDYOUT}$ . The $\overline{AS}$ signal is an input during bus grant mode and is used as an activation signal for CS generator circuits and wait-state generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |                     |                       |                        |                            |

| CS0<br>CS1<br>CS2<br>CS3<br>CS4<br>CS5 | 0    | CHIP SELECT: The chip select signals are asserted if the address ranges indicated in the Address Range Specifier Register (ARSR) and the Address Mask Register (ARSR) are referenced with the System Support Control Register (SSCR) CS enable bit (bit 4) set. An exception is CSO (i.e. the boot ROM chip select), which has no Address Range Specifier Register and is always enabled. Each address range has a corresponding wait specifier which is used to automatically assert the READY signal after a user defined number of processor clocks. This allows a variety of memory and I/O devices with different access times to be connected to the processor without the need for additional logic.                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |                     |                       |                        |                            |

| D<31:0>                                | 1/0  | <b>DATA BUS:</b> This is the 32-bit data bus. It is a bidirectional data bus used for instruction fetch, data reads, and data writes. Instruction and word data must be aligned to 32-bit boundaries, and half words must be aligned to even addresses. Double words must be aligned to addresses which are multiples of 8. In 8-bit bus mode D<7:0> is used, and in 16-bit bus mode D<15:0> is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   |                     |                       |                        |                            |

#### Table 3. Signal Descriptions (Continued)

| Symbol    | Туре |                                                                                                                                                          |                                                                                                                    |                                                                       | Description                                                                                                                                                                                                                    |                                                                                                |                                                                                                                                       |

|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

|           |      | bus width. When 8-bit bus<br>BE2 is driven with ADR1. I                                                                                                  | width is used, BE<br>BE<3:0> are valid o                                                                           | 2 and BE3 aduring the b                                               | when 32-bit bus width is used. Durare driven with ADR1 and ADR0, resus cycle period. During idle cycles be enabled, and $\overline{\text{BE2}}$ becomes the A                                                                  | spectively. When 16-bi<br>, the output is undefine                                             | It bus width is used, ed. During bus grant, the byte                                                                                  |

|           |      |                                                                                                                                                          | Bus Width                                                                                                          |                                                                       | Access Type                                                                                                                                                                                                                    | BE0,1,2,3                                                                                      |                                                                                                                                       |

|           |      |                                                                                                                                                          | 32-bit                                                                                                             | Write                                                                 | Byte 0 (D<31:24>) *1                                                                                                                                                                                                           | 0111                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Byte 1 (D<23:16>)                                                                                                                                                                                                              | 1011                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Byte 2 (D<15:8>)                                                                                                                                                                                                               | 1101                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Byte 3 (D<7:0>)                                                                                                                                                                                                                | 1110                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Half Word 0 (D<31:16>)                                                                                                                                                                                                         | 0011                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Half Word 1 (D<15:0>)                                                                                                                                                                                                          | 1100                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Word                                                                                                                                                                                                                           | 0000                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    | Read                                                                  | All data types                                                                                                                                                                                                                 | 0000                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          | 16-bit                                                                                                             | Write                                                                 | Byte 0 (D<15:8>)                                                                                                                                                                                                               | 1000                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Byte 1 (D<7:0>)                                                                                                                                                                                                                | 0100                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Byte 2 (D<15:8>)                                                                                                                                                                                                               | 1010                                                                                           |                                                                                                                                       |

| E0        | 0    |                                                                                                                                                          |                                                                                                                    |                                                                       | Byte 3 (D<7:0>)                                                                                                                                                                                                                | 0110                                                                                           |                                                                                                                                       |

| EU        | 0    |                                                                                                                                                          |                                                                                                                    |                                                                       | Half Word 0 (D<15:0>)                                                                                                                                                                                                          | 0000                                                                                           |                                                                                                                                       |

| <u>E1</u> | 0    |                                                                                                                                                          |                                                                                                                    |                                                                       | Half Word 1 (D<15:0>)                                                                                                                                                                                                          | 0010                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Word (D<15:0>) Access 0                                                                                                                                                                                                        | 0010                                                                                           |                                                                                                                                       |

| E2/ADR1   | I/O  |                                                                                                                                                          |                                                                                                                    | L                                                                     | Word (D<15:0>) Access 1                                                                                                                                                                                                        | 0000                                                                                           |                                                                                                                                       |

| _         |      |                                                                                                                                                          |                                                                                                                    | Read                                                                  | Access 0                                                                                                                                                                                                                       | 0000                                                                                           |                                                                                                                                       |

| E3/ADR0   | 0    |                                                                                                                                                          | 0.1.1                                                                                                              | \A/-!+-                                                               | Access 1                                                                                                                                                                                                                       | 0010                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          | 8-bit                                                                                                              | Write                                                                 | Byte 0                                                                                                                                                                                                                         | XX00                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Byte 1                                                                                                                                                                                                                         | XX01                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Byte 2                                                                                                                                                                                                                         | XX10<br>XX11                                                                                   |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Byte 3                                                                                                                                                                                                                         |                                                                                                |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Half Word 0 Access 0 Half Word 0 Access 1                                                                                                                                                                                      | XX11<br>XX10                                                                                   |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Half Word 1 Access 0                                                                                                                                                                                                           | XX10<br>XX01                                                                                   |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Half Word 1 Access 1                                                                                                                                                                                                           | XX00                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Word Access 0                                                                                                                                                                                                                  | XX11                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Word Access 1                                                                                                                                                                                                                  | XX10                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Word Access 2                                                                                                                                                                                                                  | XX01                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Word Access 3                                                                                                                                                                                                                  | XX00                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    | Read                                                                  | Access 0                                                                                                                                                                                                                       | XX00                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Access 1                                                                                                                                                                                                                       | XX01                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Access 2                                                                                                                                                                                                                       | XX10                                                                                           |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | Access 3                                                                                                                                                                                                                       | XX11                                                                                           |                                                                                                                                       |

|           |      | *Notation such as (D<31:2                                                                                                                                | 24>) shows the data                                                                                                | a bus bits b                                                          | eing used.                                                                                                                                                                                                                     |                                                                                                |                                                                                                                                       |

|           |      |                                                                                                                                                          |                                                                                                                    |                                                                       | w during write cycles and high duri                                                                                                                                                                                            | ng read cycles and idle                                                                        | e cycles. It is an input during b                                                                                                     |

| DWR       | I/O  |                                                                                                                                                          | for generating DW                                                                                                  |                                                                       | when the DRAM controller is enab                                                                                                                                                                                               |                                                                                                |                                                                                                                                       |

| READY     | I    | pleted and that it is ready to<br>value on the data bus at the<br>when the appropriate acce<br>In most cases, no addition<br>address of the current tran | to start with the next<br>e rising edge of CL<br>ss time has been n<br>al logic is required<br>saction. The extern | kt bus trans<br>.K_IN follow<br>net.<br>I to generate<br>nal system c | by the external memory system to in action in the following cycle. In case wing the assertion of READY. For the tethe READY signal. On-chip circuits an override the internal ready general burst transfer or when multiple bu | e of a fetch from memore case of a write, the metry can be programmed rator to terminate the c | ory, the processor will strobe t<br>lemory system will assert REAI<br>d to assert READY based on th<br>current bus cycle early. READY |

#### Table 3. Signal Descriptions (Continued)

| Symbol                                                                                 | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDYOUT                                                                                 | 0    | READY OUTPUT: Assertions of the READY signal generated by any source, including the internal wait state generator, are visible to external devices on this pin. Internally generated READY assertions are synchronized to the clock. Externally generated READY assertions will appear on this signal with a small amount of propagation delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |