#### FUJITSU MICROELECTRONICS CONTROLLER MANUAL

## F<sup>2</sup>MC-16LX 16-BIT MICROCONTROLLER PROGRAMMING MANUAL

## F<sup>2</sup>MC-16LX

# 16-BIT MICROCONTROLLER PROGRAMMING MANUAL

FUJITSU MICROELECTRONICS LIMITED

### PREFACE

#### Objectives and Intended Readership

The  $F^2MC-16LX$  series products are original 16-bit one-chip microcontrollers that support application specific ICs (ASICs). They are suitable for use in various types of industrial equipment, office-automation equipment, on-vehicle equipment, and other equipment that is required to operate at high speed in real-time mode.

Note: F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

#### Trademark

The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

#### Configuration of this Manual

This manual contains the following 9 chapters and appendix.

## CHAPTER 1 OVERVIEW OF THE F<sup>2</sup>MC-16LX CPU CORE AND SAMPLE CONFIGURATION INCLUDING IT

This chapter briefly describes the configuration of the  $F^2MC-16LX$  CPU core, and presents a sample configuration of a device incorporating it.

#### **CHAPTER 2 MEMORY SPACE**

This chapter describes the memory spaces of the  $F^2MC-16LX$  CPU.

#### **CHAPTER 3 DEDICATED REGISTERS**

This chapter describes the dedicated registers of the F<sup>2</sup>MC-16LX CPU.

#### **CHAPTER 4 GENERAL-PURPOSE REGISTERS**

This chapter describes the general-purpose registers of the F<sup>2</sup>MC-16LX CPU.

#### **CHAPTER 5 PREFIX CODES**

The operation of an instruction can be modified by prefixing it with prefix code. This chapter explains the prefix codes.

#### **CHAPTER 6 INTERRUPT HANDLING**

This chapter describes the  $F^2MC$ -16LX interrupt handling functions and their operations.

#### **CHAPTER 7 ADDRESSING**

This chapter explains the addressing mode for each instruction of the  $F^2MC-16LX$ .

#### **CHAPTER 8 INSTRUCTION OVERVIEW**

This chapter explains the meanings of items and symbols used in explanations in "CHAPTER 9 DETAILED EXECUTION INSTRUCTIONS".

#### **CHAPTER 9 DETAILED EXECUTION INSTRUCTIONS**

This chapter describes each execution instruction used in the assembler in a reference format.

#### APPENDIX

The appendix section includes lists of instructions used in the  $F^2MC-16LX$ , as well as the related instruction maps.

#### References

The following manuals should be referred along with this manual:

- F<sup>2</sup>MC-16LX/16L/16/16H/16F Assembler Manual

- F<sup>2</sup>MC-16LX Model-Specific Hardware Manual

• The contents of this document are subject to change without notice.

- Customers are advised to consult with sales representatives before ordering.

- The information, such as descriptions of function and application circuit examples, in this document are presented solely for the

purpose of reference to show examples of operations and uses of FUJITSU MICROELECTRONICS device; FUJITSU

MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When

you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of

such use of the information. FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of

the use of the information.

- Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of

the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU

MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any thirdparty's intellectual property right or other right by using such information. FUJITSU MICROELECTRONICS assumes no

liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of

information contained herein.

- The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- Exportation/release of any products described in this document may require necessary procedures in accordance with the regulations of the Foreign Exchange and Foreign Trade Control Law of Japan and/or US export control laws.

- The company names and brand names herein are the trademarks or registered trademarks of their respective owners.

Copyright ©1998-2008 FUJITSU MICROELECTRONICS LIMITED All rights reserved.

## **READING THIS MANUAL**

#### Page Layout

In this manual, an entire section is presented on a single page or spread whenever possible. You can thus view a section without having to flip pages.

The content of each section is summarized immediately below the title. You can obtain a rough overview of this product by reading through these summaries.

Also, higher level section headings are given in lower sections so that you can know to which section the text your are currently reading belongs.

## CONTENTS

| CHAPT | FER 1              | OVERVIEW OF THE F <sup>2</sup> MC-16LX CPU CORE AND SAMPLE       | 1<br>1<br>1 |

|-------|--------------------|------------------------------------------------------------------|-------------|

|       |                    | CONFIGURATION INCLUDING IT                                       | 1           |

| 1.1   | Overvi             | iew of the F <sup>2</sup> MC-16LX CPU Core                       | 2           |

| 1.2   | Sampl              | e Configuration of an F <sup>2</sup> MC-16LX Device              | 3           |

| СНАРТ | FER 2              | MEMORY SPACE                                                     | 5           |

| 2.1   |                    | lemory Space                                                     | 6           |

| 2.2   | Linear             | Addressing Mode                                                  | 7           |

| 2.3   | Bank /             | Addressing Mode                                                  |             |

| 2.4   | Memo               | ry Space Divided into Banks and Value in Each Bank Register      | 11          |

| 2.5   | Data C             | Configuration of and Access to Multi-byte Data in Memory         | 12          |

| CHAPT | FER 3              | DEDICATED REGISTERS                                              | 15          |

| 3.1   | F <sup>2</sup> MC- | 16LX Dedicated Register Types                                    | 16          |

| 3.2   | Accum              | nulator (A)                                                      | 18          |

| 3.3   | User S             | Stack Pointer (USP) and System Stack Pointer (SSP)               | 20          |

| 3.4   | Proces             | ssor Status (PS)                                                 | 22          |

| 3.4.  | 1 Inte             | errupt Level Mask Register (ILM)                                 | 23          |

| 3.4.  | 2 Re               | gister Bank Pointer (RP)                                         | 24          |

| 3.4.  | 3 Co               | ndition Code Register (CCR)                                      | 25          |

| 3.5   | Progra             | am Counter (PC)                                                  | 26          |

| 3.6   | Direct             | Page Register (DPR)                                              | 27          |

| 3.7   | Bank I             | Registers                                                        | 28          |

| CHAPT | FER 4              | GENERAL-PURPOSE REGISTERS                                        | 29          |

| 4.1   | Regist             | er Banks in RAM                                                  | 30          |

| 4.2   | Calling            | g General-purpose Registers in RAM                               | 31          |

| СНАРТ | FER 5              | PREFIX CODES                                                     | 33          |

| 5.1   | Bank S             | Select Prefix                                                    | 34          |

| 5.2   | Comm               | on Register Bank Prefix (CMR)                                    | 36          |

| 5.3   | Flag C             | Change Inhibit Prefix Code (NCC)                                 | 37          |

| 5.4   | -                  | raints Related to the Prefix Codes                               |             |

| СНАРТ | FER 6              | INTERRUPT HANDLING                                               | 41          |

| 6.1   | Interru            | pt Handling                                                      | 42          |

| 6.2   | Hardw              | are Interrupt Operation Flow                                     | 44          |

| 6.3   | Interru            | pt Handling Flowchart and Saving the Contents of Registers       | 45          |

| 6.4   | Interru            | pt Vectors                                                       | 47          |

| 6.5   |                    | ded Intelligent I/O Service                                      |             |

| 6.5.  | 1 Flo              | wchart of Extended lintelligent I/O Service Operation            | 50          |

| 6.5.  | 2 Flo              | wchart of Extended Intelligent I/O Service Application Procedure | 51          |

| 6.6   | Interru            | pt Control Register (ICR)                                        | 52          |

| 6.7            | Meanings of the Bits of Interrupt Control Register (ICR)                               | . 53 |

|----------------|----------------------------------------------------------------------------------------|------|

| 6.8            | Extended Intelligent I/O Service Descriptor (ISD)                                      | . 55 |

| 6.9            | Registers of Extended Intelligent I/O Service Descriptor                               | . 56 |

| 6.10           | Exception Processing                                                                   | . 58 |

| СНАРТ          | ER 7 ADDRESSING                                                                        | 59   |

| 7.1            | Effective Address Field                                                                | . 60 |

| 7.2            | Direct Addressing                                                                      | . 61 |

| 7.3            | Indirect Addressing                                                                    | . 63 |

| СНАРТ          | ER 8 INSTRUCTION OVERVIEW                                                              | 67   |

| 8.1            | Instruction Overview                                                                   | . 68 |

| 8.2            | Symbols (Abbreviations) Used in Detailed Execution Instructions                        | . 70 |

| 8.3            | Effective Address Field                                                                | . 72 |

| 8.4            | Execution Cycles                                                                       | . 73 |

| СНАРТ          | ER 9 DETAILED EXECUTION INSTRUCTIONS                                                   | 77   |

| 9.1            | Detailed Execution Instructions                                                        |      |

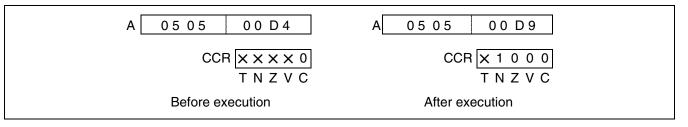

| 9.1.           | ADD (Add Byte Data of Destination and Source to Destination)                           | . 79 |

| 9.1.           | 2 ADDC (Add Byte Data of AL and AH with Carry to AL)                                   | . 81 |

| 9.1.3          |                                                                                        | . 82 |

| 9.1.4          | 4 ADDCW (Add Word Data of Accumulator and Effective Address with Carry to Accumulator) | 84   |

| 9.1.           |                                                                                        | . 86 |

| 9.1.           | 6 ADDL (Add Long Word Data of Destination and Source to Destination)                   | . 87 |

| 9.1.           |                                                                                        |      |

| 9.1.3          |                                                                                        |      |

| 9.1.9          |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.           | ( , , , , , , , , , , , , , , , , , , ,                                                |      |

| 9.1.           | · · · · · · · · · · · · · · · · · · ·                                                  |      |

| 9.1.           |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.           | · · · · · · · · · · · · · · · · · · ·                                                  |      |

| 9.1.           |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.:<br>9.1.: |                                                                                        |      |

| 9.1./<br>9.1./ |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 9.1.           |                                                                                        |      |

| 0.1.           |                                                                                        | /    |

| 9.1.29 | CWBNE (Compare Word Data and Branch if not Equal)            | 129 |

|--------|--------------------------------------------------------------|-----|

| 9.1.30 | DBNZ (Decrement Byte Data and Branch if not "0")             | 131 |

| 9.1.31 | DEC (Decrement Byte Data)                                    | 133 |

| 9.1.32 | DECL (Decrement Long Word Data)                              | 134 |

| 9.1.33 | DECW (Decrement Word Data)                                   | 135 |

| 9.1.34 | DIV (Divide Word Data by Byte Data)                          | 137 |

| 9.1.35 | DIVW (Divide Long Word Data by Word Data)                    | 139 |

| 9.1.36 | DIVU (Divide unsigned Word Data by unsigned Byte Data)       | 141 |

| 9.1.37 | DIVUW (Divide unsigned Long Word Data by unsigned Word Data) | 143 |

| 9.1.38 | DWBNZ (Decrement Word Data and Branch if not Zero)           | 145 |

| 9.1.39 | EXT (Sign Extend from Byte Data to Word Data)                | 147 |

| 9.1.40 | EXTW (Sign Extend from Word Data to Long Word Data)          | 148 |

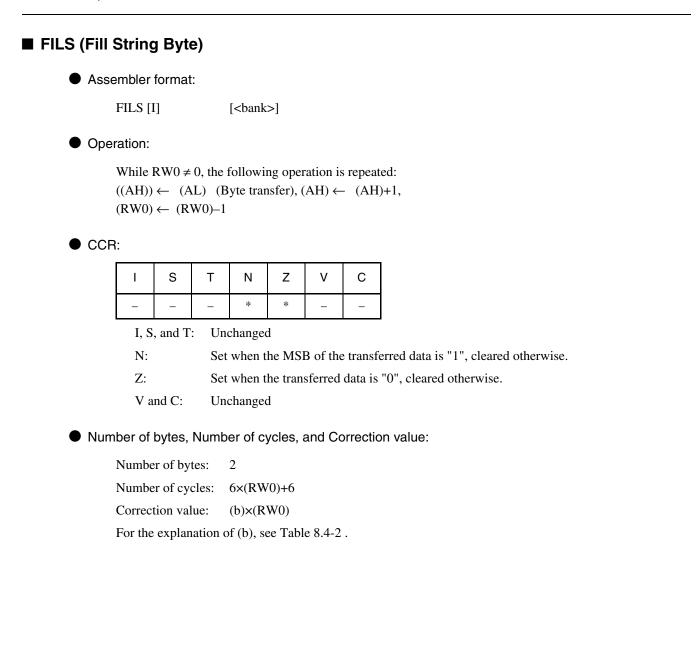

| 9.1.41 | FILS (Fill String Byte)                                      | 149 |

| 9.1.42 | FILSW (Fill String Word)                                     | 151 |

| 9.1.43 | INC (Increment Byte Data (Address Specification))            | 153 |

| 9.1.44 | INCL (Increment Long Word Data)                              | 154 |

| 9.1.45 | INCW (Increment Word Data)                                   | 155 |

| 9.1.46 | INT (Software Interrupt)                                     | 157 |

| 9.1.47 | INT (Software Interrupt (Vector Specification))              | 159 |

| 9.1.48 | INT9 (Software Interrupt)                                    | 161 |

| 9.1.49 | INTP (Software Interrupt)                                    | 163 |

| 9.1.50 | JCTX (Jump Context)                                          | 165 |

| 9.1.51 | JMP (Jump Destination Address)                               | 167 |

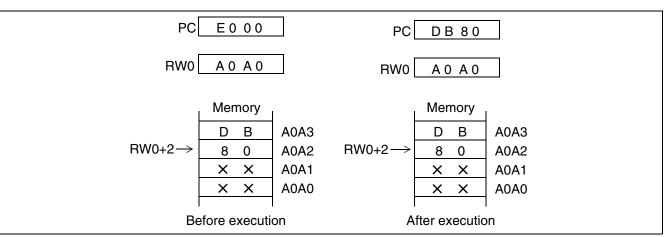

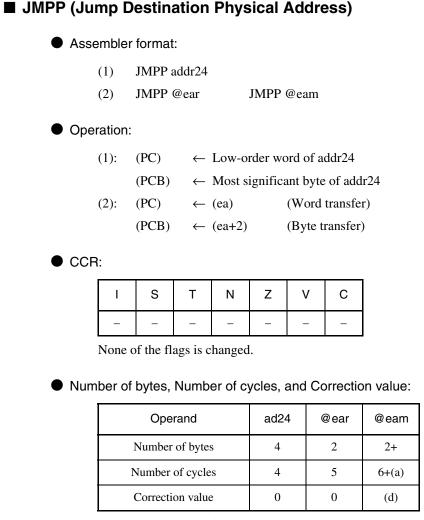

| 9.1.52 | JMPP (Jump Destination Physical Address)                     | 168 |

| 9.1.53 | LINK (Link and create new stack frame)                       | 169 |

| 9.1.54 | LSL (Logical Shift Byte Data of Accumulator to Left)         | 170 |

| 9.1.55 | LSLL (Logical Shift Long Word Data of Accumulator to Left)   | 171 |

| 9.1.56 | LSLW (Logical Shift Word Data of Accumulator to Left)        | 172 |

| 9.1.57 | LSLW (Logical Shift Word Data of Accumulator to Left)        | 173 |

| 9.1.58 | LSR (Logical Shift Byte Data of Accumulator to Right)        | 174 |

| 9.1.59 | LSRL (Logical Shift Long Word Data of Accumulator to Right)  | 176 |

| 9.1.60 | LSRW (Logical Shift Word Data of Accumulator to Right)       | 178 |

| 9.1.61 | LSRW (Logical Shift Word Data of Accumulator to Right)       | 179 |

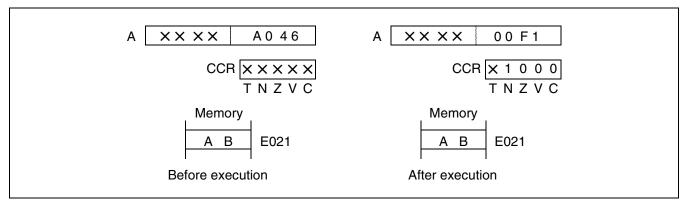

| 9.1.62 | MOV (Move Byte Data from Source to Accumulator)              | 181 |

| 9.1.63 | MOV (Move Byte Data from Accumulator to Destination)         | 183 |

| 9.1.64 | MOV (Move Byte Immediate Data to Destination)                | 184 |

| 9.1.65 | MOV (Move Byte Data from Source to Destination)              | 186 |

| 9.1.66 | MOV (Move Byte Data from AH to Memory)                       | 188 |

| 9.1.67 | MOVB (Move Bit Data from Bit Address to Accumulator)         | 189 |

| 9.1.68 | MOVB (Move Bit Data from Accumulator to Bit Address)         | 191 |

| 9.1.69 | MOVEA (Move Effective Address to Destination)                |     |

| 9.1.70 | MOVL (Move Long Word Data from Source to Accumulator)        |     |

| 9.1.71 | MOVL (Move Long Word Data from Accumulator to Destination)   | 195 |

| 9.1.72 | MOVN (Move Immediate Nibble Data to Accumulator)             |     |

| 9.1.73 | MOVS (Move String Byte)                                      |     |

| 9.1.74 | MOVSW (Move String Word)                                     |     |

| 9.1.75 | MOVW (Move Word Data from Source to Accumulator)             | 201 |

| 9.1.76           | MOVW (Move Word Data from Accumulator to Destination)                                     | 203 |

|------------------|-------------------------------------------------------------------------------------------|-----|

| 9.1.77           | MOVW (Move Immediate Word Data to Destination)                                            | 205 |

| 9.1.78           | MOVW (Move Word Data from Source to Destination)                                          | 207 |

| 9.1.79           | MOVW (Move Immediate Word Data to io)                                                     | 209 |

| 9.1.80           | MOVW (Move Word Data from AH to Memory)                                                   | 210 |

| 9.1.81           | MOVX (Move Byte Data with Sign Extension from Source to Accumulator)                      | 211 |

| 9.1.82           | MUL (Multiply Byte Data of Accumulator)                                                   |     |

| 9.1.83           | MUL (Multiply Byte Data of Accumulator and Effective Address)                             |     |

| 9.1.84           | MULW (Multiply Word Data of Accumulator)                                                  |     |

| 9.1.85           | MULW (Multiply Word Data of Accumulator and Effective Address)                            |     |

| 9.1.86           | MULU (Multiply Unsigned Byte Data of Accumulator)                                         |     |

| 9.1.87           | MULU (Multiply Unsigned Byte Data of Accumulator and Effective Address)                   |     |

| 9.1.88           | MULUW (Multiply Unsigned Word Data of Accumulator)                                        |     |

| 9.1.89           | MULUW (Multiply Unsigned Word Data of Accumulator) and Effective Address)                 |     |

| 9.1.90           | NEG (Negate Byte Data of Destination)                                                     |     |

| 9.1.91           | NEGW (Negate Word Data of Destination)                                                    |     |

| 9.1.92           | NOP (No Operation)                                                                        |     |

| 9.1.92           | NOT (Not Byte Data of Destination)                                                        |     |

| 9.1.93<br>9.1.94 | NOTW (Not Word Data of Destination)                                                       |     |

| 9.1.94<br>9.1.95 | NRML (NORMALIZE Long Word)                                                                |     |

| 9.1.95           | OR (Or Byte Data of Destination and Source to Destination)                                |     |

|                  |                                                                                           |     |

| 9.1.97           | OR (Or Byte Data of Immediate Data and Condition Code Register to Condition Code Registe  | 230 |

| 9.1.98           | ORL (Or Long Word Data of Destination and Source to Destination)                          |     |

| 9.1.99           | ORW (Or Word Data of AH and AL to AL)                                                     |     |

| 9.1.100          | ORW (Or Word Data of Destination and Source to Destination)                               |     |

| 9.1.100          | POPW (Pop Word Data of Accumulator from Stack Memory)                                     |     |

|                  | POPW (Pop Word Data of AH from Stack Memory)                                              |     |

|                  |                                                                                           |     |

|                  | POPW (Pop Word Data of Program Status from Stack Memory)                                  |     |

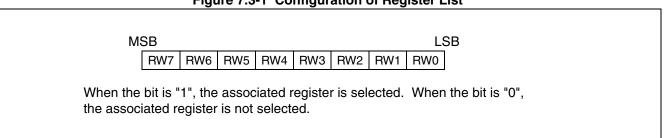

|                  | POPW (Pop Registers from Stack Memory)                                                    |     |

|                  | PUSHW (Push Word Data of Inherent Register to Stack Memory)                               |     |

|                  | PUSHW (Push Registers to Stack Memory)                                                    |     |

|                  | RET (Return from Subroutine)                                                              |     |

|                  | RETI (Return from Interrupt)                                                              |     |

|                  | RETP (Return from Physical Address)                                                       |     |

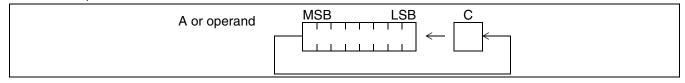

|                  | ROLC (Rotate Byte Data of Accumulator with Carry to Left)                                 |     |

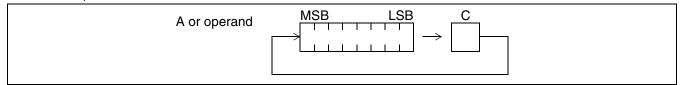

|                  | RORC (Rotate Byte Data of Accumulator with Carry to Right)                                |     |

|                  | SBBS (Set Bit and Branch if Bit Set)                                                      |     |

|                  | SCEQ (Scan String Byte Until Equal)                                                       |     |

|                  | SCWEQ (Scan String Word Until Equal)                                                      |     |

|                  | SETB (Set Bit)                                                                            |     |

|                  | SUB (Subtract Byte Data of Source from Destination to Destination)                        |     |

|                  | SUBC (Subtract Byte Data of AL from AH with Carry to AL)                                  | 266 |

| 9.1.118          | SUBC (Subtract Byte Data of Effective Address from Accumulator with Carry to Accumulator) | oc- |

|                  |                                                                                           | 267 |

| 9.1.119          | SUBCW (Subtract Word Data of Effective Address from Accumulator with Carry to Accumulate  | ,   |

| 0 1 100          | CURDE (Subtract Desimal Data of AL from ALL with Course to AL)                            | 269 |

| 9.1.120          | SUBDC (Subtract Decimal Data of AL from AH with Carry to AL)                              | 2/1 |

| 9.1.12 | 21 SUBL (Subtract Long Word Data of Source from Destination to Destination)    | 272 |

|--------|--------------------------------------------------------------------------------|-----|

| 9.1.12 | 22 SUBW (Subtract Word Data of Source from Destination to Destination)         | 274 |

| 9.1.12 | 23 SUBW (Subtract Word Data of AL from AH to AL)                               | 276 |

| 9.1.12 | 24 SWAP (Swap Byte Data of Accumulator)                                        | 277 |

| 9.1.12 | 25 SWAPW (Swap Word Data of Accumulator)                                       | 278 |

| 9.1.12 | 26 UNLINK (Unlink and Create New Stack Frame)                                  | 279 |

| 9.1.12 | 27 WBTc (Wait until Bit Condition Satisfied)                                   | 280 |

| 9.1.12 | 28 XCH (Exchange Byte Data of Source to Destination)                           | 282 |

| 9.1.12 | 29 XCHW (Exchange Word Data of Source to Destination)                          | 284 |

| 9.1.13 | 30 XOR (Exclusive Or Byte Data of Destination and Source to Destination)       | 286 |

| 9.1.13 | 31 XORL (Exclusive Or Long Word Data of Destination and Source to Destination) | 288 |

| 9.1.13 | 32 XORW (Exclusive Or Word Data of AH and AL to AL)                            | 290 |

| 9.1.13 | 33 XORW (Exclusive Or Word Data of Destination and Source to Destination)      | 291 |

| 9.1.13 | 34 ZEXT (Zero Extend from Byte Data to Word Data)                              | 293 |

| 9.1.13 | 35 ZEXTW (Zero Extend from Word Data to Long Word Data)                        | 294 |

|        |                                                                                |     |

| APPEND | DIX                                                                            | 295 |

| APPEN  | DIX A Explanation of Instruction Lists                                         | 296 |

| A.1    | Items Used in Instruction Lists                                                | 297 |

| A.2    | Symbols Used in Instruction Lists                                              | 299 |

| A.3    | Effective Address Field                                                        | 301 |

| A.4    | Calculating the Number of Execution Cycles                                     | 302 |

| APPEN  | IDIX B F <sup>2</sup> MC-16LX Instruction Lists (351 Instructions)             | 304 |

| B.1    | Transfer Instructions                                                          | 305 |

| B.2    | Numeric Data Operation Instructions                                            |     |

| B.3    | Logical Data Operation Instruction                                             | 311 |

| B.4    | Shift Instruction                                                              | 313 |

| B.5    | Branch Instructions                                                            | 314 |

| B.6    | Other Instructions                                                             | 316 |

| APPEN  | IDIX C F <sup>2</sup> MC-16LX Instruction Maps                                 | 319 |

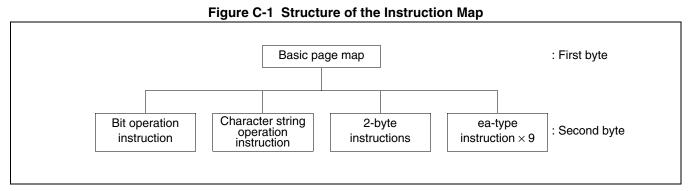

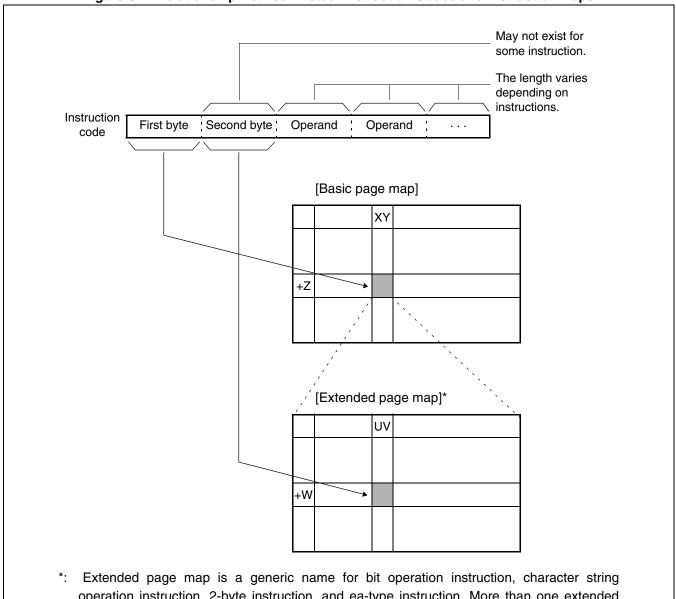

| C.1    | Structure of the Instruction Map                                               | 320 |

| C.2    | Basic Page Map                                                                 | 322 |

| C.3    | Bit Operation Instruction Map                                                  | 324 |

| C.4    | Character String Operation Instruction Map                                     | 326 |

| C.5    | 2-byte Instruction Map                                                         | 328 |

| C.6    | ea-type Instruction Map                                                        | 330 |

| C.7    | MOVEA RWi, ea Instruction Map                                                  | 340 |

| C.8    | MOV Ri, ea Instruction Map                                                     | 342 |

| C.9    | MOVW RWi, ea Instruction Map                                                   | 344 |

| C.10   | MOV ea, Ri Instruction Map                                                     | 346 |

| C.11   | MOVW ea, RWi Instruction Map                                                   | 348 |

| C.12   | XCH Ri, ea Instruction Map                                                     | 350 |

| C.13   | XCHW RWi, ea Instruction Map                                                   | 352 |

| INDEX  |                                                                                | 355 |

## Main changes in this edition

| Page | Changes (For details, refer to main body.)                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 188  | CHAPTER 9<br>DETAILED EXECUTION INSTRUCTIONS<br>9.1.66 MOV<br>(Move Byte Data from AH to Memory)  | "• Assembler format:" is changed.<br>(MOV @AL,AH / MOV @A,T $\rightarrow$ MOV @AL,AH)                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 210  | CHAPTER 9<br>DETAILED EXECUTION INSTRUCTIONS<br>9.1.80 MOVW<br>(Move Word Data from AH to Memory) | "● Assembler format:" is changed.<br>(MOVW @AL,AH / MOV @A,T → MOVW @AL,AH)                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 278  | CHAPTER 9<br>DETAILED EXECUTION INSTRUCTIONS<br>9.1.125 SWAPW<br>(Swap Word Data of Accumulator)  | "• Assembler format:" is changed.<br>(SWAPW /XCHW A,T $\rightarrow$ SWAPW)                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 305  | B.1 Transfer Instructions                                                                         | "Table B-1 Transfer Instruction (Byte): 41 Instructions" is<br>changed.<br>(MOV @AL,AH / MOV @A,T → MOV @AL,AH)                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 306  |                                                                                                   | <ul> <li>"Table B-2 Transfer Instruction (Word/Long-word):</li> <li>38 Instructions" is changed.</li> <li>(MOVW @AL,AH / MOVW @A,T → MOVW @AL,AH)</li> </ul>                                                                                                                                                                                                                                                                                                                                                             |  |

| 315  | B.5 Branch Instructions                                                                           | CBNE Instruction in "Table B-14 Branch 2: 19 Instructions" is<br>changed.<br>(CBNE ear,#imm8,rel byte(A) not equal to imm8<br>CBNE ear,#imm8,rel byte(A) not equal to imm8<br>$\rightarrow$<br>CBNE ear,#imm8,rel byte(ear) not equal to imm8<br>CBNE ear,#imm8,rel byte(eam) not equal to imm8)<br>CWBNE instruction in "Table B-14 Branch 2: 19 Instructions" is<br>changed.<br>(CWBNE ear,#imm16,rel<br>CWBNE ear,#imm16,rel<br>$\rightarrow$<br>CWBNE ear,#imm16,rel<br>CWBNE ear,#imm16,rel<br>CWBNE ear,#imm16,rel |  |

| Page | Changes (For details, refer to main body.) |                                                                                                                                                                   |  |

|------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 316  | B.6 Other Instructions                     | <ul> <li>"Table B-15 Other Control Systems (Byte/Word/Long-word):</li> <li>28 Instructions" is changed.</li> <li>(+&amp;→ *5)</li> </ul>                          |  |

|      |                                            | "Table B-15 Other Control Systems (Byte/Word/Long-word):<br>28 Instructions" is changed.<br>(*5: (number of POP operations), or (number of PUSH opera-<br>tions)) |  |

| 317  |                                            | <ul> <li>"Table B-17 Accumulator Operation Instruction (Byte/Word):</li> <li>6 Instructions" is changed.</li> <li>(SWAPW / XCHW A,T → SWAPW)</li> </ul>           |  |

| 318  |                                            | "Table B-18 String Instruction : 10 Instructions" is changed.<br>(+& $\rightarrow$ *5), (+) $\rightarrow$ *8)                                                     |  |

The vertical lines marked in the left side of the page show the changes.

## CHAPTER 1 OVERVIEW OF THE F<sup>2</sup>MC-16LX CPU CORE AND SAMPLE CONFIGURATION INCLUDING IT

This chapter briefly describes the configuration of the  $F^2MC-16LX$  CPU core, and presents a sample configuration of a device incorporating it.

- 1.1 Overview of the F<sup>2</sup>MC-16LX CPU Core

- 1.2 Sample Configuration of an F<sup>2</sup>MC-16LX Device

## 1.1 Overview of the F<sup>2</sup>MC-16LX CPU Core

The  $F^2MC-16LX$  CPU core is an advanced 16-bit CPU designed for use in various types of industrial equipment, office automation equipment, on-vehicle equipment, and other equipment required to operate at high speed in real-time mode.

#### ■ Overview of the F<sup>2</sup>MC-16LX CPU Core

The  $F^2MC-16LX$  CPU core is an advanced 16-bit CPU designed for use in various types of industrial equipment, office automation equipment, on-vehicle equipment, and other equipment required to operate at high speed in real-time mode. The design of the  $F^2MC-16LX$  instruction set is optimized for use in controllers. The instructions can perform various types of control at high speed and at high efficiency. The  $F^2MC-16LX$  is a suitable CPU for processing 16-bit data. Some of its instructions can be used also for 32-bit data processing, because its CPU incorporates a 32-bit accumulator. The memory space of the  $F^2MC-16LX$  can be expanded up to 16 Mbytes. Each location in the memory space can be accessed using either a linear pointer or a bank method. The instruction set is based on the  $F^2MC-8$  A-T architecture, but has been enhanced by adding instructions that support high-level language, extending the addressing mode, improving the multiplication and division instructions, and augmenting bit manipulation.

#### ■ Features of the F<sup>2</sup>MC-16LX CPU Core

- Minimum instruction execution time: 62.5 ns (with internal clock at 16 MHz)

- Memory space: Up to 16 Mbytes, accessible using either a linear or bank mode

- Instruction set optimized for use in controllers

- Cornucopia of data types: Bit, byte, word, and long word

- Extended addressing mode: 23 types

- High code efficiency

- Reinforcement of high-precision calculation (32-bit length) by means of a 32-bit accumulator

- Powerful interrupt functions

Interrupt priority levels: 8 levels (programmable)

- CPU-independent automatic transfer function

- Extended intelligent I/O service: Up to 16 channels

- Instruction supporting high-level language (C language) and multitasking

- Use of a system stack pointer

- Various pointers

- High symmetry of the instruction set

- Barrel shift instruction

- Increased execution speed: Use of a 4-byte queue for waiting of instructions

## 1.2 Sample Configuration of an F<sup>2</sup>MC-16LX Device

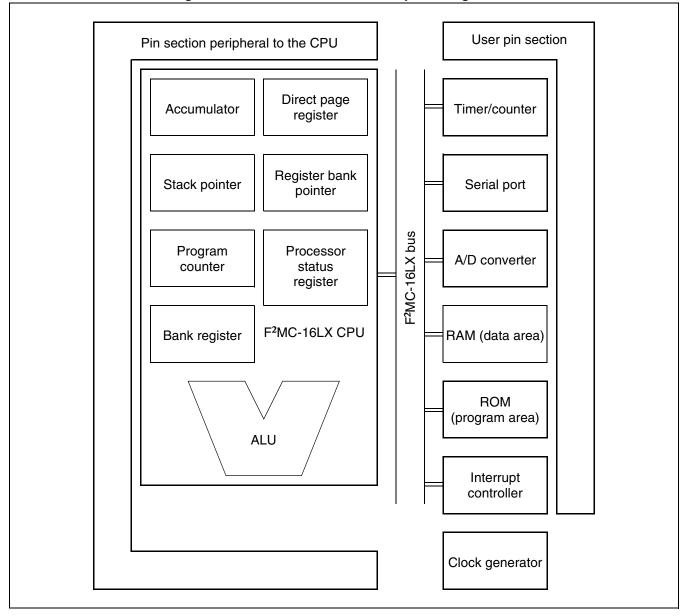

#### Figure 1.2-1 shows a sample configuration of an $F^2MC-16LX$ device.

#### ■ Sample Configuration of an F<sup>2</sup>MC-16LX Device

## CHAPTER 2 MEMORY SPACE

This chapter describes memory spaces in the F<sup>2</sup>MC-16LX CPU.

- 2.1 CPU Memory Space

- 2.2 Linear Addressing Mode

- 2.3 Bank Addressing Mode

- 2.4 Memory Space Divided into Banks and Value in Each Bank Register

- 2.5 Data Configuration of and Access to Multi-byte Data in Memory

### 2.1 CPU Memory Space

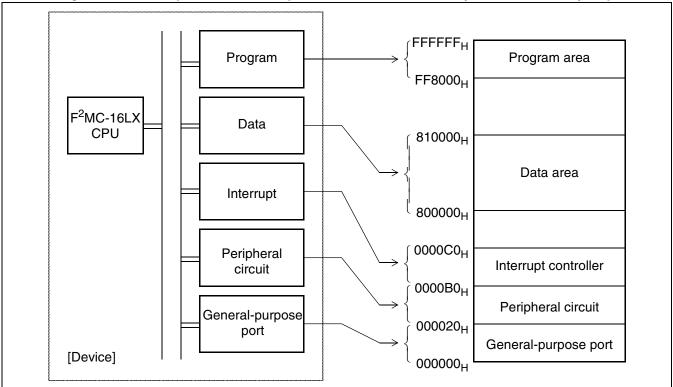

All data, programs, and I/O areas managed in the  $F^2MC-16LX$  CPU are allocated in its 16-Mbyte memory space. The CPU can access these resources using an address on the 24-bit address bus (see Figure 2.1-1).

The  $F^2MC-16LX$  addressing mode can be classified either as a linear or bank mode. The linear mode specifies an entire 24-bit address using a instruction. The bank mode specifies the upper 8 bits of each address using a bank register, and the remaining 16-bit address using an instruction.

#### ■ CPU Memory Space

### 2.2 Linear Addressing Mode

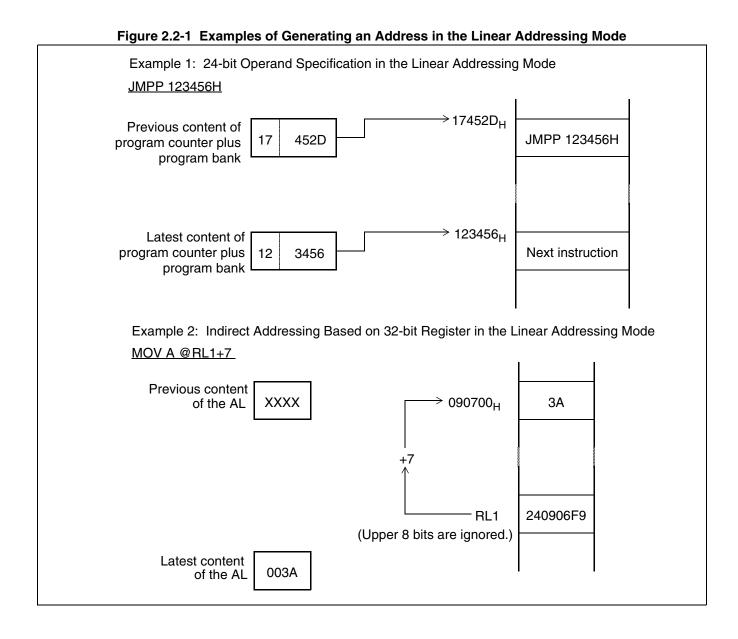

The linear addressing mode of the F<sup>2</sup>MC-16LX specifies an entire 24-bit address using an instruction.

The linear addressing mode can operate in two different ways. In the first way, an operand of an instruction directly specifies an entire 24-bit address. In the second way, the lower 24-bit of a 32-bit general-purpose register is referred as an address.

#### Linear Addressing Mode

The linear addressing mode of the  $F^2MC-16LX$  specifies an entire 24-bit address using an instruction. The address mode of the  $F^2MC-16LX$  is determined according to the specification of the effective address or instruction code (implied) of an instruction.

The linear addressing mode can operate in two different ways. In the first way, an operand of an instruction directly specifies an entire 24-bit address. In the second way, the lower 24-bit of a 32-bit general-purpose register is referred as an address (see Figure 2.2-1).

#### 8

#### 2.3 Bank Addressing Mode

## The bank addressing mode of the $F^2MC-16LX$ specifies the upper 8 bits of an address using a bank register for use, and the remaining 16 bits using an instruction.

#### Bank Addressing Mode

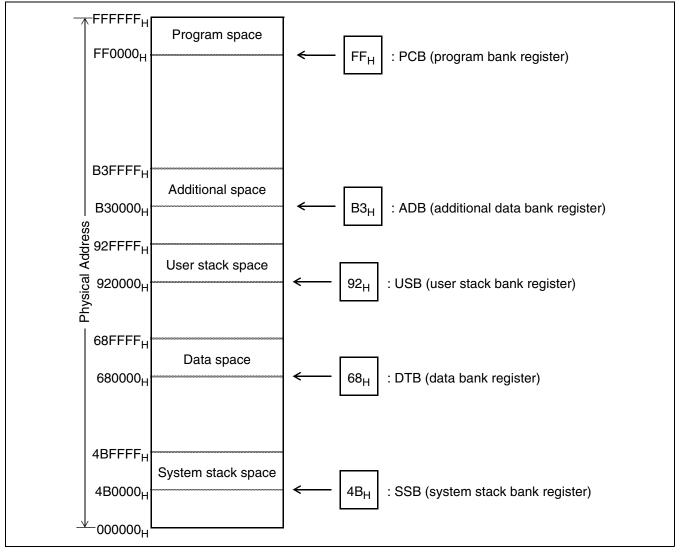

In the bank addressing mode, the 16-Mbyte memory space is divided into 256 banks of 64-Kbyte, and the corresponding bank to each space is specified by the following 4 bank registers.

#### Program bank register (PCB)

A 64-Kbyte bank specified using the PCB register is called a program (PC) space. It is used to hold mainly instruction codes, vector tables, and immediate data.

#### • Data bank register (DTB)

A 64-Kbyte bank specified using the DTB register is called a data (DT) space. It is used to hold mainly readable/writable data and control/data registers for internal and external resources.

User stack bank register (USB) and system stack bank register (SSB)

A 64-Kbyte bank specified using the USB or SSB register is called a stack (SP) space. It is accessed when the execution of a push or pop instruction or interrupt handling is performed and which to be used, the USB or SSB register, is determined according to the S flag in the condition code register to save register contents and a stack access occurs.

#### Additional data bank register (ADB)

A 64-Kbyte bank specified using the ADB register is called an additional (AD) space. It is used to hold mainly data overflowing from the DT space.

Each instruction is assigned with one of the default spaces by each addressing listed in Table 2.3-1 to improve instruction code efficiency.

| Default space    | Addressing                                                     |

|------------------|----------------------------------------------------------------|

| Program space    | PC-indirect, program access, branch type                       |

| Data space       | @A, addr16, dir, or addressing using @RW0, @RW1, @RW4, or @RW5 |

| Stack space      | Addressing using PUSHW, POPW, @RW3, @RW7, or @SP               |

| Additional space | Addressing using @RW2 or @RW6                                  |

#### Table 2.3-1 Default Spaces

If a space other than a default space is used, an arbitrary bank space corresponding to a prefix code can be accessed by specifying the prefix code before the instruction.

Table 2.3-2 lists bank select prefixes and the memory space selected using each prefix.

| Bank select prefix | Selected space                                                                  |

|--------------------|---------------------------------------------------------------------------------|

| РСВ                | Program space                                                                   |

| DTB                | Data space                                                                      |

| ADB                | Additional space                                                                |

| SPB                | System or user stack space depending on the contents of the selected stack flag |

Table 2.3-2 Bank Selection Prefix

The DTB, USB, SSB, and ADB registers are initialized to  $"00_{\text{H}}"$  at a reset. The PCB register is initialized to "FF<sub>H</sub>" at a reset. After a reset, the data, stack, and additional spaces are allocated in bank  $00_{\text{H}}$  (000000<sub>H</sub> to 00FFFF<sub>H</sub>), and the program space is allocated in bank FF<sub>H</sub> (FF0000<sub>H</sub> to FFFFFF<sub>H</sub>).

## 2.4 Memory Space Divided into Banks and Value in Each Bank Register

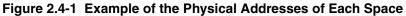

Figure 2.4-1 shows an example of a memory space divided into banks and a value in each register bank.

#### ■ Memory Space Divided into Banks and Values in Each Register Bank

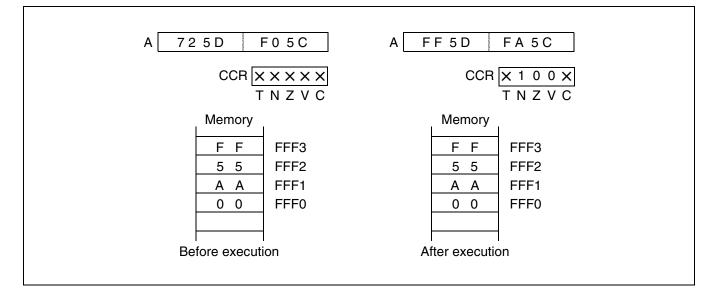

### 2.5 Data Configuration of and Access to Multi-byte Data in Memory

Multi-byte data is written to memory starting at the lowest address. If the multi-byte data is 32-bit long, the lower 16 bits are written to memory first and then upper 16 bits.

#### Multi-byte Data Layout in a Memory Space

Multi-byte data is written to memory starting at the lowest address. If the multi-byte data is 32-bit length, the lower 16 bits are written to memory first and then upper 16 bits.

If a reset signal is input immediately after the low-order data is written to memory, the high-order data may not be written. To keep the data in integrity, it is necessary to input a reset signal after the high-order data is written.

Figure 2.5-1 shows the layout of multi-byte data in memory. The lower 8 bits are placed at address n, the next lower 8 bits are placed at address n + 1, and the next lower 8 bits are placed at address n + 2, and so on.

#### Figure 2.5-1 Multi-byte Data Layout in Memory

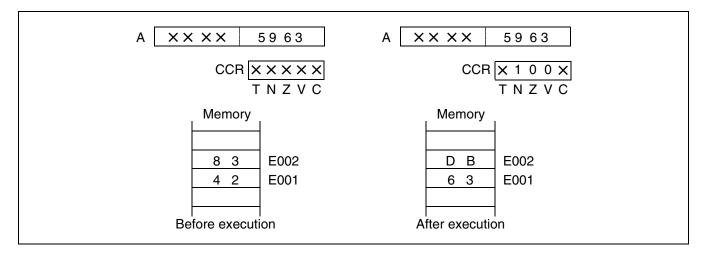

#### Access to Multi-byte Data

When multi-byte data is accessed, it is assumed that all parts of the multi-byte data are within a single bank. To put it another way, an instruction accessing multi-byte data assumes that an address that follows address  $FFFF_H$  is  $0000_H$  in the same bank as for  $FFFF_H$ .

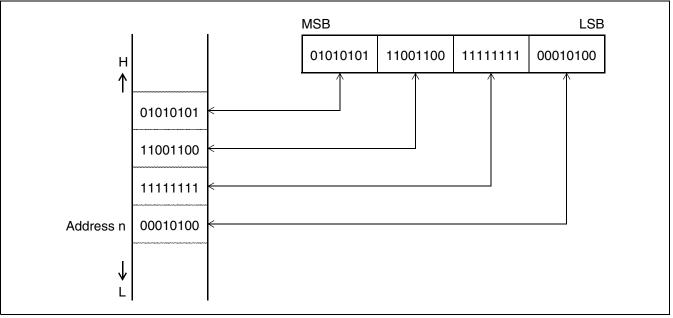

Figure 2.5-2 shows an execution example of an instruction accessing multi-byte data.

#### CHAPTER 2 MEMORY SPACE

## CHAPTER 3 DEDICATED REGISTERS

The registers of the  $F^2MC-16LX$  can be grouped into two major categories: dedicated registers in the CPU and general-purpose registers allocated in memory. This chapter describes the  $F^2MC-16LX$  dedicated registers. These registers are the dedicated hardware in the CPU. Their use is limited due to the architecture of the CPU.

- 3.1 F<sup>2</sup>MC-16LX Dedicated Register Types

- 3.2 Accumulator (A)

- 3.3 User Stack Pointer (USP) and System Stack Pointer (SSP)

- 3.4 Processor Status (PS)

- 3.5 Program Counter (PC)

- 3.6 Direct Page Register (DPR)

- 3.7 Bank Registers

## 3.1 F<sup>2</sup>MC-16LX Dedicated Register Types

#### There are 11 dedicated registers in the F<sup>2</sup>MC-16LX.

- Accumulator (A=AH:AL)

- System stack pointer (SSP)

- Program counter (PC)

- Data bank register (DTB)

- System stack bank register (SSB)

- Direct page register (DPR)

- User stack pointer (USP)

- Processor status (PS)

- Program bank register (PCB)

- User stack bank register (USB)

- Additional data bank register (ADB)

#### ■ F<sup>2</sup>MC-16LX Dedicated Register Types

Accumulator (A=AH:AL)

This is a set of two 16-bit accumulators. It can be used as a single 32-bit accumulator.

• User stack pointer (USP)

This is a 16-bit pointer indicating a user stack area.

• System stack pointer (SSP)

This is a 16-bit pointer indicating a system stack area.

Processor status (PS)

This is a 16-bit register indicating the status of the system.

• Program counter (PC)

This is a 16-bit register to hold an address where the next instruction to be executed is stored.

Program bank register (PCB)

This is an 8-bit register indicating the program space.

Data bank register (DTB)

This is an 8-bit register indicating the data space.

User stack bank register (USB)

This is an 8-bit register indicating the user stack space.

• System stack bank register (SSB)

This is an 8-bit register indicating the system stack space.

#### • Additional data bank register (ADB)

This is an 8-bit register indicating the additional space.

#### Direct page register (DPR)

This is an 8-bit register indicating the direct page.

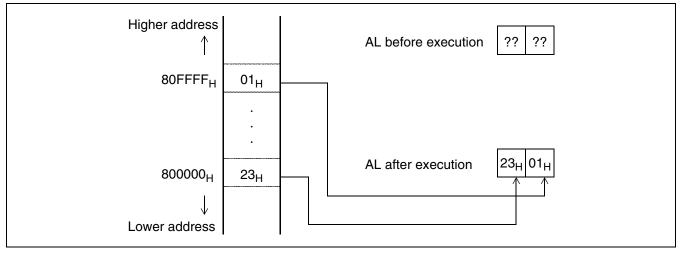

Figure 3.1-1 shows an image of the dedicated registers.

#### Figure 3.1-1 Dedicated Registers

#### 3.2 Accumulator (A)

## The accumulator (A) consists of two 16-bit length operation registers (AH and AL), is used for temporary storage of the results for an operation or of data to be transferred.

#### ■ Accumulator (A)

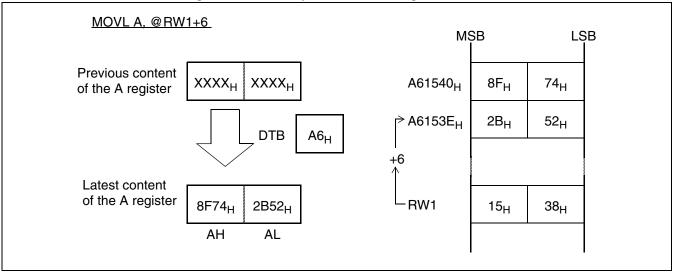

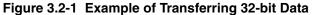

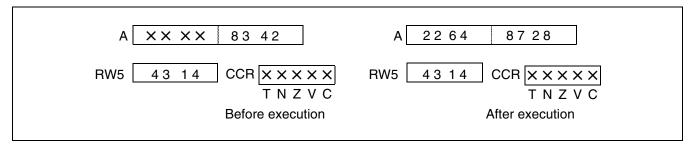

The accumulator (A) consists of two 16-bit length operation registers (AH and AL), used for temporary storage of the results for an operation or of data to be transferred. To process 32-bit data, the AH and AL registers are concatenated (see Figure 3.2-1). To process 16-bit data (used in word-unit processing) or 8-bit data (used in byte-unit processing), only the AL register is used (see Figure 3.2-2). Various types of arithmetic and logical operations can be performed between data in the accumulator (A) and data in memory or a register (such as Ri, RWi, or RLi). Similarly to the F<sup>2</sup>MC-8, the F<sup>2</sup>MC-16LX automatically transfers data from the AL register to the AH register, if it receives new data at the AL register and the new data is not larger than a word (data preservation function). Use of this data preservation function and a function to perform arithmetic and logical operations between the AL and AH registers makes various types of processing more efficient (see Figure 3.2-2).

If data transferred to the AL register is not larger than a byte, the data is sign- or zero-extended to 16 bits and it is stored in the AL register. The data in the AL register can be handled as either a word or a byte. If a byte-unit arithmetic operation is performed on the AL register, the upper 8 bits of data that have been previously set in the AL register are ignored and reset to all "0"s.

#### Figure 3.2-2 Example of Transferring Data between the AL and AH Registers by Means of the Data Preservation Function

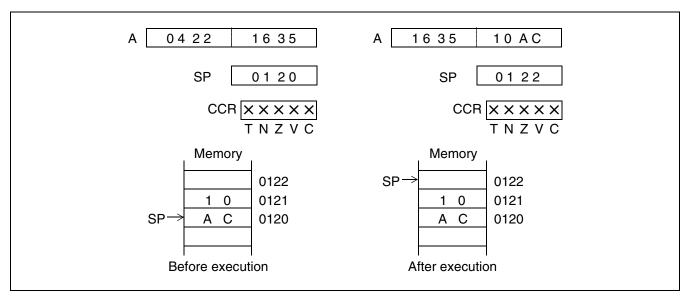

### 3.3 User Stack Pointer (USP) and System Stack Pointer (SSP)

Both the user stack pointer (USP) and system stack pointer (SSP) are 16-bit registers. They are used to indicate a data save address or return address when a push, pop instruction, or subroutine is executed.

Basically, a value to be set in a stack pointer must be an even address.

#### ■ User Stack Pointer (USP) and System Stack Pointer (SSP)

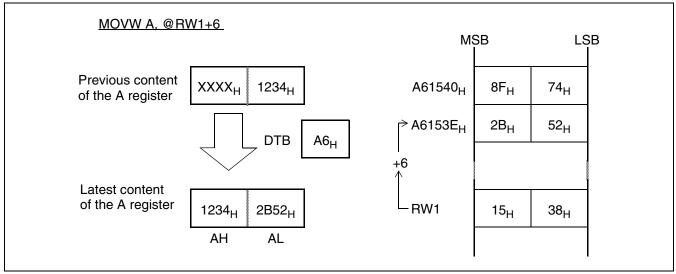

Both the user stack pointer (USP) and system stack pointer (SSP) are a 16-bit register. They are used to indicate a data save address or return address when a push, pop instruction, or subroutine is executed. The USP and SSP registers are used by stack manipulation instructions in the same manner. If the S flag in the condition code register (CCR) in the processor status (PS) register is "0", the USP register is active. If the S flag is "1", the SSP register is active (see Figure 3.3-1). Because the S flag becomes "1" when an interrupt is accepted, the SSP register is used to indicate a memory area to save register contents at an interrupt. The SSP register is used by an interrupt routine for stack manipulation, while the USP register is used by non-interrupt handling routines for stack manipulation. If it is unnecessary to divide the stack space, only the SSP register should be used.

For the SSP register, the upper 8 bits of an address used for stack manipulation are indicated by the system stack bank register (SSB). For the USP register, they are indicated by the user stack bank register (USB).

#### Figure 3.3-1 Relationships between Stack Manipulation Instruction and Stack Pointer

# 3.4 **Processor Status (PS)**

The processor status (PS) register consists of bits for controlling the CPU and those for indicating the status of the CPU. The PS register is divided into the following three registers.

- Interrupt level mask register (ILM)

- Register bank pointer (RP)

- Condition code register (CCR)

#### Processor Status (PS)

The processor status (PS) register consists of bits for controlling the CPU and those for indicating the status of the CPU.

- Interrupt level mask register (ILM): Indicates the level of an interrupt to be accepted.

- Register bank pointer (RP): Indicates the start address of a register bank.

- Condition code register (CCR): Consists of various flags that are set or reset during instruction execution or at an interrupt occurrence.

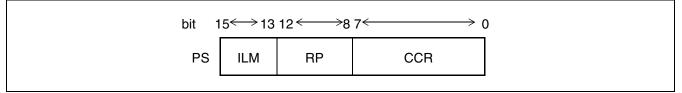

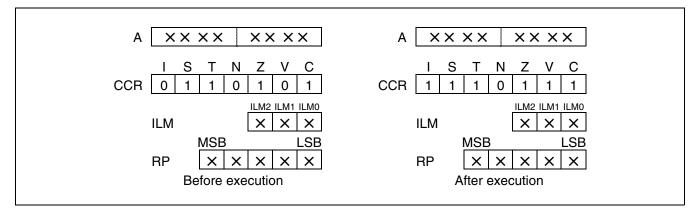

Figure 3.4-1 shows the structure of the processor status (PS) register.

#### Figure 3.4-1 Processor Status (PS) Register Structure

### 3.4.1 Interrupt Level Mask Register (ILM)

#### The following shows a configuration diagram of the interrupt level mask register (ILM).

ILM (Initial value)ightarrow

**ILM1 ILM0**

#### ■ Interrupt Level Mask Register (ILM)

ILM2

0

The interrupt level mask register (ILM) consists of 3 bits. It indicates the levels of interrupts acceptable to the CPU. If an interrupt request whose level is higher than the level indicated using these 3 bits, the interrupt is generated. Interrupt level 0 is the highest, and interrupt level 7 is the lowest (see Table 3.4-1). In other words, for an interrupt to be accepted, its interrupt level value must be smaller than the value held in the ILM register. When an interrupt is accepted, its interrupt level is set in the ILM register, thus prohibiting interrupts on lower levels from being accepted. Because the ILM register is initialized to all "0"s at a reset, the highest interrupt level is specified in the ILM register. It is possible to transfer 8-bit immediate data to the ILM register, but only the lower 3 bits of the data can be used.

Table 3.4-1 Interrupt Levels Indicated in the Interrupt Level Mask Register (ILM)

| ILM2 | ILM1 | ILM0 | Level value | Levels of acceptable interrupts |

|------|------|------|-------------|---------------------------------|

| 0    | 0    | 0    | 0           | Interrupt disabled              |

| 0    | 0    | 1    | 1           | 0                               |

| 0    | 1    | 0    | 2           | 1 and below                     |

| 0    | 1    | 1    | 3           | 2 and below                     |

| 1    | 0    | 0    | 4           | 3 and below                     |

| 1    | 0    | 1    | 5           | 4 and below                     |

| 1    | 1    | 0    | 6           | 5 and below                     |

| 1    | 1    | 1    | 7           | 6 and below                     |

## 3.4.2 Register Bank Pointer (RP)

The following shows a configuration diagram of the register bank pointer (RP).

| RP                           | B4 | B3 | B2 | B1 | В0 |

|------------------------------|----|----|----|----|----|

| (Initial value) $ ightarrow$ | 0  | 0  | 0  | 0  | 0  |

#### Register Bank Pointer (RP)

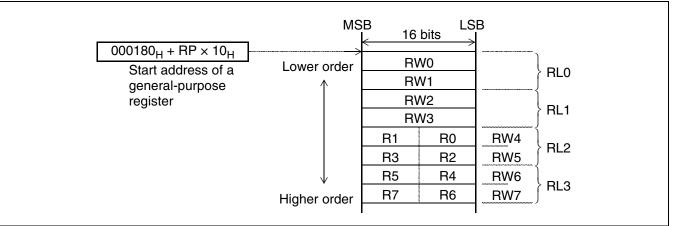

The register bank pointer (RP) indicates the address of an internal RAM area where the general-purpose registers of the  $F^2MC-16LX$  are. The start memory address of a register bank currently in use is represented using the following conversion expression:  $[000180_H + RP \times 10_H]$ . The RP register consists of 5 bits. It can hold any value between " $00_H$ " and " $1F_H$ ". So the start memory address of the register bank can be set in the range between  $000180_H$  and  $00037F_H$ . Therefore, the register bank can be allocated at memory locations in the range between  $000180_H$  and  $00037F_H$ . If the internal RAM area used as an external area, however, it cannot be used as general-purpose registers even if the register bank is within that range. It is possible to transfer 8-bit immediate data to the RP register, but only the lower 5 bits of the data can be used.

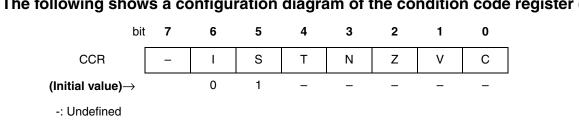

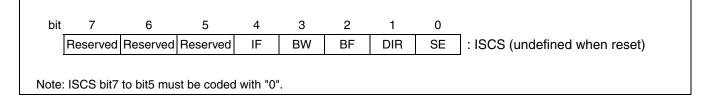

#### Condition Code Register (CCR) 3.4.3

#### The following shows a configuration diagram of the condition code register (CCR).

#### Condition Code Register (CCR)

- ٠ I (Interrupt enable flag): If the I flag is "1", all non-software interrupts are acceptable. If the flag is "0", they are disabled. The flag is cleared by a reset.

- S (Stack flag): If the S flag is "0", the user stack pointer (USP) is active as a pointer for stack manipulation. If the flag is "1", the system stack pointer (SSP) is active. The flag is set at a reset and when an interrupt is accepted.

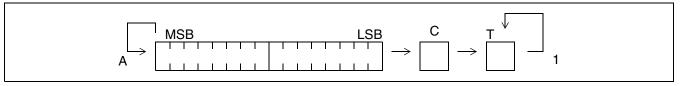

- ٠ T (Sticky bit flag): If at least one bit read from the C flag is "1" when a logical shift right instruction or an arithmetic shift right instruction is executed, this flag becomes "1". Otherwise, the flag becomes "0". The flag becomes "0" also if the amount of shifting is "0".

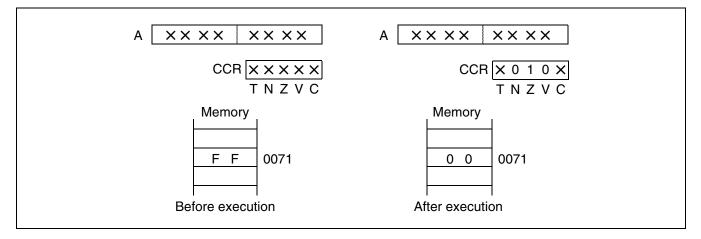

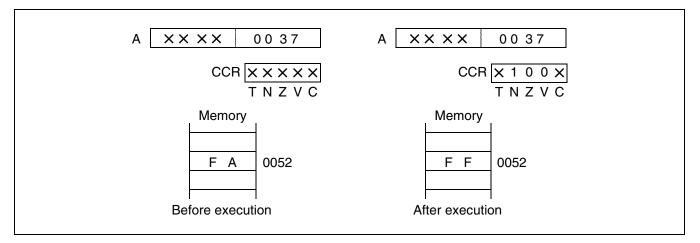

- N (Negative flag): If the most significant bit of an arithmetic or logical operation result is "1", this flag ٠ is set. If it is "0", this flag is cleared.

- Z (Zero flag): If the result of an arithmetic or logical operation is all "0"s, this flag is set. Otherwise, it is cleared.

- V (Overflow flag): This flag is set if a digit overflow occurs in a signed value generated as the result of an arithmetic or logical operation. Otherwise, the flag is cleared.

- C (Carry flag): This flag is set if an arithmetic or logical operation causes a carry from or a borrow to the most-significant bit. Otherwise, the flag is cleared.

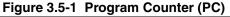

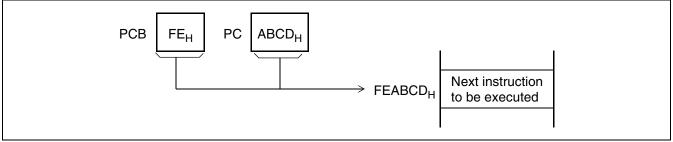

# 3.5 **Program Counter (PC)**

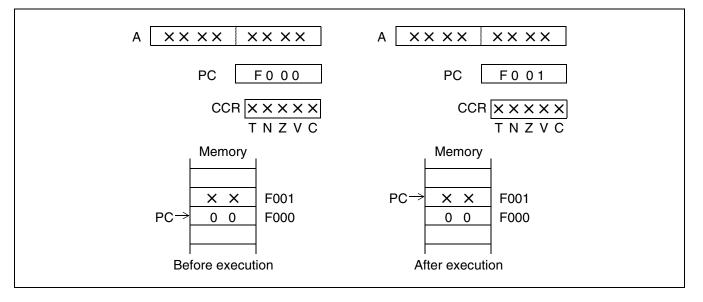

# The program counter (PC) consists of 16 bits. It indicates the upper 16 bits of a memory address where the next instruction to be executed by the CPU.

#### ■ Program Counter (PC)

The program counter (PC) consists of 16 bits. It indicates the lower 16 bits of a memory address where the next instruction to be executed by the CPU is (see Figure 3.5-1). The upper 8 bits of the memory address are indicated in the program bank register (PCB). The content of the PC register is updated, when a conditional branch or subroutine call instruction is executed, upon an interrupt occurrence, or at a reset. The PC register is used also as a base pointer for reading an operand.

# 3.6 Direct Page Register (DPR)

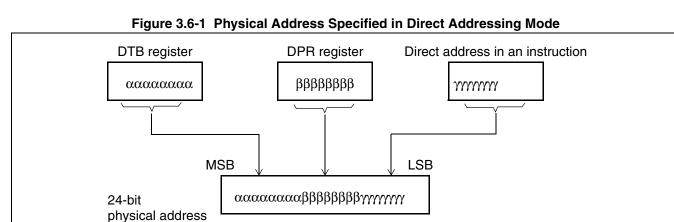

# The direct page register (DPR) specifies bits 8 to 15 (addr8 to addr15) of an operand address for an instruction in direct addressing mode.

#### ■ Direct Page Register (DPR)

The direct page register (DPR) specifies bits 8 to 15 (addr8 to addr15) of an operand address for an instruction in direct addressing mode, as shown in Figure 3.6-1. The DPR register is 8 bits long. It is initialized to " $01_{\rm H}$ " at a reset. It can be read- and write-accessed by an instruction.

# 3.7 Bank Registers

The following 5 bank registers are available in the  $F^2MC-16LX$ .

- Program bank register (PCB)

- Data bank register (DTB)

- User stack bank register (USB)

- System stack bank register (SSB)

- Additional data bank register (ADB)

These registers indicate memory banks allocated for the program, data, user stack, system stack, and additional spaces, respectively.

#### Bank Registers

All of these bank registers are 1 byte length. At a reset, the PCB register is initialized to " $0FF_H$ ", and the other registers, to " $00_H$ ". The PCB register can be read-accessed, but not write-accessed. The other bank registers can be both read- and write-accessed. The content of the PCB register is updated, when a JMPP, CALLP, RETP, or RETI instruction for a branch anywhere in the 16-Mbyte space is executed or an interrupt occurs. See "CHAPTER 2 MEMORY SPACE" for descriptions about the operation of each register.

# CHAPTER 4 GENERAL-PURPOSE REGISTERS

The registers of the  $F^2MC-16LX$  can be grouped into two major categories: dedicated registers in the CPU and general-purpose registers allocated in memory. This chapter describes the  $F^2MC-16LX$  general-purpose registers. These registers are allocated in a RAM in address space of the CPU. Similarly to the dedicated registers, the general-purpose registers can be accessed without specifying their address. However, the user can specify the purpose for which they are used in the same manner as for ordinary memory.

- 4.1 Register Banks in RAM

- 4.2 Calling General-purpose Registers in RAM

# 4.1 Register Banks in RAM

Each register bank consists of 8 words (16 bytes). They can be used as generalpurpose registers (byte registers R0 to R7, word registers RW0 to RW7, and long word registers RL0 to RL3) for performing various types of operations and specifying pointers. RL0 to RL3 can be used also as a linear pointer to gain direct access to all spaces in memory.

#### Register Banks in RAM

Table 4.1-1 lists the function of each register, and Table 4.1-2 shows relationships between the registers.

| Register name | Function                                                                                                                                             |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0 to R7      | Used to hold an operand in various types of instructions.<br>Note: R0 is also used as a barrel shift counter and a counter of normarize instruction. |

| RW0 to RW7    | Used to hold a pointer.<br>Used to hold an operand in various types of instructions.<br>Note: RW0 is used also as a string instruction counter.      |

| RL0 to RL3    | Used to hold a long pointer.<br>Used to hold an operand in various types of instructions.                                                            |

Table 4.1-1

Functions of Each Register

#### Table 4.1-2 Relationship between Registers

|    | RW0  | RL0 |

|----|------|-----|

|    | RW1  | RLU |

|    | RW2  | RL1 |

|    | RW3  | RLI |

| R0 | RW4  |     |

| R1 | U114 | RL2 |

| R2 | RW5  | nL2 |

| R3 | RVV3 |     |

| R4 | RW6  |     |

| R5 | UAAU | RL3 |

| R6 | RW7  | nlo |

| R7 | UAA1 |     |

For general-purpose registers of the  $F^2MC-16LX$ , the register bank pointer (RP) is used to specify where in internal RAM between  $000180_H$  and  $00037F_H$  the register bank currently in use is allocated.

#### Calling General-purpose Registers in RAM

The general-purpose registers of the  $F^2MC-16LX$  are allocated in internal RAM between  $000180_H$  and  $00037F_H$  (in maximum configuration). The register bank pointer (RP) is used to indicate where in internal RAM between  $000180_H$  and  $00037F_H$  the register bank currently in use is allocated. Each bank contains the following 3 different registers. These registers are not independent of one another. Instead, they have the relationships shown in Figure 4.2-1.

- R0 to R7: 8-bit general-purpose registers

- RW0 to RW7: 16-bit general-purpose registers

- RL0 to RL3: 32-bit general-purpose registers

#### Figure 4.2-1 General-purpose Registers

The relationships among the high- and low-order bytes in word registers (RW4 to RW7) and byte registers (R0 to R7) are represented using the following expression:

RW  $(i + 4) = R (i \times 2 + 1) \times 256 + R (i \times 2)$  [where i = 0 to 3]

The relationships among the high- and low-order bytes in long registers (RL0 to RL3) and word registers (RW0 to RW7) are represented using the following expression:

RL (i) = RW (i  $\times 2 + 1$ )  $\times 65536 + RW$  (i  $\times 2$ ) [where i = 0 to 3]

For example, if the data in R1 and the data in R0 are arranged as high- and low-order bytes, respectively, the resulting data equals the data (2 bytes) in RW4.

#### CHAPTER 4 GENERAL-PURPOSE REGISTERS

# CHAPTER 5 PREFIX CODES

The operation of an instruction can be modified by prefixing it with prefix code. The following 3 types of prefix codes are available.

- Bank select prefix

- Common register bank prefix

- Flag change inhibit prefix code

This chapter describes these prefixes.

- 5.1 Bank Select Prefix

- 5.2 Common Register Bank Prefix (CMR)

- 5.3 Flag Change Inhibit Prefix Code (NCC)

- 5.4 Constraints Related to the Prefix Codes

## 5.1 Bank Select Prefix

# Placing a bank select prefix before an instruction enables selecting the memory space accessed by the instruction regardless of what the current addressing mode is.

#### Bank Select Prefix

The memory space of data to be accessed is determined according to the addressing mode. Placing a bank select prefix before an instruction enables to select the memory space accessed by the instruction regardless of what the current addressing mode is. Table 5.1-1 lists the bank select prefixes and the memory space selected according to each bank select prefix.

Table 5.1-1 Bank Select Prefixes

| Bank select prefix | Memory space to be selected                                         |

|--------------------|---------------------------------------------------------------------|

| РСВ                | Program counter space                                               |

| DTB                | Data space                                                          |

| ADB                | Additional space                                                    |

| SPB                | System or user stack space depending on the state of the stack flag |

Be careful when using the following instructions.

Transfer instructions (I/O access)

| MOV A,io  | MOV io, A    | MOVX A,io      | MOVW A,io |

|-----------|--------------|----------------|-----------|

| MOVW io,A | MOV io,#imm8 | MOVW io,#imm16 |           |

These instructions access the I/O space regardless of whether there is a prefix before them.

#### Branch instruction

#### RETI

The system stack bank (SSB) is used regardless of whether there is a prefix before the branch instruction.

• Bit manipulation instructions (I/O access)

| MOVB A,io:bp | MOVB io:bp,A  | SETB io:bp    |

|--------------|---------------|---------------|

| CLRB io:bp   | BBC io:bp,rel | BBS io:bp,rel |

| WBTC         | WBTS          |               |

The I/O space is accessed regardless of whether there is a prefix before those instructions.

#### String manipulation instructions

MOVS MOVSW SCEQ SCWEQ FILS FILSW

A bank register specified in the operand is used regardless of whether there is a prefix before these instructions.

Other types of control instructions (stack manipulation)

PUSHW POPW

The system stack bank (SSB) or user stack bank (USB) is used depending on the state of the S flag, regardless of whether there is a prefix before these instructions.

POPW PS

In the following cases, the prefix of an instruction affects not only that instruction but also an instruction that follows it.

Other types of control instructions (flag change)

AND CCR,#imm8 OR CCR,#imm8

The operations of these instructions are performed normally. The prefix of each of these instructions affects not only the instructions but also an instruction that follows them.

Another type of control instruction (interrupt control)

MOV ILM,#imm8

The operation of the instruction is performed normally. The prefix of the instruction affects not only that instruction but also an instruction that follows it.

## 5.2 Common Register Bank Prefix (CMR)

Placing a common register bank prefix (CMR) before an instruction accessing a register bank enables to change that the instruction is to access only the registers in a common bank (register bank selected when RP = 0) allocated between  $000180_{\text{H}}$  and  $00018F_{\text{H}}$ , regardless of what the current value of the register bank pointer (RP) is.

#### Common Register Bank Prefix (CMR)

To make data exchange among tasks easier, it is necessary to use a method that can access a certain specified register bank relatively easily no matter what value the RP register holds. To meet this requirement, the  $F^2MC$ -16LX has a register bank that can be used by all tasks in common. It is called a common bank. The common bank is allocated in memory between address  $000180_H$  and  $00018F_H$ . It is selected when the RP register contains a value of "0".

Placing the common register bank prefix (CMR) before an instruction accessing a register bank enables to change that the instruction is to access only the registers in a common bank (register bank selected when RP = 0) allocated between  $000180_{\text{H}}$  and  $00018F_{\text{H}}$ , regardless of what the current value of the register bank pointer (RP) is.

Be careful when using the following instructions.

#### String instructions

#### MOVS NOVSW SCEQ FILS FILSW

If an interrupt is requested during execution of a string manipulation instruction attached with a prefix code, the prefix becomes ineffective for the string manipulation instruction after a return is made from the interrupt handling routine, possibly resulting in a malfunction. Do not place the CMR prefix before these string manipulation instructions.

#### • Other types of control instructions (flag change)

AND CCR,#imm8 OR CCR,#imm8 POPW PS

The operations of these instructions are performed normally. The prefix of each of these instructions affects not only the instructions but also an instruction that follows them.

#### • MOV ILM,#imm8

The operation of the instruction is performed normally. The prefix of the instruction affects not only that instruction but also an instruction that follows it.

# 5.3 Flag Change Inhibit Prefix Code (NCC)

# Placing the flag change inhibit prefix code (NCC) before an instruction inhibits flags from changing during execution of the instruction.

#### Flag Change Inhibit Prefix Code (NCC)

The flag change inhibit prefix code (NCC) is used to suppress undesired changes to flags. Placing the NCC prefix before an instruction inhibits flags from changing during execution of the instruction. Be careful when using the following instructions.

Branch instructions

INT #vct8 INT9 INT addr16

INTP addr24 RETI

These instructions change the flags in the condition code register (CCR) regardless of whether there is a prefix before them.

#### String instructions

MOVE MOVSW SCEQ SCWEQ FILS FISW

If an interrupt is requested during execution of a string manipulation instruction attached with a prefix code, the prefix becomes ineffective for the string manipulation instruction after a return is made from the interrupt handling routine, possibly resulting in a malfunction. Do not place the NCC prefix before these string manipulation instructions.

Another type of control instruction (task switching)

JCTX @A

This instruction changes the flags in the CCR register regardless of whether there is a prefix before it.

Other types of control instructions (flag change)

AND CCR,#imm8 OR CCR,#imm8 POPW PS

These instructions change the flags in the CCR register regardless of whether there is a prefix before them. The prefix of each of these instructions affects not only the instructions but also an instruction that follows them.

Another type of control instruction (interrupt control)

#### MOV ILM,#imm8

The operation of the instruction is performed normally. The prefix of the instruction affects not only that instruction but also an instruction that follows it.

# 5.4 Constraints Related to the Prefix Codes

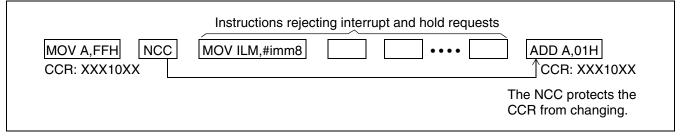

If a prefix code is placed before an instruction where interrupt and hold requests are inhibited, the effect of the prefix code lasts until an instruction where neither an interrupt nor hold request is inhibited appears for the first time, as shown in Figure 5.4-2.

If a prefix is followed by conflicting prefix codes, the last one is valid.

#### Relationships between Instructions Rejecting Interrupt Requests and Prefix Codes

The following 10 instructions/prefix codes reject interrupt and hold requests.

- MOV ILM,#imm8

- AND CCR,#imm8

- OR CCR,#imm8

- POPW PS

• PCB

- ADB DTB

- NCCSPB

- CMR

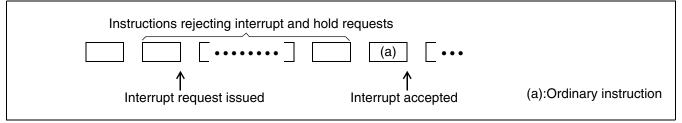

If an interrupt or hold request is issued during execution of any of the above instructions, the request is accepted only after any instruction not listed above appears for the first time after that instruction and is executed, as shown in Figure 5.4-1.

#### Figure 5.4-1 Instructions Rejecting Interrupt and Hold Requests

If a prefix code is placed before an instruction rejecting interrupt and hold requests, its effect lasts until an instruction other than instructions rejecting interrupt and hold requests appears for the first time after the prefix code and is executed, as shown in Figure 5.4-2.

#### Figure 5.4-2 Instructions Rejecting Interrupt and Hold Requests and Prefix Code

#### ■ If Two or More Prefix Codes Appear in Succession

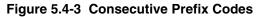

If a prefix is followed by conflicting prefix codes, the last one is valid (see Figure 5.4-3).

The term "conflicting prefix codes" indicates PCB, ADB, DTB, and SPB in the above figure.

#### CHAPTER 5 PREFIX CODES

# CHAPTER 6 INTERRUPT HANDLING

This chapter describes the interrupt function and operation of  $F^2MC-16LX$ .

- 6.1 Interrupt Handling

- 6.2 Hardware Interrupt Operation Flow

- 6.3 Interrupt Handling Flowchart and Saving the Contents of Registers

- 6.4 Interrupt Vectors

- 6.5 Extended Intelligent I/O Service

- 6.6 Interrupt Control Register (ICR)

- 6.7 Meanings of the Bits of Interrupt Control Register (ICR)

- 6.8 Extended Intelligent I/O Service Descriptor (ISD)

- 6.9 Registers of Extended Intelligent I/O Service Descriptor

- 6.10 Exception Processing

## 6.1 Interrupt Handling

In F<sup>2</sup>MC-16LX series, interrupt handling or extended intelligent I/O service is activated by the interrupt request from an internal resource. For interrupt handling, the processing appropriate to the interrupt request is performed by the interrupt handling program. For extended intelligent I/O service, the data transfer between the requesting internal resource and the memory is automatically performed. In addition, a function is provided to stop the execution of the extended intelligent I/O service by the request from the internal resource (such as built-in peripheral circuit).

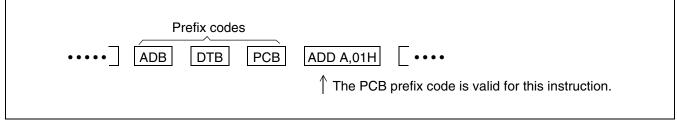

#### Interrupt Handling

To permit an internal resource to make a hardware interrupt request to the  $F^2MC-16LX$  CPU, an interrupt request flag and an interrupt enable flag are required for that resource. The interrupt request flag is set by the occurrence of an event specific to the internal resource. When the interrupt request flag indicates the request being made and the interrupt enable flag is set to the enabled state, a hardware interrupt request is issued from the internal resource.

In the case of the internal resource that requires the activation of the extended intelligent I/O service accompanied by the occurrence of a hardware interrupt request, an extended intelligent I/O service enable (ISE) flag is provided in the interrupt control register (ICR) in the interrupt controller associated with that resource.

The occurrence of an interrupt request with the ISE flag set to "1" activates the extended intelligent I/O service. If only normal hardware interrupt requests are intended, set the ISE flag to "0".

For interrupt requests by the execution of the INT instruction, which are software interrupts, no interrupt request and enable flags are applied. Whenever the INT instruction is executed, an interrupt request occurs.

Any interrupt level of hardware interrupt request can be assigned to a given group regarding interrupt request. Interrupt levels are specified by the interrupt level setting bits (IL0, IL1, and IL2) in the ICR register in the interrupt controller. It is possible to specify eight interrupt level settings 0 to 7. Definition of the interrupt levels is such that "0" is the highest and "6" is the lowest.

From a group set to interrupt level 7, no interrupt requests can be made. Hardware interrupt requests are maskable (enabled/disabled) by the I flag in the condition code register (CCR) of the processor status (PS) and the ILM register (ILM0, ILM1, and ILM2).

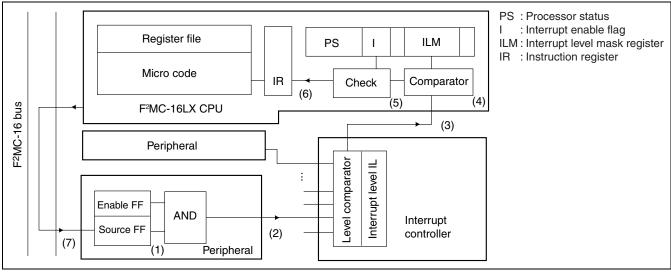

When an unmasked interrupt request occurs, the CPU takes the following actions:

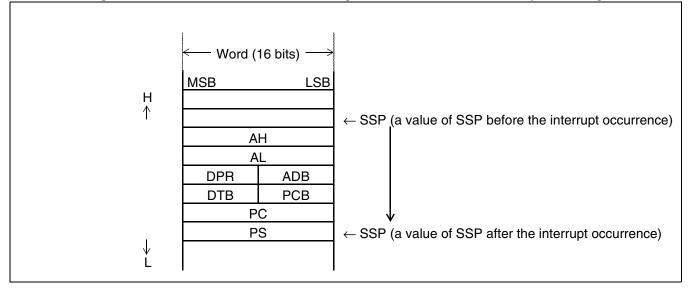

- (1) Saves the data (12 bytes) held by the following registers into the memory area indicated by the system stack bank register (SSB) and the system stack pointer (SSP).

- Processor status (PS)

- Program counter (PC)

- Program bank register (PCB)

- Data bank register (DTB)

- Additional data bank register (ADB)

- Direct page register (DPR)

- Accumulator (A)

- (2) Reads the interrupt vector in 3 bytes to PC and PCB.