# MM TIMING TECHNOLOGY PRODUCTS

# Timing Technology Products Data Book

IC DESIGNS is a trademark of Cypress Semiconductor Corporation. Cypress Semiconductor, 3901 North First St., San Jose, CA 95134 (408) 943–2600 Telex: 821032 CYPRESS SNJ UD, TWX: 910 997 0753, FAX: (408) 943–2741

Published December 1993

<sup>©</sup> Cypress Semiconductor Corporation, 1993. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor Corporation product. Nor does it convey or imply any license under patent or other rights. Cypress Semiconductor does not authorize its products for use as critical components in life-support systems where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems applications implies that the manufacturer assumes all lak of such use and in so doing indomnifies Cypress Semiconductor against all damages.

#### Backgrounder

Founded in April 1983, Cypress Semiconductor Corporation produces high-performance integrated circuits for a range of growth markets. Cypress currently offers 250 products in 6 targeted product areas: static random access memories (SRAMs), programmable logic devices (PLDs), data communications, programmable read-only memories (PROMs), multichip modules, and timing technology devices. Cypress products address these markets as leaders in speed and functionality, taking advantage of the world's most advanced process technologies. Cypress is a complete semiconductor manufacturer, performing its own process development, circuit design, wafer fabrication, assembly, and test.

Cypress products all have one thing in common -- high performance. Cypress has built a reputation throughout the industry and with its customers for providing the highest-speed products in every market it enters. It continues to bring to market new, leading-edge products, produced with Cypress's CMOS (complementary metal-oxide semiconductor), BiCMOS, and Flash process technologies. Cypress has 0.8- and 0.65-micron CMOS and BiCMOS processes, a 0.5 micron BiCMOS process, and Flash at 0.65 micron. These process technologies allow Cypress to offer state-of-the-art products that provide the optimal balance of speed and power usage for any system. Development efforts are underway to further shrink the feature sizes of Cypress process technologies, thereby increasing speed, and decreasing die size and costs.

Cypress also offers a broad range of packaging options for its products, giving customers a variety of choices of cost, pin-out configurations, and temperature grades. In addition, all Cypress products are designed to meet or exceed the full temperature and functional requirements of military products. This means that Cypress builds products to military specifications as a matter of course.

Cypress's IC Designs Division, based in Kirkland, Washington, is the leading innovator in timing technology products. IC Designs products use frequency synthesis technology to offer a complete line of programmable clock oscillators for the world's leading personal computer manufacturers.

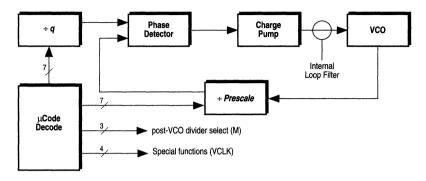

Frequency synthesis devices are built using phase-locked loops (PLLs), basic oscillators that are well known to analog circuit designers. In a frequency synthesis device, the entire functionality of a PLL is produced by a single monolithic integrated circuit. No external components are required, and sophisticated internal damping and filtering eliminate the adjustments that are often required in analog circuits. A frequency synthesis device behaves in the same way as a digital device, and can be incorporated into a circuit using familiar digital design principles and techniques.

Frequency synthesis technology was first applied to graphics cards in personal computers. Color Graphics Adapter (CGA), Enhanced Graphics Adapter (EGA), Video Graphics Array VGA, and other graphics systems write to the screen at different resolutions and intervals, and therefore require different reference frequencies. As these standards have proliferated, designs often call for as many as five different reference frequencies (i.e., five metal can oscillators) on a single board. Manufacturers of graphics boards have recognized the obvious cost and space advantages of frequency synthesis technology. The technology has found applications on computer motherboards as well.

As technology in the PC marketplace has become more complex, frequency synthesis technology has become an enabling technology -- the key to many new products and capabilities. The latest applications

for these devices include "green PCs," laptop computers, PentiumÀ) À-based and other high-performance systems, accelerator boards, multimedia video, and new generations of metal can oscillators.

IC Designs offers system logic products, graphic products, programmable products, and embedded crystal products. System logic products include clock generators for PC motherboards, workstations, laptops, and PC clones. Graphic products include a VGA clock generator, dual programmable clock generators for both graphics and ECL/TTL, and a low-voltage programmable graphics clock generator. IC Designs programmable products include both a programmable clock oscillator and a dual programmable clock oscillator. Embedded crystal products include the programmable products with embedded reference crystals, and QuiXTAL, the innovative, one-time programmable metal can oscillator.

IC Designs products are used widely in personal computers and mass storage systems. IC Designs clock oscillators control the intricate timing of all aspects of a computer system, including signals for the computer's central processing unit (CPU), keyboard, disk drives, system bus, serial port, and real-time clock. They replace all of the metal can oscillators used in the system.

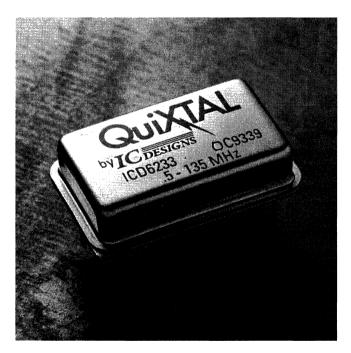

IC Designs' QuiXTAL is a programmable metal can oscillator which replaces individual oscillators used to control timing signals in virtually every type of electronics equipment. QuiXTAL can be programmed in just one day to any frequency, providing users the ability to make last-minute frequency adjustments, speeding time to market. QuiXTAL takes frequency synthesis beyond the PC market, and addresses the broad market segments of electronic instrumentation, telecommunications equipment, and medical systems.

IC Designs products will be produced in Cypress's production facilities in San Jose, California; Round Rock, Texas; and Bloomington, Minnesota. Cypress's high-volume, low-cost manufacturing capability and IC Designs' expertise in timing technology are yielding new, faster products for this rapidly growing market.

| 1 – Motl   | nerboard Frequency Synthesizers                 |           | 1   |

|------------|-------------------------------------------------|-----------|-----|

| ICD2023    | PC Motherboard Clock Generator                  | 3         |     |

| ICD2025    | Motherboard Clock Generator                     | 23        |     |

| ICD2027    | PC Motherboard Clock Generator                  | 39        |     |

| ICD2028    | PC Motherboard Clock Generator                  | 55        |     |

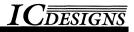

| ICD2093    | "Super-Buffer" Clock Generator                  | <b>79</b> |     |

| 2 – Low    | -Power System Logic                             |           | 101 |

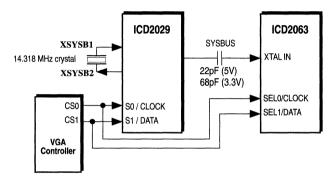

| ICD2029    | PC Notebook/Subnotebook/Palmtop Clock Generator | 103       |     |

| ICD20291   | PC Notebook/Subnotebook/Palmtop Clock Generator | 105       |     |

| 3 – Graj   | ohics Frequency Synthesizers                    |           | 107 |

| ICD2042A   | Dual VGA Clock Generator                        | 109       |     |

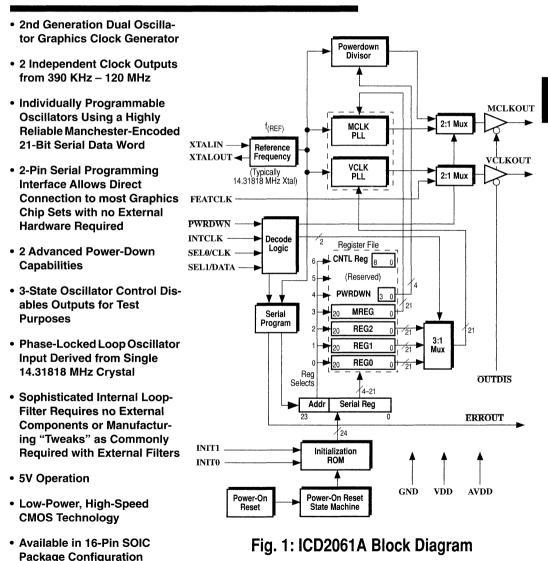

| ICD2061A   | Dual Programmable Graphics Clock Generator      | 125       |     |

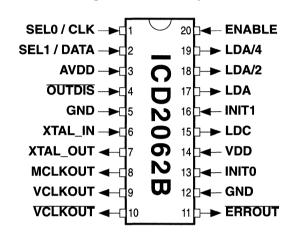

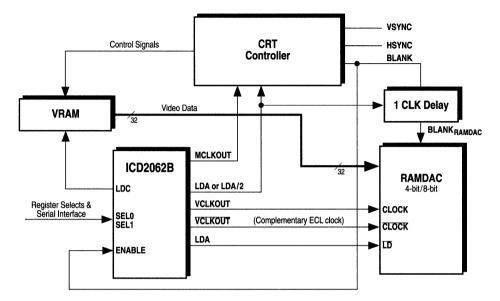

| ICD2062B   | Dual Programmable ECL/TTL Clock Generator       | 159       |     |

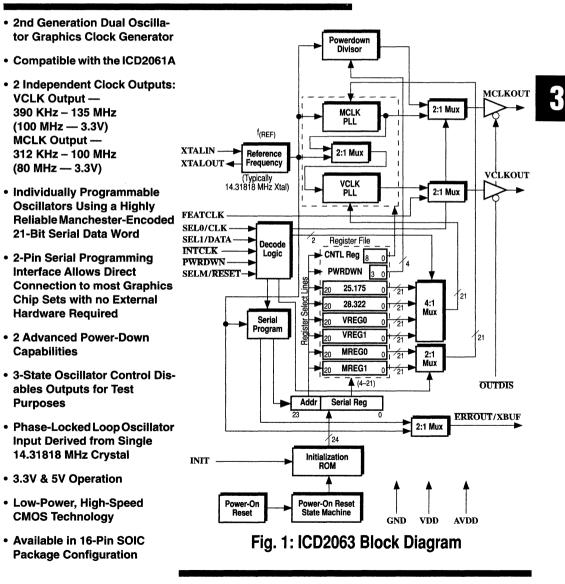

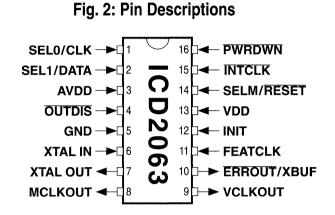

| ICD2063    | Programmable Graphics Clock Generator           | 195       |     |

| 4 – Prog   | rammable Products                               |           | 239 |

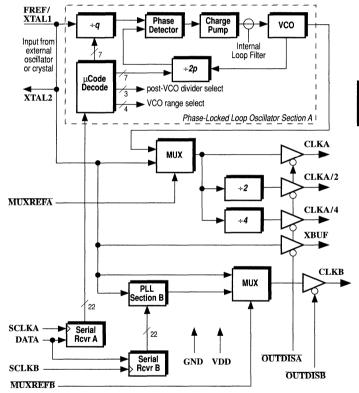

| ICD2051    | Dual Programmable Clock Oscillator              | 241       |     |

| f2PC Board | High-Performance Frequency Generator            | 261       |     |

| 5 – QuiX   | <b>KTAL Embedded Crystal Products</b>           |           | 265 |

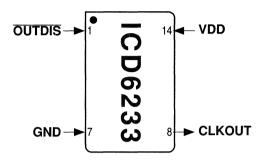

| ICD6233    | One-Time Programmable Clock Oscillator          | 267       |     |

| ICD6151    | Dual Programmable Clock Oscillator              | 275       |     |

| ICD6053    | 3-State HCMOS Programmable Clock Oscillator     | 277       |     |

| ICDESIGNS                             | Table of Contents |

|---------------------------------------|-------------------|

| 6 – Application Notes                 | 279               |

| Power Feed and Board Layout Issues    | 281               |

| Minimizing Radio Frequency Emissions  | 285               |

| ECL Outputs                           | 289               |

| Crystal Oscillator Topics             | 292               |

| Externally Driven Crystal Oscillator  | 295               |

| Revision History / Credits            | 298               |

| 7 – Quality Assurance and Reliability | 299               |

| Introduction                          | 301               |

| Revision History / Credits            | 305               |

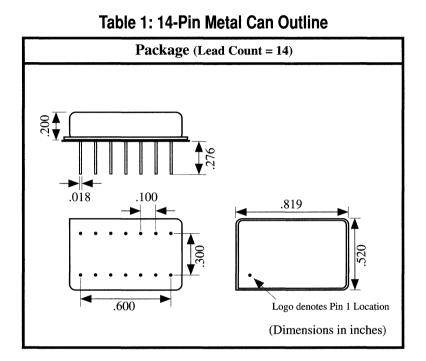

| 8 – Package Information               | 307               |

| 14-Pin Packages                       | 309               |

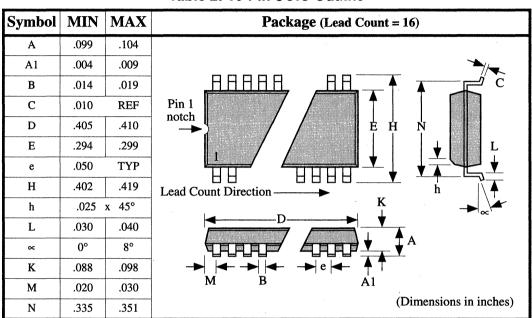

| 16-Pin Packages                       | 310               |

| 20-Pin Packages                       | 311               |

## Motherboard Frequency Synthesizers

1

## **1 – Motherboard Frequency Synthesizers**

| <i>ICD2023</i> | PC Motherboard Clock Generator | 3  |

|----------------|--------------------------------|----|

| ICD2025        | Motherboard Clock Generator    | 23 |

| ICD2027        | PC Motherboard Clock Generator | 39 |

| ICD2028        | PC Motherboard Clock Generator | 55 |

| ICD2093        | "Super-Buffer" Clock Generator | 79 |

#### CONTENTS

# ICD2023

#### **PC Motherboard Clock Generator**

Industry Standard Single-Chip Oscillator for 486/386/286 Personal Computer Motherboards

## **Contents**

| Introduction                                      | 5  | •  |

|---------------------------------------------------|----|----|

| Pin & Signal Descriptions                         | 6  |    |

| General Considerations                            | 8  |    |

| Fixed Frequency Oscillator Operation              |    |    |

| CPUCLK Programmable Oscillator:<br>Selection Mode |    | ł  |

| CPUCLK Programmable Oscillator:<br>Serial Mode    |    |    |

| Programming Constraints                           |    |    |

| ICD2023 Programming Example                       |    |    |

| Output Frequency Accuracy                         |    | •  |

| 3-State Output Operation                          |    | 1  |

| No External Components Required                   |    |    |

| PC Board Routing Issues                           |    |    |

| Circuit Description                               |    |    |

| Minimized Parasitic Problems                      |    |    |

| Stability and "Bit-Jitter"                        |    | ļ  |

| Temperature and Process Sensitivity               |    |    |

| VBATT                                             |    | -  |

| Crystal Operation                                 |    |    |

| Ordering Information                              | 17 |    |

| Device Specifications                             | 18 | 1  |

| Electrical Data                                   |    |    |

| Timing Diagrams                                   |    | 1  |

| <b>Revision History / Credits</b>                 | 22 | 1: |

## **Figures**

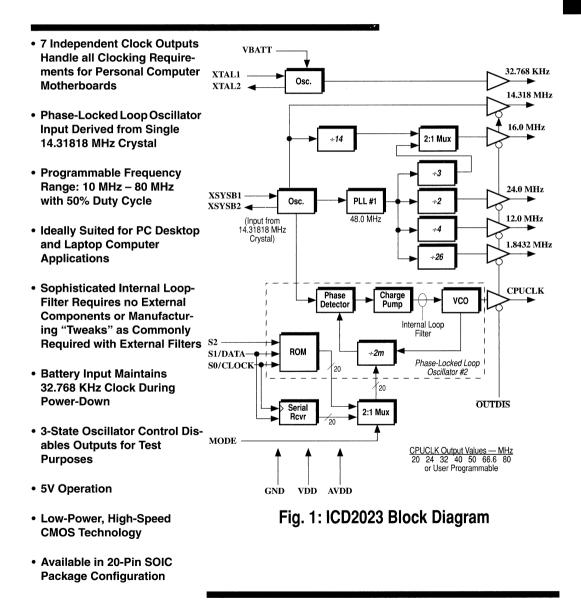

| 1: ICD2023 Block Diagram        | 3  |

|---------------------------------|----|

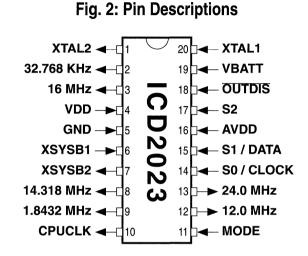

| 2: Pin Descriptions             | 6  |

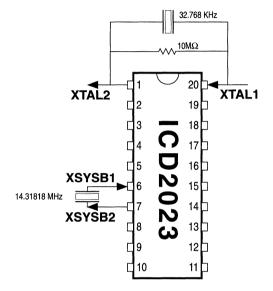

| 3: Crystal Schematic            | 16 |

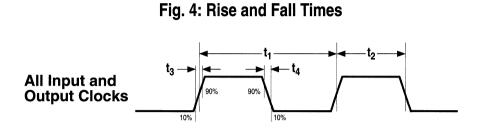

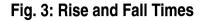

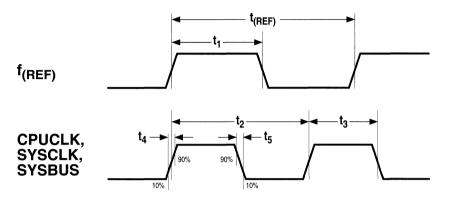

| 4: Rise and Fall Times          | 20 |

| 5: Serial Programming<br>Timing | 20 |

| 6: 3-State Timing               | 21 |

## Tables

| 1: Signal Descriptions                   | 6  |

|------------------------------------------|----|

| 2: Fixed Frequency Oscillator<br>Outputs | 8  |

| 3: CPUCLK Output with<br>MODE = 1        | 9  |

| 4: Programming Word Bit<br>Fields        | 9  |

| 5: Mux Bits M0–M1                        | 10 |

| 6: Mux Bit M2                            | 10 |

| 7: Index Field (I)                       | 11 |

| 8: Possible P & Q values                 | 12 |

| 9: Order Codes                           | 17 |

| 10: Absolute Maximum<br>Ratings          | 18 |

| 11: DC Characteristics                   | 18 |

| 12: AC Characteristics                   | 19 |

|                                          |    |

## Introduction

A modern personal computer motherboard often requires as many as six different crystal can oscillators. A new family of frequency synthesis parts from IC DESIGNS replaces the large number of the oscillators required to build such multi-function motherboards. These parts synthesize all the required frequencies in a single monolithic device, thus lowering manufacturing costs and significantly reducing the printed circuit board space required.

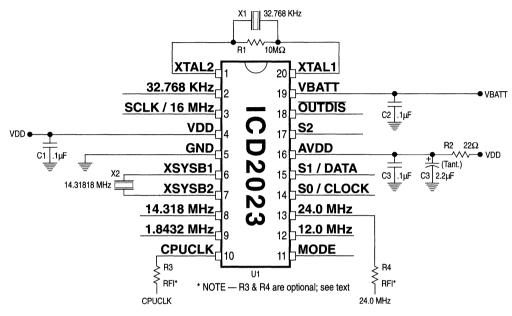

The ICD2023 PC-AT Motherboard Clock Generator offers 2 oscillators, 2 phase-locked loops and 7 different outputs in a single package. Six of the outputs are of a fixed value while the seventh oscillator is fully user-programmable and may be changed "on the fly" to any desired frequency value between 10 MHz and 80 MHz. The ICD2023 is ideally suited for use in both existing designs (since it requires no support from the motherboard chip set and outputs 7 frequencies concurrently) and new designs which can utilize the programmable nature of this device.

## **Pin & Signal Descriptions**

#### **Table 1: Signal Descriptions**

| Pin # | Signal     | . Function                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1     | XTAL2      | Oscillator Output to a 32.768 KHz Parallel-Resonant Crystal                                                                                                                                                                                                                                                                                                                                  |  |

| 2     | 32.768 KHz | 32.768 KHz Output                                                                                                                                                                                                                                                                                                                                                                            |  |

| 3     | 16 MHz     | 16 MHz Output                                                                                                                                                                                                                                                                                                                                                                                |  |

| 4     | VDD        | +5V to I/O Ring                                                                                                                                                                                                                                                                                                                                                                              |  |

| 5     | GND        | Ground                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 6     | XSYSB1     | Input Reference Oscillator for all Phase-Locked Loops (nominally 14.31818 MHz). An optional PC System Bus Clock Signal may be used as if available.                                                                                                                                                                                                                                          |  |

| 7     | XSYSB2     | Oscillator Output to a reference Series-Resonant Crystal. For higher accuracy, a Parallel-Resonant Crystal may be used. Assume CLOAD $\approx$ 17pF. For more information on crystal requirements, please refer to the IC DESIGNS Application Note <i>Crystal Oscillator Topics</i> on page 292. (Pin is no-connect if external reference oscillator or PC System Bus clock signal is used.) |  |

#### Table 1: Signal Descriptions (Continued)

| Pin # | Signal     | Function                                                                                                                                                                                |  |

|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 8     | 14.318 MHz | 14.31818 MHz Output                                                                                                                                                                     |  |

| 9     | 1.8432 MHz | 1.8432 MHz Output                                                                                                                                                                       |  |

| 10    | CPUCLK     | CPUCLK Programmable Oscillator Output (See <i>Table 3: CPUCLK Output with MODE = 1</i> on page 9)                                                                                       |  |

| 11    | MODE       | MODE=0, CPUCLK is in programmable mode<br>MODE=1, CPUCLK is in selection mode                                                                                                           |  |

| 12    | 12.0 MHz   | 12.0 MHz Output                                                                                                                                                                         |  |

| 13    | 24.0 MHz   | 24.0 MHz Output                                                                                                                                                                         |  |

| 14    | S0/CLOCK   | MODE=0, S0 is serial clock input line for CPUCLK<br>MODE=1, S0 is select line for CPUCLK (Internal pull-up)                                                                             |  |

| 15    | S1 / DATA  | MODE=0, S1 is serial data input line for CPUCLK<br>MODE=1, S1 is select line for CPUCLK (Internal pull-up)                                                                              |  |

| 16    | AVDD       | +5 volts to Analog Core                                                                                                                                                                 |  |

| 17    | S2         | MODE=0 & S2=1: CPUCLK=(14.31818 MHz) reference frequency<br>MODE=1, S2 is select line for CPUCLK (Internal pull-down)                                                                   |  |

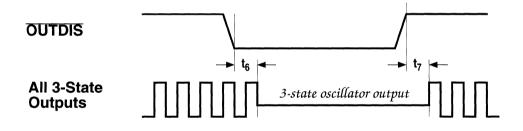

| 18    | OUTDIS     | Output Disable (3-State Output Enable) when signal is pulled low. (Internal pull-<br>up for no-connect if 3-state operation is not needed.)                                             |  |

| 19    | VBATT      | +5V for battery backup operation                                                                                                                                                        |  |

| 20    | XTAL1      | Oscillator input from a 32.768 KHz crystal. For more information on crystal requirements, please refer to the IC DESIGNS Application Note <i>Crystal Oscillator Topics</i> on page 292. |  |

## **General Considerations**

#### **Fixed Frequency Oscillator Operation**

The following table describes each output:

| Output Clock<br>Function | Desired Freq.<br>(MHz) | Actual Freq.<br>(MHz) | PPM<br>Error | Notes                          |

|--------------------------|------------------------|-----------------------|--------------|--------------------------------|

| Real-Time Clock          | 32.768 KHz             | 32.768 KHz            | 0            | Pass-through 32.768 KHz XTAL   |

| System Bus               | 14.318                 | 14.318                | 0            | Pass-through 14.31818 MHz XTAL |

| Int. Bus Clock           | 16.000                 | 15.983                | 1058         | VCO = 47.94295 / 3             |

| Keyboard Clock           | 12.000                 | 11.987                | 1058         | VCO = 47.94295 / 4             |

| Floppy Disk Clock        | 24.000                 | 23.975                | 1058         |                                |

| Serial Port              | 1.843                  | 1.844                 | 543          |                                |

#### Table 2: Fixed Frequency Oscillator Outputs

#### **CPUCLK Programmable Oscillator: Selection Mode**

CPUCLK is the programmable oscillator offering two modes of operation. The first mode uses three select lines to select one of 8 different preset frequencies, while the other mode allows the user to program any desired frequency between 10 MHz and 80 MHz. The two different modes are controlled by the MODE signal.

## ICDESIGNS

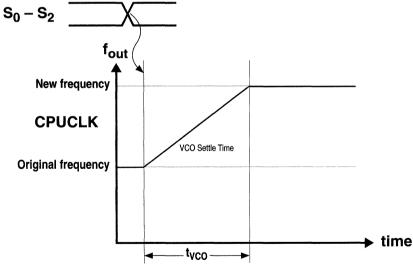

When MODE = 1, the selection lines can be changed to choose different frequencies. When this occurs, PLL #2 section will immediately seek the newly selected frequency as shown in the following table. During the transition period, the CPUCLK output will not glitch.

| <b>S2</b> | <b>S1</b> | <b>S0</b> | Desired Freq.<br>(MHz) | Actual Freq.<br>(MHz) | PPM<br>Error |

|-----------|-----------|-----------|------------------------|-----------------------|--------------|

| 0         | 0         | 0         | 20.000                 | 20.0454               | 2272         |

| 0         | 0         | 1         | 24.000                 | 23.9746               | 1058         |

| 0         | 1         | 0         | 32.000                 | 32.0455               | 1422         |

| 0         | 1         | 1         | 40.000                 | 40.0909               | 2272         |

| 1         | 0         | 0         | 50.000                 | 49.9923               | 154          |

| 1         | 0         | 1         | 66.667                 | 66.5962               | 57           |

| 1         | 1         | 0         | 80.000                 | 80.1818               | 2272         |

| 1         | 1         | 1         | 100.000 <sup>a</sup>   | 99.8182               | 1818         |

#### Table 3: CPUCLK Output with MODE = 1

a. Duty cycle specs not guaranteed above 80 MHz

#### CPUCLK Programmable Oscillator: Serial Mode

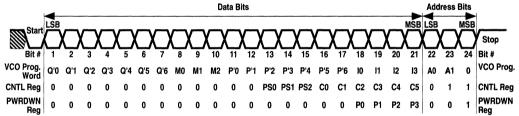

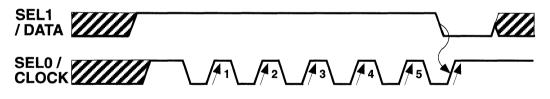

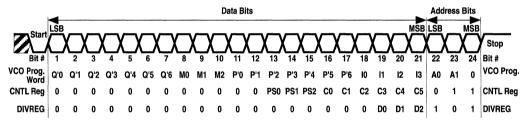

When MODE = 0, CPUCLK enters its programmable mode. Signals S0 (clock) and S1 (data) become a serial interface, allowing a 20-bit number to be shifted in. The ICD2023 programmable oscillator (CPUCLK) requires a 20-bit programming word (W). This word contains 4 fields:

| Field                | # of Bits | Notes                        |

|----------------------|-----------|------------------------------|

| Index (I)            | 4         | MSB (Most Significant Bits)  |

| P Counter value (P') | 7         |                              |

| Mux (M)              | 3         |                              |

| Q Counter Value (Q') | 6         | LSB (Least Significant Bits) |

#### **Table 4: Programming Word Bit Fields**

If signal S2=1 and MODE=0, then the reference frequency (14.31818 MHz) is multiplexed to the CPUCLK output. This enables a glitch-free transition to the reference frequency while the VCO stabilizes.

ICDESIGNS

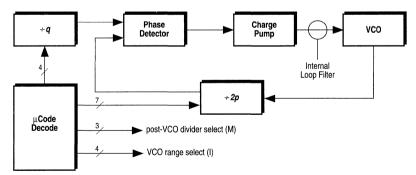

The frequency of the programmable oscillator  $f_{(VCO)}$  is determined by these fields as follows:

$$\begin{aligned} \mathbf{P}' &= \mathbf{P} - 3 \qquad \mathbf{Q}' &= \mathbf{Q} - 2 \\ \mathbf{f}_{(\text{VCO})} &= (2 \times \mathbf{f}_{(\text{REF})} \times \frac{\mathbf{P}}{\mathbf{Q}}) \end{aligned}$$

where  $f_{(REF)}$  = Reference frequency = 14.31818 MHz.

The value of  $f_{(VCO)}$  should be kept between 40 MHz and 80 MHz. Therefore, for output frequencies below 40 MHz,  $f_{(VCO)}$  must be multiplied up into the required range. The mux bits allow a post-divide of the higher VCO to bring the output to those desired values below 40 MHz.

| M <sub>1</sub> M <sub>0</sub> |   | Divisor |

|-------------------------------|---|---------|

| 0                             | 0 | 16      |

| 0                             | 1 | 4       |

| 1                             | 0 | 2       |

| 1                             | 1 | 1       |

#### Table 5: Mux Bits M<sub>0</sub>–M<sub>1</sub>

The M2 mux bit is used to select which one of the two Phase-Locked Loops is to be utilized in the CPUCLK output. Normally, the PLL #2 section (see *Fig. 1: ICD2023 Block Diagram* on page 3) is used. However, if the desired output frequency requires  $f_{(VCO)}$  to be set to 48 MHz, then PLL #1 section should be used. This both reduces power consumption (since only one VCO is activated) and eliminates the possibility of jitter which can arise when 2 VCOs of the same frequency beat (heterodyne) against each other.

#### Table 6: Mux Bit M<sub>2</sub>

| M <sub>2</sub> | CPUCLK          |  |

|----------------|-----------------|--|

| 0              | PLL #2          |  |

| 1              | PLL #1 (48 MHz) |  |

The Index field (I) is used to preset the VCO to an appropriate range. The value for this field should be chosen from the following table. (Note that this table is referenced to the VCO frequency  $f_{(VCO)}$ , rather than to the desired output frequency.)

| I f <sub>(VCO)</sub> MHz |              |  |  |

|--------------------------|--------------|--|--|

| 0001                     | 40.0 - 47.5  |  |  |

| 0010                     | 47.5 - 52.2  |  |  |

| 0011                     | 52.2 - 56.3  |  |  |

| 0100                     | 56.3 - 61.9  |  |  |

| 0101                     | 61.9 - 65.0  |  |  |

| 0110                     | 65.0 - 68.1  |  |  |

| 0111                     | 68.1 - 80.0  |  |  |

| 1111                     | Turn off VCO |  |  |

#### Table 7: Index Field (I)

If the desired VCO frequency lies on a boundary in the table — in other words, if it is exactly the upper limit of one entry and the lower limit of the next — then either index value may be used (since both limits are tested), but we recommend using the higher one.

To assist with these calculations, IC DESIGNS provides *BitCalc* (Part #ICD/BCALC), a Windows<sup>™</sup> program which automatically generates the appropriate programming words from the user's reference input and desired output frequencies, as well as assembling the program words for such things as control and power-down registers. For Macintosh or DOS environments, please ask about availability. Please specify disk size (5" or 3") when ordering *BitCalc*.

#### **Programming Constraints**

There are five primary programming constraints the user must be aware of:

$$f_{(REF)} = 14.31818 \text{ MHz}$$

$$200 \text{ KHz} \le \frac{f_{(REF)}}{Q} \le 1 \text{ MHz}$$

$$40 \text{ MHz} \le f_{(VCO)} \le 80 \text{ MHz}$$

$$3 \le Q \le 65$$

$$4 \le P \le 130$$

. . . . . . .

The constraints have to do with trade-offs between optimum speed with lowest noise, VCO stability, and factors affecting the loop equation. The factors are listed for completeness sake; however, by using the *BitCalc* program all of these constraints become transparent.

#### **ICD2023 Programming Example**

Derive the proper programming word for a 39.5 MHz output frequency, using 14.31818 MHz as the reference frequency:

Since 39.5 MHz < 40 MHz, double it to 79.0 MHz. Set M2, M1 and M0 to 0, 1 and 0, respectively. Set I to 0111. The result:

$$f_{(VCO)} = 79.0 = (2 \times 14.31818 \times \frac{P}{Q})$$

$\frac{P}{Q} = 2.7857$

Several choices of P and Q are available:

| Р  | Q  | f <sub>(VCO)</sub> | Error (in ppm) |

|----|----|--------------------|----------------|

| 69 | 25 | 79.0363            | 460            |

| 80 | 29 | 78.9969            | 40             |

| 91 | 33 | 78.9669            | 419            |

#### Table 8: Possible P & Q values

Choose (P, Q) = (80,29) as this results in the best accuracy (40 ppm).

Therefore:

CDESIGNS

P' = P - 3 = 80 - 3 = 77 = 1001101 (4dH)

$$Q' = Q - 2 = 29 - 2 = 27 = 011011$$

(1bH)

and the full programming word, W, is:

W = I, P', M, Q' = 0111, 1001101, 010, 011011 = 0111100110100011011 (79a9bH)

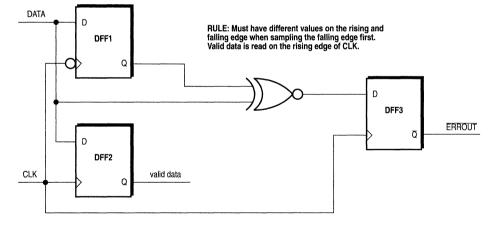

A low-to-high transition on S0 is used to shift the programming word W into S1 as a serial bit stream, LSB first. (See the set-up and hold timing specifications elsewhere in this datasheet.) If more than 20 shifts are performed, only the last 20 data bits received will be retained.

#### **Output Frequency Accuracy**

The accuracy of the ICD2023 output frequencies depends on the target output frequency. As stated previously, the output frequencies of the ICD2023 are an integral fraction of the input reference frequency:

$$f_{(OUT)} = (2 \times f_{(REF)} \times \frac{P}{Q})$$

Only certain output frequencies are possible for a particular reference frequency. However, the ICD2023 normally produces an output frequency within 0.1% of the target frequencies listed. This is more than sufficient to meet standard motherboard requirements. Specifics regarding accuracy are available from the output of the *BitCalc* program.

#### **3-State Output Operation**

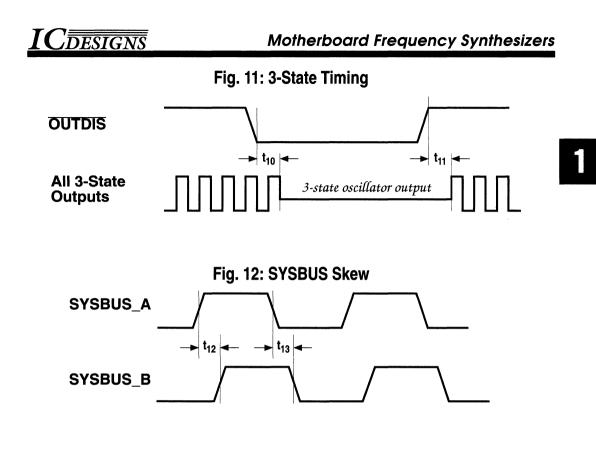

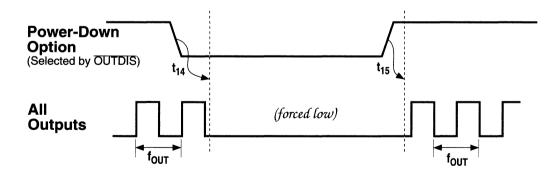

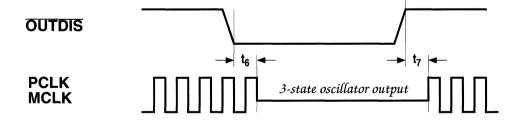

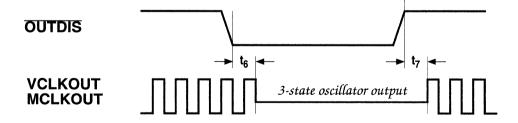

The OUTDIS signal, when pulled low, will 3-state all the clock output lines (except 32.768 KHz). This supports wired-or connections between external clock lines, and allows for procedures such as automated testing where the clock must be disabled. The OUTDIS signal contains an internal pull-up; it can be left unconnected if 3-state operation is not required.

#### **No External Components Required**

Under normal conditions no external components are required for proper operation of any of the internal circuitry of the ICD2023.

#### **PC Board Routing Issues**

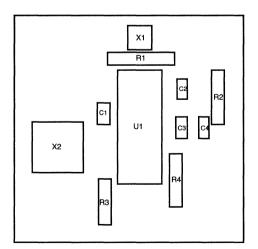

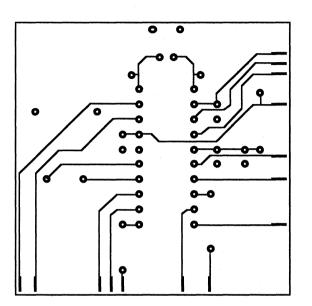

Traditionally, having multiple crystals has allowed the designer to locate them in those places on the board where they are needed. Using a monolithic circuit puts some constraints on the PC board layout to accommodate a single source of all clocks, particularly at frequencies above 50 MHz.

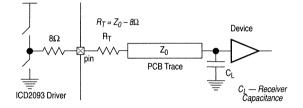

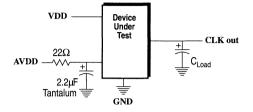

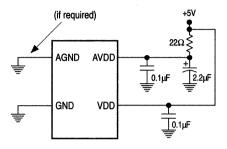

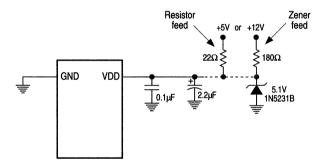

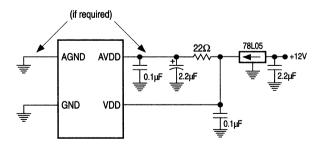

A full power and ground plane layout should be employed both under and around the IC package. The analog power pin (AVDD) should be bypassed to ground with a  $0.1\mu$ F multi-layer ceramic capacitor and a  $2.2\mu$ F/10V tantalum capacitor wired in parallel. Both capacitors should be placed within 0.15" of the power pin. A 22 $\Omega$  resistor placed between the power supply and the AVDD pin can help to filter noisy supply lines. Refer to IC DESIGNS Application Notes *Power Feed and Board Layout Issues* on page 281 and *Minimizing Radio Frequency Emissions* on page 285 for more details and for illustrative schematics.

The designer should also avoid routing any of the output traces of the ICD2023 in close parallel proximity. Large routing lengths and large fanouts add capacitance to output drivers. Capacitance affects the rise and fall times of the outputs. Large fanouts should therefore be buffered, particularly for the highest frequencies.

When designing with this device, it is best to locate the ICD2023 closest to the device requiring the highest frequency. If the high-frequency clocks must be routed to board extremes, the ICD2031 distributed "satellite" oscillators should be considered.

#### **Circuit Description**

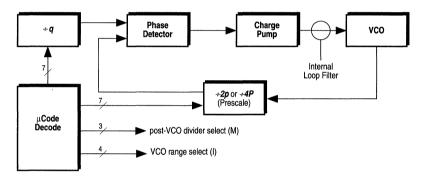

Each oscillator block is a classical phase-locked loop connected as shown in the diagram on the first page. The external input frequency  $f_{(REF)}$  is 14.31818 MHz, and goes into a divide-by-n block. The resultant signal becomes the reference frequency for the phase-locked loop circuitry.

The phase-locked loop is a feedback system which phase matches the reference signal and the variable "synthesized" signal. The system averages zero phase error between the negative edges arriving at the phase detector. The phase error at the charge pump tells the VCO to either go faster or slower as required. The greater the change in control voltage, the greater the change in the VCO's output frequency. This up and down movement of the variable frequency will ultimately lock on to the reference frequency, resulting in an output oscillation as stable as the input reference. An internal loop filter provides stability and damping.

#### **Minimized Parasitic Problems**

All of the IC DESIGNS families of frequency synthesis components have been optimized to reduce internal noise and crosstalk problems. To minimize adjacency problems, all the synthesis blocks are physically separated into discrete elements. Further, all the synthesis VCOs are separated from their digital logic. Finally, separate ground buses for the analog and digital circuitry are used.

#### Stability and "Bit-Jitter"

The long-term frequency stability of the IC DESIGNS phase-locked loop frequency synthesis components is good due to the nature of the feedback mechanism employed internally in the design. As a result, stability of the devices is affected more by the accuracy of the external reference source than by the internal frequency synthesis circuits.

## ICDESIGNS

Short-term stability (also called "bit-jitter") is a manifestation of the frequency synthesis process. The IC DESIGNS frequency synthesis parts have been designed with an emphasis on reduction of bit-jitter. The primary cause of this phenomenon is the "dance" of the VCO as it strives to maintain lock. Low-gain VCOs and sufficient loop filtering are design elements specifically included to minimize bit-jitter. The IC DESIGNS families of frequency synthesis components are all guaranteed to operate at a jitter rate low enough to be acceptable for motherboard designs.

#### **Temperature and Process Sensitivity**

Because of its feedback circuitry, the IC DESIGNS is inherently stable over temperature and manufacturing process variations. Incorporating the loop filter internal to the chip assures that the loop filter will track the same process variations as does the VCO. With the IC DESIGNS, no manufacturing "tweaks" to external filter components are required as is the case with external de-coupled filters.

#### VBATT

The VBATT input powers the Real-Time Clock Oscillator (RTC). The backup power is typically supplied by a 3V lithium battery; however, any voltage between 2V and 5V is acceptable.

#### **Crystal Operation**

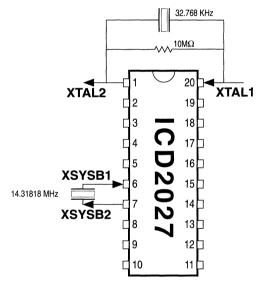

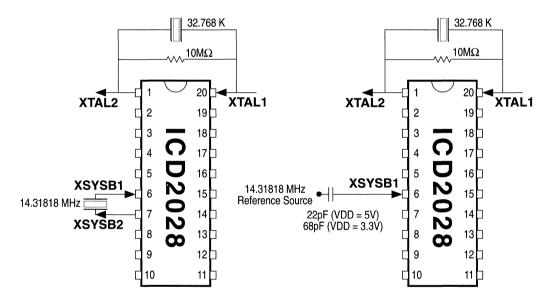

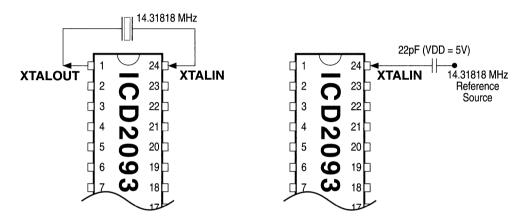

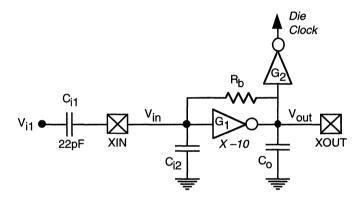

The following diagram details the proper way to hook up the two reference crystals. See the IC DESIGNS Application Note titled *Crystal Oscillator Topics* on page 292 for specifics regarding recommended crystals.

Fig. 3: Crystal Schematic

## **Ordering Information**

#### **Table 9: Order Codes**

| Part Number | Package Type    | <b>Temperature Range</b>    | <b>Clock Output Options</b>        |  |

|-------------|-----------------|-----------------------------|------------------------------------|--|

| ICD2023     | S = 20-Pin SOIC | C = Commercial <sup>a</sup> | 2 = CPUCLK ROM A,<br>16 MHz Output |  |

|             |                 |                             |                                    |  |

|             |                 |                             |                                    |  |

a.  $0^{\circ}$ C to  $+70^{\circ}$ C

Example: order ICD2023SC-2 for the ICD2023, 20-pin SOIC, commercial temperature range device which utilizes the CPUCLK ROM Option A table of frequency decodes and provides a 16 MHz output on pin 3. Custom CPUCLK ROM decodes are available by special order.

## **Device Specifications**

#### **Electrical Data**

#### Table 10: Absolute Maximum Ratings

| Name                        | Description                           | Min  | Max            | Units  |

|-----------------------------|---------------------------------------|------|----------------|--------|

| $V_{DD}$ & AV <sub>DD</sub> | Supply voltage relative to GND        | -0.5 | 7.0            | Volts  |

| V <sub>IN</sub>             | Input voltage with respect to GND     | -0.5 | $V_{DD} + 0.5$ | Volts  |

| T <sub>STOR</sub>           | Storage temperature                   | -65  | +150           | °C     |

| T <sub>SOL</sub>            | OL Max soldering temperature (10 sec) |      | +260           | °C     |

| T <sub>J</sub>              | Junction temperature                  |      | +125           | °C     |

| P <sub>DISS</sub>           | Power dissipation                     |      | 375            | mWatts |

NOTE: Above the Maximum Ratings, the useful life may be impaired. For user guidelines, not tested.

**OPERATING RANGE:**  $V_{DD}$  &  $AV_{DD} = +5V \pm 5\%$ ;  $0^{\circ}C \le T_{AMBIENT} \le 70^{\circ}C$ (This applies to all specifications below.)

| Name                  | Description                      | Min | Max  | Units | Conditions                 |

|-----------------------|----------------------------------|-----|------|-------|----------------------------|

| V <sub>BATT</sub>     | Backup battery voltage           | 2.0 | 5.0  | Volts | typ. = 3.0 Volts           |

| $V_{IH}$              | High-level input voltage         | 2.0 |      | Volts |                            |

| V <sub>IL</sub>       | Low-level input voltage          |     | 0.8  | Volts |                            |

| V <sub>OH</sub>       | High-level CMOS output voltage   | 2.4 |      | Volts | $I_{OH} = -4.0 \text{ mA}$ |

| V <sub>OL</sub>       | Low-level output voltage         |     | 0.4  | Volts | $I_{OL} = 4.0 \text{ mA}$  |

| I <sub>IH</sub>       | Input high current               |     | 150  | μΑ    | $V_{IH} = V_{DD} - 0.5V$   |

| I <sub>IL</sub>       | Input low current                |     | -250 | μΑ    | $V_{IL} = 0.5V$            |

| I <sub>OZ</sub>       | Output leakage current           |     | 10   | μA    | (3-state)                  |

| I <sub>DD</sub>       | Power supply current             | 25  | 65   | mA    |                            |

| I <sub>DD-TYP</sub>   | Power supply current (typical)   |     | 40   | mA    | CPUCLK = 66 MHz            |

| I <sub>BATT</sub>     | Backup battery current           |     | 50   | μA    | $V_{BATT} = 3.0V$          |

| I <sub>BATT-TYP</sub> | Backup battery current (typical) |     | 8    | μΑ    | $C_L = 10 pF$              |

#### **Table 11: DC Characteristics**

IC DESIGNS

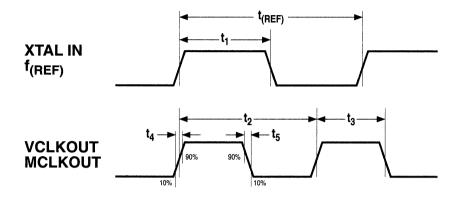

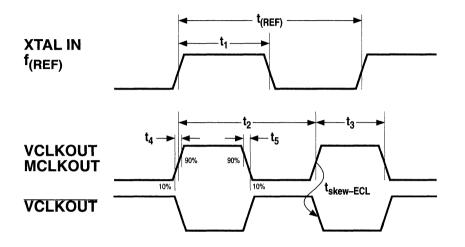

| Symbol          | Name         | Description                                                                                                       | Min | Тур | Max    | Units |

|-----------------|--------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|--------|-------|

|                 | CPUCLK       | Reference Oscillator Output                                                                                       | 10  |     | 80     | MHz   |

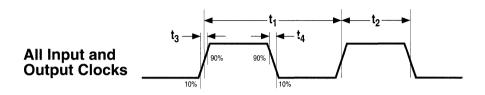

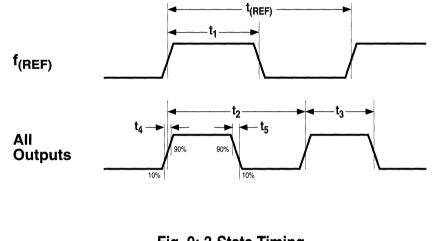

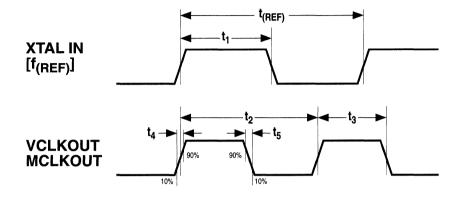

| t <sub>1</sub>  | ref freq     | Reference Oscillator nominal value                                                                                |     |     | 14.318 | MHz   |

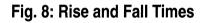

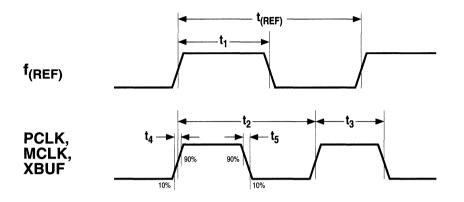

| t <sub>2</sub>  | duty cycle   | Duty cycle for the output oscillators defined as $t_2 \div t_1$                                                   | 40% |     | 60%    |       |

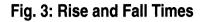

| t <sub>3</sub>  | rise time    | Rise time for the output oscillators into a 25pF load                                                             |     |     | 3      | ns    |

| t <sub>4</sub>  | fall time    | Fall time for the output oscillators into a 25pF load                                                             |     |     | 3      | ns    |

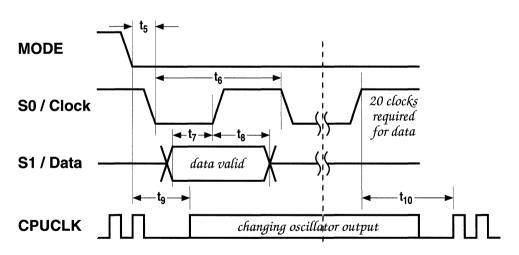

| t <sub>5</sub>  | set-up       | Delay required after MODE goes low prior to starting the S0 clock line                                            |     |     | 0      | ns    |

| t <sub>6</sub>  | cycle time   | Minimum cycle time for the S0 clock                                                                               | 200 |     |        | ns    |

| t <sub>7</sub>  | set-up       | Time required for the data to be valid prior to the rising edge of S0 / CLOCK                                     | 10  |     |        | ns    |

| t <sub>8</sub>  | hold         | Time required for the data to remain valid after the rising edge of S0 / CLOCK                                    | 5   |     |        | ns    |

| t9              | clk unstable | Time CPUCLK oscillator remains valid after MODE signal goes low                                                   |     |     | 0      | ns    |

| t <sub>10</sub> | clk stable   | Time required for the CPUCLK oscillator to become valid after last S0 clock                                       |     |     | 10     | msec  |

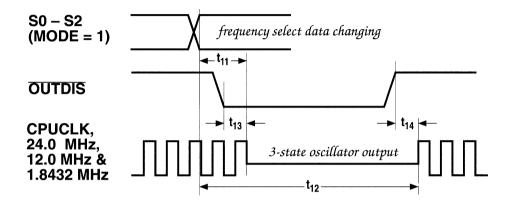

| t <sub>11</sub> | clk unstable | Time the output oscillators remain valid<br>after the S0, S1 or S2 select signals change<br>value                 |     |     | 0      | ns    |

| t <sub>12</sub> | clk stable   | Time required for the output oscillators to<br>become valid after the S0, S1 or S2 select<br>signals change value |     |     | 10     | msec  |

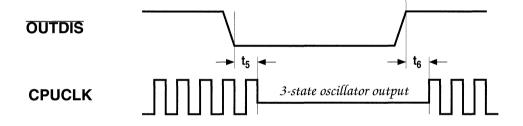

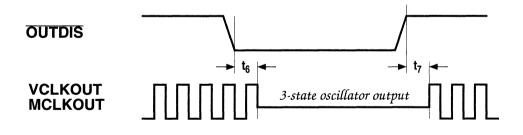

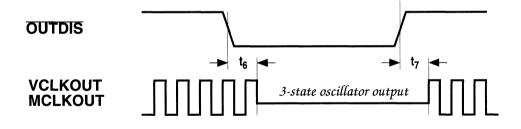

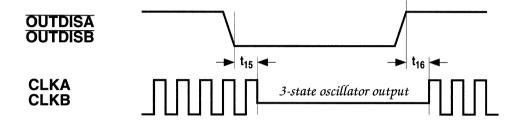

| t <sub>13</sub> | 3-state      | Time for the output oscillators to go into 3-<br>state mode after OUTDIS signal assertion                         |     |     | 12     | ns    |

| t <sub>14</sub> | clk valid    | Time for the output oscillators to recover from 3-state mode after OUTDIS signal goes high                        |     |     | 12     | ns    |

#### **Table 12: AC Characteristics**

**NOTE:** Input capacitance is typically 10pF, except for the crystal pads.

#### **Timing Diagrams**

Fig. 5: Serial Programming Timing

## **Revision History / Credits**

V2.7 (11/15/93) — Final Release Version

## ICD2025

#### **Motherboard Clock Generator**

Single-Chip Dual Oscillator for Personal Computer Motherboard Designs

- 3 Independent Clock Outputs: Separate CPUCLK, SYSCLK and Buffered Reference Clock

- Ideally Suited for 386/486

Motherboard Applications

- Phase-Locked Loop Output Range of 1.843 MHz – 100 MHz

- Phase-Locked Loop Oscillator Input Derived from Single 14.31818 MHz Crystal

- Sophisticated Internal Loop Filter Requires no External Components or Manufacturing "Tweaks" as Commonly Required with External Filters

- 3-State Oscillator Control Disables Outputs for Test Purposes

- 5V Operation

- Low-Power, High-Speed CMOS Technology

- Available in 16-Pin SOIC Package

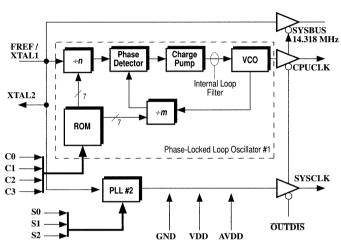

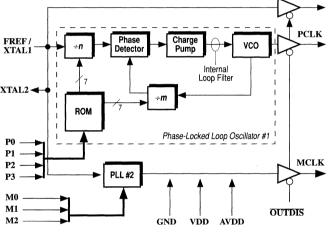

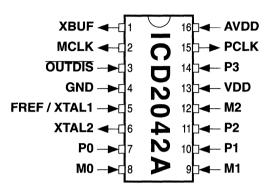

Fig. 1: ICD2025 Block Diagram

#### **Table 1: Available Frequencies**

| SYSCLK | (MHz) | CPUCLK  |  |

|--------|-------|---------|--|

| 1.843  | 1     | 16.000  |  |

| 3.686  |       | 20.000  |  |

| 8.000  |       | 25.000  |  |

| 12.000 |       | 32.000  |  |

| 18.432 |       | 33.333  |  |

| 20.000 |       | 40.000  |  |

| 24.000 |       | 50.000  |  |

| 32.000 |       | 66.667  |  |

|        | -     | 80.000  |  |

|        |       | 100.000 |  |

IC DESIGNS

## **Contents**

| Introduction                                 | 25 |

|----------------------------------------------|----|

| Pin & Signal Descriptions                    | 26 |

| General Considerations                       | 28 |

| CPU and System Clock Oscillator<br>Selection |    |

| PC Board Routing Issues                      |    |

| Output Frequency Accuracy                    |    |

| 3-State Output Operation                     |    |

| No External Components Required              |    |

| Circuit Description                          |    |

| Minimized Parasitic Problems                 |    |

| Stability and "Bit-Jitter"                   |    |

| Temperature and Process Sensitivity          |    |

| Ordering Information                         | 32 |

| Device Specifications                        | 33 |

| Electrical Data                              |    |

| Timing Diagrams                              |    |

| Revision History / Credits                   | 37 |

## Figures

| 1: ICD2025 Block Diagram | 23 |

|--------------------------|----|

| 2: Pin Descriptions      | 26 |

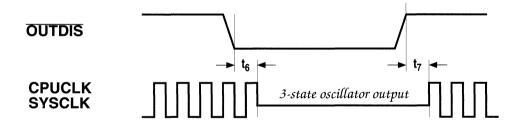

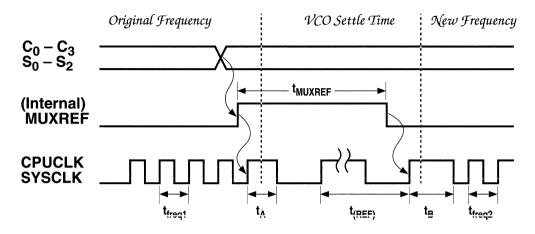

| 3: Rise and Fall Times   | 35 |

| 4: 3-StateTiming         | 35 |

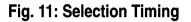

| 5: Selection Timing      | 36 |

## Tables

| 1: Available Frequencies       | 23 |

|--------------------------------|----|

| 2: Signal Descriptions         | 27 |

| 3: CPUCLK Selection            | 28 |

| 4: SYSCLK Selection            | 29 |

| 5: Order Codes                 | 32 |

| 6: Absolute Maximum<br>Ratings | 33 |

| 7: DC Characteristics          | 33 |

| 8: AC Characteristics          | 34 |

## <u>ICDESIGNS</u> Introduction

The emergence of new, highly integrated core logic chip sets has significantly simplified the clocking requirements of inexpensive PC-clone motherboards. The ICD2025 is intended to offer a low-cost approach to the generation of the necessary three clocks typically required.

While lower in cost than other IC DESIGNS motherboard devices which offer greater functionality, the ICD2025 still maintains the consistently high quality level our customers have come to expect: full temperature test, complete functional test and (still) the industry's only jitter screening test.

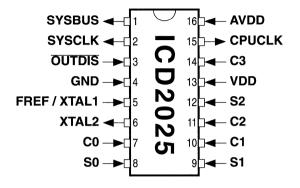

## **Pin & Signal Descriptions**

Fig. 2: Pin Descriptions

#### **Table 2: Signal Descriptions**

| Pin # | Signal       | Function                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | SYSBUS       | Buffered Reference Frequency Output (14.31818 MHz)                                                                                                                                                                                                                                                                                                                                        |

| 2     | SYSCLK       | System Clock Oscillator Output (see Table 4: SYSCLK Selection on page 29)                                                                                                                                                                                                                                                                                                                 |

| 3     | OUTDIS       | Output Disable (Enable 3-State Output) when signal is pulled low. (Internal pull-<br>up allows no-connect if 3-state operation not needed).                                                                                                                                                                                                                                               |

| 4     | GND          | Ground                                                                                                                                                                                                                                                                                                                                                                                    |

| 5     | FREF / XTAL1 | Input Reference Oscillator (nominally 14.31818 MHz) A crystal may be used if a reference oscillator is not available.                                                                                                                                                                                                                                                                     |

| 6     | XTAL2        | Oscillator Output to a reference Series-Resonant Crystal. For higher accuracy, a Parallel-Resonant Crystal may be used. Assume CLOAD $\approx$ 17pF. For more specifics on crystal requirements please refer to the IC DESIGNS Application Note <i>Crystal Oscillator Topics</i> on page 292. (Pin is no-connect if external reference oscillator or PC System Bus clock signal is used.) |

| 7     | C0           | CPUCLK Selection Signal — Bit 0 (internal pull-up)                                                                                                                                                                                                                                                                                                                                        |

| 8     | SO           | SYSCLK Clock Selection Signal — Bit 0 (internal pull-up)                                                                                                                                                                                                                                                                                                                                  |

| 9     | S1           | SYSCLK Selection Signal — Bit 1 (internal pull-up)                                                                                                                                                                                                                                                                                                                                        |

| 10    | C1           | CPUCLK Selection Signal — Bit 1 (internal pull-up)                                                                                                                                                                                                                                                                                                                                        |

| 11    | C2           | CPUCLK Selection Signal — Bit 2 (internal pull-up)                                                                                                                                                                                                                                                                                                                                        |

| 12    | S2           | SYSCLK Selection Signal — Bit 2 (internal pull-up)                                                                                                                                                                                                                                                                                                                                        |

| 13    | VDD          | +5V to I/O Ring                                                                                                                                                                                                                                                                                                                                                                           |

| 14    | C3           | CPUCLK Selection Signal — Bit 3 (internal pull-down)                                                                                                                                                                                                                                                                                                                                      |

| 15    | CPUCLK       | CPU Clock Oscillator Output (see CPUCLK Selection Table)                                                                                                                                                                                                                                                                                                                                  |

| 16    | AVDD         | +5V to Analog Core                                                                                                                                                                                                                                                                                                                                                                        |

## **General Considerations**

#### **CPU and System Clock Oscillator Selection**

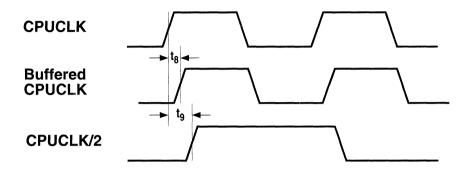

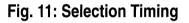

The output frequency value of the CPU clock oscillator (CPUCLK) is selected by the four CPU clock selection inputs: C0, C1, C2, and C3. This feature allows the ICD2025 to support different CPU speeds. The output frequency value of the system clock oscillator (SYSCLK) is selected by the three system clock selection inputs: S0, S1, and S2. The selection tables are shown below.

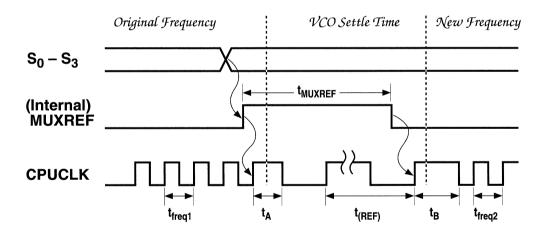

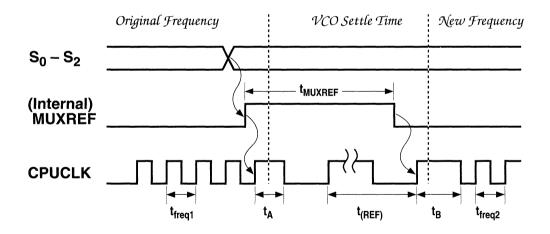

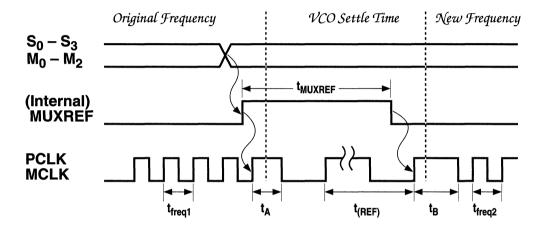

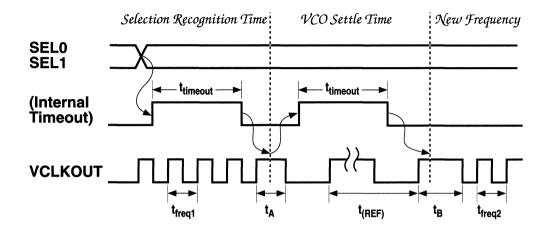

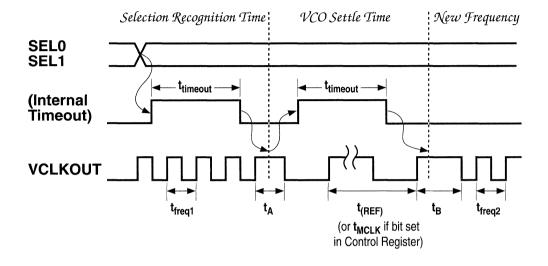

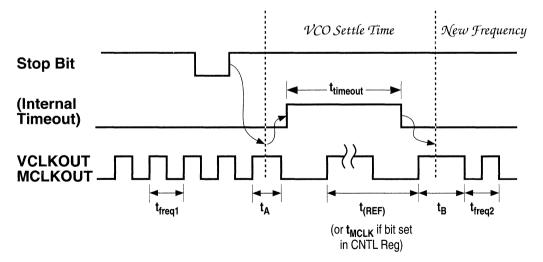

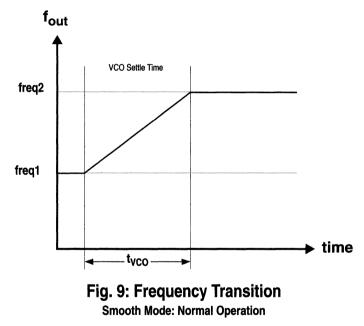

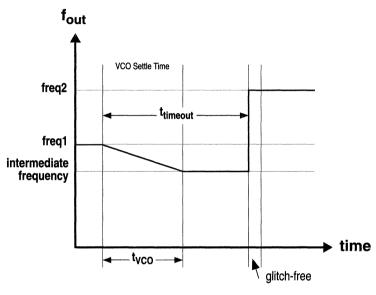

At any time during operation, the selection lines can be changed to select a different frequency. When this occurs, the internal phase-locked loop will immediately seek the newly selected frequency. During the transition period, the clock output will multiplex glitch-free to the 14.31818 MHz reference signal until the PLL settles to the new frequency. The timing for this transition is detailed in *Table 8: AC Characteristics* on page 34.

| C3 | C2 | C1 | C0 | Word | Desired Freq.<br>(MHz) | Actual Freq.<br>(MHz) | PPM<br>Error |

|----|----|----|----|------|------------------------|-----------------------|--------------|

| 0  | 0  | 0  | 0  | 0    | 40.000                 | 39.812                | 4734         |

| 0  | 0  | 0  | 1  | 1    | 80.000                 | 79.623                | 4734         |

| 0  | 0  | 1  | 0  | 2    | 33.333                 | 33.322                | 320          |

| 0  | 0  | 1  | 1  | 3    | 66.667                 | 66.645                | 335          |

| 0  | 1  | 0  | 0  | 4    | 25.000                 | 25.000                | 0            |

| 0  | 1  | 0  | 1  | 5    | 50.000                 | 50.000                | 0            |

| 0  | 1  | 1  | 0  | 6    | 16.000                 | 15.923                | 4848         |

| 0  | 1  | 1  | 1  | 7    | 32.000                 | 31.846                | 4848         |

| 1  | 0  | 0  | 0  | 8    | 20.000                 | 19.906                | 4734         |

| 1  | 0  | 0  | 1  | 9    | 100.000                | 99.840                | 1600         |

| 1  | 0  | 1  | 0  | 10   | 40.000                 | 39.812                | 4734         |

| 1  | 0  | 1  | 1  | 11   | 80.000                 | 79.623                | 4734         |

| 1  | 1  | 0  | 0  | 12   | 33.333                 | 33.322                | 320          |

| 1  | 1  | 0  | 1  | 13   | 66.667                 | 66.645                | 335          |

| 1  | 1  | 1  | 0  | 14   | 25.000                 | 25.000                | 0            |

| 1  | 1  | 1  | 1  | 15   | 50.000                 | 50.000                | 0            |

#### Table 3: CPUCLK Selection

| <b>S2</b> | <b>S1</b> | <b>S0</b> | Word | Desired Freq.<br>(MHz) | Actual Freq.<br>(MHz) | PPM<br>Error |

|-----------|-----------|-----------|------|------------------------|-----------------------|--------------|

| 0         | 0         | 0         | 0    | 18.432                 | 18.431                | 62           |

| 0         | 0         | 1         | 1    | 20.000                 | 20.003                | 167          |

| 0         | 1         | 0         | 2    | 24.000                 | 23.998                | 80           |

| 0         | 1         | 1         | 3    | 1.843                  | 1.843                 | 144          |

| 1         | 0         | 0         | 4    | 12.000                 | 11.999                | 80           |

| 1         | 0         | 1         | 5    | 8.000                  | 8.001                 | 167          |

| 1         | 1         | 0         | 6    | 3.686                  | 3.687                 | 144          |

| 1         | 1         | 1         | 7    | 32.000                 | 32.005                | 167          |

#### Table 4: SYSCLK Selection

#### **PC Board Routing Issues**

Traditionally, having multiple crystals has allowed the designer to locate them in those places on the board where they are needed. Using a monolithic circuit puts some constraints on the PC board layout to accommodate a single source of all clocks, particularly at the higher system clock frequencies above 50 MHz.

A full power and ground plane layout should be employed both under and around the IC package. It is important that the ground plane be nearly continuous with a minimum of cuts, holes, or breaks. Both analog and digital ground pins should go directly to this plane.

To produce an output of high spectral purity, additional supply noise precautions might be required, particularly in noisy environments. The analog power pin (AVDD) should be bypassed to ground with a  $0.1\mu$ F multi-layer ceramic capacitor and a  $2.2\mu$ F/10V tantalum capacitor wired in parallel. Both capacitors should be placed within 0.15" of the power pin. A  $22\Omega$  resistor placed between the power supply and AVDD can help to filter noisy supply lines.

The designer should also avoid routing the two output traces of the ICD2025 in close parallel proximity. Large routing lengths and large fanouts add capacitance to output drivers. Capacitance affects the rise and fall times of the outputs. Large fanouts should therefore be buffered, particularly for the highest frequencies.

When designing with this device, it is best to locate the ICD2025 closest to the device requiring the highest frequency. For more details concerning layout and power considerations, please see the IC DESIGNS Application Note *Power Feed and Board Layout Issues* on page 281.

### **Output Frequency Accuracy**

The accuracy of the ICD2025 output frequencies depends on the target output frequencies. The tables within this document contain target frequencies which differ from the actual frequencies produced by the clock synthesizer.

The output frequencies of the ICD2025 are an integral fraction of the input (reference) frequency:

$$f_{(OUT)} = (2 \times f_{(REF)} \times \frac{P}{Q})$$

Only certain output frequencies are possible for a particular reference frequency. However, the ICD2025 always produces an output frequency within 0.1% of the target frequencies listed, which is more than sufficient to meet standard system logic requirements. (Actual values are given in the tables.)

### **3-State Output Operation**

The OUTDIS signal, when pulled low, will 3-state the SYSCLK, CPUCLK and SYSBUF output lines. This supports procedures such as automated testing, where the clock must be disabled. The OUTDIS signal contains an internal pull-up but should be tied to VDD if not used.

### **No External Components Required**

Under normal conditions no external components other than a reference crystal are required for proper operation of any of the internal circuitry of the ICD2025.

### **Circuit Description**

Each oscillator block is a classical phase-locked loop connected as shown in the diagram on the first page. The external input frequency  $f_{(REF)}$  is typically 14.31818 MHz (as derived from the PC system bus) and goes into a divide-by-n block. The resultant signal becomes the reference frequency for the phase-locked loop circuitry.

The phase-locked loop is a feedback system which phase matches the reference signal and the variable "synthesized" signal. The system averages zero phase error between the negative edges arriving at the phase detector. The phase error at the charge pump tells the VCO to either go faster or slower as required. The greater the change in control voltage, the greater the change in the VCO's output frequency. This up and down movement of the variable frequency will ultimately lock on to the reference frequency, resulting in an output oscillation as stable as the input reference. An internal loop filter provides stability and damping.

### **Minimized Parasitic Problems**

All of the IC DESIGNS families of frequency synthesis components have been optimized to reduce internal noise and crosstalk problems. To minimize adjacency problems, all the synthesis blocks are physically separated into discrete elements with their output oscillator pins placed on separate sides of the package. Further, all the synthesis VCOs are separated from their digital logic. Finally, separate power and ground buses for the analog and digital circuitry are used.

The package leadframes are optimized for the lowest possible inductance from the supply pin on the package to the die within, and results in minimized supply noise problems such as ground-bounce and output crosstalk.

### Stability and "Bit-Jitter"

The long-term frequency stability of the IC DESIGNS phase-locked loop frequency synthesis components is good due to the nature of the feedback mechanism employed internally in the design. As a result, stability of the devices is affected more by the accuracy of the external reference source than by the internal frequency synthesis circuits.

Short-term stability (also called "bit-jitter") is a manifestation of the frequency synthesis process. The IC DESIGNS frequency synthesis parts have been designed with an emphasis on reduction of bit-jitter. The primary cause of this phenomenon is the "dance" of the VCO as it strives to maintain lock. Low-gain VCO's and sufficient loop filtering are design elements specifically included to minimize bit-jitter. The IC DESIGNS families of frequency synthesis components are all guaranteed to operate at a jitter rate low enough for system logic applications.

### **Temperature and Process Sensitivity**

Because of its feedback circuitry, the ICD2025 is inherently stable over temperature and manufacturing process variations. Incorporating the loop filter internal to the chip assures the loop filter will track the same process variations as does the VCO. With the ICD2025, no manufacturing "tweaks" to external filter components are required as is the case with external de-coupled filters.

### **Ordering Information**

#### Table 5: Order Codes

| Part Number | Package Type        | Temperature Range  |

|-------------|---------------------|--------------------|

| ICD2025     | S = 16-Pin SOIC DIP | $C = Commercial^a$ |

|             |                     |                    |

|             |                     |                    |

a.  $0^{\circ}$ C to  $+70^{\circ}$ C

Example: order ICD2025PC for the ICD2025, 16-pin plastic SOIC, commercial temperature range device.

IC DESIGNS

### **Device Specifications**

### **Electrical Data**

#### **Table 6: Absolute Maximum Ratings**

| Name                               | Description                        | Min  | Max            | Units  |

|------------------------------------|------------------------------------|------|----------------|--------|

| V <sub>DD</sub> & AV <sub>DD</sub> | Supply voltage relative to GND     | -0.5 | 7.0            | Volts  |

| V <sub>IN</sub>                    | Input voltage with respect to GND  | -0.5 | $V_{DD} + 0.5$ | Volts  |

| T <sub>STOR</sub>                  | Storage temperature                | -65  | +150           | °C     |

| T <sub>SOL</sub>                   | Max soldering temperature (10 sec) | +260 | °C             |        |

| T <sub>J</sub>                     | Junction temperature               | +125 | °C             |        |

| P <sub>DISS</sub>                  | Power dissipation                  |      | 350            | mWatts |

NOTE: Above the Maximum Ratings, the useful life may be impaired. For user guidelines, not tested.

**OPERATING RANGE:**  $V_{DD}$  &  $AV_{DD}$  = +5V ±5%; 0°C ≤  $T_{AMBIENT}$  ≤ 70°C (This applies to all specifications below.)

#### **Table 7: DC Characteristics**

| Name             | Description                    | Min | Max  | Units | Conditions                 |

|------------------|--------------------------------|-----|------|-------|----------------------------|

| V <sub>IH</sub>  | High-level input voltage       | 2.0 |      | Volts |                            |

| V <sub>IL</sub>  | Low-level input voltage        |     | 0.8  | Volts |                            |

| V <sub>OH</sub>  | High-level CMOS output voltage | 2.4 |      | Volts | $I_{OH} = -4.0 \text{ mA}$ |

| V <sub>OL</sub>  | Low-level output voltage       |     | 0.4  | Volts | $I_{OL} = 4.0 \text{ mA}$  |

| $I_{IH}$         | Input high current             |     | 150  | μA    | V <sub>IH</sub> = 5.25V    |

| I <sub>IL</sub>  | Input low current              |     | -250 | μA    | $V_{IH} = 0V$              |

| I <sub>OZ</sub>  | Output leakage current         |     | 10   | μA    | (3-state)                  |

| I <sub>DD</sub>  | Power supply current           |     | 50   | mA    | (@ hi freq)                |

| I <sub>ADD</sub> | Analog Power Supply Current    |     | 6    | mA    |                            |

#### Motherboard Frequency Synthesizers

| Symbol              | Name                           | Description                                                                                               | Min                   | Тур    | Max                    | Units |

|---------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------|--------|------------------------|-------|

| f <sub>(REF)</sub>  | reference<br>frequency         | Reference Oscillator nominal value                                                                        | 4                     | 14.318 | 26                     | MHz   |

| t <sub>(REF)</sub>  | reference<br>clock period      | $1 \div f_{(\text{REF})}$                                                                                 | 38.5                  | 69.8   | 2500                   | ns    |

| t <sub>1</sub>      | input duty<br>cycle            | Duty cycle for the input oscillator defined as $t1 \div t_{(REF)}$                                        | 25%                   | 50%    | 75%                    |       |

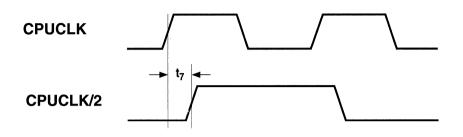

| t <sub>2</sub>      | output<br>period               | CPUCLK oscillator value                                                                                   | 8.3<br>120 MHz        |        | 2857<br>350 KHz        | ns    |

| t <sub>3</sub>      | output duty cycle              | Duty cycle for the output oscillator defined as $t_3 + t_2$ (measured at 2.5V)                            | 40%                   |        | 60%                    |       |

| t <sub>4</sub>      | rise time                      | Rise time for the output oscillator into a 25pF load                                                      |                       |        | 3                      | ns    |

| t <sub>5</sub>      | fall time                      | Fall time for the output oscillator into a 25 pF load                                                     |                       |        | 3                      | ns    |

| t <sub>6</sub>      | 3-state                        | Time for the output oscillators to go into 3-<br>state mode after OUTDIS signal assertion                 |                       |        | 12                     | ns    |

| t <sub>7</sub>      | clk valid                      | Time for the output oscillators to recover<br>from 3-state mode after OUTDIS signal<br>goes high          |                       |        | 12                     | ns    |

| t <sub>MUXREF</sub> | clk stable                     | Time required for the output oscillators to become valid after C0–C3 or S0–S2 select signals change value | 3.4                   | 5      | 6.9                    | msec  |

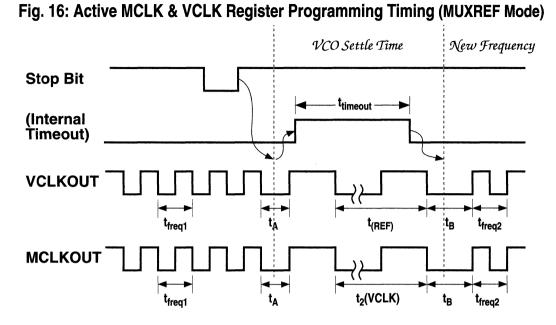

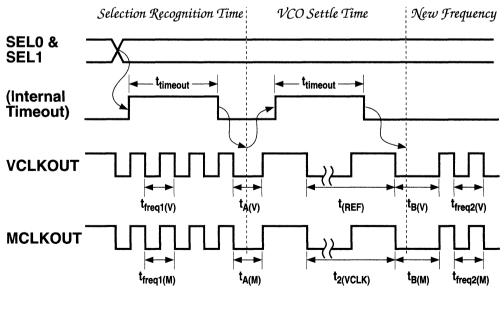

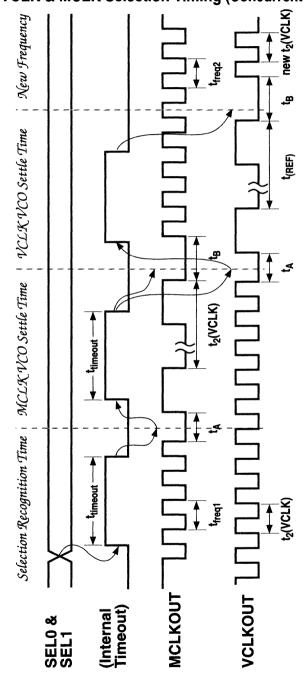

| t <sub>freq1</sub>  | freq1 output                   | Old frequency output                                                                                      |                       |        |                        |       |

| t <sub>freq2</sub>  | freq2 output                   | New frequency output                                                                                      |                       |        |                        |       |

| t <sub>A</sub>      | f <sub>(REF)</sub> mux<br>time | Time clock output remains high while output muxes to reference frequency                                  | $\frac{t_{(REF)}}{2}$ |        | $3\frac{t_{(REF)}}{2}$ | ns    |

| t <sub>B</sub>      | t <sub>freq2</sub> mux<br>time | Time clock output remains high while output muxes to new frequency value                                  | $\frac{t_{freq2}}{2}$ |        | $3\frac{t_{freq2}}{2}$ | ns    |

### Table 8: AC Characteristics

**NOTE:** Input capacitance is typically 10pF, except for the crystal pads.

**IC**DESIGNS

### **Timing Diagrams**

Fig. 5: Selection Timing

### **Revision History / Credits**

V1.4 (11/15/93) — Final Release Version

# ICD2027

### **PC Motherboard Clock Generator**

Single-Chip Oscillator Ideally Suited for 486/386/286 Laptop/Notebook Computer Applications

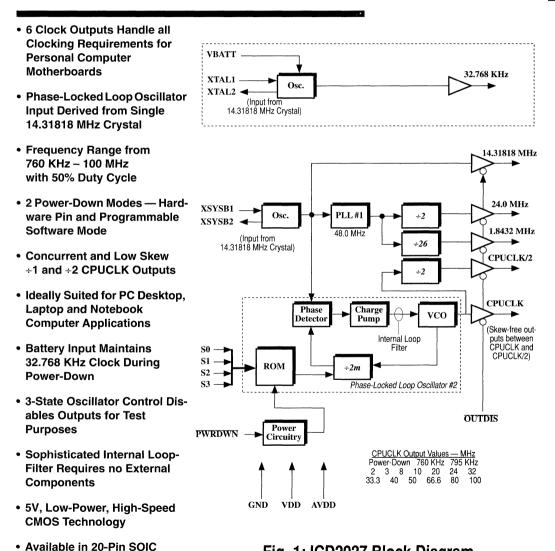

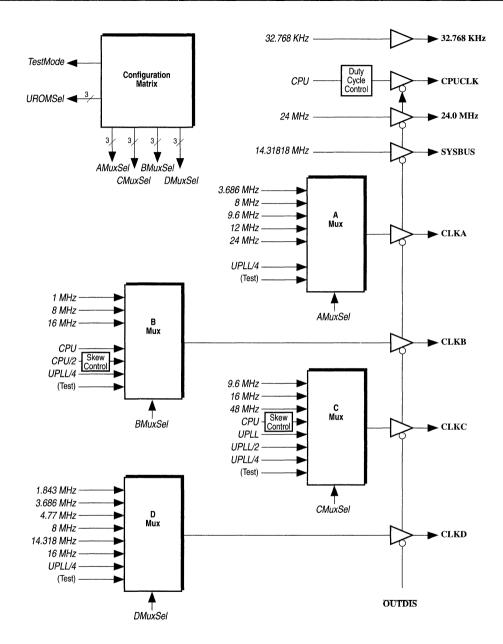

### Fig. 1: ICD2027 Block Diagram

Package Configuration

### **Contents**

| Introduction                         | 41 |

|--------------------------------------|----|

| Pin & Signal Descriptions            | 42 |

| General Considerations               | 44 |

| CPUCLK Oscillator Operation          |    |

| Fixed Frequency Oscillator Operation |    |

| Power-Down Operation                 |    |

| 3-State Output Operation             |    |

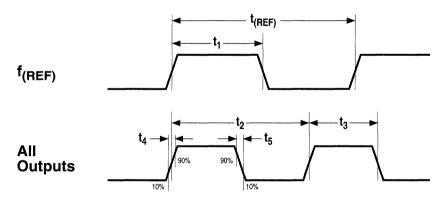

| Skew-Free ÷2 on CPUCLK/2             |    |

| PC Board Routing Issues              |    |

| Circuit Description                  |    |

| VBATT                                |    |

| Crystal Operation                    |    |

| Ordering Information                 | 48 |

| Device Specifications                | 49 |

| Electrical Data                      |    |

| Timing Diagrams                      |    |

| Revision History / Credits           | 53 |

### **Figures**

| 1: ICD2027 Block Diagram | 39 |

|--------------------------|----|

| 2: Pin Descriptions      | 42 |

| 3: Crystal Schematic     | 47 |

| 4: Rise and Fall Times   | 51 |

| 5: 3-StateTiming         | 51 |

| 6: CPUCLK Skew           | 52 |

| 7: Selection Timing      | 52 |

### Tables

| 1: Signal Descriptions                    | 42 |

|-------------------------------------------|----|

| 2: CPUCLK ROM Selection<br>Outputs        | 44 |

| 3: Fixed Frequency<br>Oscillators         | 45 |

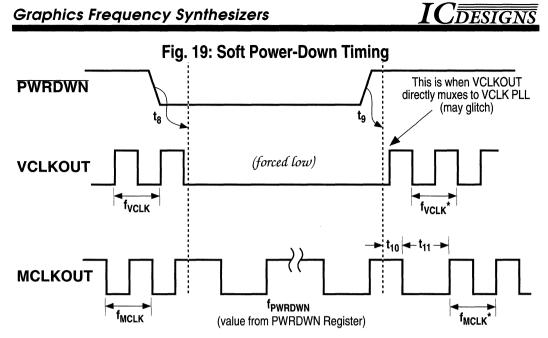

| 4: Soft Power-Down Mode<br>(S0–S3 = 0000) | 45 |

| 5: Order Codes                            | 48 |

| 6: Absolute Maximum<br>Ratings            | 49 |

| 7: DC Characteristics                     | 49 |

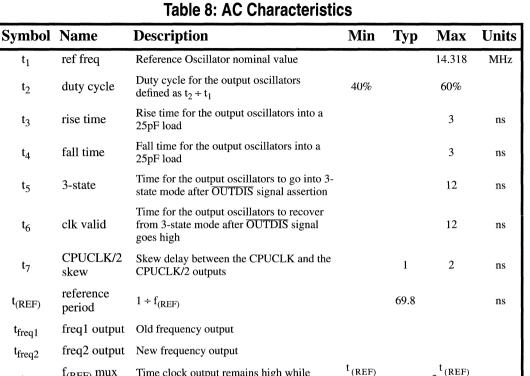

| 8: AC Characteristics                     | 50 |

# ICDESIGNS

# Introduction

A modern personal computer motherboard often requires as many as six different crystal can oscillators per printed circuit board. A new family of frequency synthesis parts from IC DESIGNS replaces the large number of the oscillators required to build such multi-function motherboards. These parts synthesize all the required frequencies in a single monolithic device, thus lowering manufacturing costs and significantly reducing the printed circuit board space required.

The ICD2027 PC Motherboard Clock Generator offers 2 oscillators, 2 phase-locked loops, and 6 different outputs in a single package. Four of the outputs are of a fixed value while the other two may be changed "on the fly" to any one of 16 preset frequency values between 760 KHz and 100 MHz. The ICD2027 is ideally suited for use in new laptop/notebook designs due to its dual power-down modes. The ICD2027 also requires no support from the motherboard chip set and outputs all 6 frequencies concurrently.

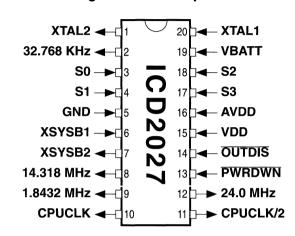

### **Pin & Signal Descriptions**

Fig. 2: Pin Descriptions

Table 1: Signal Descriptions

| Pin # | Signal     | Function                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | XTAL2      | Oscillator Output to a 32.768 KHz Parallel-Resonant Crystal                                                                                                                                                                                                                                                                                                                               |

| 2     | 32.768 KHz | 32.768 KHz Output                                                                                                                                                                                                                                                                                                                                                                         |

| 3     | S0         | Bit 0 (LSB) of S0–S3, used to select CPUCLK frequency (Internal pull-down)                                                                                                                                                                                                                                                                                                                |

| 4     | S1         | Bit 1 of S0-S3, used to select CPUCLK frequency (Internal pull-down)                                                                                                                                                                                                                                                                                                                      |

| 5     | GND        | Ground                                                                                                                                                                                                                                                                                                                                                                                    |

| 6     | XSYSB1     | Input Reference Oscillator for all Phase-Locked Loops (nominally 14.31818 MHz). An optional PC System Bus Clock Signal may be used as input if available.                                                                                                                                                                                                                                 |