# • C Y P R E S S •

# SEMICONDUCTOR

.

K

N

A

B

Cypress Semiconductor, 3901 North First St., San Jose, CA 95134 (408) 943-2600 Telex: 821032 CYPRESS SNJ UD, TWX: 910 997 0753, FAX: (408) 943-2741 Cypress Semiconductor, Cypress PLD Toolkit, and QuickPro II are trademarks of Cypress Semiconductor Corporation.

IBM, IBM PC, and PC/XT are registered trademarks of the International Business Machine Corporation. SPARC is a registered trademark of SPARC International.

Data I/O is a registered trademark of the Data I/O Corporation.

PLD Test and ABEL are trademarks of the Data I/O Corporation.

STAG is a registered trademark of Stag Microsystems Ltd.

#### Published August 1991

© Cypress Semiconductor Corporation, 1991. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress Semiconductor Corporation product. Nor does it convey or imply any license under patient or other rights. Cypress Semiconductor does not attribute to rule as circuitry other than circuitry embodied in a Cypress Semiconductor corporation product any circuitry other than circuitry embodied in a Cypress Semiconductor does not attribute of the product any reasonably be expected to result in significant injury to the user. The inclusion of Cypress Semiconductor products in life-support systems applications implies that the manufacturer assumes all risk of such use and in so doing indemnifies Cypress Semiconductor against all damages.

### Preface

#### **About This Book**

This Applications Handbook is a learning tool for using Cypress devices. The application notes included here range from general product overview articles, such as "Understanding Dual-Port RAMs," to specific design examples.

The general overviews describe product-family characteristics and explain some of the products' capabilities. These application notes appear at the beginning of this *Handbook*.

Next appear application examples that show how to use specific Cypress devices in the context of real designs. The application examples are organized by product type (e.g., SRAMs or EPLDs). Within each product type examples are arranged by product number, using the product that is the article's primary focus.

Although your specific application might not appear explicitly in an application note, the design examples can still be useful to you. If the design example is similar to your application, you might be able to adapt the hardware or software to your design easily. Many of the application notes provide PLD software code for design tools from a variety of vendors, so that you can copy the code and use it as a skeleton for your own PLD designs. Even if none of the examples relate directly to your design, they can stimulate new ideas by showing features or applications that might not have occurred to you. The information can also significantly reduce the learning curve normally associated with unfamiliar ICs.

Most of the designs described in this *Handbook* are based on actual circuits produced either by Cypress or by one of our customers. Application notes that discuss specific designs indicate whether the designs have been simulated and/or built and completely debugged.

If you have questions about any Cypress product, please contact your local Field Applications Engineer at the nearest direct sales office. A list of Cypress sales offices, representatives, and distributors is included at the back of this Handbook. For continuous on-line information about Cypress products, you can connect to the Cypress Bulletin Board at (408) 943-2954.

#### **About Cypress Semiconductor**

Since its incorporation in 1982, Cypress has successfully addressed diverse, high-performance niche markets by creating technologically sophisticated products, using innovative packaging, and emphasizing quality. Cypress is a complete semiconductor manufacturer, performing its own process development, circuit design, wafer fabrication, assembly, and test. Its core CMOS and BiCMOS processes lead the industry with 0.8-micron design rules. Cypress ships over 200 products in seven product areas: SRAMs, PROMs, PLDs, logic devices, SPARC microprocessors and peripherals, multichip modules, and high-speed BiCMOS PLD and memory devices. Cypress is an international company, with headquarters in San Jose, California and fabrication facilities in San Jose; Round Rock, Texas; and Bloomington, Minnesota. The company has started up five subsidiaries that are funded by Cypress but run as independent businesses, including Cypress Semiconductor (Texas) Inc., Aspen Semicon-Multichip Technology Incorductor Corporation, porated, Ross Technology Inc., and Cypress Semiconductor (Minnesota) Inc.

## Contents

|                                                                  | Page |

|------------------------------------------------------------------|------|

| General Information                                              |      |

| System Design Considerations When Using Cypress CMOS Circuits    | 1–1  |

| Power Characteristics of Cypress Products                        | 1-23 |

| Tips for High-Speed Logic Design                                 |      |

| Protection, Decoupling, and Filtering of Cypress CMOS Circuits   | 1–34 |

| Modules                                                          |      |

| Choosing Packages in High-Density Module Designs                 | 2-1  |

| The Multichip Family of Universal JEDEC ZIP/SIMM Modules         | 2–7  |

| ECL and TTL BiCMOS                                               |      |

| Noise Considerations in High-Speed Logic Systems                 | 3–1  |

| Using ECL in Single + 5V TTL Systems                             |      |

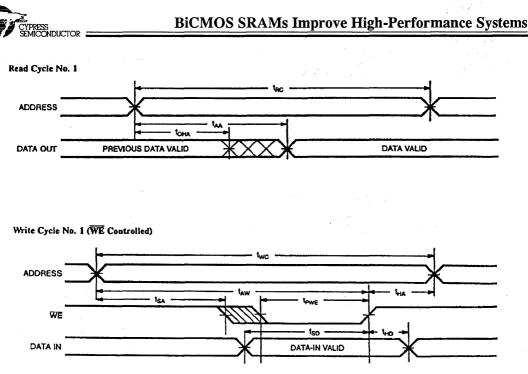

| BiCMOS TTL and ECL SRAMs Improve High-Performance Systems        | 3-7  |

| PLCC and CLCC Packaging for High-Speed Parts                     |      |

| A New Generation of BiCMOS High-Speed TTL SRAMs                  |      |

| Access Time vs. Load Capacitance for High-Speed BiCMOS TTL SRAMs |      |

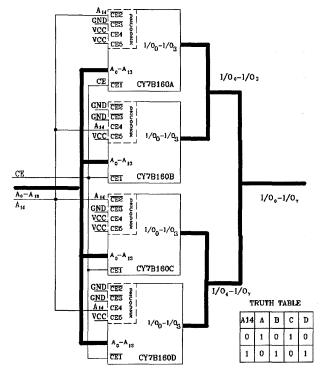

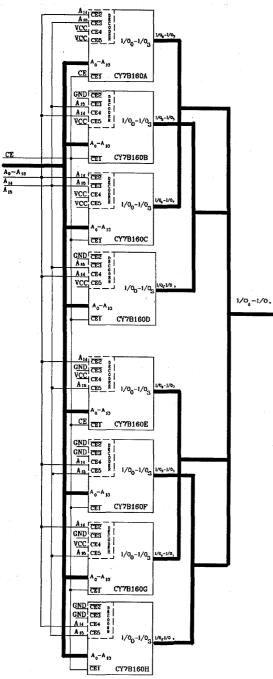

| Combining SRAMs Without an External Decoder                      |      |

| BiCMOS TTL SRAMs Improve MIPS R3000 and R3000A Systems           |      |

| Memory and Support Logic for Next-Generation ECL Systems         | 3–33 |

| SRAMs                                                            |      |

| RAM I/O Characteristics                                          |      |

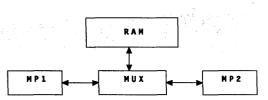

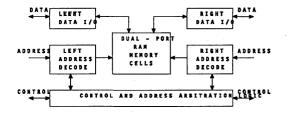

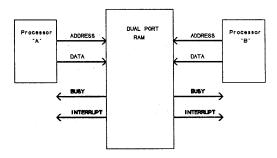

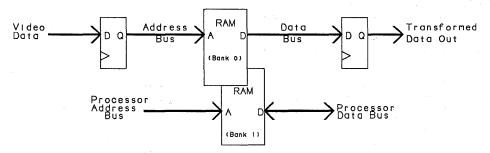

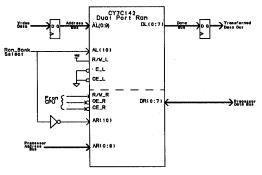

| Understanding Dual-Port RAMs                                     |      |

| Using Dual-Port RAMs Without Arbitration                         |      |

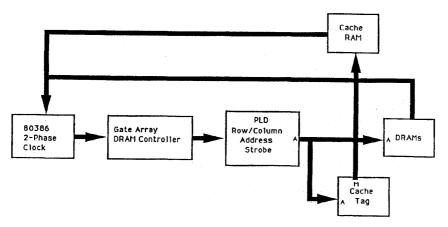

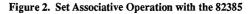

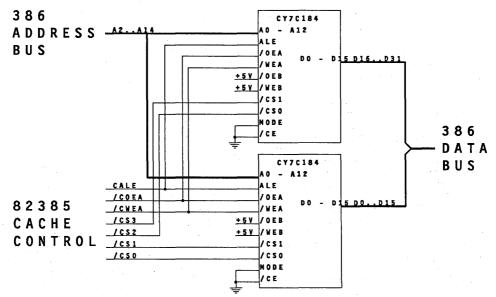

| Using Cypress SRAMs to Implement 386 Cache                       | 4–23 |

| PROMs                                                            |      |

| Pin-out Compatibility Considerations of SRAMs and PROMs          | 5–1  |

| Introduction to Diagnostic PROMs                                 |      |

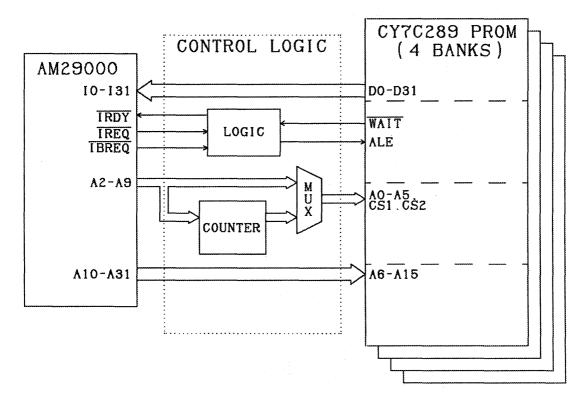

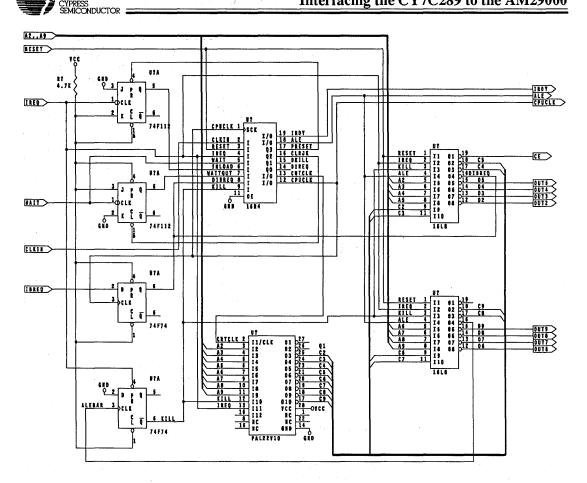

| Interfacing the CY7C289 to the AM29000                           |      |

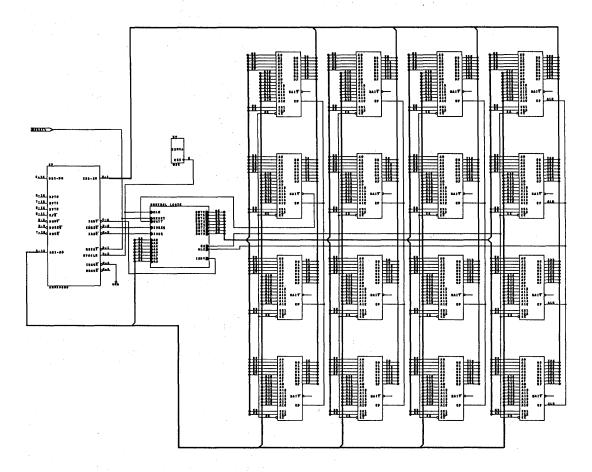

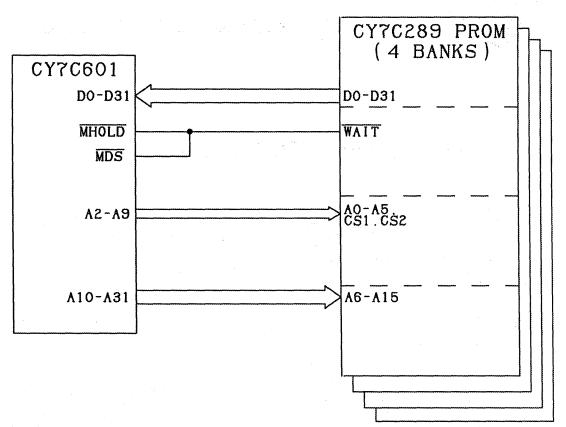

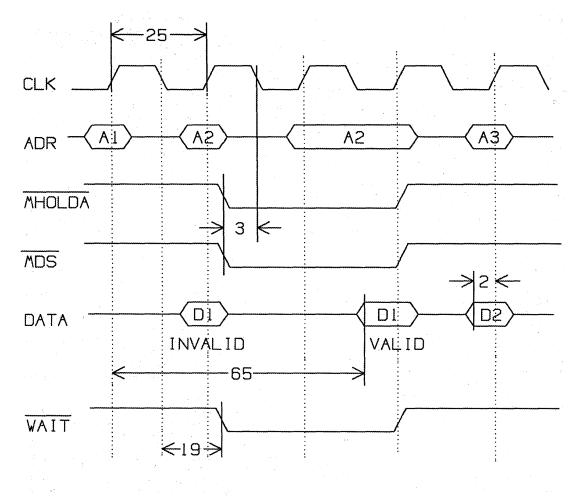

| Interfacing the CY7C289 to the CY7C601                           | 5–23 |

| PLDs                                                             |      |

| Introduction to Programmable Logic                               |      |

| CMOS PAL Basics                                                  |      |

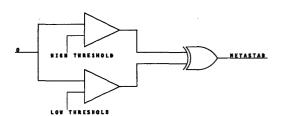

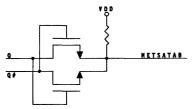

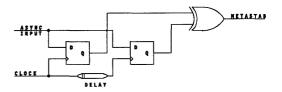

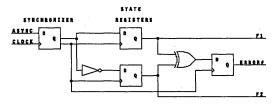

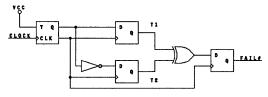

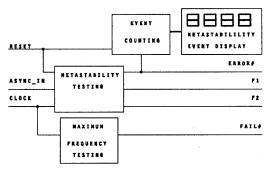

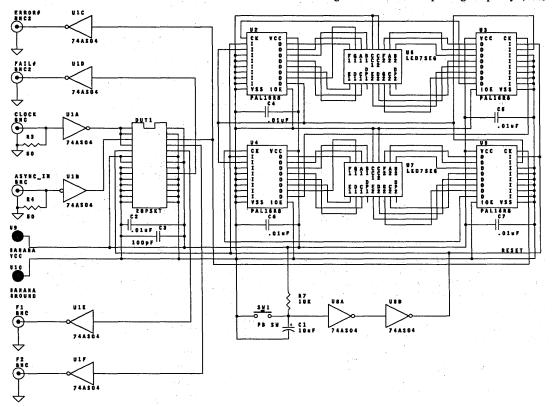

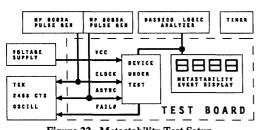

| Are Your PLDs Metastable?                                        |      |

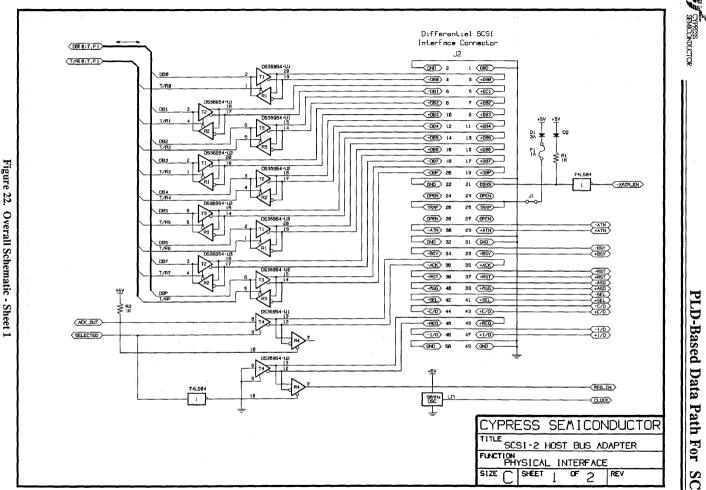

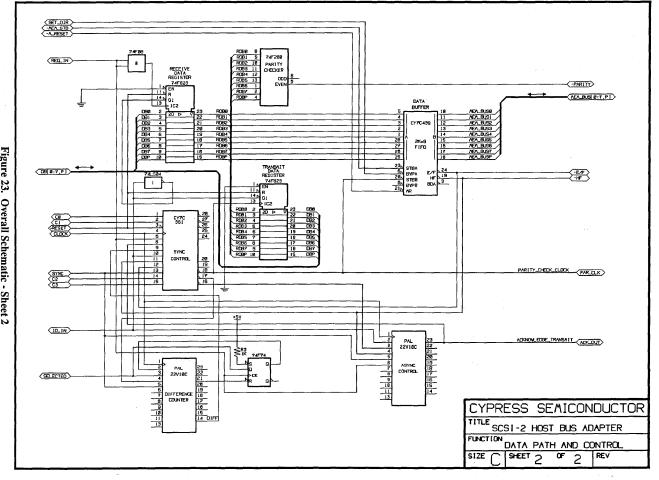

| PLD-Based Data Path For SCSI-2                                   | 6-40 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ge             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| PLDs (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

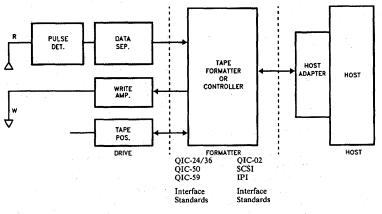

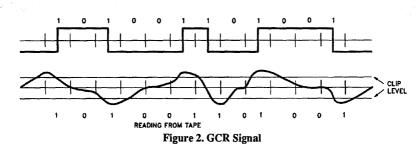

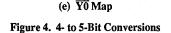

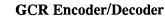

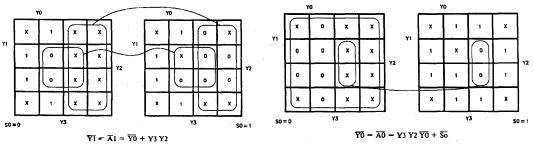

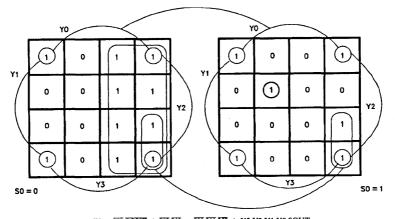

| PAL Design Example: A GCR Encoder/Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53             |

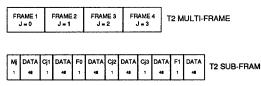

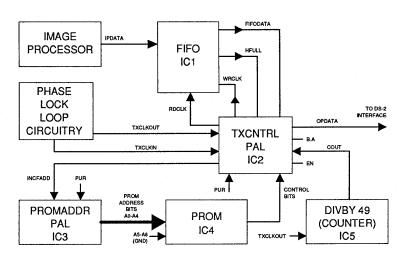

| T2 Framing Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76             |

| Using CUPL with Cypress PLDs 6-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <del>)</del> 3 |

| Using ABEL to Program the Cypress 22V10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

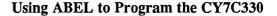

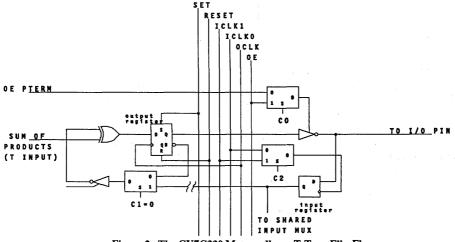

| Using ABEL to Program the CY7C330                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

| Using ABEL 3.2 to Program the Cypress CY7C331                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Using Log/IC to Program the CY7C330                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

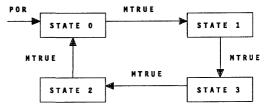

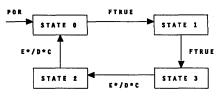

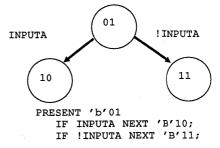

| State Machine Design Considerations and Methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

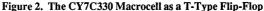

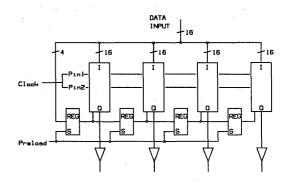

| Understanding the CY7C330 Synchronous EPLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

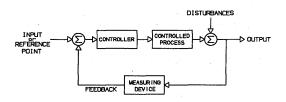

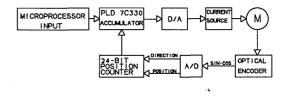

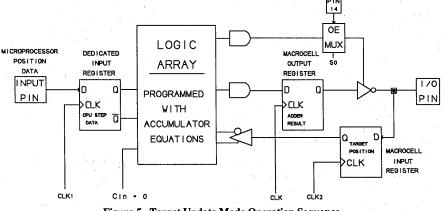

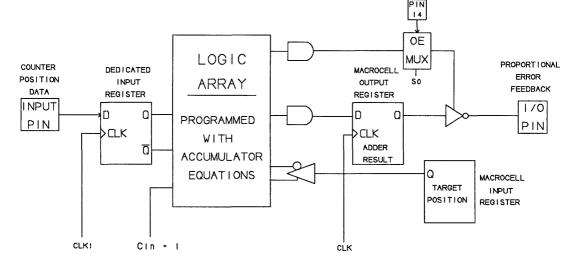

| Using the CY7C330 in Closed-Loop Servo Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

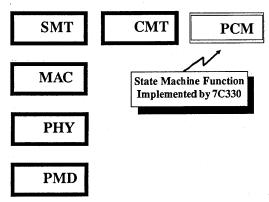

| FDDI Physical Connection Management Using the CY7C330                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

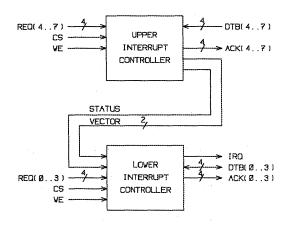

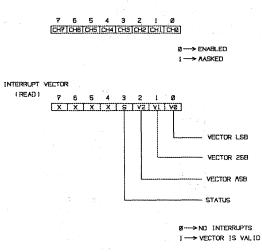

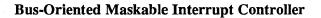

| Bus-Oriented Maskable Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |

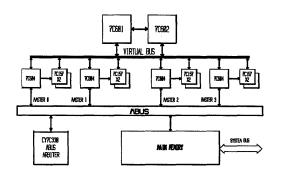

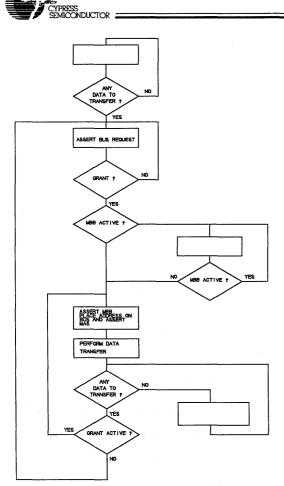

| Using the CY7C330 as a Multi-channel Mbus Arbiter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

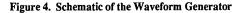

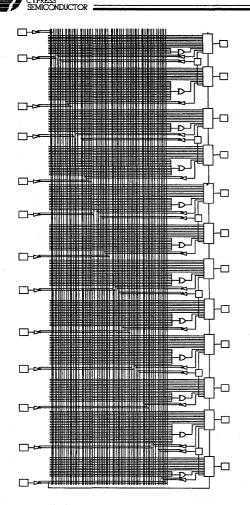

| Using the CY7C331 as a Waveform Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| CY7C331 Application Example: Asynchronous, Self-Timed VMEbus Requestor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

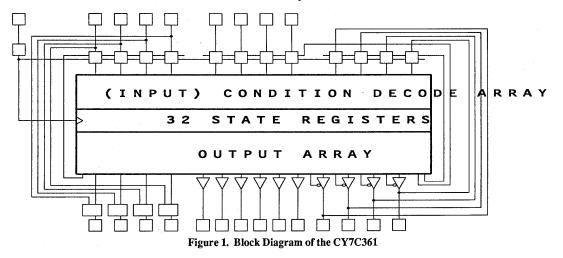

| Understanding the 361                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

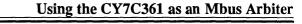

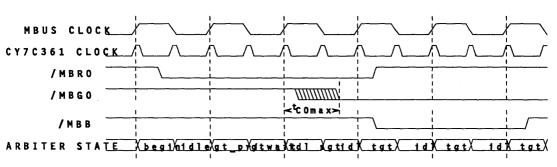

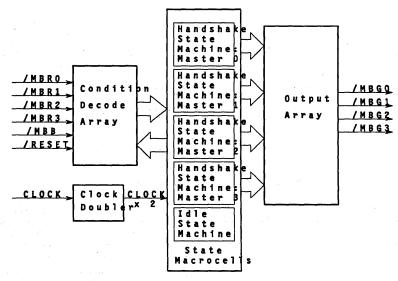

| Using the CY7C361 as an Mbus Arbiter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5              |

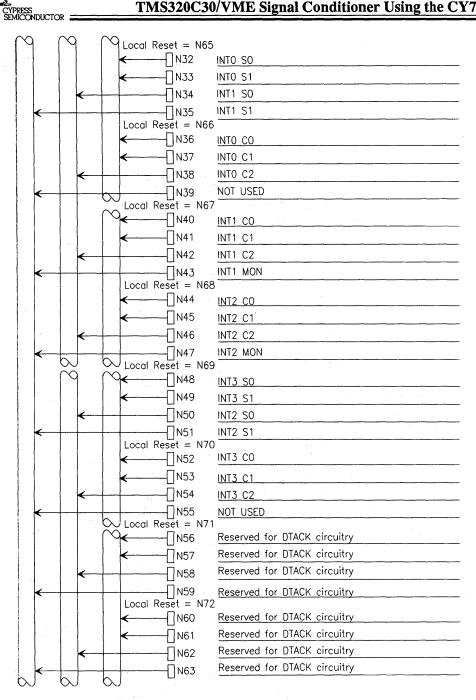

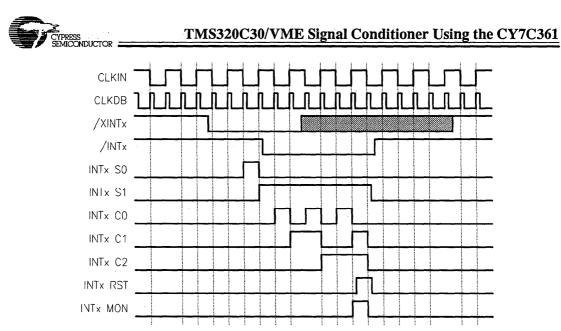

| TMS320C30/VME Signal Conditioner Using the CY7C361                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

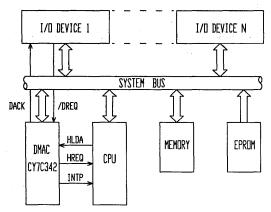

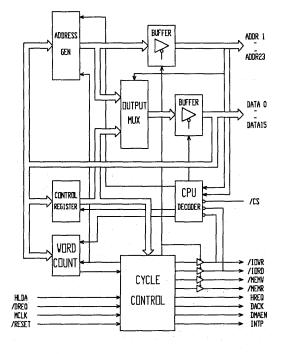

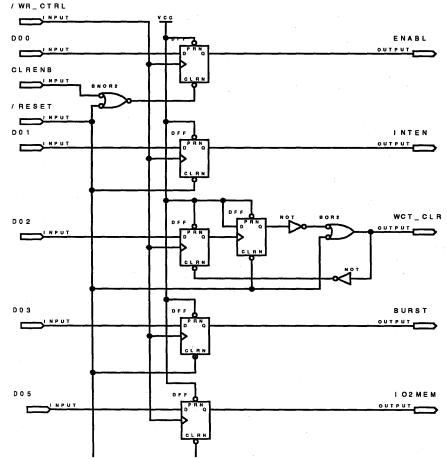

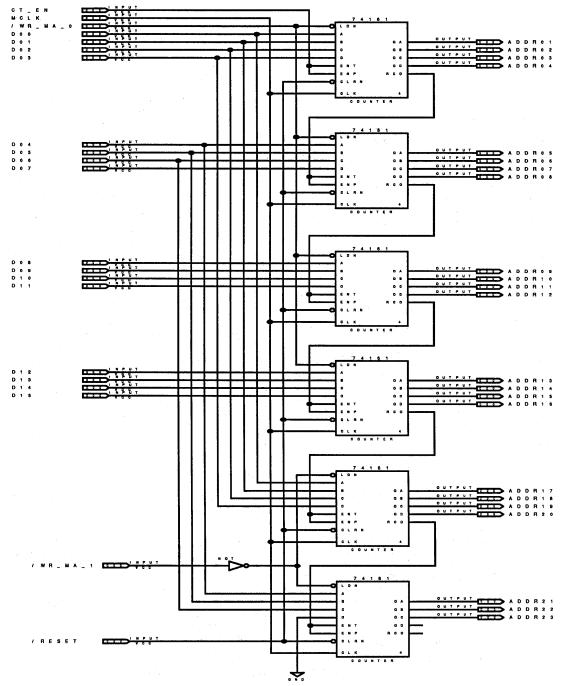

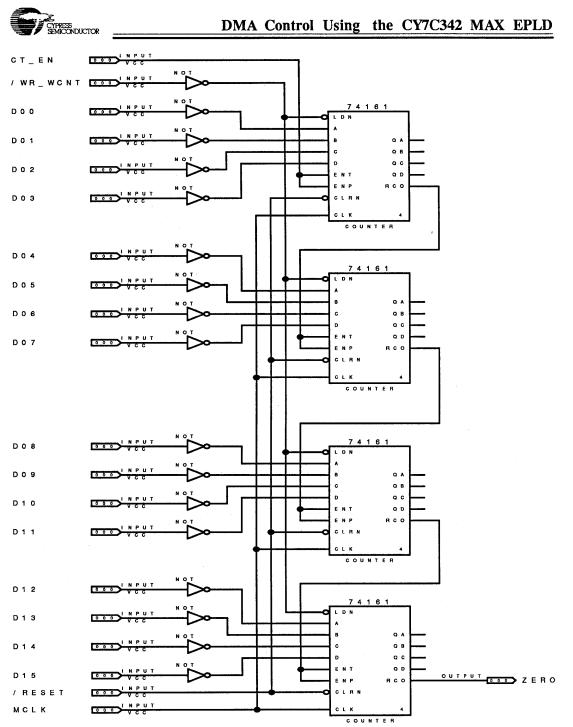

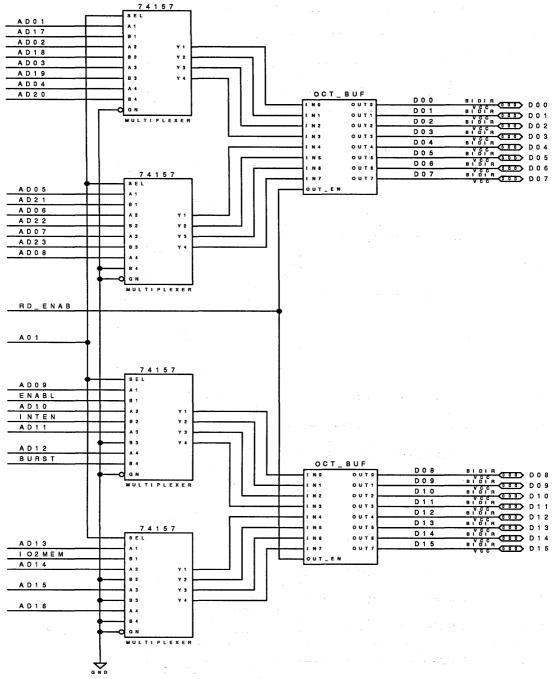

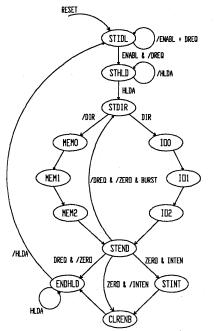

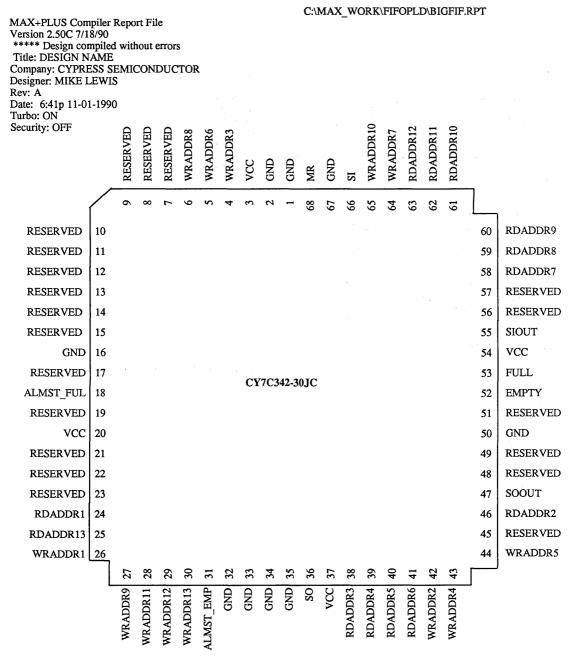

| DMA Control Using the CY7C342 MAX EPLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

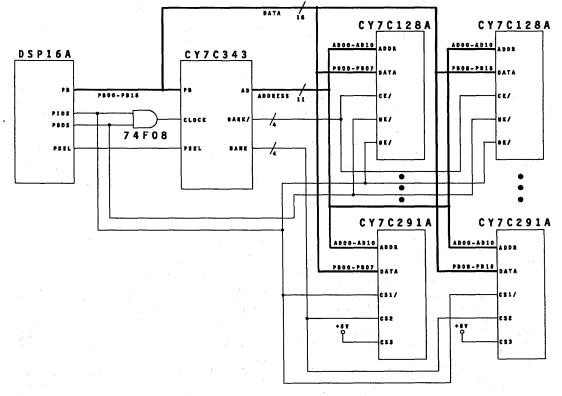

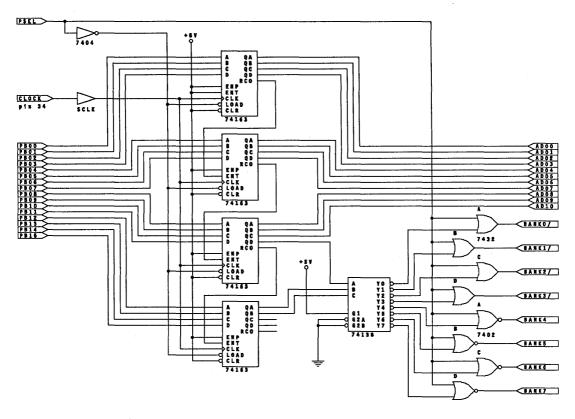

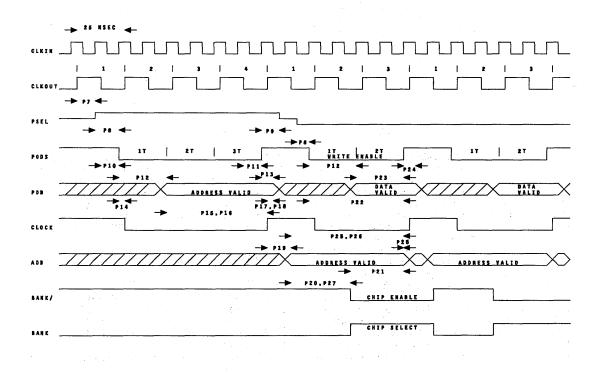

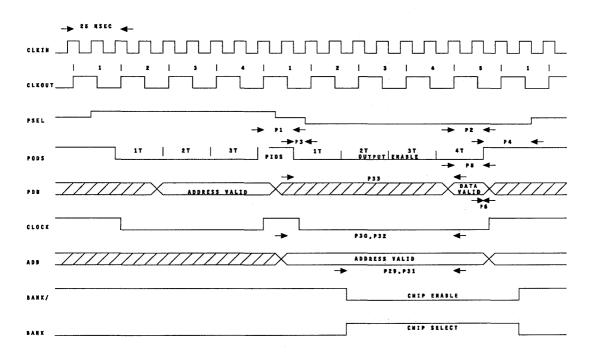

| Interfacing PROMs and RAMs to High-Speed DSP Using MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

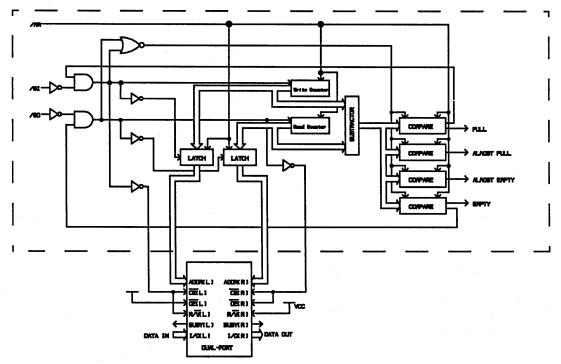

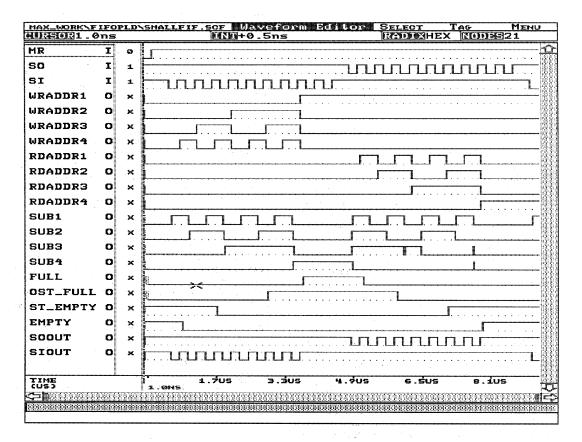

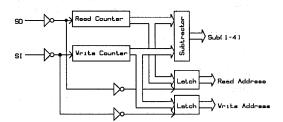

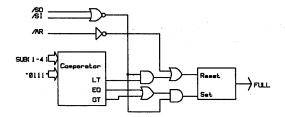

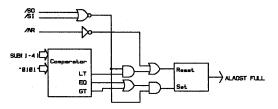

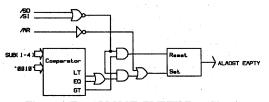

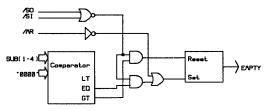

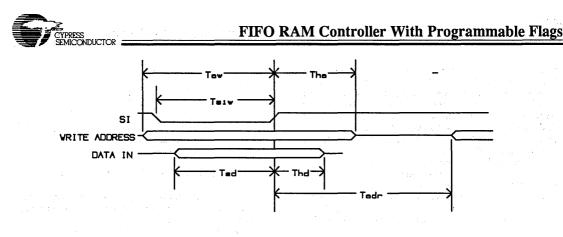

| FIFO RAM Controller with Programmable Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                |

| FIFO RAM Controller with Frogrammable Flags                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | )1             |

| in the second se |                |

| Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

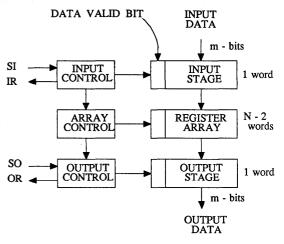

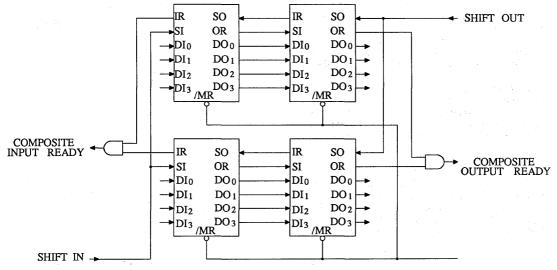

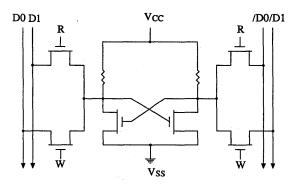

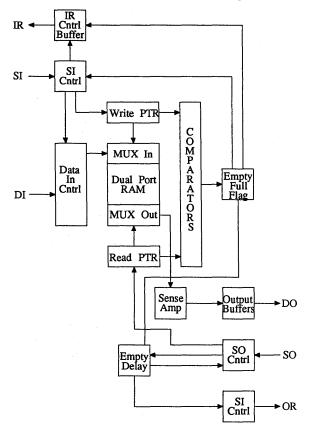

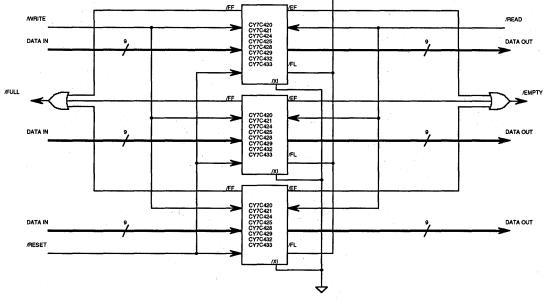

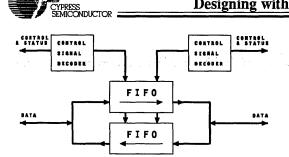

| Understanding Small FIFOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

| Understanding Large FIFOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                |

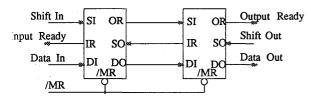

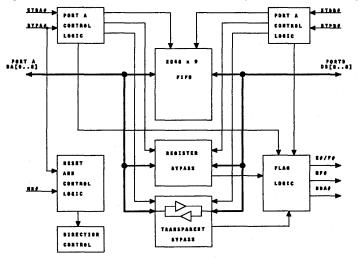

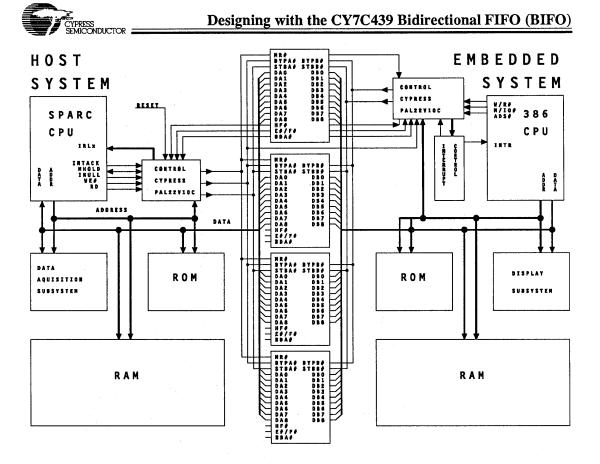

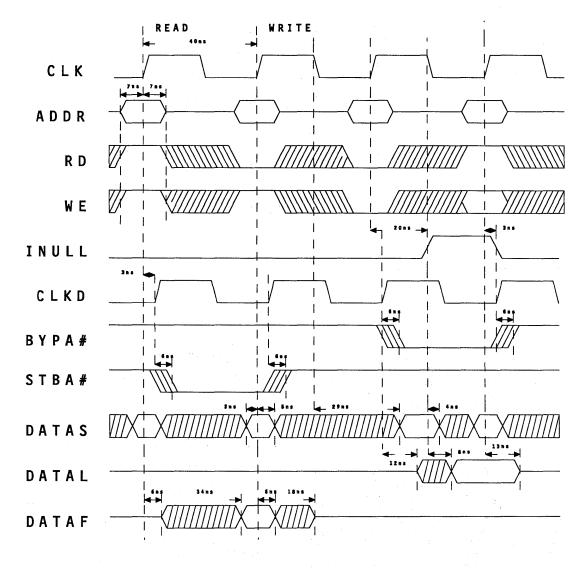

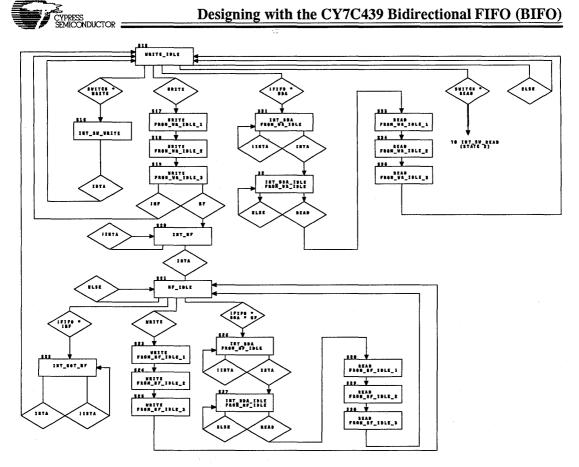

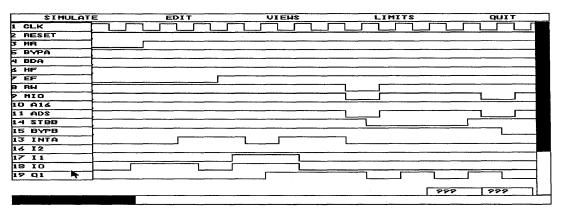

| Designing with the CY7C439 Bidirectional FIFO (BIFO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

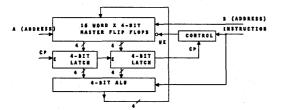

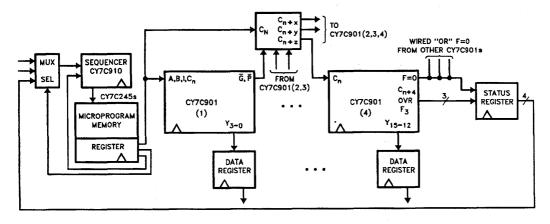

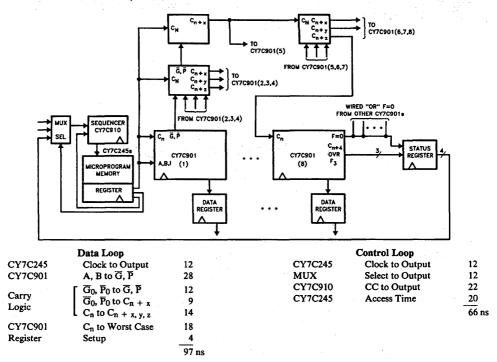

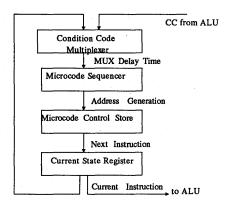

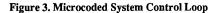

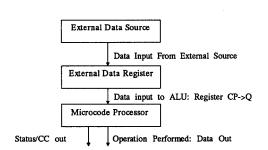

| Microcoded System Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

| Systems with CMOS 16-Bit Microprocessor ALUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 50             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| RISC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                |

| SPARC Software Advantages Over CISC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -1             |

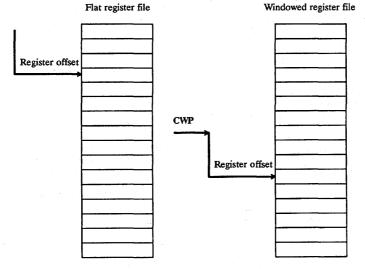

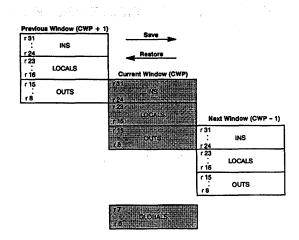

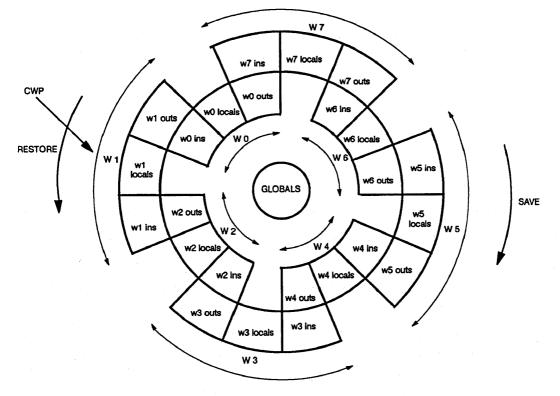

| Register Windows                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -3             |

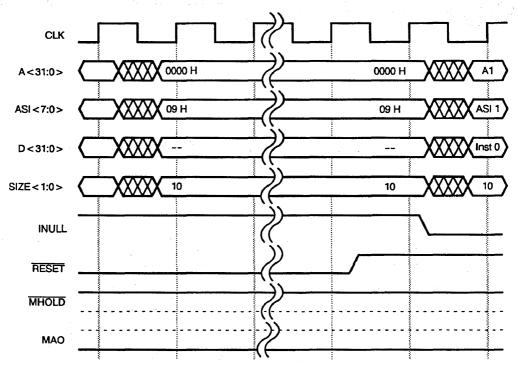

| CY7C600 System Design Footnotes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

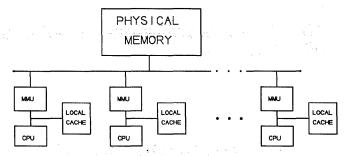

| The Impact of Memory on High-Performance RISC Microprocessors 8-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                |

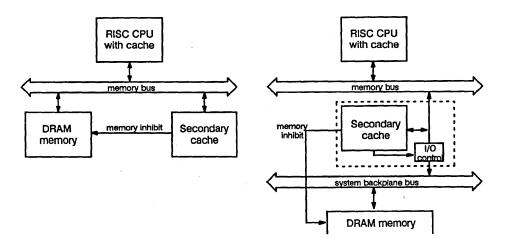

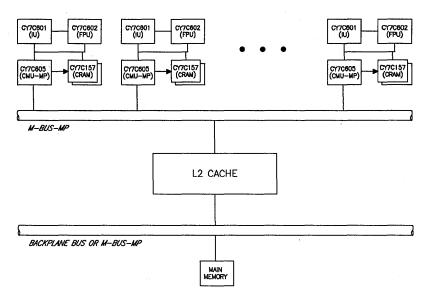

| High-Speed CMOS SPARC Design 8-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23             |

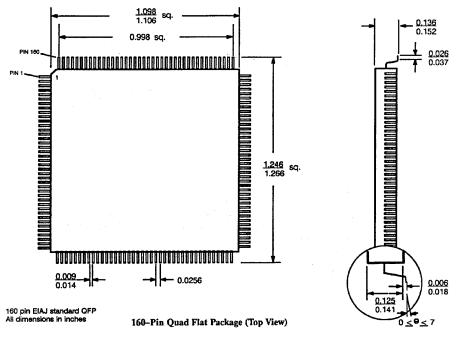

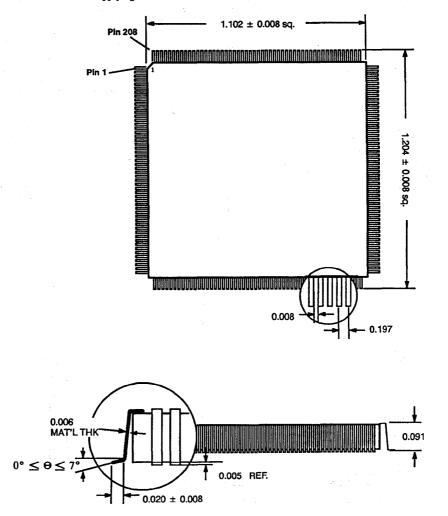

| SPARC System Surface-Mount Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33             |

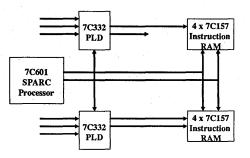

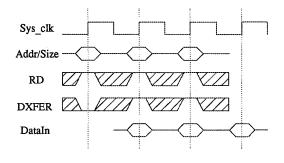

| Memory System Design for the CY7C601 SPARC Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38             |

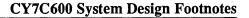

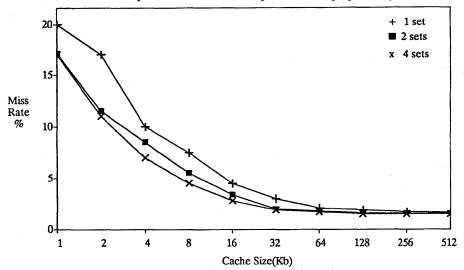

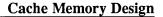

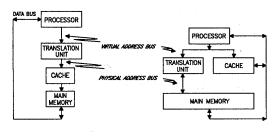

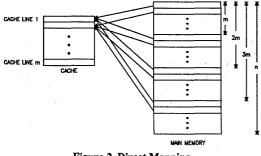

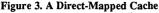

| Cache Memory Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

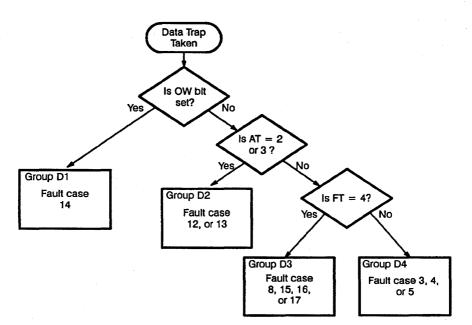

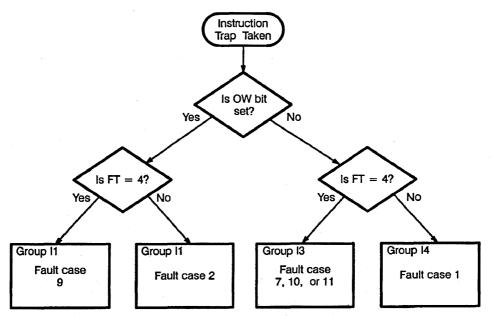

| Synchronous Trap Identification for CY7C600 Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55             |

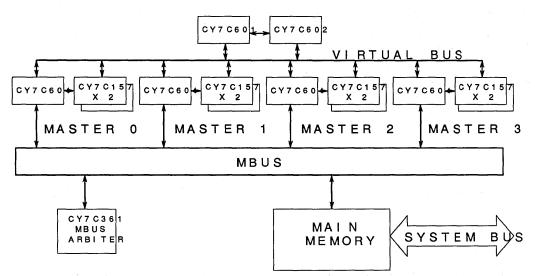

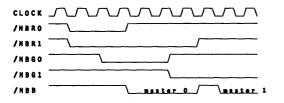

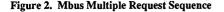

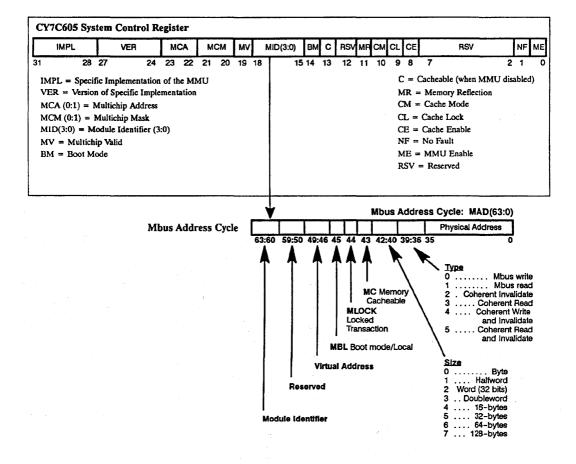

| An Introduction to Mbus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

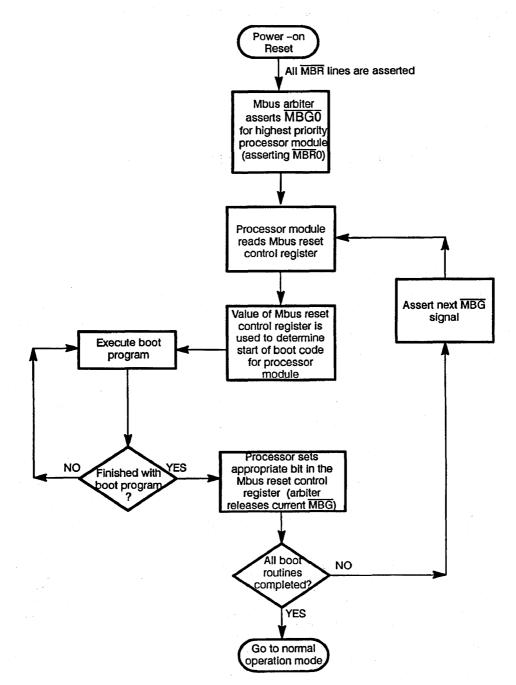

| Multiprocessing System Boot-Up 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

\_\_\_\_\_

| Page |

|------|

|      |

| RISC (continued)                                                                     |

|--------------------------------------------------------------------------------------|

| Porting UNIX to the CY7C604 or CY7C605                                               |

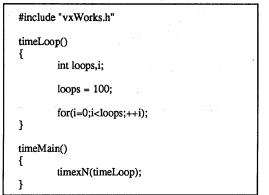

| Getting Started with Real-Time Embedded System Development                           |

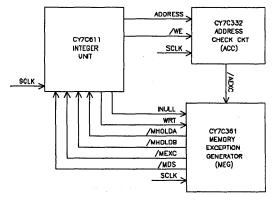

| SPARC as a Real-Time Controller                                                      |

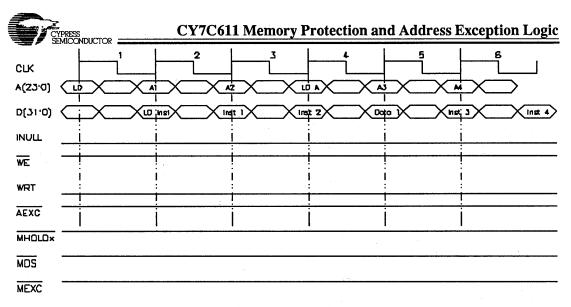

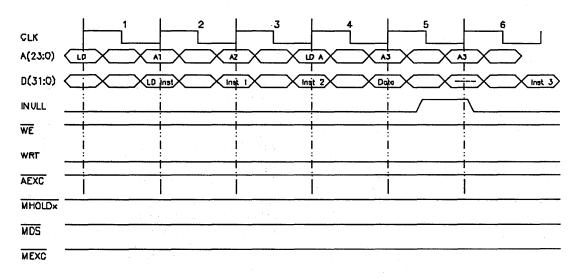

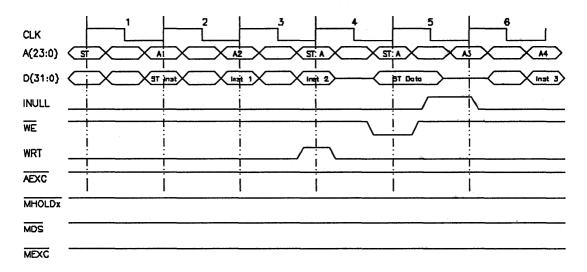

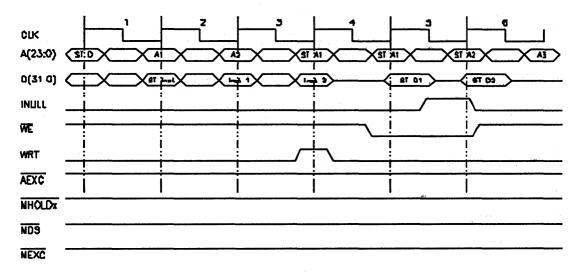

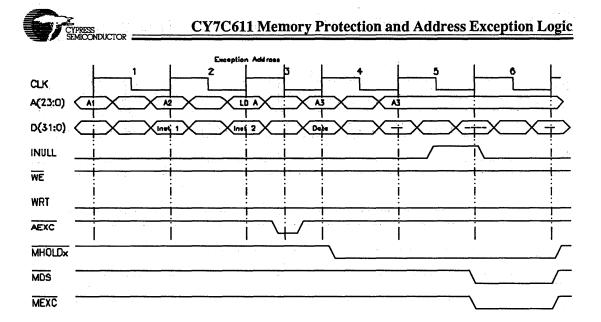

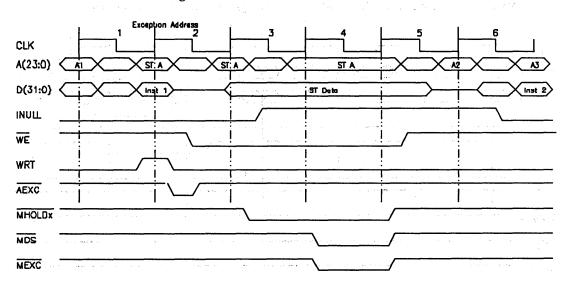

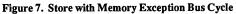

| Memory Protection and Address Exception Logic for the CY7C611 SPARC Controller 8-108 |

| Bus Products                                                                         |

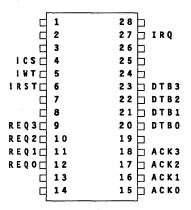

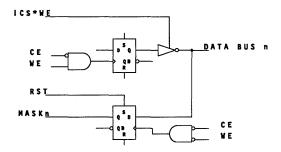

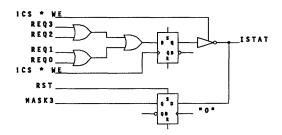

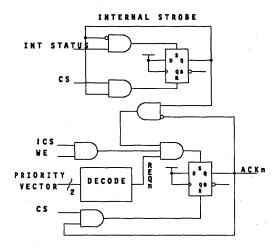

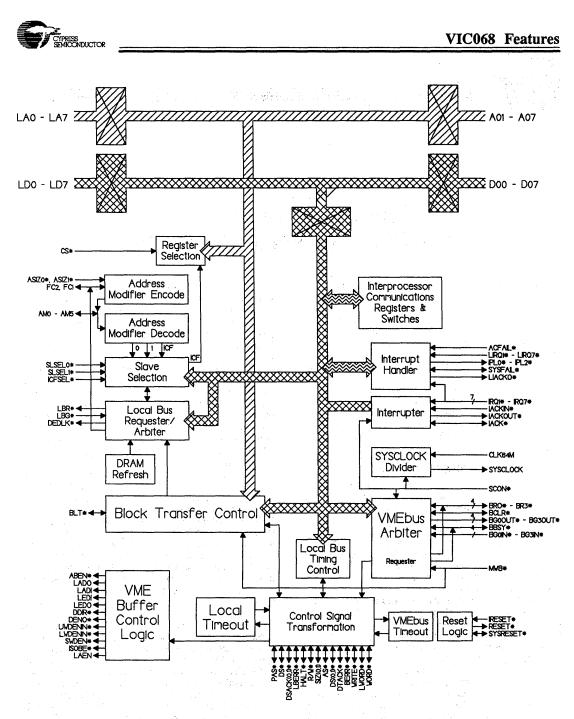

| VIC068 Special Features and Tips                                                     |

| Interfacing the VIC068 to MC68020                                                    |

| Glossary 10-1                                                                        |

| Index                                                                                |

\_\_\_\_\_

a a serie de la companya de la comp La companya de la com La companya de la comp

## **Section Contents**

# General Information System Design Considerations When Using Cypress CMOS Circuits Power Characteristics of Cypress Products 1-23 Tips for High-Speed Logic Design Protection, Decoupling, and Filtering of Cypress CMOS Circuits

#### Page

## Systems Design Considerations When Using Cypress CMOS Circuits

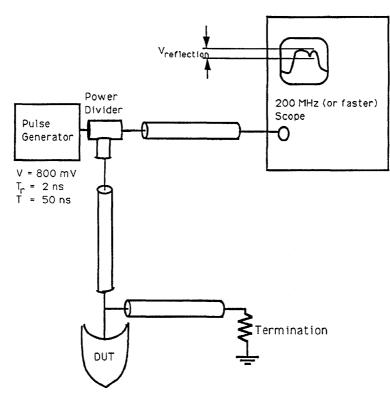

This application note describes some factors to consider when designing new systems using Cypress high-performance CMOS integrated circuits or when using Cypress products to replace either bipolar or NMOS circuits in existing systems. The two major areas of concern are device input sensitivity and transmission line effects due to impedance mismatching between the source and load.

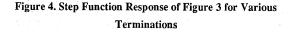

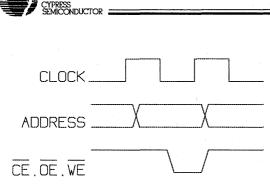

To achieve maximum performance when using Cypress CMOS ICs, pay attention to the placement of the components on the printed circuit board (PCB); the routing of the metal traces that interconnect the components; the layout and decoupling of the power distribution system on the PCB; and perhaps most important of all, the impedance matching of some traces between the source and the loads. The latter traces must, under certain conditions, be analyzed as transmission lines. The most critical traces are those of clocks, write strobes on SRAMs and FIFOs, output enables, and chip enables.

#### **Replacing Bipolar or NMOS ICs**

Cypress CMOS ICs are designed to replace both bipolar ICs and NMOS products and to achieve equal or better performance at one-third (or less) the power of the components they replace.

When high-performance Cypress CMOS circuits replace either bipolar or NMOS circuits in existing sockets, be aware of conditions in the existing system that could cause the Cypress ICs to behave in unexpected ways. These conditions fall into two general categories: device input sensitivity and sensitivity to reflected voltages.

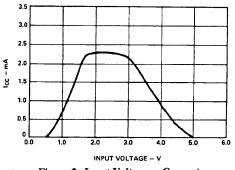

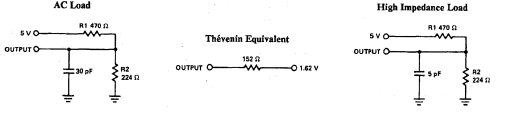

#### Input Sensitivity

High-performance products, by definition, require less energy at their inputs to change state than low- or medium-performance products.

Unlike a bipolar transistor, which is a current-sensing device, a MOS transistor is a voltage-sensing device. In fact, a MOS circuit design parameter called K' is analogous to the gm of a vacuum tube and is inversely proportional to the gate oxide thickness.

Thin gate oxides, which are required to achieve the desired performance, result in highly sensitive inputs. These inputs require very little energy at or above the device input-voltage threshold (approximately 1.5V at 25°C) to be detected. CMOS products might detect high-frequency signals to which bipolar devices would not respond.

MOS transistors also have extremely high input impedances (5 to 10 M $\Omega$ ), which make these transistors' gate inputs analogous to the input of a high-gain amplifier or an RF antenna. In contrast, because bipolar ICs have input impedances of 1000 $\Omega$  or less, these devices require much more energy to change state than do MOS ICs. In fact, a typical Cypress IC requires less that 10 picojoules of energy to change state. Thus, when Cypress CMOS ICs replace bipolar or NMOS ICs in existing systems, the CMOS ICs might respond to pulses of energy in the system that are not detected by the bipolar or NMOS products.

#### **Reflected Voltages**

Cypress CMOS ICs have very high input impedances and — to achieve TTL compatibility and drive capacitive loads — low output impedances. The impedance mismatch due to low-impedance outputs driving high-impedance inputs might cause unwanted voltage reflections and ringing, under certain conditions. This behavior could result in less-than-optimum system operation.

When the impedance mismatch is very large, a nearly equal and opposite negative pulse reflects back from the load to the source when the line's electrical length (PCB trace) is greater than

$$l = \frac{t_r}{2 T_{pd}}$$

where  $t_R$  is the rise time of the signal at the source, and  $T_{pd}$  is the one-way propagation delay of the line per unit length.

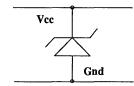

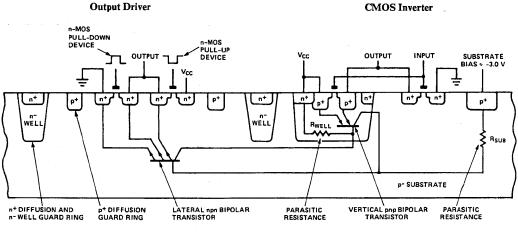

The input clamping diodes in bipolar IC families (e.g., TTL, LS, ALS, FAST, FACT) are inherent in the

fabrication process. The P substrate is usually grounded and N-wells are used for the NPN transistors and Ptype resistors. The wells are reverse biased by connecting them to the V<sub>cc</sub> supply. As a result, a PN junction diode is formed between every input pin (cathode or N material) and the substrate (anode or P material). A negative voltage at an input pin due to either lead inductance or a voltage reflection forward biases the diode, which turns on and clamps the input pin to a Vf below ground (approximately -0.8V).

Historically, as circuit performance improved, the output rise and fall times of the bipolar circuits decreased to the point where voltage reflections began to occur even for short traces when an impedance mismatch existed between the line and the load. Most users, however, were unaware of these reflections because the reflections were suppressed by the diodes' clamping action.

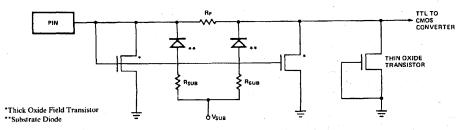

Conventional CMOS processing results in PN junction diodes, which adversely affect the ESD (electrostatic discharge) protection circuitry at each input pin and cause an increased susceptibility to latch-up. In addition, when the input pin is negative enough to forward bias the input clamping diodes, electrons are injected into the substrate. When a sufficient number of electrons are injected, the resulting current can disturb internal nodes, causing soft errors at the system level.

To eliminate this problem, all Cypress CMOS products use a substrate bias generator. The substrate is maintained at a negative 3V potential, so the substrate diodes cannot be forward biased unless the voltage at the input pin becomes a diode drop more negative than -3V. (See *Figure 5* in "CMOS PAL Basics" for a schematic of the input protection circuits used on all Cypress CMOS products.) To the systems designer, this translates to approximately five times (3.8V divided by 0.8V = 4.75) the negative undershoot safety margin for Cypress CMOS integrated circuits versus those that do not use a bias generator.

Voltage reflections should be eliminated by using impedance matching techniques and passive components that dissipate excess energy before it can cause soft errors. Crosstalk should be reduced to acceptable levels by careful PCB layout and attention to details.

#### Crosstalk

The rise and fall times of the waveforms generated by Cypress CMOS circuit outputs are 2 to 4 ns between levels of 0.4 and 4V. The fast transition times and the large voltage swings could cause capacitive and inductive coupling (crosstalk) between signals if insufficient attention is paid to PCB layout.

You can reduce crosstalk by avoiding running PCB traces parallel to each other. If this is not possible, run ground traces between signal traces.

In synchronous systems, the worst time for the crosstalk to occur is during the clock edge that samples the data. In most systems, it is sufficient to isolate the

clock, chip select, output enable, and write and read control lines from each other and from data and address lines so that the signals do not cause coupling to each other or to the data lines.

It is standard practice to use ground or power planes between signal layers on multi-layered PCBs to reduce crosstalk. The capacitance of these isolation planes increases the propagation delay of the signals on the signal layers, but this drawback is more than compensated for by the isolation the planes provide.

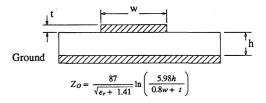

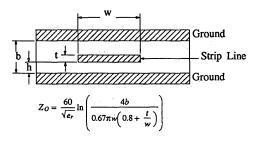

#### The Theory of Transmission Lines

A connection (trace) on a PCB should be considered as a transmission line if the wavelength of the applied frequency is short compared to the line length. If the wavelength of the applied frequency is long compared to the length of the line, you can use conventional circuit analysis.

In practice, transmission lines on PCBs are designed to be as nearly lossless as possible. This simplifies the mathematics required for their analysis, compared to a lossy (resistive) line.

Ideally, all signals between ICs travel over constantimpedance transmission lines that are terminated in their characteristic impedances at the load. In practice, this ideal situation is seldom achieved for a variety of reasons.

Perhaps the most basic reason is that the characteristic impedances of all real transmission lines are not constants, but present different impedances depending upon the frequency of the applied signal. For "classical" transmission lines driven by a single-frequency signal source, the characteristic impedance is "more constant" than when the transmission line is driven by a square wave or a pulse.

According to Fourier series expansion, a square wave consists of an infinite set of discrete frequency components — the fundamental plus odd harmonics of decreasing amplitude. When the square wave propagates down a transmission line, the higher frequencies are attenuated more than the lower frequencies. Due to dispersion, the different frequencies do not travel at the same speed.

Dispersion indicates the dependence of phase velocity upon the applied frequency (*Reference 1* pg. 192). The result is that the square wave or pulse is distorted when the frequency components are added together at the load.

A second reason why practical transmission lines are not ideal is that they frequently have multiple loads. You can distribute the loads along the line at regular or irregular intervals or lump them together as close as practical at the end of the line. The signal-line reflections and ringing caused by impedance mismatches, non-uniform transmission line impedances, inductive leads, and non-ideal resistors could compromise the dynamic system noise margins and cause inadvertent switching.

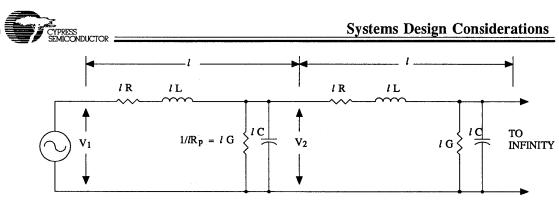

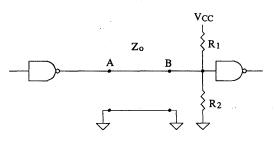

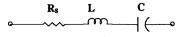

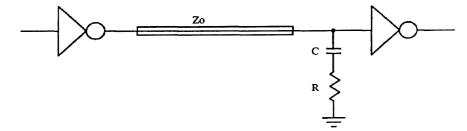

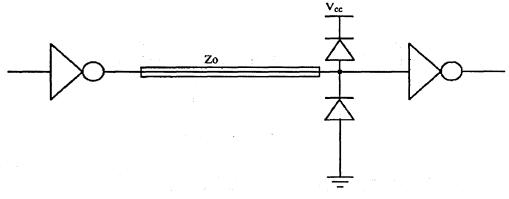

Figure 1. Transmission Line Model

One system design objective is to analyze the critical signal paths and design the interconnections such that adequate system noise margins are maintained. There will always be signal overshoot and undershoot. The objective is to accurately predict these effects, determine acceptable limits, and keep the undershoot and overshoot within the limits.

#### The Ideal Transmission Line

An equivalent circuit for a transmission line appears in Figure 1. The circuit consists of subsections of series resistance (R) and inductance (L) and parallel capacitance (C) and shunt admittance (G) or parallel resistance, Rp. For clarity and consistency, these parameters are defined per unit length. Multiply the values of R, L, C, and R<sub>p</sub> by the length of the subsection, 1, to find the total value. The line is assumed to be infinitely long.

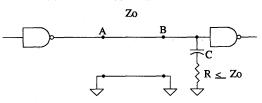

If the line of Figure 1 is assumed to be lossless (R = 0,  $R_p$  = infinity) Figure 1 reduces to Figure 2. A small series resistance has little effect upon the line's characteristic impedance. In practice and by design, the series resistance is quite small. For 1-ounce (0.0015inch-thick), 1-mil-wide (0.010-inch) copper traces on G-10 glass epoxy PCBs, the trace resistance is between 0.5 and  $0.3\Omega$  per foot. 2-ounce copper has a resistance 50 percent lower than that of 1-ounce copper.

Input or Characteristic Impedance

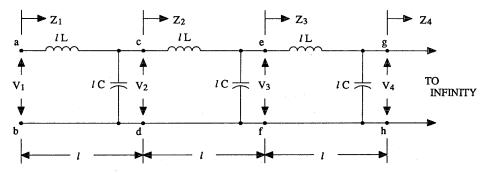

To calculate the characteristic impedance (also called AC impedance or surge impedance) looking into terminals a-b of the circuit in Figure2, use the following procedure.

Let Z<sub>1</sub> be the input impedance looking into terminals a-b, with Z<sub>2</sub> for terminals c-d, Z<sub>3</sub> for terminals e-f, etc. Z<sub>1</sub> is the series impedance of the first inductor (IL) in series with the parallel combination of Z<sub>2</sub> and the impedance of the capacitor (IC). AC theory:

$$X_L = j\omega L$$

where X<sub>L</sub> is the inductive reactance.

$$X_C = \frac{1}{i\omega lC}$$

where X<sub>C</sub> is the capacitive reactance. Then

$$Z_1 = X_L + \frac{Z_2 X_C}{Z_2 + X_C} \qquad \qquad Eq. \ l$$

If the line is reasonably long,  $Z_1 = Z_2 = Z_3$ . Substituting  $Z_1 = Z_2$  into Equation 1 yields

$$Z_{1} = X_{L} + \frac{Z_{1}X_{C}}{Z_{1} + X_{C}}$$

or,

$$Z_{1}^{2} - Z_{1}X_{L} - X_{C}X_{L} = 0$$

Eq. 2

Figure 2. Ideal Transmission Line Model

Substituting the expressions for X<sub>C</sub> and X<sub>L</sub> yields

$$Z_1^2 - j\omega lL = \frac{L}{C} \qquad \qquad Eq. 3$$

Equation 3 contains a complex component that is frequency dependent. You can eliminate the complex component by allowing 1 to become very small and by recognizing that the ratio L/C is constant and independent of l or  $\omega$ :

$$Z_1 = \sqrt{L/C} \qquad \qquad Eq. 4$$

The AC input impedance of a purely reactive, uniform, lossless line is a resistance. This is true for AC or DC excitation.

#### Propagation Velocity and Delay

The propagation velocity (or phase velocity) of a sinusoid traveling on an ideal line (*Reference 1* pg. 33) is

$$\alpha = \frac{1}{\sqrt{LC}}$$

The propagation delay for a lossless line is the reciprocal of the propagation velocity:

$$\begin{aligned} \Gamma_{pd} &= \sqrt{LC} & Eq. 5 \\ &= Z_1 C \end{aligned}$$

where L and C are once again the intrinsic line inductance and capacitance per unit length.

Adding additional stubs or loads to the line (*Reference* 2 pg. 129) increases the propagation delay by the factor

$\sqrt{1 + C_{D/C}}$

where CD is the load capacitance.

Therefore, the propagation delay of a loaded line,  $T_{pdL},\,is$

$T_{pdL} = T_{pd} \sqrt{1 + C_{D'C}} \qquad Eq. 6$

This application note shows later that a transmission line's unloaded or intrinsic propagation delay is proportional to the square root of the dielectric constant of the medium surrounding or adjacent to the line. Propagation delay is not a function of the line's geometry.

The characteristic impedance of a capacitively loaded line decreases by the same factor that the propagation delay increases:

$$Z_1' = \frac{Z_1}{\sqrt{1 + C\rho/C}} \qquad \qquad Eq. 7$$

Note that the capacitance per unit length must be multiplied by the line length, l, to calculate an equivalent lumped capacitance.

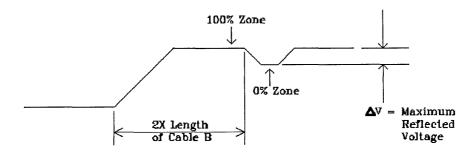

#### The Condition for Voltage Reflection

It is relatively straightforward to obtain a closedform solution for a transmission line's maximum allowable length, which, if exceeded, might cause a voltage reflection. If the line is not terminated in its characteristic impedance, a reflection is guaranteed to occur. The reflection's amplitude depends on the amount of impedance mismatch between the line and the load and whether the rise time of the signal at the source equals or is greater (slower) than two times the propagation delay of the line.

The condition for a voltage reflection to occur is

$$L \ge \frac{t_r}{2 T_{pdL}} \qquad \qquad Eq. 8$$

Solving for the loaded propagation delay yields

$$T_{pdL} = \frac{t_r}{2L} \qquad \qquad Eq. 9$$

However, the actual physical length of the line is

$$l = \frac{t_r}{2T_{pd}} \qquad \qquad Eq. \ 10$$

The intrinsic capacitance of the line from Equation 5 is  $T_{Pd}$

$$C_o = \frac{I_{pa}}{Z_o} \qquad \qquad Eq. \, 11$$

It is standard practice to use  $C_o$  to designate the intrinsic line capacitance,  $L_o$  the intrinsic line self inductance, and  $Z_o$  the intrinsic line characteristic impedance .

Substituting the expressions from Equations 9, 10, and 11 into Equation 6 gives the relationship for the line length at which voltage reflections might occur. Two conditions must be present for voltage reflections to occur: The line must be long, and there must be an impedance mismatch between the line and the load.

$$\frac{t_r}{2L} = T_{pd} / 1 + \frac{C_D}{\frac{t_r}{T_{pd}} \times \frac{T_{pd}}{Z_o}} Eq. 12$$

Solving Equation 12 for the line length, l, yields

$$L = \frac{t_r}{2T_{pd}} \sqrt{\frac{1}{1 + \frac{C_D Z_o}{t_r}}} \qquad Eq. 13$$

Equation 13 is very useful to the system designer. It is generic and applies to all products irrespective of circuit type, logic family, or voltage levels. The equation allows you to estimate when a line requires termination, using variables you can easily determine.

When driving a distributed or non-lumped load, the signal's rise time depends on the source — not the load, as you might expect. The intrinsic, or unloaded, line propagation delay per unit length is a function of the dielectric constant and can be easily calculated. The intrinsic line characteristic impedance is a function of the dielectric constant and the PCB's physical construction or geometry and can also be calculated. Finally, you can estimate the equivalent (lumped) load capacitance by adding up the number of loads (device inputs) being driven and multiplying by 10 pF. For I/O pins, use 15 pF per pin.

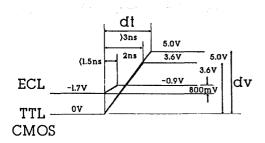

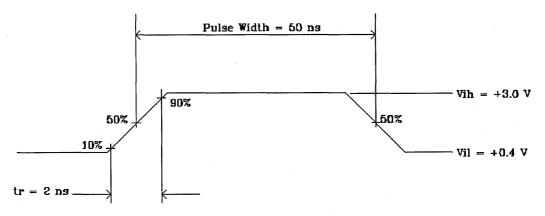

#### Signal Transition Times

The standard Cypress  $0.8\mu$  (L drawn) CMOS process yields output buffers whose signals transition approximately 4V in 2 ns, or, have a slew rate of 2V per

nanosecond. The rise time/fall time is 2 ns. Products fabricated using the Cypress BiCMOS process have the same rise times.

The Cypress ECL process yields products with 500ps output signal rise times and fall times, or slew rates of 1V/0.5 ns = 2V per nanosecond. Internal signal slew rates are 10V per nanosecond, but only for short (usually less than 500 mV) voltage excursions. Thus, high-frequency noise is generated on chip, which you can eliminate by using 100- to 500-pF ceramic or mica filter capacitors between V<sub>cc</sub> and ground.

The values in *Table 1* come from using Equation 13 to calculate the line length at which voltage reflections might occur. The calculations assume a  $50\Omega$  intrinsic line characteristic impedance and that the PCB is multilayer, using stripline construction on G-10 glass epoxy material (dielectric constant of 5). These conditions result in an unloaded line propagation delay of 2.27 ns per foot.

Table 1 reveals that decreasing the source rise time from 2 to 0.5 ns (a factor of 4) decreases the line length at which a voltage reflection might occur by a factor of 5 (4.73 divided by 0.93 = 5.09) for the same load (10 pF) and intrinsic propagation delay (2.27 ns/ft.). A second observation is that for signals with rise times of 0.5 ns, you should terminate all lines.

#### **Reflection Coefficients**

Another attribute of the ideal transmission line is reflection coefficients, which are not actually line characteristics. The line is treated as a circuit component, and reflection coefficients are defined that measure the impedance mismatches between the line and its source and the line and its load. The reason for defining and presenting the reflection coefficients becomes apparent later when it is shown that if the impedance mismatch is sufficiently large, either a negative or positive voltage

Table 1. Line Length at which a Voltage Reflection

Occurs

| t <sub>r</sub> (ns) | Cp (pF) | L (inches) |

|---------------------|---------|------------|

| 2                   | 10      | 4.73       |

| 2                   | 20      | 4.32       |

| 2                   | 40      | 3.74       |

| 2                   | 80      | 3.05       |

| 1                   | 10      | 2.16       |

| 1                   | 20      | 1.87       |

| 1                   | 40      | 1.53       |

| 1                   | 80      | 1.18       |

| 0.5                 | 10      | 0.93       |

| 0.5                 | 20      | 0.76       |

| 0.5                 | 40      | 0.59       |

| 0.5                 | 80      | 0.44       |

reflects back from the load to the source, where the voltage either adds to or subtracts from the original signal. A mismatch between the source and line impedance might also cause a voltage reflection, which in turn reflects back to the load. Therefore, two reflection coefficients are defined.

For classical transmission lines driven by a single frequency source, the impedance mismatches cause standing waves. When pulses are transmitted and the source's output impedance changes depending upon whether a Low-to-High or a High-to-Low transition occurs, the analysis is complicated further.

You can use classical transmission line analysis where pulses are represented by complex variables with exponentials — to calculate the voltages at the source and the load after several back and forth reflections. However, these complex equations tend to obscure what is physically happening.

#### **Energy Considerations**

Now consider the effects of driving the ideal transmission line with digital pulses and analyze the behavior of the line under various driving and loading conditions. The first task is to define the load and source reflection coefficients.

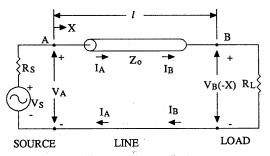

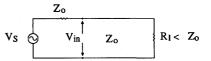

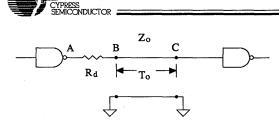

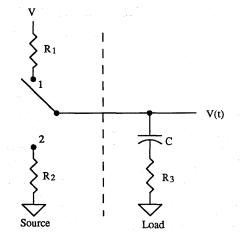

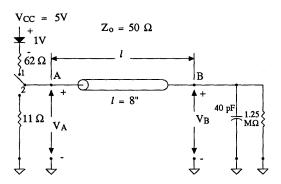

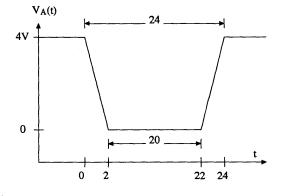

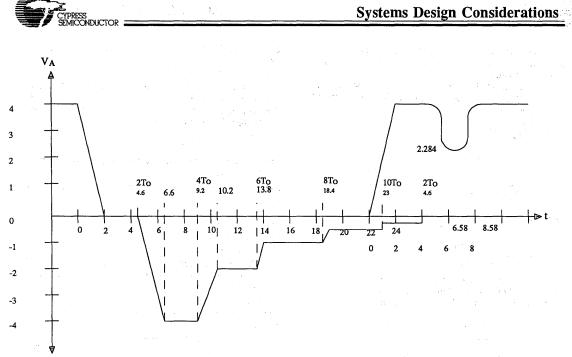

Figure 3 shows the circuit to be analyzed. The ideal transmission line of length 1 is driven by a digital source of internal resistance  $R_s$  and loaded with a resistive load  $R_L$ . The characteristic impedance of the line appears as a pure resistance,

$Z_o = \sqrt{L/C}$

to any excitation.

The ideal case is when  $R_s = Z_o = R_L$ . The maximum energy transfer from source to load occurs under this condition, and no reflections occur. Half the energy is dissipated in the source resistance,  $R_s$ , and the other half is dissipated in the load resistance,  $R_L$  (the line is lossless).

If the load resistor is larger than the line's characteristic impedance, extra energy is available at the load and is reflected back to the source. This is called the underdamped condition, because the load under-uses the energy available. If the load resistor is smaller than the line impedance, the load attempts to dissipate more energy than is available. Because this is not possible, a reflection occurs that signals the source to send more energy. This is called the overdamped condition. Both the underdamped and overdamped cases cause negative traveling waves, which cause standing waves if the excitation is sinusoidal. The condition  $Z_0 = R_L$  is called critically damped.

The safest termination condition, from a systems design viewpoint, is the slightly overdamped condition, because no energy is reflected back to the source.

#### Line Voltage For a Step Function

To determine the line voltage for a step function excitation, you apply a step function to the ideal line

and analyze the behavior of the line under various loading conditions. The step function response is important because any pulse can be represented by the superposition of a positive step function and a negative step function, delayed in time with respect to each other. By proper superposition, you can predict the response of any line and load to any width pulse. The principle of superposition applies to all linear systems.

According to theory, the rise time of the signal driven by the source is not affected by the characteristics of the line. This has been substantiated in practice by using a special coaxially constructed reed relay that delivers a pulse of 18A into  $50\Omega$  with a rise time of 0.070 ns (*Reference 1* pg. 162).

The equation representing the voltage waveform going down the line (*Figure 3*) as a function of distance and time is

$$V_L(X, t) = V_A(t) U(t - X t_{pd}) \text{ for } t < T_O \qquad Eq. 14$$

$$V_A(t) = V_S(t) \left( \frac{Z_o}{Z_o + R_S} \right) \qquad Eq. 15$$

where

$V_A$  = the voltage at point A

X = the voltage at a point X on the line

l = the total line length

$t_{pd}$  = the propagation delay of the line in nanoseconds per foot

$T_o = 1 t_{pd}$ , or the one-way line propagation delay

U(t) = a unit step function occurring at x = 0

$V_s(t)$  = the source voltage

When the incident voltage reaches the end of the line, a reflected voltage, VL', occurs if  $R_L$  does not equal  $Z_0$ . The reflection coefficient at the load, $\rho_L$ , can be obtained by applying Ohm's Law.

The voltage at the load is  $V_L + V_L'$ , which must be equal to  $(I_L + I_L')R_L$ . But

$$I_L = \frac{V_L}{Z_o}$$

and

$I_L' = -\frac{V_L'}{Z_o}$

(The minus sign is due to  $I_L$  being negative; i.e.,  $I_L$  is opposite to the current due to  $V_L$ .) Therefore,

$$V_B = V_L + V_L' = \left(\frac{V_L}{Z_o} - \frac{V_L'}{Z_o}\right) R_L \qquad Eq. 16$$

By definition:

$$\rho_L = \frac{\text{reflected voltage}}{\text{incident voltage}} = \frac{V_L'}{V_L}$$

Solving for  $V_L'/V_L$  in Equation 16 and substituting in the equation for  $\rho_L$  yields

$$\rho_L = \frac{R_L - Z_o}{R_L + Z_o} \qquad \qquad Eq. 17$$

The reflection coefficient at the source is

Rearranging Equation 16 yields

$$V_B = V_L + V_L' = \left(1 + \frac{V_L'}{V_L}\right) V_L \qquad \qquad Eq. 19$$

$= (1 + \rho_L) V_L$

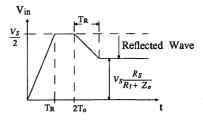

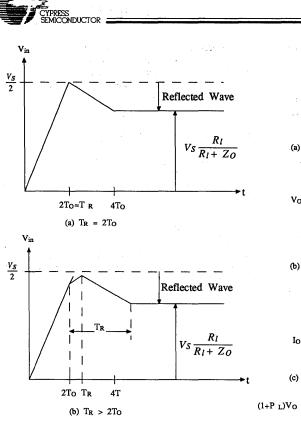

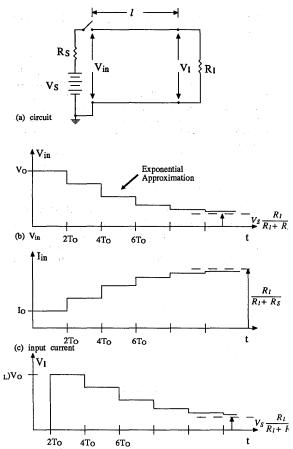

Equation 19 describes the voltage at the load (VB) as the sum of an incident voltage (VL) and a reflected voltage ( $\rho_L$  VI) at time  $t = T_0$ . When  $R_L = Z_0$ , no voltage is reflected. When  $R_L < Z_0$ , the reflection coefficient at the load is negative; thus, the reflected voltage subtracts from the incident voltage, giving the load voltage. When  $R_L > Z_0$ , the reflection coefficient is positive; thus, the reflected voltage adds to the incident voltage, again giving the load voltage.

Note that the reflected voltage at the load has been defined as positive when traveling toward the source. This means that the corresponding current is negative, subtracting from the current driven by the source.

This piecewise analysis is cumbersome and can be tedious. However, it does provide an insight into what is physically happening and demonstrates that a complex problem can be solved by dividing it into a series of simpler problems. Also, eliminating the exponentials which provide phase information in the classical transmission line equations — simplifies the mathematics. To use the piecewise method, you must do careful bookkeeping to combine the reflections at the proper time. This is quite straightforward, because a pulse travels with a constant velocity along an ideal or low-loss line, and the time delay between reflected pulses can be predicted.

The rules to keep in mind are that at any location and time the voltage or the current is the algebraic sum of the waves traveling in both directions. For example, two voltage waves of the same polarity and equal amplitudes, traveling in opposite directions, at a given location and time add together to yield a voltage of twice the amplitude of one wave. The same reasoning applies to all points of termination and discontinuities on the line. The total voltage or current is the algebraic sum of all the incident and reflected waves. Polarities must be observed. A positive voltage reflection results in a negative current reflection and vice versa.

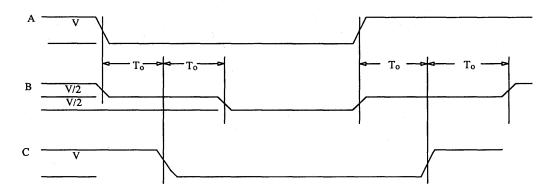

#### Step Function Response of the Ideal Line

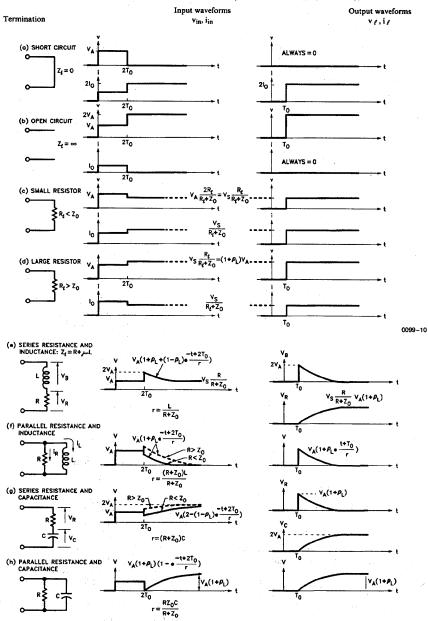

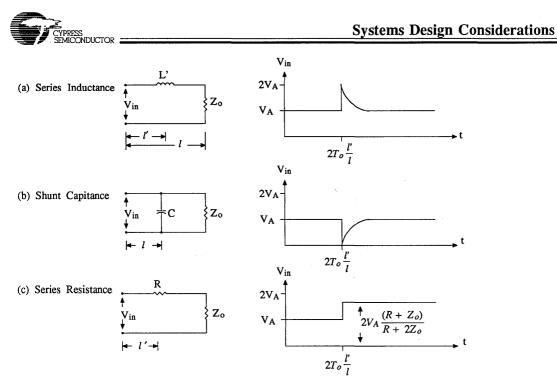

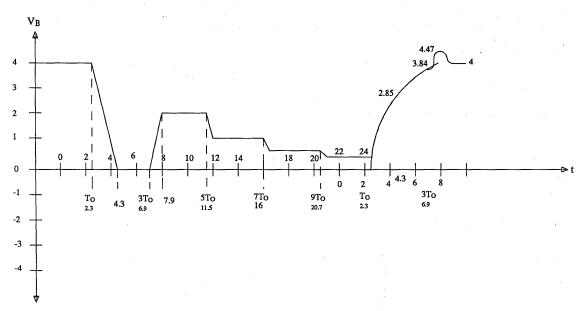

Before examining reflections at the source due to mismatches between the source and line impedances, consider the behavior of the ideal line with various loads when driven by a step function. The circuit for analysis appears in *Figure 3*. *Figure 4* shows the voltage and current waveforms at point A (line input) and point B (the load) for various loads. (These values are drawn from *Reference 1* pg. 158 - 159.) Note that  $R_s = Z_0$  and that  $V_A$  at t = 0 equals  $V_s/2$ . This means that no impedance mismatch exists between the source and the line; thus, there is no reflection from the source at t = $2T_0$ .  $T_0$  is the one-way propagation delay of the line.

The time-domain response of the reactive loads are obtained by applying a step function to the LaPlace transform of the load, then taking the inverse transform.

Note that the reflection coefficient at the load is not the total reflection coefficient (a complex number) but represents only the real part of the load. The piecewise method eliminates the complex ( $j\omega t$ ) terms by performing the bookkeeping involving the phase relationships, which the complex terms account for in classical transmission line analysis.

Note that for the open-circuit condition in Figure 4b,  $Z_L =$  infinity, so that  $\rho_L = +1$ . The voltage is reflected from the load to the source (at amplitude  $V_0 = V_s/2$ ). Thus, at time = 2 T<sub>0</sub>, the reflected voltage adds to the original voltage,  $V_0 = V_s/2$ , to give a value of  $2V_0 = V_s$ . While the voltage wave is traveling down to and back from the load, a current of