# FEATURES

- Selectable open-drain or push-pull SCSI drivers

- Fast microcontroller interface —16 MHz 8051, 12 MHz 68HC11, etc.

- NRZ data rates up to 24 Mbits/second

- Selectable 16-bit CRC/32-bit ECC/56-bit ECC polynominal with fast hardware correction circuitry<sup>†</sup>

- Support of concurrent non-interleaved disk transfer and SCSI bus transfer

- Interrupt or polled microcontroller interface

- Direct buffer memory addressing up to 64K bytes static RAM

- Dual port circular buffer memory control with access priority resolver

- User-modifiable format sequencer with a RAM-based Writable Control Store (WCS – 31 x 4 bytes)

- Microcontroller access to eight external switch settings

- Can be used with ST506/412, ST412HP, ESDI, and SMD disk interfaces

- Support of buffer memory throughput up to 6 Mbytes/second

- SCSI DMA handshake logic that handles asynchronous transfer at rates up to 3 Mbytes/second

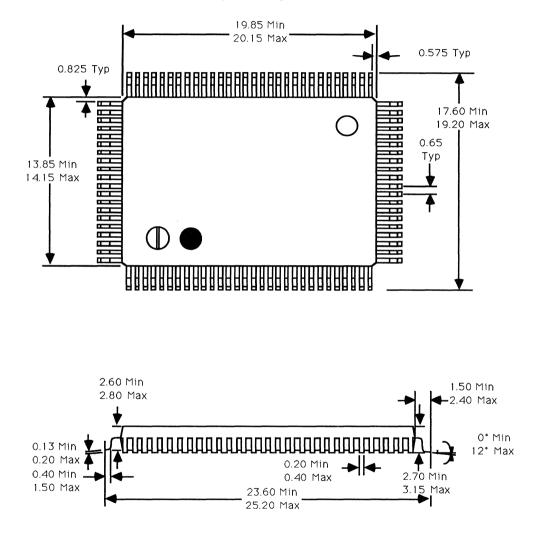

- Low-power CMOS technology in a 100-pin QFP

# Integrated SCSI Disk Controller

- for low-cost systems -

## OVERVIEW

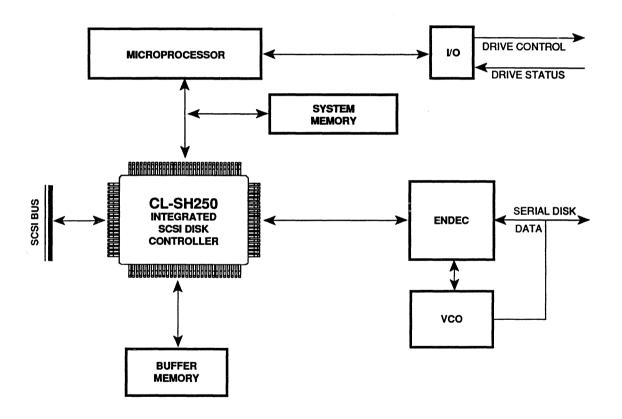

The highly integrated CL–SH250 provides a large portion of the hardware necessary to build a SCSI Winchester disk controller. The controller includes an advanced Winchester disk formatter, a dual-port Buffer Manager, and extensive hardware support (including 48 mA drivers). Also, disk data rates up to 24 Mbits/second are supported.

The CL-SH250 disk formatter consists of a serializer/deserializer, a flexible RAM-based sequencer, and CRC/ECC generation circuitry. Industrystandard 16-bit CCITT-CRC, 32-bit Fire Code, and computer-generated 56-bit ECC polynomials are all supported in hardware. (cont. next page)

† U.S. Patents No.4,293,783 and No.4,979,173

## OVERVIEW (cont.)

The ECC circuitry includes hardware correction assist logic to speed the correction process. The CL-SH250 buffer manager will control up to 64K bytes of SRAM buffer memory as a dual port circular buffer.

The CL-SH250 works with a local microcontroller

which has a multiplexed address and data bus similar to that provided by the Intel® 8051 family of microcontrollers and the Motorola® 68HC11. It is easily adaptable to other microcontroller I/O techniques and supports both interrupt and polled processor interfaces. Maskable interrupts and status bits include 13 disk and host interface events.

.....

## ADVANTAGES

#### **Unique Features**

- 31 Words of Writable Control Store

- Computer generated 56-bit ECC polynomial embedded in hardware

- Fire Code 32-bit ECC polynomial embedded in hardware

- ECC circuitry provides logic to speed the correction process

- Data rate up to 24 Mbits/second

- Maskable microcontroller interrupt capability

- Sector Size Counter

- Directly accesses 64K bytes of SRAM

- Provides microcontroller access to eight external switch settings

- 3 Mbytes/second SCSI transfer rate

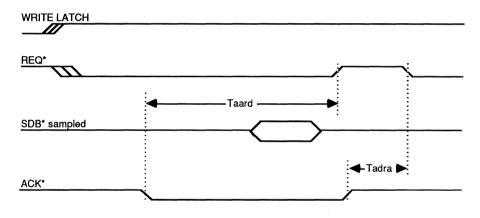

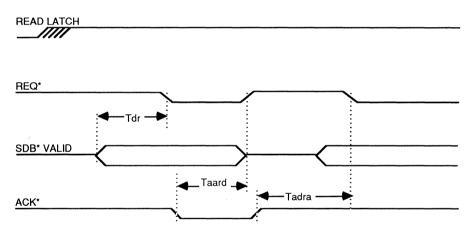

- Direct I/O path, with REQ/ACK handshake, between the microcontroller and the SCSI bus during disk/buffer memory transfer

- Provides on-chip, SCSI-specified, 48 mA open-drain drivers

- Provides programmable, on-chip push-pull drivers for SCSI bus

- Pin-out organized for optimum board layout efficiency

#### Benefits

Provides flexibility for the sequencer to perform various disk controller operations.

Supports single-burst error correction up to 23 bits. Probability of miscorrection as low as  $10^{-14}$  per bit corrected.

Supports single-burst correction up to 11 bits.

Provides hardware correction with minimal MPU intervention. Can correct within a single sector time.

Can be used in high-performance applications.

Relieves the microcontroller from polling and thus enables it to perform other tasks. Provides status information to the microcontroller when interrupts are disabled.

Reads and writes sectors larger than 512 bytes without microcontroller intervention.

Requires no external hardware for buffer memory sizes up to 64K bytes.

Enables the microcontroller to read SCSI ID, SCSI Parity Enable or other switch-settable information.

Allows fast data transfer to the host.

Ensures that the microcontroller is never locked off from the SCSI bus.

Eliminates external transceiver ICs.

Can eliminate termination networks in some cabling configurations.

Simplifies board layout, reduces need for multilayered board. Data Sheet

# CONTENTS

| 1.       | PIN                                                                                                                                                                | INFORMATION 4                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1                                                                                                                                                                | 100-pin Diagram4                                                                                                                                                                                                                                                                                                                                                                                         |

|          | 1.2                                                                                                                                                                | Pin Assignments5                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.       | REG                                                                                                                                                                | ISTER TABLES 12                                                                                                                                                                                                                                                                                                                                                                                          |

|          | 2.1                                                                                                                                                                | Buffer Manager/SCSI Interface Registers 12                                                                                                                                                                                                                                                                                                                                                               |

|          | 2.2                                                                                                                                                                | Disk Formatter Registers 13                                                                                                                                                                                                                                                                                                                                                                              |

|          | 2.3                                                                                                                                                                | External Access Registers 13                                                                                                                                                                                                                                                                                                                                                                             |

|          | 2.4                                                                                                                                                                | Writable Control Store (WCS) 13                                                                                                                                                                                                                                                                                                                                                                          |

|          | 2.5                                                                                                                                                                | Sequencer Registers 13                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.       | FUN                                                                                                                                                                | CTIONAL DESCRIPTION 14                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 3.1                                                                                                                                                                | Microcontroller Interface14                                                                                                                                                                                                                                                                                                                                                                              |

|          | 3.2                                                                                                                                                                | Disk Formatter 15                                                                                                                                                                                                                                                                                                                                                                                        |

|          | 3.3                                                                                                                                                                | Buffer Memory Interface 16                                                                                                                                                                                                                                                                                                                                                                               |

|          | 3.4                                                                                                                                                                | SCSI Bus Interface 18                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.       |                                                                                                                                                                    | CTIONAL OPERATION 20                                                                                                                                                                                                                                                                                                                                                                                     |

|          | 4.1                                                                                                                                                                | Sector Identification 20                                                                                                                                                                                                                                                                                                                                                                                 |

|          | 4.2                                                                                                                                                                | Sector Read                                                                                                                                                                                                                                                                                                                                                                                              |

|          | 4.3                                                                                                                                                                | Sector Write                                                                                                                                                                                                                                                                                                                                                                                             |

|          | 4.4<br>4.5                                                                                                                                                         | Format Sector                                                                                                                                                                                                                                                                                                                                                                                            |

|          | 4.5<br>4.6                                                                                                                                                         | Search Data                                                                                                                                                                                                                                                                                                                                                                                              |

|          | 4.0                                                                                                                                                                | Extended Data Handling                                                                                                                                                                                                                                                                                                                                                                                   |

|          | 4.7                                                                                                                                                                | Extended Data Handling22                                                                                                                                                                                                                                                                                                                                                                                 |

|          | -                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.       |                                                                                                                                                                    | ISTER ADDRESSES                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.       | 5.1                                                                                                                                                                | Memory Map23                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.       | 5.1<br>5.2                                                                                                                                                         | Memory Map                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.<br>6. | 5.1<br>5.2<br><b>BUF</b>                                                                                                                                           | Memory Map                                                                                                                                                                                                                                                                                                                                                                                               |

|          | 5.1<br>5.2<br>BUF<br>REG                                                                                                                                           | Memory Map                                                                                                                                                                                                                                                                                                                                                                                               |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1                                                                                                                      | Memory Map       23         WCS Worksheet       24         FER MANAGER/SCSI INTERFACE       25         ISTERS       25         SCSI Interrupt Status       25                                                                                                                                                                                                                                            |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2                                                                                                               | Memory Map       23         WCS Worksheet       24         FER MANAGER/SCSI INTERFACE       25         ISTERS       25         SCSI Interrupt Status       25         SCSI Interrupt Enable       26                                                                                                                                                                                                     |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3                                                                                                        | Memory Map       23         WCS Worksheet       24         FER MANAGER/SCSI INTERFACE       25         ISTERS       25         SCSI Interrupt Status       25         SCSI Interrupt Enable       26         SCSI Selection Control       27                                                                                                                                                             |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3<br>6.4                                                                                                 | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28                                                                                                                                                                                                                                                         |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3                                                                                                        | Memory Map       23         WCS Worksheet       24         FER MANAGER/SCSI INTERFACE       25         ISTERS       25         SCSI Interrupt Status       25         SCSI Interrupt Enable       26         SCSI Selection Control       27                                                                                                                                                             |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                                                          | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29SCSI Mode Control30                                                                                                                                                                                                                         |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6                                                                                   | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29                                                                                                                                                                                                                                            |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7                                                                            | Memory Map       23         WCS Worksheet       24         FER MANAGER/SCSI INTERFACE       15         ISTERS       25         SCSI Interrupt Status       25         SCSI Interrupt Enable       26         SCSI Selection Control       27         DMA Control       28         Buffer Size       29         SCSI Mode Control       30         SCSI Reset Control       30                            |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8                                                                     | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29SCSI Mode Control30SCSI Reset Control30SAH Read Address Pointer31                                                                                                                                                                           |

|          | 5.1<br>5.2<br><b>BUF REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9                                                                        | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29SCSI Mode Control30SCSI Reset Control30SAH Read Address Pointer315BH Read Address Pointer31                                                                                                                                                 |

|          | 5.1<br>5.2<br><b>BUF REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10                                                                | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29SCSI Mode Control30SCSI Reset Control30SAH Read Address Pointer315BH Read Address Pointer315CH Write Address Pointer31                                                                                                                      |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13                              | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29SCSI Mode Control30SCSI Reset Control30SAH Read Address Pointer315BH Read Address Pointer315DH Write Address Pointer315DH Write Address Pointer315EH SCSI Stop Pointer325FH SCSI Stop Pointer32                                             |

|          | 5.1<br>5.2<br><b>BUF REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12                                                | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29SCSI Mode Control30SCSI Reset Control30SAH Read Address Pointer315BH Read Address Pointer315DH Write Address Pointer315DH Write Address Pointer315EH SCSI Stop Pointer32                                                                    |

|          | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14                      | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29SCSI Mode Control30SCSI Reset Control30SAH Read Address Pointer315BH Read Address Pointer315DH Write Address Pointer315DH Write Address Pointer315EH SCSI Stop Pointer325FH SCSI Stop Pointer32                                             |

| 6.       | 5.1<br>5.2<br><b>BUF</b><br><b>REG</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14<br><b>FOR</b><br>7.1 | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29SCSI Mode Control30SCSI Reset Control30SCH Read Address Pointer315CH Write Address Pointer315CH Write Address Pointer315CH Write Address Pointer32SFH SCSI Stop Pointer32SCSI Info Phase Control33MATTER REGISTERS34Disk Interrupt Status34 |

| 6.       | 5.1<br>5.2<br><b>BUF</b><br>REG<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8<br>6.9<br>6.10<br>6.11<br>6.12<br>6.13<br>6.14<br><b>FOR</b>               | Memory Map23WCS Worksheet24FER MANAGER/SCSI INTERFACEISTERS25SCSI Interrupt Status25SCSI Interrupt Enable26SCSI Selection Control27DMA Control28Buffer Size29SCSI Mode Control30SCSI Reset Control30SCSI Reset Control30SCH Read Address Pointer315CH Write Address Pointer315CH Write Address Pointer315CH Write Address Pointer32SCSI Stop Pointer32SCSI Info Phase Control33MATTER REGISTERS34        |

| 35<br>35<br>36<br>37                                                                         |

|----------------------------------------------------------------------------------------------|

| 36                                                                                           |

|                                                                                              |

| 37                                                                                           |

|                                                                                              |

| 37                                                                                           |

| 37                                                                                           |

| 37                                                                                           |

| 37                                                                                           |

| 38                                                                                           |

| 39                                                                                           |

| 39                                                                                           |

| 40                                                                                           |

| 40                                                                                           |

| 41                                                                                           |

| 42                                                                                           |

| 42                                                                                           |

| 42                                                                                           |

| 43                                                                                           |

| 44                                                                                           |

| 44                                                                                           |

| 44                                                                                           |

| 45                                                                                           |

|                                                                                              |

| 45                                                                                           |

|                                                                                              |

| 47                                                                                           |

| 47<br>48                                                                                     |

| 47                                                                                           |

| 47<br>48                                                                                     |

| 47<br>48<br>50                                                                               |

| 47<br>48<br>50<br><b> 51</b>                                                                 |

| 47<br>48<br>50<br><b> 51</b><br>51<br>51                                                     |

| 47<br>48<br>50<br><b> 51</b><br>51<br>51                                                     |

| 47<br>48<br>50<br><b> 51</b><br>51<br>51<br>51                                               |

| 47<br>48<br>50<br><b></b> 51<br>51<br>51<br>51<br>51<br>51                                   |

| 47<br>48<br>50<br><b></b> 51<br>51<br>51<br>51<br><b></b> 51<br><b></b> 52                   |

| 47<br>48<br>50<br><b></b> 51<br>51<br>51<br>51<br><b></b> 51<br><b></b> 52<br>52             |

| 47<br>48<br>50<br><b></b> 51<br>51<br>51<br>51<br><b></b> 51<br><b></b> 52                   |

| 47<br>48<br>50<br><b></b> 51<br>51<br>51<br>51<br><b></b> 51<br><b></b> 52<br>52             |

| 47<br>48<br>50<br><b></b> 51<br>51<br>51<br>51<br><b></b> 51<br><b></b> 52<br>52<br>52<br>53 |

| 47<br>48<br>50<br><b></b> 51<br>51<br>51<br><b></b> 52<br>52<br>52<br>53<br><b></b> 66       |

| 47<br>48<br>50<br><b> 51</b><br>51<br>51<br>51<br>52<br>52<br>52<br>66<br>66                 |

| 47<br>48<br>50<br><b></b> 51<br>51<br>51<br><b></b> 52<br>52<br>52<br>53<br><b></b> 66       |

| 47<br>48<br>50<br><b> 51</b><br>51<br>51<br>51<br>52<br>52<br>52<br>66<br>66                 |

| 47<br>48<br>50<br><b> 51</b><br>51<br>51<br>51<br>52<br>52<br>52<br>66<br>66                 |

|                                                                                              |

## 1. PIN INFORMATION

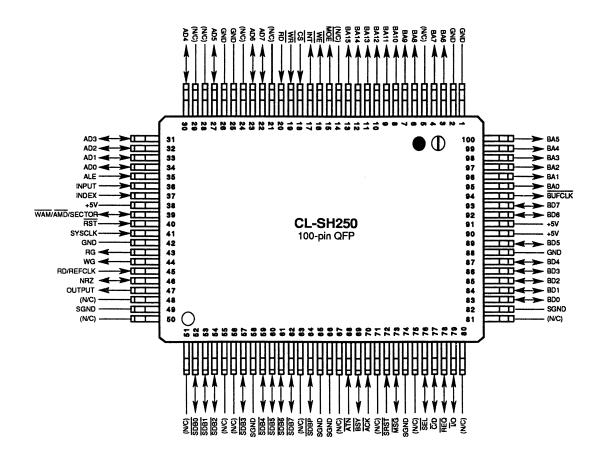

## 1.1 Pin Diagram for the 100-Pin Quad Flat Pack (QFP)

The CL-SH250 is available only in a 100-pin Quad Flat Pack (QFP). The package's pinouts diagram is shown below. All unused inputs must be tied to their inactive state to VCC or GND, respectively.

## 1.2 Pin Assignments

The following conventions are used on the pin assignment tables. An asterisk (\*) denotes a negative true signal. An (I) indicates an input pin. An (O) indicates an output pin. An input/output pin is indicated by (I/O). Open drain output pins are indicated by (OD). All unused inputs must be tied to their inactive state to VCC or GND, respectively.

| SYMBOL  | PIN NUMBER<br>QFP | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                 |

|---------|-------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BD7:0   | 83-87, 89, 92-93  | I/O  | <b>BUFFER MEMORY DATA BUS</b> : These eight signals are<br>Bits 0-7 of the 8-bit parallel data lines to/from the buffer<br>memory.                                                                                                                                                                                          |

| BUFCLK* | 94                | 0    | <b>BUFFER CLOCK:</b> This signal defines buffer memory access cycles. During disk access, this clock is derived from RD/REF CLK (Pin 45). Otherwise, it is derived from the SYSCLK input (Pin 41). The relationship of both these clocks to BUFCLK* is controlled by the contents of the CLOCK/SYNC CONTROL Register (7FH). |

| BA0:15  | 95-100, 3-4, 6-13 | 0    | <b>BUFFER MEMORY ADDRESS LINES</b> : These 16 signals provide up to 64K of buffer memory addressing capability.                                                                                                                                                                                                             |

| MOE*    | 15                | 0    | <b>MEMORY OUTPUT ENABLE</b> : This signal is asserted low when a buffer memory operation is active.                                                                                                                                                                                                                         |

| WE*     | 16                | 0    | <b>WRITE ENABLE</b> : This signal is asserted low when a buffer memory Write operation is active.                                                                                                                                                                                                                           |

### **BUFFER MEMORY INTERFACE PINS**

------

1.2 Pin Assignments (cont.)

## MICROCONTROLLER INTERFACE PINS

|        | PIN NUMBER       |       |                                                                                                                                                                                                    |

|--------|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL | QFP              | TYPE  | DESCRIPTION                                                                                                                                                                                        |

| INT*   | 17               | O, OD | <b>LOCAL MICROCONTROLLER INTERRUPT</b> : This signal is programmable for either push-pull or open-drain output circuitry.                                                                          |

| CS     | 18               |       | <b>CHIP SELECT</b> : This signal must be asserted to access the CL–SH250.                                                                                                                          |

| WR*    | 19               | I     | <b>WRITE</b> : When the WR* signal (Pin 19) is asserted low and the CHIP SELECT signal (Pin 18) is asserted high, the data on the Address/Data lines will be written in to the specified register. |

| RD*    | 20               | I     | <b>READ</b> : When the RD* signal (Pin 20) is asserted low and the CHIP SELECT signal (Pin 18) is asserted high, the data from the specified register is read on to the Address/Data lines.        |

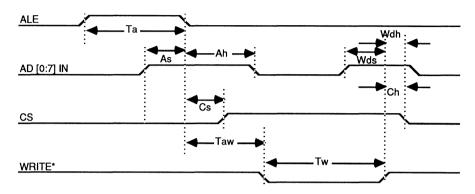

| AD7:0  | 22-23, 27, 30-34 | I/O   | <b>LOCAL MICROCONTROLLER ADDRESS / DATA</b> : These are tristate Address/Data lines which interface with a multiplexed microcontroller Address/Data bus.                                           |

| ALE    | 35               | I     | ADDRESS LATCH ENABLE: This control signal latches the address on the Address/Data lines on the falling edge of this signal.                                                                        |

## **1.2 Pin Assignments** (cont.)

\_\_\_\_\_

## MICROCONTROLLER INTERFACE PINS (cont.)

|        | PIN NUMBER |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL | QFP        | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RST*   | 40         | I    | <b>RESET:</b> Asserting this signal stops all operations within the chip and deasserts the READ GATE (Pin 43) and the WRITE GATE signals (Pin 44). All I/O signals are set to a high-impedance statethe BUFFER MEMORY DATA BUS (Pins 83-87, 89, 92-93), AD7:0 (Pins 22-23, 27, 30 34), the WAM*/AMD*/SECTOR signal (Pin 39), the NRZ signal (Pin 46), the SCSI DATA BUS (Pins 52-54, 57, 59-62), the SCSI DATA BUS PARITY signal (Pin 64), the SCSI BUSY signal (Pin 69), the SCSI MESSAGE signal (Pin 73), the SCSI SELECT signal (Pin 76), the SCSI COMMAND/DATA signal (Pin 77), the SCSI INPUT/OUTPUT signal (Pin 79), and the SCSI REQUEST signal (Pin 78). |

|        |            |      | When this signal is asserted low, the BUFFER MANAGER<br>RESET bit (Register 59H, Bit 0) and the FORMATTER<br>RESET bit of the ECC CONTROL (Register 71H, Bit 5) are<br>set, and the following bits are reset: the ALTERNATE<br>BRANCH SELECTION MODE ENABLE bit (Register 77H,<br>Bit 6), and Bits 0-6 of the DISK INTERRUPT STATUS<br>Register (41H/61H).                                                                                                                                                                                                                                                                                                       |

|        |            |      | Assertion of this signal resets the following registers: the<br>READ ADDRESS POINTER (RAP) Registers (5AH and<br>5BH), the WRITE ADDRESS POINTER (WAP) Registers<br>(5CH and 5DH), the SHADOW LATCH Register (4DH), the<br>WAM CONTROL Register (7BH), the SYNC PATTERN<br>Register (7CH), and the CLOCK/SYNC CONTROL Register<br>(7FH). When this signal is asserted low, the ECC STATUS<br>Registers (73H-76H) and the SCSI STOP POINTER<br>(Registers 5EH and 5FH) are set.                                                                                                                                                                                   |

.....

## DISK INTERFACE PINS

|                           | PIN NUMBER |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL                    | QFP        | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INPUT                     | 36         | I    | <b>INPUT PIN:</b> This signal is available to synchronize the Sector<br>Format Sequencer to an external event using a branch input<br>to the Sequencer. The state of this signal is sampled by<br>reading the SEQUENCER INPUT bit (Bit 4) of SCSI<br>INFORMATION PHASE CONTROL (Register 7EH).                                                                                                                                                                                                                                                                                                              |

| INDEX                     | 37         | I    | <b>INDEX</b> : This is input for the INDEX pulse received from the disk drive. The rising (leading) edge of the INDEX pulse sets the INDEX PAST bit (Bit 0) of the OPERATION CONTROL/STATUS Register (7AH).                                                                                                                                                                                                                                                                                                                                                                                                 |

| WAM* /<br>AMD*/<br>SECTOR | 39         | I/O  | WRITE ADDRESS MARK/ADDRESS MARK<br>DETECT/SECTOR: This pin can be configured to operate in<br>Hard or Soft Sector mode by initializing the<br>HARD/SOFT*SECTOR MODE CONTROL bit (Bit 7) of the<br>FORMATTER/BUFFER MANAGER MODE SELECTION<br>Register (77H). The default is Soft Sector mode. In Soft<br>Sector mode, when the READ GATE signal (Pin 43) is<br>asserted, a low-level input on this bit indicates Address Mark<br>detected. In Hard Sector mode, this is the input for the<br>SECTOR pulse. The rising (leading) edge of the SECTOR<br>pulse sets the SECTOR PAST bit (Register 7AH, Bit 1). |

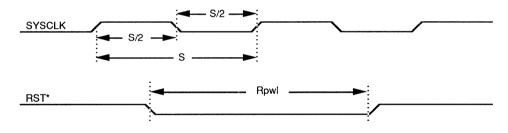

| SYSCLK                    | 41         | I    | SYSTEM CLOCK: This is a 2.5 to 24 MHz clock input which<br>is used to generate time slots for buffer memory access<br>when not reading or writing disk data. This is also used for<br>SCSI Arbitration and Reselection time constants.                                                                                                                                                                                                                                                                                                                                                                      |

| RG                        | 43         | 0    | <b>READ GATE</b> : This signal is asserted when the CL–SH250 is reading NRZ data from the disk interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WG                        | 44         | 0    | WRITE GATE: This signal is asserted when the CL–SH250 is writing NRZ data to the disk interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## **1.2 Pin Assignments** (cont.)

\_\_\_\_\_

DISK INTERFACE PINS (cont.)

|               | PIN NUMBER |      |                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYMBOL        | QFP        | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                       |

| RD/REF<br>CLK | 45         | 1    | <b>READ/REFERENCE CLOCK</b> : This is the primary clock for the chip and must be present at all times including during the Reset operation. It is used in conjunction with the the NRZ signal (Pin 46) to clock data in and out of the chip. Typically, it is sourced from the VFO Oscillator when the READ GATE signal (Pin 43) is asserted; otherwise, it is sourced from the Write Oscillator. |

| NRZ           | 46         | I/O  | <b>NRZ</b> : Read data input from the disk when the READ GATE signal (Pin 43) is asserted; write data output to the disk when the WRITE GATE signal (Pin 44) is asserted.                                                                                                                                                                                                                         |

| OUTPUT        | 47         | 0    | <b>OUTPUT PIN:</b> This signal is controlled by Bit 2 of the formatter sequencer's CONTROL FIELD (A0H thru BEH).                                                                                                                                                                                                                                                                                  |

## SCSI BUS PINS

| SYMBOL   | PIN NUMBER<br>QFP | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDB0*:7* | 52-54, 57, 59-62  | I/O,<br>OD** | SCSI DATA BUS: These eight signals are the parallel data lines to and from the SCSI bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SDBP*    | 64                | I/O,<br>OD** | SCSI DATA BUS PARITY: This signal indicates odd parity on the SCSI data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ATN*     | 68                | J            | SCSI ATTENTION: This signal indicates the ATTENTION condition on the SCSI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| BSY*     | 69                | I/O, OD      | <b>SCSI BUSY</b> : This signal indicates that the SCSI bus is being used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ACK*     | 70                | I            | SCSI ACKNOWLEDGE: When this signal is asserted low, it indicates that a SCSI Initiator has acknowledged the data transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SRST*    | 72                | 1            | SCSI RESET: This signal indicates the Reset condition on<br>the SCSI bus. When this signal is asserted low, the SCSI<br>BUSY signal (Pin 69) and the SCSI SELECT signal (Pin 76)<br>are not actively driven; the ARBITRATION bit (Register 52H,<br>Bit 0), the BUS OUTPUT ENABLE bit (Register 52H, Bit 3),<br>and the ENABLE TARGET bit (Register 53H, Bit 7) will be<br>reset. The SCSI DATA BUS (Pins 52-54, 57, 59-62), the<br>SCSI DATA BUS PARITY (Pin 64), the SCSI<br>INPUT/OUTPUT (Pin 79), the SCSI COMMAND/DATA (Pin<br>77), the SCSI MESSAGE (Pin 73), and the SCSI REQUEST<br>(Pin 78) signals also go to a high-impedance state. Bit 1 of<br>Register 52H will also be set. |

| MSG*     | 73                | 1/O,<br>OD** | SCSI MESSAGE: This signal indicates the SCSI Message phase on the SCSI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SEL*     | 76                | I/O, OD      | SCSI SELECT: This is a signal used by a SCSI Initiator to select a SCSI Target or by a SCSI Target to reselect a SCSI Initiator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| C*/D     | 77                | I/O,<br>OD** | SCSI COMMAND/DATA: This signal indicates whether<br>CONTROL (when low) or DATA (when high) information is<br>on the SCSI data bus signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| REQ*     | 78                | I/O,<br>OD** | SCSI REQUEST: This signal indicates that a request for a REQ/ACK data transfer handshake is on the SCSI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

SCSI BUS PINS (cont.)

| SYMBOL | PIN NUMBER<br>QFP | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                              |

|--------|-------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I*/O   | 79                | I/O,<br>OD** | SCSI INPUT/OUTPUT: This signal controls the direction of<br>data movement on the SCSI data bus signals with respect to<br>a SCSI Initiator. Low indicates information input to the SCSI<br>Initiator and high indicates output from the SCSI Initiator.<br>This signal is also used to distinguish between the SCSI<br>Selection and Reselection phases. |

OD\*\* The open-drain capability of these signals is programmable (see Register 58H, Bit 3).

## POWER AND GROUND PINS

| SYMBOL | PIN NUMBER<br>QFP                                                        | TYPE | DESCRIPTION          |  |

|--------|--------------------------------------------------------------------------|------|----------------------|--|

| +5V    | 38, 90-91                                                                | N/A  | POWER SUPPLY.        |  |

| GND    | 1-2, 25-26, 42, 88                                                       |      | GROUND.              |  |

| SGND   | 49, 58, 65-66, 74,<br>82                                                 | N/A  | HIGH CURRENT GROUND. |  |

| N/C    | 5, 14, 21,24, 28-<br>29, 48, 50, 51, 55-<br>56, 63, 67, 71, 75,<br>80-81 | N/A  | NO CONNECTION.       |  |

## 2. REGISTER TABLES

## 2.1 Buffer Manager and SCSI Interface Registers

| ADDRESS  | TYPE | DESCRIPTION/FUNCTION                |

|----------|------|-------------------------------------|

| 40H/60H  | R    | SCSI INTERRUPT STATUS               |

| 42H/62H  | R/W  | SCSI INTERRUPT ENABLE               |

| 52H      | R/W  | SCSI SELECTION CONTROL              |

| 53H      | R/W  | DMA CONTROL                         |

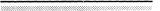

| 54H      | R/W  | BUFFER SIZE                         |

| 58H      | R/W  | SCSI MODE CONTROL REGISTER          |

| 59H      | R/W  | BUFFER MANAGER / SCSI RESET CONTROL |

| 5AH, 5BH | R/W  | READ ADDRESS POINTER (RAP)          |

| 5CH, 5DH | R/W  | WRITE ADDRESS POINTER (WAP)         |

| 5EH, 5FH | R/W  | SCSI STOP POINTER (SCSI-SP)         |

| 7EH      | R/W  | SCSI INFORMATION PHASE CONTROL      |

## 2.2 Disk Formatter Registers

| ADDRESS    | TYPE   | DESCRIPTION/FUNCTION                            |

|------------|--------|-------------------------------------------------|

| 41H/61H    | R      | DISK INTERRUPT STATUS                           |

| 43H/63H    | R/W    | DISK INTERRUPT ENABLE                           |

| 4DH        | R      | SHADOW LATCH                                    |

| 4EH        | R/W    | SECTOR SIZE                                     |

| 71H        | R/W    | ECC CONTROL                                     |

| 72H        | R/W    | ECC CORRECTION SHIFT-REGISTER / COUNTER         |

| 73H - 76H  | R      | ECC STATUS                                      |

| 77H        | R/W    | FORMATTER / BUFFER MANAGER MODE SELECTION       |

| 78H<br>78H | R<br>W | NEXT ACTIVE SEQUENCER ADDRESS<br>BRANCH ADDRESS |

| 79H        | R      | SEQUENCER STATUS                                |

| 79H        | W      | SEQUENCER START ADDRESS                         |

## 2. REGISTER TABLES (cont.)

\_\_\_\_\_

## 2.2 Disk Formatter Registers (cont.)

| ADDRESS    | TYPE   | DESCRIPTION/FUNCTION                       |  |

|------------|--------|--------------------------------------------|--|

| 7AH        | R/W    | OPERATION CONTROL / STATUS                 |  |

| 7BH        | R/W    | WAM CONTROL                                |  |

| 7CH        | R/W    | SYNC PATTERN                               |  |

| 7FH<br>7FH | R<br>W | FORMATTER STACK READ<br>CLOCK/SYNC CONTROL |  |

## 2.3 External Access Registers

| ADDRESS | TYPE | DESCRIPTION/FUNCTION |

|---------|------|----------------------|

| 50H     | R/W  | SCSI BUS ACCESS      |

| 70H     | R/W  | BUFFER MEMORY ACCESS |

## 2.4 Writable Control Store (WCS)

| ADDRESS | TYPE | DESCRIPTION/FUNCTION |

|---------|------|----------------------|

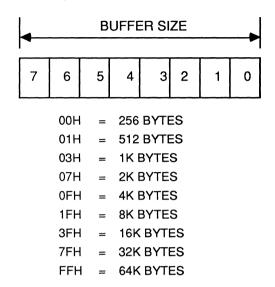

| 80H-9EH | R/W  | NEXT ADDRESS FIELD   |

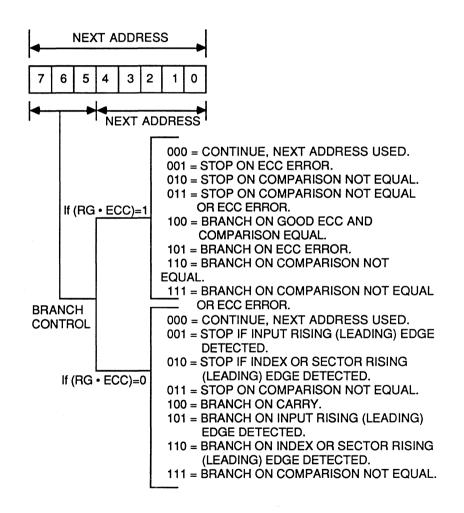

| A0H-BEH | R/W  | CONTROL FIELD        |

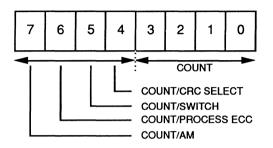

| C0H-DEH | R/W  | COUNT FIELD          |

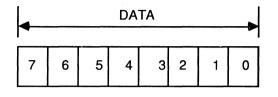

| E0H-FEH | R/W  | DATA FIELD           |

## 2.5 Sequencer Registers

| ADDRESS | TYPE | DESCRIPTION/FUNCTION   |

|---------|------|------------------------|

| 49H-4CH | R/W  | CURRENT SEQUENCER WORD |

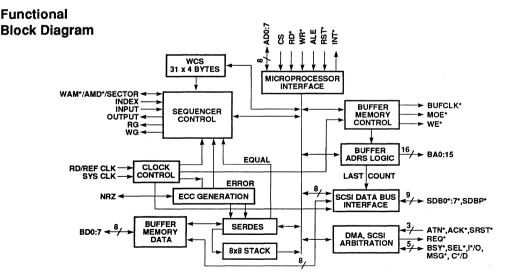

## 3. FUNCTIONAL DESCRIPTION

The CL-SH250 is designed to be used with a lowcost microcontroller, which allows it to maintain a "loose" synchronization with the real-time disk operation. The CL-SH250 maintains "close" synchronization with the data to and from the disk drive and provides the signals necessary to control this path. Using the CL-SH250 means a lower total part count for the intelligent disk drive design.

The CL-SH250 is divided into four major functional blocks:

- Microcontroller Interface

- Disk Formatter

- Buffer Memory Interface

- SCSI Bus Interface

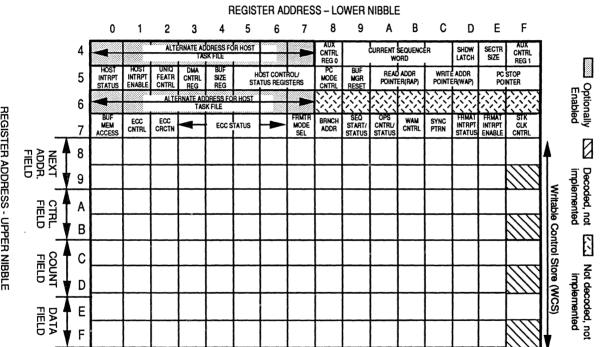

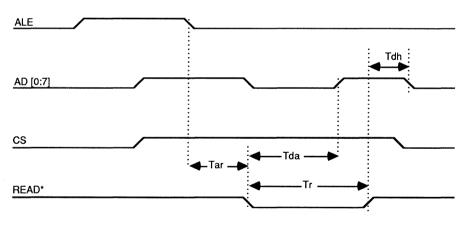

#### 3.1 Microcontroller Interface

The microcontroller interface is based on an eight-bit multiplexed address and data bus found on popular microcontrollers such as the Intel 8085/8031/8051 and the Motorola 68HC11.

The CL-SH250 decodes addresses from 40H to FFH. In order to prevent erroneous operations, the disk controller board design should reserve the decoding of addresses 40H to FFH for the CL-SH250 only. However, the CL-SH250 does not decode addresses 68H to 6FH. The decoding of addresses 40H-47H and 60H-67H can be totally disabled by resetting the INTERRUPT REGISTER ACCESS ENABLE bit (Register 77H, Bit 1). In that case, the CL-SH250 will not decode addresses 40H-47H and 60H-67H as well.

The CL-SH250 has a programmable interrupt circuit available. There are 13 interrupt sources available from both the Buffer Manager/SCSI Interface Registers and from the Formatter Registers, as shown in Tables 3.1 and 3.2:

CL-SH250 Data Sheet

#### Table 3.1 Buffer/SCSI Interrupt Sources

| SCSI DMA Done           | SCSI Arbitration Detected     |

|-------------------------|-------------------------------|

| SCSI Attention Detected | SCSI Selection Phase Detected |

| SCSI Parity Error       | SCSI Reset Detected           |

#### Table 3.2 Formatter Interrupt Sources

| Index Past        | Sector Past               |

|-------------------|---------------------------|

| Input Detected    | Data Transfer Detected    |

| ECC Error         | Sequencer Output Detected |

| Sequencer Stopped |                           |

The interrupt capability can be completely disabled (by resetting Register 77H, Bit 3), or the individual interrupt sources can be masked. Four interrupt registers provide the status and mask programmability for the interrupt sources. When the interrupt registers are enabled (Register 77H, Bit 1 is set), the four registers can be mapped to either 40H-43H or 60H-63H by programming the INTERRUPT REGISTER DEČODE SELECT bit (Register 77H, Bit 2). Mapping these registers into addresses 40H-43H will disable the CL-SH250 from decoding addresses 60H-67H (they can be used for external system usage). Mapping them into 60H-63H will make addresses 40H-47H available for external system usage. Even when the interrupts are disabled (Register 77H, Bit 3 is reset) if the access to the registers is enabled (Register 77H, Bit 1 is set), the Interrupt Status Registers may be used as a focal point for microcontroller control when the CL-SH250 is being used in a polled mode.

The CL-SH250 provides the microcontroller read access to external switch settings. The microcontroller accesses these switches by reading Register 70H, with the MOE\* DISABLE bit (Register 58H, Bit 1) set to a logical 1. The microcontroller-readable switches are connected to the buffer memory data bus. These switches must be installed with relatively high impedance pull-ups and pull-downs so that the resistor impedance does not affect buffer memory performance (it is recommended to use 270 K $\Omega$  pull-up and 27 K $\Omega$  pull-down and wait 25 µsec after the last buffer memory access for stability).

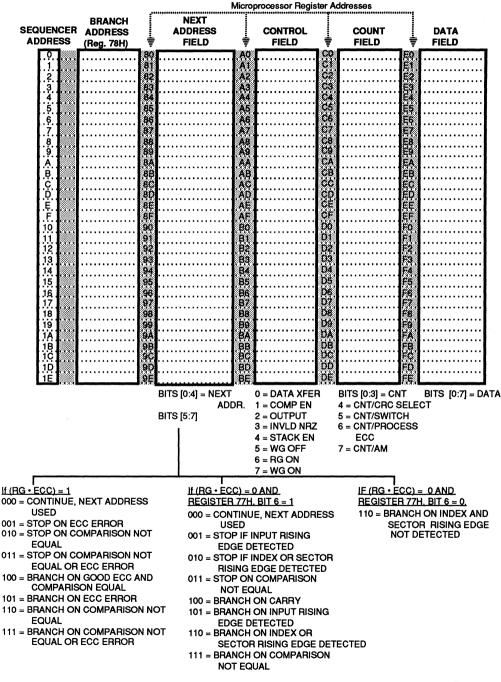

## 3.2 Disk Formatter

The basic operation of the Disk Formatter is controlled by the contents of the Sequencer Writable Control Store (WCS). A Sequencer program must be entered into the WCS before the CL-SH250 Disk Formatter can function properly. Under firmware control, the Disk Formatter can be made to sequence through different types of operations, such as: Read ID, Read ID and Read Data, Read ID and Write Data, and Write ID and Write Data.

The Sequencer controls the timing relationships between the disk interface output signals and monitors disk interface input lines to branch to different Sequencer locations. The track layout, such as gap lengths, sector size, and sector data fill character, can be flexibly defined in the WCS. The CL-SH250 Disk Formatter also has other registers that can be used to control the definition of the track format such as the SYNC character and the ADDRESS MARK.

The WCS consists of 124 bytes, organized as 31 words, each four bytes wide. The WCS word can be broken down into DATA, COUNT, NEXT ADDRESS and CONTROL FIELDS.

The DATA FIELD contains data which may be used to initialize the track format, including gap, ID field, and sector data fill characters. This data can also be compared to the NRZ data-in to identify various fields in a sector or to execute sector data compares.

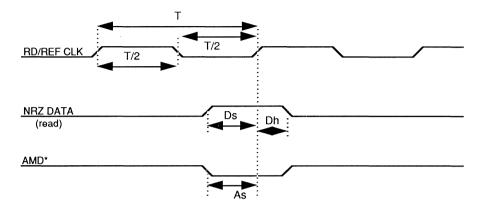

The COUNT FIELD specifies the initial value minus one of the Sequencer Counter for the current word. The Sequencer Counter is decremented once every eight READ/-REFERENCE CLOCK (RD/REF CLK) cycles. When the count reaches zero, the Sequencer will go to the next address.

The next address will be based on the contents of the NEXT ADDRESS FIELD of the WCS word unless a branch condition has been programmed and met during the last byte of the current WCS word. If a branch condition has been programmed and met, then the next address to be executed is based on the contents of the BRANCH AD-DRESS Register (78H). Thus, by programming different branch conditions which are based on external or internal events, the chip can be made to sequence through different operations.

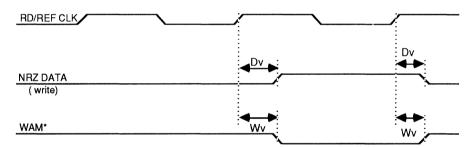

The CONTROL FIELD is used to generate and initiate all synchronous NRZ data handling operations.

The microcontroller's control of the Sequencer revolves around the SEQUENCER START ADDRESS (Register 79H) and the BRANCH ADDRESS (Register 78H). Writing to Register 79H loads the starting address (where the Sequencer is to begin execution), and causes the four bytes at that WCS word to be fetched and written into the Current Sequencer Word Registers (Registers 49H-4CH).

The serial data flow portion of the Disk Formatter consists of a CRC/ECC generator and a serializer/deserializer. Data to be written to the disk enters the CL-SH250 in a byte-wide format. It is serialized and run through a CRC/ECC generator. An NRZ serial bit stream is then shifted out to the disk drive. Note that the NRZ serial bit stream will include serialized constants required for address marks, gaps, and ID fields, as well as the serialized data and ECC generated output.

The CL-SH250 can be programmed (in the WCS COUNT FIELD) for the 16-bit CRC, or one of the ECC polynomials. It can also be fully suppressed to use external ECC circuitry.

The CL-SH250 can be configured for one of two ECC modes. After the RST\* signal (pin 40) is asserted, Register 77, bit 5 is reset (to a logic zero) and the 56-bit computer generated polynomial is selected. Also, the ECC circuitry (or linear feedback shift register) is initialized to all logic 1's before use.

When Register 77, bit 5 is set (to a logic 1), the 32-bit Fire Code polynomial is selected. Also, the ECC circuitry is initialized to all logic 0's before use.

The CRC polynomical used is the CCITT-CRC code:

$$X^{16} + X^{12} + X^5 + 1$$

.

The CL-SH250 provides the option of using an ECC polynomial by programming the COUNT FIELD of the appropriate WCS word. The forward and reverse 32-bit Fire Code polynomials are derived from the root polynomials

$$(X^{21}+1)$$

and  $(X^{11}+X^2+1)$

The forward 32-bit polynomial is:

$$x^{32} + x^{23} + x^{21} + x^{11} + x^{2} + 1$$

The reverse 32-bit polynomial is:

$$X^{32} + X^{30} + X^{21} + X^{11} + X^{9} + 1$$

The forward and reverse 56-bit ECC polynomial is a computer-generated code provided under license from Neal Glover of Data Systems Technology, Broomfield, CO. The forward 56-bit polynomial is:

$x^{56} + x^{52} + x^{50} + x^{43} + x^{41} + x^{34} + x^{30} + x^{26} + x^{24} + x^{8} + 1$

The reverse 56-bit polynomial is:

$x^{56} + x^{48} + x^{32} + x^{30} + x^{26} + x^{22} + x^{15} + x^{13} + x^6 + x^4 + 1$

This polynomial can detect single burst errors up to 56 bits in length, and double-burst errors, where the combination of bursts is less than or equal to 41 bits. This polynomial can also correct single-burst errors up to 23 bits in length. CL-SH250 Data Sheet

Data read from the disk enters the CL-SH250 as an NRZ serial bit stream. The input data stream is run through the ECC generator and deserialized into a byte-wide format. The syndrome is saved in the ECC registers and will not be reset until a new Read operation is started.

If an ECC error is detected after a Read Data operation, the microcontroller uses the information stored in Registers 71H - 76H to determine if the error is correctable and to calculate the error pattern and displacement from the beginning of the sector. After this, the error can be corrected in the data bytes in the buffer memory. The CL-SH250 has hardware assist circuitry to speed up the correction process.

During a read process from the device, the CL-SH250 also has the ability to compare the data being received on a byte-by-byte basis with information either from the DATA FIELD of the WCS (such as verifying the ID field) or from the external buffer memory (such as during a data field search operation).

The CL-SH250 also has a circular stack eight bytes deep. By enabling this (setting Bit 4 of the WCS CONTROL FIELD) during the Read operation, information read from the disk drive can be pushed onto the stack to be examined later at a lower speed by the microcontroller (Register 7FH). This capability can be used to pass the ID field to the microcontroller for defect management, seek verification and other disk controller tasks.

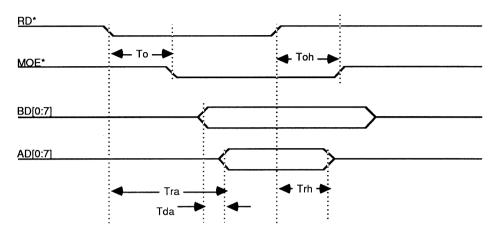

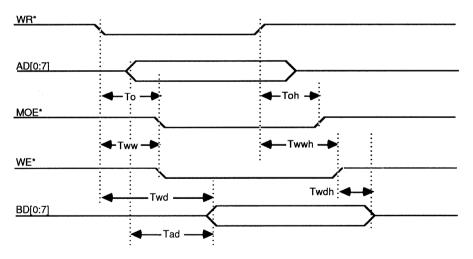

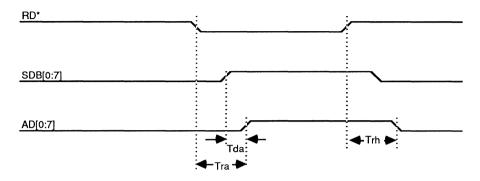

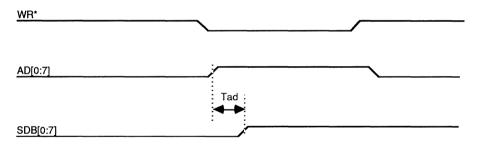

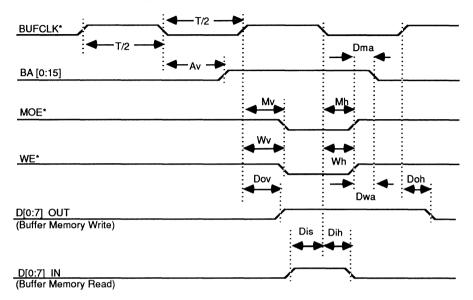

## 3.3 Buffer Memory Interface

Byte-wide data transferred by the CL-SH250 is passed to and from the buffer memory on the buffer memory data bus.

The CL-SH250 is capable of controlling buffer memory sizes up to 64K bytes of static RAM. The chip provides 16 buffer memory address lines (BA0 - BA15) along with a Memory-Output-Enable (MOE\*) signal (Pin 15), and a Write-Enable (WE\*) signal (Pin 16) for the static buffer memory.

# CL-SH250

## Data Sheet

One buffer memory cycle must be initiated for each byte transferred by the serializer/deserializer. The BUFCLK\* output (Pin 94) defines the buffer memory access cycles. There must be a minimum of two memory cycles per byte-serialization time (eight RD/REF CLK cycles) to maintain concurrent transfer between the disk and buffer memory, and between the host and buffer memory. Four memory cycles per byteserialization time allow more host accesses for each disk access of the buffer memory. The CL-SH250 is designed to take advantage of this burst speed for high SCSI throughput. The number of buffer memory access cycles (BUFCLK\* cycles) per byte-serialization time is programmed in Register 7FH, Bit 4. If this bit is set, there will be two BUFCLK\* cycles per byteserialization time. This is the Two Window Mode. If this bit is reset, then there will be four BUFCLK\* cycles per byte-serialization time. This is the Four Window Mode. If the CL-SH250 is not performing a data transfer operation, then the source of the BUFCLK\* output is the SYSTEM CLOCK (SYSCLK) input, which is divided per Register 7FH, Bits 6.7.